TM

Virtual Components for the Converging World

Amphion continues to expand its family of application-specific cores

1

See http://www.amphion.com for a current list of products

MPEG-4 Video Encoder

CS6701 Preliminary Product Brief

The CS6701 Simple Profile Video Encoder is designed for high performance interactive motion image

applications. The hybrid solution consists of optimized hardware and software components for low power and

low gate count applications with the full capabilities of the suite of MPEG-4 video compression tools. The CS6701

compresses input video to a ISO/IEC14496-2 Simple Profile compliant stream (through levels 0 to 3).

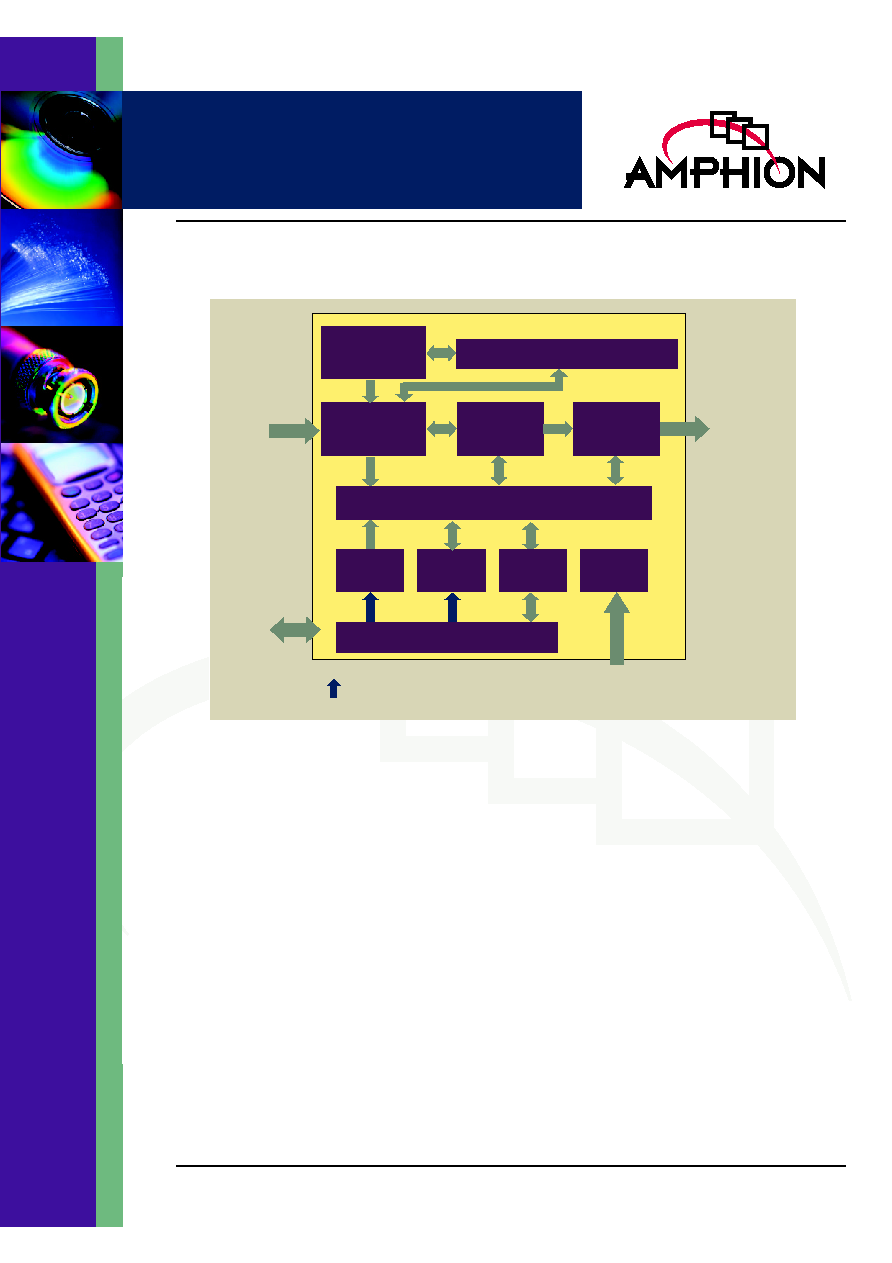

Figure 1: CS6701 System Overview

Motion

Estimation

Controller

Input Picture

Data

Output Video

Data Stream

Host Interface

Optional

MPEG-4 User

Defined Data

Optional

Host

Interface

Reset only

Video Input

Pre-processing

Controller/Sequencer

Scratch

RAM

Program

RAM

Pixel

Compression

Bit stream

Packing

Frame RAM

Register

Interface

User Data

In

FEATURES

Full compliance with ISO/IEC14496-2 video

simple profile levels L0-L3 and thus baseline

H263

-

Typical resolution of QCIF to CIF

-

Real-time Encode typically at 15/30 FPS

Optional Pre-Processing

-

RGB to 4:2:0 YCbCr

-

CCIR656 input

Motion Estimation

-

+/- 16 Range for the Motion Vectors (Search

Window)

-

Integer and Half Pixel Accuracy

-

Unrestricted Motion Vectors

-

Up to 4 Motion vectors per macroblock

DCT and IDCT compatible with IEEE Std 1180-

1990

Quantization and Inverse Quantization Type 2

Accelerated Motion Compensation model

AC/DC Prediction

Rate Control including Variable and Constant

Bit Rate output

Programmable I-VOP refresh

Error Resilience tools

-

Automatic and specified packet formation with

Re-synchronization markers

-

RVLC and normal VLC

-

Data partitioning and Header extension codes

BENEFITS

Hybrid HW and SW solution requiring only

basic processor support

Low input clock rate requirement (Level 1

compliant at under 10MHz)

Silicon efficient (Sub 120K gates)

Ultra Low power (Level 1 compliant at less

than 25mW)

Processor agnostic

ASIC and FPGA support

Flexible memory integration support for ease

of SoC integration

Scalable solution for best fit with end

application requirements

Sand-alone hardware accelerators available

3

TM

PRE-PROCESSOR HARDWARE BLOCK

The Video-input Pre-Processing block is an optional block

with several functions as follows:

∑

RGB to YCbCr Color Space Conversion

∑

Chroma sub-sampling to the required 4:2:0 format

∑

Noise pre-filtering

∑

Address mapping for storage of incoming data to the

Frame memory

MOTION ESTIMATION CONTROLLER

HARDWARE BLOCK

Motion Estimation Controller (MEC) has been heavily

optimized as the key cycle consuming part of the MPEG-4

Encoding process. The following is the feature list for the

MEC block:

∑

Upgradable Fast Search Algorithm - The accelerator

contains a micro-sequencer, which executes a small set

of compact instructions to implement a Search Algorithm.

Essentially the instructions are based around 'performing

the Block Matching Algorithm at a specified address in the

Search Window.' The base case Search Algorithm

offering is the 2D Logarithmic Search

∑

Sum of Absolute Differences (SAD) Block Matching

Algorithm

∑

+/- 16 Range for the Motion Vectors (Search Window)

∑

Integer and Half Pixel Accuracy

∑

Unrestricted Motion Vectors

∑

Single 16x16 and Four 8x8 Block Motion Vectors

Production

∑

Motion Vectors Absolute Differences produced for the

Matched Block

∑

Activity Figure for the Block

∑

Frame memory interface module, initial interface option

will be AMBA AHB compliant

∑

Motion compensation module that interfaces with the

back channel IQ/IDCT path of the pixel compression unit.

Inverse texture coded pixel difference blocks are

reconstructed with the original reference block used for

the original motion prediction and then stored back to the

frame memory. This module also handles not-coded and

pure intra coded blocks

PIXEL COMPRESSION HARDWARE

BLOCK

The pixel compression block is based on accelerated Amphion

DCT and IDCT blocks with the additional MPEG-4 compliant

processes of Quantization, ACDC prediction and Scanning.

∑

DCT and IDCT compatible with

IEEE Std 1180-1990

with

Continuous one symbol per cycle processing capability

∑

Quantization and Inverse Quantization

-

Method 2 with rate control selectable Quantization.

-

Automatic Luminance, Chrominance, Intra, Inter and

Short header mode handling

-

Hooks for upgrade path to method 1 Quantization that

comprises stream configurable matrices

∑

ACDC QP scaled prediction. Software API functions

control the predictor storage but all cycle consuming parts

of the algorithm are completed in Hardware

∑

The three permissible Scan types are auto selected from

ACDC prediction direction and applied as coefficients

leave block

∑

Full compliance with I

SO/IEC14496-2

section 7.4.2 Inverse

Scan, 7.4.4 Inverse Quantization and 7.4.5 IDCT (simple

profile)

∑

Memory mapped peripheral with simple busy flag control

for block processing

BIT STREAM PACKING HARDWARE

BLOCK

Hardware accelerator to enable full compliance with

ISO/IEC14496-2 sections 6 visual bit stream syntax and 7.4.1

variable length decoding simple profile

∑

Run length packing for texture coefficients from Pixel

compression block

∑

Huffman encoding including RVLC tables

∑

Register interface for VOP control parameters and

Macroblock type and motion vector information

∑

Bit stream packing to output buffer

∑

Automatic Resynchronization marker and packet header

insertion mode

∑

Running bit output count for rate control

∑

Buffer level indication

∑

Byte Port output

EMBEDDED SOFTWARE CONTROL

Optimized for a simple embedded controller, with minimal

processing and memory requirements, the remaining software

for the encoding process falls into the following categories.

∑

Hardware Sequencing

∑

Rate Control

-

Adaptive Quantization Parameter control based on

matching the actual bits to the target bits per frame

-

A Quantization Parameter is determined for each

frame and the spatial activity of the macroblock deter-

mines deviancies from this parameter within the frame

∑

Error Resilience

∑

VOP control parameters for the bit stream out

∑

ACDC predictor access and setting

∑

Multiple objects control

The embedded controller carries out the control functions that

are inefficient to complete in hardware, and provides

flexibility and scalability to the solution. It is anticipated that

the software can be upgraded to include new MPEG-4 tools,

or integrated with audio and system tools or indeed to

introduce proprietary video compression techniques such as

pre-processing.

CS6701

MPEG-4 Video Encoder

TM

Virtual Components for the Converging World

CORPORATE HEADQUARTERS

Amphion Semiconductor Ltd

50 Malone Road

Belfast BT9 5BS

Northern Ireland, UK

Tel:

+44.28.9050.4000

Fax: +44.28.9050.4001

EUROPEAN SALES

Amphion Semiconductor Ltd

CBXII, West Wing

382-390 Midsummer Boulevard

Central Milton Keynes

MK9 2RG England, UK

Tel:

+44 1908 847109

Fax:

+44 1908 847580

WORLDWIDE SALES & MARKETING

Amphion Semiconductor, Inc

2001 Gateway Place, Suite 130W

San Jose, CA 95110

Tel:

(408) 441 1248

Fax:

(408) 441 1239

CANADA & EAST COAST US SALES

Amphion Semiconductor, Inc

Montreal

Quebec

Canada

Tel:

(450) 455 5544

Fax:

(450) 455 5543

Web: www.amphion.com

Email: info@amphion.com

© 2002 Amphion Semiconductor Ltd. All rights reserved.

Amphion, the Amphion logo,"Virtual Components for the Converging World", are trademarks of Amphion Semiconductor Ltd. All others are the property of their

respective owners.

4

04/02 Publication #: PB6701 v1.1

ABOUT AMPHION

Amphion (formerly Integrated

Silicon Systems) is the leading

supplier of speech coding,

video/image processing and

channel coding application specific

silicon cores for system-on-a-chip

(SoC) solutions in the broadband,

wireless, and mulitmedia markets

SALES AGENTS

SPS-DA PTE LTD

21 Science Park Rd

#03-19 The Aquarius

Singapore Science P ark II

Singapore 117628

T el:

+65 774 9070

Fax:

+65 774 9071

SPINNAKER SYSTEMS INC

Hatchobori SF Bldg. 5F 3-12-8

Hatchobori, Chuo-ku

T oky o 104-0033 Japan

Tel:

+81 3 3551 2275

Fax:

+81 3 3351 2614

V oy ageur T echnical Sales Inc

1 Rue Holiday

T our Est, Suite 501

P oint Claire, Quebec

Canada H9R 5N3

T el:

(905) 672 0361

Fax:

(905) 677 4986

JASONTECH, INC

Hansang Building, Suite 300

Bangyidong 181-3, Songpaku

Seoul Korea 138-050

T el:

+82 2 420 6700

Fax:

+82 2 420 8600

Phoenix T echnologies Ltd

3 Gavish Street

Kfar -Saba, 44424

Israel

T el:

+972 9 7644 800

Fax:

+972 9 7644 801