Clock Generator with VCXO

CY241V08A-12

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

,

CA 95134

∑

408-943-2600

Document #: 38-07676 Rev. **

Revised June 02, 2004

Features

∑ Integrated phase-locked loop (PLL)

∑ Low-jitter, high-accuracy outputs

∑ VCXO with analog adjust

∑ 3.3V operation

Benefits

∑ Highest-performance PLL tailored for multimedia

applications

∑ Meets critical timing requirements in complex system

designs

∑ Application compatibility for a wide variety of designs

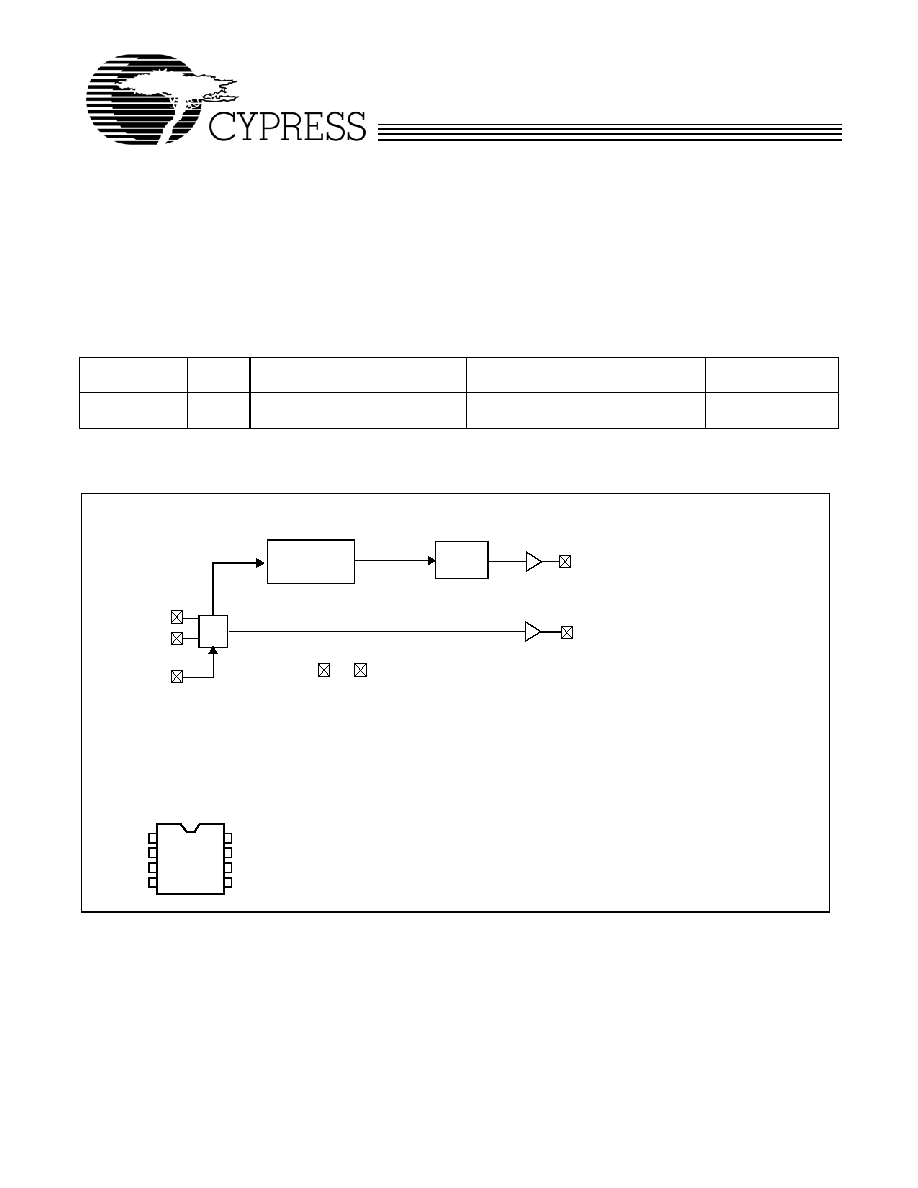

Frequency Table

Part Number

Outputs

Input Frequency Range

Output Frequencies

VCXO Control

Curve

CY241V08A-12

2

27-MHz pullable crystal input per

Cypress specification

One copy of 27 MHz

One copy of 74.25 MHz

linear

27

XIN

XOUT

OSC

VCXO

VDD

VSS

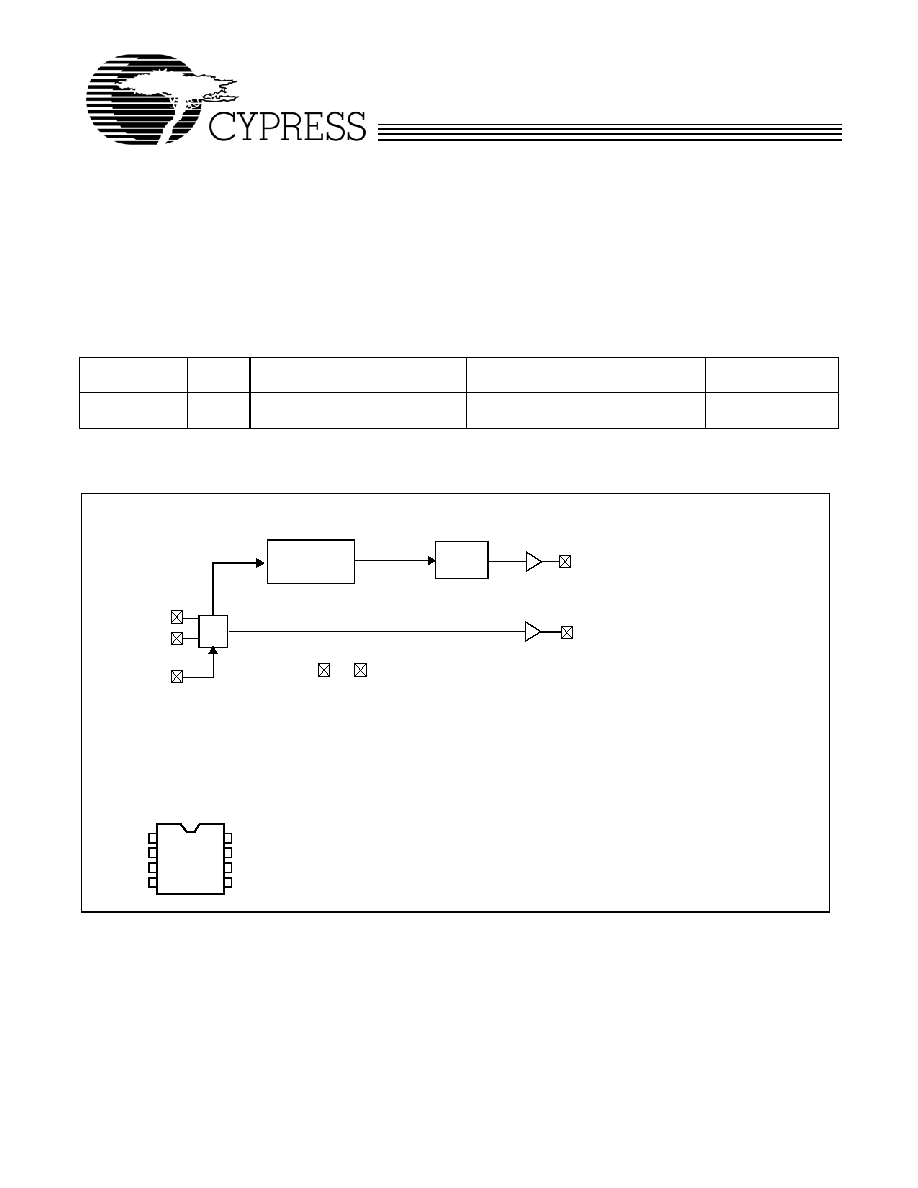

Block Diagram

8-pin SOIC

CY241V08A-12

1

2

3

4

XOUT

XIN

VCXO

XBUF/27 MHz

VSS

NC

74.25 MHz

5

6

7

8

VDD

Pin Configuration

OUTPUT

DIVIDER

PLL

74.25MHz

XBUF/27MHz

CY241V08A-12

Document #: 38-07676 Rev. **

Page 2 of 6

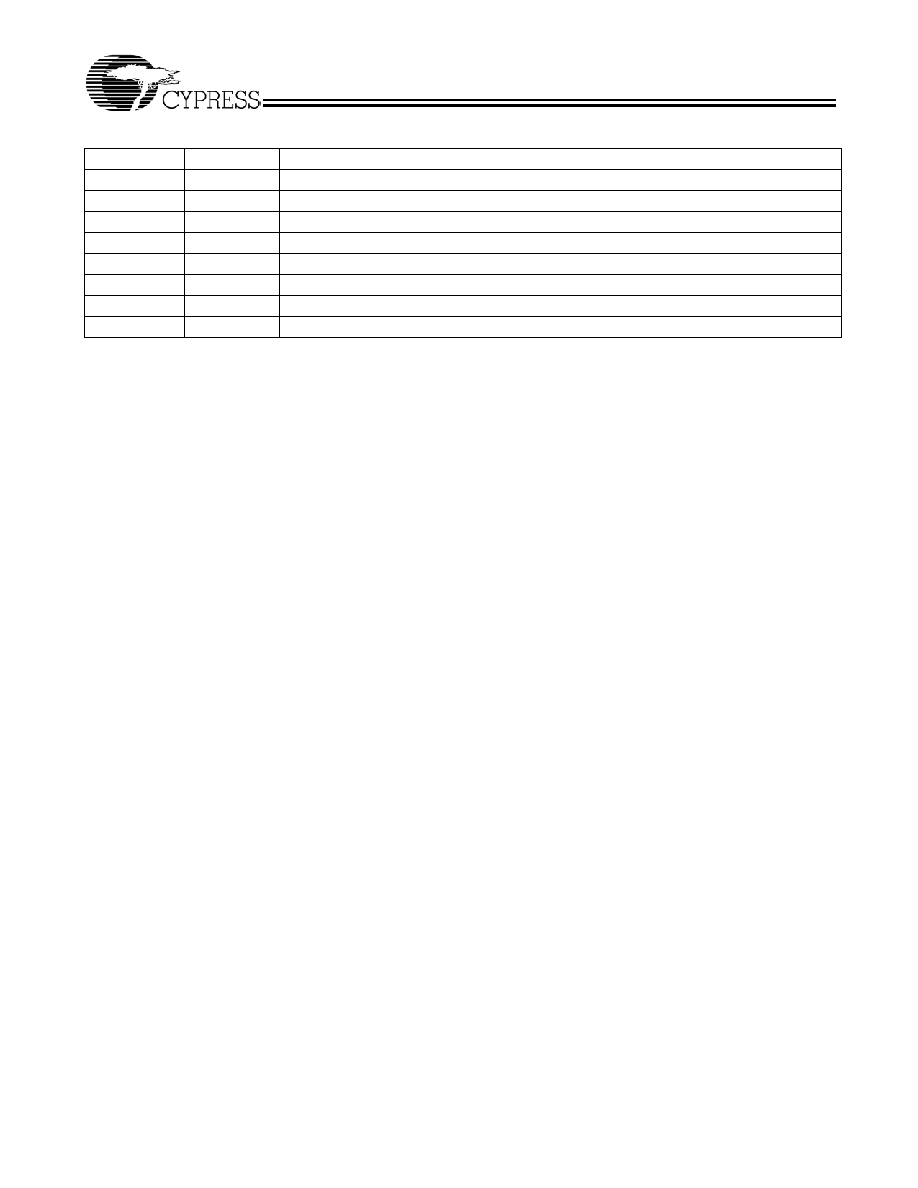

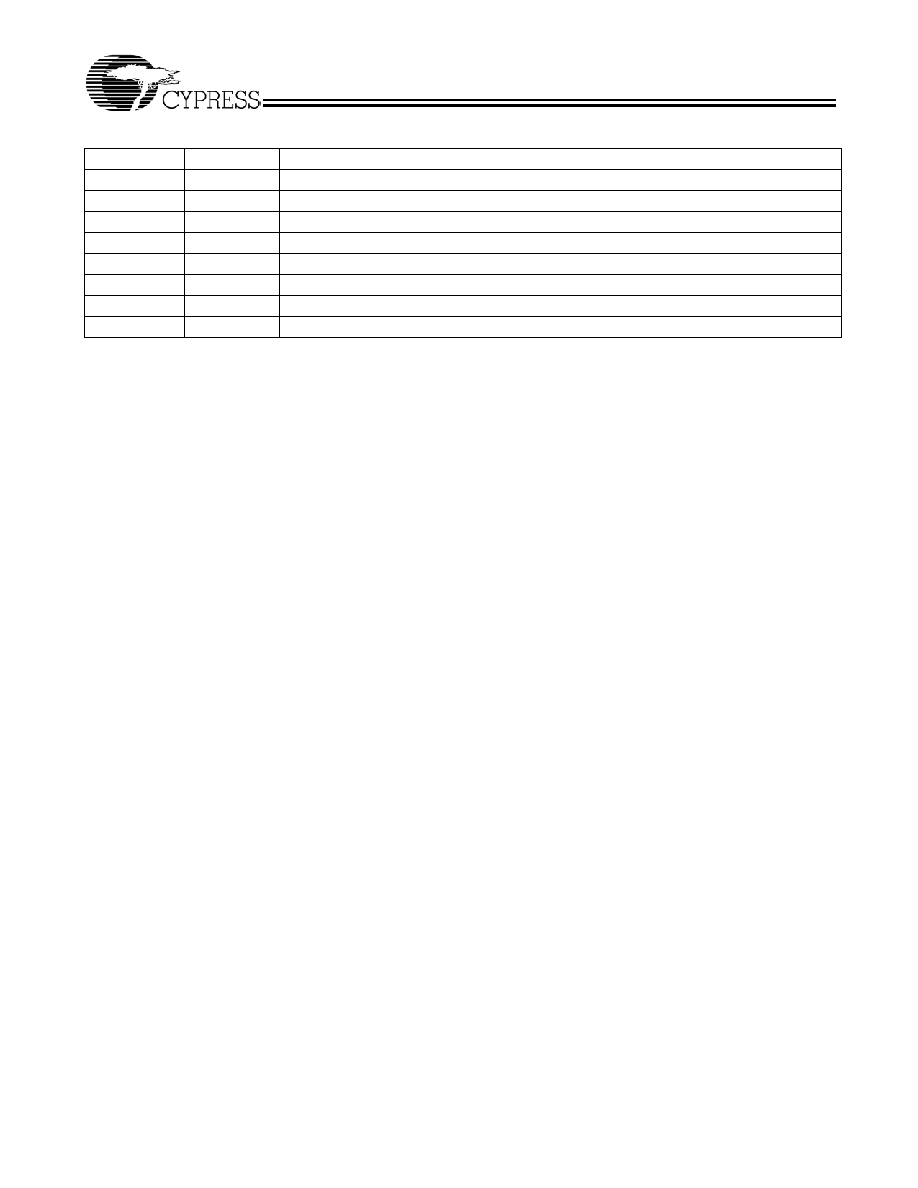

Pin Definitions

Name

Pin Number

Description

XIN

1

Reference crystal input.

VDD

2

Voltage supply.

VCXO

3

Input analog control for VCXO.

VSS

4

Ground.

XBUF/27 MHz 5

27 MHz buffered crystal output.

74.25 MHz

6

74.25 MHz clock output.

NC

7

No Connect.

XOUT

8

Reference crystal output.

CY241V08A-12

Document #: 38-07676 Rev. **

Page 3 of 6

Absolute Maximum Conditions

Supply Voltage (V

DD

) ........................................≠0.5 to +7.0V

DC Input Voltage...................................... ≠0.5V to V

DD

+ 0.5

Storage Temperature (Non-condensing).....≠55

∞C to +125∞C

Junction Temperature ................................ ≠40

∞C to +125∞C

Data Retention @ Tj = 125

∞C................................> 10 years

Package Power Dissipation...................................... 350 mW

ESD (Human Body Model) JESD22-A114-B ............ > 2000V

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

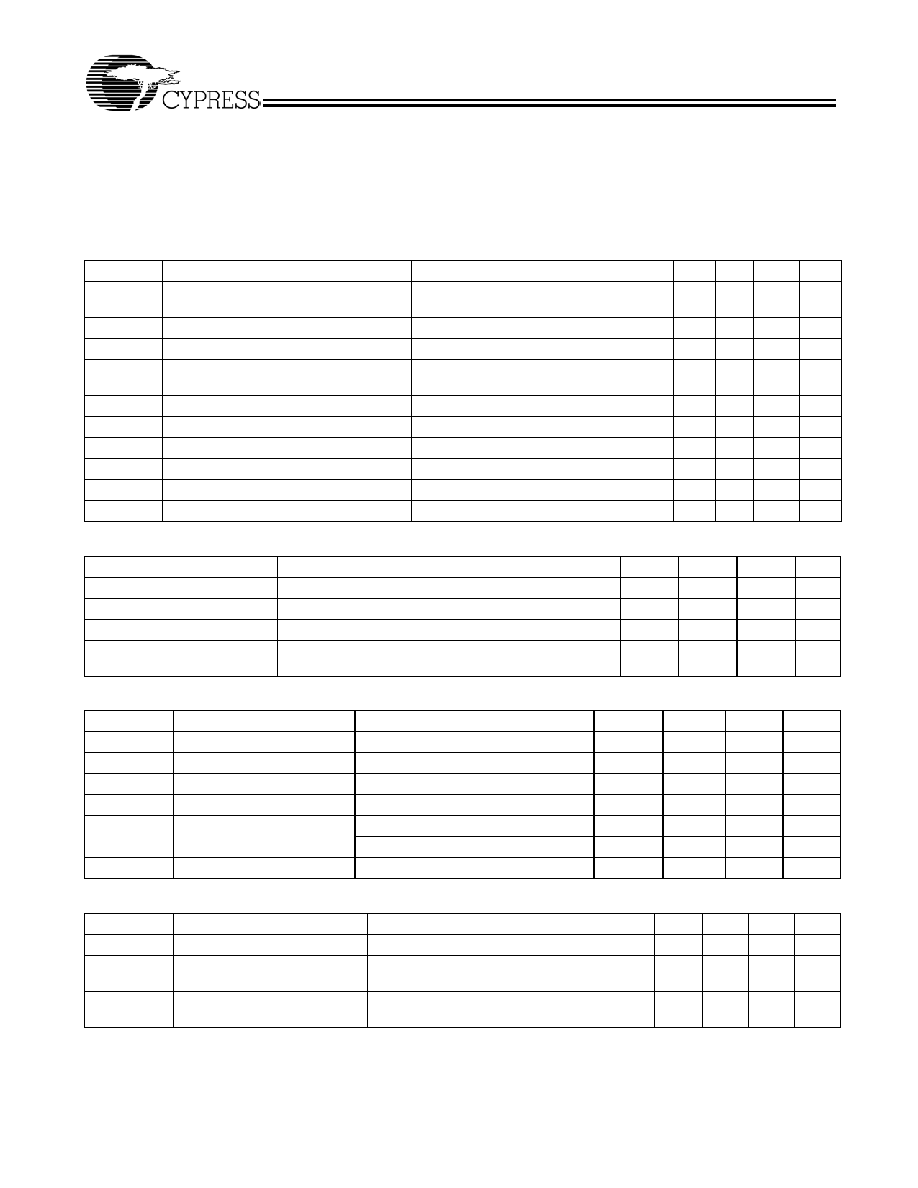

Pullable Crystal Specifications

[1]

Parameter

Description

Comments

Min. Typ. Max.

Unit

F

NOM

Nominal crystal frequency

Parallel resonance, fundamental mode, AT

cut

≠

27

≠

MHz

C

LNOM

Nominal load capacitance

≠

14

≠

pF

R

1

Equivalent series resistance (ESR)

Fundamental mode

≠

≠

25

R

3

/R

1

Ratio of third overtone mode ESR to

fundamental mode ESR

Ratio used because typical R

1

values are

much less than the maximum spec

3

≠

≠

≠

DL

Crystal drive level

No external series resistor assumed

150

≠

≠

µW

F

3SEPHI

Third overtone separation from 3*F

NOM

High side

300

≠

≠

ppm

F

3SEPLO

Third overtone separation from 3*F

NOM

Low side

≠

≠

≠150

ppm

C

0

Crystal shunt capacitance

≠

≠

7

pF

C

0

/C

1

Ratio of shunt to motional capacitance

180

≠

250

≠

C

1

Crystal motional capacitance

14.4

18

21.6

fF

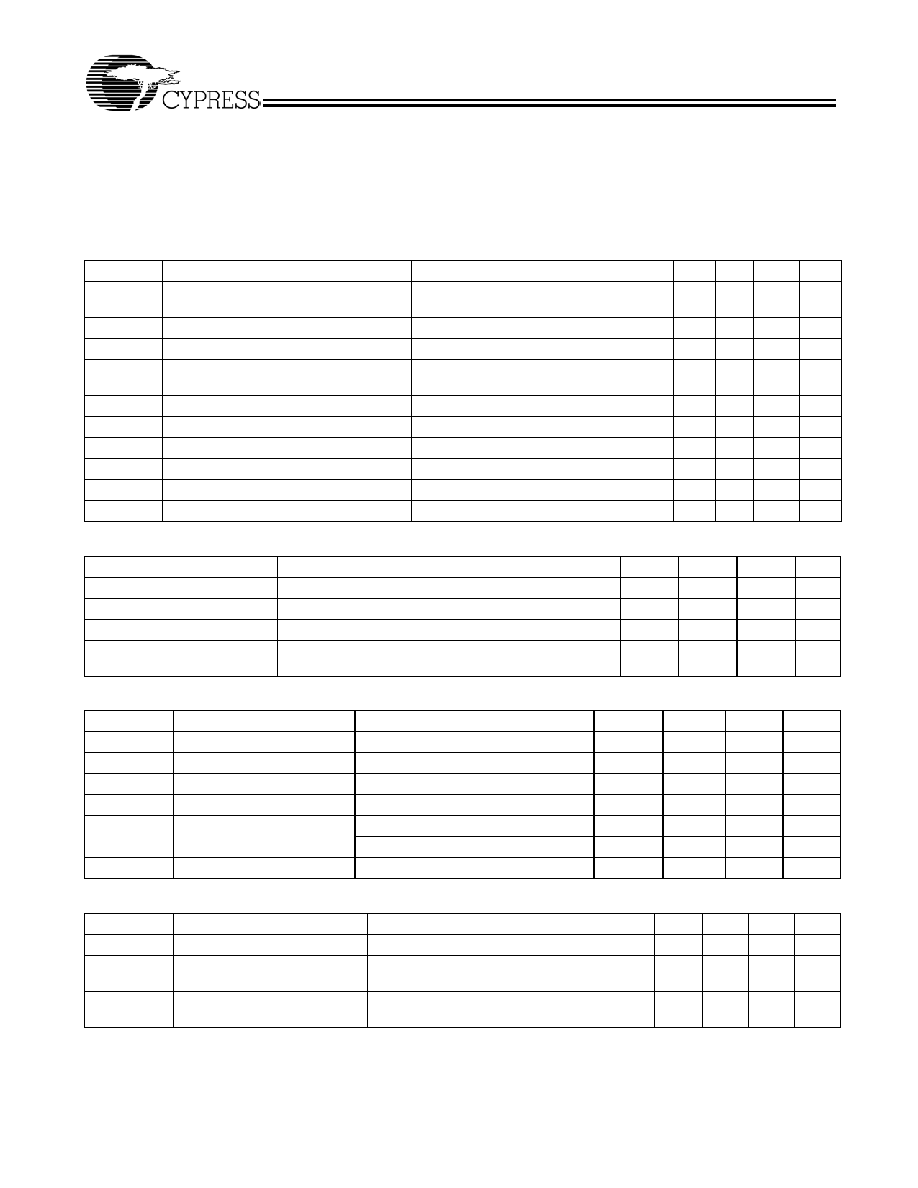

Recommended Operating Conditions

Parameter

Description

Min.

Typ.

Max.

Unit

V

DD

Operating Voltage

3.135

3.3

3.465

V

T

A

Ambient Temperature

0

≠

70

∞C

C

LOAD

Max. Load Capacitance

≠

≠

15

pF

t

PU

Power-up time for all V

DD

pins to reach minimum specified

voltage (power ramps must be monotonic)

0.05

≠

500

ms

DC Electrical Specifications

Parameter

Name

Description

Min.

Typ.

Max.

Unit

I

OH

Output HIGH Current

V

OH

= V

DD

≠ 0.5V, V

DD

= 3.3V

12

24

≠

mA

I

OL

Output LOW Current

V

OL

= 0.5V, V

DD

= 3.3V

12

24

≠

mA

C

IN

Input Capacitance

Except XIN, XOUT pins

≠

≠

7

pF

V

VCXO

VCXO Input Range

0

≠

V

DD

V

f

XO

[2]

VCXO Pullability Range

Low Side

≠

≠

≠115

ppm

High Side

115

≠

≠

ppm

I

VDD

Supply Current

≠

≠

40

mA

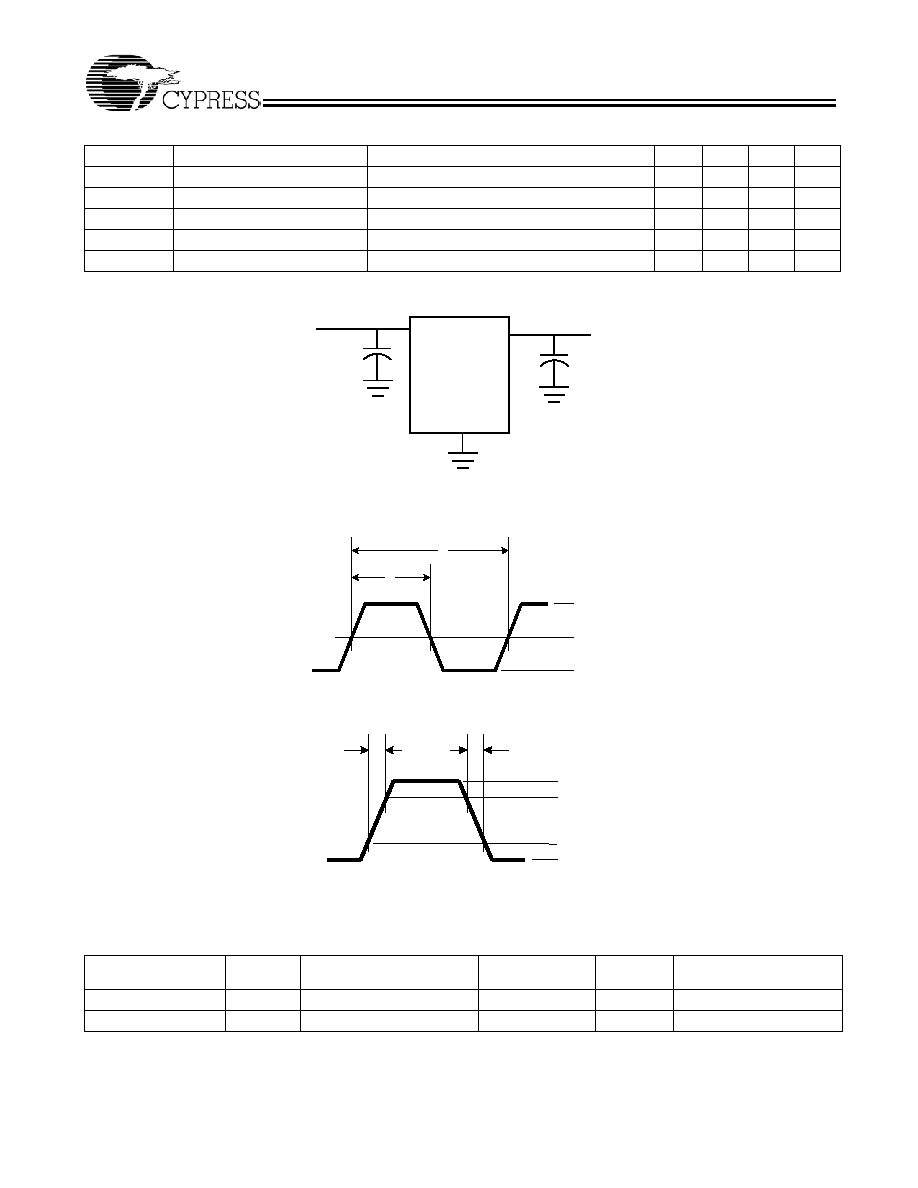

AC Electrical Specifications

(V

DD

= 3.3V)

[3]

Parameter

[3]

Name

Description

Min.

Typ.

Max.

Unit

DC

Output Duty Cycle

Duty Cycle is defined in Figure 1, 50% of V

DD

45

50

55

%

ER

Rising Edge Rate

Output Clock Edge Rate, Measured from 20%

to 80% of V

DD

, C

LOAD

= 15 pF. See Figure 2.

0.8

1.4

≠

V/ns

EF

Falling Edge Rate

Output Clock Edge Rate, Measured from 80%

to 20% of V

DD

, C

LOAD

= 15 pF. See Figure 2.

0.8

1.4

≠

V/ns

Notes:

1.

Crystals that meet this specification includes: Ecliptek ECX-5808-27.000M

2.

≠115/+115 ppm assumes 2.5 pF of additional board level load capacitance. This range will be shifted down with more board capacitance or shifted up with less

board capacitance.

3.

Not 100% tested.

CY241V08A-12

Document #: 38-07676 Rev. **

Page 4 of 6

Voltage and Timing Definitions

t

9

Clock Jitter 74.25 MHz

Peak-to-peak period jitter

≠

150

≠

ps

t

9

Clock Jitter XBUF/27 MHz

Peak-to-peak period jitter

≠

250

≠

ps

t

9

Clock Jitter 74.25 MHz

1000-cycle long term jitter

≠

430

≠

ps

t

9

Clock Jitter XBUF/27 MHz

1000-cycle long term jitter

≠

270

≠

ps

t

10

PLL Lock Time

≠

≠

3

ms

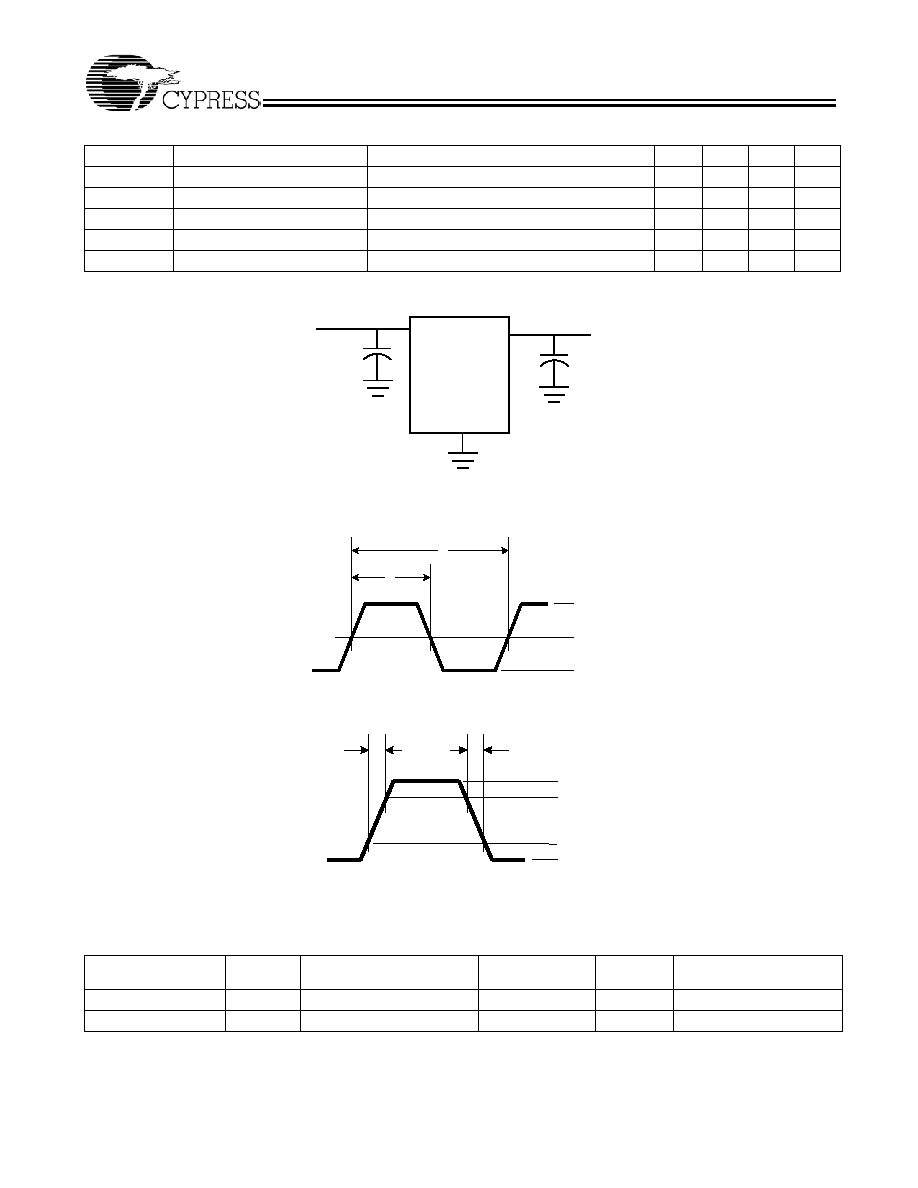

Test and Measurement Set-up

AC Electrical Specifications

(V

DD

= 3.3V) (continued)

[3]

Parameter

[3]

Name

Description

Min.

Typ.

Max.

Unit

0.1

µF

VDD

Outputs

C

LOAD

GND

DUT

Ordering Information

Ordering Code

Package

Name

Package Type

Operating Range

Operating

Voltage

Features

CY241V8ASXC-12

SZ08

8-pin SOIC

Commercial

3.3V

Linear VCXO control curve

CY241V8ASXC-12T

SZ08

8-pin SOIC ≠ Tape and Reel Commercial

3.3V

Linear VCXO control curve

Clock

Output

V

DD

50% of V

DD

0V

t

1

t

2

Figure 1. Duty Cycle Definition

Clock

Output

t

3

t

4

V

DD

80% of V

DD

20% of V

DD

0V

Figure 2. ER = (0.6 x V

DD

) /t3, EF = (0.6 x V

DD

) /t4

CY241V08A-12

Document #: 38-07676 Rev. **

Page 5 of 6

© Cypress Semiconductor Corporation, 2004. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be

used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

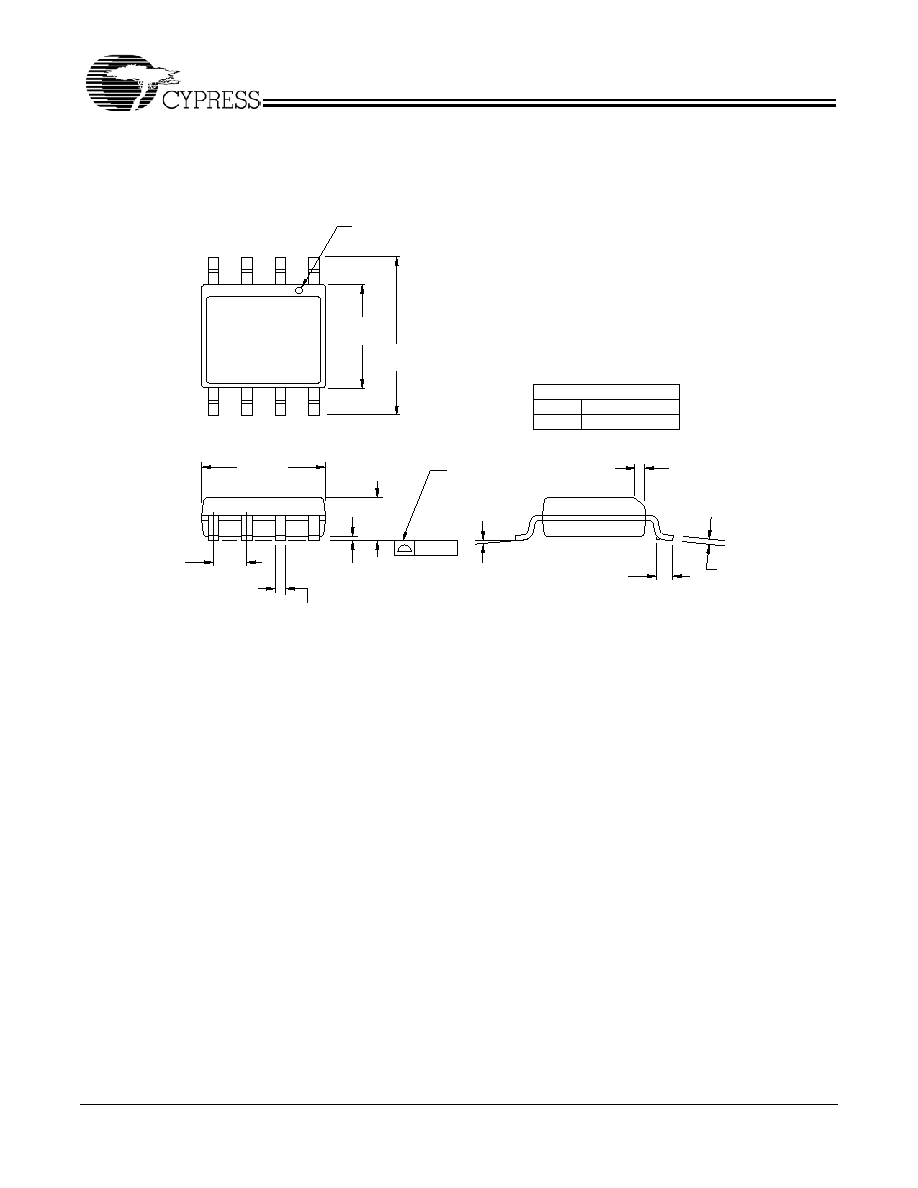

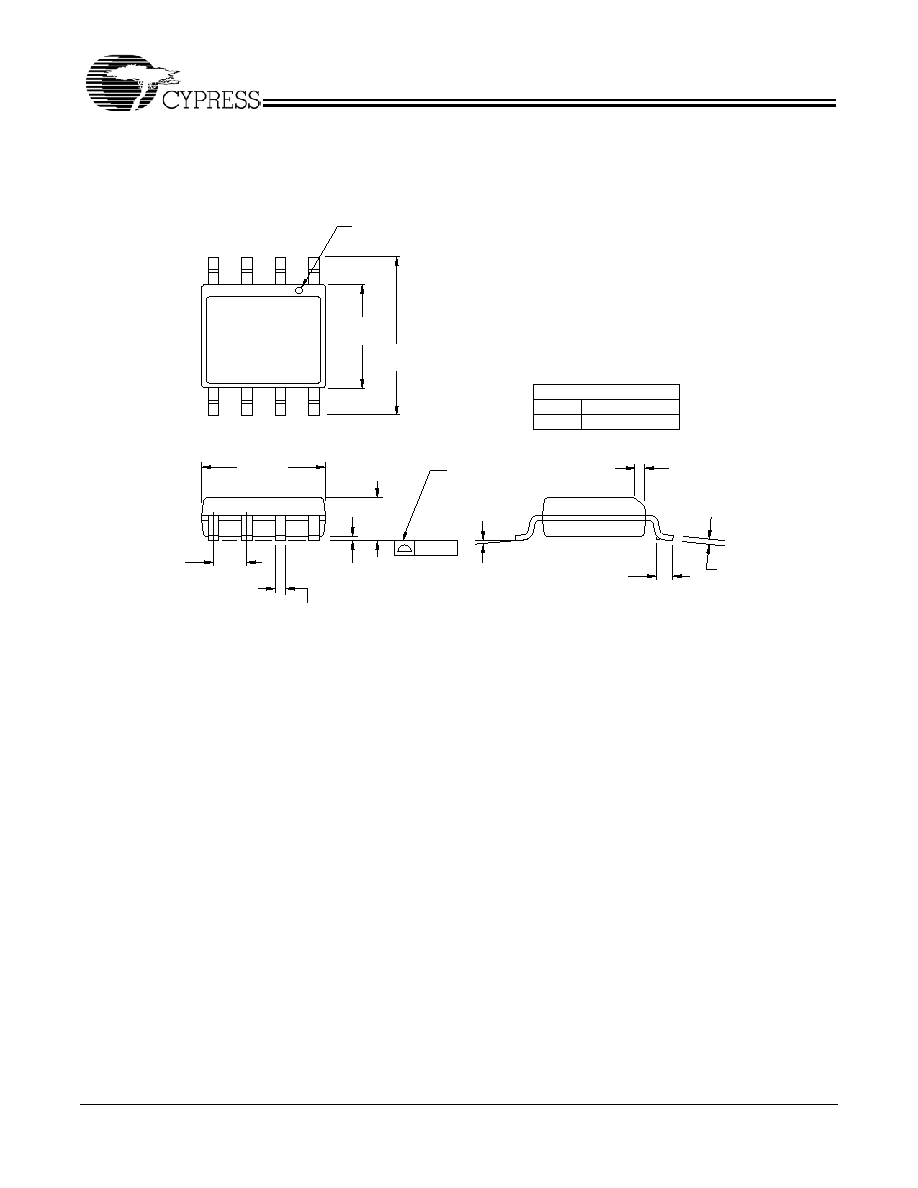

Package Drawing and Dimensions

All product or company names mentioned in this document may be the trademarks of their respective holders.

SEATING PLANE

PIN 1 ID

0.230[5.842]

0.244[6.197]

0.157[3.987]

0.150[3.810]

0.189[4.800]

0.196[4.978]

0.050[1.270]

BSC

0.061[1.549]

0.068[1.727]

0.004[0.102]

0.0098[0.249]

0.0138[0.350]

0.0192[0.487]

0.016[0.406]

0.035[0.889]

0.0075[0.190]

0.0098[0.249]

1. DIMENSIONS IN INCHES[MM] MIN.

MAX.

0∞~8∞

0.016[0.406]

0.010[0.254]

X 45∞

2. PIN 1 ID IS OPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

0.004[0.102]

8 Lead (150 Mil) SOIC - S08

1

4

5

8

3. REFERENCE JEDEC MS-012

PART #

S08.15 STANDARD PKG.

SZ08.15 LEAD FREE PKG.

4. PACKAGE WEIGHT 0.07gms

8-lead (150-Mil) SOIC S8

51-85066-*C