| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CY26118SC | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

19.6608-MHz Clock Generator

CY26118

PRELIMINARY

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

∑

CA 95134

∑

408-943-2600

Document #: 38-07274 Rev. *A

Revised December 14, 2001

025/0251

Features

Benefits

∑ Integrated phase-locked loop (PLL)

Highest-performance PLL tailored for multimedia applications

∑ Low-jitter, high-accuracy outputs

Meets critical timing requirements in complex system designs

∑ 3.3V operation

Part Number

Outputs

Input Frequency Range

Output Frequencies

CY26118

1

15.0000 MHz

19.6608 MHz

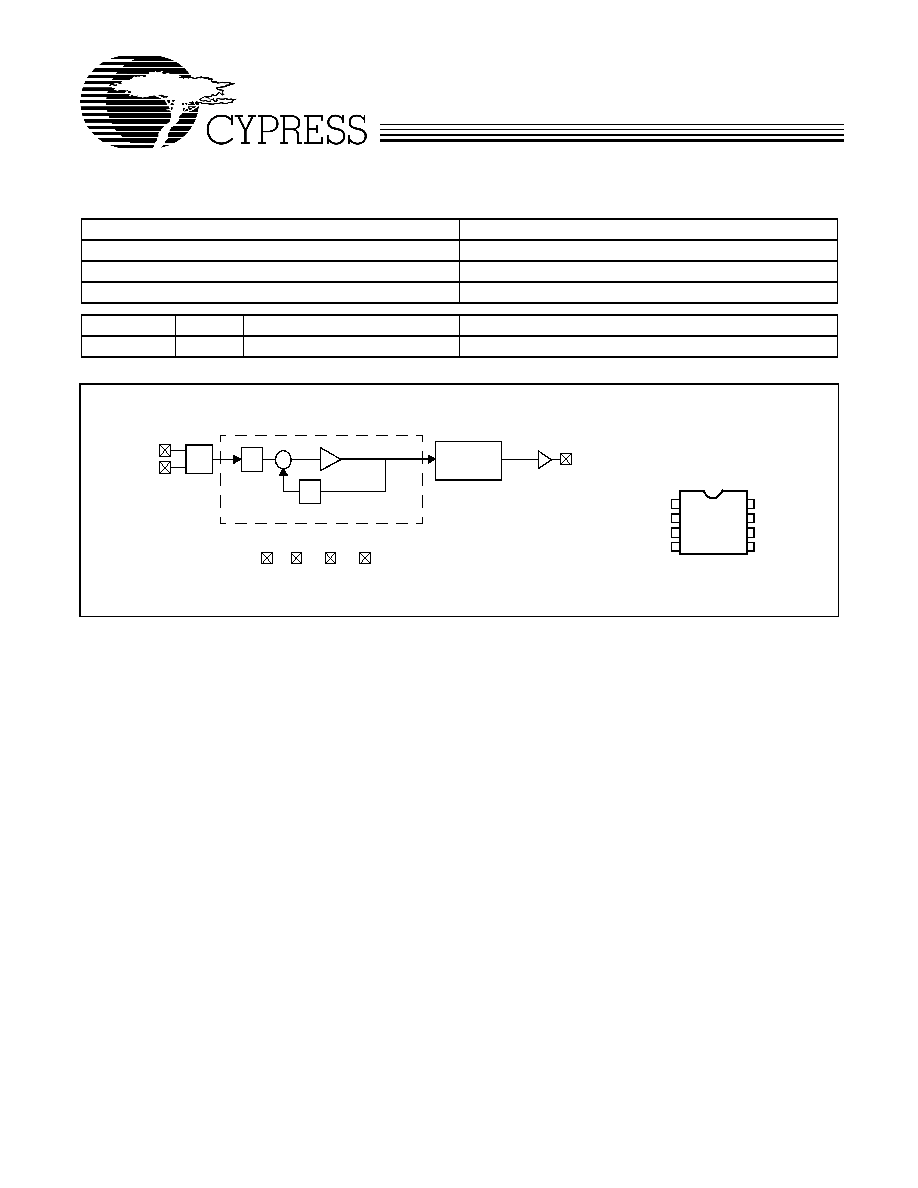

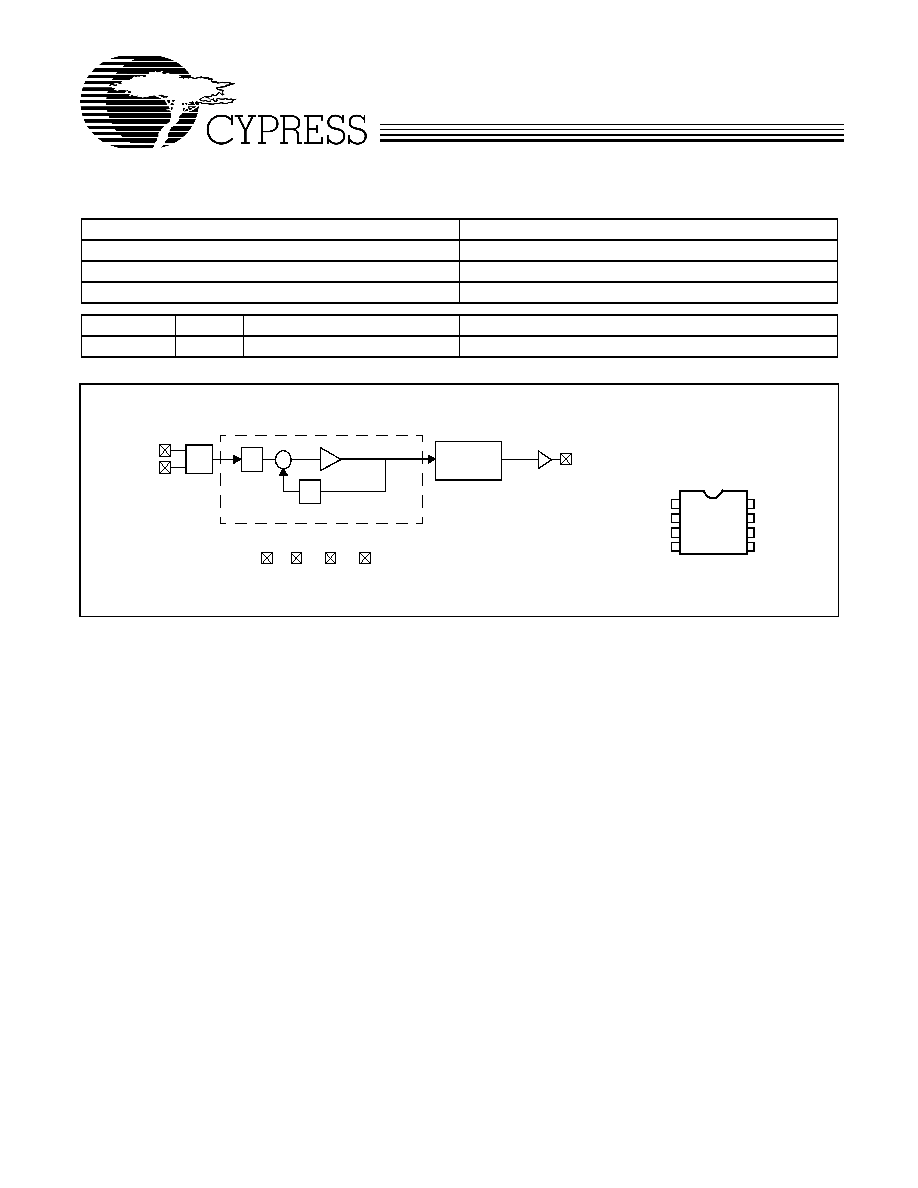

Logic Block Diagram

Pin Configuration

15.0000 XIN

XOUT

19.6608 MHz

OUTPUT

DIVIDER

PLL

OSC

Q

P

VCO

VDD

AVSS

AVDD

VSS

8-pin SOIC

CY26118

1

2

3

4

XOUT

XIN

N/C

19.6608 MHz

AVSS

VSS

VDD

5

6

7

8

AVDD

CY26118

PRELIMINARY

Document #: 38-07274 Rev. *A

Page 2 of 5

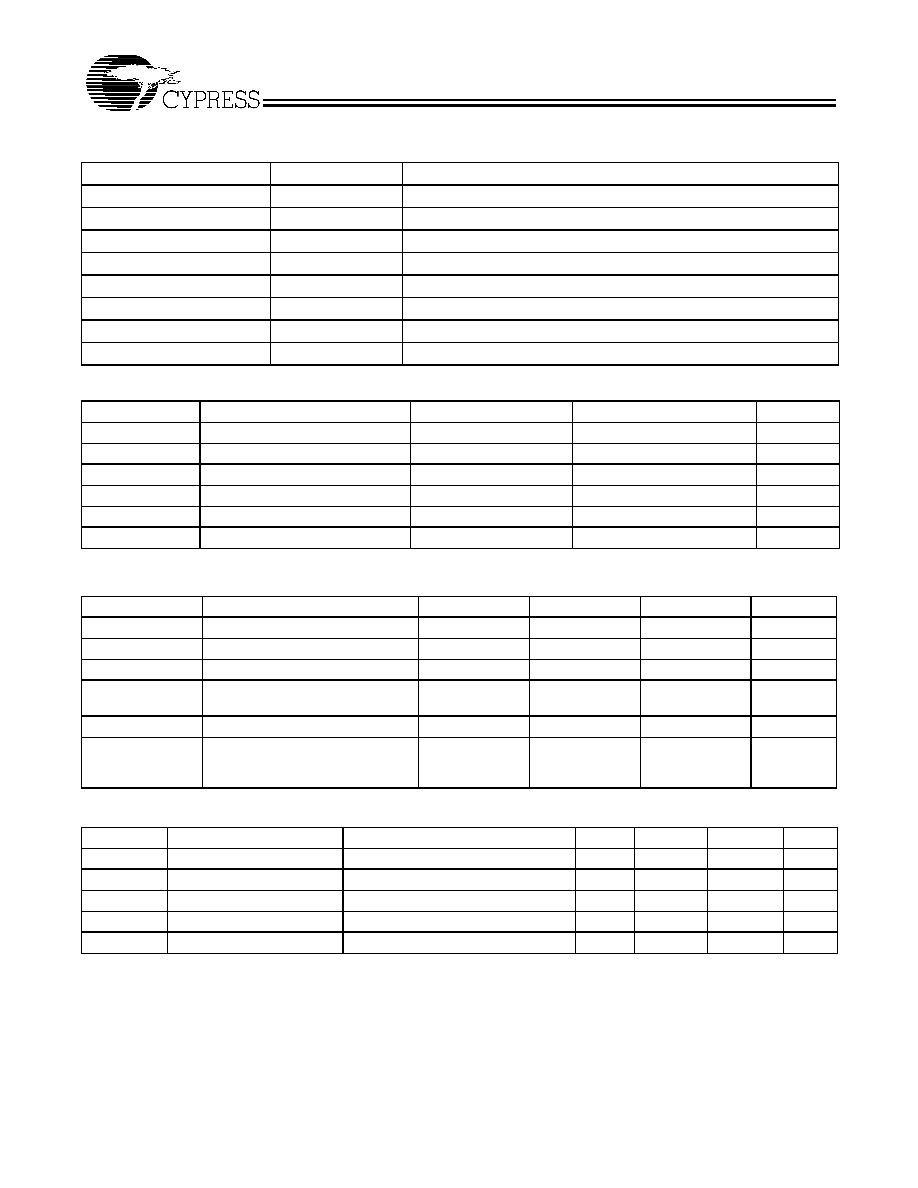

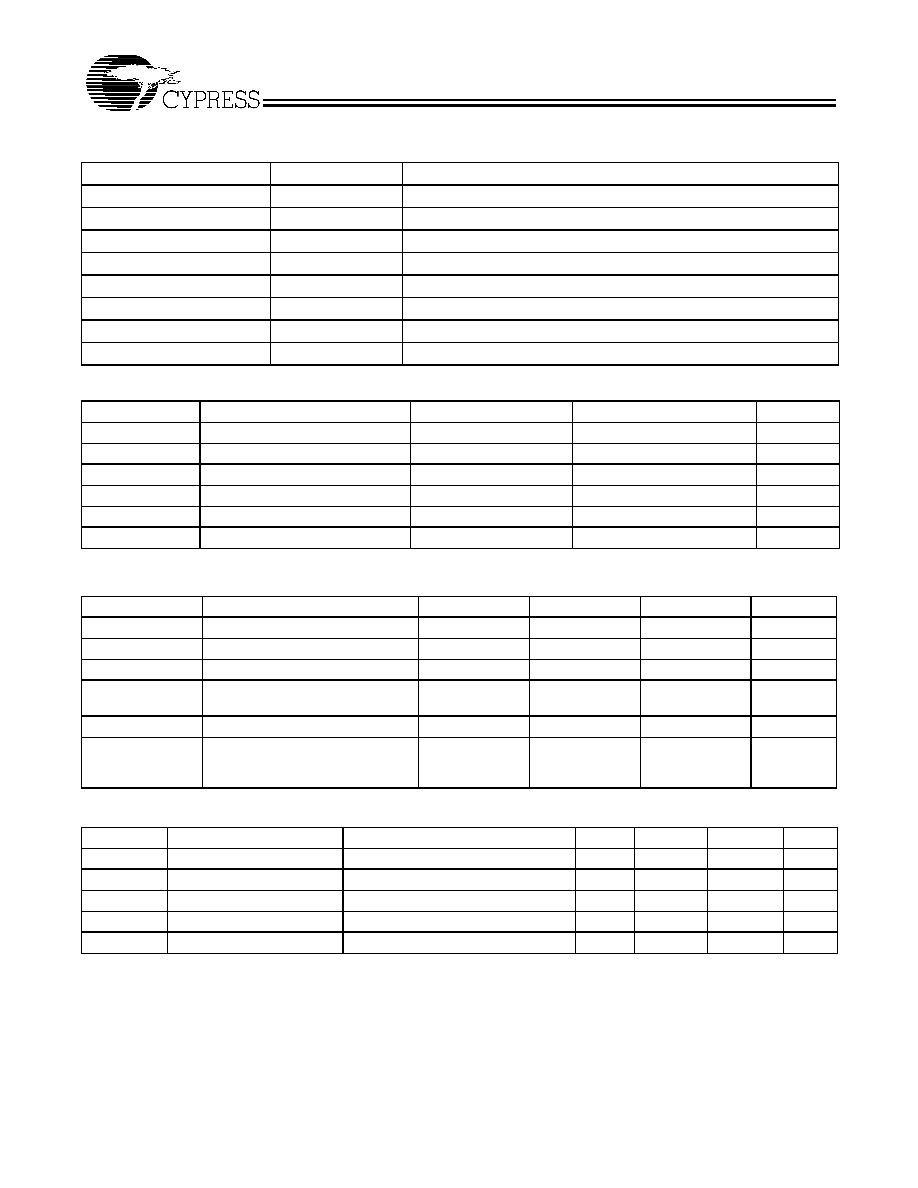

Recommended

Operating Conditions

DC

Electrical Characteristics

Pin Summary

Name

Pin Number

Description

X

IN

1

15.000 MHz Reference Crystal Input

A

VDD

2

Analog Voltage Supply

N/C

3

No Connect

AV

SS

4

Analog Ground

V

DD

5

Output Voltage Supply

19.6608 MHz

6

19.6608-MHz clock output

V

SS

7

Output Ground

X

OUT

[1]

8

Reference Crystal Output

Absolute Maximum Conditions

Parameter

Description

Min.

Max.

Unit

V

DD

Supply Voltage

≠0.5

7.0

V

T

S

Storage Temperature

[2]

≠65

125

∞ C

T

J

Junction Temperature

125

∞ C

Digital Inputs

V

SS

≠ 0.3

V

DD

+ 0.3

V

Digital Outputs referred to V

DD

V

SS

≠ 0.3

V

DD

+ 0.3

V

Electro-Static Discharge

2000

V

Parameter

Description

Min.

Typ.

Max.

Unit

V

DD

Operating Voltage

3.0

3.3

3.6

V

T

A

Ambient Temperature

0

70

∞ C

C

LOAD

Max Load Capacitance

15

pF

P

max

Max Output Power Dissipation,

8-pin package

150

∞ C/W

f

REF

Reference Frequency

15.000

MHz

t

PU

Power-up time for all VDD's to

reach minimum specified voltage

(power ramps must be monotonic)

0.05

500

ms

Parameter

Name

Description

Min.

Typ.

Max.

Unit

I

OH

Output High Current

V

OH

= V

DD

≠ 0.5, V

DD

= 3.3V

12

24

mA

I

OL

Output Low Current

V

OL

= 0.5, V

DD

= 3.3V

12

24

mA

C

IN

Input Capacitance

7

pF

I

IZ

Input Leakage Current

5

mA

I

DD

Supply Current

Sum of Core and Output Current

20

mA

Notes:

1.

Float XOUT if XIN is externally driven.

2.

Rated for 10 years.

CY26118

PRELIMINARY

Document #: 38-07274 Rev. *A

Page 3 of 5

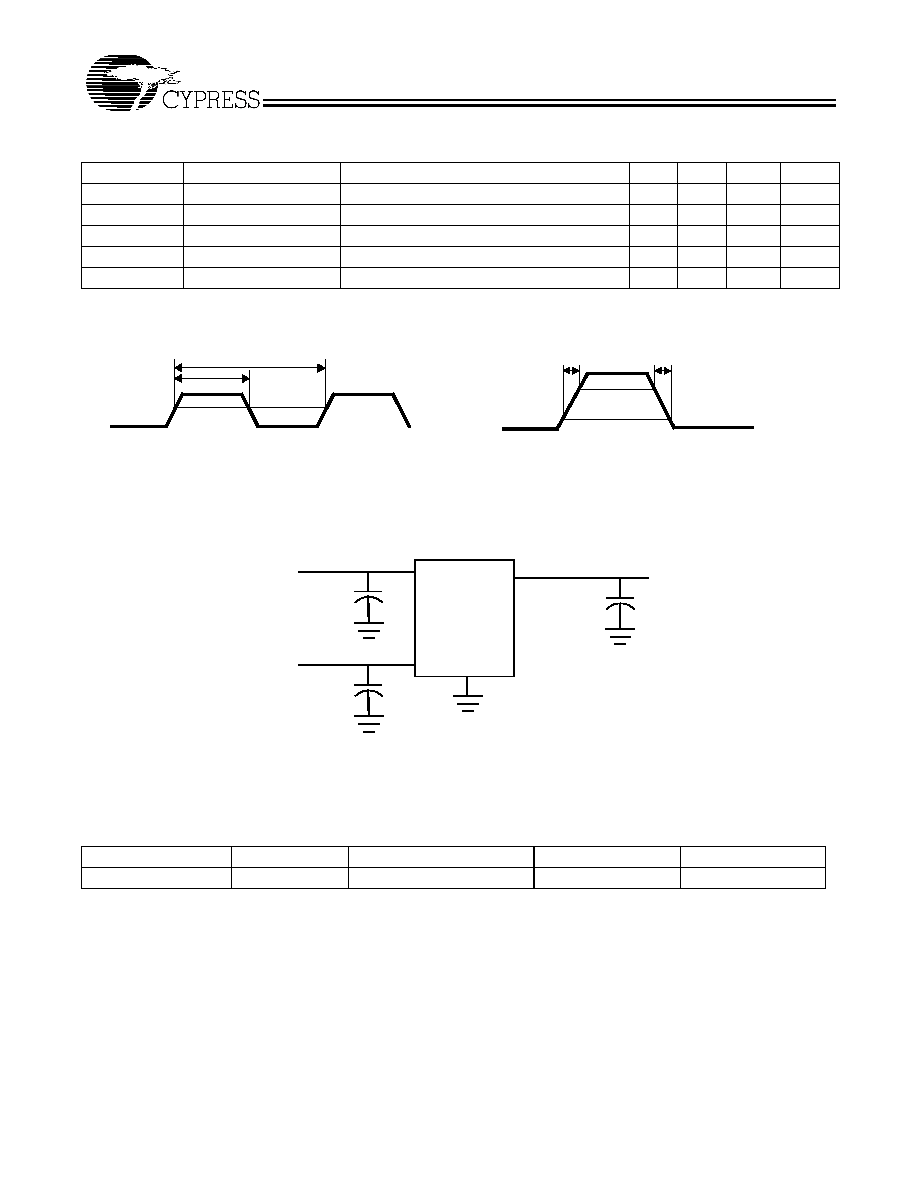

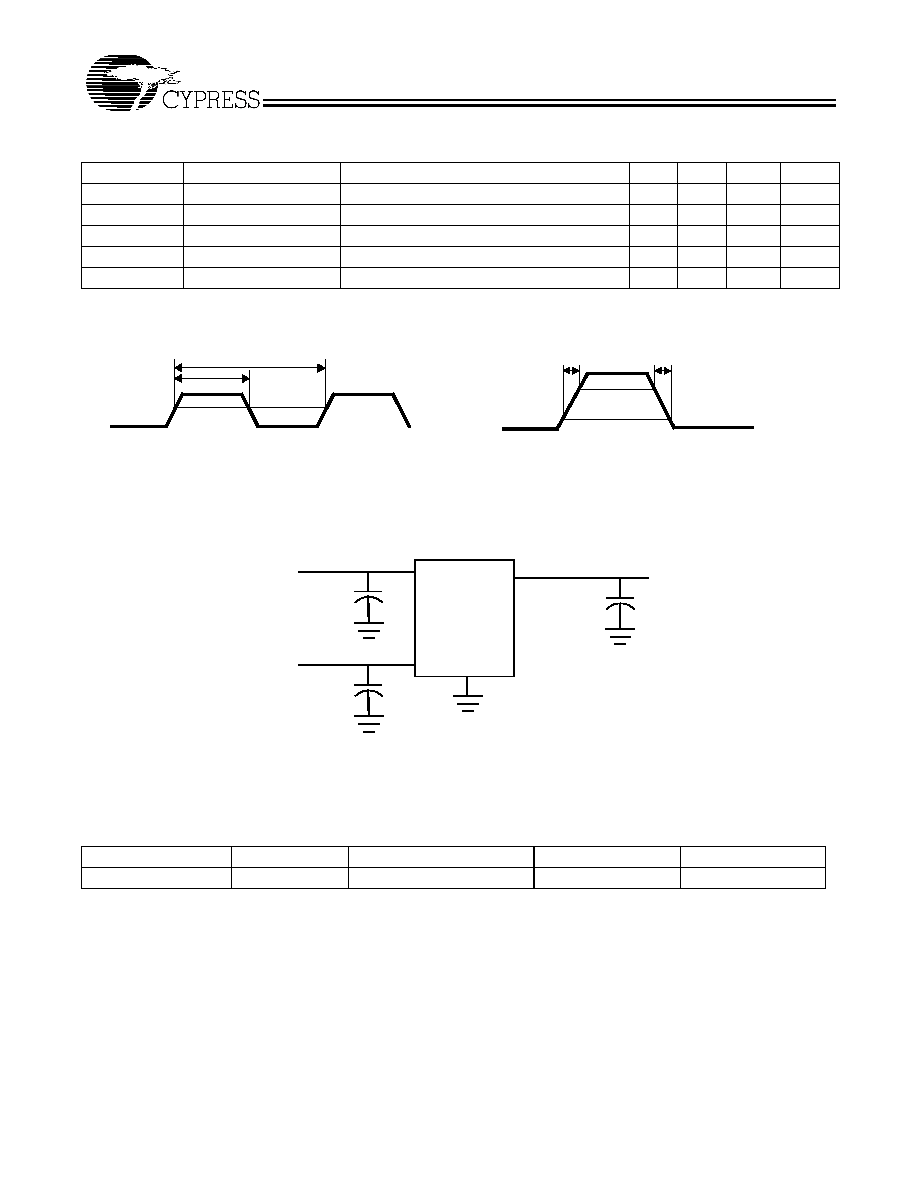

AC Electrical

Characteristics

(V

DD

= 3.3V)

Figure 1. Duty Cycle Definition; DC = t

2

/t

1

Figure 2. Rise and Fall Time Definitions

Parameter

[3]

Name

Description

Min.

Typ.

Max.

Unit

DC

Output Duty Cycle

Duty Cycle is defined in Figure 1 50% of V

DD

45

50

55

%

t

3

Rising Edge Slew Rate

Output Clock Rise Time 20% - 80% of V

DD

0.8

1.8

V/ns

t

4

Falling Edge Slew Rate

Output Clock Fall Time 80% to 20% of V

DD

0.8

1.8

V/ns

t

9

Clock Jitter

Peak-to-Peak period jitter

200

ps

t

10

PLL Lock Time

3

ms

Note:

3.

Not 100% tested.

t

1

t

2

19.6608 MHz

50%

t

3

19.6608 MHz

80%

20%

t

4

Test Circuit

Ordering Information

Ordering Code

Package Name

Package Type

Operating Range

Operating Voltage

CY26118SC

S8

8-Pin SOIC

Commercial

3.3V

0.1

µ

F

AV

DD

0.1

µ

F

V

DD

CLK out

C

LOAD

GND

OUTPUTS

CY26118

PRELIMINARY

Document #: 38-07274 Rev. *A

Page 4 of 5

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

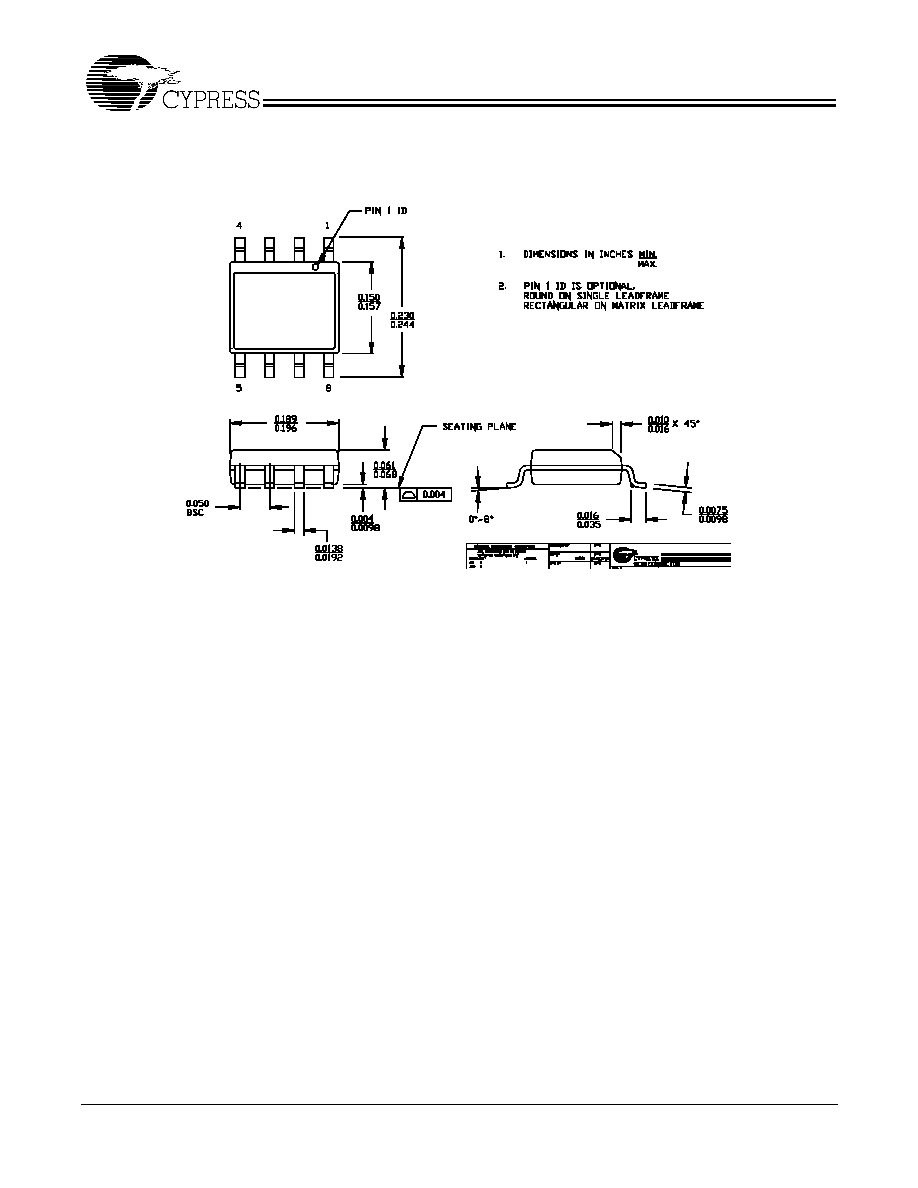

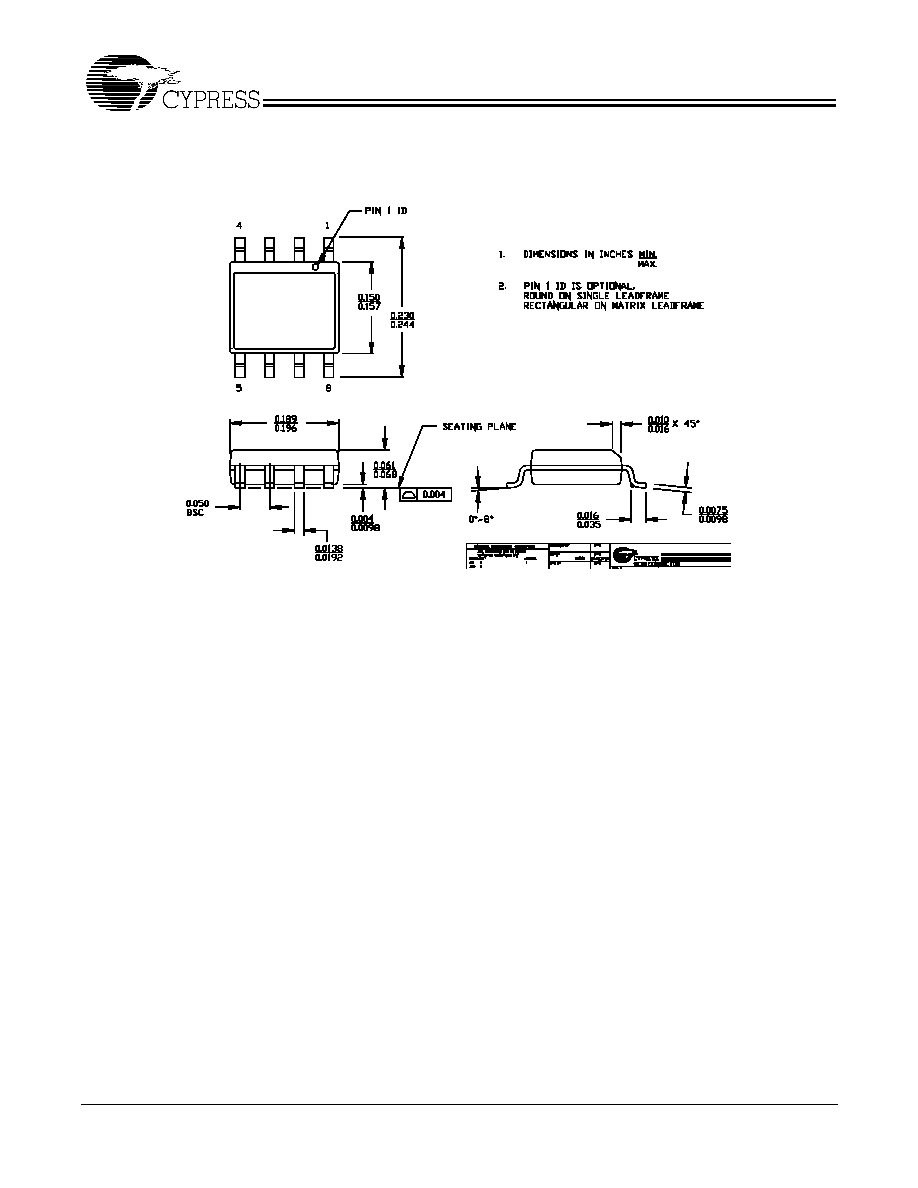

Pin Diagrams

8-Lead (150-Mil) SOIC S8

CY26118

PRELIMINARY

Document #: 38-07274 Rev. *A

Page 5 of 5

Document Title: CY26118 19.6608-MHz Clock Generator

Document Number: 38-07274

REV.

ECN NO.

Issue

Date

Orig. of

Change

Description of Change

**

110764

02/06/02

CKN

New Data Sheet

*A

121883

12/14/02

RBI

Power up requirements added to Operating Conditions Information