| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CY28346 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Clock Synthesizer with Differential CPU Outputs

CY28346

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

∑

CA 95134

∑

408-943-2600

Document #: 38-07331 Rev. *B

Revised December 26, 2002

Features

∑ Compliant with IntelÆ CK 408 Mobile Clock Synthesizer

specifications

∑ 3.3V power supply

∑ Three differential CPU clocks

∑ Ten copies of PCI clocks

∑ 5/6 copies of 3V66 clocks

∑ SMBus support with read-back capabilities

∑ Spread Spectrum electromagnetic interference (EMI)

reduction

∑ Dial-a-FrequencyTM features

∑ Dial-a-dBTM features

∑ 56-pin TSSOP and SSOP packages

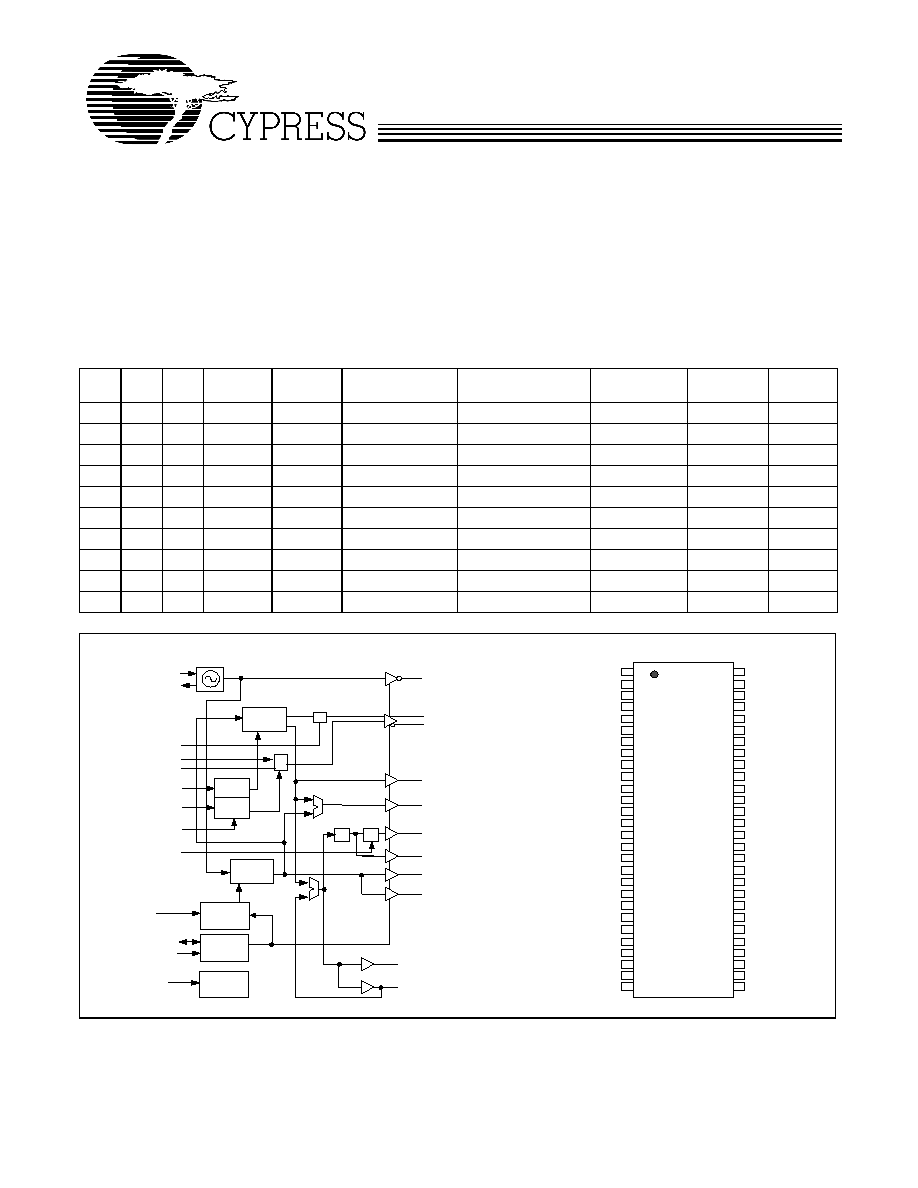

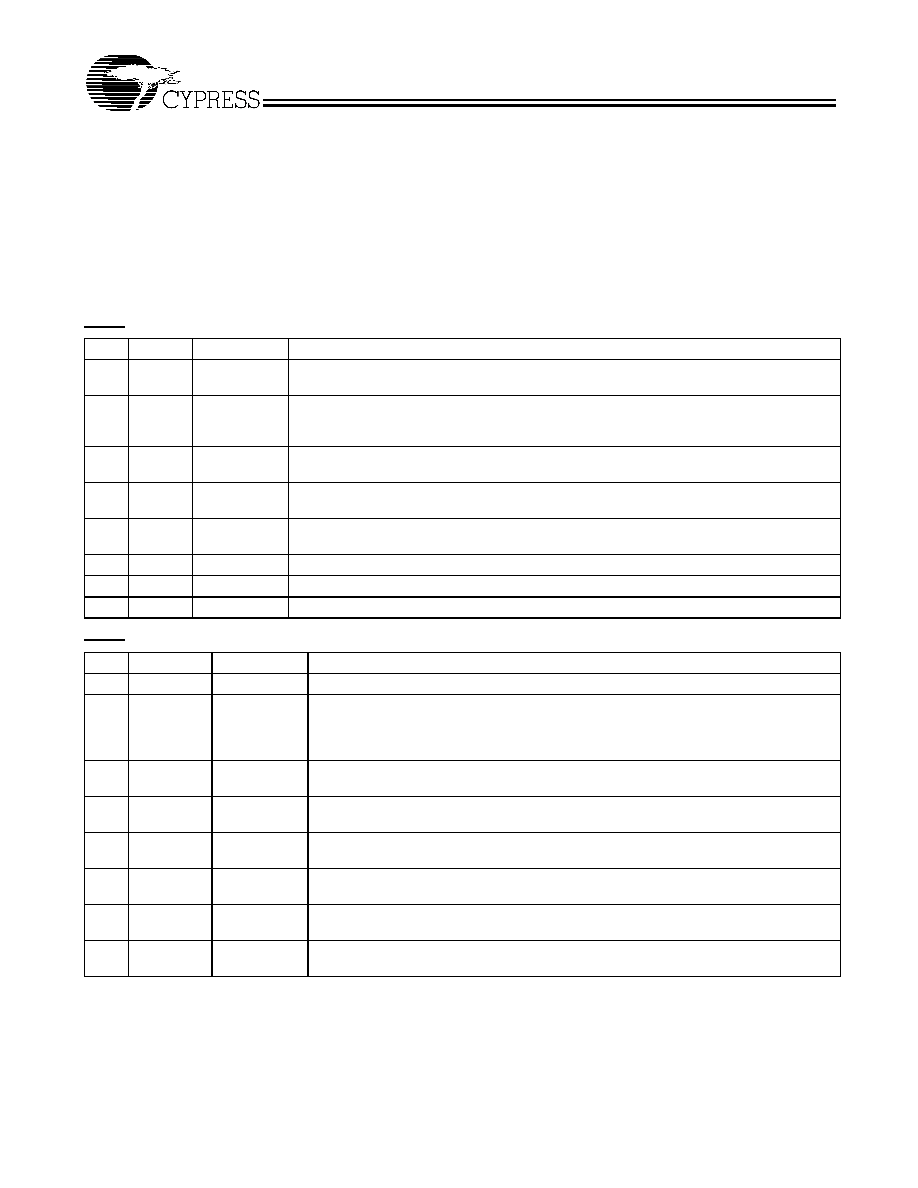

Table 1. Frequency Table

[1]

S2 S1

S0

CPU

(0:2)

3V66

66BUFF(0:2)/

3V66(0:4)

66IN/3V66≠5

PCI_FPCI

REF

USB/ DOT

1

0

0

66M

66M

66IN

66-MHz clock input

66IN/2

14.318M

48M

1

0

1

100M

66M

66IN

66-MHz clock input

66IN/2

14.318M

48M

1

1

0

200M

66M

66IN

66-MHz clock input

66IN/2

14.318M

48M

1

1

1

133M

66M

66IN

66-MHZ clock input

66IN/2

14.318M

48M

0

0

0

66M

66M

66M

66M

33 M

14.318M

48M

0

0

1

100M

66M

66M

66M

33 M

14.318M

48M

0

1

0

200M

66M

66M

66M

33 M

14.318M

48M

0

1

1

133M

66M

66M

66M

33 M

14.318M

48M

M

0

0

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

M

0

1

TCLK/2

TCLK/4

TCLK/4

TCLK/4

TCLK/8

TCLK

TCLK/2

Note:

1.

TCLK is a test clock driven on the XTAL_IN input during test mode. M= driven to a level between 1.0V and 1.8V. If the S2 pin is at a M level during power-up, a

0 state will be latched into the device's internal state register.

PLL1

PLL2

/2

W D

Logic

Power

Up Logic

XIN

XOUT

CPU_STP#

IREF

VSSIREF

S(0:2)

MULT0

VTT_PG#

PCI_STP#

PD#

SDATA

SCLK

VDDA

66B[0:2]/3V66[2:4]

48M DOT

48M USB

PCI_F(0:2)

PCI(0:6)

3V66_1/VCH

3V66_0

CPUC(0:2)

CPUT(0:2)

REF

66IN/3V66-5

I2C

Logic

VDD

XIN

XOUT

VSS

PCIF0

PCIF1

PCIF2

VDD

VSS

PCI0

PCI1

PCI2

PCI3

VDD

VSS

PCI4

PCI5

PCI6

VDD

VSS

66B0/3V66_2

66B1/3V66_3

66B2/3V66_4

66IN/3V66_5

PD#

VDDA

VSSA

VTT_PG#

REF

S1

S0

CPU_STP#

CPUT0

CPUC0

VDD

CPUT1

CPUC1

VSS

VDD

CPUT2

CPUC2

MULT0

IREF

VSSIREF

S2

48MUSB

48MDOT

VDD

VSS

3V66_1/VCH

PCI_STP#

3V66_0

VDD

VSS

SCLK

SDATA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

C

Y

28

34

6

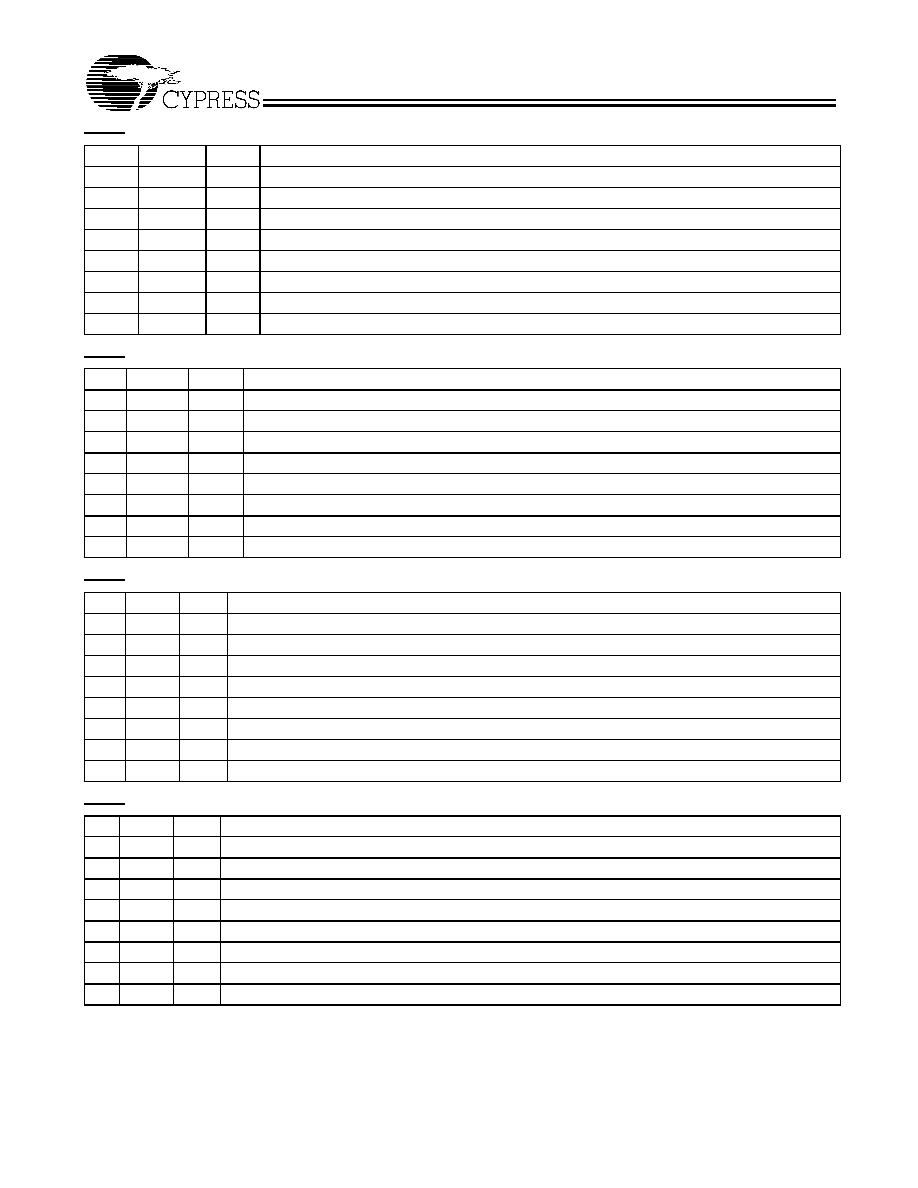

Pin Configuration

Block Diagram

CY28346

Document #: 38-07331 Rev. *B

Page 2 of 20

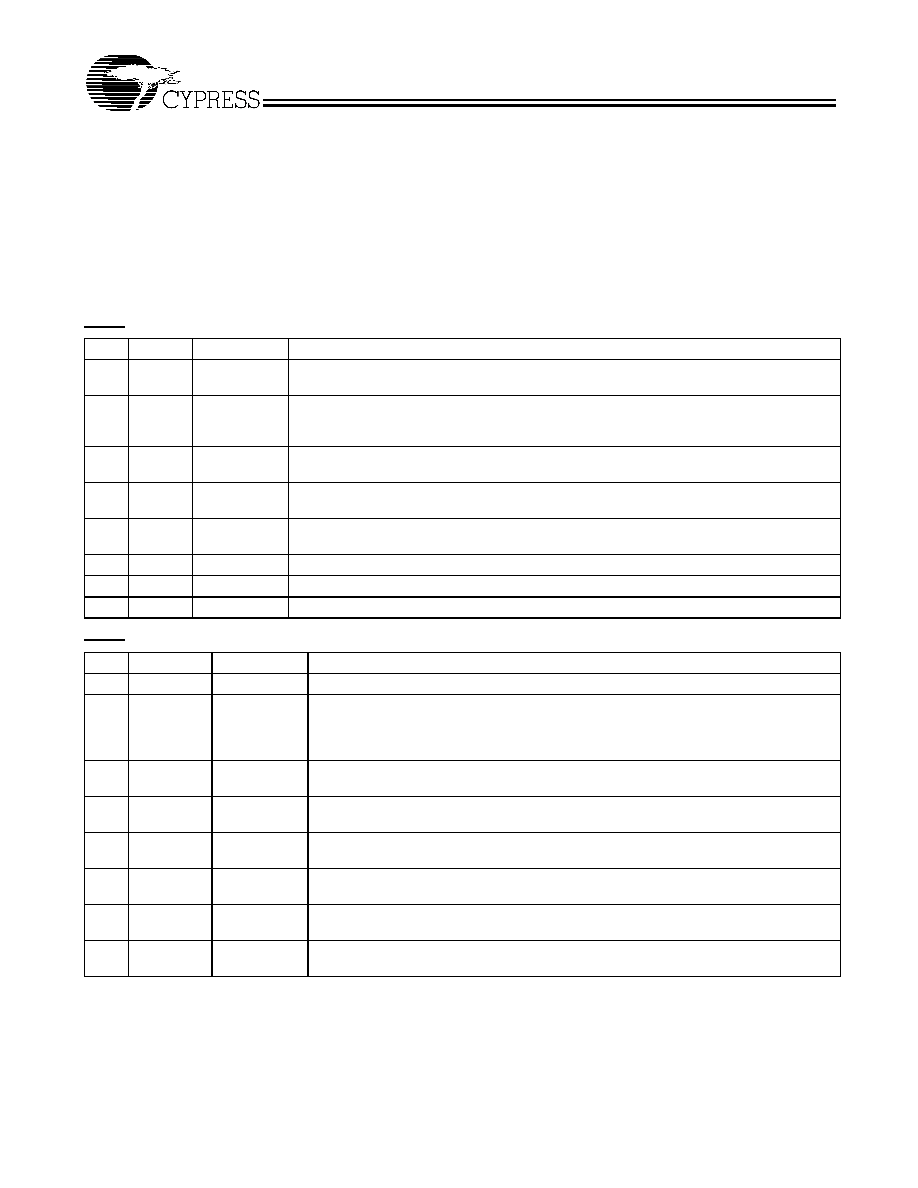

Pin Description

Pin

Name

PWR

I/O

Description

2

XIN

I

Oscillator Buffer Input. Connect to a crystal or to an external clock.

3

XOUT

V

DD

O

Oscillator Buffer Output. Connect to a crystal. Do not connect when an external

clock is applied at X

IN

.

52, 51, 49, 48,

45, 44

CPUT(0:2),

CPUC(0:2)

V

DD

O

Differential Host Output Clock Pairs. See Table 1 for frequency/functionality.

10, 11, 12, 13,

16, 17, 18

PCI(0:6)

V

DDP

O

PCI Clock Outputs. Are synchronous to 66IN or 3V66 clock. See Table 1.

5, 6, 7

PCIF (0:2)

V

DD

O

33-MHz PCI Clocks.

˜

2 copies of 66IN or 3V66 clocks that may be free running

(not stopped when PCI_STP# is asserted LOW) or may be stoppable depending

on the programming of SMBus register Byte3,Bits (3:5).

56

REF

V

DD

O

Buffered Output Copy of the Device's X

IN

Clock.

42

IREF

V

DD

I

Current Reference Programming Input for CPU Buffers. A resistor is

connected between this pin and VSSIREF.

28

VTT_PG#

V

DD

I

Qualifying Input that Latches S(0:2) and MULT0. When this input is at a logic

LOW, the S(0:2) and MULT0 are latched.

39

48MUSB

V

DD48

O

Fixed 48-MHz USB Clock Outputs.

38

48MDOT

V

DD48

O

Fixed 48-MHZ DOT Clock Outputs.

33

3V66_0

V

DD

O

3.3V 66-MHz Fixed-frequency Clock.

35

3V66_1/VCH

V

DD

O

3.3V Clock Selectable with SMBus Byte0,Bit5, When Byte5,Bit5. When Byte

0,Bit 5 is at a logic 1, then this pin is a 48M output clock. When Byte0,Bit5 is a

logic 0, this is a 66M output clock (default).

25

PD#

V

DD

I

PU

Power-down Mode Pin. A logic LOW level causes the device to enter a

power-down state. All internal logic is turned off except for the SMBus logic. All

output buffers are stopped.

43

MULT0

I

PU

Programming Input Selection for CPU Clock Current Multiplier.

55, 54

S(0,1)

I

I

Frequency Select Inputs. See Table 1.

29

SDATA

I

I

Serial Data Input. Conforms to the SMBus specification of a Slave

Receive/Transmit device. It is an input when receiving data. It is an open drain

output when acknowledging or transmitting data.

30

SCLK

I

I

Serial Clock Input. Conforms to the SMBus specification.

40

S2

V

DD

I

T

Frequency Select Input. See Table 1. This is a Tri-level input which is driven

HIGH, LOW or driven to a intermediate level.

34

PCI_STP#

V

DD

I

PU

PCI Clock Disable Input. When asserted LOW, PCI (0:6) clocks are synchro-

nously disabled in a LOW state. This pin does not effect PCIF (0:2) clocks'

outputs if they are programmed to be PCIF clocks via the device's SMBus

interface.

53

CPU_STP#

V

DD

I

PU

CPU Clock Disable Input. When asserted LOW, CPUT (0:2) clocks are synchro-

nously disabled in a HIGH state and CPUC(0:2) clocks are synchronously

disabled in a LOW state.

24

66IN/3V66_5

V

DD

I/O

Input Connection for 66CLK(0:2) Output Clock Buffers if S2 = 1, or output

clock for fixed 66-MHz clock if S2 = 0. See Table 1.

21, 22, 23

66B(0:2)/

3V66(2:4)

V

DD

O

3.3V Clock Outputs. These clocks are buffered copies of the 66IN clock or fixed

at 66 MHz. See Table 1.

1, 8, 14, 19, 32,

37, 46, 50

V

DD

PWR 3.3V Power Supply.

4, 9, 15, 20, 27,

31, 36, 47

V

SS

PWR Common Ground.

41

V

SS

IREF

PWR Current Reference Programming Input for CPU Buffers. A resistor is

connected between this pin and IREF. This pin should also be returned to device

V

SS

.

26

V

DDA

≠

PWR Analog Power Input. Used for phase-locked loops (PLLs) and internal analog

circuits. It is also specifically used to detect and determine when power is at an

acceptable level to enable the device to operate.

CY28346

Document #: 38-07331 Rev. *B

Page 3 of 20

Two-Wire SMBus Control Interface

The two-wire control interface implements a Read/Write slave

only interface according to SMBus specification.

The device will accept data written to the D2 address and data

may read back from address D3. It will not respond to any other

addresses, and previously set control registers are retained as

long as power in maintained on the device.

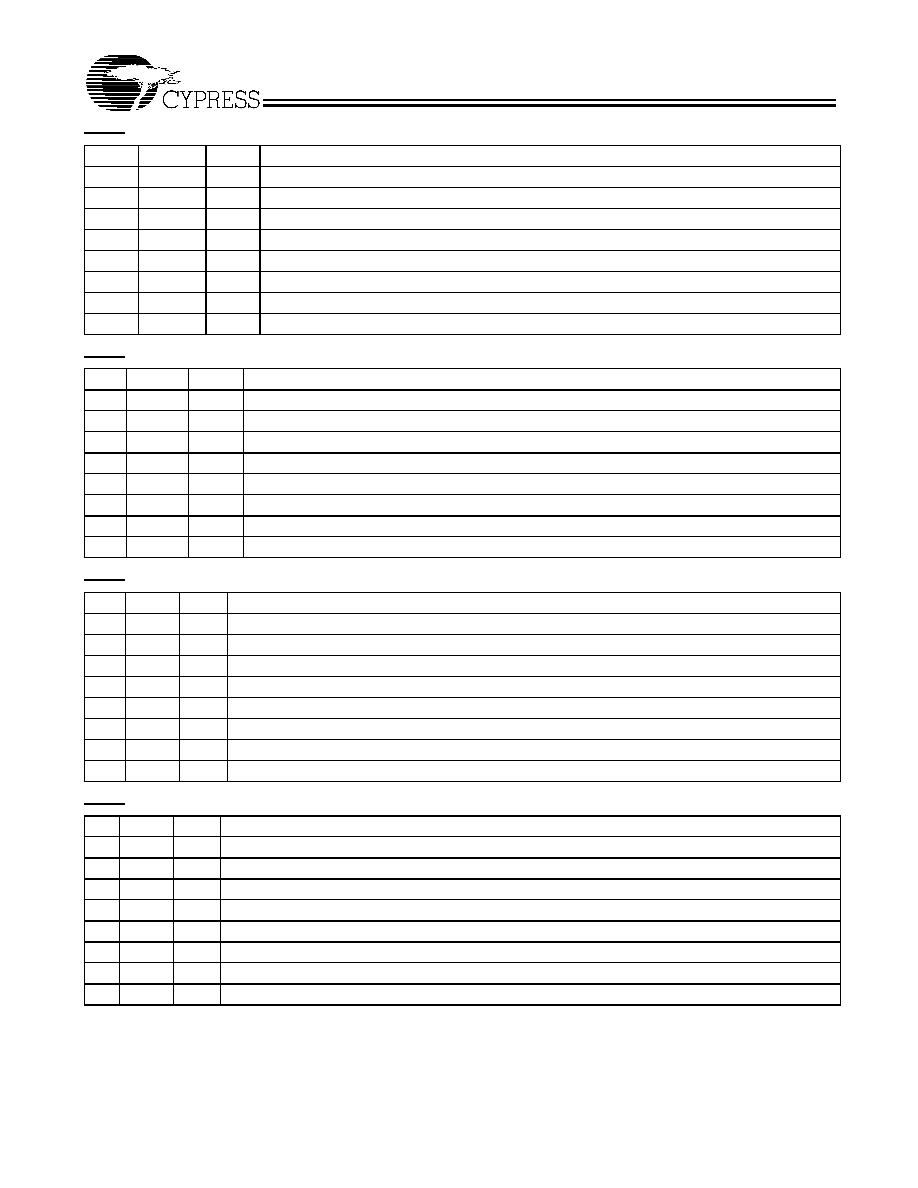

Serial Control Registers

Following the acknowledge of the Address Byte, two additional

bytes must be sent:

1. "Command code" byte

2. "Byte count" byte.

Although the data (bits) in the command is considered "don't

care," it must be sent and will be acknowledged. After the

Command Code and the Byte Count have been acknowl-

edged, the sequence (Byte 0, Byte 1, and Byte 2) described

below will be valid and acknowledged.

Byte 0: CPU Clock Register

[2,3]

Bit

@Pup

Pin#

Description

7

0

Spread Spectrum Enable. 0 = Spread Off, 1 = Spread On

This is a Read and Write control bit.

6

0

CPU Clock Power-down Mode Select. 0 = Drive CPUT(0:2) to 4 or 6 IREF and drive CPUC(0:2)

LOW when PD# is asserted LOW. 1 = Tri-state all CPU outputs. This is only applicable when

PD# is LOW. It is not applicable to CPU_STP#.

5

0

35

3V66_1/VCH Frequency Select, 0 = 66M selected, 1 = 48M selected

This is a Read and Write control bit.

4

Pin 53

44,45,48,49,5

1,52

CPU_STP#. Reflects the current value of the external CPU_STP# (pin 53) This bit is

Read-only.

3

Pin 34

10,11,12,13,1

6,17,18

Reflects the current value of the internal PCI_STP# function when read. Internally PCI_STP#

is a logical AND function of the internal SMBus register bit and the external PCI_STP# pin.

2

Pin 40

Frequency Select Bit 2. Reflects the value of SEL2 (pin 40). This bit is Read-only.

1

Pin 55

Frequency Select Bit 1. Reflects the value of SEL1 (pin 55). This bit is Read-only.

0

Pin 54

Frequency Select Bit 0. Reflects the value of SEL0 (pin 54). This bit is Read-only.

Byte 1: CPU Clock Register

Bit

@Pup

Pin#

Description

7

Pin 43

43

MULT0 (Pin 43) Value. This bit is Read-only.

6

0

53

CPUT/C(0:2) Output Functionality Control When CPU_STP# is Asserted. 0 = Drive

CPUT(0:2) to 4 or 6 IREF and drive CPUC(0:2) LOW when CPU_STP# asserted LOW.

1 = three-state all CPU outputs. This bit will override Byte0,Bit6 such that even if it is 0,

when PD# goes LOW the CPU outputs will be three-stated.

5

0

44,45

CPU2 Functionality Control When CPU_STP# is Asserted LOW. 1 = Free Running, 0 =

Stopped LOW with CPU_STP# asserted LOW. This is a Read and Write control bit.

4

0

48,49

CPU1 Functionality Control When CPU_STP# is Asserted LOW. 1 = Free Running, 0 =

Stopped LOW with CPU_STP# asserted LOW. This is a Read and Write control bit.

3

0

51,52

CPUT0 Functionality Control When CPU_STP# is Asserted LOW. 1 = Free Running, 0 =

Stopped LOW with CPU_STP# asserted LOW. This is a Read and Write control bit.

2

1

44,45

CPUT/C2 Output Control. 1 = enabled, 0 = disable HIGH and CPUC2 disables LOW. This

is a Read and Write control bit.

1

1

48,49

CPUT/C1 Output Control. 1 = enabled, 0 = disable HIGH and CPUC1 disables LOW. This

is a Read and Write control bit.

0

1

51,52

CPUT/C0 Output Control. 1 = enabled, 0 = disable HIGH and CPUC0 disables LOW. This

is a Read and Write control bit.

Notes:

2.

PU = internal pull-up. PD = internal pull-down. T = tri-level logic input with valid logic voltages of LOW = < 0.8V, T = 1.0 ≠ 1.8V and HIGH = > 2.0V.

3.

The "Pin#" column lists the relevant pin number where applicable. The "@Pup" column gives the default state at power-up.

CY28346

Document #: 38-07331 Rev. *B

Page 4 of 20

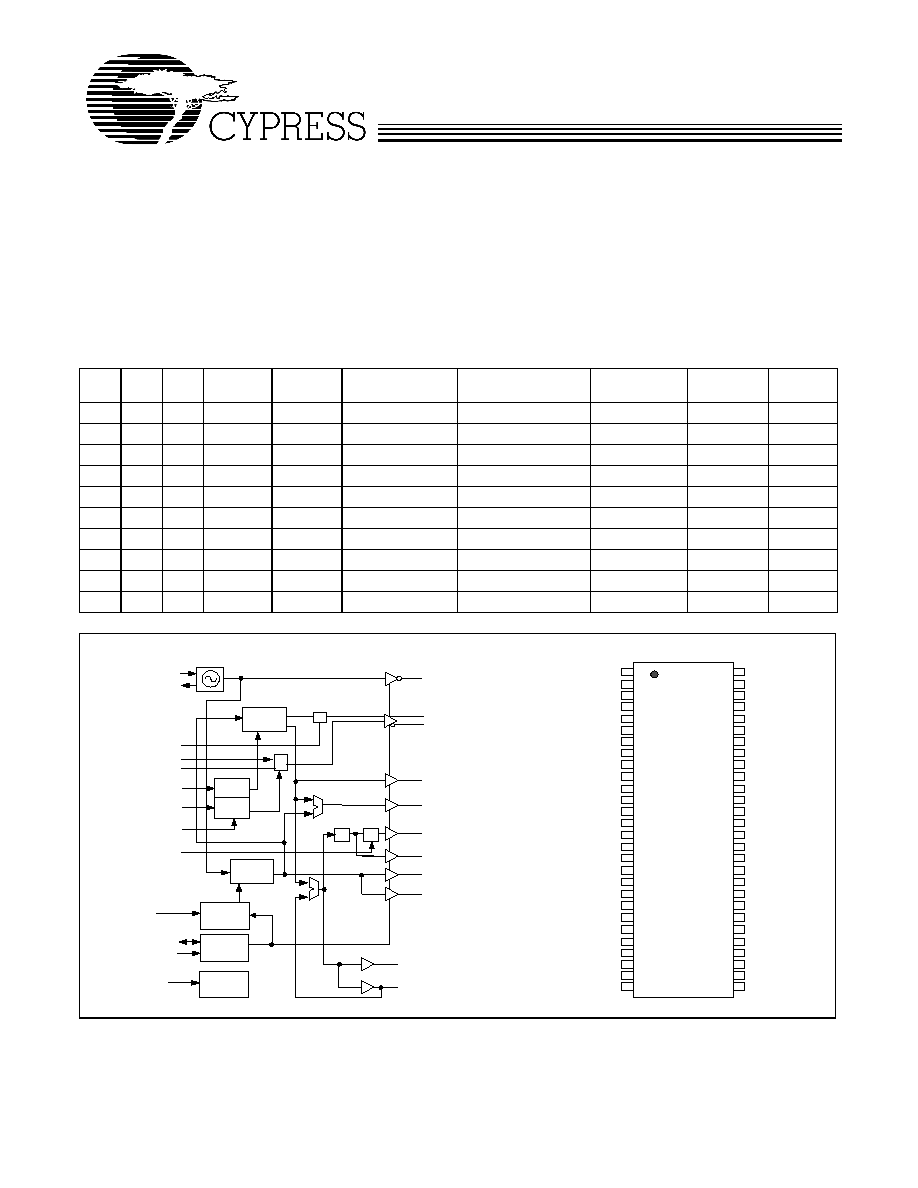

Byte 2: PCI Clock Control Register (all bits are Read and Write functional)

Bit

@Pup

Pin#

Description

7

0

53

REF Output Control. 0 = high strength, 1 = low strength.

6

1

18

PCI6 Output Control. 1 = enabled, 0 = forced LOW.

5

1

17

PCI5 Output Control. 1 = enabled, 0 = forced LOW.

4

1

16

PCI4 Output Control. 1 = enabled, 0 = forced LOW.

3

1

13

PCI3 Output Control. 1 = enabled, 0 = forced LOW.

2

1

12

PCI2 Output Control. 1 = enabled, 0 = forced LOW.

1

1

11

PCI1 Output Control. 1 = enabled, 0 = forced LOW.

0

1

10

PCI0 Output Control. 1 = enabled, 0 = forced LOW.

Byte 3: PCI_F Clock and 48M Control Register (all bits are Read and Write functional)

Bit

@Pup

Pin#

Description

7

1

38

48MDOT Output Control. 1 = enabled, 0 = forced LOW.

6

1

39

48MUSB Output Control. 1 = enabled, 0 = forced LOW.

5

0

7

PCI_STP#, Control of PCI_F2. 0 = Free Running, 1 = Stopped when PCI_STP# is LOW.

4

0

6

PCI_STP#, Control of PCI_F1. 0 = Free Running, 1 = Stopped when PCI_STP# is LOW.

3

0

5

PCI_STP#, Control of PCI_F0. 0 = Free Running, 1 = Stopped when PCI_STP# is LOW.

2

1

7

PCI_F2 Output Control. 1 = running, 0 = forced LOW.

1

1

6

PCI_F1 Output Control. 1 = running, 0 = forced LOW.

0

1

5

PCI_F0 Output Control. 1 = running, 0 = forced LOW.

Byte 4: DRCG Control Register (all bits are Read and Write functional)

Bit

@Pup

Pin#

Description

7

0

SS2 Spread Spectrum Control Bit (0 = down spread, 1 = center spread).

6

0

Reserved. Set = 0.

5

1

33

3V66_0 Output Enabled. 1 = enabled, 0 = disable.

4

1

35

3V66_1/VCH Output Enable. 1 = enabled, 0 = disabled.

3

1

24

3V66_5 Output Enable. 1 = enabled, 0 = disabled.

2

1

23

66B2/3V66_4 Output Enabled. 1 = enabled, 0 = disabled.

1

1

22

66B1/3V66_3 Output Enabled. 1 = enabled, 0 = disabled.

0

1

21

66B0/3V66_2 Output Enabled. 1 = enabled, 0 = disabled.

Byte 5: Clock Control Register (all bits are Read and Write functional)

Bit

@Pup

Pin#

Description

7

0

SS1 Spread Spectrum Control Bit.

6

1

SS0 Spread Spectrum Control Bit.

5

0

66IN to 66M delay Control MSB.

4

0

66IN to 66M delay Control LSB.

3

0

Reserved. Set = 0.

2

0

48MDOT Edge Rate Control. When set to 1, the edge is slowed by 15%.

1

0

Reserved. Set = 0.

0

0

USB edge rate control. When set to 1, the edge is slowed by 15%.

CY28346

Document #: 38-07331 Rev. *B

Page 5 of 20

Byte 6: Silicon Signature Register

[4]

(all bits are Read-only)

Bit

@Pup

Pin#

Description

7

0

Revision = 0001

6

0

5

0

4

1

3

0

Vendor Code = 0011

2

0

1

1

0

1

Byte 7: Reserved Register

Bit

@Pup

Pin#

Description

7

0

Reserved. Set = 0.

6

0

Reserved. Set = 0.

5

0

Reserved. Set = 0.

4

0

Reserved. Set = 0.

3

0

Reserved. Set = 0.

2

0

Reserved. Set = 0.

1

0

Reserved. Set = 0.

0

0

Reserved. Set = 0.

Byte 8: Dial-a-Frequency Control Register N

Bit

@Pup

Name

Description

7

0

Reserved. Set = 0.

6

0

N6, MSB

These bits are for programming the PLL's internal N register. This access allows the user to

modify the CPU frequency at very high resolution (accuracy). All other synchronous clocks

(clocks that are generated from the same PLL, such as PCI) remain at their existing ratios

relative to the CPU clock.

5

0

N5

4

0

N4

3

0

N3

2

0

N2

1

0

N3

0

0

N0, LSB

Byte 9: Dial-a-Frequency Control Register R

Bit

@Pup

Name

Description

7

0

Reserved. Set = 0.

6

0

R5, MSB

These bits are for programming the PLL's internal R register. This access allows the user to

modify the CPU frequency at very high resolution (accuracy). All other synchronous clocks

(clocks that are generated from the same PLL, such as PCI) remain at their existing ratios

relative to the CPU clock.

5

0

R4

4

0

R3

3

0

R2

2

0

R1

1

0

R0

0

0

DAF_ENB

R and N register mux selection. 0 = R and N values come from the ROM. 1 = data is loaded

from DAF (SMBus) registers.

Note:

4.

When writing to this register, the device will acknowledge the Write operation, but the data itself will be ignored.