| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CY28347ZC | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Universal Single-chip Clock Solution

for VIA P4M266/KM266 DDR Systems

CY28347

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

,

CA 95134

∑

408-943-2600

Document #: 38-07352 Rev. *C

Revised December 26, 2002

Features

∑ Supports VIA P4M266/KM266 chipsets

∑ Supports Pentium

Æ

4, Athlon

processors

∑ Supports two DDR DIMMS

∑ Provides

-- Two different programmable CPU clock pairs

-- Six differential DDR SDRAM pairs

-- Two low-skew/low-jitter AGP clocks

-- Six low-skew/low-jitter PCI clocks

-- One 48M output for USB

-- One programmable 24M or 48M for SIO

∑ Dial-a-Frequency

and Dial-a-dB

features

∑ Spread Spectrum for best electromagnetic interference

(EMI) reduction

∑ SMBus-compatible for programmability

∑ 56-pin SSOP and TSSOP packages

Note:

1.

Pins marked with [*] have internal pull-up resistors. Pins marked with [**] have internal pull-down resistors.

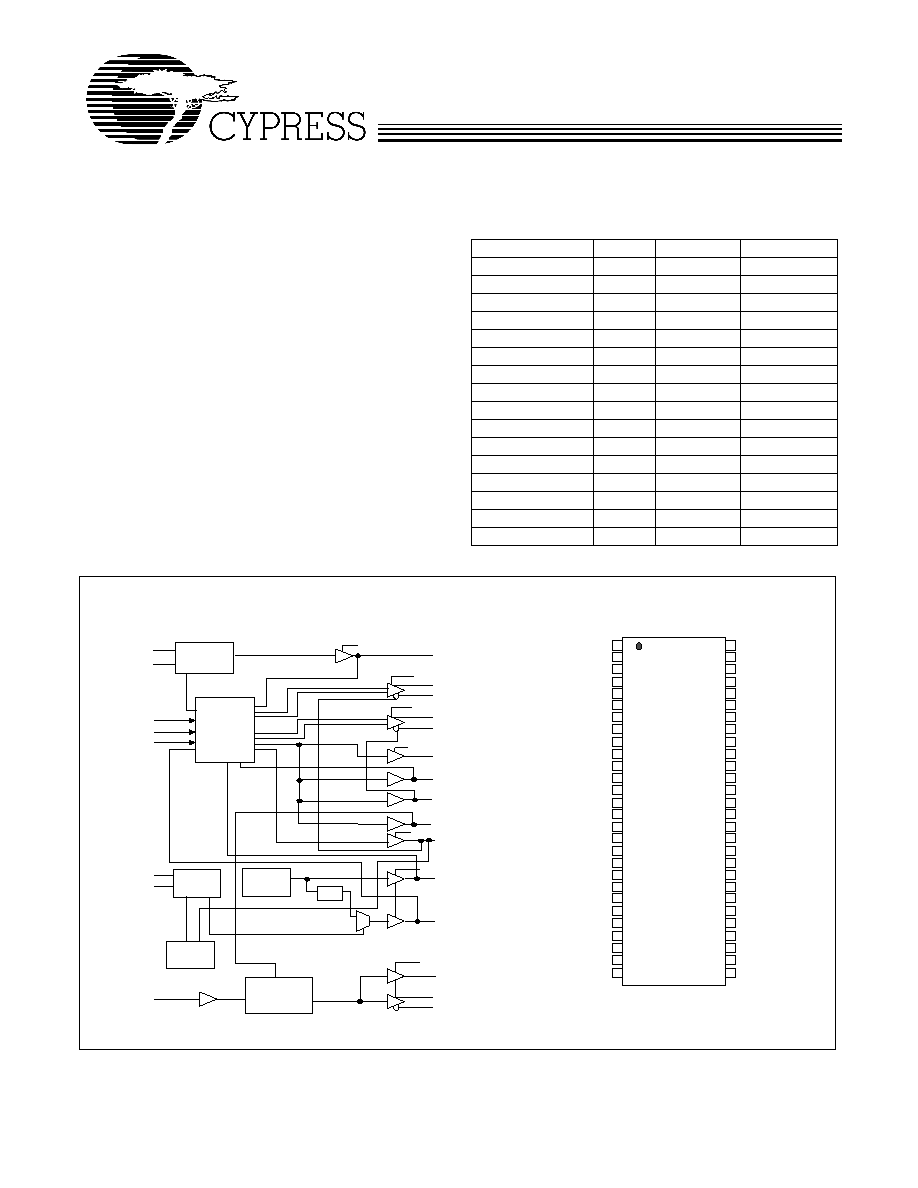

Table 1. Frequency Selection Table

FS(3:0)

CPU

AGP

PCI

0000

66.80

66.80

33.40

0001

100.20

66.80

33.40

0010

120.00

60.00

30.00

0011

133.33

66.67

33.33

0100

72.00

72.00

36.00

0101

105.00

70.00

35.00

0110

160.00

64.00

32.00

0111

140.00

70.00

35.00

1000

77.00

77.00

38.50

1001

110.00

73.33

36.67

1010

180.00

60.00

30.00

1011

150.00

60.00

30.00

1100

90.00

60.00

30.00

1101

100.00

66.67

33.33

1110

200.00

66.67

33.33

1111

133.33

66.67

33.33

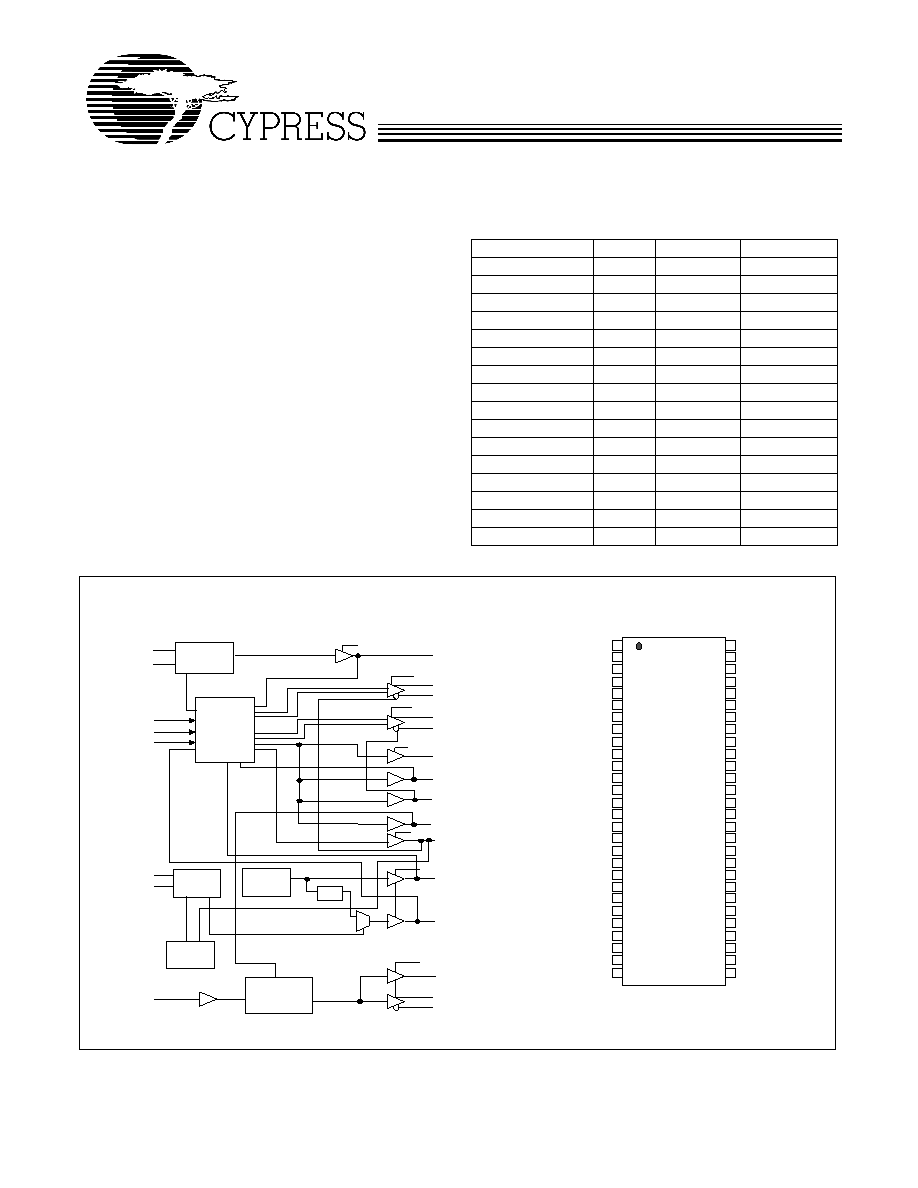

Block Diagram

Pin Configuration

[1]

VSSR

*FS0/REF0

XIN

XOUT

VDDAGP

*MODE/AGP0

*SELP4_K7#/AGP1

VSSAGP

*PCI_STP#

PCI1

*MULTSEL/PCI2

VSSPCI

PCI3

PCI4

VDDPCI

PCI5

*CPU_STP#

VSS48M

**FS3/48M

**FS2/24_48M

VDD48M

VDD

VSS

IREF

*PD#

SCLK

SDATA

**FS1/PCI_F

VDDR

VTTPWRGD#/REF1

VSSC

CPUT/CPUOD_T

CPUC/CPUOD_C

VDDC

VDDI

CPUCS_T

CPUCS_C

FBOUT

BUF_IN

DDRT0

DDRC0

DDRT1

DDRC1

VDDD

VSSD

DDRT2

DDRC2

DDRT3

DDRC3

VDDD

VSSD

DDRT4

DDRC4

DDRT5

DDRC5

VSSI

CY

2

834

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

1

2

3

4

5

6

7

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

PLL1

S2D

CONVERT

SMBus

CPUCS_T

VDDC

VDDI

CPUT/CPU0D_T

SELP4_K7#

PCI(3:5)

PCI_F

FS1

REF(0:1)

VDDR

FS0

48M

24_48M

FBOUT

DDRT(0:5)

SCLK

SDATA

PD#

AGP(0:1)

VDDAGP

VDD48M

VDDD

XTAL

XOUT

XIN

FS2

PCI2

PCI1

VDDPCI

PLL2

/ 2

BUF_IN

REF0

FS3

MULTSEL

SELSDR_DDR#

DDRC(0:5)

CPU_STP#

PCI_STP#

CPUCS_C

CPUC/CPU0D_C

CY28347

Document #: 38-07352 Rev. *C

Page 2 of 22

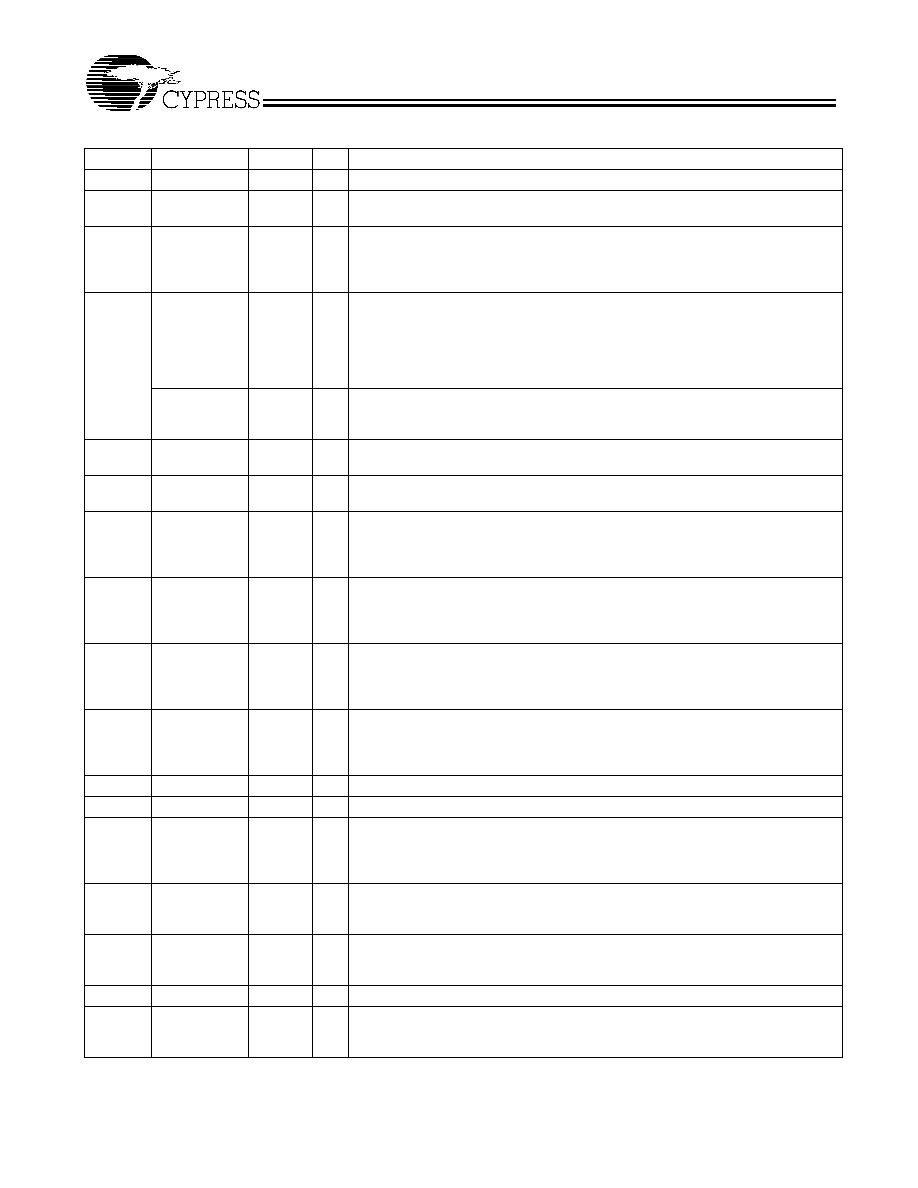

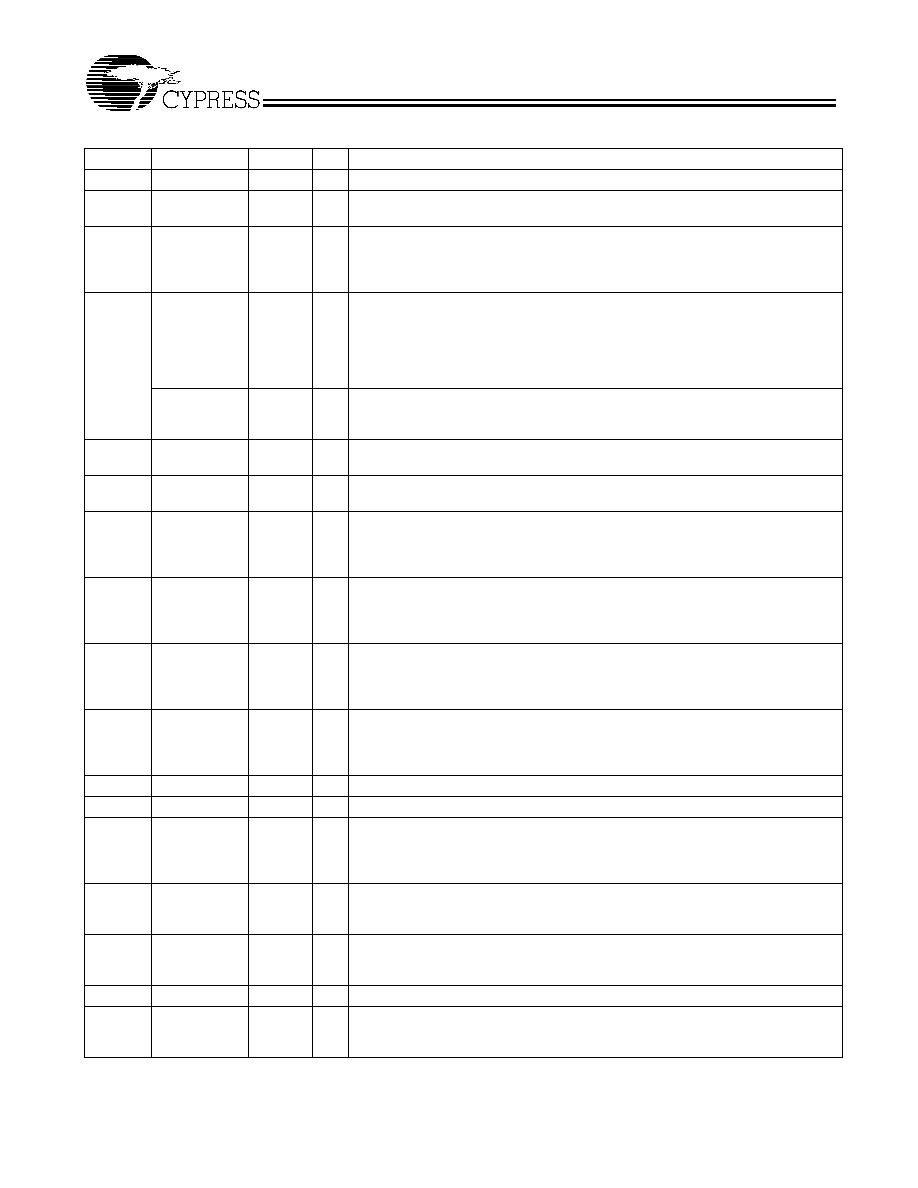

Pin Description

[2]

Pin

Name

PWR

I/O

Description

3

XIN

I

Oscillator Buffer Input. Connect to a crystal or to an external clock.

4

XOUT

VDD

O

Oscillator Buffer Output. Connect to a crystal. Do not connect when an external

clock is applied at XIN.

1

FS0/REF0

VDD

I/O

PU

Power-on Bidirectional Input/Output. At power-up, FS0 is the input. When the

power supply voltage crosses the input threshold voltage, FS0 state is latched and

this pin becomes REF0, buffered copy of signal applied at XIN. (1≠2 x strength,

selectable by SMBus. Default value is 1 x strength.)

56

VTTPWRGD# VDDR

I

If SELP4_K7# = 1, with a P4 processor setup as CPU(T:C). At power-up,

VTT_PWRGD# is an input. When this input is sampled LOW, the FS (3:0) and

MULTSEL are latched and all output clocks are enabled. After the first transition to

a LOW on VTT_PWRGD#, this pin is ignored and will not effect the behavior of the

device thereafter. When the VTT_PWRGD# feature is not used, please connect this

signal to ground through a 10K

resistor.

REF1

VDDR

O

If SELP4_K7# = 0, with an Athlon (K7) processor as CPUOD_(T:C).

VTT_PWRGD# function is disabled, and the feature is ignored. This pin becomes

REF1 and is a buffered copy of the signal applied at XIN.

44,42,38,

36,32,30

DDRT(0:5)

VDDD

O

These pins are configured for DDR clock outputs. They are "True" copies of

signal applied at Pin45, BUF_IN.

43,41,37

35,31,29

DDRC(0:5)

VDDD

O

These pins are configured for DDR clock outputs. They are "Complementary"

copies of signal applied at Pin45, BUF_IN.

7

SELP4_K7#/

AGP1

VDDAGP I/O

PU

Power-on Bidirectional Input/Output. At power-up, SELP4_K7# is the input.

When the power supply voltage crosses the input threshold voltage, SELP4_K7#

state is latched and this pin becomes AGP1 clock output. SELP4_K7# = 1 selects

P4 mode. SELP4_K7# = 0 selects K7 mode.

12

MULTSEL/PCI2 VDDPCI

I/O

PU

Power-on Bidirectional Input/Output. At power-up, MULTSEL is the input. When

the power supply voltage crosses the input threshold voltage, MULTSEL state is

latched and this pin becomes PCI2 clock output. MULTSEL = 0, Ioh is 4 x

IREFMULTSEL = 1, Ioh is 6 x IREF

53

CPUT/CPUOD_T

VDDC

O

3.3V True CPU Clock Outputs. This pin is programmable through strapping pin7,

SELP4_K7#. If SELP4_K7# = 1, this pin is configured as the CPUT Clock Output.

If SELP4_K7# = 0, this pin is configured as the CPUOD_T Open Drain Clock Output.

See Table 1.

52

CPUC/CPUOD_C

VDDC

O

3.3V Complementary CPU Clock Outputs. This pin is programmable through

strapping pin7, SELP4_K7#. If SELP4_K7# = 1, this pin is configured as the CPUC

Clock Output. If SELP4_K7# = 0, this pin is configured as the CPUOD_C Open

Drain Clock Output. See Table 1.

14,15,17

PCI (3:5)

VDDPCI

O

PCI Clock Outputs. Are synchronous to CPU clocks. See Table 1.

48,49

CPUCS_T/C

VDDI

O

2.5V CPU Clock Outputs for Chipset. See Table 1.

18

CPU_STP#

VDDPCI

I

PU

If pin 6 is pulled down at power on reset, then this pin becomes CPU_STP#. When

CPU_STP# is asserted LOW, then both of the CPU signals stop at the next HIGH

to LOW transition or stays LOW if it already is LOW. This does not stop the CPUCS

signals.

10

FS1/PCI_F

VDDPCI

I/O

PD

Power-on Bidirectional Input/Output. At power-up, FS1 is the input. When the

power supply voltage crosses the input threshold voltage, FS1 state is latched and

this pin becomes PCI_F clock output.

20

FS3/48M

VDD48M

I/O

PD

Power-on Bidirectional Input/Output. At power-up, FS3 is the input. When the

power supply voltage crosses the input threshold voltage, FS3 state is latched and

this pin becomes 48M, a USB clock output.

11

PCI1

VDDPCI

O

PCI Clock Output.

21

FS2/24_48M

VDD48M

I/O

PD

Power-on Bidirectional Input/Output. At power-up, FS2 is the input. When the

power supply voltage crosses the input threshold voltage, FS2 state is latched and

this pin becomes 24_48M, a SIO programmable clock output.

Note:

2.

PU = internal pull-up. PD = internal pull-down. Typically = 250 k

(range 200 k

to 500 k

).

CY28347

Document #: 38-07352 Rev. *C

Page 3 of 22

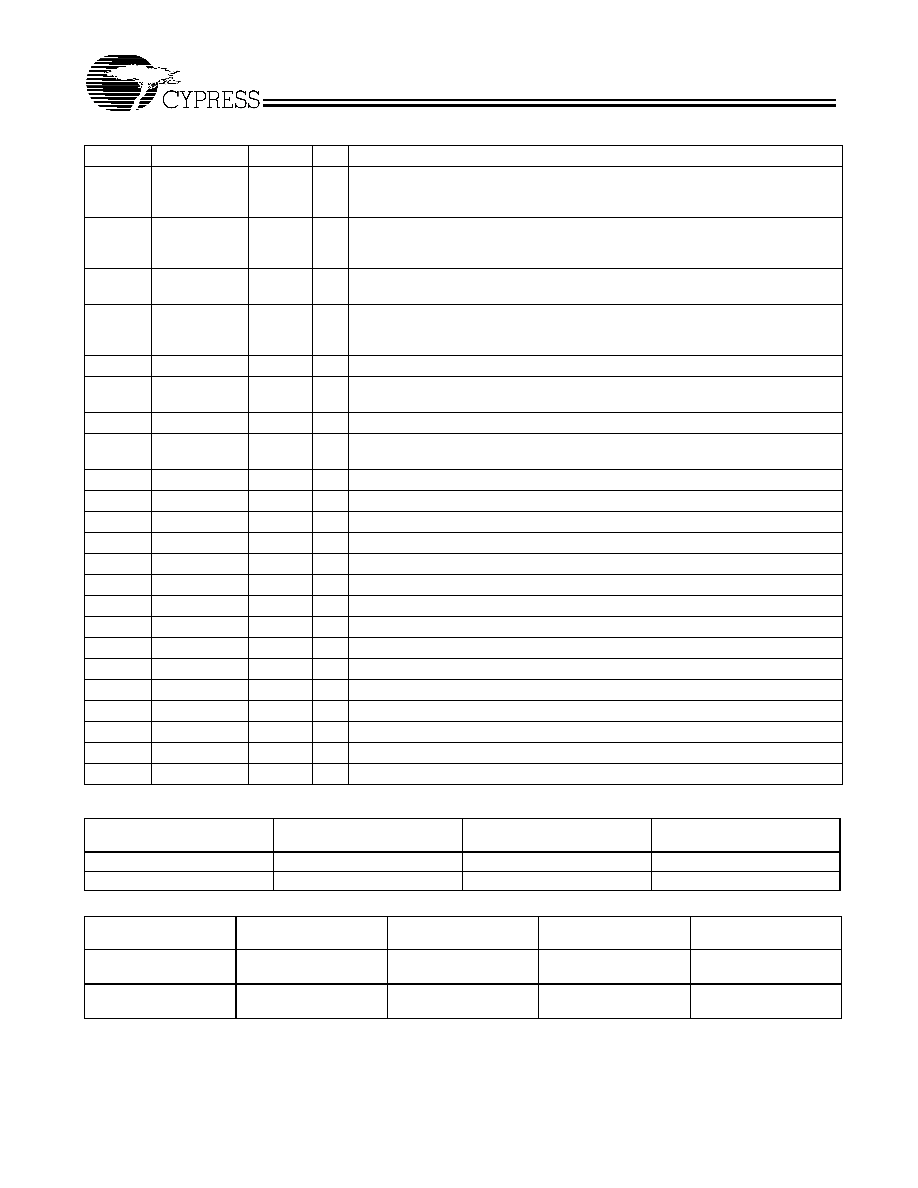

6

MODE/AGP0

VDDAGP I/O

PU

Power-on Bidirectional Input/Output. At power-up, MODE is an input and

becomes AGP0 output after the power supply voltage crosses the input threshold

voltage. Must have 10K

resistor to V

SS

. See Table 2.

8

PCI_STP#

VDDAGP

I

PU

If pin 6 is pulled down at power on reset, then this pin becomes PCI_STP#.

When PCI_STP# is asserted LOW, then all of the PCI signals, except the PCI_F,

stops at the next HIGH to LOW transition or stays LOW if it already is LOW.

25

IREF

I

Current reference programming input for CPU buffers. A precise resistor is

attached to this pin, which is connected to the internal current reference.

28

SDATA

I/O Serial Data Input. Conforms to the SMBus specification of a Slave

Receive/Transmit device. It is an input when receiving data. It is an open drain output

when acknowledging or transmitting data.

27

SCLK

I

Serial Clock Input. Conforms to the SMBus specification.

26

PD#

I

PU

When PD# is asserted LOW, the device enters power down mode. See power

management function.

45

BUF_IN

I

2.5V CMOS type input to the DDR differential buffers.

46

FBOUT

O

This is the single-ended, SDRAM buffered output of the signal applied at

BUF_IN. It is in phase with the DDRT(0:5) signals.

5

VDDAGP

3.3V power supply for AGP clocks.

51

VDDC

3.3V power supply for CPU (T: C) clocks.

16

VDDPCI

3.3V power supply for PCI clocks.

55

VDDR

3.3V power supply for REF clock.

50

VDDI

2.5V power supply for CPUCS_T/C clocks.

22

VDD48M

3.3V power supply for 48M.

23

VDD

3.3V Common power supply.

34,40

VDDD

2.5V power supply for DDR clocks.

9

VSSAGP

Ground for AGP clocks.

13

VSSPCI

Ground for PCI clocks.

54

VSSC

Ground for CPU (T:C) clocks.

33,39

VSSD

Ground for DDR clocks.

19

VSS48M

Ground for 48M clock.

47

VSSI

Ground for CPUCS_T/C clocks.

24

VSS

Common ground.

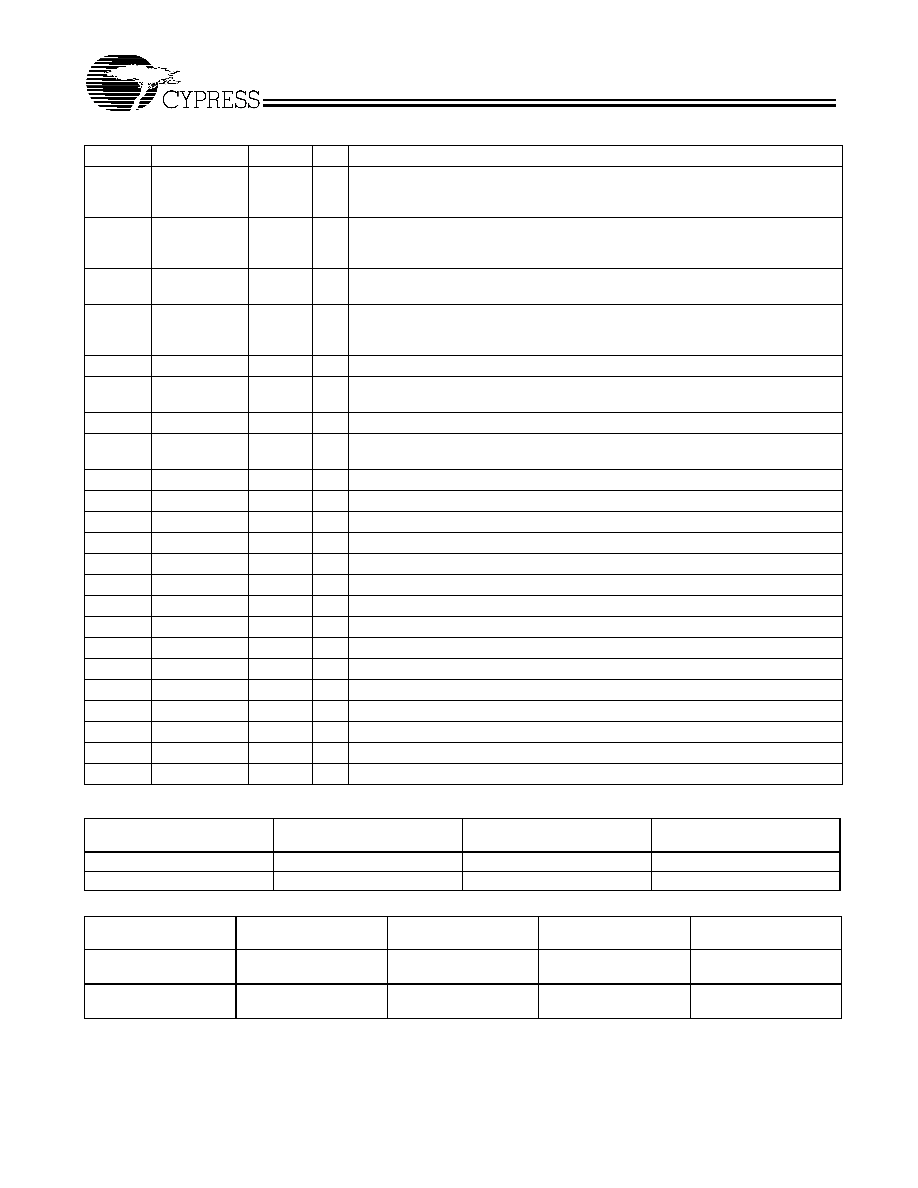

Pin Description

(continued)

[2]

Pin

Name

PWR

I/O

Description

Table 2. MODE Pin-Power Management Input Control

MODE, Pin 6

(Latched Input)

Pin 26

Pin 18

Pin 8

0

PD#

CPU_STP#

PCI_STP#

Invalid

Reserved

Reserved

Reserved

Table 3. Swing Select Functions Through Hardware

MULTSEL

Board Target

Trace/Term Z

Reference R,

IREF = VDD/(3*Rr)

Output Current

VOH@Z

0

50 Ohm

Rr = 221 1%,

IREF = 5.00 mA

IOH = 4* Iref

1.0V@50

1

50 Ohm

Rr = 475 1%,

IREF = 2.32 mA

IOH = 6* Iref

0.7V@50

CY28347

Document #: 38-07352 Rev. *C

Page 4 of 22

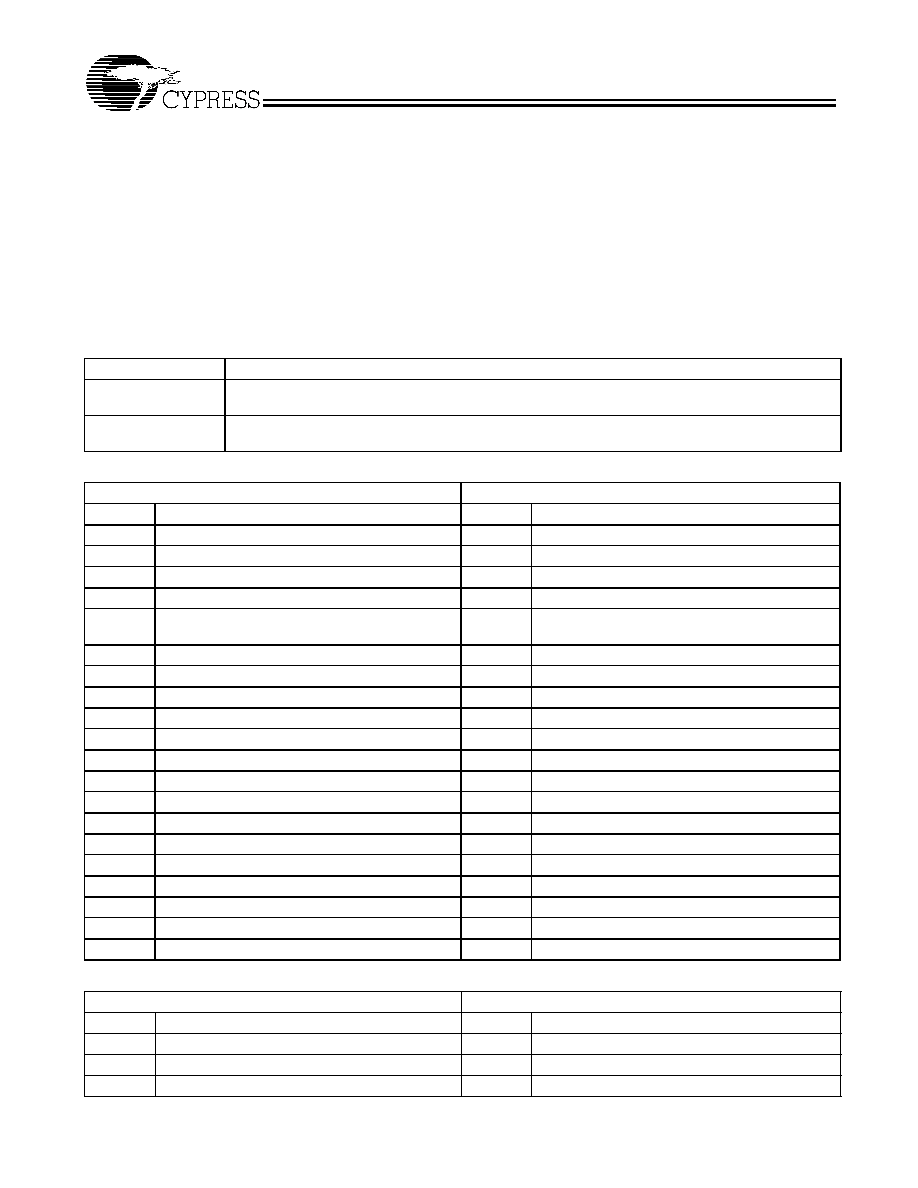

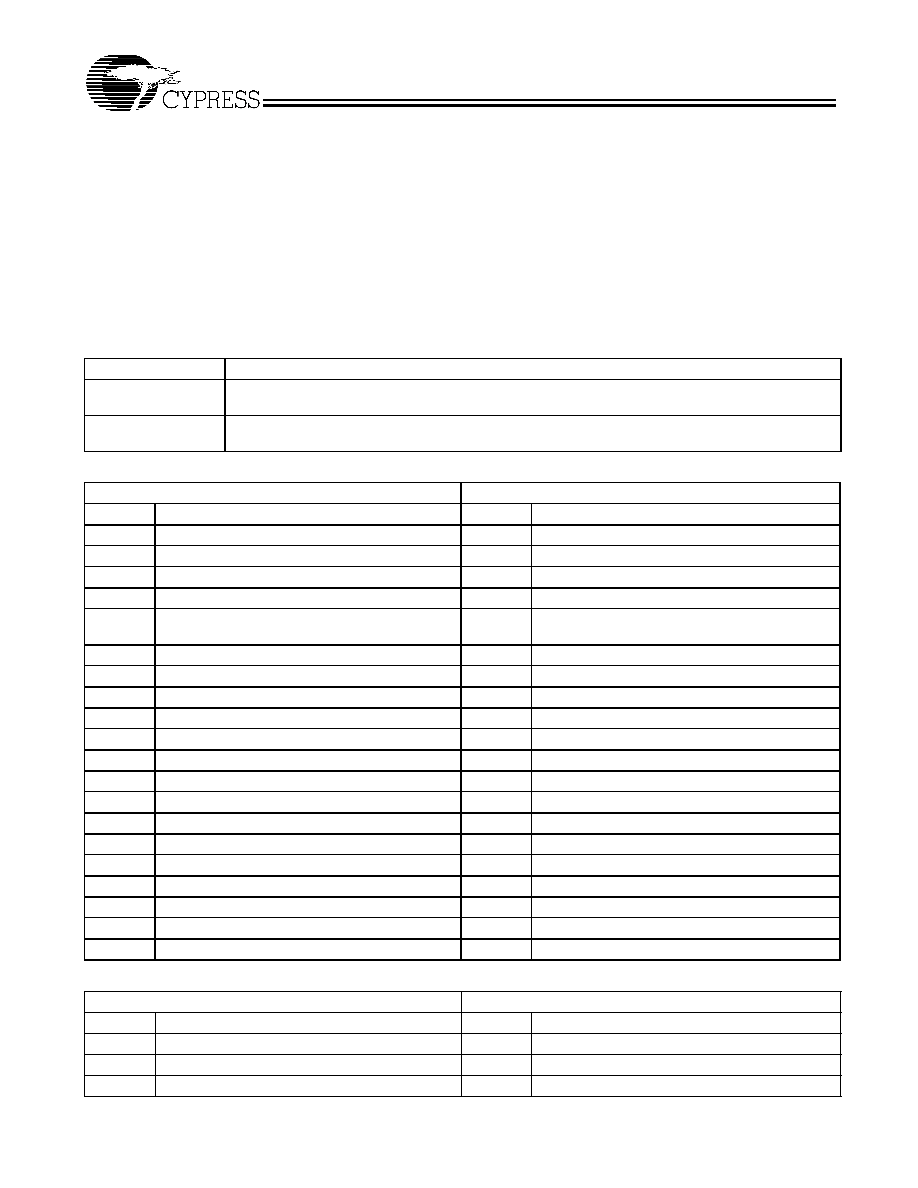

Serial Data Interface

To enhance the flexibility and function of the clock synthesizer,

a two-signal serial interface is provided. Through the Serial

Data Interface, various device functions such as individual

clock output buffers, etc., can be individually enabled or

disabled.

The registers associated with the Serial Data Interface

initializes to their default setting upon power-up, and therefore

use of this interface is optional. Clock device register changes

are normally made upon system initialization, if any are

required. The interface can also be used during system

operation for power management functions.

Data Protocol

The clock driver serial protocol accepts Byte Write, Byte Read,

Block Write, and Block Read operation from the controller. For

Block Write/Read operation, the bytes must be accessed in

sequential order from lowest to highest byte (most significant

bit first) with the ability to stop after any complete byte has

been transferred. For Byte Write and Byte Read operations,

the system controller can access individual indexed bytes. The

offset of the indexed byte is encoded in the command code,

as described in Table 4.

The Block Write and Block Read protocol is outlined in Table 5

while Table 6 outlines the corresponding Byte Write and Byte

Read protocol. The slave receiver address is 11010010 (D2H).

Table 4. Command Code Definition

Bit

Description

7

0 = Block Read or Block Write operation

1 = Byte Read or Byte Write operation

(6:0)

Byte offset for Byte Read or Byte Write operation. For Block Read or Block Write operations, these bits

should be "0000000"

Table 5. Block Read and Block Write Protocol

Block Write Protocol

Block Read Protocol

Bit

Description

Bit

Description

1

Start

1

Start

2:8

Slave address - 7 bits

2:8

Slave address - 7 bits

9

Write

9

Write

10

Acknowledge from slave

10

Acknowledge from slave

11:18

Command Code - 8 Bit "00000000" stands for block

operation

11:18

Command Code - 8 Bit "00000000" stands for block

operation

19

Acknowledge from slave

19

Acknowledge from slave

20:27

Byte Count - 8 bits

20

Repeat start

28

Acknowledge from slave

21:27

Slave address - 7 bits

29:36

Data byte 0 - 8 bits

28

Read

37

Acknowledge from slave

29

Acknowledge from slave

38:45

Data byte 1 - 8 bits

30:37

Byte count from slave - 8 bits

46

Acknowledge from slave

38

Acknowledge

....

Data Byte N/Slave Acknowledge...

39:46

Data byte from slave - 8 bits

....

Data Byte N - 8 bits

47

Acknowledge

....

Acknowledge from slave

48:55

Data byte from slave - 8 bits

....

Stop

56

Acknowledge

....

Data bytes from slave/Acknowledge

....

Data byte N from slave - 8 bits

....

Not Acknowledge

....

Stop

Table 6. Byte Read and Byte Write Protocol

Byte Write Protocol

Byte Read Protocol

Bit

Description

Bit

Description

1

Start

1

Start

2:8

Slave address - 7 bits

2:8

Slave address - 7 bits

9

Write

9

Write

CY28347

Document #: 38-07352 Rev. *C

Page 5 of 22

10

Acknowledge from slave

10

Acknowledge from slave

11:18

Command Code - 8 bits "1xxxxxxx" stands for byte

operation bit[6:0] of the command code represents

the offset of the byte to be accessed

11:18

Command Code - 8 bits "1xxxxxxx" stands for byte

operation bit[6:0] of the command code represents

the offset of the byte to be accessed

19

Acknowledge from slave

19

Acknowledge from slave

20:27

Data Byte from Master ≠ 8 Bits

20

Repeat start

28

Acknowledge from slave

21:27

Slave address - 7 bits

29

Stop

28

Read

29

Acknowledge from slave

30:37

Data byte from slave - 8 bits

38

Not Acknowledge

39

Stop

Table 6. Byte Read and Byte Write Protocol (continued)

Byte 0: Frequency Select Register

Bit

@Pup

Pin#

Name

Description

7

0

Reserved.

6

H/W Setting

21

FS2

For Selecting Frequencies see Table 1.

5

H/W Setting

10

FS1

For Selecting Frequencies see Table 1.

4

H/W Setting

1

FS0

For Selecting Frequencies see Table 1.

3

0

If this bit is programmed to "1," it enables WRITES to bits (6:4,1) for

selecting the frequency via software (SMBus)

If this bit is programmed to a "0" it enables only READS of bits

(6:4,1), which reflect the hardware setting of FS(0:3).

2

H/W Setting

11

Reserved

Reserved

1

H/W Setting

20

FS3

For Selecting frequencies in Table 1.

0

H/W Setting

7

SELP4_K7#

Only for reading the hardware setting of the CPU interface mode,

status of SELP4_K7# strapping.

Byte 1: CPU Clocks Register

Bit

@Pup

Pin#

Name

Description

7

0

SSMODE

0 = Down Spread. 1 = Center Spread. See Table 9.

6

1

SSCG

1 = Enable (default). 0 = Disable

5

1

SST1

Select spread bandwidth. See Table 9.

4

1

SST0

Select spread bandwidth. See Table 9.

3

1

48,49

CPUCS_T/C_ EN#

1 = output enabled (running). 0 = output disabled asynchronously

in a LOW state.

2

1

53,52

CPUOD_T/C_EN#

1 = output enabled (running). 0 = output disable asynchronously

in a LOW state.

1

0

53,52

CPUT/C_PD_CNTRL

In K7 mode, this bit is ignored. In P4 mode, when PD# asserted

LOW, 0 = drive CPUT to 2xIref and CPUC LOW and

1 = three-state CPUT and CPUC.

0

1

11

MULT0

Only For reading the hardware setting of the Pin11 MULT0 value.

Byte 2: PCI Clock Register

Bit

@Pup

Pin#

Name

Description

7

0

PCI_DRV

PCI clock output drive strength 0 = Normal, 1 = increase the drive

strength 20%.

6

1

10

PCI_F

1 = output enabled (running). 0 = output disabled asynchronously

in a LOW state.

5

1

Reserved, set = 1.