CPLDs at FPGA DensitiesTM

Delta39KTM ISRTM

CPLD Family

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

∑

CA 95134

∑

408-943-2600

Document #: 38-03039 Rev. *H

Revised August 1, 2003

Features

∑ High density

-- 30K to 200K usable gates

-- 512 to 3072 macrocells

-- 136 to 428 maximum I/O pins

-- Twelve dedicated inputs including four clock pins,

four global I/O control signal pins and four JTAG

interface pins for boundary scan and reconfig-

urability

∑ Embedded memory

-- 80K to 480K bits embedded SRAM

∑ 16K to 96K bits of (dual-port) channel memory

∑ High speed ≠ 233-MHz in-system operation

∑ AnyVoltTM

interface

-- 3.3V, 2.5V,1.8V, and 1.5V I/O capability

∑ Low-power operation

-- 0.18-mm six-layer metal SRAM-based logic process

-- Full-CMOS implementation of product term array

-- Standby current as low as 5mA

∑ Simple timing model

-- No penalty for using full 16 product terms/macrocell

-- No delay for single product term steering or sharing

∑ Flexible clocking

-- Spread AwareTM PLL drives all four clock networks

∑ Allows 0.6% spread spectrum input clocks

∑ Several multiply, divide and phase shift options

-- Four synchronous clock networks per device

-- Locally generated product term clock

-- Clock polarity control at each register

∑ Carry-chain logic for fast and efficient arithmetic opera-

tions

∑ Multiple I/O standards supported

-- LVCMOS (3.3/3.0/2.5/1.8V), LVTTL, 3.3V PCI, SSTL2

(I-II), SSTL3 (I-II), HSTL (I-IV), and GTL+

∑ Compatible with NOBLTM, ZBTTM, and QDRTM SRAMs

∑ Programmable slew rate control on each I/O pin

∑ User-programmable Bus Hold capability on each I/O pin

∑ Fully 3.3V PCI-compliant (to 66-MHz 64-bit PCI spec,

rev. 2.2)

∑ CompactPCI hot swap ready

∑ Multiple package/pinout offering across all densities

-- 208 to 676 pins in PQFP, BGA, and FBGA packages

-- Simplifies design migration across density

-- Self-BootTM solution in BGA and FBGA packages

∑ In-System ReprogrammableTM (ISRTM)

-- JTAG-compliant on-board programming

-- Design changes do not cause pinout changes

∑ IEEE1149.1 JTAG boundary scan

Development Software

∑ Warp

Æ

-- IEEE 1076/1164 VHDL or IEEE 1364 Verilog context

sensitive editing

-- Active-HDL FSM graphical finite state machine editor

-- Active-HDL SIM post-synthesis timing simulator

-- Architecture Explorer for detailed design analysis

-- Static Timing Analyzer for critical path analysis

-- Available on Windows

95/98/2000/XPTM and

Windows NTTM for $99

-- Supports all Cypress programmable logic products

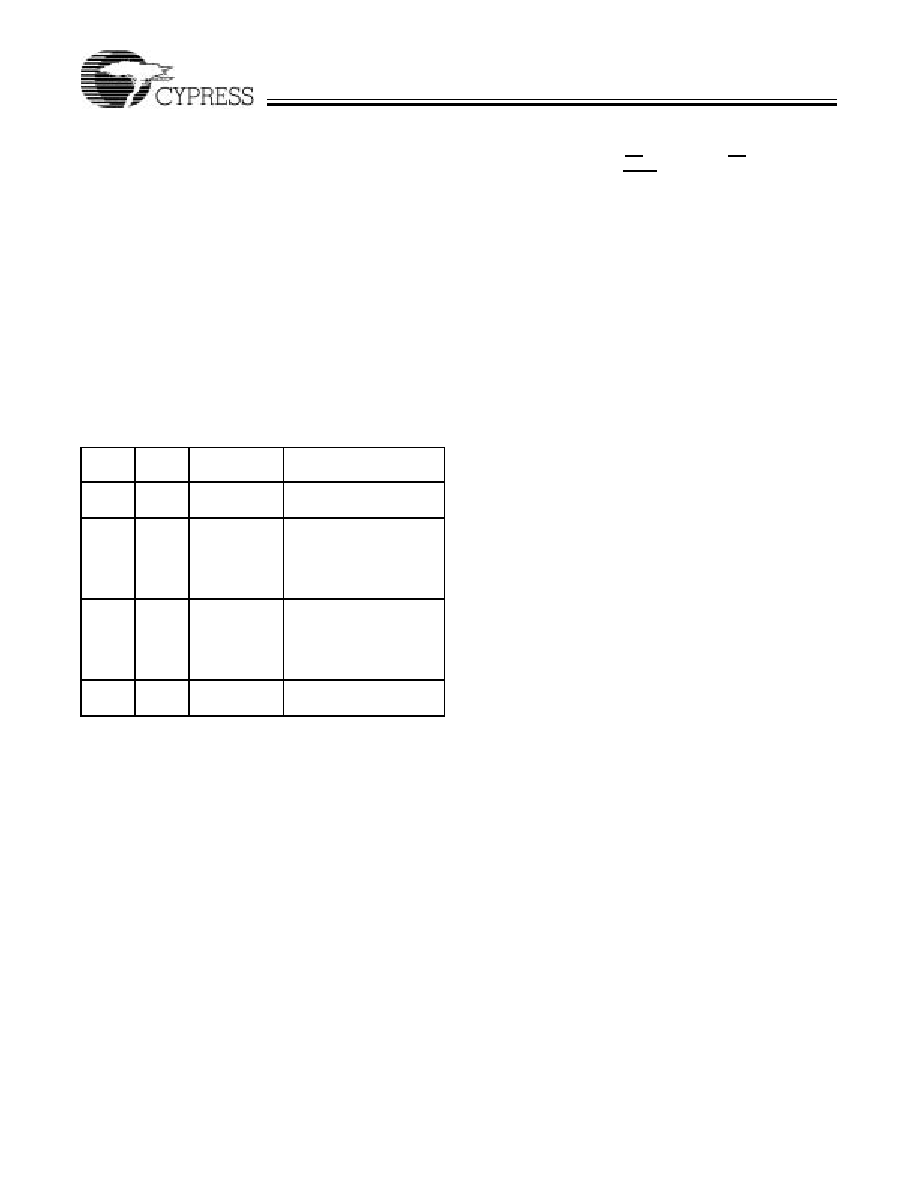

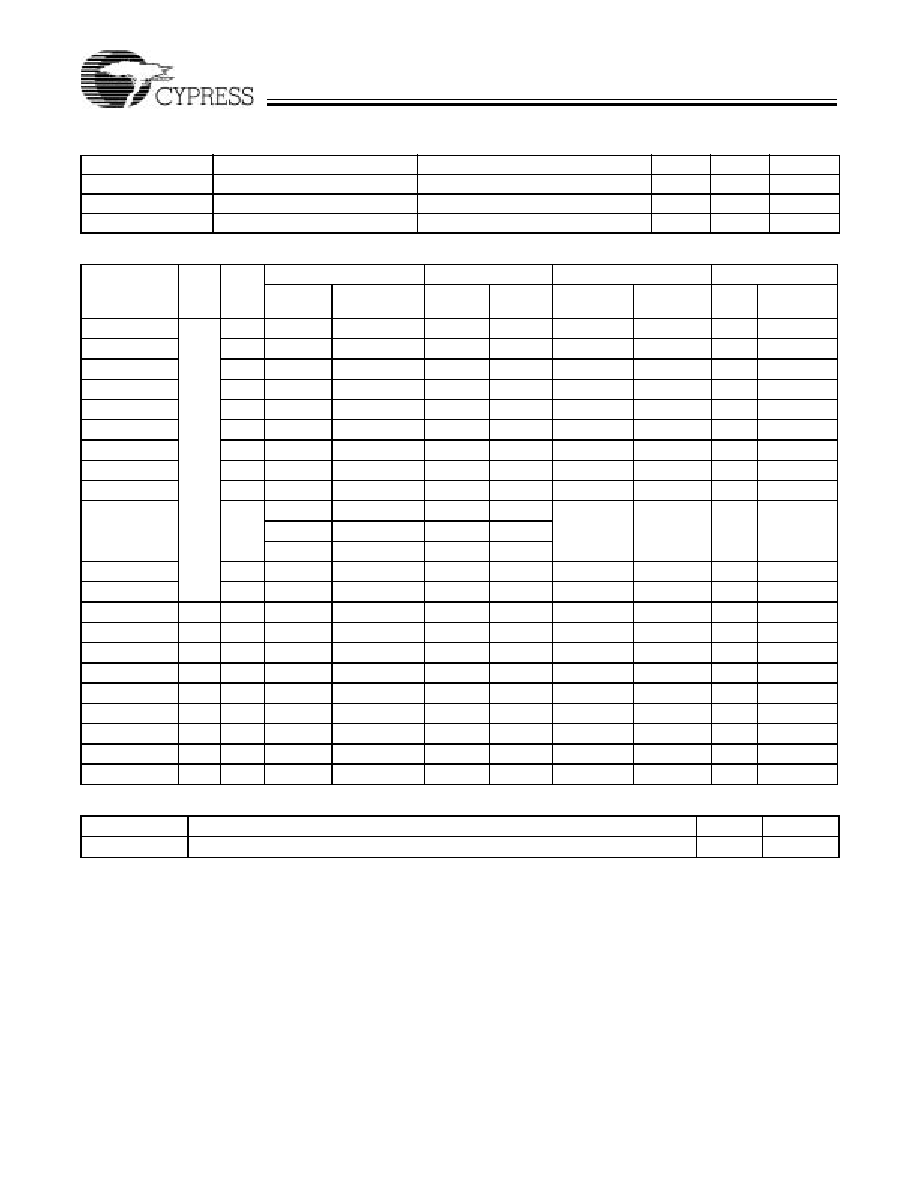

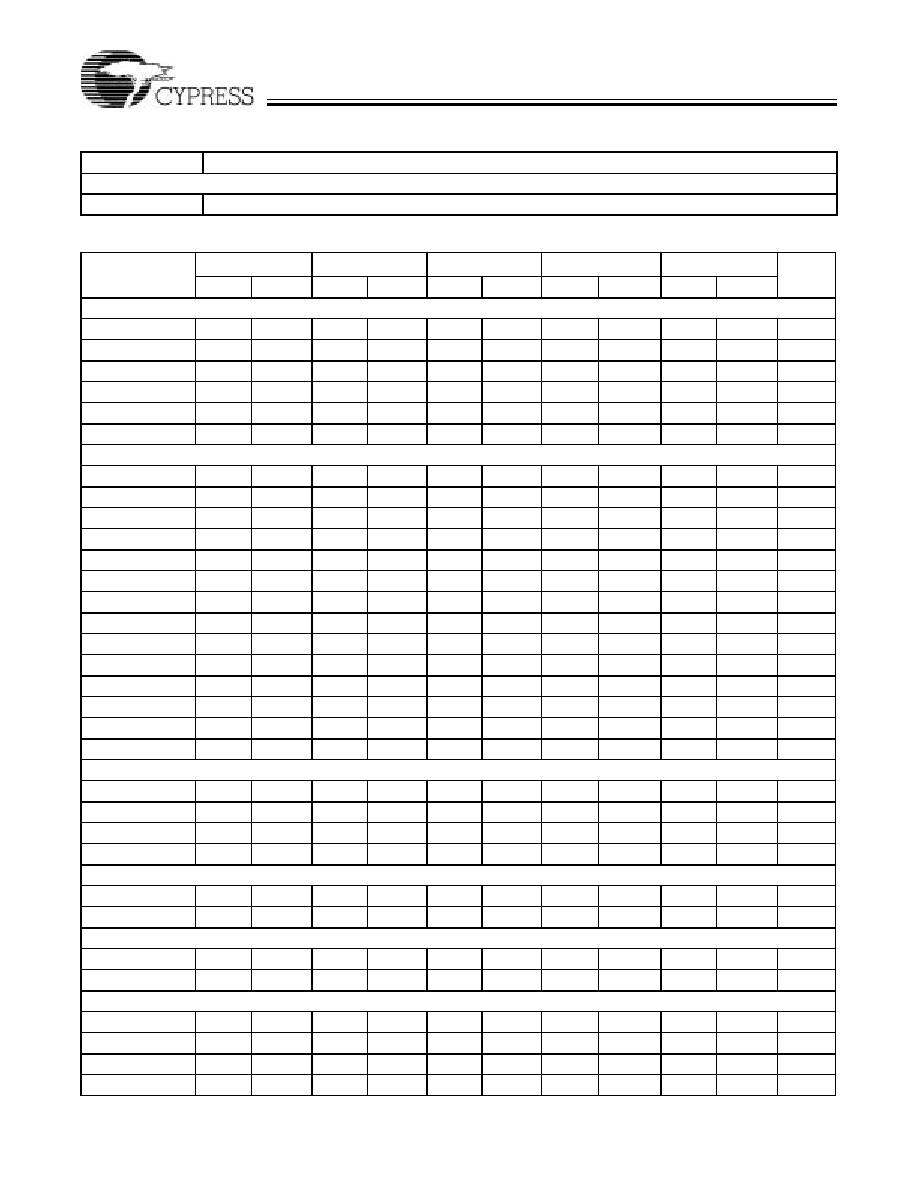

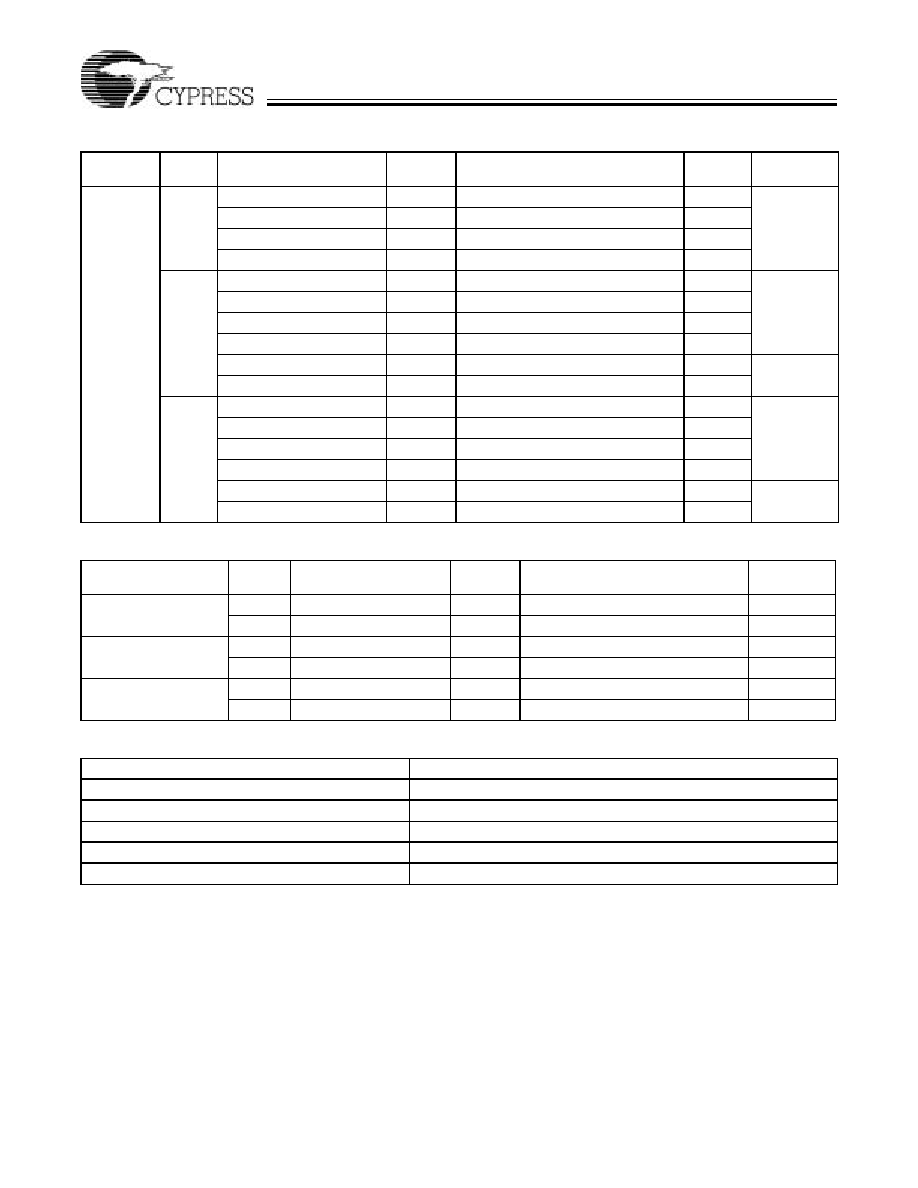

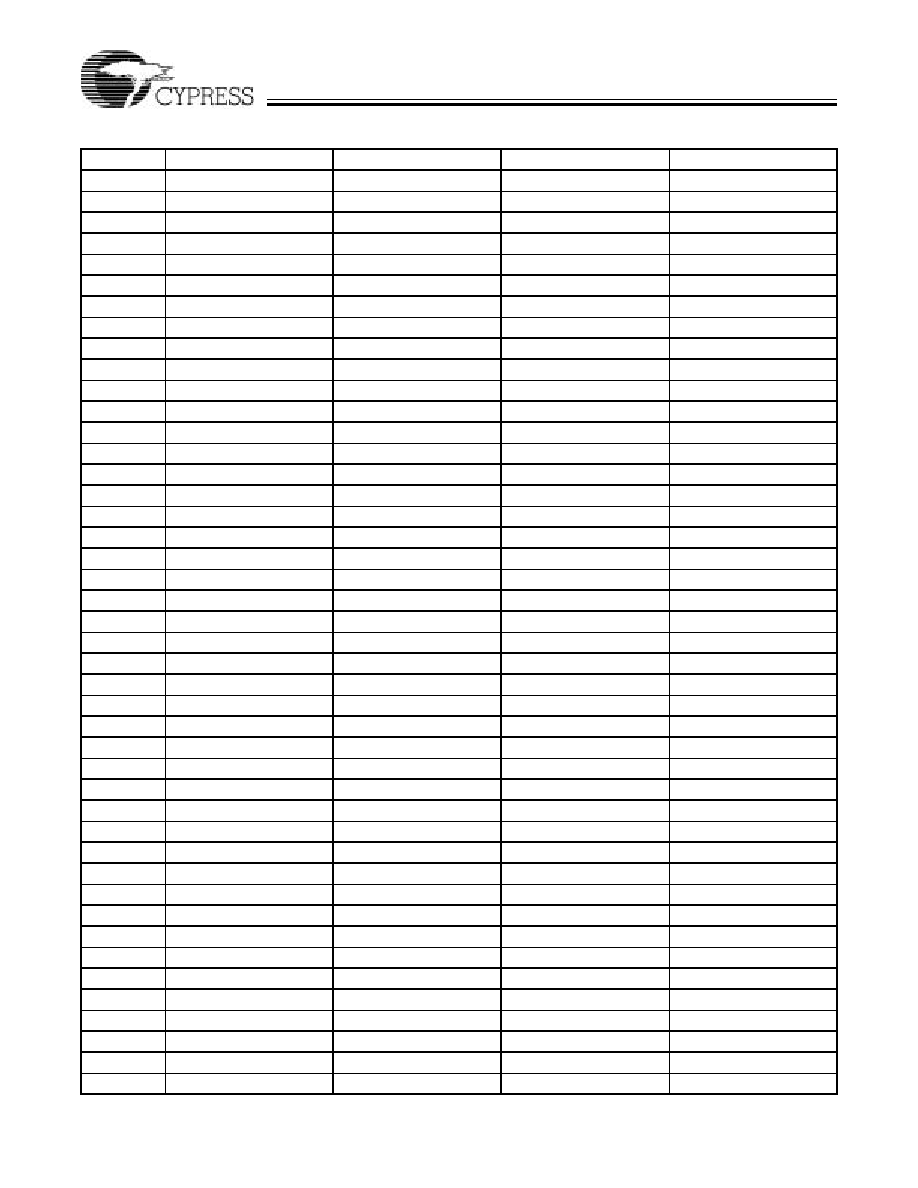

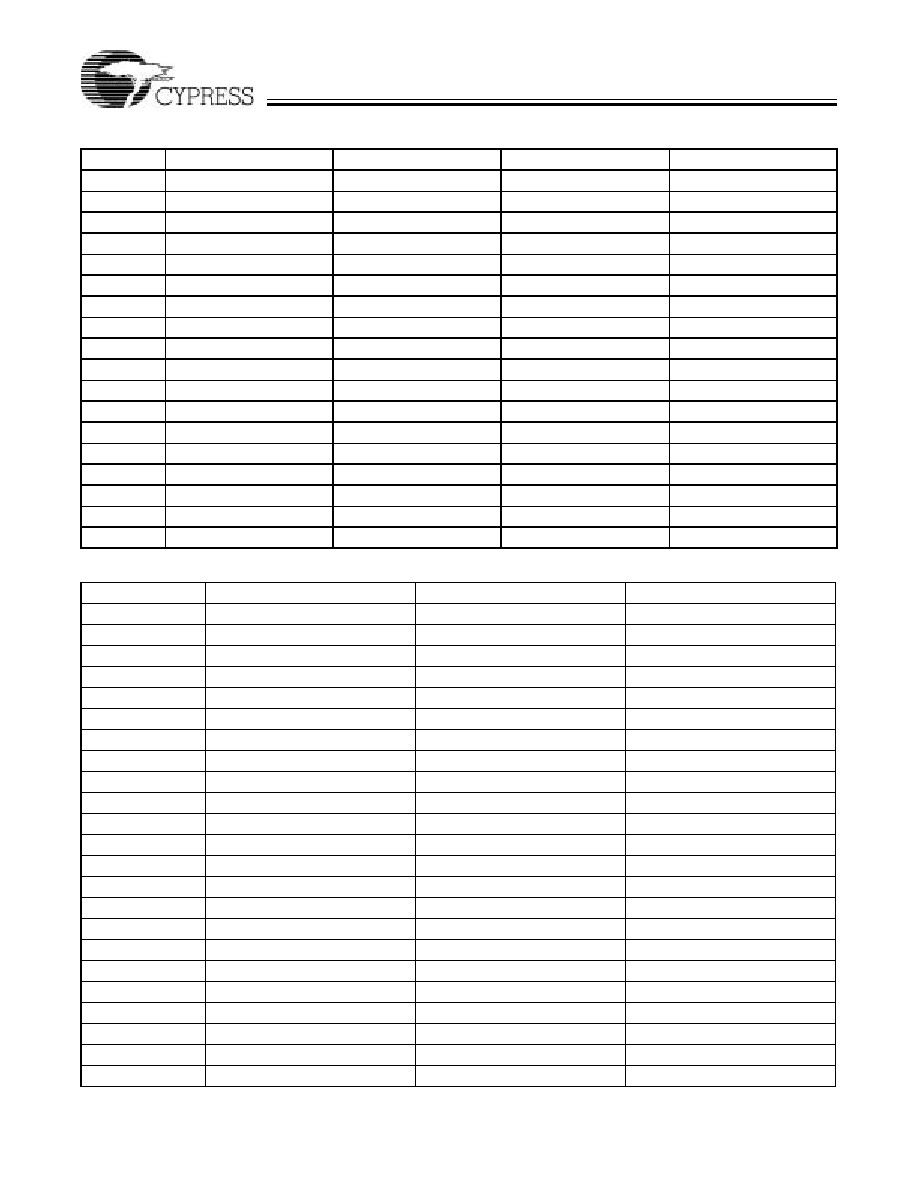

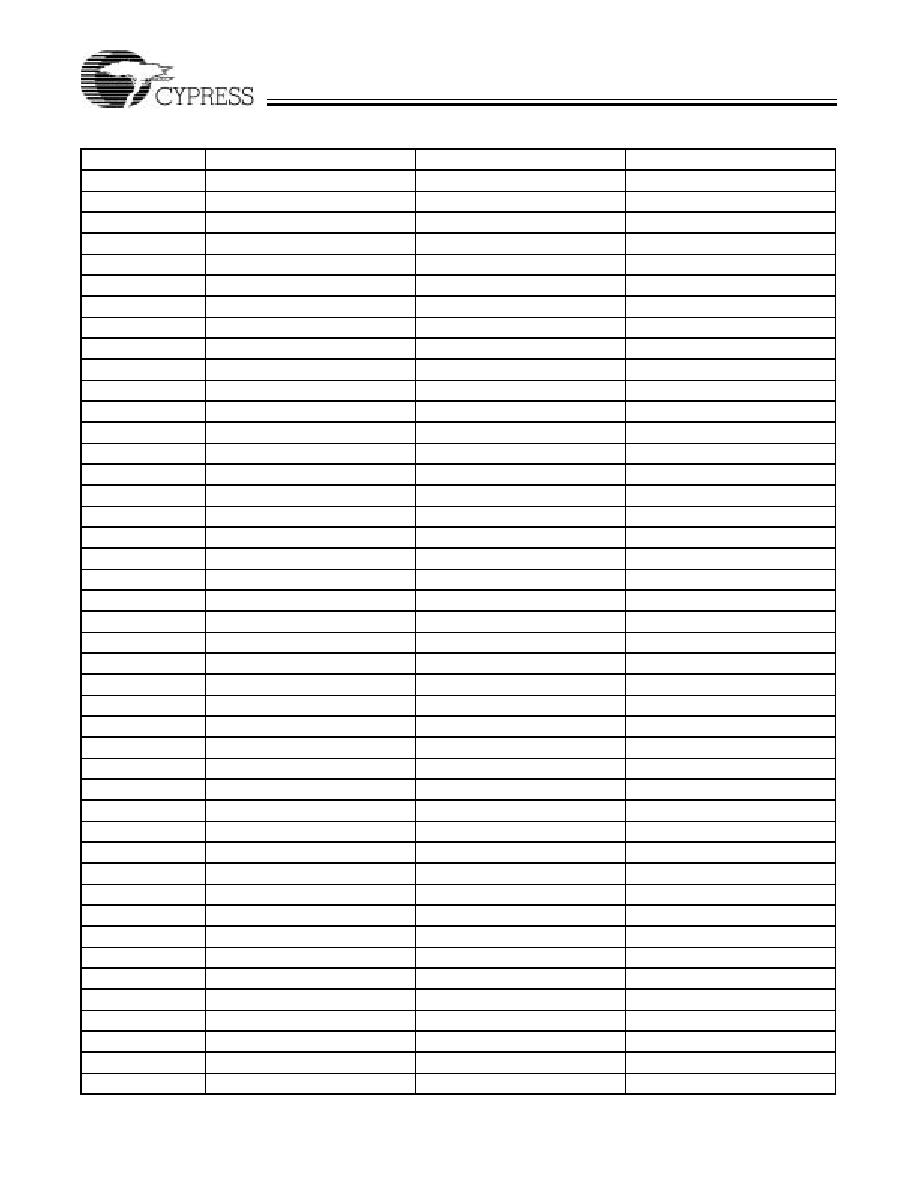

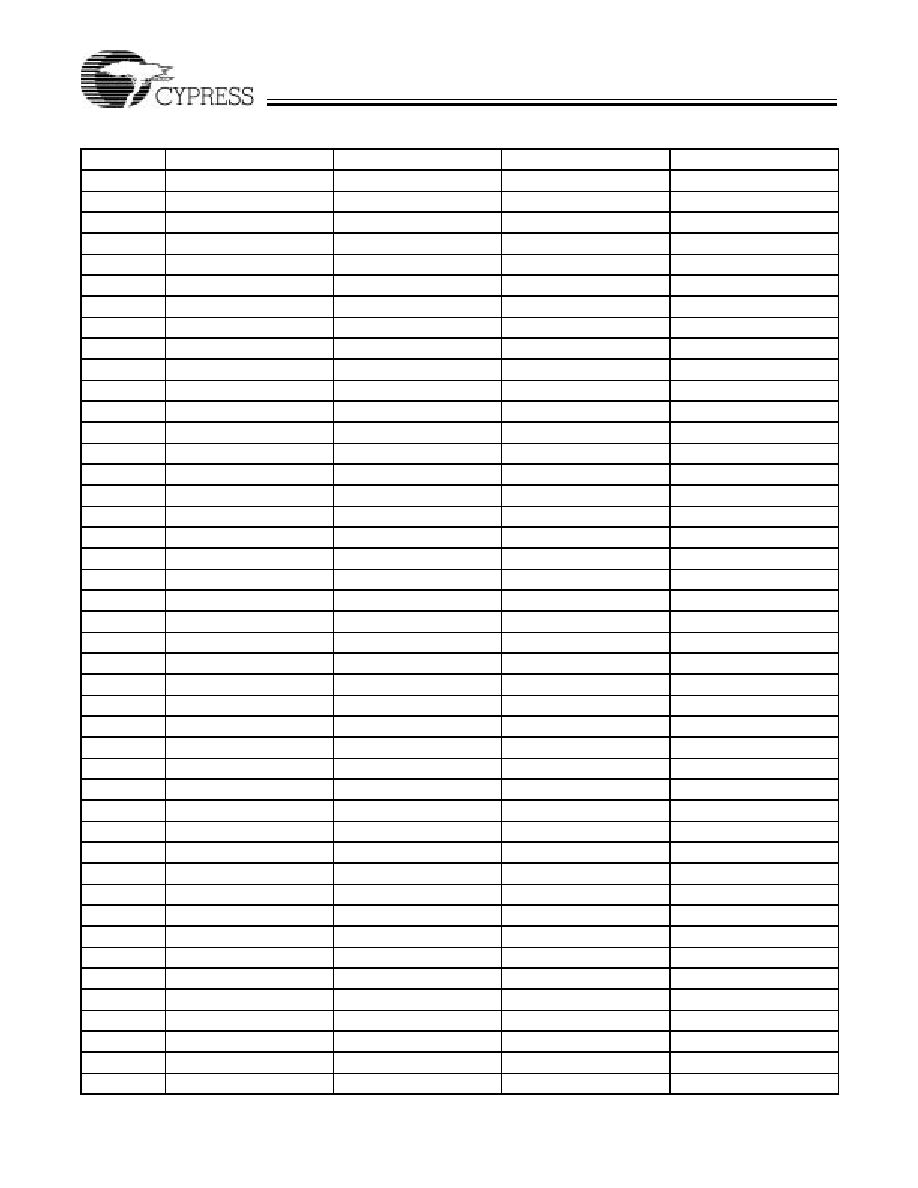

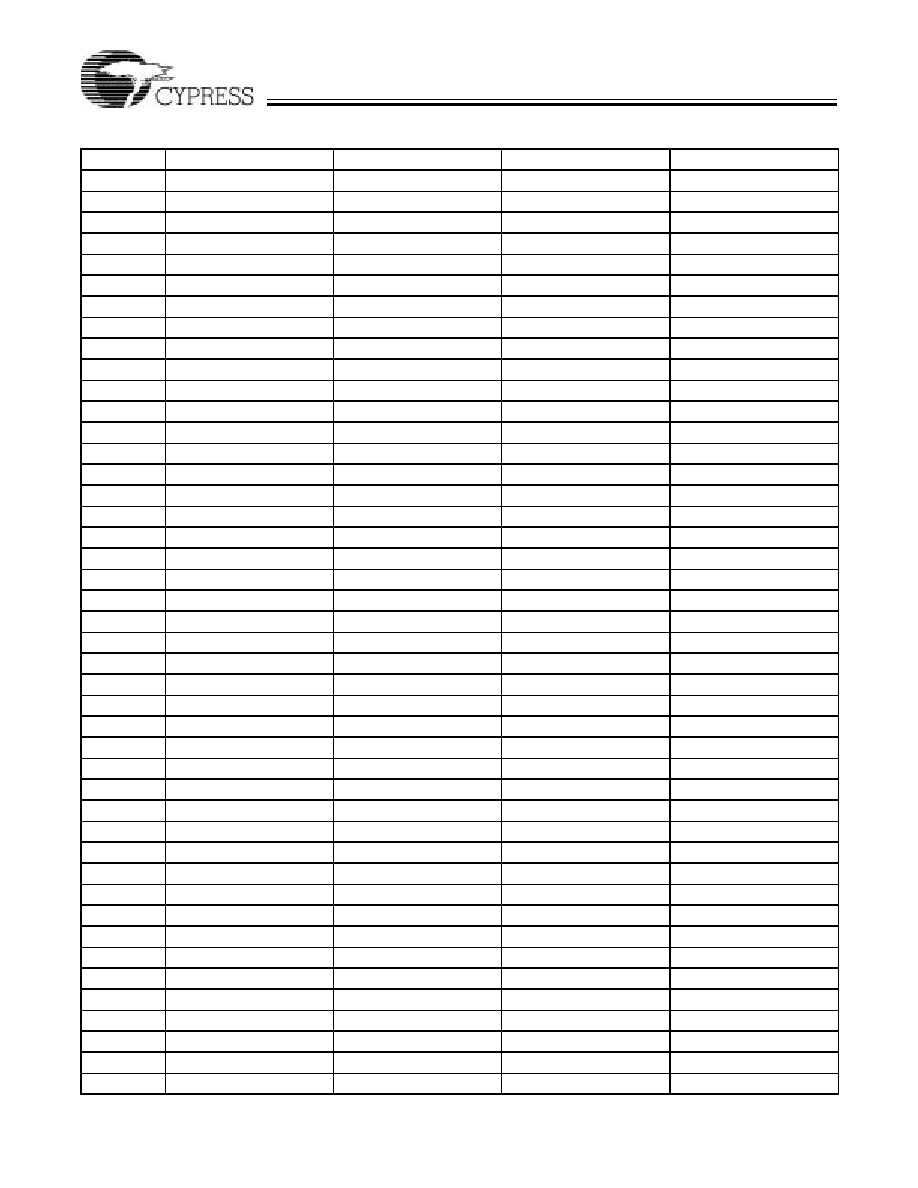

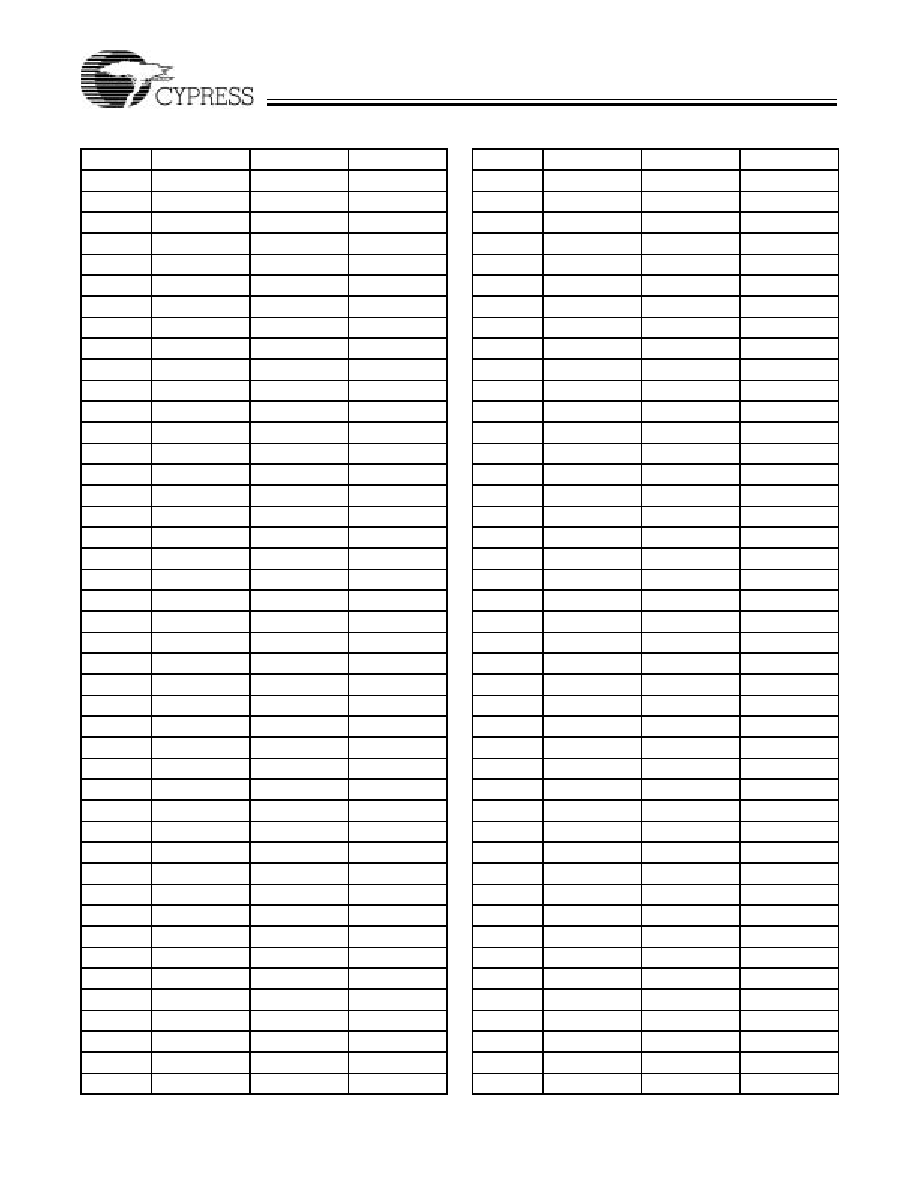

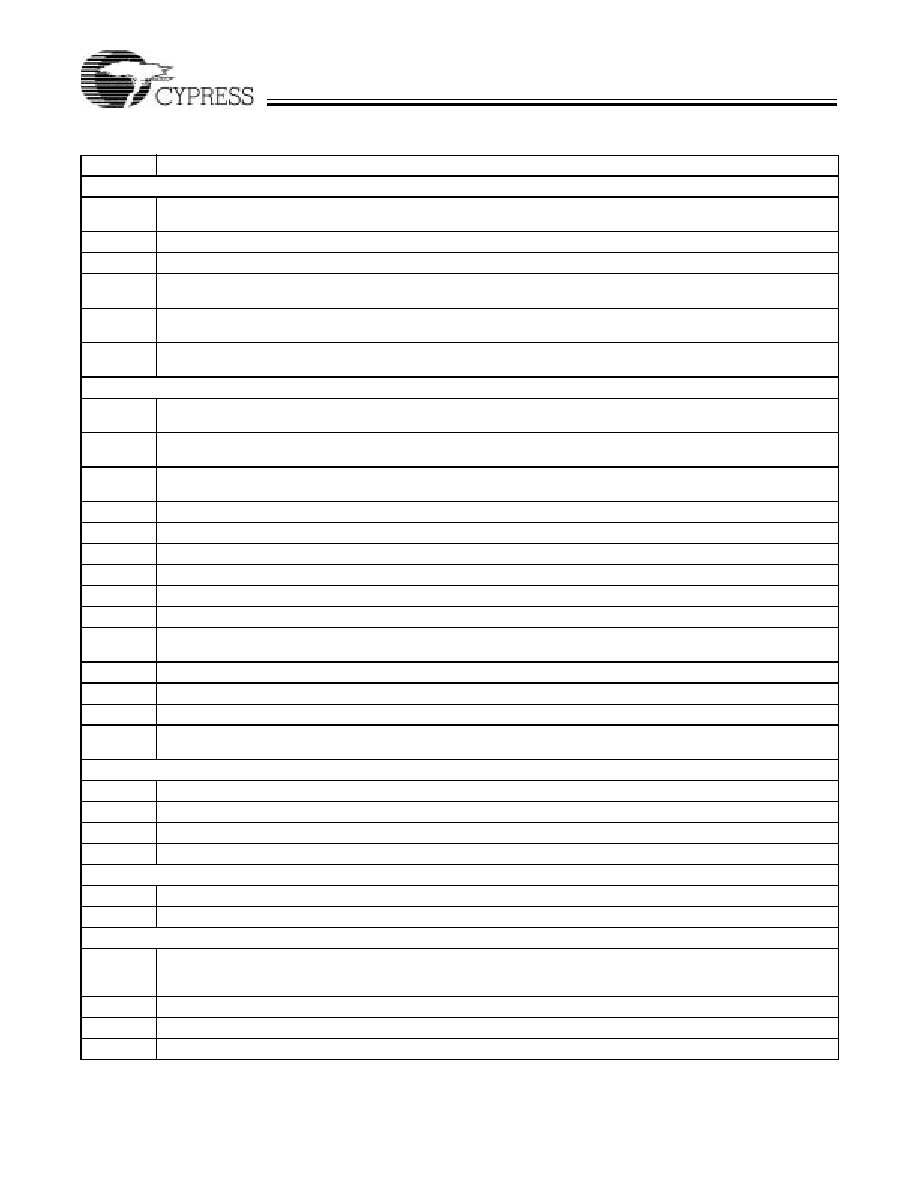

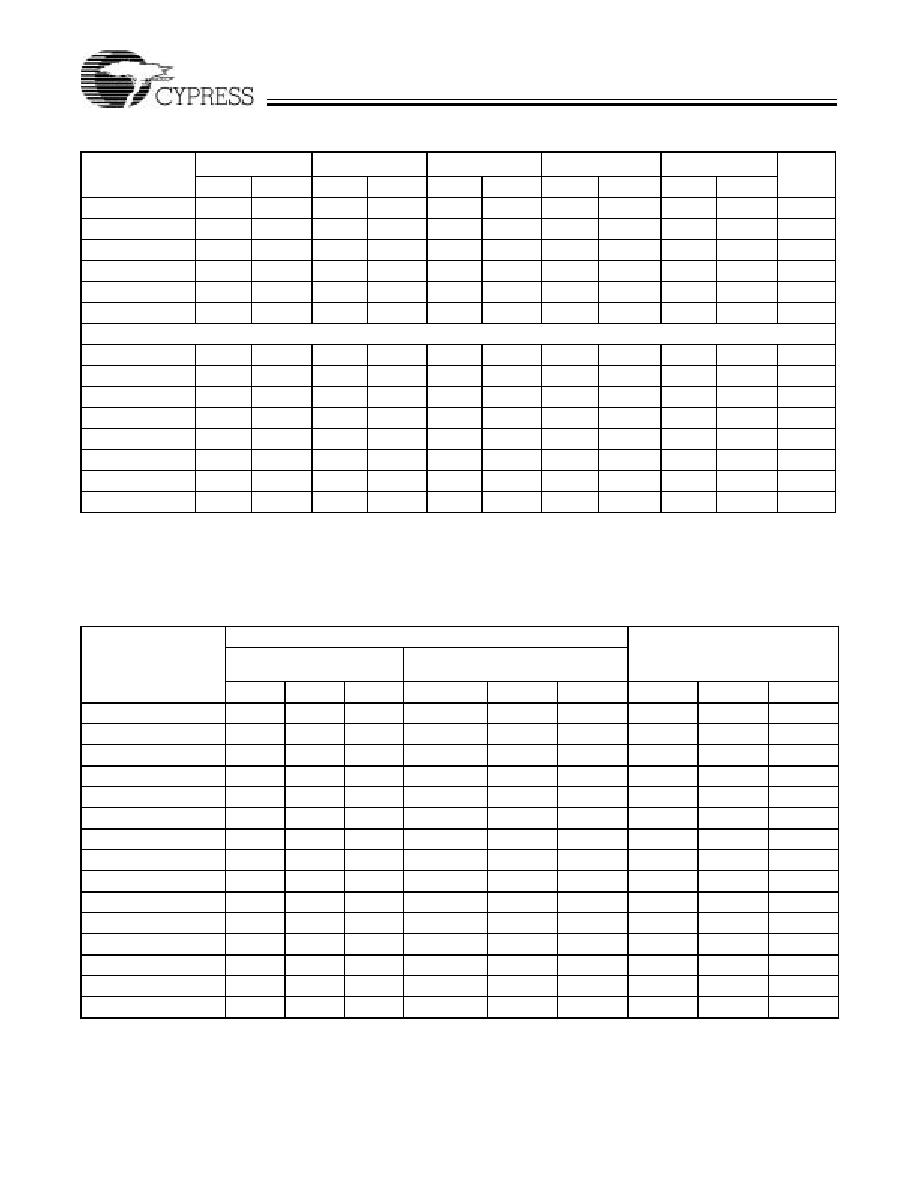

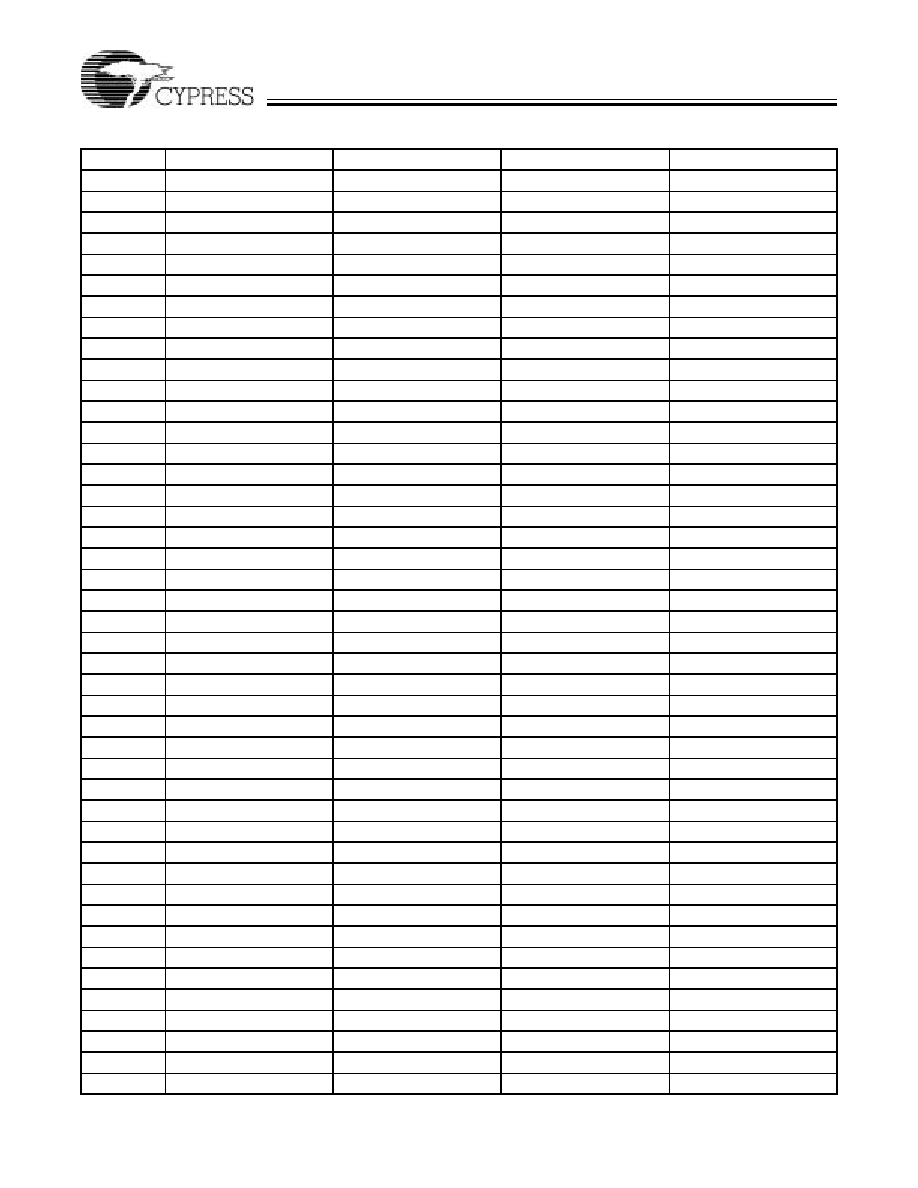

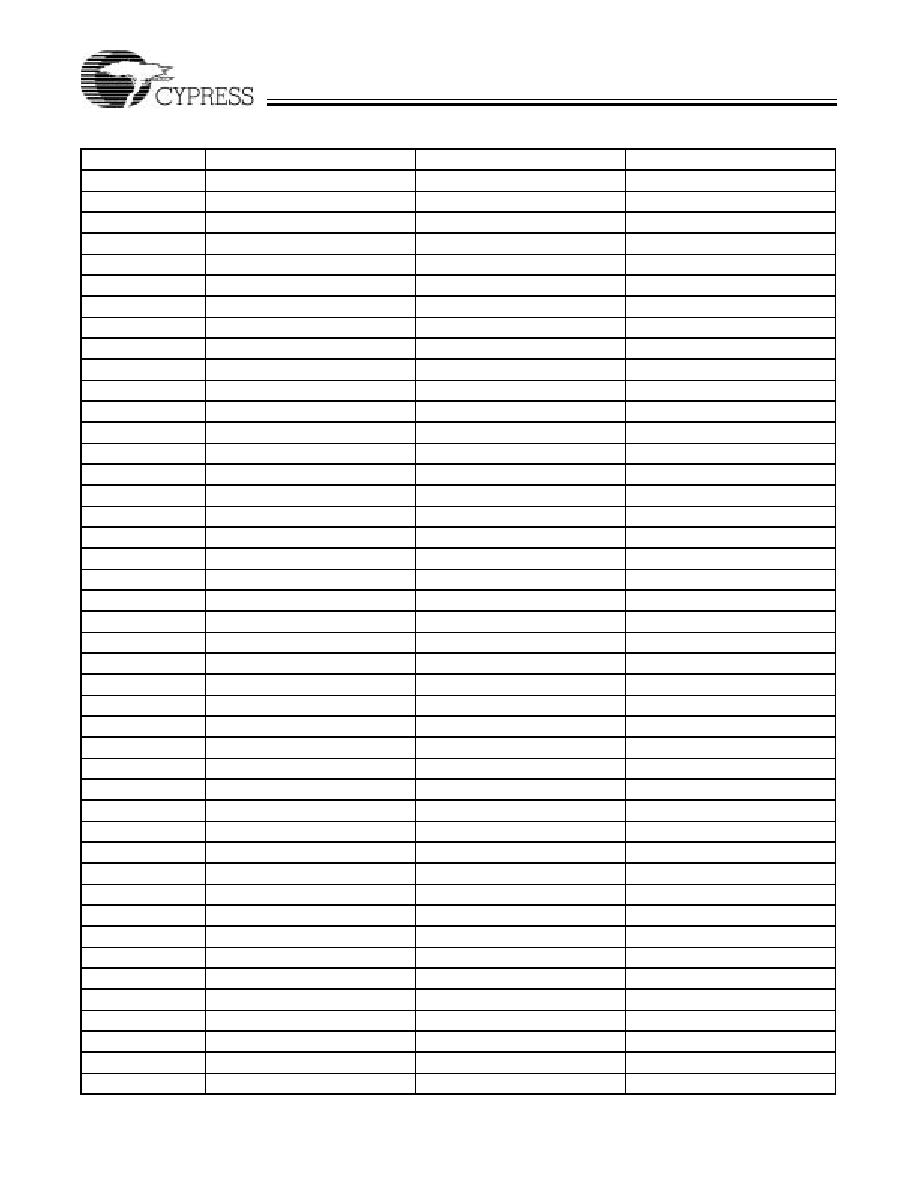

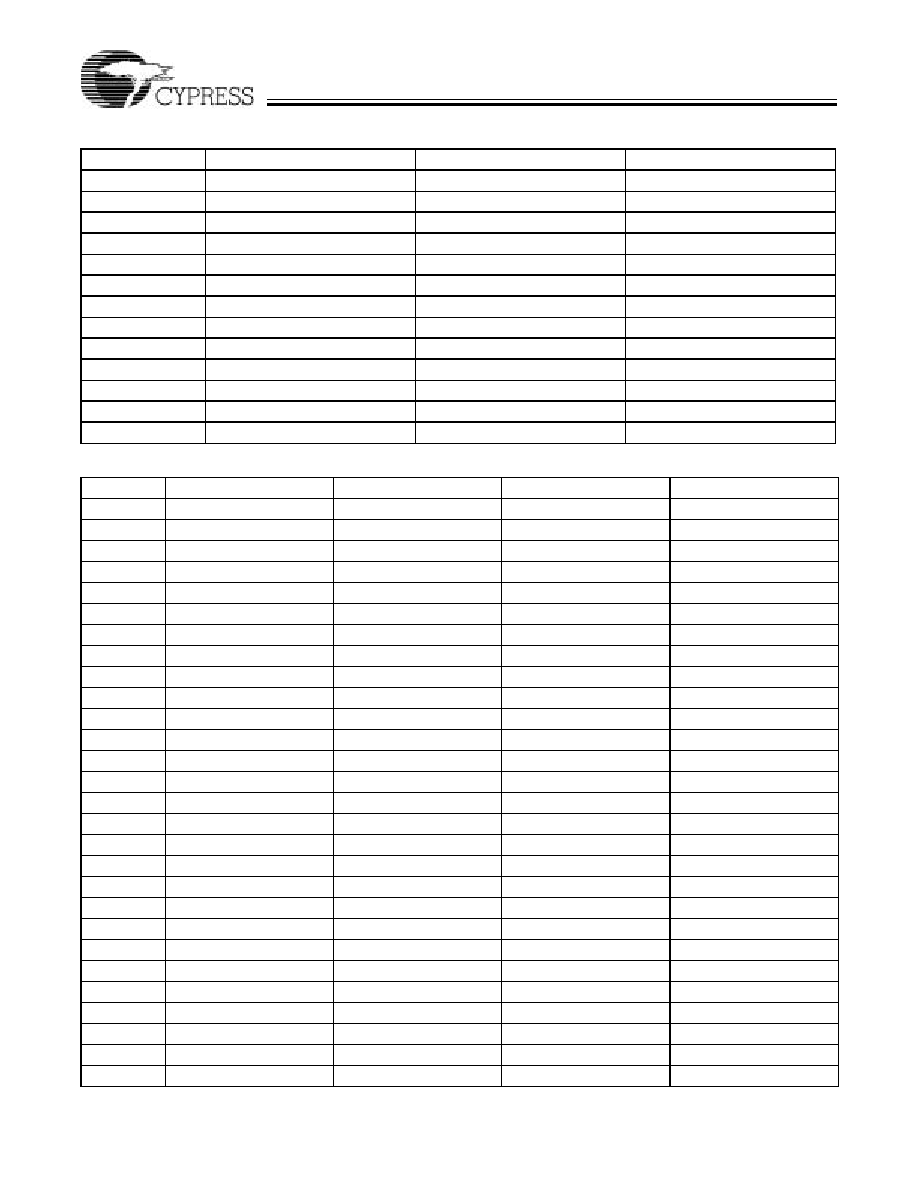

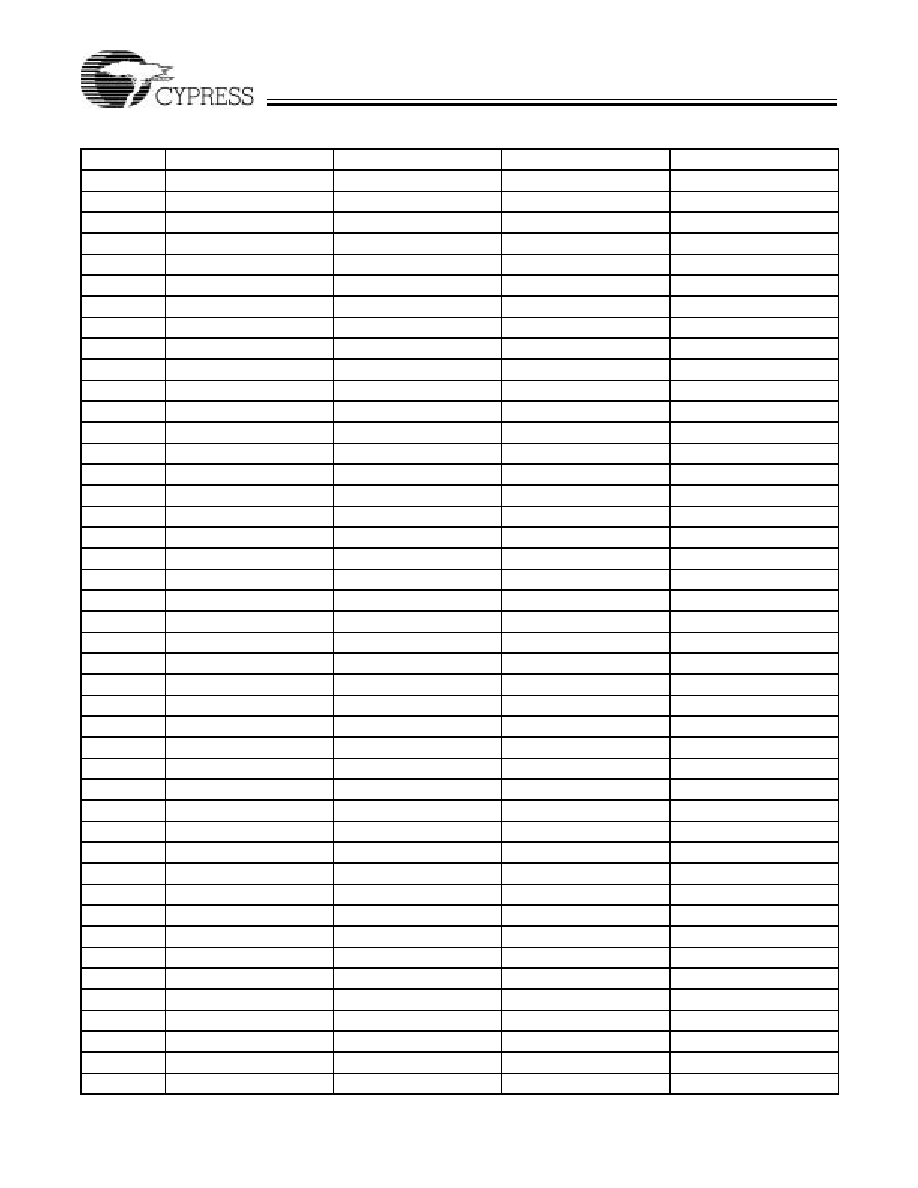

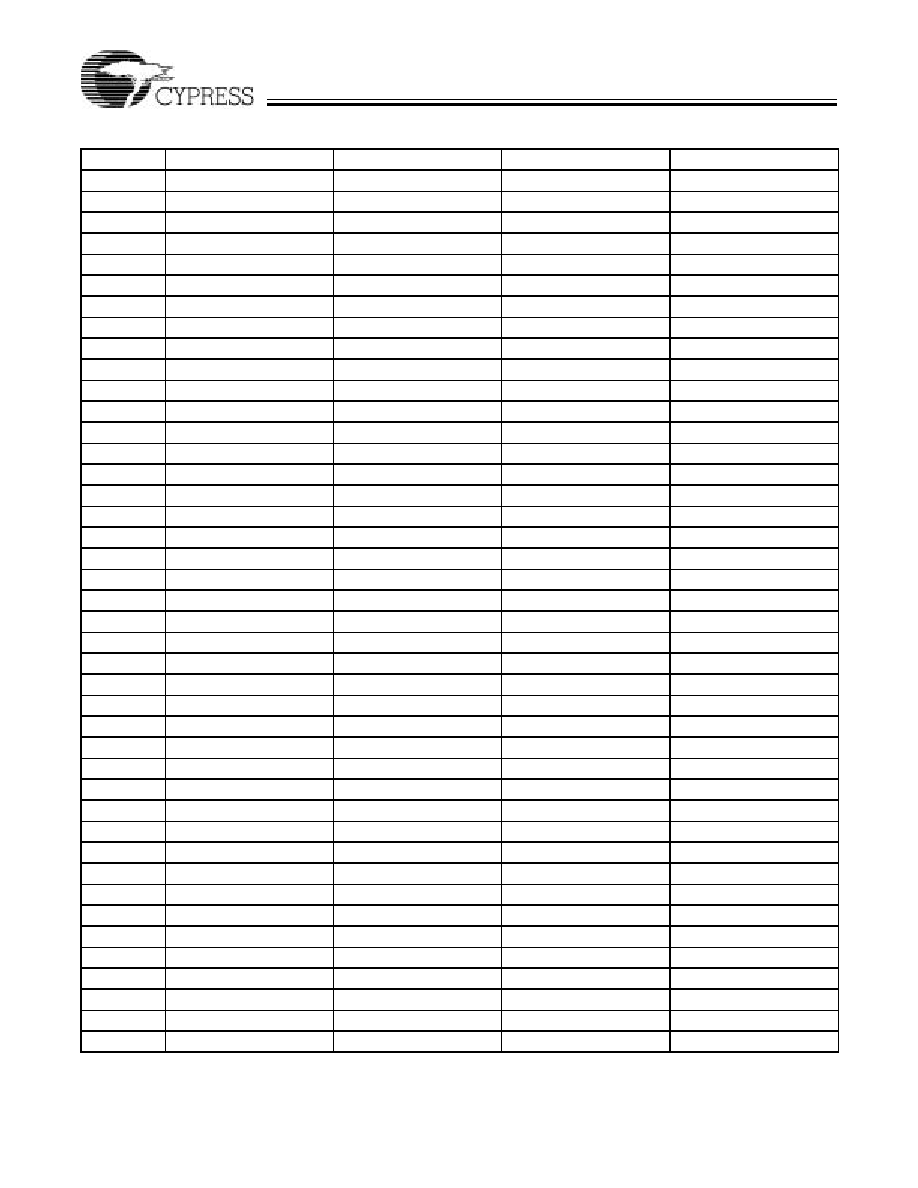

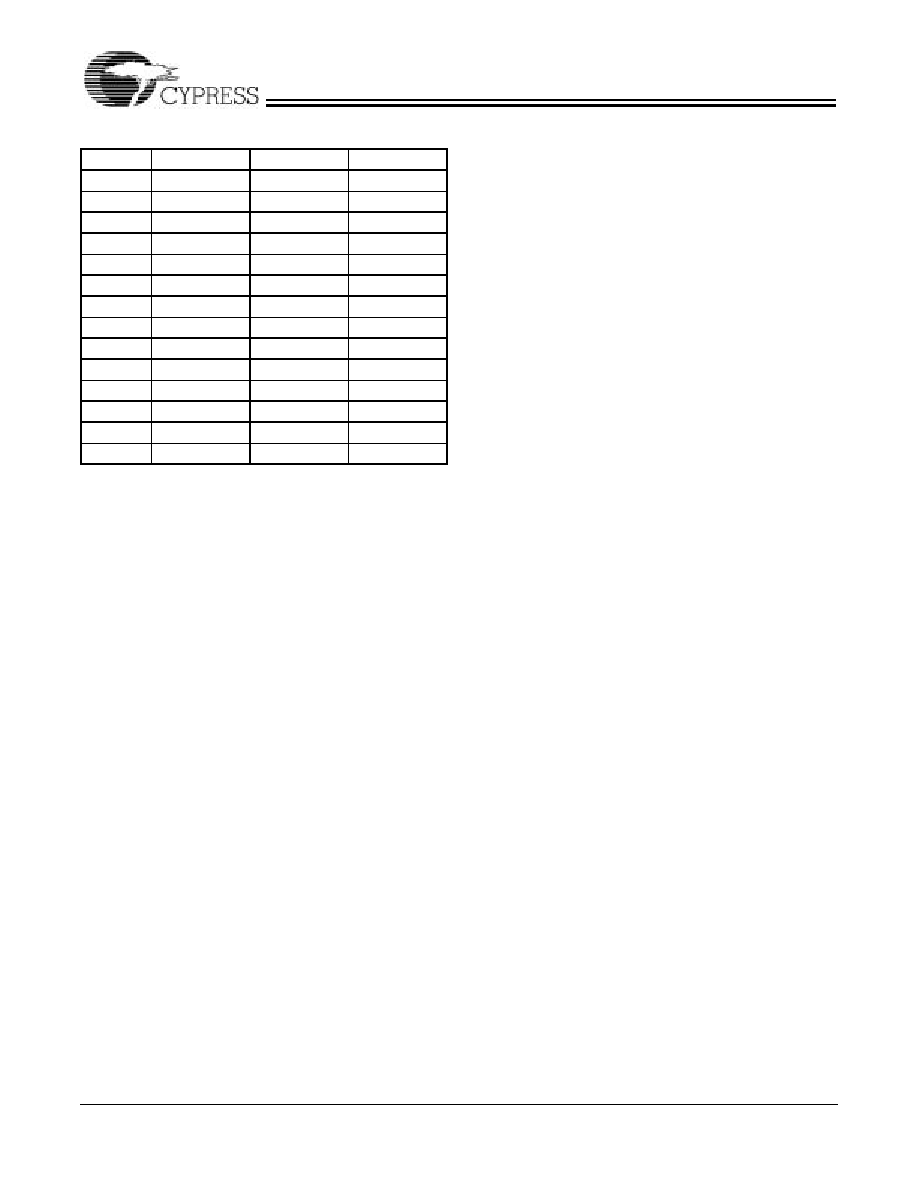

Delta39KTM ISR CPLD Family Members

Device

Typical

Gates

[1]

Macrocells

Cluster

memory

(Kbits)

Channel

memory

(Kbits)

Maximum

I/O Pins

f

MAX2

(MHz)

Speed-t

PD

Pin-to-Pin

(ns)

Standby I

CC

[2]

T

A

= 25

∞

C

3.3/2.5V

39K30

16K ≠ 48K

512

64

16

174

233

7.2

5 mA

39K50

23K ≠ 72K

768

96

24

218

233

7.2

5 mA

39K100

46K ≠ 144K

1536

192

48

302

222

7.5

10 mA

39K165

77K ≠ 241K

2560

320

80

386

181

8.5

20 mA

39K200

92K ≠ 288K

3072

384

96

428

181

8.5

20 mA

Notes:

1.

Upper limit of typical gates is calculated by assuming only 10% of the channel memory is used.

2.

Standby I

CC

values are with PLL not utilized, no output load and stable inputs.

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 2 of 86

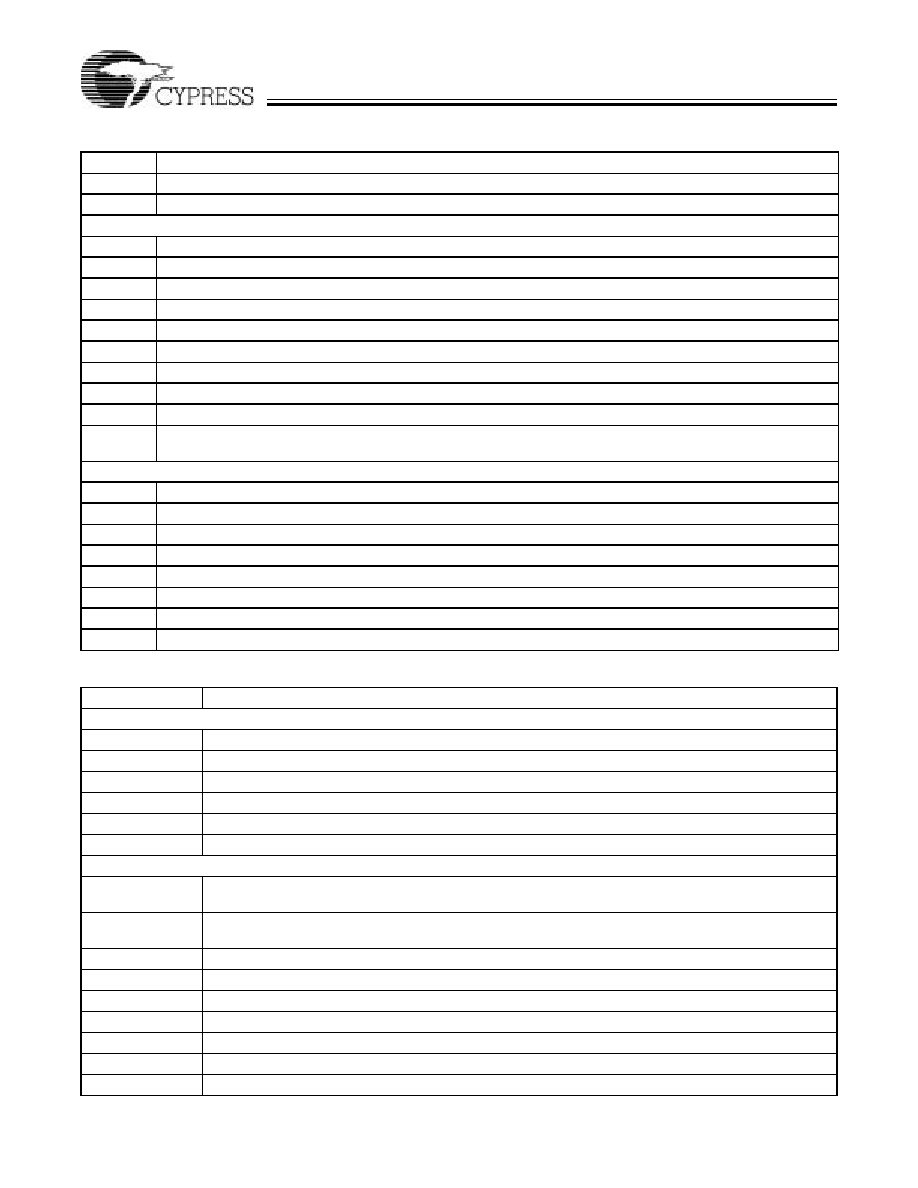

Notes:

3.

Speed bins shown here are for commercial operating range. Please refer to Delta39K ordering information on industrial-range speed bins on page 38.

4.

Self-boot solution integrates the boot PROM (flash memory) with Delta39K die inside the same package. This flash memory can endure at least 10,000

programming/erase cycles and can retain data for at least 100 years.

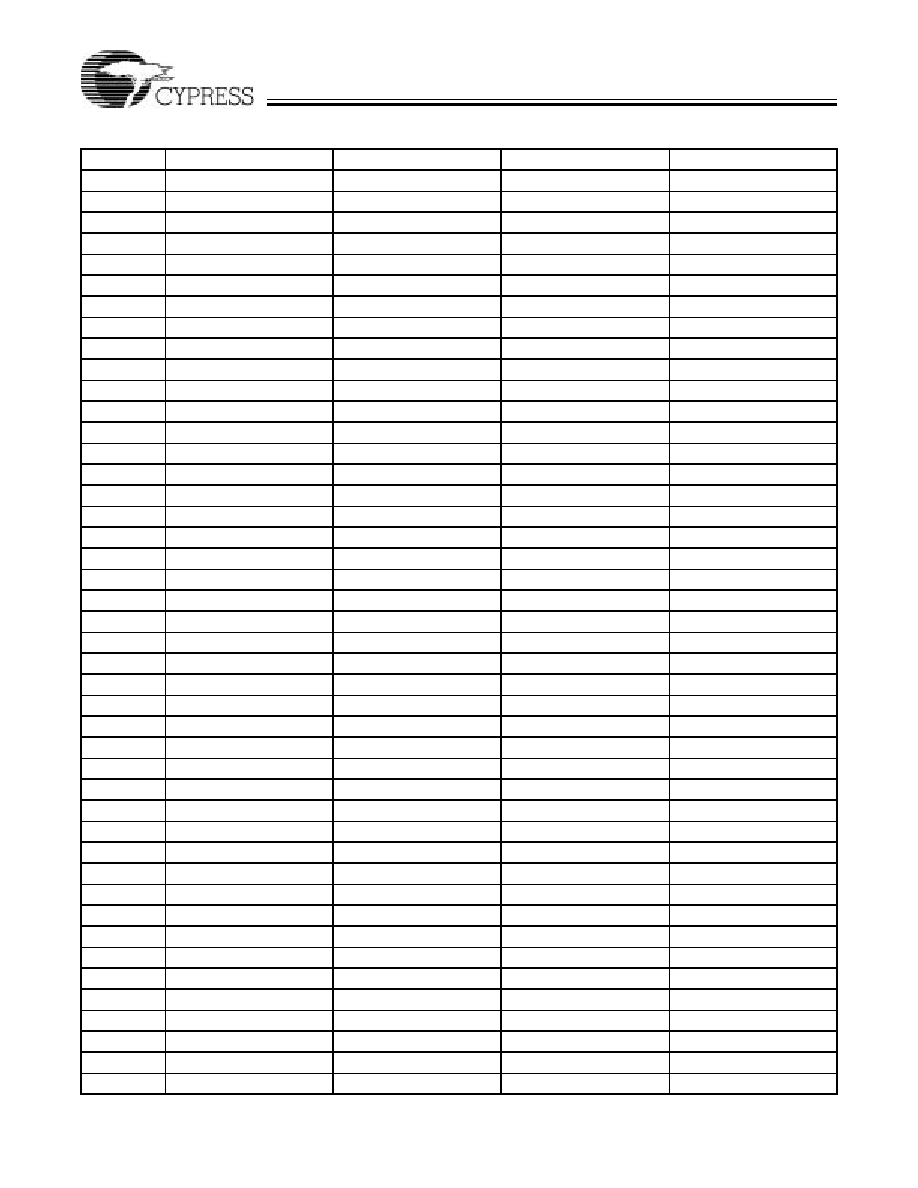

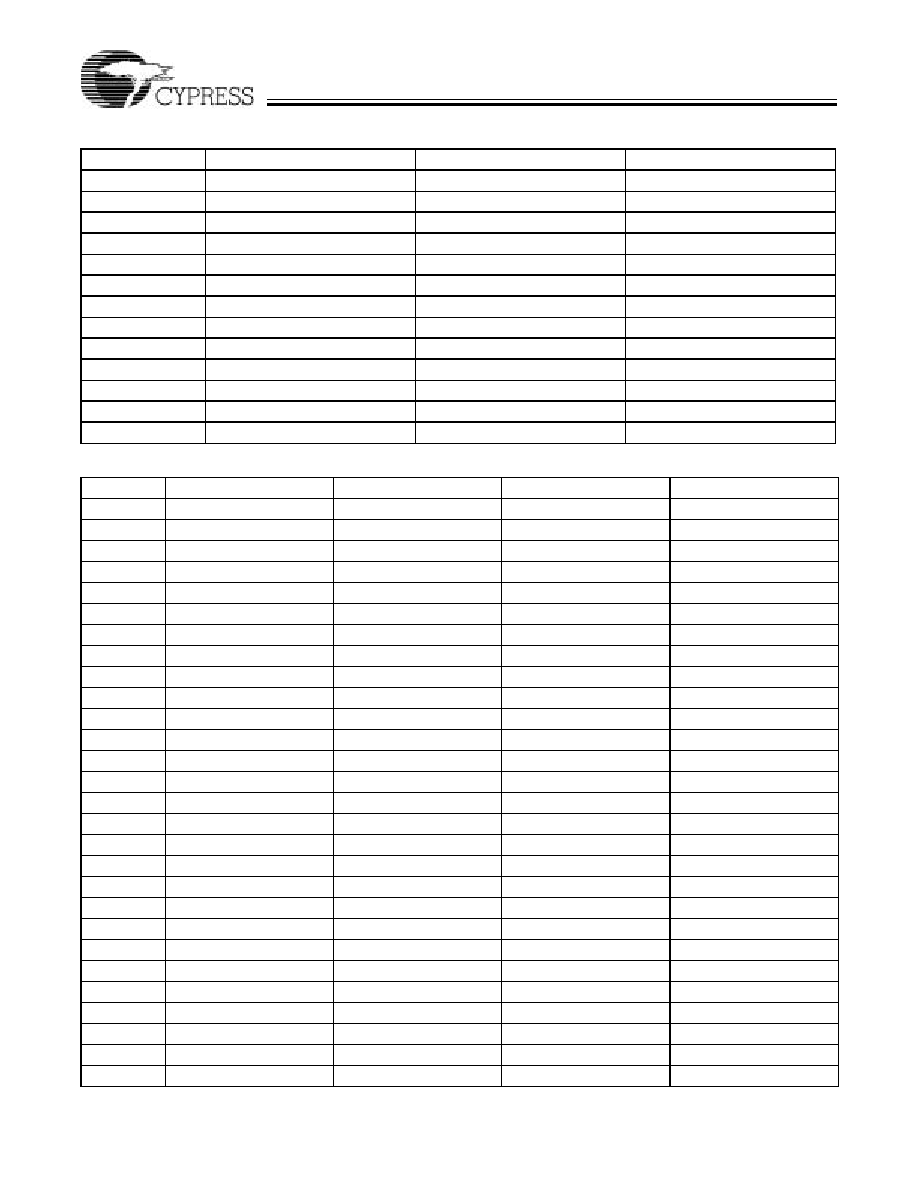

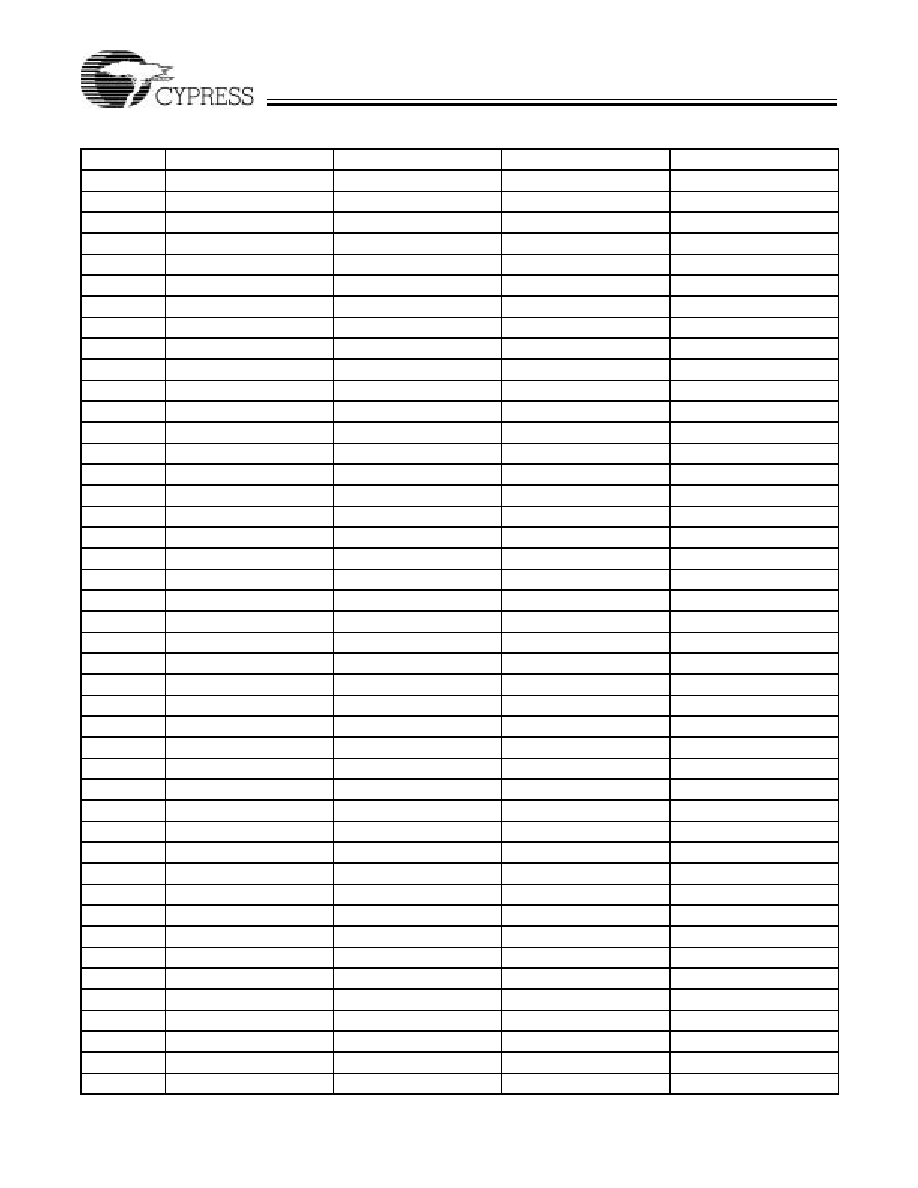

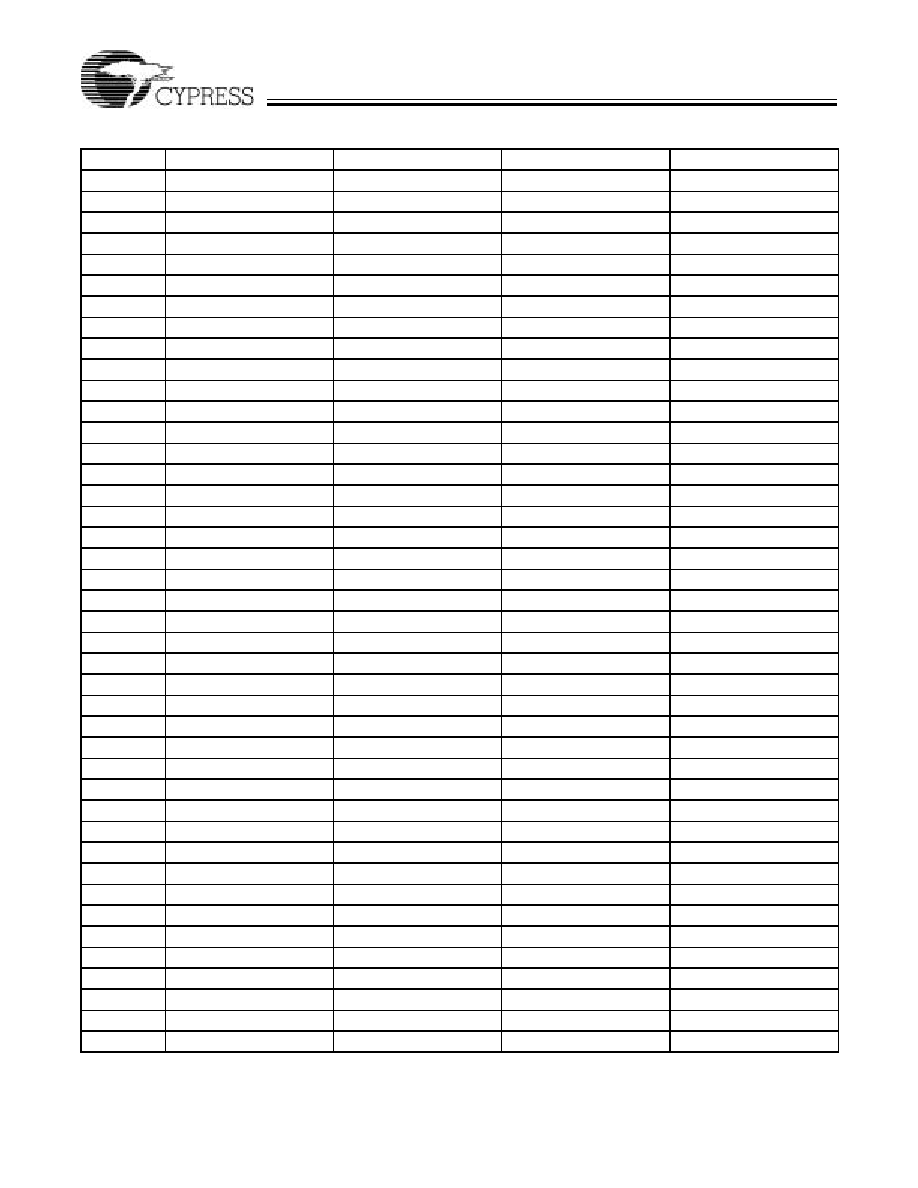

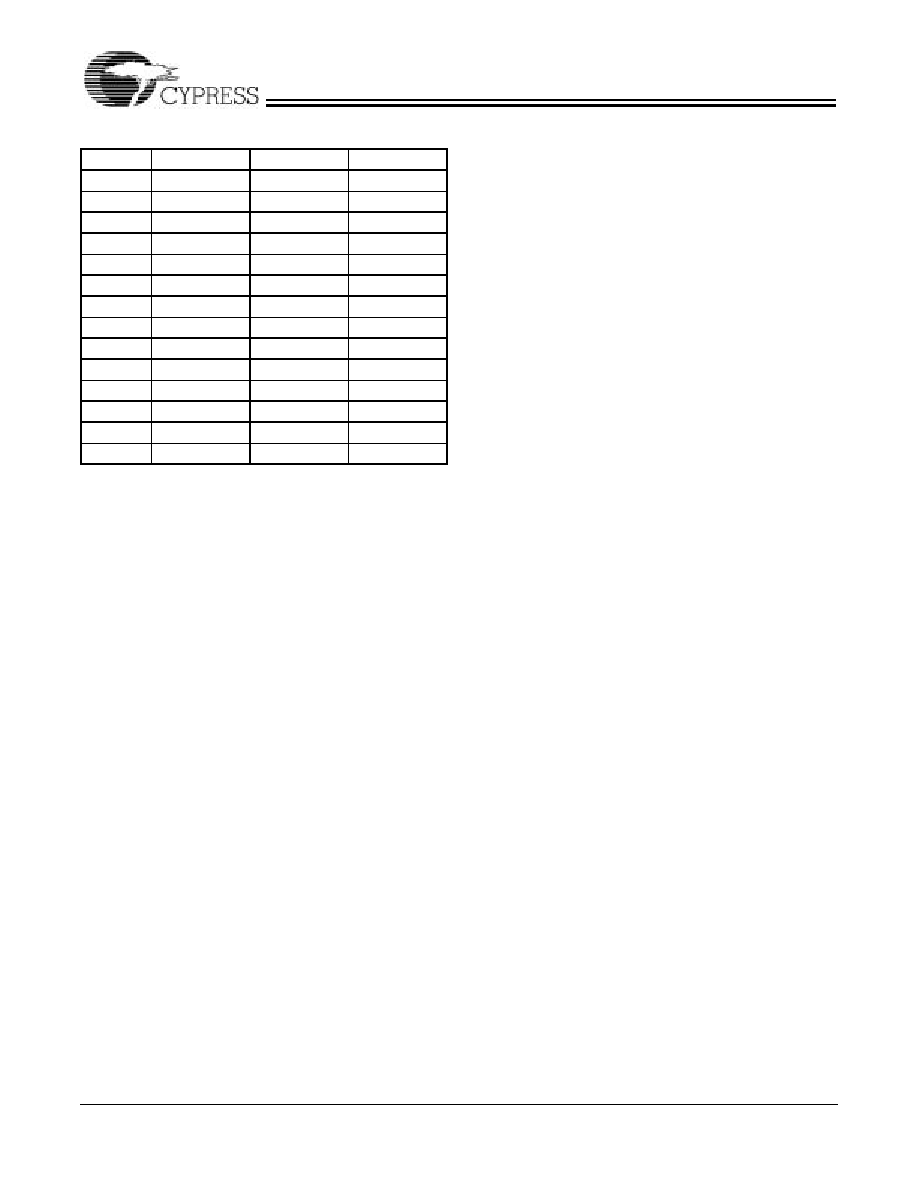

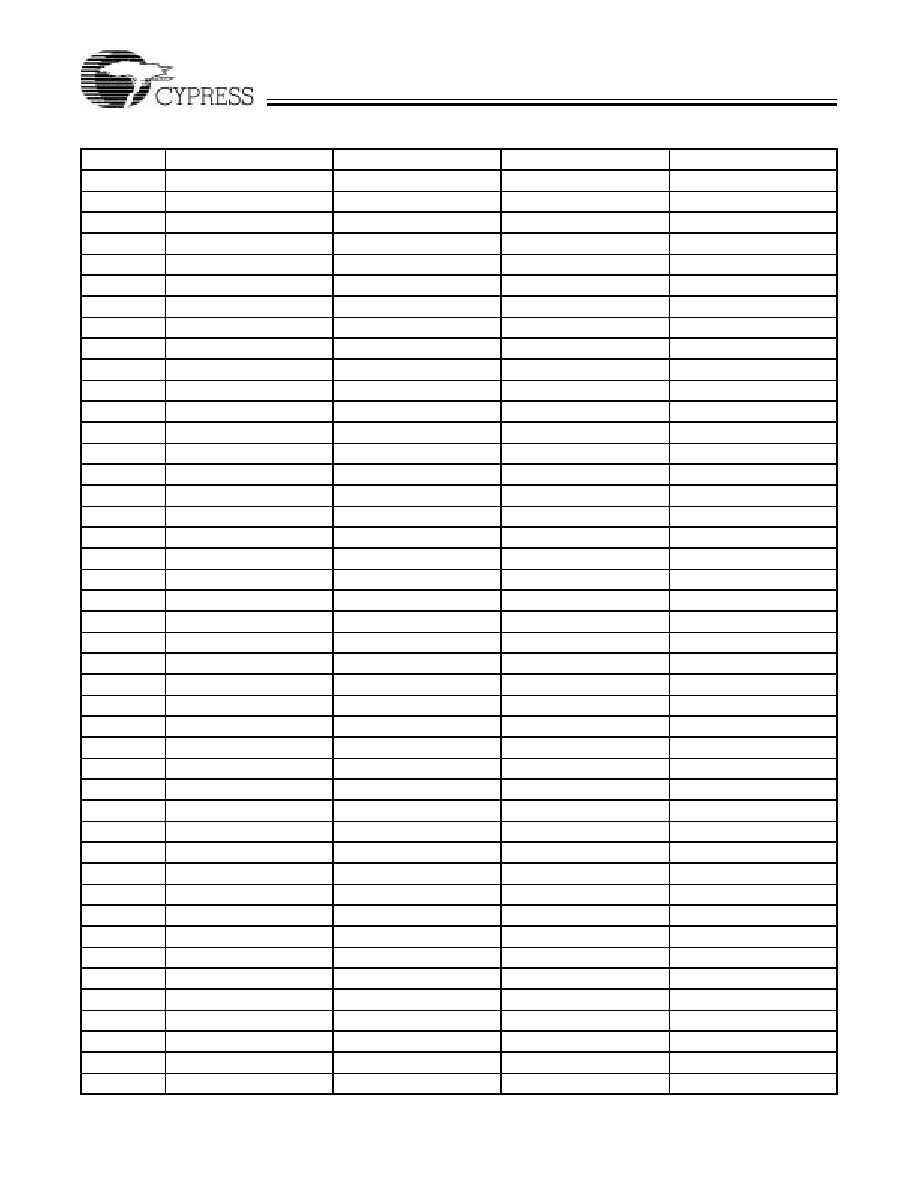

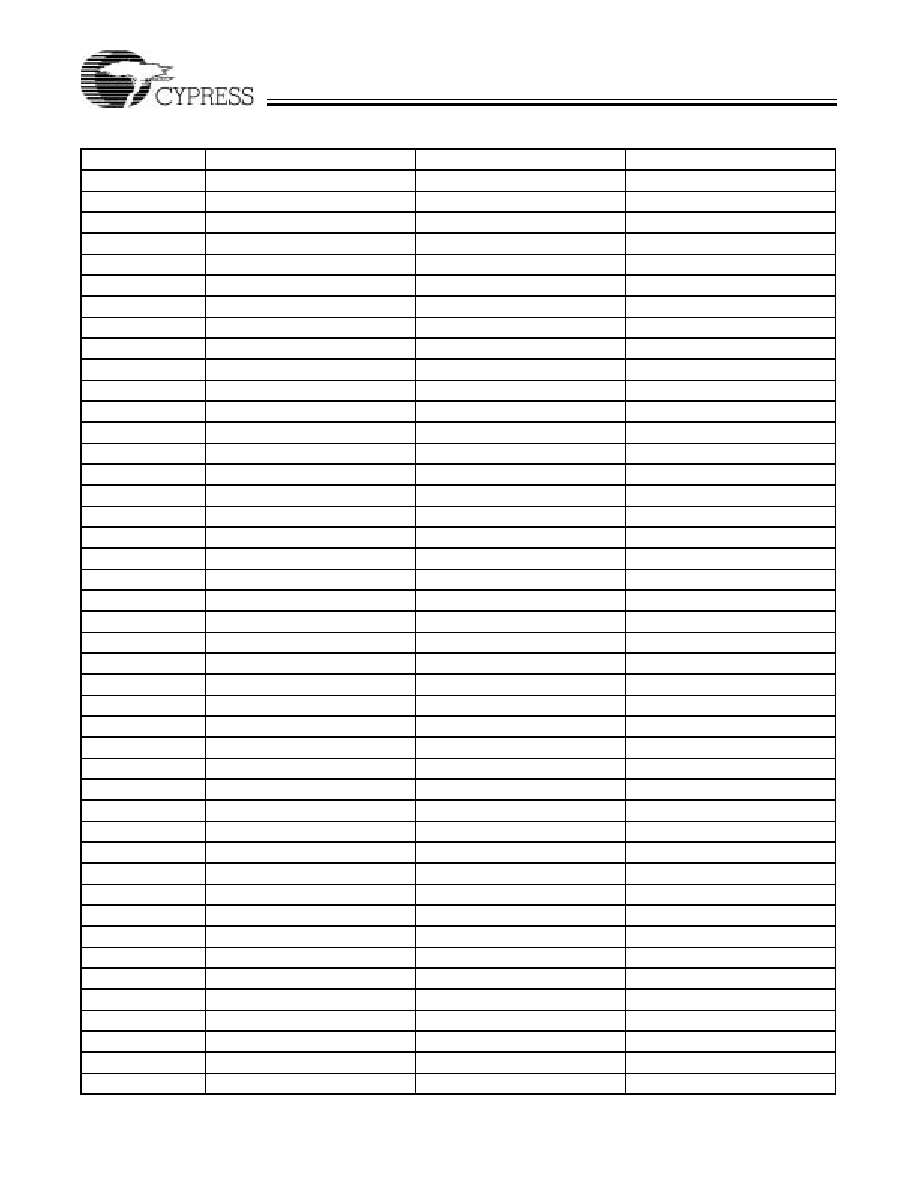

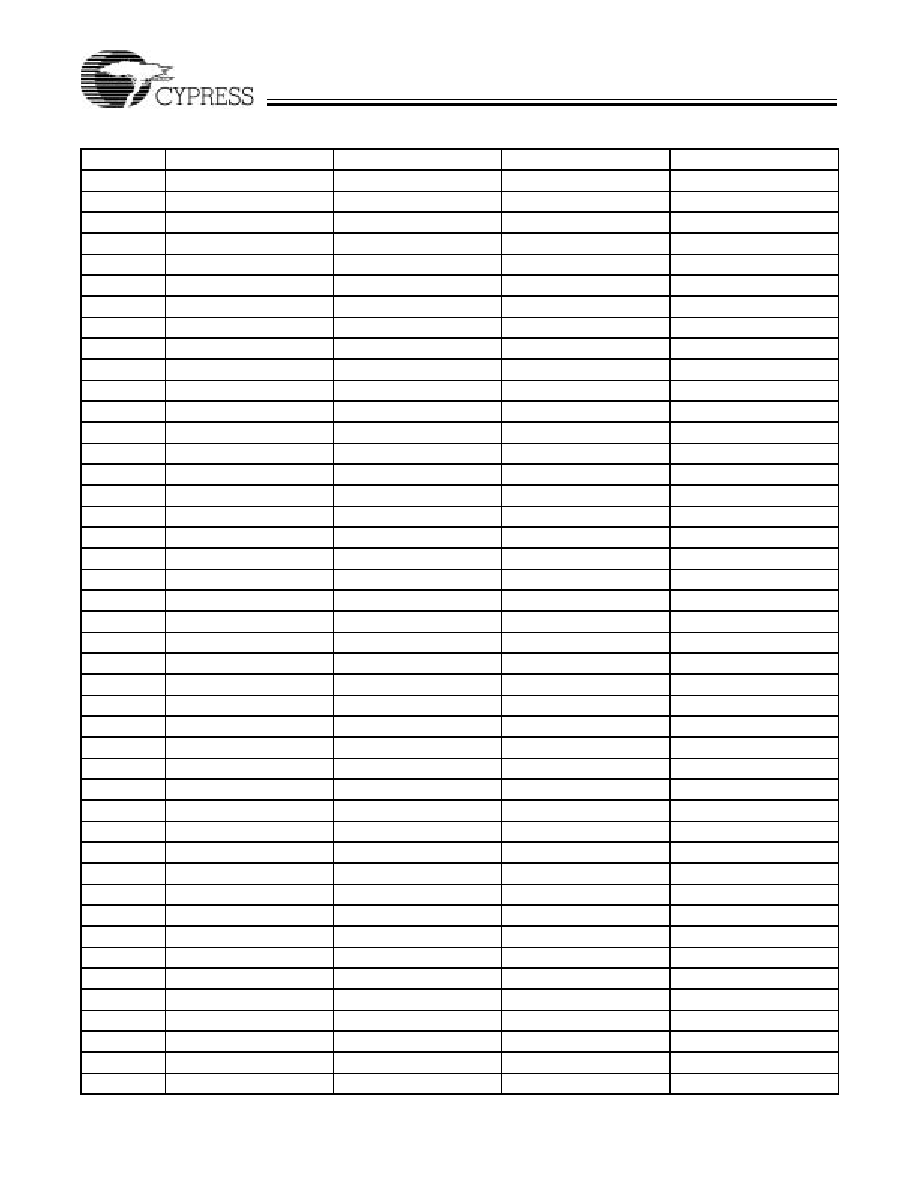

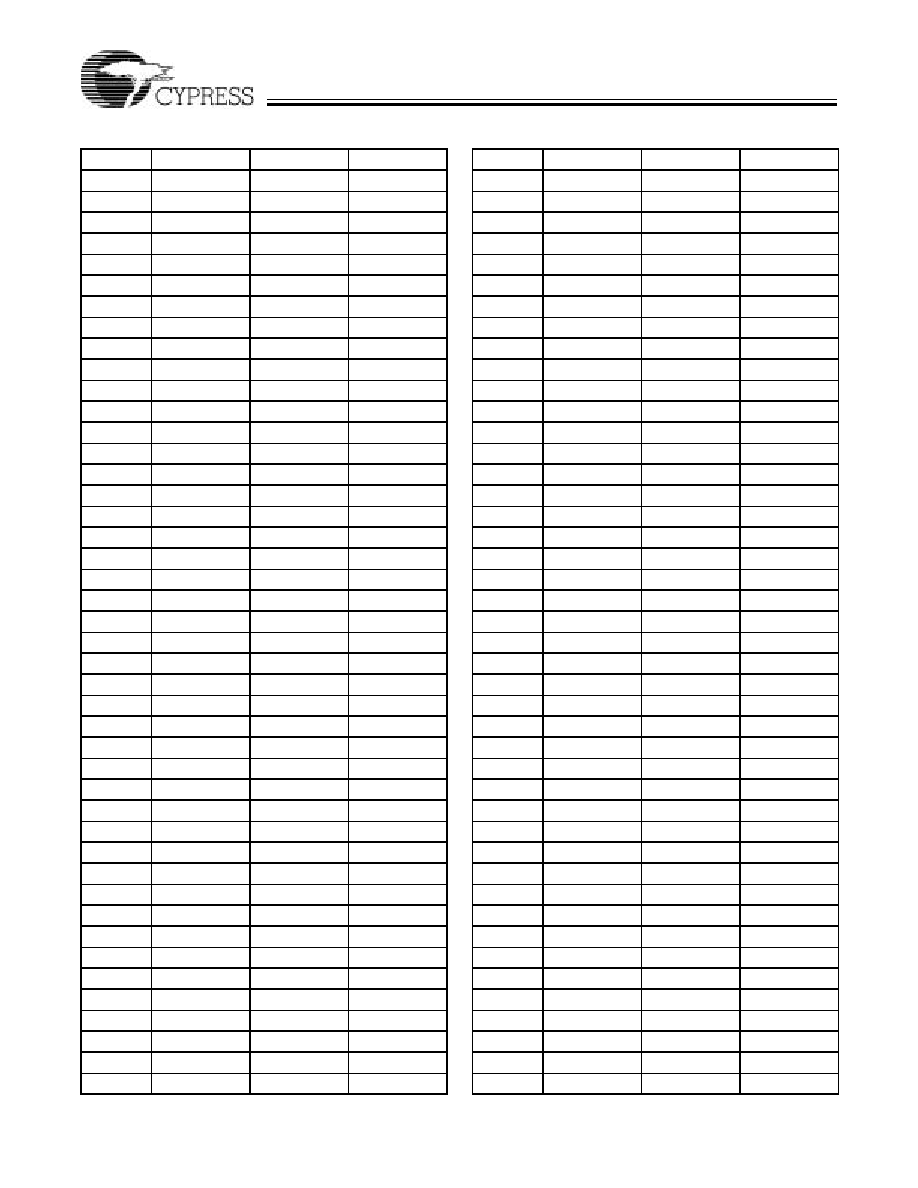

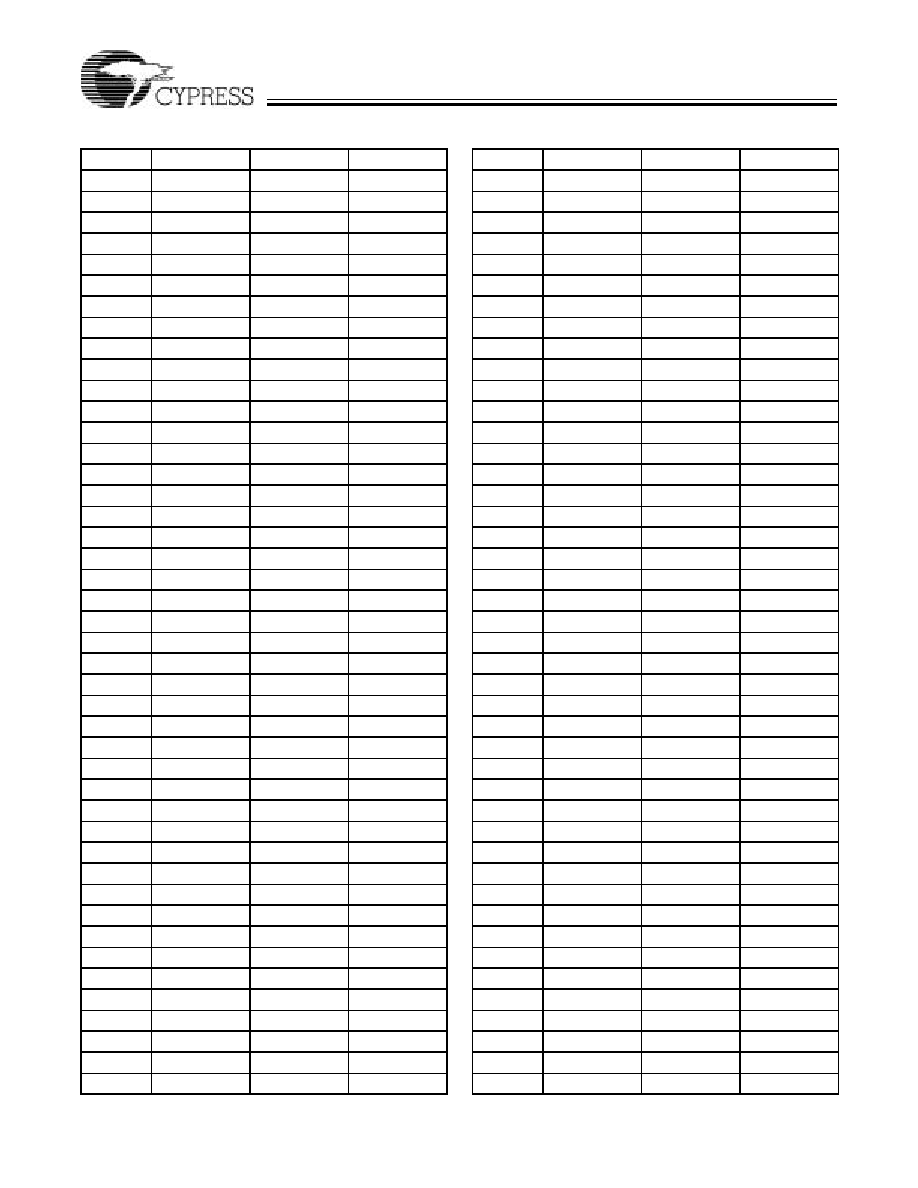

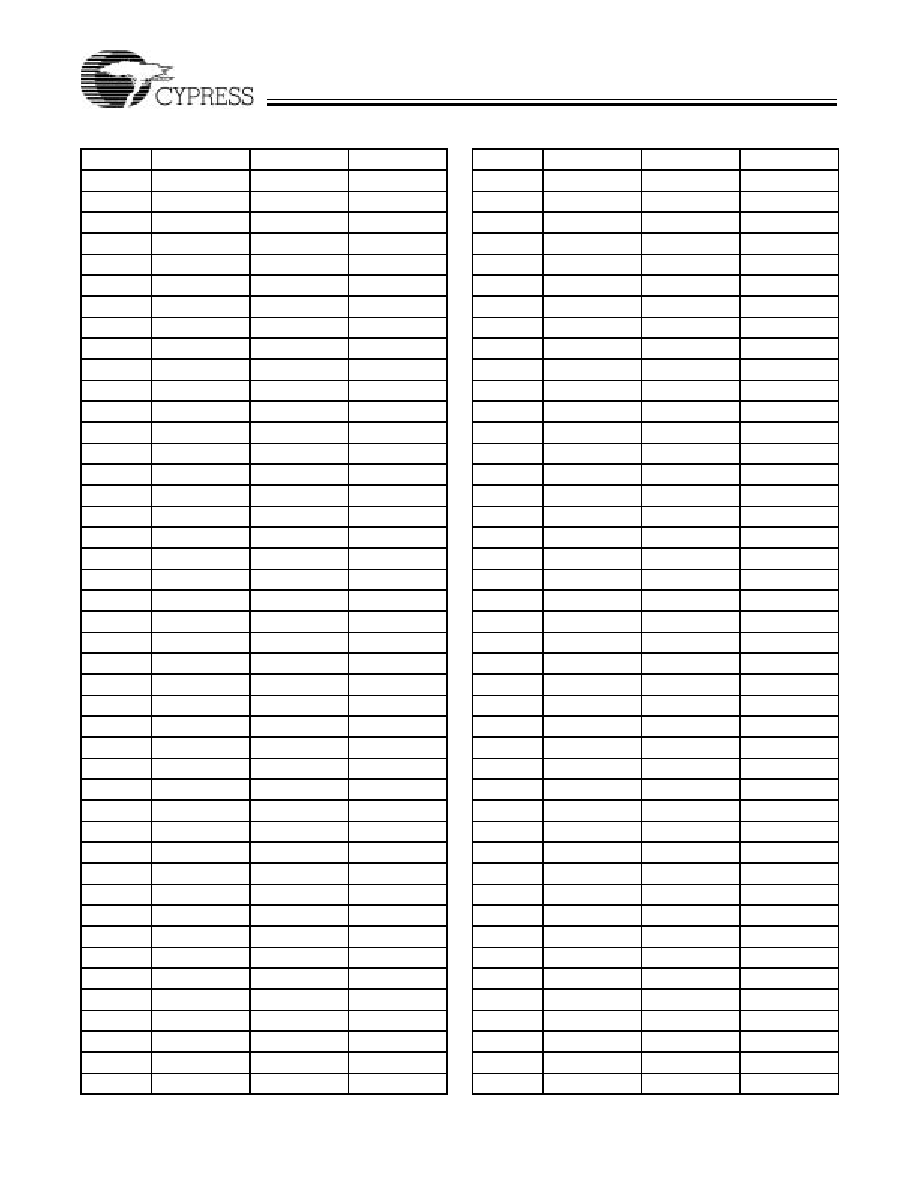

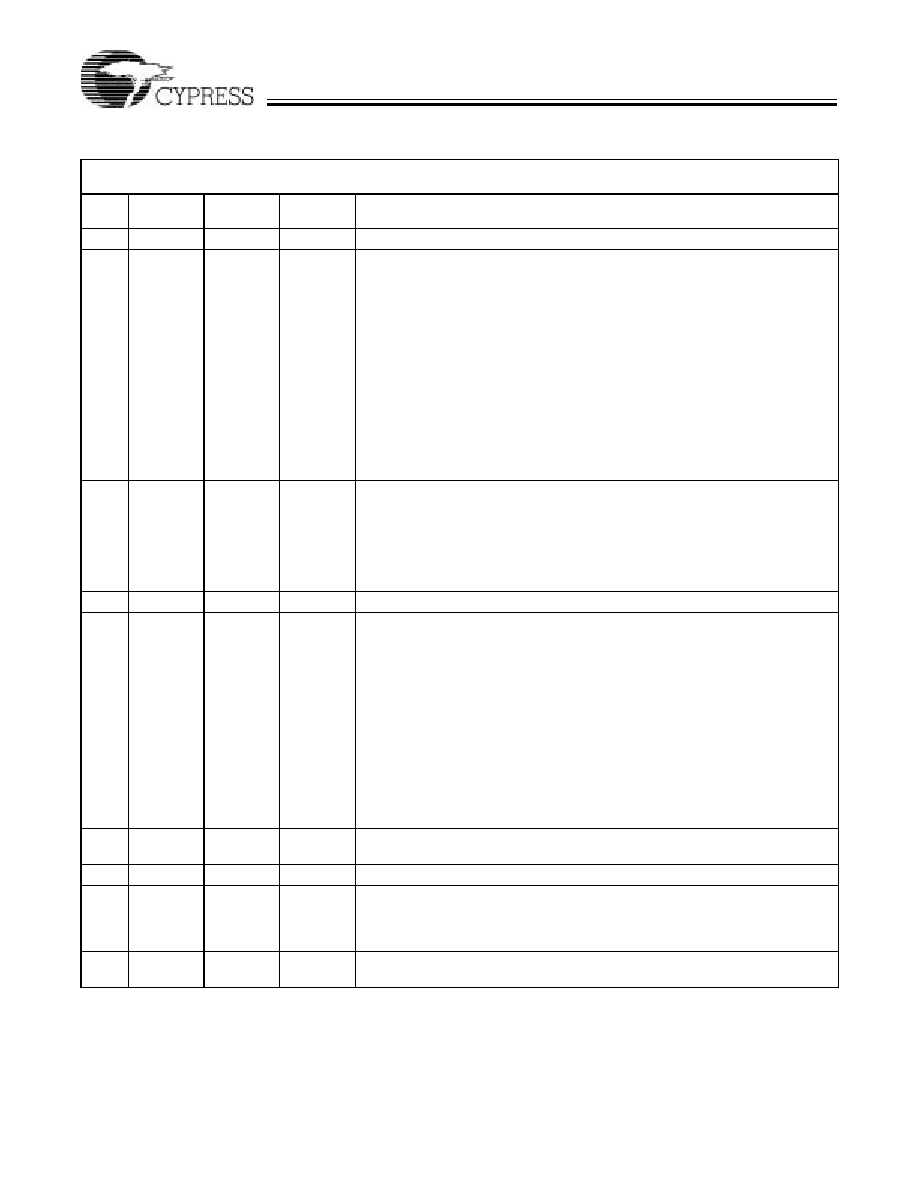

Delta39K Speed Bins

[3]

Device

V

CC

233

200

181

125

83

39K30

3.3/2.5V

X

X

X

39K50

3.3/2.5V

X

X

X

39K100

3.3/2.5V

X

X

X

39K165

3.3/2.5V

X

X

X

39K200

3.3/2.5V

X

X

X

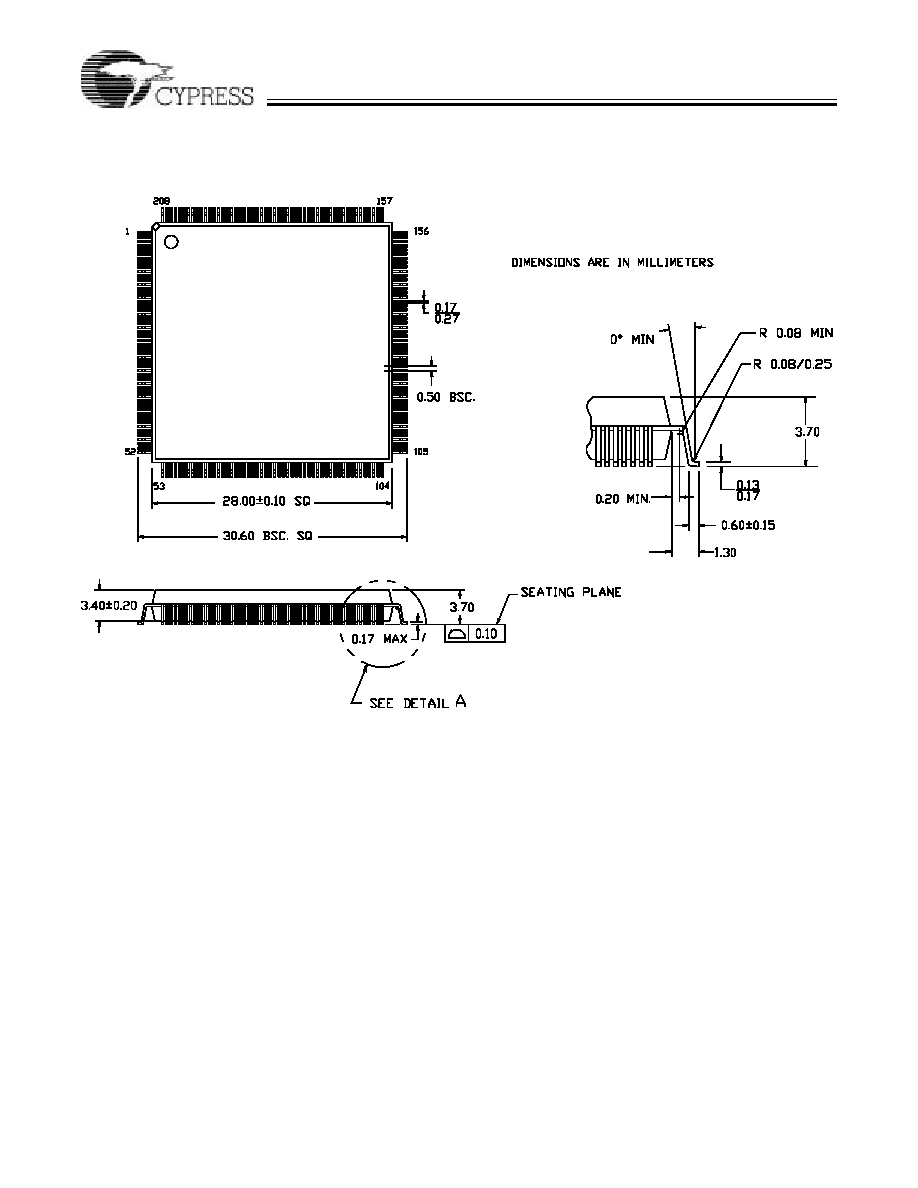

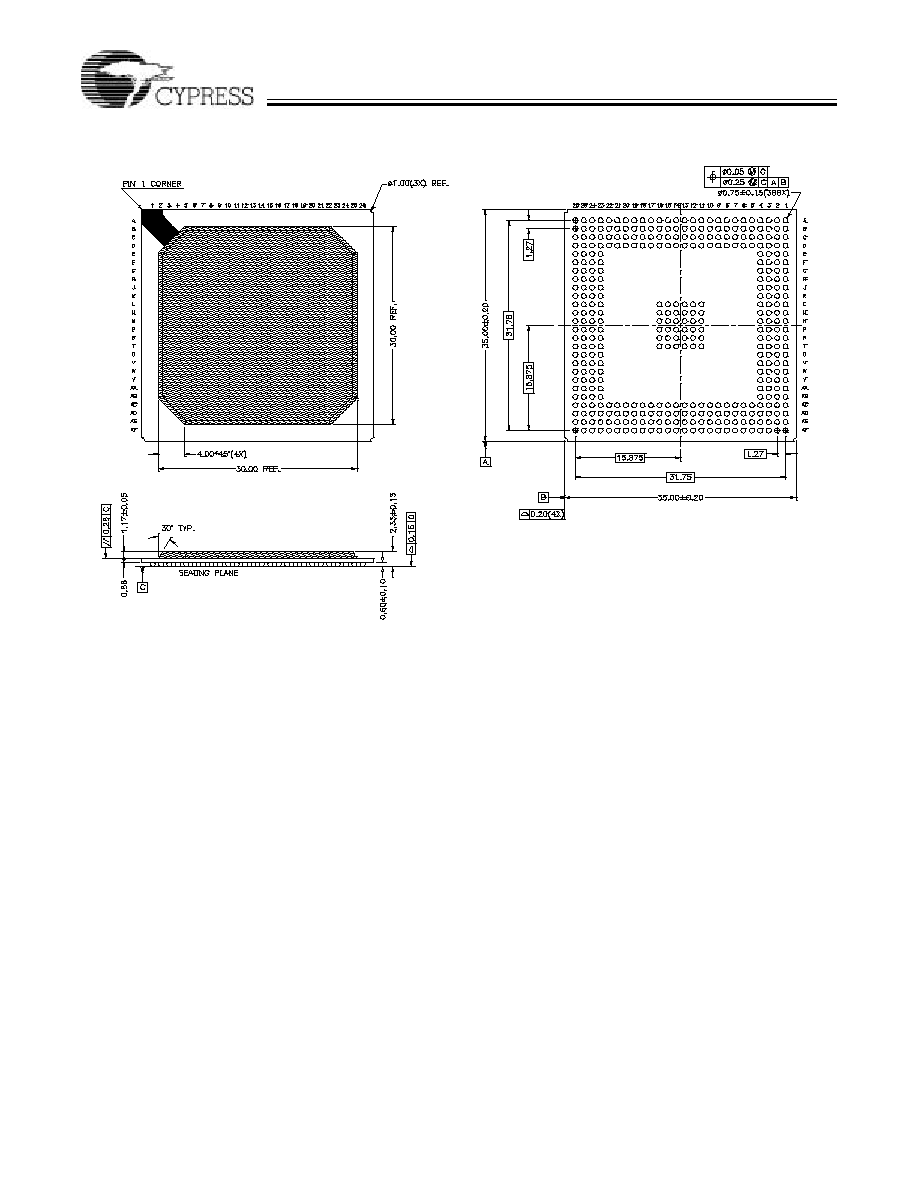

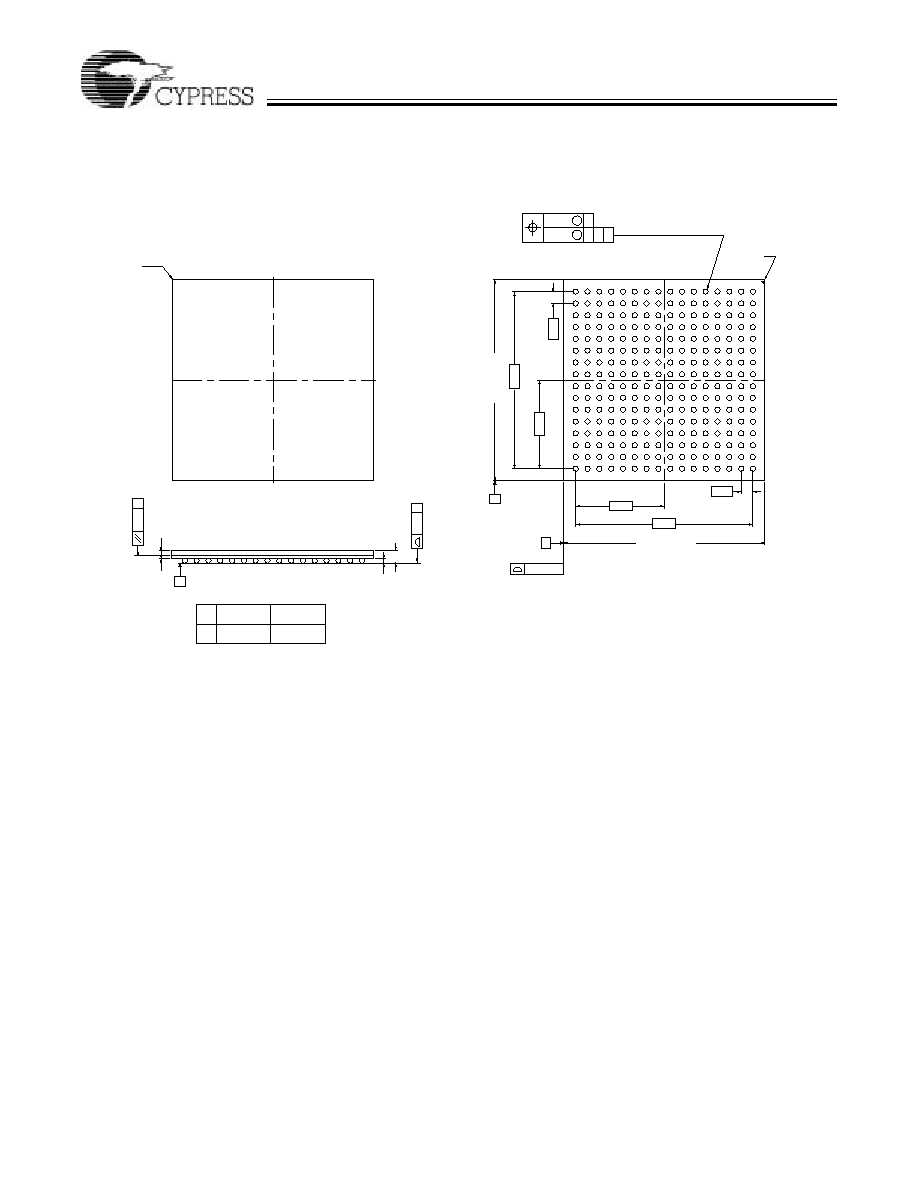

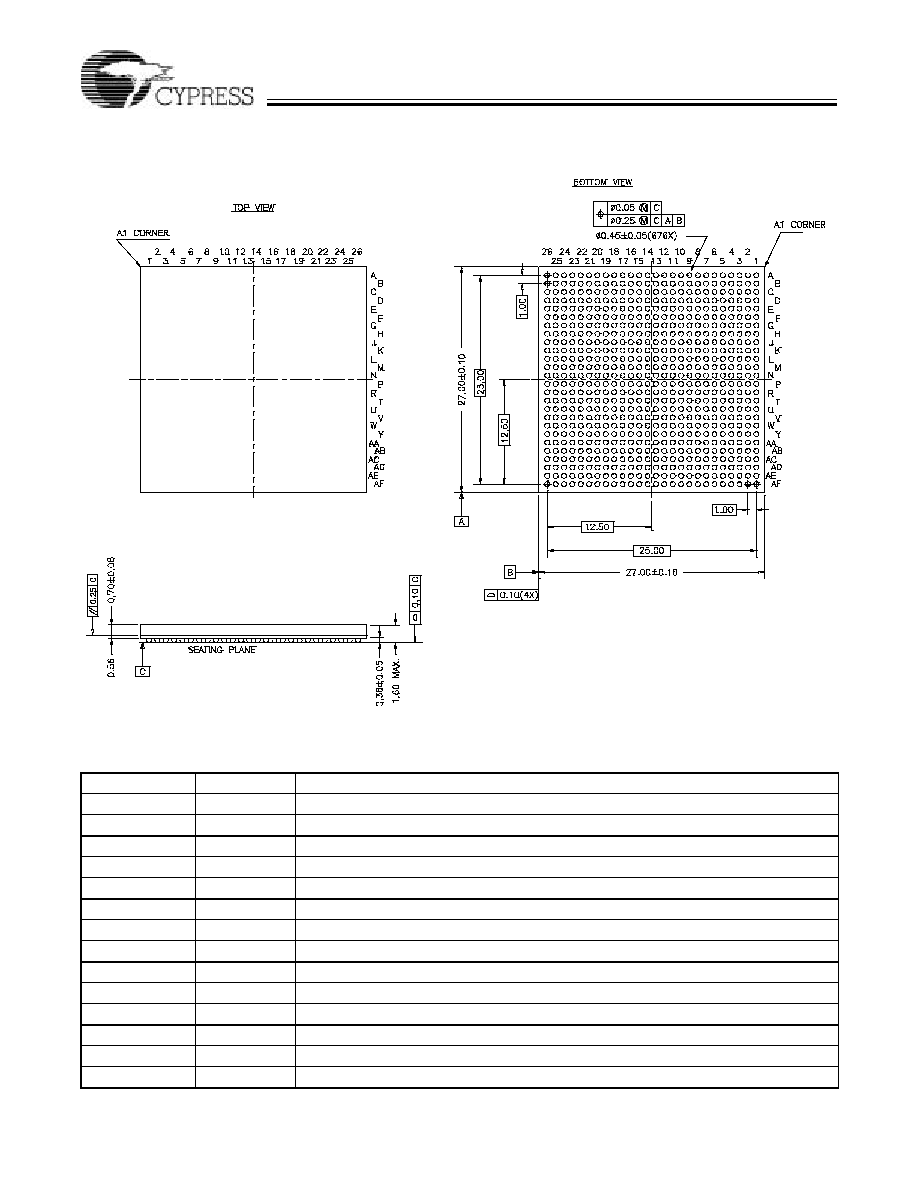

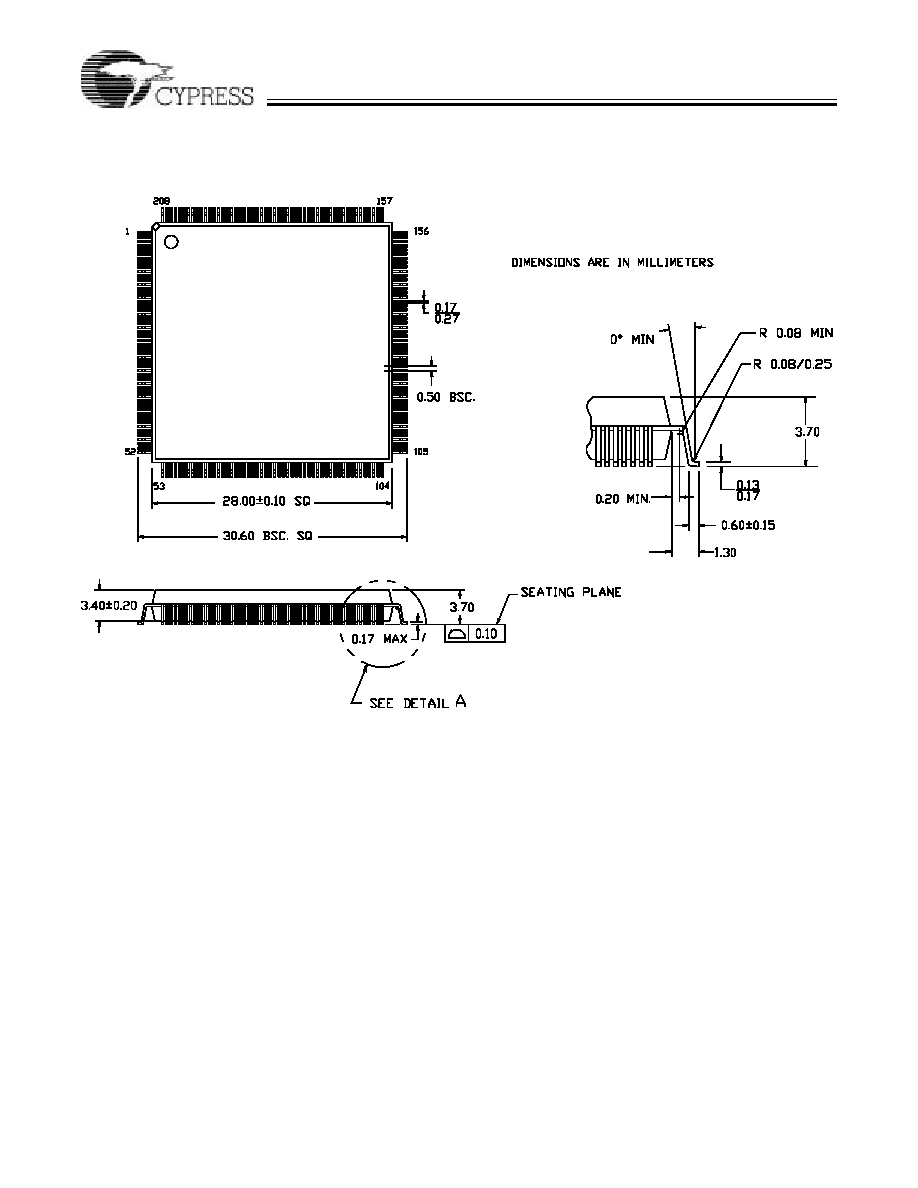

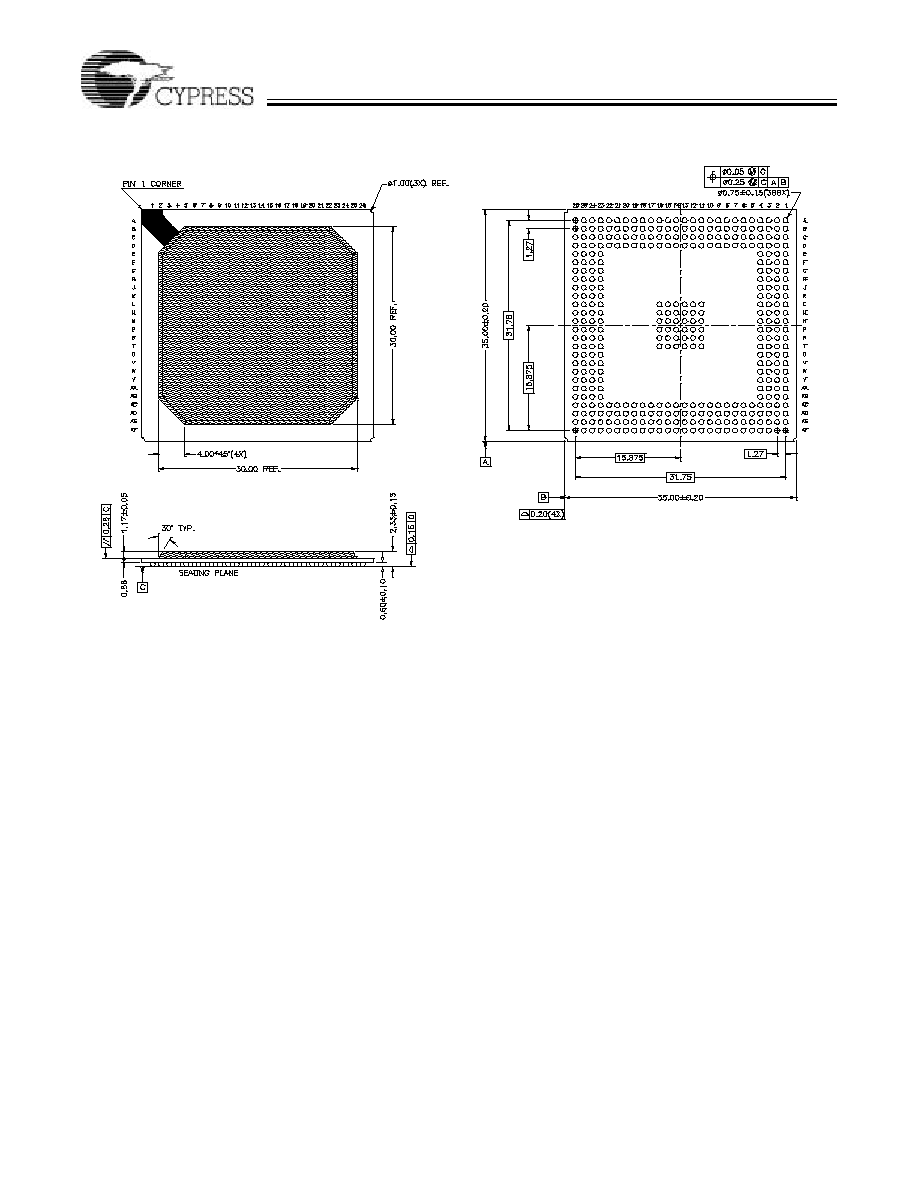

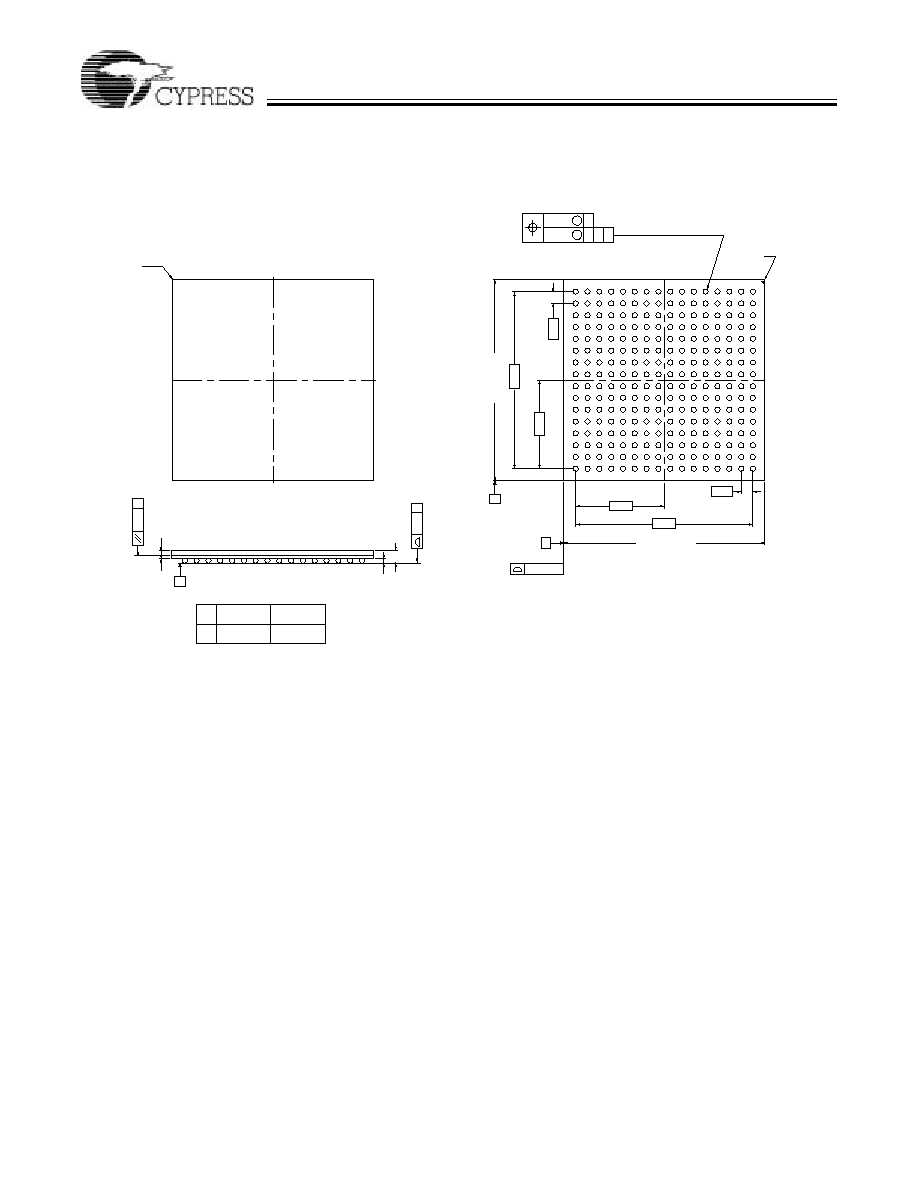

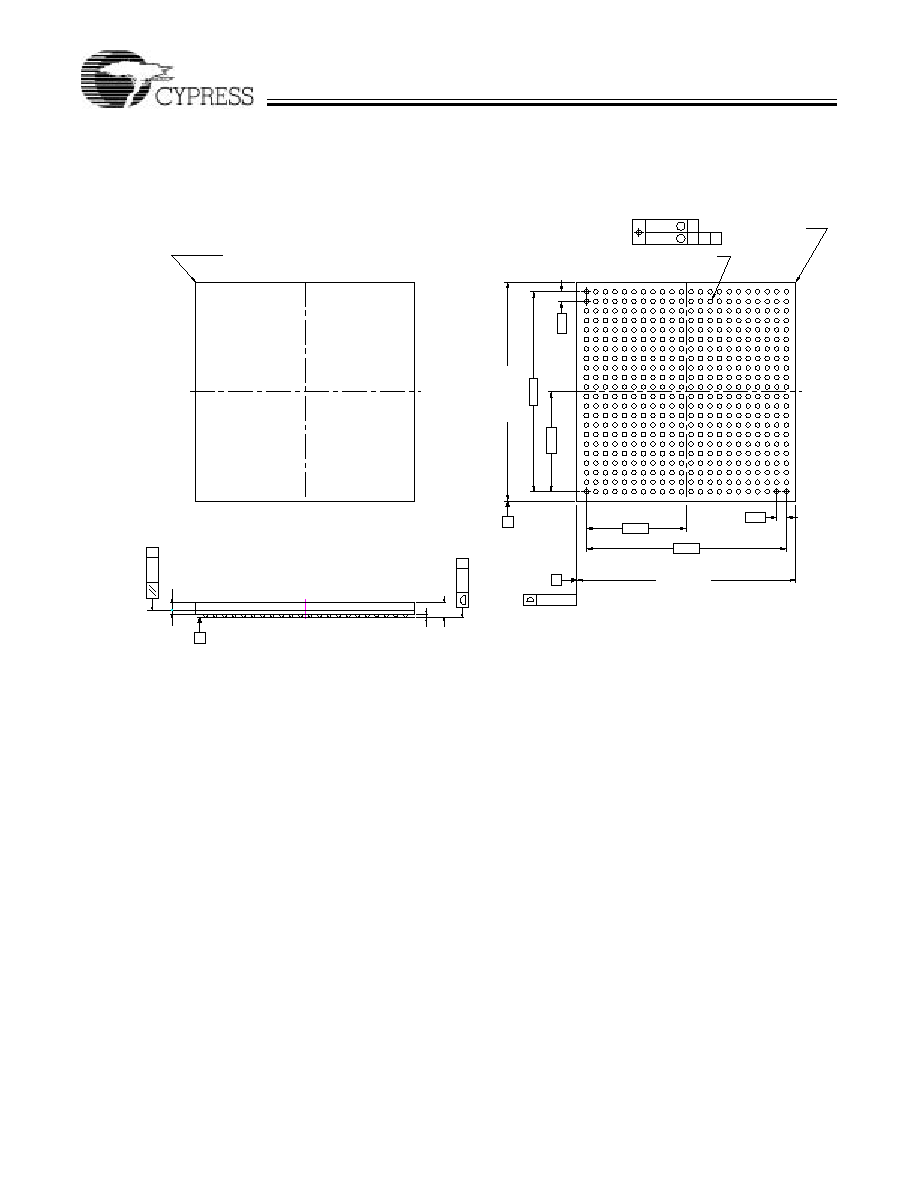

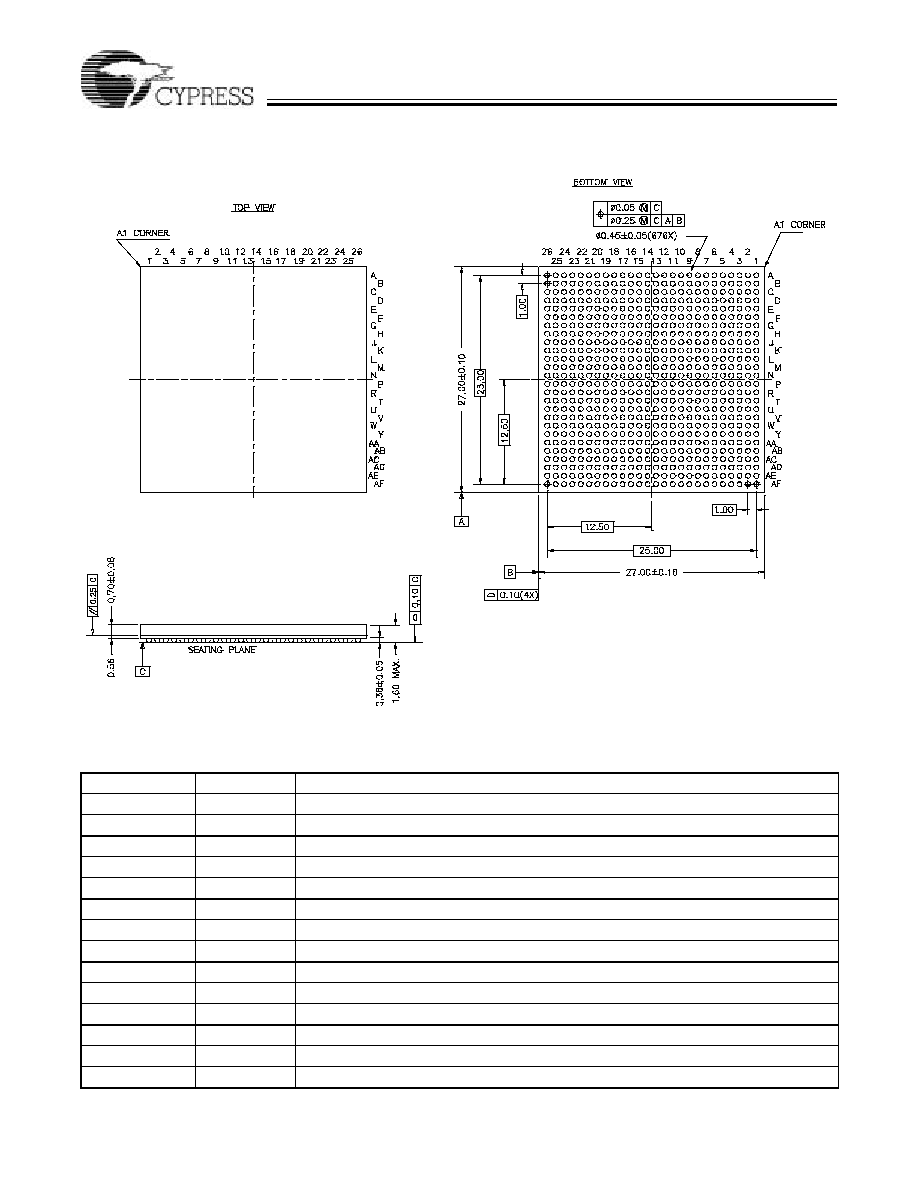

Device Package Offering and I/O Count Including Dedicated Clock and Control Inputs

Device

208 EQFP

28 ◊ 28 mm

0.5-mm pitch

256 FBGA

17 ◊ 17 mm

1.0-mm pitch

484-FBGA

23 ◊ 23 mm

1.0-mm pitch

Self-Boot

Solution

[4]

256-FBGA

17 ◊ 17 mm

1.0-mm pitch

388-BGA

35 ◊ 35 mm

1.27-mm pitch

484-FBGA

23 ◊ 23 mm

1.0-mm pitch

676-FBGA

27 ◊ 27 mm

1.0-mm pitch

39K30

136

174

174

39K50

136

180

218

218

39K100

136

180

302

294

302

39K165

136

356

294

386

39K200

136

368

294

428

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 3 of 86

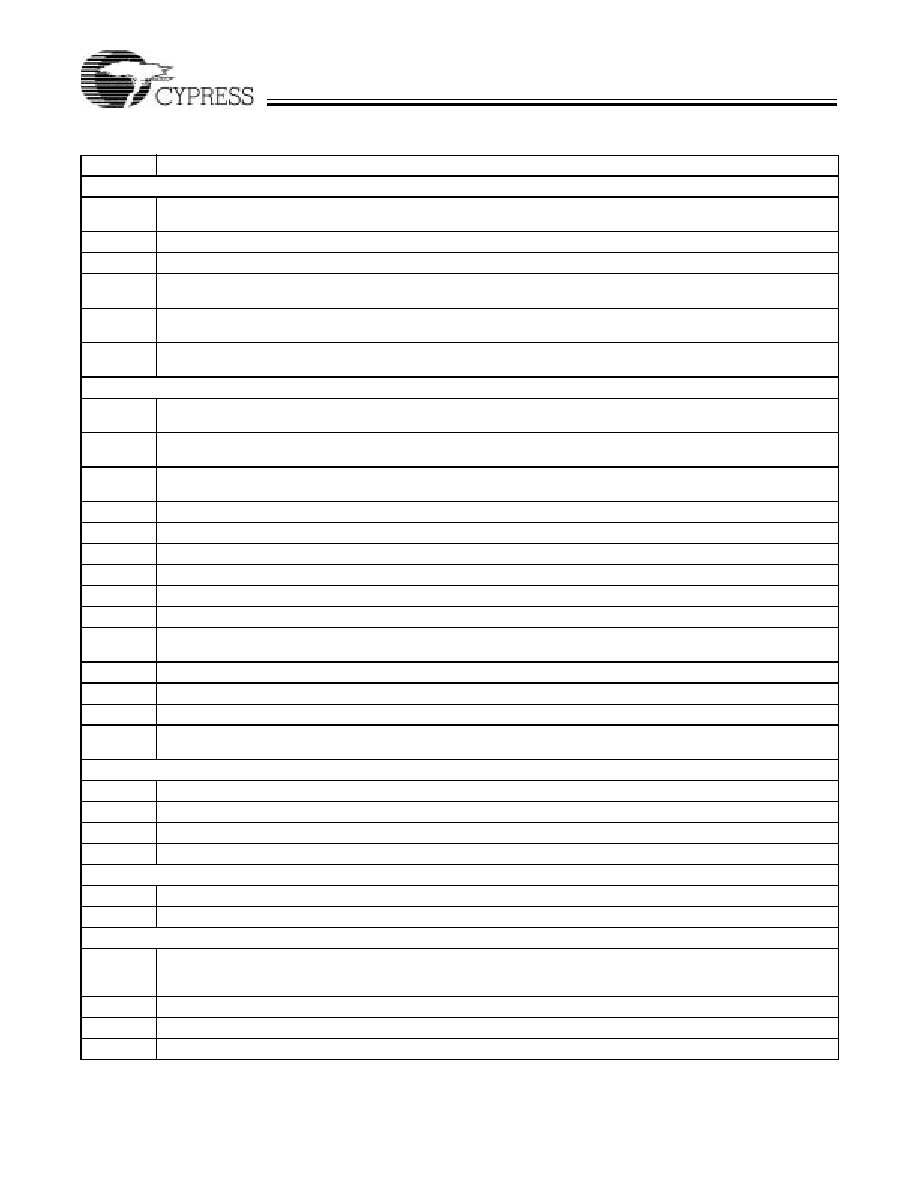

General Description

The Delta39K family, based on a 0.18-mm, six-layer metal

CMOS logic process, offers a wide range of high-density

solutions at unparalleled system performance. The Delta39K

family is designed to combine the high speed, predictable

timing, and ease of use of CPLDs with the high densities and

low power of FPGAs. With devices ranging from 30,000 to

200,000 usable gates, the family features devices ten times

the size of previously available CPLDs. Even at these large

densities, the Delta39K family is fast enough to implement a

fully synthesizable 64-bit, 66-MHz PCI core.

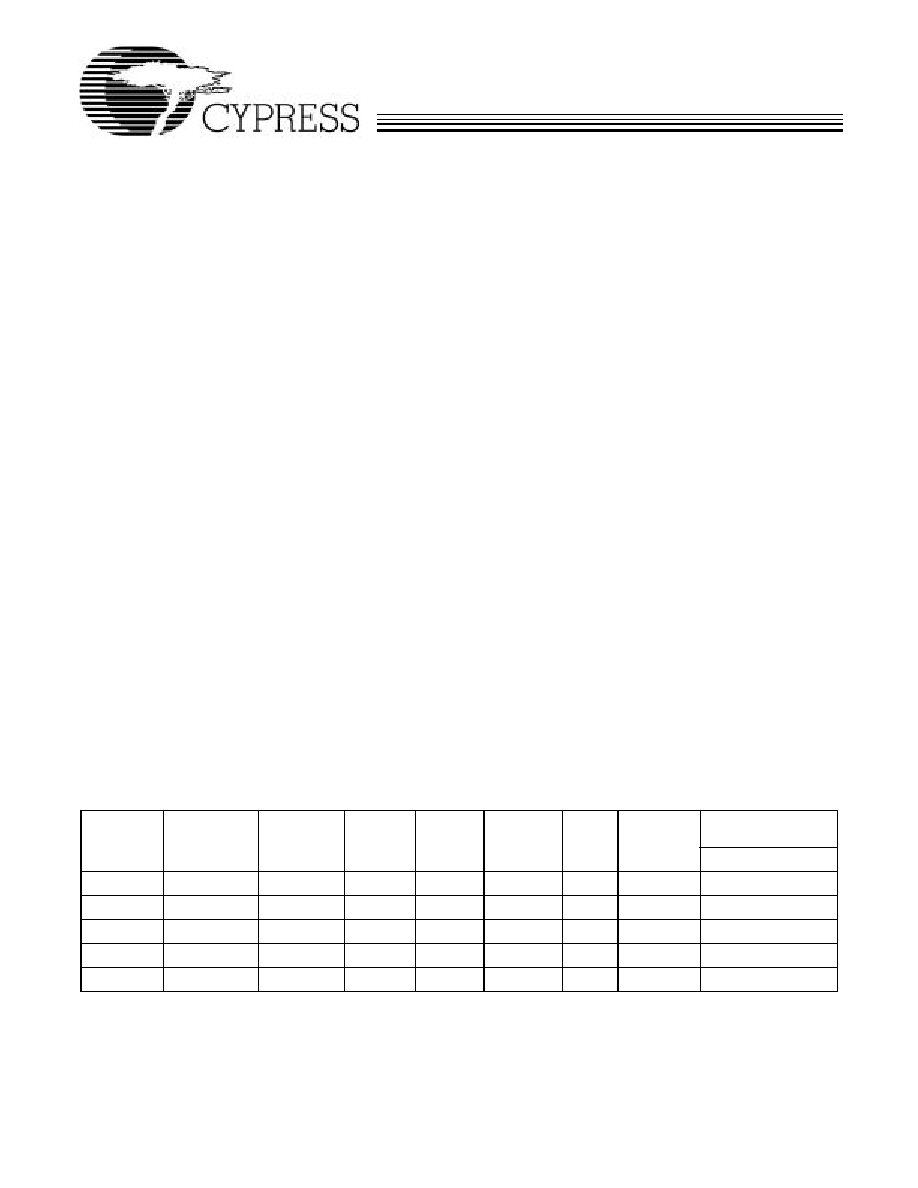

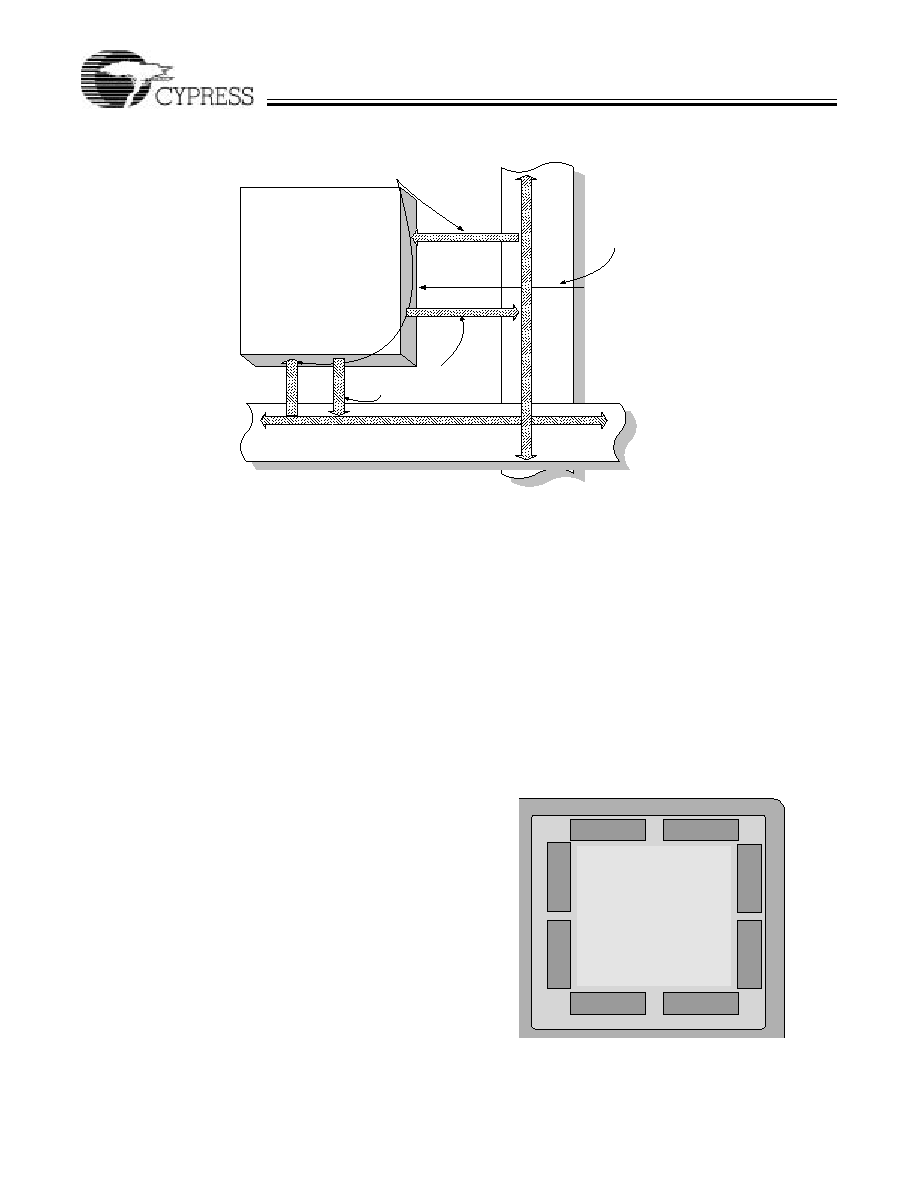

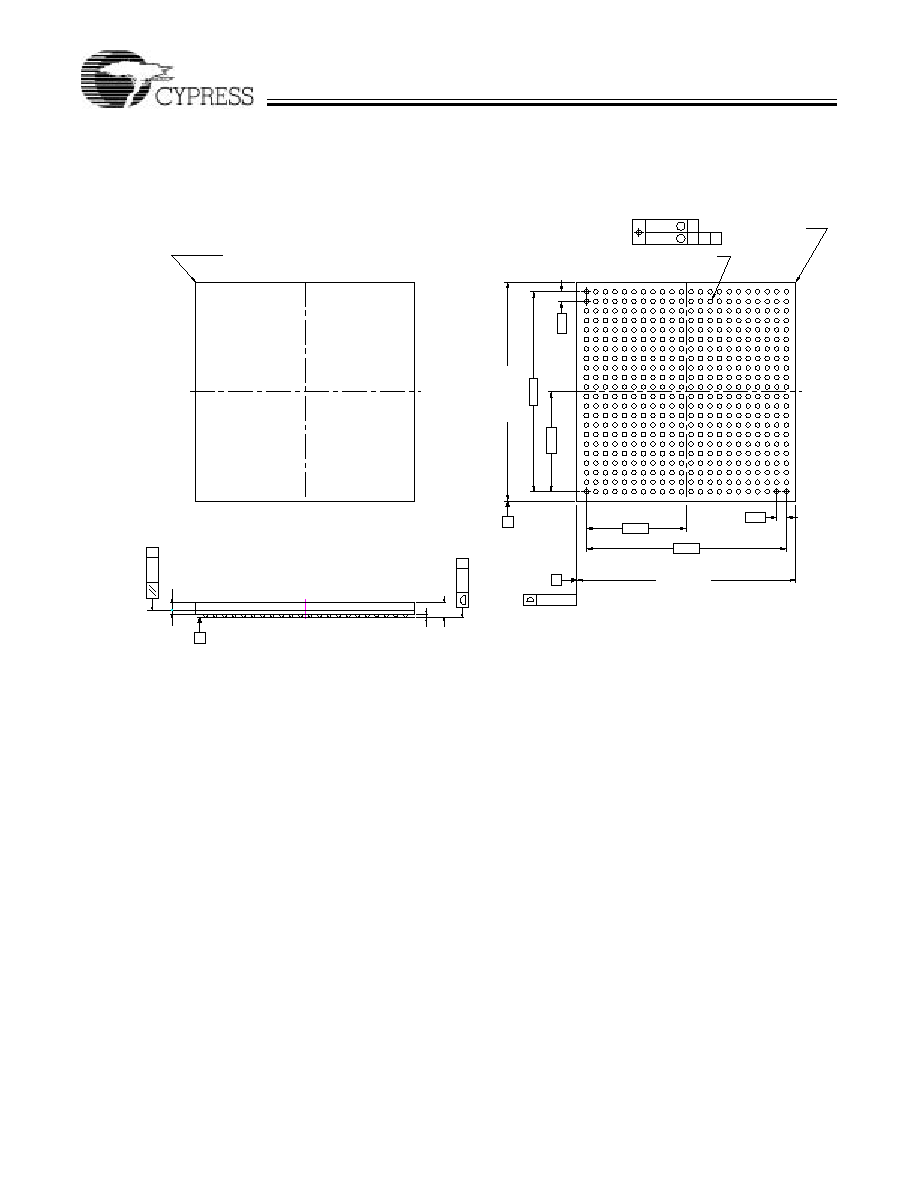

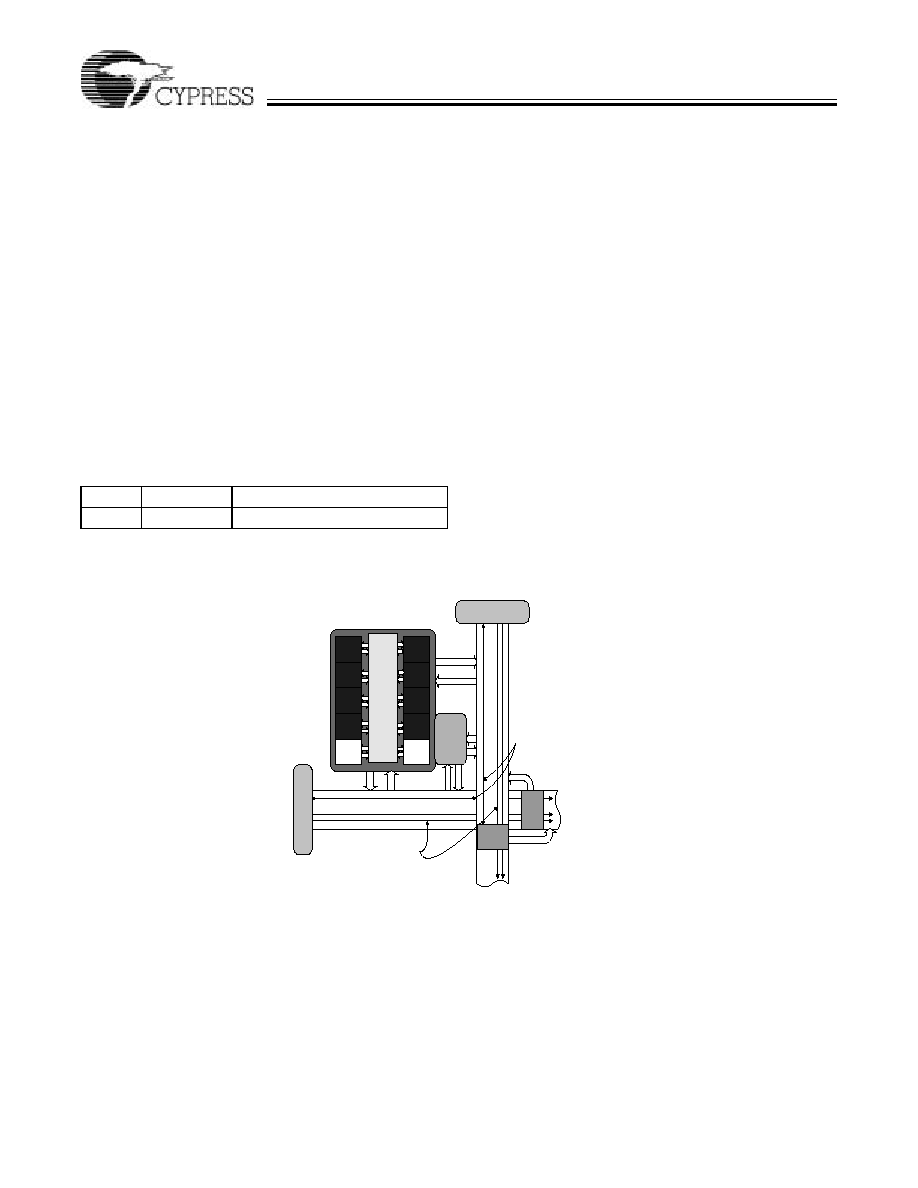

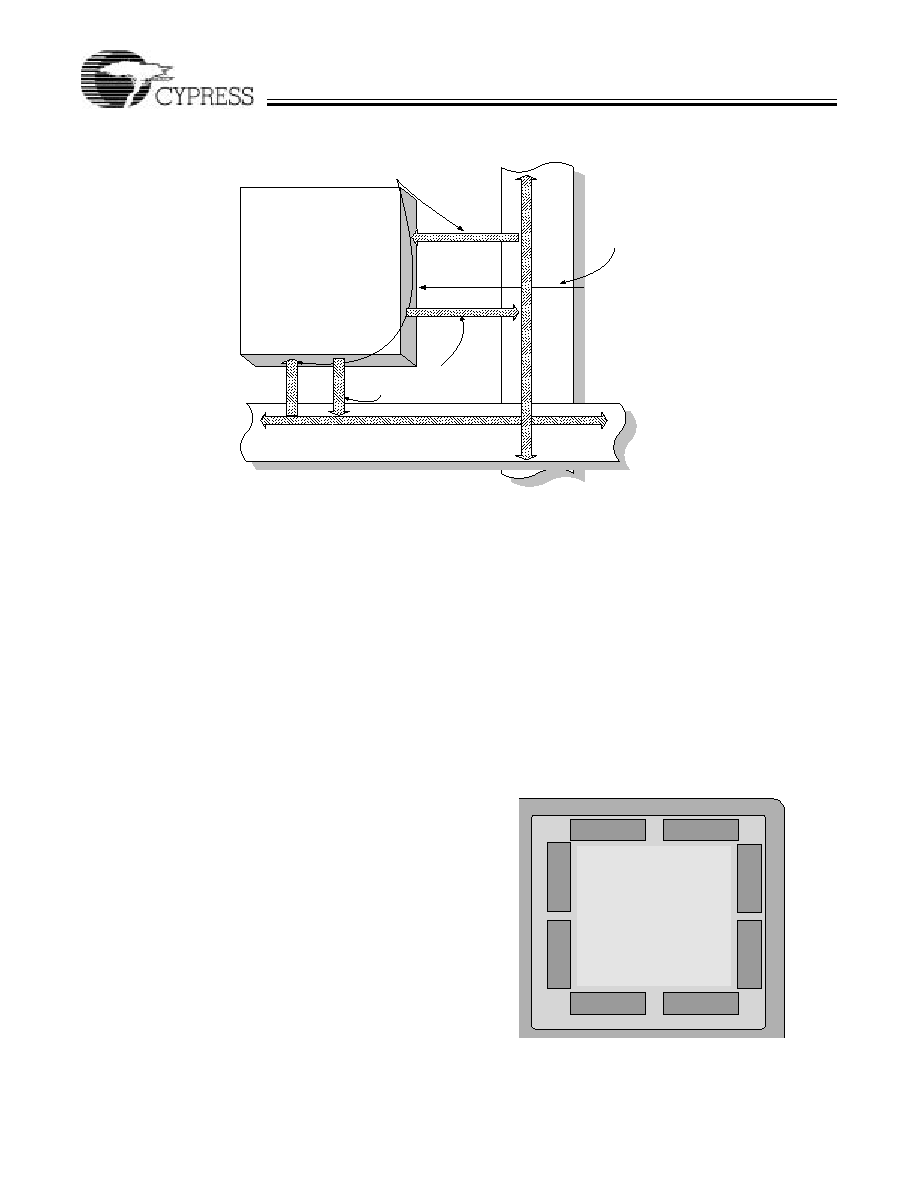

The architecture is based on Logic Block Clusters (LBC) that

are connected by Horizontal and Vertical (H and V) routing

channels. Each LBC features eight individual Logic Blocks

(LB) and two cluster memory blocks. Adjacent to each LBC is

a channel memory block, which can be accessed directly from

the I/O pins. Both types of memory blocks are highly config-

urable and can be cascaded in width and depth. See Figure 1

for a block diagram of the Delta39K architecture.

All the members of the Delta39K family have Cypress's highly

regarded In-System Reprogrammability (ISR) feature, which

simplifies both design and manufacturing flows, thereby

reducing costs. The ISR feature provides the ability to recon-

4

GCLK[3:0]

4

4

4

Channel

RAM

4

GCLK[3:0]

4

4

4

4

GCLK[3:0]

4

4

4

4

4

GCLK[3:0]

PLL and Clock MUX

GCTL[3:0]

I/O Bank 6

I/O Bank 7

I/O Bank 3

I/O Bank 2

I/

O

B

a

n

k

4

I/O

Ba

n

k

5

I/O

Ba

n

k

1

I/O

Ba

n

k

0

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

Channel

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

LB 4

LB 3

LB 0

Cluster

RAM

LB 5

LB 6

LB 7

LB 2

LB 1

PIM

Cluster

RAM

Figure 1. Delta39K100 Block Diagram (Three Rows ◊ Four Columns) with I/O Bank Structure

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 4 of 86

figure the devices without having design changes cause

pinout or timing changes in most cases. The Cypress ISR

function is implemented through a JTAG-compliant serial

interface. Data is shifted in and out through the TDI and TDO

pins respectively. Superior routability, simple timing, and the

ISR allows users to change existing logic designs while simul-

taneously fixing pinout assignments and maintaining system

performance.

The entire family features JTAG for ISR and boundary scan,

and is compatible with the PCI Local Bus specification,

meeting the electrical and timing requirements. The Delta39K

family also features user programmable bus-hold and slew

rate control capabilities on each I/O pin.

AnyVolt Interface

All Delta39KV devices feature an on-chip regulator, which

accepts 3.3V or 2.5V on the V

CC

supply pins and steps it down

to 1.8V internally, the voltage level at which the core operates.

With Delta39K's AnyVolt technology, the I/O pins can be

connected to either 1.8V, 2.5V, or 3.3V. All Delta39K devices

are 3.3V-tolerant regardless of V

CCIO

or V

CC

settings.

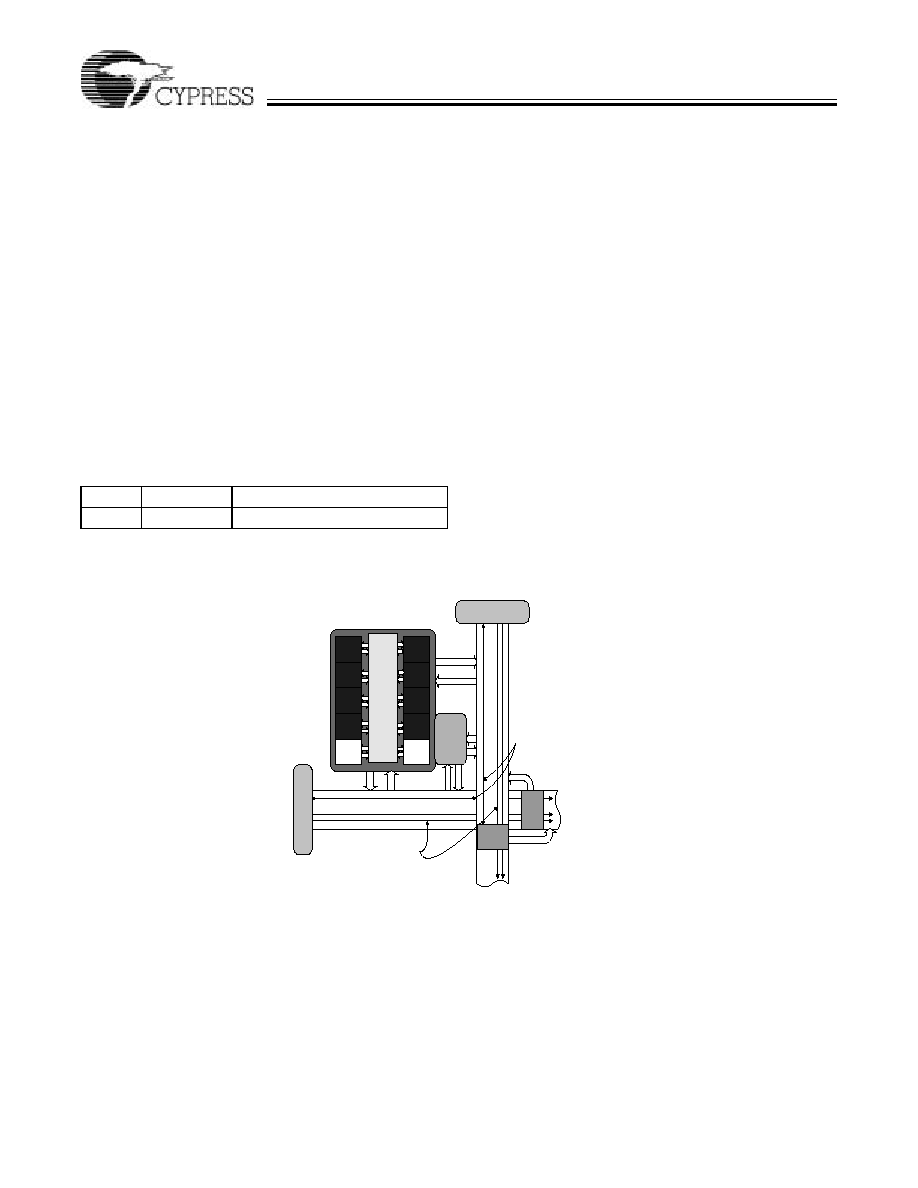

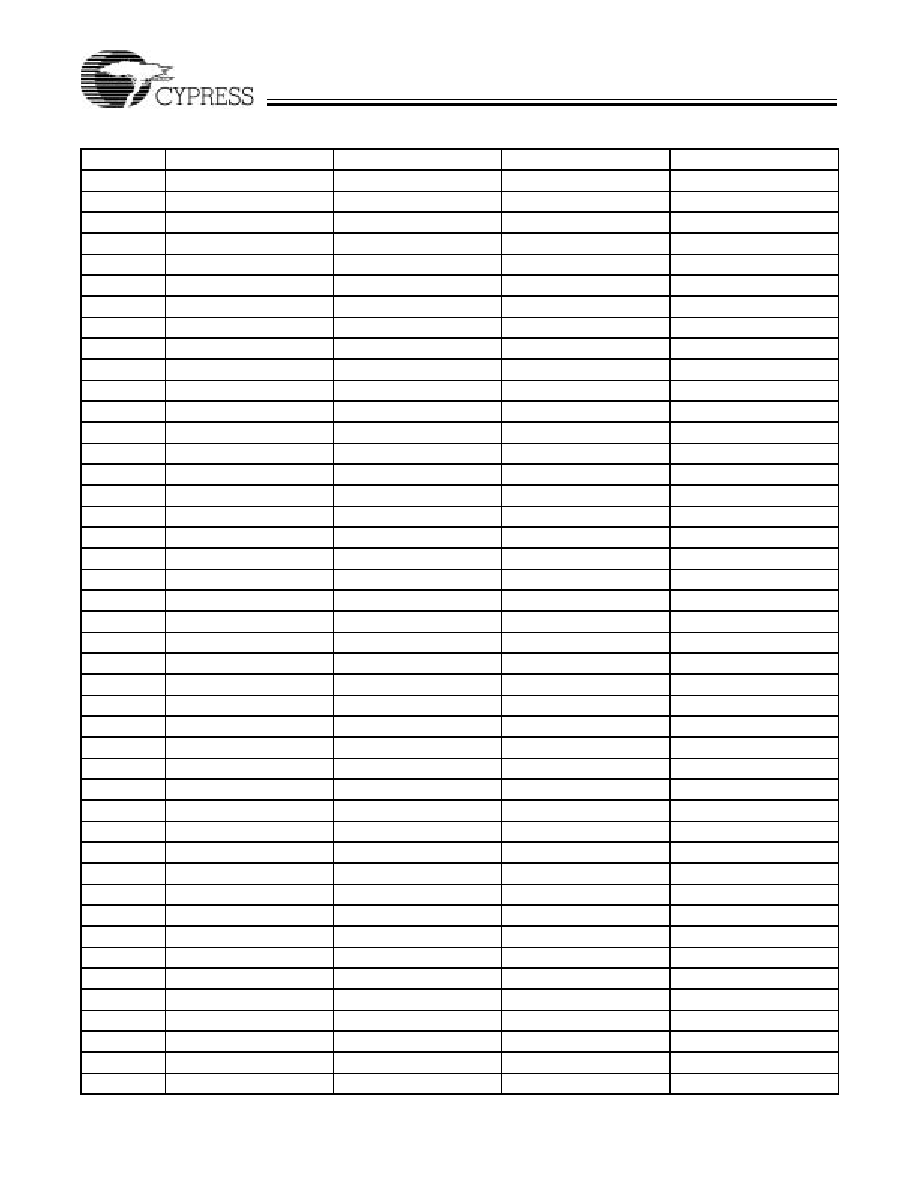

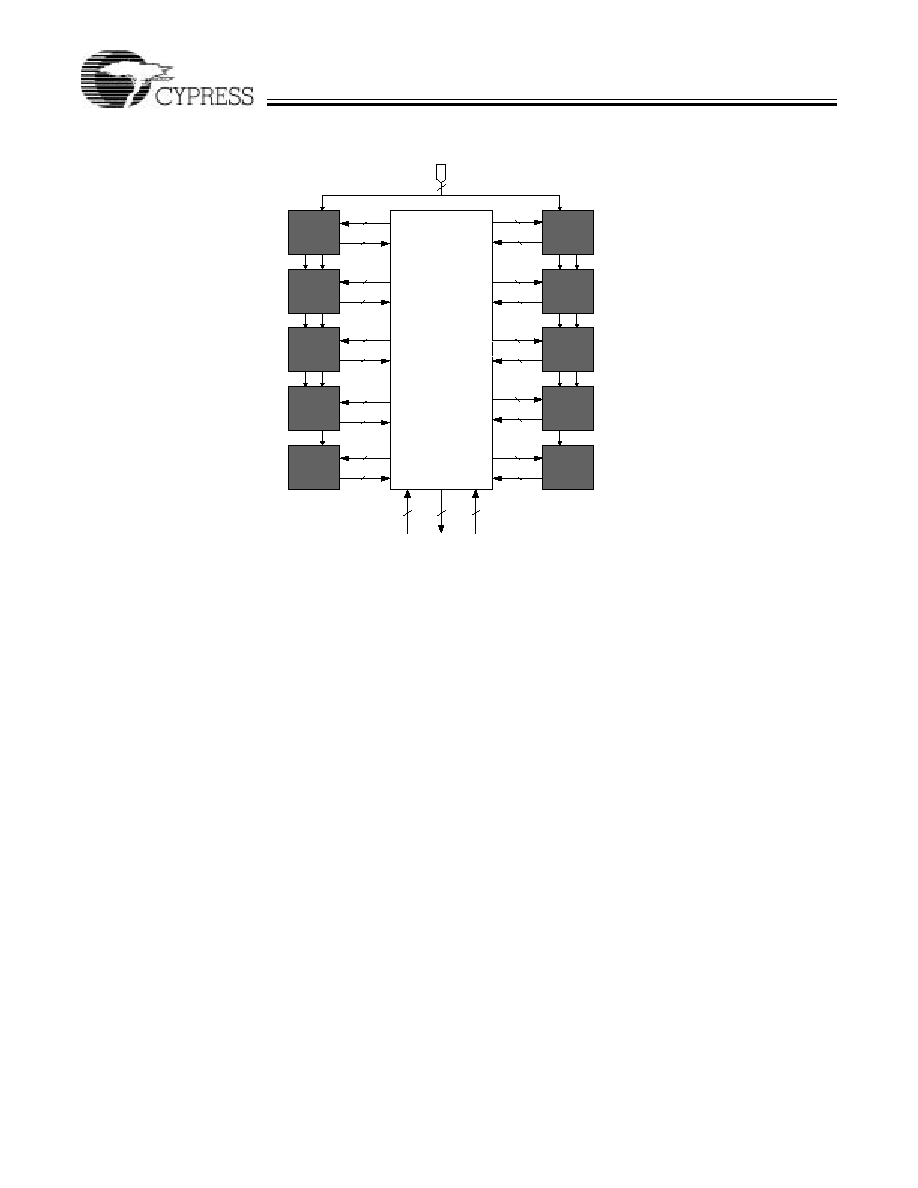

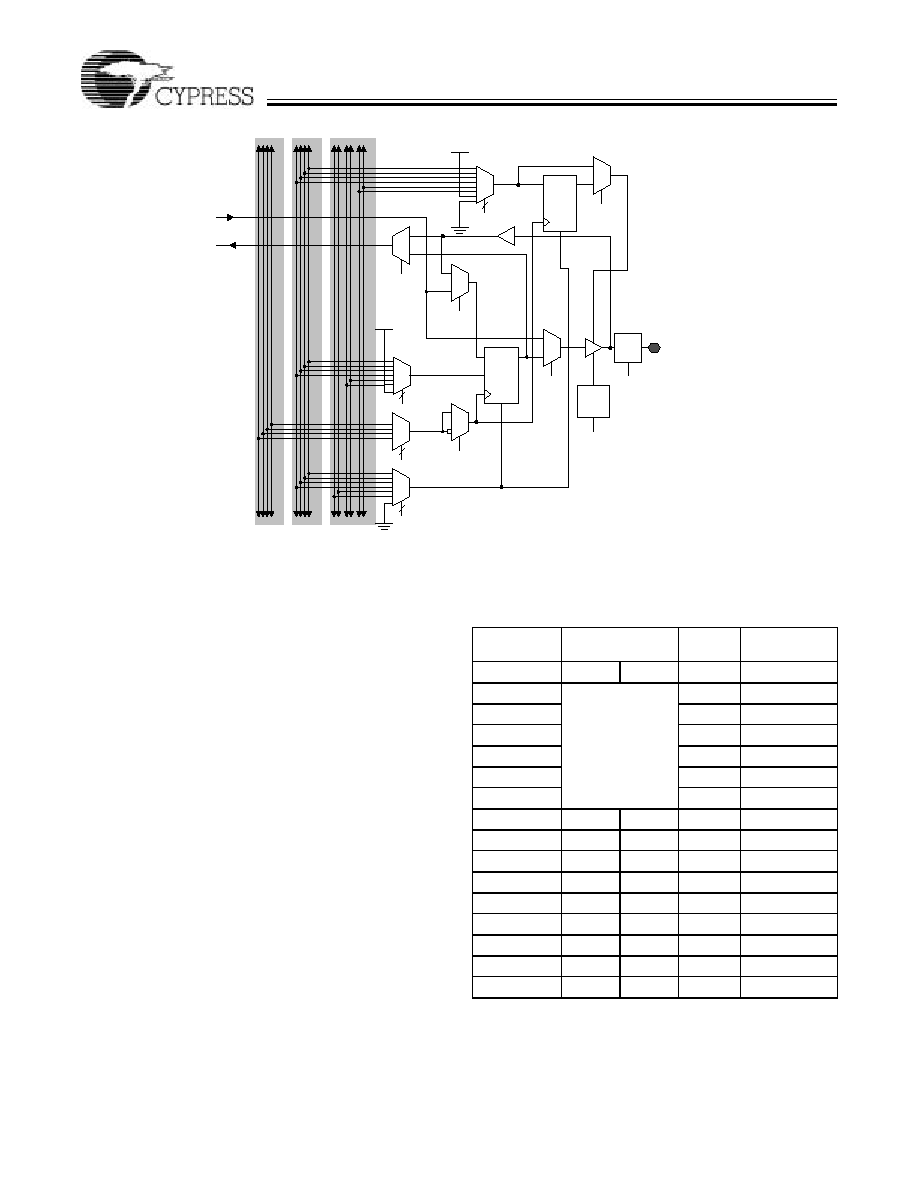

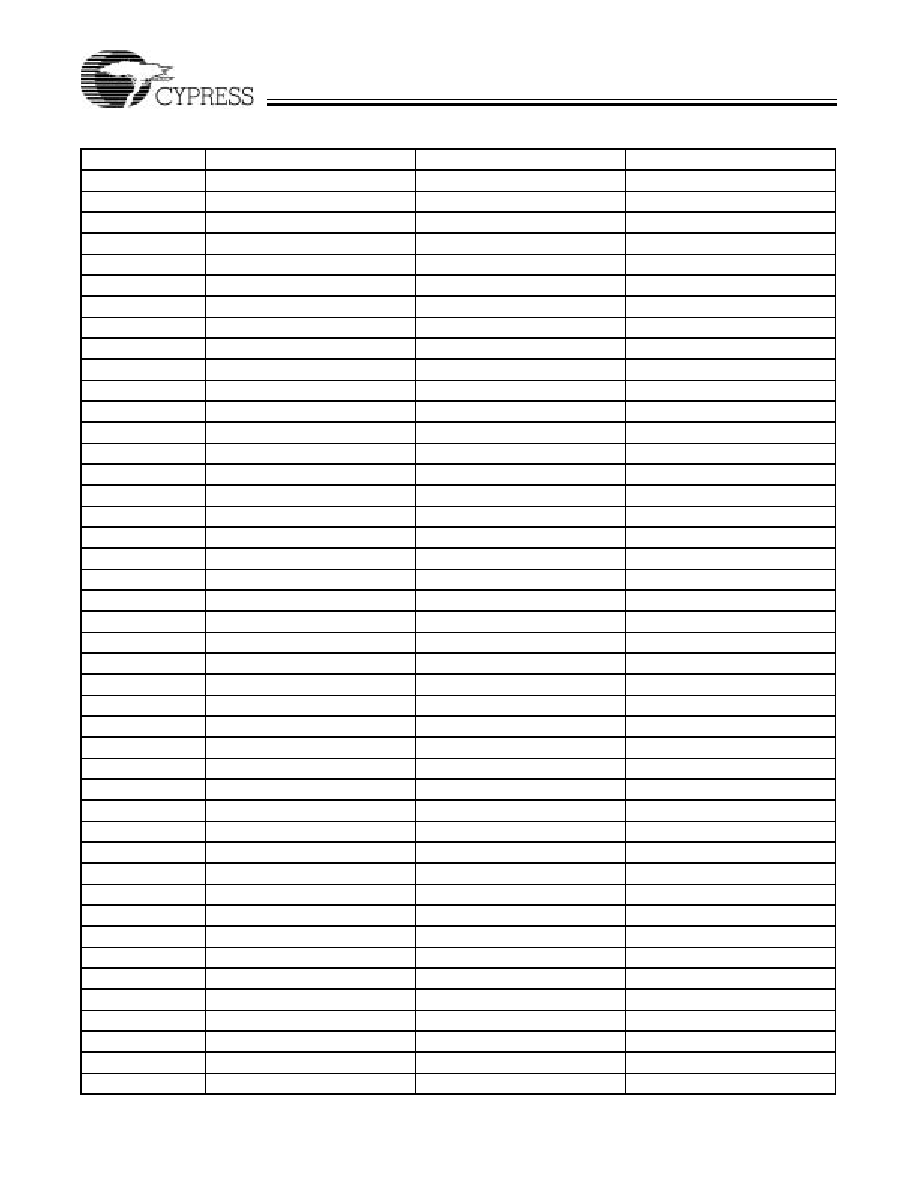

Global Routing Description

The routing architecture of the Delta39K is made up of

horizontal and vertical (H and V) routing channels. These

routing channels allow signals from each of the Delta39K

architectural components to communicate with one another. In

addition to the horizontal and vertical routing channels that

interconnect the I/O banks, channel memory blocks, and logic

block clusters, each LBC contains a Programmable Inter-

connect Matrix

(PIMTM), which is used to route signals

among the logic blocks and the cluster memory blocks.

Figure 2 is a block diagram of the routing channels that

interface within the Delta39K architecture. The LBC is exactly

the same for every member of the Delta39K CPLD family.

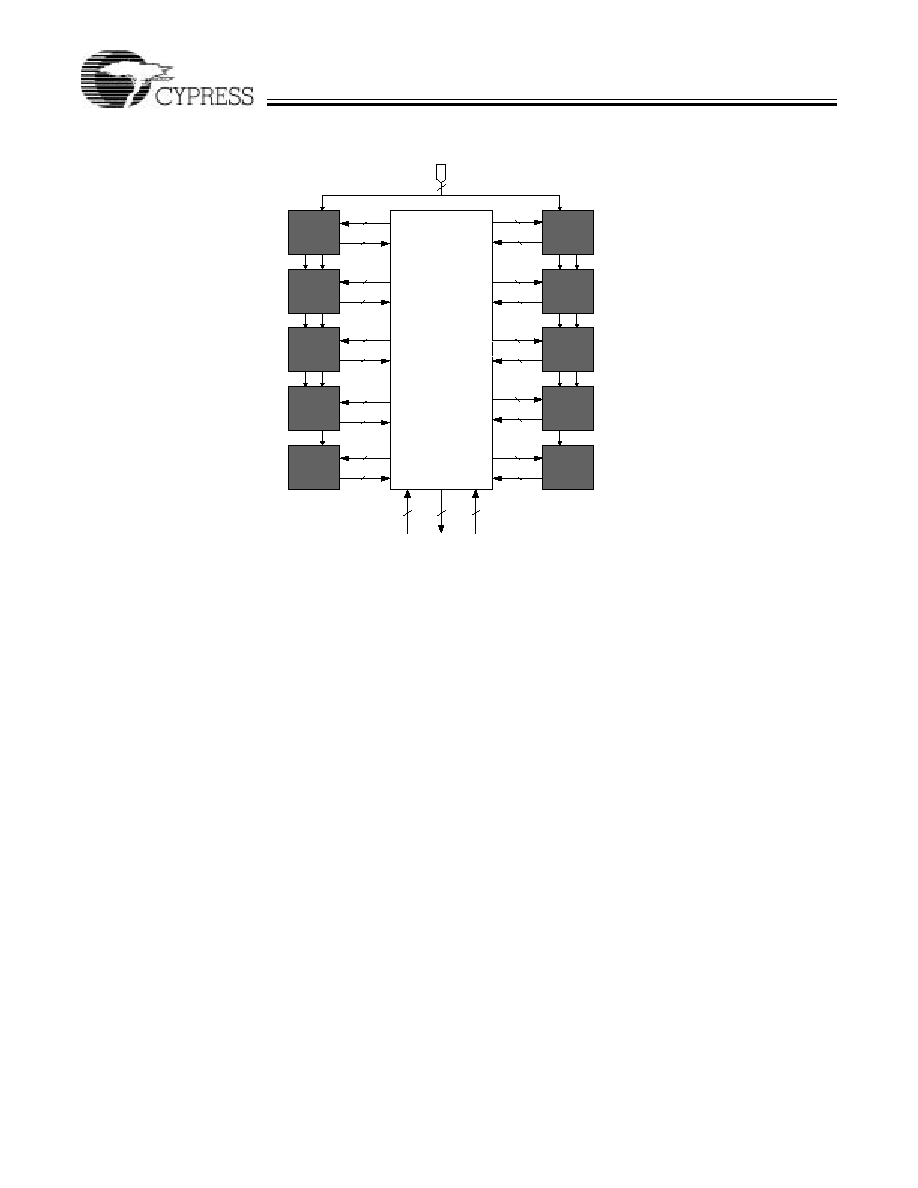

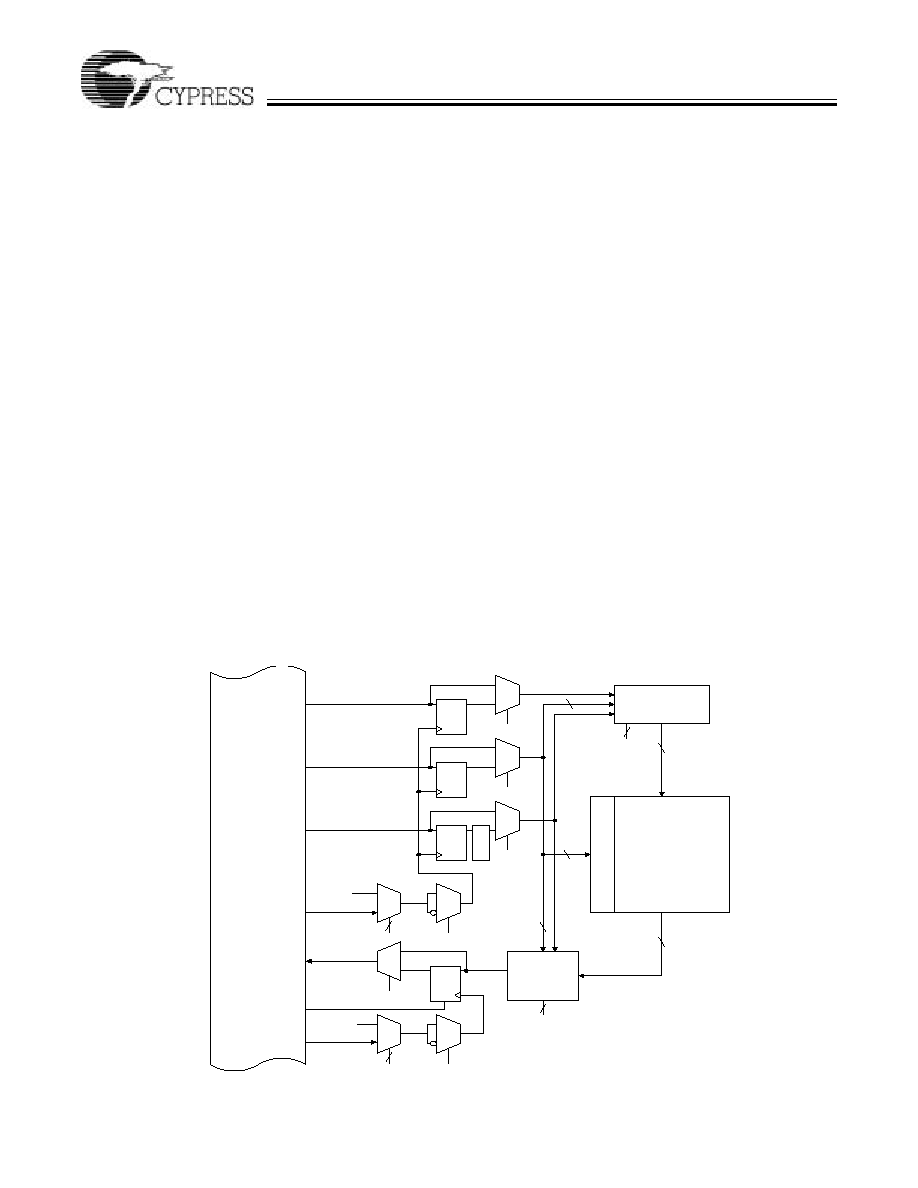

Logic Block Cluster (LBC)

The Delta39K architecture consists of several logic block

clusters, each of which have eight Logic Blocks (LB) and two

cluster memory blocks connected via a Programmable Inter-

connect Matrix (PIM) as shown in Figure 3. Each cluster

memory block consists of 8-Kbit single-port RAM, which is

configurable as synchronous or asynchronous. The cluster

memory blocks can be cascaded with other cluster memory

blocks within the same LBC as well as other LBCs to

implement larger memory functions. If a cluster memory block

is not specifically utilized by the designer, Cypress's Warp

software can automatically use it to implement large blocks of

logic.

All LBCs interface with each other via horizontal and vertical

routing channels.

Note:

5.

For HSTL only.

Table 1.

Device

V

CC

V

CCIO

39KV

3.3V or 2.5V

3.3V or 2.5V or 1.8V or 1.5V

[5]

LB

Cluster

PIM

Cluster

Memory

Block

LB

LB

LB

LB

Cluster

Memory

Block

LB

LB

LB

Channel

Memory

Block

I/O Block

I/O B

l

ock

Channel memory

outputs drive

dedicated tracks in the

horizontal and vertical

routing channels

H-to-V

PIM

V-to-H

PIM

Pin inputs from the I/O cells

drive dedicated tracks in the

horizontal and vertical routing

channels

72

72

64

64

Figure 2. Delta39K Routing Interface

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 5 of 86

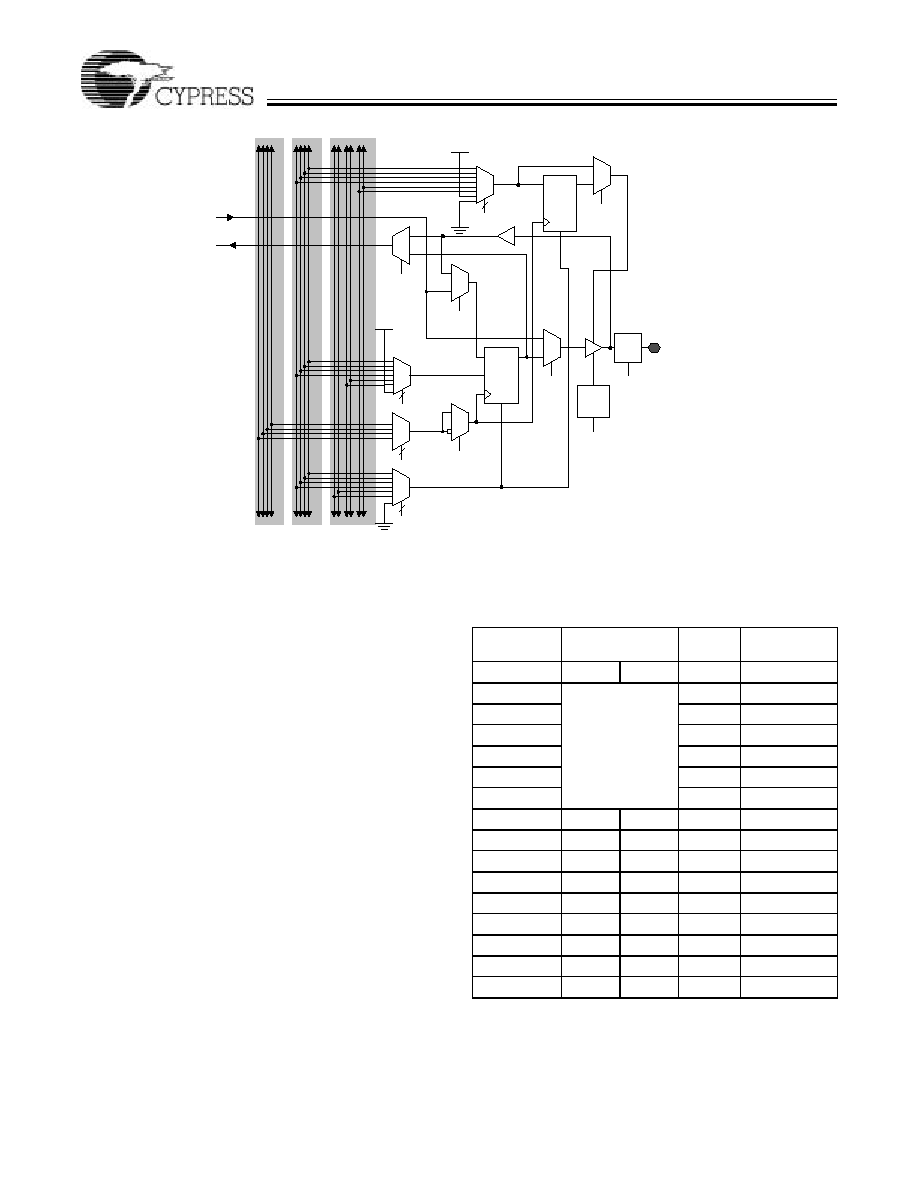

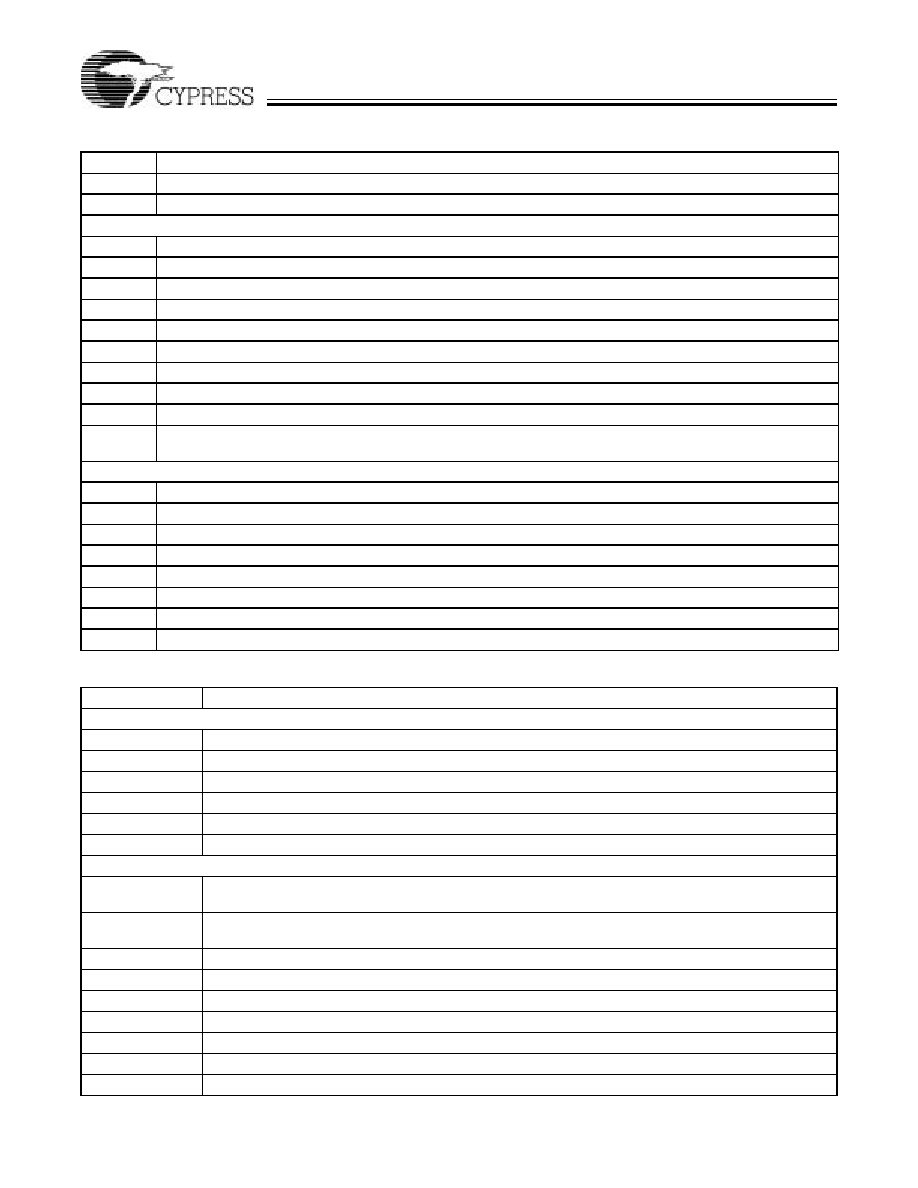

Logic Block

The LB is the basic building block of the Delta39K architecture.

It consists of a product term array, an intelligent product-term

allocator, and 16 macrocells.

Product Term Array

Each logic block features a 72 x 83 programmable product

term array. This array accepts 36 inputs from the PIM. These

inputs originate from device pins and macrocell feedbacks as

well as cluster memory and channel memory feedbacks.

Active LOW and active HIGH versions of each of these inputs

are generated to create the full 72-input field. The 83 product

terms in the array can be created from any of the 72 inputs.

Of the 83 product terms, 80 are for general-purpose use for

the 16 macrocells in the logic block. Two of the remaining three

product terms in the logic block are used as asynchronous set

and asynchronous reset product terms. The final product term

is the Product Term clock (PTCLK) and is shared by all 16

macrocells within a logic block.

Product Term Allocator

Through the product term allocator, Warp software automati-

cally distributes the 80 product terms as needed among the 16

macrocells in the logic block. The product term allocator

provides two important capabilities without affecting perfor-

mance: product term steering and product term sharing.

Product Term Steering

Product term steering is the process of assigning product

terms to macrocells as needed. For example, if one macrocell

requires ten product terms while another needs just three, the

product term allocator will "steer" ten product terms to one

macrocell and three to the other. On Delta39K devices,

product terms are steered on an individual basis. Any number

between 1 and 16 product terms can be steered to any

macrocell.

Product Term Sharing

Product term sharing is the process of using the same product

term among multiple macrocells. For example, if more than

one function has one or more product terms in its equation that

are common to other functions, those product terms are only

programmed once. The Delta39K product term allocator

allows sharing across groups of four macrocells in a variable

fashion. The software automatically takes advantage of this

capability so that the user does not have to intervene.

Note that neither product term sharing nor product term

steering have any effect on the speed of the product. All

steering and sharing configurations have been incorporated in

the timing specifications for the Delta39K devices.

.

Logic

Block

0

Logic

Block

1

Logic

Block

3

Logic

Block

2

Cluster

Memory

0

PIM

Logic

Block

7

Logic

Block

6

Logic

Block

4

Logic

Block

5

Cluster

Memory

1

64 Inputs From

Horizontal Routing

Channel

64 Inputs From

Vertical Routing

Channel

144 Outputs to

Horizontal and Vertical

cluster-to-channel PIMs

Clock Inputs

GCLK[3:0]

CC

CC

CC

CC

CC

CC

CC = Carry Chain

16

36

16

36

16

36

16

36

16

36

16

36

16

36

8

25

8

25

4

16

36

Figure 3. Delta39K Logic Block Cluster Diagram

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 6 of 86

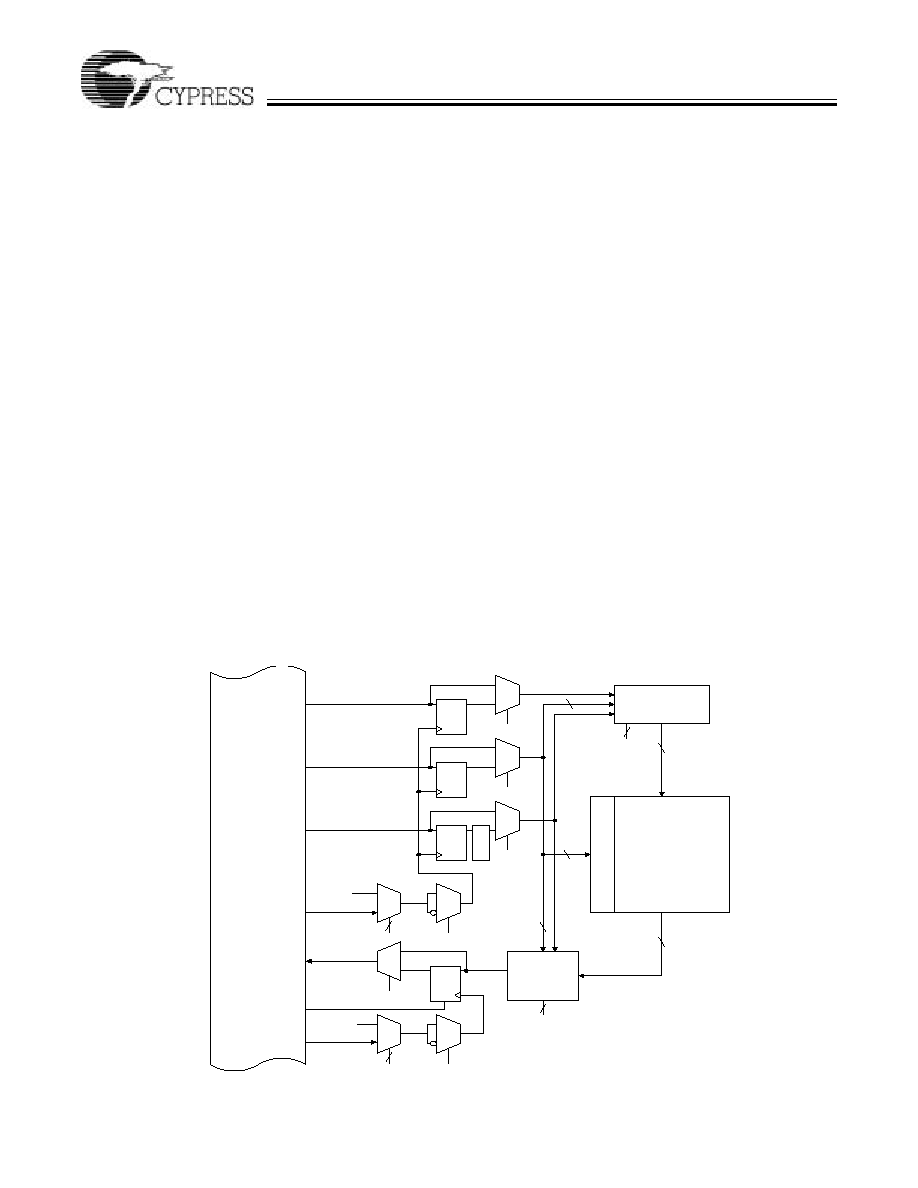

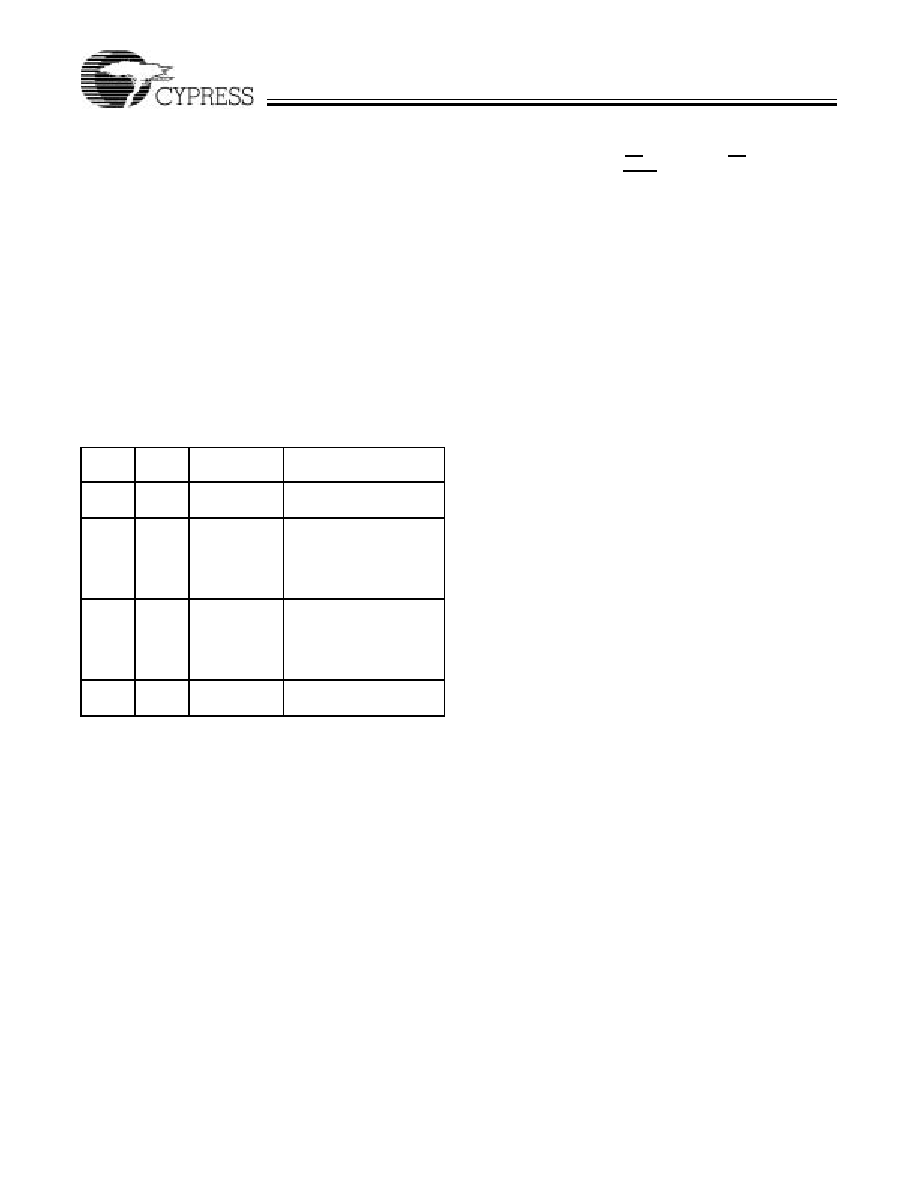

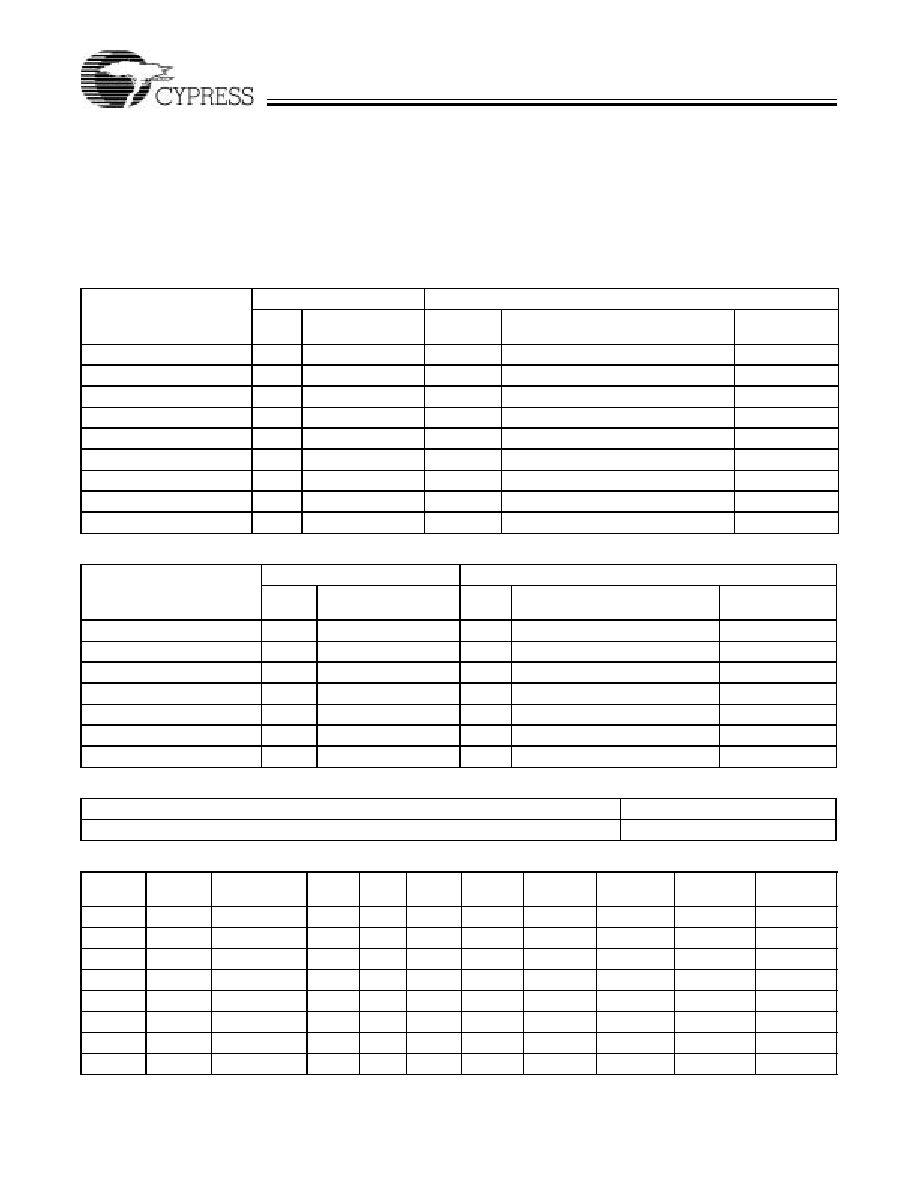

Macrocell

Within each logic block there are 16 macrocells. Each

macrocell accepts a sum of up to 16 product terms from the

product term array. The sum of these 16 product terms can be

output in either registered or combinatorial mode. Figure 4

displays the block diagram of the macrocell. The register can

be asynchronously preset or asynchronously reset at the

macrocell level with the separate preset and reset product

terms. Each of these product terms features programmable

polarity. This allows the registers to be preset or reset based

on an AND expression or an OR expression.

An XOR gate in the Delta39K macrocell allows for many

different types of equations to be realized. It can be used as a

polarity mux to implement the true or complement form of an

equation in the product term array or as a toggle to turn the D

flip-flop into a T flip-flop. The carry-chain input mux allows

additional flexibility for the implementation of different types of

logic. The macrocell can utilize the carry chain logic to

implement adders, subtractors, magnitude comparators,

parity tree, or even generic XOR logic. The output of the

macrocell is either registered or combinatorial.

Carry Chain Logic

The Delta39K macrocell features carry chain logic which is

used for fast and efficient implementation of arithmetic opera-

tions. The carry logic connects macrocells in up to four logic

blocks for a total of 64 macrocells. Effective data path opera-

tions are implemented through the use of carry-in arithmetic,

which drives through the circuit quickly. Figure 4 shows that

the carry chain logic within the macrocell consists of two

product terms (CPT0 and CPT1) from the PTA and an input

carry-in for carry logic. The inputs to the carry chain mux are

connected directly to the product terms in the PTA. The output

of the carry chain mux generates the carry-out for the next

macrocell in the logic block as well as the local carry input that

is connected to an input of the XOR input mux. Carry-in and a

configuration bit are inputs to an AND gate. This AND gate

provides a method of segmenting the carry chain in any

macrocell in the logic block.

Macrocell Clocks

Clocking of the register is highly flexible. Four global

synchronous clocks (GCLK[3:0]) and a PTCLK are available

at each macrocell register. Furthermore, a clock polarity mux

within each macrocell allows the register to be clocked on the

rising or the falling edge (see macrocell diagram in Figure 4).

PRESET/RESET Configurations

The macrocell register can be asynchronously preset and

reset using the PRESET and RESET mux. Both signals are

active high and can be controlled by either of two Preset/Reset

product terms (PRC[1:0] in Figure 4) or GND. In situations

where the PRESET and RESET are active at the same time,

RESET takes priority over PRESET.

D

Q

PSET

RES

GCLK[3:0]

PTCLK

FROM PTM

CPT0

CPT1

P

R

C

[1:0]

0

1

0

1

To PIM

C

Carry Out

(to macrocell n+1)

Carry In

(from macrocell n-1)

Up To 16 PTs

PRESET

Mux

Clock

Polarity

Mux

RESET

Mux

Clock Mux

Carry Chain

Mux

XOR Input

Mux

Output

Mux

Q

C

3

3

2

3

C

C

C

C

C

C

Figure 4. Delta39K Macrocell

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 7 of 86

Embedded Memory

Each member of the Delta39K family contains two types of

embedded memory blocks. The channel memory block is

placed at the intersection of horizontal and vertical routing

channels. Each channel memory block is 4096 bits in size and

can be configured as asynchronous or synchronous Dual-Port

RAM, Single-Port RAM, Read-Only memory (ROM), or

synchronous FIFO memory. The memory organization is

configurable as 4K ◊ 1, 2K ◊ 2, 1K ◊ 4 and 512K ◊ 8. The

second type of memory block is located within each LBC and

is referred to as a cluster memory block. Each LBC contains

two cluster memory blocks that are 8192 bits in size. Similar

to the channel memory blocks, the cluster memory blocks can

be configured as 8K ◊ 1, 4K ◊ 2, 2K ◊ 4 and 1K ◊ 8

asynchronous or synchronous Single-Port RAM or ROM.

Cluster Memory

Each logic block cluster of the Delta39K contains two 8192-bit

cluster memory blocks. Figure 5 is a block diagram of the

cluster memory block and the interface of the cluster memory

block to the cluster PIM.

The output of the cluster memory block can be optionally regis-

tered to perform synchronous pipelining or to register

asynchronous Read and Write operations. The output

registers contain an asynchronous RESET which can be used

in any type of sequential logic circuits (e.g., state machines).

There are four global clocks (GCLK[3:0]) and one local clock

available for the input and the output registers. The local clock

for the input registers is independent of the one used for the

output registers. The local clock is generated in the user

design in a macrocell or comes from an I/O pin.

Cluster Memory Initialization

The cluster memory powers up in an undefined state, but is set

to a user-defined known state during configuration. To facilitate

the use of look-up-table (LUT) logic and ROM applications, the

cluster memory blocks can be initialized with a given set of

data when the device is configured at power up. For LUT and

ROM applications, the user cannot write to memory blocks.

Channel Memory

The Delta39K architecture includes an embedded memory

block at each crossing point of horizontal and vertical routing

channels. The channel memory is a 4096-bit embedded

memory block that can be configured as asynchronous or

synchronous single-port RAM, dual-port RAM, ROM, or

synchronous FIFO memory.

Data, address, and control inputs to the channel memory are

driven from horizontal and vertical routing channels. All data

and FIFO logic outputs drive dedicated tracks in the horizontal

and vertical routing channels. The clocks for the channel

memory block are selected from four global clocks and pin

inputs from the horizontal and vertical channels. The clock

muxes also include a polarity mux for each clock so that the

user can choose an inverted clock.

Dual-Port (Channel Memory) Configuration

Each port has distinct address inputs, as well as separate data

and control inputs that can be accessed simultaneously. The

inputs to the Dual-Port memory are driven from the horizontal

and vertical routing channels. The data outputs drive

dedicated tracks in the routing channels. The interface to the

routing is such that Port A of the Dual-Port interfaces primarily

with the horizontal routing channel and Port B interfaces

primarily with the vertical routing channel.

5:1

DIN[7:0]

D

Q

ADDR[12:0]

D

Q

Cluster PIM

D

Q

WE

Wr

i

t

e

Pu

l

s

e

Write

Control

Logic

1024x8

Asynchronous

SRAM

Read

Control

Logic

Row Dec

ode (

1024 Rows

)

DOUT[7:0]

8

3

3

8

10

C

C

D

Q

GCLK[3:0]

5:1

R

RESET

GCLK[3:0]

C

Local CLK

2

Local CLK

3

2

3

C

C

C

C

C

C

C

Figure 5. Block Diagram of Cluster Memory Block

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 8 of 86

The clocks for each port of the Dual-Port configuration are

selected from four global clocks and two local clocks. One

local clock is sourced from the horizontal channel and the

other from the vertical channel. The data outputs of the dual-

port memory can also be registered. Clocks for the output

registers are also selected from four global clocks and two

local clocks. One clock polarity mux per port allows the use of

true or complement polarity for input and output clocking

purposes.

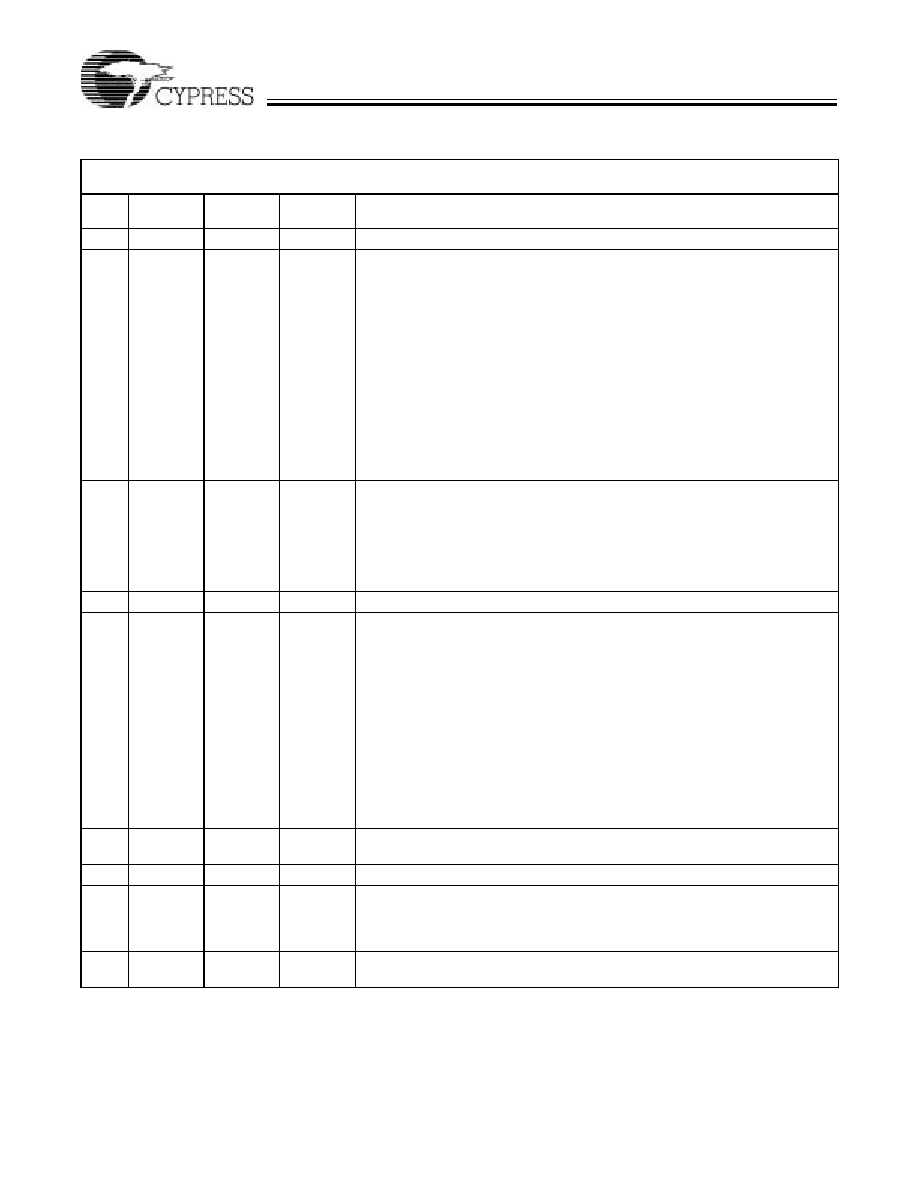

Arbitration

The Dual-Port configuration of the Channel Memory Block

provides arbitration when both ports access the same address

at the same time. Depending on the memory operation being

attempted, one port always gets priority. See Table 2 for

details on which port gets priority for Read and Write opera-

tions. An active-LOW "Address Match" signal is generated

when an address collision occurs.

FIFO (Channel Memory) Configuration

The channel memory blocks are also configurable as

synchronous FIFO RAM. In the FIFO mode of operation, the

channel memory block supports all normal FIFO operations

without the use of any general-purpose logic resources in the

device.

The FIFO block contains all of the necessary FIFO flag logic,

including the Read and Write address pointers. The FIFO flags

include an empty/full flag (EF), half-full flag (HF), and program-

mable almost-empty/full (PAEF) flag output. The FIFO config-

uration has the ability to perform simultaneous Read and Write

operations using two separate clocks. These clocks may be

tied together for a single operation or may run independently

for asynchronous Read/Write (with regard to each other) appli-

cations. The data and control inputs to the FIFO block are

driven from the horizontal or vertical routing channels. The

data and flag outputs are driven onto dedicated routing tracks

in both the horizontal and vertical routing channels. This allows

the FIFO blocks to be expanded by using multiple FIFO blocks

on the same horizontal or vertical routing channel without any

speed penalty.

In FIFO mode, the Write and Read ports are controlled by

separate clock and enable signals. The clocks for each port

are selected from four global clocks and two local clocks.

One local clock is sourced from the horizontal channel and the

other from the vertical channel. The data outputs from the

Read port of the FIFO can also be registered. One clock

polarity mux per port allows using true or complement polarity

for Read and Write operations. The Write operation is

controlled by the clock and the Write enable pin. The Read

operation is controlled by the clock and the Read enable pin.

The enable pins can be sourced from horizontal or vertical

channels.

Channel Memory Initialization

The channel memory powers up in an undefined state, but is

set to a user-defined known state during configuration. To facil-

itate the use of look-up-table (LUT) logic and ROM applica-

tions, the channel memory blocks can be initialized with a

given set of data when the device is configured at power up.

For LUT and ROM applications, the user cannot write to

memory blocks.

Channel Memory Routing Interface

Similar to LBC outputs, the channel memory blocks feature

dedicated tracks in the horizontal and vertical routing channels

for the data outputs and the flag outputs, as shown in

Figure 6. This allows the channel memory blocks to be

expanded easily. These dedicated lines can be routed to I/O

pins as chip outputs or to other logic block clusters to be used

in logic equations.

Table 2. Arbitration Result: Address Match Signal

Becomes Active

Port A

Port B

Result of

Arbitration

Comment

Read

Read

No arbitration

required

Both ports read at the

same time

Write Read

Port

A

gets

priority

If Port B requests first then

it will read the current

data. The output will then

change to the newly

written data by Port A

Read

Write

Port B gets

priority

If Port A requests first then

it will read the current

data. The output will then

change to the newly

written data by Port B

Write

Write

Port A gets

priority

Port B is blocked until Port

A is finished writing

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 9 of 86

I/O Banks

The Delta39K interfaces the horizontal and vertical routing

channels to the pins through I/O banks. There are eight I/O

banks per device as shown in Figure 7, and all I/Os from an

I/O bank are located in the same section of a package for PCB

layout convenience.

Delta39K devices support True Vertical MigrationTM (i.e., for

each package type, Delta39K devices of different densities

keep given pins in the same I/O banks). This allows for easy

and simple implementation of multiple I/O standards during the

design and prototyping phase, before a final density has been

determined. Please refer to the application note titled "Family,

Package and Density Migration in Delta 39K and Quantum38K

CPLDs."

Each I/O bank contains several I/O cells, and each I/O cell

contains an input/output register, an output enable register,

programmable slew rate control and programmable bus hold

control logic. Each I/O cell drives a pin output of the device;

the cell also supplies an input to the device that connects to a

dedicated track in the associated routing channel.

Each I/O bank can use any supported I/O standard by

supplying appropriate V

REF

and V

CCIO

voltages and config-

uring the I/O through the Warp software. All the V

REF

and

V

CCIO

pins in an I/O bank must be connected to the same V

REF

and V

CCIO

voltage respectively. This requirement restricts the

number of I/O standards supported by an I/O bank at any given

time.

The number of I/Os which can be used in each I/O bank

depend on the type of I/O standards and the number of V

CCIO

and GND pins being used. This restriction is derived from the

electromigration limit of the V

CCIO

and GND bussing on the

chip. Please refer to the note on page 17 and the application

note titled "Delta39K Family Device I/O Standards and Config-

urations" for details.

I/O Cell

Figure 8 is a block diagram of the Delta39K I/O cell. The I/O

cell contains a three-state input buffer, an output buffer, and a

register that can be configured as an input or output register.

The output buffer has a slew rate control option that can be

used to configure the output for a slower slew rate. The input

of the device and the pin output can each be configured as

registered or combinatorial; however, only one path can be

configured as registered in a given design.

The output enable in an I/O cell can be selected from one of

the four global control signals or from one of two Output

Control Channel (OCC) signals. The output enable can be

configured as always enabled or always disabled or it can be

controlled by one of the remaining inputs to the mux. The

selection is done via a mux that includes V

CC

and GND as

inputs.

Figure 6. Block Diagram of Channel Memory Block

4096-bit Dual-Port

Array

Configurable as

Async/Sync Dual-Port

or Sync FIFO

Configurable as

4K x 1, 2K x 2, 1K x 4,

and 512 x 8 block sizes

Horizontal Channel

All channel memory

inputs are driven from

the routing channels

All channel memory outputs

drive dedicated tracks in the

routing channels

GCLK[3:0]

Global Clock

Signals

Ver

t

i

c

al

C

hannel

Delta39K

bank

0

bank

1

bank

4

bank

5

bank 2

bank 3

bank 6

bank 7

Delta39K

Figure 7. Delta39K I/O Bank Block Diagram

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 10 of 86

I/O Signals

There are four dedicated inputs (GCTL[3:0]) that are used as

Global I/O Control Signals available to every I/O cell. These

global I/O control signals may be used as output enables,

register resets and register clock enables as shown in

Figure 8. These global control signals, driven from four

dedicated pins, can only be used as active-high signals and

are available only to the I/O cells thereby implementing fast

resets, register and output enables.

In addition, there are six OCC signals available to each I/O

cell. These control signals may be used as output enables,

register resets and register clock enables as shown in

Figure 8. Unlike global control signals, these OCC signal can

be driven from internal logic or and I/O pin.

One of the four global clocks can be selected as the clock for

the I/O cell register. The clock mux output is an input to a clock

polarity mux that allows the input/output register to be clocked

on either edge of the clock

Slew Rate Control

The output buffer has a slew rate control option. This allows

the output buffer to slew at a fast rate (3 V/ns) or a slow rate

(1 V/ns). All I/Os default to fast slew rate. For designs

concerned with meeting FCC emissions standards the slow

edge provides for lower system noise. For designs requiring

very high performance the fast edge rate provides maximum

system performance.

D

Q

RES

E

G

l

obal

I/O

C

ontr

o

l

Si

gnal

s

O

u

tput C

ontr

o

l

C

hannel

O

C

C

G

l

obal

C

l

oc

k

Si

gnal

s

Slew

Rate

Control

C

I/O

From

Output PIM

To Routing

Channel

OE Mux

Register Input

Mux

Register Enable

Mux

Output Mux

Clock Mux

Clock

Polarity

Mux

Register Reset

Mux

Input

Mux

Bus

Hold

C

D

Q

RES

C

Registered OE

Mux

C

C

C

3

C

3

C

2

3

C

C

C

Figure 8. Block Diagram of I/O Cell

Table 3.

I/O Standards

I/O

Standard

V

REF

(V)

V

CCIO

Termination

Voltage (V

TT

)

Min.

Max.

LVTTL

N/A

3.3V

N/A

LVCMOS

3.3V

N/A

LVCMOS3

3.0V

N/A

LVCMOS2

2.5V

N/A

LVCMOS18

1.8V

N/A

3.3V PCI

3.3V

N/A

GTL+ 0.9

1.1

N/A

1.5

SSTL3 I

1.3

1.7

3.3V

1.5

SSTL3 II

1.3

1.7

3.3V

1.5

SSTL2 I

1.15

1.35

2.5V

1.25

SSTL2 II

1.15

1.35

2.5V

1.25

HSTL I

0.68

0.9

1.5V

0.75

HSTL II

0.68

0.9

1.5V

0.75

HSTL III

0.68

0.9

1.5V

1.5

HSTL IV

0.68

0.9

1.5V

1.5

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 11 of 86

Programmable Bus Hold

On each I/O pin, user-programmable-bus-hold is included.

Bus-hold, which is an improved version of the popular internal

pull-up resistor, is a weak latch connected to the pin that does

not degrade the device's performance. As a latch, bus-hold

maintains the last state of a pin when the pin is placed in a

high-impedance state, thus reducing system noise in bus-

interface applications. Bus-hold additionally allows unused

device pins to remain unconnected on the board, which is

particularly useful during prototyping as designers can route

new signals to the device without cutting trace connections to

V

CC

or GND. For more information, see the application note

titled "Understanding Bus-Hold≠A Feature of Cypress

CPLDs."

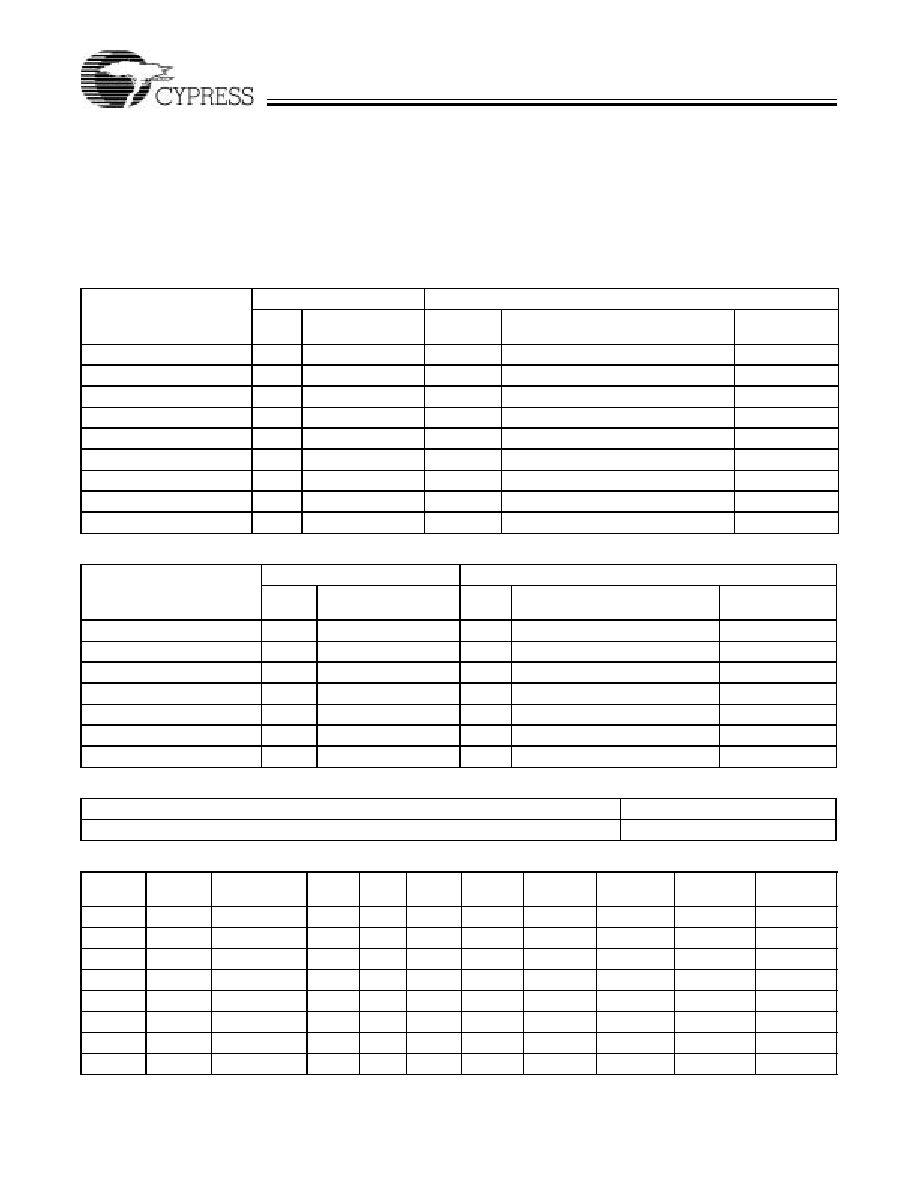

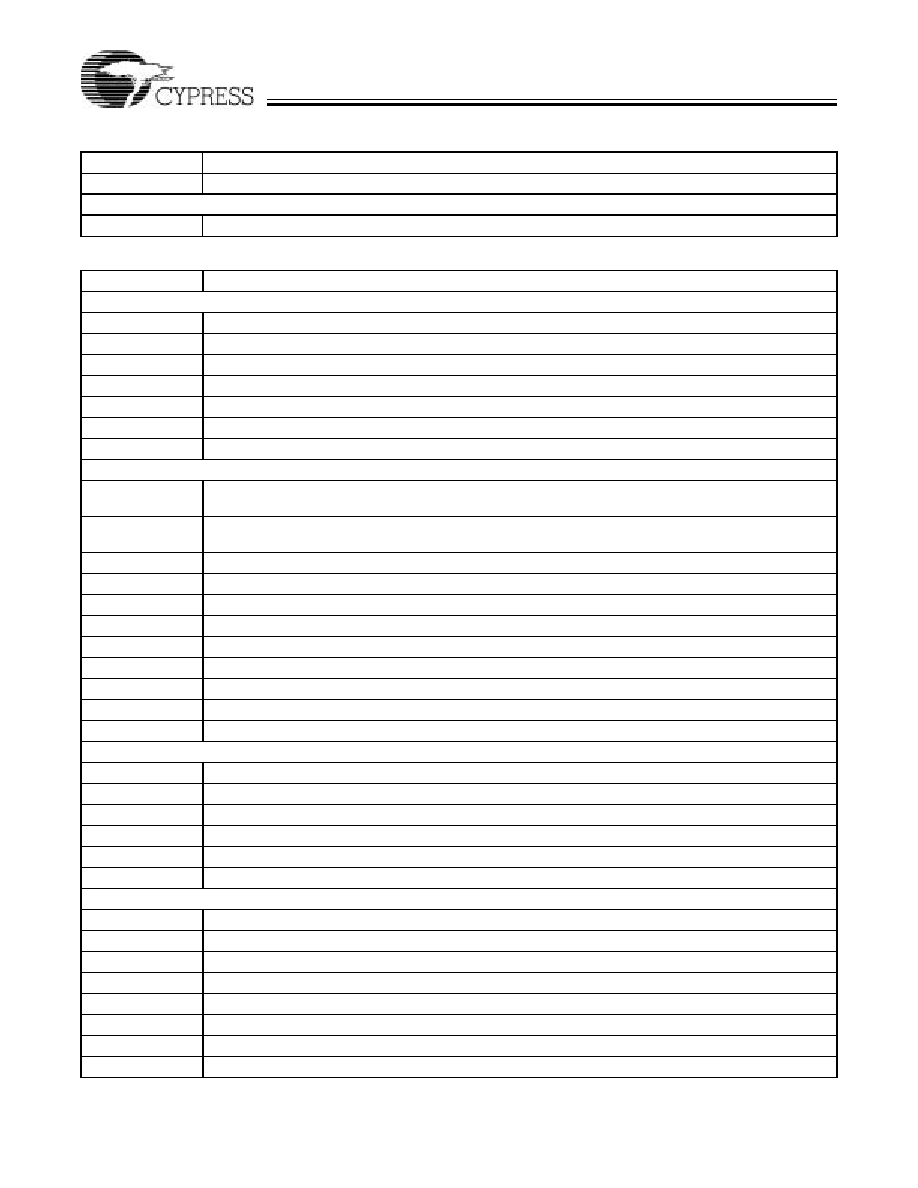

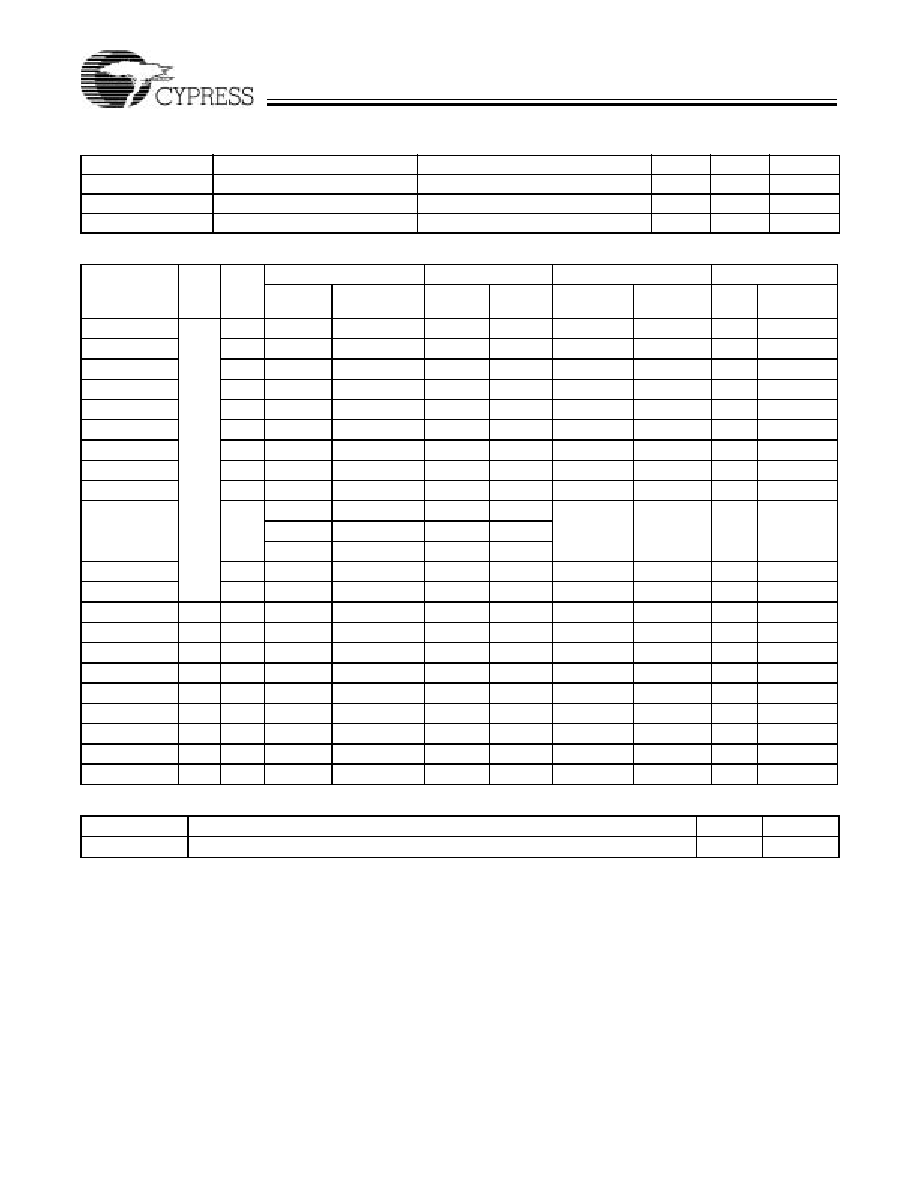

Clocks

Delta39K has four dedicated clock input pins (GCLK[3:0]) to

accept system clocks. One of these clocks (GCLK[0]) may be

selected to drive an on-chip phase-locked loop (PLL) for

frequency modulation (see Figure 9 for details).

The global clock tree for a Delta39K device can be driven by

a combination of the dedicated clock pins and/or the PLL-

derived clocks. The global clock tree consists of four global

clocks that go to every macrocell, memory block, and I/O cell.

Clock Tree Distribution

The global clock tree performs two primary functions. First, the

clock tree generates the four global clocks by multiplexing four

dedicated clocks from the package pins and four PLL driven

clocks. Second, the clock tree distributes the four global clocks

to every cluster, channel memory, and I/O block on the die.

The global clock tree is designed such that the clock skew is

minimized while maintaining an acceptable clock delay.

Spread Aware PLL

Each device in the Delta39K family features an on-chip PLL

designed using Spread Aware technology for low EMI applica-

tions. In general, PLLs are used to implement time-division-

multiplex circuits to achieve higher performance with fewer

device resources.

For example, a system that operates on a 32-bit data path that

runs at 40 MHz can be implemented with 16-bit circuitry that

runs internally at 80 MHz. PLLs can also be used to take

advantage of the positioning of the internally generated clock

edges to shift performance towards improved setup, hold or

clock-to-out times.

There are several frequency multiply (X1, X2, X3, X4, X5, X6,

X8, X16) and divide (/1, /2, /3, /4, /5, /6, /8, /16) options

available to create a wide range of clock frequencies from a

single clock input (GCLK[0]). For increased flexibility, there are

seven phase shifting options which allow clock skew/deskew

by 45∞, 90∞, 135∞, 180∞, 225∞, 270∞, or 315∞.

The Spread Aware feature refers to the ability of the PLL to

track a spread-spectrum input clock such that its spread is

seen on the output clock with the PLL staying locked. The total

amount of spread on the input clock should be limited to 0.6%

of the fundamental frequency. Spread Aware feature is

supported only with X1, X2, and X4 multiply options.

The Voltage Controlled Oscillator (VCO), the core of the

Delta39K PLL is designed to operate within the frequency

range of 100 MHz to 266 MHz. Hence, the multiply option

combined with input (GCLK[0]) frequency should be selected

such that this VCO operating frequency requirement is met.

This is demonstrated in Table 4 (columns 1, 2, and 3).

Another feature of this PLL is the ability to drive the output

clock (INTCLK) off the Delta39K chip to clock other devices on

the board, as shown in Figure 9 above. This off-chip clock is

half the frequency of the output clock as it has to go through a

register (I/O register or a macrocell register).

This PLL can also be used for board de-skewing purpose by

driving a PLL output clock off-chip, routing it to the other

devices on the board and feeding it back to the PLL's external

feedback input (GCLK[1]). When this feature is used, only

limited multiply, divide and phase shift options can be used.

Table 4 describes the valid multiply and divide options that can

be used without external feedback. Table 5 describes the valid

multiply and divide options that can be used with an external

feedback.

G

C

L

K

[

3:0]

GCLK0

GCLK1

fb

Source

Clock

Clock Tree

Delay

Lock

PLL

X1, X2, X3, X4, 5X,

X6, X8, X16

GCLK0

GCLK1

GCLK2

INTCLK0

INTCLK1

INTCLK2

Normal I/O signal path

Lock Detect/IO pin

Any Register (TFF)

INTCLK0, INTCLK1, INTCLK2, INTCLK3

Send a global clock off

chip

C

C

C

C

C

C

Clk

0

0

Clk

90

0

Clk 180

0

Clk

270

0

Clk

225

0

Clk 135

0

Clk 45

0

Clk

315

0

Divide

GCLK3

INTCLK3

2

2

2

2

2

fb

off-chip signal (external feedback)

Phase selection

Phase selection

Phase selection

Phase selection

∏ 1-6,8,16

Divide

∏ 1-6,8,16

Divide

∏ 1-6,8,16

Divide

∏ 1-6,8,16

Figure 9. Block Diagram of Spread Aware PLL

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 12 of 86

Table 6 describes the valid phase shift options that can be

used with or without an external feedback.

Table 7 is an example of the effect of all the available divide

and phase shift options on a VCO output of 250 MHz. It also

shows the effect of division on the duty cycle of the resultant

clock. Note that the duty cycle is 50-50 when a VCO output is

divided by an even number. Also note that the phase shift

applies to the VCO output and not to the divided output.

For more details on the architecture and operation of this PLL

please refer to the application note entitled "Delta39K PLL and

Clock Tree".

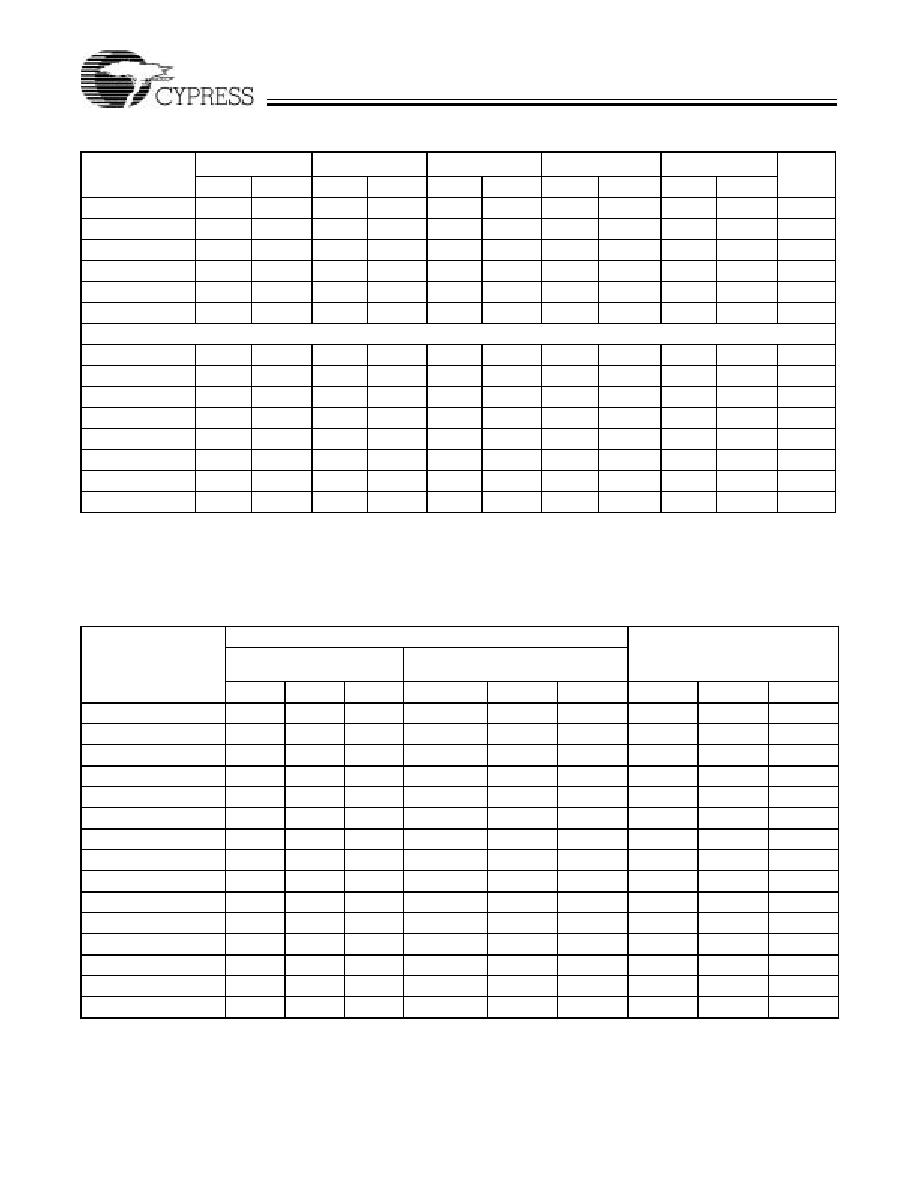

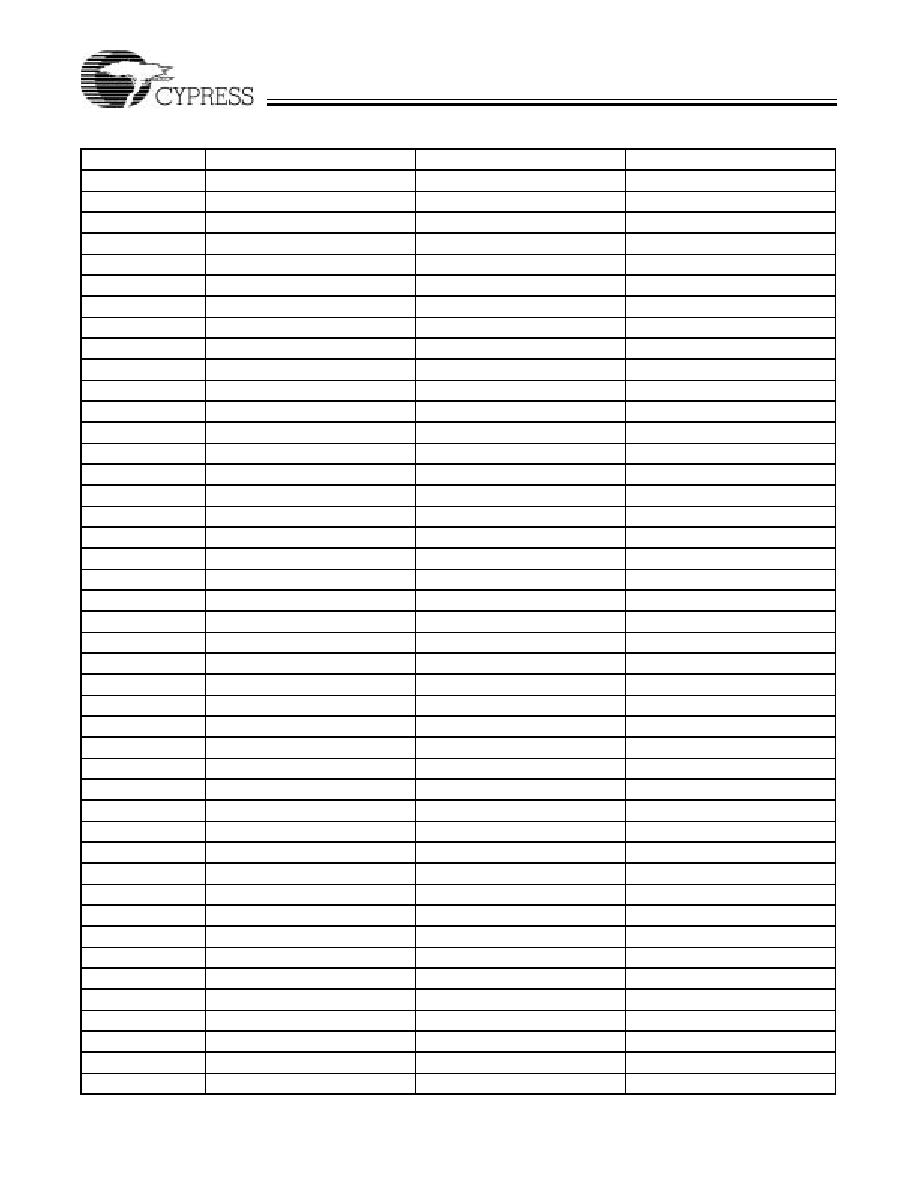

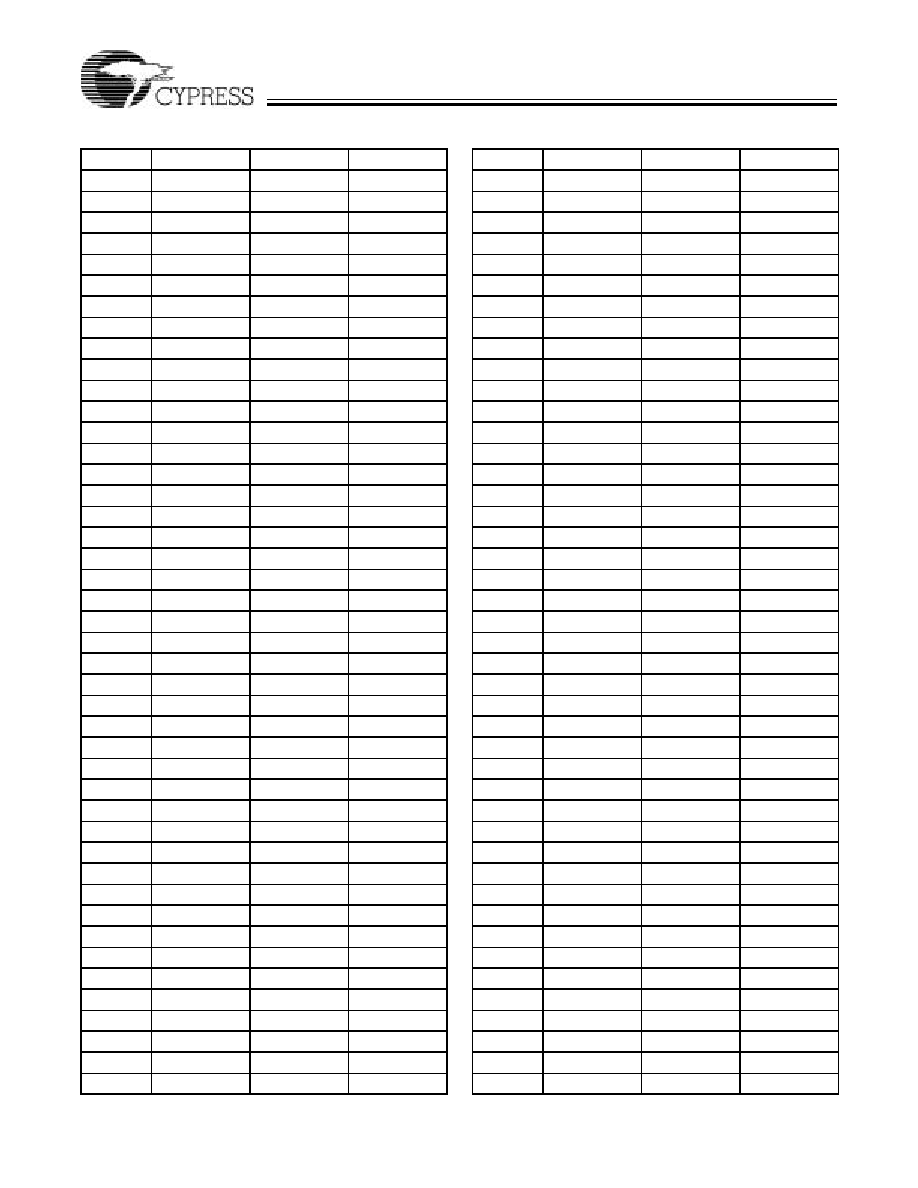

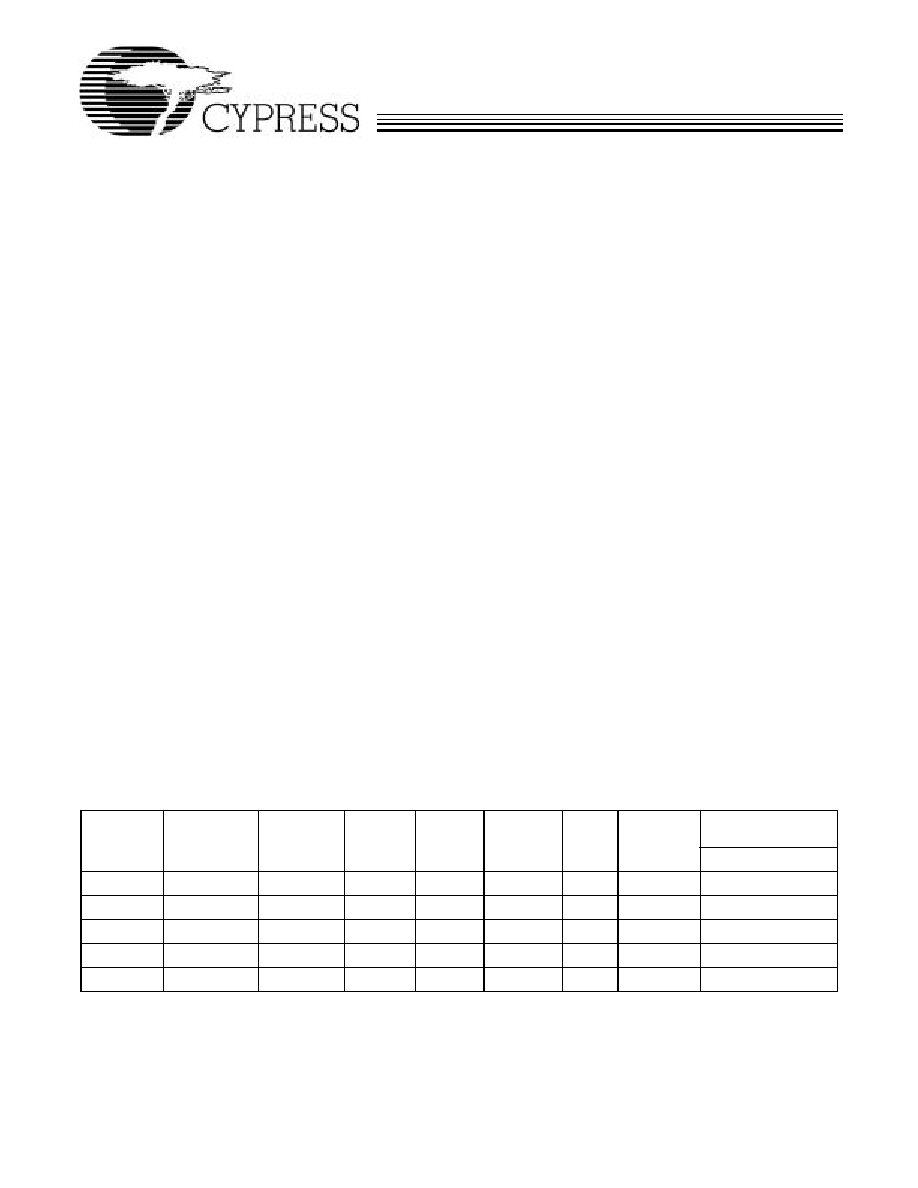

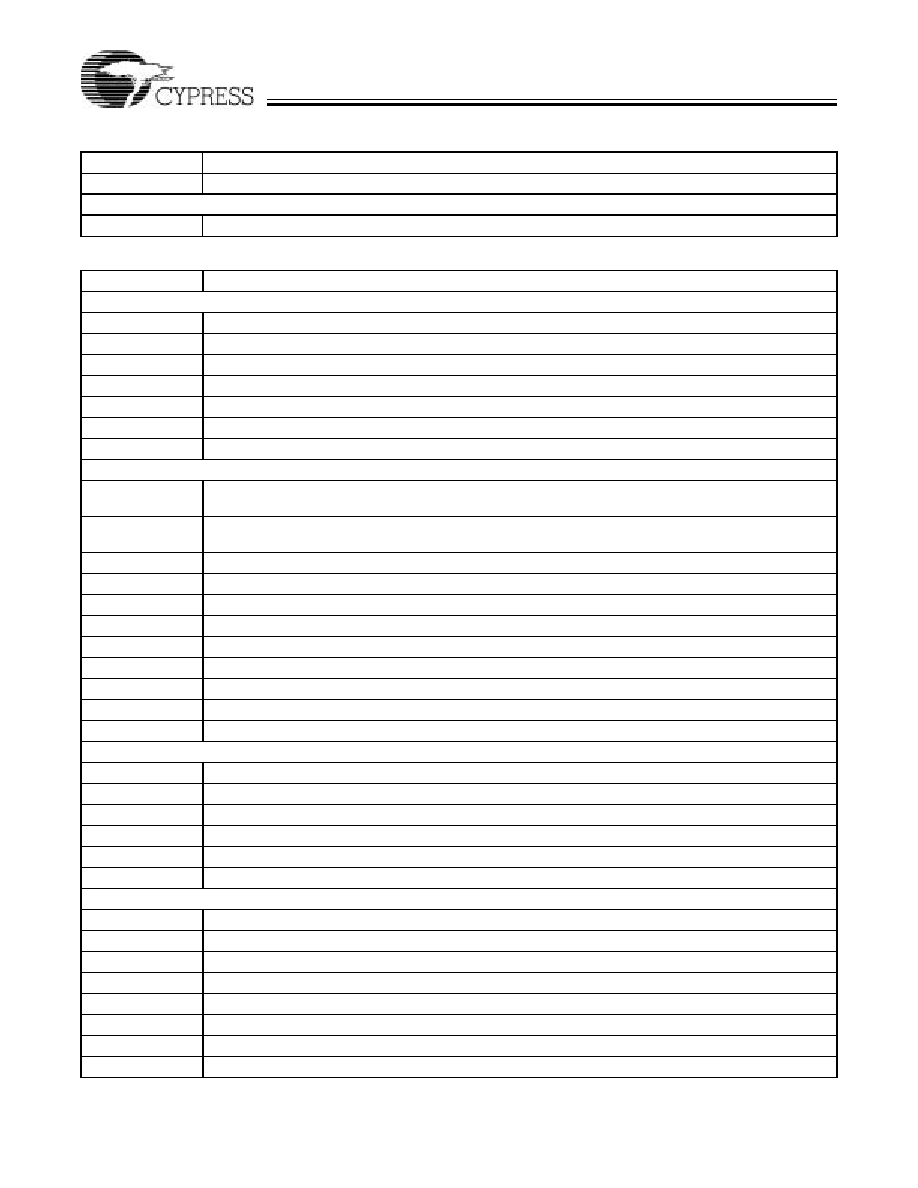

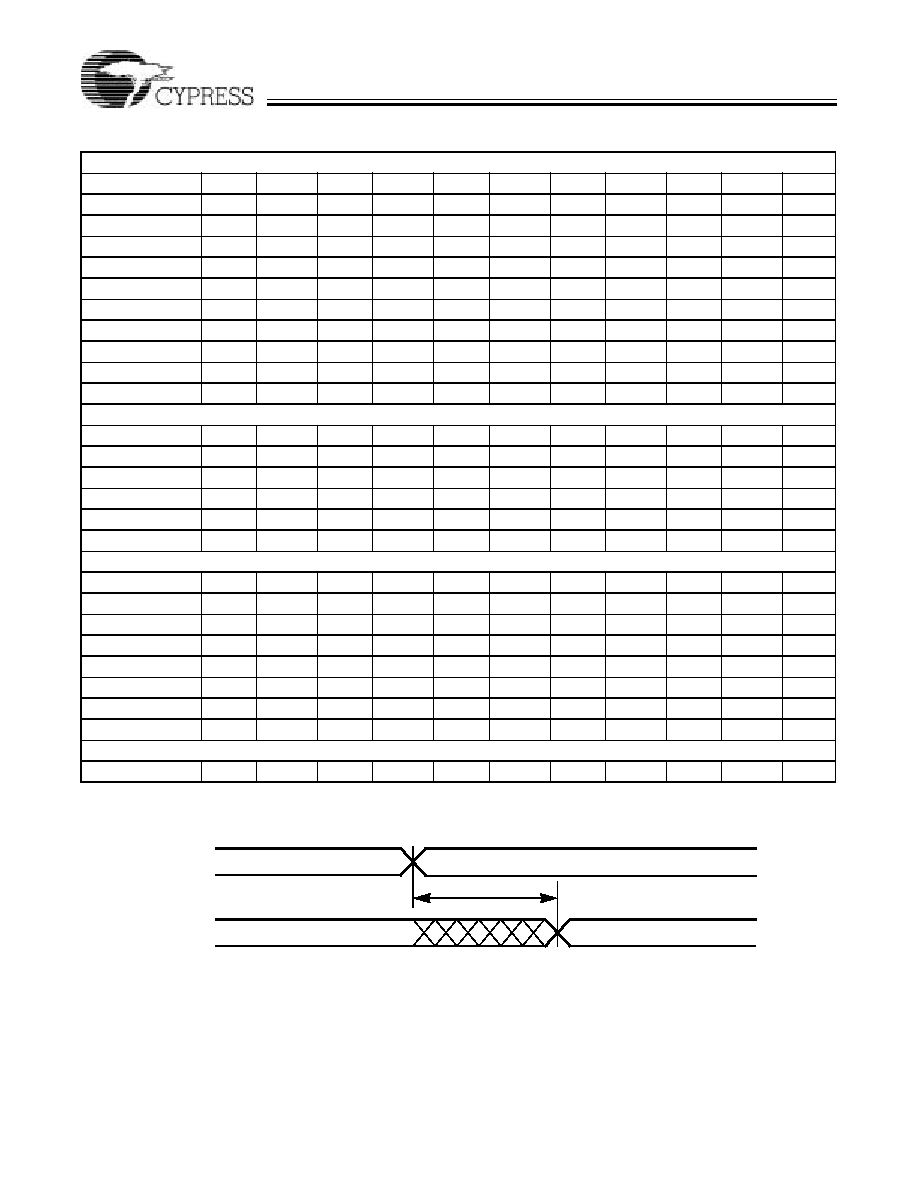

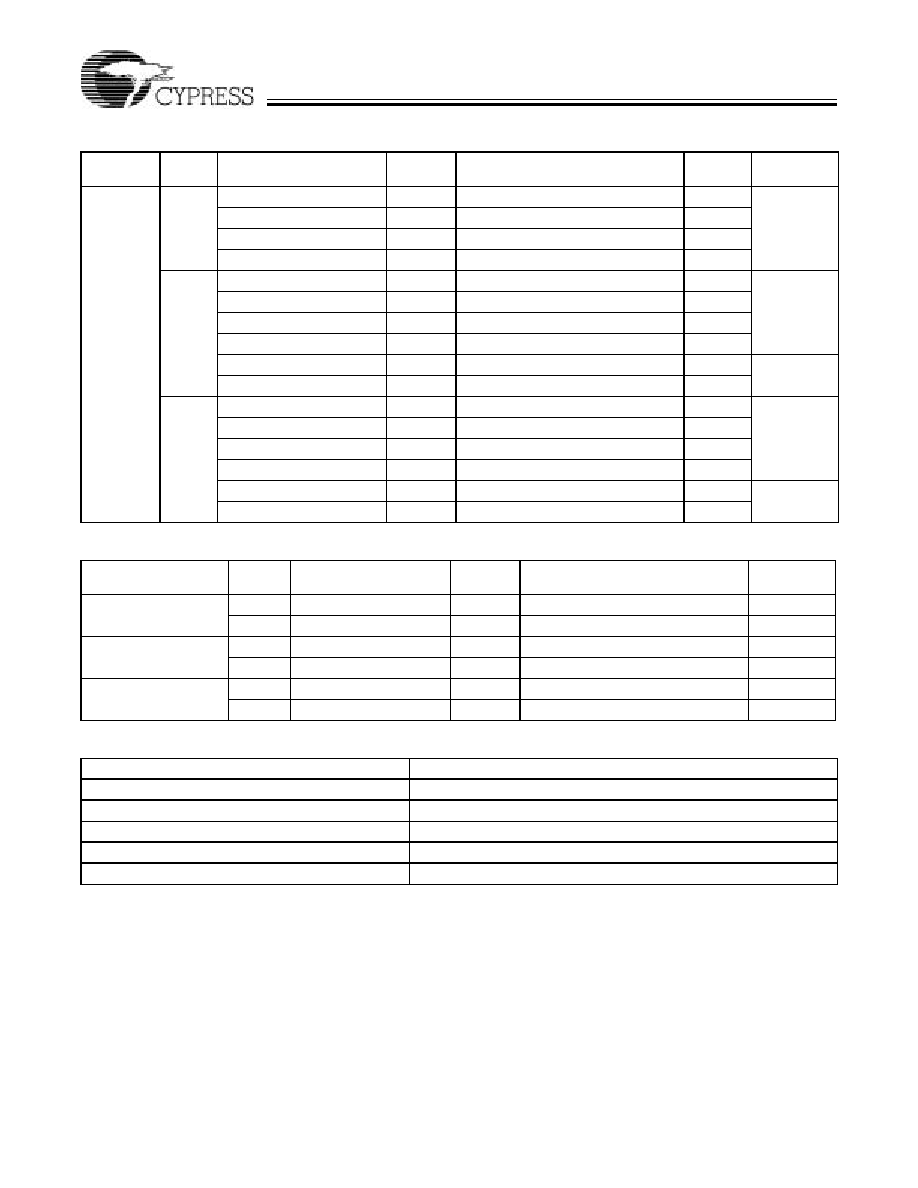

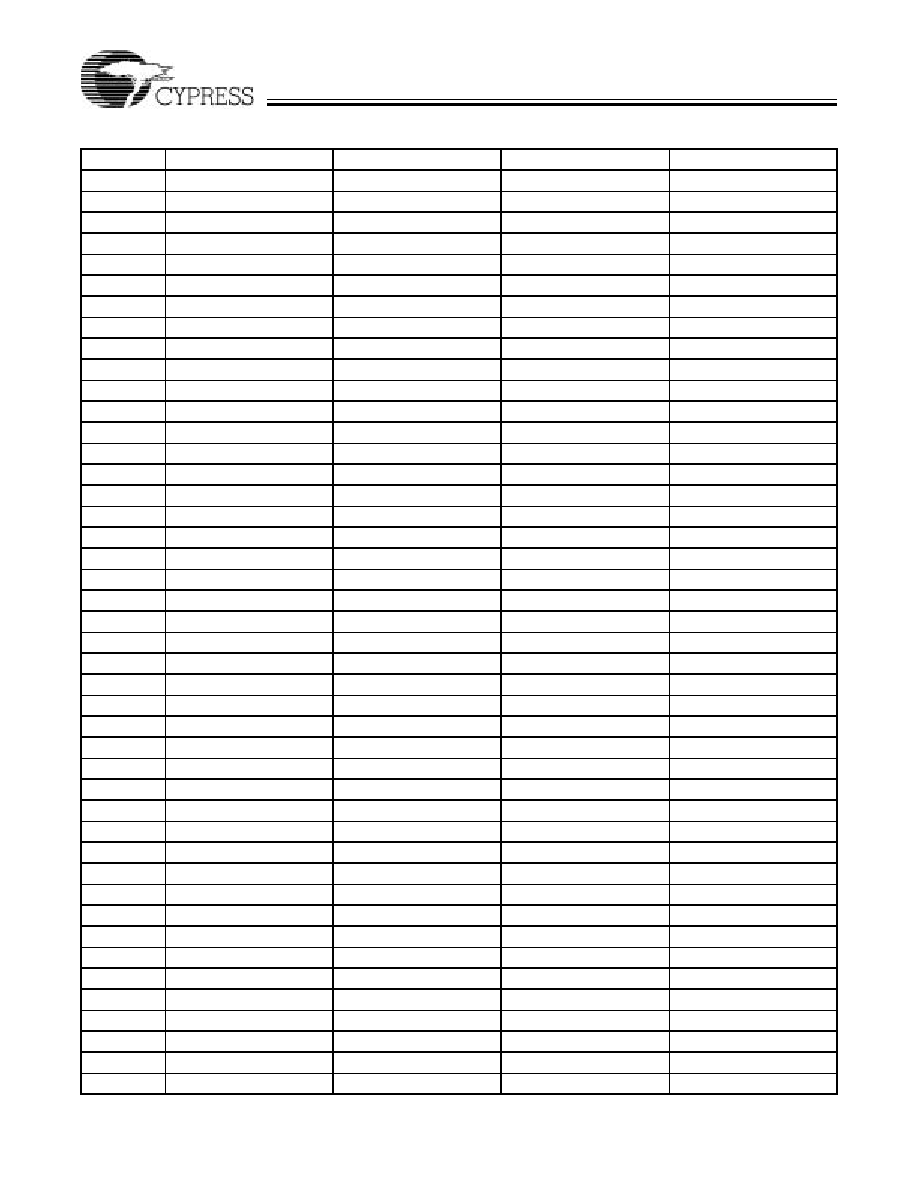

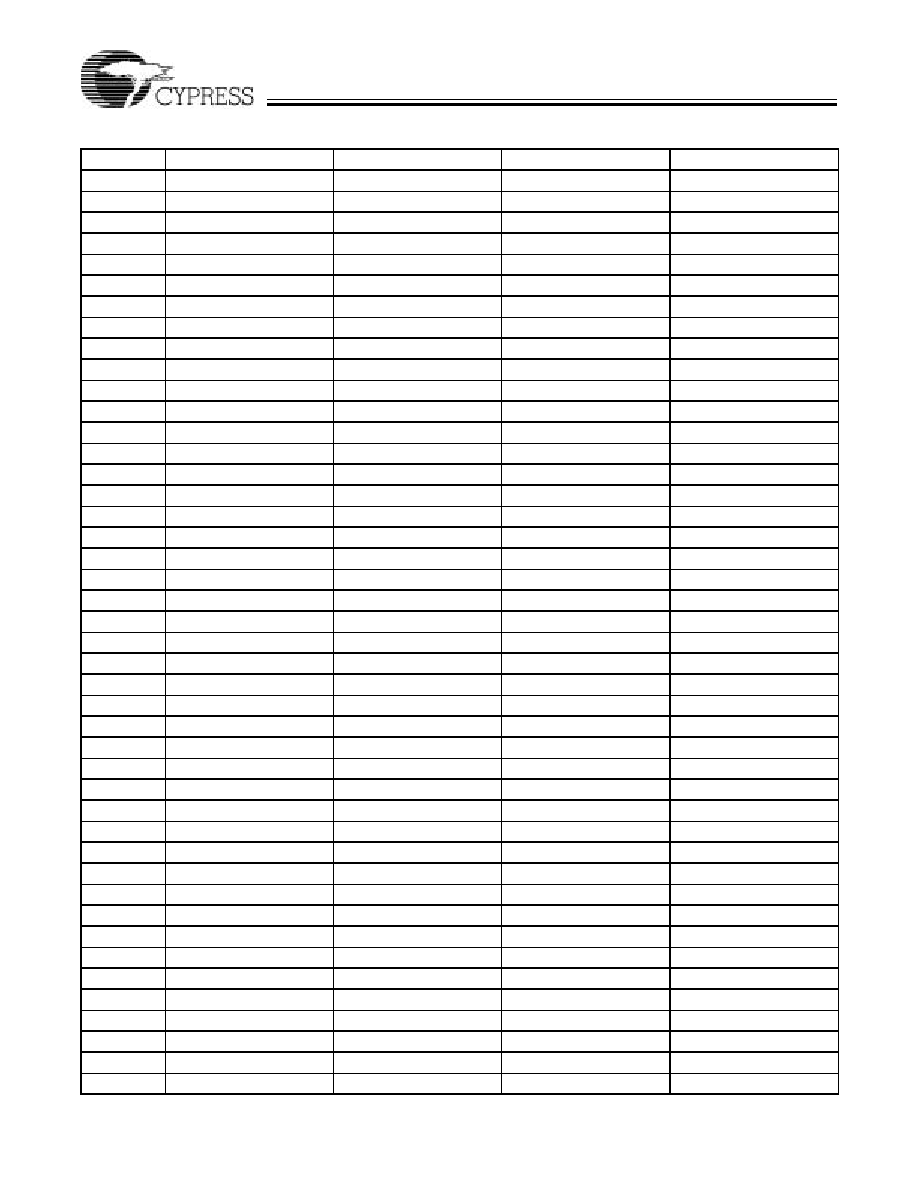

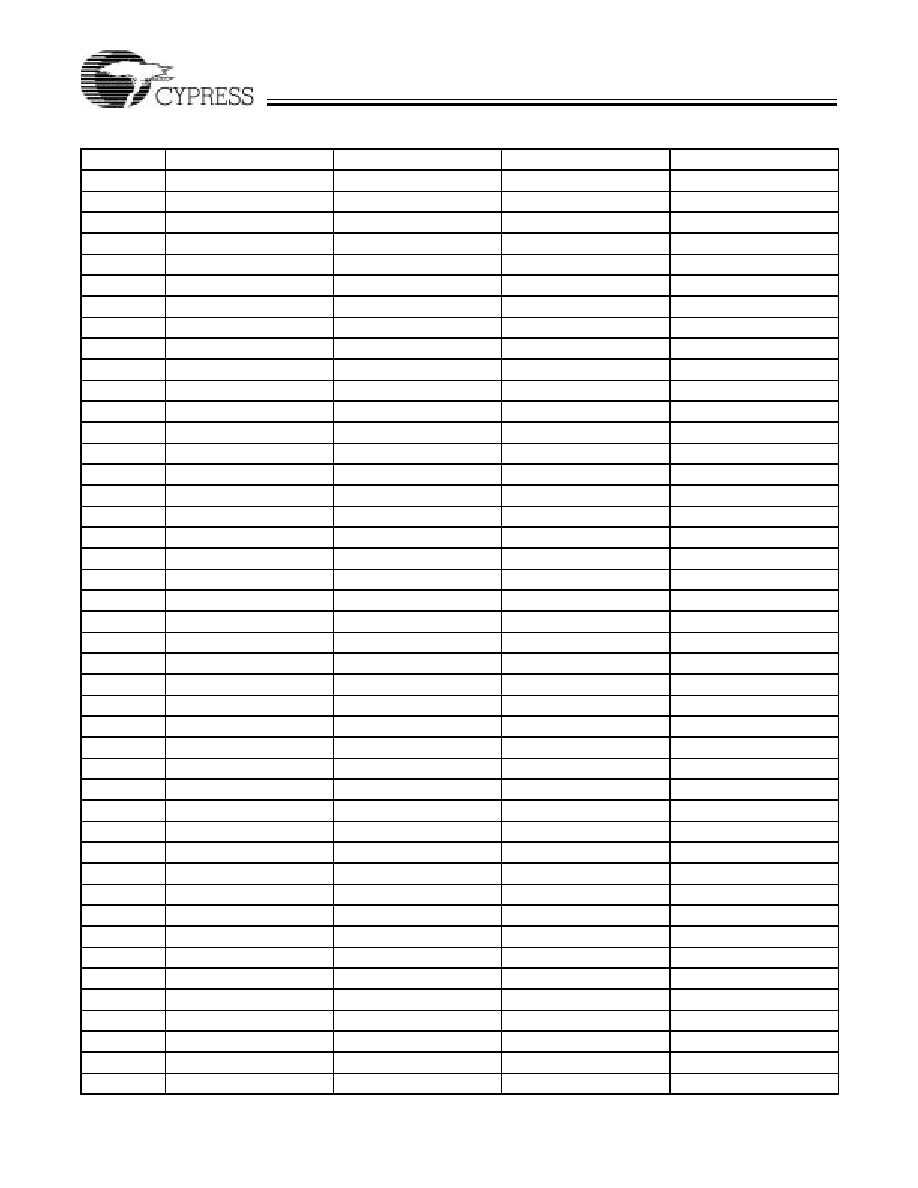

Table 4. Valid PLL Multiply and Divide Options--without External Feedback

Input Frequency

(GCLK[0])

f

PLLI

(MHz)

Valid Multiply Options

Valid Divide Options

Value

VCO Output

Frequency (MHz)

Value

Output Frequency (INTCLK[3:0])

f

PLLO

(MHz)

Off-chip Clock

Frequency

DC≠12.5

N/A

N/A

N/A

DC≠12.5

DC≠6.25

100≠133

1

100≠133

1≠6, 8, 16

6.25≠133

3.125≠66

50≠133

2

100≠266

1≠6, 8, 16

6.25≠266

3.125≠133

33.3≠88.7

3

100≠266

1≠6, 8, 16

6.25≠266

3.1≠266

25≠66

4

100≠266

1≠6, 8, 16

6.25≠266

3.125≠133

20≠53.2

5

100≠266

1≠6, 8, 16

6.25≠266

3.1≠133

16.6≠44.3

6

100≠266

1≠6, 8, 16

6.25≠266

3.1≠133

12.5≠33

8

100≠266

1≠6, 8, 16

6.25≠266

3.125≠133

12.5≠16.625

16

200≠266

1≠6, 8, 16

6.25≠266

3.125≠133

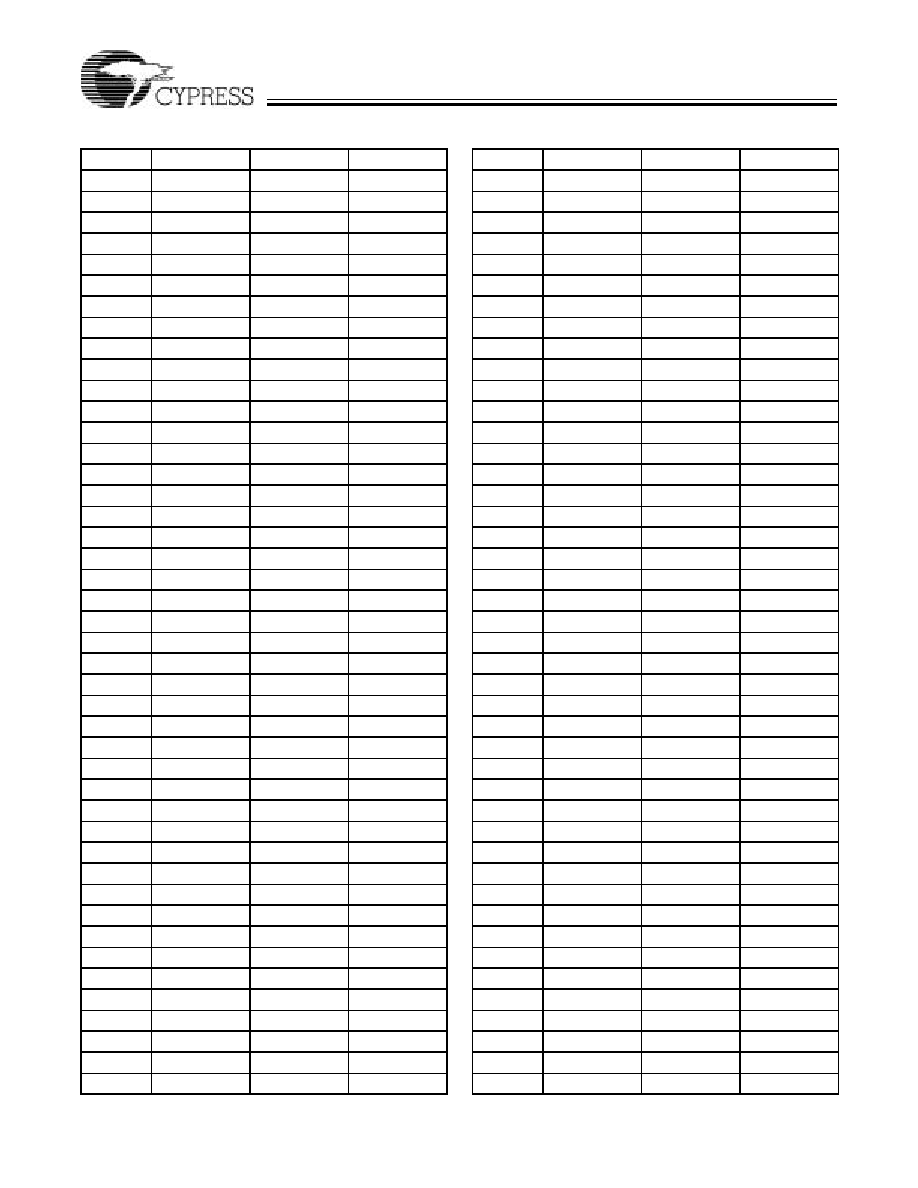

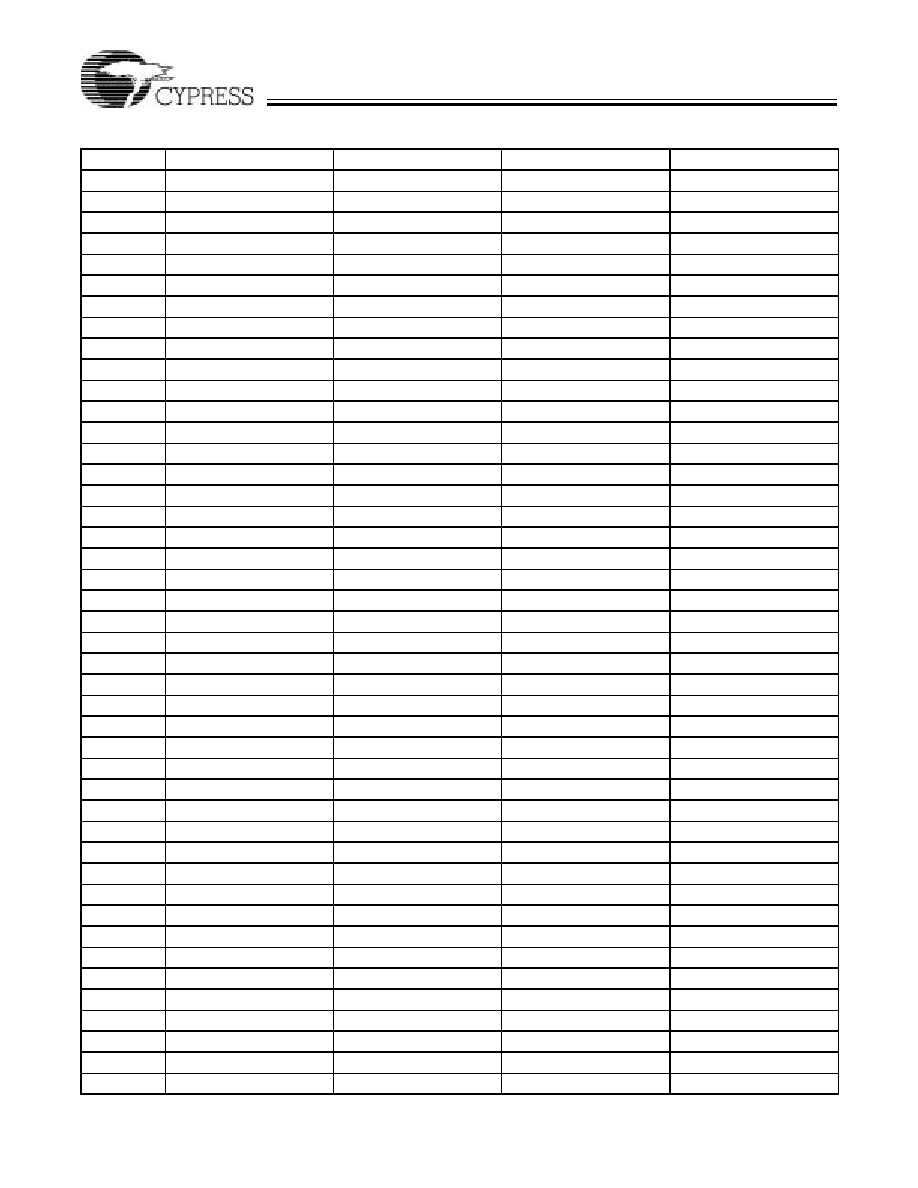

Table 5. Valid PLL Multiply and Divide Options--With External Feedback

Input (GCLK) Frequency

f

PLLI

(MHz)

Valid Multiply Options

Valid Divide Options

Value

VCO Output

Frequency (MHz)

Value

Output (INTCLK) Frequency

f

PLLO

(MHz)

Off-chip Clock

Frequency

50≠133

1

100≠266

1

100≠266

50≠133

25≠66.5

1

100≠266

2

50≠133

25≠66.5

16.67≠44.33

1

100≠266

3

33.33≠88.66

16.67≠44.33

12.5≠33.25

1

100≠266

4

25≠66.5

12.5≠33.25

12.5≠26.6

1

125≠266

5

25≠53.2

12.5≠26.6

12.5≠22.17

1

150≠266

6

25≠44.34

12.5≠22.17

12.5≠16.63

1

200≠266

8

25≠33.25

12.5≠16.63

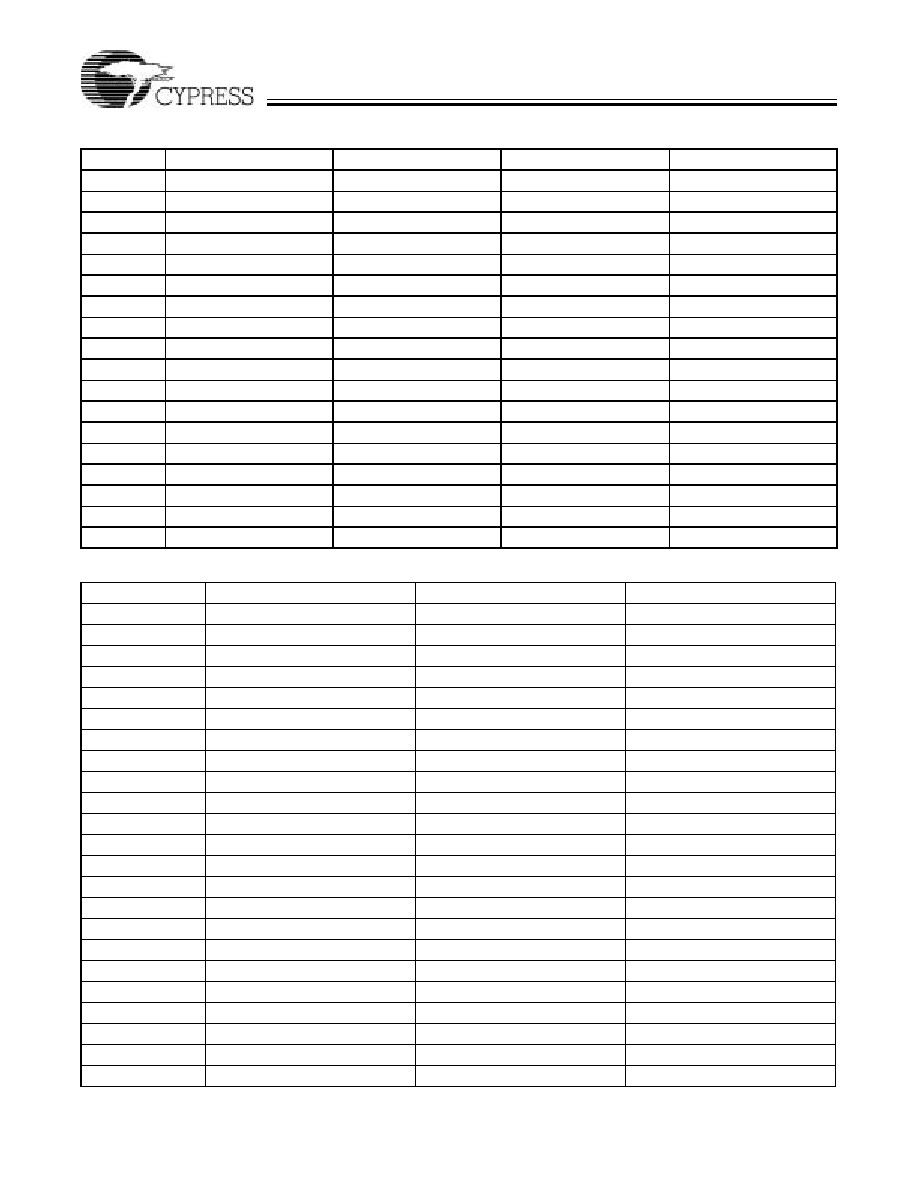

Table 6. Recommended PLL Phase Shift Options

Without External Feedback

With External Feedback

0∞,45∞, 90∞, 135∞, 180∞, 225∞, 270∞, 315∞

0∞

Table 7. Timing of Clock Phases for all Divide Options for a V

CO

Output Frequency of 250 MHz

Divide

Factor

Period

(ns)

Duty Cycle%

0∞

(ns)

45∞

(ns)

90∞

(ns)

135∞

(ns)

180∞

(ns)

225∞

(ns)

270∞

(ns)

315∞

(ns)

1

4

40≠60

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

2

8

50

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

3

12

33≠67

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4

16

50

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

5

20

40≠60

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

6

24

50

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

8

32

50

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

16

64

50

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 13 of 86

CompactPCI Hot Swap

The CompactPCI Hot Swap specification allows the removal

and insertion of cards into CompactPCI sockets without

switching-off the bus. Delta39K CPLDs can be used as a

CompactPCI host or target on these cards.

This feature is useful in telecommunication and networking

applications as it allows implementation of high availability

systems, where repairs and upgrades can be done without

downtime.

Delta39K CPLDs are CompactPCI Hot Swap Ready per

CompactPCI Hot Swap specification R2.0, with the following

exception:

∑ The I/O cells do not provide bias voltage support. External

resistors can be used to achieve this, per section 3.1.3.1 of

the CompactPCI Hot Swap specification R2.0. A simple

board level solution is provided in the application note titled

"Hot-Swapping Delta39K and Quantum38K CPLDs."

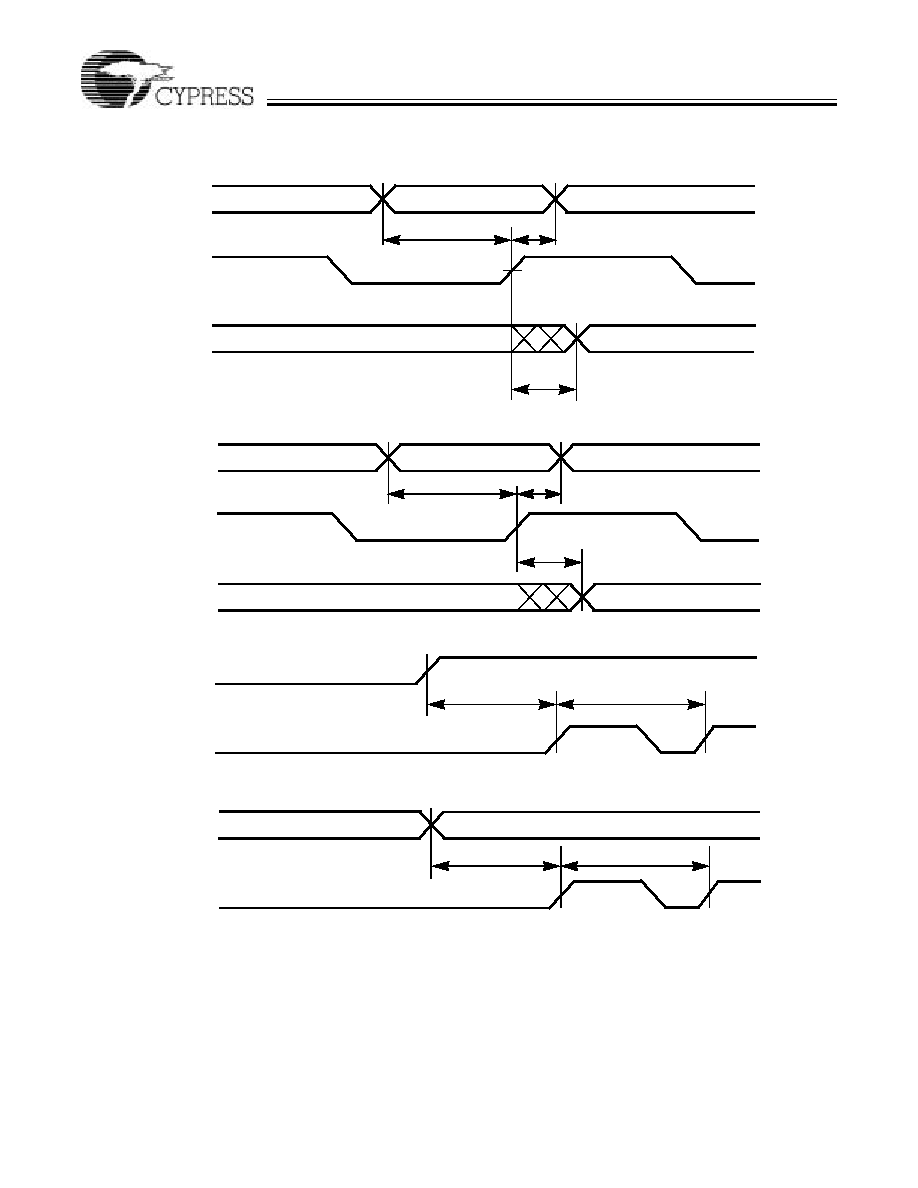

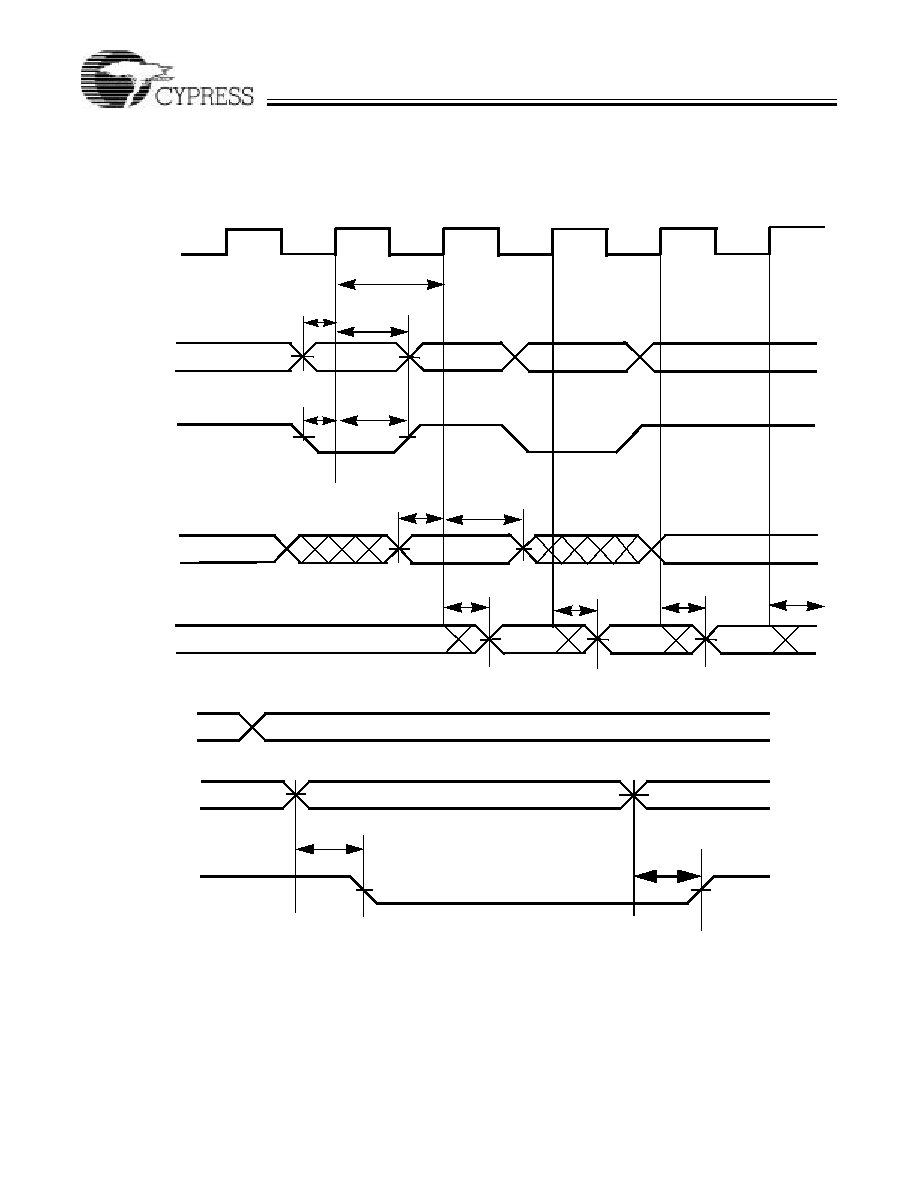

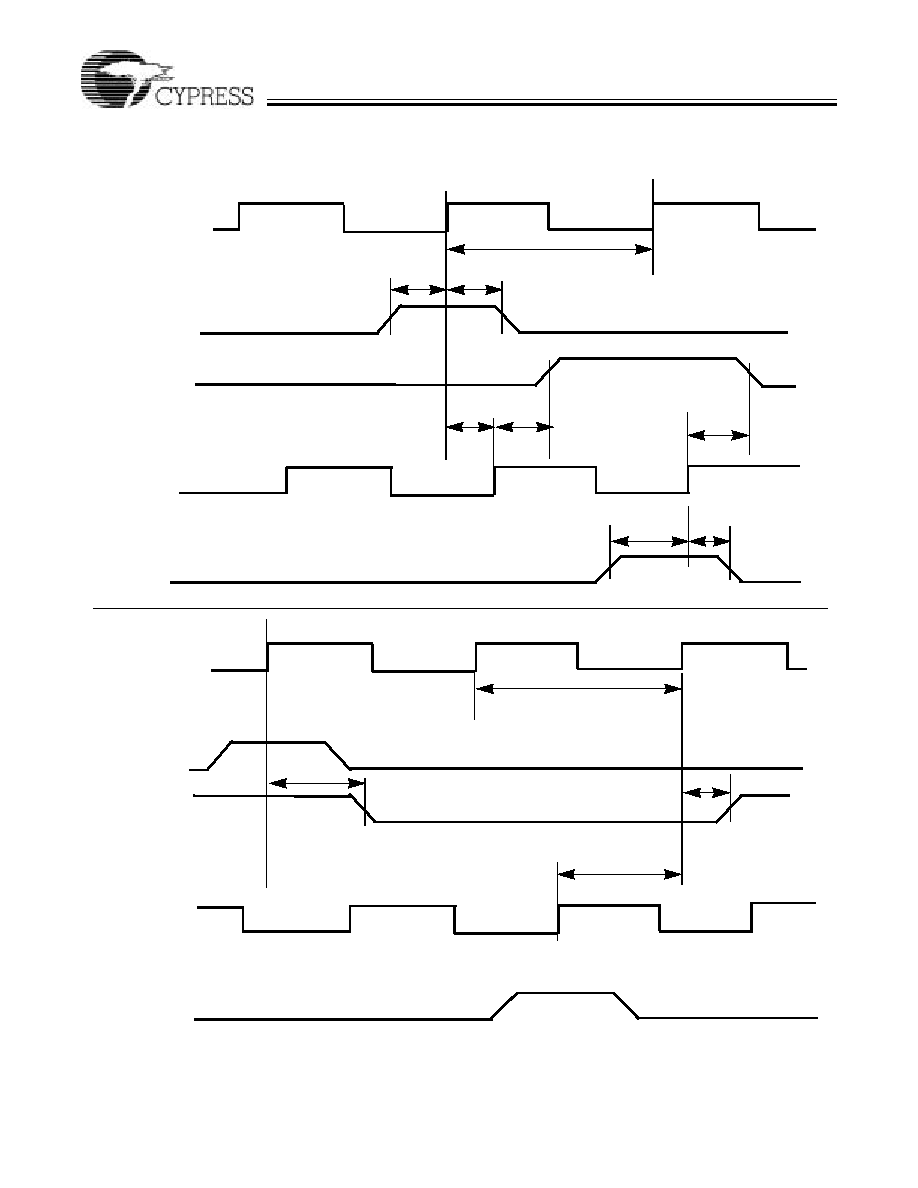

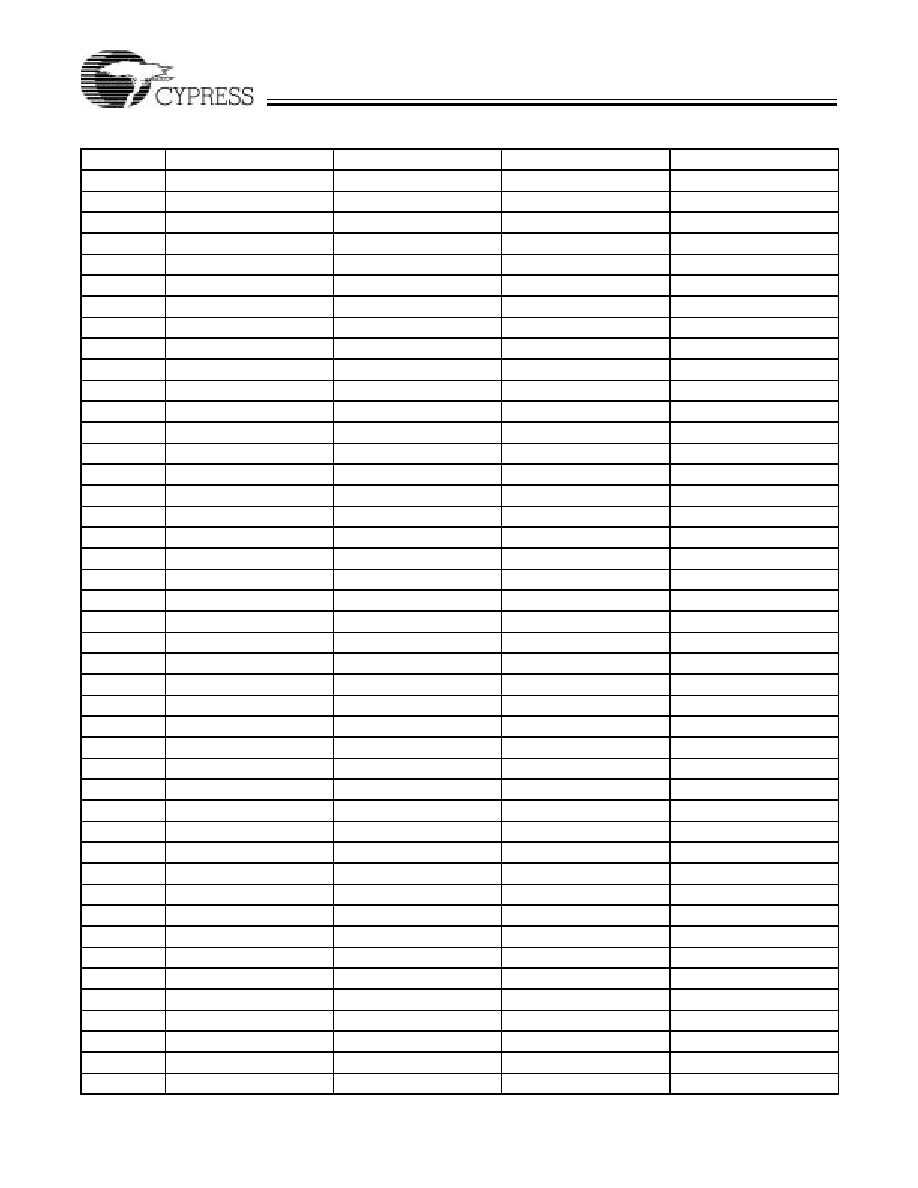

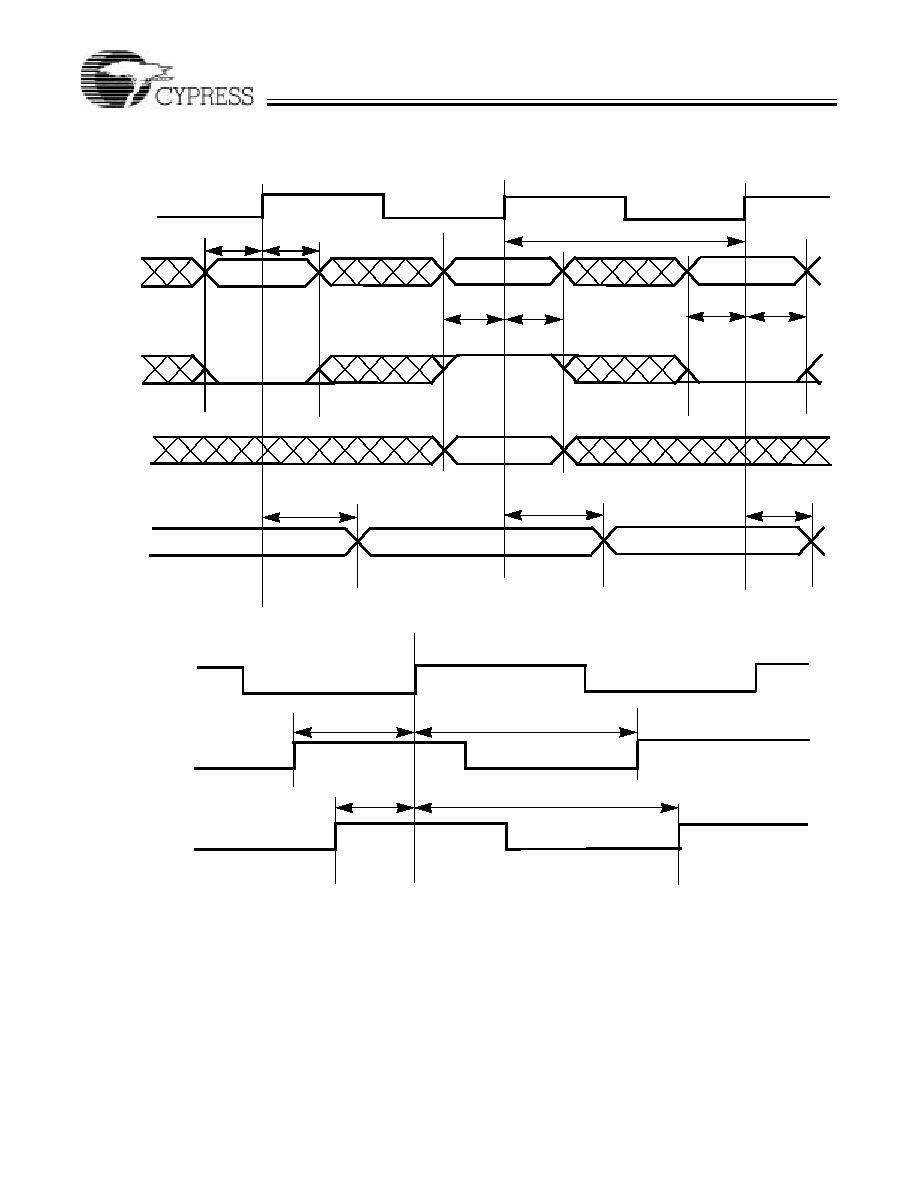

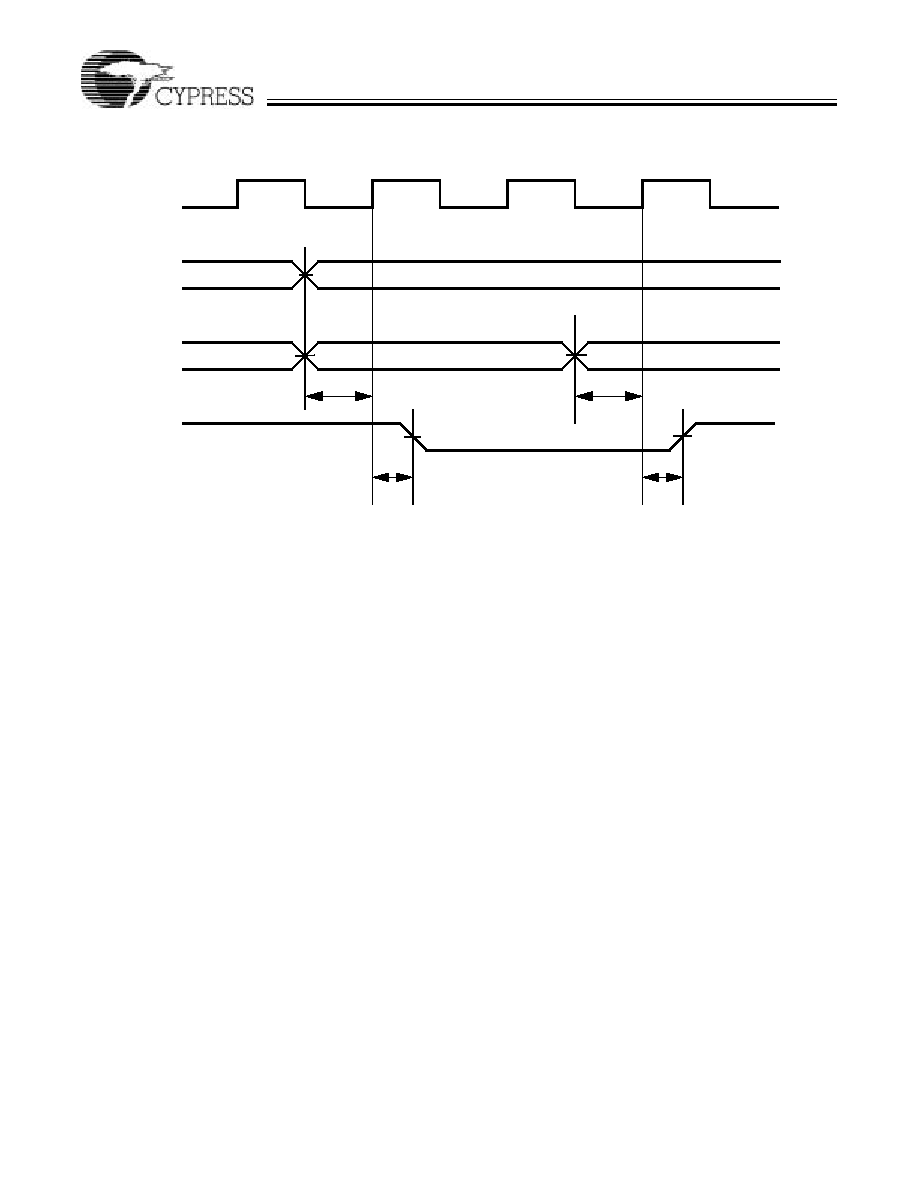

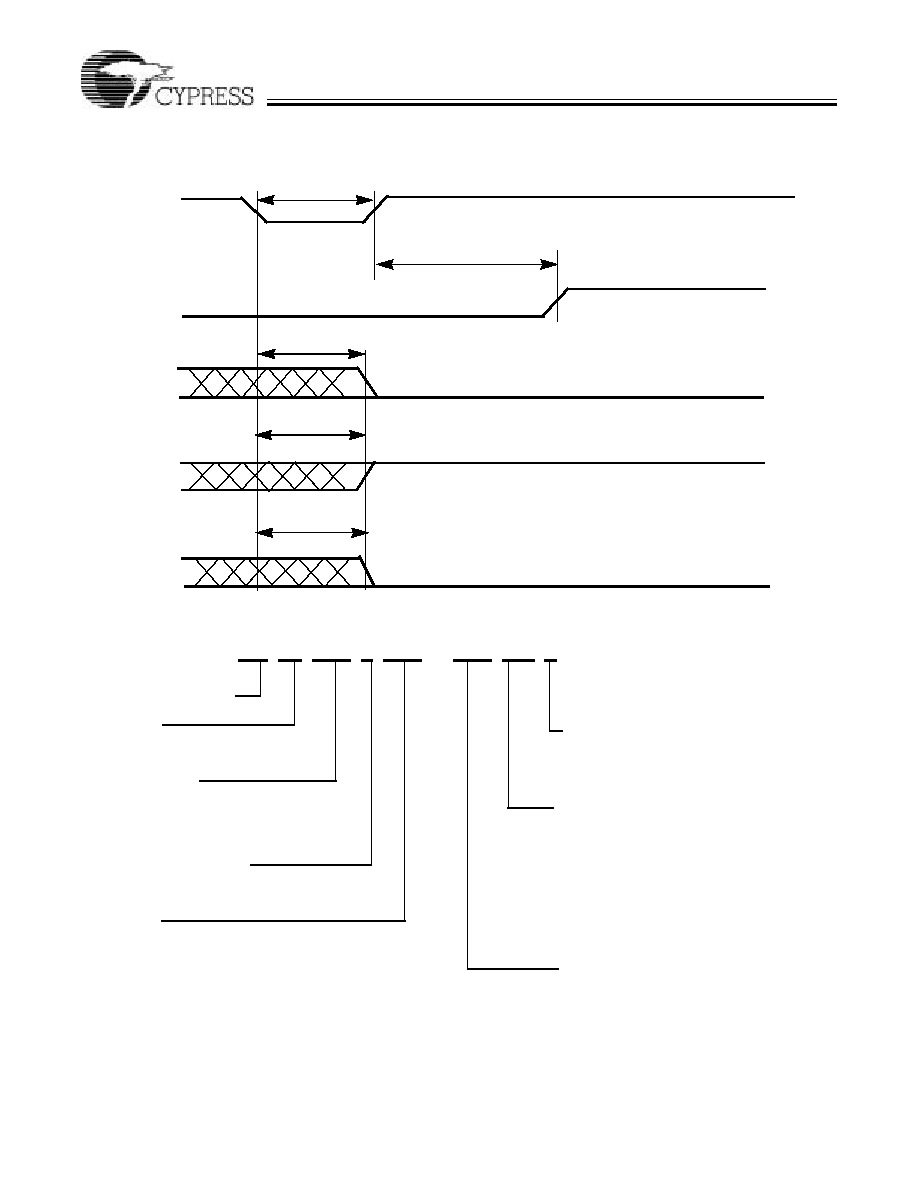

Timing Model

One important feature of the Delta39K family is the simplicity

of its timing. All combinatorial and registered/synchronous

delays are worst case and system performance is static (as

shown in the AC specs section) as long as data is routed

through the same horizontal and vertical channels. Figure 10

illustrates the true timing model for the 200-MHz devices. For

synchronous clocking of macrocells, a delay is incurred from

macrocell clock to macrocell clock of separate Logic Blocks

within the same cluster, as well as separate Logic Blocks

within different clusters. This is respectively shown as t

SCS

and

t

SCS2

in Figure 10. For combinatorial paths, any input to any

output (from corner to corner on the device), incurs a worst-

case delay in the 39K100 regardless of the amount of logic or

which horizontal and vertical channels are used. This is the t

PD

shown in Figure 10. For synchronous systems, the input set-

up time to the output macrocell register and the clock to output

time are shown as the parameters t

MCS

and t

MCCO

shown in

the Figure 10. These measurements are for any output and

synchronous clock, regardless of the logic placement.

The Delta39K features:

∑ no dedicated vs. I/O pin delays

∑ no penalty for using 0 ≠ 16 product terms

∑ no added delay for steering product terms

∑ no added delay for sharing product terms

∑ no output bypass delays.

The simple timing model of the Delta39K family eliminates

unexpected performance penalties.

Family, Package, and Density Migration in Delta39K

CPLDs

The Delta39K CPLDs combine dense logic, embedded mem-

ory and configurable I/O standards. Further design flexibility is

added by the easy migration options available between differ-

ent packages and densities of Delta39K CPLD offerings.

This migration flexibility makes changes or additions to

designs simple even after PCB layout. It also provides the

ability for experimental designs to be used on production

PCBs. Please refer to the application note titled "Family,

Package, and Density Migration in Delta39K CPLDs."

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 14 of 86

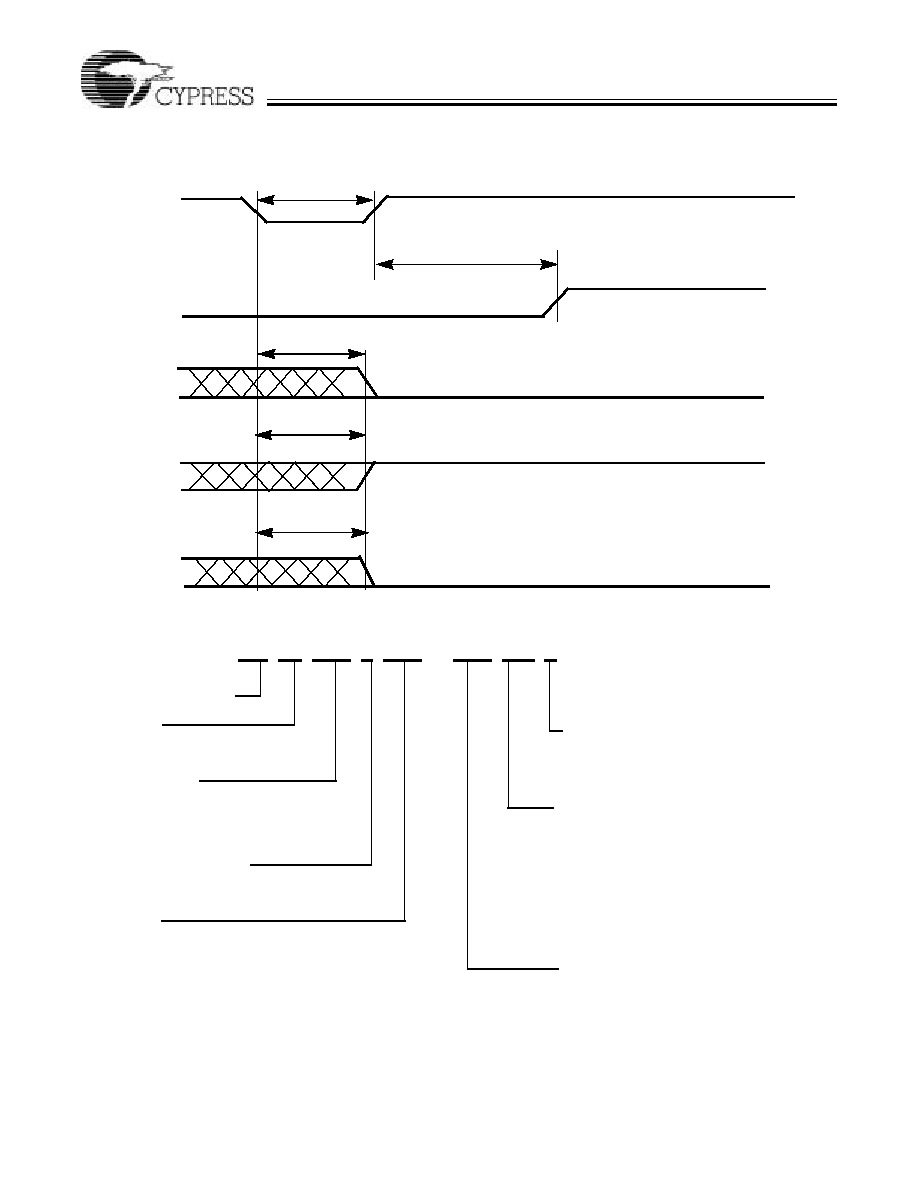

IEEE 1149.1-compliant JTAG Operation

The Delta39K family has an IEEE 1149.1 JTAG interface for

both Boundary Scan and ISR operations.

Four dedicated pins are reserved on each device for use by

the Test Access Port (TAP).

Boundary Scan

The Delta39K family supports Bypass, Sample/Preload,

Extest, Intest, Idcode and Usercode boundary scan instruc-

tions. The JTAG interface is shown in Figure 11.

In-System Reprogramming (ISR)

In-System Reprogramming is the combination of the capability

to program or reprogram a device on-board, and the ability to

support design changes without changing the system timing

or device pinout. This combination means design changes

during debug or field upgrades do not cause board respins.

The Delta39K family implements ISR by providing a JTAG

compliant interface for on-board programming, robust routing

resources for pinout flexibility, and a simple timing model for

consistent system performance.

Configuration

Each device of the Delta39K family is available in a volatile and

a Self-Boot package. Cypress's CPLD boot EEPROM is used

to store configuration data for the volatile solution and an

embedded on-chip FLASH memory device is used for the Self-

Boot solution.

For volatile Delta39K packages, programming is defined as

the loading of a user's design into the external CPLD boot

EEPROM. For Self-Boot Delta39K packages, programming is

defined as the loading of a user's design into the on-chip

FLASH internal to the Delta39K package. Configuration is

defined as the loading of a user's design into the Delta39K die.

Channel

RAM

4

GCLK[3:0]

LB 0

PIM

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

8 Kb

SRAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

8 Kb

SRAM

Channel

RAM

4

GCLK[3:0]

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

4

LB 0

PIM

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

GCLK[3:0]

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

4

LB 0

PIM

Cluster

RAM

LB 5

LB 4

LB 6

LB 7

LB 2

LB 3

LB 1

Cluster

RAM

Channel

RAM

Channel

RAM

Cluster

Cluster

Cluster

t

MCS

t

PD

t

SCS

t

MCCO

t

SCS2

Figure 10. Timing Model for 39K100 Device

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 15 of 86

Configuration can begin in two ways. It can be initiated by

toggling the Reconfig pin from LOW to HIGH, or by issuing the

appropriate IEEE STD 1149.1 JTAG instruction to the

Delta39K device via the JTAG interface. There are two IEEE

STD 1149.1 JTAG instructions that initiate configuration of the

Delta39K. The Self Config instruction causes the Delta39K to

(re)configure with data stored in the serial boot PROM or the

embedded FLASH memory. The Load Config instruction

causes the Delta39K to (re)configure according to data

provided by other sources such as a PC, automatic test

equipment (ATE), or an embedded micro-controller/processor

via the JTAG interface. For more information on configuring

Delta39K devices, refer to the application note titled "Config-

uring Delta39K/Quantum38K" at http://www.cypress.com.

There are two configuration options available for issuing the

IEEE STD 1149.1 JTAG instructions to the Delta39K. The first

method is to use a PC with the C3ISR programming cable and

software. With this method, the ISR pins of the Delta39K

devices in the system are routed to a connector at the edge of

the printed circuit board. The C3ISR programming cable is

then connected between the PC and this connector. A simple

configuration file instructs the ISR software of the

programming operations to be performed on the Delta39K

devices in the system. The ISR software then automatically

completes all of the necessary data manipulations required to

accomplish configuration, reading, verifying, and other ISR

functions. For more information on the Cypress ISR interface,

see the ISR Programming Kit data sheet (CY3900i).

The second configuration option for the Delta39K is to utilize

the embedded controller or processor that already exists in the

system. The Delta39K ISR software assists in this method by

converting the device HEX file into the ISR serial stream that

contains the ISR instruction information and the addresses

and data of locations to be configured. The embedded

controller then simply directs this ISR stream to the chain of

Delta39K devices to complete the desired reconfiguration or

diagnostic operations. Contact your local sales office for infor-

mation on the availability of this option.

Programming

The on-chip FLASH device of the Delta39K Self-Boot package

is programmed by issuing the appropriate IEEE STD 1149.1

JTAG instruction to the internal FLASH memory via the JTAG

interface. This can be done automatically using ISR/STAPL

software. The configuration bits are sent from a PC through

the JTAG port into the Delta39K via the C3ISR programming

cable. The data is then internally passed from Delta39K to the

on-chip FLASH. For more information on how to program the

Delta39K through ISR/STAPL, please refer to the ISR/STAPL

User Guide.

The external CPLD boot EEPROM used to store configuration

data for the Delta39K volatile package is programmed through

Cypress's CYDH2200E CPLD Boot PROM Programming Kit

via a two-wire interface. For more information on how to

program the CPLD boot EEPROM, please refer to the data

sheet titled "CYDH2200E CPLD Boot PROM Programming

Kit." For more information on the architecture and timing speci-

fication of the boot EEPROM, refer to the data sheet titled

"512K/1Mb CPLD Boot EEPROM" or "2-Mbit CPLD Boot

EEPROM."

Third-Party Programmers

Cypress support is available on a wide variety of third-party

programmers. All major programmers (including BP Micro,

System General, Hi-Lo) support the Delta39K family.

Development Software Support

Warp

Warp is a state-of-the-art design environment for designing

with Cypress programmable logic. Warp utilizes a subset of

IEEE 1076/1164 VHDL and IEEE 1364 as the Hardware

Description Language (HDL) for design entry. Warp accepts

VHDL or Verilog input, synthesizes and optimizes the entered

design, and outputs a configuration bitstream for the desired

Delta39K device. For simulation, Warp provides a graphical

waveform simulator as well as VHDL and Verilog Timing

Models.

VHDL and Verilog are open, powerful, non-proprietary

Hardware Description Languages (HDLs) that are standards

for behavioral design entry and simulation. HDL allows

designers to learn a single language that is useful for all facets

of the design process.

Third-Party Software

Cypress products are supported in a number of third-party

design entry and simulation tools. Refer to the third-party

software data sheet or contact your local sales office for a list

of currently supported third party vendors.

Instruction Register

Boundary Scan

idcode

Usercode

ISR Prog.

Bypass Reg.

Data Registers

JTAG

TAP

CONTROLLER

TDO

TDI

TMS

TCLK

Figure 11. JTAG Interface

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 16 of 86

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature

(39K200, 208 EQFP) ................................. ≠45

∞

C to +125

∞

C

Storage Temperature

(all other densities and packages) .............. ≠65

∞

C to +150

∞

C

Soldering Temperature................................................. 220

∞

C

Ambient Temperature with

Power Applied............................................... ≠40

∞

C to +85

∞

C

Junction Temperature ...................................................135∞C

V

CC

to Ground Potential ................................... ≠0.5V to 4.6V

V

CCIO

to Ground Potential ................................ ≠0.5V to 4.6V

DC Voltage Applied to Outputs

in High-Z state .................................................. ≠0.5V to 4.5V

DC Input voltage...............................................≠0.5V to 4.5V

DC Current into Outputs ........................................ ± 20 mA

[6]

Static Discharge Voltage

(per JEDEC EIA./JESD22≠A114A)............................ >2001V

Latch-up Current ..................................................... >200 mA

Note:

6.

DC current into outputs is 36 mA with HSTL III, 48 mA with HSTL IV, and 36 mA with GTL+ (with 25W pull-up resistor and V

TT

= 1.5).

7.

Input Leakage current is ±10

µ

A for all the pins on all the Delta39K package except the following pins in Delta39K100 packages: The input leakage current spec

for these pins in ±200

µ

A

8.

Not more than one output should be tested at a time. Duration of the short circuit should not exceed 1 second. V

OUT

= 0.5V has been chosen to avoid test

problems caused by tester-ground degradation. Tested initially and after any design or process changes that may affect these parameters.

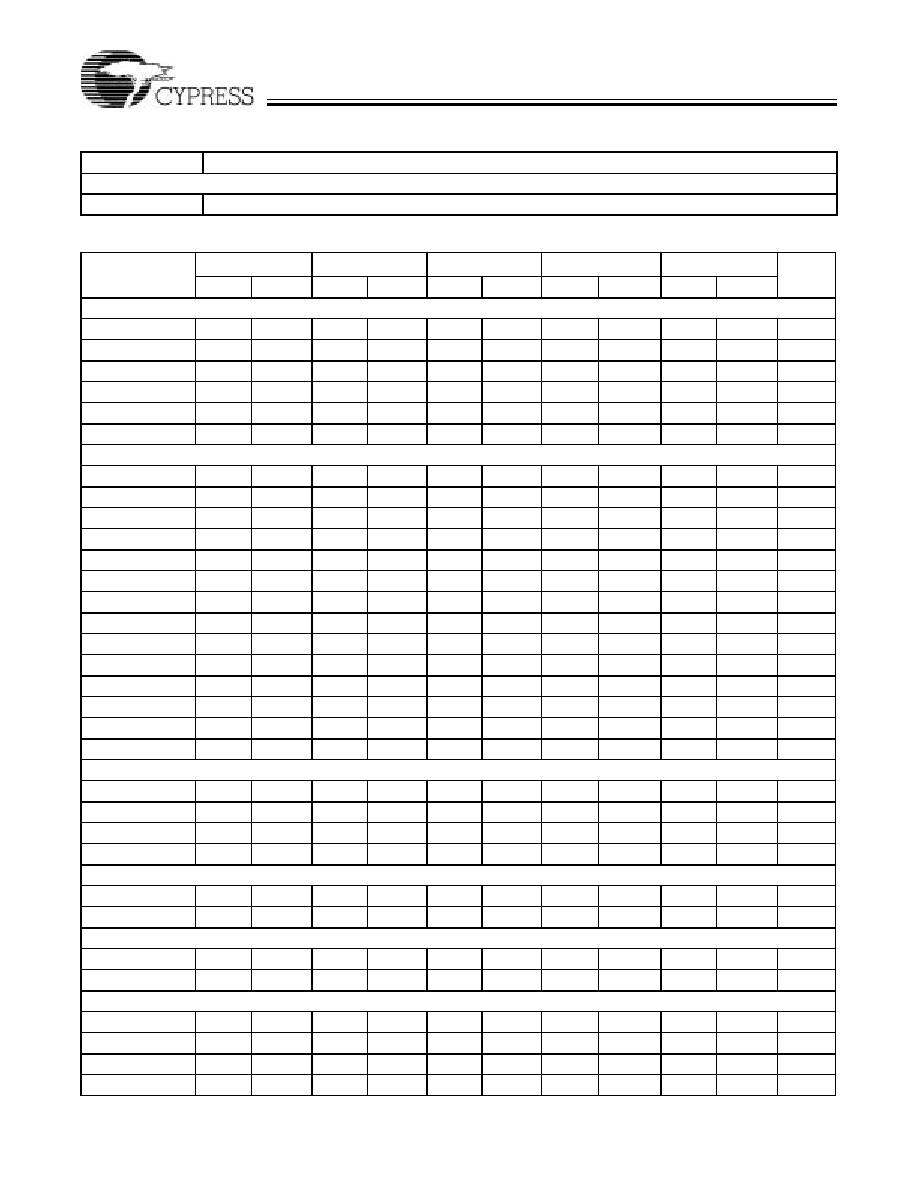

Operating Range

Range

Ambient

Temperature

Junction

Temperature

Output

Condition

V

CCIO

V

CC

V

CCJTAG

/

V

CCCNFG

V

CCPLL

V

CCPRG

Commercial

0

∞

C to +70

∞

C

0

∞

C to +85

∞

C

3.3V

3.3V ± 0.3V

3.3V ± 0.3V or

2.5V ± 0.2V

(39KV)

Same as

V

CCIO

Same as

V

CC

3.3V ±

0.3V

2.5V

2.5V ± 0.2V

1.8V

1.8V ± 0.15V

1.5V

1.5V ± 0.1V

[5]

Industrial

≠40

∞

C to +85∞C

≠40

∞

C to +100∞C

3.3V

3.3V ± 0.3V

2.5V

2.5V ± 0.2V

1.8V

1.8V ± 0.15V

1.5V

1.5V ± 0.1V

[5]

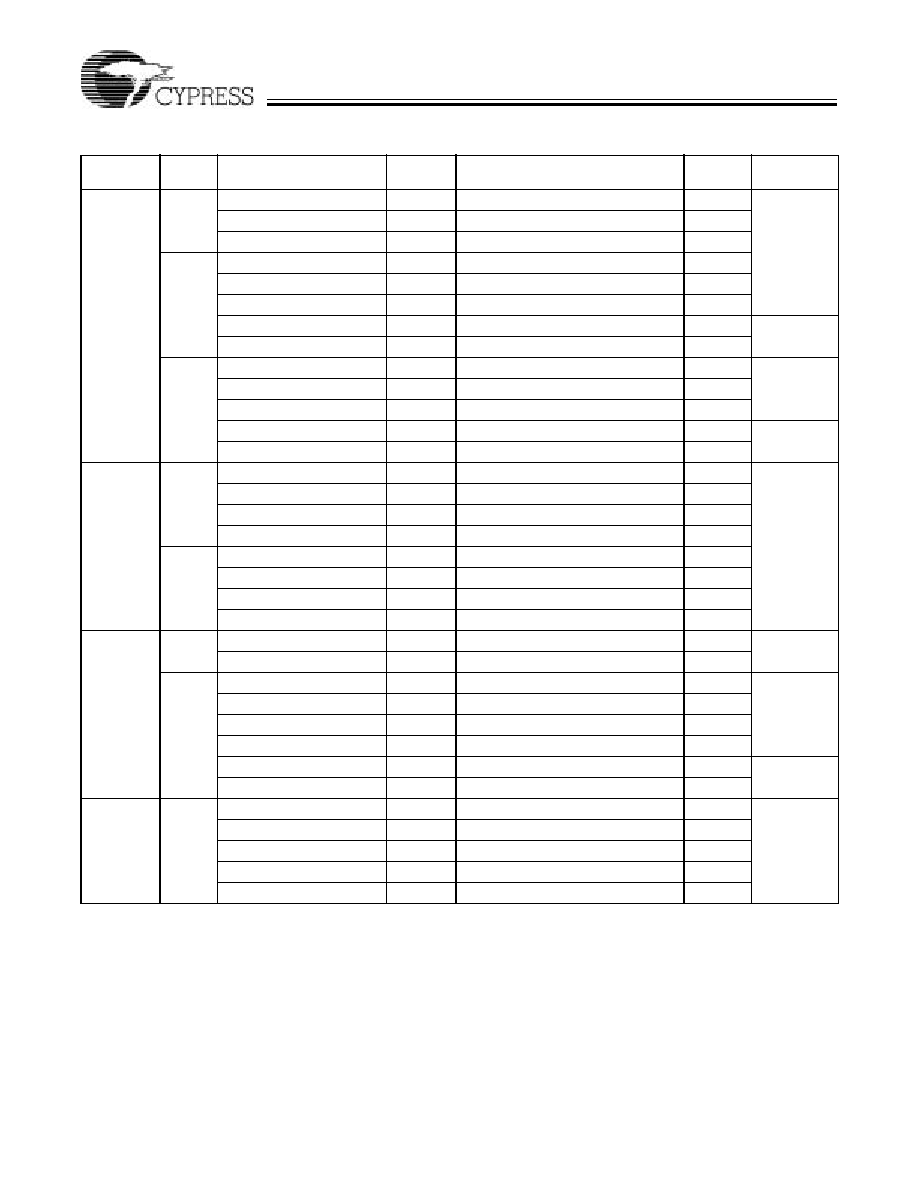

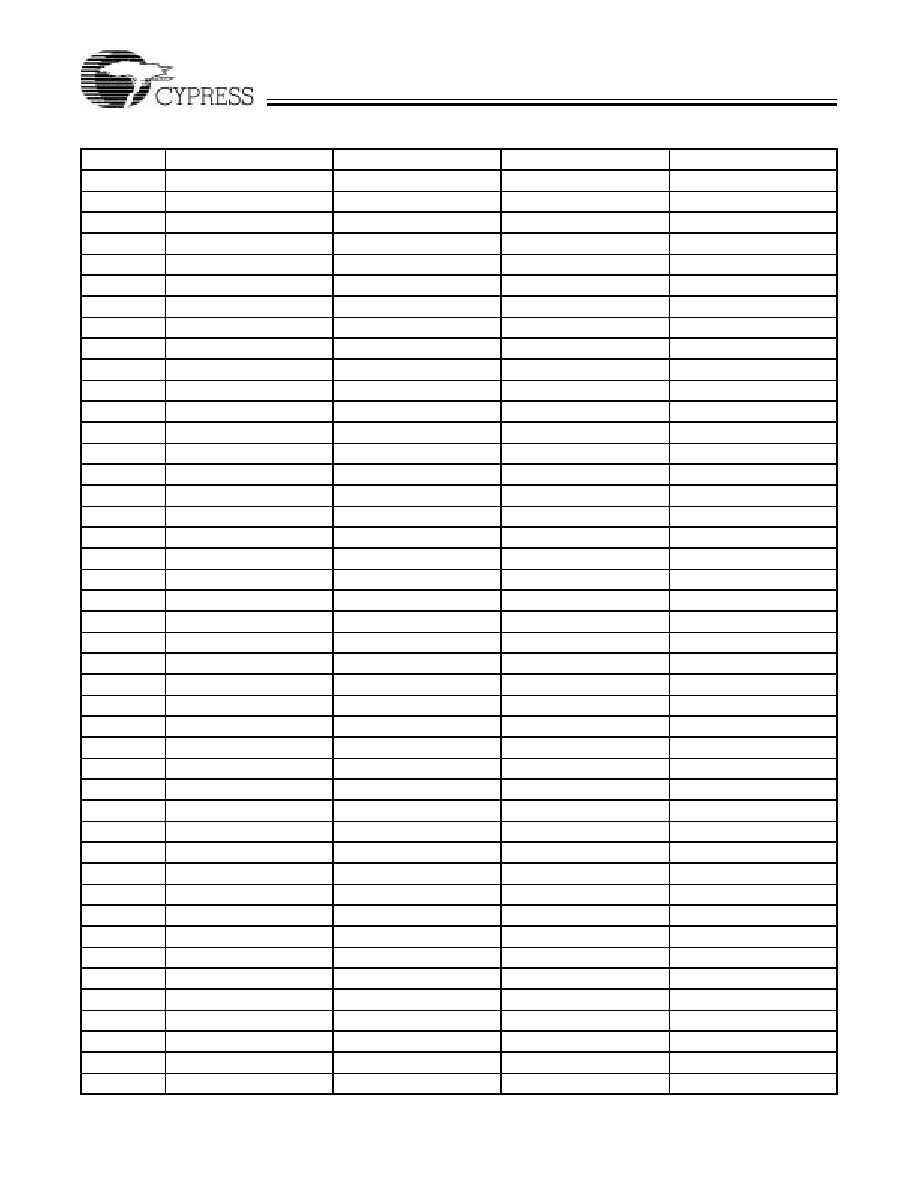

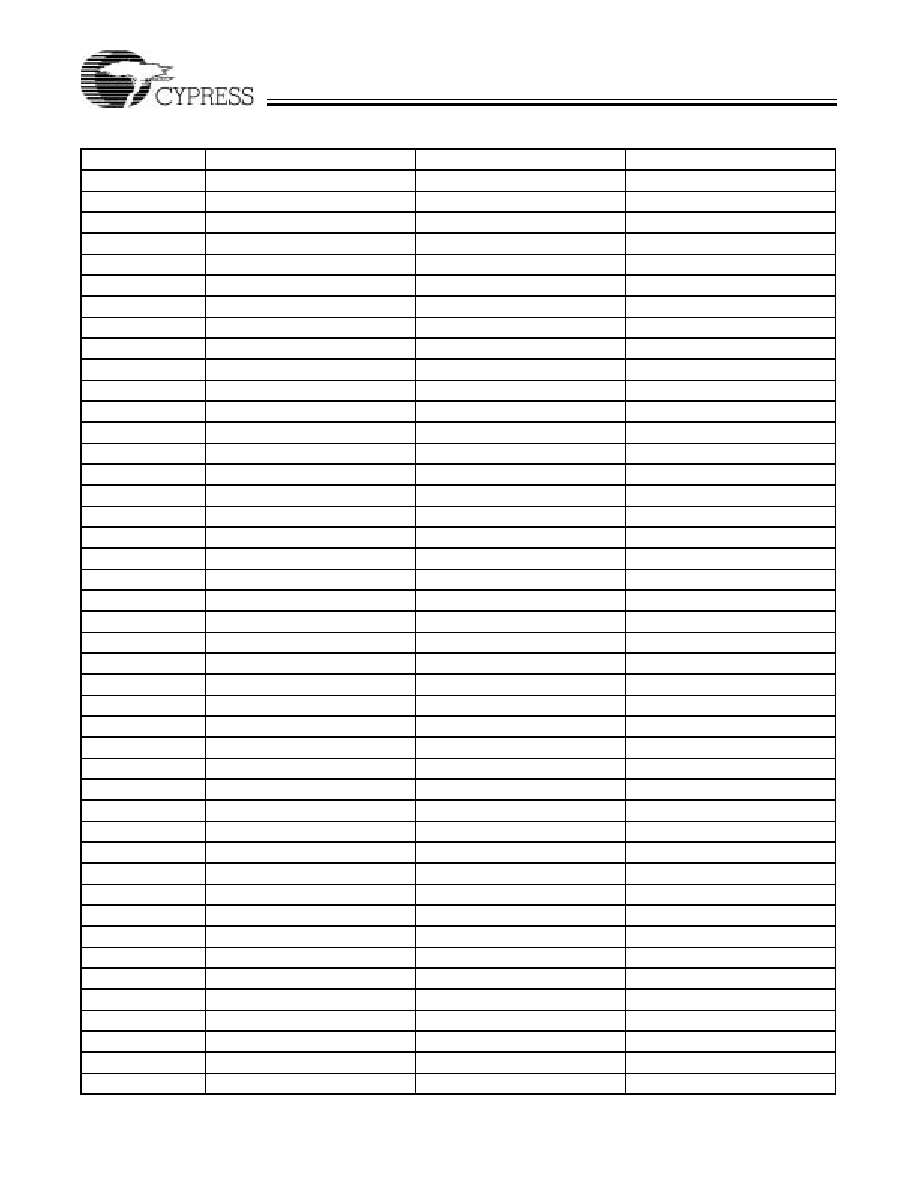

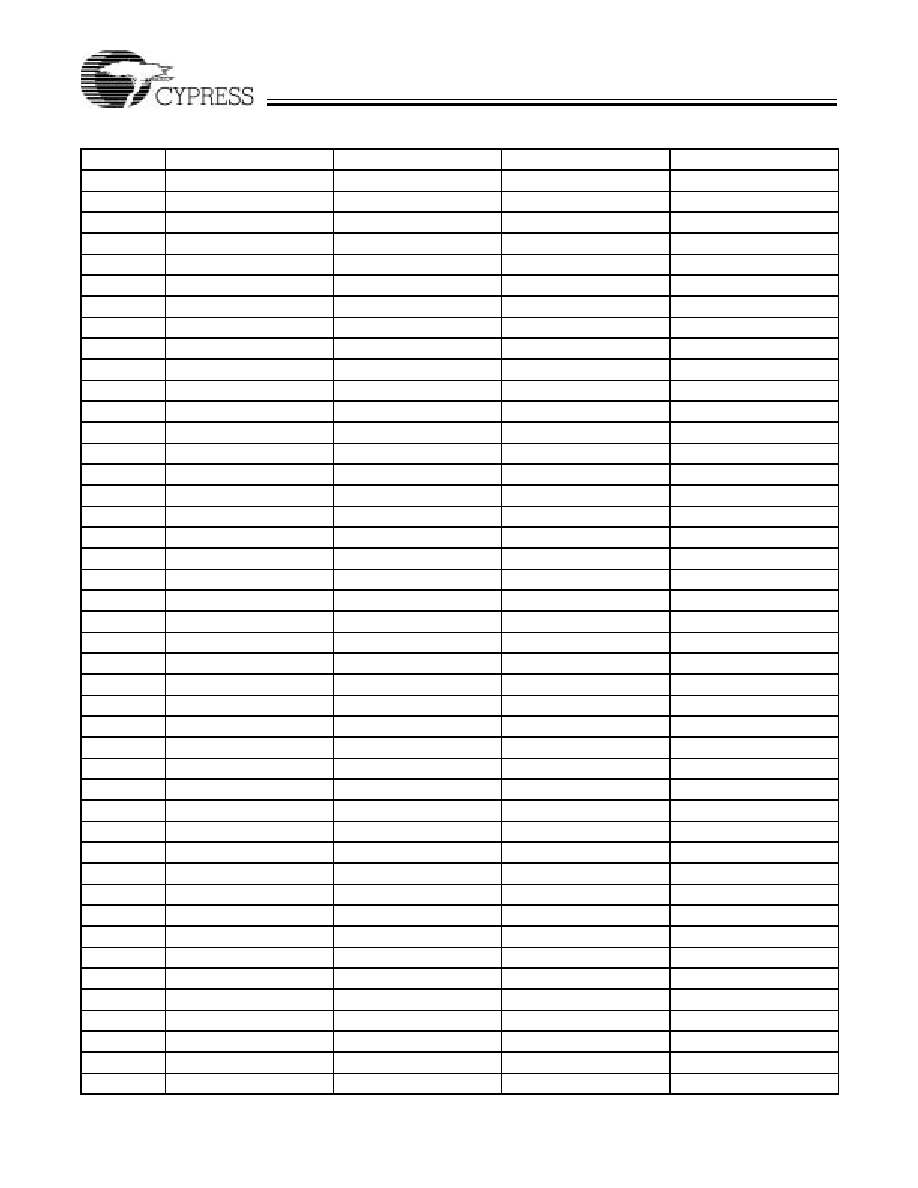

DC Characteristics

Parameter

Description

Test

Conditions

V

CCIO

= 3.3V V

CCIO

= 2.5V

V

CCIO

= 1.8V

Unit

Min. Max.

Min.

Max.

Min.

Max.

V

DRINT

Data Retention V

CC

Voltage

(config data may be lost below this)

1.5

1.5

1.5

V

V

DRIO

Data Retention V

CCIO

Voltage

(config data may be lost below this)

1.2

1.2

1.2

V

I

IX

[7]

Input Leakage Current

GND

V

I

3.6V

≠10

10

≠10

10

≠10

10

µA

I

OZ

Output Leakage Current

GND

V

O

V

CCIO

≠10

10

≠10

10

≠10

10

µA

I

OS

[8]

Output Short Circuit Current

V

CCIO

= Max.

V

OUT

= 0.5V

≠160

≠160

≠160

µA

I

BHL

Input Bus Hold LOW Sustaining Current V

CC

= Min.

V

PIN

= V

IL

+40

+30

+25

µA

I

BHH

Input Bus Hold HIGH Sustaining Current V

CC

= Min.

V

PIN

= V

IH

≠40

≠30

≠25

µA

I

BHLO

Input Bus Hold LOW Overdrive Current V

CC

= Max.

+250

+200

+150

µA

I

BHHO

Input Bus Hold HIGH Overdrive Current V

CC

= Max.

≠250

≠200

≠150

µA

I

CC0

Standby Current

39K30

39K50

39K100

39K165

39K200

All bins

20

20

30

60

60

All bins

20

20

30

60

60

≠125 bin

3

3

5

10

10

≠83 bin

12

12

20

40

40

µA

Delta39K100

Package

Pins

388-BGA

B4, C2

484-FBGA

B8, G9

676-FBGA

F11, J11

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 17 of 86

Power-up Sequence Requirements

∑ Upon power-up, all the outputs remain three-stated until all

the V

CC

pins

have powered-up to the nominal voltage and

the part has completed configuration.

∑ The part will not start configuration until V

CC

, V

CCIO

,

V

CCJTAG

, V

CCCNFG

, V

CCPLL

and V

CCPRG

have reached

nominal voltage.

∑ V

CC

pins can be powered up in any order. This includes

V

CC

, V

CCIO

, V

CCJTAG

, V

CCCNFG

, V

CCPLL

and V

CCPRG

.

∑ All V

CCIO

s on a bank should be tied to the same potential

and powered up together.

∑ All V

CCIO

s (even the unused banks) need to be powered up

to at least 1.5V before configuration has completed.

∑ Maximum ramp time for all V

CC

s should be 0V to nominal

voltage in 100 ms.

Notes:

9.

PCI spec (rev 2.2) requires the IDSEL pin to have capacitance less than or equal to 8 pF. Delta39K Pin Tables starting from page 45, identify all the I/O pins in

a given package, which can be used as IDSEL in a PCI design. All other I/O pins meet the PCI requirement of capacitance less than or equal to 10 pf.

10. The number of I/Os which can be used in each I/O bank depends on the type of I/O standards and the number of V

CCIO

and GND pins being used. Please refer

to the application note titled "Delta39K and Quantum38K I/O Standards and Configurations" for details.

∑

The source current limit per I/O bank per Vccio pin is 165 mA.

∑

The sink current limit per I/O bank per GND pin is 230 mA.

11. See "Power-up Sequence Requirements" below for V

CCIO

requirement.

12. 25W resistor terminated to termination voltage of 1.5V.

Capacitance

Parameter

Description

Test Conditions

Min.

Max.

Unit

C

I/O

Input/Output Capacitance

V

in

= V

CCIO

@ f = 1 MHz 25∞C

10

pF

C

CLK

Clock Signal Capacitance

V

in

= V

CCIO

@ f = 1 MHz 25∞C

5

12

pF

C

PCI

PCI-compliant

[9]

Capacitance

V

in

= V

CCIO

@ f = 1 MHz 25∞C

8

pF

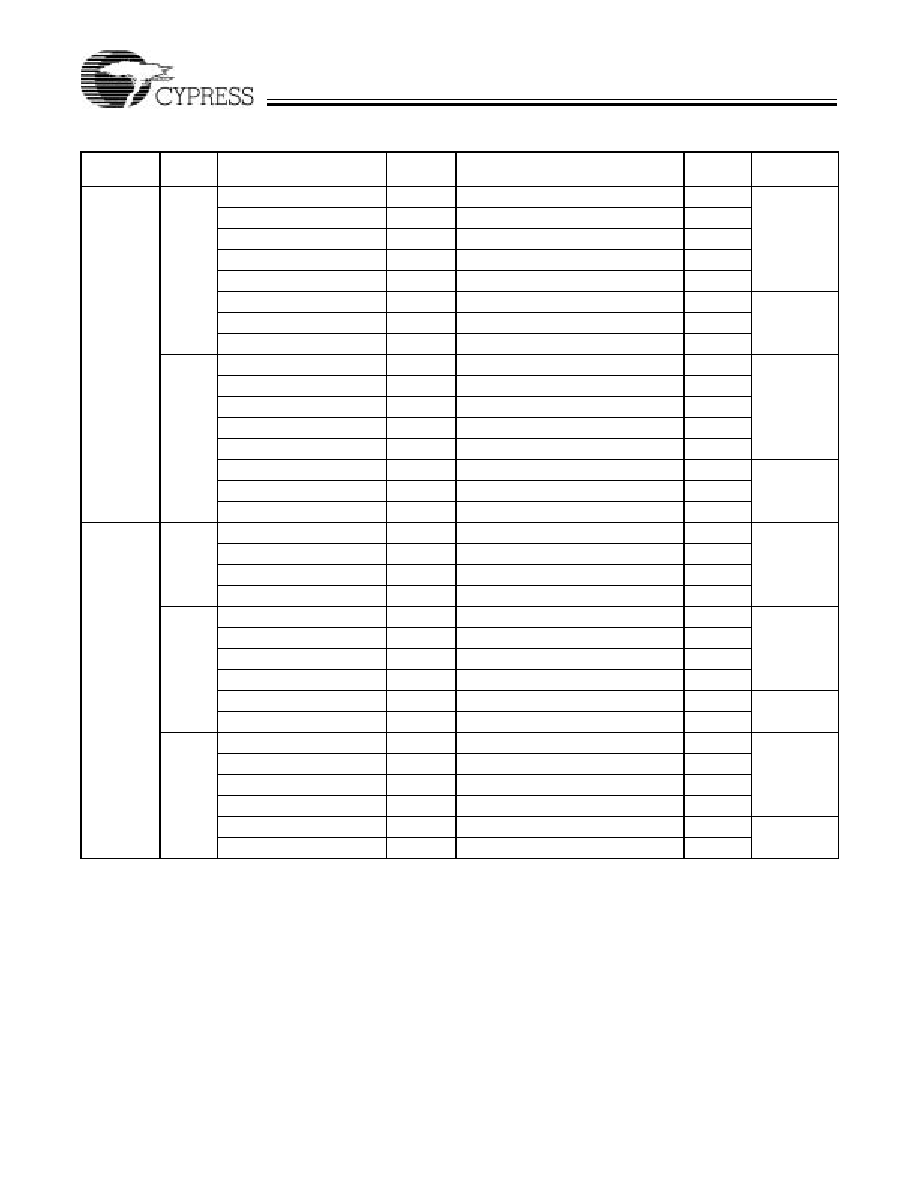

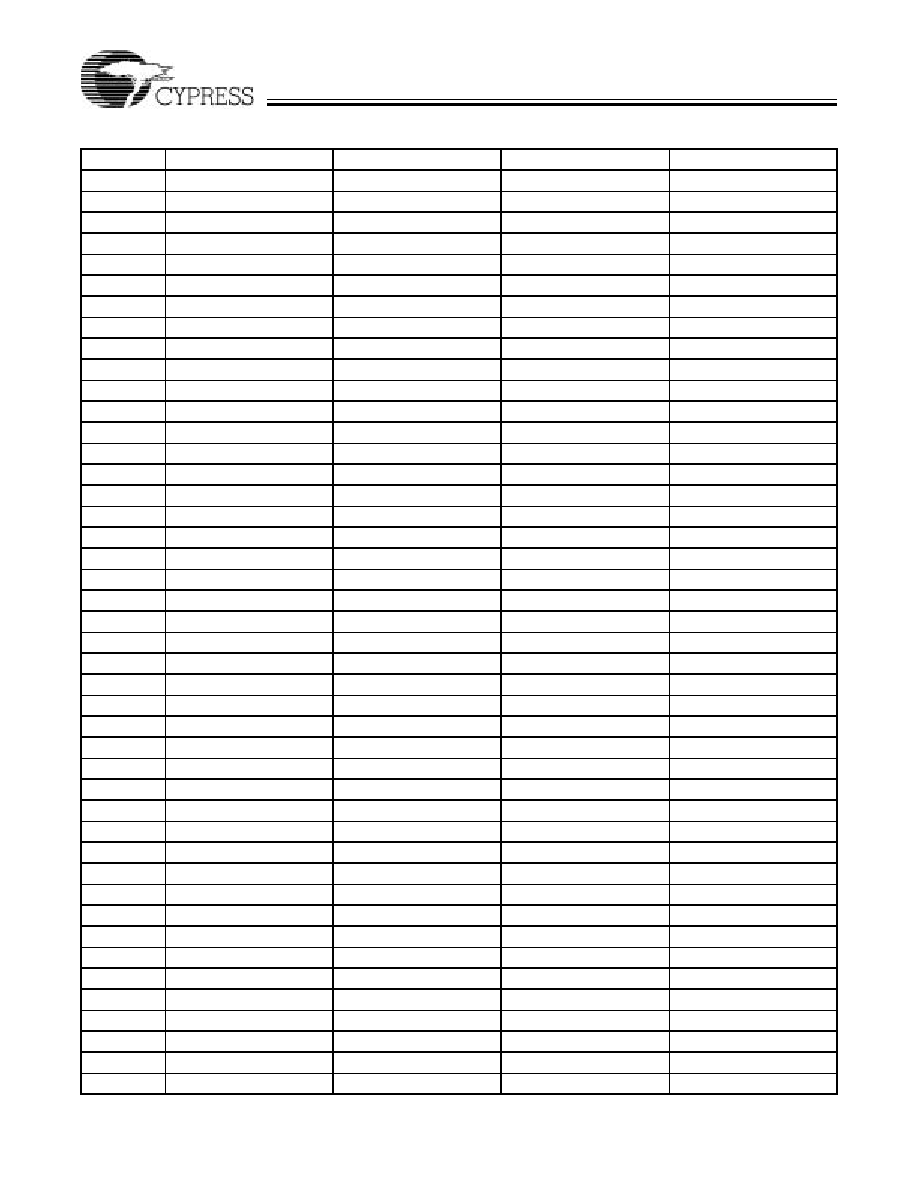

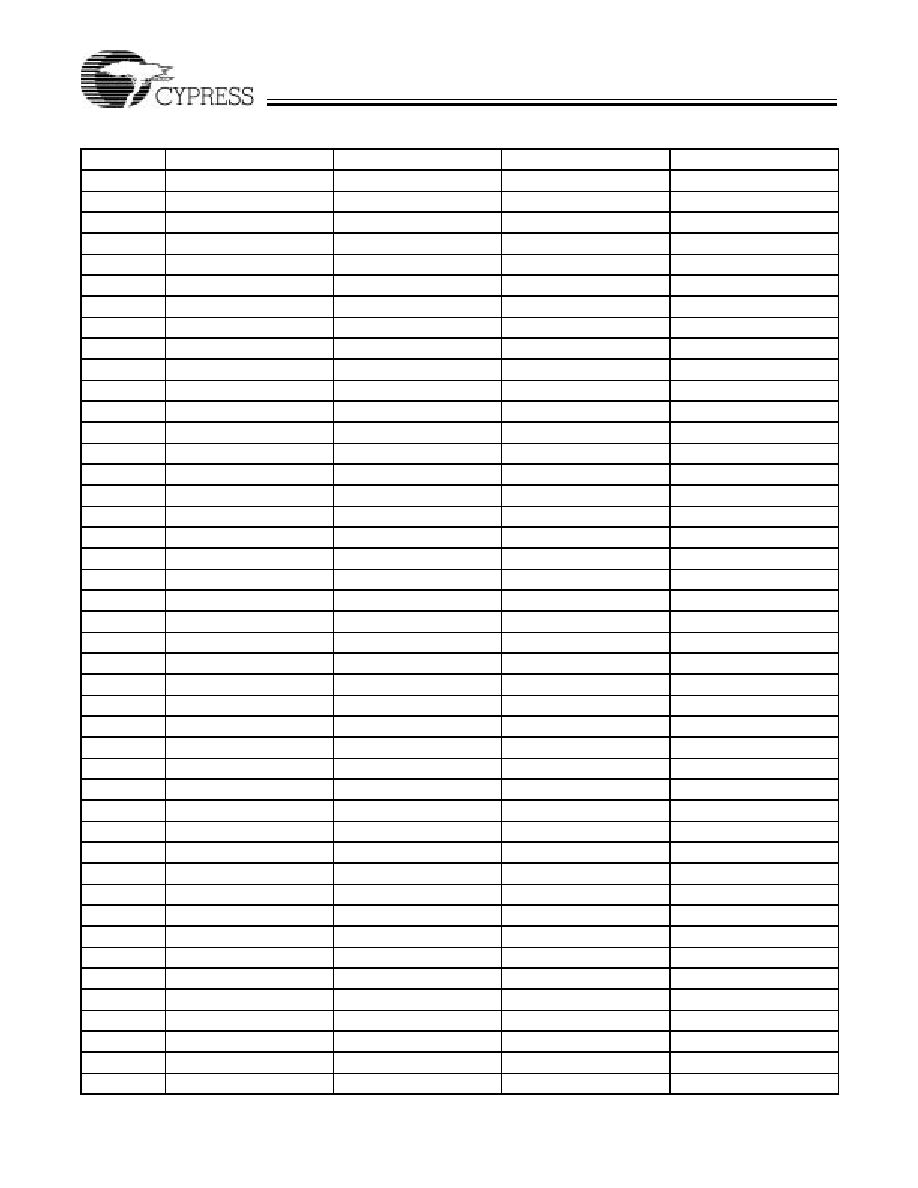

DC Characteristics (I/O)

[10]

I/O Standards

V

REF

(V)

V

CCIO

(V)

V

OH

(V)

V

OL

(V)

V

IH

(V)

V

IL

(V)

@ I

OH

=

V

OH

(min.)

@ I

OL

=

V

OL

(max.)

Min.

Max.

Min.

Max.

LVTTL ≠2 mA

N/A

3.3

≠2 mA

2.4

2 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠4 mA

3.3

≠4 mA

2.4

4 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠6 mA

3.3

≠6 mA

2.4

6 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠8 mA

3.3

≠8 mA

2.4

8 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠12 mA

3.3

≠12 mA

2.4

12 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠16 mA

3.3

≠16 mA

2.4

16 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVTTL ≠24 mA

3.3

≠24 mA

2.4

24 mA

0.4

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVCMOS

3.3 ≠0.1

mA

V

CCIO

≠ 0.2V

0.1 mA

0.2

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVCMOS3

3.0

≠0.1 mA

V

CCIO

≠ 0.2V

0.1 mA

0.2

2.0V

V

CCIO

+ 0.3 ≠0.3V

0.8V

LVCMOS2

2.5

≠0.1 mA

2.1

0.1 mA

0.2

1.7V

V

CCIO

+ 0.3 ≠0.3V

0.7V

≠1.0 mA

2.0

1.0 mA

0.4

≠2.0 mA

1.7

2.0 mA

0.7

LVCMOS18

1.8 ≠2

mA

V

CCIO

≠ 0.45V

2.0 mA

0.45

0.65V

CCIO

V

CCIO

+ 0.3 ≠0.3V

0.35V

CCIO

3.3V PCI

3.3

≠0.5 mA

0.9V

CCIO

1.5 mA

0.1V

CCIO

0.5V

CCIO

V

CCIO

+ 0.5 ≠0.5V

0.3V

CCIO

GTL+ 1.0

[11]

36 mA

[12]

0.6

V

REF

+ 0.2

V

REF

≠ 0.2

SSTL3 I

1.5

3.3

≠8 mA

V

CCIO

≠ 1.1V

8 mA

0.7

V

REF

+ 0.2

V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.2

SSTL3 II

1.5

3.3

≠16 mA

V

CCIO

≠ 0.9V

16 mA

0.5

V

REF

+ 0.2

V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.2

SSTL2 I

1.25

2.5

≠7.6 mA V

CCIO

≠ 0.62V

7.6 mA

0.54

V

REF

+ 0.18 V

CCIO

+ 0.3 ≠0.3V V

REF

≠ 0.18

SSTL2 II

1.25

2.5

≠15.2 mA V

CCIO

≠ 0.43V 15.2 mA

0.35

V

REF

+ 0.18 V

CCIO

+ 0.3 ≠0.3V V

REF

≠ 0.18

HSTL I

0.75

1.5

≠8 mA

V

CCIO

≠ 0.4V

8 mA

0.4

V

REF

+ 0.1

V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.1

HSTL II

0.75

1.5

≠16 mA

V

CCIO

≠ 0.4V

16 mA

0.4

V

REF

+ 0.1

V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.1

HSTL III

0.9

1.5

≠8 mA

V

CCIO

≠ 0.4V

24 mA

0.4

V

REF

+ 0.1

V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.1

HSTL IV

0.9

1.5

≠8 mA

V

CCIO

≠ 0.4V

48 mA

0.4

V

REF

+ 0.1 V

CCIO

+ 0.3 ≠0.3V

V

REF

≠ 0.1

Configuration Parameters

Parameter

Description

Min.

Unit

t

RECONFIG

Reconfig pin LOW time before it goes HIGH

200

ns

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 18 of 86

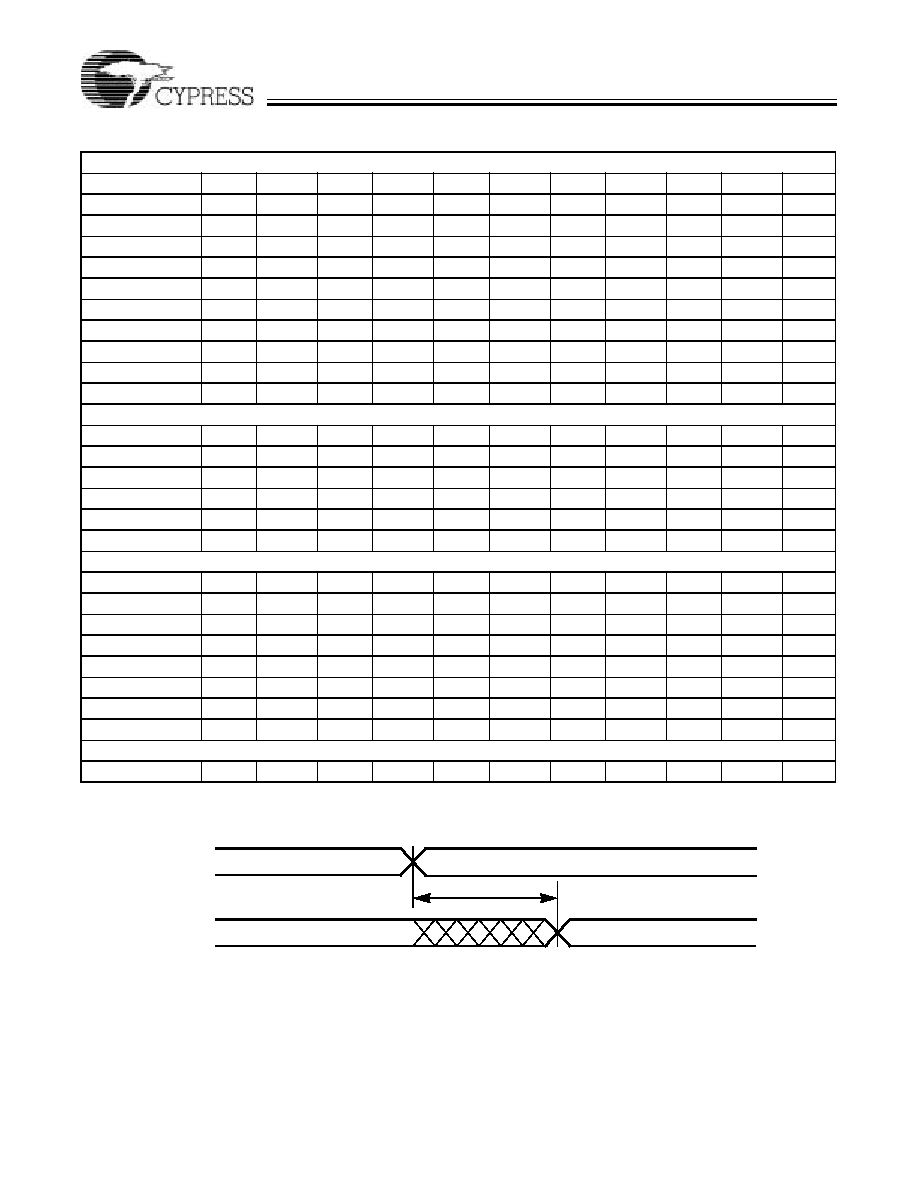

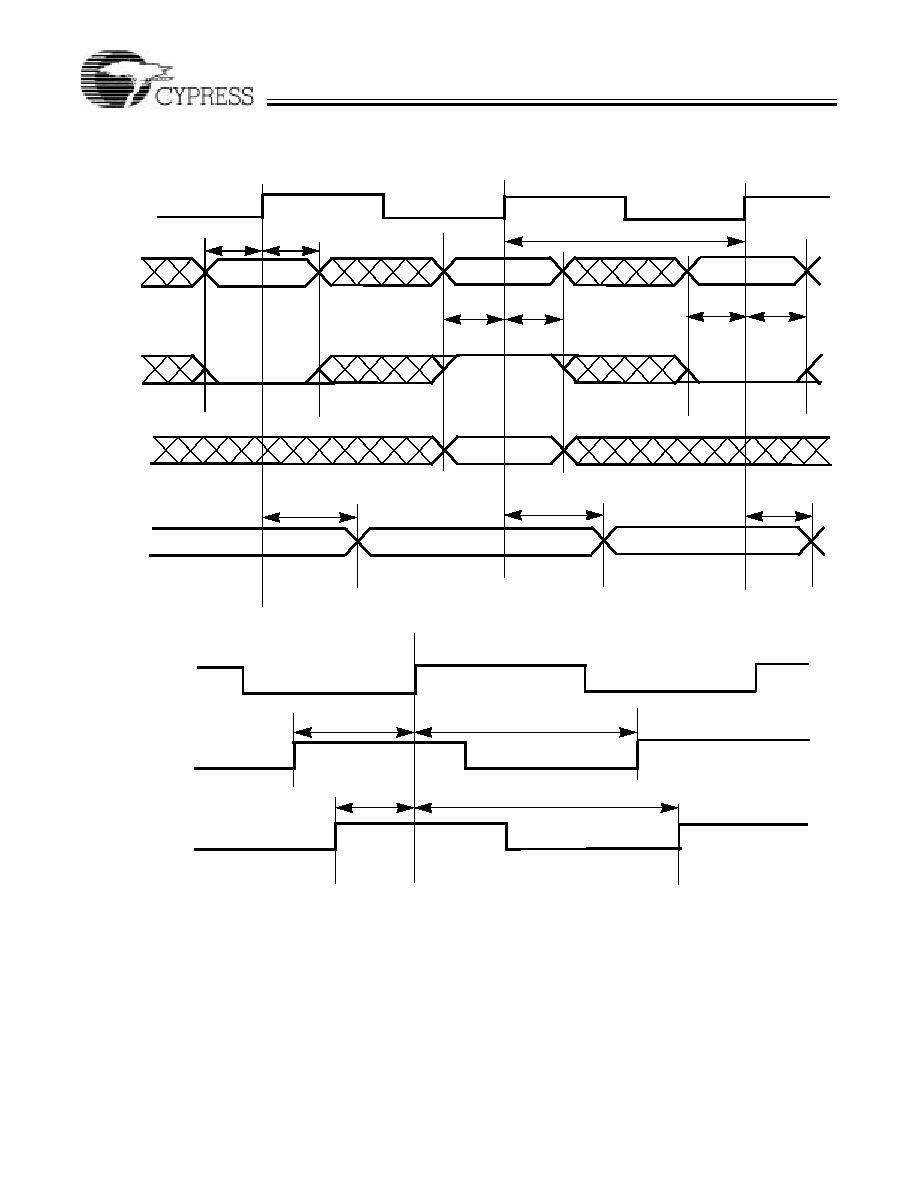

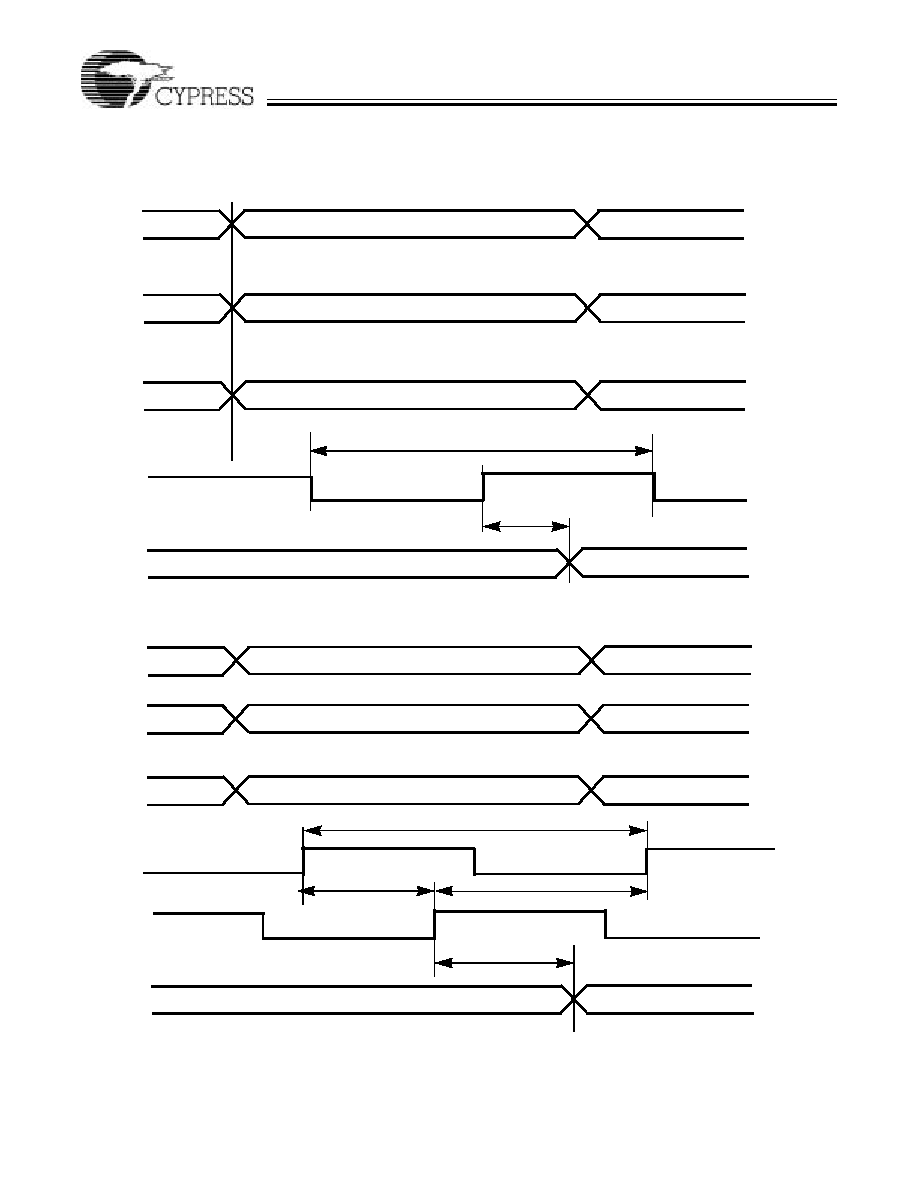

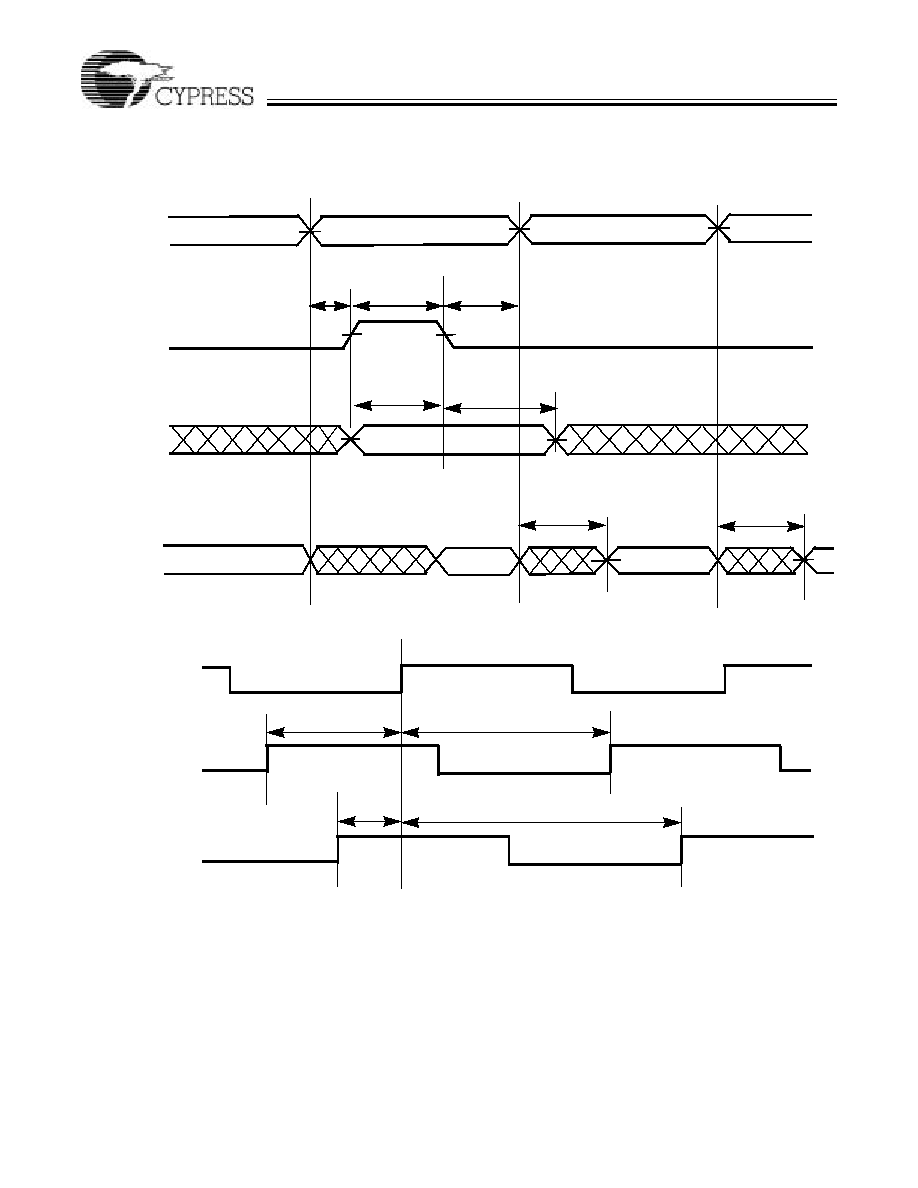

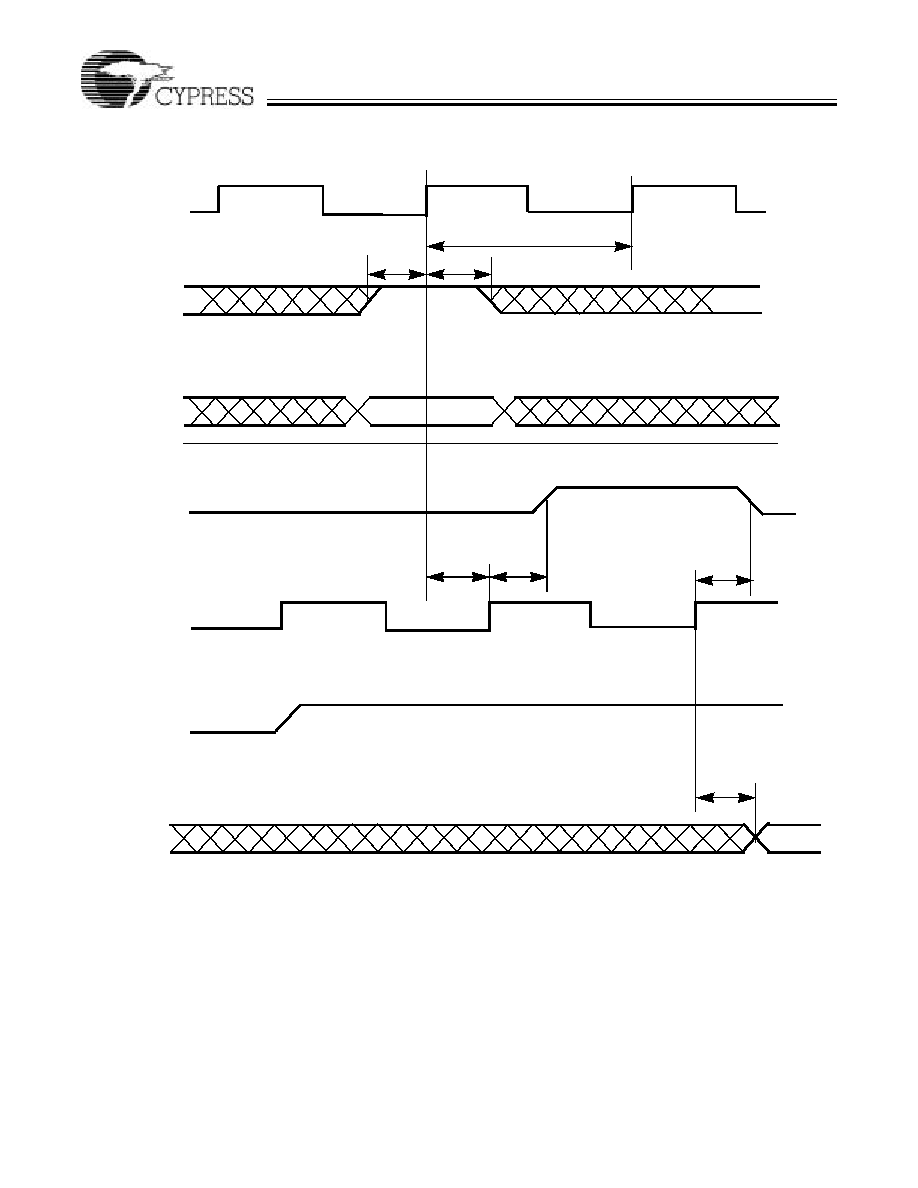

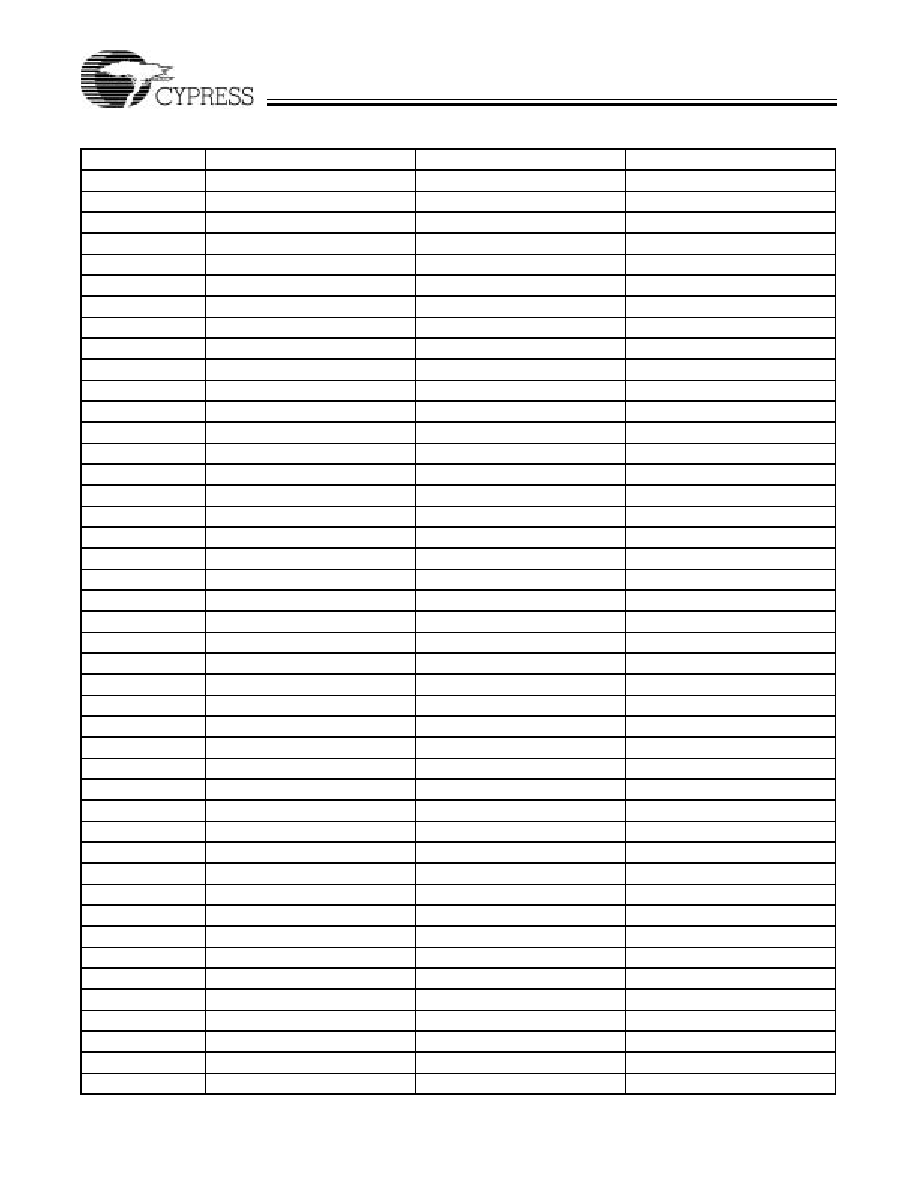

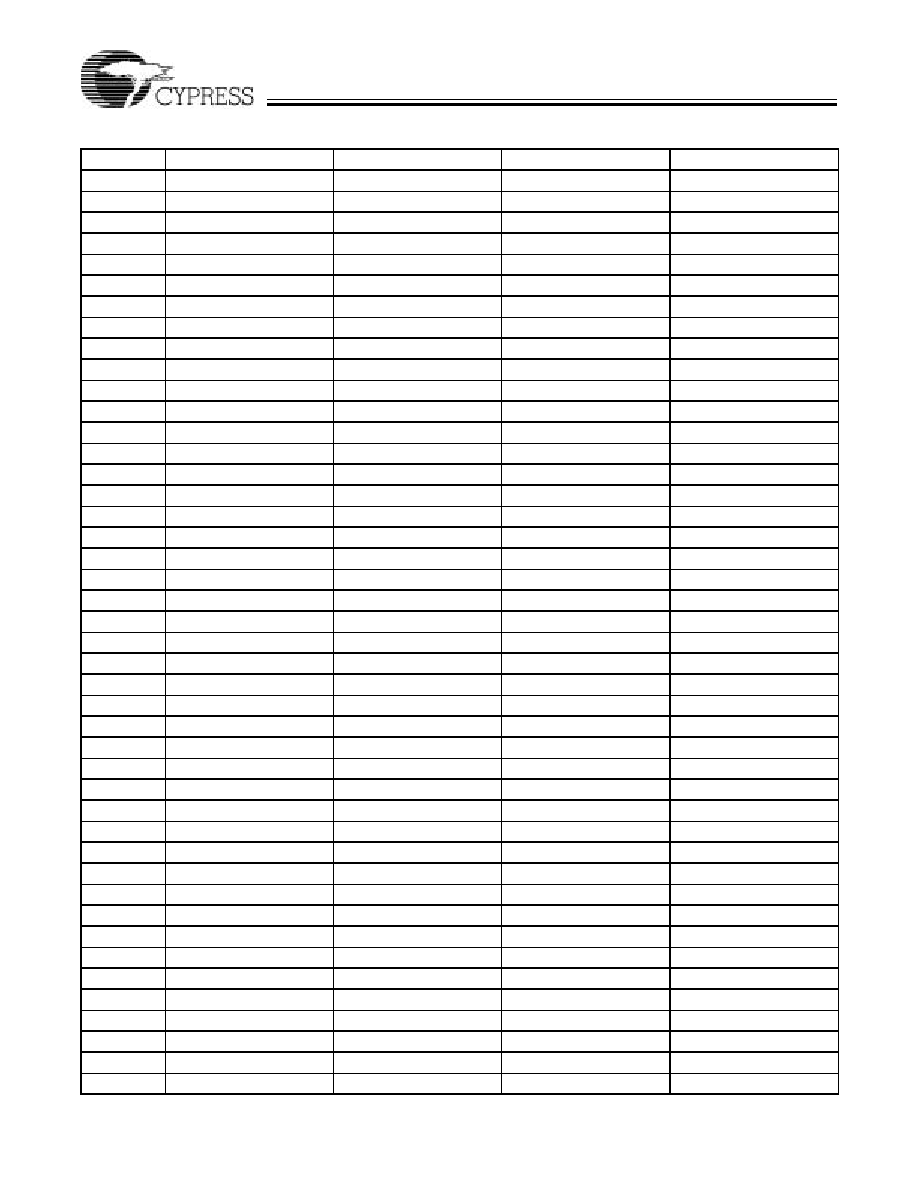

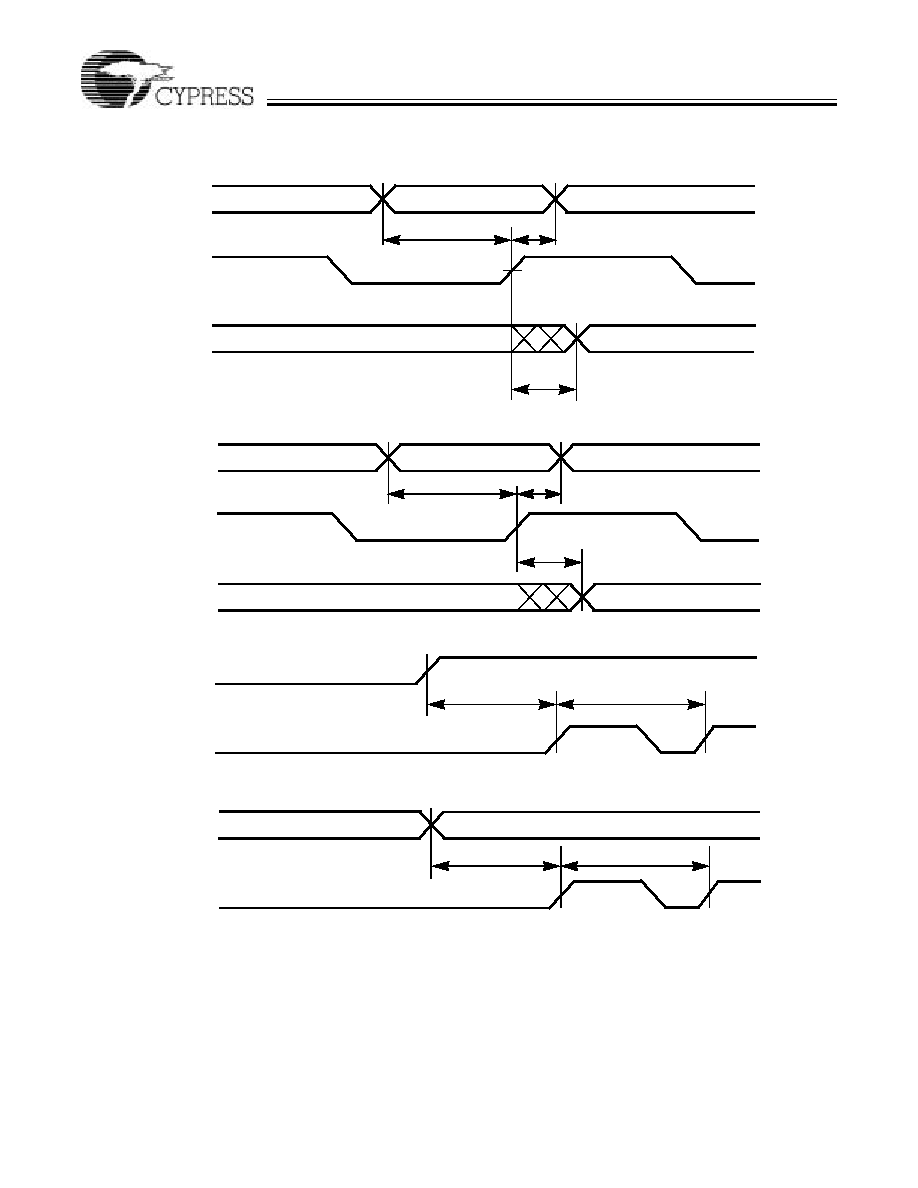

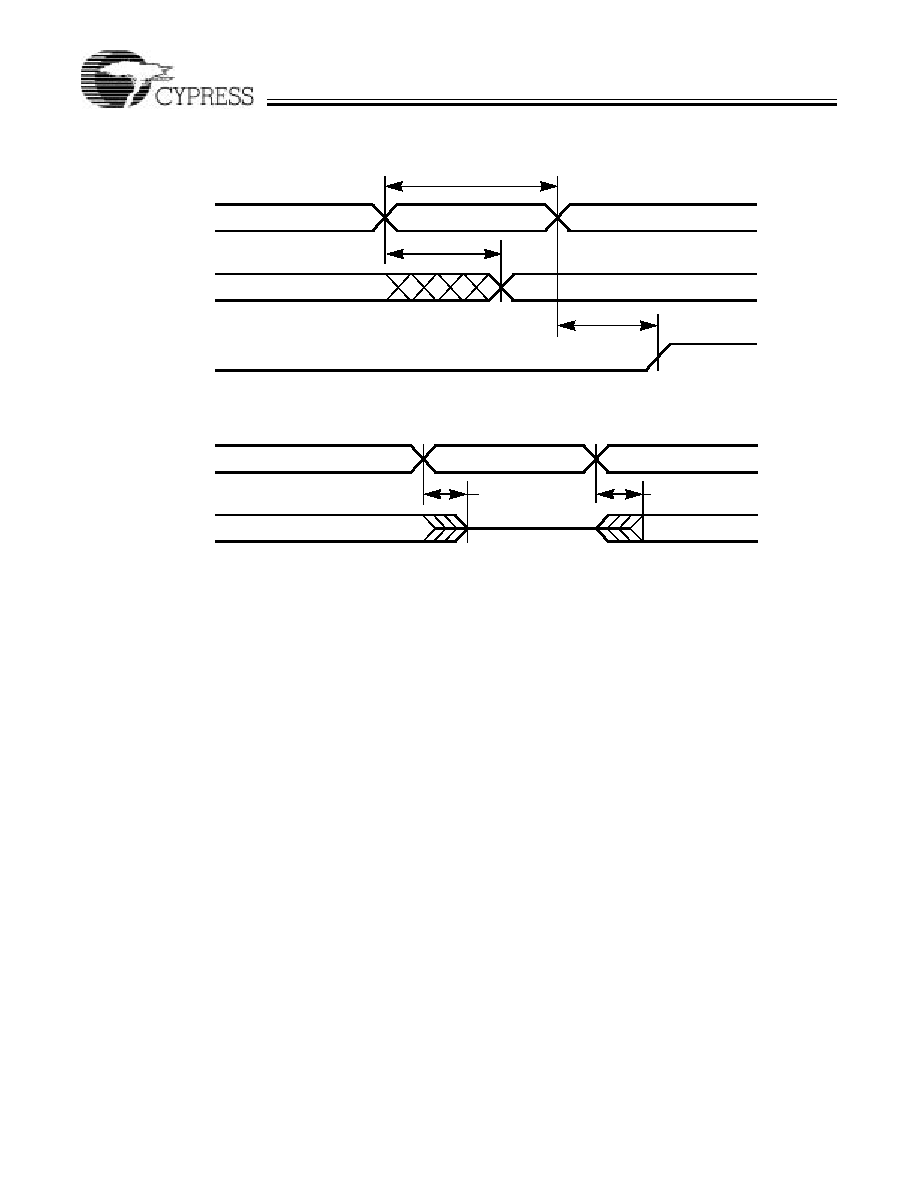

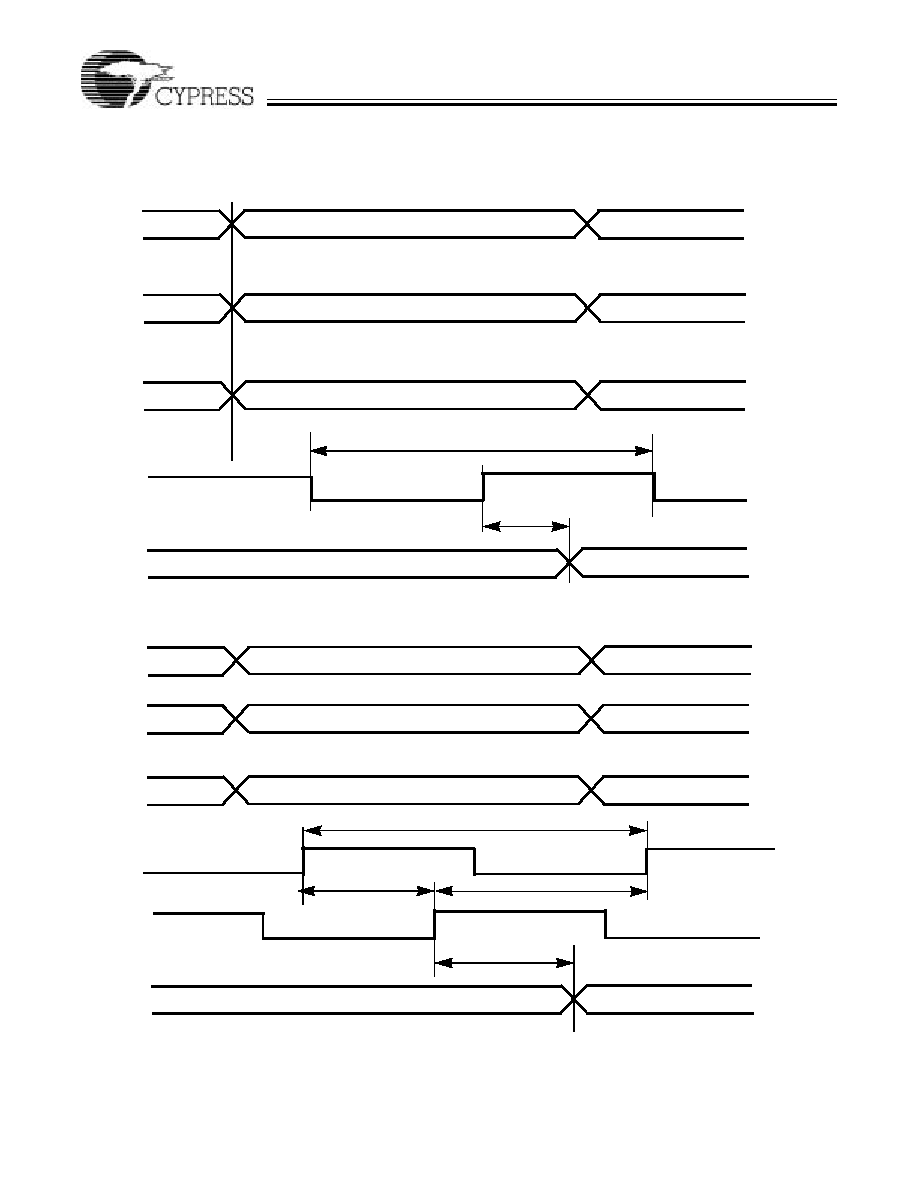

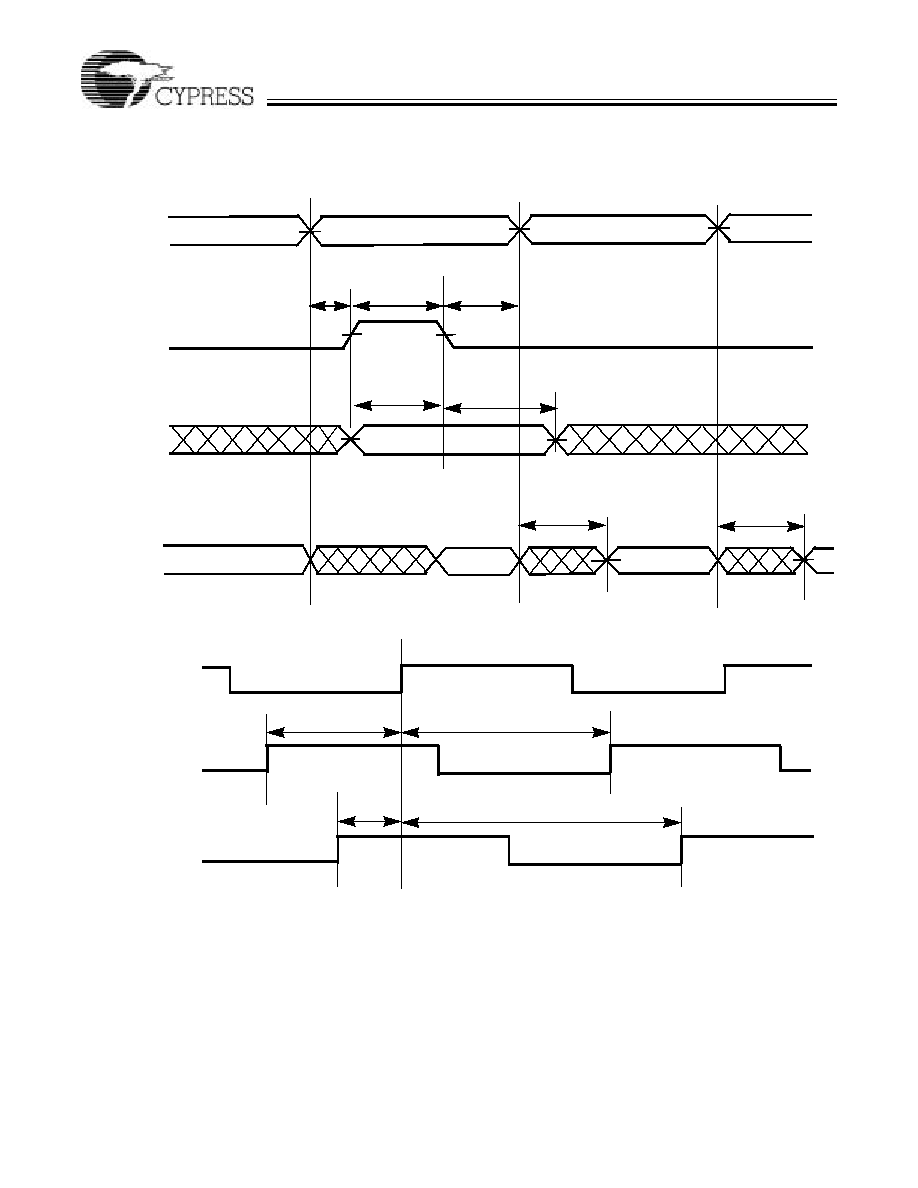

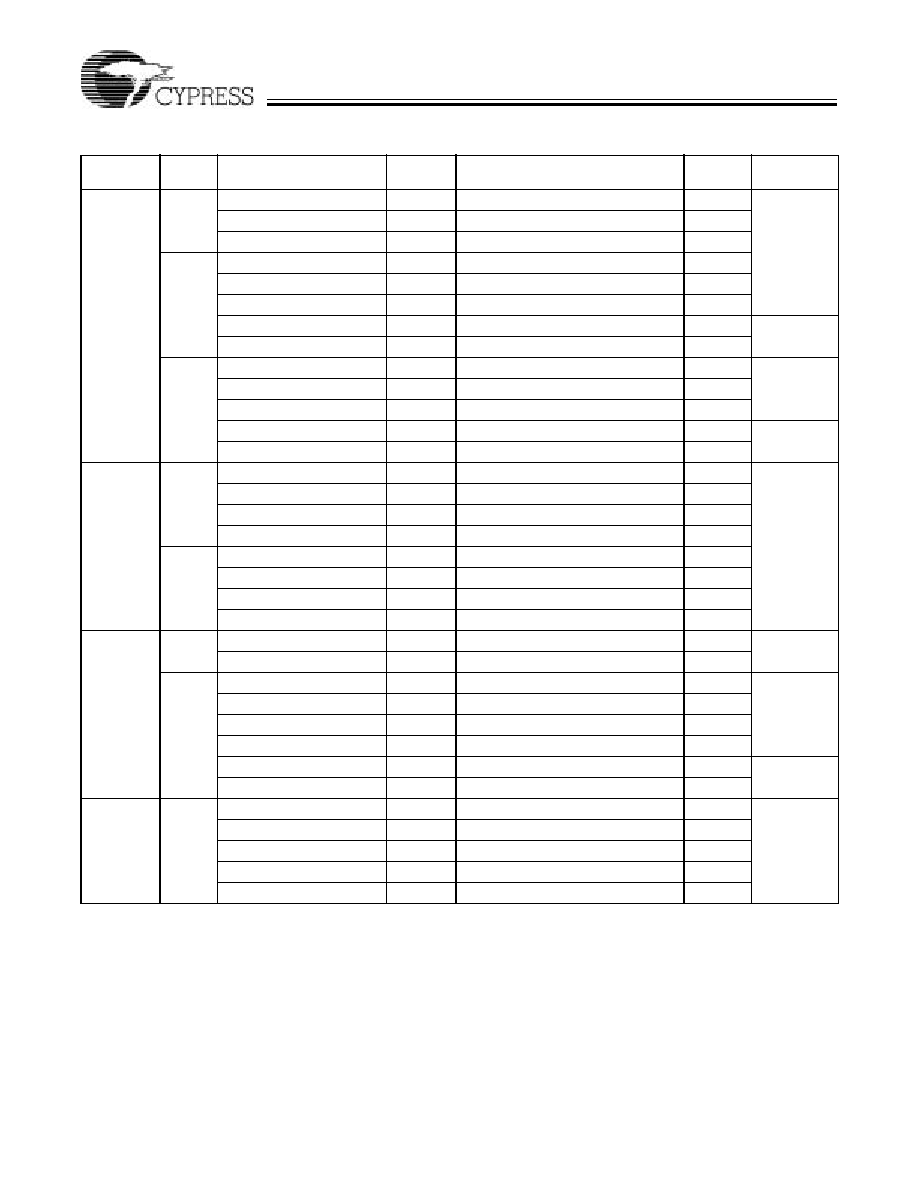

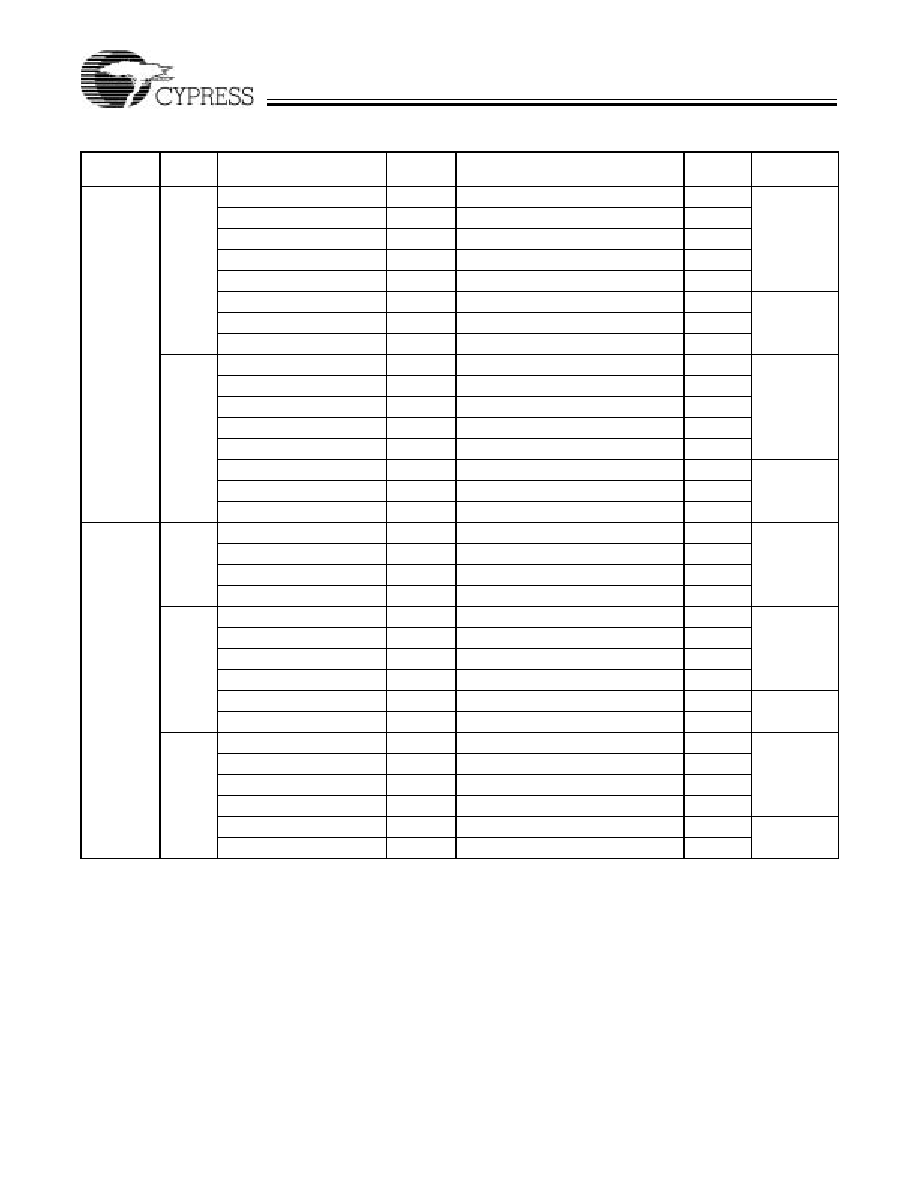

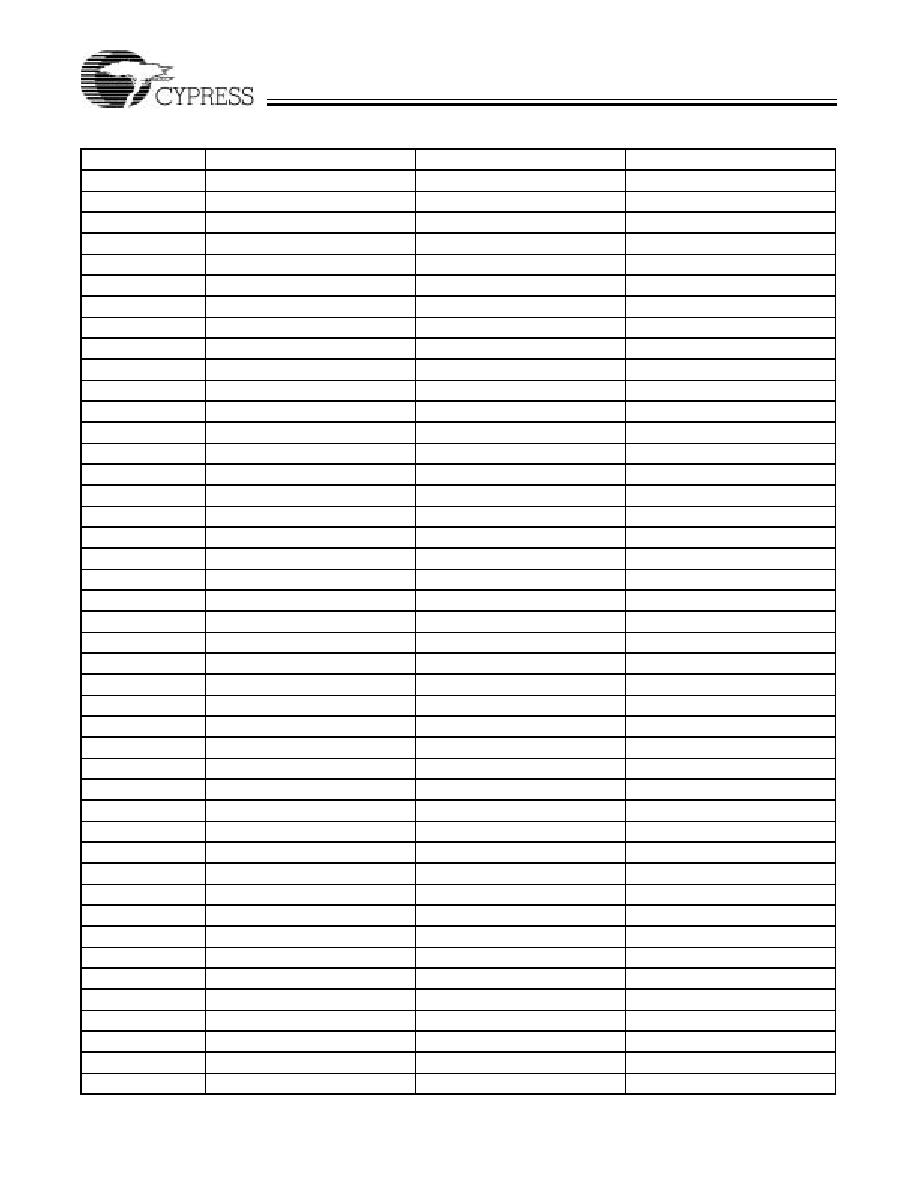

Switching Characteristics -- Parameter Descriptions

Over the Operating Range

[13]

Parameter

Description

Combinatorial Mode Parameters

t

PD

Delay from any pin input, through any cluster on the channel associated with that pin input, to any pin output on the

horizontal or vertical channel associated with that cluster

t

EA

Global control to output enable

t

ER

Global control to output disable

t

PRR

Asynchronous macrocell RESET or PRESET recovery time from any pin input on the horizontal or vertical channel

associated with the cluster the macrocell is in

t

PRO

Asynchronous macrocell RESET or PRESET from any pin input on the horizontal or vertical channel associated

with the cluster that the macrocell is in to any pin output on those same channels

t

PRW

Asynchronous macrocell RESET or PRESET minimum pulse width, from any pin input to a macrocell in the farthest

cluster on the horizontal or vertical channel the pin is associated with

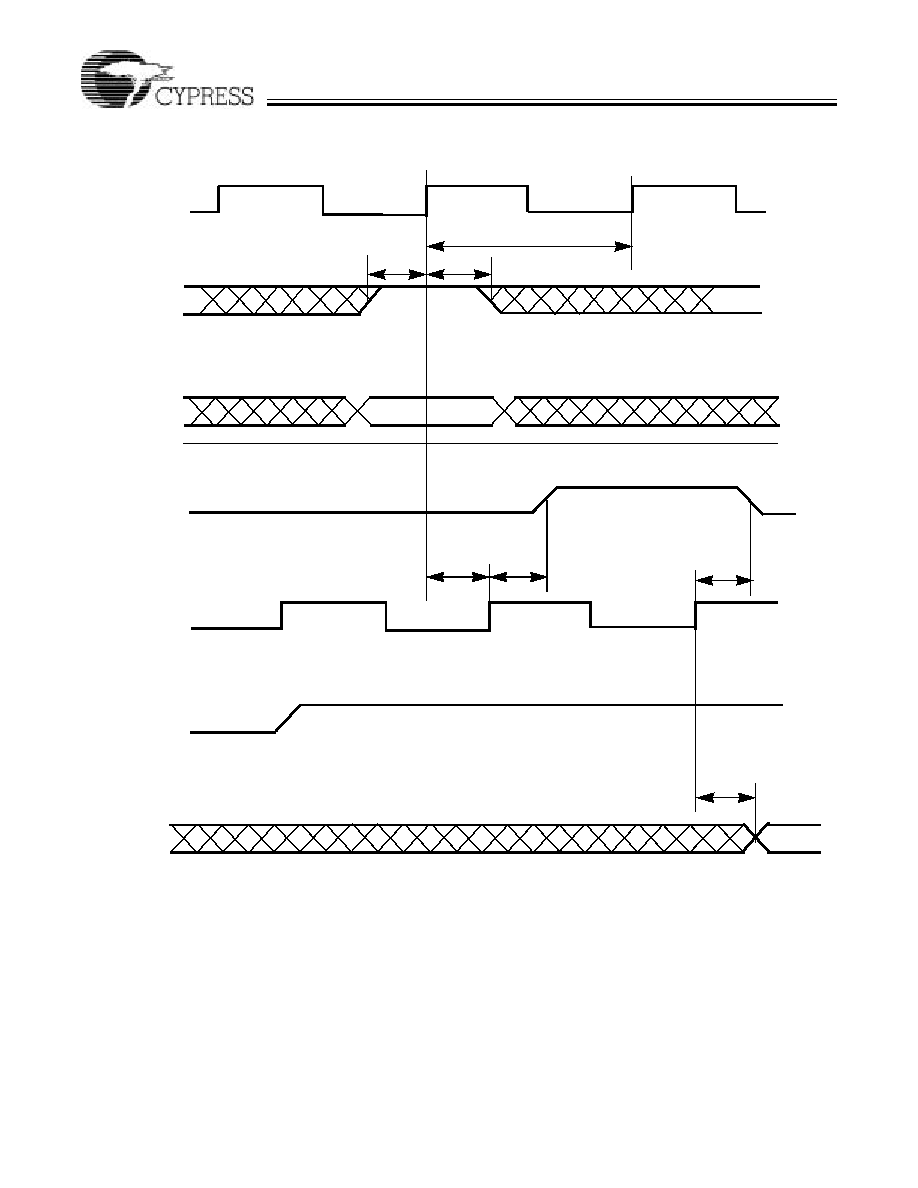

Synchronous Clocking Parameters

t

MCS

Set-up time of any input pin to a macrocell in any cluster on the channel associated with that input pin, relative to a

global clock

t

MCH

Hold time of any input pin to a macrocell in any cluster on the channel associated with that input pin, relative to a

global clock

t

MCCO

Global clock to output of any macrocell to any output pin on the horizontal or vertical channel associated with the

cluster that macrocell is in

t

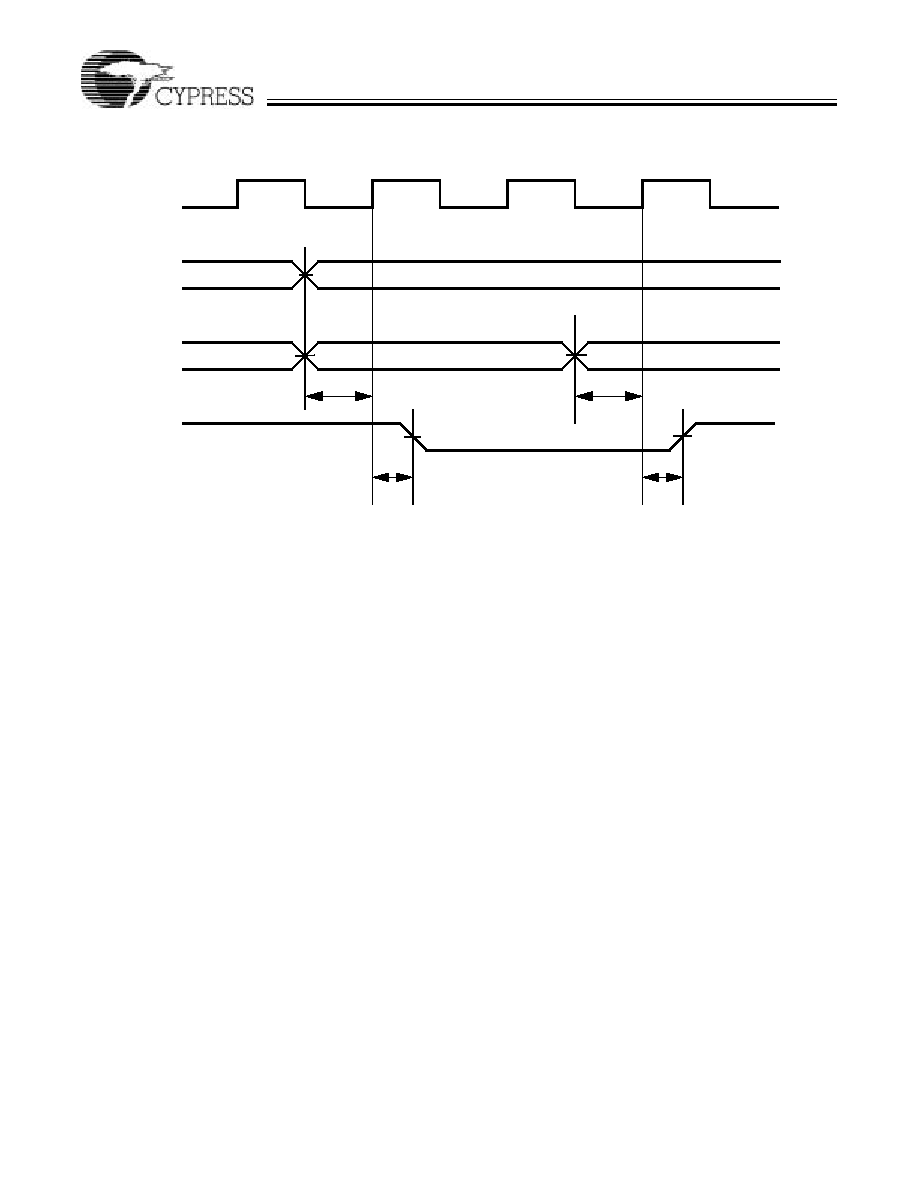

IOS

Set-up time of any input pin to the I/O cell register associated with that pin, relative to a global clock

t

IOH

Hold time of any input pin to the I/O cell register associated with that pin, relative to a global clock

t

IOCO

Clock to output of an I/O cell register to the output pin associated with that register

t

SCS

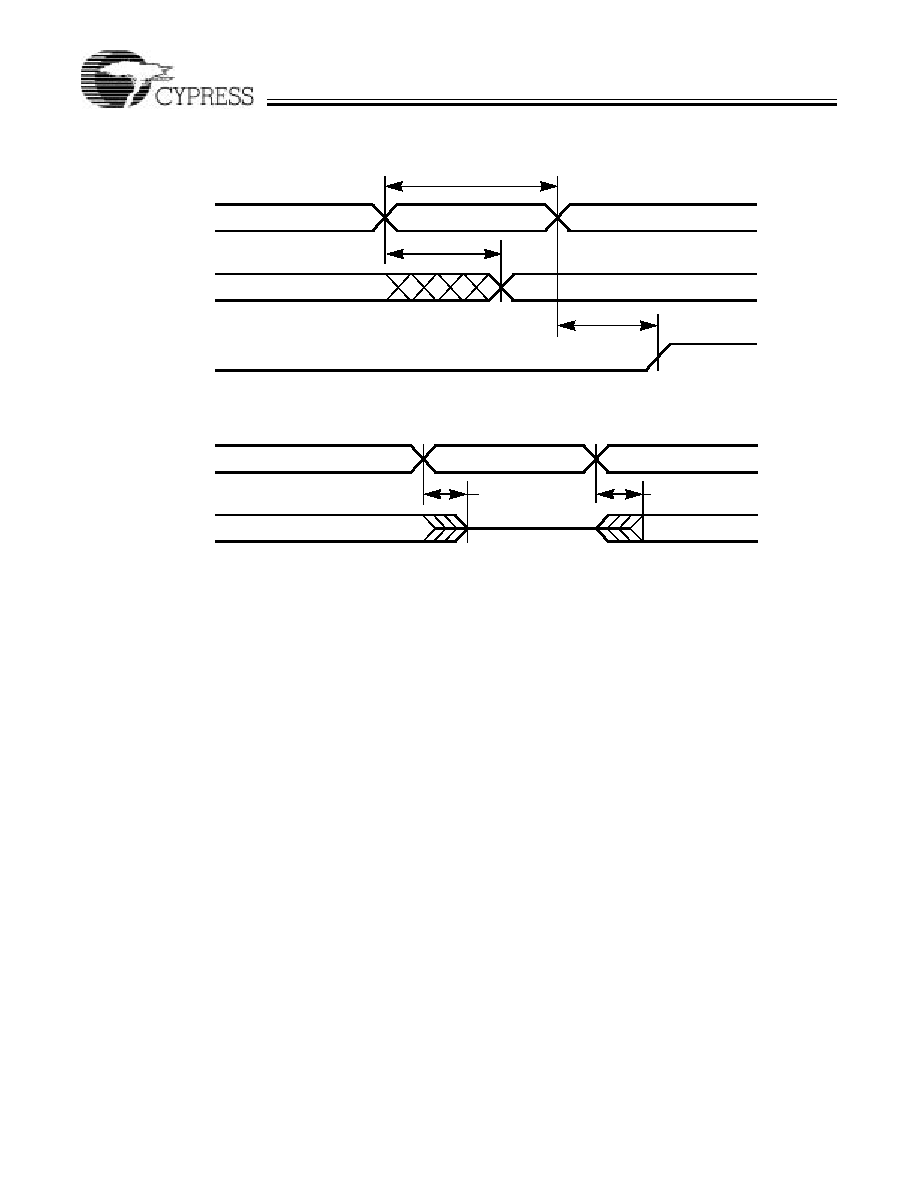

Macrocell clock to macrocell clock through array logic within the same cluster

t

SCS2

Macrocell clock to macrocell clock through array logic in different clusters on the same channel

t

ICS

I/O register clock to any macrocell clock in a cluster on the channel the I/O register is associated with

t

OCS

Macrocell clock to any I/O register clock on the horizontal or vertical channel associated with the cluster that the

macrocell is in

t

CHZ

Clock to output disable (high-impedance)

t

CLZ

Clock to output enable (low-impedance)

f

MAX

Maximum frequency with internal feedback--within the same cluster

f

MAX2

Maximum frequency with internal feedback--within different clusters at the opposite ends of a horizontal or vertical

channel

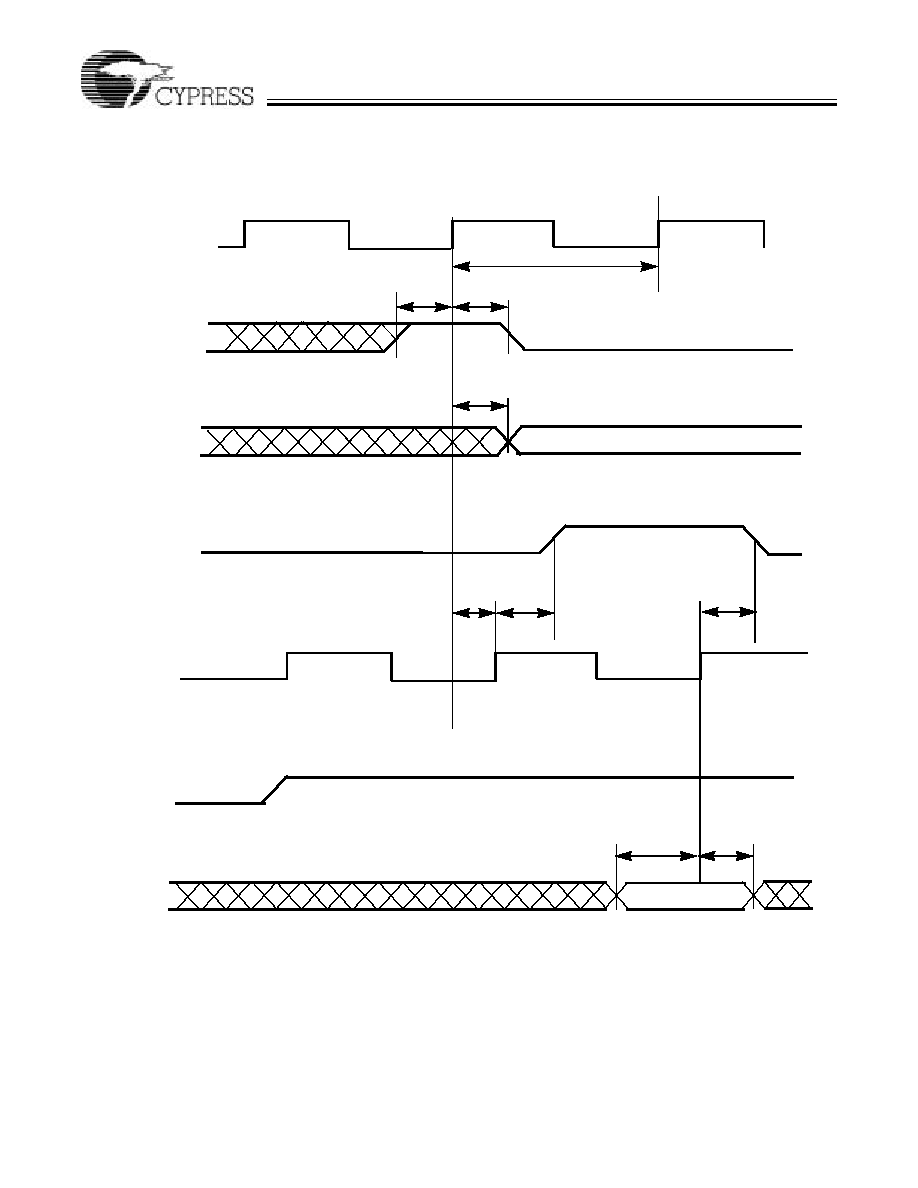

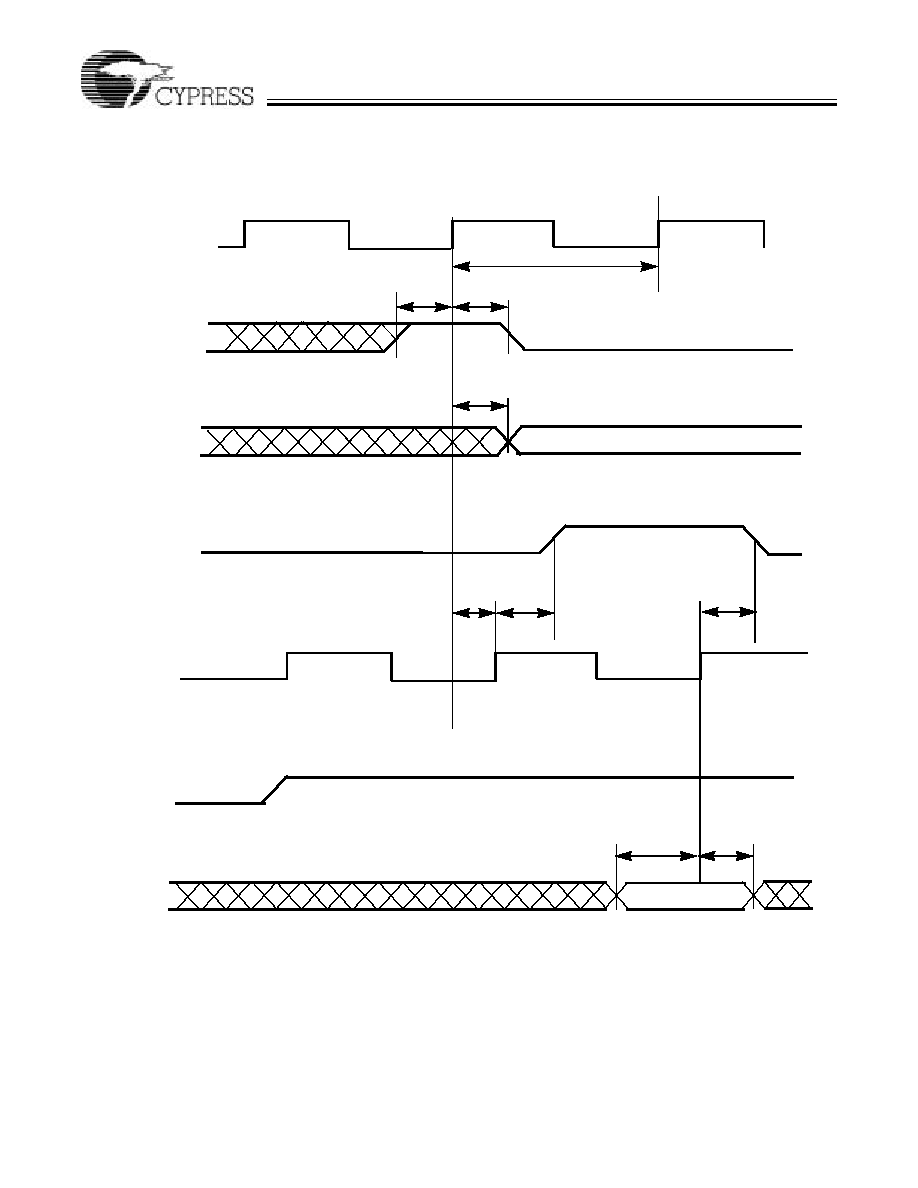

Product Term Clock

t

MCSPT

Set-up time for macrocell used as input register, from input to product term clock

t

MCHPT

Hold time of macrocell used as an input register

t

MCCOPT

Product term clock to output delay from input pin

t

SCS2PT

Register to register delay through array logic in different clusters on the same channel using a product term clock

Channel Interconnect Parameters

t

CHSW

Adder for a signal to switch from a horizontal to vertical channel and vice-versa

t

CL2CL

Cluster-to-cluster delay adder (through channels and channel PIM)

Miscellaneous Delays

t

CPLD

Delay from the input of a cluster PIM, through a macrocell in the cluster, back to a cluster PIM input. This parameter

can be added to the t

PD

and t

SCS

parameters for each extra pass through the AND/OR array required by a given

signal path

t

MCCD

Adder for carry chain logic per macrocell

t

IOD

Delay from the input of the output buffer to the I/O pin

t

IOIN

Delay from the I/O pin to the input of the channel buffer

Note:

13. Add t

CHSW

to signals making a horizontal to vertical channel switch or vice-versa.

Delta39KTM ISRTM

CPLD Family

Document #: 38-03039 Rev. *H

Page 19 of 86

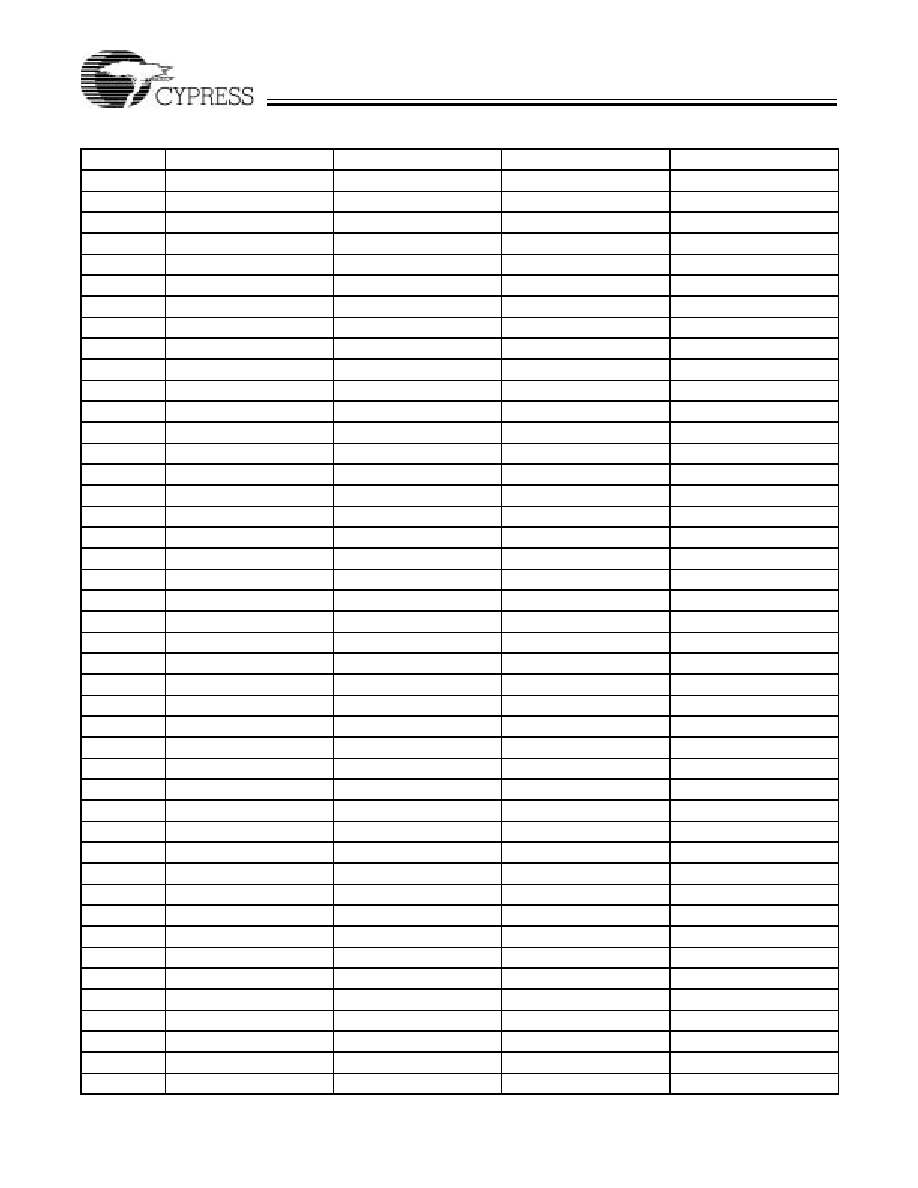

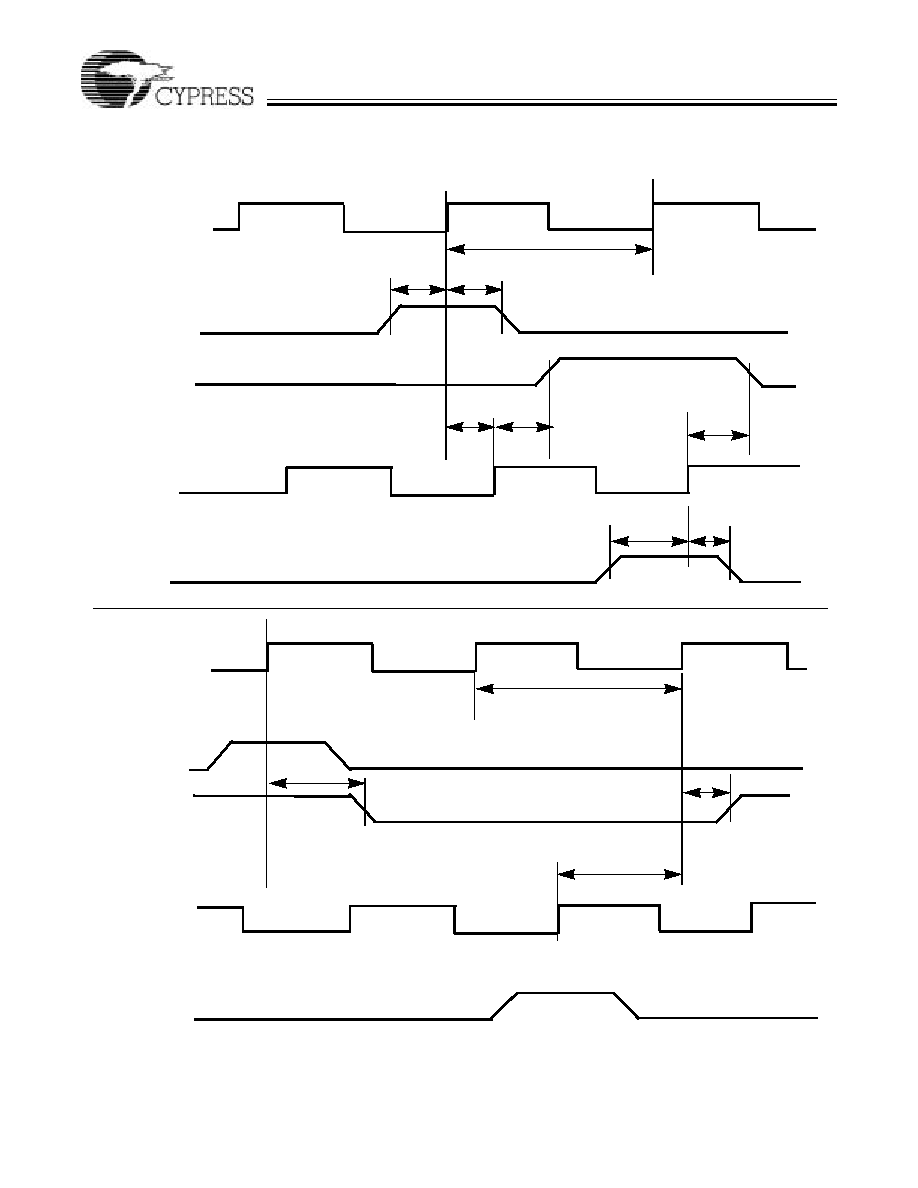

t

CKIN

Delay from the clock pin to the input of the clock driver

t

IOREGPIN

Delay from the I/O pin to the input of the I/O register

PLL Parameters

t

MCCJ

Maximum cycle to cycle jitter time

t

DWSA

PLL zero phase delay with clock tree deskewed

t

DWOSA

PLL zero phase delay without clock tree deskewed

t

LOCK

Lock time for the PLL

t

INDUTY

Input duty cycle

f

PLLI

Input frequency of the PLL

f

PLLO

Output frequency of the PLL

f

PLLVCO

PLL VCO frequency of operation

P

SAPLLI

Percentage modulation allowed (spread awareness) on the PLL input clock

f

MPLLI

Frequency of modulation allowed on PLL input clock. This specifies how fast the f

PLLI

sweeps between f

PLLI

*

(1≠P

SAPLLI

/100) and f

PLLI

* (1+ P

SAPLLI

/100)

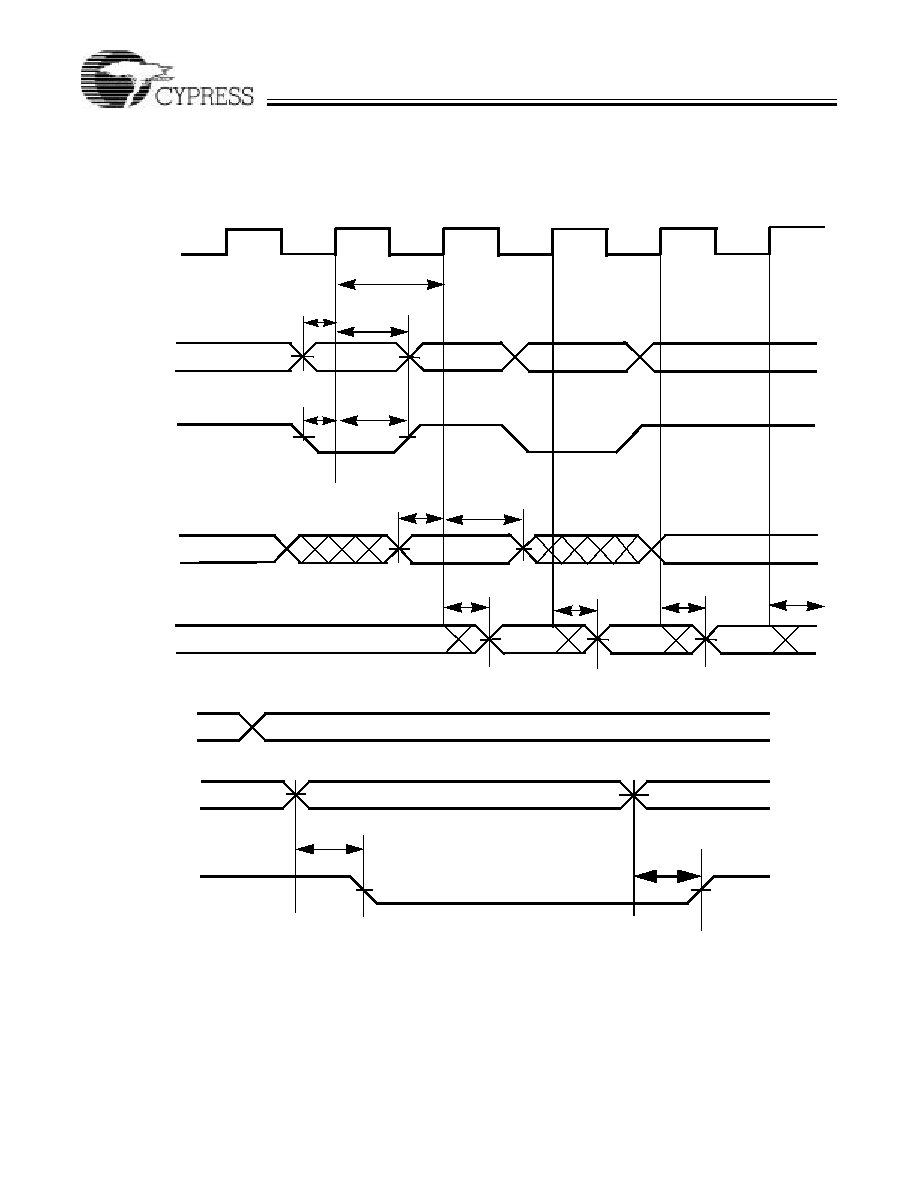

JTAG Parameters

t

JCKH

TCLK HIGH time

t

JCKL

TCLK LOW time

t

JCP

TCLK clock period

t

JSU

JTAG port set-up time (TDI/TMS inputs)

t

JH