2M x 8 Static RAM

CY7C1069AV33

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

,

CA 95134

∑

408-943-2600

Document #: 38-05255 Rev. *D

Revised February 10, 2003

Features

∑ High speed

-- t

AA

= 8, 10, 12 ns

∑ Low active power

-- 1080 mW (max.)

∑ Operating voltages of 3.3 ± 0.3V

∑ 2.0V data retention

∑ Automatic power-down when deselected

∑ TTL-compatible inputs and outputs

∑ Easy memory expansion with CE

1

and CE

2

features

Functional Description

The CY7C1069AV33 is a high-performance CMOS Static

RAM organized as 2,097,152 words by 8 bits. Writing to the

device is accomplished by enabling the chip (by taking CE

1

LOW and CE

2

HIGH) and Write Enable (WE) inputs LOW.

Reading from the device is accomplished by enabling the chip

(CE

1

LOW and CE

2

HIGH) as well as forcing the Output

Enable (OE) LOW while forcing the Write Enable (WE) HIGH.

See the truth table at the back of this data sheet for a complete

description of Read and Write modes.

The input/output pins (I/O

0

through I/O

7

) are placed in a

high-impedance state when the device is deselected (CE

1

HIGH or CE

2

LOW), the outputs are disabled (OE HIGH), or

during a Write operation (CE

1

LOW, CE

2

HIGH, and WE

LOW).

The CY7C1069AV33 is available in a 54-pin TSOP II package

with center power and ground (revolutionary) pinout, and a

48-ball fine-pitch ball grid array (FBGA) package.

Selection Guide

≠8

≠10

≠12

Unit

Maximum Access Time

8

10

12

ns

Maximum Operating Current

Commercial

300

275

260

mA

Industrial

300

275

260

Maximum CMOS Standby Current

Commercial/Industrial

50

50

50

mA

15

16

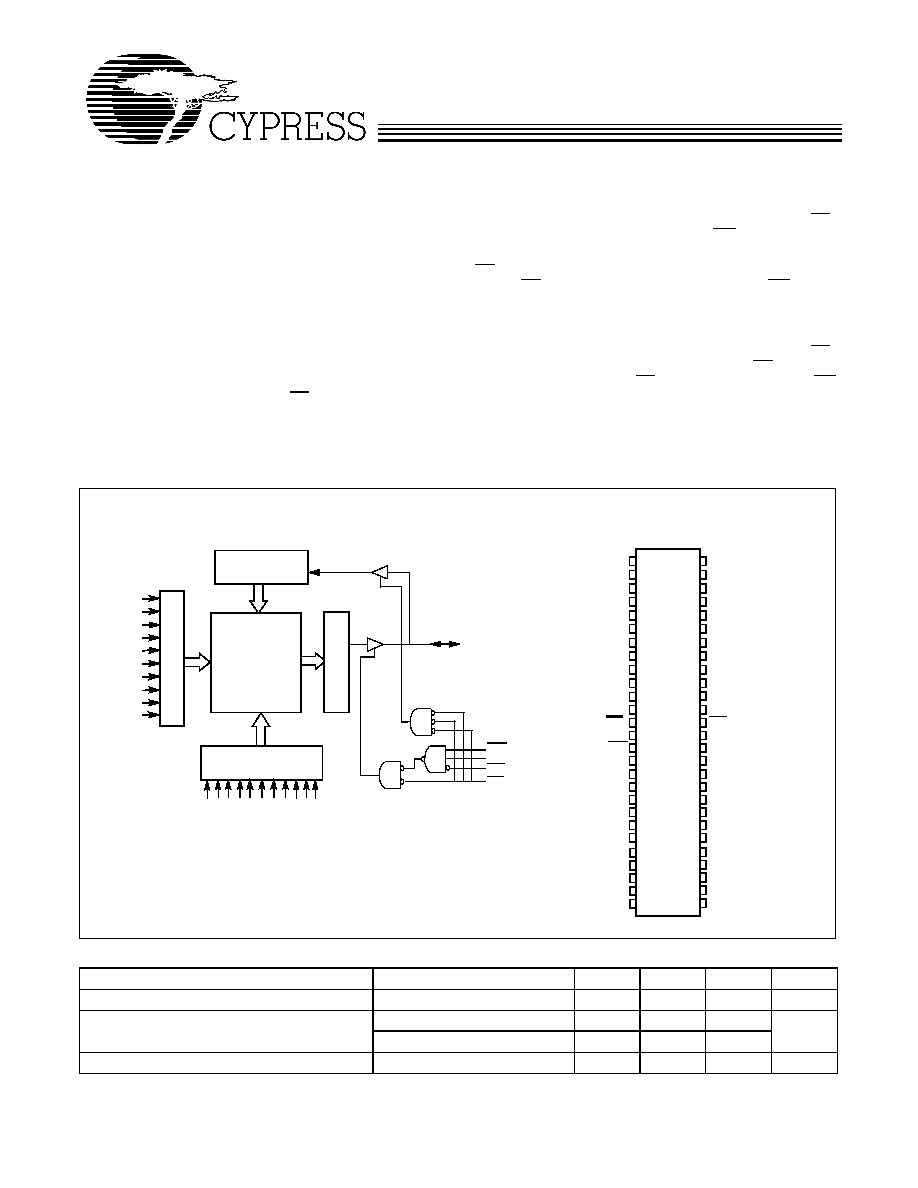

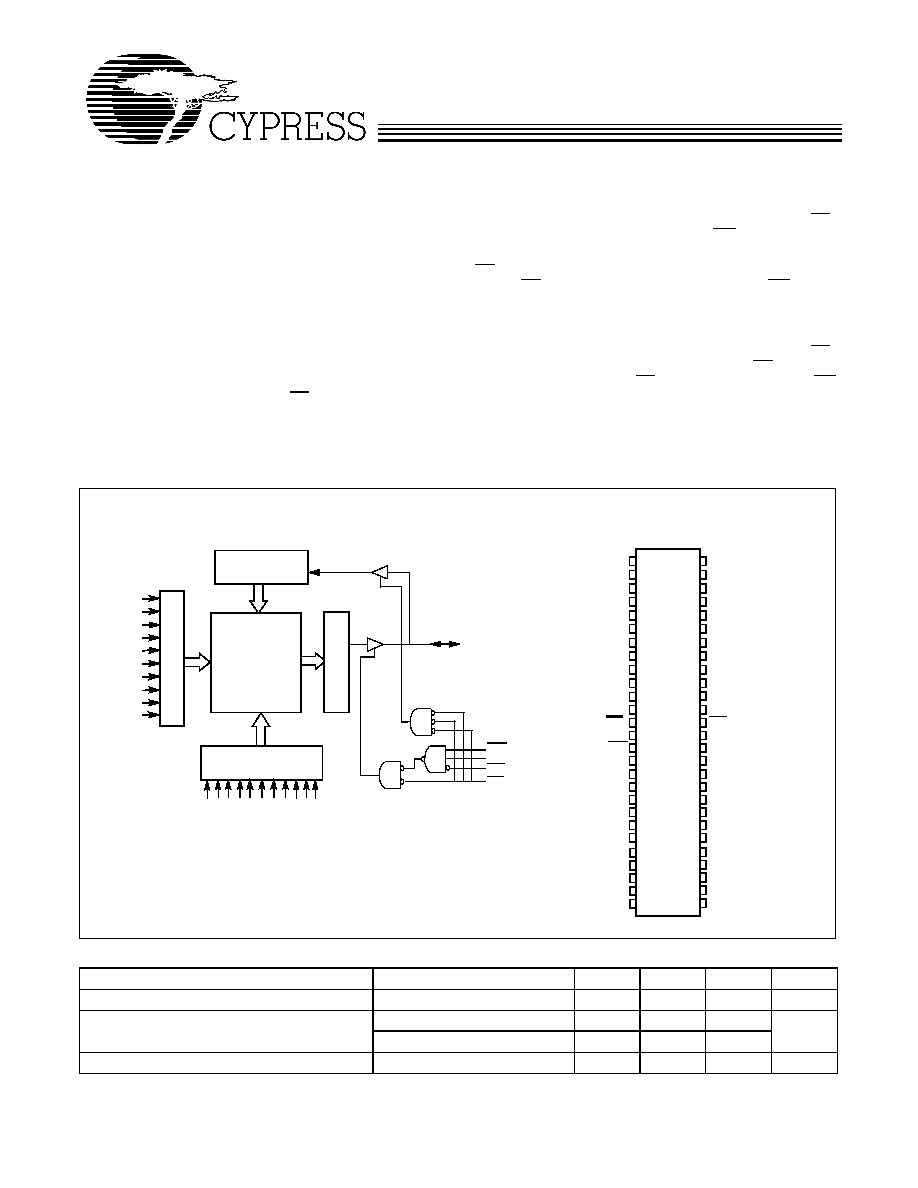

Logic Block Diagram

Pin Configuration

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

ROW DEC

O

DE

R

SE

NSE AM

PS

INPUT BUFFER

2M x 8

ARRAY

A

0

A

12

A

14

A

13

A

A

A

17

A

18

A

10

A

11

4096 x 4096

I/O

0

≠I/O

7

OE

CE

2

WE

CE

1

Top View

TSOP II

WE

1

2

3

4

5

6

7

8

9

10

11

14

31

32

36

35

34

33

37

40

39

38

12

13

41

43

42

16

15

29

30

A

5

A

6

A

7

A

8

A

0

A

1

OE

V

SS

A

17

I/O

7

A

2

CE

1

I/O

0

I/O

1

A

3

A

4

18

17

20

19

27

28

25

26

22

21

23

24

I/O

2

I/O

3

A

16

A

15

V

CC

I/O

6

NC

I/O

5

I/O

4

A

14

A

13

A

12

A

11

A

9

A

10

CE

2

44

46

45

47

50

49

48

51

53

52

54

V

SS

V

CC

A

19

A

18

V

CC

V

CC

V

SS

DNU

V

SS

NC

V

CC

V

SS

A

9

A

19

A

20

NC

NC

NC

NC

NC

NC

NC

NC

A

20

CY7C1069AV33

Document #: 38-05255 Rev. *D

Page 2 of 9

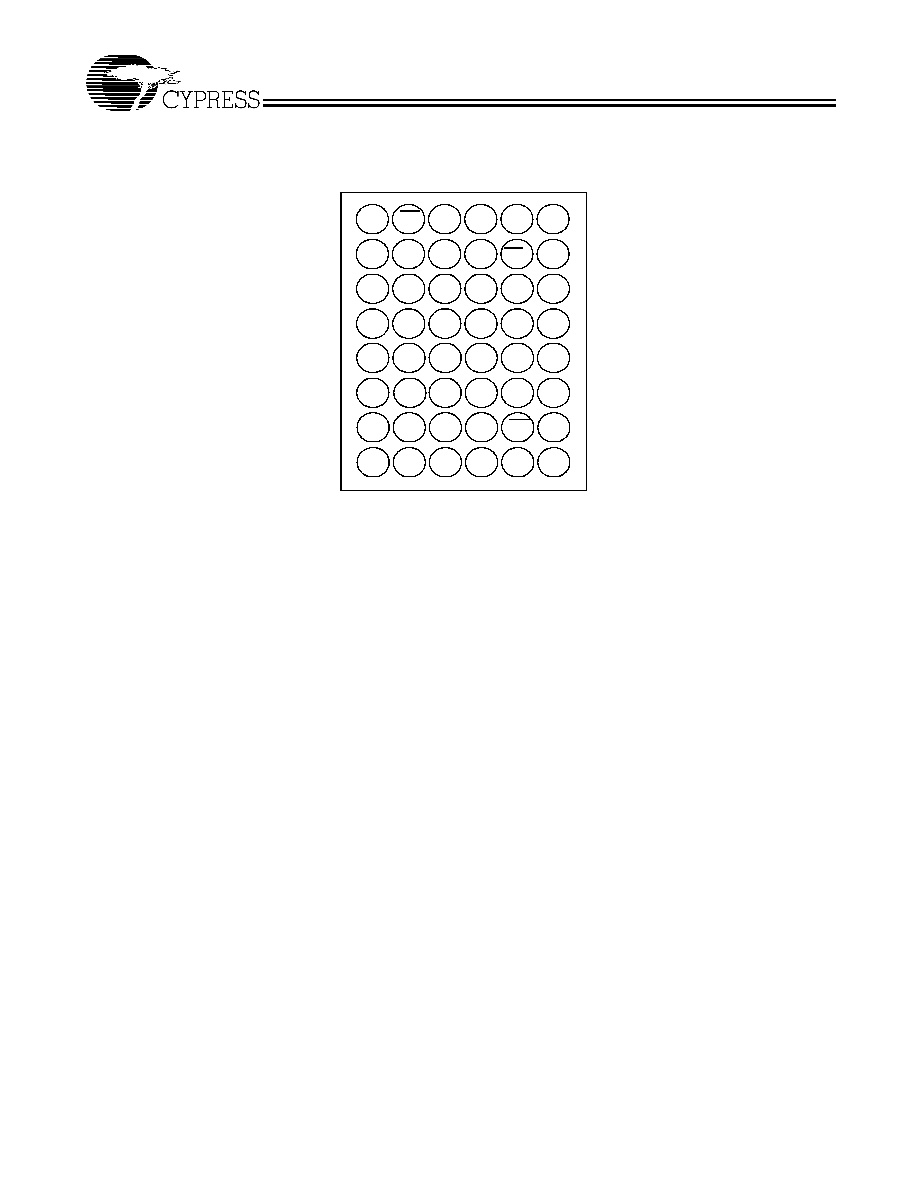

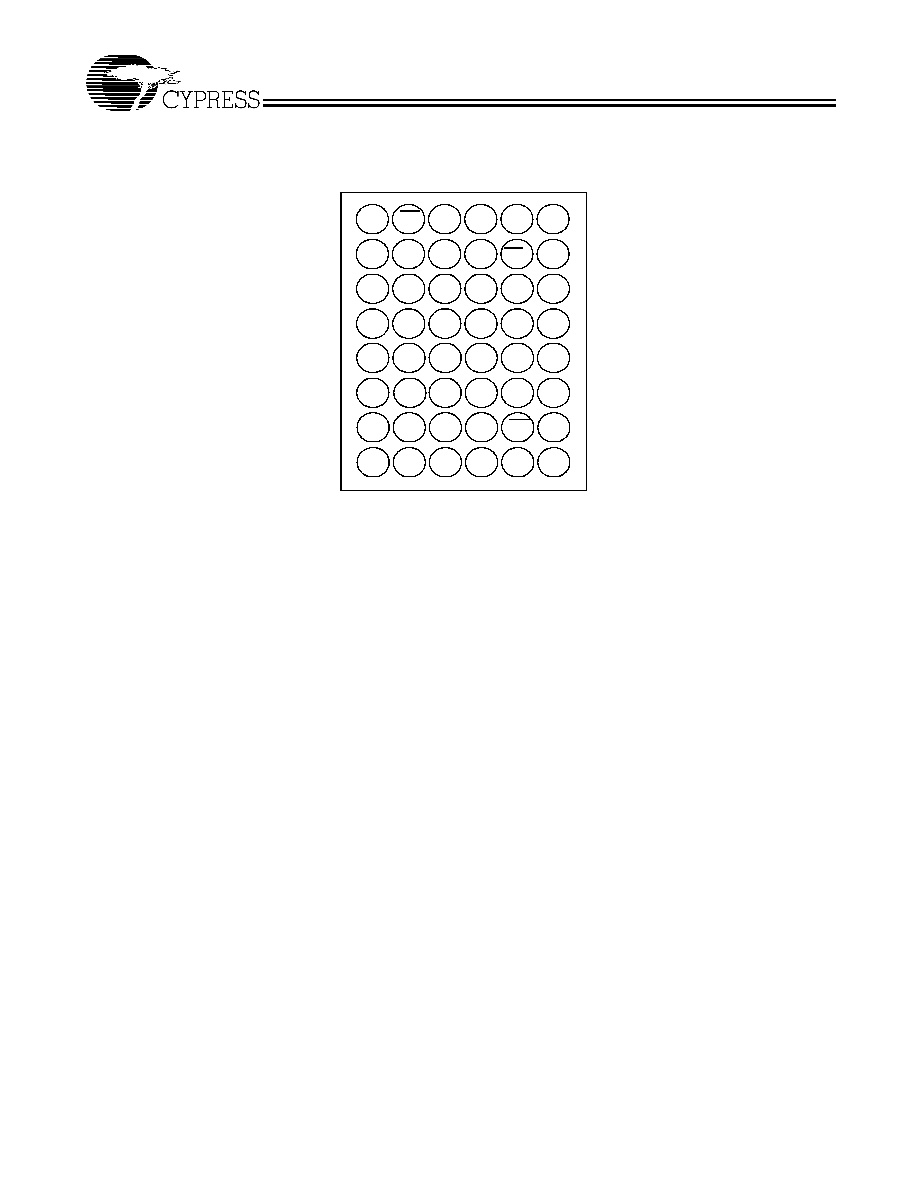

Pin Configurations

48-ball FBGA

WE

V

CC

A11

A10

A6

A0

A3

CE1

I/O0

A4

A5

I/O1

I/O2

I/O3

NC

V

SS

A9

A8

OE

V

SS

A7

NC

CE2

A17

A2

A1

VCC

I/O4

I/O5

I/O6

I/O7

NC

A15

A14

A13

A12

DNU

3

2

6

5

4

1

D

E

B

A

C

F

G

H

(Top View)

A16

A19

A20

NC

NC

NC

NC

A18

NC

NC

NC

CY7C1069AV33

Document #: 38-05255 Rev. *D

Page 3 of 9

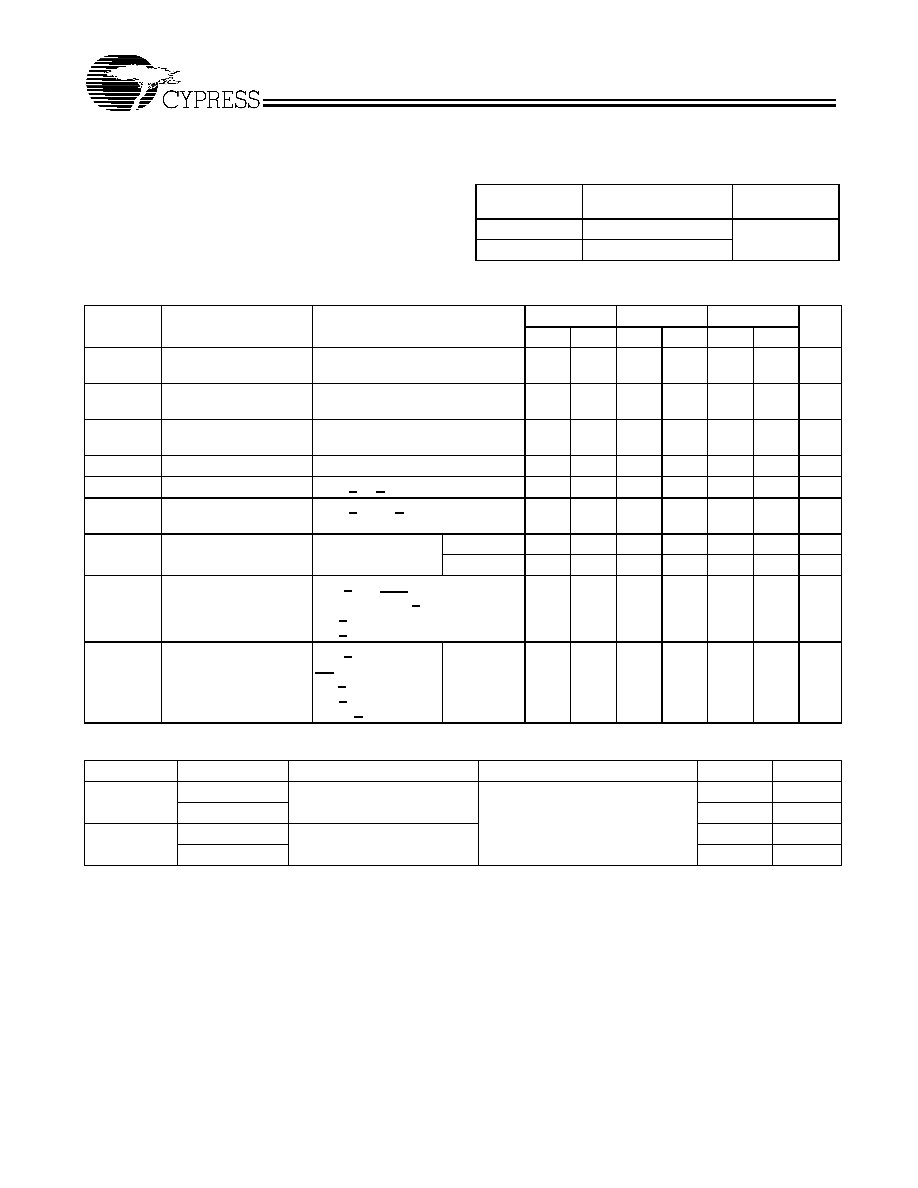

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature .................................≠65

∞

C to +150

∞

C

Ambient Temperature with

Power Applied............................................. ≠55

∞

C to +125

∞

C

Supply Voltage on V

CC

to Relative GND

[1]

.... ≠0.5V to +4.6V

DC Voltage Applied to Outputs

in High-Z State

[1]

....................................≠0.5V to V

CC

+ 0.5V

DC Input Voltage

[1]

................................ ≠0.5V to V

CC

+ 0.5V

Current into Outputs (LOW)......................................... 20 mA

Operating Range

Range

Ambient

Temperature

V

CC

Commercial

0

∞

C to +70

∞

C

3.3V

±

0.3V

Industrial

≠40

∞

C to +85

∞

C

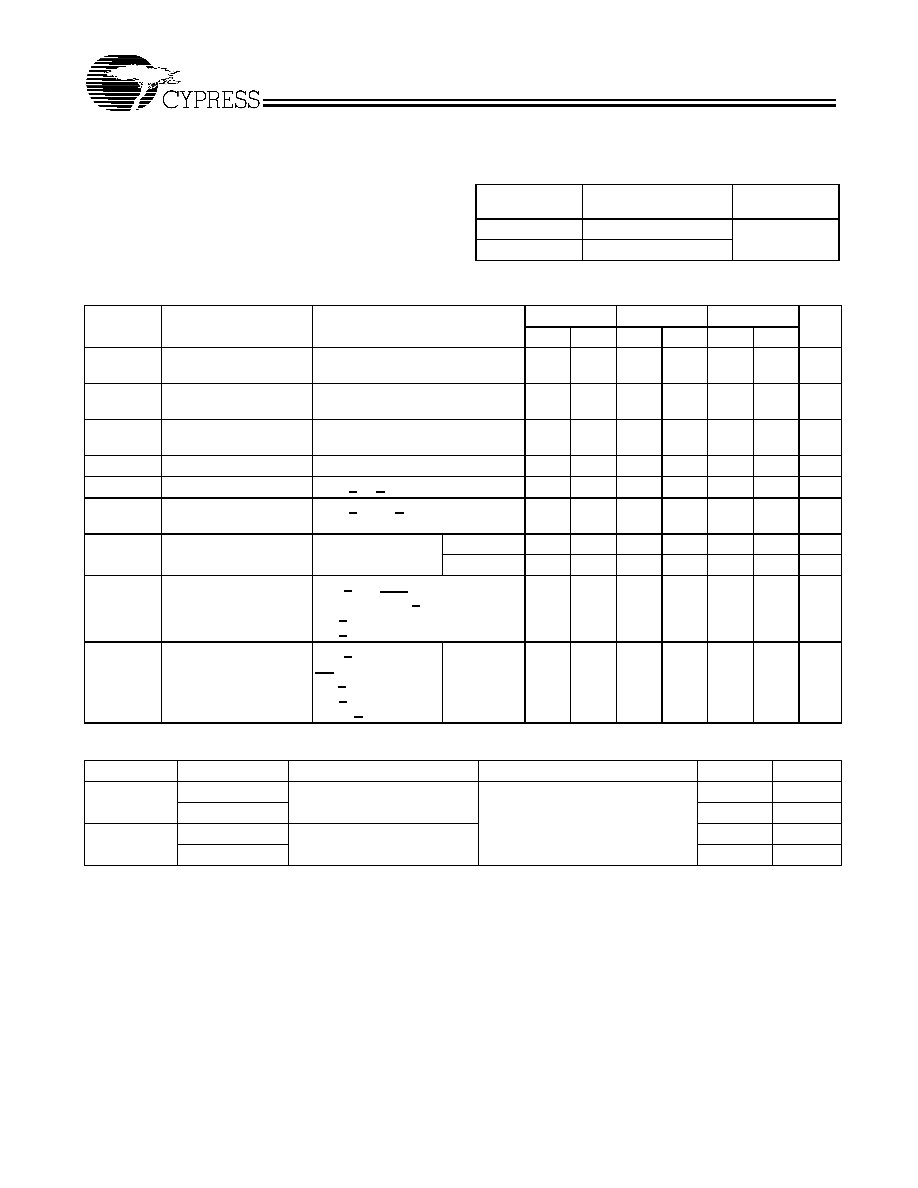

DC Electrical Characteristics

Over the Operating Range

Parameter

Description

Test Conditions

≠8

≠10

≠12

Unit

Min.

Max.

Min.

Max.

Min.

Max.

V

OH

Output HIGH Voltage

V

CC

= Min.,

I

OH

= ≠4.0 mA

2.4

2.4

2.4

V

V

OL

Output LOW Voltage

V

CC

= Min.,

I

OL

= 8.0 mA

0.4

0.4

0.4

V

V

IH

Input HIGH Voltage

2.0

V

CC

+ 0.3

2.0

V

CC

+ 0.3

2.0

V

CC

+ 0.3

V

V

IL

Input LOW Voltage

[1]

≠0.3

0.8

≠0.3

0.8

≠0.3

0.8

V

I

IX

Input Load Current

GND < V

I

< V

CC

≠1

+1

≠1

+1

≠1

+1

µ

A

I

OZ

Output Leakage Current GND < V

OUT

< V

CC

, Output

Disabled

≠1

+1

≠1

+1

≠1

+1

µ

A

I

CC

V

CC

Operating

Supply Current

V

CC

= Max., f = f

MAX

= 1/t

RC

Commercial

300

275

260

mA

Industrial

300

275

260

mA

I

SB1

Automatic CE

Power-down Current

--TTL Inputs

CE

2

< V

IL

,

Max. V

CC

, SCE > V

IH

V

IN

> V

IH

or

V

IN

< V

IL

, f = f

MAX

70

70

70

mA

I

SB2

Automatic CE

Power-down Current

--CMOS Inputs

CE

2

< 0.3V

Max. V

CC

,

CE > V

CC

≠ 0.3V,

V

IN

> V

CC

≠ 0.3V,

or V

IN

< 0.3V, f = 0

Commercial/

Industrial

50

50

50

mA

Capacitance

[2]

Parameter

Package

Description

Test Conditions

Max.

Unit

C

IN

Z54

Input Capacitance

T

A

= 25

∞

C, f = 1 MHz, V

CC

= 3.3V

6

pF

BA48

8

pF

C

OUT

Z54

I/O Capacitance

8

pF

BA48

10

pF

Notes:

1.

V

IL

(min.) = ≠2.0V for pulse durations of less than 20 ns.

2.

Tested initially and after any design or process changes that may affect these parameters.

CY7C1069AV33

Document #: 38-05255 Rev. *D

Page 4 of 9

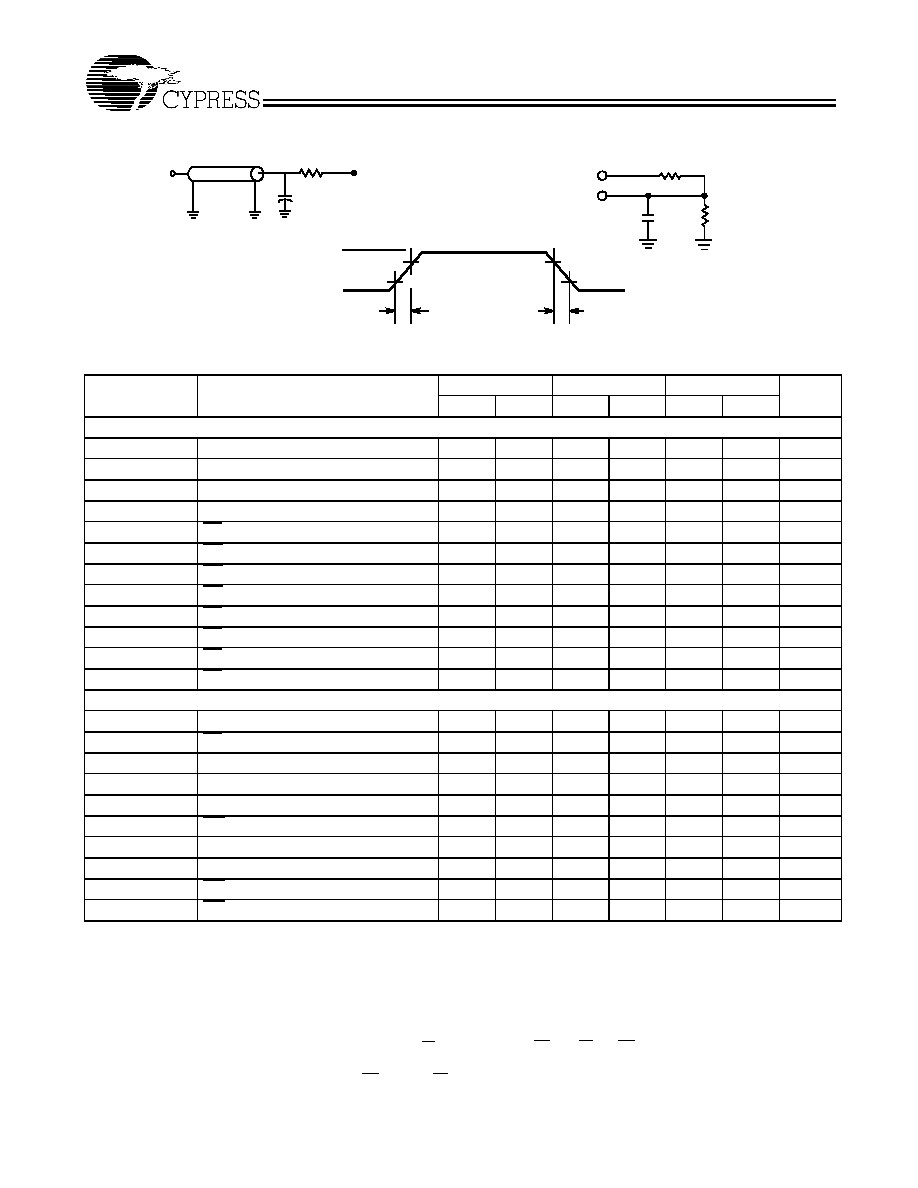

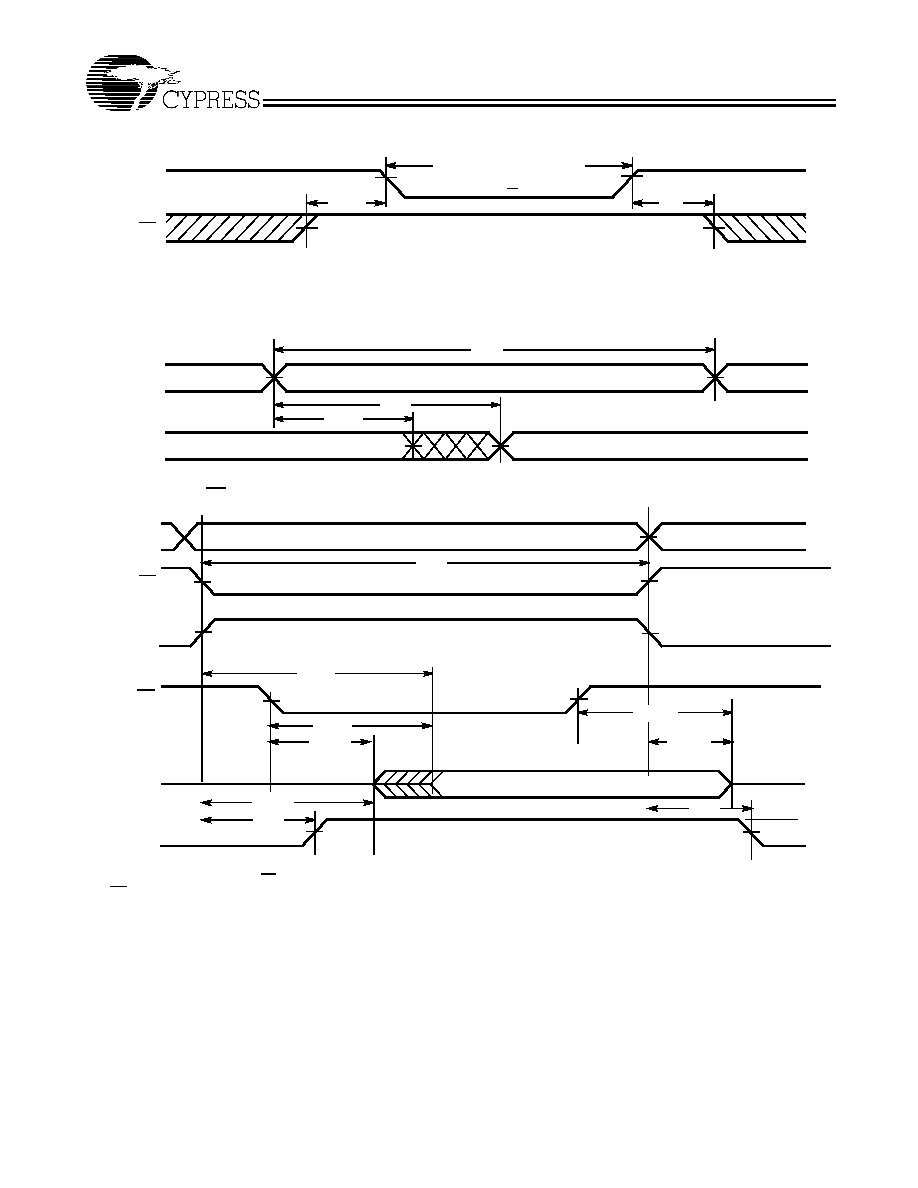

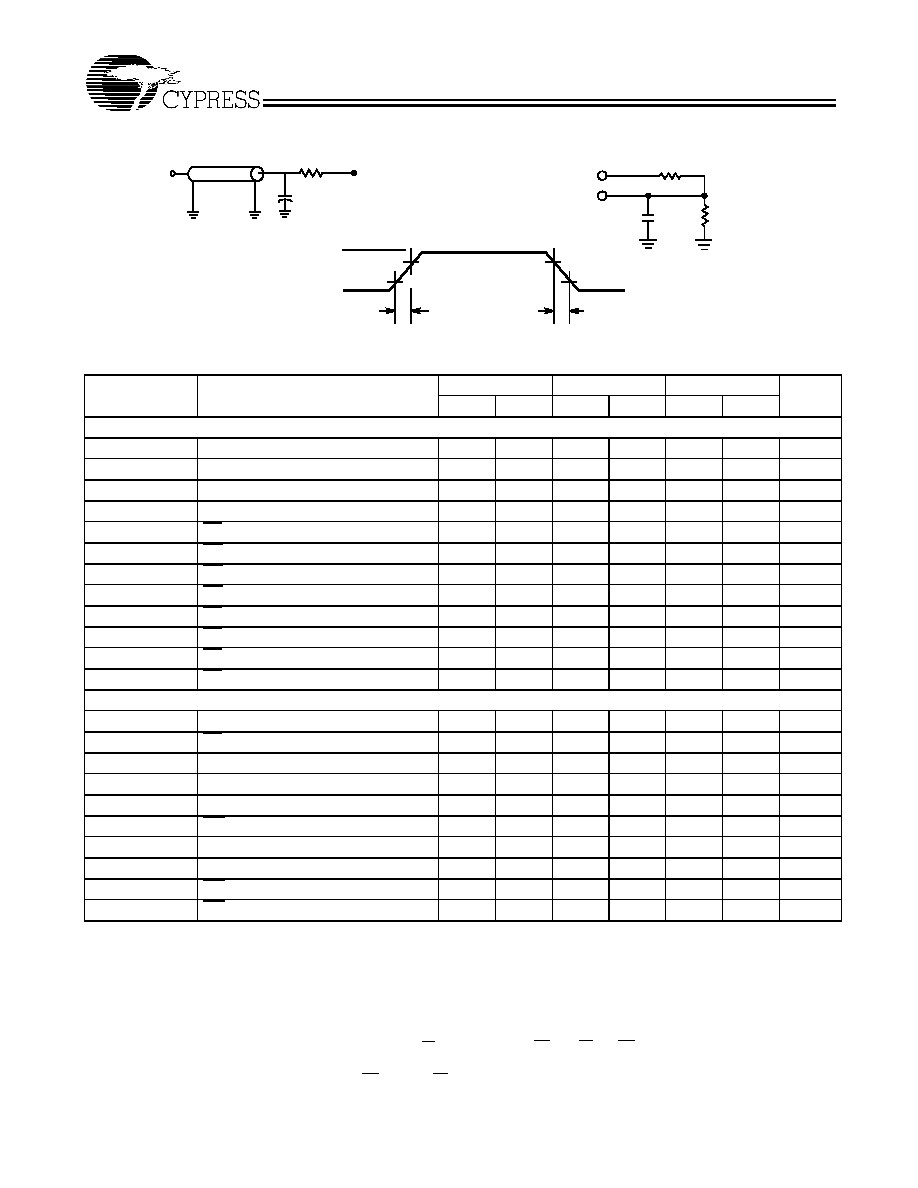

AC Test Loads and Waveforms

[3]

AC Switching Characteristics

Over the Operating Range

[4]

Parameter

Description

≠8

≠10

≠12

Unit

Min.

Max.

Min.

Max.

Min.

Max.

Read Cycle

t

power

V

CC

(typical) to the First Access

[5]

1

1

1

ms

t

RC

Read Cycle Time

8

10

12

ns

t

AA

Address to Data Valid

10

10

12

ns

t

OHA

Data Hold from Address Change

3

3

3

ns

t

ACE

CE

1

LOW/CE

2

HIGH to Data Valid

8

10

12

ns

t

DOE

OE LOW to Data Valid

5

5

6

ns

t

LZOE

OE LOW to Low-Z

[6]

1

1

1

ns

t

HZOE

OE HIGH to High-Z

[6]

5

5

6

ns

t

LZCE

CE

1

LOW/CE

2

HIGH to Low-Z

[6]

3

3

3

ns

t

HZCE

CE

1

HIGH/CE

2

LOW to High-Z

[6]

5

5

6

ns

t

PU

CE

1

LOW/CE

2

HIGH to Power-up

[7]

0

0

0

ns

t

PD

CE

1

HIGH/CE

2

LOW to Power-down

[7]

8

10

12

ns

Write Cycle

[8, 9]

t

WC

Write Cycle Time

8

10

12

ns

t

SCE

CE

1

LOW/CE

2

HIGH to Write End

6

7

8

ns

t

AW

Address Set-up to Write End

6

7

8

ns

t

HA

Address Hold from Write End

0

0

0

ns

t

SA

Address Set-up to Write Start

0

0

0

ns

t

PWE

WE Pulse Width

6

7

8

ns

t

SD

Data Set-up to Write End

5

5.5

6

ns

t

HD

Data Hold from Write End

0

0

0

ns

t

LZWE

WE HIGH to Low-Z

[6]

3

3

3

ns

t

HZWE

WE LOW to High-Z

[6]

5

5

6

ns

Notes:

3.

Valid SRAM operation does not occur until the power supplies have reached the minimum operating V

DD

(3.0V). As soon as 1ms (T

power

) after reaching the

minimum operating V

DD

, normal SRAM operation can begin including reduction in V

DD

to the data retention (V

CCDR

, 2.0V) voltage.

4.

Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified

I

OL

/I

OH

and transmission line loads. Test conditions for the Read cycle use output loading shown in part a) of the AC test loads, unless specified otherwise.

5.

This part has a voltage regulator which steps down the voltage from 3V to 2V internally. t

power

time has to be provided initially before a Read/Write operation

is started.

6.

t

HZOE

, t

HZSCE

, t

HZWE

and t

LZOE

, t

LZCE

, and t

LZWE

are specified with a load capacitance of 5 pF as in (b) of AC Test Loads. Transition is measured

±

200 mV

from steady-state voltage.

7.

These parameters are guaranteed by design and are not tested.

8.

The internal Write time of the memory is defined by the overlap of

CE

1

LOW / CE

2

HIGH

, and WE LOW. CE

1

and WE must be LOW along with CE

2

HIGH to initiate

a Write, and the transition of any of these signals can terminate the Write. The input data set-up and hold timing should be referenced to the leading edge of

the signal that terminates the Write.

9.

The minimum Write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of t

HZWE

and t

SD

.

90%

10%

3.3V

GND

90%

10%

All input pulses

3.3V

OUTPUT

5 pF*

*Including

jig and

scope

(a)

(b)

R1 317

R2

351

Rise time > 1V/ns

Fall time:

> 1V/ns

(c)

OUTPUT

50

Z0= 50

V

TH

= 1.5V

30 pF*

*Capacitive Load consists of all

components of the test environment

CY7C1069AV33

Document #: 38-05255 Rev. *D

Page 5 of 9

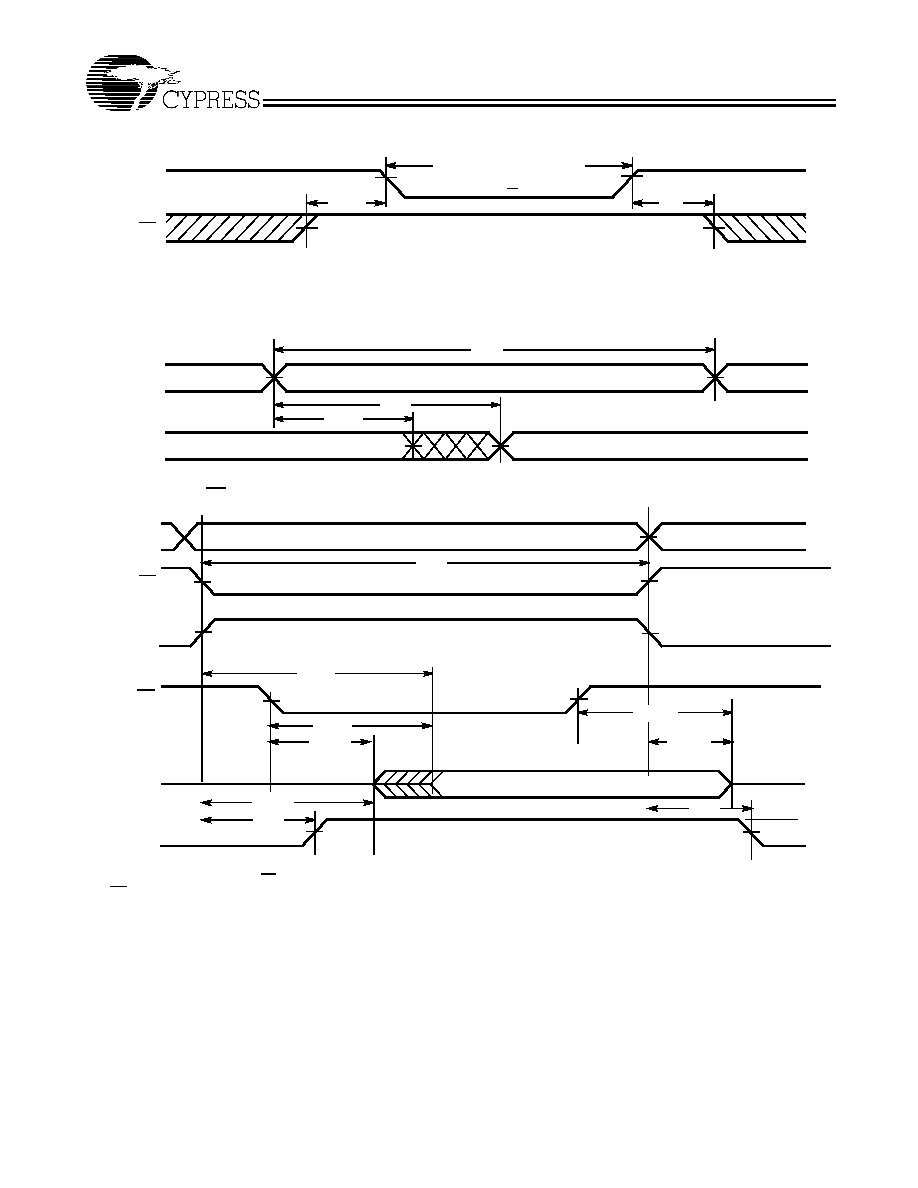

Data Retention Waveform

Switching Waveforms

Notes:

10. Device is continuously selected. CE

1

= V

IL

, CE

2

= V

IH

.

11. WE is HIGH for Read cycle.

3.0V

3.0V

t

CDR

V

DR

> 2V

DATA RETENTION MODE

t

R

CE

V

CC

Read Cycle No. 1

PREVIOUS DATA VALID

DATA VALID

t

RC

t

AA

t

OHA

ADDRESS

DATA OUT

[10, 11]

Read Cycle No. 2 (OE Controlled)

50%

50%

DATA VALID

t

RC

t

ASCE

t

DOE

t

LZOE

t

LZSCE

t

PU

HIGH IMPEDANCE

t

HZOE

t

PD

HIGH

OE

CE

1

IMPEDANCE

ADDRESS

DATA OUT

V

CC

SUPPLY

t

HZSCE

[11, 12]

CURRENT

I

CC

I

SB

CE

2