| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CY7C1324F | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

2-Mb (128K x 18) Flow-Through Sync SRAM

CY7C1324F

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

,

CA 95134

∑

408-943-2600

Document #: 38-05431 Rev. **

Revised January 29, 2004

Features

∑ 128K x 18 common I/O

∑ 3.3V ≠5% and +10% core power supply (V

DD

)

∑ 3.3V I/O supply (V

DDQ

)

∑ Fast clock-to-output times

-- 6.5 ns (133-MHz version)

-- 7.5 ns (117-MHz version)

∑ Provide high-performance 2-1-1-1 access rate

∑ User-selectable burst counter supporting Intel

Pentium

interleaved or linear burst sequences

∑ Separate processor and controller address strobes

∑ Synchronous self-timed write

∑ Asynchronous output enable

∑ Supports 3.3V I/O level

∑ Offered in JEDEC-standard 100-pin TQFP package

∑ "ZZ" Sleep Mode option

Functional Description

[1]

The CY7C1324F is a 131,072 x 18 synchronous cache RAM

designed to interface with high-speed microprocessors with

minimum glue logic. Maximum access delay from clock rise is

6.5 ns (133-MHz version). A 2-bit on-chip counter captures the

first address in a burst and increments the address automati-

cally for the rest of the burst access. All synchronous inputs

are gated by registers controlled by a positive-edge-triggered

Clock Input (CLK). The synchronous inputs include all

addresses, all data inputs, address-pipelining Chip Enable

(CE

1

), depth-expansion Chip Enables (CE

2

and

CE

3

), Burst

Control inputs (ADSC, ADSP, and ADV), Write Enables

(BW

[A:B]

, and BWE), and Global Write (GW). Asynchronous

inputs include the Output Enable (OE) and the ZZ pin.

The CY7C1324F allows either interleaved or linear burst

sequences, selected by the MODE input pin. A HIGH selects

an interleaved burst sequence, while a LOW selects a linear

burst sequence. Burst accesses can be initiated with the

Processor Address Strobe (ADSP) or the cache Controller

Address Strobe (ADSC) inputs. Address advancement is

controlled by the Address Advancement (ADV) input.

Addresses and chip enables are registered at rising edge of

clock when either Address Strobe Processor (ADSP) or

Address Strobe Controller (ADSC) are active. Subsequent

burst addresses can be internally generated as controlled by

the Advance pin (ADV).

The CY7C1324F operates from a +3.3V core power supply

while all outputs may operate with a +3.3V supply. All inputs

and outputs are JEDEC-standard JESD8-5-compatible.

Note:

1. For best-practices recommendations, please refer to the Cypress application note System Design Guidelines on www.cypress.com.

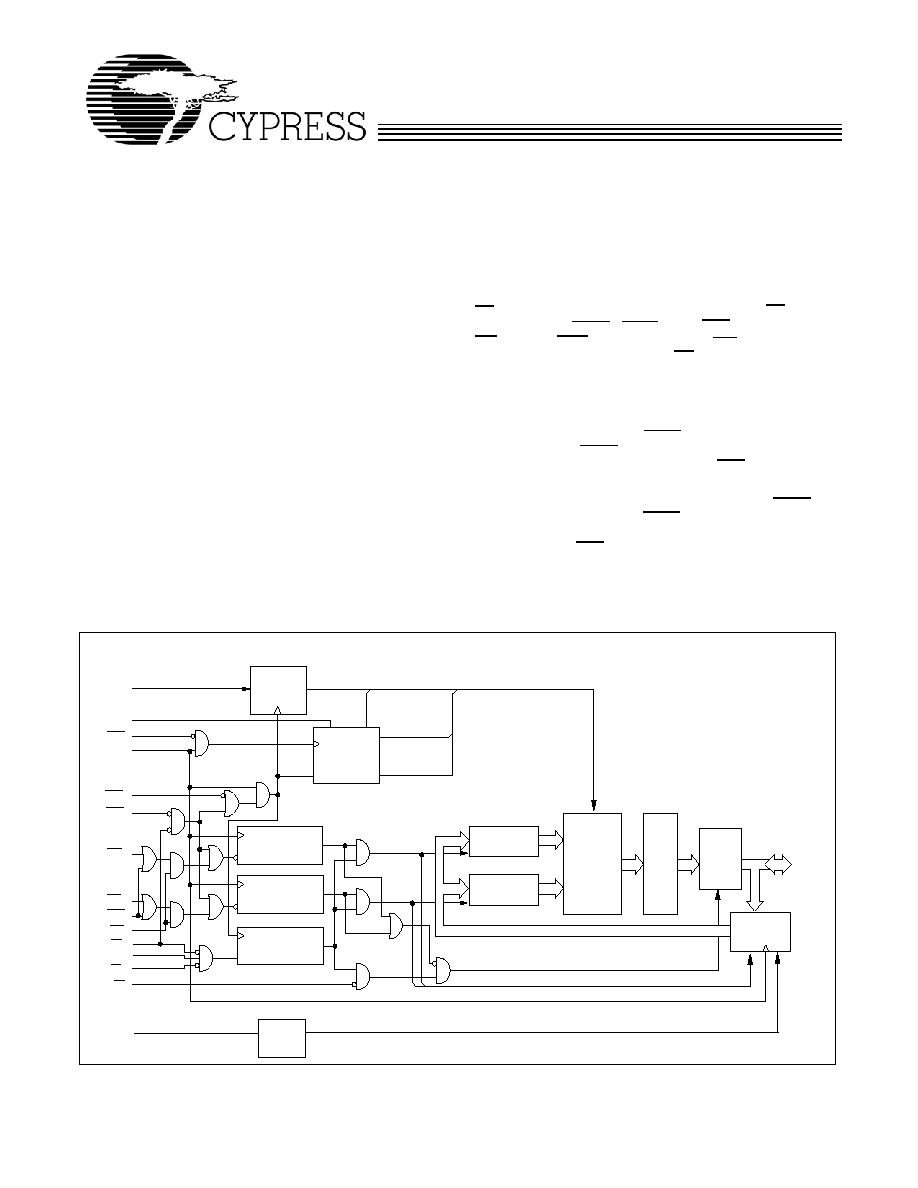

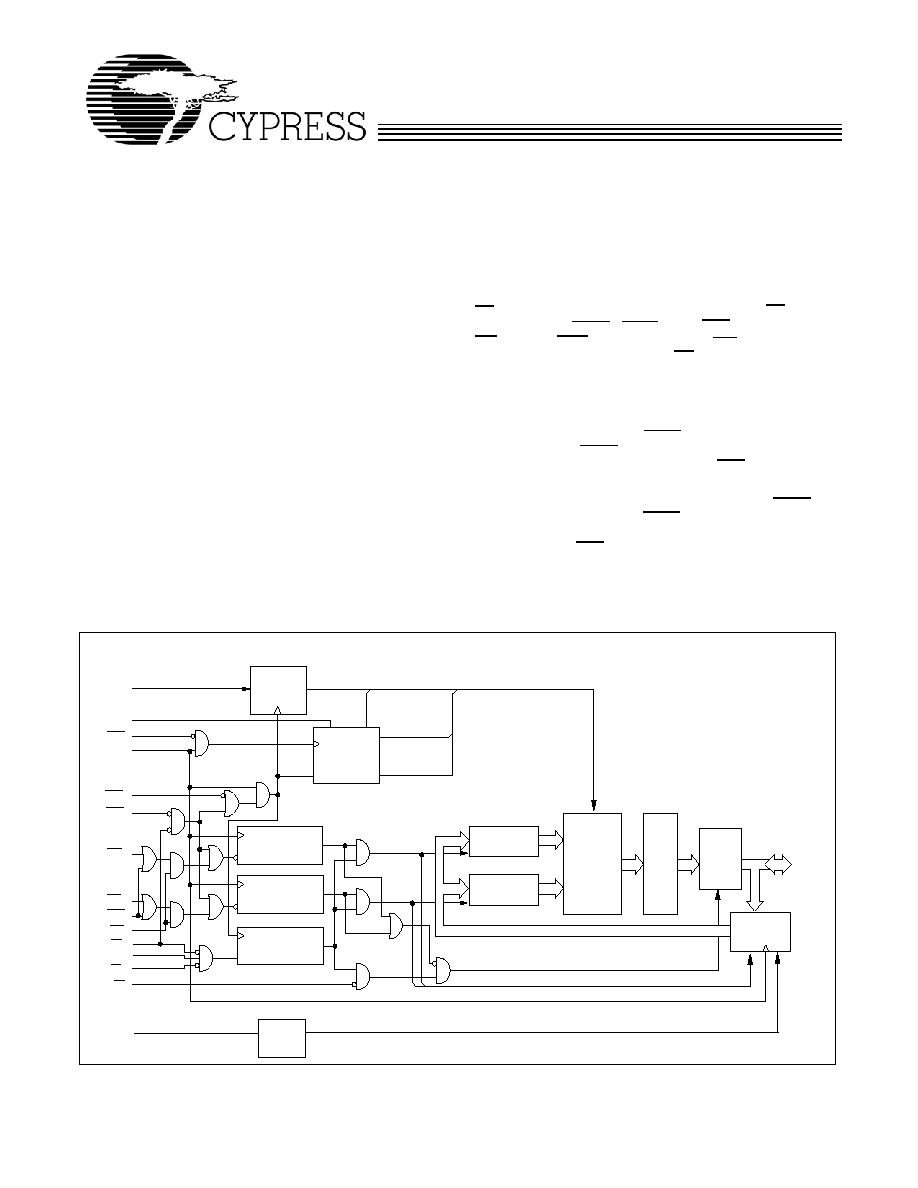

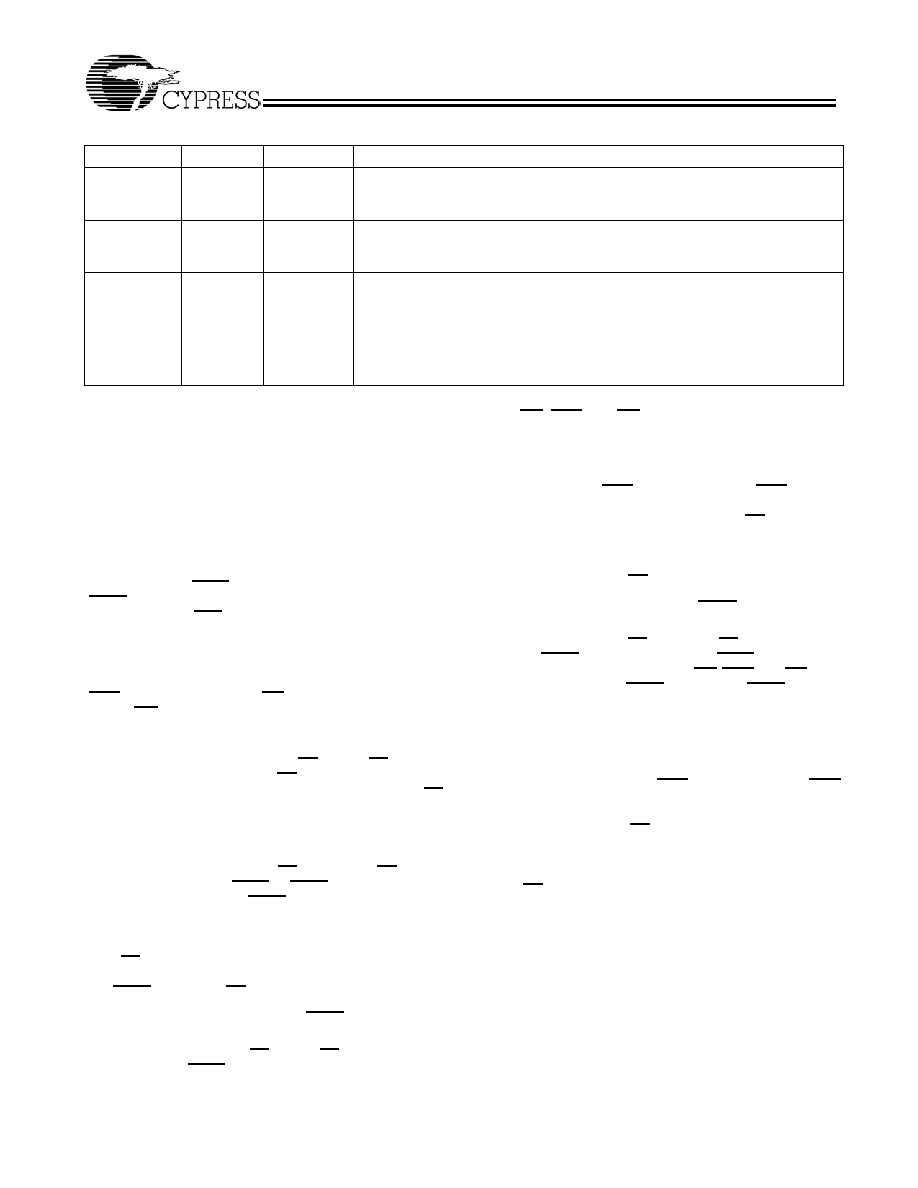

Logic Block Diagram

ADDRESS

REGISTER

ADV

CLK

BURST

COUNTER AND

LOGIC

CLR

Q1

Q0

ADSC

CE

1

OE

SENSE

AMPS

MEMORY

ARRAY

ADSP

OUTPUT

BUFFERS

INPUT

REGISTERS

MODE

CE

2

CE

3

GW

BWE

A0,A1,A

BW

B

BW

A

DQ

B

,DQP

B

WRITE REGISTER

DQ

A

,DQP

A

WRITE REGISTER

ENABLE

REGISTER

A[1:0]

DQs

DQP

A

DQP

B

DQ

B

,DQP

B

WRITE DRIVER

DQ

A

,DQP

A

WRITE DRIVER

SLEEP

CONTROL

ZZ

CY7C1324F

Document #: 38-05431 Rev. **

Page 2 of 15

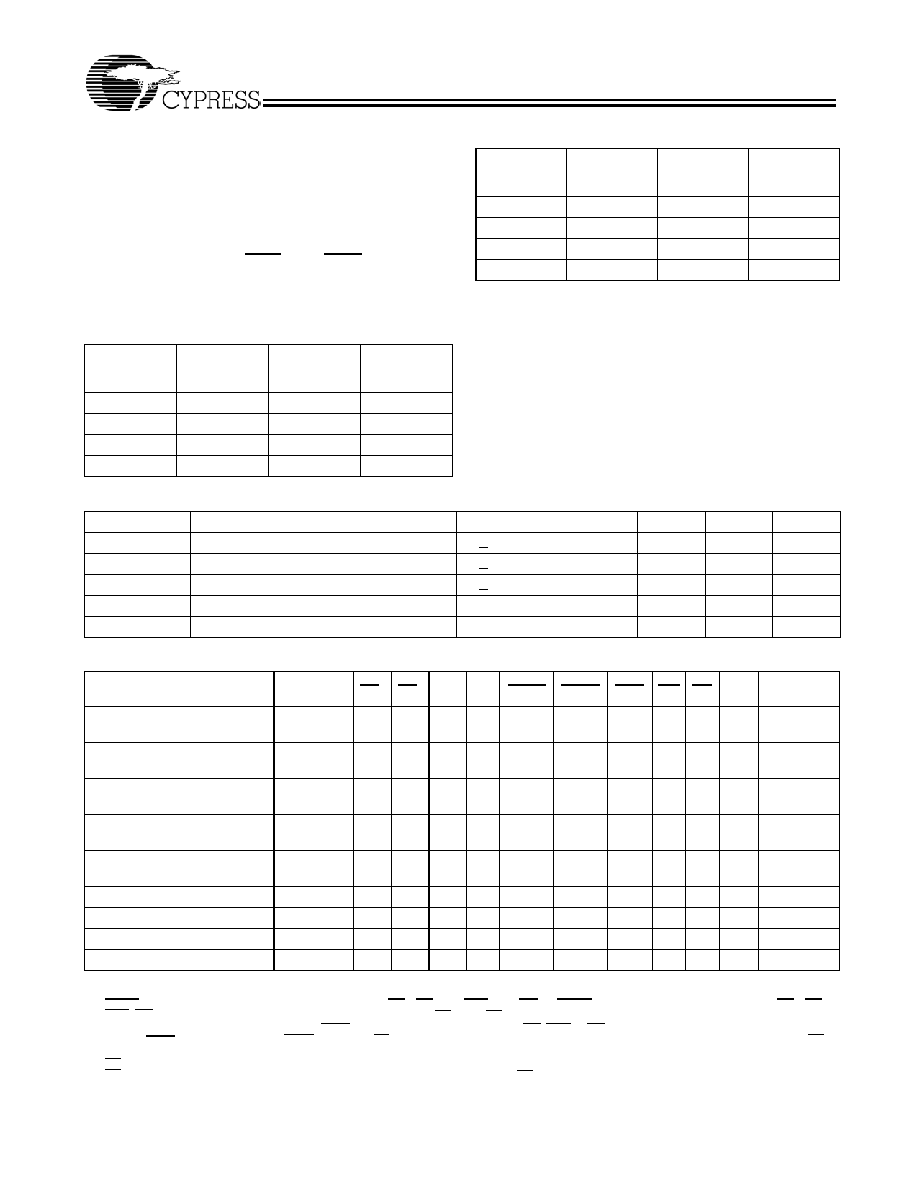

Selection Guide

133 MHz

117 MHz

Unit

Maximum Access Time

6.5

7.5

ns

Maximum Operating Current

225

220

mA

Maximum Standby Current

40

40

mA

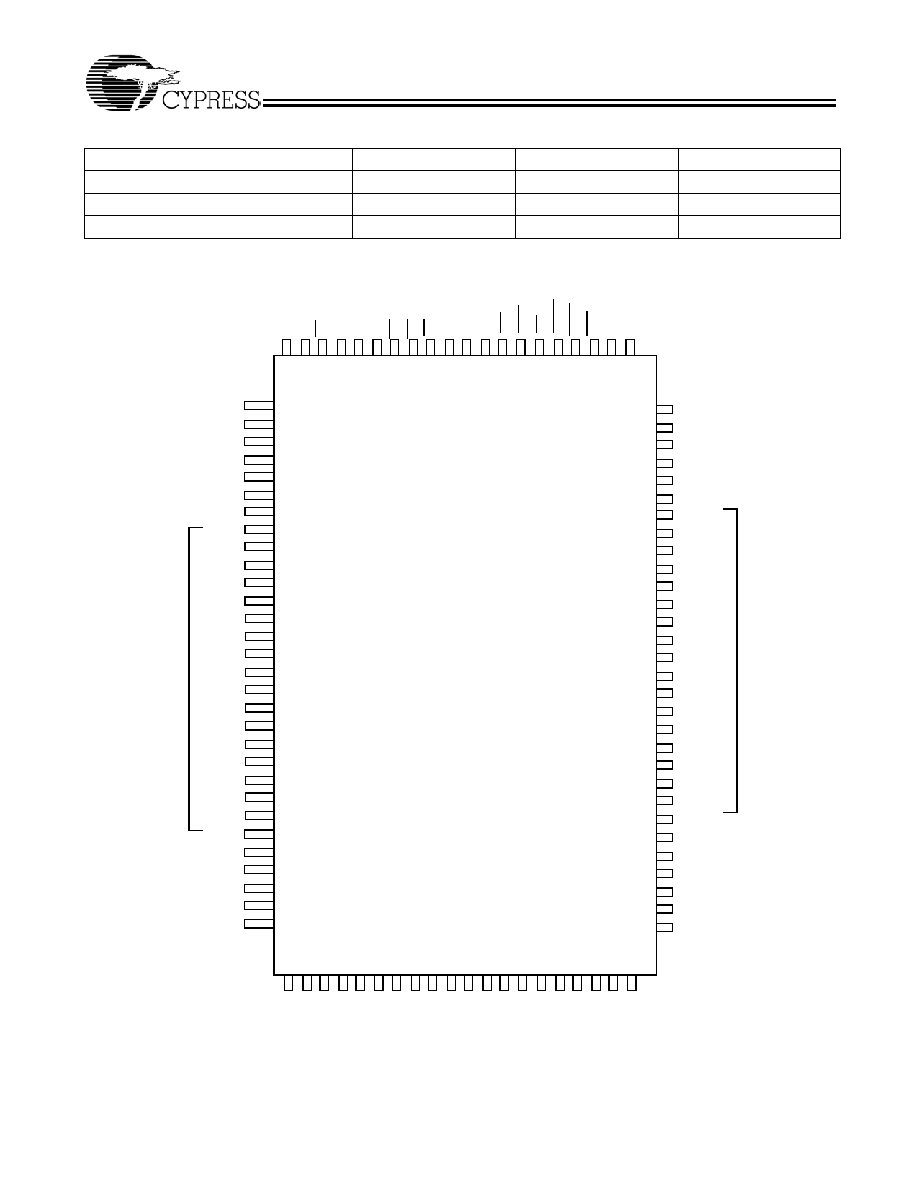

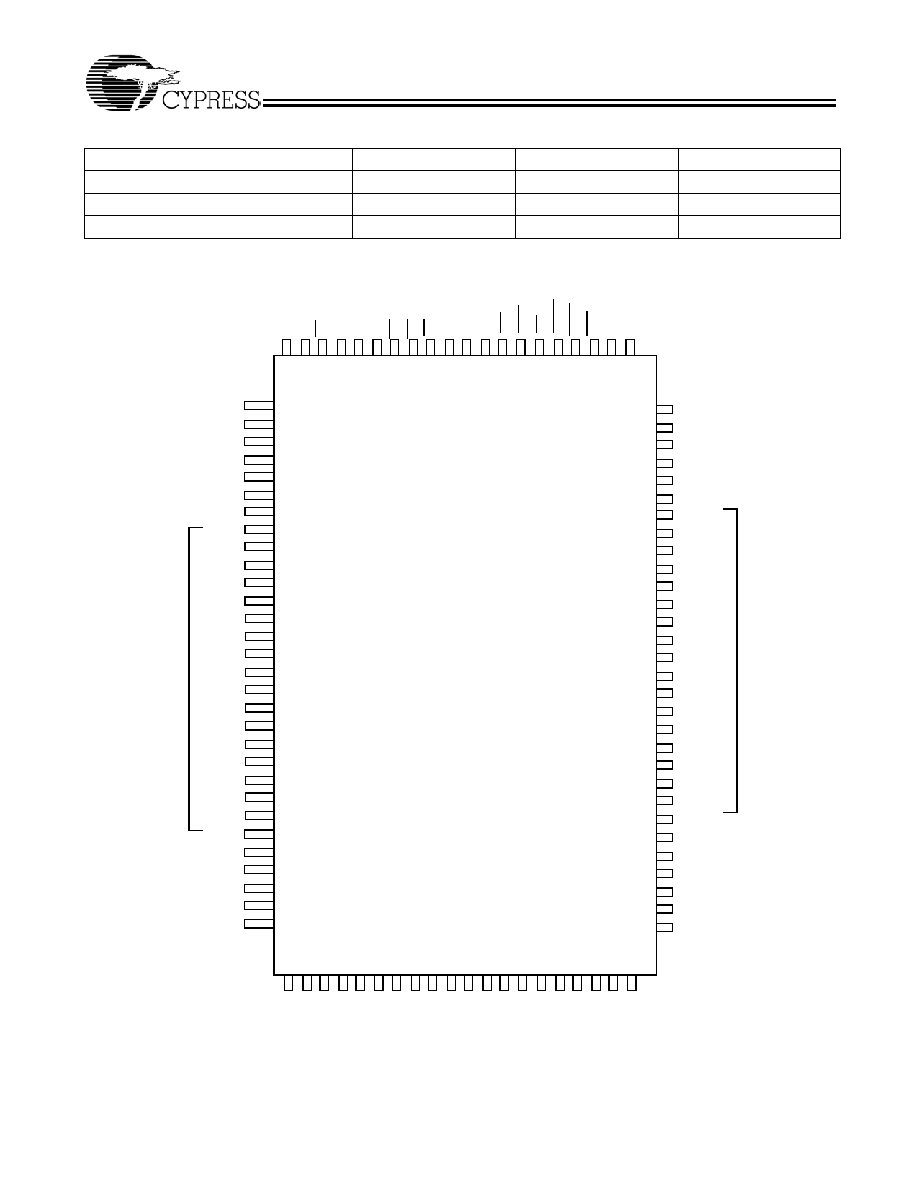

Pin Configurations

100-Pin TQFP

A

A

A

A

A

1

A

0

NC

NC

V

SS

V

DD

NC

A

A

A

A

A

NC

A

NC

V

DDQ

V

SS

NC

DQP

B

DQ

A

DQ

A

V

SS

V

DDQ

DQ

A

DQ

A

V

SS

NC

V

DD

DQ

A

DQ

A

V

DDQ

V

SS

DQ

A

DQ

A

NC

NC

V

SS

V

DDQ

NC

NC

NC

NC

NC

NC

V

DDQ

V

SS

NC

NC

DQ

B

DQ

B

V

SS

V

DDQ

DQ

B

DQ

B

NC

V

DD

NC

V

SS

DQ

B

DQ

B

V

DDQ

V

SS

DQ

B

DQ

B

DQP

B

NC

V

SS

V

DDQ

NC

NC

NC

A

A

CE

1

CE

2

NC

NC

BW

B

BW

A

CE

3

V

DD

V

SS

CLK

GW

BWE

OE

ADSP

A

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

BYTE A

A

ADV

ADSC

ZZ

MOD

E

NC

NC

BYTE B

CY7C1324F

CY7C1324F

Document #: 38-05431 Rev. **

Page 3 of 15

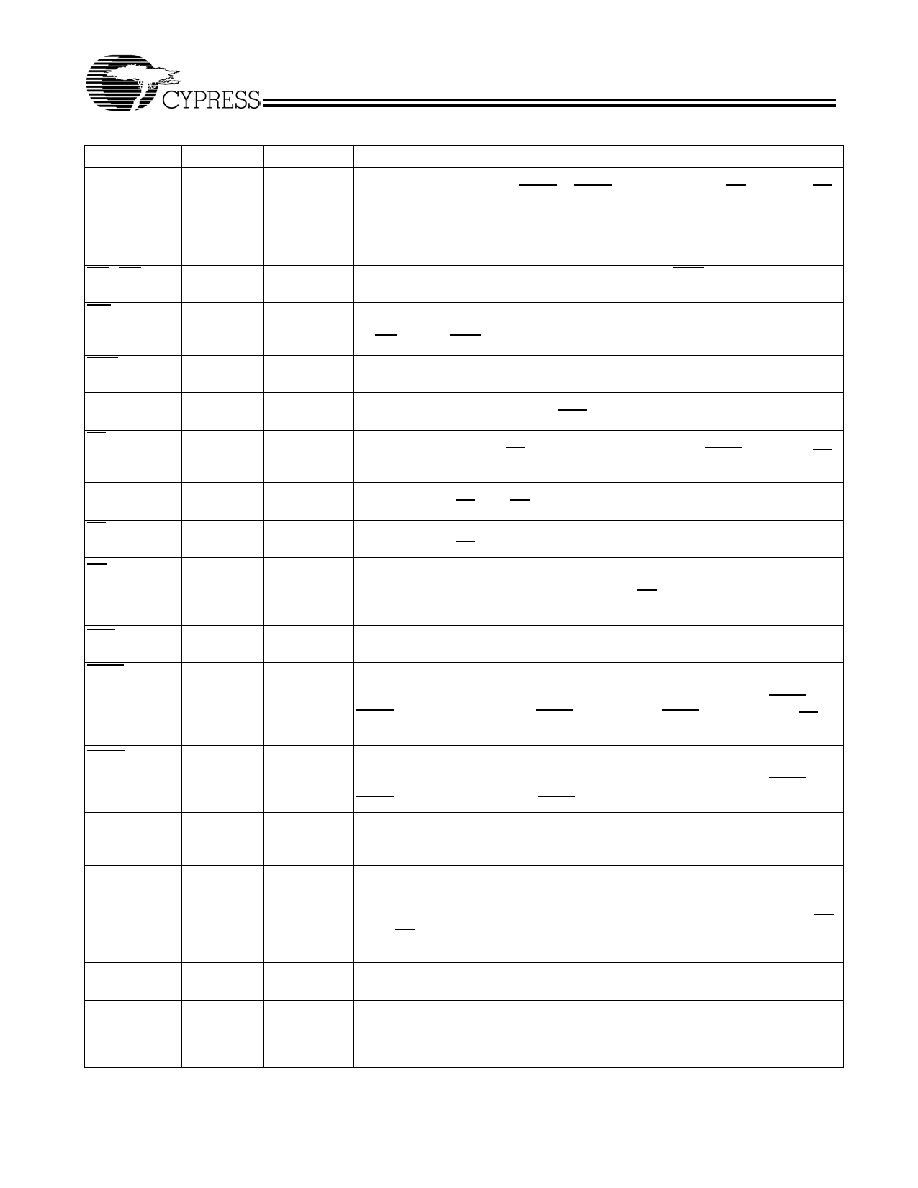

Pin Descriptions

Name

TQFP

I/O

Description

A0, A1, A

37,36,32,

33,34,35,

44,45,46,

47,48,49,80,

81,82,

99,100

Input-

Synchronous

Address Inputs used to select one of the 128K address locations. Sampled at

the rising edge of the CLK if ADSP or ADSC is active LOW, and CE

1

,

CE

2

, and

CE

3

are sampled active. A

[1:0]

feed the 2-bit counter.

BW

A,

BW

B

93,94,

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with BWE to conduct Byte Writes

to the SRAM. Sampled on the rising edge of CLK.

GW

88

Input-

Synchronous

Global Write Enable Input, active LOW. When asserted LOW on the rising edge

of CLK, a global Write is conducted (ALL bytes are written, regardless of the values

on BW

[A:B]

and BWE).

BWE

87

Input-

Synchronous

Byte Write Enable Input, active LOW. Sampled on the rising edge of CLK. This

signal must be asserted LOW to conduct a Byte Write.

CLK

89

Input-Clock Clock Input. Used to capture all synchronous inputs to the device. Also used to

increment the burst counter when ADV is asserted LOW, during a burst operation.

CE

1

98

Input-

Synchronous

Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in

conjunction with CE

2

and CE

3

to select/deselect the device. ADSP is ignored if CE

1

is HIGH.

CE

2

97

Input-

Synchronous

Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in

conjunction with CE

1

and CE

3

to select/deselect the device.

CE

3

92

Input-

Synchronous

Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in

conjunction with CE

1

and

CE

2

to select/deselect the device.

OE

86

Input-

Asynchronou

s

Output Enable, asynchronous input, active LOW. Controls the direction of the

I/O pins. When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O

pins are three-stated, and act as input data pins. OE is masked during the first clock

of a Read cycle when emerging from a deselected state.

ADV

83

Input-

Synchronous

Advance Input signal, sampled on the rising edge of CLK. When asserted, it

automatically increments the address in a burst cycle.

ADSP

84

Input-

Synchronous

Address Strobe from Processor, sampled on the rising edge of CLK, active

LOW. When asserted LOW, addresses presented to the device are captured in the

address registers. A

[1:0]

are also loaded into the burst counter. When ADSP and

ADSC are both asserted, only ADSP is recognized. ASDP is ignored when CE

1

is

deasserted HIGH

ADSC

85

Input-

Synchronous

Address Strobe from Controller, sampled on the rising edge of CLK, active

LOW. When asserted LOW, addresses presented to the device are captured in the

address registers. A

[1:0]

are also loaded into the burst counter. When ADSP and

ADSC are both asserted, only ADSP is recognized.

ZZ

64

Input-

Asynchronou

s

ZZ "sleep" Input, active HIGH. When asserted HIGH places the device in a

non-time-critical "sleep" condition with data integrity preserved. For normal

operation, this pin has to be LOW or left floating. ZZ pin has an internal pull-down.

DQs

DQP

A,

DQP

B

58,59,62,63,

68,69,72,

73,8,9,12,

13,18,19,22,

23

24,74

I/O-

Synchronous

Bidirectional Data I/O Lines. As inputs, they feed into an on-chip data register

that is triggered by the rising edge of CLK. As outputs, they deliver the data

contained in the memory location specified by the addresses presented during the

previous clock rise of the Read cycle. The direction of the pins is controlled by OE.

When OE is asserted LOW, the pins behave as outputs. When HIGH, DQs and

DQP

[A:B]

are placed in a three-state condition.

V

DD

15,41,

65, 91

Power

Supply

Power supply inputs to the core of the device.

V

SS

5,10,17,21,

26,40,55,60,

67,71,76,

90

Ground

Ground for the device.

CY7C1324F

Document #: 38-05431 Rev. **

Page 4 of 15

Functional Overview

All synchronous inputs pass through input registers controlled

by the rising edge of the clock. Maximum access delay from

the clock rise (t

CDV

) is 6.5 ns (133-MHz device).

The CY7C1324F supports secondary cache in systems

utilizing either a linear or interleaved burst sequence. The

interleaved burst order supports Pentium and i486TM

processors. The linear burst sequence is suited for processors

that utilize a linear burst sequence. The burst order is

user-selectable, and is determined by sampling the MODE

input. Accesses can be initiated with either the Processor

Address Strobe (ADSP) or the Controller Address Strobe

(ADSC). Address advancement through the burst sequence is

controlled by the ADV input. A two-bit on-chip wraparound

burst counter captures the first address in a burst sequence

and automatically increments the address for the rest of the

burst access.

Byte write operations are qualified with the Byte Write Enable

(BWE) and Byte Write Select (BW[A:B]) inputs. A Global Write

Enable (GW) overrides all byte write inputs and writes data to

all four bytes. All writes are simplified with on-chip

synchronous self-timed write circuitry.

Three synchronous Chip Selects (CE

1

, CE

2

, CE

3

) and an

asynchronous Output Enable (OE) provide for easy bank

selection and output tri-state control. ADSP is ignored if CE

1

is HIGH.

Single Read Accesses

A single read access is initiated when the following conditions

are satisfied at clock rise: (1) CE

1

, CE

2

, and CE

3

are all

asserted active, and (2) ADSP or ADSC is asserted LOW (if

the access is initiated by ADSC, the write inputs must be

deasserted during this first cycle). The address presented to

the address inputs is latched into the address register and the

burst counter/control logic and presented to the memory core.

If the OE input is asserted LOW, the requested data will be

available at the data outputs a maximum to t

CDV

after clock

rise. ADSP is ignored if CE

1

is HIGH.

Single Write Accesses Initiated by ADSP

This access is initiated when the following conditions are

satisfied at clock rise: (1) CE

1

, CE

2

, CE

3

are all asserted

active, and (2) ADSP is asserted LOW. The addresses

presented are loaded into the address register and the burst

inputs (GW, BWE, and BW[A:B]) are ignored during this first

clock cycle. If the write inputs are asserted active (see Write

Cycle Descriptions table for appropriate states that indicate a

Write) on the next clock rise, the appropriate data will be

latched and written into the device. Byte Writes are allowed.

During Byte Writes, BWA controls DQA and BWB controls

DQB. All I/Os are three-stated during a Byte Write. Since this

is a common I/O device, the asynchronous OE input signal

must be deasserted and the I/Os must be three-stated prior to

the presentation of data to DQs. As a safety precaution, the

data lines are three-stated once a write cycle is detected,

regardless of the state of OE.

Single Write Accesses Initiated by ADSC

This write access is initiated when the following conditions are

satisfied at clock rise: (1) CE

1

, CE

2

, and CE

3

are all asserted

active, (2) ADSC is asserted LOW, (3) ADSP is deasserted

HIGH, and (4) the write input signals (GW, BWE, and BW[A:B])

indicate a write access. ADSC is ignored if ADSP is active

LOW.

The addresses presented are loaded into the address register

and the burst counter/control logic and delivered to the

memory core. The information presented to DQ[A:D] will be

written into the specified address location. Byte Writes are

allowed. During Byte Writes, BWA controls DQA and BWB

controls DQB. All I/Os are three-stated when a Write is

detected, even a Byte Write. Since this is a common I/O

device, the asynchronous OE input signal must be deasserted

and the I/Os must be three-stated prior to the presentation of

data to DQs. As a safety precaution, the data lines are

three-stated once a Write cycle is detected, regardless of the

state of OE.

Burst Sequences

The CY7C1324F provides an on-chip two-bit wraparound

burst counter inside the SRAM. The burst counter is fed by

A

[1:0]

, and can follow either a linear or interleaved burst order.

The burst order is determined by the state of the MODE input.

A LOW on MODE will select a linear burst sequence. A HIGH

on MODE will select an interleaved burst order. Leaving

MODE unconnected will cause the device to default to an

interleaved burst sequence.

V

DDQ

4,11,20,

27,54,61,

70,77

I/O Power

Supply

Power supply for the I/O circuitry.

MODE

31

Input-

Static

Selects Burst Order. When tied to GND selects linear burst sequence. When tied

to V

DD

or left floating selects interleaved burst sequence. This is a strap pin and

should remain static during device operation. Mode Pin has an internal pull-up.

NC

1,2,3,6,714,

16,25,28,29,

30,38,39,

42,43,50,51,

52,53,56,

57,66,75,78,

79,95,96

No Connects. Not Internally connected to the die.

Pin Descriptions

(continued)

Name

TQFP

I/O

Description

CY7C1324F

Document #: 38-05431 Rev. **

Page 5 of 15

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ

places the SRAM in a power conservation "sleep" mode. Two

clock cycles are required to enter into or exit from this "sleep"

mode. While in this mode, data integrity is guaranteed.

Accesses pending when entering the "sleep" mode are not

considered valid nor is the completion of the operation

guaranteed. The device must be deselected prior to entering

the "sleep" mode. CEs, ADSP, and ADSC must remain

inactive for the duration of t

ZZREC

after the ZZ input returns

LOW.

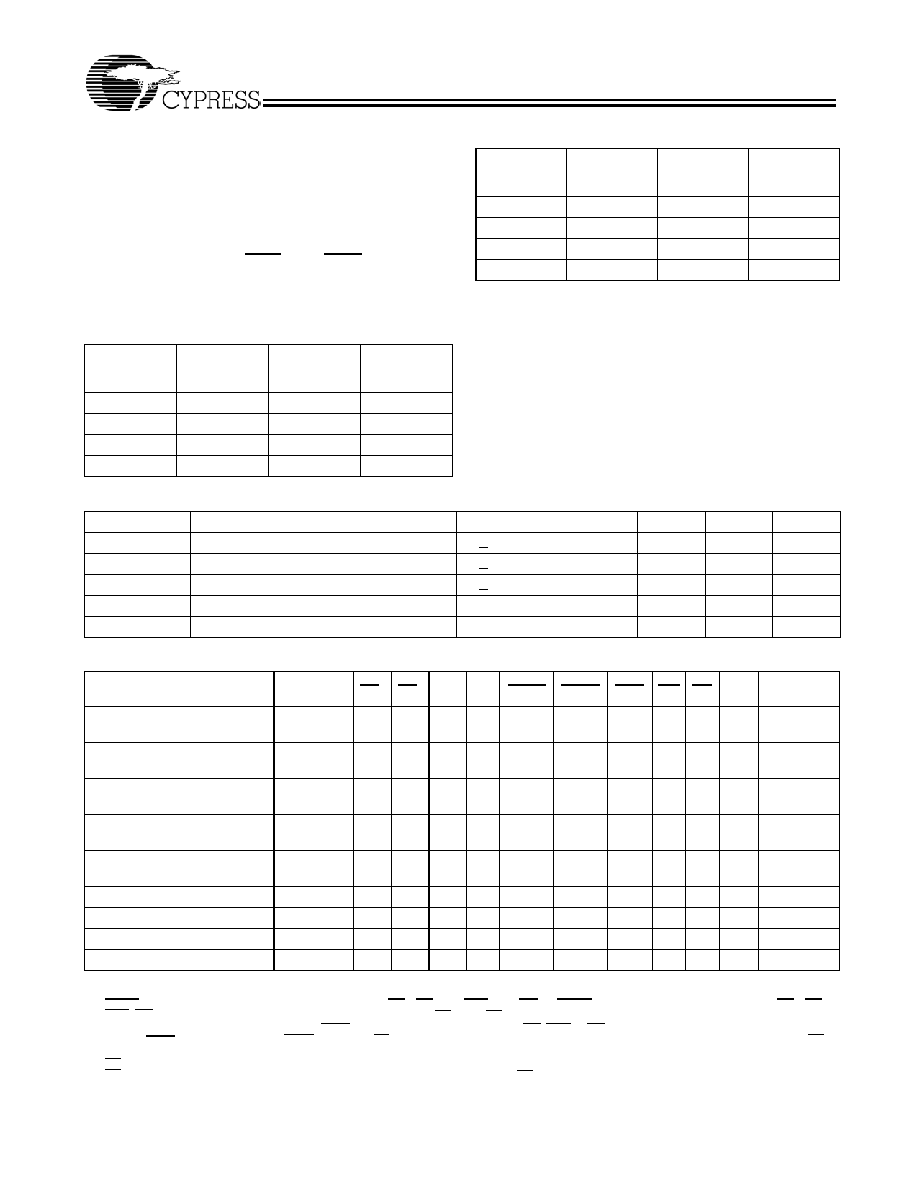

Interleaved Burst Address Table

(MODE = Floating or V

DD

)

First

Address

A1, A0

Second

Address

A1, A0

Third

Address

A1, A0

Fourth

Address

A1, A0

00

01

10

11

01

00

11

10

10

11

00

01

11

10

01

00

Linear Burst Address Table (MODE = GND)

First

Address

A

1

,

A

0

Second

Address

A

1

,

A

0

Third

Address

A

1

,

A

0

Fourth

Address

A

1

,

A

0

00

01

10

11

01

10

11

00

10

11

00

01

11

00

01

10

ZZ Mode Electrical Characteristics

Parameter

Description

Test Conditions

Min.

Max.

Unit

I

DDZZ

Snooze mode standby current

ZZ > V

DD

≠ 0.2V

40

mA

t

ZZS

Device operation to ZZ

ZZ > V

DD

≠ 0.2V

2t

CYC

ns

t

ZZREC

ZZ recovery time

ZZ < 0.2V

2t

CYC

ns

t

ZZI

ZZ Active to snooze current

This parameter is sampled

2t

CYC

ns

t

RZZI

ZZ Inactive to exit snooze current

This parameter is sampled

0

ns

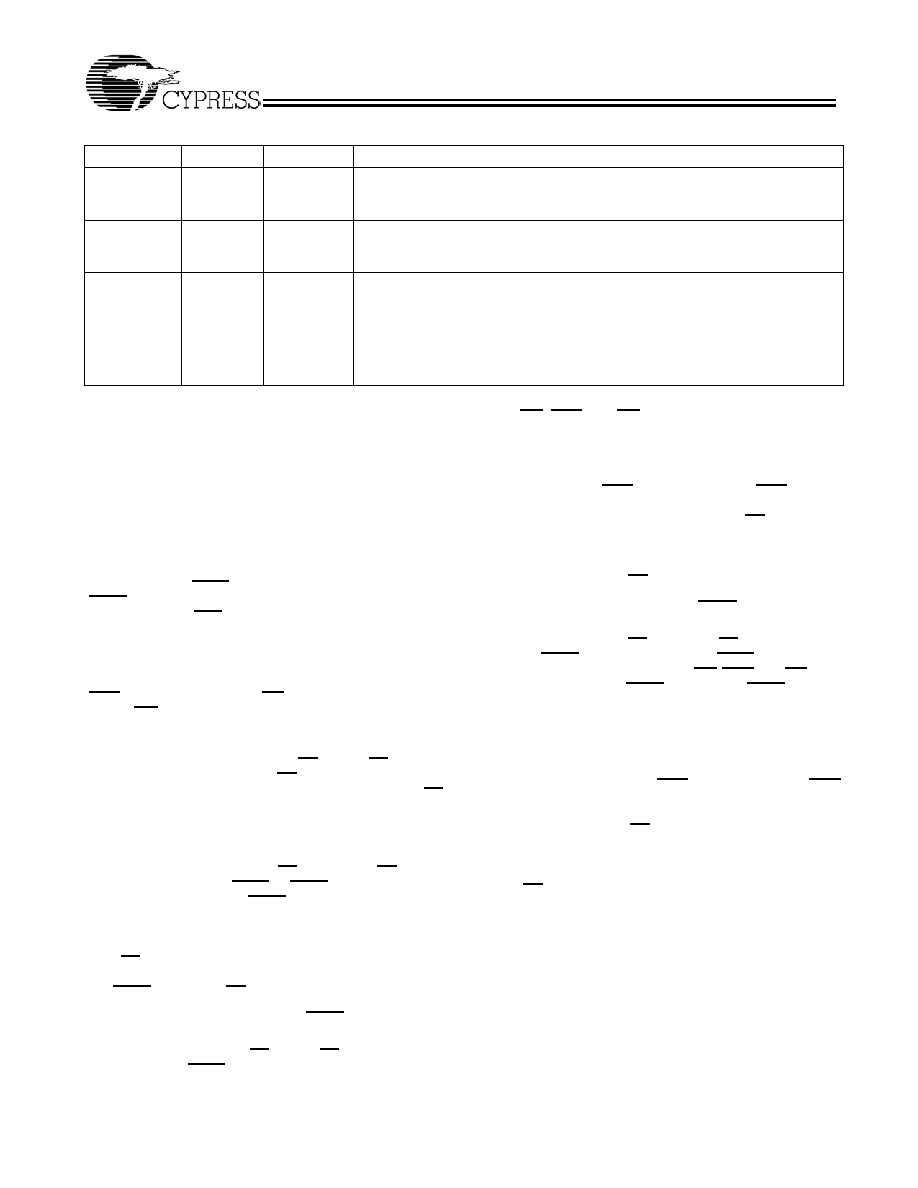

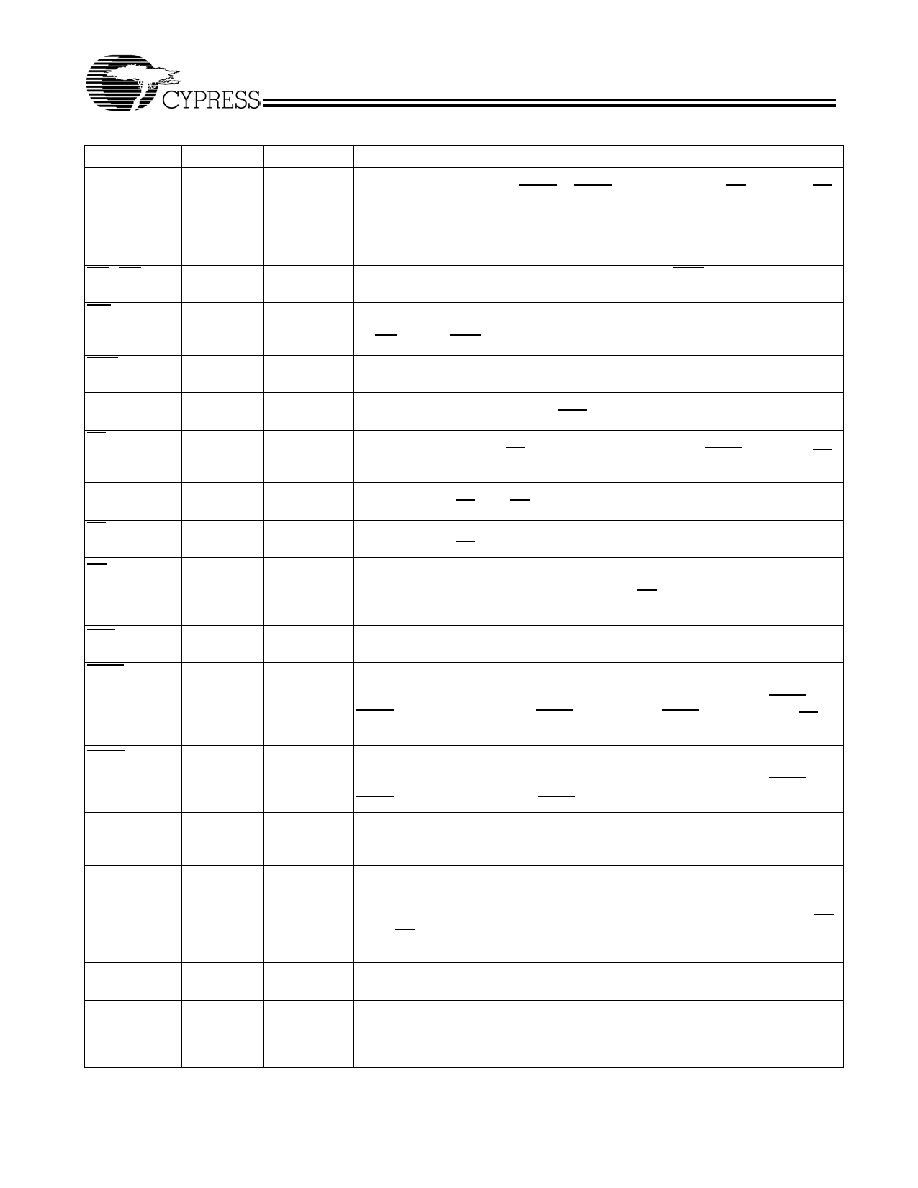

Truth Table

[2, 3, 4, 5]

Cycle Description

ADDRESS

Used

CE

1

CE

3

CE

2

ZZ

ADSP

ADSC

ADV WE OE CLK

DQ

Deselected Cycle,

Power-down

None

H

X

X

L

X

L

X

X

X

L-H Three-State

Deselected Cycle,

Power-down

None

L

X

L

L

L

X

X

X

X

L-H Three-State

Deselected Cycle,

Power-down

None

L

H

X

L

L

X

X

X

X

L-H Three-State

Deselected Cycle,

Power-down

None

L

X

L

L

H

L

X

X

X

L-H Three-State

Deselected Cycle,

Power-down

None

X

X

X

L

H

L

X

X

X

L-H Three-State

Snooze Mode, Power-down

None

X

X

X

H

X

X

X

X

X

X

Three-State

Read Cycle, Begin Burst

External

L

L

H

L

L

X

X

X

L

L-H Q

Read Cycle, Begin Burst

External

L

L

H

L

L

X

X

X

H

L-H Three-State

Write Cycle, Begin Burst

External

L

L

H

L

H

L

X

L

X

L-H D

Notes:

2. X = "Don't Care." H = Logic HIGH, L =Logic LOW.

3. WRITE = L when any one or more Byte Write Enable signals (BW

A

, BW

B

) and BWE = L or GW= L. WRITE = H when all Byte Write Enable signals (BW

A

, BW

B

),

BWE, GW = H.The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

4. The SRAM always initiates a Read cycle when ADSP is asserted, regardless of the state of GW, BWE, or BW

[A: B]

. Writes may occur only on subsequent clocks

after the ADSP or with the assertion of ADSC. As a result, OE must be driven HIGH prior to the start of the Write cycle to allow the outputs to three-state. OE is

a don't care for the remainder of the Write cycle

5. OE is asynchronous and is not sampled with the clock rise. It is masked internally during Write cycles. During a read cycle all data bits are Three-State when

OE is inactive or when the device is deselected, and all data bits behave as output when OE is active (LOW)