PRELIMINARY

CY7C1481V33

CY7C1483V33

CY7C1487V33

Document #: 38-05284 Rev. *A

Page 3 of 30

.

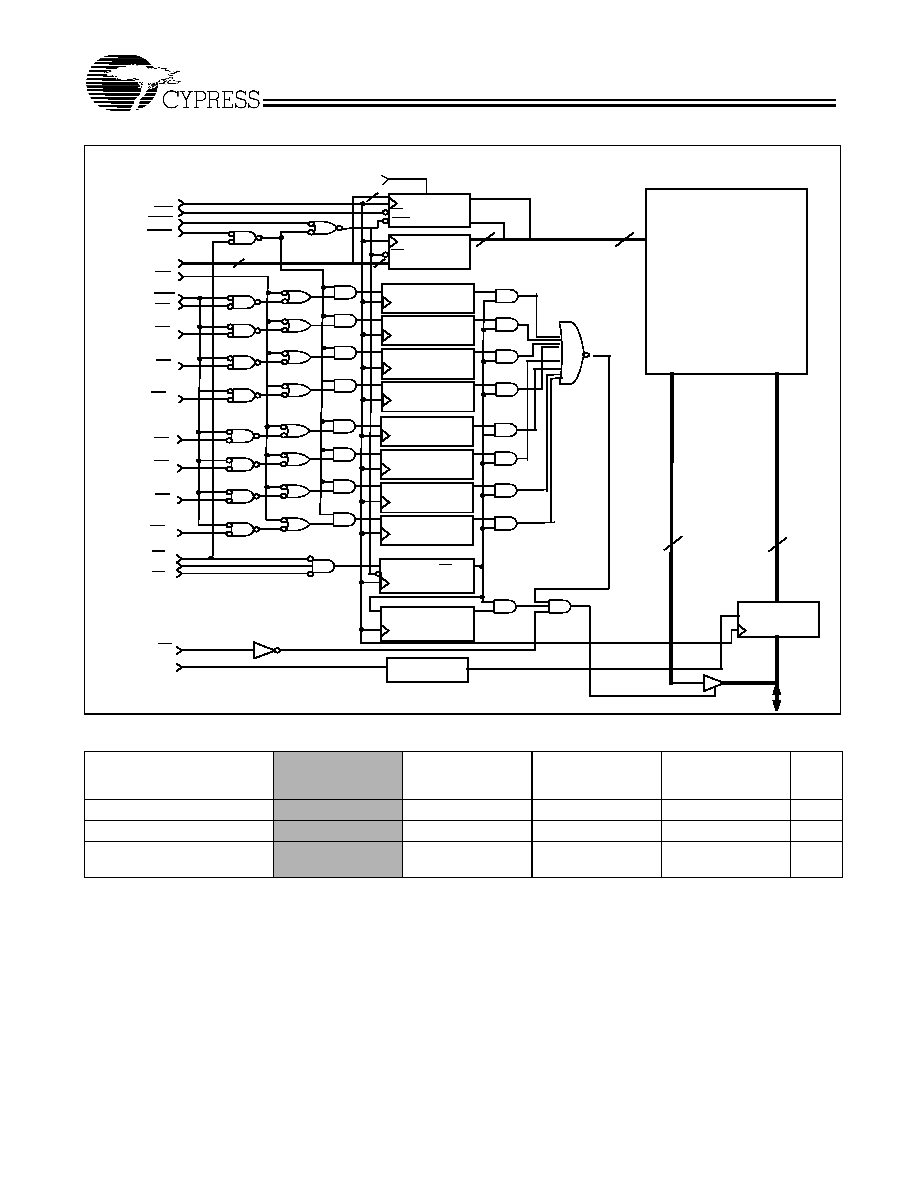

CY7C1487V33 ≠ 1M x72

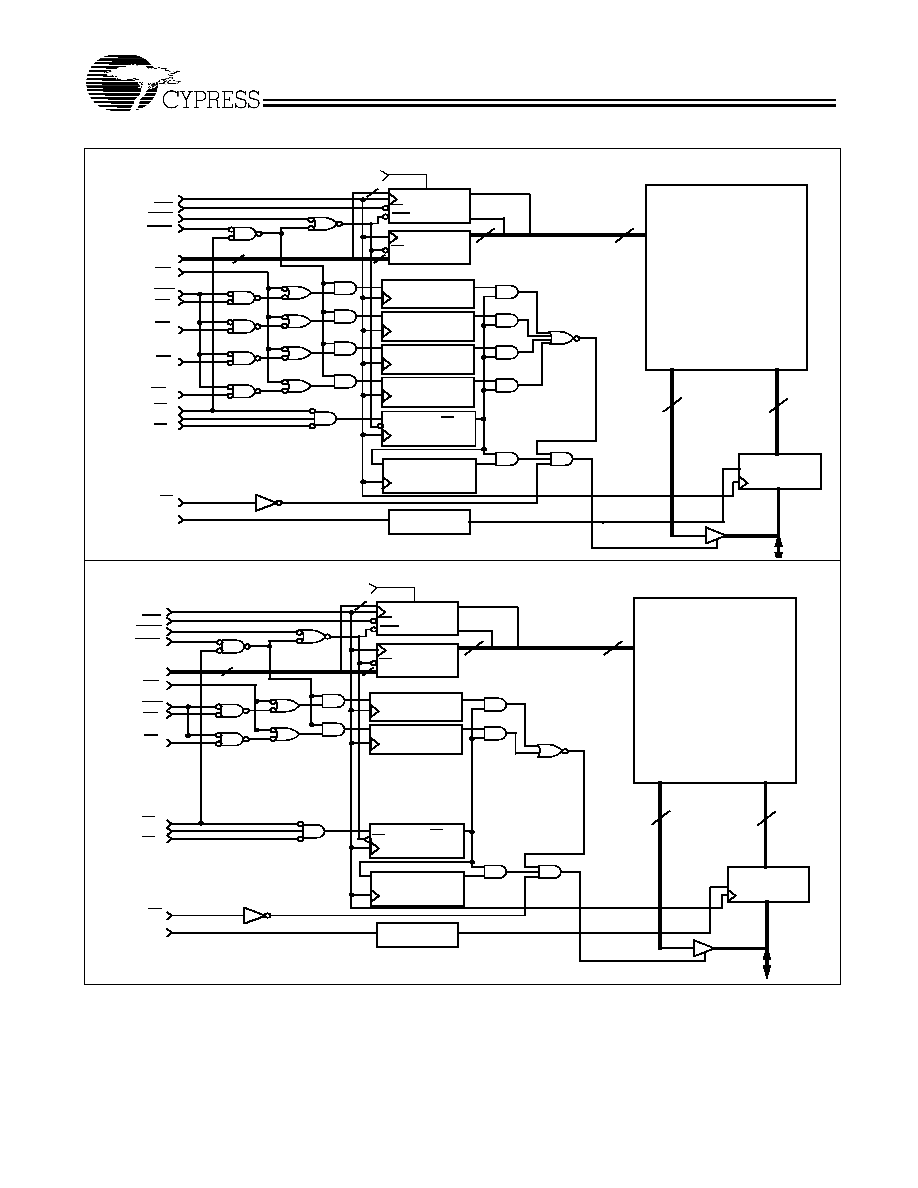

Logic Block Diagrams

(continued)

CLK

ADV

ADSC

A

[19:0]

GW

BWE

BW

h

BW

g

BW

f

BW

e

CE

1

CE

3

CE

2

OE

ZZ

BURST

COUNTER

ADDRESS

REGISTER

INPUT

REGISTERS

1M

X72

MEMORY

ARRAY

CLK

Q

0

Q

1

Q

D

CE

CE

CLR

SLEEP

CONTROL

72

72

20

18

18

20

(A

[1;0]

)

2

MODE

ADSP

DQ

a,b,c,d,e,f,g,h

DP

a,b,c,d,e,f,g,h

DQ

h

, DP

h

BYTEWRITE

REGISTERS

D

Q

DQ

g

, DP

g

BYTEWRITE

REGISTERS

D

Q

D

Q

DQ

f

, DP

f

BYTEWRITE

REGISTERS

DQ

e

, DP

e

BYTEWRITE

REGISTERS

D

Q

ENABLE CE

REGISTER

D

Q

ENABLE DELAY

REGISTER

D

Q

BW

d

BW

c

BW

b

BW

a

DQ

c

, DP

c

BYTEWRITE

REGISTERS

D

Q

D

Q

DQ

b

, DP

b

BYTEWRITE

REGISTERS

DQ

a

, DP

a

BYTEWRITE

REGISTERS

D

Q

DQ

d

, DP

d

BYTEWRITE

REGISTERS

D

Q

Selection Guide

CY7C1481V33-150

CY7C1483V33-150

CY7C1487V33-150

CY7C1481V33-133

CY7C1483V33-133

CY7C1487V33-133

CY7C1481V33-117

CY7C1483V33-117

CY7C1487V33-117

CY7C1481V33-100

CY7C1483V33-100

CY7C1487V33-100

Unit

Maximum Access Time

5.5

6.5

7.5

8.5

ns

Maximum Operating Current

TBD

TBD

TBD

TBD

mA

Maximum CMOS Standby

Current

TBD

TBD

TBD

TBD

mA

PRELIMINARY

CY7C1481V33

CY7C1483V33

CY7C1487V33

Document #: 38-05284 Rev. *A

Page 4 of 30

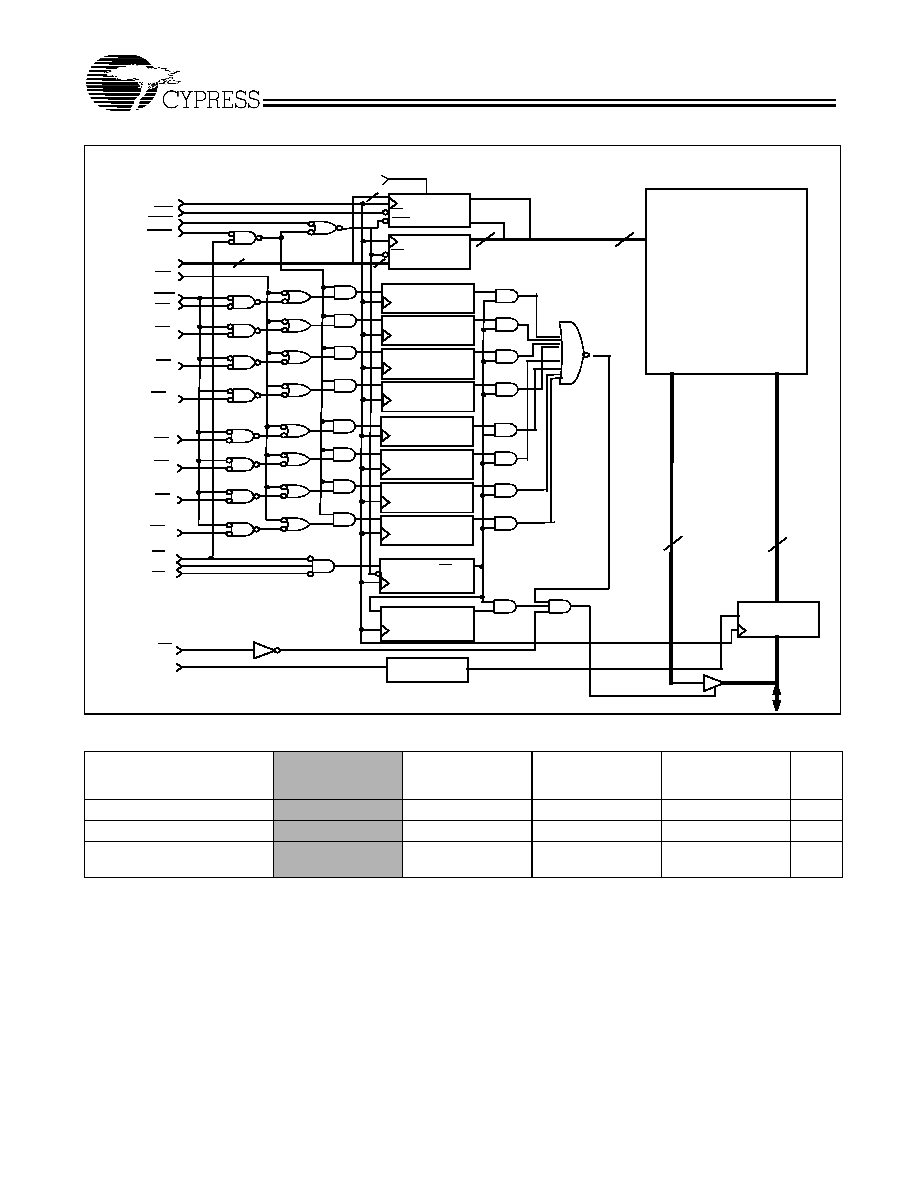

Pin Configurations

A

A

A

A

A

1

A

0

A

V

SS

V

DD

A

A

A

A

A

A

A

A

A

NC

NC

V

DDQ

V

SSQ

NC

DPa

DQa

DQa

V

SSQ

V

DDQ

DQa

DQa

V

SS

NC

V

DD

ZZ

DQa

DQa

V

DDQ

V

SSQ

DQa

DQa

NC

NC

V

SSQ

V

DDQ

NC

NC

NC

NC

NC

NC

V

DDQ

V

SSQ

NC

NC

DQb

DQb

V

SSQ

V

DDQ

DQb

DQb

V

DD

NC

V

SS

DQb

DQb

V

DDQ

V

SSQ

DQb

DQb

DPb

NC

V

SSQ

V

DDQ

NC

NC

NC

A

A

CE

1

CE

2

NC

NC

BW

b

BW

a

CE

3

V

DD

V

SS

CL

K

GW

BW

E

OE

AD

SC

AD

SP

AD

V

A

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

MOD

E

CY7C1483V33

(4M x 18)

NC

A

A

A

A

A

1

A

0

A

V

SS

V

DD

A

A

A

A

A

A

A

A

A

DQPb

DQb

DQb

V

DDQ

V

SSQ

DQb

DQb

DQb

DQb

V

SSQ

V

DDQ

DQb

DQb

V

SS

NC

V

DD

ZZ

DQa

DQa

V

DDQ

V

SSQ

DQa

DQa

DQa

DQa

V

SSQ

V

DDQ

DQa

DQa

DQPa

DQPc

DQc

DQc

V

DDQ

V

SSQ

DQc

DQc

DQc

DQc

V

SSQ

V

DDQ

DQc

DQc

V

DD

NC

V

SS

DQd

DQd

V

DDQ

V

SSQ

DQd

DQd

DQd

DQd

V

SSQ

V

DDQ

DQd

DQd

DQPd

A

A

CE

1

CE

2

BW

d

BW

c

BW

b

BW

a

CE

3

V

DD

V

SS

CL

K

GW

BW

E

OE

AD

SC

AD

SP

AD

V

A

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

10

0

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

MO

DE

CY7C1481V33

(2M X 36)

NC

A

100-pin TQFP

(Top View)

A

A