| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: W218 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

FTG for Integrated Core Logic with 133-MHz FSB

W218

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

∑

CA 95134

∑

408-943-2600

Document #: 38-07221 Rev. **

Revised September 27, 2001

Features

∑ Maximized EMI suppression using Cypress's Spread

Spectrum technology

∑ Three copies of CPU clock at 66/100/133 MHz

∑ Nine copies of 100-MHz SDRAM clocks

∑ Seven copies of PCI clock

∑ Two copies of APIC clock at 33 MHz, synchronous to

CPU clock

∑ Two copies of 48-MHz clock (non-spread spectrum) op-

timized for USB reference input and video dot clock

∑ Three copies of 3V 66-MHz fixed clock

∑ One copy of 14.31818-MHz reference clock

∑ Power down control

∑ SMBus interface for turning off unused clocks

Key Specifications

CPU, SDRAM Outputs Cycle-to-Cycle Jitter:.............. 250 ps

APIC, 48-MHz, 3V66, PCI Outputs

Cycle-to-Cycle Jitter:................................................... 500 ps

APIC, SDRAM Output Skew: ...................................... 250 ps

CPU, 3V66 Output Skew: ............................................ 175 ps

PCI Output Skew: ........................................................ 500 ps

CPU to SDRAM Skew (@ 133 MHz):.........................±0.5 ns

CPU to SDRAM Skew (@ 100 MHz):................. 4.5 to 5.5 ns

CPU to 3V66 Skew (@ 66 MHz): ....................... 7.0 to 8.0 ns

3V66 to PCI Skew (3V66 lead):..........................1.5 to 3.5 ns

PCI to APIC Skew: .....................................................±0.5 ns

Intel is a registered trademark of Intel Corporation.

Table 1. Pin Selectable Functions

Tristate#

FSEL0

FSEL1

CPU

SDRAM

0

0

x

Three-state

Three-state

0

1

x

Test

Test

1

0

0

66 MHz

100 MHz

1

1

0

100 MHz

100 MHz

1

0

1

133 MHz

133 MHz

1

1

1

133 MHz

100 MHz

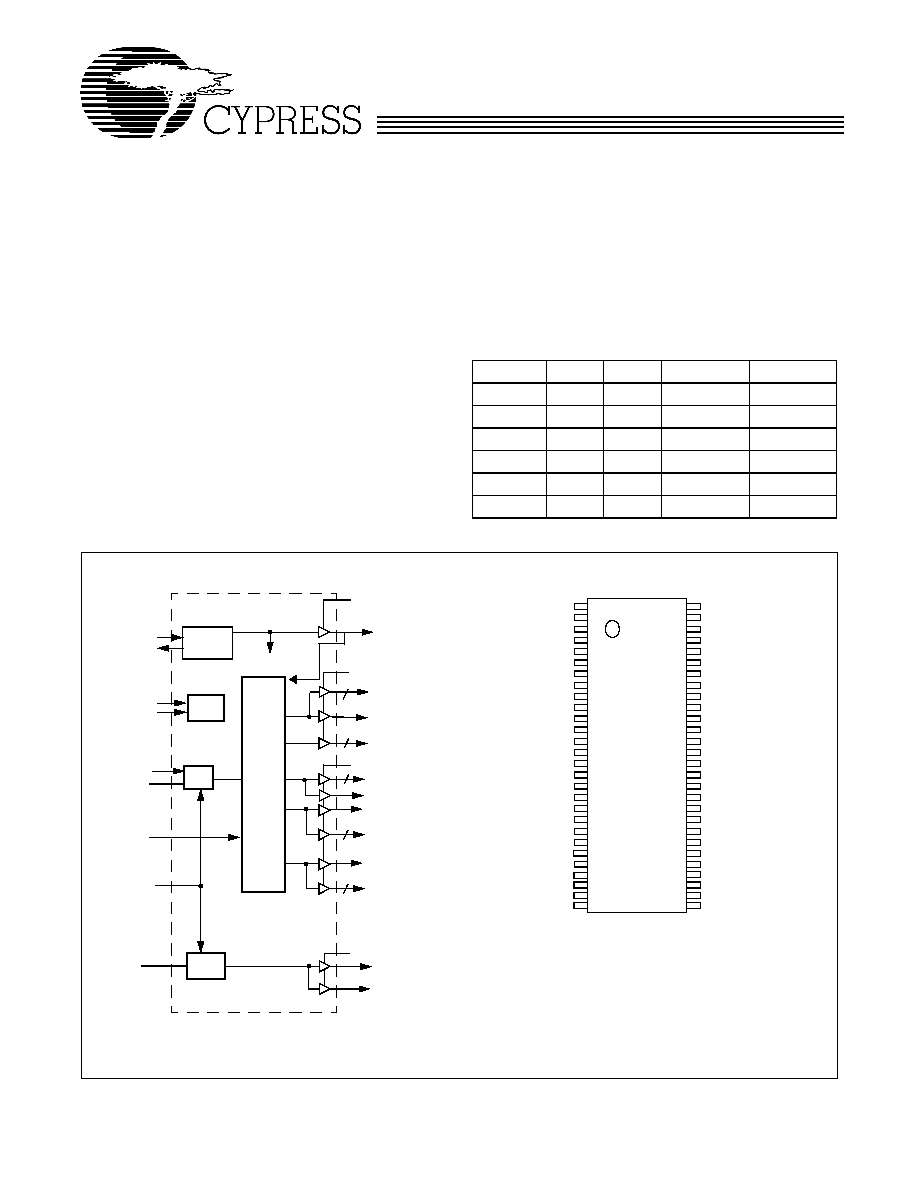

Block Diagram

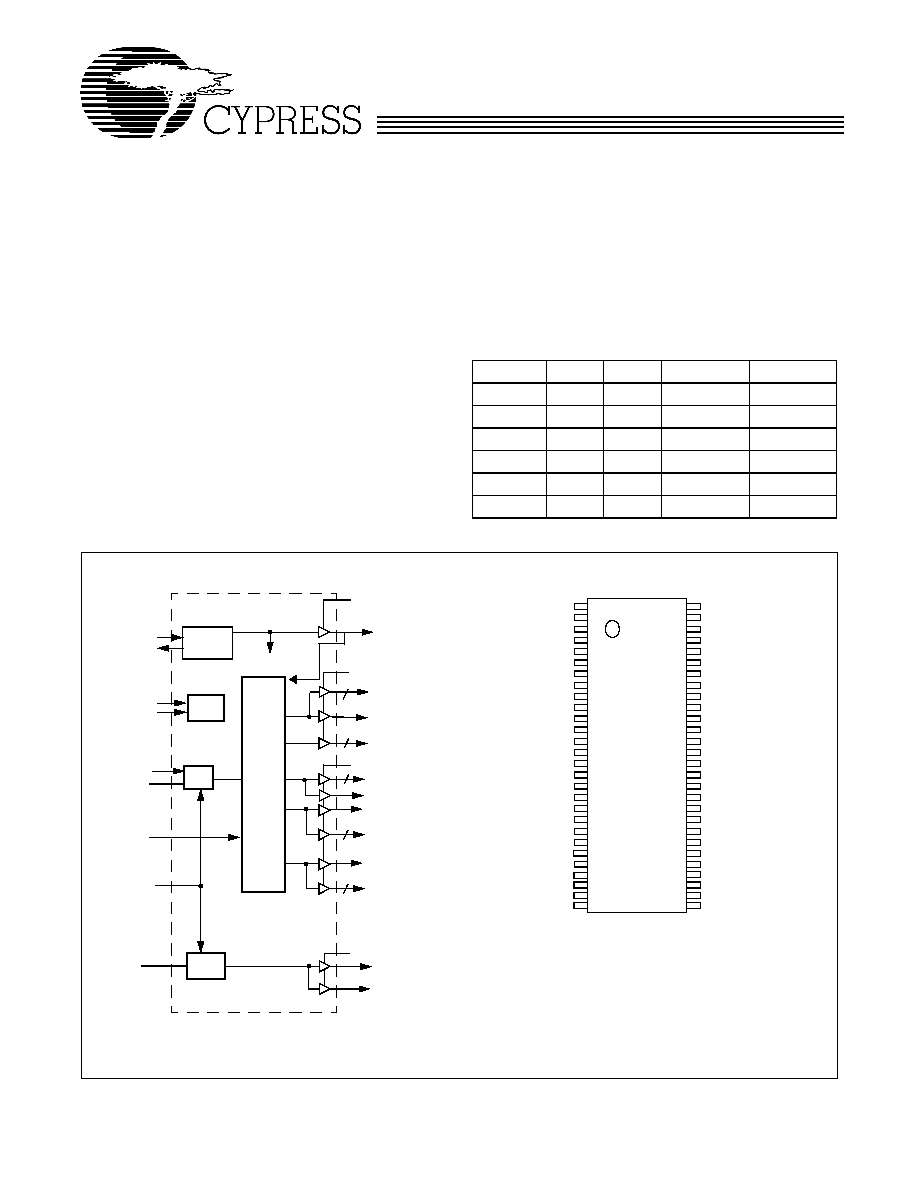

Pin Configuration

Note:

1.

Internal pull-down resistors present on input marked with *.

Design should not solely rely on internal pull-down resister to

set I/O pin LOW.

[1]

VDDQ3

VDDQ2

CPU2_ITP

PCI0_ICH

XTAL

PLL REF FREQ

PLL 1

X2

X1

REF0/FSEL1

PCI1:6

USB

DOT

PLL2

OSC

VDDQ3

I

2

C

SDATA

Logic

SCLK

3V66_0:1

CPU0:1

FSEL0:1

APIC0:1

Divider,

Delay,

and

Phase

Control

Logic

7

2

VDDQ3

2

2

DCLK

SDRAM0:7

8

PWR_DWN#

3V66_AGP

VDDA

VDDA

Tristate#

*REF0/FSEL1

VDDQ3

X1

X2

GND

GND

3V66_0

3V66_1

3V66_AGP

VDDQ3

VDDQ3

PCI0_ICH

PCI1

GND

PCI2

PCI3

GND

PCI4

PCI5

PCI6

VDDQ3

VDDA

GNDA

GND

W218

GND

APIC0

APIC1

VDDQ2

CPU0

VDDQ2

CPU1

CPU2_ITP

GND

GND

SDRAM0

SDRAM1

VDDQ3

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDDQ3

SDRAM6

SDRAM7

GND

DCLK

VDDQ3

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

32

31

30

29

USB

DOT

VDDQ3

FSEL0

PWR_DWN#

SCLK

SDATA

Tristate#

W218

Document #: 38-07221 Rev. **

Page 2 of 17

Pin Definitions

Pin Name

Pin No.

Pin

Type

Pin Description

REF0/FSEL1

1

I/O

Reference Clock: 3.3V 14.318-MHz clock output. This pin also serves as a strap

option for CPU frequency selection. See Table 1 for detailed descriptions.

X1

3

I

Crystal Input: This pin has dual functions. It can be used as an external

14.318-MHz crystal connection or as an external reference frequency input.

X2

4

O

Crystal Output: A connection for an external 14.318-MHz crystal. If using an ex-

ternal reference, this pin must be left unconnected.

PCI0_ICH,

PCI1:6

12, 13, 15, 16,

18, 19, 20

O

PCI Clock 0 through 6: 3.3V 33-MHz PCI clock outputs. PCI1:7 can be individually

turned off via SMBus interface.

3V66_0:1/

3V66_AGP

7, 8, 9

O

66-MHz Clock Output: 3.3V fixed 66-MHz clock.

USB

25

O

USB Clock Output: 3.3V fixed 48-MHz, non-spread spectrum USB clock output.

DOT

26

O

Dot Clock Output: 3.3V 48-MHz, non-spread spectrum signal.

FSEL0,

Tristate#

28, 29

I

Clock Function Selection pins: LVTTL-compatible input to select device func-

tions. See Table 1 for detailed descriptions.

PWR_DWN#

32

I

Power-Down Control: LVTTL-compatible asynchronous input that places the de-

vice in power-down mode when held LOW. This input can be used as the

VTT_PWRGD input to support Intel

VRM 8.5 implementation.

CPU2_ITP,

CPU0:1

49,52,50

O

CPU Clock Outputs: Clock outputs for the host bus interface and integrated test

port. Output frequencies run at 66 MHz, 100 MHz, or 133 MHz depending on the

configuration of SEL0:1 and SEL133. Voltage swing set by V

DDQ2

.

SDRAM0:7,

DCLK

46, 45, 43, 42,

40, 39, 37, 36,

34

O

SDRAM Clock Outputs: 3.3V outputs running at 100 MHz. SDRAM0:7 can be

individually turned off via SMBus interface.

APIC0:1

55, 54

O

Synchronous APIC Clock Outputs: Clock outputs running synchronous with the

PCI clock outputs (33 MHz). Voltage swing set by V

DDQ2

.

SDATA

30

I/O

Data pin for SMBus circuitry.

SCLK

31

I

Clock pin for SMBus circuitry.

VDDQ3

2, 10, 11, 21, 27,

33, 38, 44

P

3.3V Power Connection: Power supply for SDRAM output buffers, PCI output

buffers, 3V66 output buffers, reference output buffers, and 48-MHz output buffers.

Connect to 3.3V.

VDDA

22

P

3.3V Power Connection: Power supply for core logic, PLL circuitry. Connect to

3.3V.

VDDQ2

51, 53

P

2.5V Power Connection: Power supply for IOAPIC and CPU output buffers. Con-

nect to 2.5V or 3.3V.

GND

5, 6, 14, 17, 24,

35, 41, 47, 48,

56

G

Ground Connections: Connect all ground pins to the common system ground

plane.

GNDA

23

G

Ground Connections: Ground for core logic, PLL circuitry.

W218

Document #: 38-07221 Rev. **

Page 3 of 17

Overview

The W218 is a highly integrated frequency timing generator,

supplying all the required clock sources for an IntelÆ architec-

ture platform using graphics integrated core logic.

Functional Description

I/O Pin Operation

REF0/FSEL1is a dual-purpose l/O pin. Upon power-up the pin

acts as a logic input. If the pin is strapped to a HIGH state

externally, CPU clock outputs will run at 133 MHz. If it is

strapped LOW, CPU clock outputs will be determined by the

status of FSEL input pin. An external 10-k

strapping resistor

should be used. Figure 1 shows a suggested method for strap-

ping resistor connections.

After 2 ms, the pin becomes an output. Assuming the power

supply has stabilized by then, the specified output frequency

is delivered on the pins. If the power supply has not yet

reached full value, output frequency initially may be below tar-

get but will increase to target once supply voltage has stabi-

lized. In either case, a short output clock cycle may be pro-

duced from the CPU clock outputs when the outputs are

enabled.

Pin Selectable Functions

Table 1 outlines the device functions selectable through

Threestate#, FSEL0 and FSEL1. Specific outputs available at

each pin are detailed in Table 2 below. The SEL0 pin requires

a 220

pull-up resistor to 3.3V for the W218 to sense the max-

imum host bus frequency of the processor and configure itself

accordingly. Also note that FSEL0, Threestate# input levels

should be stable within 500

µ

s of the later of V

DDQ3

, V

DDQ2

,

PWR_DWN# rising edge.

Notes:

2.

Provided for board-level "bed of nails" testing.

3.

"Normal" mode of operation.

4.

TCLK is a test clock overdriven on the XTAL_IN input during test mode.

5.

Required for DC output impedance verification.

6.

Range of reference frequency allowed is min. = 14.316 MHz, nominal = 14.31818 MHz, max. = 14.32 MHz.

7.

Frequency accuracy of 48 MHz must be +167 PPM to match USB default.

Power-on

Reset

Timer

Output Three-state

Data

Latch

Hold

Q

D

W218

V

DD

Clock Load

10 k

Output

Buffer

(Load Option 1)

10 k

(Load Option 0)

Output

Low

Output Strapping Resistor

Series Termination Resistor

Figure 1. Input Logic Selection Through Resistor Load Option

Table 2. CK Whitney Truth Table

Tristate#

FSEL0

FSEL1

CPU

SDRAM

3V66

PCI

48 MHz

REF

APIC

Notes

0

0

X

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

2

0

1

X

TCLK/4

TCLK/4

TCLK/6

TCLK/12

TCLK/2

TCLK

TCLK/12

4, 5

1

0

0

66 MHz

100 MHz

66 MHz

33 MHz

48 MHz

14.318 MHz

33 MHz

3, 6, 7

1

1

0

100 MHz

100 MHz

66 MHz

33 MHz

48 MHz

14.318 MHz

33 MHz

3, 6, 7

1

0

1

133 MHz

133 MHz

66 MHz

33 MHz

48 MHz

14.318 MHz

33 MHz

3, 6, 7

1

1

1

133 MHz

100 MHz

66 MHz

33 MHz

48 MHz

14.318 MHz

33 MHz

3, 6, 7

W218

Document #: 38-07221 Rev. **

Page 4 of 17

How to use PD# input to support VTT_PWRGD

The PD# input can be used to support the VTT_PWRGD sig-

nal specified in the Intel

VRM 8.5 specification. The

VTT_PWRGD is used to indicated that the frequency select

output pins (BSEL[0:1]) from the CPU are valid and the clock

generator can use them to determine the CPU FSB frequency.

The assertion of PD# input pin during initial power up will delay

the start of the PLL, keep all the multiplexed I/O pins as input

and keep all the output inactive. The functionality of PD# will

allow system designer to use this input to support the

VTT_PWRGD output from the VRM 8.5 module. Please refer

to the Figure 2 for power up sequence details.

3.3V & 2.5V

PD# (connected to

VTT_PWRGD)

Outputs

Input Latch

(pin 4 & pin21)

1 ms

PLL & Output

Synchronization

Figure 2. Power up sequence with PD# (VTT_PWRGD) hold LOW

W218

Document #: 38-07221 Rev. **

Page 5 of 17

Offsets Among Clock Signal Groups

Figure 3 and Figure 4 represent the phase relationship among

the different groups of clock outputs from W218 when it is pro-

viding a 66-MHz CPU clock and a 100-MHz CPU clock, re-

spectively. It should be noted that when CPU clock is operating

at 100 MHz, CPU clock output is 180 degrees out of phase

with SDRAM clock outputs.

0 ns

Figure 3. Group Offset Waveforms (66-MHz CPU/100-MHZ SDRAM Clock)

40 ns

30 ns

20 ns

10 ns

CPU 66-MHz

SDRAM 100-MHz

3V66 66-MHz

PCI 33-MHz

REF 14.318-MHz

USB 48-MHz

DOT 48-MHz

Cycle Repeat

APIC33-MHz

0 ns

Figure 4. Group Offset Waveforms (100-MHz CPU/100-MHZ SDRAM Clock)

40 ns

30 ns

20 ns

10 ns

CPU 100-MHz

SDRAM 100-MHz

3V66 66-MHz

PCI 33-MHz

REF 14.318-MHz

USB 48-MHz

DOT 48-MHz

APIC 33-MHz

Cycle Repeat