DESCRIPTION:

The Memory StackTM series is a family of interchangeable memory devices. The 512 Mb, CMOS DDR Synchronous DRAM, Narrow

Rail assembly utilizes the space saving LP-StackTM technology to increase memory density. This stack is constructed with two

256Mb (64M x 4) DDR SDRAMs.

This 512 Mb LP-StackTM, has been designed to fit in the

same footprint as the 256Mb (64M x 4) DDR SDRAM

TSOPII monolithic. This allows system upgrade without

electrical or mechanical redesign, providing an alternative

low cost memory solution.

FEATURES:

∑

Electrical characteristics meet semiconductor

manufacturers' datasheets

∑

Memory organization:

(2) 256Mb Memory devices. Each device arranged

as 64M x 4 bits (16M x 4 bits x 4 banks)

∑

Memory stack organization:

128M x 4 bits (32M x 4 bits x 4 banks)

∑

JEDEC approved, 2 Rank stack pinout and footprint

(with 2 CSs and 2 CKEs)

∑

Optimized for RDIMMs

∑

IPC-A-610, class 2, manufacturing standards

∑

Lead free manufacturing process

∑

Package: 66-Pin TSOPII Narrow Rail stack

This document contains information on a product that is currently released to production at DPAC Technologies Corp.

DPAC reserves the right to change products or specifications herein without prior notice.

30A235-01

REV. B 2/03

512 Megabit Narrow Rail CMOS DDR SDRAM

DPDD128MX4WSANY5

1

ADVAN C E D C O M P O N E NTS PAC K AG I N G

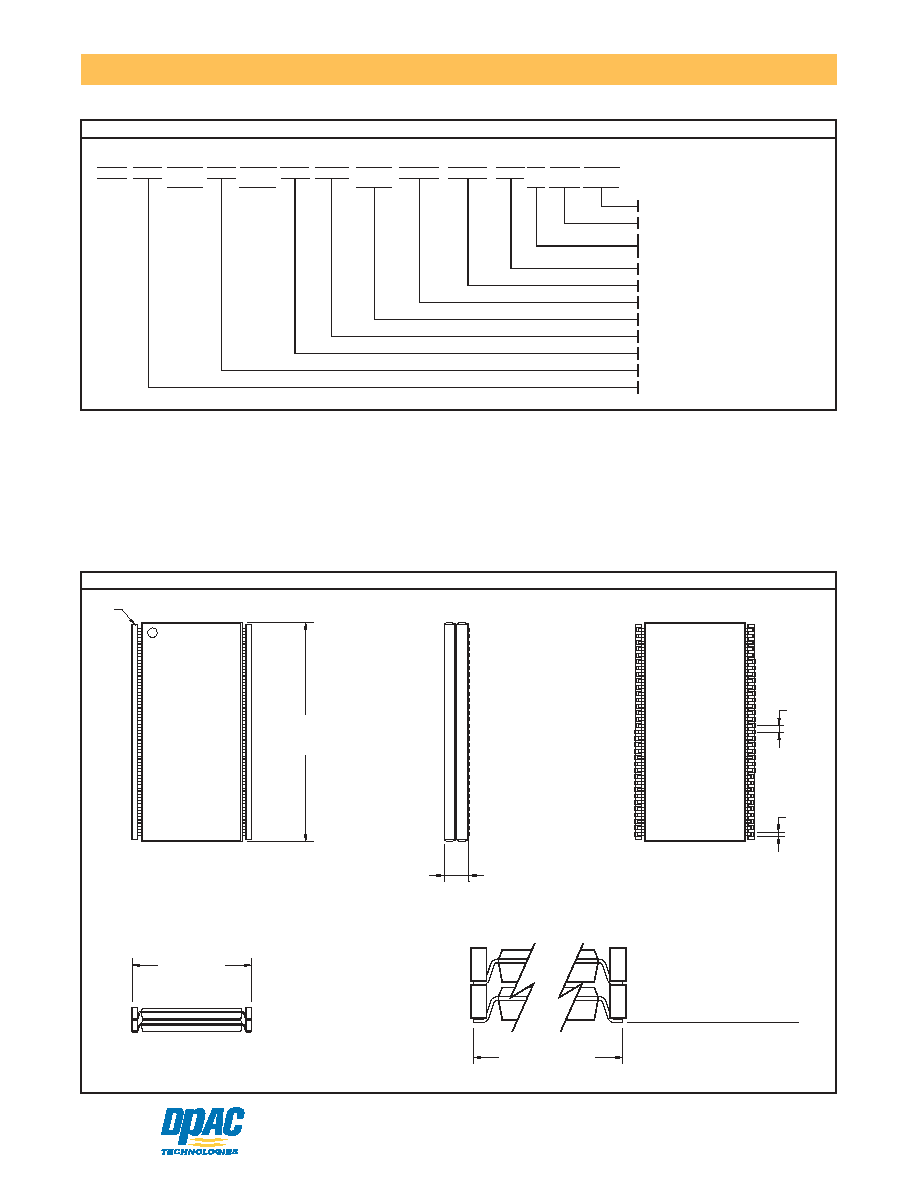

FUNCTIONAL BLOCK DIAGRAM

DM

CAS

WE

DQ0-DQ3

CS0

(16M x 4 bits x 4 banks)

RAS

CK

DQS

CS1

CK

A0-A12

VREF

CKE1

CKE0

(16M x 4 bits x 4 banks)

BA0-BA1

256 Mb DDR SDRAM

PINOUT DIAGRAM

1

(TOP VIEW)

60

NC

VDD

1

2

54

NC

VDDQ

3

53

NC

4

52

VSSQ

DQ0

5

51

DQS

VSSQ

6

50

DNU

NC

7

49

VREF

8

48

VSS

VDDQ

9

47

NC

10

46

CK

DQ1

11

45

CK

VSSQ

12

44

CKE0

NC

13

43

CKE1

NC

14

42

A12

VDDQ

15

41

A11

NC

16

40

A9

NC

17

39

A8

VDD

18

38

A7

DNU

19

37

A6

NC

20

36

A5

WE

21

35

A4

CAS

22

34

VSS

RAS

23

59

NC

CS0

24

58

VSSQ

CS1

25

57

NC

BA0

26

56

DQ2

BA1

27

55

VDDQ

NC

NC

DM

NC

33

VDD

32

A3

31

A2

30

A1

29

A0

28

A10/AP

VDDQ

61

DQ3

62

NC

63

VSSQ

64

NC

65

VSS

66

PIN NAMES

A0-A12

Row Address:

A0-A12

Column Address:

A0-A9, A11

BA0, BA1

Bank Select Address

A10/AP

Auto Precharge

DQ0-DQ3

Data In/Data Out

CAS

Column Address Strobe

CS0, CS1

Chip Selects

RAS

Row Address Strobe

WE

Data Write Enable

CK, CK

Differential Clock Inputs

CKE0, CKE1

Clock Enables

DQS

Data Strobe

DM

Data Mask

V

DD

Power Supply

V

SS

Ground

V

DDQ

DQ Power Supply

V

SSQ

DQ Ground

VREF

SSTL_2 Reference Voltage

NC

No Connect

DNU

Do Not Use

2

DPAC Technologies Products & Services for the Integration Age

7321 Lincoln Way, Garden Grove, CA 92841 Tel 714 898 0007 Fax 714 897 1772

www.dpactech.com Nasdaq: DPAC

©2003 DPAC Technologies, all rights reserved. DPAC TechnologiesTM, Memory StackTM, System StackTM, LP-StackTM, CS-StackTM are trademarks of DPAC Technologies Corp.

DPDD128MX4WSANY5

512 Megabit Narrow Rail CMOS DDR SDRAM

30A235-01

REV. B 2/03

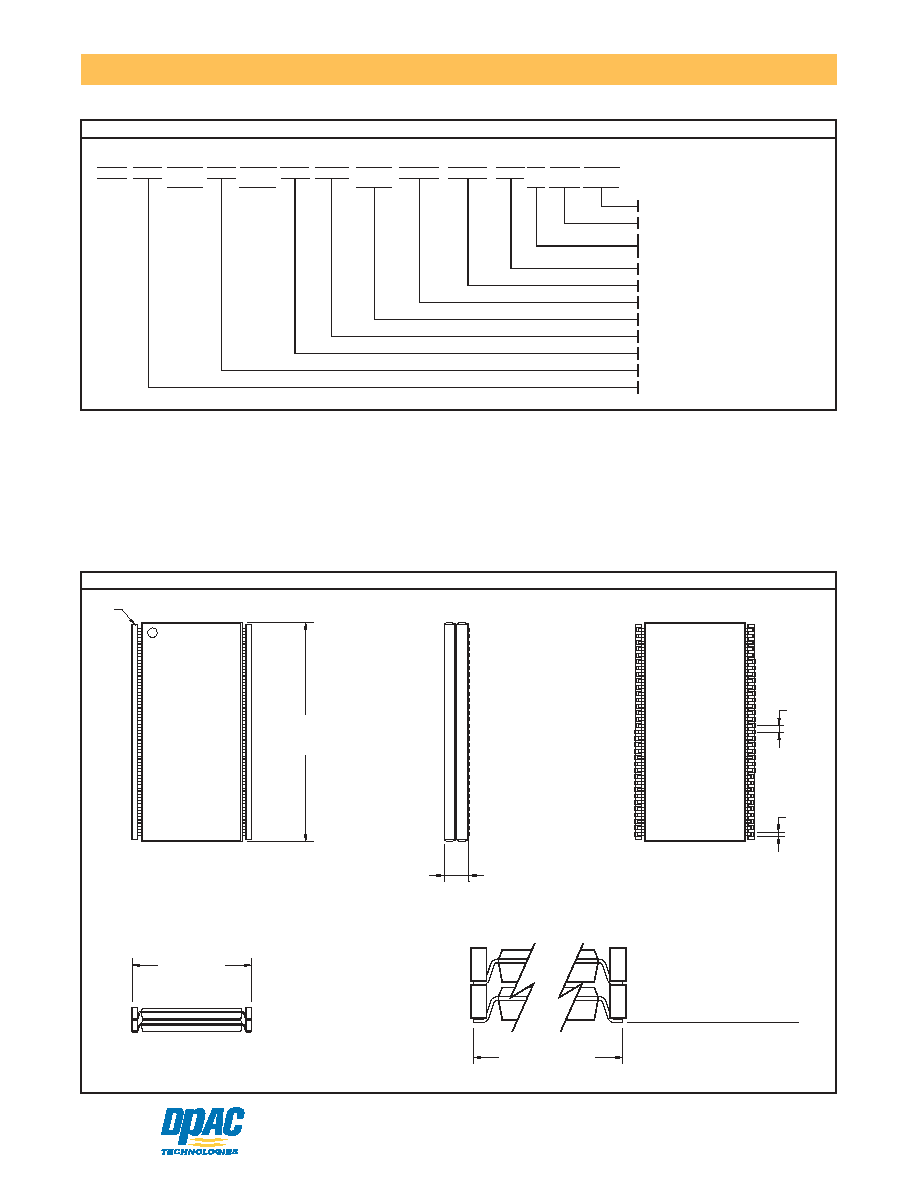

MECHANICAL DIAGRAM

1

.015 [.18]

.0256 [.65

.102 MAX

PIN 1

INDEX

TOP VIEW

SIDE VIEW

BOTTOM VIEW

END VIEW

.478

.891 MAX.

[12.14 ]

[22.63 MAX.]

[2.59 MAX]

TYP

TYP

-.002

+.006

+.15

-.05

Inch [mm]

Lead Toe-to-Toe per device datasheet

COPLANARITY:

.004 [.10] from seating plane

.463 [11.76] TYP

END VIEW DETAIL

ORDERING INFORMATION

DP

X

-

MFR

DOUBLE DATA RATE SYNCHRONOUS DRAM

PREFIX

DD 128M X

4

NY5

PACKAGE

MEMORY

DESIG

MEMORY

TYPE

MEMORY MODULE WITHOUT SUPPORT LOGIC

DEPTH

WIDTH

DESIG

W

256 MEGABIT BASED

STACKABLE TSOP, NARROW RAIL

MANUFACTURER CODE *

XX

-

MFR ID

SUPPLIER

DP

SUPPLIER CODE *

I/O TYPE

S

SSTL INPUTS/OUTPUTS

WIDTH

DEVICE

A

x8 MEMORY BASED

CLOCK

XX

SPEED

REV

REVISION NOT SPECIFIED

MANUFACTURER DIE REVISION

BLANK

X

XX

LATENCY

CAS

CAS LATENCY

CLOCK SPEED (ns)

* Contact your sales representative for supplier and manufacturer codes.

NOTES:

1. AC Parameters of base memory are unchanged from device manufacturers' specifications.

2. DC Parameters may be affected by stacking. Please refer to application note 53A004-00 for further information.

3. For assembly and inspection procedures, refer to application note 53A001-00.

4. Maximum reflow temperature recommendation is 215∞C.