8 Megabit High Speed CMOS SRAM

DPS1MX8MKN3-A

DESCRIPTION:

The DPS1MX8MKN3-A High Speed SRAM

`'STACK'' devices are a revolutionary new memory

subsystem using Dense-Pac Microsystems' ceramic

Stackable Leadless Chip Carriers (SLCC) mounted

on a co-fired ceramic substrate having side-brazed

leads. The device packs 8-Megabits of low-power

CMOS static RAM in a 600-mil-wide, 32-pin

dual-in-line package.

The DPS1MX8MKN3-A STACK devices contain

two 512K x 8 SRAM die, each packaged in a

hermetically sealed SLCC, making the devices

suitable for commercial, industrial and military

applications.

By using SLCCs, the `'Stack'' family of devices offer

a higher board density of memory than available

with conventional through-hole, surface mount or

hybrid techniques.

FEATURES:

∑

Organizations Available: 1Meg x 8

∑

Access Times: 20*, 25, 30, 35, 45ns

∑

Fully Static Operation

- No clock or refresh required

∑

Single +5V Power Supply,

±

10% Tolerance

∑

TTL Compatible

∑

Common Data Inputs and Outputs

∑

Low Data Retention Voltage: 2.0V min.

∑

Package Available:

32 Pin DIP

*

Commercial and Industrial Grade only.

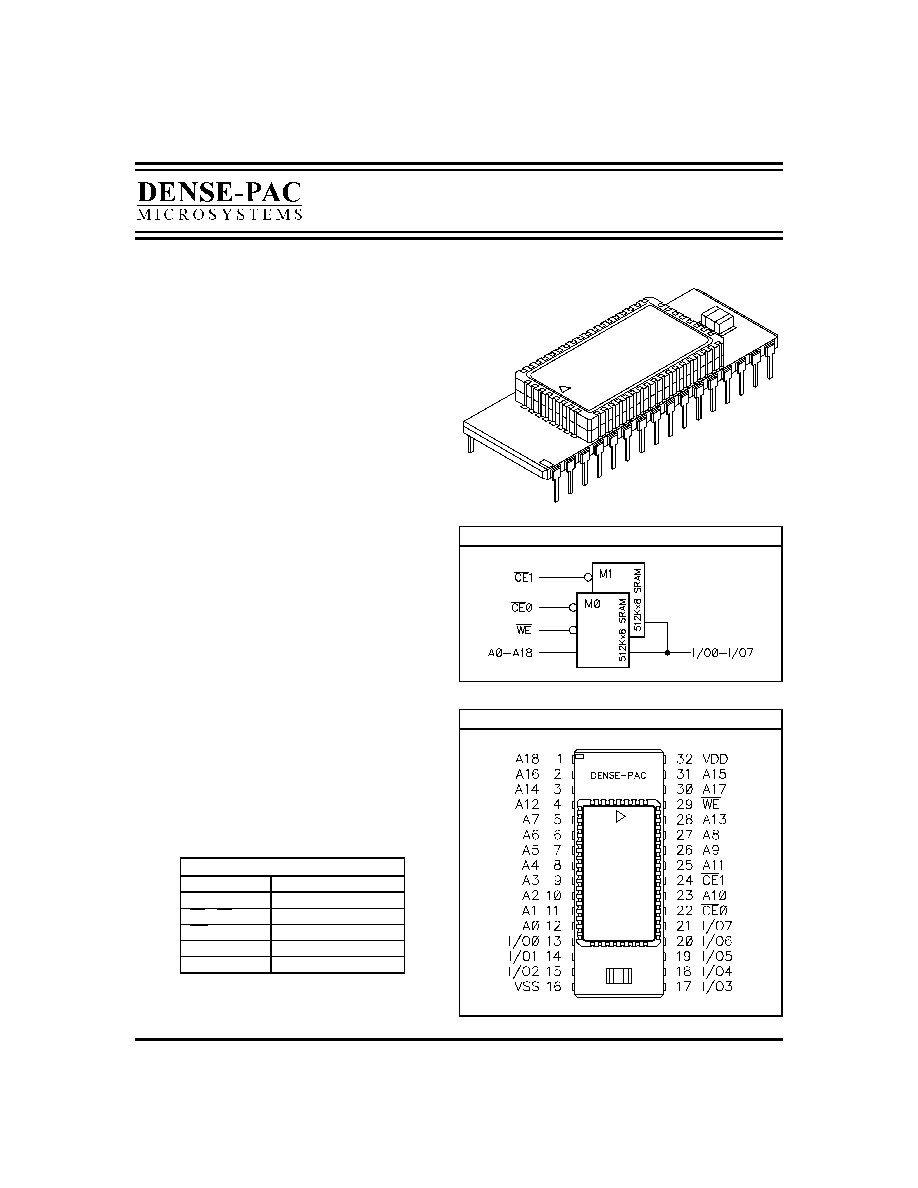

PIN-OUT DIAGRAM

FUNCTIONAL BLOCK DIAGRAM

This document contains information on a product that is currently released

to production at Dense-Pac Microsystems, Inc. Dense-Pac reserves the

right to change products or specifications herein without prior notice.

PIN NAMES

A0 - A18

Address

I/O0 - I/O7

Data Input / Output

CE0, CE1

Low Chip Enables

WE

Write Enable

V

DD

Power (+5.0V)

VSS

Ground

30A129-92

REV. A

1

DPS1MX8MKN3-A

Dense-Pac Microsystems, Inc.

DC OPERATING CHARACTERISTICS:

Over Operating Ranges

Symbol

Characteristics

Test Condition

Typ.

()

C

I

M/B

Unit

Min. Max. Min. Max. Min. Max.

I

IN

Input

Leakage Current

V

IN

= 0V to V

DD

-

-10

+10

-10

+10

-10

+10

µ

A

I

OUT

Output

Leakage Current

V

I/O

= 0V to V

DD ,

CE = V

IH

or WE = V

IL

-

-20

+20

-20

+20

-20

+20

µ

A

I

CC

Operating

Supply Current

Cycle = min., Duty = 100%,

I

OUT

= 0mA

145

230

240

240

mA

I

SB1

Full Standby

Supply Current

V

IN

V

DD

-0.2V or

V

IN

V

SS

+0.2V

2

20

20

30

mA

I

SB2

Standby Current (TTL)

CE = V

IH

40

120

120

120

mA

I

DR3

Data Retention

Supply Current (3.0V)

V

DR

= 3V, CE

V

DR

-0.2V

300

1000

2000

4000

µ

A

I

DR2

Data Retention

Supply Current (2.0V)

V

DR

= 2V, CE

V

DR

-0.2V

200

600

1600

360

µ

A

V

OL

Output LOW Voltage

I

OL

= 8.0mA

-

0.4

0.4

0.4

V

V

OH

Output HIGH Voltage

I

OH

= -4.0mA

-

2.4

2.4

2.4

V

Typical measurement made at +25∞C, Cycle = min., V

DD

= 5.0V.

TRUTH TABLE

Mode

CE

WE

I/O Pin

Supply

Current

Not Selected

H

X

HIGH-Z

Standby

Read

L

H

D

OUT

Active

Write

L

L

D

IN

Active

H = HIGH L = LOW X = Don't Care

ABSOLUTE MAXIMUM RATING

3

Symbol

Parameter

Max.

Unit

T

STC

Storage Temperature

-65 to +150

∫

C

T

BIAS

Temperature Under Bias

-55 to +125

∫

C

V

DD

Supply Voltage

1

-0.5 to +7.0

V

V

I/O

Input/Output Voltage

1

-0.5 to V

DD

+0.5 V

CAPACITANCE

4

:

T

A

= +25

∫

C, F = 1.0MHz

Symbol

Parameter

Max. Unit Condition

C

ADR

Address Input

18

pF

V

IN2

= 0V

C

CE

Chip Enable

12

C

WE

Write Enable

18

C

I/O

Data Input/Output

22

DC OUTPUT CHARACTERISTICS

Symbol

Parameter

Conditions Min. Max. Unit

V

OH

HIGH Voltage

I

OH

= -4mA

2.4

V

V

OL

LOW Voltage

I

OL

=8mA

0.4

V

RECOMMENDED OPERATING RANGE

3

Symbol

Characteristic

Min. Typ.

Max.

Unit

V

DD

Supply Voltage

4.5

5.0

5.5

V

V

IH

Input HIGH Voltage 2.2

V

DD

+0.3 V

V

IL

Input LOW Voltage -0.5

2

0.8

V

T

A

Operating

Temperature

M/B -55 +25

+125

∫

C

I

-40 +25

+85

C

-0

+25

+70

AC TEST CONDITIONS

Input Pulse Levels

0V to 3.0V

Input Pulse Rise and Fall Times

5ns*

Input and Output Timing Reference Levels

1.5V

OUTPUT LOAD

Load

C

L

Parametric Measured

1

100pF except t

LZ

, t

HZ

and t

WHZ

2

5pF

t

LZ

, t

HZ

and t

WHZ

Figure 1.

Output Load

* Including Probe and Jig Capacitance.

+5V

480

255

C

L

*

D

OUT

30A129-92

REV. A

2

Dense-Pac Microsystems, Inc.

DPS1MX8MKN3-A

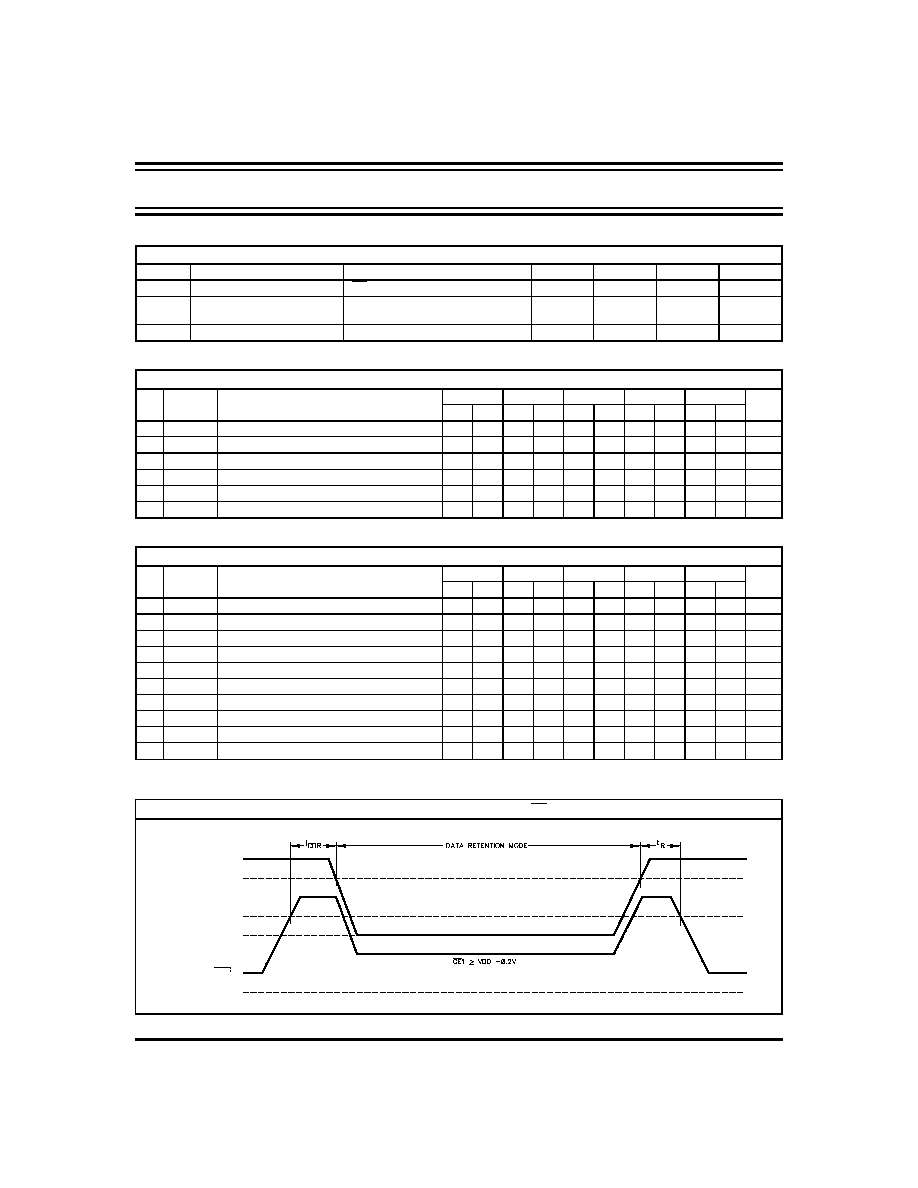

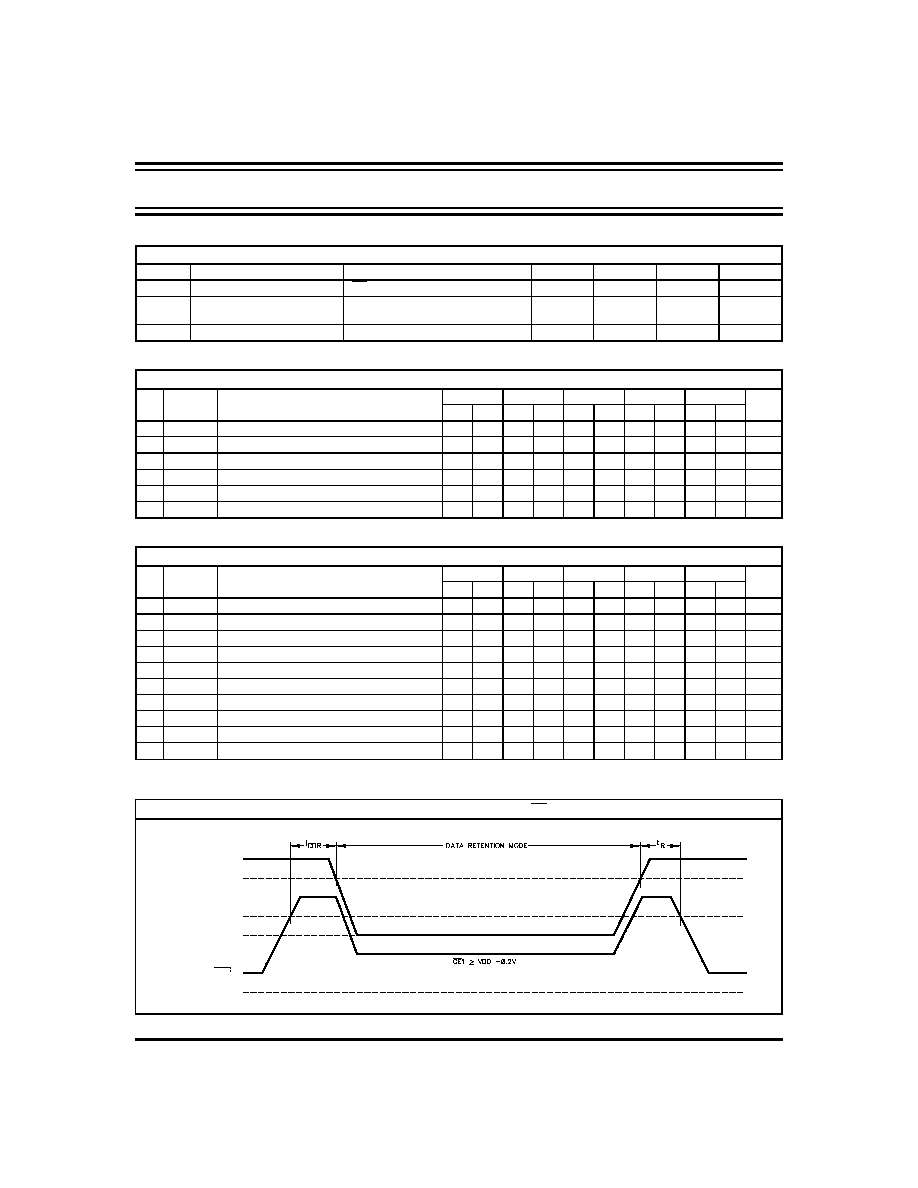

Data Retention AC Characteristics

8

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

V

DR

V

DD

for Data Retention

CE

V

DR

-0.2V

2.0

-

-

V

V

CDR

Chip Disable to Data

Retention Time

See Data Retention Waveform

0

-

-

ns

t

R

Operating Recovery Time

See Data Retention Waveform

5

-

-

ms

AC OPERATING CONDITIONS AND CHARACTERISTICS - READ CYCLE:

Over Operating Ranges

No. Symbol

Parameter

20ns*

25ns

30ns

35ns

45ns

Unit

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

1

t

RC

Read Cycle Time

20

25

30

35

45

ns

2

t

AA

Address Cycle Time

20

25

30

35

45

ns

3

t

CO

Chip Enable Output Valid

20

25

30

35

45

ns

4

t

CLZ

Chip Enable to Output in LOW-Z

4, 6

3

3

3

3

3

ns

5

t

CHZ

Chip Enable to Output in HIGH-Z

4, 5

8

10

15

20

25

ns

6

t

OH

Output Hold from Address Change

4

5

5

5

5

ns

AC OPERATING CONDITION AND CHARACTERISTIC READ CYCLE:

Over Operating Ranges

6, 7

No. Symbol

Parameter

20ns*

25ns

30ns

35ns

45ns

Unit

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

7

t

WC

Write Cycle Time

20

25

30

35

45

ns

8

t

AW

Address Valid to End of Write

13

15

20

25

35

ns

9

t

CW

Chip Enable to End of Write

13

15

20

25

35

ns

10

t

AS

Address Setup Time **

0

0

0

0

0

ns

11

t

WP

Write Pulse Width

13

15

20

25

35

ns

12

t

WR

Write Recovery Time

0

0

0

0

0

ns

13

t

WHZ

Write Enable to Output in HIGH-Z

4, 5

0

8

0

10

0

12

0

15

0

20

ns

14

t

DW

Data to Write Time Overlap

9

10

12

15

20

ns

15

t

DH

Data Hold from Write Time

0

0

0

0

0

ns

16

t

OW

Output Active from End of Write

3

3

3

3

3

ns

* Available in Commercial and Industrial Grade Only.

** Valid for both Read and Write Cycles.

DATA RETENTION WAVEFORM:

CE Controlled.

V

DD

4.5V

2.3V

V

DR1

CE

0V

30A129-92

REV. A

3

DPS1MX8MKN3-A

Dense-Pac Microsystems, Inc.

WRITE CYCLE 1:

CE Controlled.

ADDRESS

CE

WE

DATA IN

DATA OUT

READ CYCLE

ADDRESS

CE

DATA I/O

30A129-92

REV. A

4

Dense-Pac Microsystems, Inc.

DPS1MX8MKN3-A

WRITE CYCLE 2:

WE Controlled.

8

ADDRESS

CE

WE

DATA IN

DATA OUT

NOTE:

1. All voltages are with respect to V

SS

.

2. -2.0V min. for pulse width less than 20ns (V

IL

min. = -0.5V

at DC level).

3. Stresses greater than those under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device.

This is a stress rating only and functional operation of the

device at these or any other conditions above those

indicated in the operational sections of this specification

is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

4. This parameter is guaranteed and not 100% tested.

5. Transition is measured at the point of

±

500mV from steady

state voltage.

6. When CE is LOW and WE is HIGH, I/O pins are in the

output state, and input signals of opposite phase to the

outputs must not be applied.

7. The outputs are in a high impedance state when WE is

LOW.

8. CE and WE can initiate and terminate WRITE Cycle.

WAVEFORM KEY

Data Valid

Transition from

Transition from

Data Undefined

HIGH to LOW

LOW to HIGH

or Don't Care

30A129-92

REV. A

5

DPS1MX8MKN3-A

Dense-Pac Microsystems, Inc.

* Customer to be notified of changes to the die.

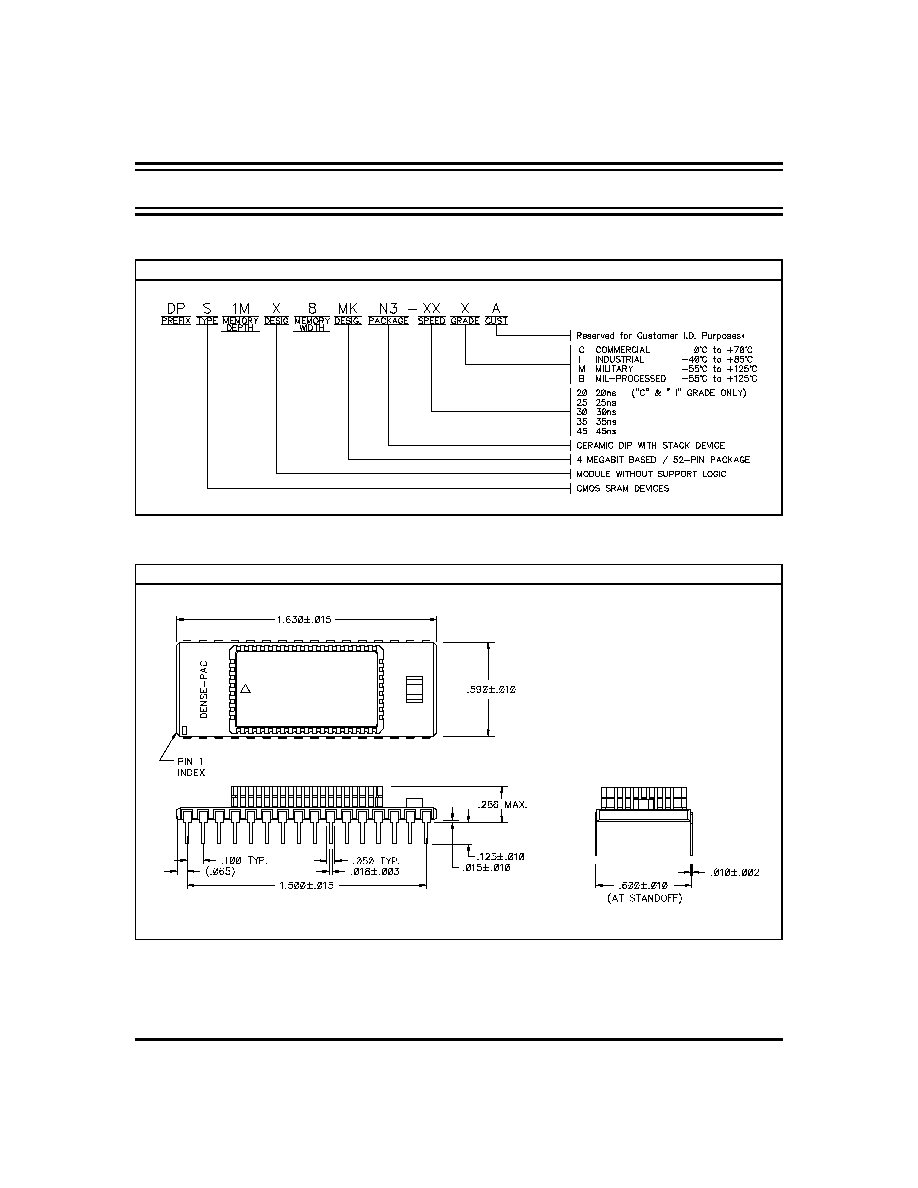

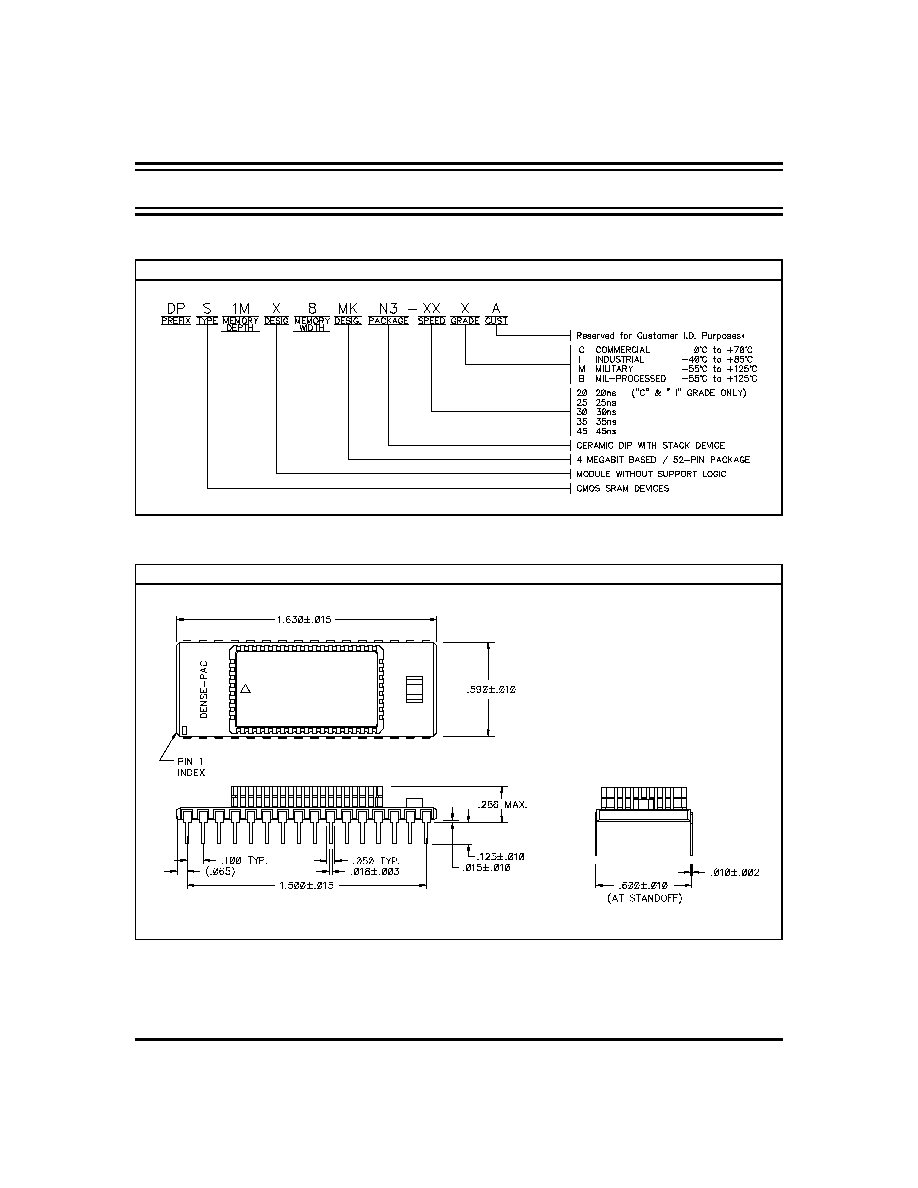

ORDERING INFORMATION

MECHANICAL DRAWING

Dense-Pac Microsystems, Inc.

7321 Lincoln Way, Garden Grove, California 92841-1431

(714) 898-0007 u (800) 642-4477 u FAX: (714) 897-1772 u http://www.dense-pac.com

30A129-92

REV. A

6