| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: V6173 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

EM MICROELECTRONIC--MARIN SA

V6173

1

Accurate Voltage Window Surveillance,

Software Monitoring and Chip Select

Features

n

Standby mode, maximum current 35

µ

A

n

Reset output guaranteed for V

DD

voltage

down to 1.2 V

n

Comparator for voltage monitoring,

voltage reference 1.17 V

n

±

1.5

%

voltage reference accuracy at + 25

∞

C

±

3

%

voltage reference accuracy for

-

40 to +85

∞

C

n

Programmable reset voltage monitoring

n

Voltage window, high threshold 5.9 V

n

Programmable power-on reset (POR) delay

n

Watchdog with programmable time window

guarantees a minimum time and a maximum time

between software clearing of the watchdog

n

Time base accuracy

±

10

%

n

System enable (EN) output offers added security

n

3 chip select feed-thru circuit controlled by EN

n

TTL / CMOS compatible

n

-

40 to +85

∞

C temperature range

n

DIP14 and SO14 packages

Description

The V6173 offers a high level of integration by voltage

monitoring and software monitoring in a 14 lead

package. A comparator monitors the voltage applied at

the V

IN

input comparing it with an internal 1.17 V

reference. The power-on reset function is initialized after

V

IN

reaches 1.17 V and takes the reset output inactive

after T

POR

depending of external resistance. The reset

output goes active low when the V

IN

voltage is less than

1.17 V or when V

DD

is higher than 5.9 V. The RES and EN

outputs are guaranteed to be in a correct state for a

supply voltage as low as 1.2 V. The watchdog function

monitors software cycle time and execution. If the

software clears the watchdog too quickly (incorrect cycle

time) or too slowly (incorrect execution), it will cause the

system to be reset. The system enable output prevents

critical control functions being activated until software

has successfully cleared the watchdog three times. Such

a security could be used to prevent motor controls being

energized on repeated resets of a faulty system.

Applications

n

Industrial electronics

n

Cellular telephones

n

Security systems

n

Battery powered products

n

Automotive electronics

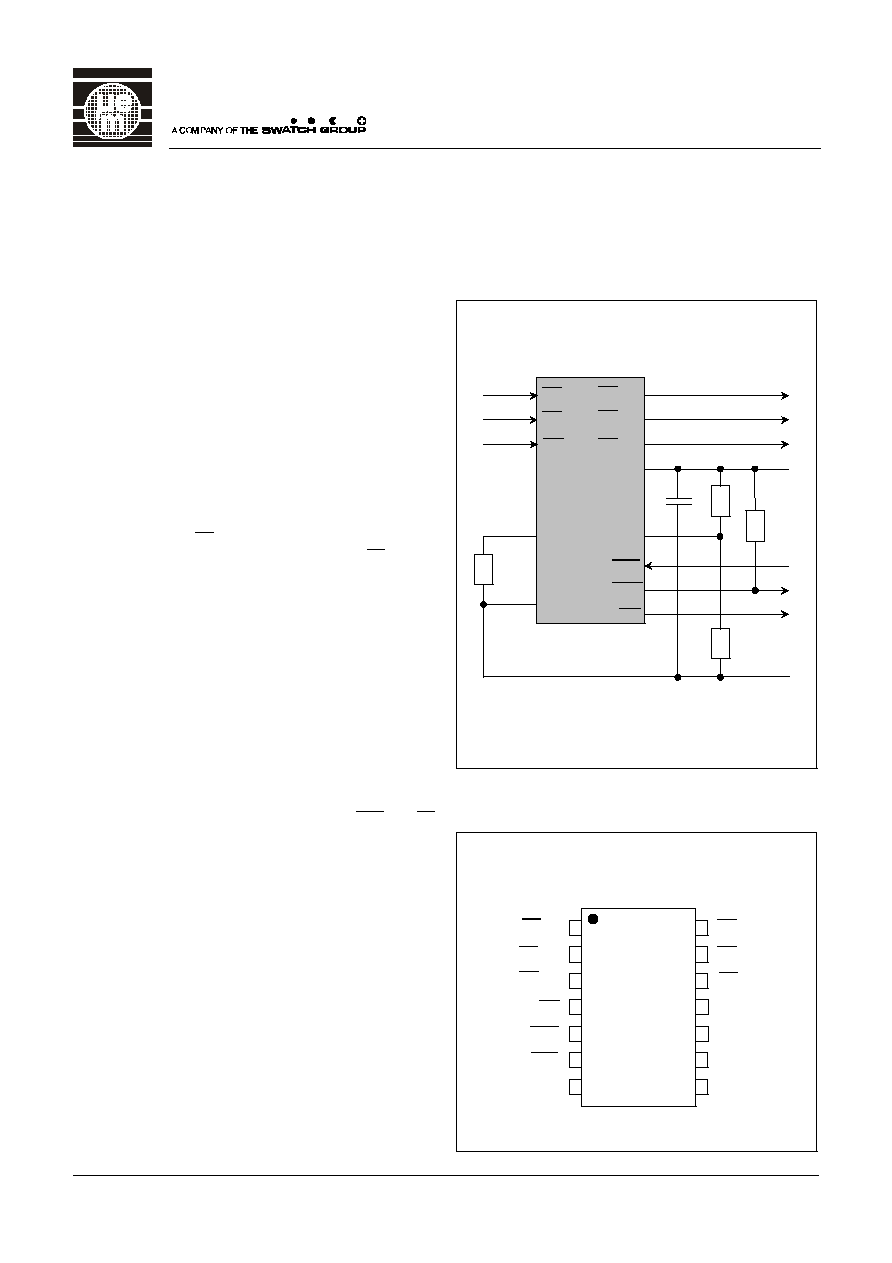

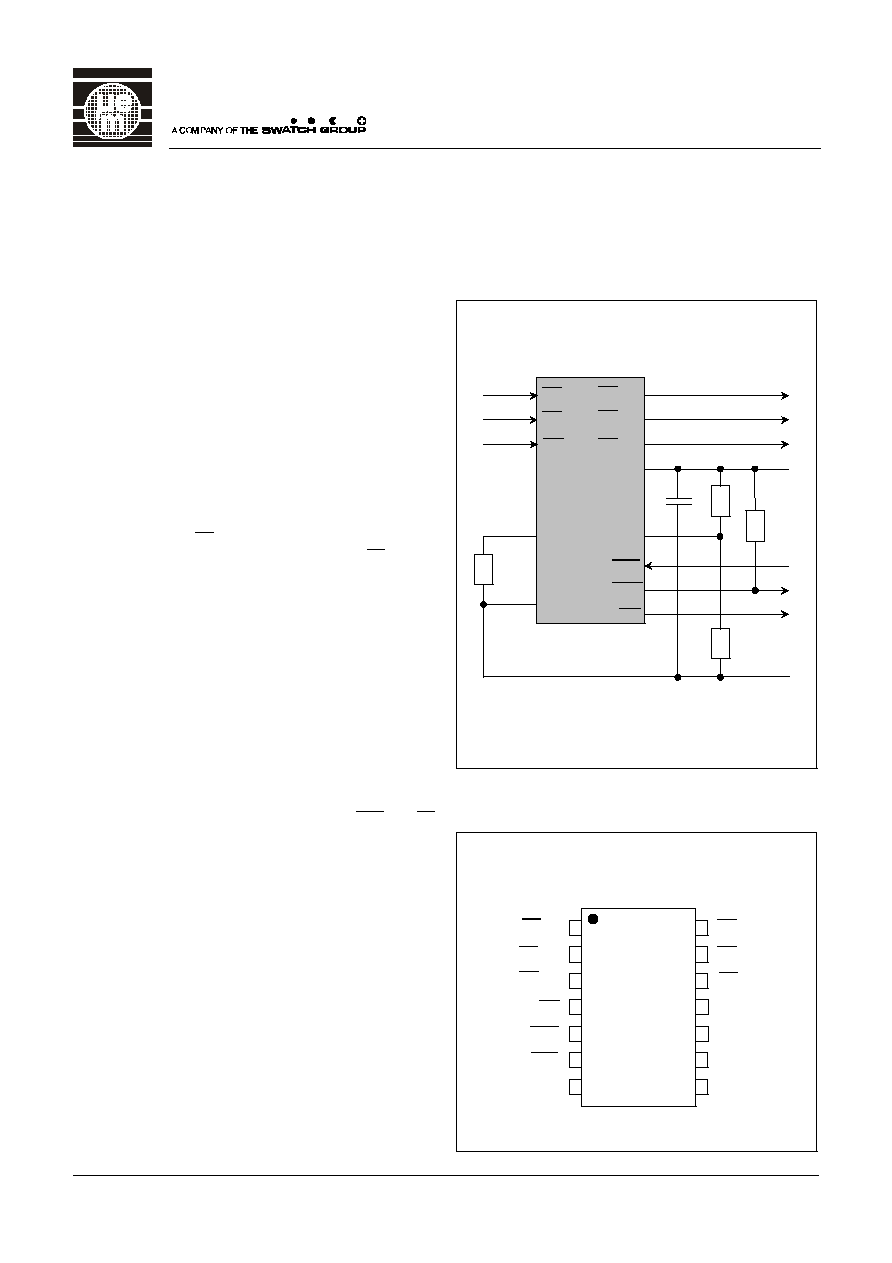

Typical Operating Configuration

Pin Assignment

R

V

SS

EN

TCL

V

IN

V

DD

Fig. 1

V6173

RES

GND

100 nF

CS

IN3

CS

IN2

CS

IN1

CS

OUT3

CS

OUT2

CS

OUT1

TCL

RES

V

IN

V

SS

EN

R

V

DD

NC

Fig. 2

DIP14 / SO14

V6173

CS

OUT3

CS

OUT2

CS

OUT1

CS

IN3

CS

IN2

CS

IN1

V6173

2

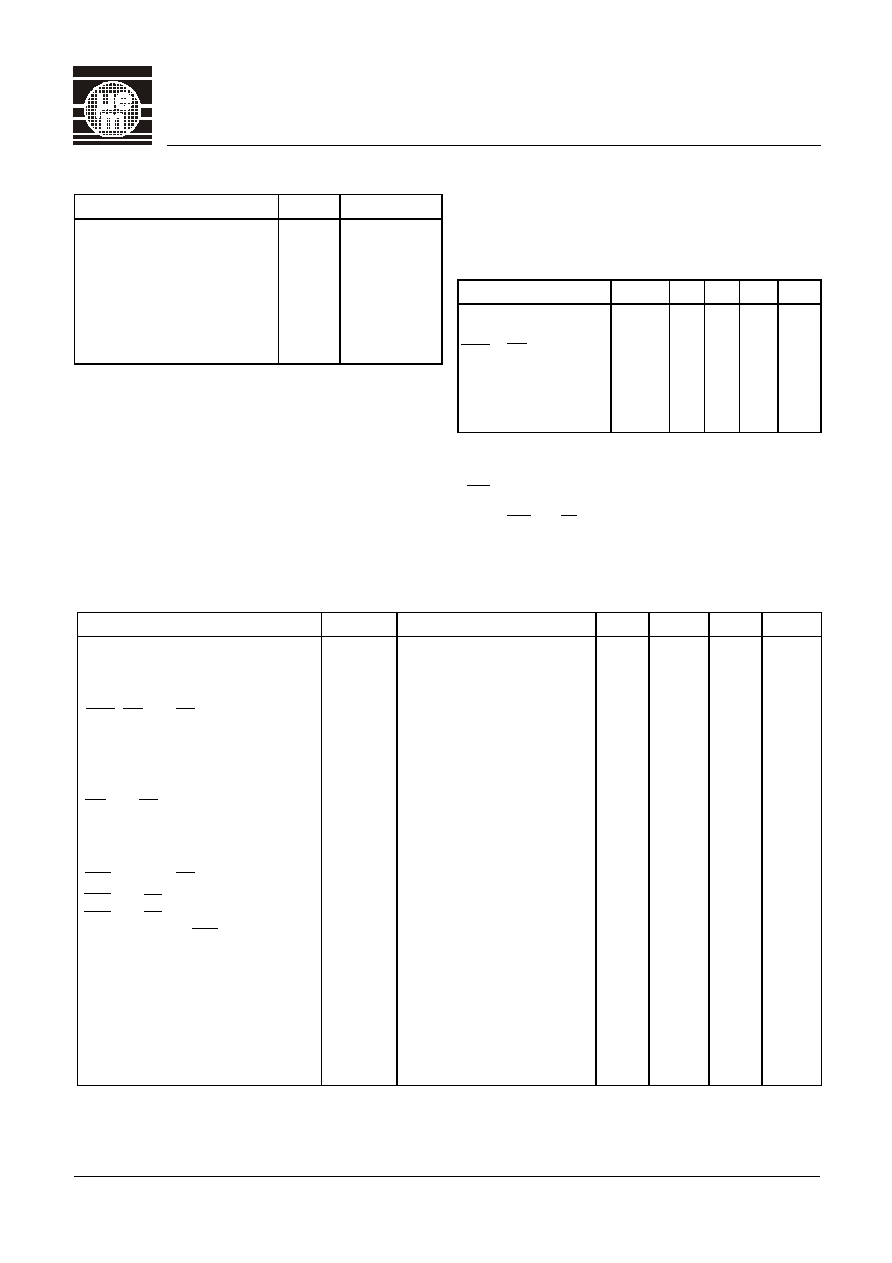

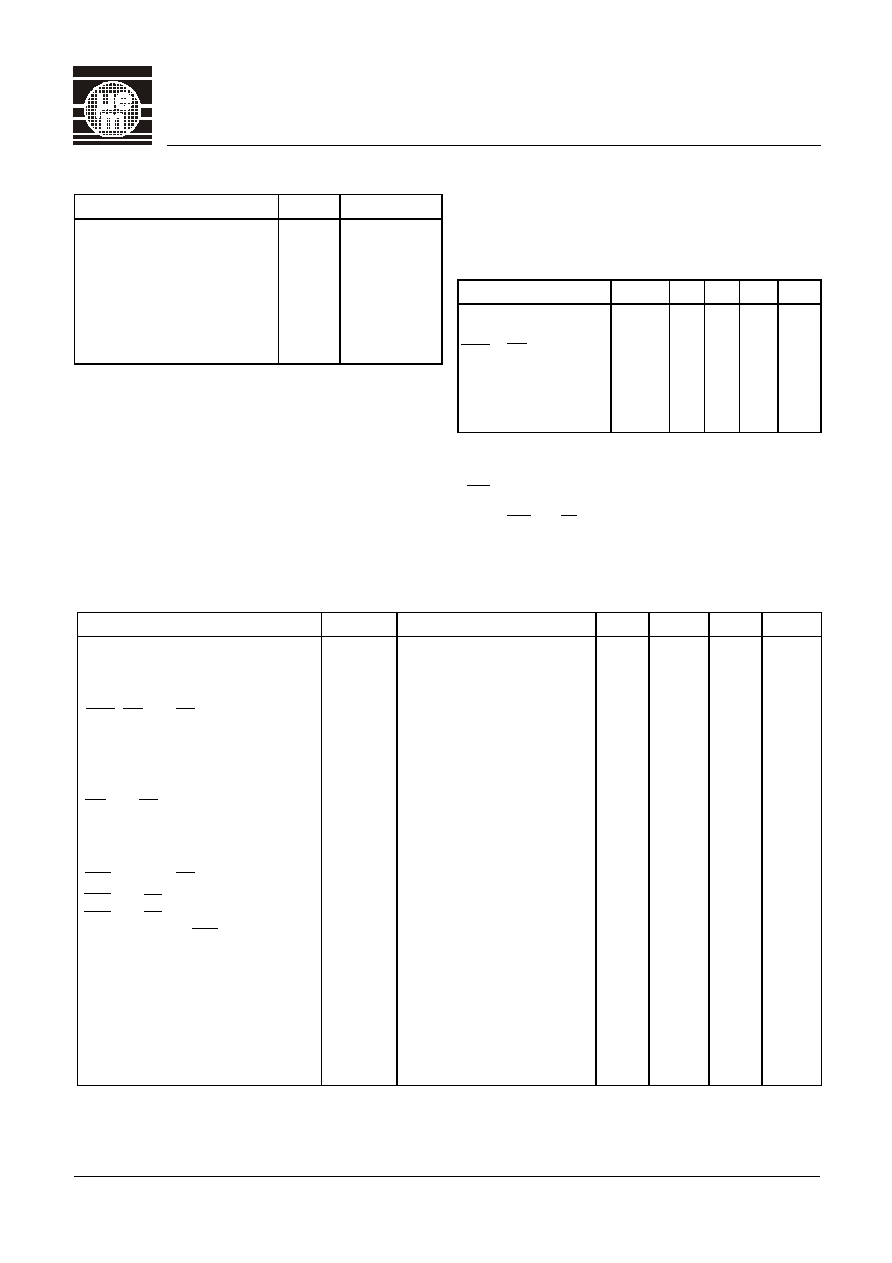

Absolute Maximum Ratings

Parameter

Symbol Conditions

Maximum voltage at V

DD

Minimum voltage at V

DD

Max. voltage at any signal pin

Min. voltage at any signal pin

Storage temperature

Electrostatic discharge max. to

MIL-STD-883C method 3015

Max. soldering conditions

V

DDmax

V

DDmin

V

MAX

V

MIN

T

STO

V

Smax

T

Smax

V

SS

+ 8 V

V

SS

-

0.3 V

V

DD

+ 0.3 V

V

SS

-

0.3 V

-65 to+150

∞

C

1000 V

250

∞

C x 10 s

Table 1

Stresses above these listed maximum ratings may cause

permanent damage to the device. Exposure beyond

specified operating conditions may affect device

reliability or cause malfunction.

Handling Procedures

This device has built-in protection against high static

voltages or electric fields; however, anti-static

precautions must be taken as for any other CMOS

component. Unless otherwise specified, proper

operation can only occur when all terminal voltages are

kept within the supply voltage range. Unused inputs

must always be tied to a defined logic voltage level.

Operating Conditions

Parameter

Symbol Min. Typ. Max. Units

Operating temperature

Supply voltage

1)

& guaranteed

2)

Comparator input

voltage

RC-oscillator

programming

T

A

V

DD

V

DD

V

IN

R

-40

1.2

1.2

0

10

+85

7

V

DD

1000

∞

C

V

V

V

k

Table 2

1)

A 100 nF decoupling capacitor is required on the

supply voltage V

DD

for stability.

2)

RES must be pulled up externally to V

DD

event if it is

unused.

(Note: RES and EN are used as inputs by EM test.)

Electrical Characteristics

3

V

DD

5.5 V, C = 100 nF, T

A

= -40 to +85

∞

C, unless otherwise specified

Parameter

Symbol

Test Conditions

Min.

Typ.

Max.

Units

Supply current in standby mode

Supply current

RES, EN and CS

OUT1/2/3

Output Low Voltage

EN and CS

OUT1/2/3

Output High Voltage

TCL , V

IN

and CS

IN1/2/3

TCL and CS

IN1/2/3

Input Low Level

TCL and CS

IN1/2/3

Input High Level

Leakage current TCL input

V

IN

input resistance

Comparator reference

1)

Comparator hysteresis

1)

Level detector of V

DD

2)

Hysteresis

2)

I

SS

I

SS

V

OL

V

OL

V

OL

V

OL

V

OH

V

OH

V

OH

V

IL

V

IH

I

LI

R

VIN

V

REF

V

REF

V

REF

V

HY1

V

HIGH

V

HIDH

V

HY2

R

EXT

= don't care, TCL = V

DD

,

V

IN

= 0 V

R

EXT

= 100 k

, I/Ps at V

DD

O/Ps 1 M

to V

DD

V

DD

= 4.5 V, I

OL

= 20 mA

V

DD

= 4.5 V, I

OL

= 8 mA

V

DD

= 2.0 V, I

OL

= 4 mA

V

DD

= 1.2 V, I

OL

= 0.5 mA

V

DD

= 4.5 V, I

OH

=

-

1 mA

V

DD

= 2.0 V, I

OH

=

-

100

µ

A

V

DD

= 1.2 V, I

OH

=

-

30

µ

A

3V

V

DD

5.5 V

3V

V

DD

5.5 V

V

SS

V

TCL

V

DD

T

A

= +25

∞

C

T

A

=

-

20 to +70

∞

C

T

A

= +25

∞

C

T

A

=

-

40 to +70

∞

C

3.5

1.8

1.0

V

SS

2.0

1.148

1.123

1.123

5.78

5.60

24

55

0.4

0.2

0.2

0.06

4.1

1.9

1.1

0.05

100

1.170

2

5.95

50

35

100

0.4

0.4

0.2

0.8

V

DD

1

1.200

1.218

1.222

6.12

6.30

µ

A

µ

A

V

V

V

V

V

V

V

V

V

µ

A

M

V

V

V

mV

V

V

mV

1)

The comparator reference is the power-down reset threshold. The power-on reset threshold equals the comparator

Table3

reference voltage plus the comparator hysteresis (see Fig. 6).

2)

The level detector of V

DD

(V

HIGH

) is the level when V

DD

is rising. The level detector when V

DD

is falling equals V

HIGH

minus

the hysteresis (V

HY2

) (see Fig. 6).

RES

EN

V6173

3

I

SS

Standby versus Temperature at V

DD

= 5.5 V

Timing Characteristics

V

DD

= 5.0 V

±

3

%

, C = 100 nF, T

A

=

-

40 to

+

85

∞

C, unless otherwise specified

Parameter

Symbol

Test Conditions

Min.

Typ.

Max. Units

Propagation delays:

to Output Pins

CS

INx

to CS

OUTx

at rising edge

CS

INx

to CS

OUTx

at falling edge

V

IN

sensitivity

Logic Transition Times on all Output Pins

Power-on Reset delay

Watchdog Time

Open Window Percentage

Closed Window Time

Open Window Time

Watchdog Reset Pulse

T

CL

Input Pulse Width

T

DIDO

T

CSH

T

CSL

T

SEN

T

TR

T

POR

T

WD

OWP

T

CW

T

CW

T

OW

T

OW

T

WDR

T

WDR

T

TCL

Load 10 k

, 50 pF

R

EXT

= 118 k

,

±

1%

R

EXT

= 118 k

,

±

1%

R

EXT

= 118 k

,

±

1%

R

EXT

= 118 k

,

±

1%

R

EXT

= 118 k

,

±

1%

1

90

90

72

36

150

250

125

75

5

30

100

100

±

0.2 T

WD

0.8 T

WD

80

0.4 T

WD

40

T

WD

/ 40

2.5

500

200

150

20

100

110

110

88

44

ns

ns

ns

µ

s

ns

ms

ms

ms

ms

ms

ns

Table 4

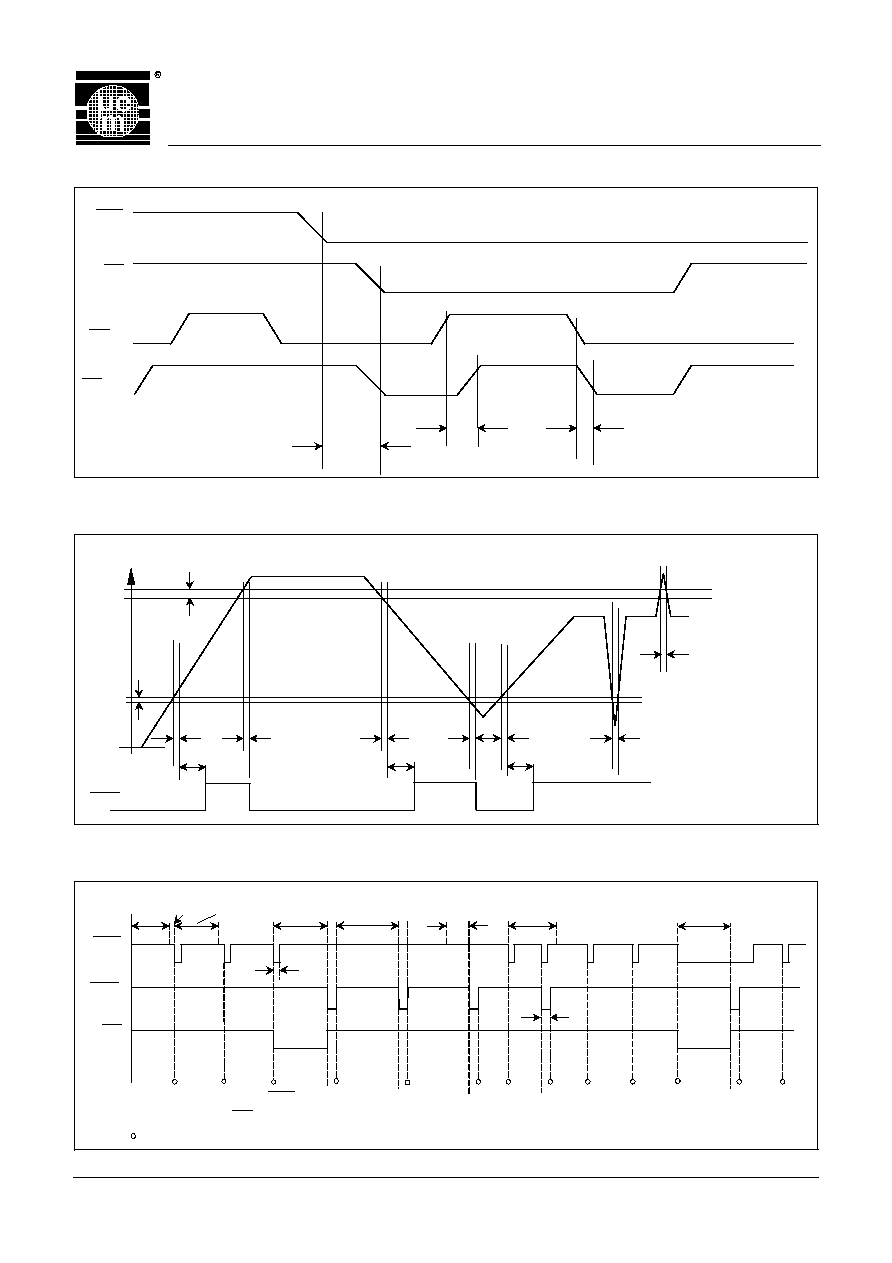

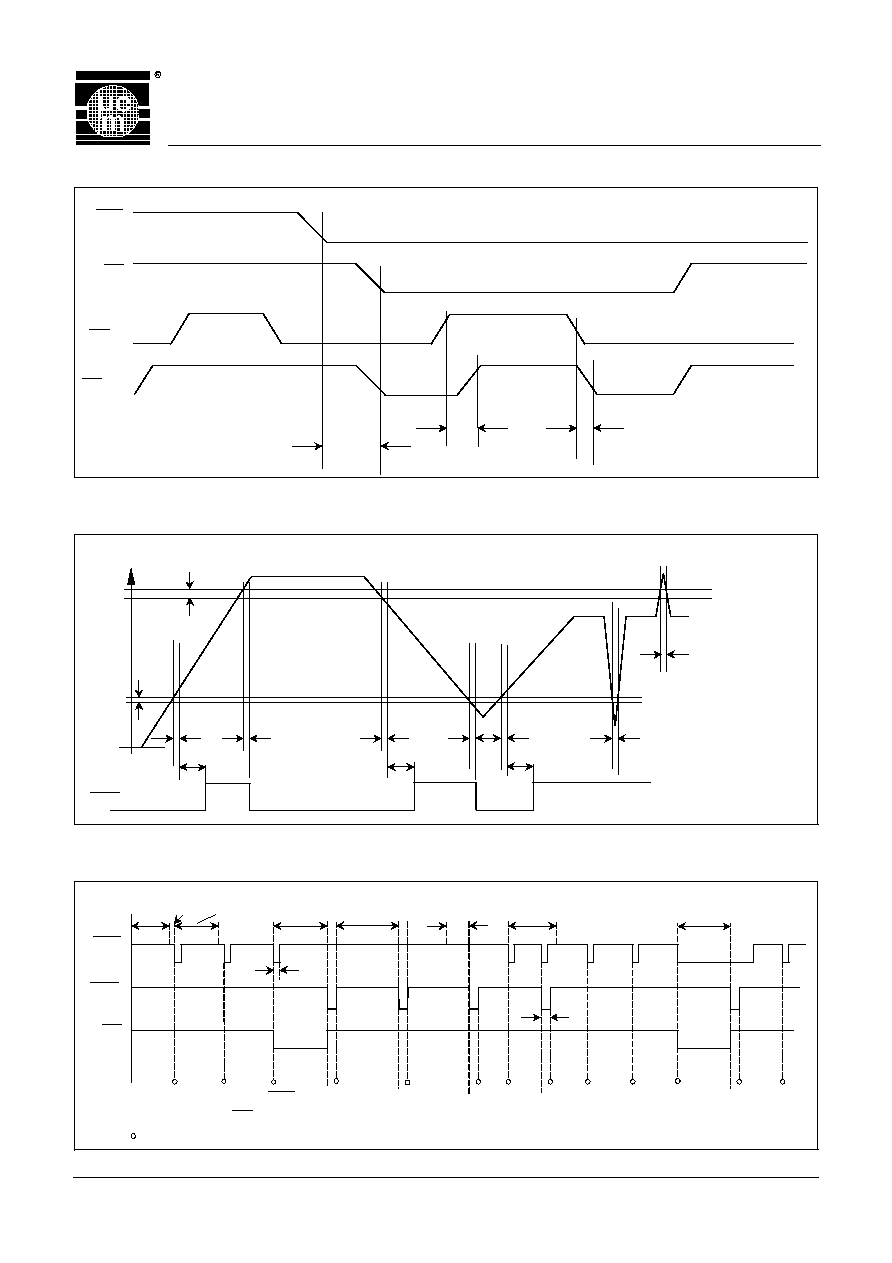

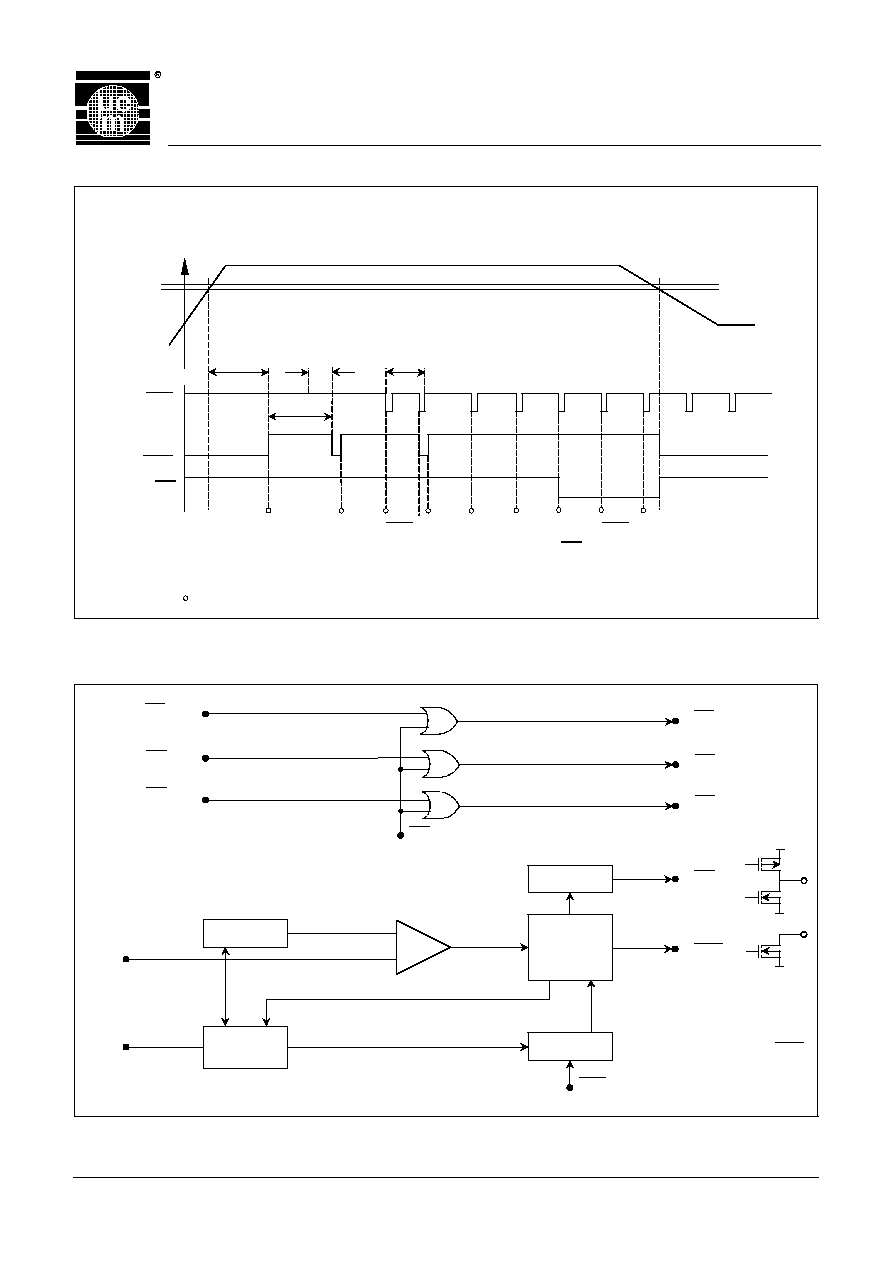

Timing Waveforms

Watchdog Timeout Period

TCL

T

WD

= T

POR

T

CW

≠ closed window

T

OW

≠ open window

Watchdog

timer reset

Condition:

R

EXT

= 115 k

-

OWP

-

20%

+ OWP

+ 20%

80

100

120

Fig. 4

t [ms]

10

12

14

16

18

18

20

24

22

26

28

30

I

SS

[

µ

A]

-

10

0

-

20

-

30

-

40

10

20

30

40

50

60

70

80

T

A

[

∞

C]

Fig. 3

V6173

4

Chip Select

Voltage Monitoring

Timer Reaction

V

Condition:

V

DD

3 V

Fig. 6

RES

T

POR

V

REF

V

HIGH

No timeout

T

POR

T

POR

V

HY1

V

HY2

T

SEN

T

SEN

T

SEN

T

SEN

T

SEN

T

SEN

T

SEN

T

TCL

T

OW

Fig. 7

- Watchdog timer reset

Conditions: V

IN

>

V

REF

after power-up sequence

TCL

RES

EN

EN

3 correct TCL services

goes active low

1

2

3

Timeout

T

CW

+T

OW

T

CW

T

CW

+T

OW

T

CW

T

CW

+T

OW

T

CW

T

OW

T

WDR

EN

TCL

T

DIDO

T

CSL

T

CSH

Fig. 5

CS

INx

CS

OUTx

V6173

5

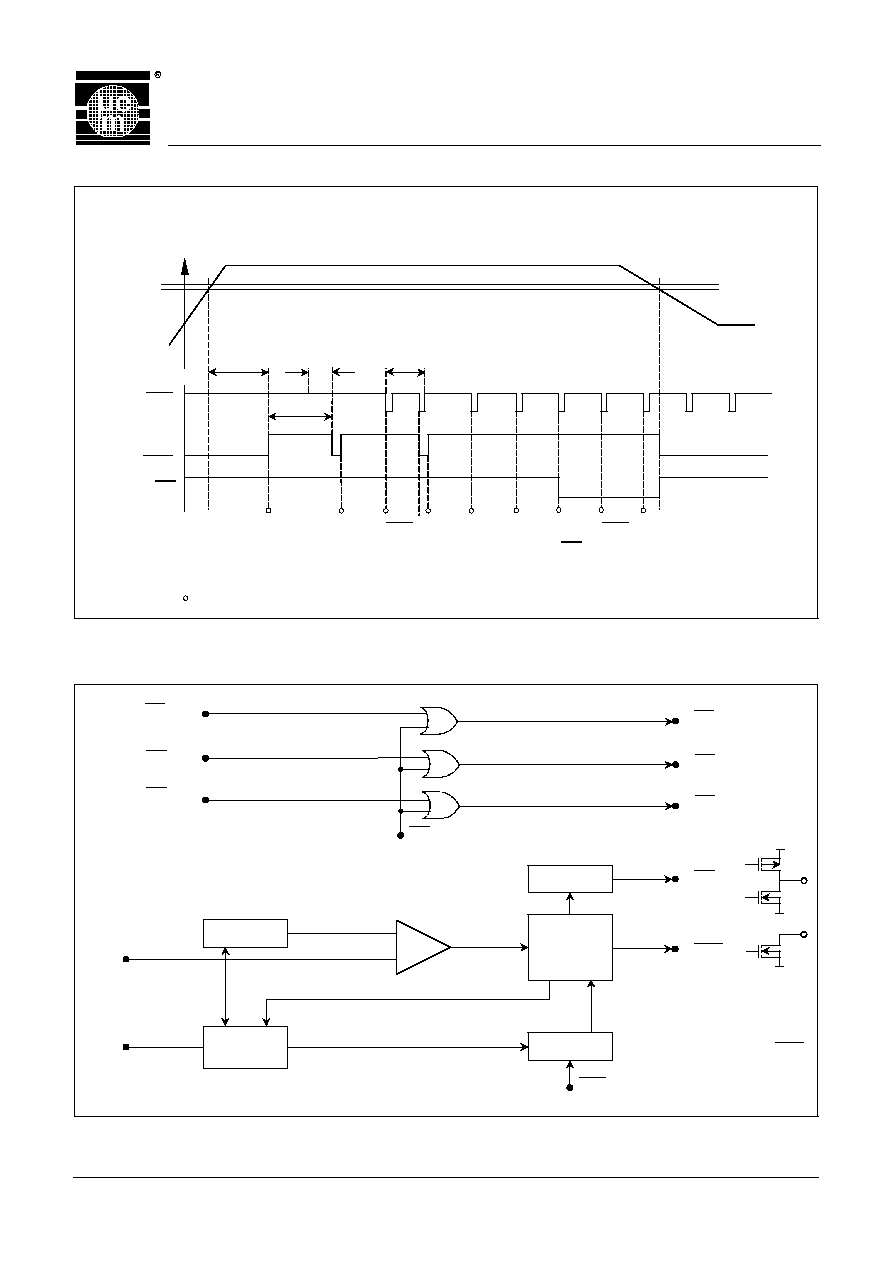

Combined Voltage and Timer Reaction

Block Diagram

T

CW

+T

OW

T

POR

=T

WD

T

OW

T

CW

V

IN

V

REF

Condition:

V

DD

3 V

Fig. 8

TCL

TCL

RES

EN

too early

3 correct TCL service

EN goes active low

- Watchdog timer reset

1

2

3

-

+

EN

RES

EN

TCL

Fig. 9

V

REF

R

V

IN

Open drain

output RES

Current

Controlled

Oscillator

Voltage

Reference

Enable

Logic

Timer

Reset

Control

Comparator

CS

IN1

CS

IN2

CS

IN3

CS

OUT2

CS

OUT3

CS

OUT1

V6173

6

Pin Description

Pin Name

Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

CS

OUT3

CS

OUT2

CS

OUT1

V

SS

NC

V

DD

R

V

IN

CS

IN1

CS

IN2

CS

IN3

Push-pull active low chip select output 3

Push-pull active low chip select output 2

Push-pull active low chip select output 1

Push-pull active low enable output

Open drain active low reset output.

must be pulled up to V

DD

even

if unused

Watchdog timer clear input signal

GND terminal

No connection

Voltage supply

R

EXT

input for RC oscillator tuning

Voltage comparator input

Chip select input 1

Chip select input 2

Chip select input 3

Table 5

Functional Description

V

IN

Monitoring

The power-on reset and the power-down reset are

generated as a response to the external voltage level on

the V

IN

input. The external voltage level is typically

obtained from a voltage divider as shown in Fig. 10. The

user defines an external voltage divider to set the

desired threshold level for power-on reset and power-

down reset in his system. The internal comparator

reference voltage is typically 1.17 V.

At power-up the reset output (RES)

is held low (see Fig.

6). When V

IN

becomes greater than V

REF

, the RES output

is held low for an additional power-on reset (POR) delay

which is equal to the watchdog time T

WD

(typically 100

ms with an external resistor of 115 k

connected at R

pin). The POR delay prevents repeated toggling of RES

even if V

IN

and the INPUT voltage drops out and

recovers. The POR delay allows the microprocessor's

crystal oscillator to start and stabilize and ensures

correct recognition of the reset signal to the

microprocessor.

The RES output goes active low generating the power-

down reset whenever V

IN

falls below V

REF

. The sensitivity

or reaction time of the internal comparator to the voltage

level on V

IN

is typically 5

µ

s.

Voltage Window

The reset output (RES) is inactive when V

IN

is higher than

V

REF

and when V

DD

is lower than V

HIGH

. If V

IN

is less than

V

REF

or V

DD

higher than V

HIGH

, the reset output goes active

low (see Fig. 6).

Timer Programming

The on-chip oscillator needs an external resistor R

EXT

connected between the R pin and V

SS

(see Fig.

10). It

allows the user to

adjust the power-on reset (POR)

delay, watchdog time T

WD

and with this also the closed

and open time windows as well as the watchdog reset

pulse width (T

WD

/40).

With R

EXT

= 115 k

, the typical delays are:

- Power-on reset delay: T

POR

is 100 ms

- Watchdog time:

T

WD

is 100 ms

- Closed window:

T

CW

is 80 ms

- Open window:

T

OW

is 40 ms

- Watchdog reset:

T

WDR

is 2.5 ms

Note the current consumption increases as the

frequency increases.

Watchdog Timeout Period Description

The watchdog timeout period is divided into two parts, a

"closed" window and an "open" window (see

Fig. 4) and

is

defined by two parameters, T

WD

and the Open Window

Percentage (OWP).

The closed window starts just after the watchdog timer

resets and is defined by T

CW

= T

WD

-

OWP(T

WD

).

The open window starts after the closed time window

finishes and lasts till T

WD

+ OWP(T

WD

). The open window

time is defined by T

OW

= 2 x OWP(T

WD

).

For example if T

WD

= 100 ms (actual value) and OWP =

±

20% this means the closed window lasts during first

the 80 ms (T

CW

= 80 ms = 100 ms

-

0.2 (100 ms)) and

the open window the next 40 ms (T

OW

= 2 x 0.2 (100 ms)

= 40 ms). The watchdog can be serviced between 80

ms and 120 ms after the timer reset. However as the

time base is

±

10% accurate, software must use the

following calculation for servicing signal TCL during the

open window:

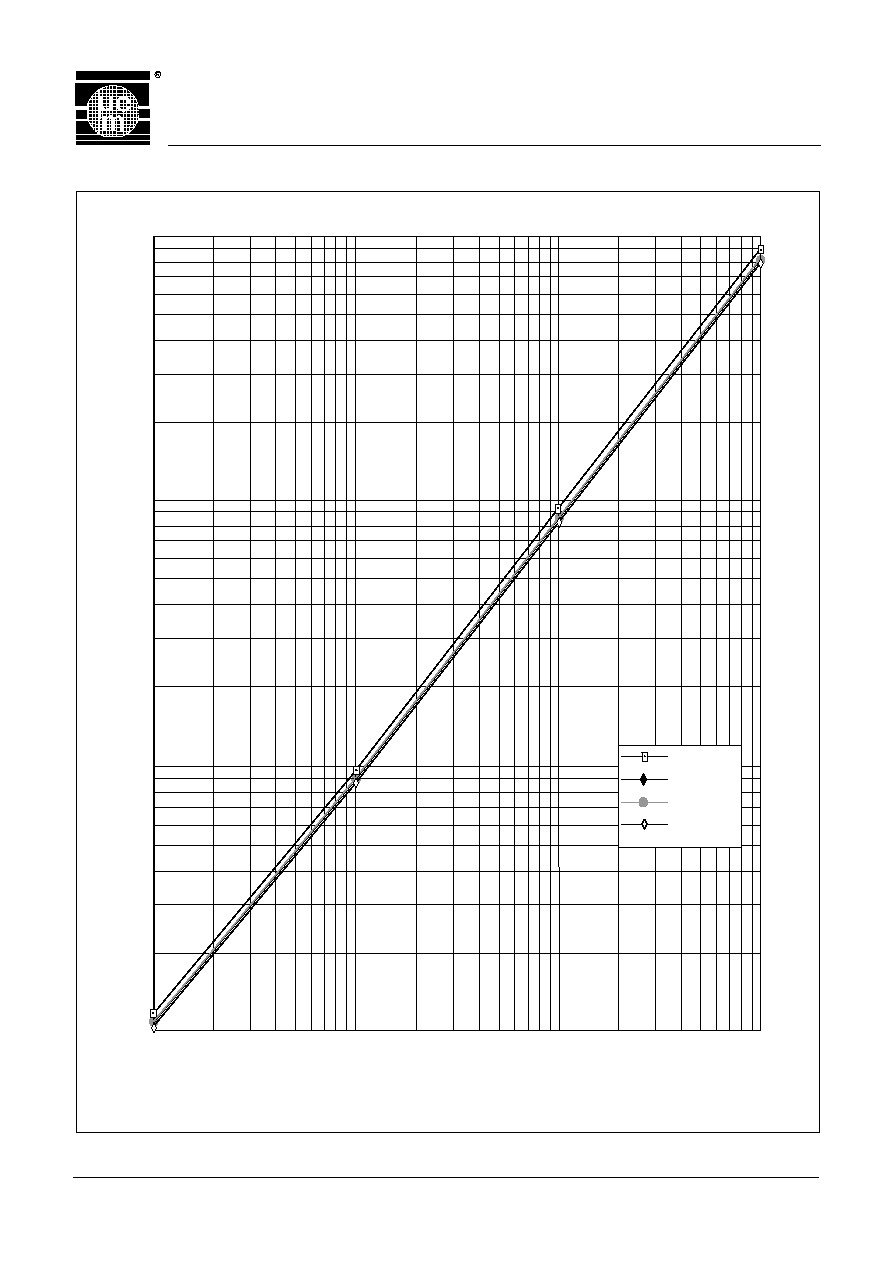

Related to curves (Fig. 11 to Fig. 21), especially Fig. 20

and Fig. 21, the relation between T

WD

and R

EXT

could

easily be defined. Let us take an example describing the

variations due to production and temperature:

1. Choice, T

WD

= 26 ms.

2. Related to Fig. 21, the coefficient (T

WD

to R

EXT

) is 1.125

where R

EXT

is in k

and T

WD

in ms.

3. R

EXT

(typ.) = 26 x 1.125 = 29.3 k

.

4. 26 ms at +25

∞

C

a)

(26

-

10% = 23.4 ms) (26 + 10% = 28.6 ms)

a)

b)

(23.4

-

5% = 22.2 ms) (28.6 + 5% = 30.0 ms)

b)

min.: (30.0

-

20% = 24.0 ms) max.: (22.2 + 20% = 26.7 ms)

Typical TCL period of

(24.0 + 26.7) / 2 = 25.4 ms

The ratio between T

WD

= 26 ms and the (TCL period) =

25.4 ms is 0.975.

EN

RES

RES

TCL

V6173

7

Then the relation over the production and the full

temperature range is, TCL period = 0.975 x T

WD

or TCL period = , as typical value.

a) While PRODUCTION value unknown for the custo-

mer when R

EXT

118 k

.

b) While operating TEMPERATURE range

-

40

∞

C

T

A

+85

∞

C.

5. If you fixed a TCL period = 26 ms

R

EXT

= 30 k

If during your production the T

WD

time can be

measured, at T

A

= +25

∞

C and the

µ

C can adjust

the

TCL period, then

the TCL period range will be much

larger for the full operating temperature.

Timer Clearing and RES Action

The watchdog circuit monitors the activity of the

processor. If the user's software does not send a pulse

to the TCL input within the programmed open window

timeout period, a short watchdog RES pulse is

generated which is equal to T

WD

/40 = 2.5 ms typically

(see Fig. 7).

With the open window constraint, new security is added

to conventional watchdogs by monitoring both software

cycle time and execution. Should software clear the

watchdog too quickly (incorrect cycle time) or too slowly

(incorrect execution), it will cause the system to be reset.

If the software is stuck in a loop which includes the

routine to clear the watchdog, a conventional watchdog

will not reset the system even though the software is

malfunctioning; the V6173 will generate a system reset

because the watchdog is cleared too quickly.

If no TCL pulse is applied before the closed and open

windows expire, RES will start to generate square waves

of period (T

CW

+ T

OW

+ T

WDR

). The watchdog will remain

in this state until the next TCL falling edge appears

during an open window, or until a fresh power-up

sequence. The system enable output, EN, can be used

to prevent critical control

functions being activated in the

event of the system going into this failure mode (see

section "Enable

-

EN Output").

The RES output must be pulled up to V

DD

even if the

output is not used by the system (see Fig. 10).

Combined Voltage and Timer Action

The combination of voltage and timer actions is

illustrated by the sequence of events shown in Fig. 8. On

power-up, when the voltage at V

IN

reaches V

REF

, the

power-on reset, POR, delay is initialized and holds RES

active for the time of the POR delay. A TCL pulse will

have no effect until this power-on reset delay is

completed. After the POR delay has elapsed, RES goes

inactive and the watchdog timer starts acting. If no TCL

pulse occurs, RES goes active low for a short time T

WDR

after each closed and open window period. A TCL pulse

coming during the open window clears the watchdog

timer. When the TCL pulse occurs too early (during the

closed window), RES goes active and a new timeout

sequence starts. A voltage drop below the V

REF

level for

longer than

typically 5

µ

s, overrides the timer and

immediately forces RES active and EN inactive. Any

further TCL pulse has no effect until the next power-up

sequence has completed.

Enable

--

EN Output

The system enable output, EN, is inactive always when

RES is active and remains inactive after a RES pulse

until the watchdog is serviced correctly 3 consecutive

times (ie. the TCL pulse must come in the open

window). After three consecutive services of the

watchdog

with TCL during the open window, the EN

goes active low.

A malfunctioning system would be repeatedly reset by

the watchdog. In a conventional system critical motor

controls could be energized each time reset goes

inactive (time allowed for the system to restart) and in

this way the electrical motors driven by the system could

function out of control. The V6173 prevents the above

failure mode by using the EN output to disable the motor

controls until software has successfully cleared the

watchdog three times (ie. the system has correctly

restarted after a reset condition)

0.975 x R

EXT

1.125

26 x 1.125

0.975

V6173

8

Typical Application

V

DD

TCL

RES

R

V6173

RD

WR

RAM

CS

V3023

D0

WEN

Wcl. FIFO

I/O

CPU

Y1

A/D

Addr. Dec.

Interface

Supply Voltage

Periphery

100 k

100

k

Fig. 10

V

IN

V

SS

R2

R1

EN

V

SS

Y2 Y3

RES

A/D

V

SS

V

DD

I/O

V

DD

V

DD

A/D

RD

WR

A/D

CS

WR

RD

D7

V

DD

V

DD

D0...D7

V

SS

EN

V

DD

EN

CS

OUT3

CS

OUT2

CS

OUT1

CS

IN3

CS

IN2

CS

IN1

V6173

9

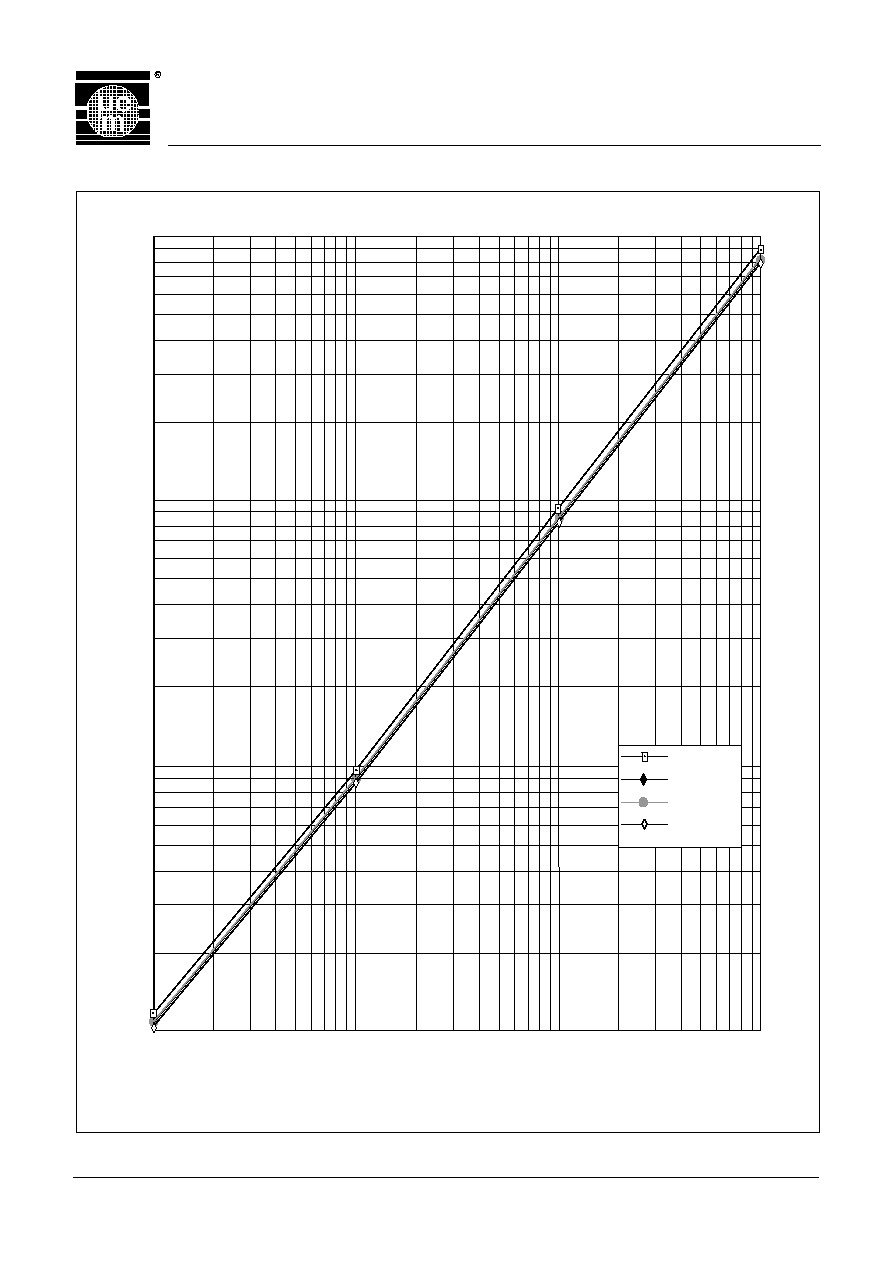

T

WD

versus Temperature at 5 V

T

WD

versus R at 5 V

T

WD

versus V

DD

at T

A

=

+

+

25

∞

∞

C

T

WD

versus R at T

A

=

+

+

25

∞

∞

C

+

85

Fig. 11

-

40

-

20

+

25

T

A

[

∞

C]

10'000

1000

100

10

1

T

WD

[ms]

R = 10 M

R = 1 M

R = 100 k

R = 10 k

1

-

40 to 85

∞

C

10'000

1000

100

10

10'000

1000

100

10

1

T

WD

[ms]

R [k

]

Fig. 12

Fig. 13

10'000

1000

100

10

3.0

4.0

5.0

V

DD

[V]

T

WD

[ms]

R = 10 M

R = 1 M

R = 100 k

R = 10 k

10'000

1000

100

10

10

100

1000

10'000

R [k

]

Fig. 14

T

WD

[ms]

3 V

4.5 V

5 V

5.5 V

V6173

10

T

WD

versus R at T

A

= +25

∞

∞

C

3 V

4.5 V

5 V

5.5 V

10'000

1000

100

10

10

100

1000

10'000

R [k

]

Fig. 15

T

WD

[ms]

V6173

11

T

WD

versus V

DD

at T

A

=

+

+

85

∞

∞

C

T

WD

versus R at T

A

=

+

+

85

∞

∞

C

T

WD

versus V

DD

at T

A

=

-

-

40

∞

∞

C

T

WD

versus R at T

A

=

-

-

40

∞

∞

C

Fig. 16

10'000

1000

100

10

3.0

4.0

5.0

V

DD

[V]

R = 10 M

R = 1 M

R = 100 k

R = 10 k

T

WD

[ms]

10'000

1000

100

10

10

100

1000

10'000

R [k

]

Fig. 17

T

WD

[ms]

3 V

4.5 V

5 V

5.5 V

10'000

1000

100

10

1

3.0

4.0

5.0

V

DD

[V]

Fig. 18

T

WD

[ms]

R = 10 M

R = 1 M

R = 100 k

R = 10 k

10'000

1000

100

10

10

100

1000

10'000

R [k

]

Fig. 19

T

WD

[ms]

3 V

4.5 V

5 V

5.5 V

V6173

12

T

WD

Coefficient versus R

EXT

at T

A

=

+

+

25

∞

∞

C

R

EXT

Coefficient versus T

WD

at T

A

=

+

+

25

∞

∞

C

1.00

0.98

0.96

0.94

0.92

0.90

0.88

0.86

0.84

0.82

0.80

T

WD

Coefficient

10

1000

100

R

EXT

[k

]

Fig. 20

Fig. 21

1.24

1.22

1.20

1.18

1.16

1.14

1.12

1.10

1.08

1.06

1.04

1.02

1.00

R

EXT

Coefficient

10

100

1000

T

WD

[ms]

V6173

13

Ordering Information

The V6173 is available in the following packages:

Type Package

V6173 14P DIP14

V6173 14S SO14

When ordering please specify complete part number.

© 1997 EM Microelectronic-Marin SA, 09/97, Rev. C/169

EM Microelectronic-Marin SA cannot assume any responsibility for use of any circuitry described other than entirely

embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the

circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given

has not been superseded by a more up-to-date version.

EM Microelectronic-Marin SA, CH - 2074 Marin, Switzerland, Tel. (+41) 32 - 755 51 11, Fax (+41) 32 - 755 54 03