Rev 1.0 ≠ July 2005 www.enpirion.com

1

EN5330

3A Voltage Mode Synchronous Buck PWM

DC-DC Converter

Description

The EN5330 is a Power System on a Chip DC-DC

converter. It is specifically designed to meet the

precise voltage and fast transient requirements of

present and future high-performance, low-power

processor, DSP, FPGA, memory boards and system

level applications in a distributed power architecture.

Advanced circuit techniques, ultra high switching

frequency, and very advanced, high-density,

integrated circuit and proprietary inductor technology

deliver high-quality, ultra compact, non-isolated DC-

DC conversion. Operating this converter requires only

three external components that include small value

input and output ceramic capacitors and a soft-start

capacitor.

The EN5330 significantly helps in system design and

productivity by offering greatly simplified board

design, layout and manufacturing requirements. In

addition, a reduction in the number of vendors

required for the complete power solution helps to

enable an overall system cost savings.

Typical Application Circuit

VID Output

Voltage Select

V

OUT

V

IN

VSENSE

47

µ

F

22

µ

F

15nF

VOUT

VS0

VS1

VS2

POK

PGND

AGND

SS

PVIN

AVIN

Features

∑ Up to 10W output power (at V

OUT

=3.3V)

∑ External inductor is NOT required

∑ Lead-Free packaging

∑ 5MHz operating frequency

∑ More than 90% efficient

∑ V

OUT

accuracy of 2% over line, load and

temperature

∑ 1/3 the board area of discrete component solutions

∑ Very fast transient response

∑ All high speed switching signals contained inside

the part

∑ Wide input voltage range of 2.375V to 5.5V

∑ Digital voltage selector with options for common

output voltages from 0.8V to 3.3V

∑ External resistor divider and OVP option for

output voltages from 0.8V to V

IN

-600mV

∑ Output enable pin and Power OK signal

∑ Programmable soft-start time

∑ Over-current protection

∑ Thermal shutdown, short circuit, output over-

voltage and input under-voltage protection

Applications

∑ Servers, workstations and PCs

∑ Broadband, networking, LAN/WAN, optical

telecommunications equipment

∑ Point of load regulation for low-power processors,

network processors, DSPs, FPGAs, and ASICs

∑ Low voltage, distributed power architectures with

2.5V, 3.3V or 5V rails

Ordering Information

Part Number

Temp Rating (∞C)

Package

EN5330DC

0 to 70

36-pin DFN

EN5330DC-T

0 to 70

36-pin DFN T&R

EN5330DI

-40 to +85

36-pin DFN

EN5330DI-T

-40 to +85

36-pin DFN T&R

EN5330DC-E

DFN Evaluation Board

Rev 1.0 ≠ July 2005

www.enpirion.com

EN5330

4

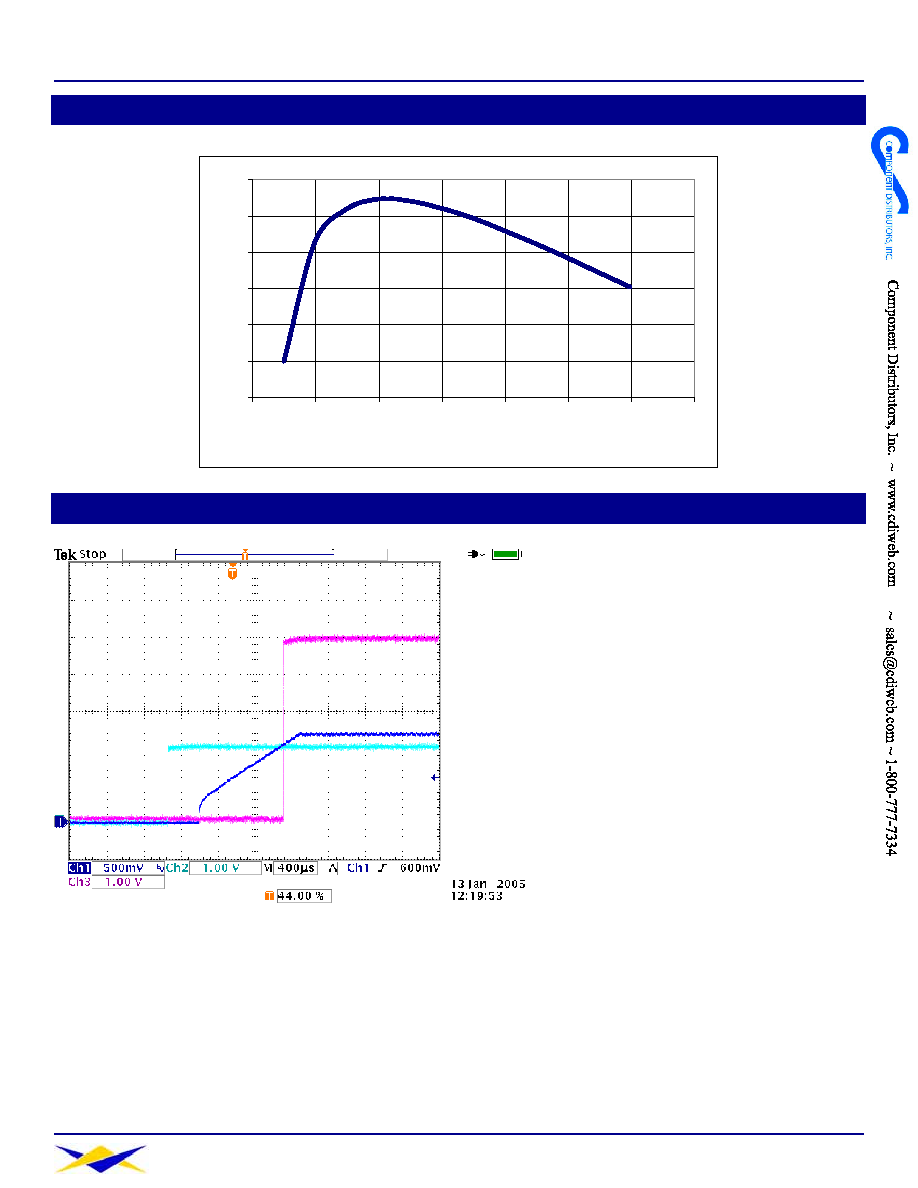

5Vin / 1.2Vout

0-3A Load step

Absolute Maximum Ratings

CAUTION: Stresses in excess of the absolute maximum ratings may cause permanent damage to the device.

Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

PARAMETER

SYMBOL MIN

MAX UNITS

Input Supply Voltage

V

IN

-0.5 6.5 V

Input Voltage ≠ Enable

-0.5

V

IN

V

Input Voltage ≠ VS0, VS1 & VS2 (Note 1)

-0.5

2.8

V

Storage Temperature Range

T

STG

-65 150 ∞C

Operating Junction Temperature

T

J

150 ∞C

MSL per JEDEC J-STD-020A Level 3 (Note 2)

240

∞C

ESD Rating (based on Human Body Model)

2000

V

NOTES:

1. VS0, VS1 and VS2 pins have an internal pull-up resistor, only ground potentials should be placed on them as required.

2. Evaluation for MSL3 at 255∞C in process.

Recommended Operating Conditions

PARAMETER

SYMBOL MIN

MAX UNITS

Input Supply Voltage

V

IN

2.375 5.5

V

Operating Junction Temperature

T

J

-40 125 ∞C

Thermal Characteristics

PARAMETER

SYMBOL

TYPICAL UNITS

Thermal Resistance: Junction to Ambient (0 LFM)

(Note 3)

JA

28 ∞C/W

Thermal Resistance: Junction to Case (0 LFM)

JC

6 ∞C/W

NOTES:

3. Based on a four-layer board and proper thermal design in line with JEDEC EIJ/JESD 51 Standards.

Electrical Characteristics

NOTE: V

IN

=3.3V and over operating temperature range unless otherwise noted. Typical values are at T

A

=

Rev 1.0 ≠ July 2005

www.enpirion.com

EN5330

5

25∞C.

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX UNITS

Operating Input

Voltage

V

IN

2.375

5.5

V

Quiescent Supply

Current

I

Q

No switching, AVIN = 3.3V,

PVIN = 3.3V, ENABLE=0V

15 mA

No-Load Operating

Current

I

NL

Includes PWM, gate drive and

inductor ripple current.

45 mA

Switching

Frequency

F

OSC

5

MHz

Thermal Overload

Trip Point

T

J

160 ∞C

V

OUT

Range V

OUT

Using external voltage divider

0.8

V

Accuracy V

OUT

Over line, load and temperature

±2.0

%

Line Regulation

V

OUT

V

IN

= 2.5 to 5.0 volts

3

mV

Load Regulation

V

OUT

I

LOAD

= 0 to 3A

3

mV

V

OUT

T

A

= 0 to 70∫C

+0.25

-0.45

%

Temperature

Regulation

V

OUT

T

A

= -40 to 85∫C

+0.65

-0.55

%

Transient Response (I

OUT

= 0% to 100% or 100% to 0% of Rated Load)

Peak Deviation

V

OUT

V

IN

= 5V, 1.2V < V

OUT

< 3.3V

3

5

%

Output Voltage Ripple (with 5 x 10µF X5R or X7R ceramic capacitors)

Peak-to-peak V

OUT-PP

V

IN

= 5.0V, V

OUT

= 1.2V, I

OUT

= 3A,

C

OUT

= 50uF, 5 x 10µF X5R or X7R

ceramic capacitors

20 mV

Output Current (Note 4)

Max Continuous

Output Current

I

OUT

3

A

Over-Current

Threshold

I

OCP

4.5 A

Short-Circuit

Current

I

SC

4 A

Enable Operation

Disable Threshold

V

DISABLE

Max voltage to ensure the converter

is disabled

0.8

V

Enable Threshold

V

ENABLE

Min voltage to ensure the converter

is enabled

1.8 V

Power OK Operation

POK low voltage

V

POK

I

POK

= 1mA

0.4

V

Max POK Voltage

V

POK

Supply voltage applied to POK

5.5

V

NOTES:

4. Maximum output current may need to be de-rated, based on operating condition, to meet T

J

requirements.