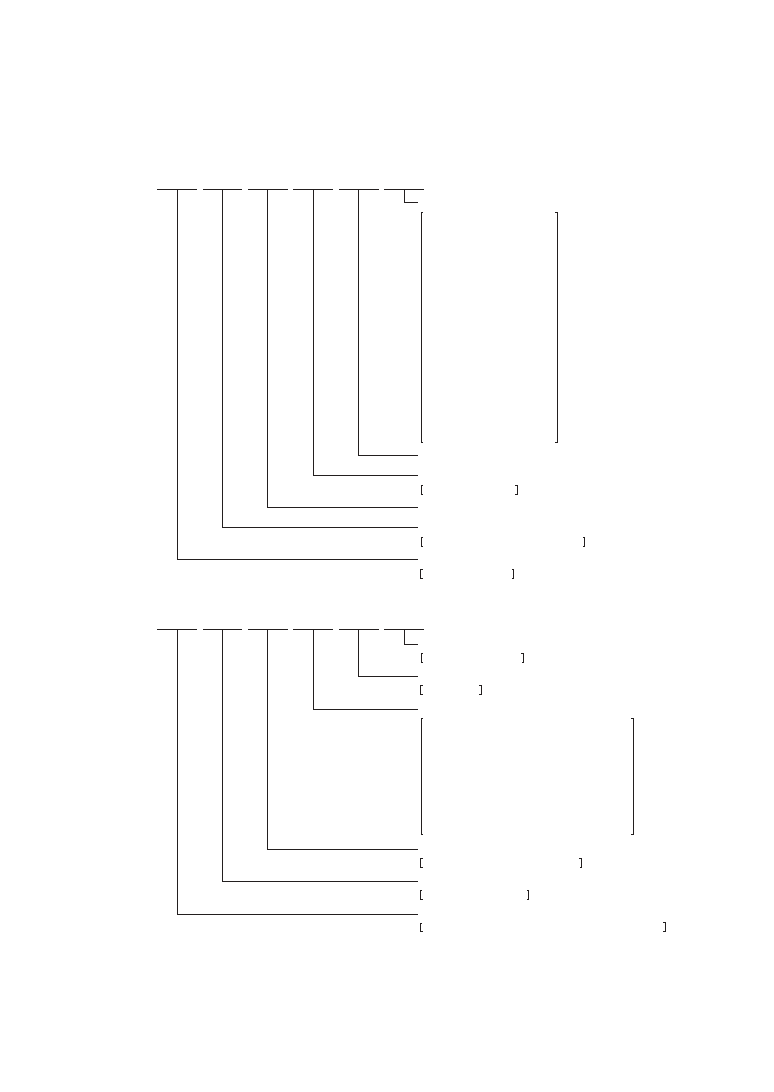

S1C63 Family

Devices

S1

C

63158

F

0A01

Packing specifications

00 : Besides tape & reel

0A : TCP BL

2 directions

0B : Tape & reel BACK

0C : TCP BR

2 directions

0D : TCP BT

2 directions

0E : TCP BD

2 directions

0F : Tape & reel FRONT

0G : TCP BT

4 directions

0H : TCP BD

4 directions

0J : TCP SL

2 directions

0K : TCP SR

2 directions

0L : Tape & reel LEFT

0M : TCP ST

2 directions

0N : TCP SD

2 directions

0P : TCP ST

4 directions

0Q : TCP SD

4 directions

0R : Tape & reel RIGHT

99 : Specs not fixed

Specification

Package

D: die form; F: QFP

Model number

Model name

C: microcomputer, digital products

Product classification

S1: semiconductor

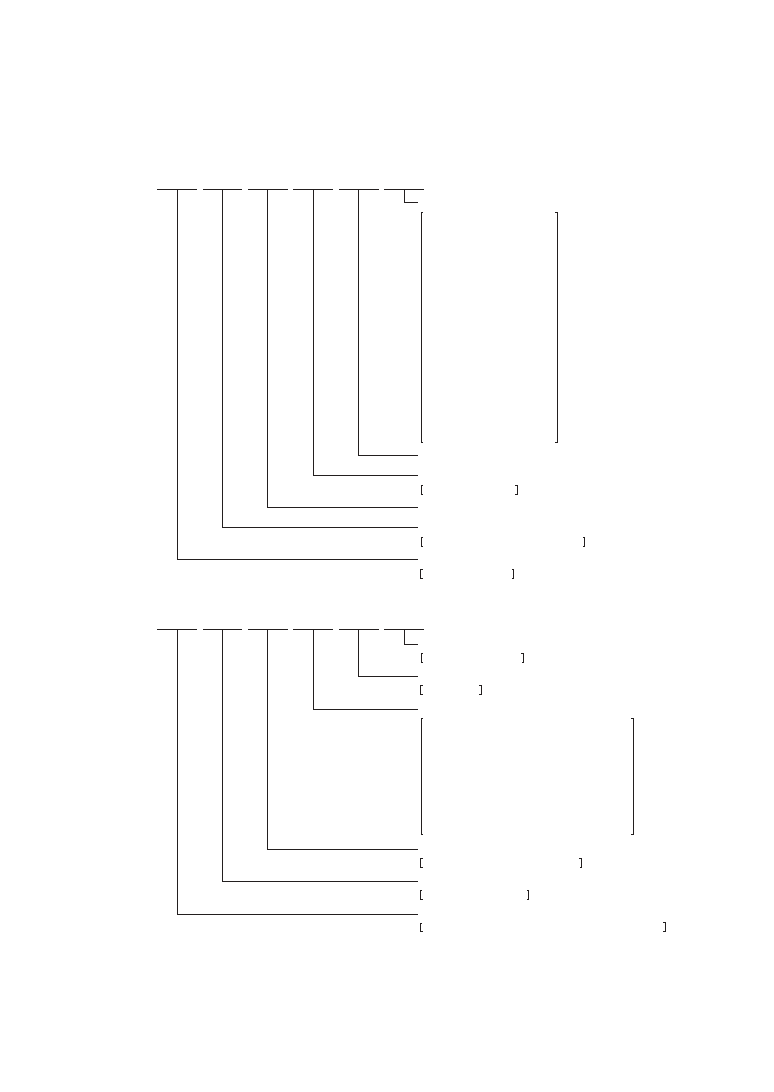

Development tools

S5U1

C

63000

A1

1

Packing specifications

00: standard packing

Version

1: Version 1

Tool type

Hx : ICE

Ex : EVA board

Px : Peripheral board

Wx : Flash ROM writer for the microcomputer

Xx : ROM writer peripheral board

Cx : C compiler package

Ax : Assembler package

Dx : Utility tool by the model

Qx : Soft simulator

Corresponding model number

63000: common to S1C63 Family

Tool classification

C: microcomputer use

Product classification

S5U1: development tool for semiconductor products

00

00

Configuration of product number

S1C63406/408 TECHNICAL MANUAL

EPSON

i

CONTENTS

C

ONTENTS

CHAPTER

1 O

UTLINE

________________________________________________ 1

1.1

Features ......................................................................................................... 1

1.2

Block Diagram .............................................................................................. 3

1.3

Pin Layout Diagram ..................................................................................... 5

1.4

Pin Description ............................................................................................. 7

1.5

Mask Option .................................................................................................. 9

CHAPTER

2 P

OWER

S

UPPLY

AND

I

NITIAL

R

ESET

____________________________ 11

2.1

Power Supply ............................................................................................... 11

2.1.1 Voltage <V

D1

> for internal circuits .......................................................... 12

2.1.2 Voltage <V

OSC

> for OSC1 oscillation circuit .......................................... 12

2.1.3 Voltage <V

C1

, V

C2

, V

C4

, V

C5

> for LCD driving ....................................... 12

2.2

Initial Reset .................................................................................................. 13

2.2.1 Reset terminal (RESET) ............................................................................ 13

2.2.2 Simultaneous low input to terminals K00K03 ........................................ 14

2.2.3 Internal reset circuit .................................................................................. 14

2.2.4 Internal register at initial resetting ........................................................... 15

2.2.5 Terminal settings at initial resetting ......................................................... 15

2.3

Test Terminal (TEST) ................................................................................... 15

CHAPTER

3 CPU, ROM, RAM ________________________________________ 16

3.1

CPU .............................................................................................................. 16

3.2

Code ROM .................................................................................................... 16

3.3

RAM ............................................................................................................. 17

3.4

Data ROM .................................................................................................... 17

CHAPTER

4 P

ERIPHERAL

C

IRCUITS

AND

O

PERATION

__________________________ 18

4.1

Memory Map ................................................................................................ 18

4.2

Watchdog Timer ........................................................................................... 23

4.2.1 Configuration of watchdog timer .............................................................. 23

4.2.2 Interrupt function ...................................................................................... 23

4.2.3 I/O memory of watchdog timer ................................................................. 24

4.2.4 Programming notes ................................................................................... 24

4.3

Oscillation Circuit ....................................................................................... 25

4.3.1 Configuration of oscillation circuit .......................................................... 25

4.3.2 OSC1 oscillation circuit ............................................................................ 26

4.3.3 OSC3 oscillation circuit ............................................................................ 27

4.3.4 Switching of operating voltage ................................................................. 28

4.3.5 Clock frequency and instruction execution time ....................................... 28

4.3.6 I/O memory of oscillation circuit .............................................................. 29

4.3.7 Programming notes ................................................................................... 30

4.4

Input Ports (K00K03) ................................................................................ 31

4.4.1 Configuration of input ports ..................................................................... 31

4.4.2 Mask option ............................................................................................... 31

4.4.3 Interrupt function ...................................................................................... 31

4.4.4 I/O memory of input ports ......................................................................... 33

4.4.5 Programming notes ................................................................................... 35