| –≠–Ľ–Ķ–ļ—ā—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā: 8255PPI | –°–ļ–į—á–į—ā—Ć:  PDF PDF  ZIP ZIP |

1

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

Programmierbarer

paralleler

PPI

Interfaceschaltkreis

8255

PPI 8255

Inhalt:

1. Leistungsmerkmale

2. Architektur

3. Pinbelegung

4. Programmierung

4.1. Mode 0

4.2. Mode 1

4.3. Mode 2

4.4. Einzelbitausgabe fŁr Port C

1. Leistungsmerkmale

Der programmierbare parallele Schnittstellenschaltkreis 8255 ist ein universell verwendbarer Peripheriebaustein,

der drei einzelne Ports A, B und C enthšlt und in drei verschiedenen Betriebsarten (Modi) programmierbar ist.

- 3 programmierbare Ein/Ausgabeports; Port A,B,C

- 3 Betriebsarten

Mode 0: Byte Input/Output

Mode 1: Strobed Input/Output

Mode 2: Strobed bidirectional BUS

- Einzelbit Set/Reset-Operation an Port C

- InterruptauslŲsung in Mode 1 und 2 in Verbindung mit einem

Interruptcontroller 8259

- kein Systemtakt erforderlich

2

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

2. Architektur

Bild 1: Architektur PPI 8255

Der Datenbuspuffer stellt die Schnittstelle zum Systemdatenbus dar. Das Senden und Empfangen von Daten

erfolgt mit IN/OUT-Operationen der CPU. ‹ber den Datenbuspuffer werden zwei Basisfunktionen des PPI

ausgefŁhrt:

- Programmieren des Mode

- Lesen oder Schreiben von Daten in oder von den Ports A, B oder C.

Die Lese/Schreib-Logik verarbeitet die Informationen der Eingšnge Read, Write und Chip Select. Die zwei

AdreŖeingšnge A1 und A0 dienen zur internen Adressierung der 3 Ports sowie der Erkennung des Steuerbytes.

A1 A0 Funktion

0 0

Port A

0 1

Port B

1 0

Port C

1 1

Steuerbyte (nur Schreiben)

Tabelle 1: 8255 Basisportadressen

Die Programmierung des Schaltkreises erfolgt mit einem Steuerbyte.

3

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

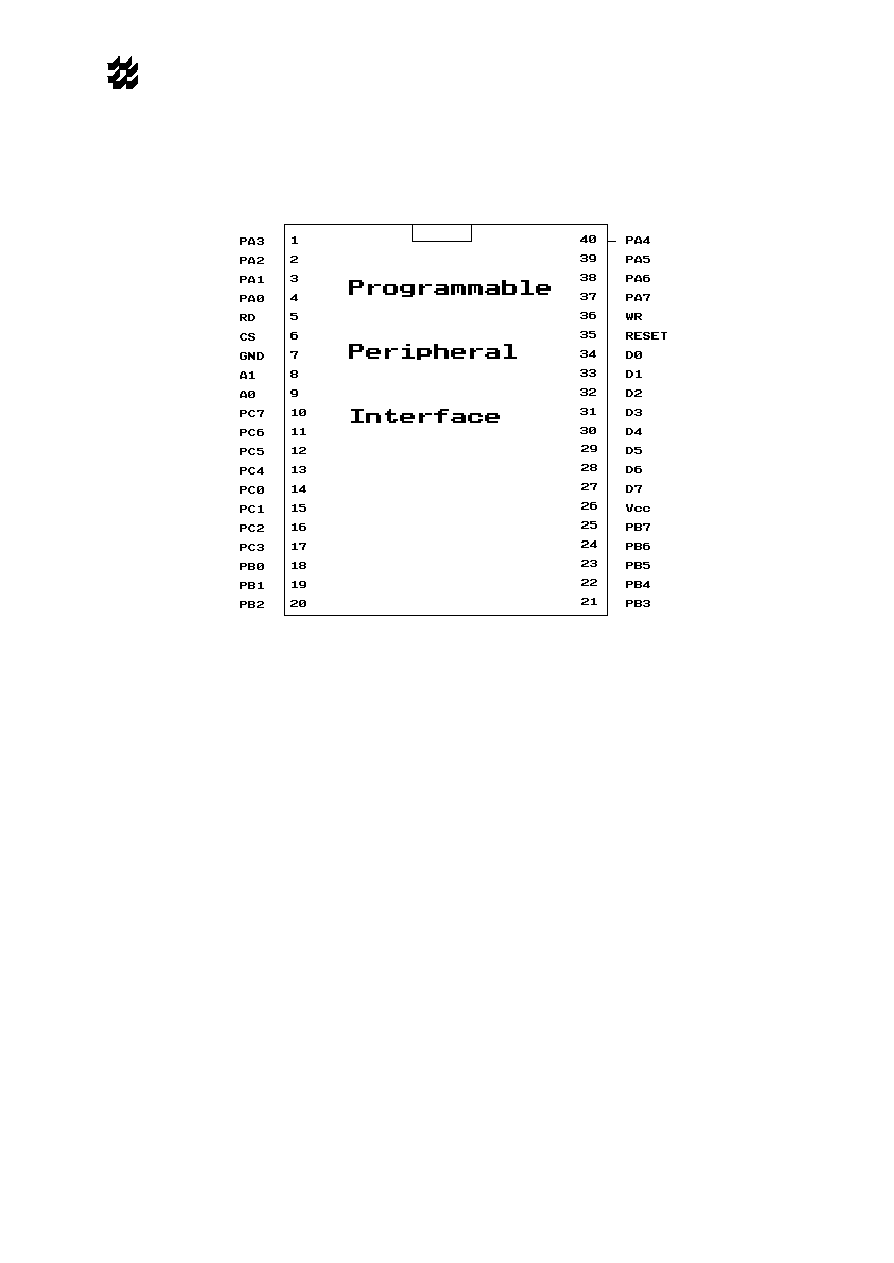

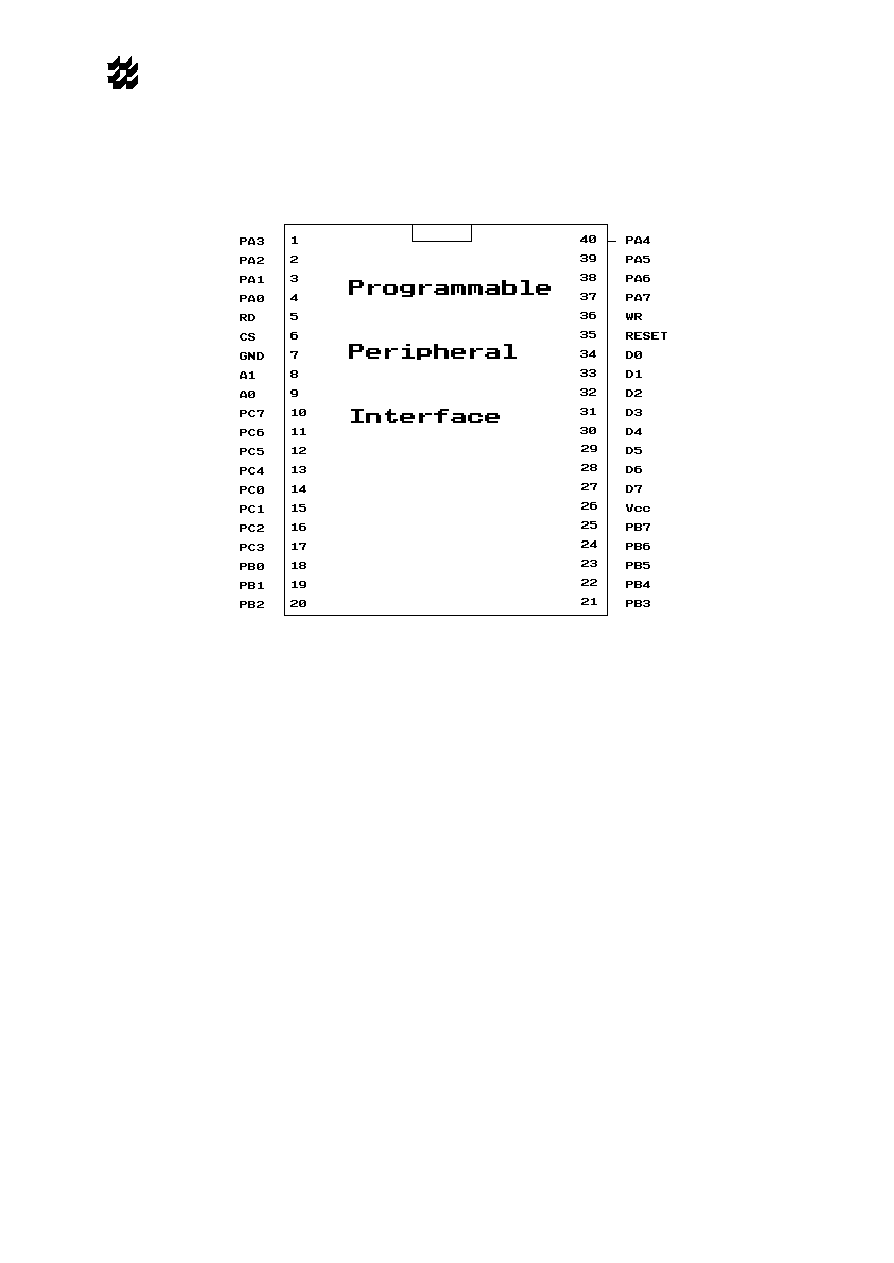

3. Pinbelegung

Der PPI 8255 wird in einem 40-poligen DIL-GehaŁse gefertigt. Die AnschlŁsse (Bild 1) haben folgende Funktionen:

Bild 2 : Pinbelegung des Schaltkreises PPI 8255

D7..D0

8Bit-Datenbus bidirektional;

__

tristate

RD

Readsignal (Inputoperation)

__

low aktiv

WR

Writesignal (Outputopearion)

__

low aktiv

CS

Chip Select Steuersignal zur Bausteinauswahl

low aktiv

RESET

RŁcksetzen; LŲscht das Steuerbyteregister und schaltet

alle PortanschlŁsse als Eingang; Eingang high aktiv

A1,A0

AdreŖeingšnge zur Portauswahl; (Tabelle 1)

PA0-PA7

Port A

U

OL

<= 0,45V, I

OL

<= 1,7mA

U

OH

>= 2,40V, I

OH

>= -200

Ķ

A

PB0-PB7

Port B

PC0-PC7

Port C

Port B,C Darlington-Strom R

ext

= 750Ř

U

ext

= 1,5V

I = -1,0..-4.0mA

Vcc

Betriebsspannung +5V

GND

MasseanschluŖ

4

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

4. Programmierung

Die Programmierung des 8255 erfolgt mit Hilfe eines Steuerbytes zur Programmierung der entsprechenden

Betriebsarten der Ports A,B und C . Mit einem zweiten Steuerbyte wird die Einzelbit-Ausgabe Łber Port C

realisiert.

Modesteuerbyte:

Aufbau des Steuerbytes:

D7 D6 D5 D4 D3 D2 D1 D0

Gruppe A Gruppe B

Modesteuerung

S=1 M2 M1 A CH M0 B CL

Einzelbit-Ausgabe

S=0 X X X C2 C1 C0 S/R

Port C

Modesteuerung S=1

mŲgliche Betriebsarten:

Port A: Mode 0 oder 1 oder 2

Port B: Mode 0 oder 1

Port C: Mode 0 oder Einzelbitausgabe

5

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

4.1. Mode 0 Byte Input/Output

Im Mode 0 werden Ein-/Ausgabe-Operationen ohne Quittung vorgenommen. Sind z.B. alle Ports des 8255 im

Mode 0 programmiert (M2=M1=M0=0), so stehen folgende Ein-/Ausgaben zur VerfŁgung:

- zwei 8Bit-Ports fŁr Byte Ein-/Ausgabe (Port A,B)

- zwei 4Bit-Ports fŁr Halbbyte Ein-/Ausgabe (Port C)

Die Portausgšnge sind gelatcht, die Porteingšnge sind nicht gelatcht.

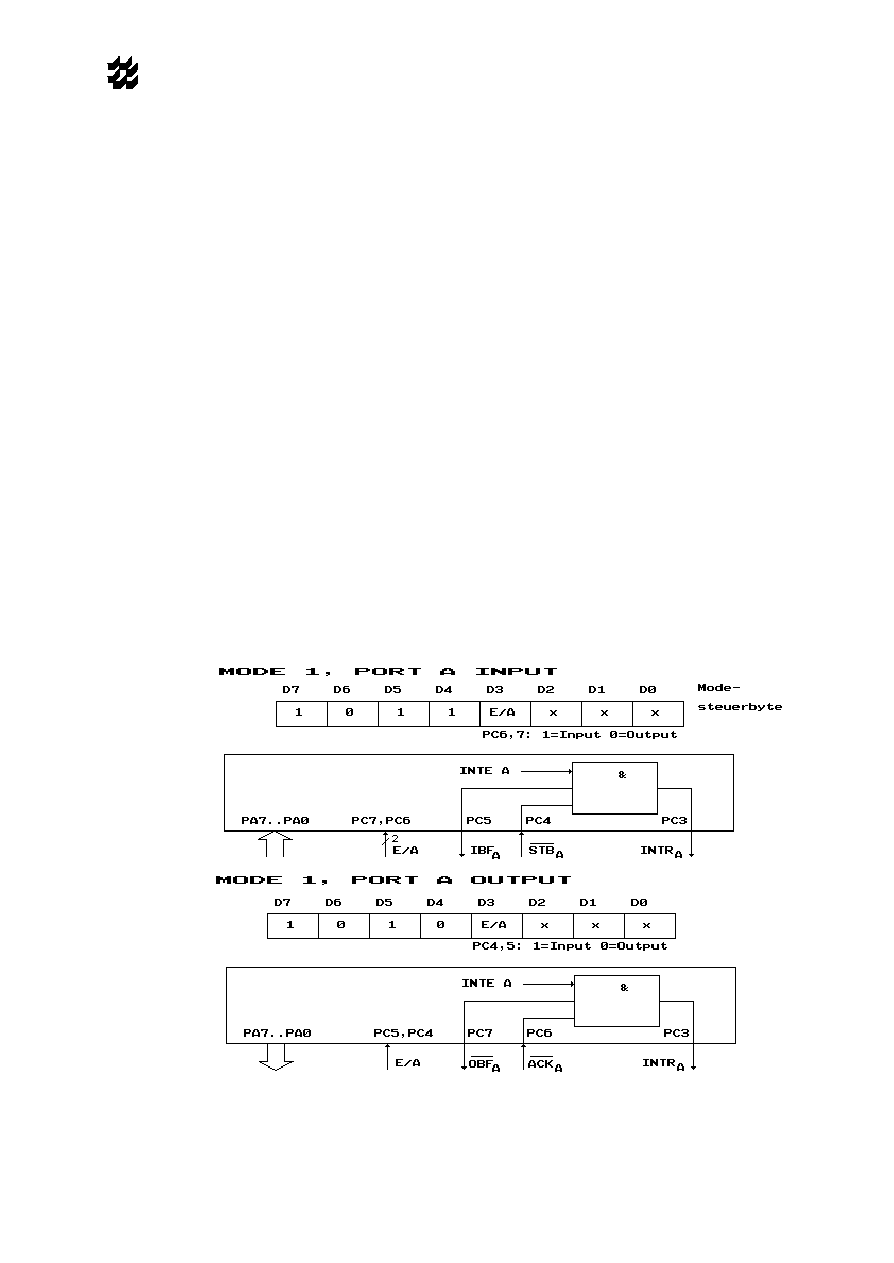

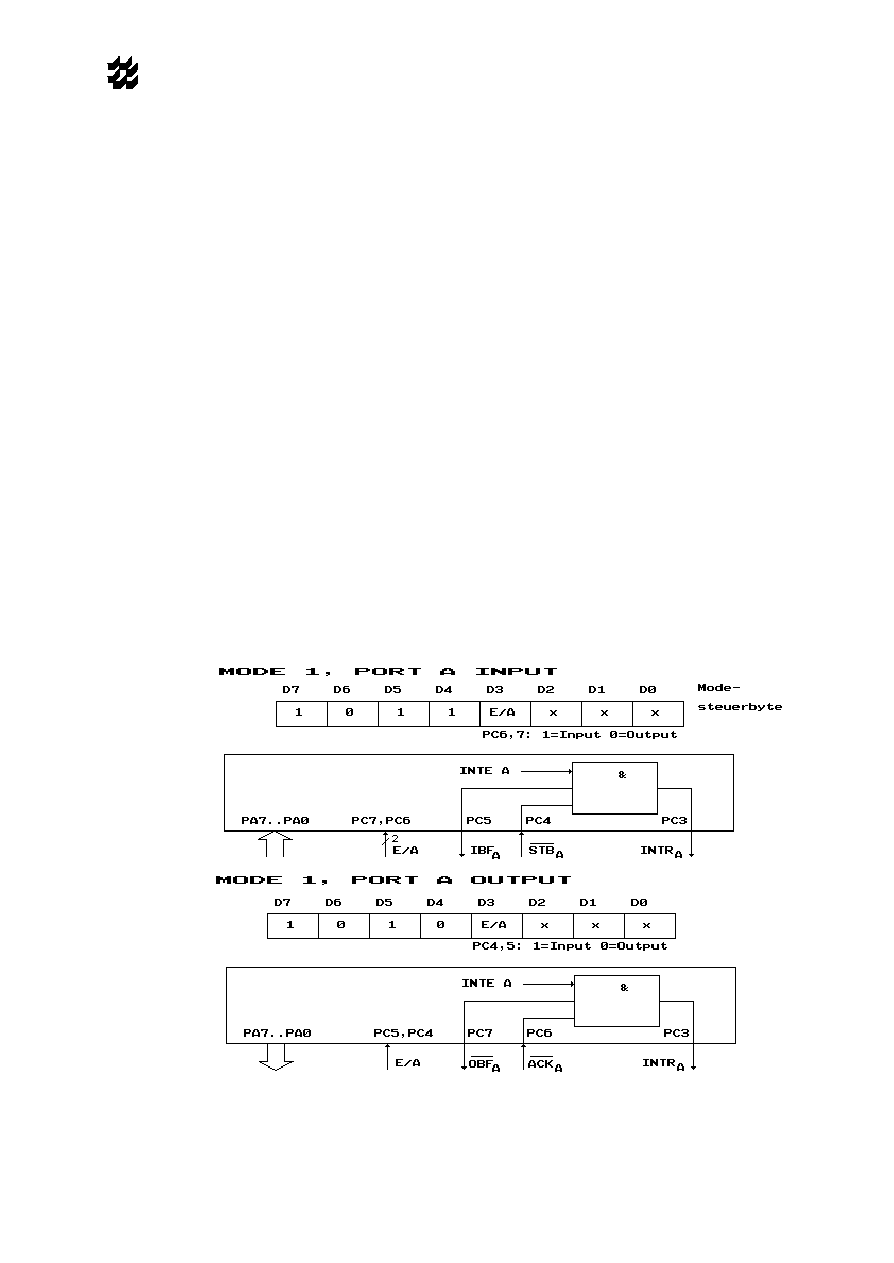

4.2. Mode 1 Strobed Input/Output

Die Ports A und B arbeiten als Ein- oder Ausgabeports im Quittungsbetrieb in Verbindung mit dem Port C,

welches die Handshake-Signale verwaltet. In den quittungsgesteuerten Ein-/Ausgaben kann vom 8255 eine

Interrupt-Anforderung an den PIC 8259 angemeldet werden. Die Interruptfreigabe des 8255 wird durch ein

internes INTE-Flip-Flop organisiert, welches durch Einzelbit Set/Reset-Operationen von Port C aus beeinfluŖt

werden kann.

- Bit-Set = Interrupt Freigabe

- Bit-Reset = Interrupt Sperre

Die entsprechenden Steuersignale haben im Mode 1 folgenden Funktionen:

Steuersignale fŁr Port-Input-Operationen:

___ ___

STB

Strobe, Eingang, low aktiv; STB=low lšdt die Daten in das Port-Eingangslatch.

IBF

Input Buffer Full; Ausgang, low aktiv

High notiert, daŖ Daten in das Eingangslatch geladen worden sind und stellt somit ein

Bestštigungssignal dar.

IBF wird mit STB=low gesetzt und mit RD (low->high) zurŁckgesetzt.

INTR

Interrupt Request, Ausgang, high aktiv

INTR wird gesetzt, wenn nach dem Latchen der Port-Eingabedaten STB und IBF gleich high sind. In

der darauf eingeleiteten Interrupt-Service-Routine mit dem Lesen der Port-Eingabe-Daten wird INTR

mit RD (high->low) zurŁckgesetzt. Die INTE-Flip-Flops von Port A und B werden kontrolliert durch:

INTE Port A: Bit Set/Reset PC4

INTE Port B: Bit Set/Reset PC2

Steuersignale fŁr Port-Output-Operationen

____

OBF

Output-Buffer Full, Ausgang, low aktiv

OBF aktiv = low notiert, daŖ die CPU Daten in das Port geschrieben hat, die an den Portausgšngen

gŁltig bereitstehen.

Die Aktivierung von OBF erfolgt nach WR (low->high).

____

ACK

Acknowledge Input, Eingang, low aktiv

ACK = low notiert, daŖ die Peripherie vom 8255 die gŁltigen Daten Łbernommen hat. Mit ACK = low

wird OBF wieder inaktiv d.h. OBF=high.

INTR

Interrupt Request, Ausgang, high aktiv

Mit OBF = high und ACK = high lŲst ein aktives INTR = high einen Interrupt aus, der in der

Interrupt-Service-Routine zum Schreiben neuer Port-Ausgabe-Daten fŁhren kann.

6

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

Mit der high-low Flanke von WR wird INTR wieder inaktiv d.h. INTR = low. Am Ende des

Bestštigungszyklusses mit der low-high Flanke von ACK wird INTR wieder aktiv d.h. INTR = high

und damit wird ein neuer Interrupt ausgelŲst.

Die INTE-Flip-Flops von Port A und Port B werden kontrolliert durch:

INTE Port A: Bit/Reset PC6

INTE Port B: Bit/Reset PC2

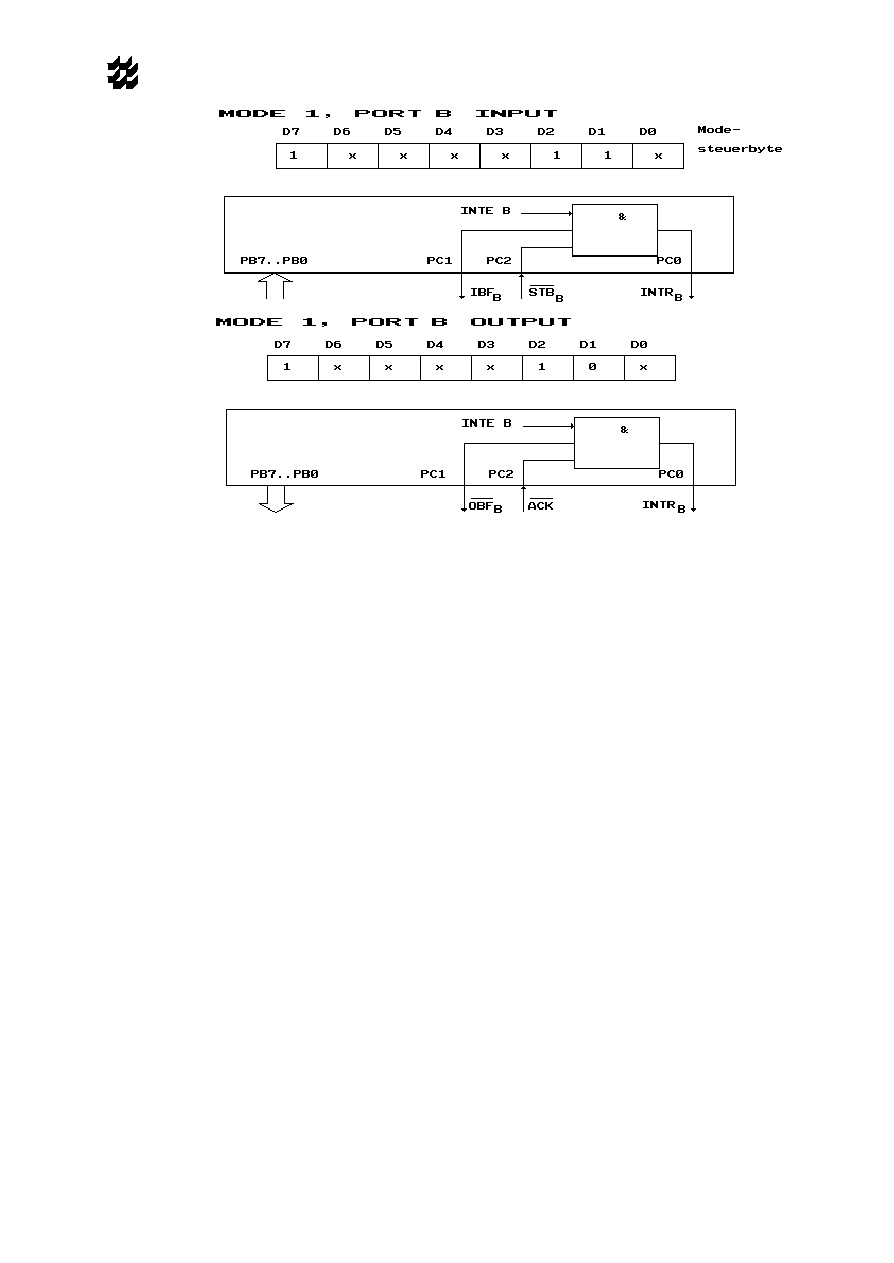

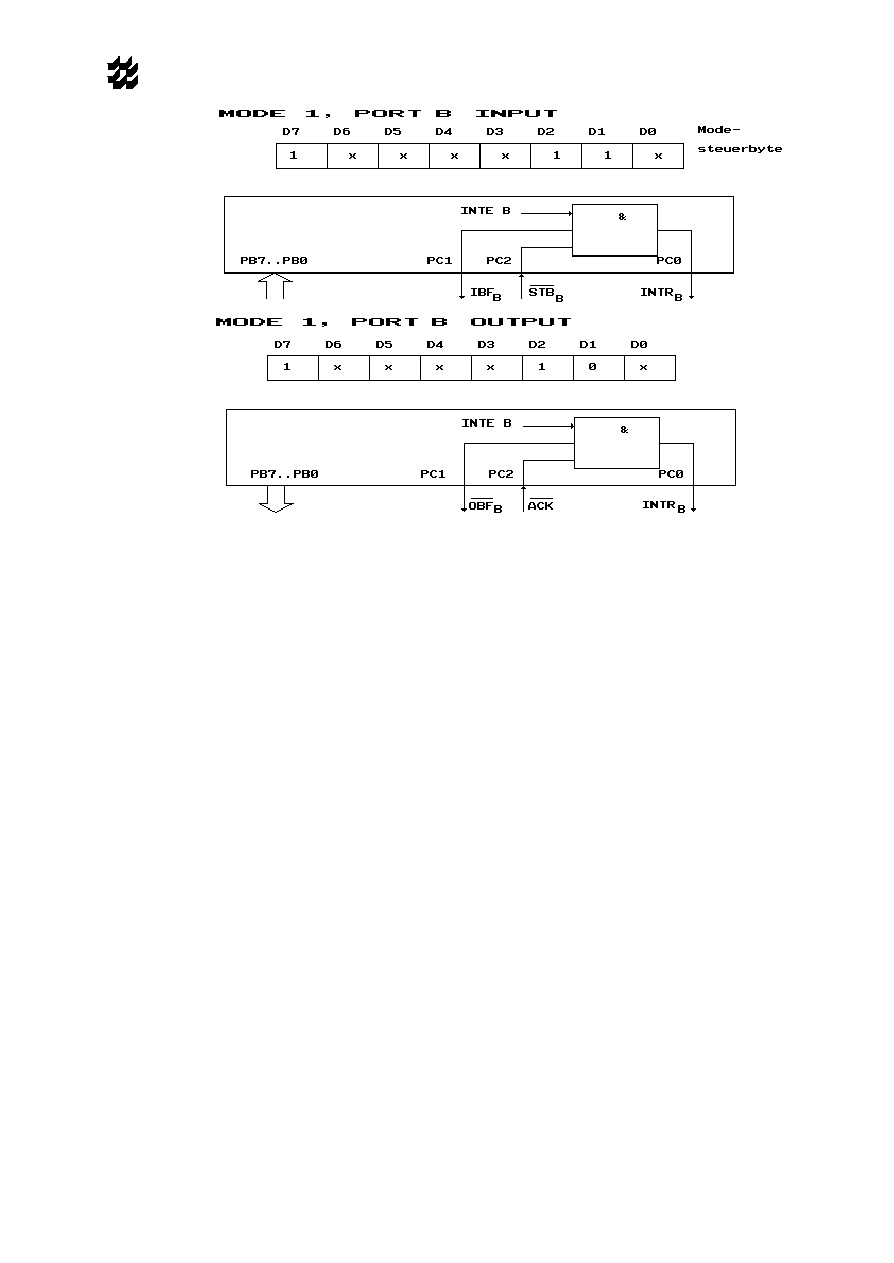

Die entsprechenden Varianten der Programmierung im Mode 1, getrennt nach Port A und Port B, jeweils fŁr

Eingang/Ausgang zeigen die folgenden Bilder.

Informationen Łber den Zustand der Bestštigungssignale IBF,OBF, des Interrupt-Freigabe-FF INTE und der

Interrupt Anforderung INTR erhšlt man durch Lesen eines Statusbytes von Port C (Tabelle 3).

Format der Statusinformation Mode 1 (IN Port C)

FŁr Port-Eingabe

D7 D6 D5 D4

D3 D2 D1 D0

E/A E/A IBFA INTEA

INTRA INTEB BFB INTRB

Gruppe A

Gruppe B

FŁr Port-Ausgabe

D7 D6 D5 D4 D3 D2 D1 D0

OBFA INTEA E/A E/A INTRA INTEB OBFB

INTRB

Gruppe A

Gruppe B

7

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

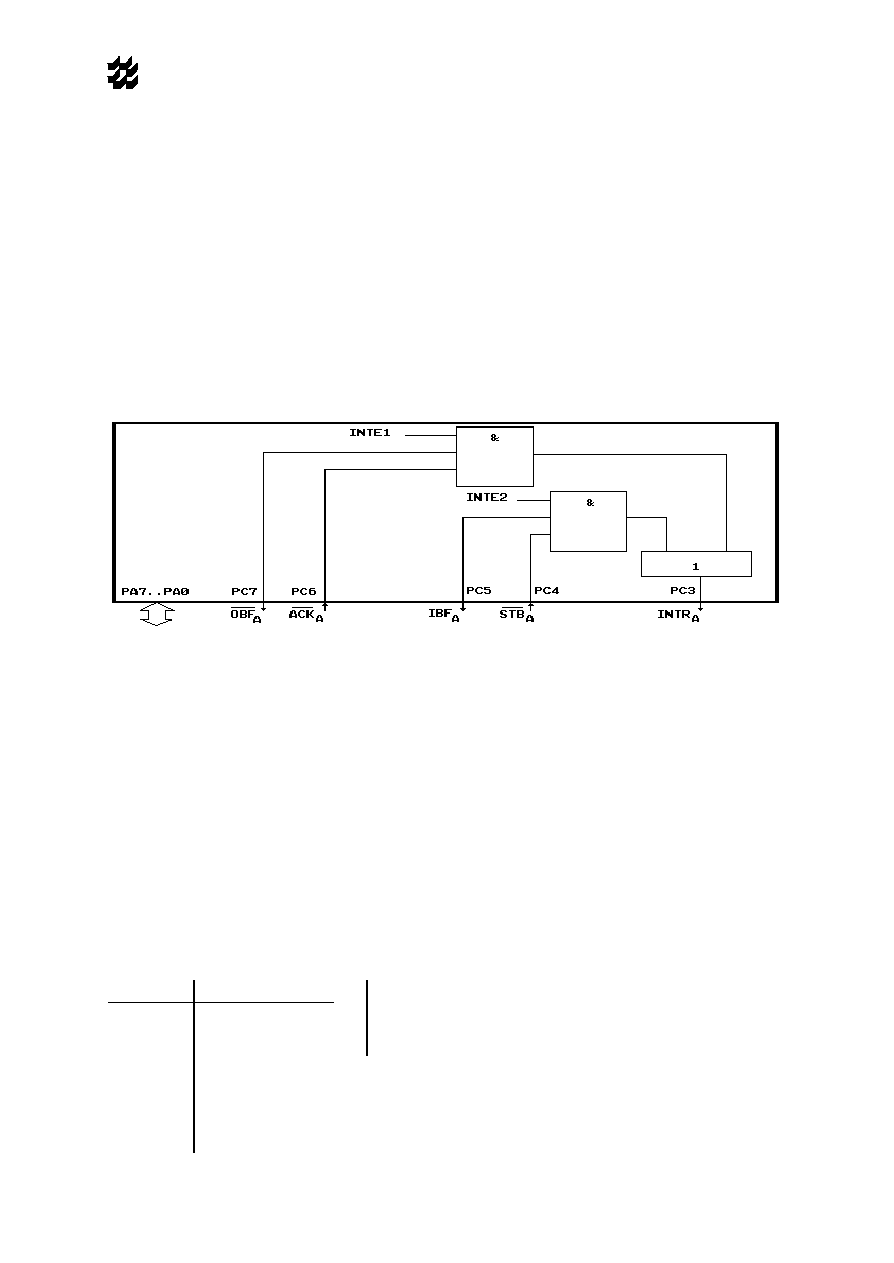

Bild 4: Mode 1, Port B

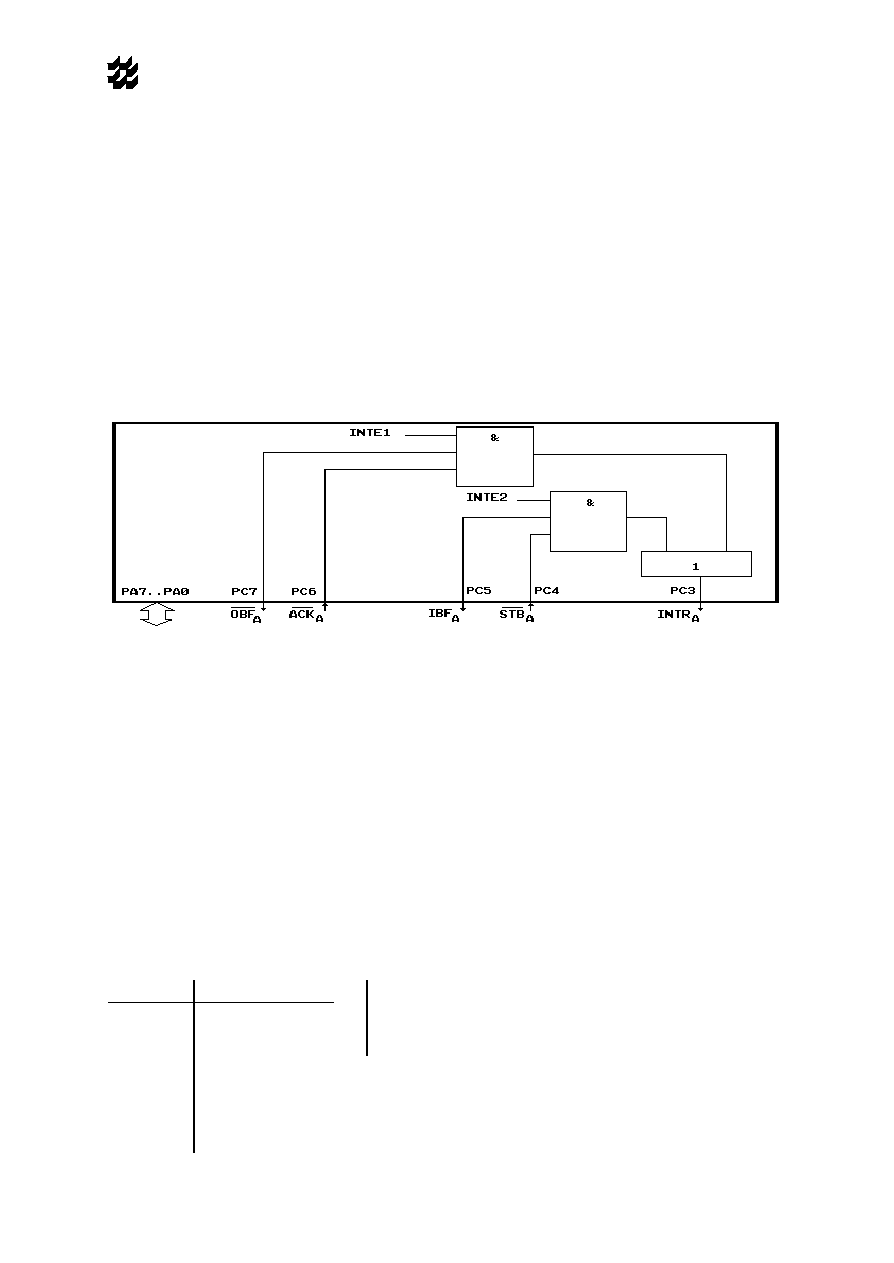

4.3. Mode 2 Strobed bidrektional BUS

Die bidirektionale Port-Eing-/Ausgabe im Quittungsbetrieb wird nur Łber Port A realisiert. Am Port C befinden

sich die Steuersignale fŁr die Ausgabe OBFA und ACKA (beide low aktiv) und fŁr die Eingabe STBA (low aktiv)

und IBFA (high aktiv) und das Interrupt-Anforderungssignal INTRA. Die Interrupt-Freigabe-FF werden wiederum

mit den Bit-Set-Resetfunktionen von Port C beeinfluŖt.

Ausgabe: Bit Set/Reset PC6 (INTE1)

Eingabe: Bit Set/Reset PC4 (INTE2)

Das Modesteuerbyte fŁr den Mode 2 hat den folgenden Aufbau:

D7 D6 D5 D4 D3 D2 D1 D0

1 1 x x 1/0 1/0

PC0..2

1: Input

0: Output

Port B E/A-Definition

1: Input

0: Output

Port B Mode-Definition

1: Mode 1

8

FH Kiel FB Informatik & Elektrotechnik Prof.Dr. K. KiŖig klaus.kissig@fh-kiel.de

0: Mode 0

Ist der Mode 2 fŁr das Port A programmiert, kann man Port B noch wie folgt verwenden:

Mode 1: Strobed Input/Output mit den Handshake-Signalen an

PC0, PC1 und PC2

Mode 0: Byte Input/Output fŁr PB0..PB7 mit freiwšhlbaren Leitungen an PC0..PC2

Das Format der Statusinformation von Mode 2 ist folgendes:

D7 D6 D5 D4 D3 D2 D1 D0

OBFA INTE1 IBFA INTE2 INTRA xx xx xx

Gruppe A

Gruppe B

Bild : Mode 2 von Port A

4.4. Einzelbitausgabe fŁr Port C

Jedes der 8 Bit von Port C kann einzeln gesetzt oder rŁckgesetzt werden durch Einzelbit-Ausgabe-Operationen

von Port C unter der Bedingung S=0 beim Modesteuerbyte.

Damit ist es mŲglich in den Handshake-Betriebsarten Mode 1 oder 2, in denen Port C als Status/Control-Byte fŁr

Port A oder B verwendet wird, die Interruptlogikbits INTE-A, INTE-B, INTE1 und INTE2 gezielt zu beeinflussen.

Alle anderen Statusbits sind nicht durch Einzelbit-Ausgaben beeinfluŖbar.

C2 C1 C0

Bitauswahl Port C

S/R Setz-/RŁcksetzfunktion PC7..PC0

0 0 0

Portleitung PC0

0 rŁcksetzen

0 0 1

Portleitung PC1

1 setzen

0 1 0

Portleitung PC2

0 1 1

Portleitung PC3

1 0 0

Portleitung PC4

1 0 1

Portleitung PC5

1 1 0

Portleitung PC6

1 1 1

Portleitung PC7