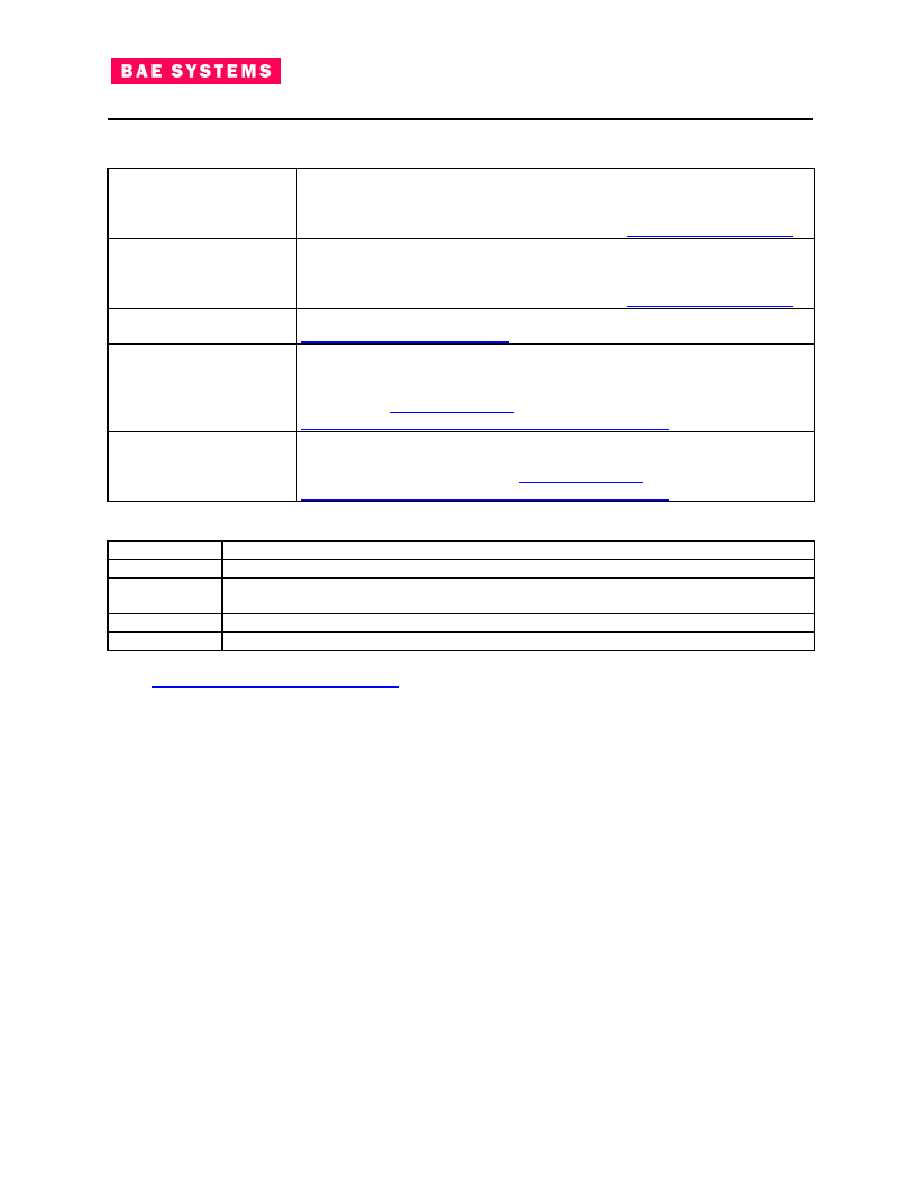

| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: RAD750 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

RAD750

TM

TM

Board

Hardware User's Manual

Document Number

234A533

Release Date

December 20, 2000

Copyright by BAE SYSTEMS

All Rights Reserved

i

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

Notices

Before using this information and the product it supports, be sure to read the general information on the

back cover of this book.

Trademarks

The following are trademarks of International Business Machines Corporation in the United States, or

other countries, or both:

IBM

IBM Logo

PowerPC

PowerPC 750

The following are trademarks of BAE SYSTEMS in the United States, or other countries, or both:

RAD750

The following are registered trademarks of PCI Industrial Computer Manufacturing Group in the United

States, or other countries, or both:

PICMG

CompactPCI

Other company, product, and service names may be trademarks or service marks of others.

Preliminary Edition (Version 2.10, 12/21/2000)

This unpublished document is the RAD750

TM

Board Hardware Users Manual. Make sure you are using

the correct edition for the level of the product.

This document contains information on a new product under development by BAE SYSTEMS. BAE

SYSTEMS reserves the right to change or discontinue this product without notice.

© BAE SYSTEMS 2001.

All rights reserved.

ii

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

Preface

Notice for reviewers:

This is an update to the preliminary release of this document.

At this time, some of the information contained in this document is in a state of flux until completion of first

Flight unit bring-up, and may be slightly behind the hardware specifications.

Items marked

TBA

or

TBD

will be filled in for a subsequent release.

When reviewing the document, please keep the following in mind when providing comments:

∑

Is the document presented in a usable order?

∑

Do I need to include any test set information?

∑

Since this is intended to be an all-encompassing, standalone document, is there any information

that can be found somewhere else that should be included here

∑

Does the document provide enough information to stand-alone?

∑

Has too much detail been provided in some areas? What document should that detail be placed?

∑

What information is missing and should be added?

∑

Does the appendix belong as a separate document or should it be merged into this document?

iii

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

Table of Contents

1

USING THIS MANUAL ....................................................................................................................1

1.1

A

UDIENCE OF THE

H

ARDWARE

U

SERS

M

ANUAL

..............................................................................1

1.2

O

VERVIEW OF THE

M

ANUAL

S

ET

...................................................................................................1

1.3

S

OFTWARE

U

SERS

M

ANUAL

.........................................................................................................2

1.4

RAD750 / P

OWER

PCI S

ET OF

D

ATA

S

HEETS

...............................................................................2

1.5

R

EVISION

H

ISTORY

.....................................................................................................................2

1.6

C

ONVENTIONS

/ N

OMENCLATURE

.................................................................................................2

1.7

T

ERMINOLOGY

............................................................................................................................3

2

OVERVIEW......................................................................................................................................5

2.1

RAD750 3U C

OMPACT

PCI B

OARD

F

UNCTIONS

............................................................................5

2.1.1

RAD750 PowerPC Processor................................................................................................6

2.1.2

Power PCI Bridge Function ...................................................................................................6

2.1.3

SUROM ................................................................................................................................7

2.1.4

Local Memory .......................................................................................................................7

2.1.5

Clocking................................................................................................................................7

2.1.6

Power Regulation and Consumption .....................................................................................8

2.2

S

PECIFICATION

...........................................................................................................................8

2.3

O

RDERING

I

NFORMATION

.............................................................................................................9

2.4

SUROM D

ESCRIPTION

.............................................................................................................10

3

INSTALLATION INSTRUCTIONS..................................................................................................11

3.1

S

AFETY

P

RECAUTIONS

..............................................................................................................11

3.2

U

NPACKING AND

I

NSPECTING

.....................................................................................................11

3.2.1

Unpacking...........................................................................................................................11

3.2.2

Board Identification .............................................................................................................11

3.2.3

Malfunction or damage to the board or connected components ...........................................11

3.3

W

ARNINGS

...............................................................................................................................12

3.4

C

OMPACT

PCI C

ONNECTOR

K

EYING

............................................................................................12

3.5

I

NSERTION

L

EVERS

/ J

ACK

S

CREWS

............................................................................................12

3.6

W

EDGELOCKS

..........................................................................................................................12

3.7

P

OWER

R

EQUIREMENTS

............................................................................................................12

3.8

B

ACKPLANE

D

ESIGN

G

UIDELINES

................................................................................................12

3.9

P

OWER

-

UP AND

O

PERATIONAL

D

ESCRIPTION

...............................................................................13

3.9.1

Power-up ............................................................................................................................13

3.9.2

Operation Description .........................................................................................................13

3.9.3

Resetting the RAD750 board...............................................................................................13

3.10

T

ROUBLESHOOTING

..................................................................................................................15

3.10.2

Debugging.......................................................................................................................16

3.11

RAD750 B

OARD

E

LECTRICAL

C

ONNECTORS

...............................................................................17

3.11.1

J1 Connector Pin Assignment .........................................................................................17

3.11.2

J2 Connector Pin Assignments........................................................................................18

3.12

C

OMPACT

PCI S

LOT

G

UIDELINES FOR

M

ULTIPROCESSOR

C

ONFIGURATIONS

...................................19

3.13

C

OMPATIBILITY WITH

RAD6000 .................................................................................................20

iv

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.14

F

RONT

P

ANEL

C

ONNECTOR

.......................................................................................................20

3.14.1

J7 Pin Assignments.........................................................................................................20

4

HARDWARE / ELECTRICAL.........................................................................................................21

4.1

RAD750..................................................................................................................................21

4.1.1

RAD750 Microprocessor Features ......................................................................................23

4.2

P

OWER

PCI .............................................................................................................................25

4.2.1

Environment........................................................................................................................26

4.2.2

Compliance Summary.........................................................................................................26

4.2.3

Architecture Overview .........................................................................................................26

4.2.4

Power PCI Features............................................................................................................27

4.2.5

Endian Conventions ............................................................................................................40

4.2.6

RAD750 Interrupts and Vector Interrupts.............................................................................42

5

EXTERNAL ELECTRICAL INTERFACE........................................................................................50

5.1

C

OMPACT

PCI D

EFINED

S

IGNALS

................................................................................................50

5.1.1

PCI Interface I/O .................................................................................................................56

5.1.2

PCI Central Resource I/O (external) ....................................................................................60

5.1.3

PCI Miscellaneous Interface................................................................................................61

5.2

N

ON

-PCI I

NTERFACES

..............................................................................................................61

5.2.1

JTAG Interfaces..................................................................................................................66

5.2.2

UART Interface ...................................................................................................................71

5.2.3

Interrupts and Discretes ......................................................................................................72

5.2.4

Resets and Clocks ..............................................................................................................75

5.2.5

Configuration Inputs ............................................................................................................75

5.3

P

OWER

I

NTERFACES

.................................................................................................................76

6

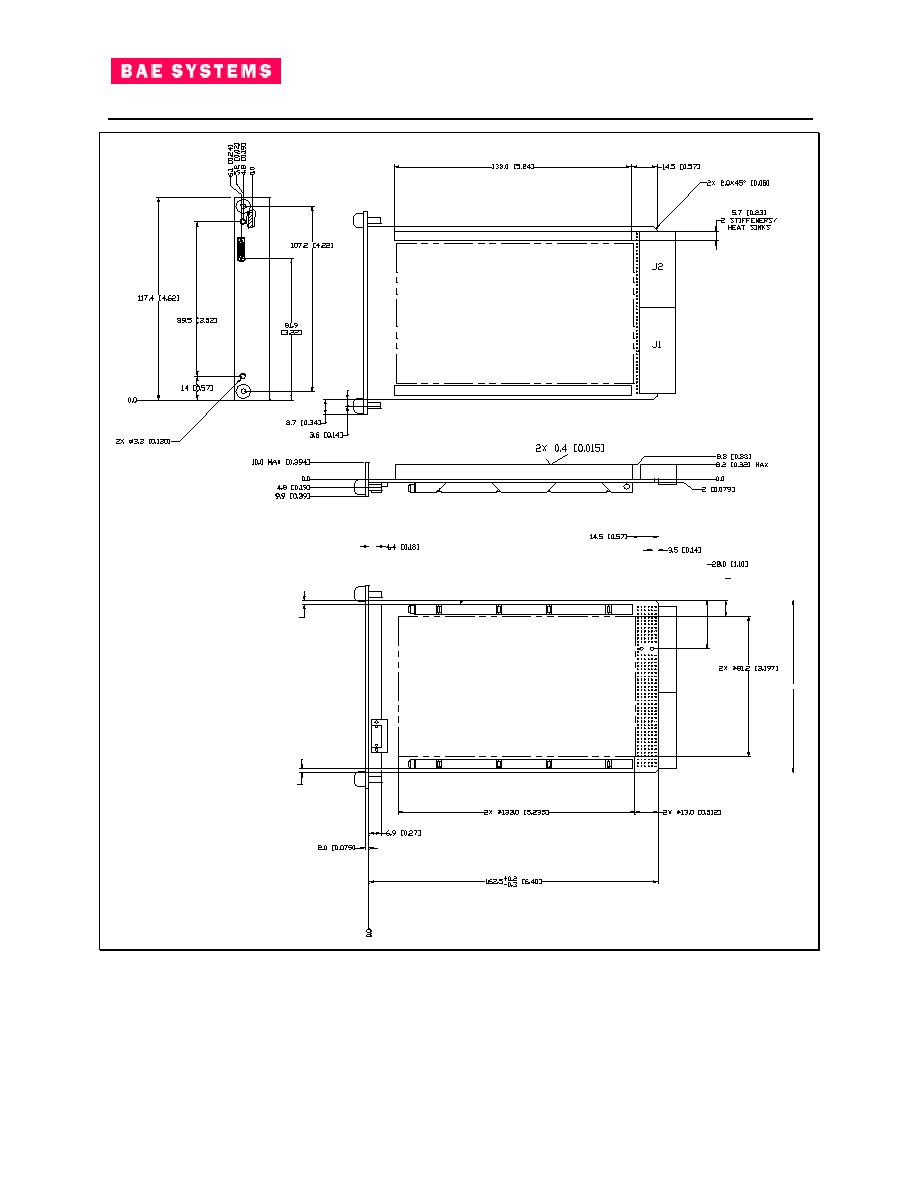

HARDWARE / MECHANICAL .......................................................................................................77

6.1

L

OCATION

O

VERVIEW

................................................................................................................78

6.2

G

ROUNDING

.............................................................................................................................79

6.2.1

Structural Grounding ...........................................................................................................79

6.2.2

Circuit Grounding, General..................................................................................................79

6.2.3

Wire Shield Grounding ........................................................................................................79

6.2.4

ESD Grounding...................................................................................................................79

7

MANUFACTURING .......................................................................................................................81

7.1

O

RGANIC

M

ATERIALS

................................................................................................................81

7.2

I

NORGANIC

M

ATERIALS

..............................................................................................................83

7.3

P

ROCESSES

.............................................................................................................................83

7.4

B

ILL OF

M

ATERIALS

...................................................................................................................85

8

DOCUMENTATION .......................................................................................................................88

8.1

S

UGGESTED

R

EADING

...............................................................................................................88

8.1.1

General PowerPC Information.............................................................................................88

8.1.2

IBM PowerPC Documentation.............................................................................................88

8.2

A

PPLICABLE

D

OCUMENTS

..........................................................................................................89

8.2.1

Specifications......................................................................................................................89

8.2.2

Standards ...........................................................................................................................90

v

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

8.2.3

Design Descriptions and Design Guides..............................................................................90

9

COMMENTS ..................................................................................................................................91

vi

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

List of Figures

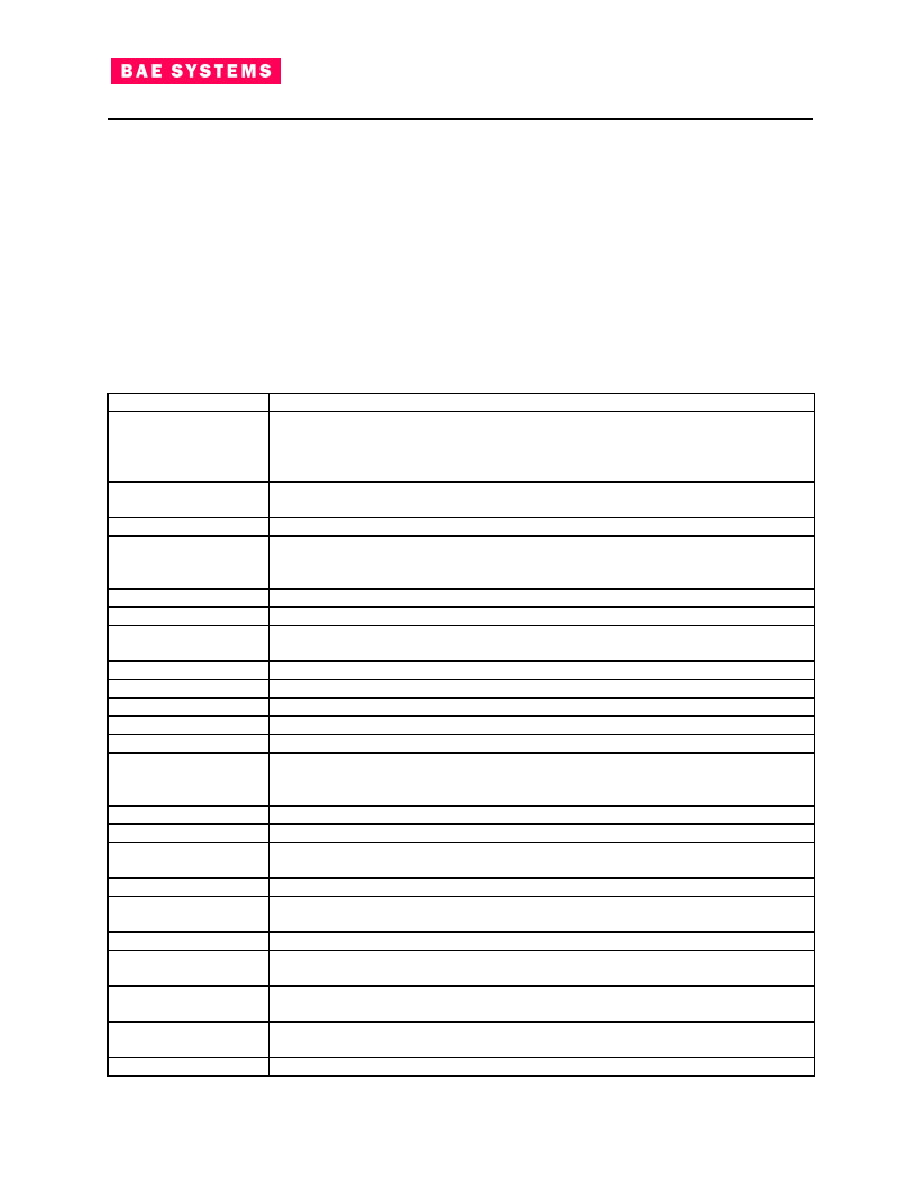

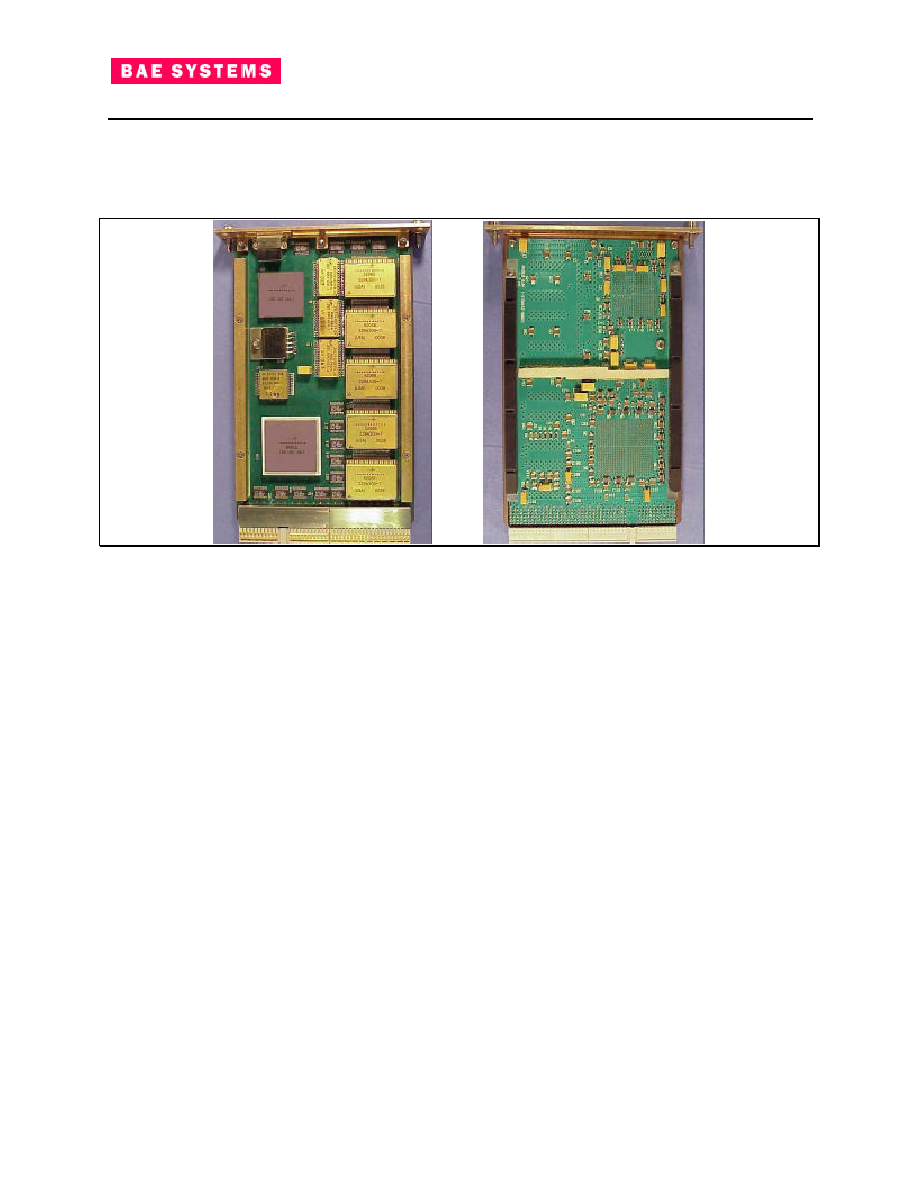

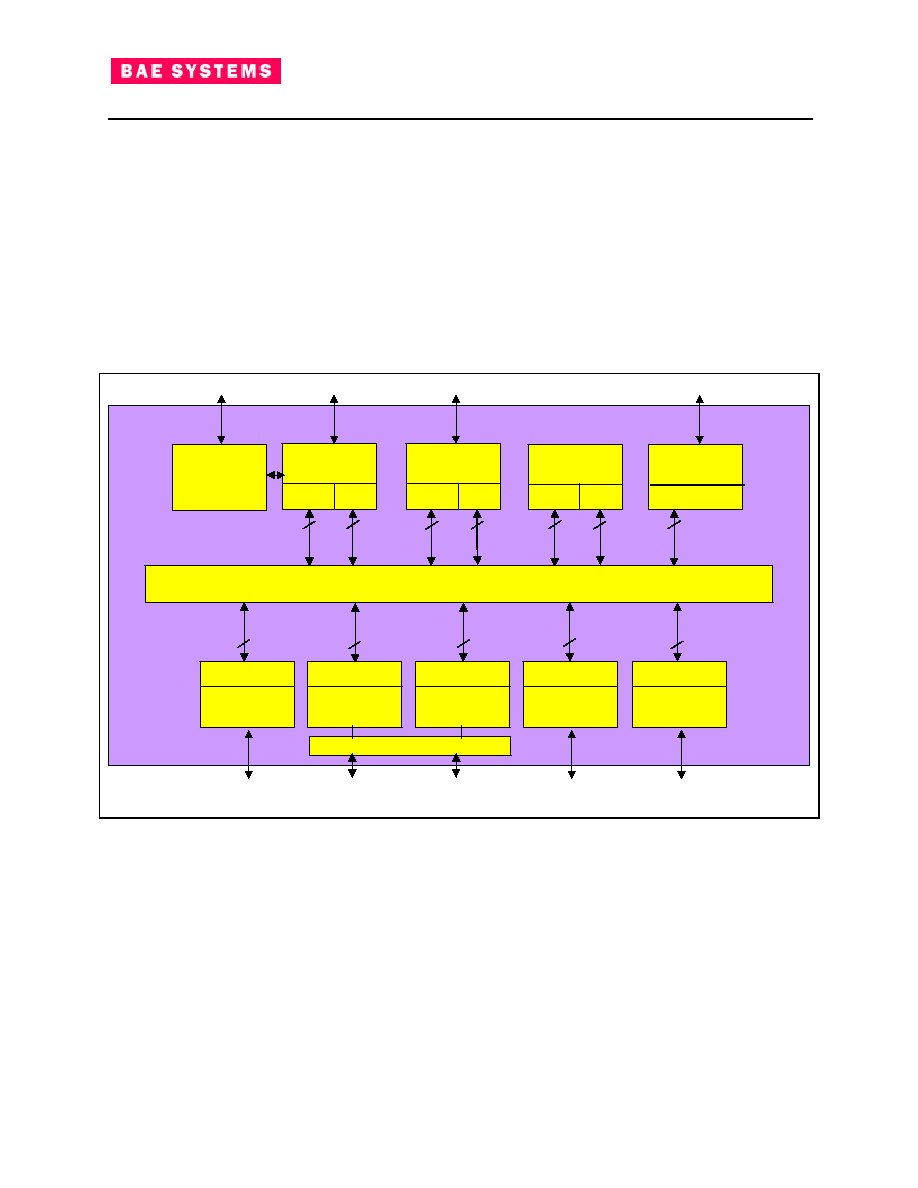

Figure 1: Notional C&DH Architecture using a RAD750 board ..................................................................5

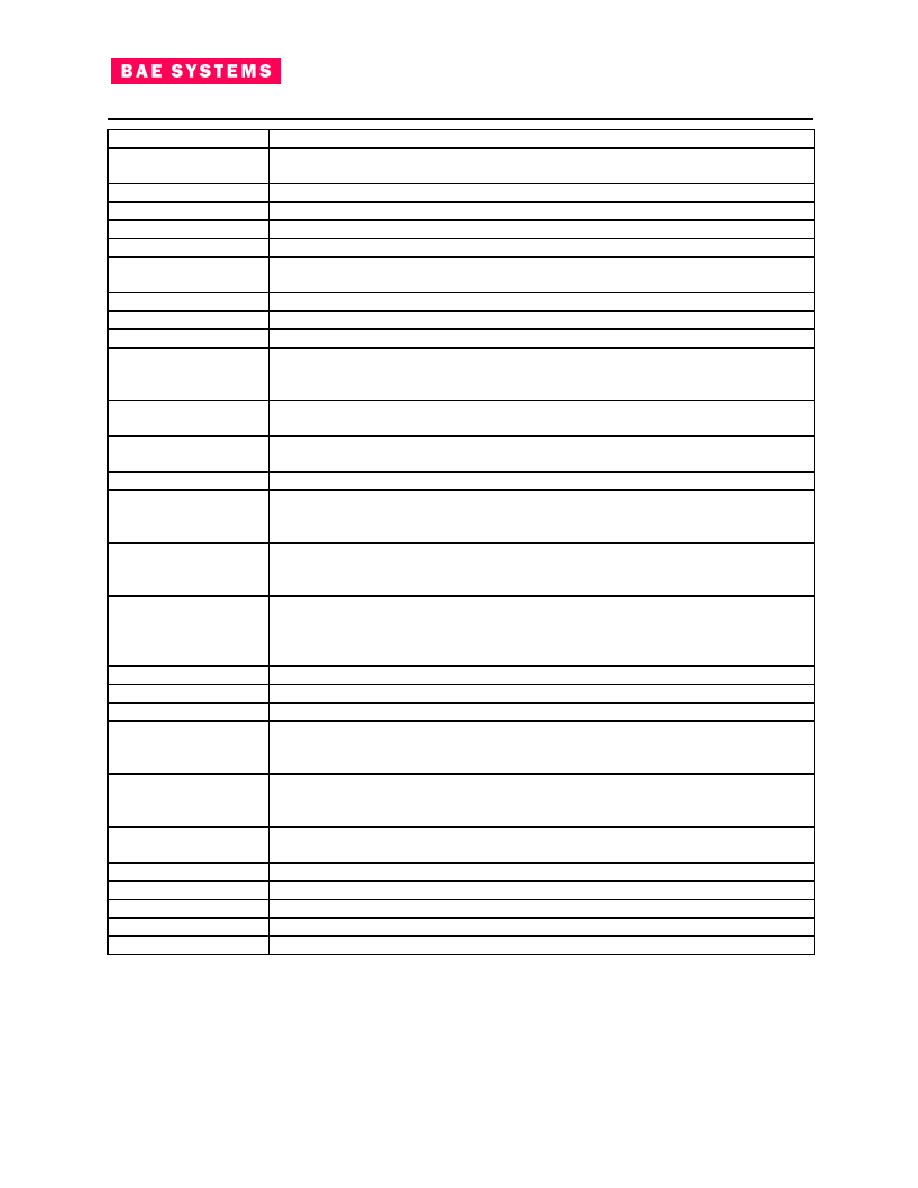

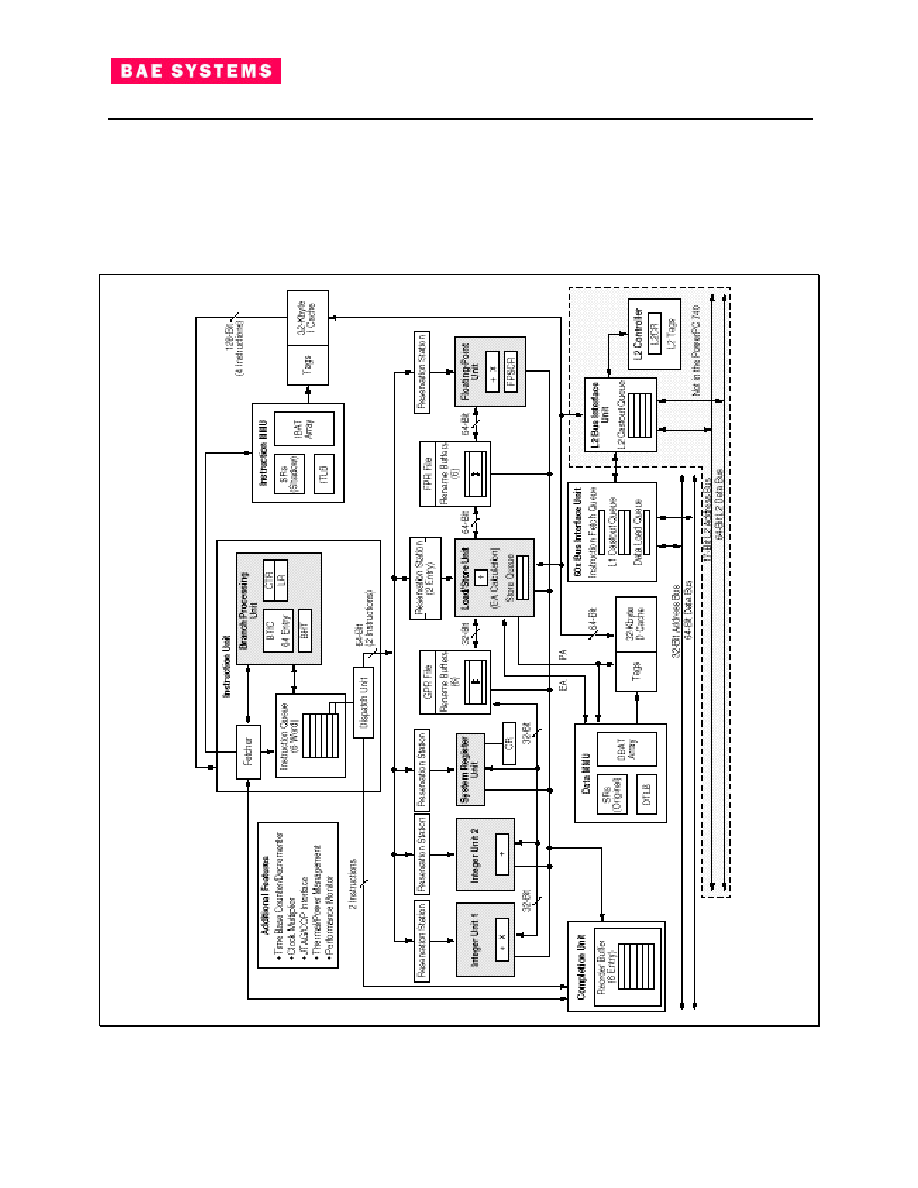

Figure 2: RAD750 Board Block Diagram ..................................................................................................6

Figure 3: Board identification label .........................................................................................................11

Figure 4: RAD750 Microprocessor Block Diagram..................................................................................22

Figure 5: Power PCI Chip on a Processor Board ....................................................................................26

Figure 6: Power PCI Cores ....................................................................................................................27

Figure 7: PCI Core Block Diagram .........................................................................................................28

Figure 8: 60X Core functional block diagram ..........................................................................................32

Figure 9: GP Timer Functional Block Diagram........................................................................................35

Figure 10: Clock Generation Logic .........................................................................................................36

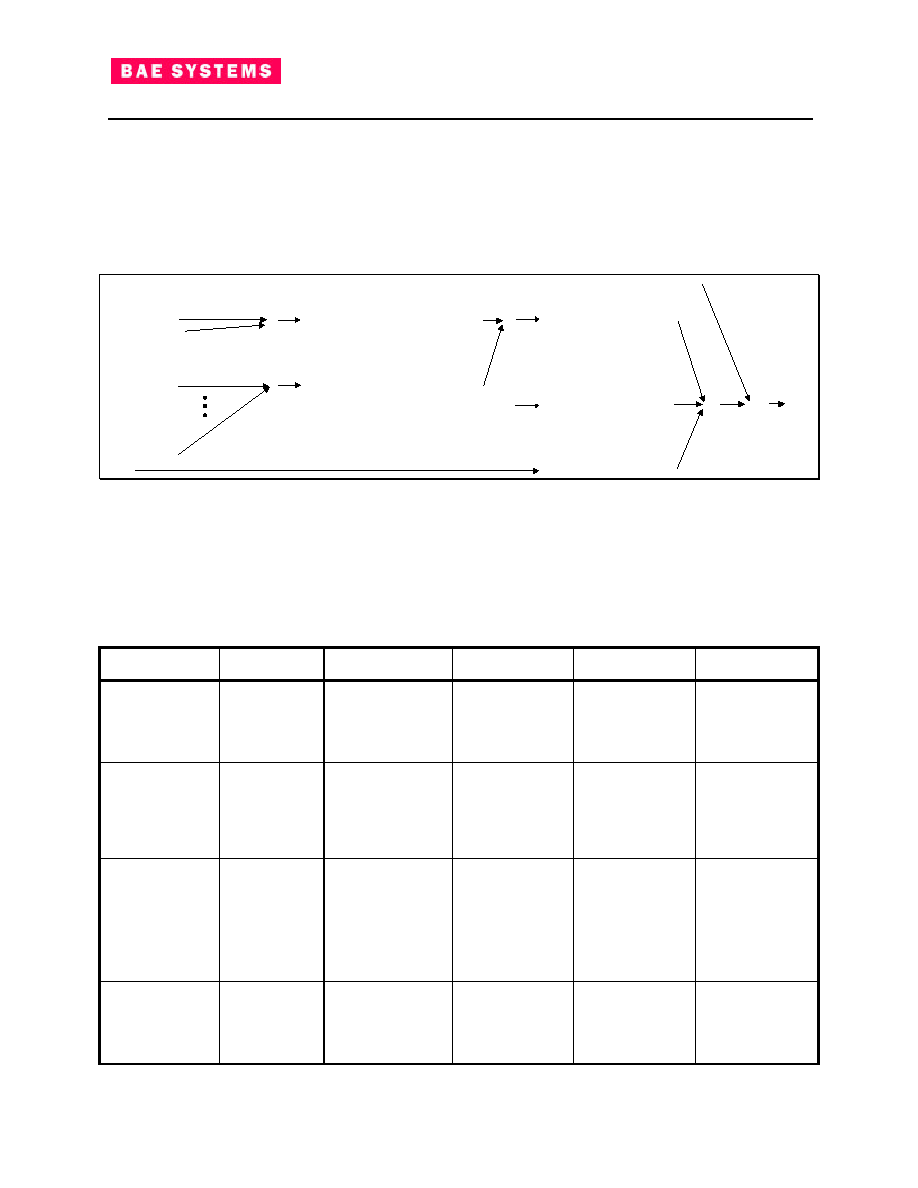

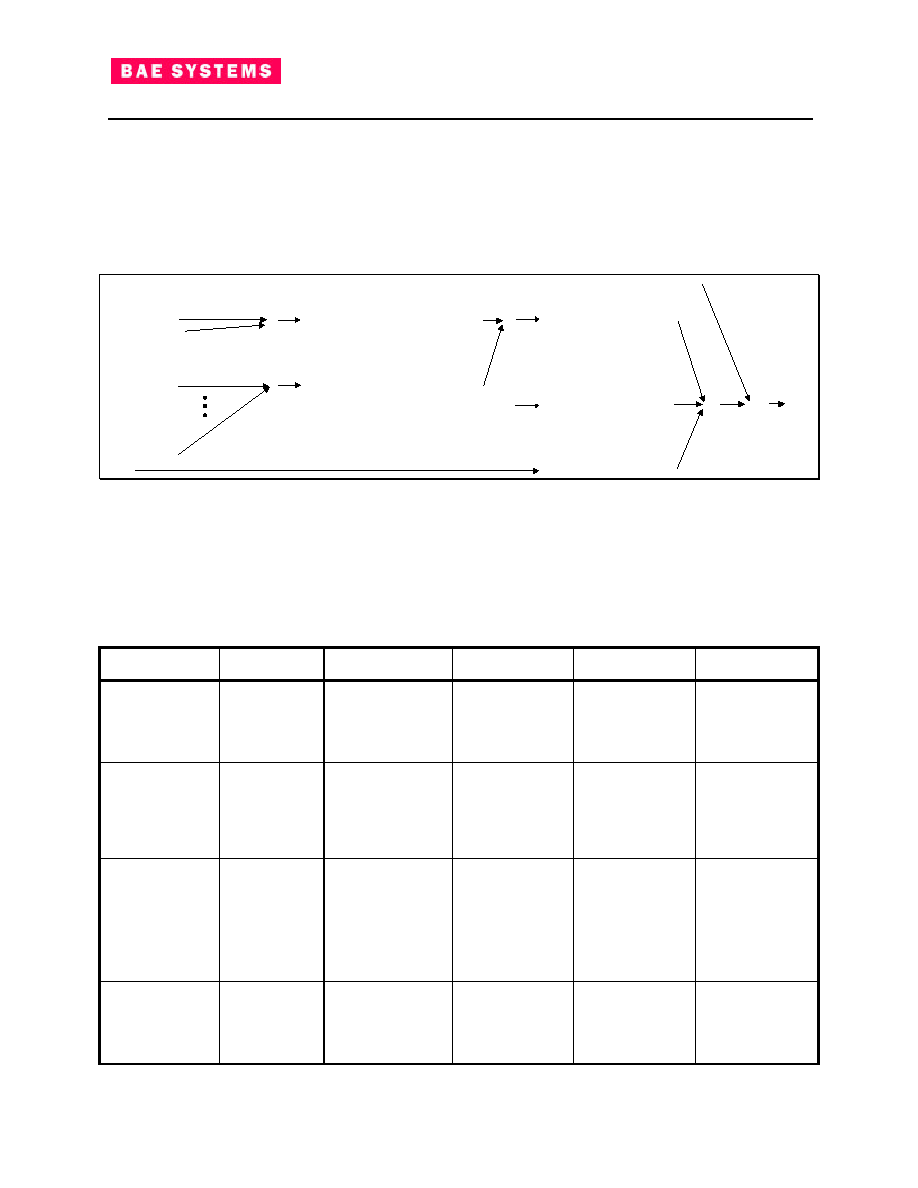

Figure 11: Data Transfers in Big Endian Mode. ......................................................................................41

Figure 12: Data Transfers in Little Endian Mode.....................................................................................42

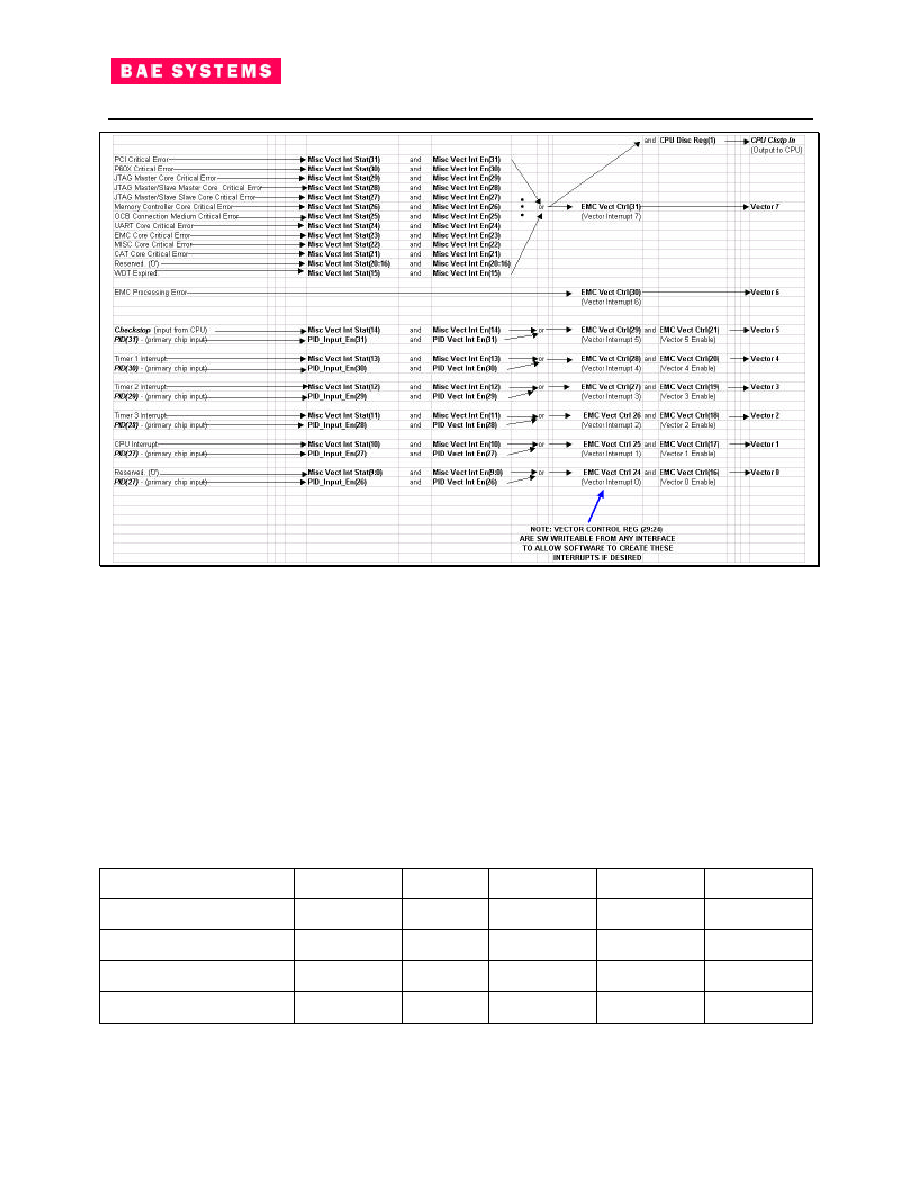

Figure 13: Power PCI Interrupt Collection ..............................................................................................43

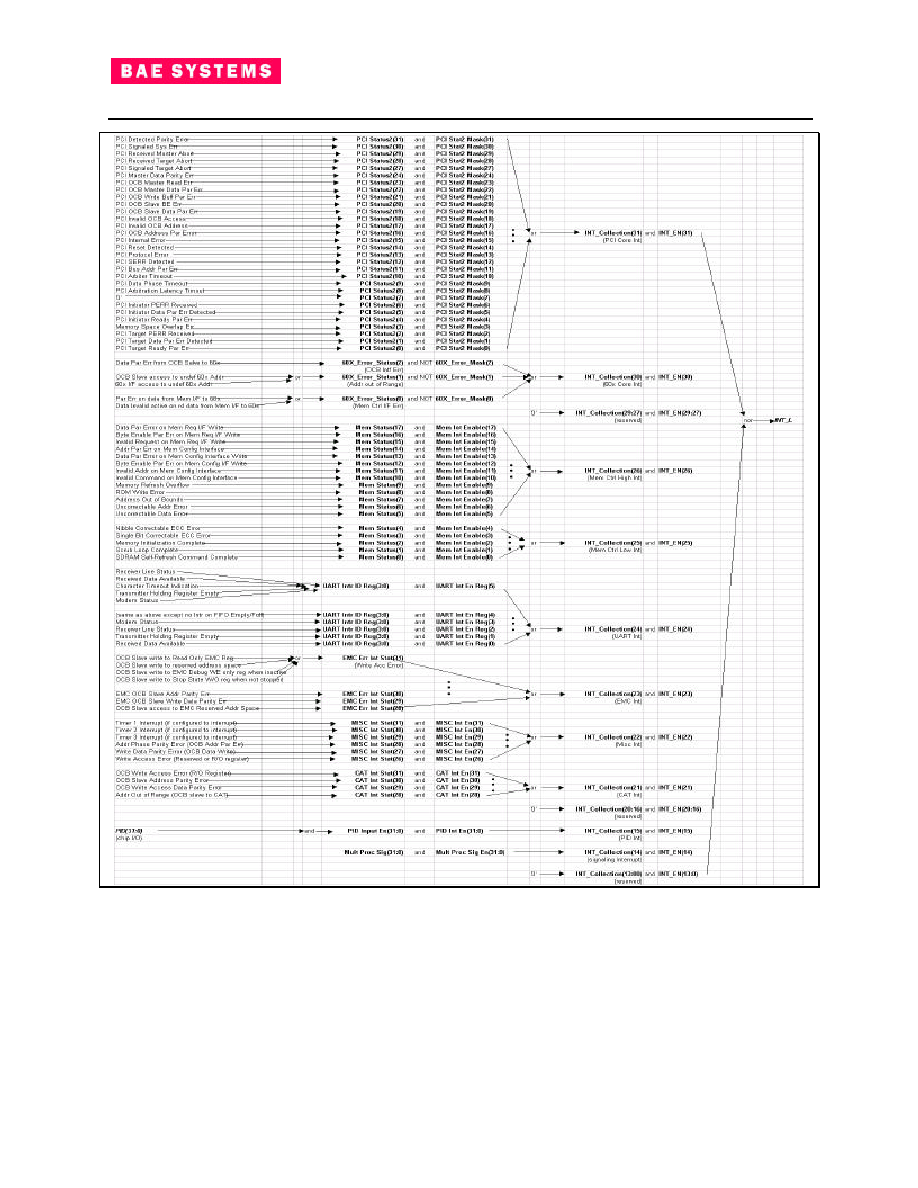

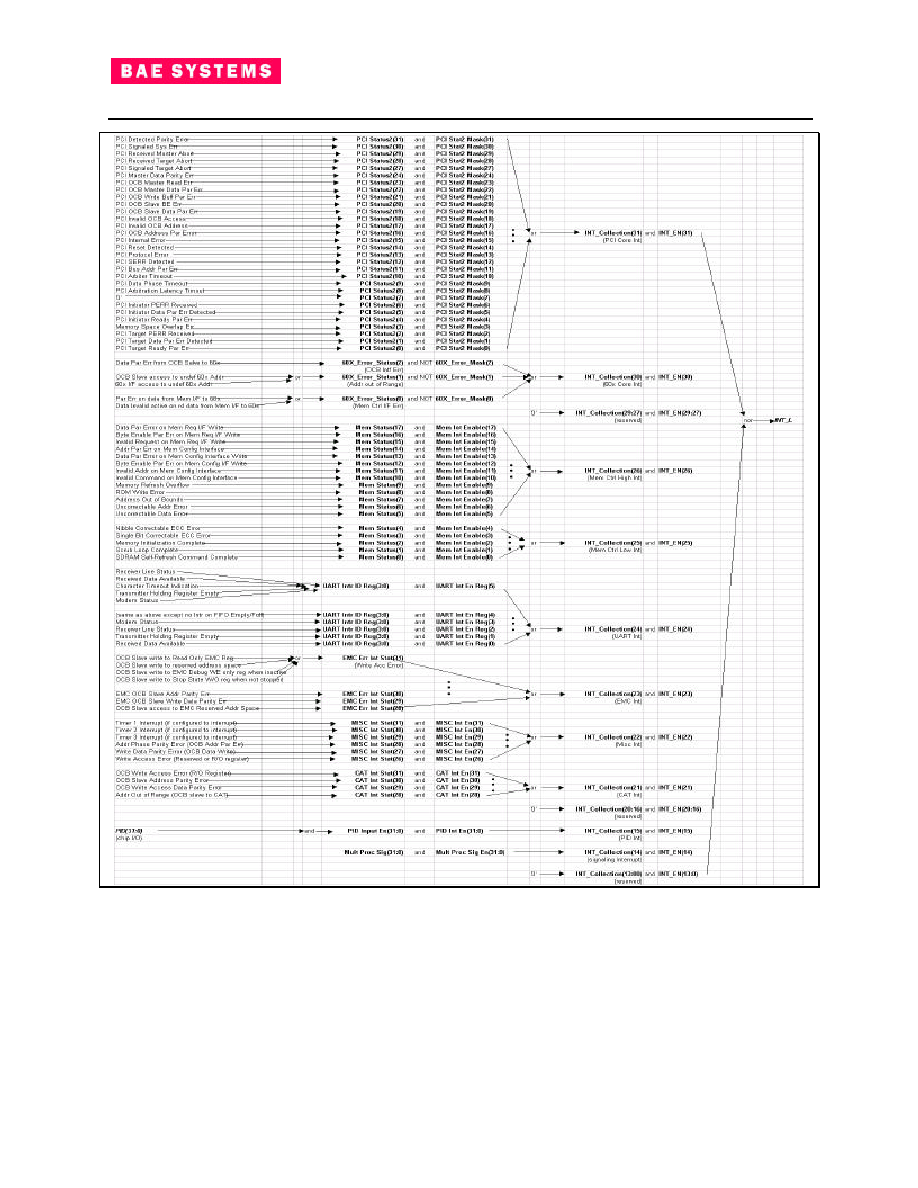

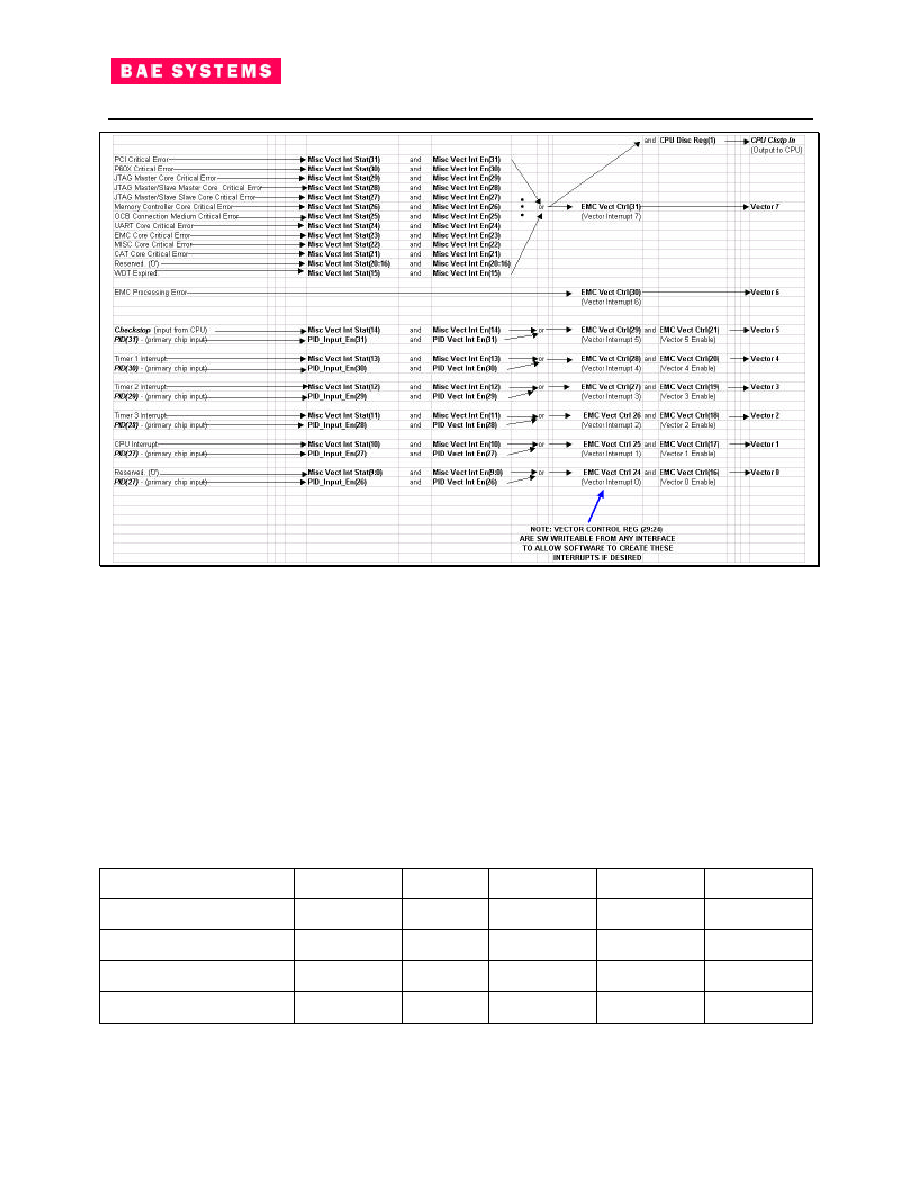

Figure 14: Power PCI INT_L Interrupt Tree ............................................................................................44

Figure 15: Power PCI MCP Generation Tree..........................................................................................46

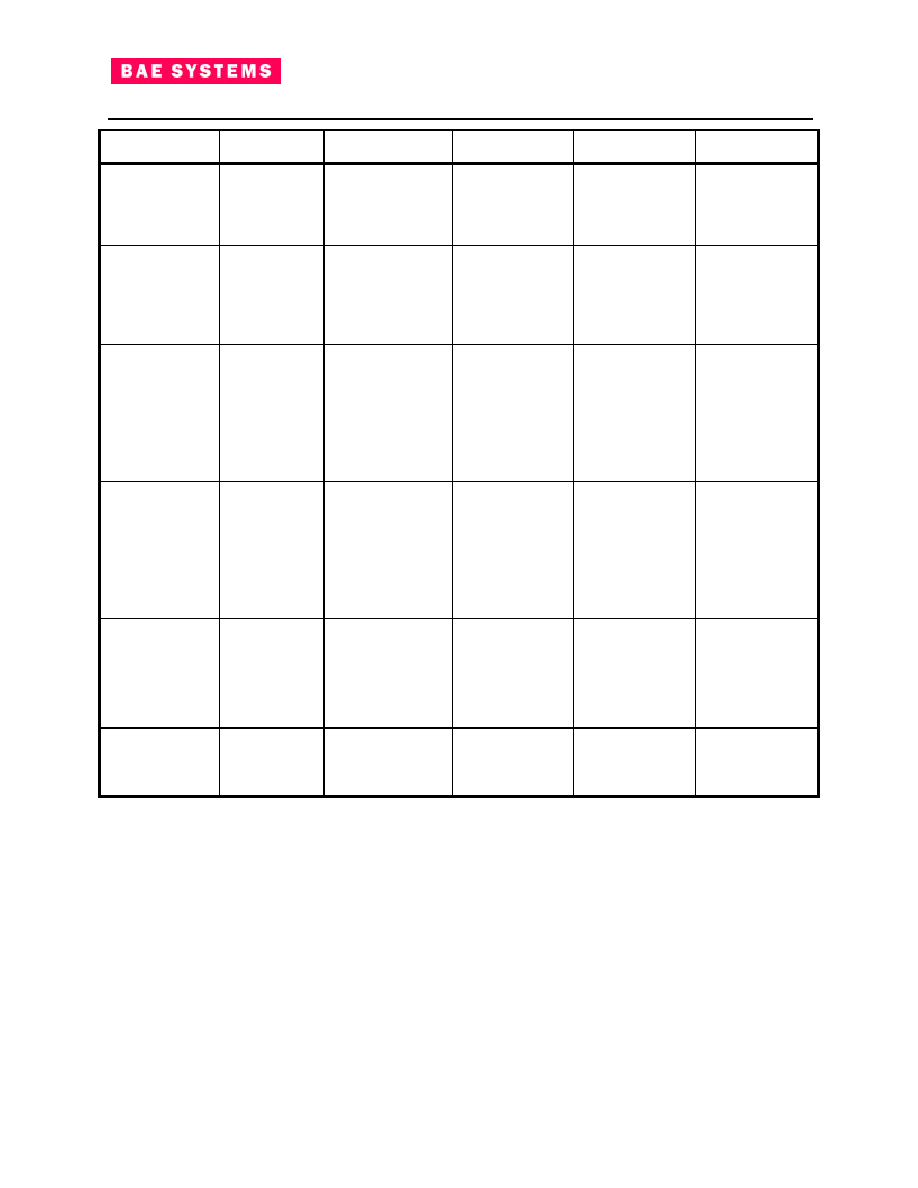

Figure 16: Power PCI Checkstop Generation Tree and Vector Interrupt Tree .........................................49

Figure 17: JTAG Backpanel Interface I/O ...............................................................................................67

Figure 18: JTAG RAD750 Interface I/O ..................................................................................................69

Figure 19: JTAG Slave Interface I/O.......................................................................................................70

Figure 20: Peripheral Device Interface I/O..............................................................................................71

Figure 21: Isometric View of the RAD750 Board Layout .........................................................................77

Figure 22: Standard View of the RAD750 Board Layout .........................................................................78

Figure 23: RAD750 Board Layout ..........................................................................................................79

vii

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

List of Tables

Table 1 - RAD750 3U CompactPCI board Maximum Power Consumption with V

cc

= 3.3

±

5% VDC, GND =

0 VDC, -55

T

j

< 125

o

C....................................................................................................................8

Table 2 - RAD750 3U CompactPCI board Typical Power Consumption with V

cc

= 3.3 VDC, GND = 0 VDC,

T

MR

= 25

o

C........................................................................................................................................8

Table 3 - Specification of the RAD750 board (Flight Configuration) ..........................................................8

Table 4 - RAD750 board Part Number Listing ........................................................................................10

Table 5 - CompactPCI J1 Connector Signals .........................................................................................17

Table 6 - CompactPCI J2 Connector Pinouts .........................................................................................18

Table 7 - Front Panel Connector J7 Pin Assignments.............................................................................20

Table 8 - PCI User Defined Register Definitions .....................................................................................28

Table 9 - UART Baud Rate Programming ..............................................................................................34

Table 10 - Power PCI Power Management Operational Modes ..............................................................40

Table 11 - Interrupt Register Definition...................................................................................................45

Table 12 - Error Mechanisms .................................................................................................................46

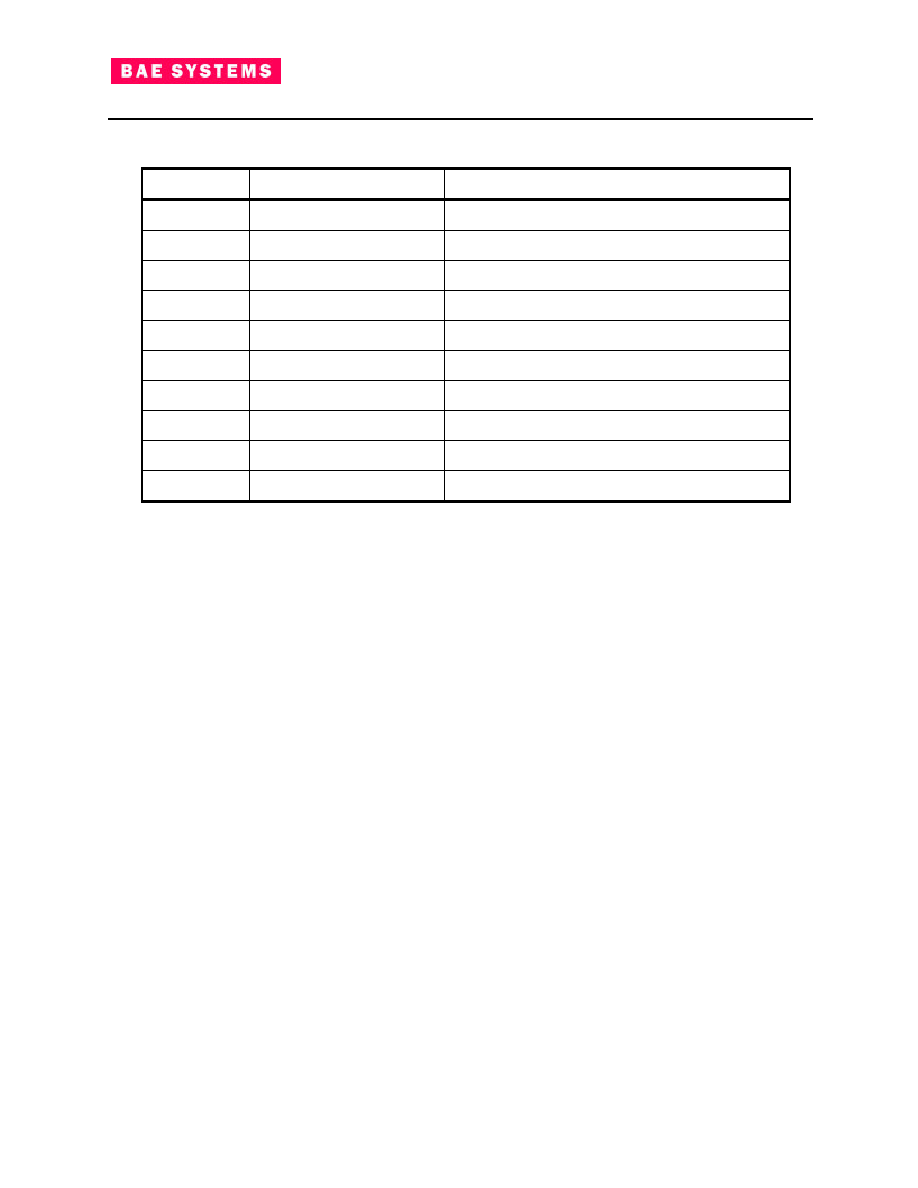

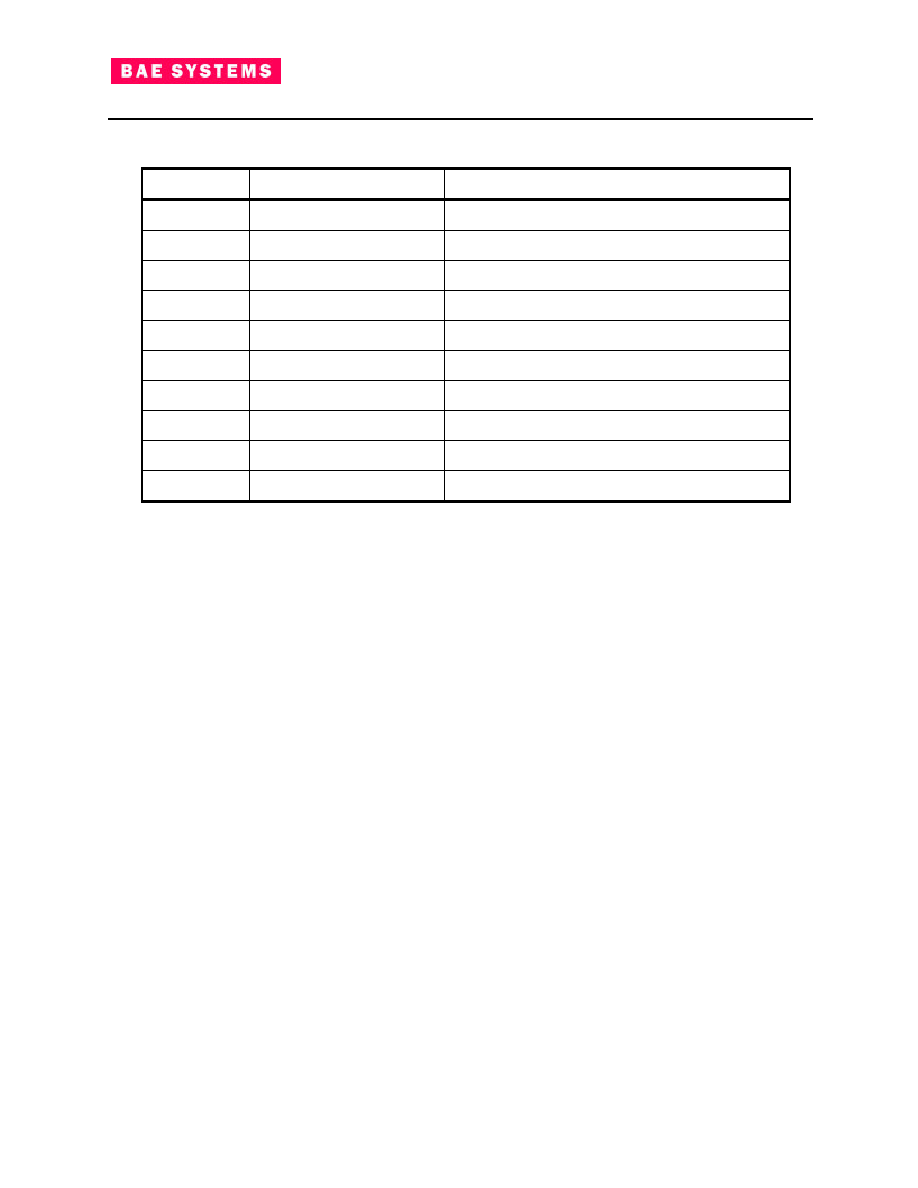

Table 13 - RAD750 board Interrupt Latencies.........................................................................................49

Table 14 - X2000 System Flight Computer PCI Interface Signals ...........................................................50

Table 15 - X2000 System Flight Computer Non-PCI Signals ..................................................................62

Table 16 - PID Definition Table ..............................................................................................................73

Table 17 - Organic Materials ..................................................................................................................82

Table 18 - Inorganic Materials................................................................................................................83

Table 19 - Processes .............................................................................................................................83

Table 20 - Bill of Materials......................................................................................................................85

1

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

1 Using This Manual

This section does not provide information on the product, but on features of the manual itself:

∑

its structure,

∑

special layout conventions, and

∑

related documents.

This manual is separated into two parts: The main Hardware User's Manual (this document), and an

Appendix. The Appendix contains the detailed register maps and descriptions that are part of the Power

PCI ASIC and how they are utilized on this board.

1.1 Audience of the Hardware Users Manual

The Hardware Users Manual is intended for hardware and software developers installing and integrating

the RAD750 3U CompactPCI board into their systems. Software engineers who are developing or

troubleshooting code are expected to use the interface portion of this manual. The manual includes full

descriptions of all dedicated I/O locations, specific I/O commands and registers, programmed I/O, and I/O

command partitioning. It includes a detailed memory map with the paging scheme.

1.2 Overview of the Manual Set

The Hardware Users Manual provides a comprehensive hardware guide to your board.

IMPORTANT: Take a moment to examine the "Table of Contents" of the Hardware Users Manual to see

how this documentation is structured. This will be of value to you when looking for information in the

future. The Hardware Users Manual includes:

∑

A brief overview of the product, the specifications, and the ordering information: see Section 2

"Overview".

∑

The installation instructions for powering up the board: see Section 3 "Installation Instructions". It

includes the default configuration, initialization, and connector pinouts.

∑

A detailed hardware description: See Section 4"Hardware / Electrical".

∑

A detailed description of the CompactPCI connector I/O: see Section 5 "CompactPCI Defined

Signals".

∑

A detailed mechanical description of the RAD750 board: see Section 6 "Hardware / Mechanical".

∑

A description of the RAD750 board manufacturing processes: see Section 7 "Manufacturing".

∑

Sources of additional information, including the latest version of the document: see Section 8

"Documentation".

This manual includes a pictorial/diagrammatic description of the RAD750 board hardware internal

functions. External interfaces are included to ensure logical written and pictorial continuity and

completeness. The descriptions are written so that reference to other documents is not required for

immediate understanding. The manual includes explanations of internal hardware. The Power PCI

internal controller, it's addressing modes, I/O control and memory mapping are explained in detail.

Interrupts, status registers, fault types, causes and protection are included. Error detection and correction

strategies, as used, are detailed. The test, power, electronic and electrical interface specifics are

described. Mechanical, structural and environmental requirements and interfaces are also detailed. A

troubleshooting tree is included.

All implemented I/O commands are included. This manual includes detailed coverage and explanation of

interrupts, and memory mapping. Peculiar system interfaces such as dedicated memory locations,

channel register definitions, command code assignments and definitions, multiple channel priorities, and

page register access are detailed. Although this manual is a software tool, hardware handling of the I/O

process internal and external to the hardware/software is included. All hardware/software configurations

are included. Interfaces peculiar to the test configuration are clearly described and illustrated.

2

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

The Hardware Users Manual addresses the engineering model and flight versions of the RAD750 board

in detail.

1.3 Software Users Manual

In addition to the Hardware Users Manual, BAE SYSTEMS provides a software Users Manual and a

Support Equipment Users Manual. These two documents describe how to develop software for the

RAD750 3U CompactPCI board, describe the Board Support Package (BSP) and SUROM products, and

the recommended test development environment for the RAD750 board. See Section 8 to see how to

obtain copies of these 2 documents.

1.4 RAD750 / Power PCI Set of Data Sheets

The RAD750 / Power PCI Set of Data Sheets, which contains the data sheets relevant for configuring and

integrating the board into systems, is packaged in an separate binder to ease handling. It is always

shipped together with the Hardware Users Manual. The RAD750 / Power PCI Set of Data Sheets

includes the following datasheets:

∑

LM/STC RAD750

∑

LM/STC PowerPC-to-PCI Bridge

∑

Q-Tech Oscillator

∑

LM/STC 256 Mbit SDRAM Stack

∑

SEI EEPROM

∑

OmniRel Voltage DC/DC Converter

1.5 Revision History

REVISION

REVISION HISTORY

DATE

1.0

Initial release

9/9/99

2.0

Updated Release ≠ Environmental Spec changes, minor updates

4/28/00

3.1

12/20/00

1.6 Conventions / Nomenclature

The following conventions are used in the text of this document:

The following conventions apply except were specifically noted.

∑

In PowerPC terminology, multiple bit fields are numbered from 0 to n, where 0 is the MSB and n

is the LSB.

∑

PCI terminology follows the convention that bit 0 is the LSB and n is the MSB.

∑

When counting N elements, the first element is designated element 0 and the last element is

designated element N-1.

∑

Information of particular importance is in bold typeface and is further highlighted by the NOTE

reference.

∑

Signal names are fully capitalized and use a bold font: SIGNAL1

∑

Active low PCI I/O signals are suffixed with the `#' symbol to be consistent with the PCI

specification. All other active low signals are suffixed with `_L'. Note that this does not

supersede the coding requirement that all active low signal names are coded using the `_L' suffix:

FRAME#, SIGNAL2_L

∑

Internal register names have leading caps and use a bold font: Device ID, Status

∑

Register field or bit names have leading caps and use a bold and italicized font: Bus Master

∑

All numbers are expressed in decimal, except addresses and memory or register data, which are

expressed in hexadecimal: 0x'0F'; or binary: 0b'0110' or `1', following the 'C' programming

language convention.

3

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

∑

An `n' denotes bit definitions.

∑

An `xnnnn' denotes word definitions.

∑

The multipliers 'k', 'M' and 'G' have their conventional scientific and engineering meanings of *10

3

,

*10

6

and *10

9

, respectively. The only exception to this is in the description of the size of memory

areas, when 'K', 'M' and 'G' mean *2

10

, *2

20

and *2

30

, respectively.

∑

When describing transfer rates, `k', `M' and `G' mean *10

3

, *10

6

and *10

9,

not *2

10

, *2

20

and *2

30

,

respectively.

∑

Names of external signals which have a single destination are of the form <source

block>_<destination block>_<signal>.

∑

Names of external signals which have a multiple destinations are of the form <source

block>_<signal>.

1.7 Terminology

The following terms are used throughout this document.

Term

Description

Active Bank

A physical bank (or sub-bank) of SDRAM which has already received a "Bank

Activate" command, thereby selecting a row. Once a bank is active, the bank

must be precharged before another "Bank Activate" command can be issued to

select a different row.

Active Scrubbing

A memory scrubbing process in which the memory controller inserts extra

memory read operations during idle cycles to detect and correct data errors.

ASIC

Application Specific Integrated Circuit

Bank

A memory part (or, more typically, a group of memory parts) which provides a

complete data vector. A complete data vector typically contains 64-bits of data

and 8, 16 or 24 ECC bits.

Bank Miss

A memory operation that does not address an open bank.

BAR

Base Address register

Big Endian

The ordering of data such that the most significant byte is stored at the lowest

order address.

BIST

Built-in Self Test

Byte

An 8-bit value.

Byte-Enabled Write

A write in which some bytes of a data beat are not stored to memory.

Cache Line

A cache line consists of 4 double words (32 bytes).

Character

In this document a character refers to a byte of data that is stored into a FIFO.

Column

In the context of internal SDRAM layout, the column is used in conjunction with

the SDRAM row to select a single bit (per data output bit) from the SDRAM

memory matrix.

Data Beat

A single unit of data, usually a data beat is a double word.

Double word

A 64-bit value.

Doze Mode

A power management mode that consumes more power than Sleep Mode, but

less power than Normal Mode. . See also Nap, Normal and Sleep Modes.

DWORD

32-bit block of data (4 bytes)

FIFO

First In First Out. Bank of registers that store data, such that the first set of data

stored is the first data that is read out.

Half word

A 16-bit value.

HDL

Hardware Description Language - A language for describing digital electronic

systems.

JTAG

Joint Test Action Group Interface. Refers to the test interface standardized in

IEEE 1149.1a

JTAG Master

A TAP Controller and associated logic that controls JTAG Slave(s) located

outside the function.

Little Endian

The ordering of data such that the most significant byte is stored at the highest

4

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

Term

Description

order address. The endian ordering of data never extends beyond an 8 byte

group of storage.

lsb

least-significant bit

LSB

Least-Significant Byte

Marking State

Logic `1'.

Memory Scrubbing

The process of writing memory to correct a data error in the memory.

Memory Sparing

The process of using extra (or spare) columns of memory to replace failed

columns.

msb

Most-significant bit

MSB

Most-Significant Byte

Munging

A transformation of the address to convert between endian modes.

Nap Mode

A power management mode of the RAD750 or Power PCI, which consumes

more power than Sleep Mode, but less power than Normal Mode. See also

Normal, Doze and Sleep Modes.

Normal Mode

The typical (full-power) operational mode of the RAD750 or Power PCI. See

also Doze, Nap and Sleep Modes.

One-hot State

Machine

Each state of the state machine has its own register bit.

Open Bank

Same as Active Bank.

Parity

Can be odd or even. Even Parity indicates that the number of ones in the data

and parity bit is even, and likewise odd parity indicates that the number of ones

is odd.

Passive Scrubbing

A memory scrubbing process in which the Power PCI memory controller only

looks for and corrects data errors at memory locations that the Power PCI has

read.

PCI

Peripheral Component Interconnect. Refers to the PCI Local Bus as defined in

the PCI Local Bus Specification. Version 1.0 of the PCI specification was

developed by Intel Corporation and released on 6/22/92. The PCI Special

Interest Group (SIG) currently manages the specification.

POR

Power on Reset

Precharge

An SDRAM command that closes an open bank.

Record

A VHDL construct that can contain many signals of different types.

Row

In the context of internal SDRAM layout, a single bit-line selected by the Bank

Activate command. When used in conjunction with an SDRAM column, a single

bit (per data output bit) is selected from an SDRAM memory matrix.

RTL

Register Transfer Level. Refers to a HDL coding style that is characterized by

the explicit definition of all register to register transfers within the device being

described.

Sleep Mode

The lowest power operational mode of the RAD750 or Power PCI. See also

Normal, Doze and Nap Modes.

Spacing State

Logic `0'.

Sub-bank

A single internal bank in an SDRAM part with multiple internal banks.

VHDL

VHSIC Hardware Description Language - standardized in IEEE standard 1076

VHSIC

Very High Speed Integrated Circuit

Word

A 32-bit value.

5

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

2 Overview

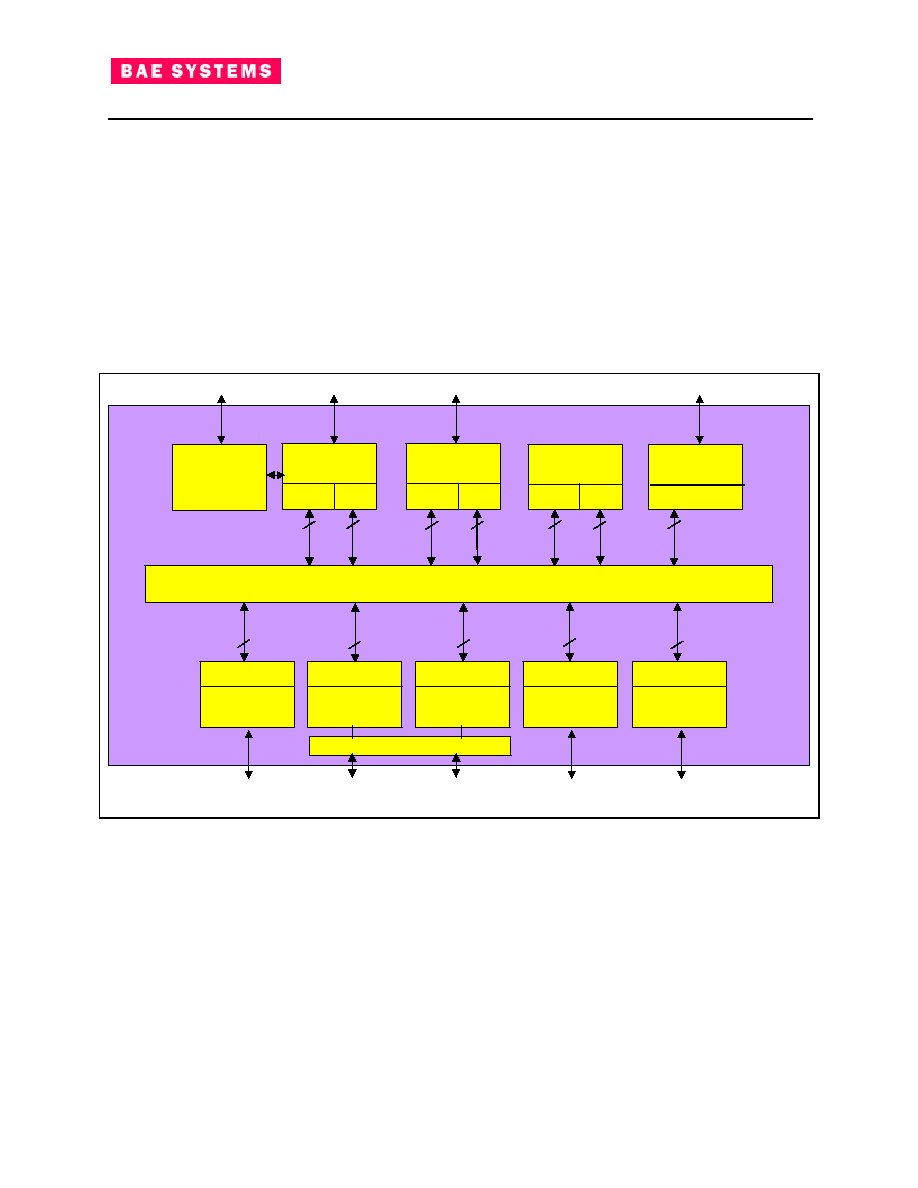

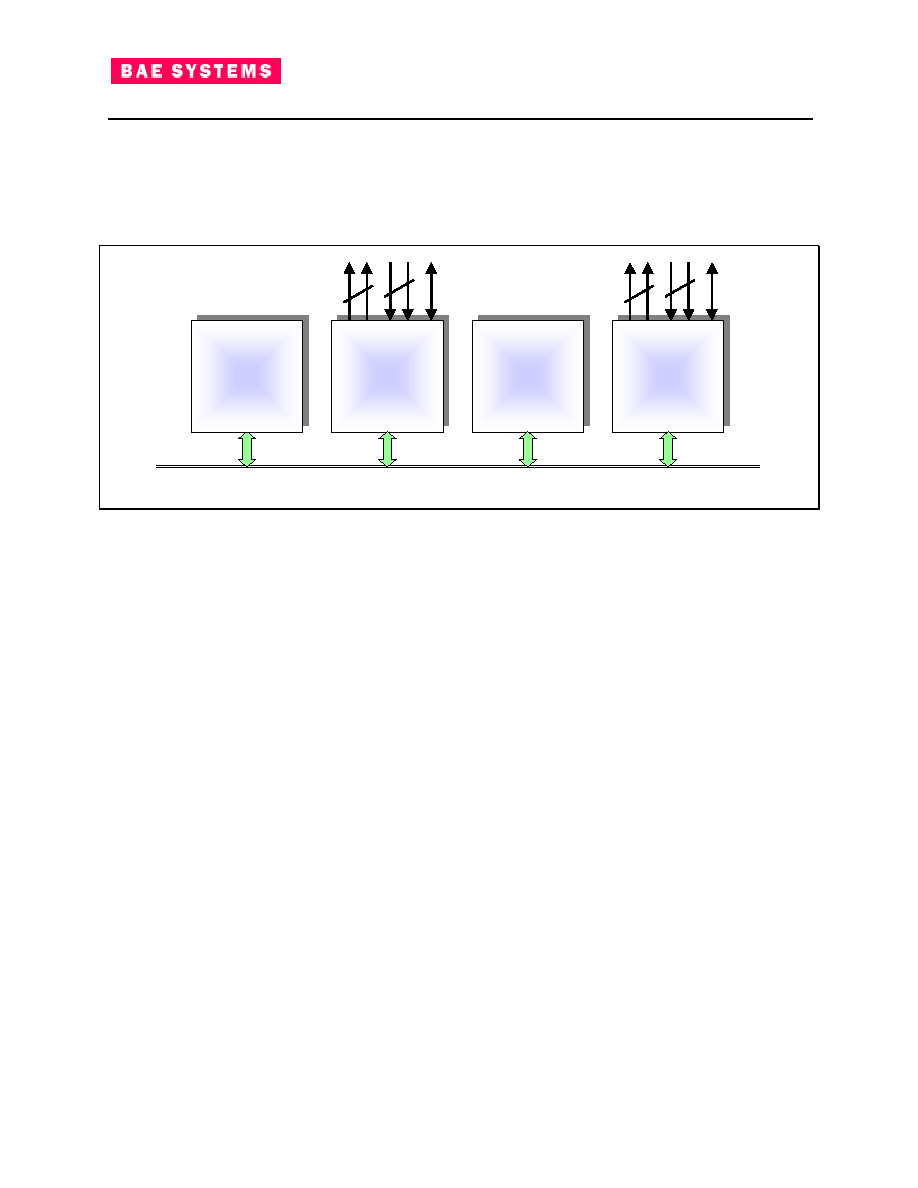

The RAD750 3U CompactPCI board is designed to provide the main computational capability for a

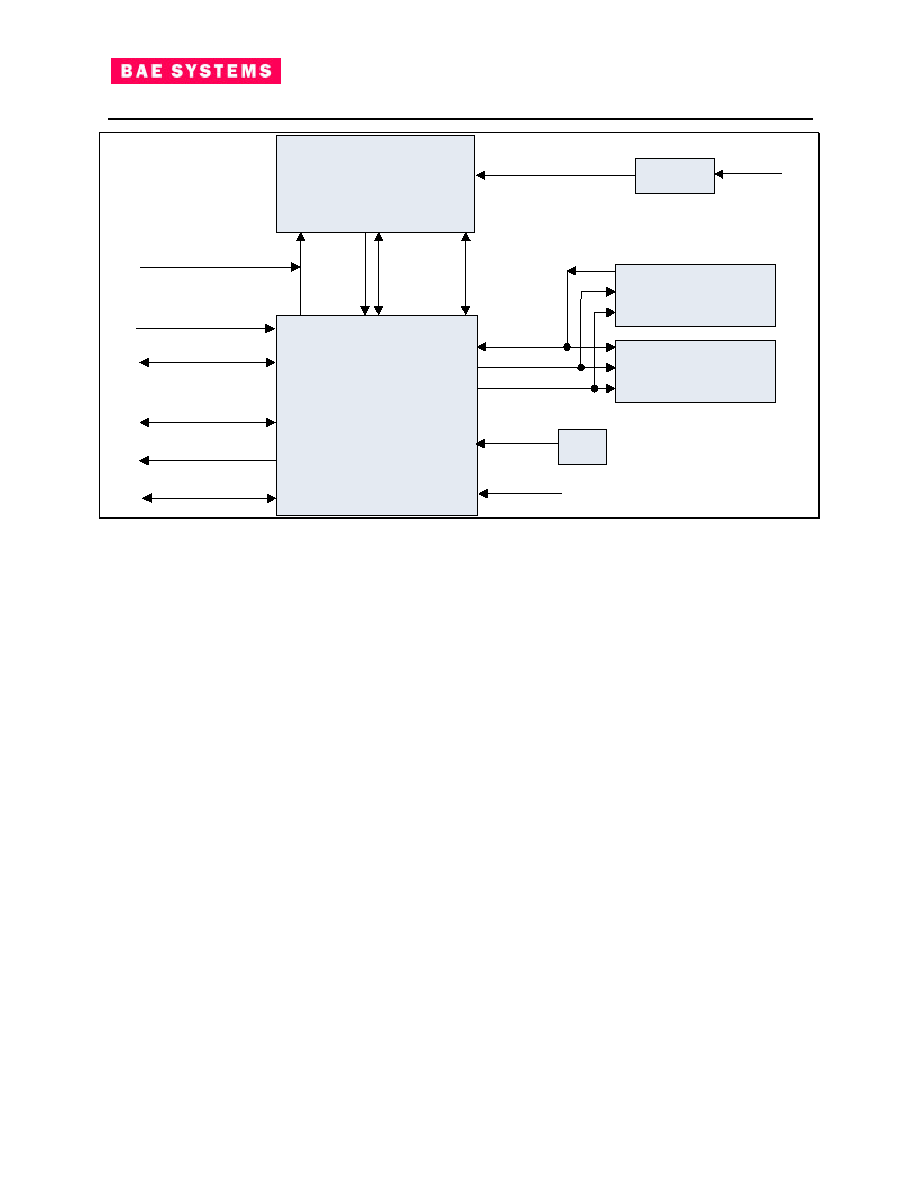

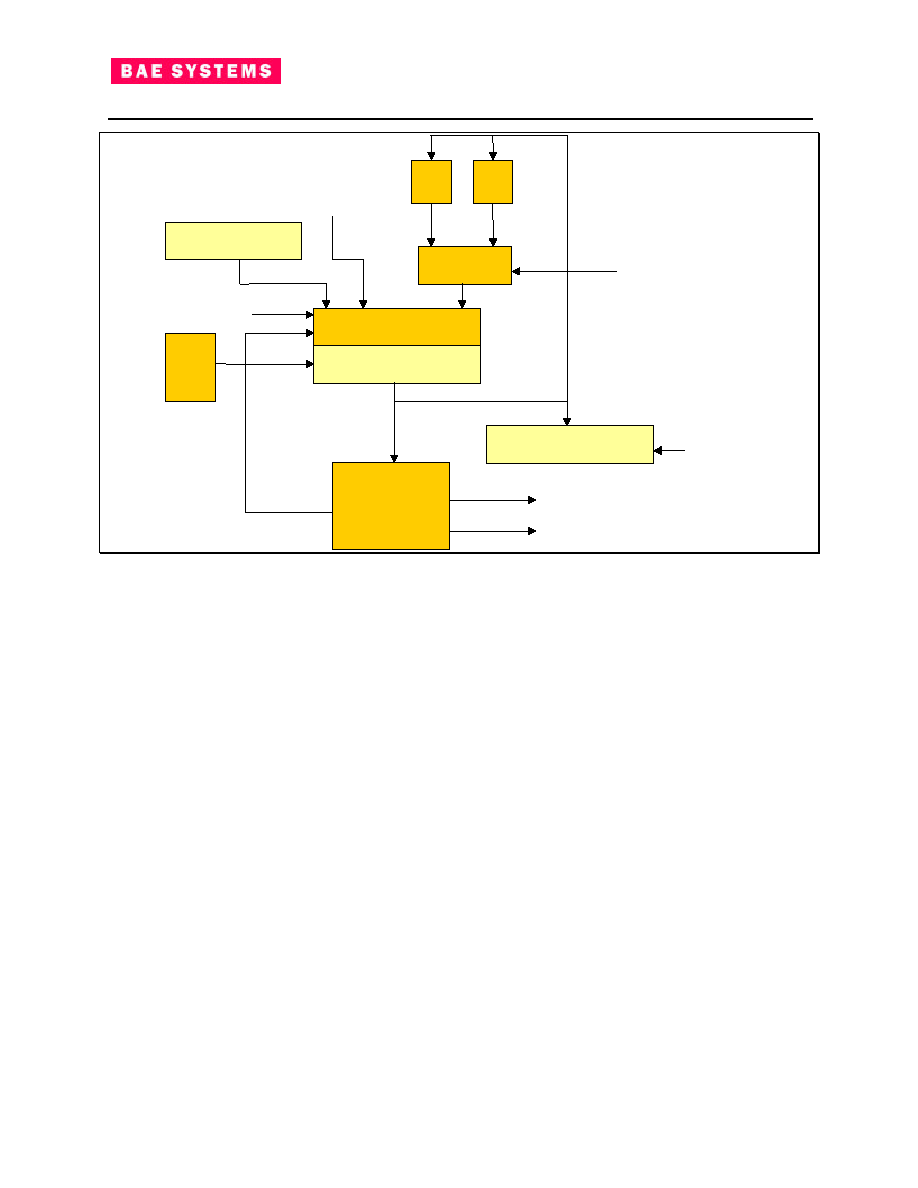

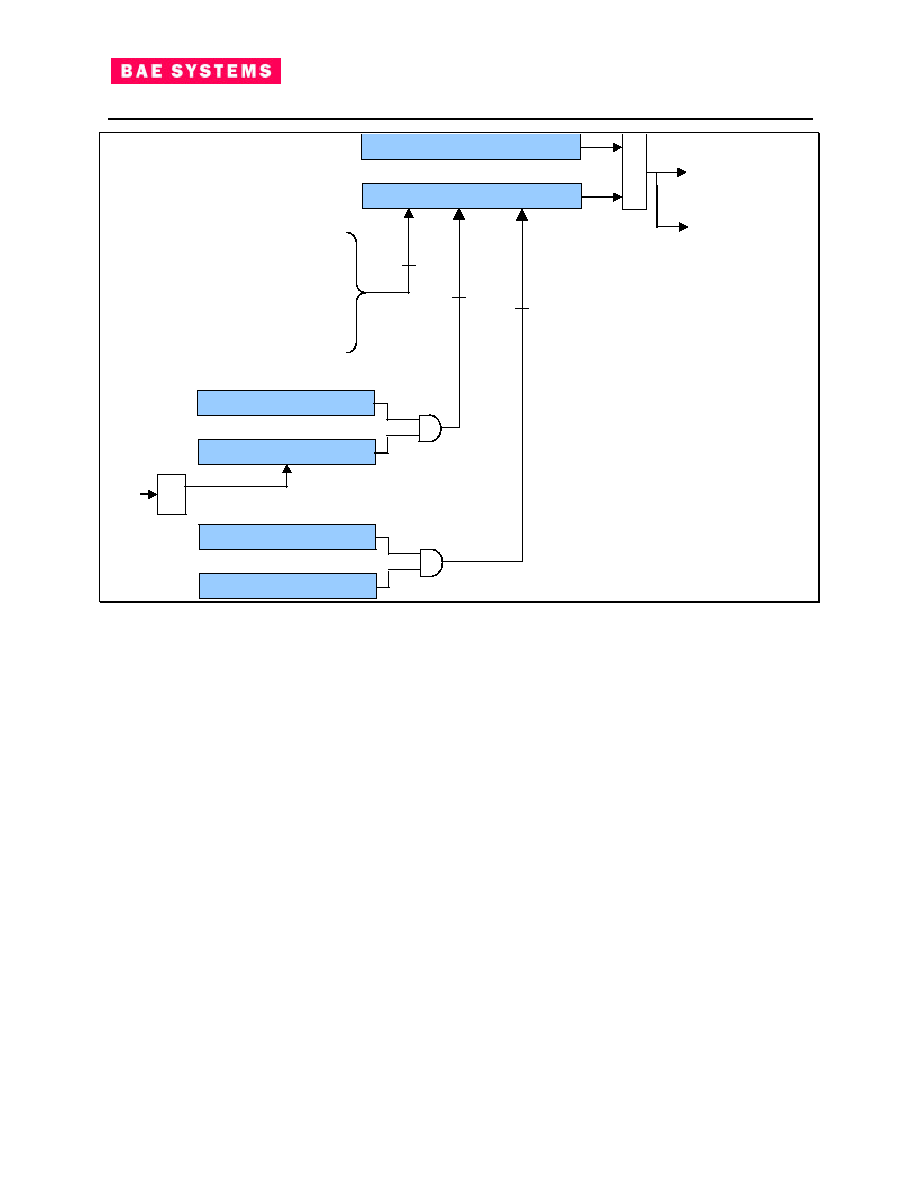

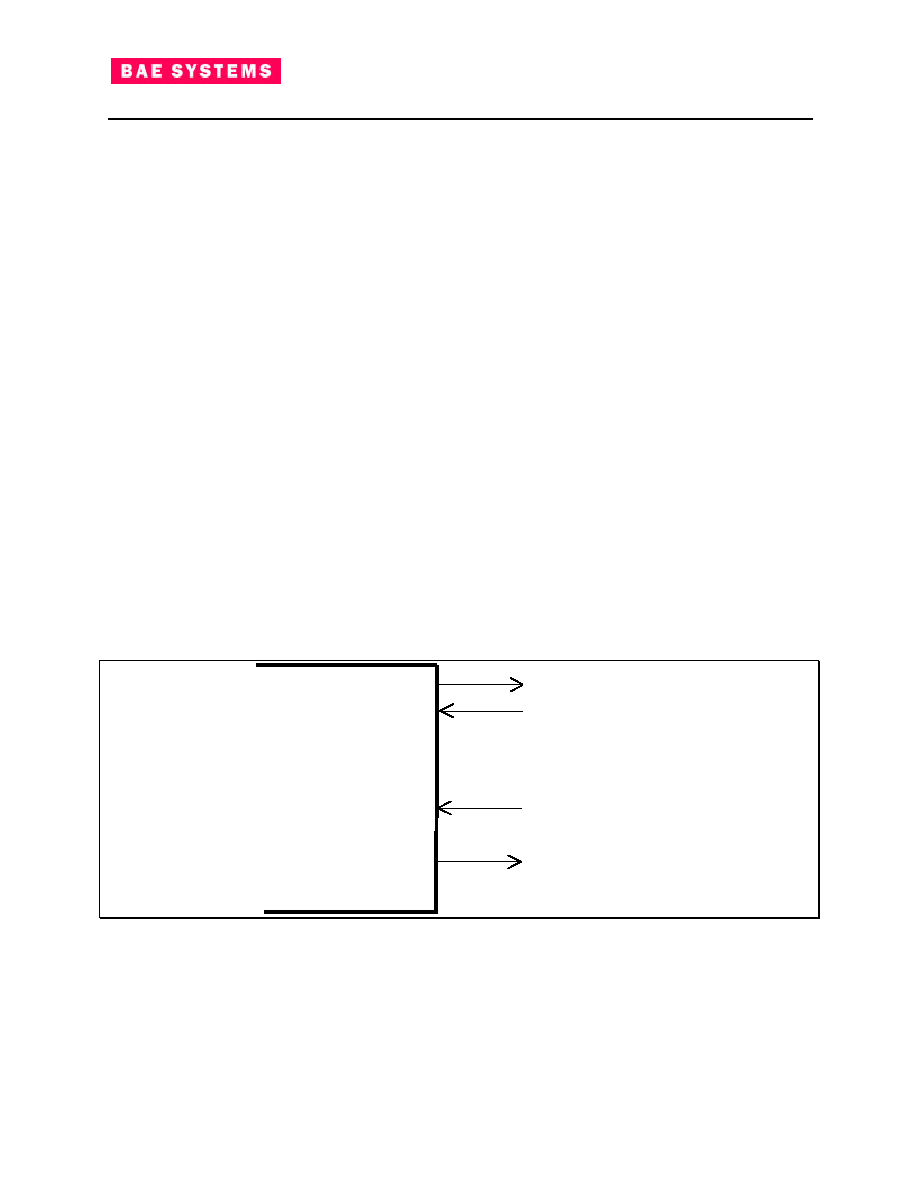

spacecraft. Figure 1 shows the RAD750 3U CompactPCI board combined with other I/O and memory

boards to form the main processing elements of an spacecraft avionics command and data handling

(C&DH) system.

Bulk Memory

Bulk Memory

Spacecraft

I/O and TT&C

Spacecraft

I/O and TT&C

RAD750

RAD750

Payload I/O

Payload I/O

PCI and JTAG Buses

Figure 1: Notional C&DH Architecture using a RAD750 board

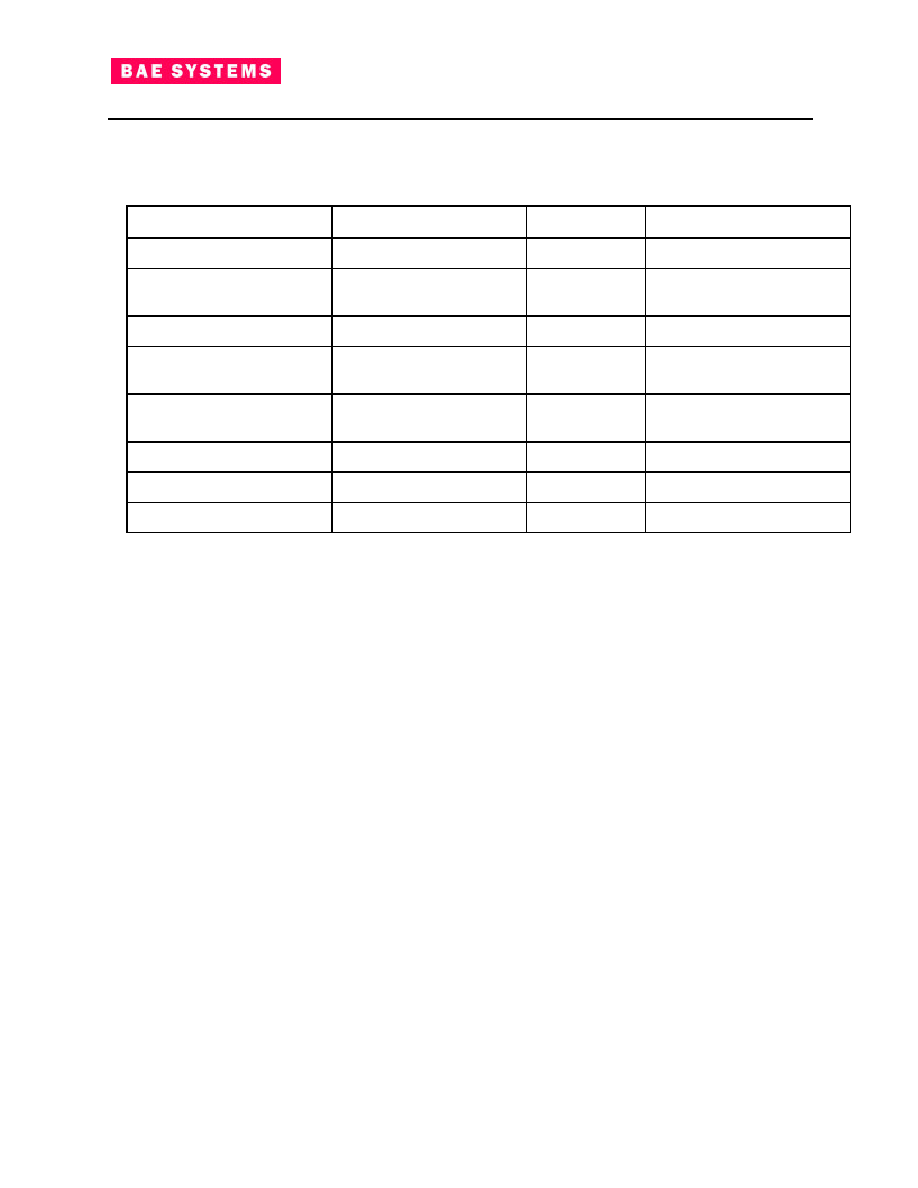

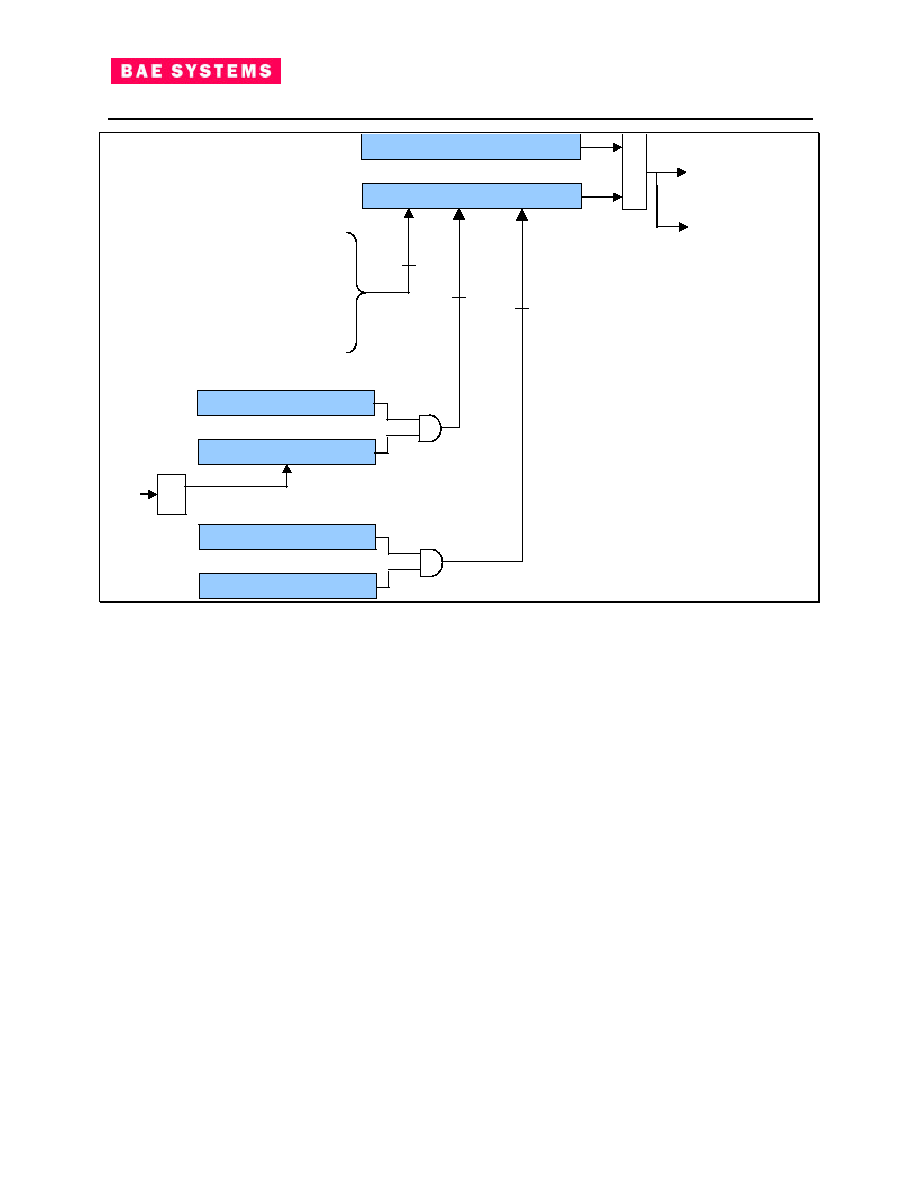

2.1 RAD750 3U CompactPCI Board Functions

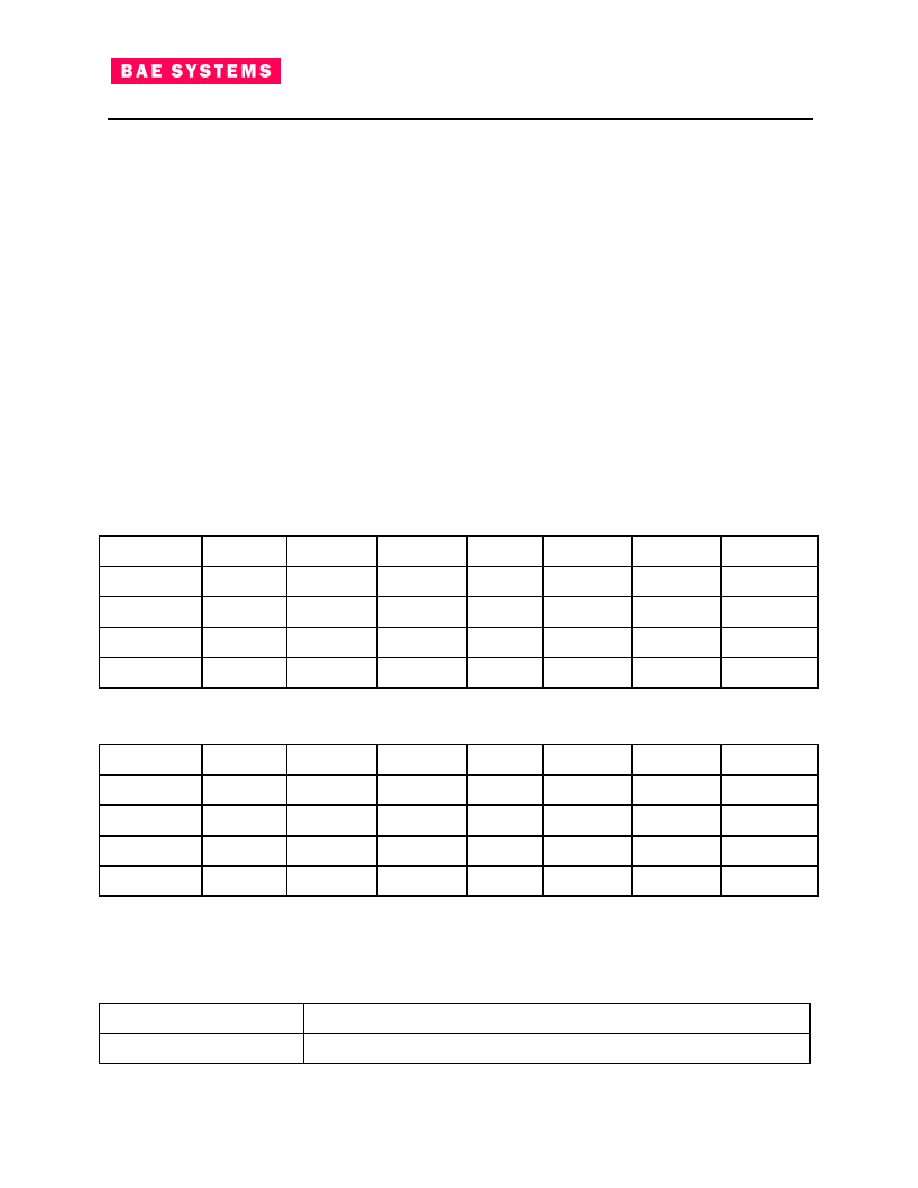

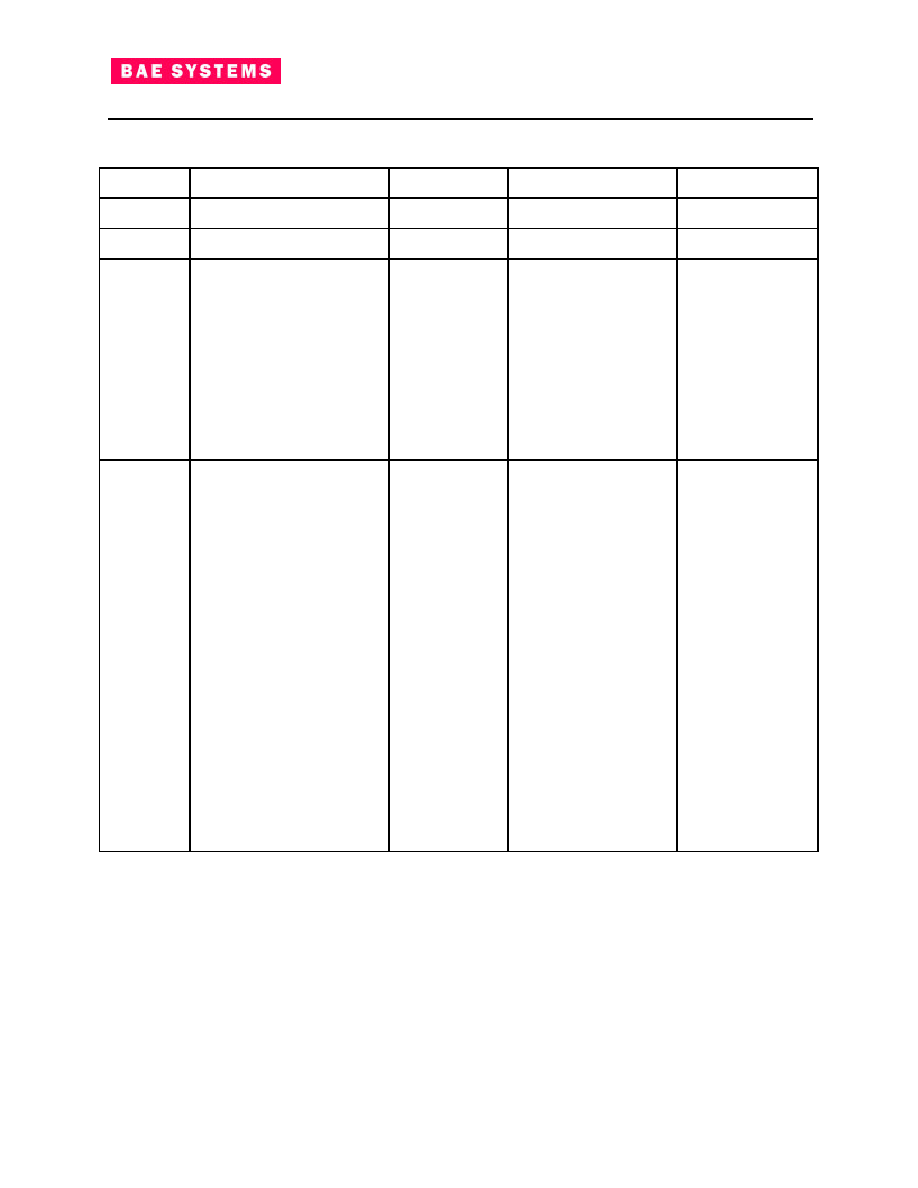

As shown in Figure 2, the RAD750 board consists of the following major functions:

∑

RAD750 PowerPC processor and its 3.3V/2.5V regulator,

∑

Power PCI Bridge function and its oscillator,

∑

SUROM, and

∑

Local Memory.

The following section is divided into subsections corresponding to the top-level capabilities of each of

these major functions.

6

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

RAD750 CPU

Power PCI Bridge

Local Memory

SUROM

OSC

Memory Control

Memory Data

6xx

Data

6xx

Address

& Control

Clocks,

Interrupts

and

Controls

Memory Address

PCI Bus

UART Port

Slave

JTAG Port

RAD750

JTAG Port

Master

JTAG Port

Reset,Interrupts

& Discretes

Clock

2.5V

Regulator

3.3V

2.5V

Configuration

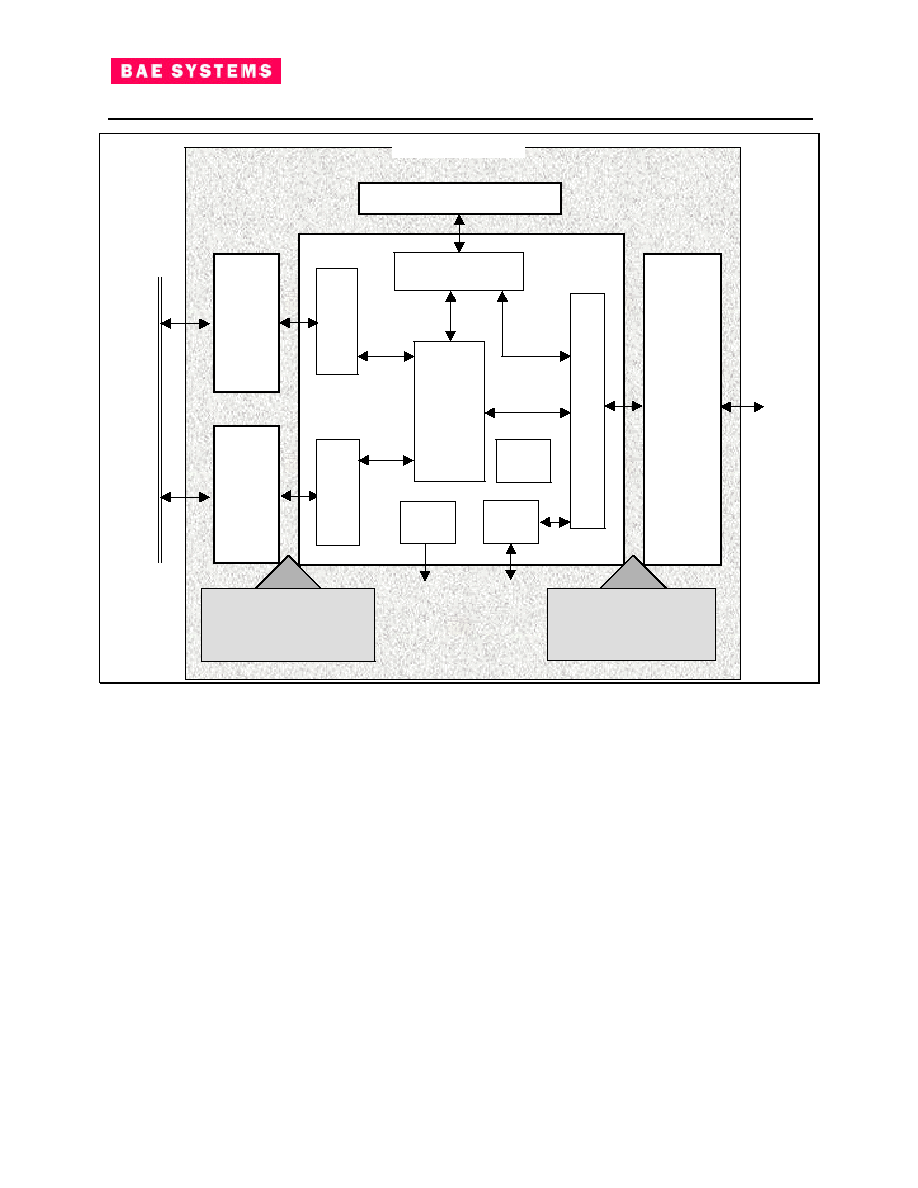

Figure 2: RAD750 Board Block Diagram

2.1.1 RAD750 PowerPC Processor

The RAD750 is functionally and pin-for-pin compatible with a commercial PowerPC 750. The RAD750

PowerPC processor provides the RAD750 board with the following functions:

∑

PowerPC 750 Instruction Set Architecture (ISA),

∑

Floating Point Unit which implements the IEEE-754 floating point standard

∑

32 Kbytes of instruction cache,

∑

32 Kbytes of data cache, and

∑

An L2 cache interface (No L2 cache is implemented on the RAD750 board).

A more detailed description can be found in Section 4.1.1.

2.1.2 Power PCI Bridge Function

The primary function of the Power PCI Bridge is to provide a bridge between the native RAD750 6xx bus

and a Version 2.1 compatible PCI bus. The Power PCI Bridge provides the RAD750 board a:

∑

Version 2.1 compatible PCI bus interface,

∑

PCI burst mode with contiguous data transfers,

∑

PCI arbitration and resource control,

∑

Memory data and address interface,

∑

Memory error detection and correction (EDAC),

∑

Auto memory scrub,

∑

Cache snooping on system memory accesses,

∑

16550 compatible UART interface,

∑

RAD750, PCI and JTAG clock control,

∑

Three programmable timers which may be used to provide operating system tick and cycle start

interrupts,

7

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

∑

A watchdog timer,

∑

Interrupts and discretes,

∑

Embedded micro-controller that may control complex DMA operations,

∑

Power saving modes to match the RAD750,

∑

Dual JTAG master interfaces, and a

∑

JTAG tap controller.

The Power PCI provides enhanced features over the most used COTS PowerPC bridge chip (Motorola

MPC-106), and thus it is not pin compatible with any COTS bridge chip. More details on the Power PCI

chip can be found in Section 4.2. In addition, the many registers of the Power PCI chip are discussed in

more detail in the Appendix to this User's Manual.

2.1.3 SUROM

The SUROM consists of 256 Kbytes of nonvolatile EEPROM memory and provides nonvolatile program

store for the initial program load of the RAD750. The SUROM is organized as 128K x 24 with 16 bits of

data and 8 bits of error correction code. All SUROM memory can be directly addressed by the RAD750

and by any internal master function of the Power PCI. This includes the internal EMC, an external JTAG

master connected through the backpanel or Power PCI JTAG port to the RAD750 board, or any PCI

initiator device connected to the RAD750 board. The error correction code provides single bit error

correction and double bit error detection. Section 2.4 provides a brief description of the contents of

SUROM. A more detailed description can be found in the software Users Manual (see Section 8 for

directions on obtaining the manual).

2.1.4 Local Memory

The Local Memory consists of 128 Mbytes of Synchronous DRAM (SDRAM) and provides processor

program and data store. All local memory is directly addressable by the RAD750 and by any internal

master function of the Power PCI. The local memory is organized as 16M x 80 with 64 bits of data and

16 bits of error correction code. The error correction coding provides single nibble error correction and

double nibble error detection so that cluster SEU events within the SDRAM components will be

correctable. The Local Memory, when placed in a self-refresh mode by software, retains its contents

during a reset of any duration so long as the RAD750 3U CompactPCI board power input is not

interrupted, however, scrubbing of the memory is disabled during self-refresh so SEU errors will be

accumulating.

2.1.5 Clocking

The RAD750 board uses a single 33 MHz Oscillator to drive the PCI Clock, Processor Clock and Real

Time Clock inputs on the Power PCI chip. Section 4.2.4.7 provides more details on the clock generation

logic, which is contained in the Power PCI chip. Details of the configuration and status registers used to

control the clock function can be found in the Appendix to this User's Manual. The RAD750 board is

configurable to use the 33 MHz Oscillator to run the RAD750 at the following speeds:

∑

133 MHz using a 4x Tap (Full speed mode)

∑

99 MHz using a 3x Tap

∑

66 MHz using a 2x Tap

∑

33 MHz using no PLL

∑

16.5 MHz using no PLL and a divide by 2 (half speed mode)

∑

8.25 MHz using no PLL and a divide by 4 (quarter speed mode), and

∑

4.125 MHz using no PLL and a divide by 8 (eighth speed mode).

Clock speeds higher than 133 MHz will be available at a future date.

8

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

The RAD750 board is configurable to use the 33 MHz Oscillator to run the PCI Bus at the following

speeds:

∑

33 MHz

∑

16.5 MHz

∑

8.25 MHz

∑

4.125 MHz

The RAD750 board uses the 33 MHz Oscillator to run the real time clock at 33 MHz divided down by 4, 8,

16, or 32.

2.1.6 Power Regulation and Consumption

The RAD750 board draws all required power from an external 3.3V supply. The power source is

expected to be regulated to 3.3V

±

5% and a maximum ripple of 60 mV p-p with a power converter

switching frequency of 1 MHz. An on-card regulator provides the +2.5V required for the RAD750. The

RAD750 board has the power consumption characteristics listed in Table 1 and Table 2. Maximum

power includes worst case temperature, voltage, and post-radiation exposure. Typical power is an

average value measured at V

cc

= 3.3V and +25

∞

C in a system executing typical applications or

benchmarks.

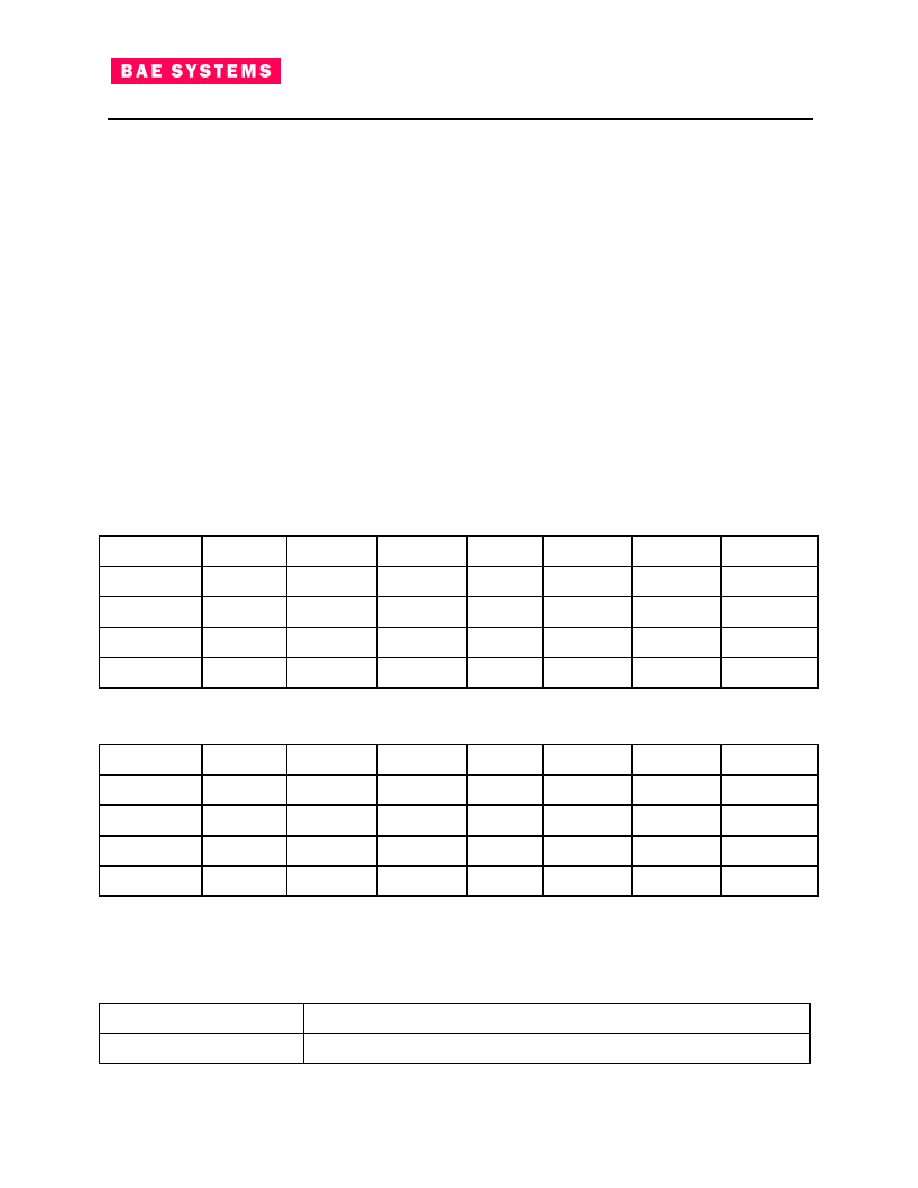

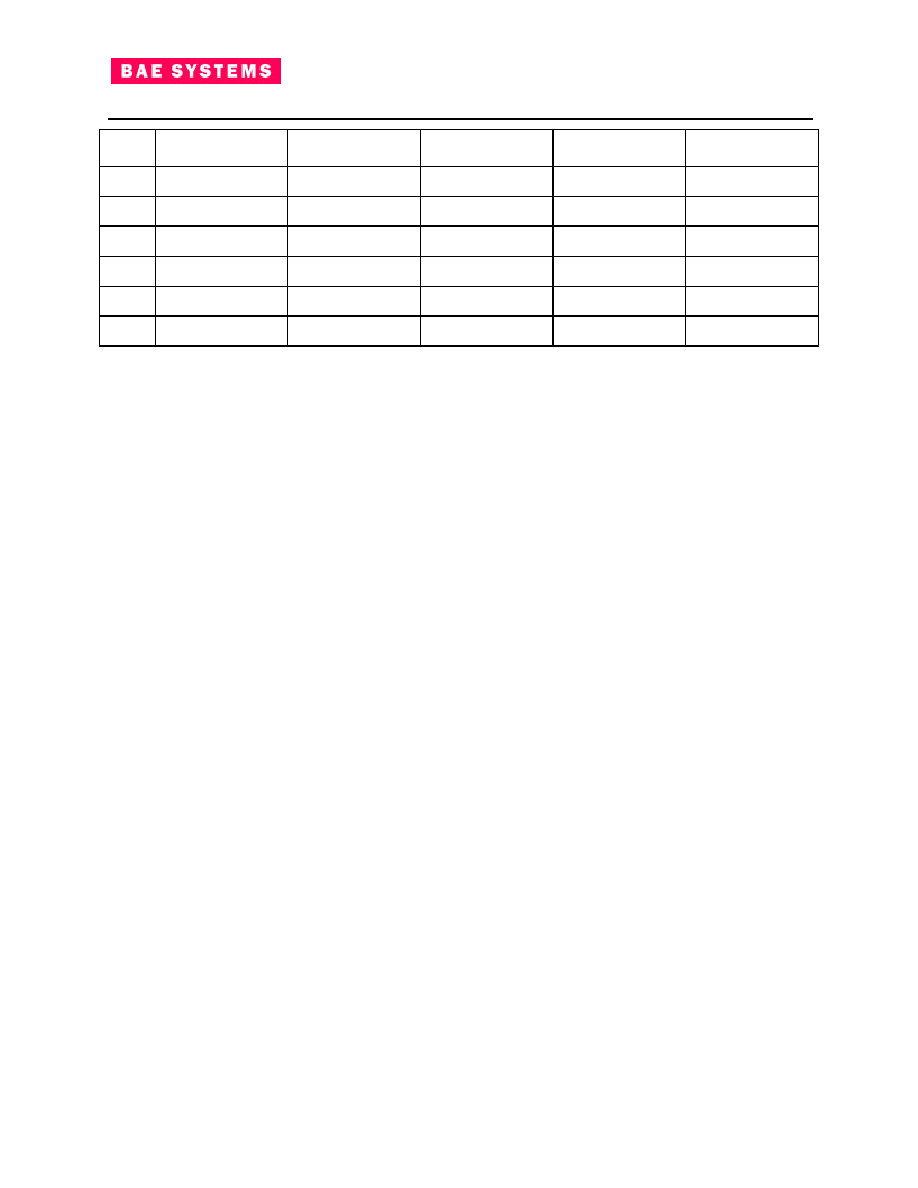

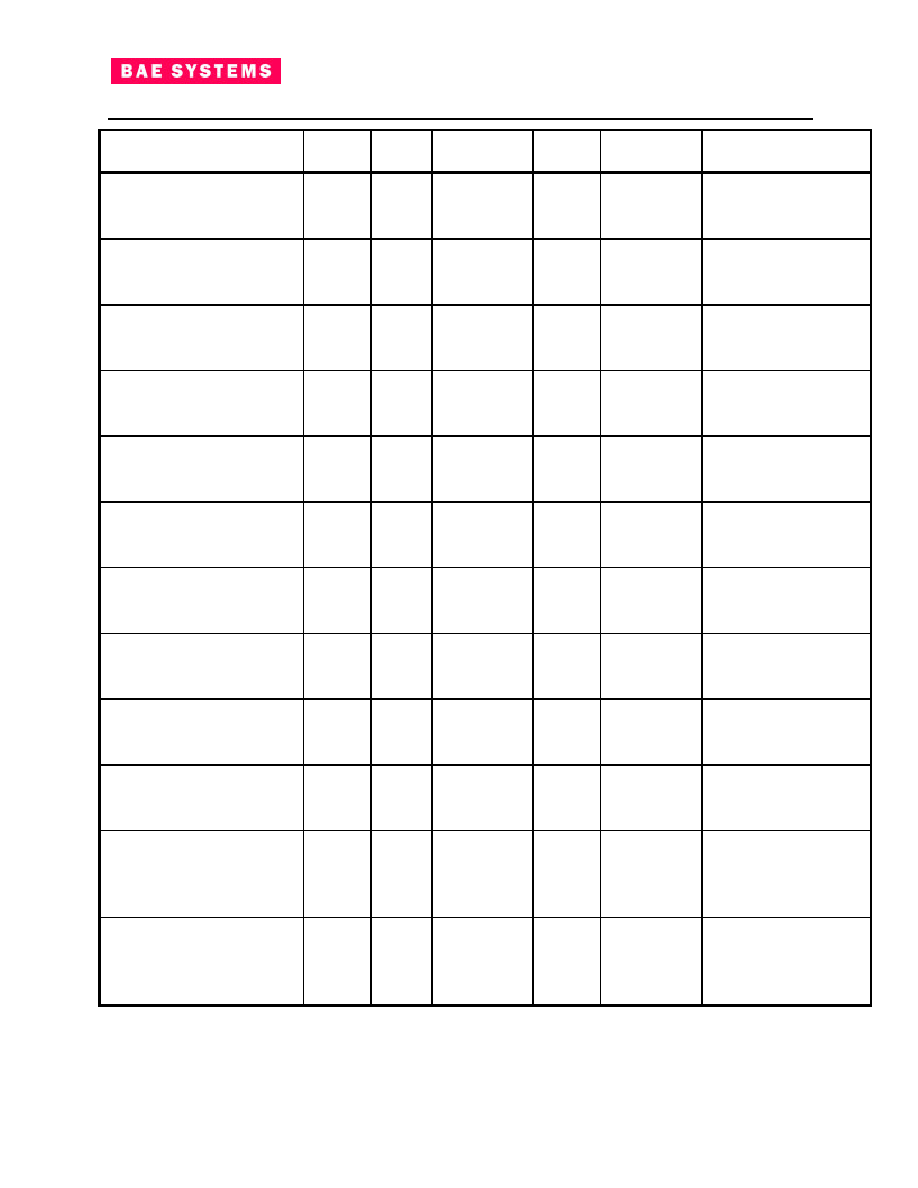

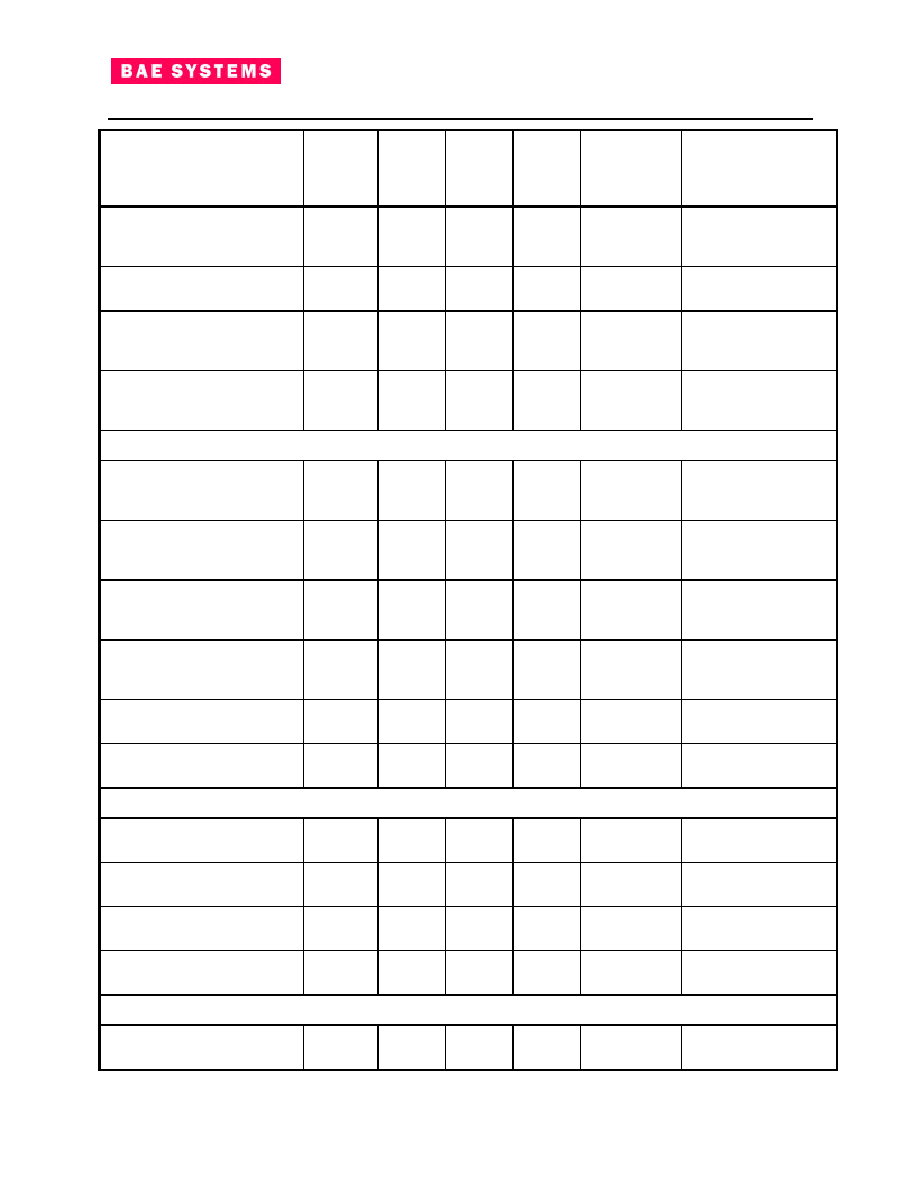

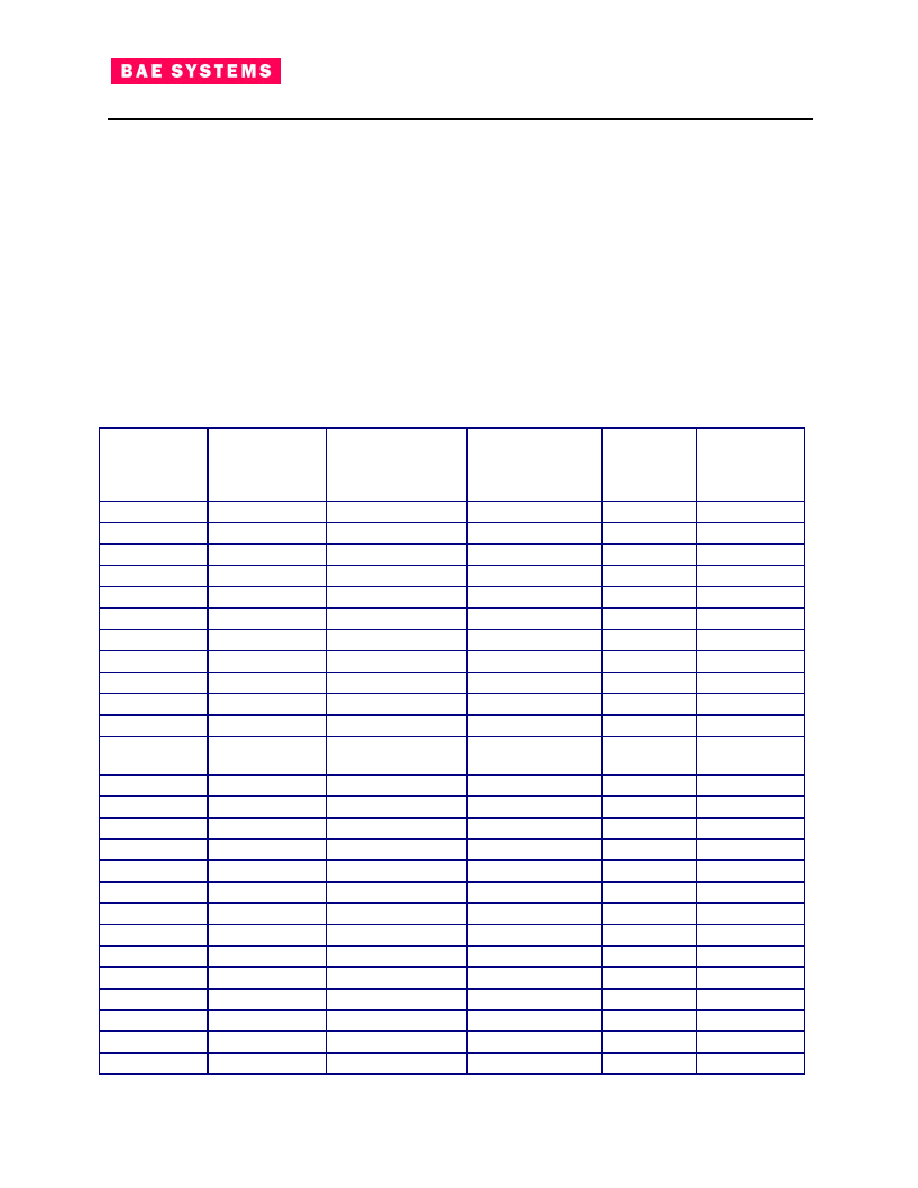

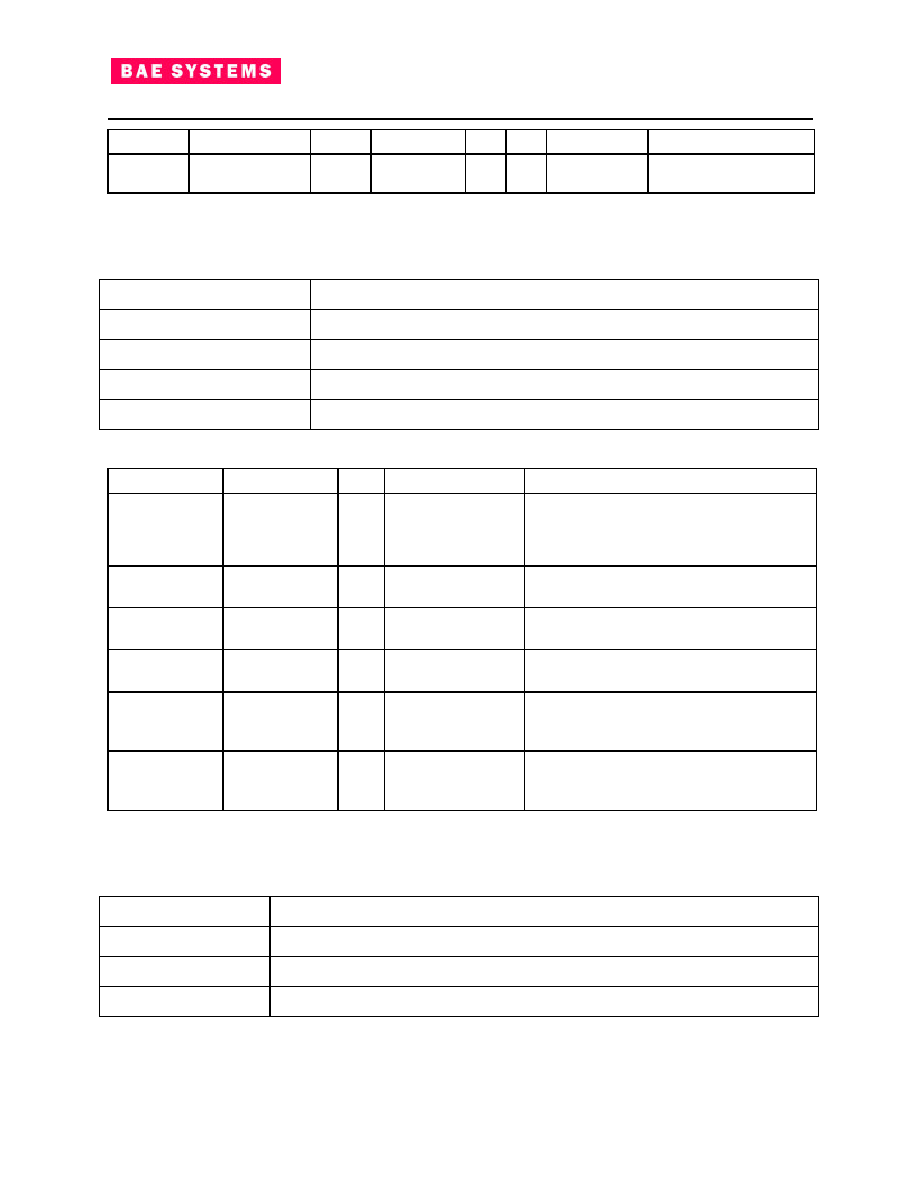

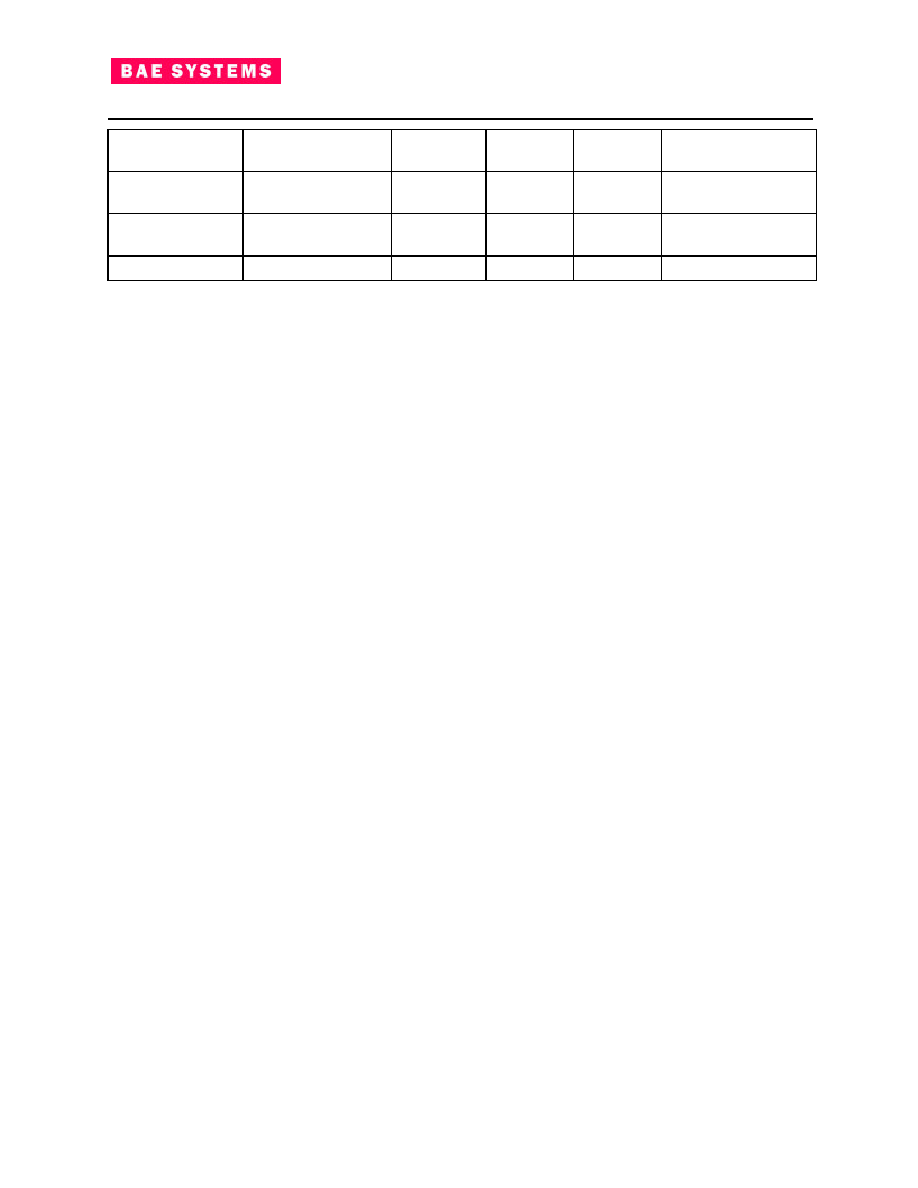

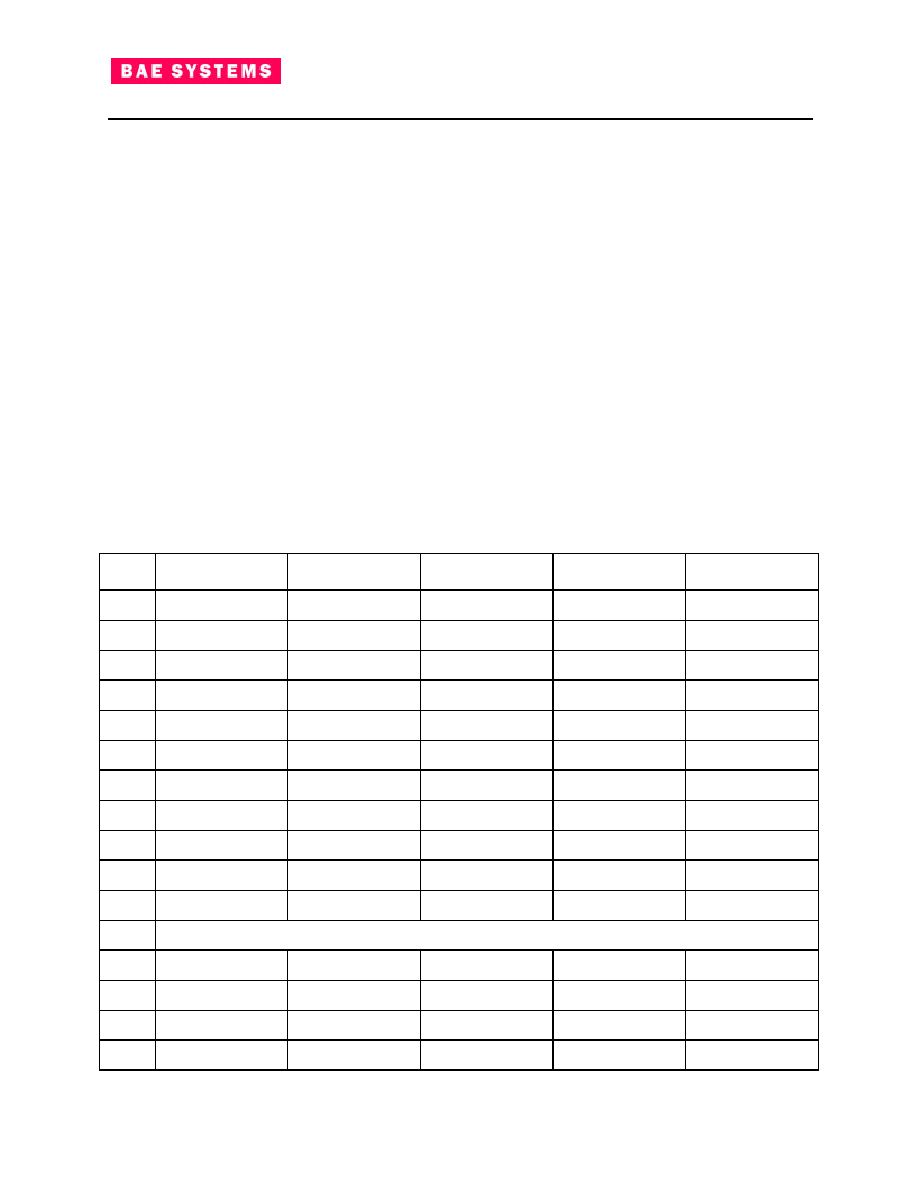

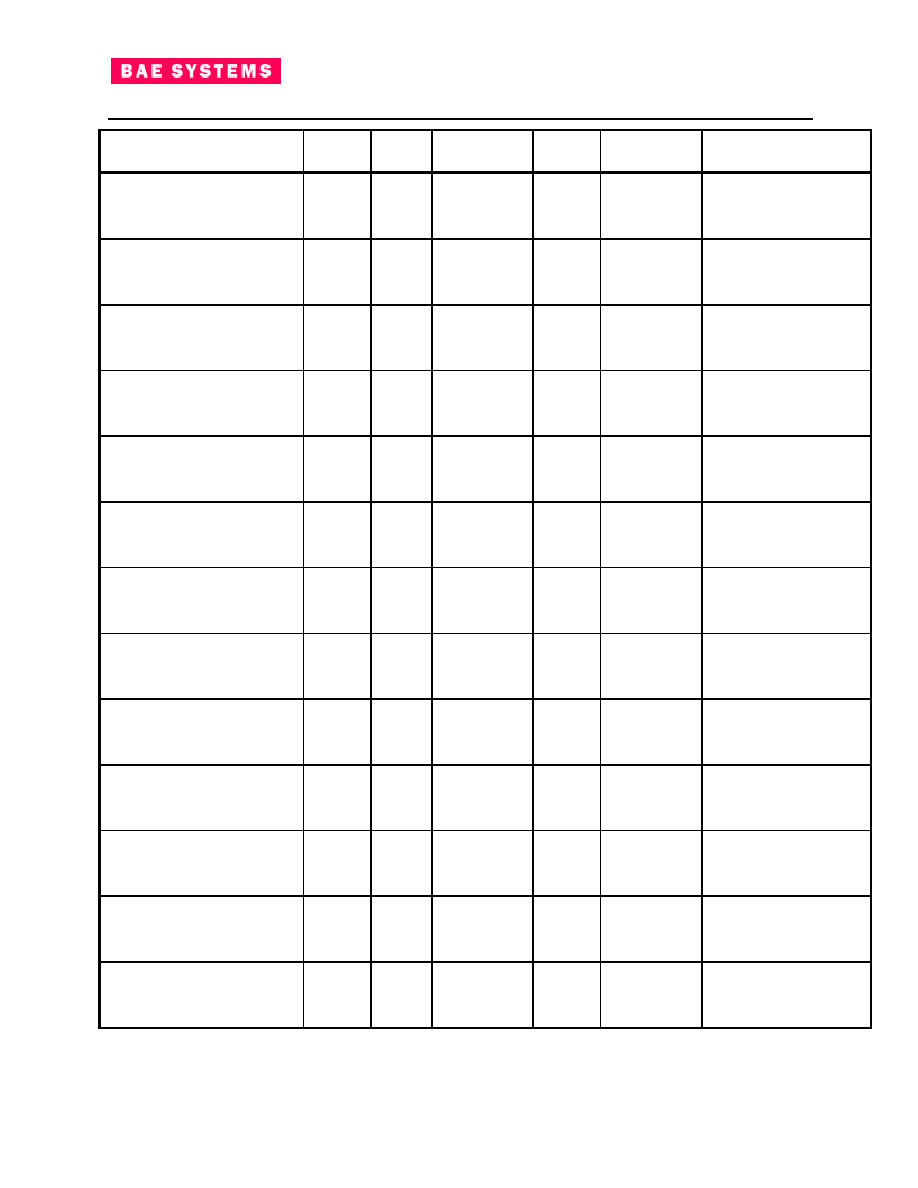

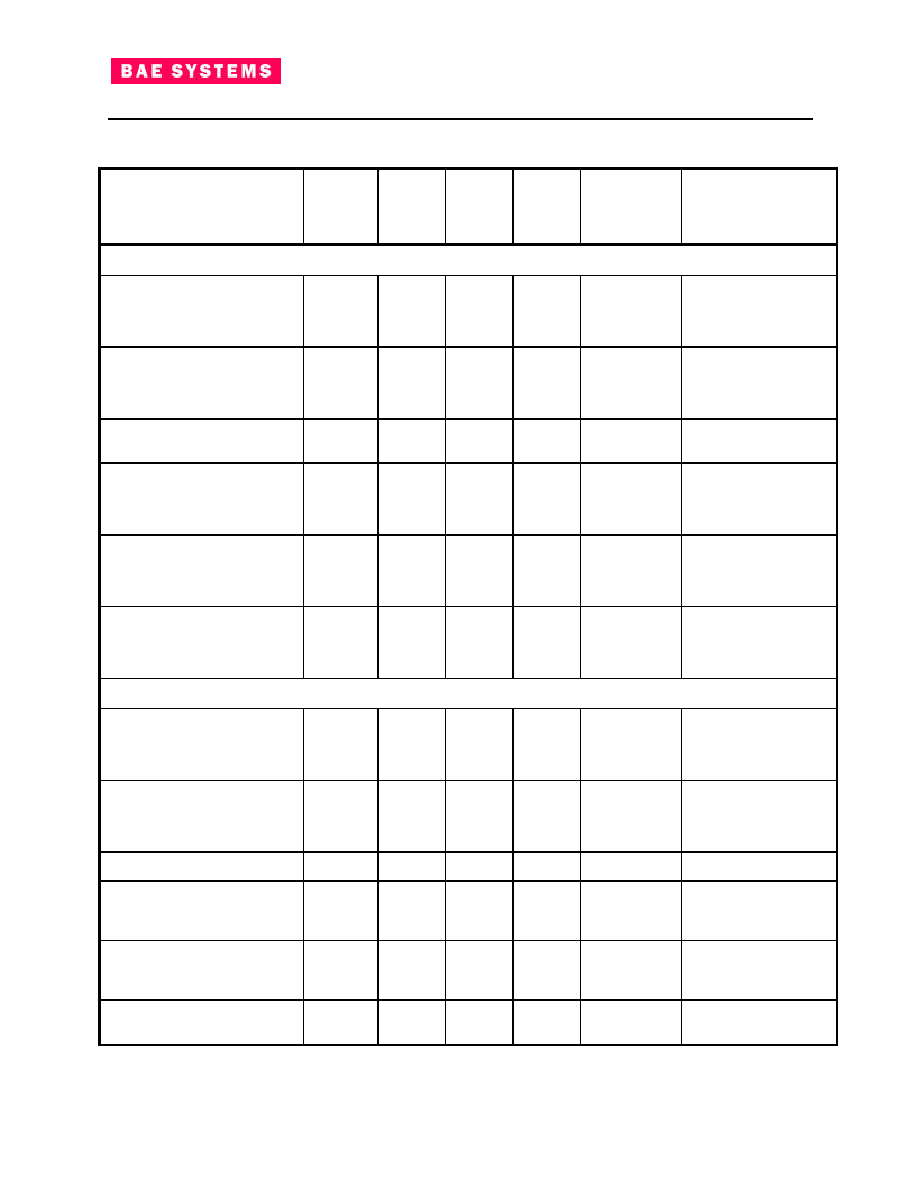

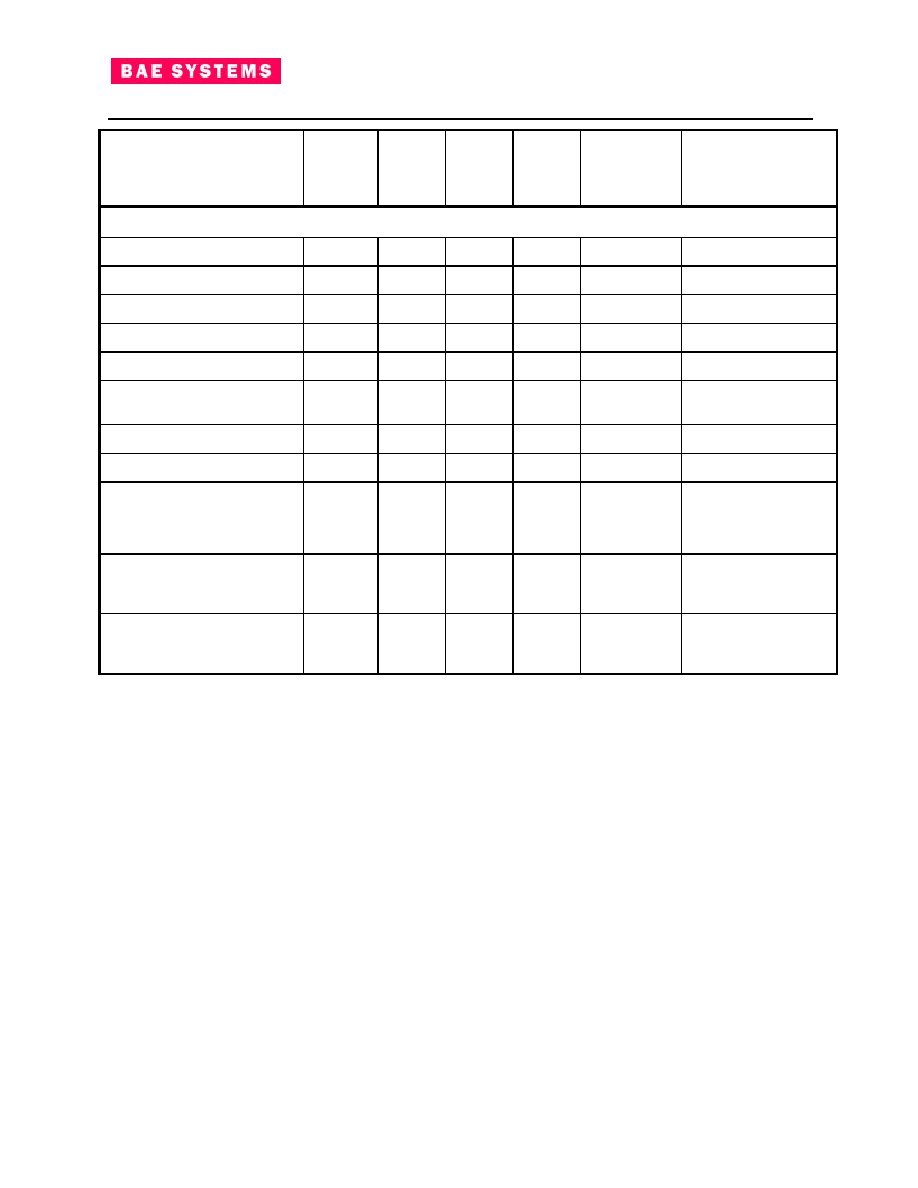

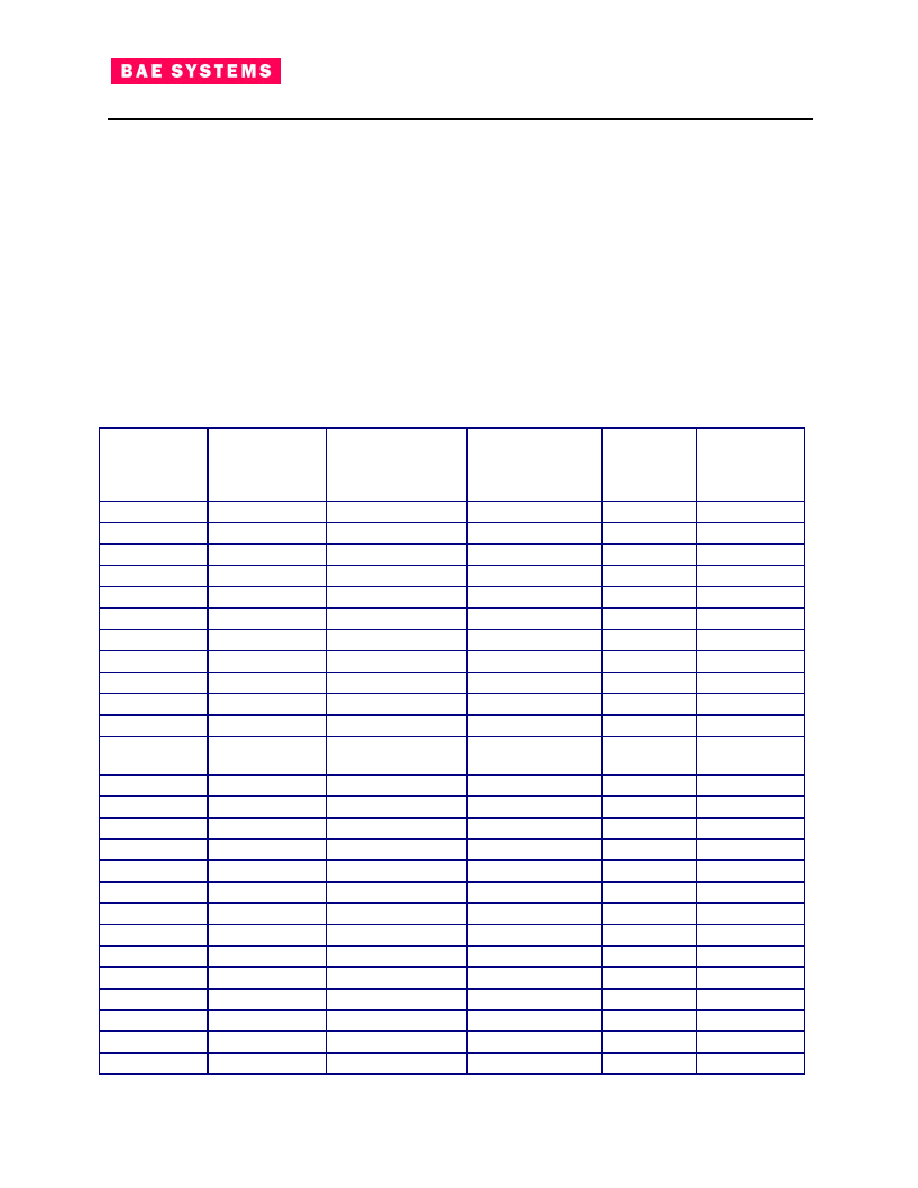

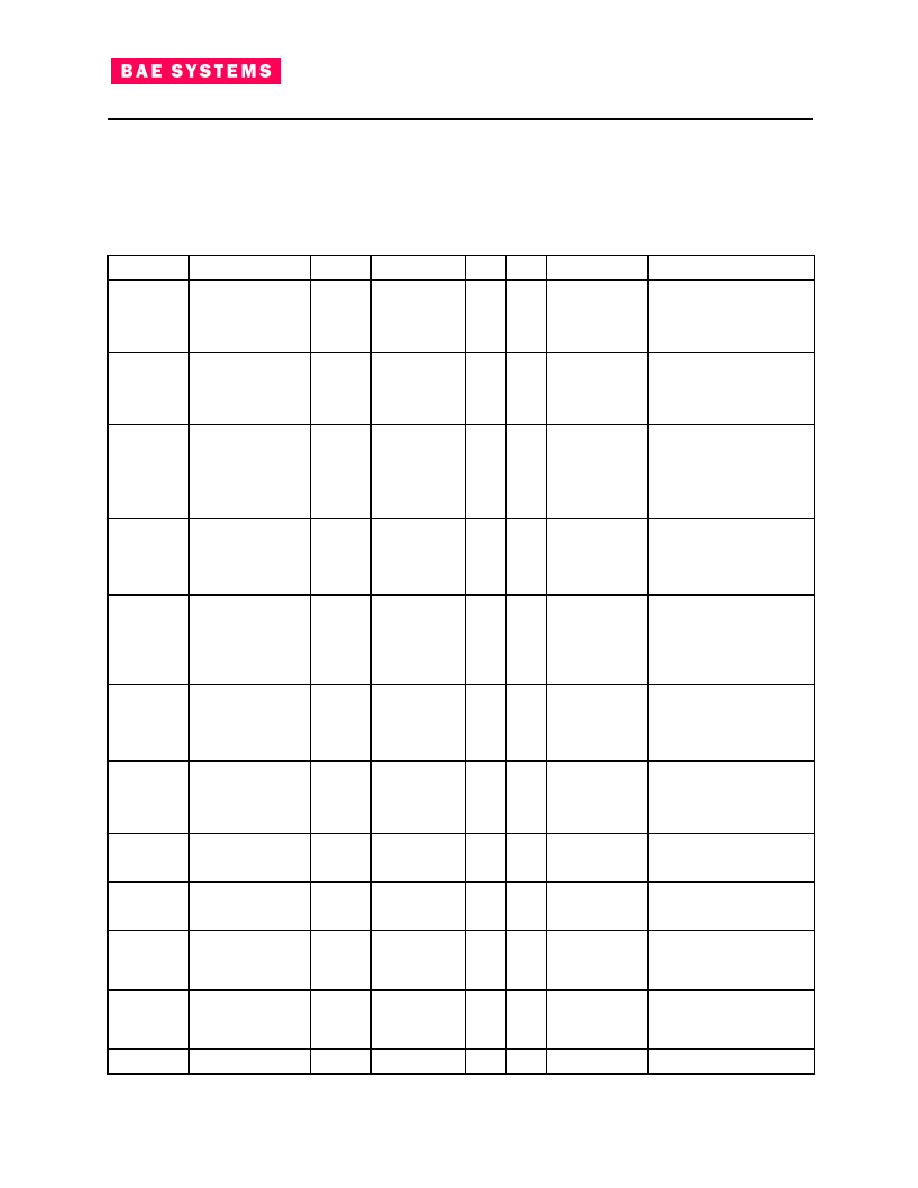

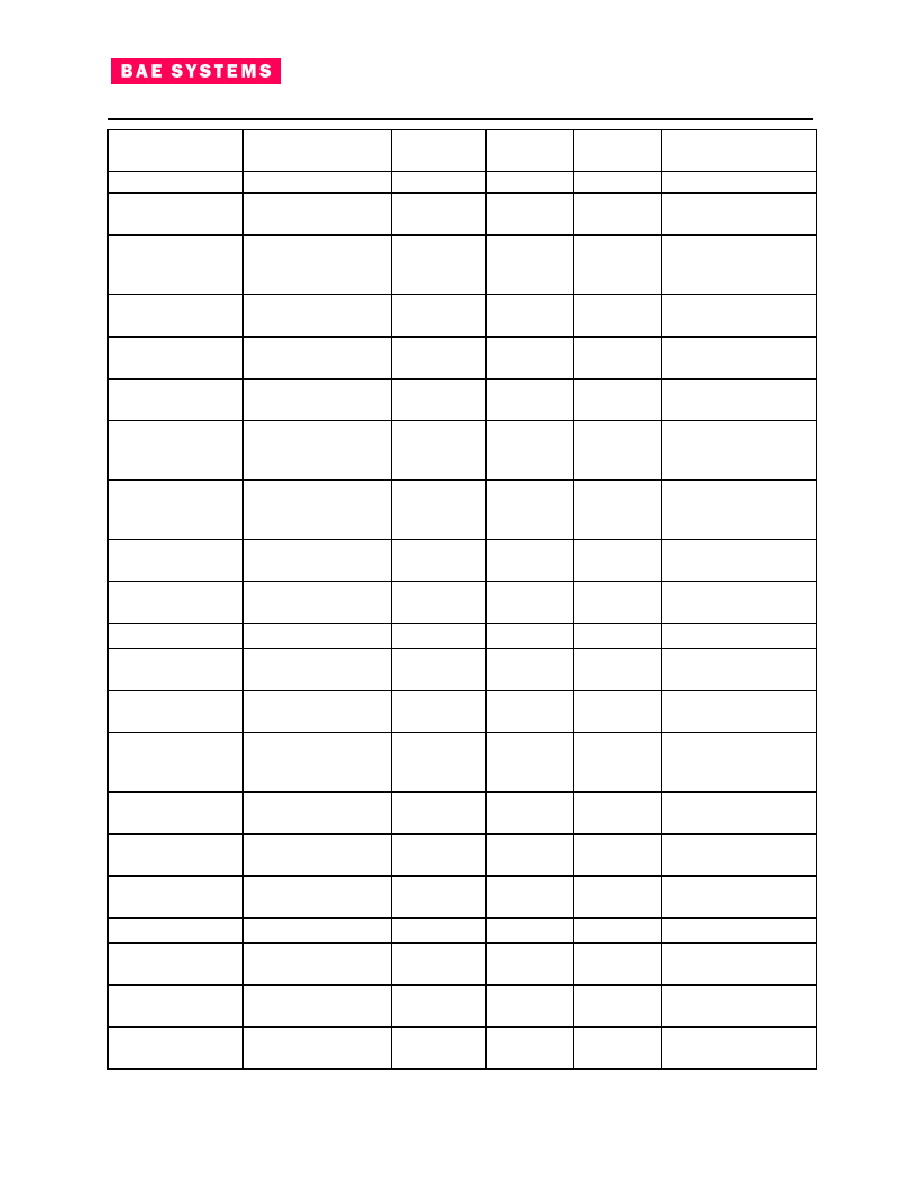

Table 1 - RAD750 3U CompactPCI board Maximum Power Consumption with V

cc

= 3.3

±

5% VDC,

GND = 0 VDC, -55

T

j

< 125

o

C

Mode

132 MHz

99 MHz

66 MHz

33 MHz

16.5 MHz

8.25 MHz

4.125 MHz

Full-On (W)

14.5 W

11.5 W

10.0 W

8.5 W

7.1 W

6.3 W

6.0 W

Doze (W)

5.2 W

4.6 W

4.0 W

3.4 W

3.1 W

2.9 W

2.9 W

Nap (W)

2.7 W

2.7 W

2.7 W

2.7 W

2.7 W

2.7 W

2.7 W

Sleep (W)

2.3 W

2.3 W

2.3 W

2.3 W

2.3 W

2.3 W

2.3 W

Table 2 - RAD750 3U CompactPCI board Typical Power Consumption with V

cc

= 3.3 VDC, GND = 0

VDC, T

MR

= 25

o

C

Mode

132 MHz

99 MHz

66 MHz

33 MHz

16.5 MHz

8.25 MHz

4.125 MHz

Full-On (W)

10.0 W

8.0 W

7.0 W

5.9 W

4.9 W

4.4 W

4.2 W

Doze (W)

4.3 W

3.8 W

3.3 W

2.8 W

2.6 W

2.4 W

2.4 W

Nap (W)

2.2 W

2.2 W

2.2 W

2.2 W

2.2 W

2.2 W

2.2 W

Sleep (W)

1.9 W

1.9 W

1.9W

1.9 W

1.9 W

1.9 W

1.9 W

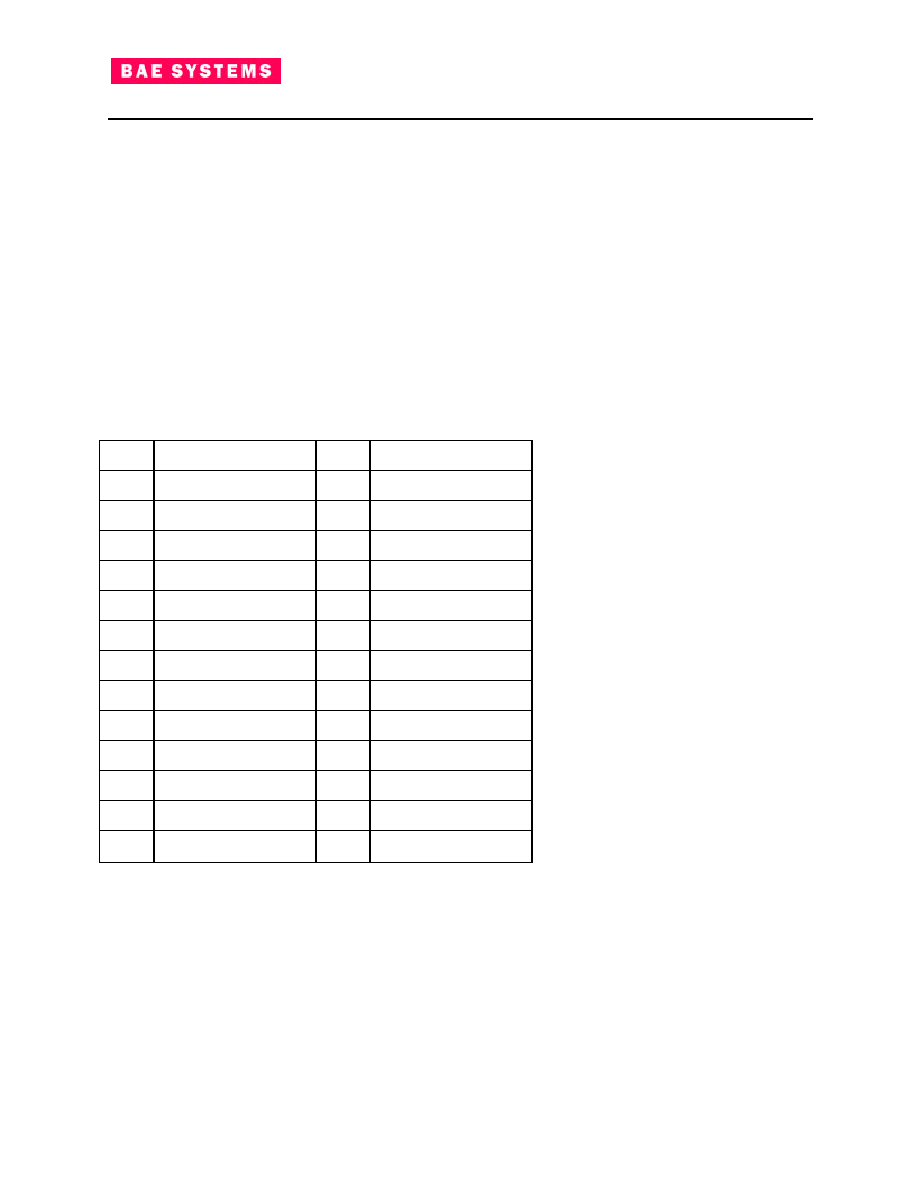

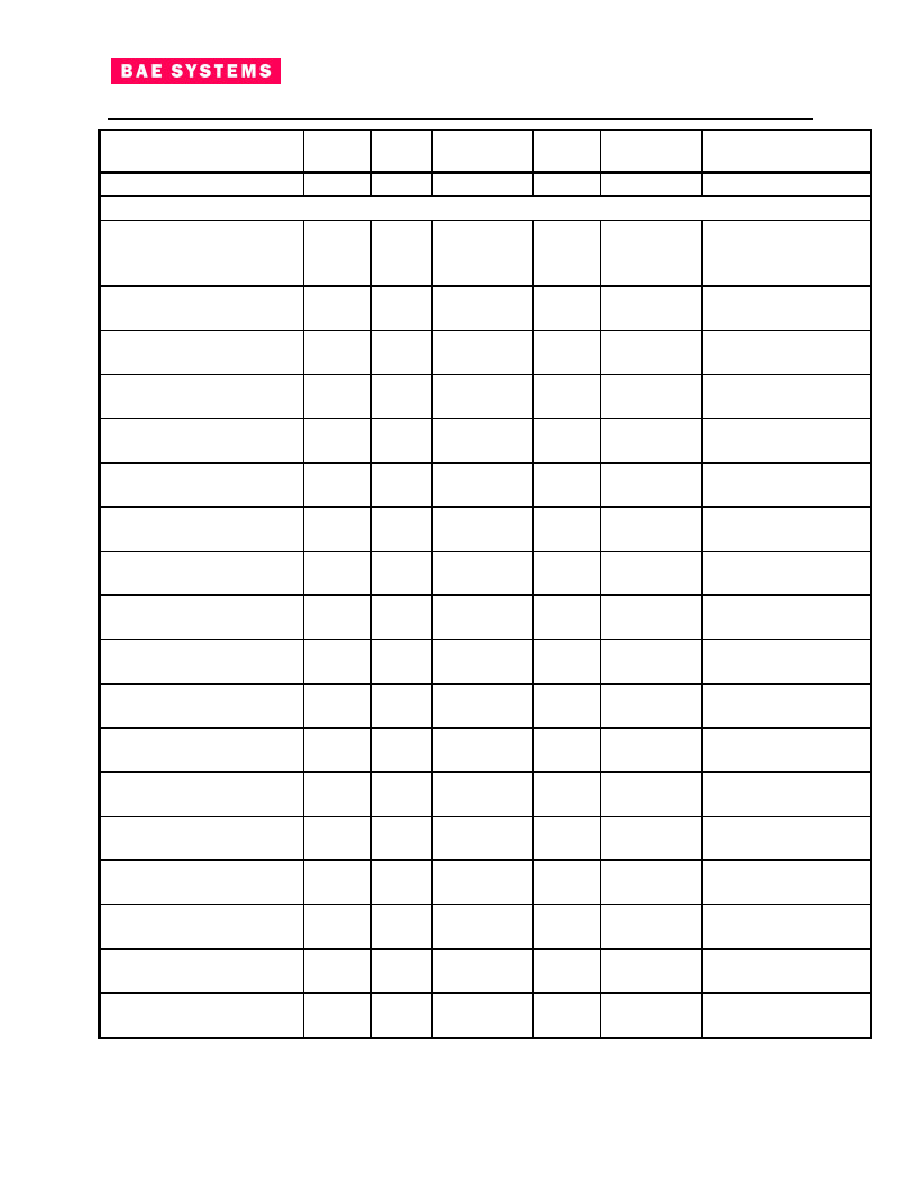

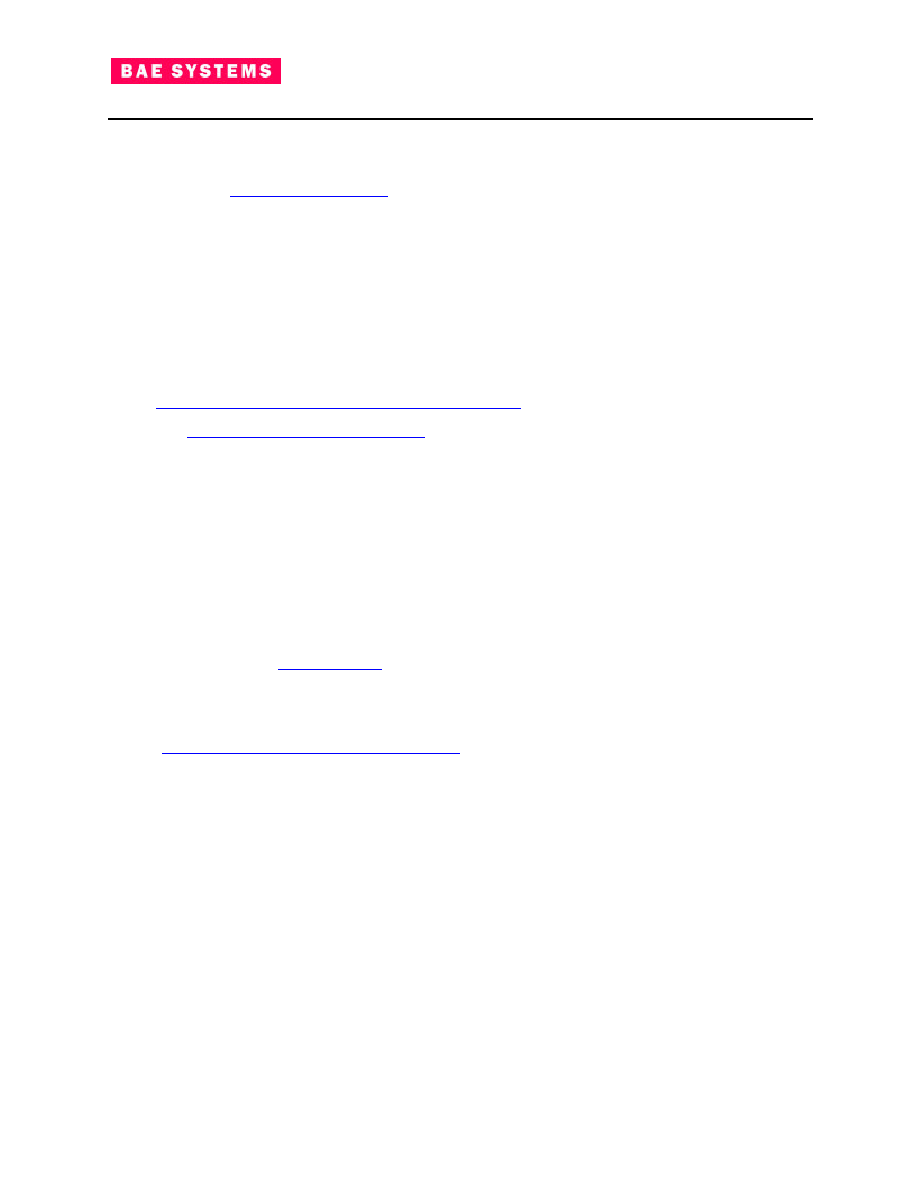

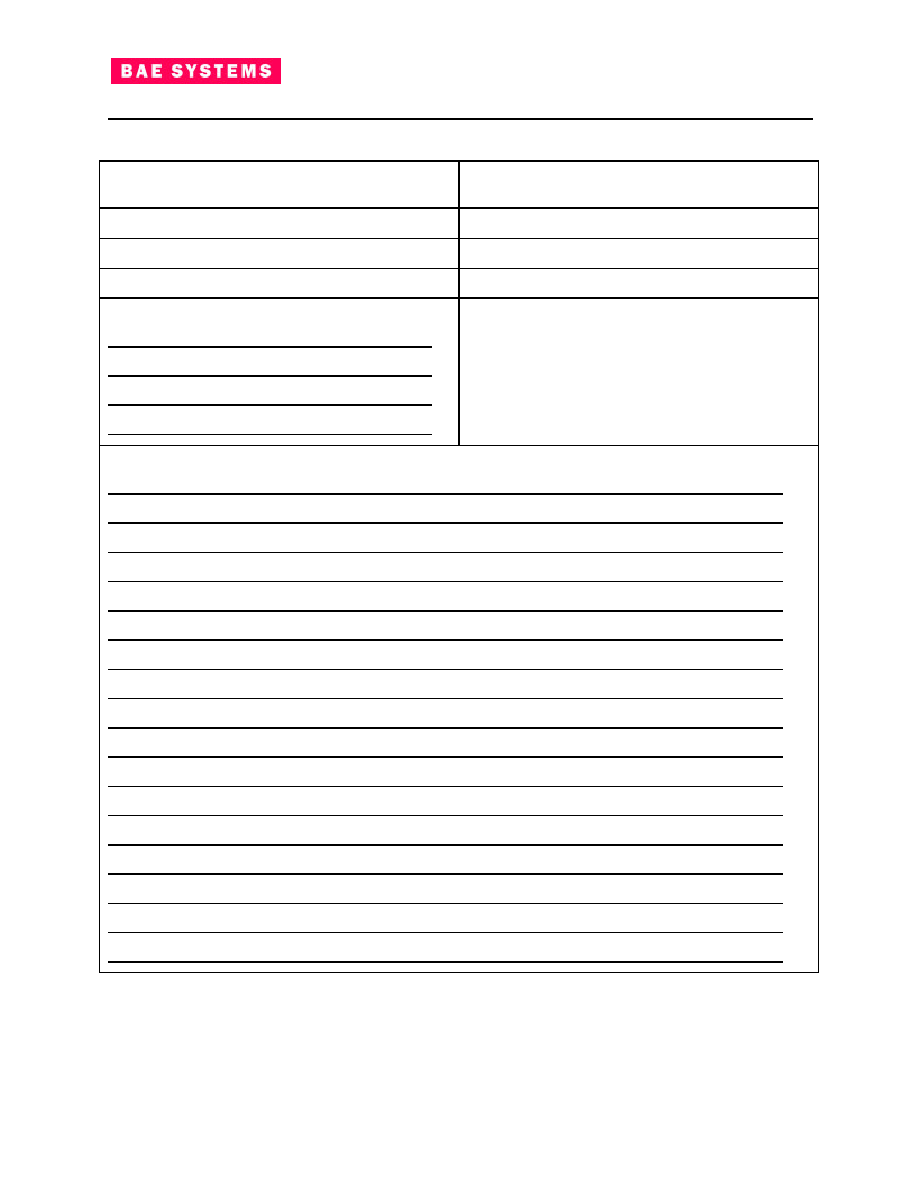

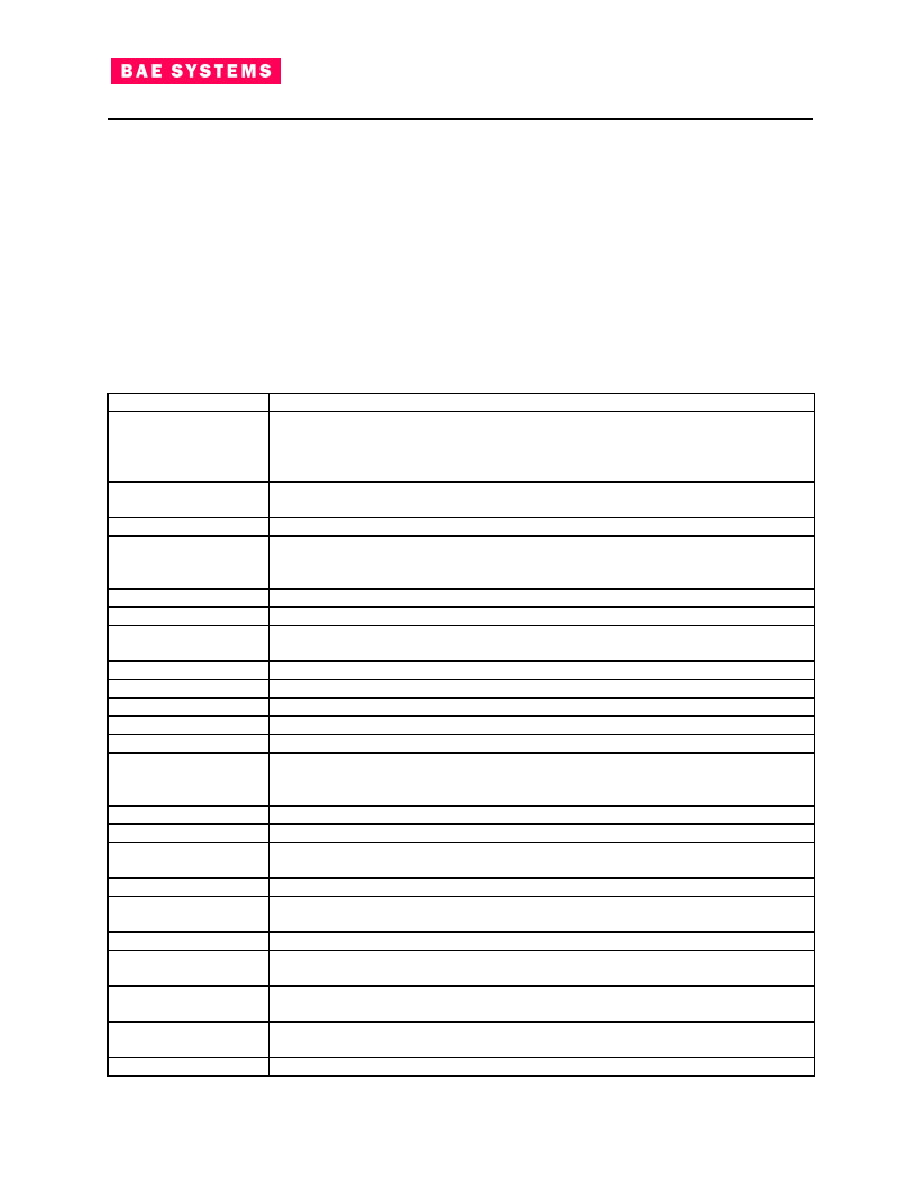

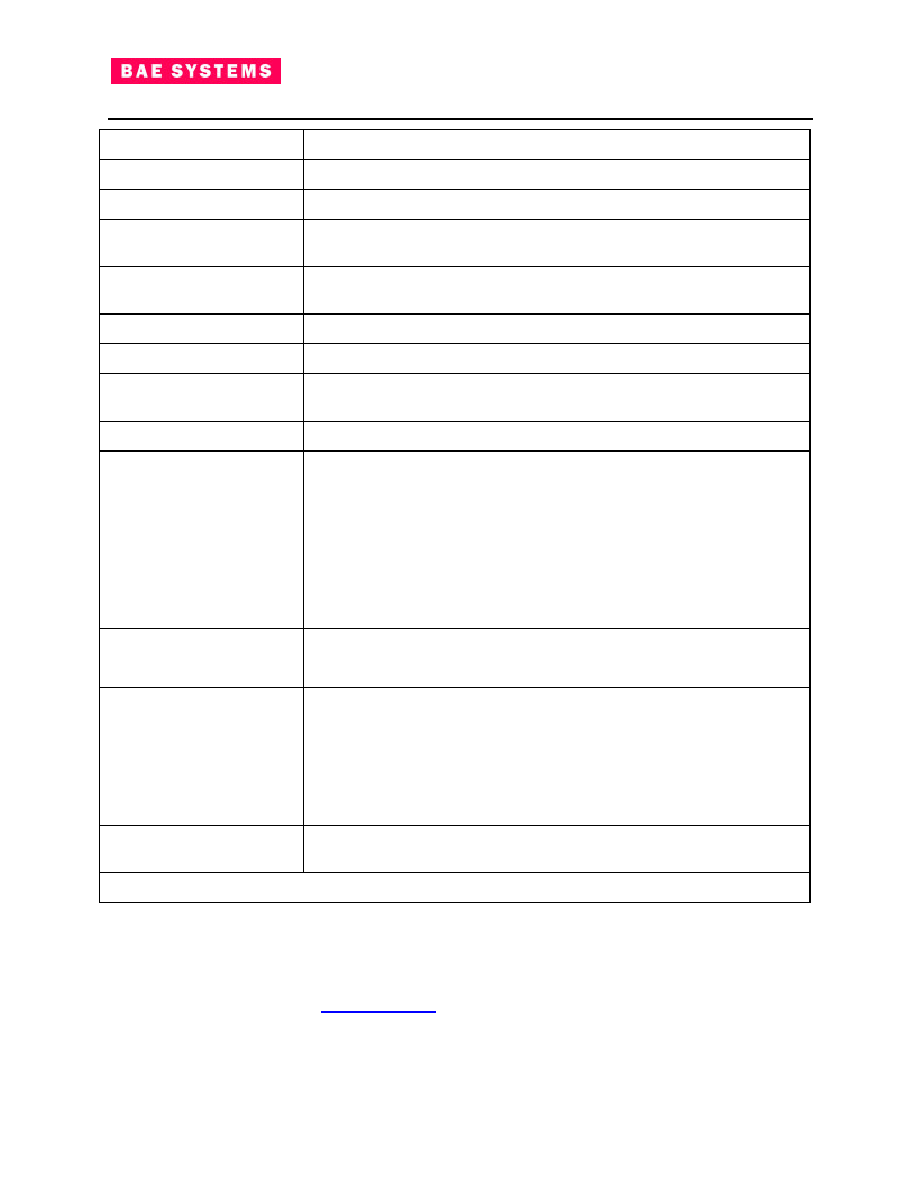

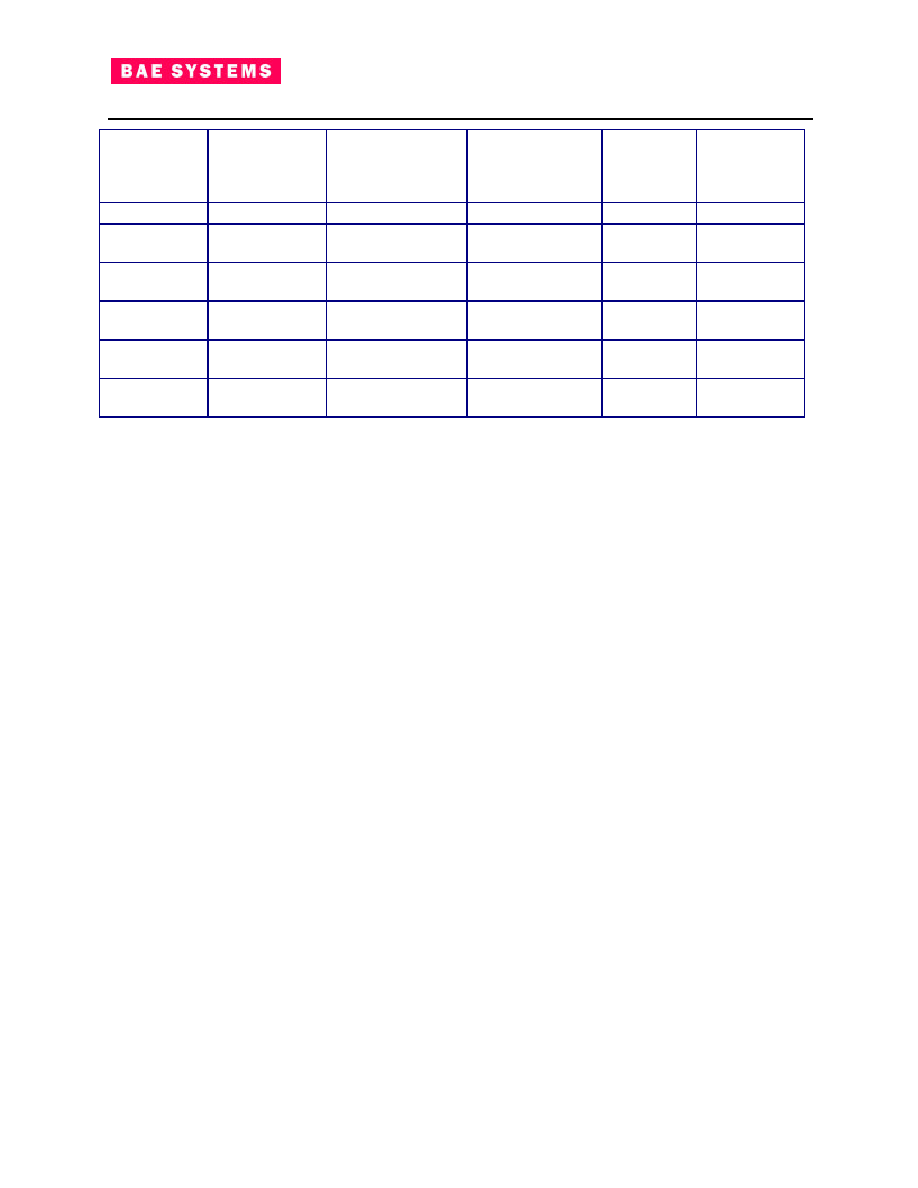

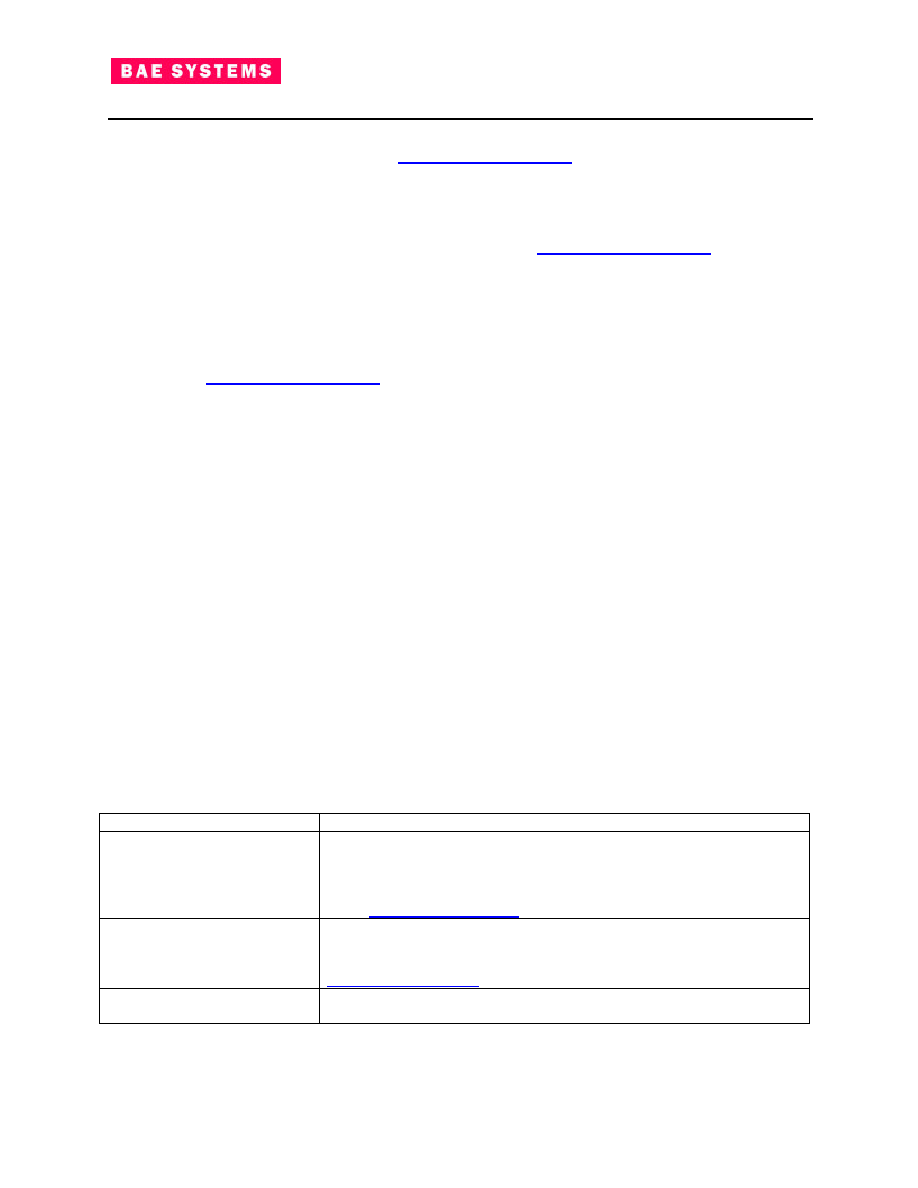

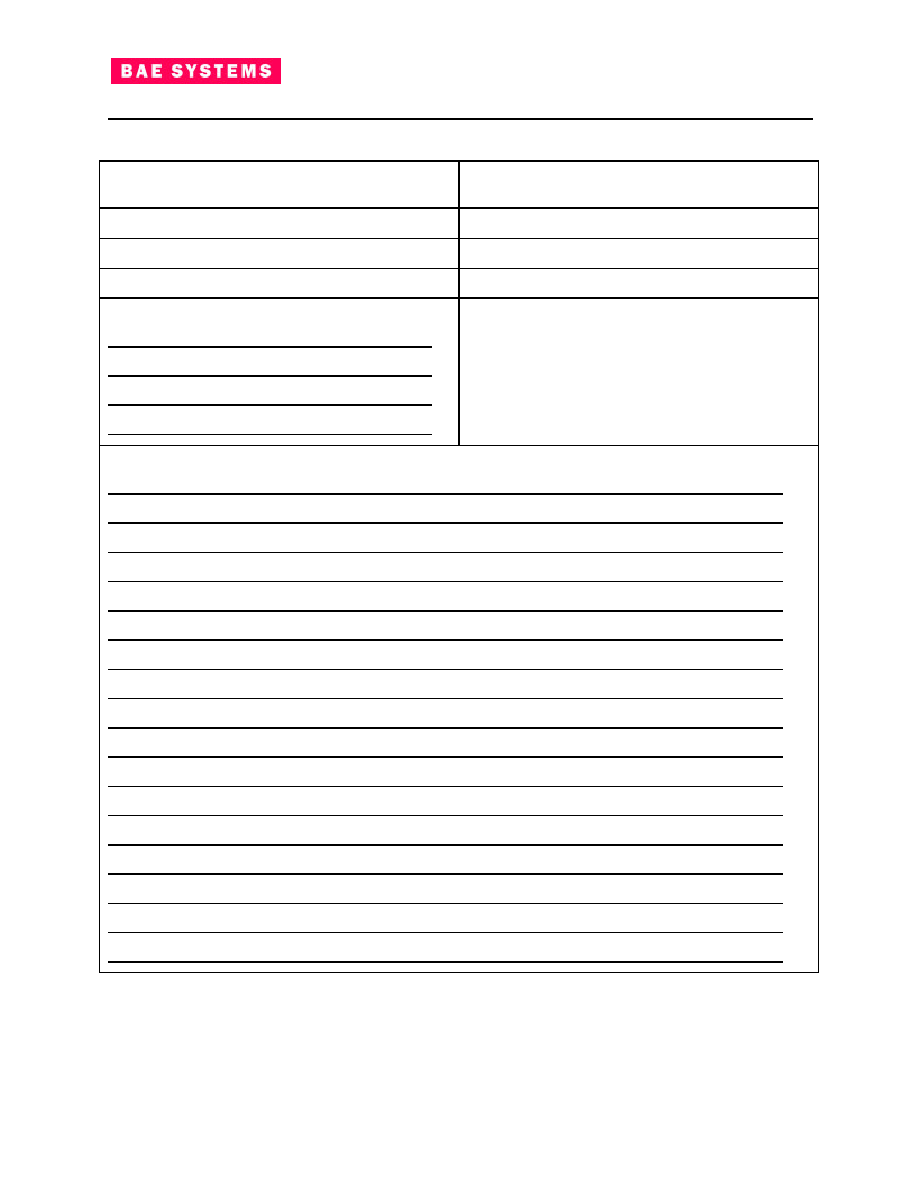

2.2 Specification

Table 3 provides a high level specification of the RAD750 board Flight Unit.

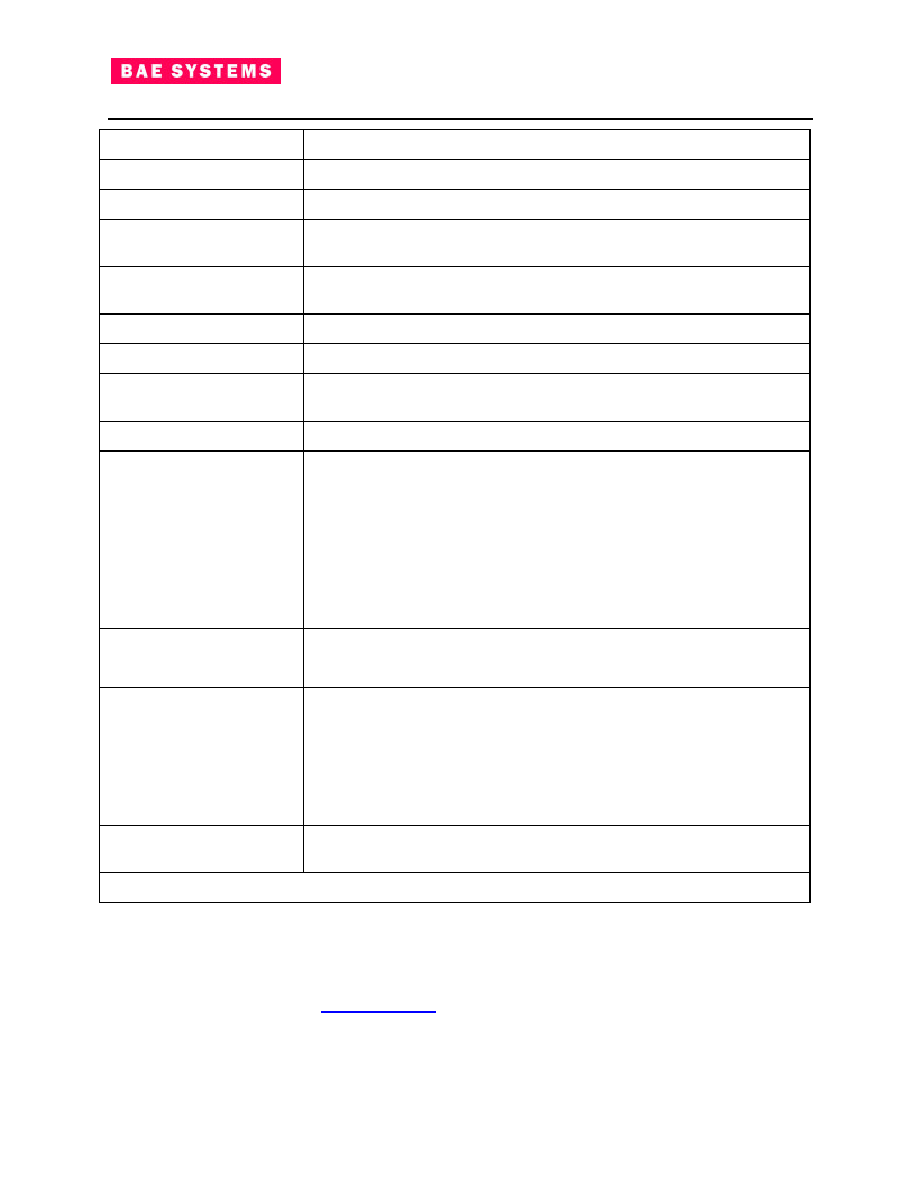

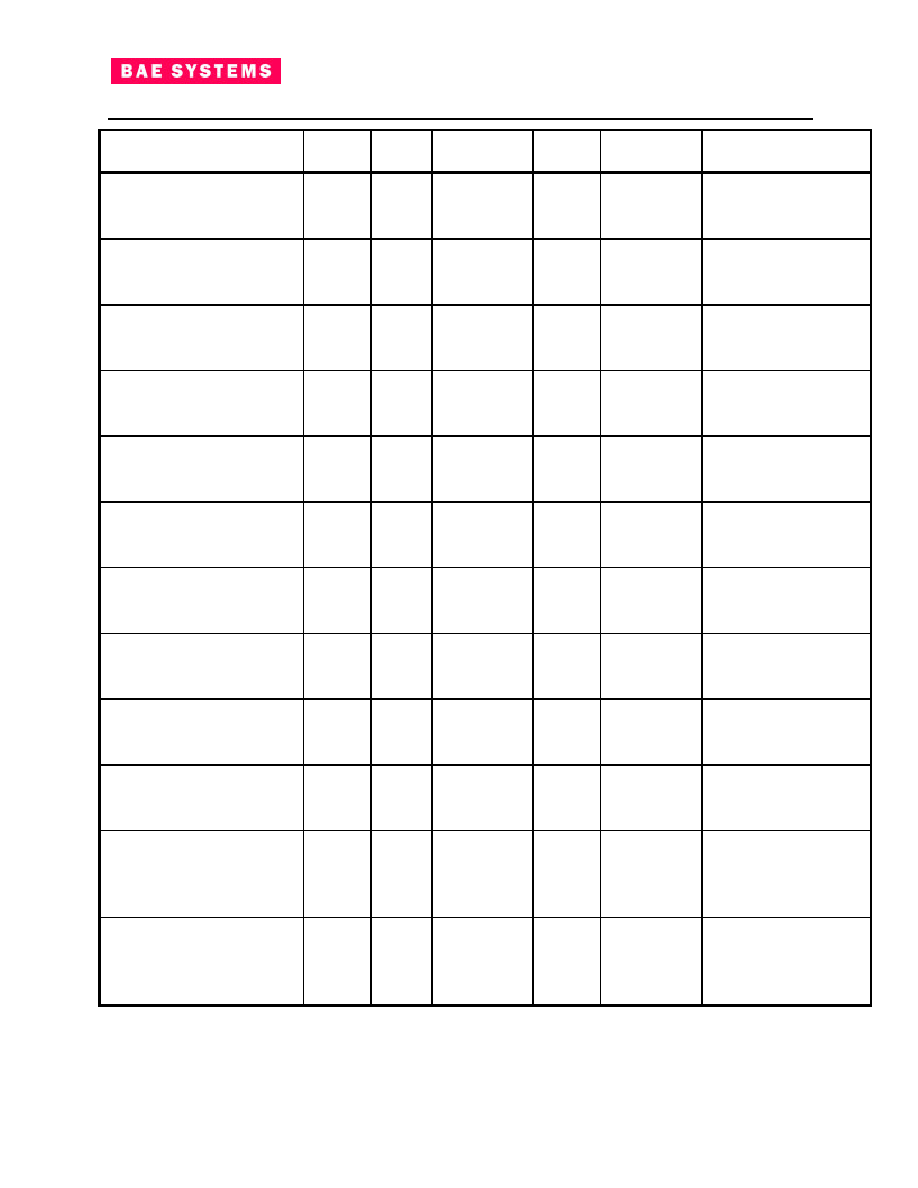

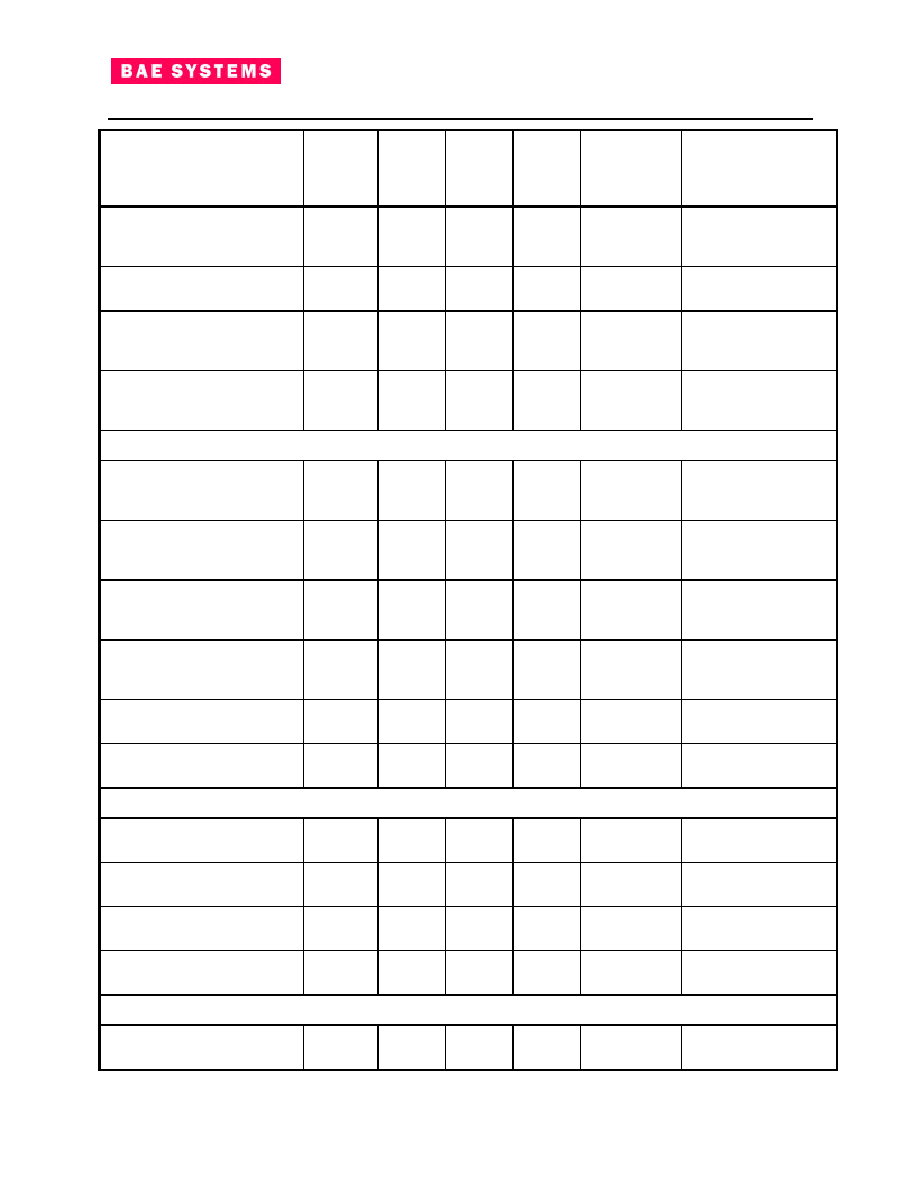

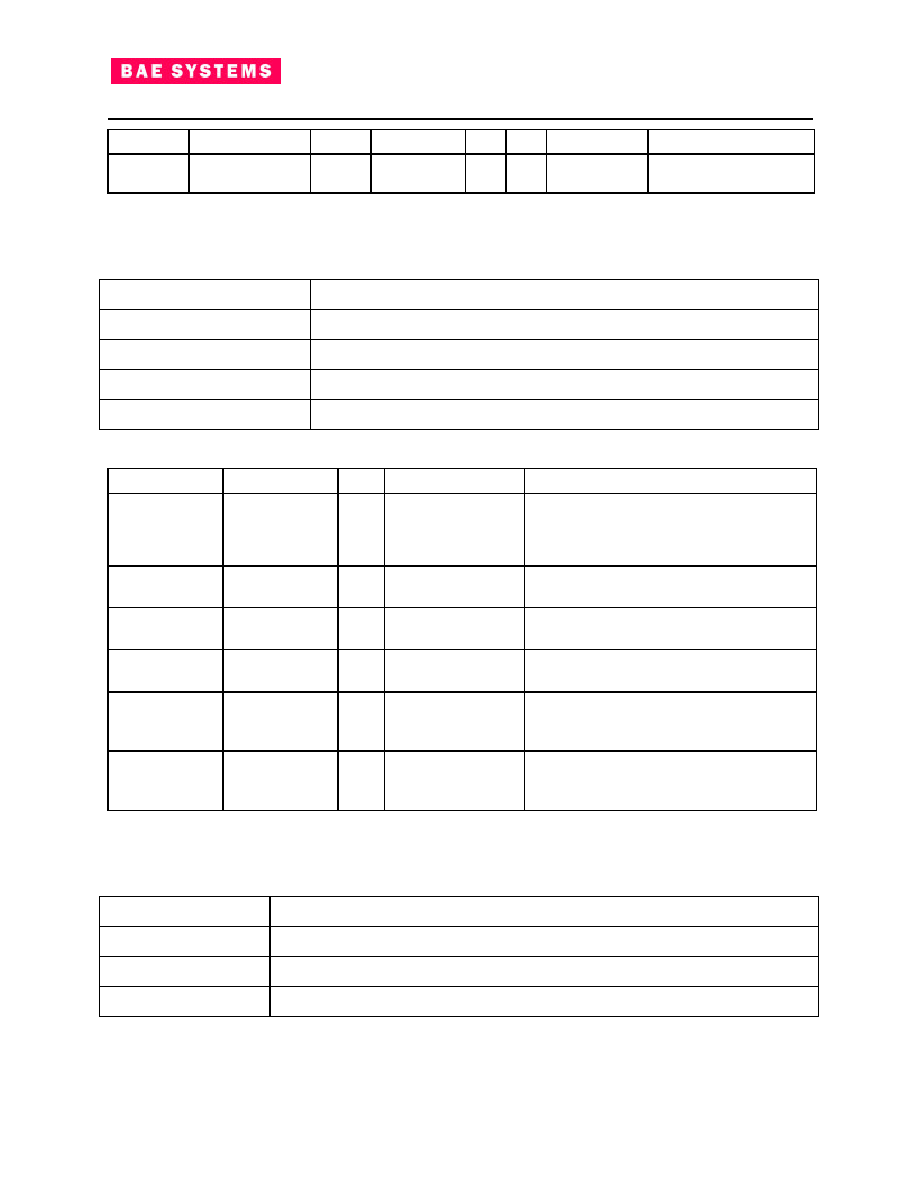

Table 3 - Specification of the RAD750 board (Flight Configuration)

Item

Description

Processor

RAD750

9

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

Item

Description

Shared main memory

128-MByte SDRAM with ECC

Board

Conduction Cooled, double sided, CompactPCI RAD750 3U format

CompactPCI interface

PowerPC-to-PCI bridge, 32 bit, 33 MHz, full system slot function or

peripheral slot.

Serial I/O

JTAG and UART I/O on front panel and CompactPCI J2 connector

(factory option)

Counters/timers

Three 32-bit, programmable, and a Watchdog Timer

SUROM

256 KByte On-board programmable, Hardware write protection

Additional features

26 Programmable discrete and Interrupts on CompactPCI J2 connector,

PCI Ready Parity on CompactPCI J1 connector

Power consumption

see Section 2.1.6 "Power Regulation and Consumption"

Environmental Conditions:

Temperature (operating)

Temperature (storage)

Humidity

Thermal Shock

Vibration

-55 ∞C to +70 ∞C

-55 ∞C to +125 ∞C

5 % to 95 % non-condensing

±

5

∞

C per minute

20 to 2000 Hz @ 12.3grms

Radiation

TBD

SEU

100 KRad Total dose

Performance:

RAD750

PCI Bus

- DMA Read(*)

- DMA Write(*)

240 Dhrystone 2.1 MIPS, 5.75 SPECint95 and 3.25 SPECfp95 @ 133

MHz

90 Mbytes per second

130 Mbytes per second

Standards compliance

PCI Local Bus Specification Rev. 2.1 CompactPCI Specification Rev.

D1.10

(*) ≠ External DMA controller with no snooping HITS during transfer

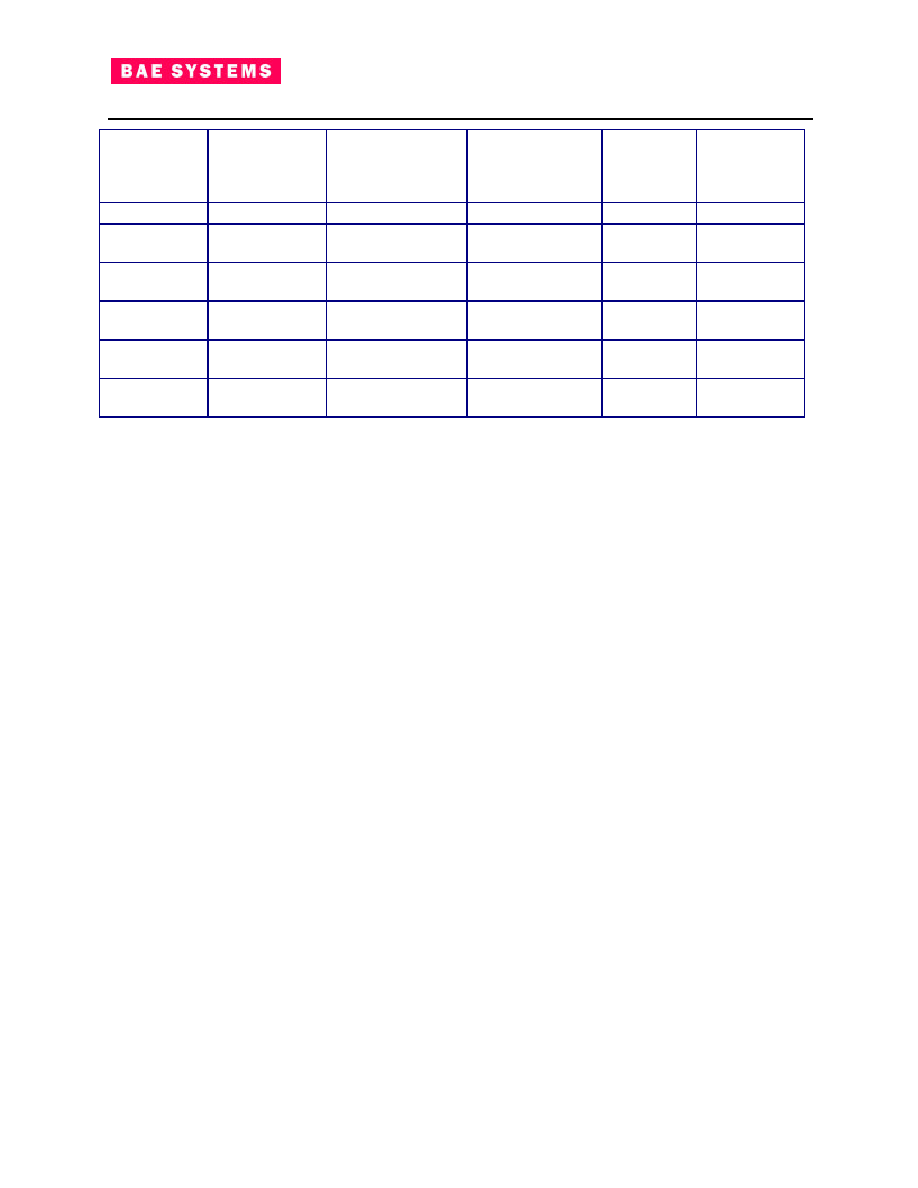

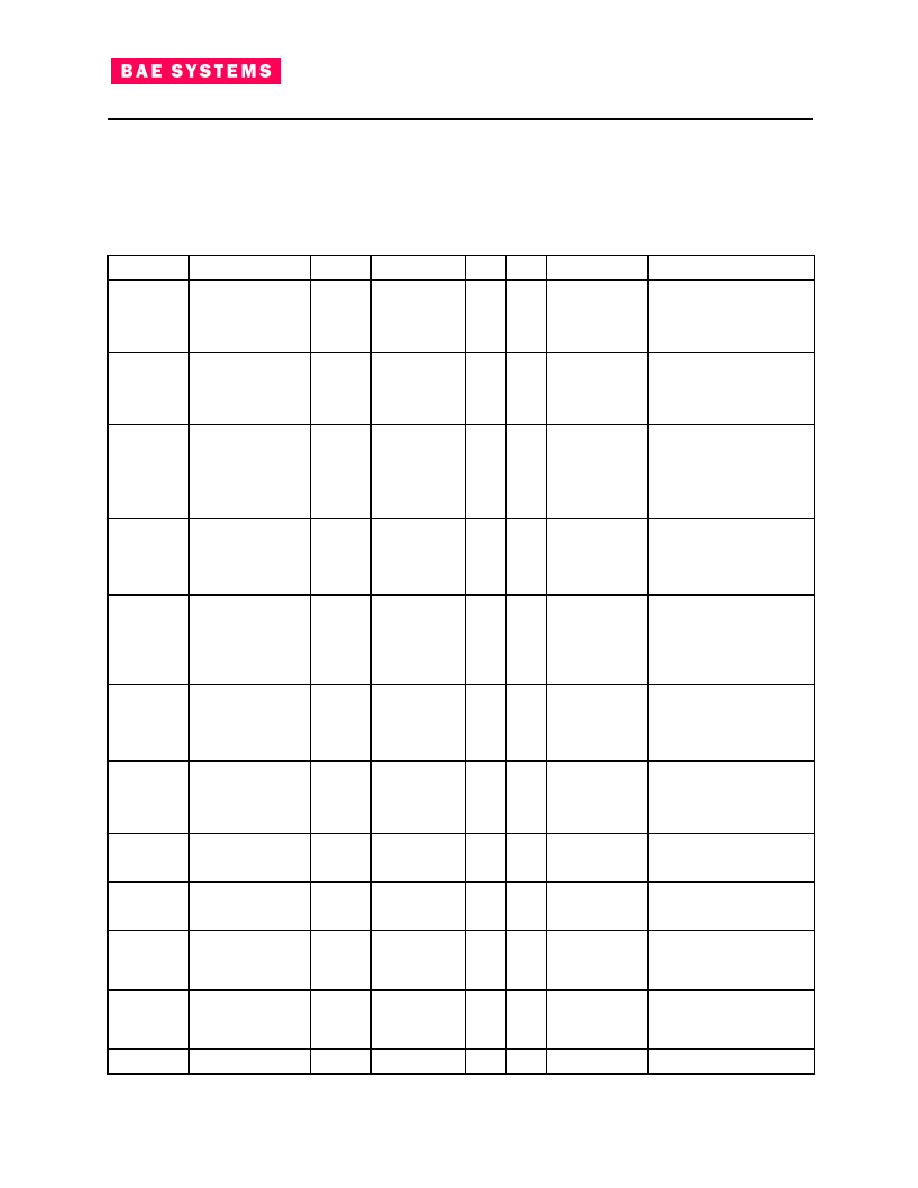

2.3 Ordering Information

This section provides the part numbering nomenclature for the RAD750 boards. Note that the individual

part numbers correspond to combinations of processor core frequencies, populated memory, and

environmental levels. For availability of RAD750 board variations, contact BAE SYSTEMS in Manassas,

Virginia or visit our web site at

www.rad750.com

. Table 4 shows the designated part numbers that are

currently offered.

10

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

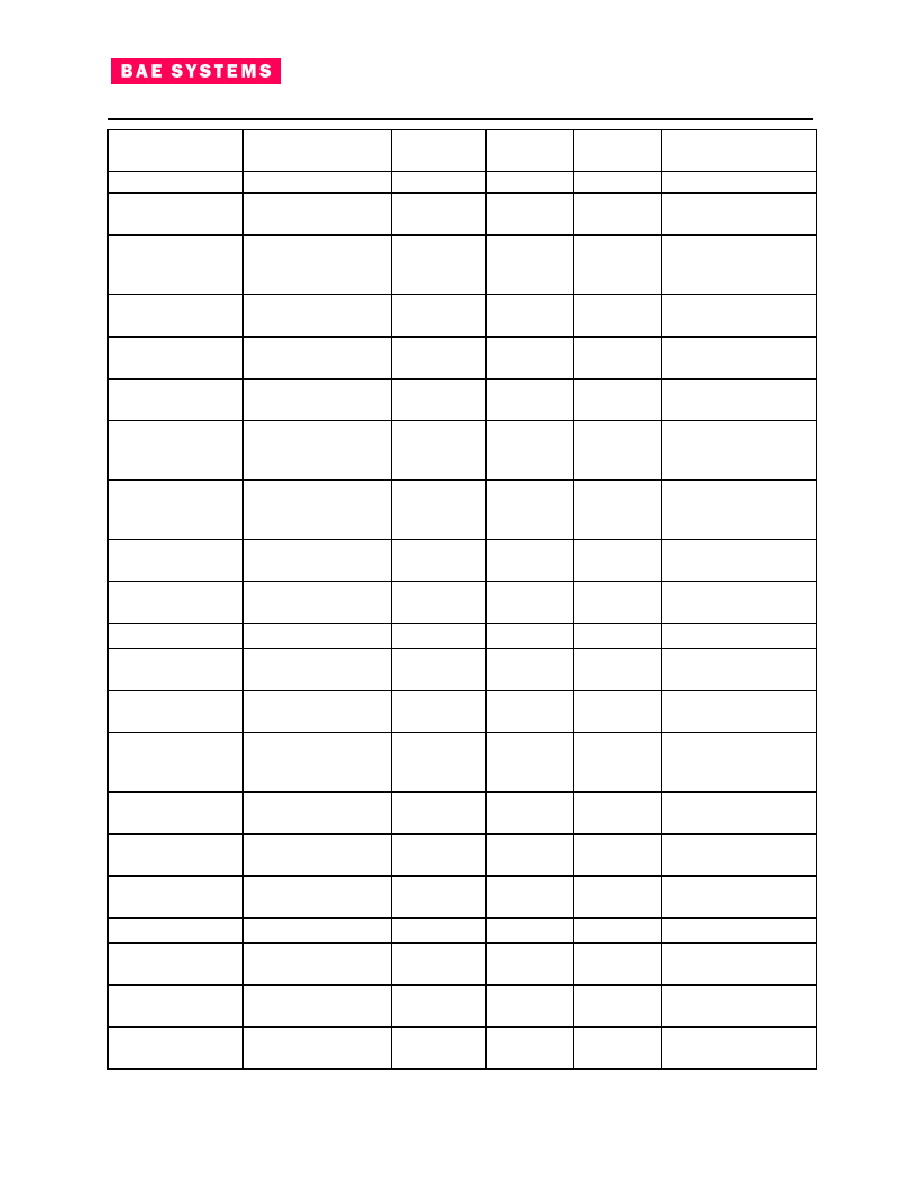

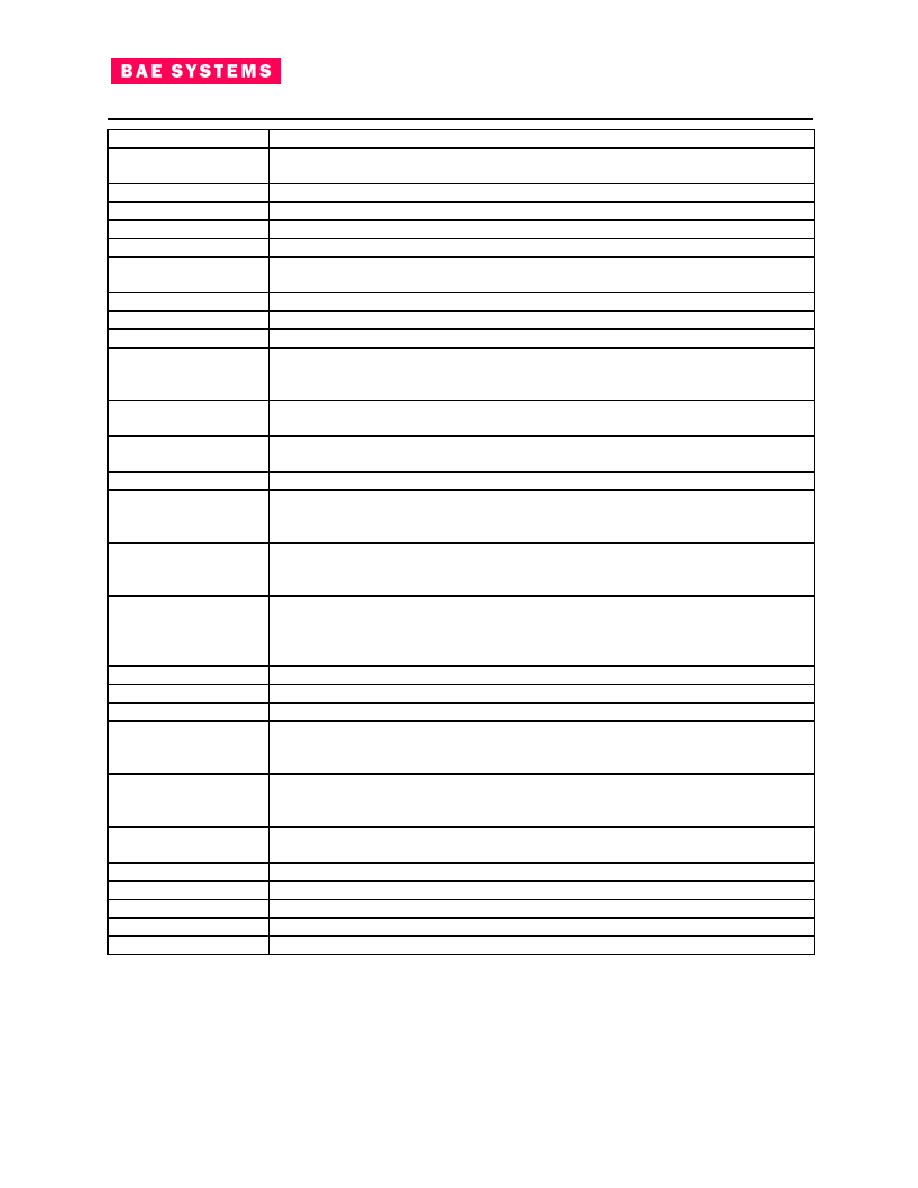

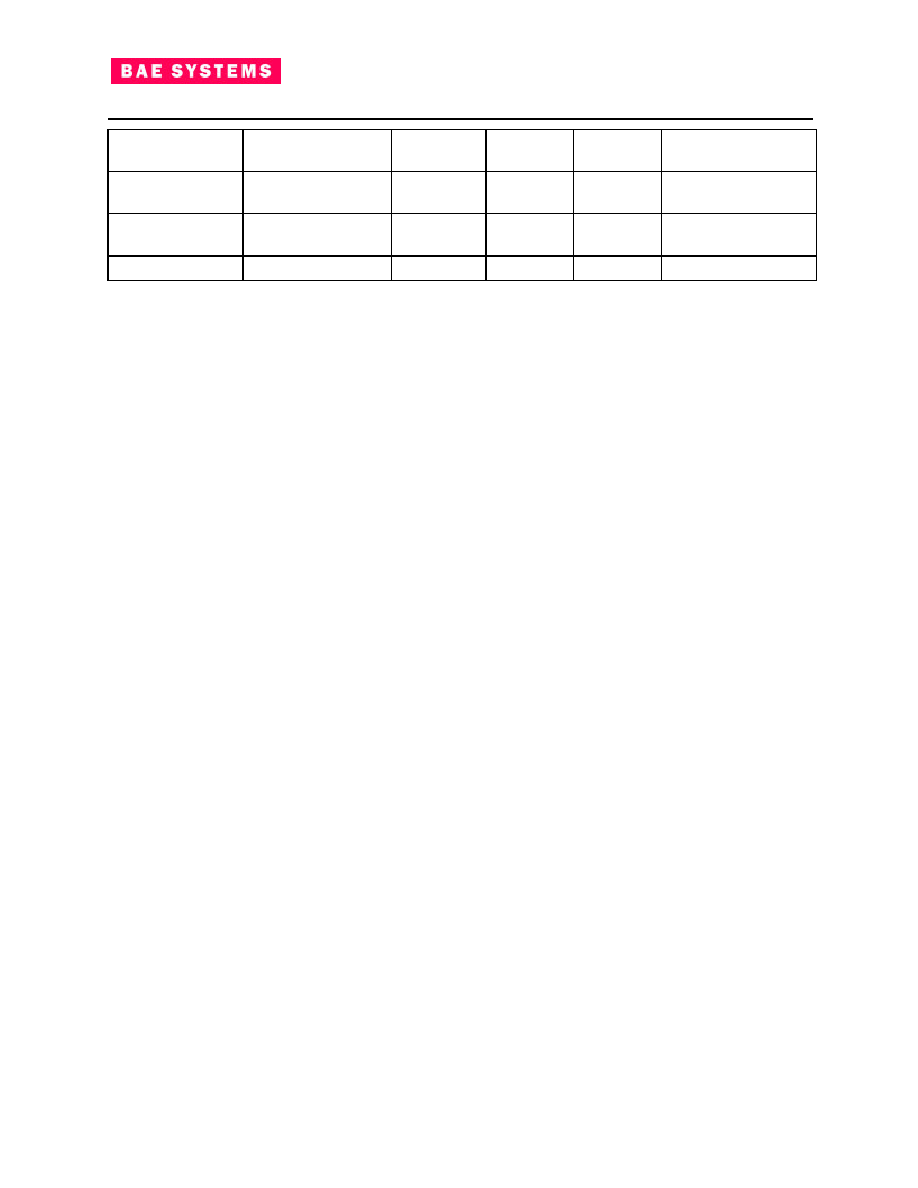

Table 4 - RAD750 board Part Number Listing

Part Number /

Designation

Maximum

Processor

Frequency

SUROM

SDRAM

Environmental

Available

244A325 /

Commercial

Configuration

132 MHz

256 KB

EEPROM

128 MB

Commercial

Parts, may be

different vendors

Now

234A510 /

Engineering

Model

132 MHz

256 KB

EEPROM

128 MB

Equivalent to

Flight - no burn-

in or screening;

Available for

Qualification

Now

234A511 /

Flight Model

132 MHz

256 KB

EEPROM

128 MB

Space Qualified

2001

2.4 SUROM Description

The RAD750 boards contain embedded software for initial program load of the RAD750 and the Power

PCI Embedded Microcontroller in the SUROM. The embedded software contains the following elements:

∑

Boot routine to load an image into DRAM and transfer control to this image

∑

Initialization routines for POR and push button reset

∑

Self test routines for the RAD750 and Power PCI ASIC

∑

Software interface drivers for all functions and interfaces in the Power PCI ASIC

∑

Memory test routines

∑

Exception handling routine(s)

∑

VxWorks loader

∑

Support for the software debug using UART interface

∑

Support for the hardware debug using JTAG interface

11

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3 Installation Instructions

3.1 Safety Precautions

To ensure proper functioning of the product during its usual lifetime, take the following precautions before

handling the board.

3.2 Unpacking and Inspecting

This section gives guidelines on unpacking and inspecting the RAD750 Board.

3.2.1 Unpacking

Note: This product is Class 1 Electrostatic Discharge Sensitive. Use ESD precautionary measures

when handling it.

An antistatic envelope protects RAD750 boards. Observe antistatic precautions and work at an approved

antistatic workstation when unpacking the board.

The RAD750 board is shipped in an individual, reusable shipping box. When you receive the shipping

container, inspect it for any evidence of physical damage. If the container is damaged, request that the

carrier's agent is present when the carton is opened. Keep the contents and packing materials for the

agent's inspection and notify BAE SYSTEMS customer service department of the incident. Retain the

packing list for reference.

Assuming that there is no obvious damage, you may still want to keep the shipping carton in case you

want to ship the RAD750 board on elsewhere.

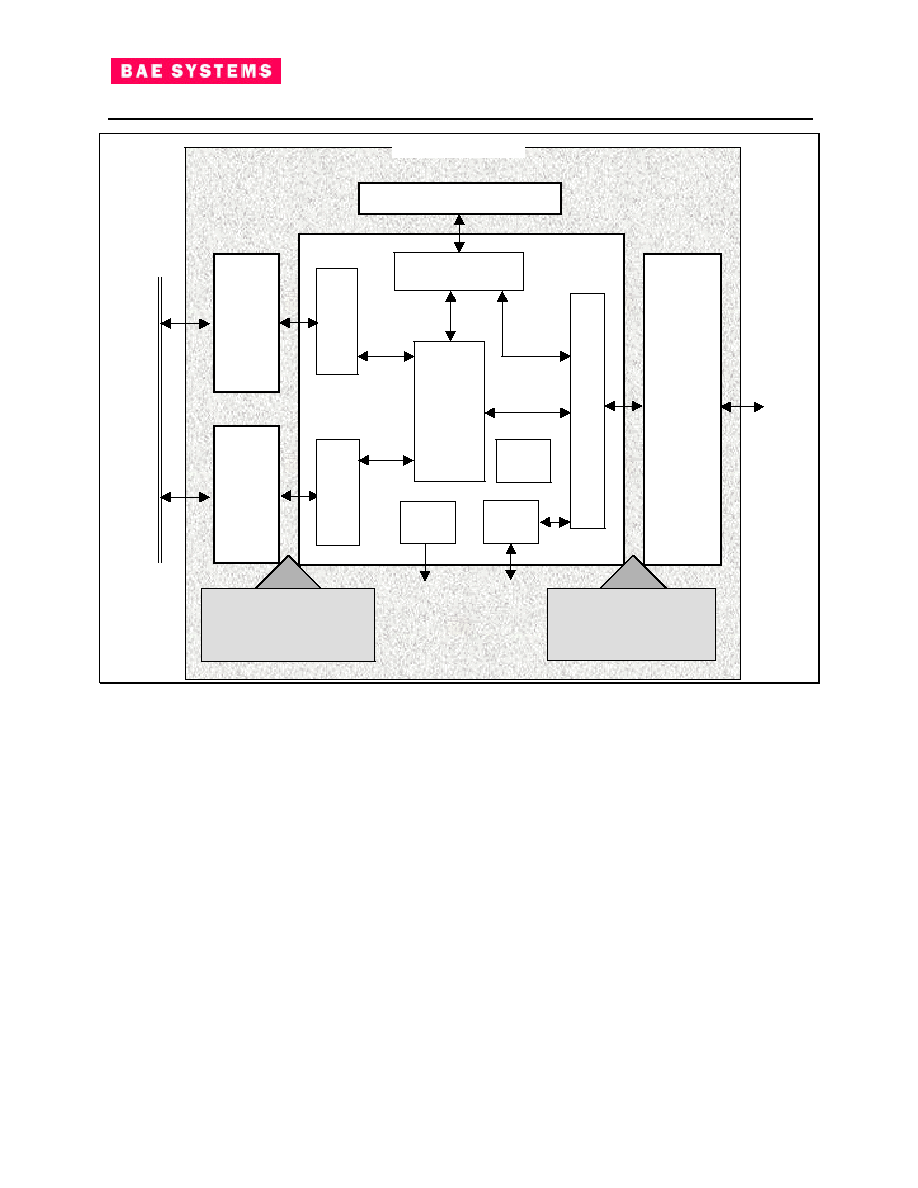

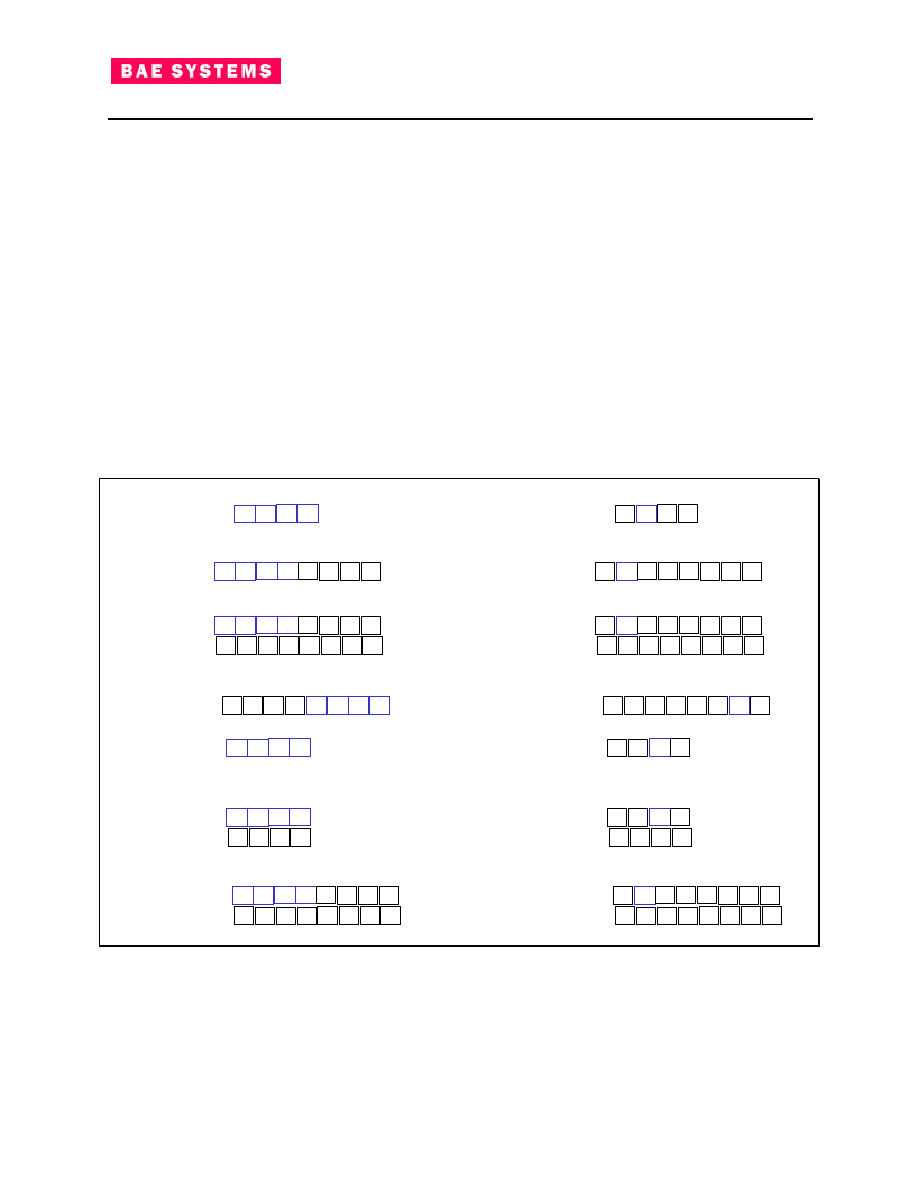

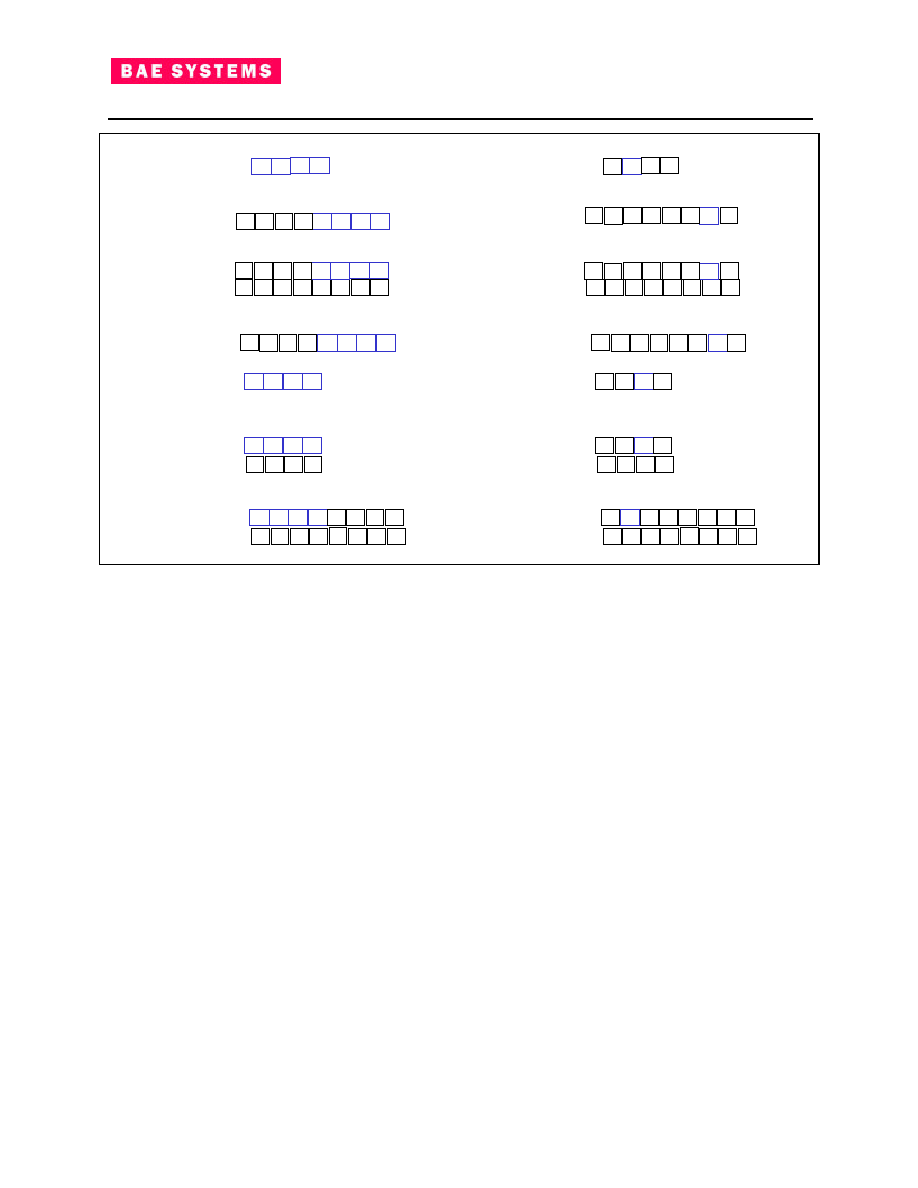

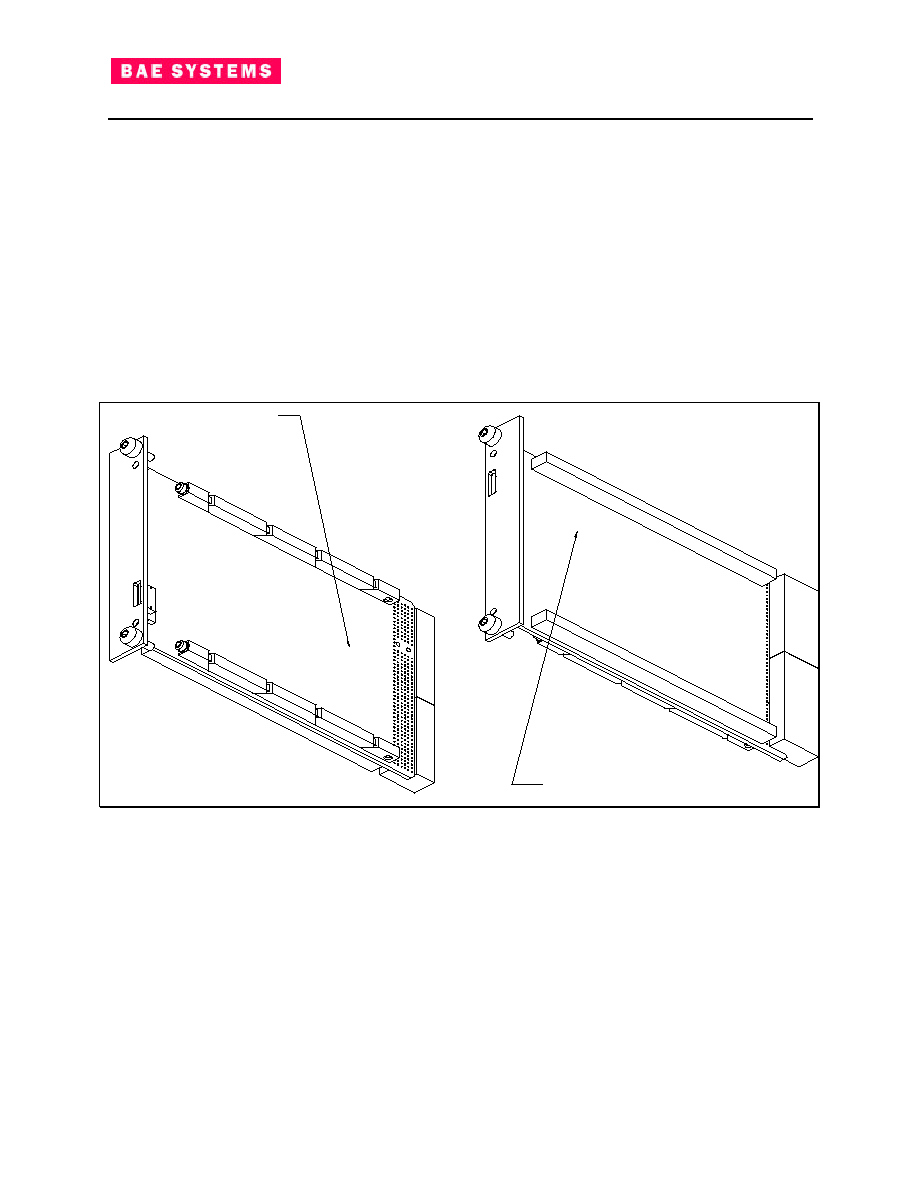

3.2.2 Board Identification

BAE SYSTEMS RAD750 boards are identified by a label on the non-component side of the board near

the front panel, and on the front panel itself. This label gives the revision state of the board, the root code

part number, and the board serial number, etc. as shown in the following diagram:

Figure 3: Board identification label

3.2.3 Malfunction or damage to the board or connected components

Electrostatic discharge and incorrect board installation and uninstallation can damage circuits or

shorten their lifetime.

∑

Before installing or uninstalling the board read this Installation section.

∑

Before installing or uninstalling the board in a CompactPCI rack: - Check all installed boards for

steps that you have to take before turning on / off the power.

∑

Take those steps.

∑

Ensure that the board is connected to the CompactPCI via both the J1 and the J2 connectors and

that the power is available on both CompactPCI connectors.

∑

Finally turn on / off the power.

12

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

∑

Before touching integrated circuits ensure that you are working in an electrostatic free

environment, and use a tested wrist and heel grounding strap.

3.3 Warnings

Do not exceed the maximum rated input voltages or apply reversed bias to the assembly. If such

conditions occur, toxic fumes may be produced due to the destruction of components.

Only use the RAD750 board in backplanes that supply power on both J1 and J2 connectors. Failure to

observe this warning may result in damage to the board.

3.4 CompactPCI Connector Keying

According to the CompactPCI Specification 2.0, R2.1, boards are marked and keyed according to their

slot type and power supply voltages. The RAD750 board is keyed as a 3.3V signaling I/O board. The

RAD750 board will operate in any CompactPCI slot.

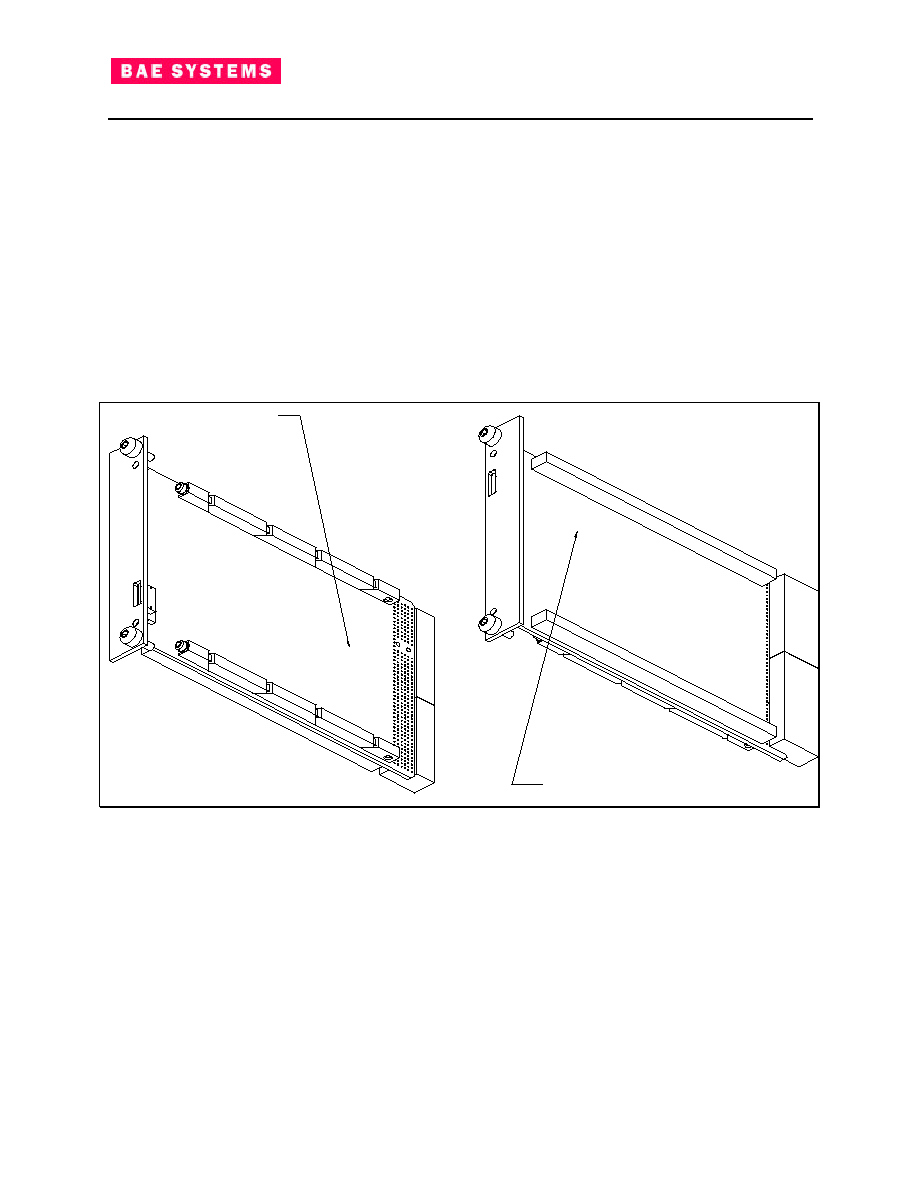

3.5 Insertion Levers/ Jack Screws

The RAD750 board comes with insertion jacks and a front panel. Exercise caution when applying

pressure to the levers during board insertion. Improper seating of the board will cause pin damage on the

J1 and J2 CompactPCI connectors. When plugging the board in or out, do not press at the front panel,

otherwise the front panel can be damaged. Use the handle for plugging the board in or out.

With or without insertion levers, do not apply more than

TBD

pounds of force when inserting this

card in a CompactPCI rack.

3.6 Wedgelocks

The RAD750 board is a conduction-cooled design, utilizing industry standard, multiple segment,

wedgelock retainers and stiffeners. The RAD750 board may be operated without the wedgelocks and

stiffeners and plugged into any commercial CompactPCI rack. The wedgelocks and stiffeners can be

removed by simply unscrewing them. When using a board with the wedgelocks, make sure that the

wedgelocks are tightened down properly. Wedgelocks should be tightened with a torque wrench to

TBD

pounds of torque. When using a board without the wedgelocks mounted, make sure there is sufficient

cooling so that the components are not damaged.

3.7 Power Requirements

The RAD750 board operates on a single +3.3V power supply and is keyed for operation in a 3.3V

signaling CompactPCI system. The Power supply for the box must be capable of supplying at a minimum

of 4.0 A, plus any additional 3.3V power (or other voltages) for other boards in the unit. The voltage

should be highly regulated to a worst case of

±

10% (+/-5% recommended).

The operating temperature of the board is -55

∞

C to +70

∞

C (5% to 95% noncondensing humidity). The

operation of the RAD750 board at the maximum operating temperature requires a minimum airflow of 300

LFM (linear feet per minute) if operated without the wedgelocks installed.

3.8 Backplane Design Guidelines

The RAD750 board is fully compliant with the CompactPCI J1 pin assignments as called out in the

CompactPCI Specification 2.0, R2.1. The RAD750 board connects B09 on J1 to the PCI_RDY_PAR

Sideband Signal from the Power PCI bridge, which is currently specified as reserved. This signal was

added for increased fault tolerance and complies with the PCI specification for sideband signals. Boards

and devices that do not utilize this signal need not connect to B09.

13

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.9 Power-up and Operational Description

This chapter describes power-up and subsequent operation of the RAD750 board.

3.9.1 Power-up

Having configured the backplane and taken note of the system configuration suggestions previously, with

the RAD750 board firmly secured in the rack, power-up the rack.

The SUROM for the RAD750 board, which controls its operation after power-up, is described in the

RAD750 Software Reference Manual.

3.9.2 Operation Description

The POR signal into the processor board must be held active while power is applied. The POR signal to

the processor board will result in an automatic hardware flush reset of the ASIC's, leaving them in their

default state. The EMC in the Power PCI will then take over operational control of the board to run the

desired initialization steps programmed into SUROM (checkout of CPU, Initialization of key structures

such as PCI address and control registers, etc.). The EMC will then hand-off control of the initialization to

the RAD750 CPU by releasing the reset line to the processor. The code that will be run by the EMC as

well as the code run by the processor are programmable and may be different for each mission.

3.9.3 Resetting the RAD750 board

The following section will briefly describe each of the resets available on the RAD750 CompactPCI card.

These resets are:

∑

Power on Reset

∑

PCI Reset

∑

JTAG TRST

∑

JTAG Reset

∑

Software Activated Reset ≠ RAD750

∑

Software Activated Reset ≠ Card

∑

Internal Hardware Critical Error Reset

∑

Built In Self Test (BIST) Reset

The above reset types are the basic types of reset classes for the board from a hardware perspective.

Software can also provide some tailored Reset options through the use of leaving fingerprints in memory

prior to reset or through looking at the state of Programmable Interrupts and Discretes (PIDS) into the

card to select different grouping of instructions to be run during bring-up following a reset.

During a speed change to the RAD750, the bridge chip will generate a HRESET signal to the RAD750

(not SRESET). No PCI reset will be issued since that bus is not effected.

The source of the reset is recorded in the BIST Core Status register that will not be flushed on reset.

Bits 4:0 of this register will be set to indicate the source of the reset as follows:

∑

Bit 4: Logic BIST

∑

Bit 3: JTAG SW Reset

∑

Bit 2: Power PCI internal bus Software Reset (soft reset)

∑

Bit 1: Internal Hardware Reset (Critical Error)

∑

Bit 0: POR

14

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.9.3.1 Power on Reset

A Power on Reset is caused by either the POR signal from the backpanel or the Reset signal from the J7

test connector being activated. This reset causes a flush-reset of all the registers in the Power PCI to

their Reset Value and all outputs will be placed in a safe state as documented in the RAD750

CompactPCI Board Hardware User's manual. The HRESET signal to the RAD750 is also activated

during POR. After the flush reset completes, the Power PCI is then used to check out board health and

reinitialize the chip (dependent on how Power PCI code is written). Control is generally then passed to

the RAD750 to complete the bring-up sequence.

3.9.3.2 PCI Reset

When the Power PCI is configured as PCI central resource (primary input CENTRAL_RESOURCE = `1')

the Power PCI holds PCI_RESET# active while in the Power On Reset state and until the PCI Bus Reset

bit of the PCI Bus Reset register is cleared. When the Power PCI is not the central resource

PCI_RESET# is an input to the Power PCI and reset some of the PCI logic but not the entire Power PCI.

The Power PCI generates PCI RST# when it is configured as central resource and POR or BIST is active,

or the PCI Reset Active bit is set in the Bus Reset register.

The PCI Reset Active bit is read/write from the both the PCI and Power PCI internal bus interfaces in

Power PCI Internal register space. Additionally, this bit is set automatically under any of the following

conditions:

∑

A Data Phase Timeout is detected

∑

An Arbitration Latency Timeout is detected

The PCI Reset Active bit is set to `1' on a flush reset.

Once this bit is set (and RST# is active), it can only be reset via the Power PCI internal bus interface. It is

software's responsibility to ensure that the 1ms minimum reset requirement of the PCI Specification is

met.

With the exception of external I/O tri-state control, the Power PCI responds to a PCI reset in the same

manner, whether it is generating it, or responding to it.

PCI reset is handled as a broad side reset in the Power PCI, and has the following affects:

∑

All PCI defined registers are reset to the states required by the PCI Specification.

∑

All non-PCI defined internal registers remain unchanged.

∑

All PCI state machines are returned to their idle states.

∑

The Power PCI internal bus Master completes its current transaction(s) and then terminate.

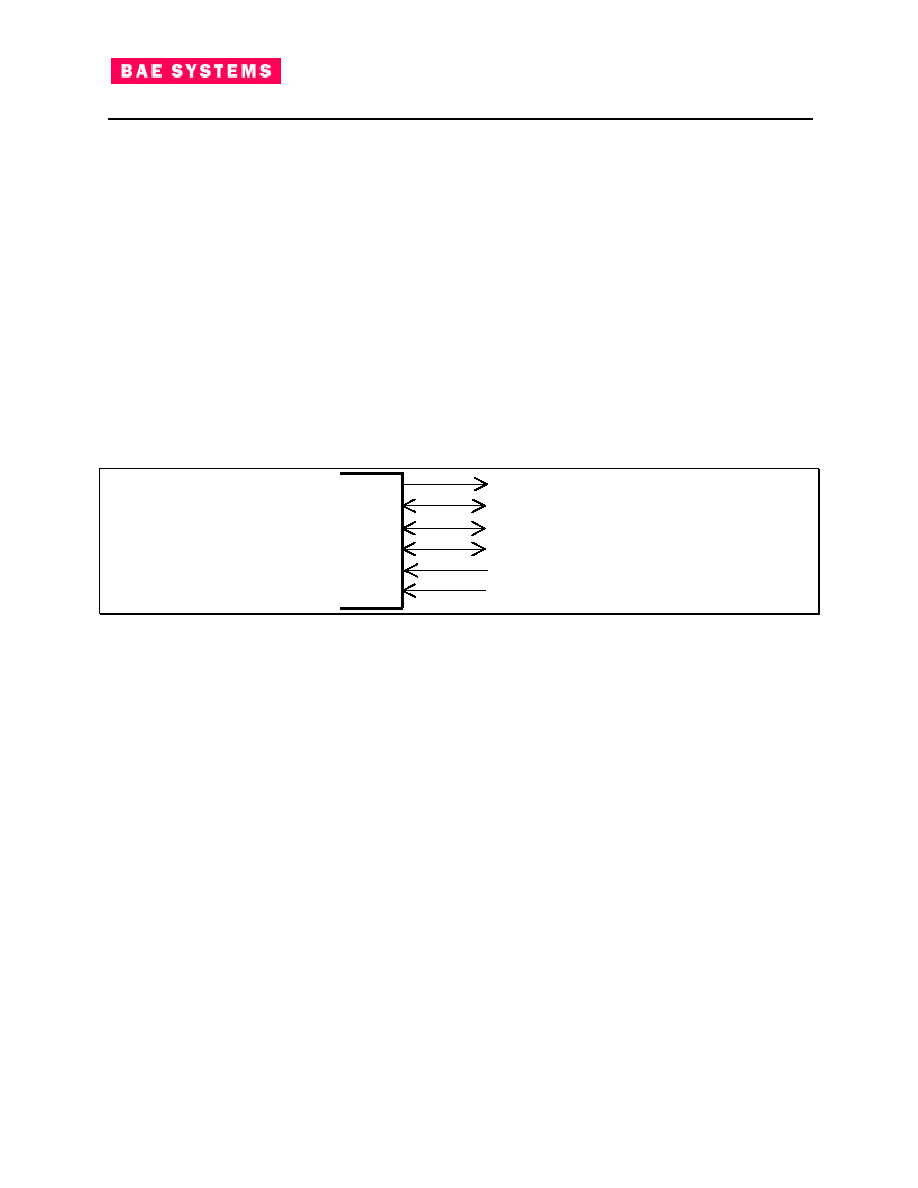

∑

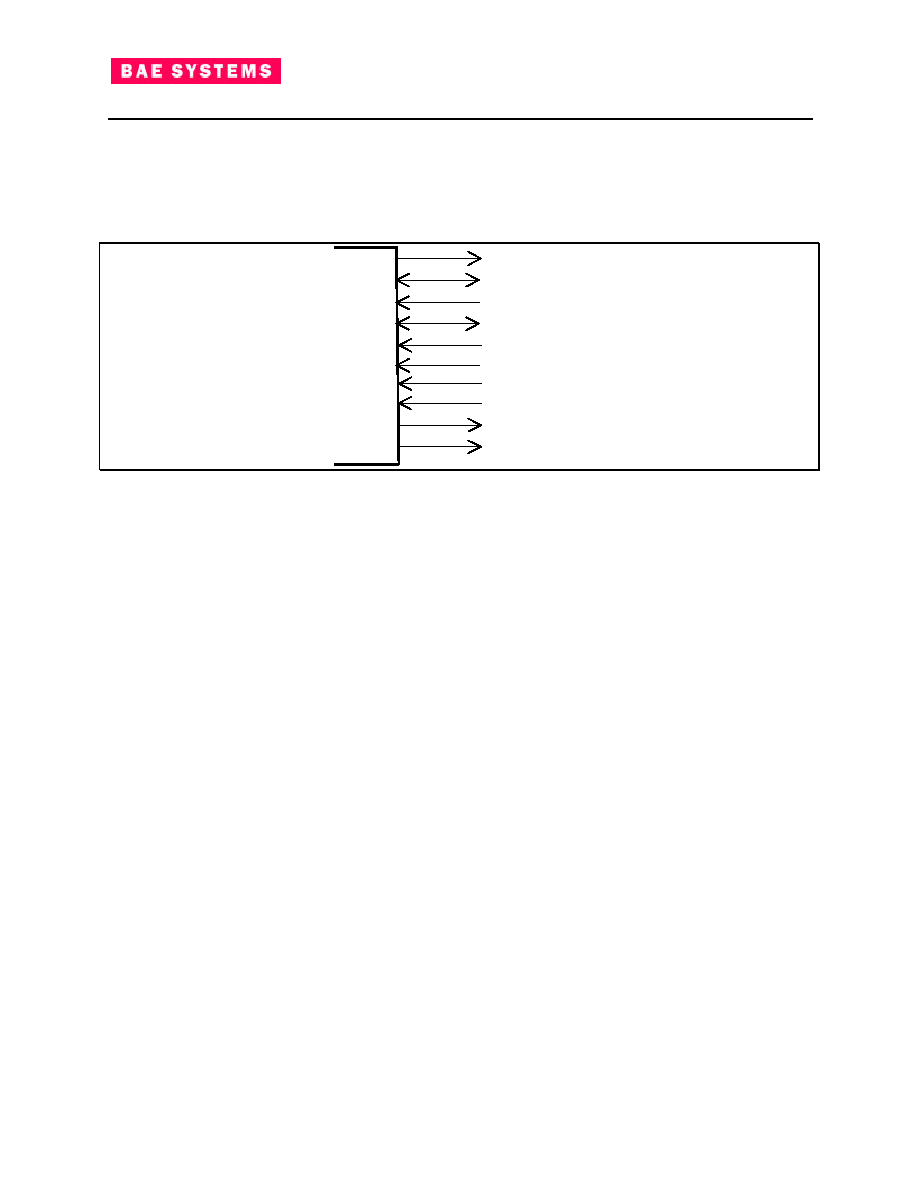

All internal buffers are invalidated with the exception of Power PCI internal bus reads and writes

of PCI internal register space.

During a PCI reset, the Power PCI internal bus has access to the PCI internal register space. However,

the PCI defined registers will be held reset as long as PCI RST# is active, so writes to these registers

have no affect.

Any attempted Power PCI internal bus access other than to PCI internal register spaces during a PCI

reset causes an Invalid Power PCI internal bus access error. This results in error signaling back to the

Power PCI internal bus, the setting of the Invalid Power PCI internal bus Access bit in the Status 2

register, and the INTERRUPT_OUT signal going active if not masked in the Status 2 Mask register.

3.9.3.3 JTAG TRST

The Power PCI tri-states its Master JTAG Tap-Reset outputs (JTM_TRST_L and JTMS_TRST_L) while

in the Power on Reset state. JTM_TRST_L and JTMS_TRST_L will be pulled down on card to force the

15

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

JTAG interface of attached ASICs into the Test-Logic-Reset state during POR and anytime TRST_L is tri-

stated. When JTMS_TRST_L is active the Power PCI's JTAG slave port will be forced to the Test-Logic-

Reset state. This signal has no effect on any other Power PCI logic.

3.9.3.4 JTAG Reset

The Power PCI can be reset via the JTAG slave interface by using the clock control instruction (op code =

`010') and JTAG Address (2:0) = `011'. This Reset is identical to a Power on Reset.

3.9.3.5 Software Activated Reset - RAD750

The Power PCI bridge chip also contains a RAD750 Discretes register which can be to initiate a HRESET

signal to the RAD750 by setting bit 0 of the register. This register can be used as part of error recovery

routines, clock change routines, etc. as determined by the application.

3.9.3.6 Software Activated Reset - Card

In addition, a write to 0x`BF86 0040' from any of the interfaces initiates a full reset of Power PCI.

3.9.3.7 Internal Hardware Critical Error Reset

When the Power PCI internal logic generates a critical error, the Power PCI attempts to handle the error

via vector interrupt 7. If the Power PCI cannot successfully resolve the error condition, it will issue a

software reset. If the internal error prevents the Power PCI from accessing memory, the Power PCI's

Watchdog timer expires, causing an internal hardware generated reset.

3.9.3.8 Built In Self Test (BIST) Reset

The Power PCI enters the BIST Reset state just before exiting BIST. Only bistable logic will be reset

during BIST reset. During BIST reset the Power PCI initializes all internal registers to their Reset Value

with the exception of the Clock and Test registers and the JTAG Tap Controller.

3.10 Troubleshooting

This chapter gives some suggestions for what to do when your RAD750 board doesn't work.

Don't panic!

Use a step-by-step method for looking at the problem.

Try to diagnose the problem type (i.e., hardware or software).

If all else fails, phone or fax your nearest BAE SYSTEMS technical support office for assistance.

3.10.1.1 Step 1- No Power

Check that your enclosure's mains power lead is plugged into the main outlet and into the chassis.

Remove the board during the remainder of the power debug procedure.

Check that you have switched on at the mains and at the system.

Check that you are receiving power from the main outlet (test this with a lamp for example).

Ensure that no fuses have blown.

If the system refuses to start up, this suggests a problem with the power supply. It is essential that only

qualified personnel deal with the problem from now on.

16

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.10.1.2 Step 2 - Power On, Unexpected Behavior

Power the equipment off.

Ensure that the board is firmly seated and secured in the rack and that all male/female connectors mate

together correctly.

Check the links on the board and the system backplane.

If you are unsure of which link configuration to use, use the default configuration initially.

Check that the CompactPCI rack has diode terminators, if these are not built in (the manual for your rack

should tell you whether the terminators are built in).

Check that the power supply is within CompactPCI limits on +3.3V, +5V, +12V and -12V with a digital

voltmeter. Note: The RAD750 board only operates on +3.3V.

Check that there is only one board configured as system controller and that this is in the slot keyed to

receive it.

Check that there are no vacant slots in the rack without jumpers (or that an automatic daisy chaining

backplane is being used).

If you are still getting unexpected behavior, try removing all other CompactPCI boards from the rack and

proving the RAD750 board's operation in isolation, then adding a board at a time until the offending

element is found.

3.10.1.3 Step 3 - Power On, No Terminal Display on the Support Equipment

Check that all cables are plugged in correctly.

If you have made your own cable, check that the pinout and wiring is correct. Note that the Rx and Tx

lines are switched in the cable. See Section 5.2for a description of the cable.

Check that all connections are tight.

Check that the terminal is receiving power and is on.

Check that the terminal is set up for DTE (56 Kbaud, 8 bits/character, 1 stop bit, parity disabled).

3.10.1.4 Step 4 - Overheating

Check that no grilles are blocked in the chassis, either internally or externally.

Check that the fans are working.

Clean or replace any air filters fitted to fans.

Check that there is a free airflow around the chassis exterior (i.e., it should not be in an alcove or other

confined space, or on a thick pile carpet).

Check that the enclosure is not next to a radiator or other heat source.

3.10.1.5 Step 5 - RAD750 board Locks up

Try resetting the RAD750 board or powering the system down and then up again.

3.10.2 Debugging

When debugging software, disable the caches to make tracing the software execution easier.

17

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.11 RAD750 Board Electrical Connectors

The J1 and J2 connectors load a shield at row F on the board. This shield covers the top of the IEC-1076

connector and help to provide a low impedance return path for ground between the board and the

CompactPCI backpanel. The lower shield option that is provided for in IEC-1076 is not required and is

not loaded if it protrudes into the interboard separation plane. Descriptions of the signals on the two

connectors can be found in Section 5.

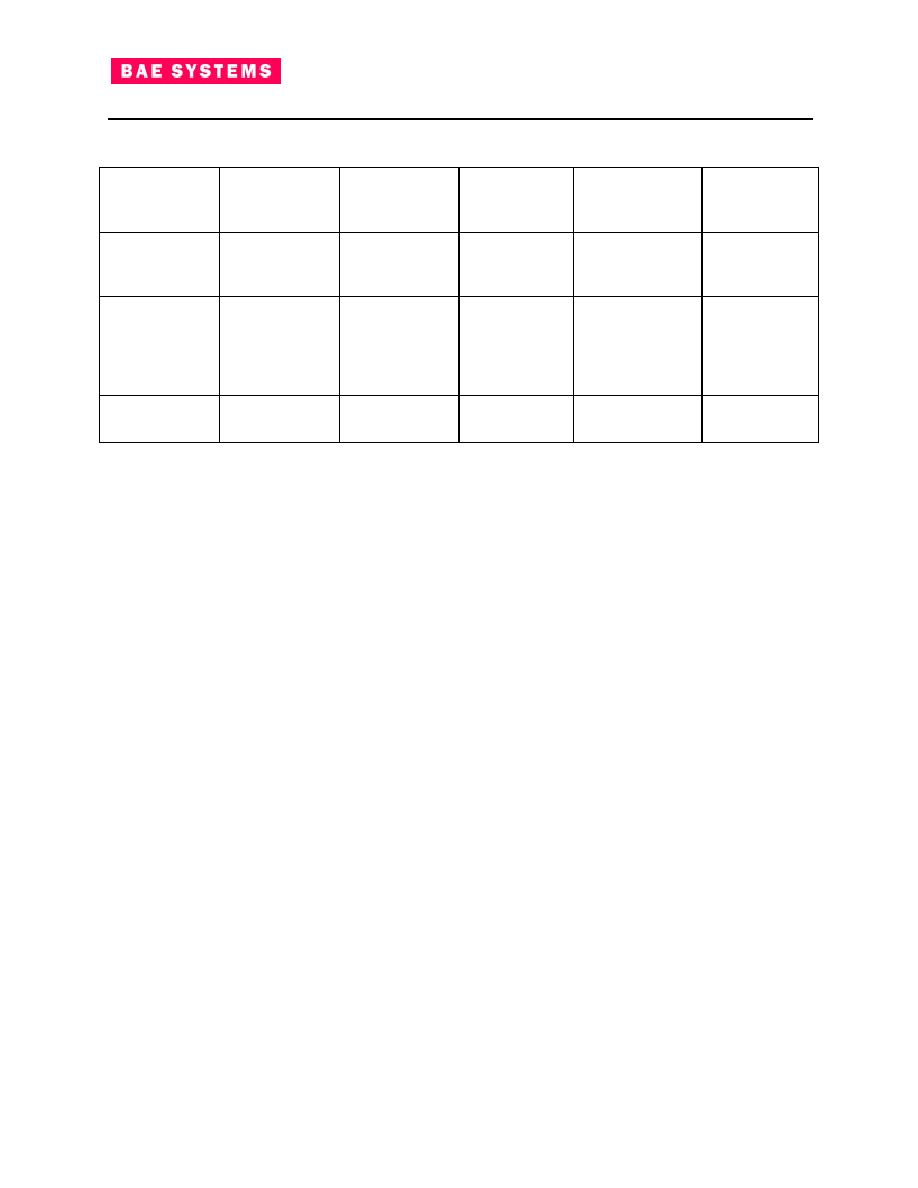

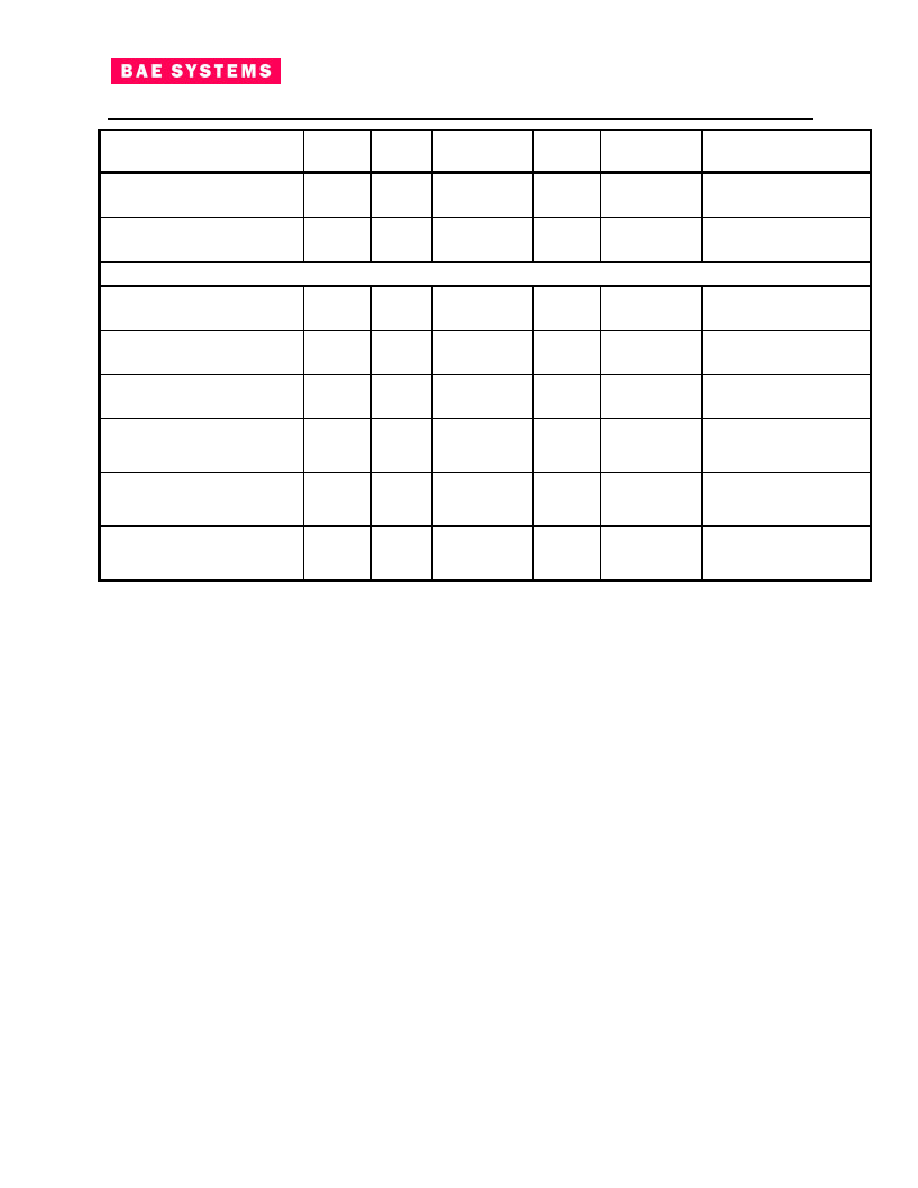

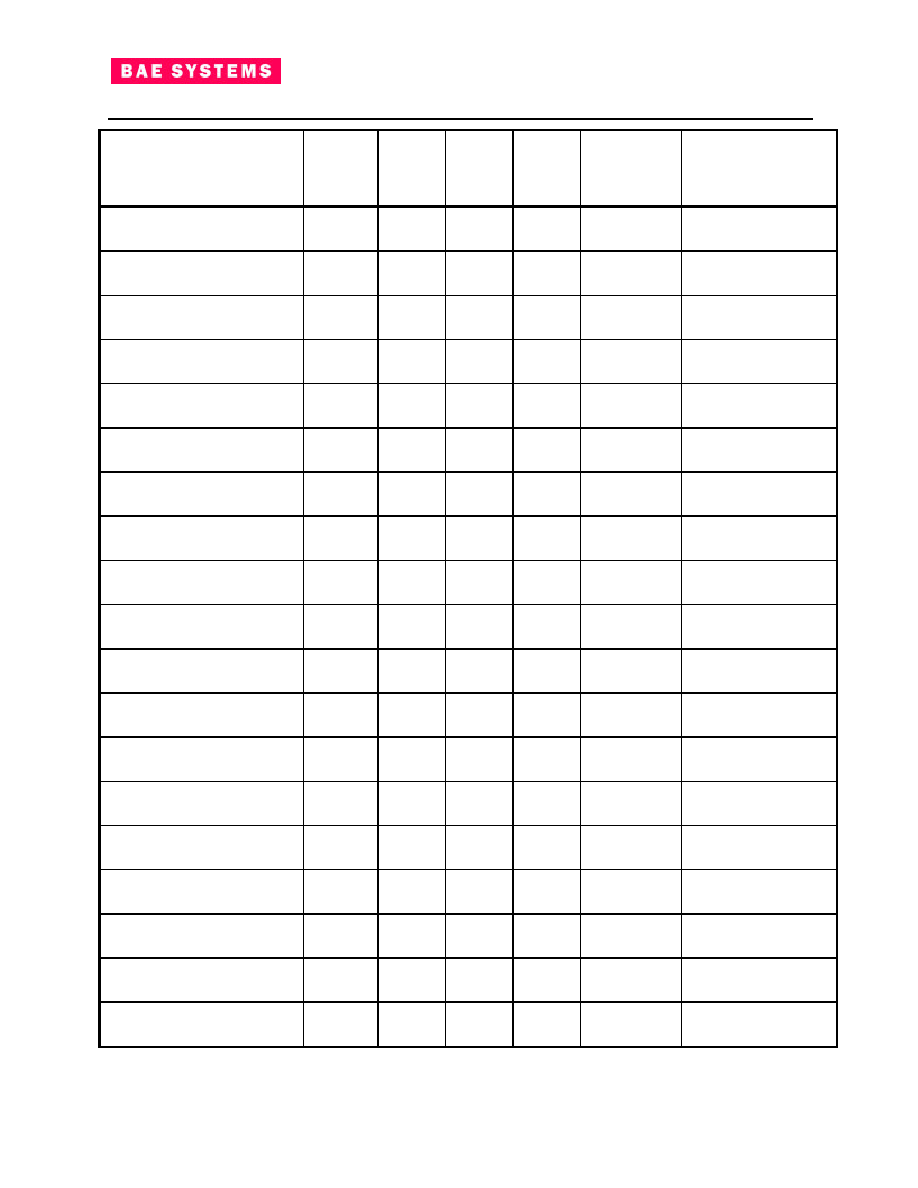

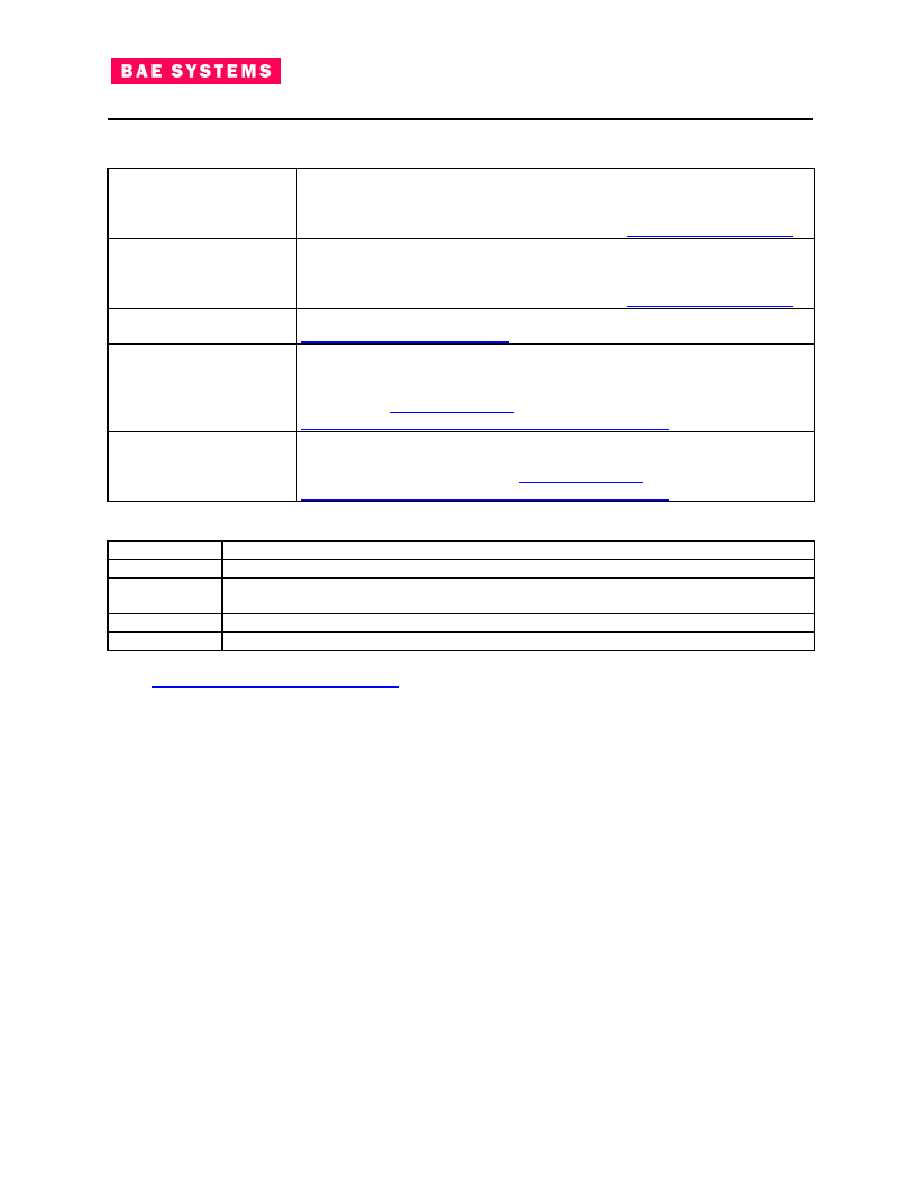

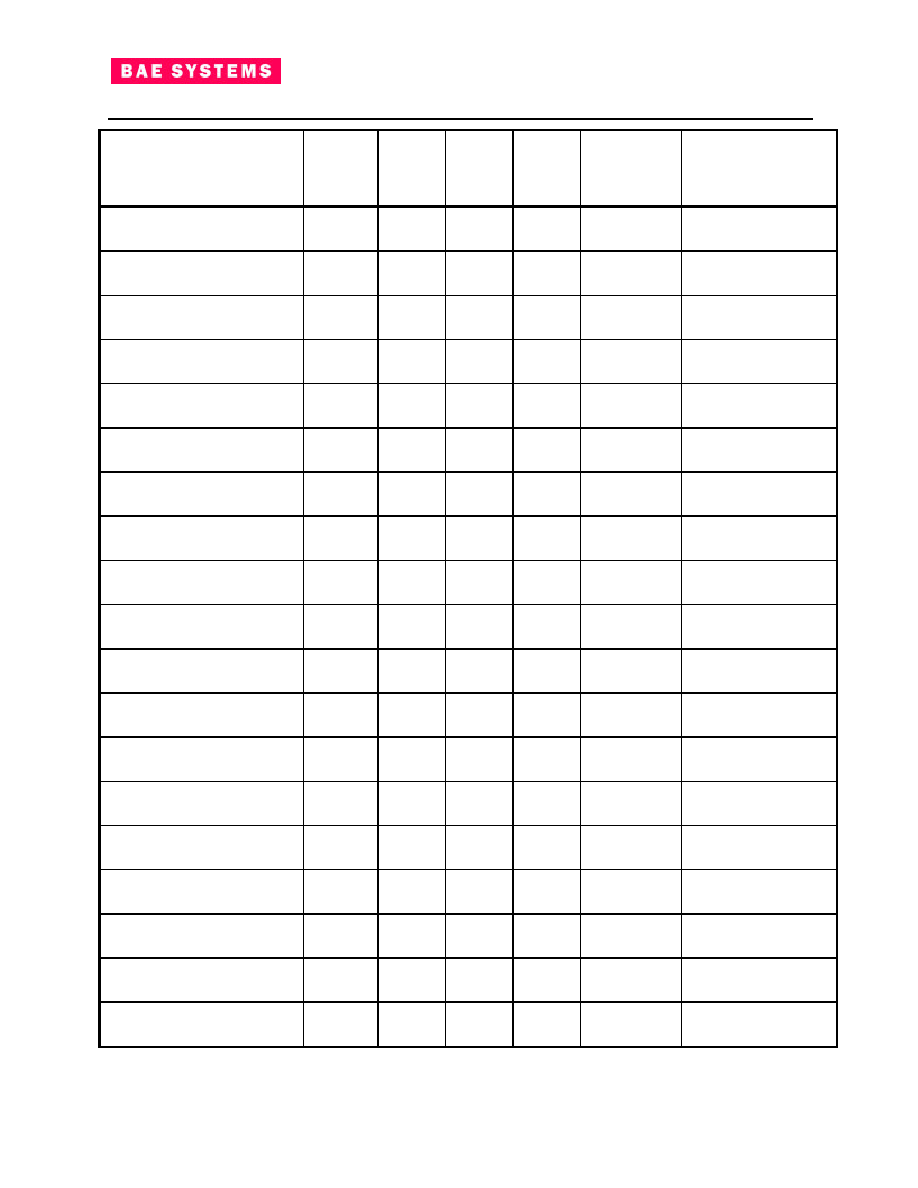

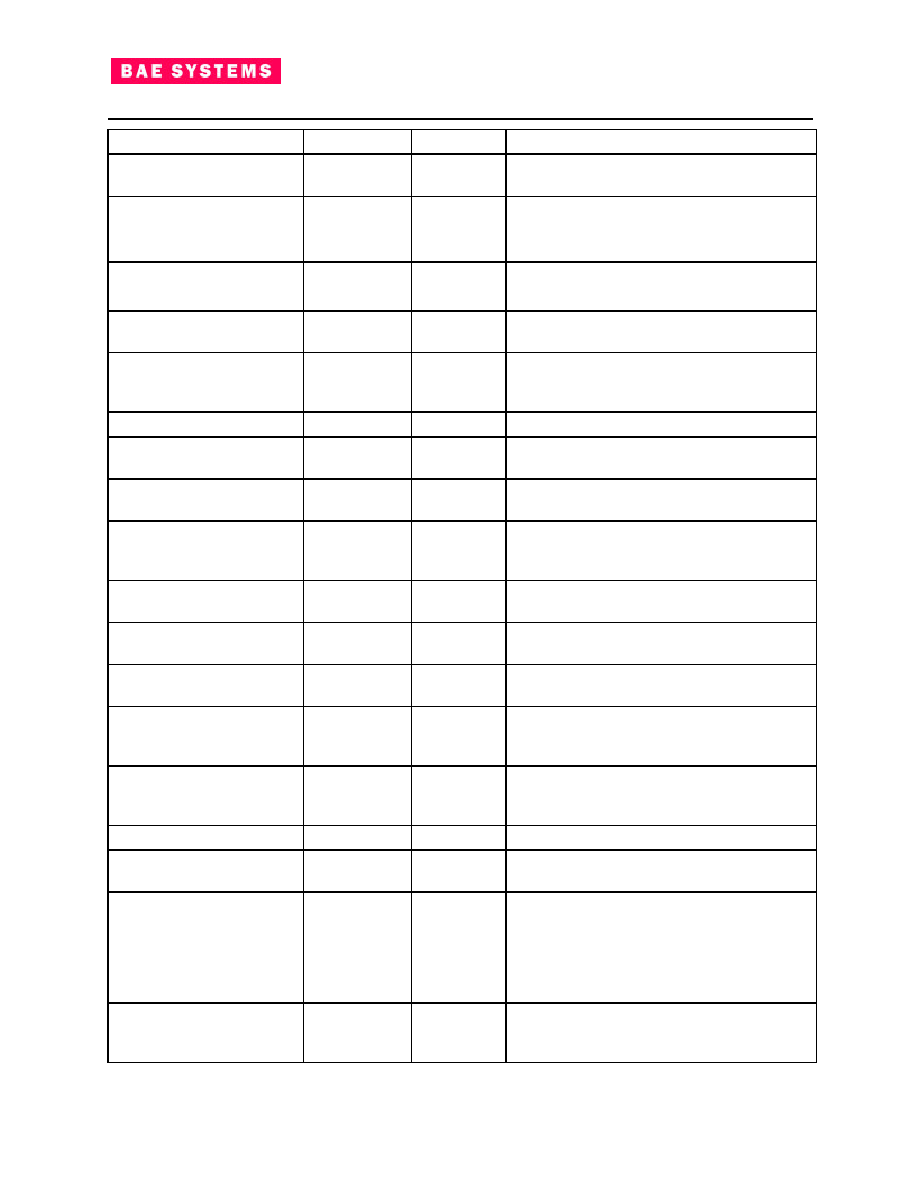

3.11.1 J1 Connector Pin Assignment

The J1 connector is the primary bus interface for the RAD750 board to the assembly it resides in. The

main PCI and backpanel JTAG signals are mostly routed on this connector. The following color coding is

used in Table 5 and Table 6:

Black - Power and Ground Assignments

Red - Base CompactPCI 32 bit System Mappings

Blue - Fully Compliant Mappings to Unused 64-bit System Signals

Green - Mapping onto Reserved Signals

Purple - Unused Reserved Signals

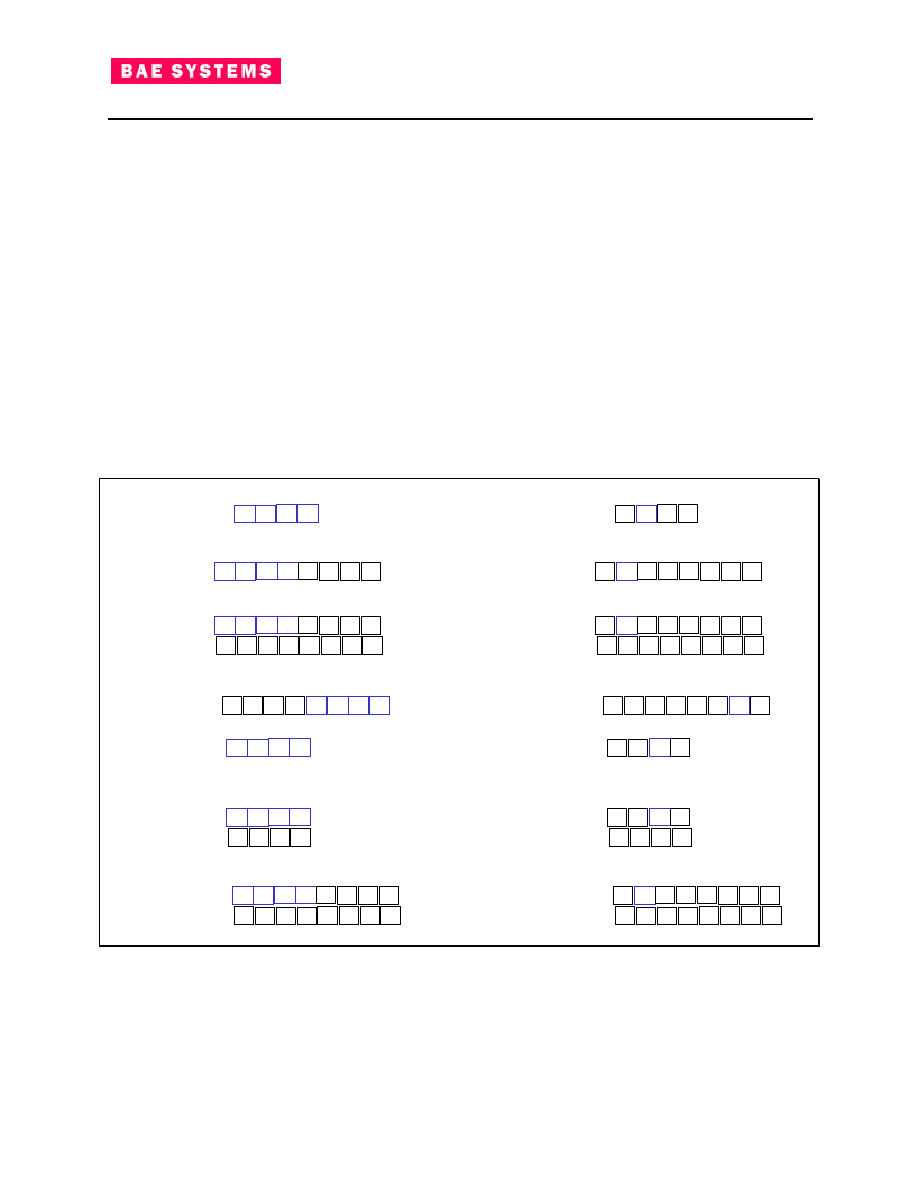

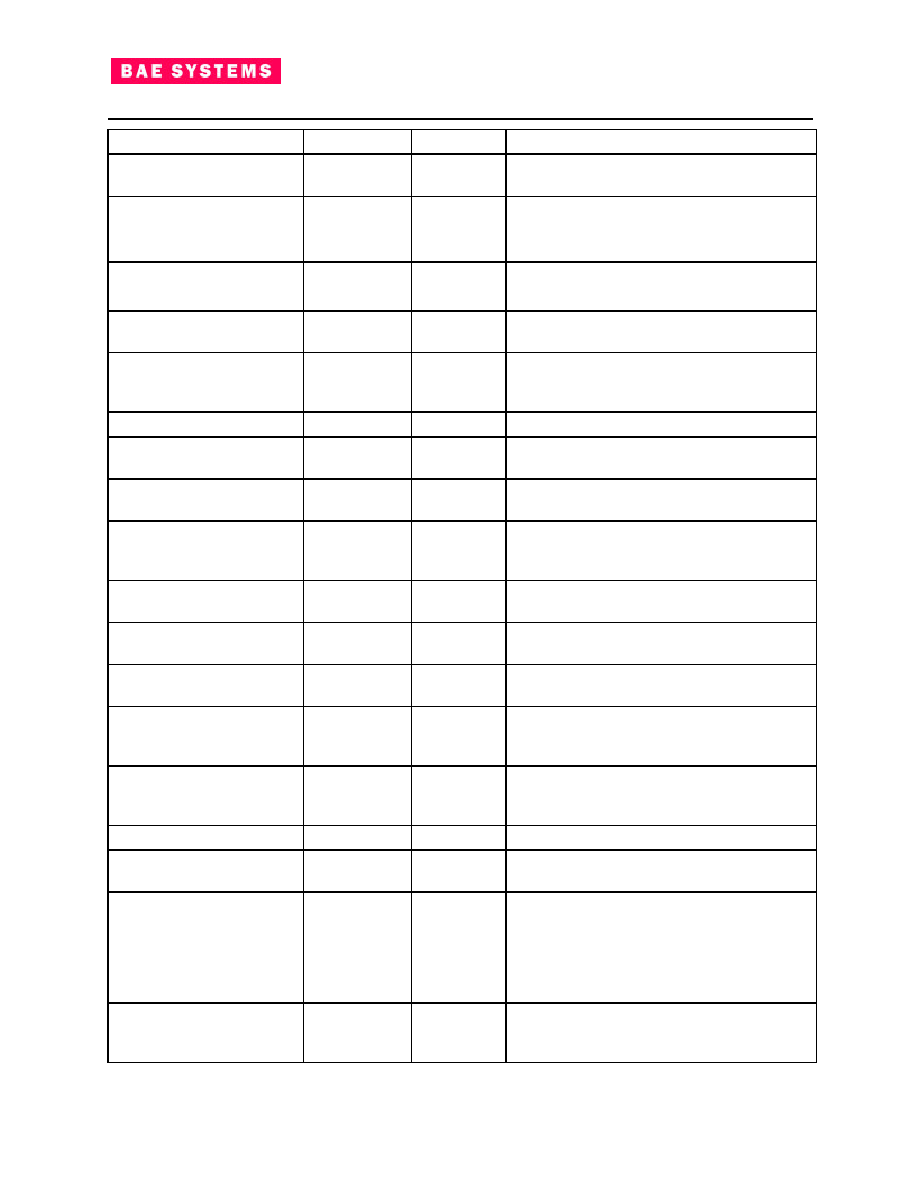

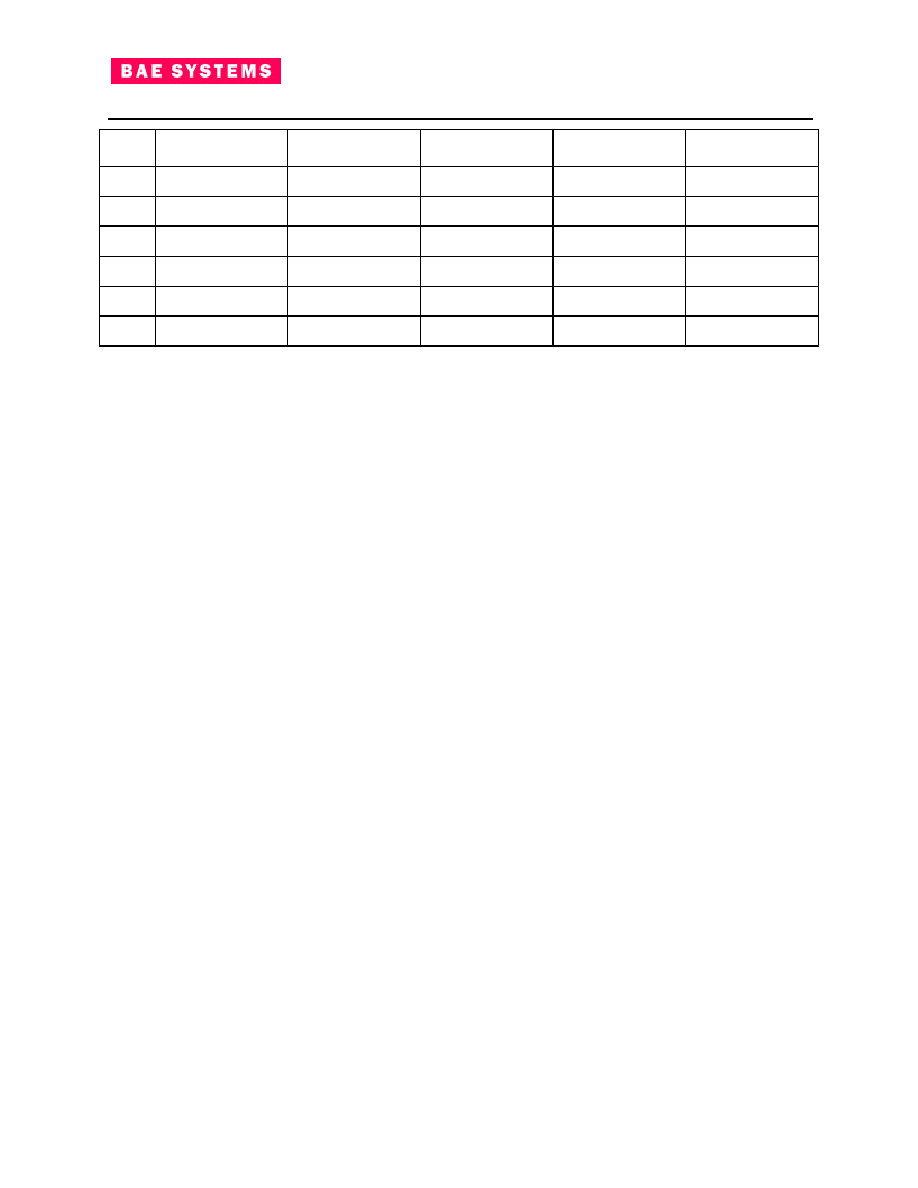

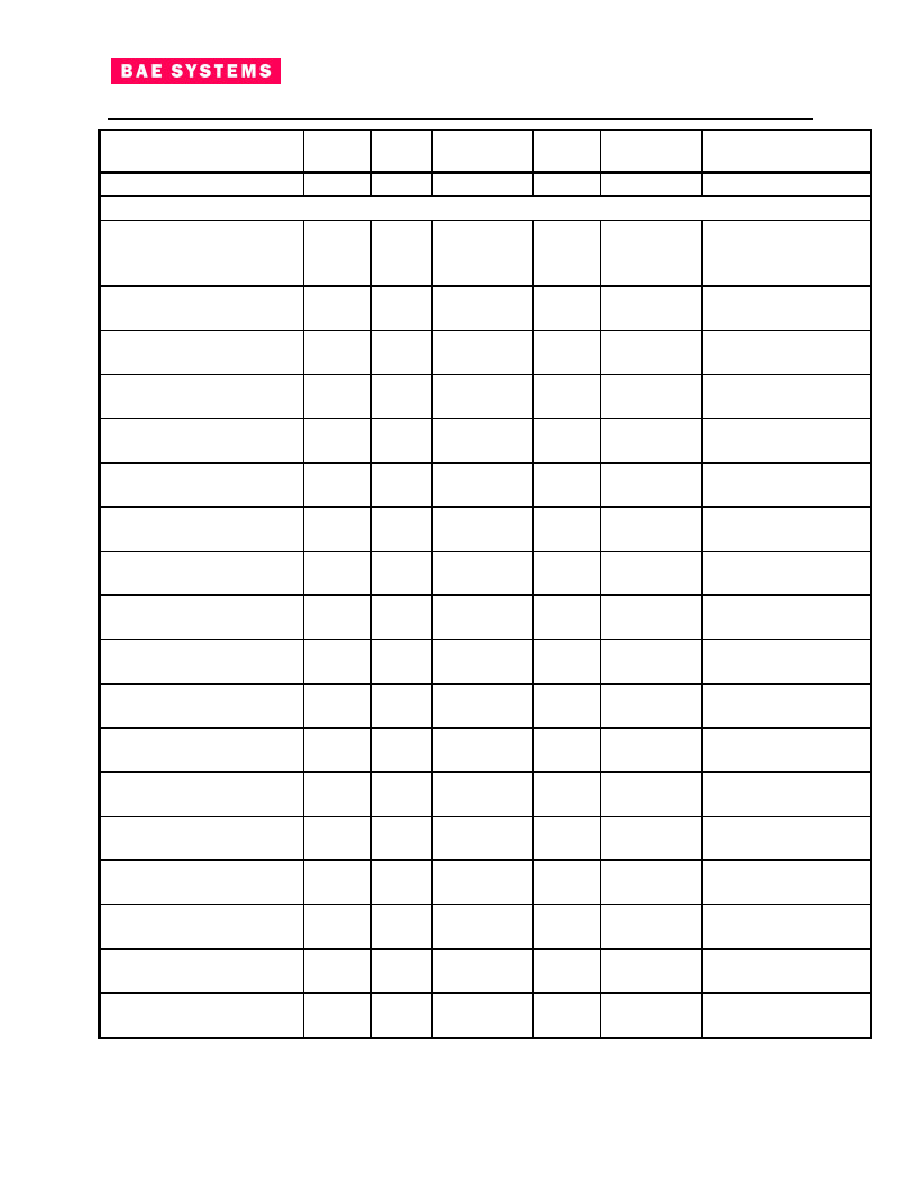

Table 5 - CompactPCI J1 Connector Signals

PIN

A

B

C

D

E

25

5V

REQ64#

ENUM# -

PID20

3.3V

5V

24

AD1

5V

V(I/O)

AD0

ACK64#

23

3.3V

AD4

AD3

5V

AD2

22

AD7

GND

3.3V

AD6

AD5

21

3.3V

AD9

AD8

GND

C/BE0#

20

AD12

GND

V(I/O)

AD11

AD10

19

3.3V

AD15

AD14

GND

AD13

18

SERR#

GND

3.3V

PAR

C/BE1#

17

3.3V

SDONE

SBO#

GND

PERR#

16

DEVSEL#

GND

V(I/O)

STOP#

LOCK#

15

3.3V

FRAME#

IRDY#

GND

TRDY#

12-14

KEY AREA

11

AD18

AD17

AD16

GND

C/BE2#

10

AD21

GND

3.3V

AD20

AD19

9

C/BE3#

IDSEL

AD23

GND

AD22

8

AD26

GND

V(I/O)

AD25

AD24

18

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

PIN

A

B

C

D

E

7

AD30

AD29

AD28

GND

AD27

6

REQ#

GND

3.3V

CLK

AD31

5

BRSV

RDY_PARITY

RST#

GND

GNT#

4

BRSV

GND

V(I/O)

INTP

-PID14

INTS

-PID15

3

INTA# -

PID16 -

UART_OUT2

INTB# -

PID17

INTC# -

PID28

5V

INTD# -

PID29

2

TCK

5V

TMS

TDO

TDI

1

5V

-12V

TRST_L

+12V

5V

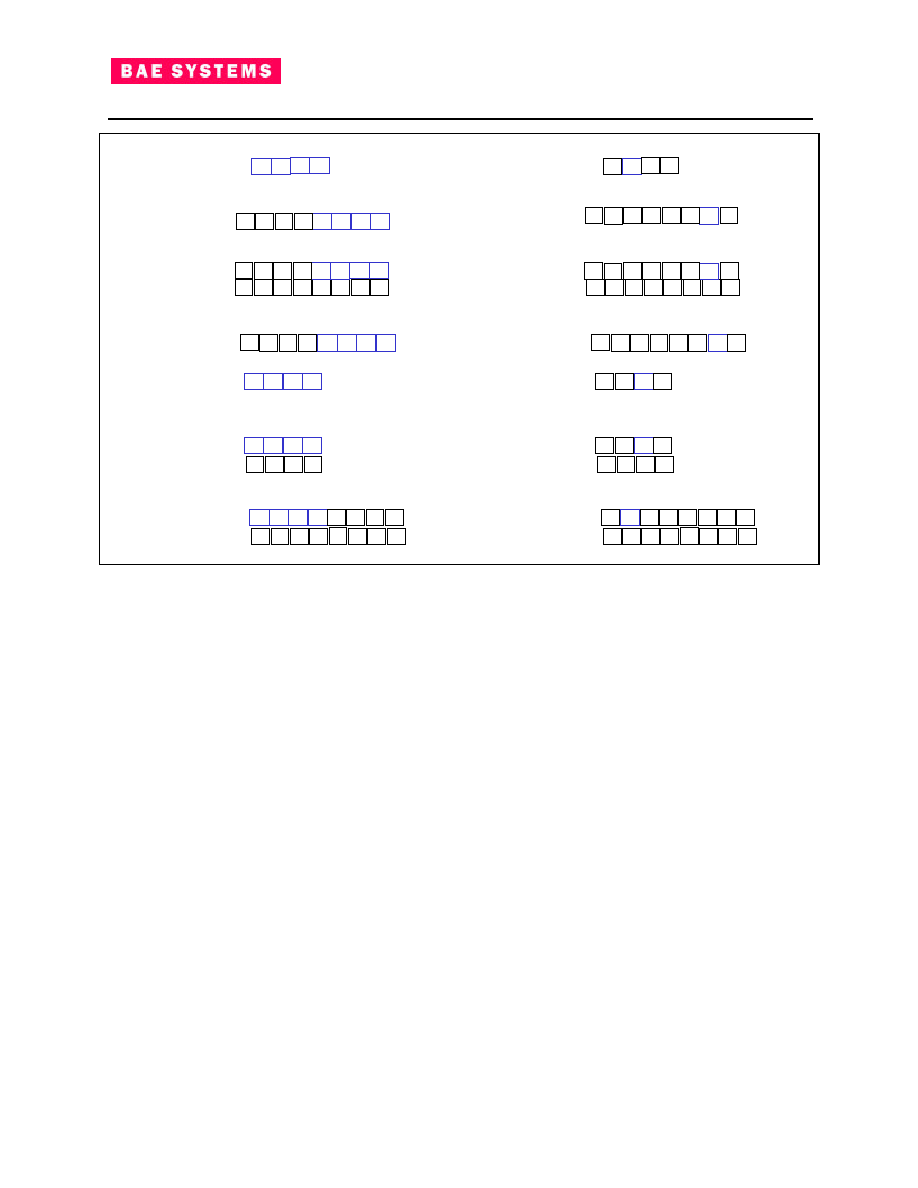

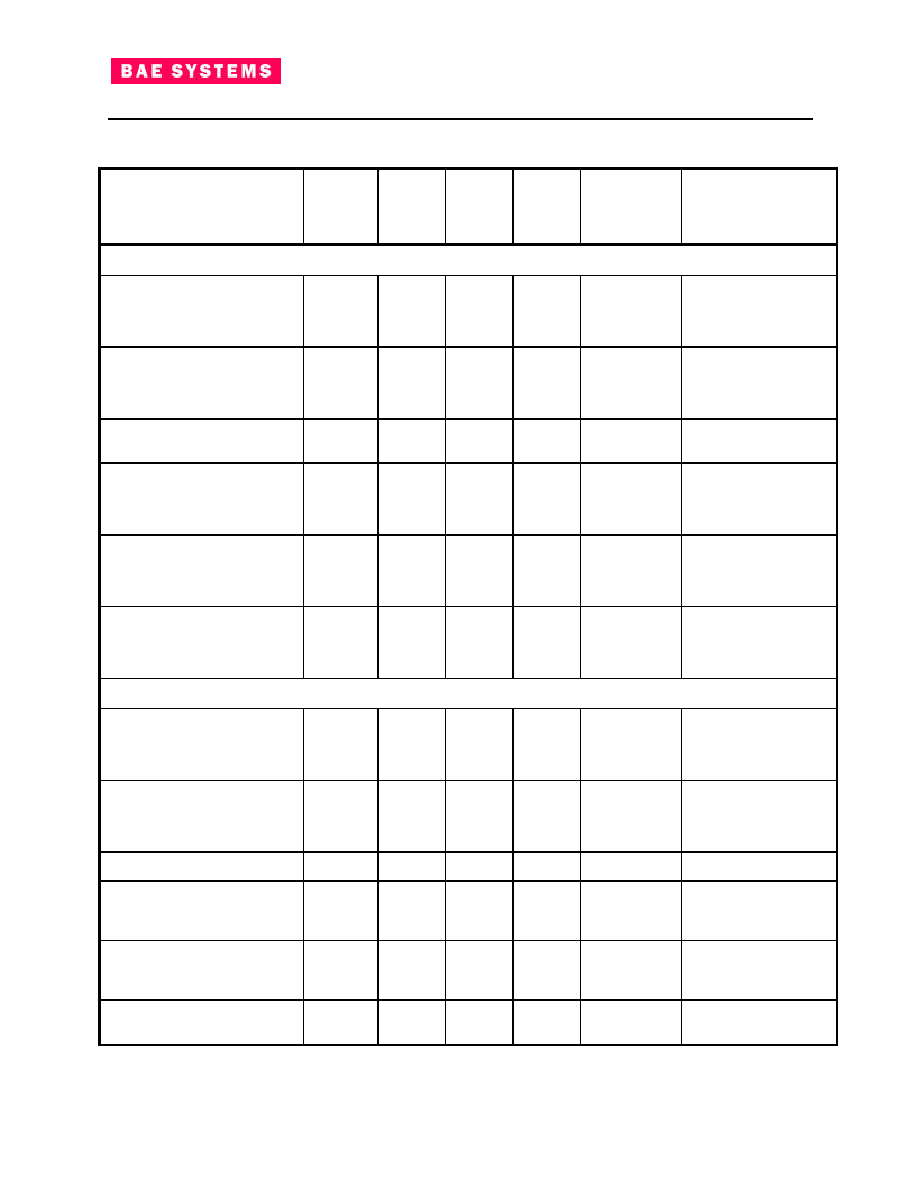

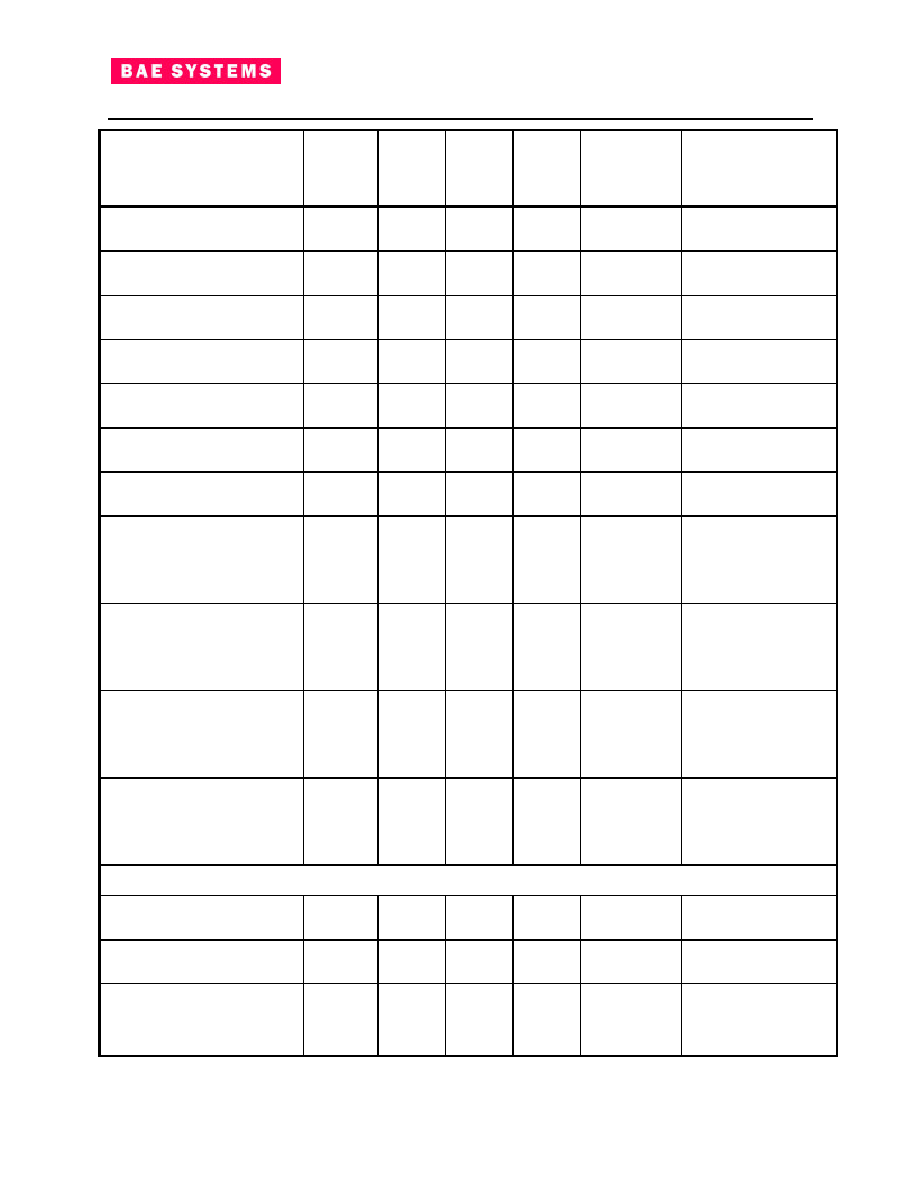

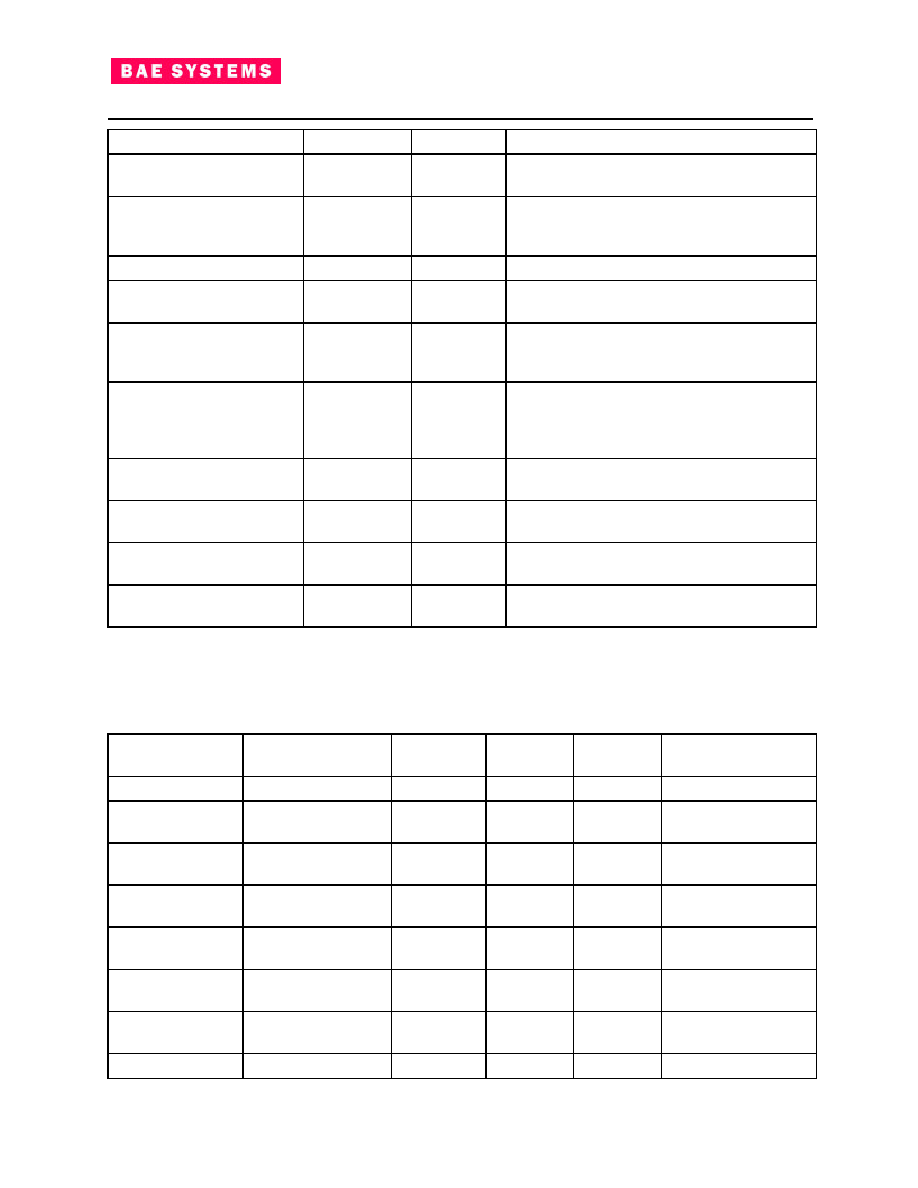

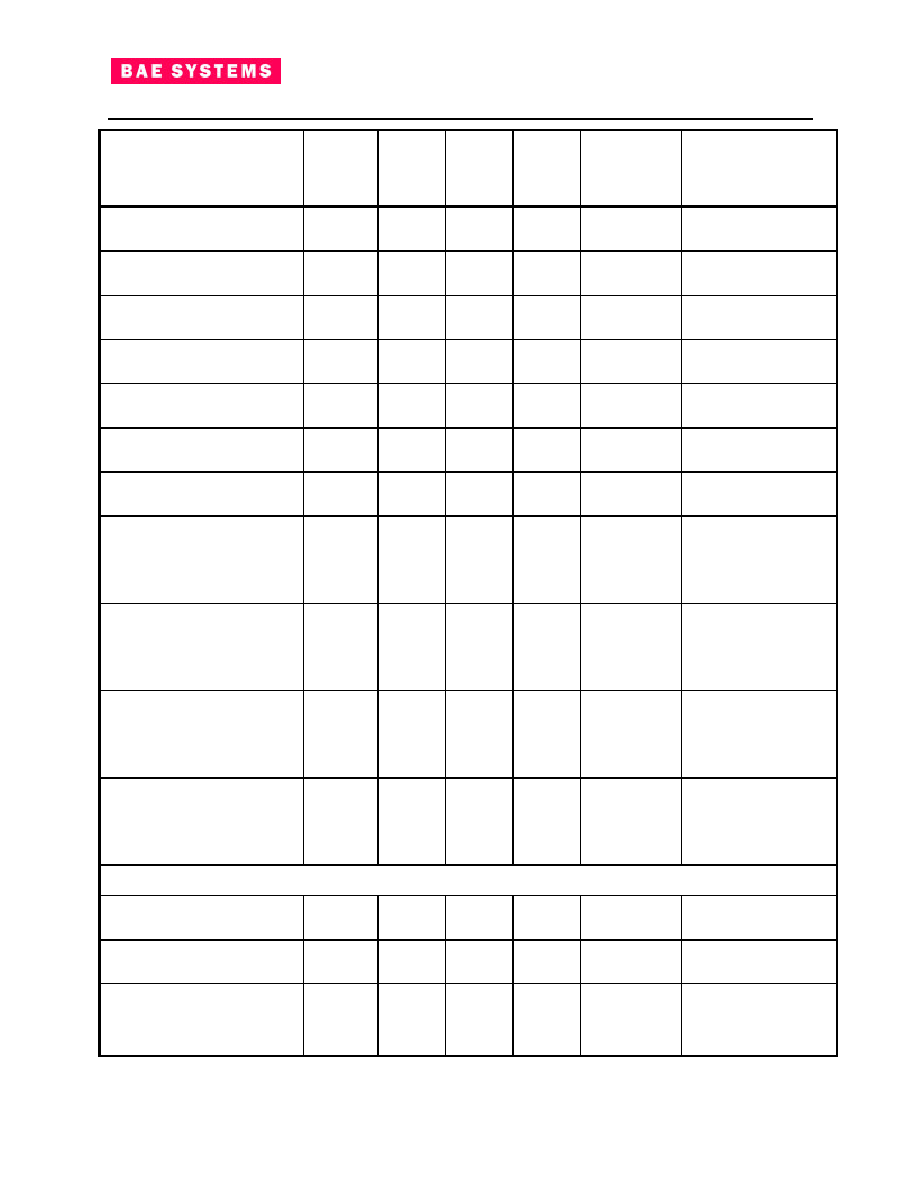

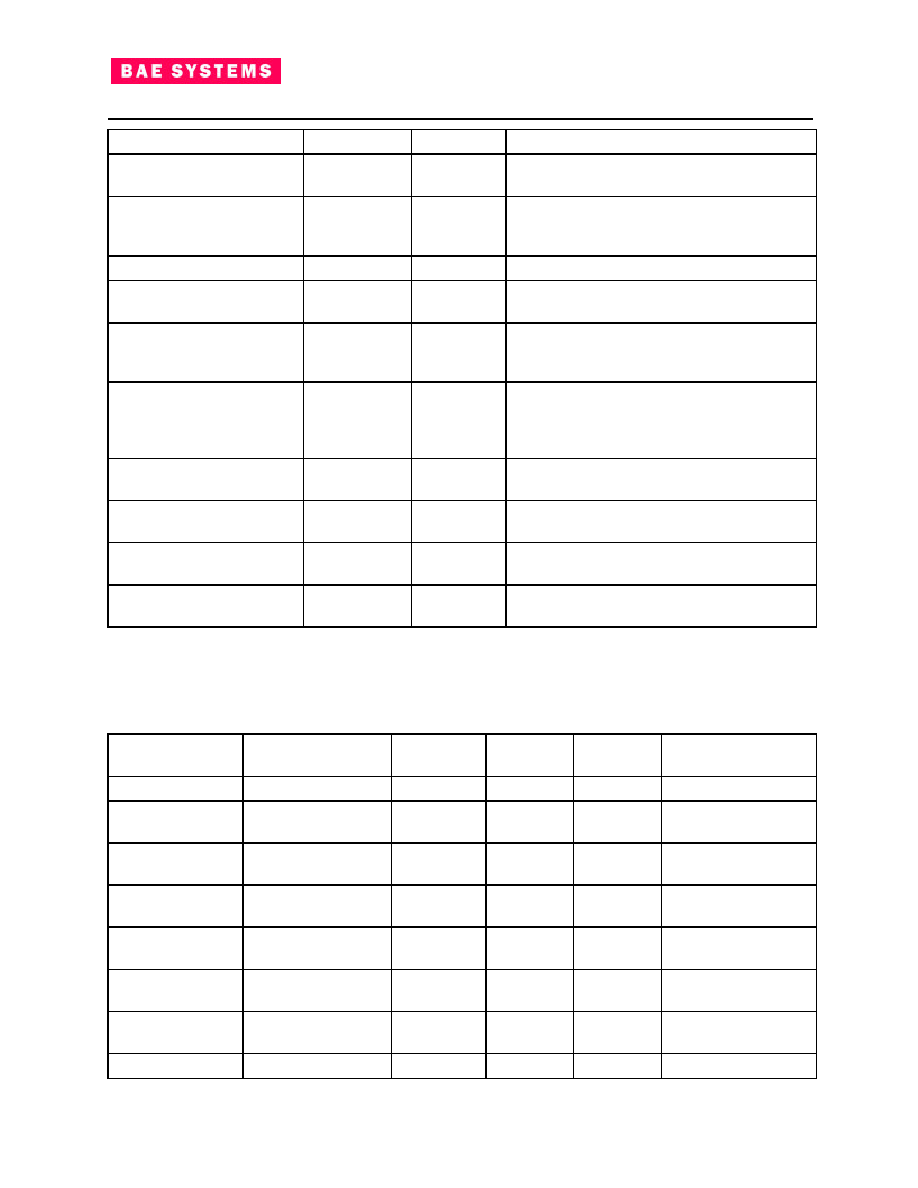

3.11.2 J2 Connector Pin Assignments

The J2 connector provides the additional PCI signals for the resource controller and all user-defined pins

to the backpanel.

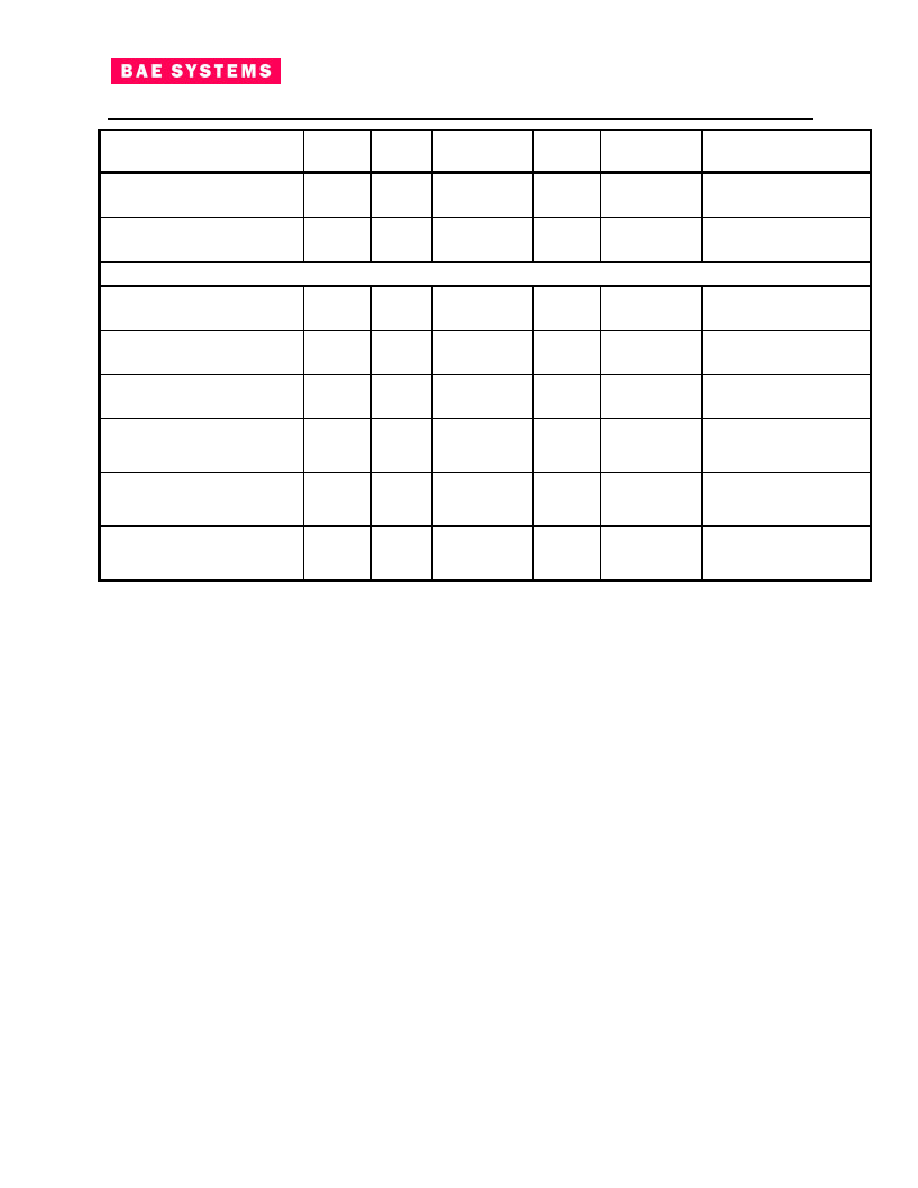

Table 6 - CompactPCI J2 Connector Pinouts

PIN

A

B

C

D

E

22

GA4

GA3

GA2

GA1

GA0

21

CLK6

GND

CLK7

GAP

JTMS_MSTR_E

N

20

CLK5

GND

UART_RTS_L

GND

UART_CTS_L

19

GND

GND

RSV

UART_RX_DAT

UART_TX_DAT

18

BRSV

I2C_1

I2C_0

GND

NMI

17

BRSV

GND

PRST#

REQ6#

GNT6#

16

ROM_ON_PCI

CHAS_GND_0

DEG# -

PID18

GND

CHAS_GND_1

15

BRSV

GND

FAL# -

PID19

REQ5#

GNT5#

14

B64

B64

PID31

GND

PID30

13

B64

GND

V(I/O)

PID08

PID00

12

UART_OUT1

B64

PID25

GND

PID01

11

B64

GND

V(I/O)

PID09

PID02

10

B64

B64

PID26

GND

PID03

9

B64

GND

V(I/O)

PID10

PID04

8

B64

PID21

PID27

GND

PID05

7

B64

GND

V(I/O)

PID11

PID06

19

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

PIN

A

B

C

D

E

6

B64

PID22

PID24

GND

PID07

5

B64

GND

V(I/O)

B64

PID12

4

V(I/O)

POR_N

PID23

GND

PID13

3

CLK4

GND

GNT3

REQ4#

GNT4#

2

CLK2

CLK3

SYSEN#

GNT2#

REQ3#

1

CLK1

GND

REQ1#

GNT1#

REQ2#

3.12 CompactPCI Slot Guidelines for Multiprocessor Configurations

The Power PCI Bridge chip designed by BAE SYSTEMS and used on the RAD750 processor card is

enhanced over the commercially available MPC-106 chip to allow the multiple processor cards to be

combined on a single compact PCI backpanel. Cards constructed using the Power PCI Bridge chip can

be used in either a system controller or non-system controller slot without any changes being required to

the card design.

The Power PCI chip on the RAD750 processor board uses the SYS_EN signal from the compact PCI

backpanel to determine if it is to act as the system controller for the backpanel. When this signal is active

(i.e., the card is plugged into slot 0 of a standard CompactPCI backpanel), the Power PCI bridge chip on

the board will act as the controller (arbiter). When acting as controller, the Power PCI will supply and then

release (under SW control) the PCI reset signal to the rest of the backpanel.

Each Power PCI chip contains a set of two Base Address Registers (BARs) which are used as follows:

∑

BAR1 - defines the base address for system memory. Its size is selectable by external chip I/O

pins as 2 GByte, 1 GByte, 512 MByte, or 256Mbyte. Furthermore, an internal Power PCI

configuration register (SM_SIZE) is used to determine the number of 8 KByte pages that are

mapped to the PCI bus. The number of 8K pages ranges from 1 to 32768.

∑

BAR2 - defines the base address for the internally architected Power PCI registers. It defines a 1

MByte PCI Memory region. Write access to the lower half of the BAR2 memory region from the

PCI Bus is enabled by the BAR2_WE bit stored in the PCI configuration space.

The following is an example of the use of the BARs:

∑

BAR1 = 0x'1000 0000' with a window size of 256MB.

PCI requests between 0x'1000 0000' and 0x'1FFF FFFF' are translated to PCI memory (local

memory) requests between 0 and 0x'0FFF FFFF'

∑

BAR2 = 0x'2000 0000'

PCI requests between 0x'2000 0000' and 0x'200F FFFF' are translated to PCI memory

(Power PCI register) requests between 0x'BD80 0000' and 0x'BF8F FFFF'.

The BARs must be set in order to access the Power PCI as a target. Both BARs will reset to a base

address of zero so they must be set to avoid conflicts. The local processor may set the BARs or, once

PCI Reset is removed, other PCI masters may set the BARs using configuration cycles.

Power PCI Bridge chips can be used on designs, such as memory cards, which do not contain a

processor. In these applications, an outside PCI master would generally be used to supply configuration

cycles to configure the BAR registers to the required address range.

20

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

3.13 Compatibility with RAD6000

The RAD750 processor card is fully compatible with the previous RAD6000 based product set. The

Power PCI Bridge to the PCI bus is backward compatible to the PCI version 2.0 bus used in the

RAD6000 family designs. Any required endian conversions can be controlled by software through the

endian conversion hardware in the Power PCI bridge.

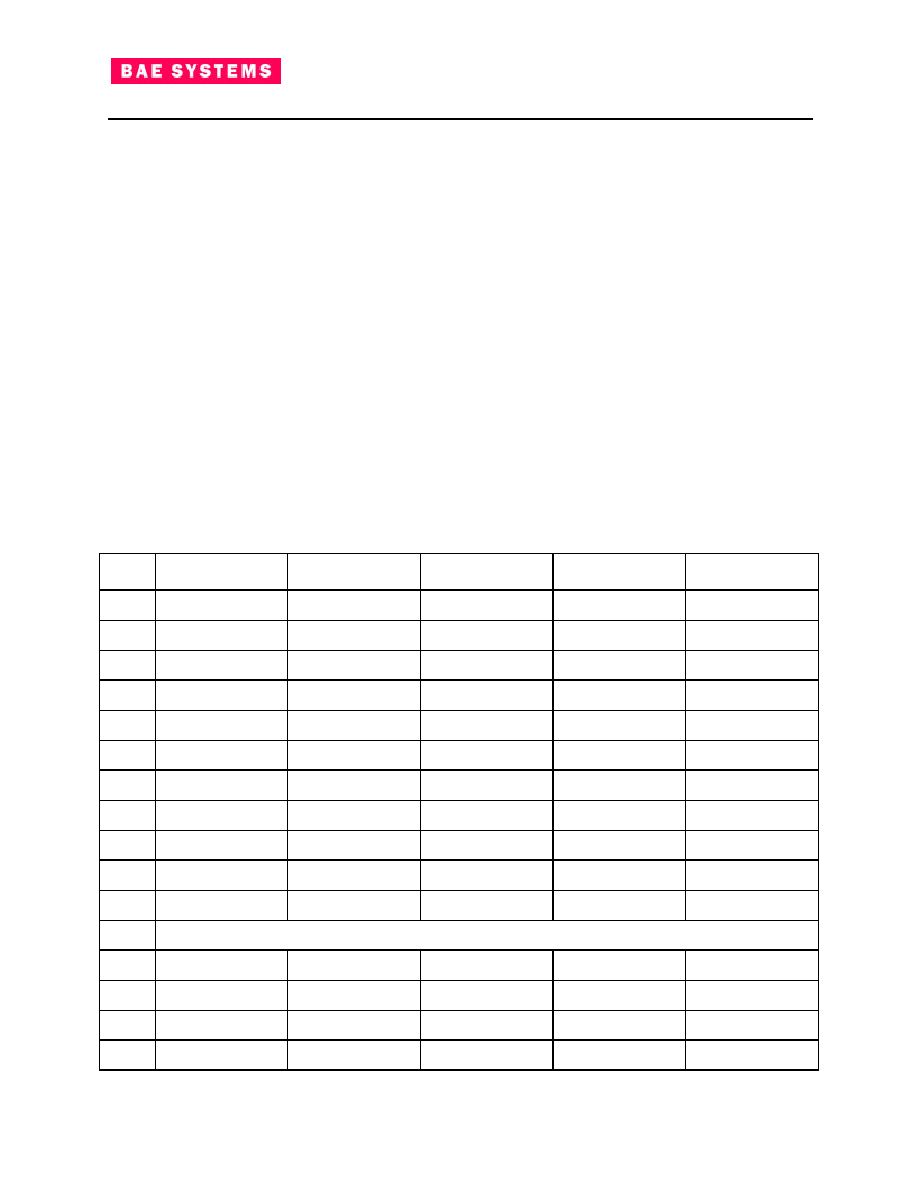

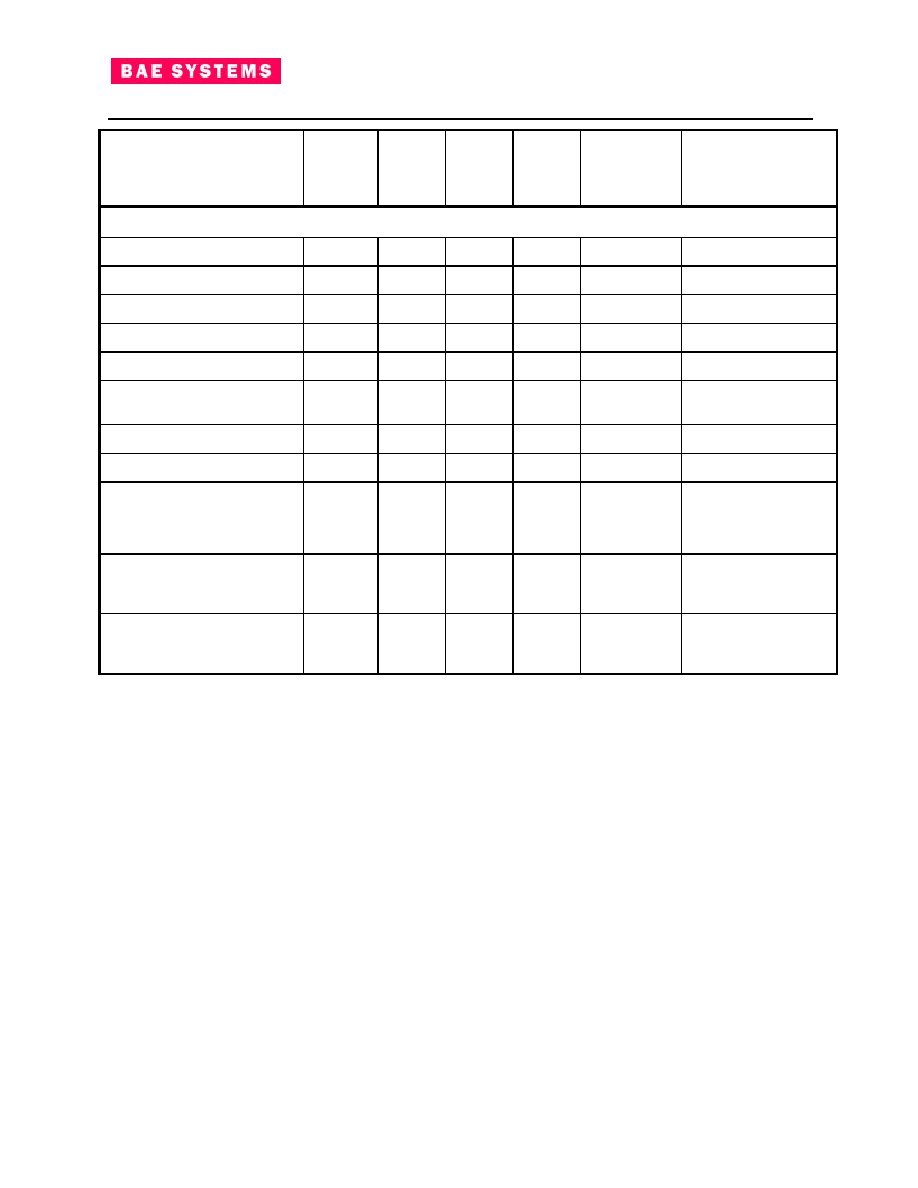

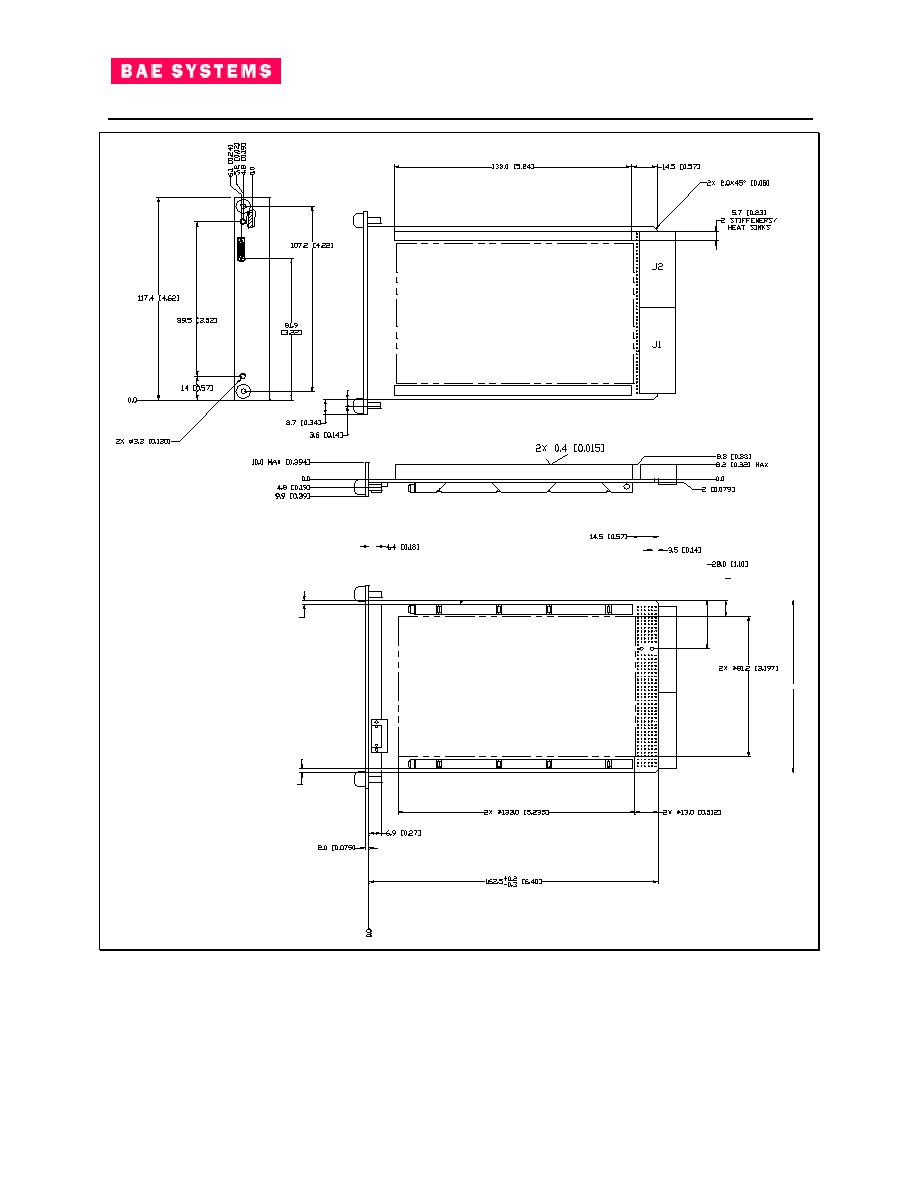

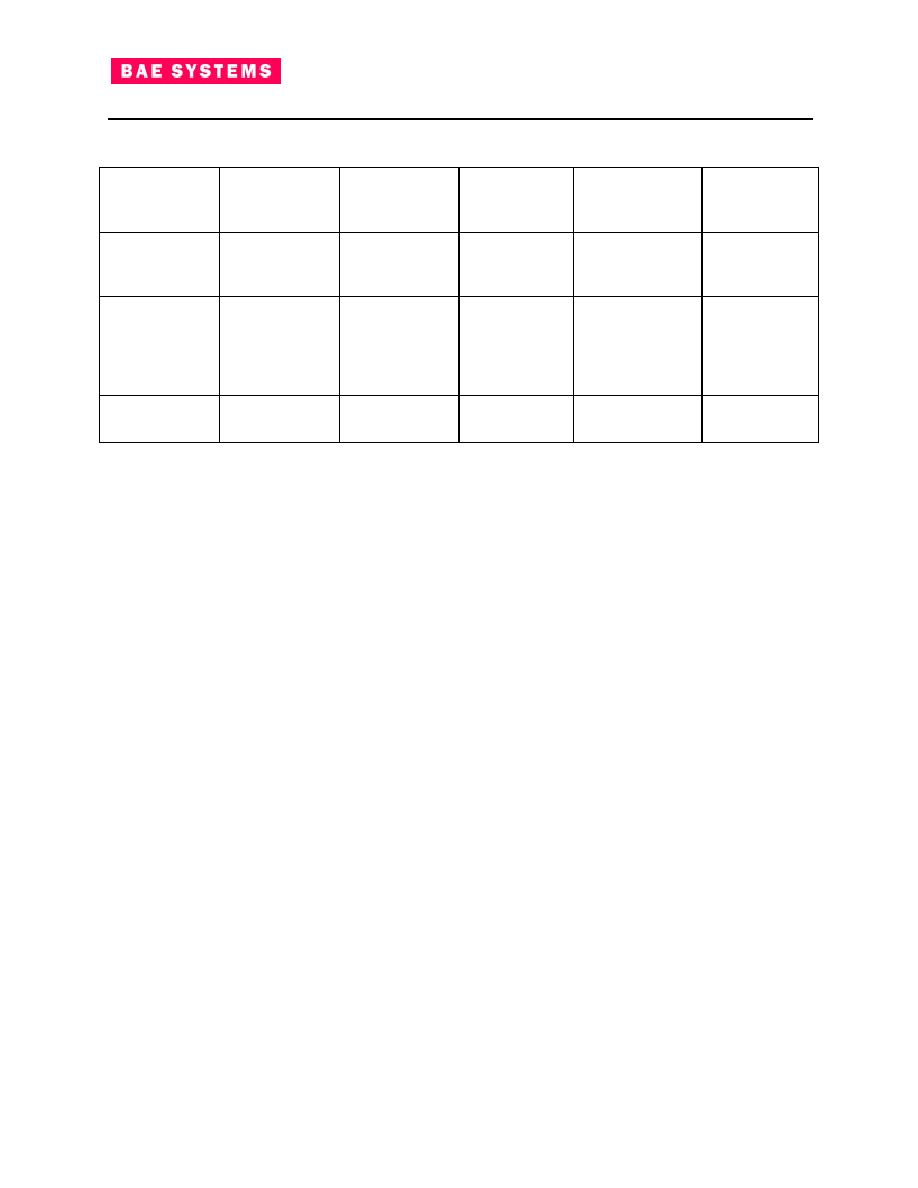

3.14 Front Panel Connector

The J7 Front Panel connector provides all external UART, debug and test signals that are brought out to

the front panel. The front panel connector is wired as shown in Table 7.

The J7 front panel connector is a Nanonics Dualobe two row 25 pin connector.

3.14.1 J7 Pin Assignments

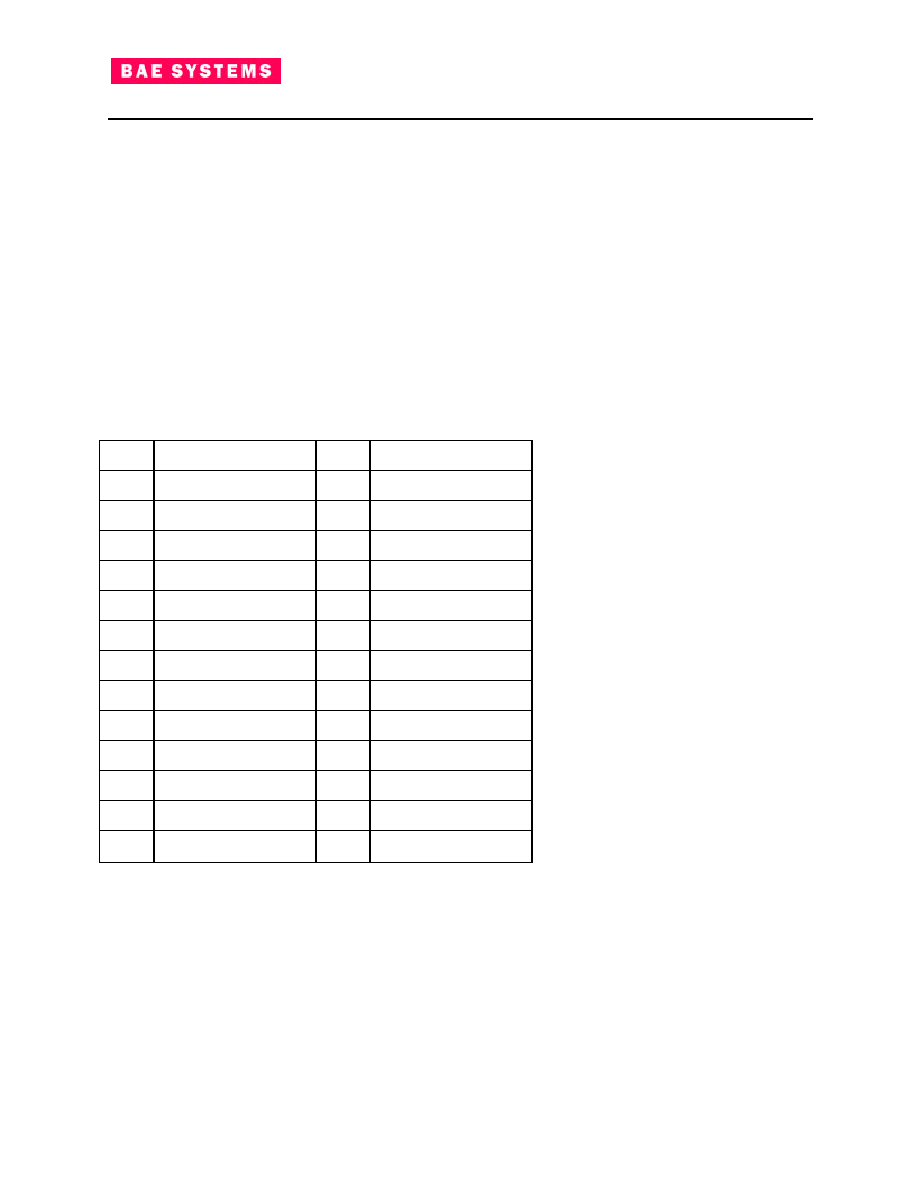

Table 7 - Front Panel Connector J7 Pin Assignments

PIN

Signal

PIN

Signal

1

JTM_TDO

2

JTM_TRST_L

3

JTM_TDI

4

JTM_POWER

5

JTM_TCLK

6

JTM_SRESET_L

7

JTM_TMS

8

JTM_RESET_L

9

CPU_CKSTP_L

10

JT7_MSTR_EN_IN

11

GND

12

GND

13

JTS_TDI

14

UART_RX_DATA

15

JTS_TDO

16

UART_TX_DATA

17

JTS_TMS

18

UART_RTS_L

19

JTS_TCLK

20

UART_CTS_L

21

JTS_PROBE_PR_L

22

JTS_TRST_L

23

GND

24

X_SYS_OSC_SEL_L

25

X_SYS_OSC

21

Document #: 234A533

RAD750 3U CompactPCI

Hardware Users Manual

4 Hardware / Electrical

This section describes the electrical and functional characteristics of the RAD750 board. Included are

descriptions of the RAD750, memory maps, register descriptions, etc. Details in the register section are

predominantly about the Power PCI chip.

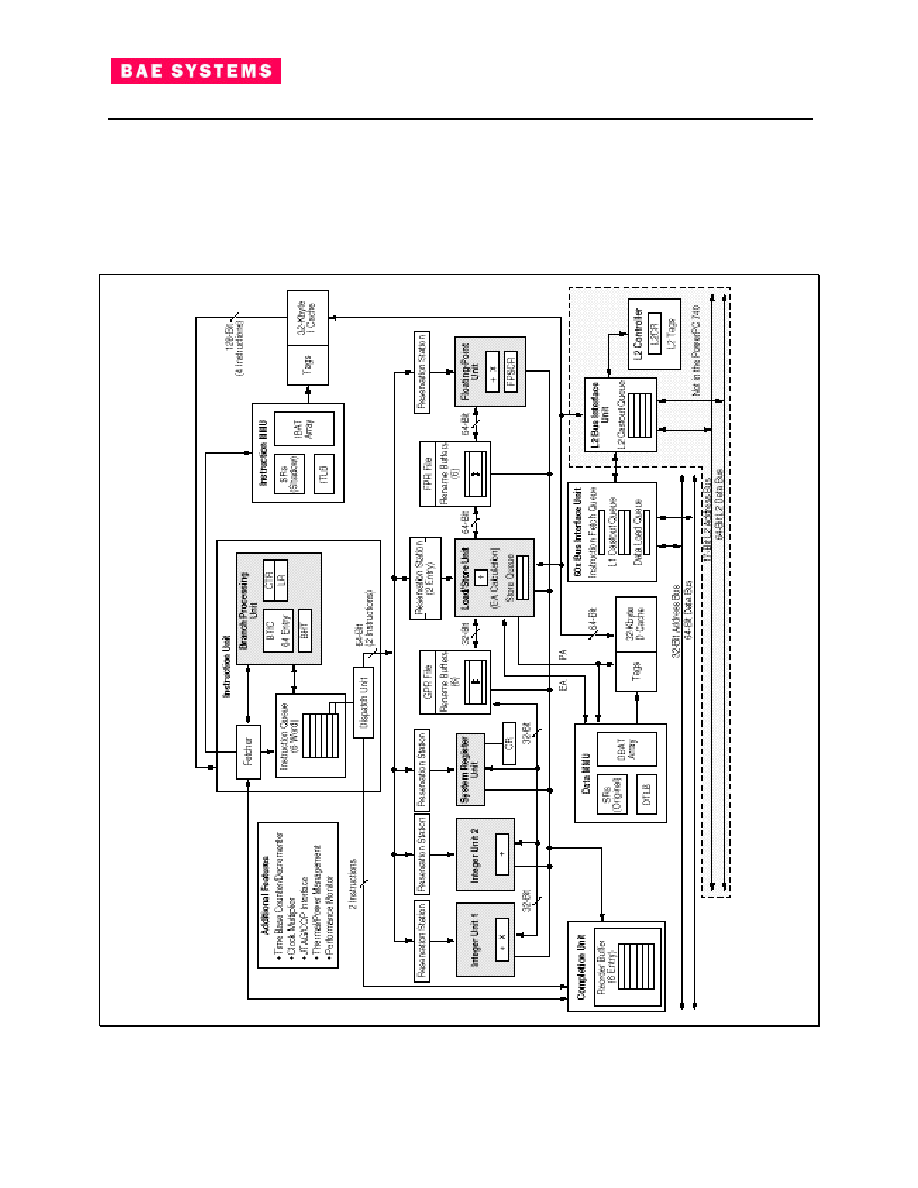

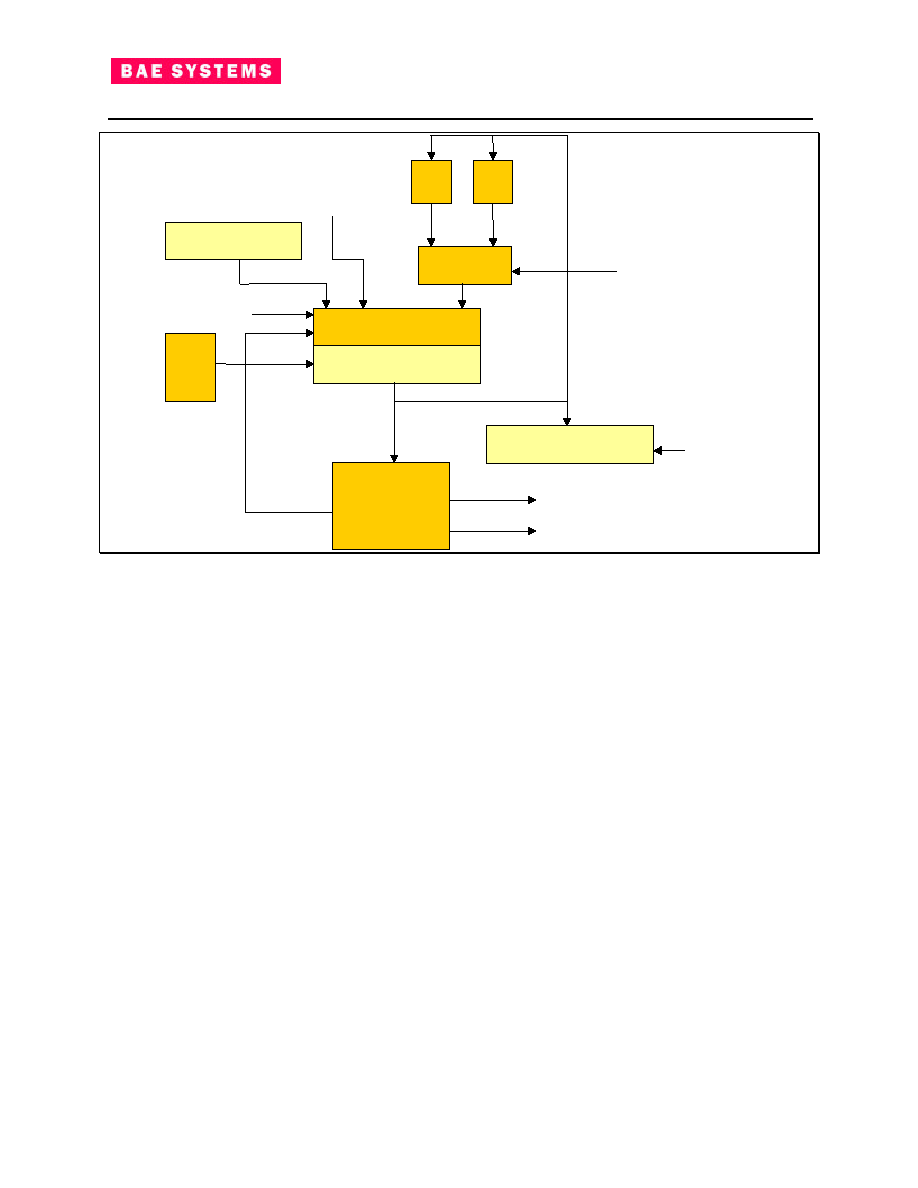

4.1 RAD750

The RAD750 is functionally equivalent to the PowerPC 750. Users should refer to Section 8.1 for

information on the PowerPC Users Manual.

This section briefly describes the features and general operation of the RAD750 and provides a block

diagram showing major functional units. The RAD750 is an implementation of the PowerPC

microprocessor family of reduced instruction set computer (RISC) microprocessors. The RAD750

implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses,

integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits. The RAD750 is a

superscalar processor that can complete two instructions simultaneously. It incorporates the following six

execution units:

∑

Floating-point unit (FPU)

∑

Branch processing unit (BPU)

∑

System register unit (SRU)

∑

Load/store unit (LSU)

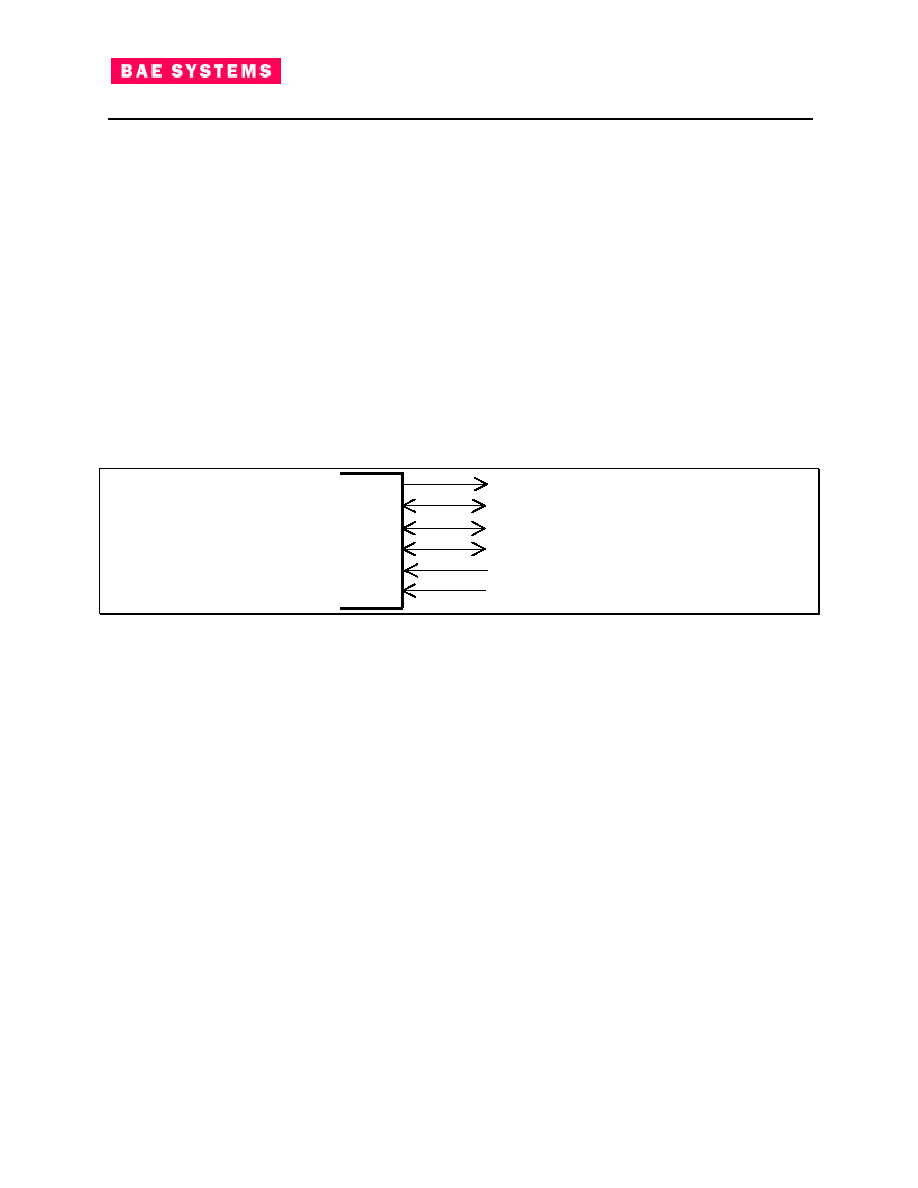

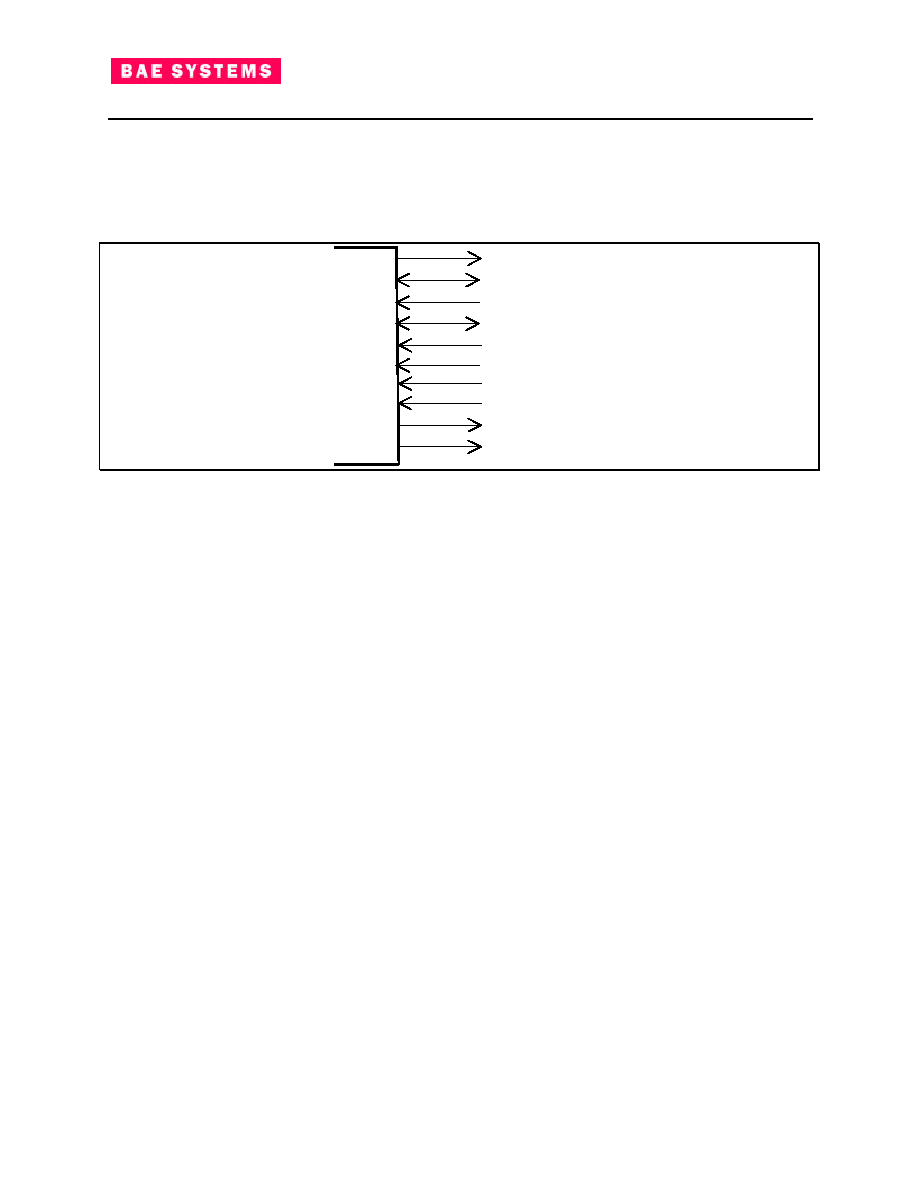

∑