P R O D U C T B R I E F

S1

92

33

Description

The S19233 is a fully integrated low power dual

CDR device with Electronic Dispersion

Compensation (EDC). It is suitable for use in 10

GbE/10G FC/SONET/SDH PMD modules, such as

the XFP MSA modules. This device can be used

to compensate channel impairments caused by

either single mode fiber up to 120 km or FR-4

copper medium over 24". Integrated in this

device on the receive optical side, an AGC

amplifier with offset cancellation circuitry, EDC/

Equalization with control circuitry, and CDR. On

the transmit electrical side the S19233 also has

an equalization circuit, and CDR that reshapes

the data after up to 24" of transmission over

copper on FR-4 PWB material. The low-jitter

CML interfaces guarantees compliance with the

bit error rate requirements of the Telcordia and

ITU-T standards. The S19233 is packaged in a 6 x

6 mm

2

PBGA, offering designers a small

package outline.

Value Proposition - Design multiple XFP

modules ranging from 2 km to 120 km link with

one footprint. The S19233 is pin compatible to

the lower cost 10G Dual CDR S19256 (no EDC).

S19256: 2 km-30 km;

S19233: 2 km-120 km

Overview

The S19233 can be used to implement the front

end of SONET/SDH/FEC/10GbE/FC/G.709

equipment which consists primarily of the serial

transmit interface and the serial receive

interface. The system timing circuitry consists of

a high-speed phase detector, clock and data

recovery unit and equalization circuitry. The

device utilizes on-chip clock recovery PLL

components that allow the use of a slower

external clock reference, 155.52 MHz (or

equivalent FEC/10GbE/10 Gbps FC rate), in

support of existing system clocking schemes.

The EDC function is embedded in the optical

receive side. It provides control to compensate

chromatic dispersion in different fiber links. On

the transmitter side, an equalizer is integrated in

the receive front end to reshape the data after

transmission over FR-4. This enables low bit

error rate and transmission over longer trace

length.

The low-jitter, 1-bit, CML interfaces guarantee

compliance with the bit-error rate requirements

of the Telcordia and ITU-T standards. The

10 Gbps serial electrical interface specifications

are compliant with the XFI as specified in the

XFP MSA module specification. The high speed

serial input and output can be connected to the

AMCC SerDes (S19235 or S19237) across 60 cm

(24") of improved FR-4 material or across 40 cm

of standard FR-4 with one connector.

Features

∑ Complies with ITU-T specifications, 50 mUI

pp

max. jitter generation (50 KHz - 80 MHz)

∑ Complies with XFP MSA Specifications

∑ 25 mUI

pp

Jitter Generation

∑ CML serial input sensitivity at 5 mV

pp

Diff.

∑ Dual CDR - 9.95 to 11.32 Gbps operation

∑ Superior Crosstalk Isolation

∑ Electronic Dispersion Compensation (EDC)

Optimized for 0 to 100 Km SMF with 2 dB dis-

persion penalty

∑ Low power EDC ideal for Power Level 2 XFP

modules

∑ Suitable for low Optical Signal to Noise Ratio

(OSNR) environments

∑ Automatic Threshold Adjust

∑ External threshold & Phase Adjust

∑ AGC embedded equalizer

∑ LOS Function - Compliant to GR-253

∑ Integrated equalizer that support over 24" FR-

4 on Transmitter Electrical Side

∑ Transmitter (Optical Side) - CDR

∑ Lock detect indication

∑ 650 mW Typical Power

∑ -40 to 85∞C operation

∑ CMOS 0.13 Micron Technology

∑ 1.8 and 3.3 Volt Power Supply

∑ 6 x 6 mm

2

PBGA package with RoHS compli-

ant lead free option

∑ ESD - 1500 V, 500 V High Speed Inputs

Applications

∑ 10 G Fibre Channel and Ethernet Designs

∑ 10 GbE with FEC

∑ 10 G SONET/SDH/FEC Designs

∑ SONET/SDH Test Equipment

∑ SONET/SDH/FEC DWDM Equipment

∑ XFP MSA Modules

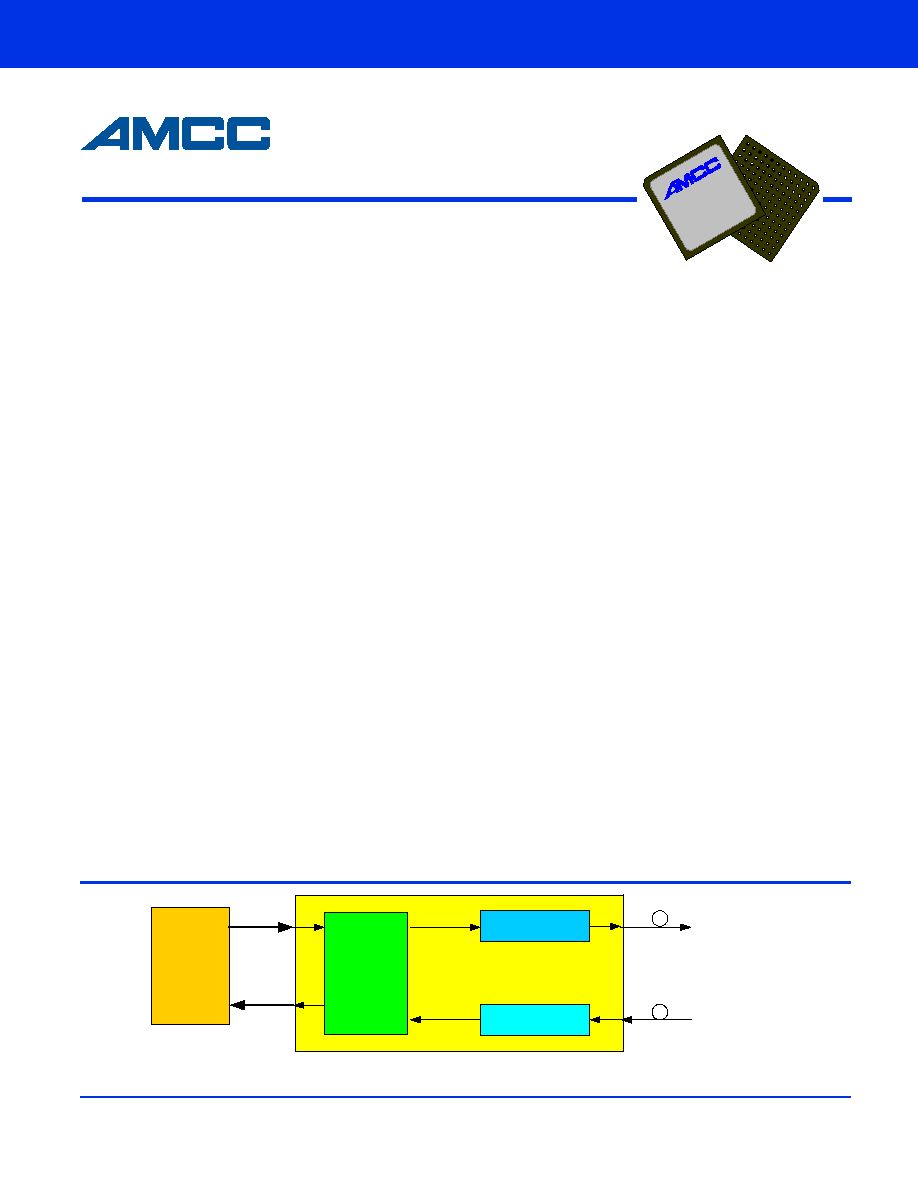

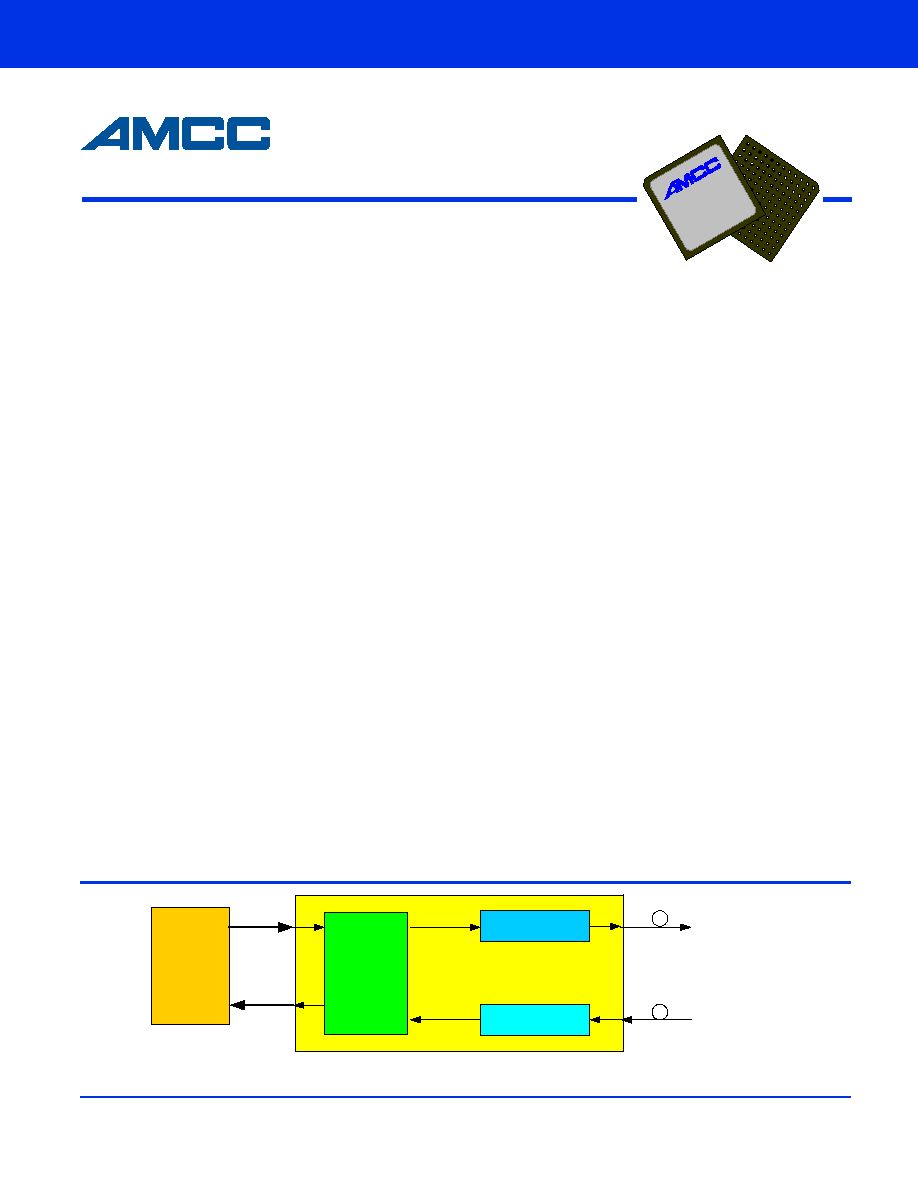

S19233

10 G Ethernet/Fibre Channel/SONET/SDH Dual CDR

System Block Diagram with the S19233

OC-192/10GE/10FC

AMCC

S19235/37

XFP Module

10 Gbps Line Card

XFI

TOSA

ROSA

AMCC

S19233

Dual CDR

S19233

S P E C I F I C AT I O N S

6290 Sequence Dr.

San Diego, CA 92121

P 858 450 9333

F 858 450 9885

www.amcc.com

For technical support, please call 1-800-840-6055 or 858-535-6517, or email support@amcc.com.

AMCC reserves the right to make changes to its products, its datasheets, or related documentation, without notice and warrants its products solely pursuant to its terms and

conditions of sale, only to substantially comply with the latest available datasheet. Please consult AMCC's Term and Conditions of Sale for its warranties and other terms, conditions

and limitations. AMCC may discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify,

before placing orders, that the information is current. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does

it convey any license under its patent rights nor the rights of others. AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR

OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation. PowerPC and the PowerPC logo are registered trademarks of IBM Corporation. All other trademarks are the

property of their respective holders. Copyright © 2006 Applied Micro Circuits Corporation. All Rights Reserved.

S19233_PB1592_v1.02_20061031

AMCC Suggested Interface Devices

Transmitter Side Operations

∑ 1-bit serial data input

∑ Equalization to compensate for FR-4

∑ Threshold and Offset cancellation adjust

∑ Clock and Data recovery

∑ Data retime

Serial data output

∑ Receiver Side Operations

∑ Serial input with AGC (Equalization)

∑ 10 mV

pp

Differential Sensitivity with threshold adjust

∑ Loss of signal detection

∑ Clock and Data recovery

∑ Serial data output

Common Operations

∑ Optical and Electrical Loopbacks

∑ Power Down CDR

∑ Squelch

∑ Polarity Invert

S19235

SFI4 Phase 1

SONET/SDH STS-192/10 Gig Ethernet CMOS Transceiver with ISI Compen-

sation

S19237

SFI4 Phase 1

SONET/SDH STS-192/10 Gig Ethernet CMOS Transceiver with ISI Compen-

sation