STK10C68

September 2003

2

Document Control # ML0006 rev 0.1

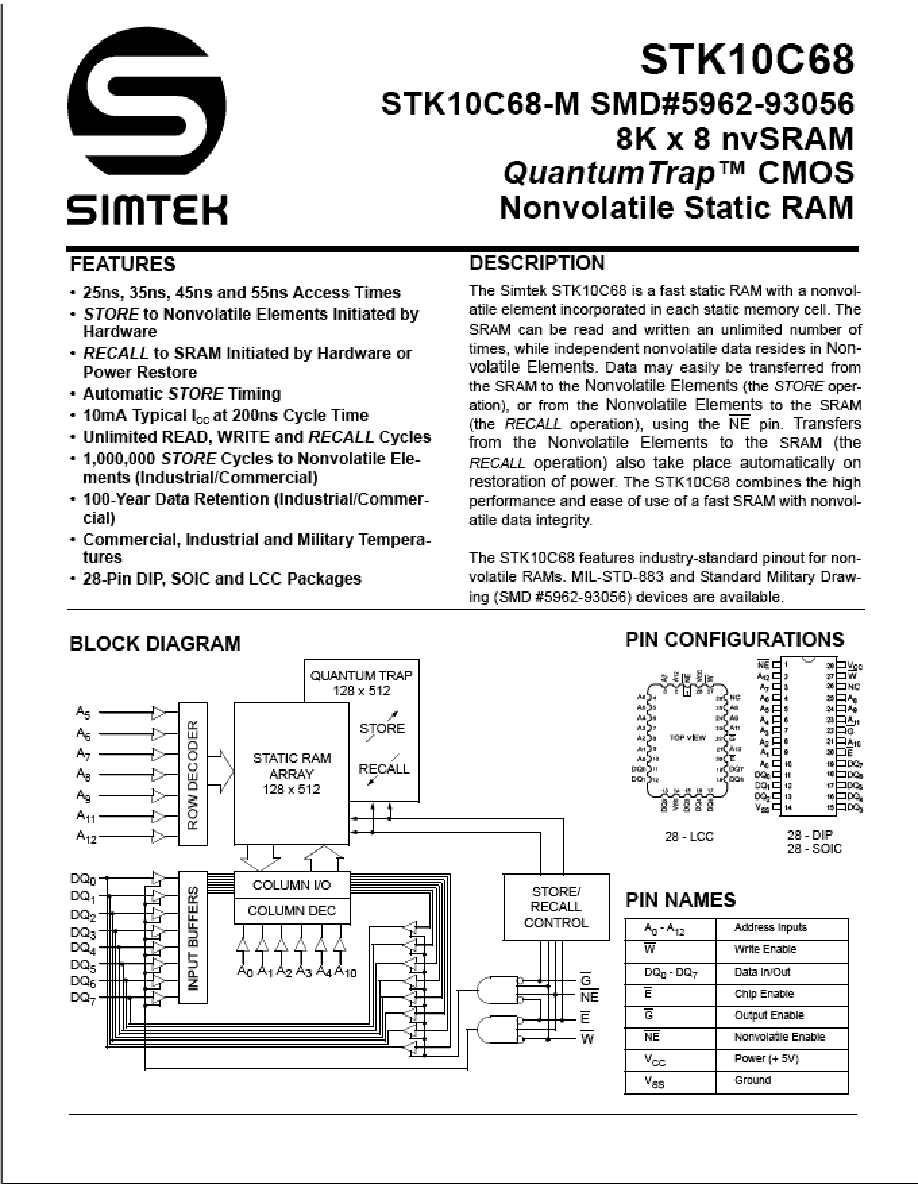

ABSOLUTE MAXIMUM RATINGS

a

Voltage on Input Relative to Ground . . . . . . . . . . . . . .0.5V to 7.0V

Voltage on Input Relative to V

SS

. . . . . . . . . . 0.6V to (V

CC

+ 0.5V)

Voltage on DQ

0-7

. . . . . . . . . . . . . . . . . . . . . . 0.5V to (V

CC

+ 0.5V)

Temperature under Bias . . . . . . . . . . . . . . . . . . . . . 55

°

C to 125

°

C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . 65

°

C to 150

°

C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

DC Output Current (1 output at a time, 1s duration) . . . . . . . . 15mA

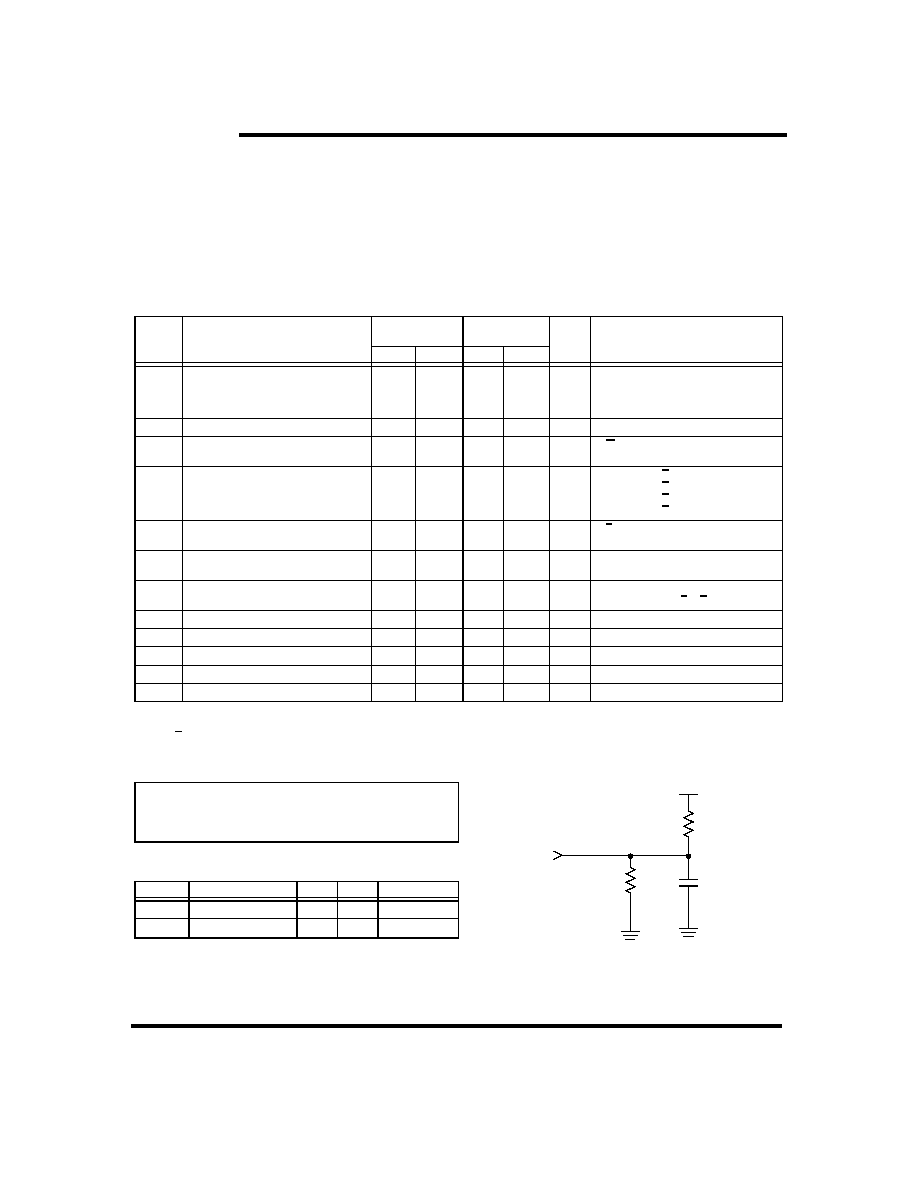

DC CHARACTERISTICS

(V

CC

= 5.0V

±

10%)

Note b: I

CC1

and I

CC3

are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

Note c: I

CC2

is the average current required for the duration of the

STORE

cycle (t

STORE

) .

Note d: E

V

IH

will not produce standby current levels until any nonvolatile cycle in progress has timed out.

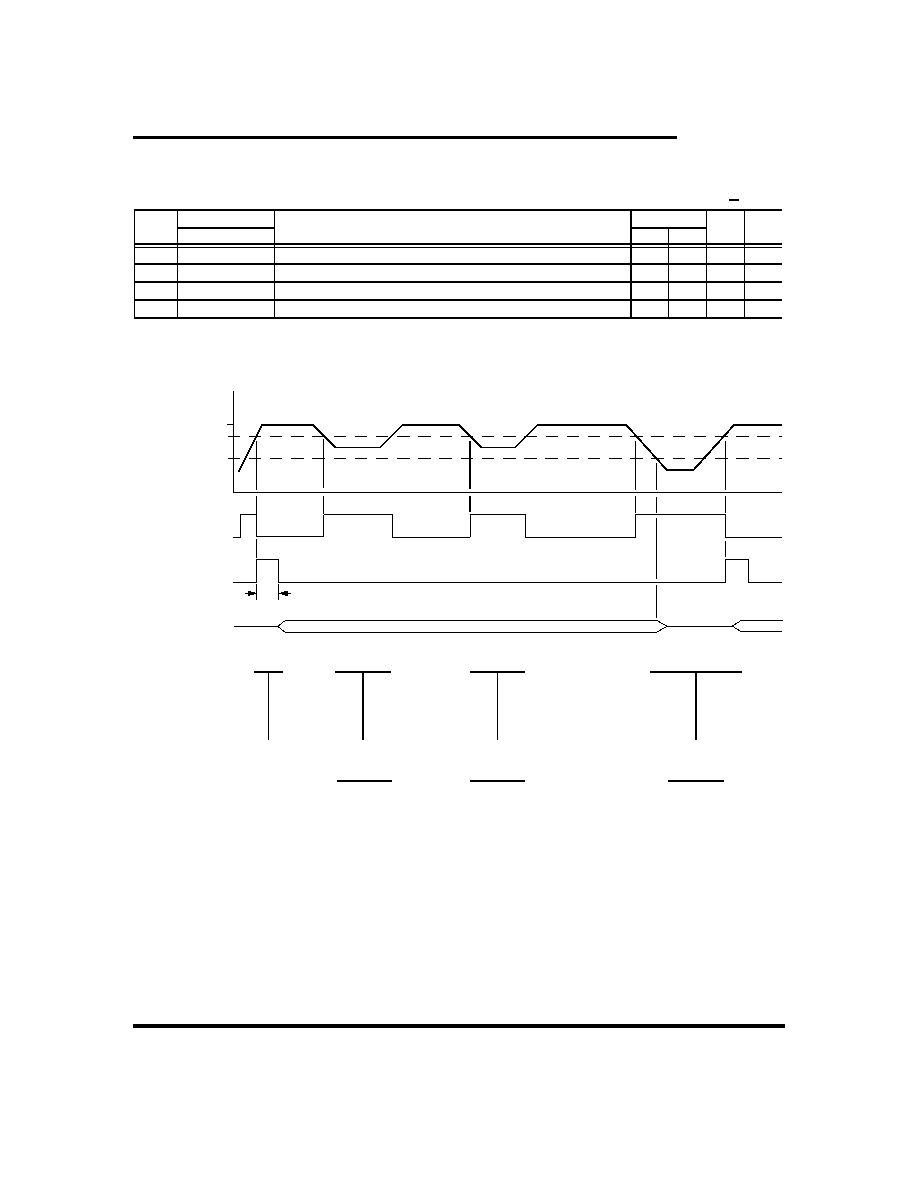

AC TEST CONDITIONS

CAPACITANCE

e

(T

A

= 25

°

C, f = 1.0MHz)

Note e: These parameters are guaranteed but not tested.

SYMBOL

PARAMETER

COMMERCIAL

INDUSTRIAL/

MILITARY

UNITS

NOTES

MIN

MAX

MIN

MAX

I

CC1

b

Average V

CC

Current

85

75

65

N/A

90

75

65

55

mA

mA

mA

mA

t

AVAV

= 25ns

t

AVAV

= 35ns

t

AVAV

= 45ns

t

AVAV

= 55ns

I

CC2

c

Average V

CC

Current during STORE

3

3

mA

All Inputs Don't Care, V

CC

= max

I

CC3

b

Average V

CC

Current at t

AVAV

= 200ns

5V, 25°C, Typical

10

10

mA

W

(V

CC

0.2V)

All Others Cycling, CMOS Levels

I

SB1

d

Average

V

CC

Current

(Standby, Cycling TTL Input Levels)

27

23

20

N/A

28

24

21

20

mA

mA

mA

mA

t

AVAV

= 25ns, E

V

IH

t

AVAV

= 35ns, E

V

IH

t

AVAV

= 45ns, E

V

IH

t

AVAV

= 55ns, E

V

IH

I

SB2

d

V

CC

Standby Current

(Standby, Stable CMOS Input Levels)

750

1500

µ

A

E

(V

CC

0.2V)

All Others V

IN

0.2V or

(V

CC

0.2V)

I

ILK

Input Leakage Current

±

1

±

1

µ

A

V

CC

= max

V

IN

= V

SS

to V

CC

I

OLK

Off-State Output Leakage Current

±

5

±

5

µ

A

V

CC

= max

V

IN

= V

SS

to V

CC

, E or G

V

IH

V

IH

Input Logic "1" Voltage

2.2

V

CC

+ .5

2.2

V

CC

+ .5

V

All Inputs

V

IL

Input Logic "0" Voltage

V

SS

.5

0.8

V

SS

.5

0.8

V

All Inputs

V

OH

Note a: Output Logic "1" Voltage

2.4

2.4

V

I

OUT

= 4mA

V

OL

Output Logic "0" Voltage

0.4

0.4

V

I

OUT

= 8mA

T

A

Operating Temperature

0

70

40/-55

85/125

°

C

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to 3V

Input Rise and Fall Times

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5ns

Input and Output Timing Reference Levels . . . . . . . . . . . . . . . 1.5V

Output Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Figure 1

SYMBOL

PARAMETER

MAX

UNITS

CONDITIONS

C

IN

Input Capacitance

8

pF

V = 0 to 3V

C

OUT

Output Capacitance

7

pF

V = 0 to 3V

Figure 1: AC Output Loading

480 Ohms

30 pF

255 Ohms

5.0V

INCLUDING

OUTPUT

SCOPE AND

FIXTURE

Note a: Stresses greater than those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device. This is a

stress rating only, and functional operation of the device at condi-

tions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rat-

ing conditions for extended periods may affect reliability.

STK10C68

September 2003

3

Document Control # ML0006 rev 0.1

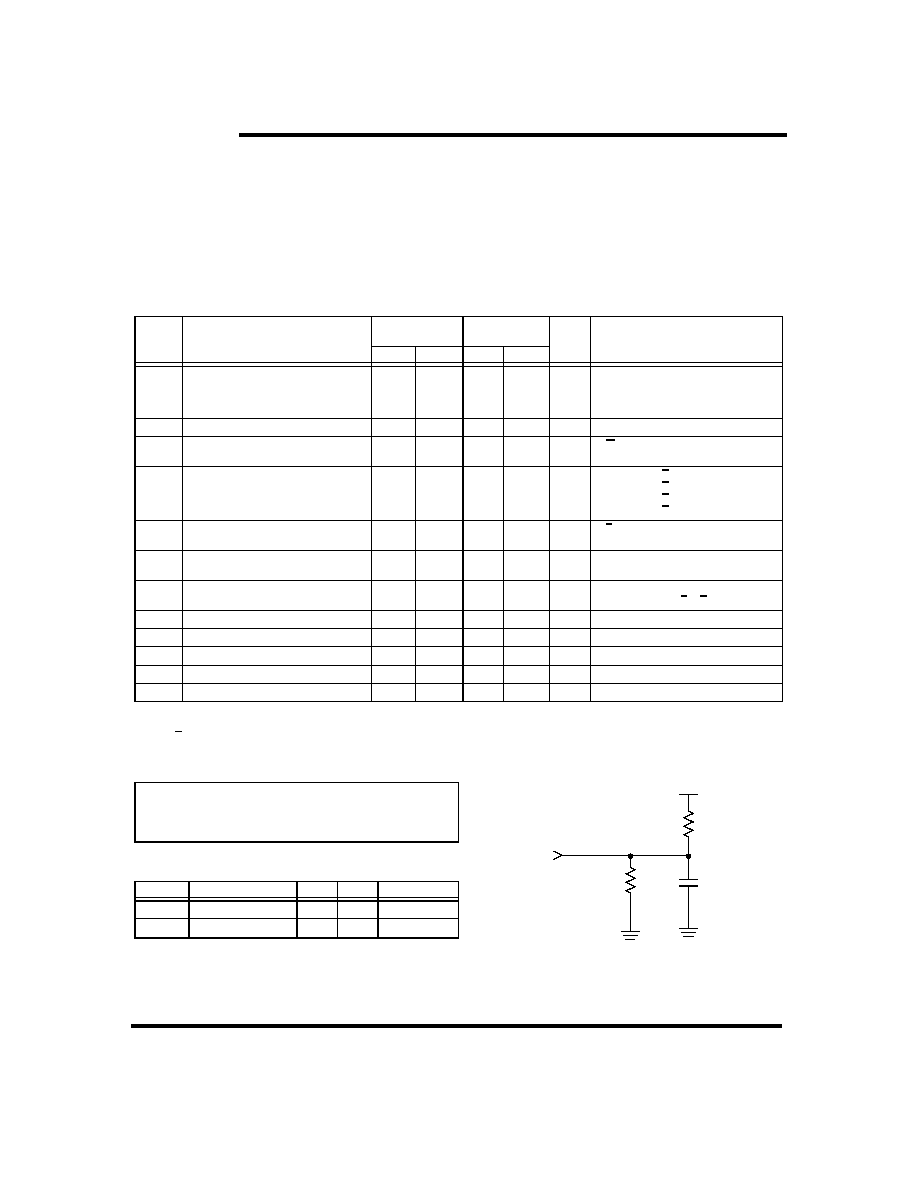

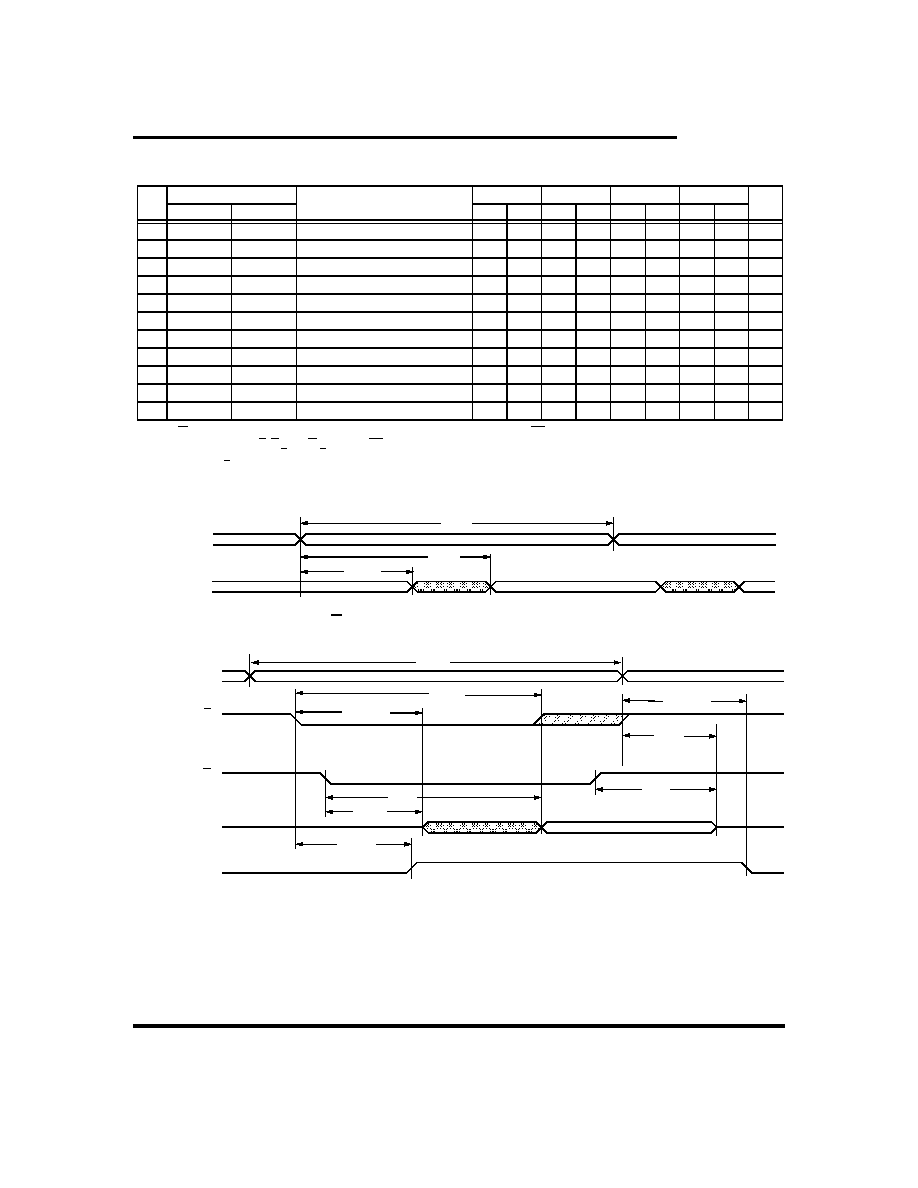

SRAM READ CYCLES #1 & #2

(V

CC

= 5.0V

±

10%)

Note f:

W must be high during SRAM READ cycles and low during SRAM WRITE cycles. NE must be high during entire cycle.

Note g: I/O state assumes E, G < V

IL

, W > V

IH

, and NE

V

IH

; device is continuously selected.

Note h: Measured + 200mV from steady state output voltage.

SRAM READ CYCLE #1: Address Controlled

f, g

SRAM READ CYCLE #2: E Controlled

f

NO.

SYMBOLS

PARAMETER

STK10C68-25

STK10C68-35

STK10C68-45

STK10C68-55

UNITS

#1, #2

Alt.

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

1

t

ELQV

t

ACS

Chip Enable Access Time

25

35

45

55

ns

2

t

AVAV

f

t

RC

Read Cycle Time

25

35

45

55

ns

3

t

AVQV

g

t

AA

Address Access Time

25

35

45

55

ns

4

t

GLQV

t

OE

Output Enable to Data Valid

10

15

20

25

ns

5

t

AXQX

g

t

OH

Output Hold after Address Change

5

5

5

5

ns

6

t

ELQX

t

LZ

Chip Enable to Output Active

5

5

5

5

ns

7

t

EHQZ

h

t

HZ

Chip Disable to Output Inactive

10

10

12

12

ns

8

t

GLQX

t

OLZ

Output Enable to Output Active

0

0

0

0

ns

9

t

GHQZ

h

t

OHZ

Output Disable to Output Inactive

10

10

12

12

ns

10

t

ELICCH

e

t

PA

Chip Enable to Power Active

0

0

0

0

ns

11

t

EHICCL

d, e

t

PS

Chip Disable to Power Standby

25

35

45

55

ns

DATA VALID

5

t

AXQX

3

t

AVQV

DQ (DATA OUT)

ADDRESS

2

t

AVAV

6

t

ELQX

STANDBY

DATA VALID

8

t

GLQX

4

t

GLQV

DQ (DATA OUT)

E

ADDRESS

2

t

AVAV

G

I

CC

ACTIVE

1

t

ELQV

10

t

ELICCH

11

t

EHICCL

7

t

EHQZ

9

t

GHQZ

STK10C68

September 2003

4

Document Control # ML0006 rev 0.1

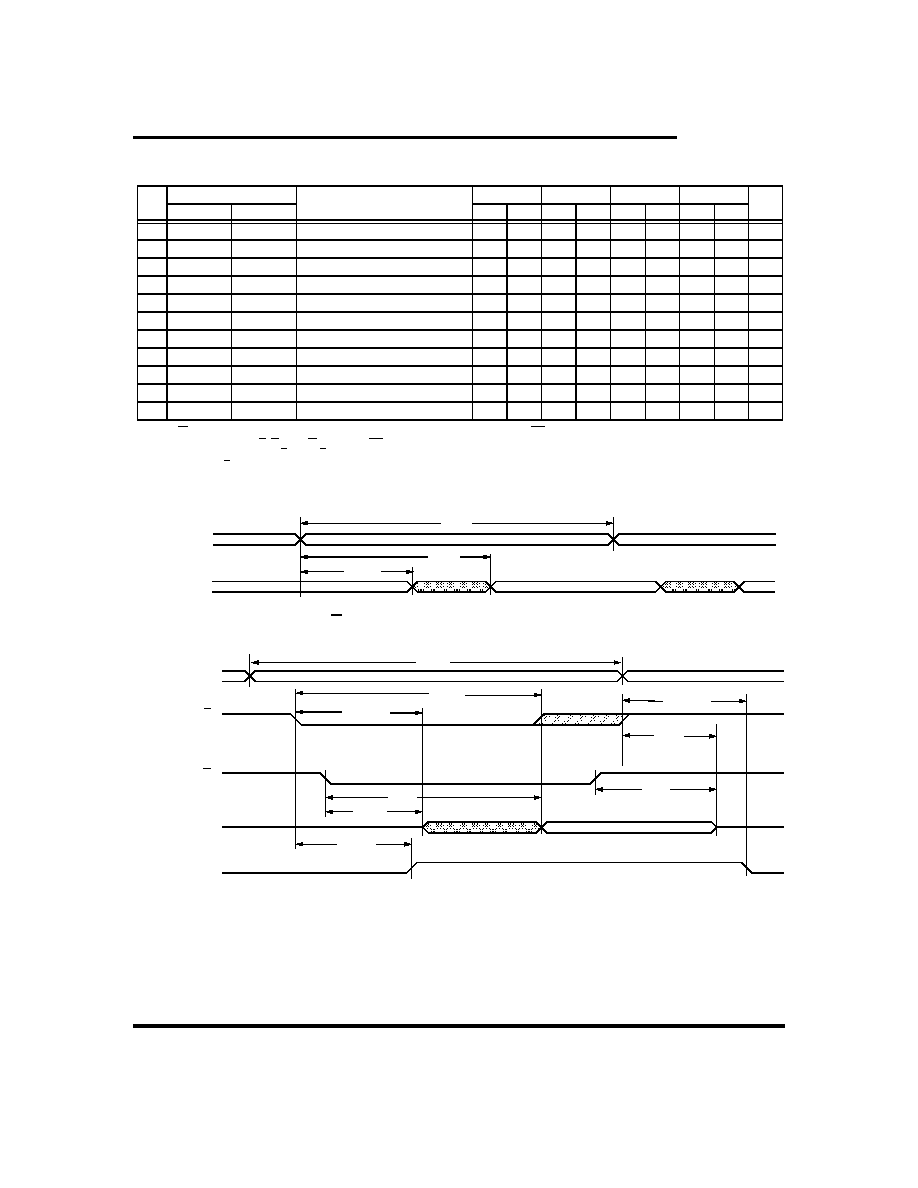

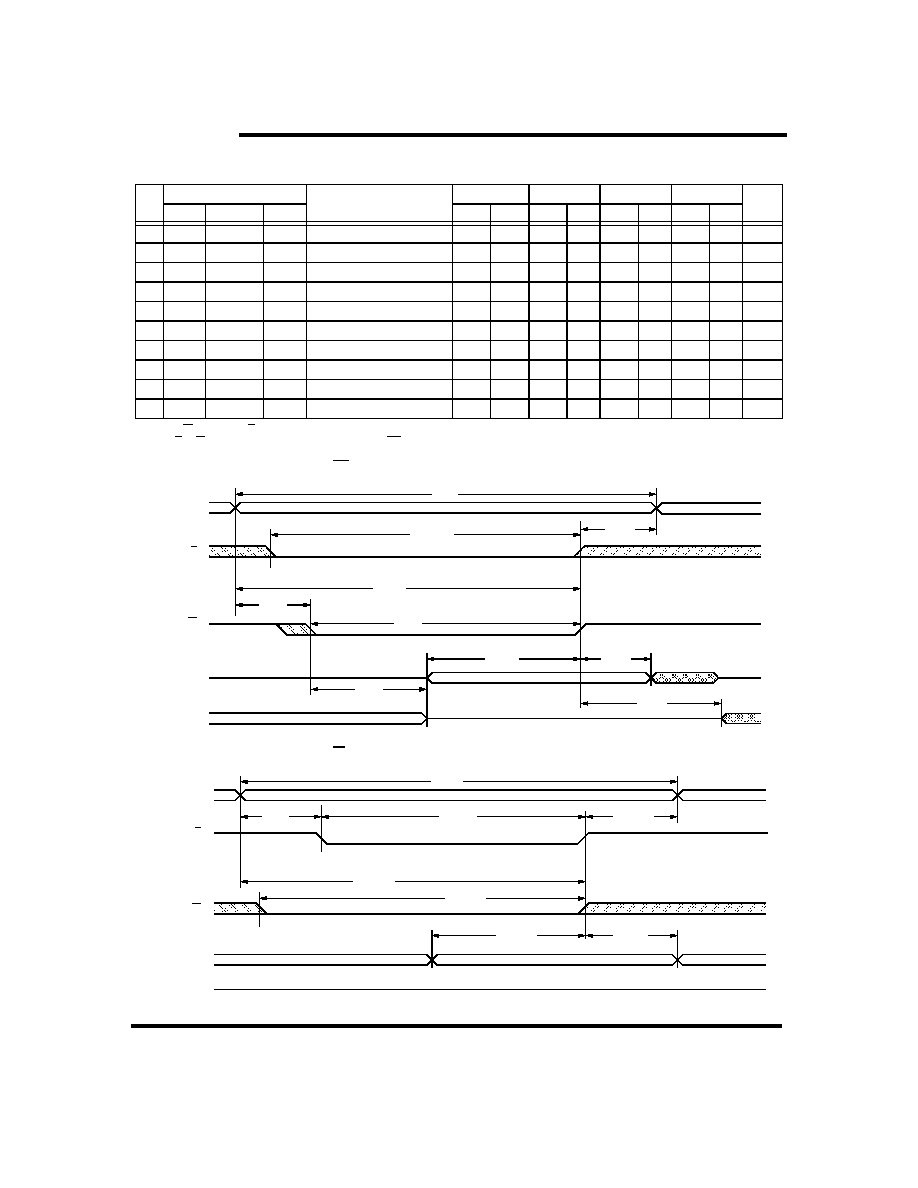

SRAM WRITE CYCLES #1 & #2

(V

CC

= 5.0V

±

10%)

Note i:

If W is low when E goes low, the outputs remain in the high-impedance state.

Note j:

E or W must be

V

IH

during address transitions. NE

V

IH

.

SRAM WRITE CYCLE #1: W Controlled

j

SRAM WRITE CYCLE #2: E Controlled

j

NO.

SYMBOLS

PARAMETER

STK10C68-25

STK10C68-35

STK10C68-45

STK10C68-55

UNITS

#1

#2

Alt.

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

12

t

AVAV

t

AVAV

t

WC

Write Cycle Time

25

35

45

55

ns

13

t

WLWH

t

WLEH

t

WP

Write Pulse Width

20

25

30

45

ns

14

t

ELWH

t

ELEH

t

CW

Chip Enable to End of Write

20

25

30

45

ns

15

t

DVWH

t

DVEH

t

DW

Data Set-up to End of Write

10

12

15

30

ns

16

t

WHDX

t

EHDX

t

DH

Data Hold after End of Write

0

0

0

0

ns

17

t

AVWH

t

AVEH

t

AW

Address Set-up to End of Write

20

25

30

45

ns

18

t

AVWL

t

AVEL

t

AS

Address Set-up to Start of Write

0

0

0

0

ns

19

t

WHAX

t

EHAX

t

WR

Address Hold after End of Write

0

0

0

0

ns

20

t

WLQZ

h, i

t

WZ

Write Enable to Output Disable

10

13

14

15

ns

21

t

WHQX

t

OW

Output Active after End of Write

5

5

5

5

ns

PREVIOUS DATA

DATA OUT

E

ADDRESS

12

t

AVAV

W

16

t

WHDX

DATA IN

19

t

WHAX

13

t

WLWH

18

t

AVWL

17

t

AVWH

DATA VALID

20

t

WLQZ

15

t

DVWH

HIGH IMPEDANCE

21

t

WHQX

14

t

ELWH

DATA OUT

E

ADDRESS

12

t

AVAV

W

DATA IN

13

t

WLEH

17

t

AVEH

DATA VALID

HIGH IMPEDANCE

14

t

ELEH

18

t

AVEL

19

t

EHAX

15

t

DVEH

16

t

EHDX