| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: XRT7245 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

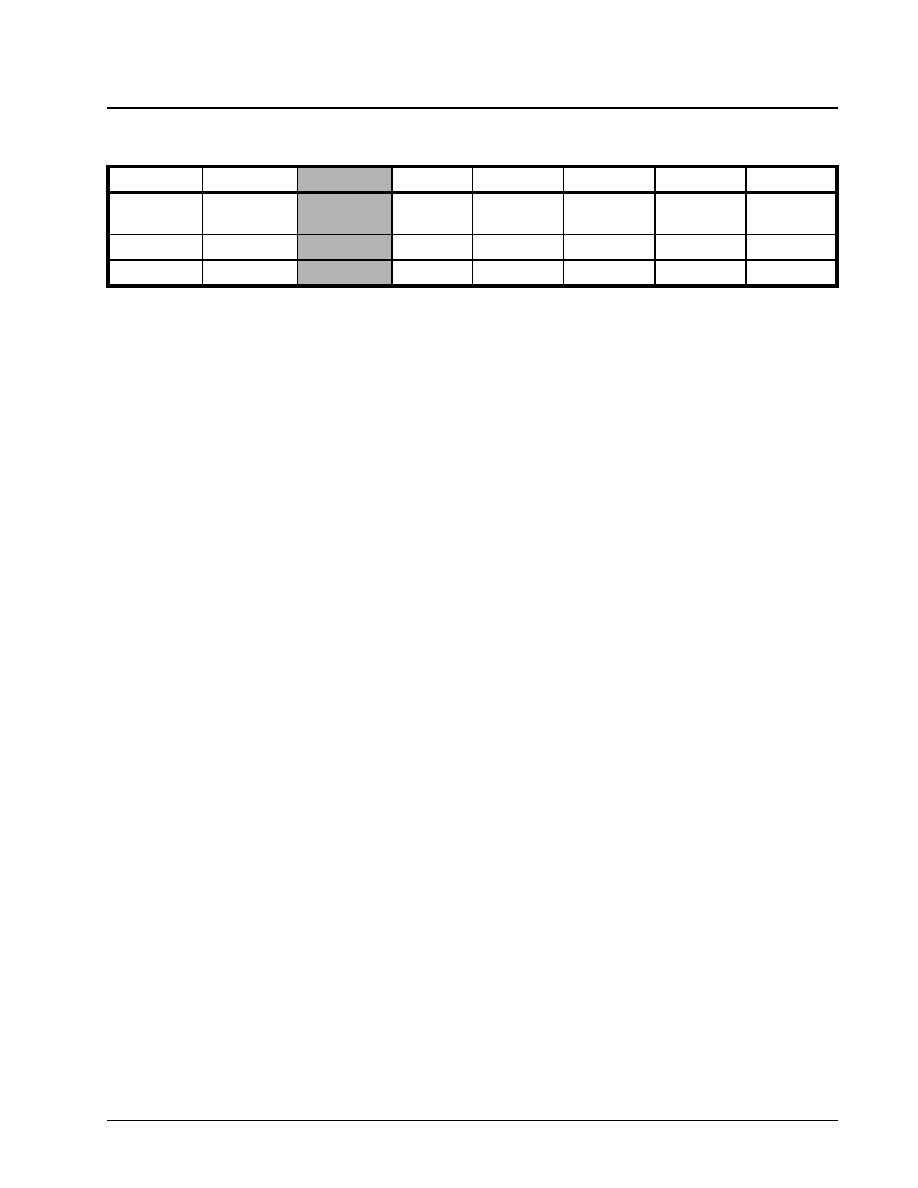

- GENERAL DESCRIPTION

- Features

- Applications

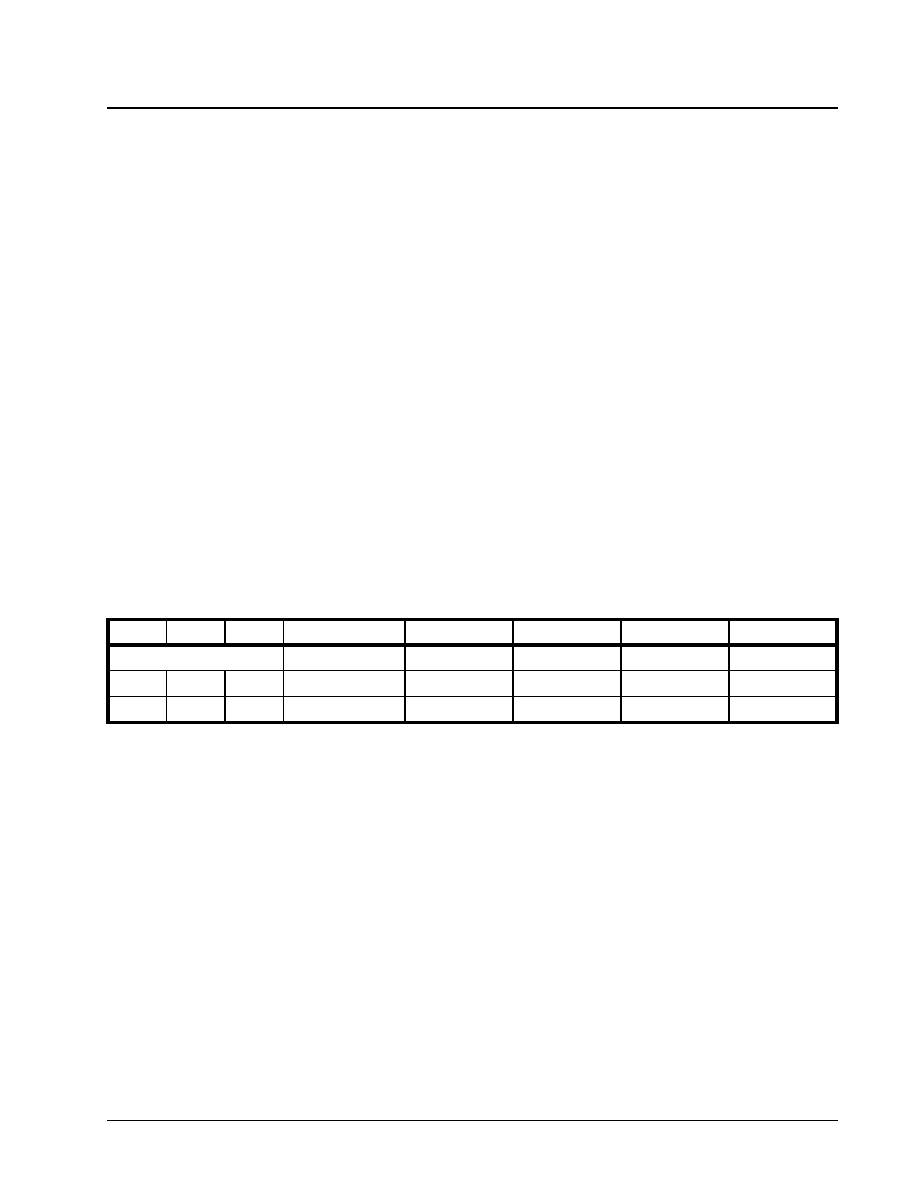

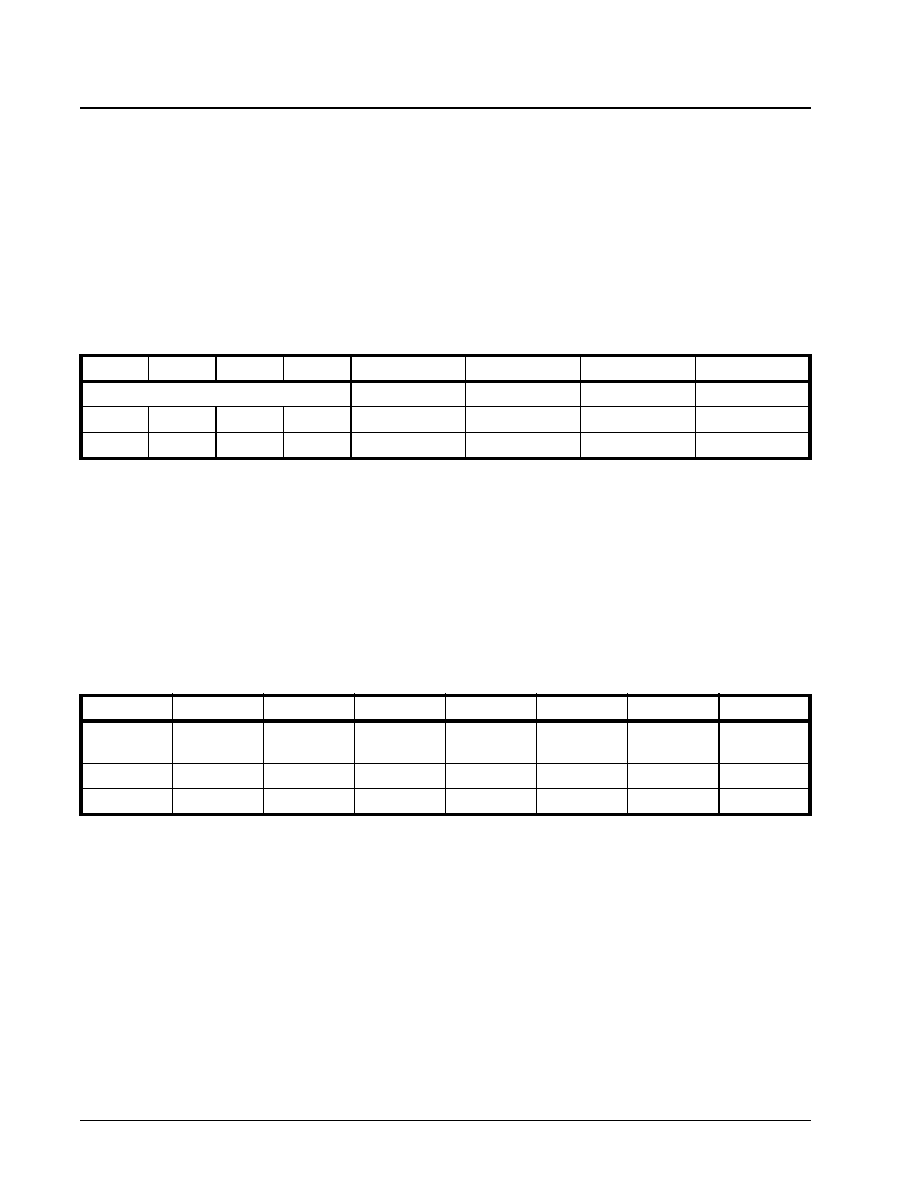

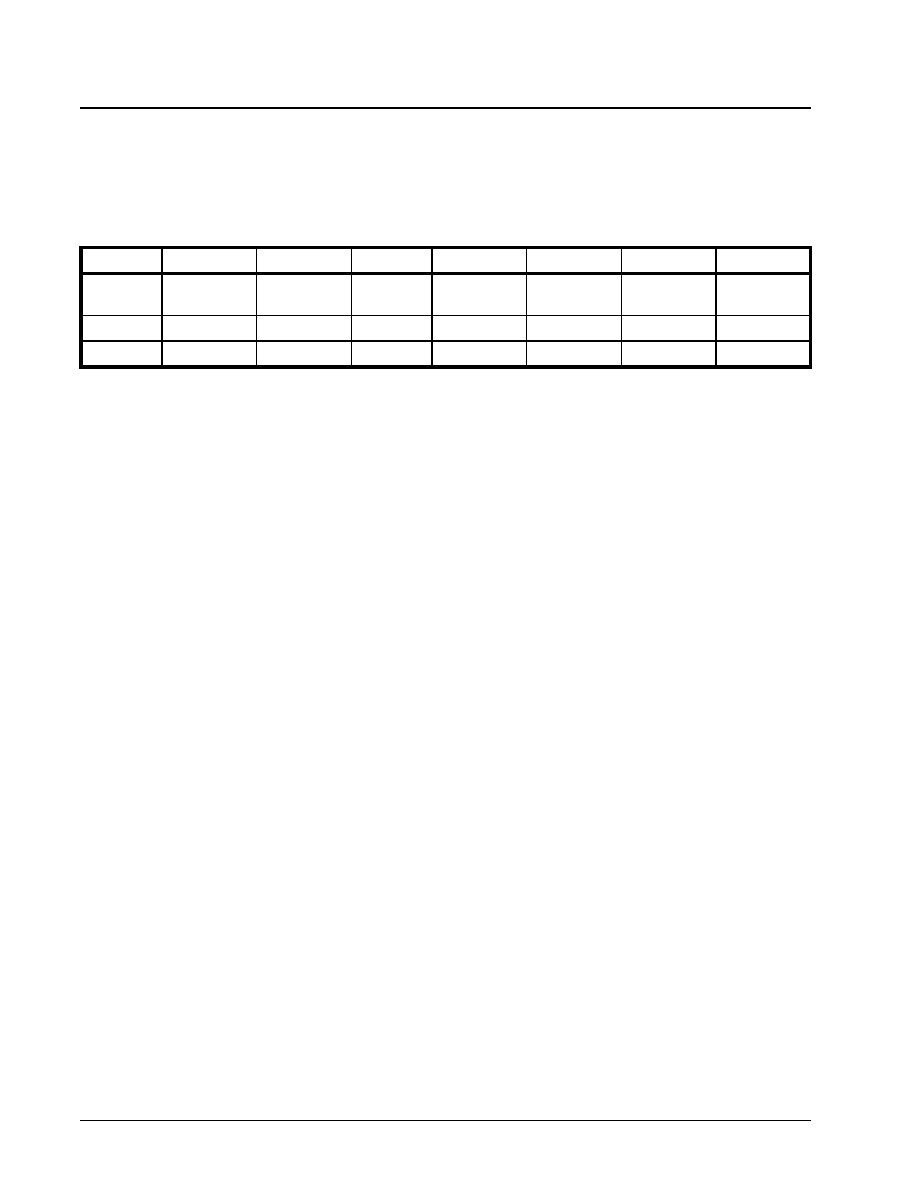

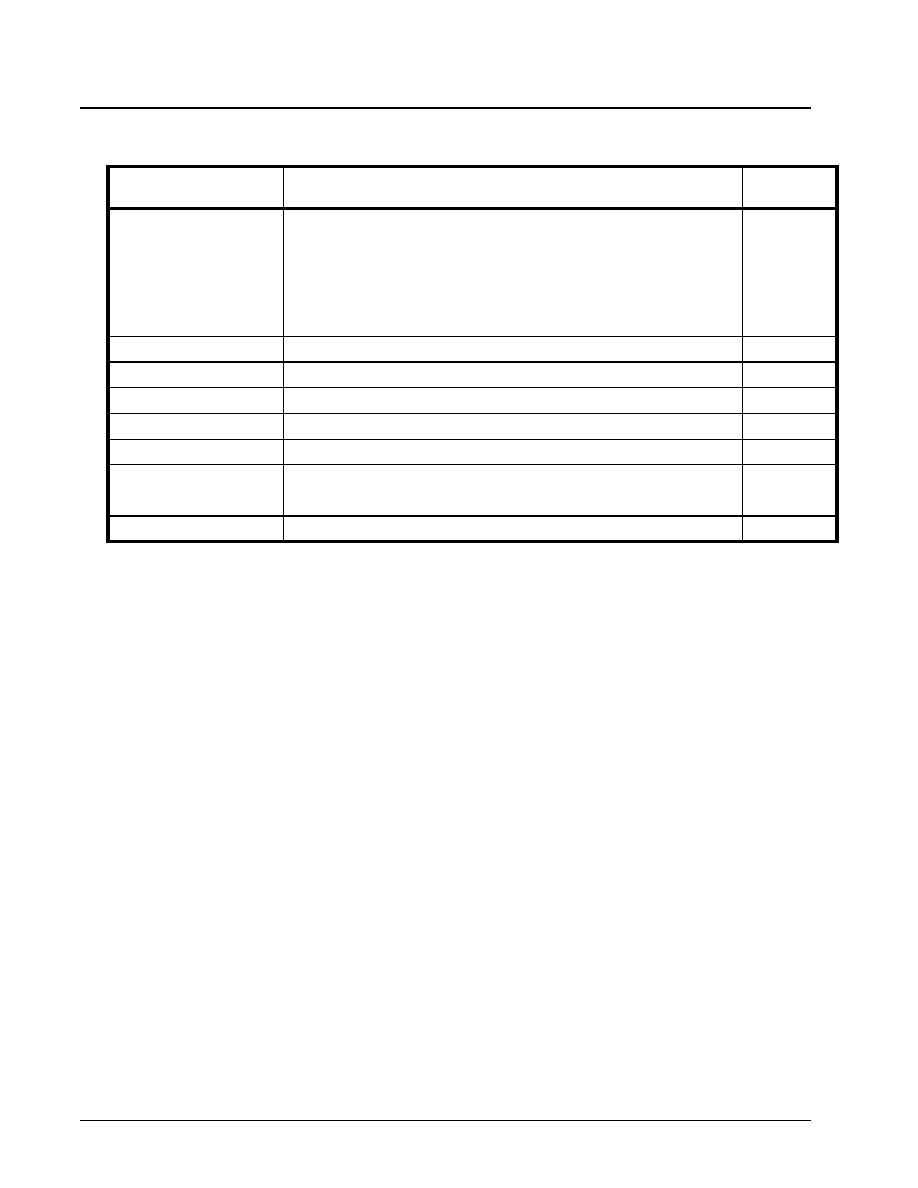

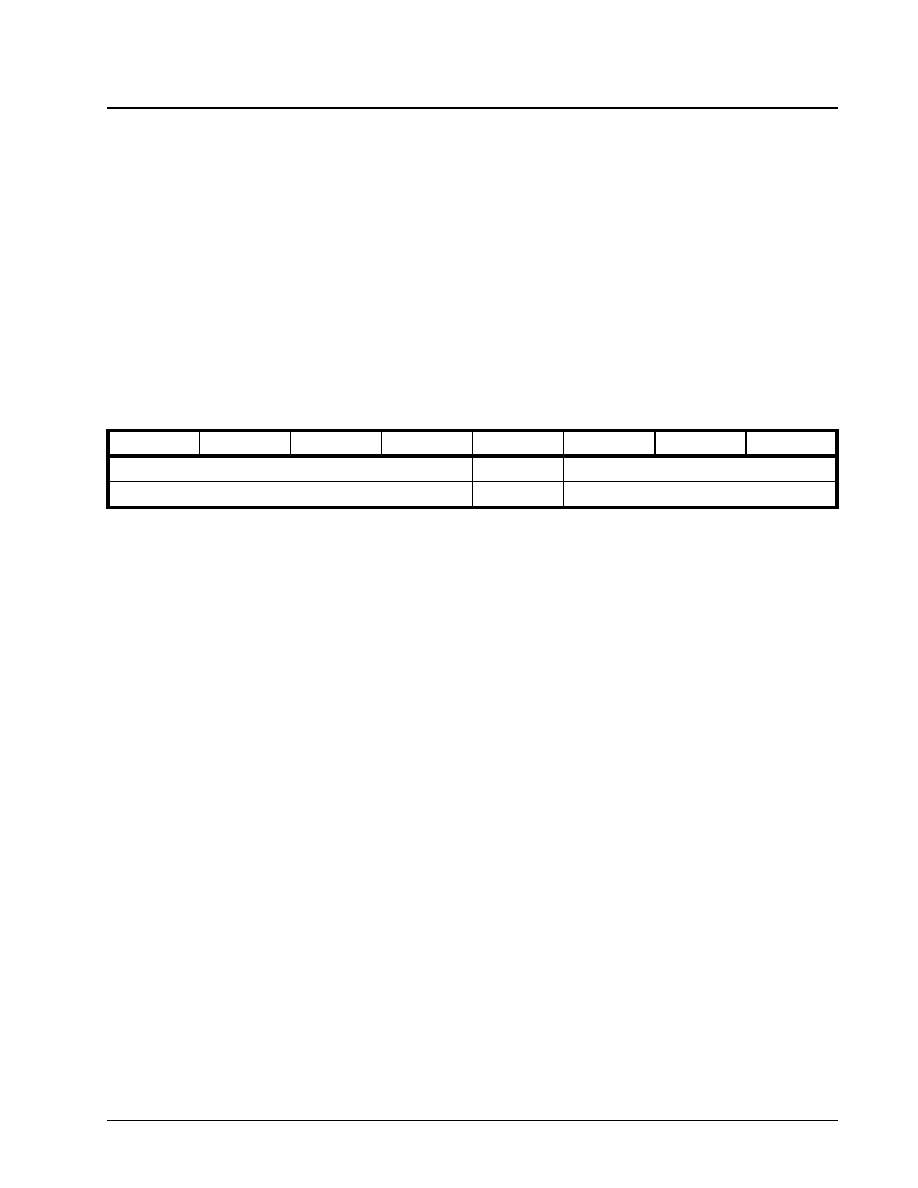

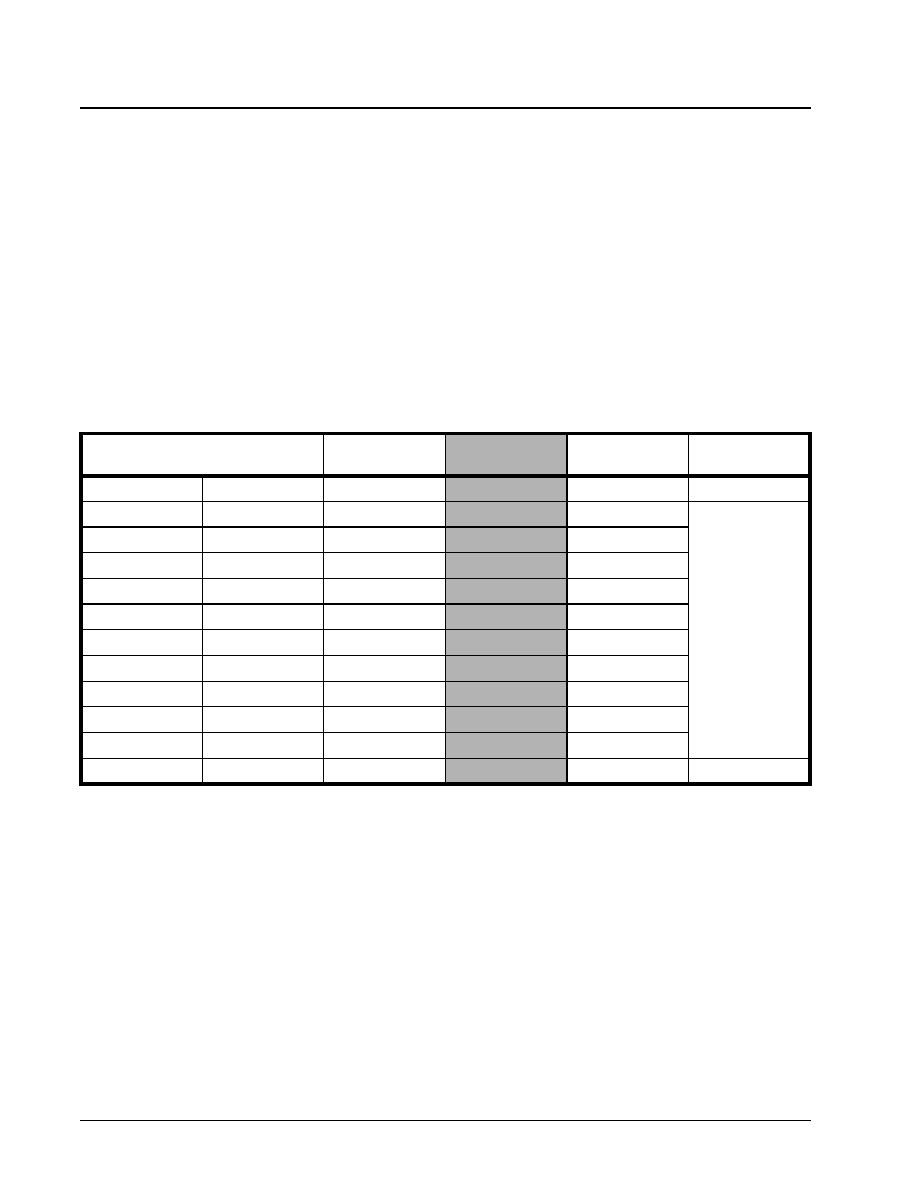

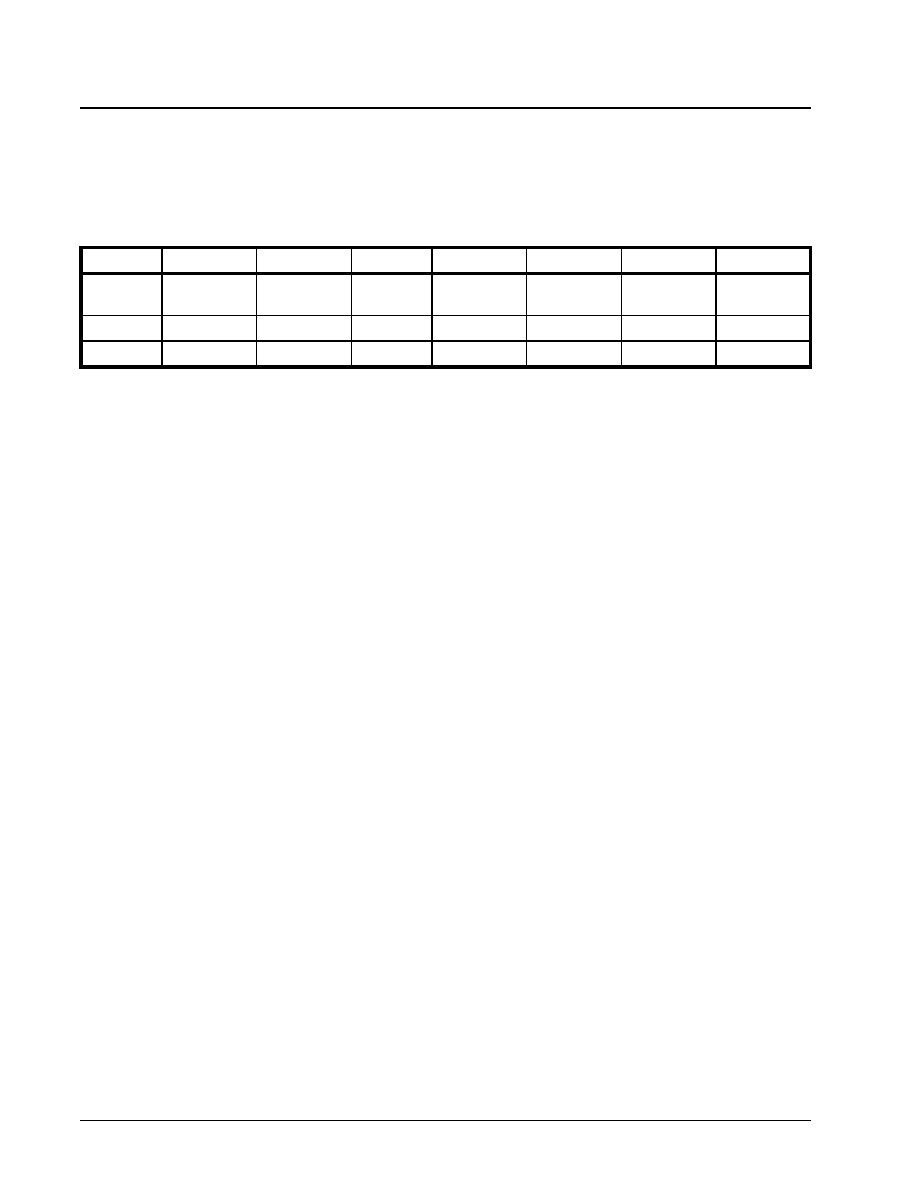

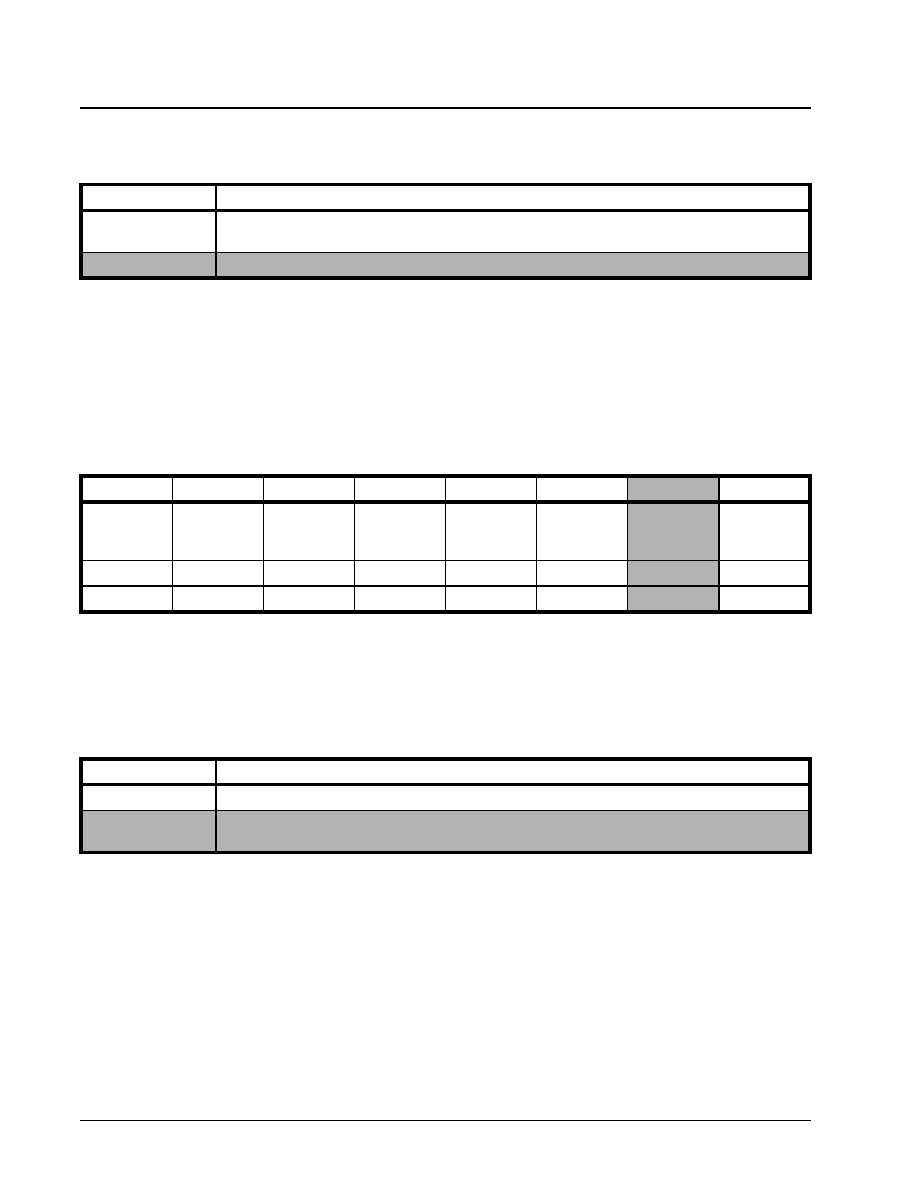

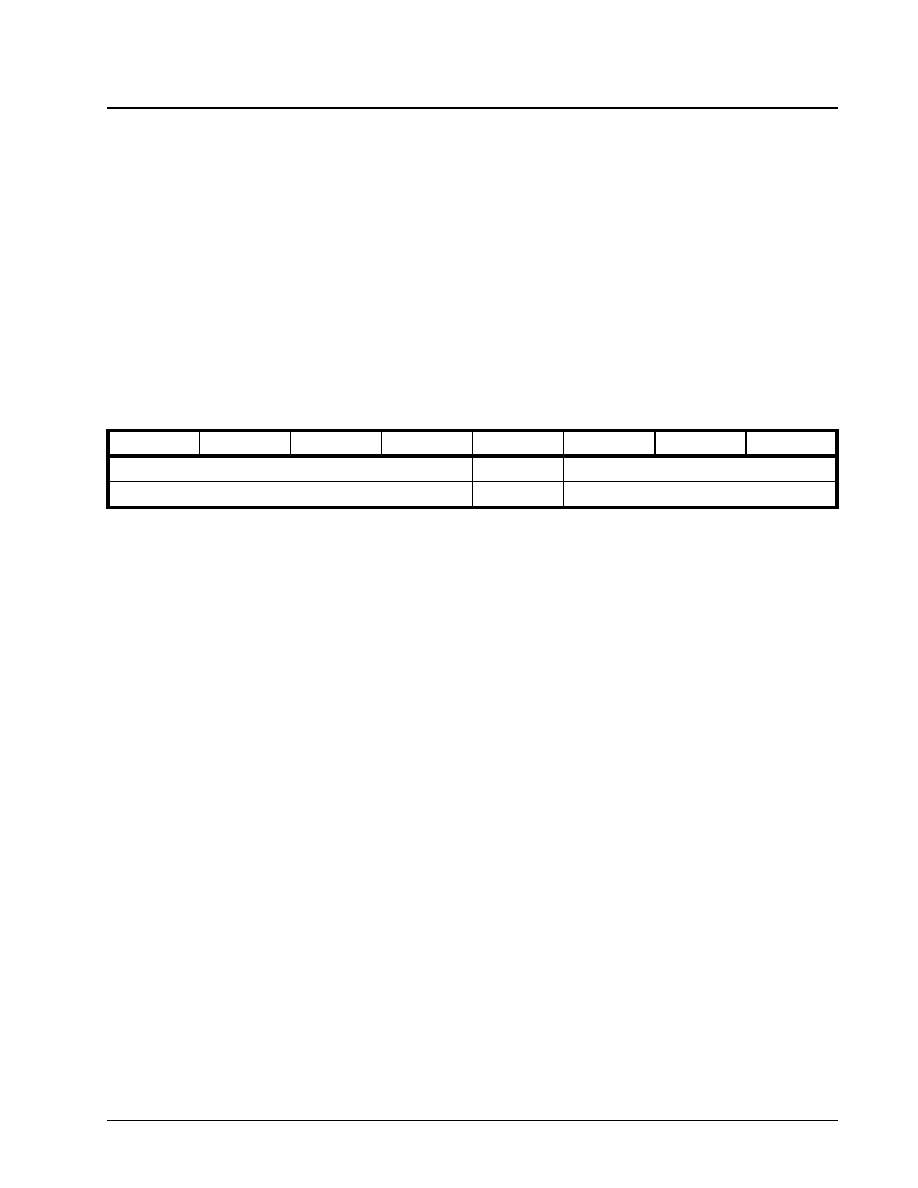

- Ordering Information

- Functional Description

- The Receive Section

- The Transmit Section

- The Microprocessor Interface Section

- Performance Monitor Section

- Test and Diagnostic Section

- Line Interface Drive and Scan Section

- FEATURES

- Transmit and Receive Sections

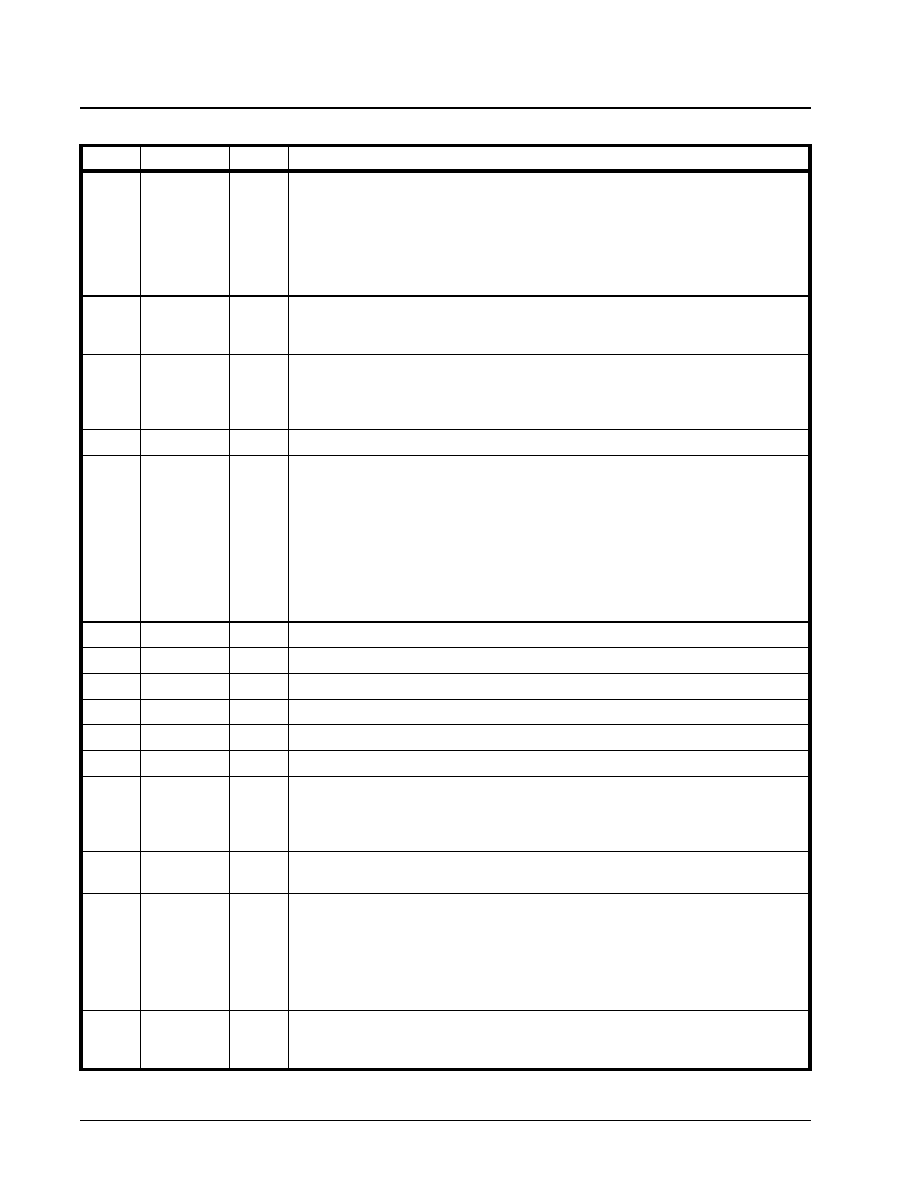

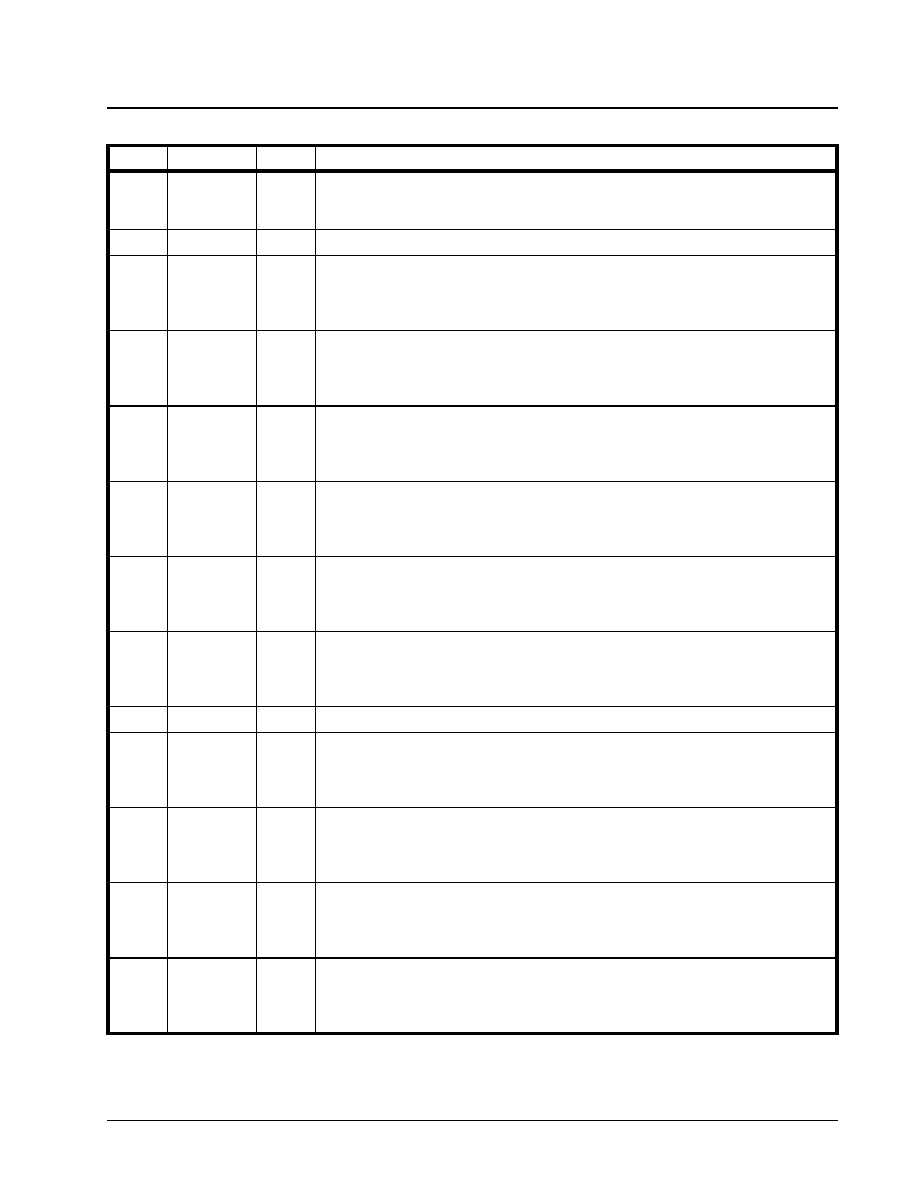

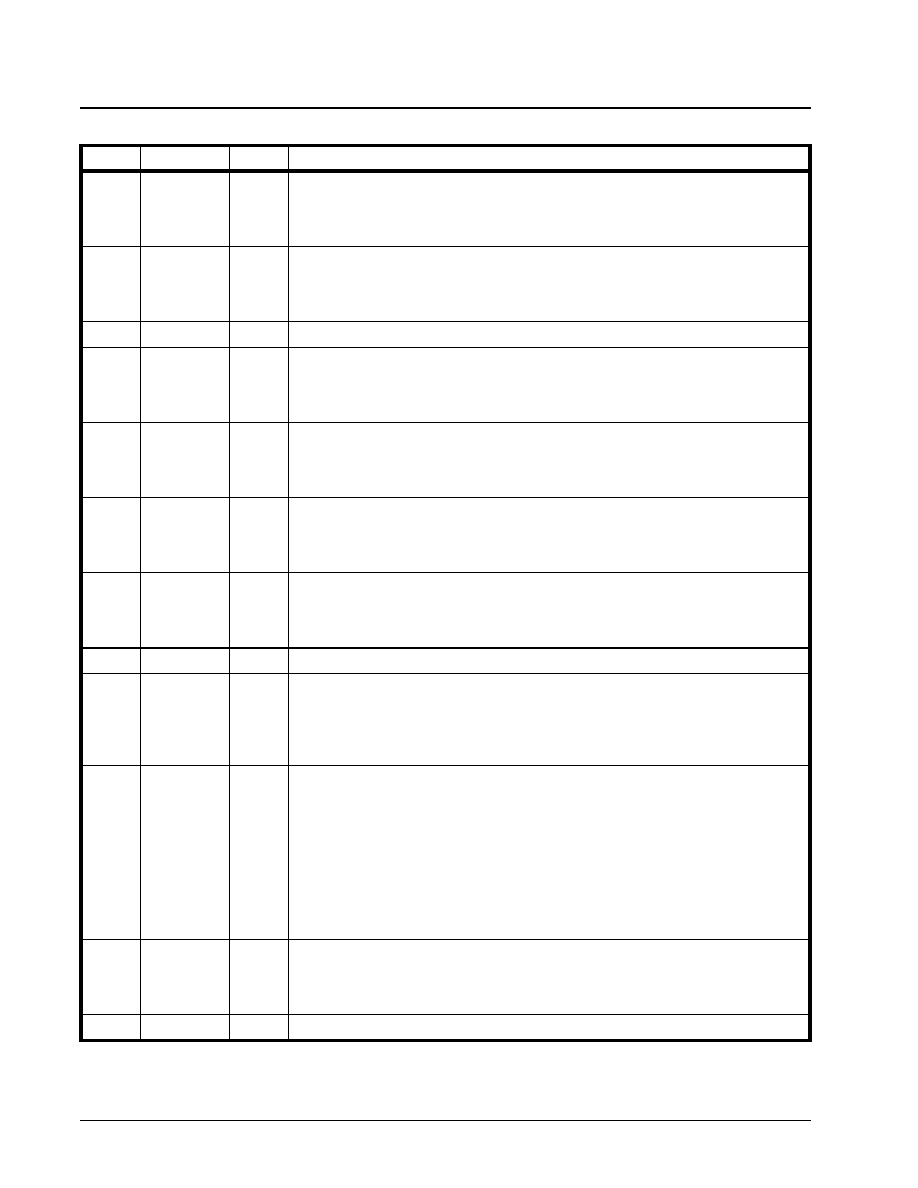

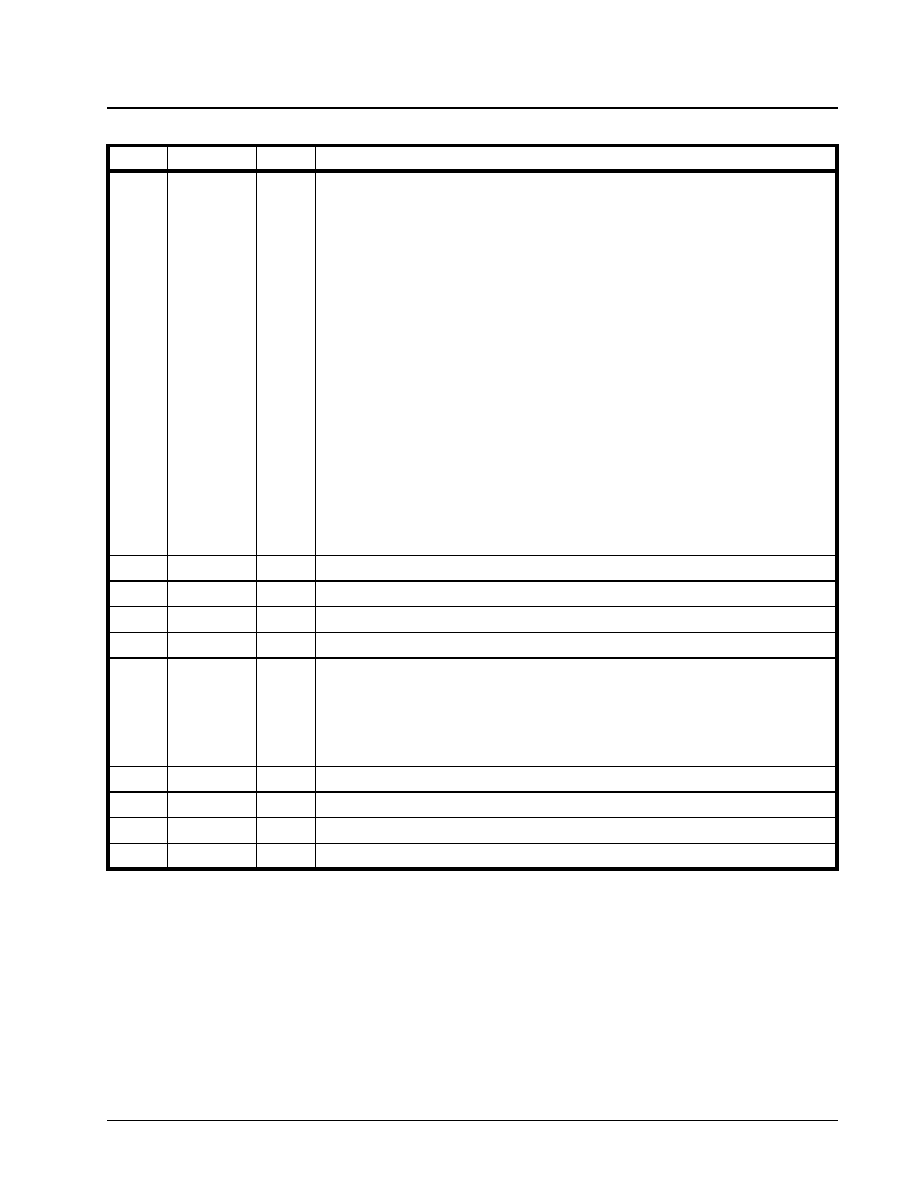

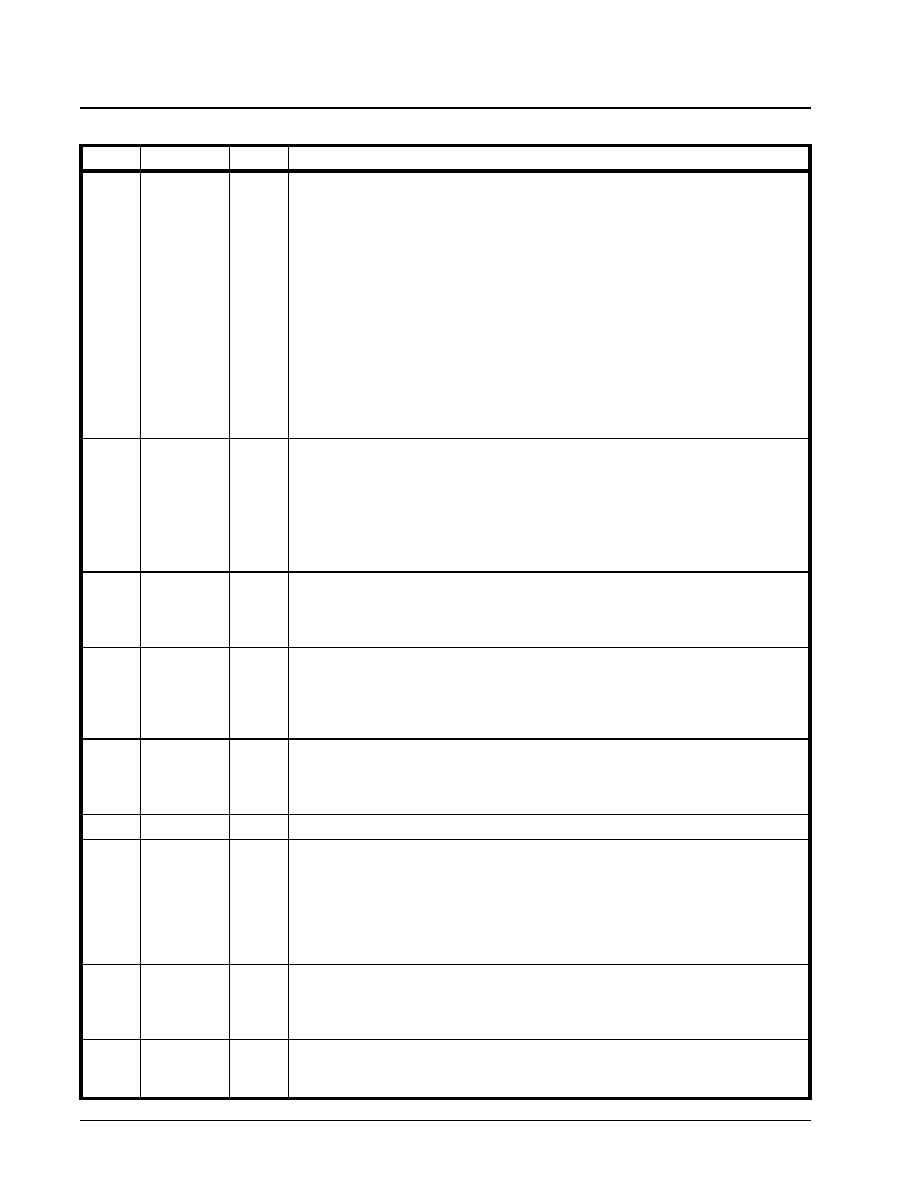

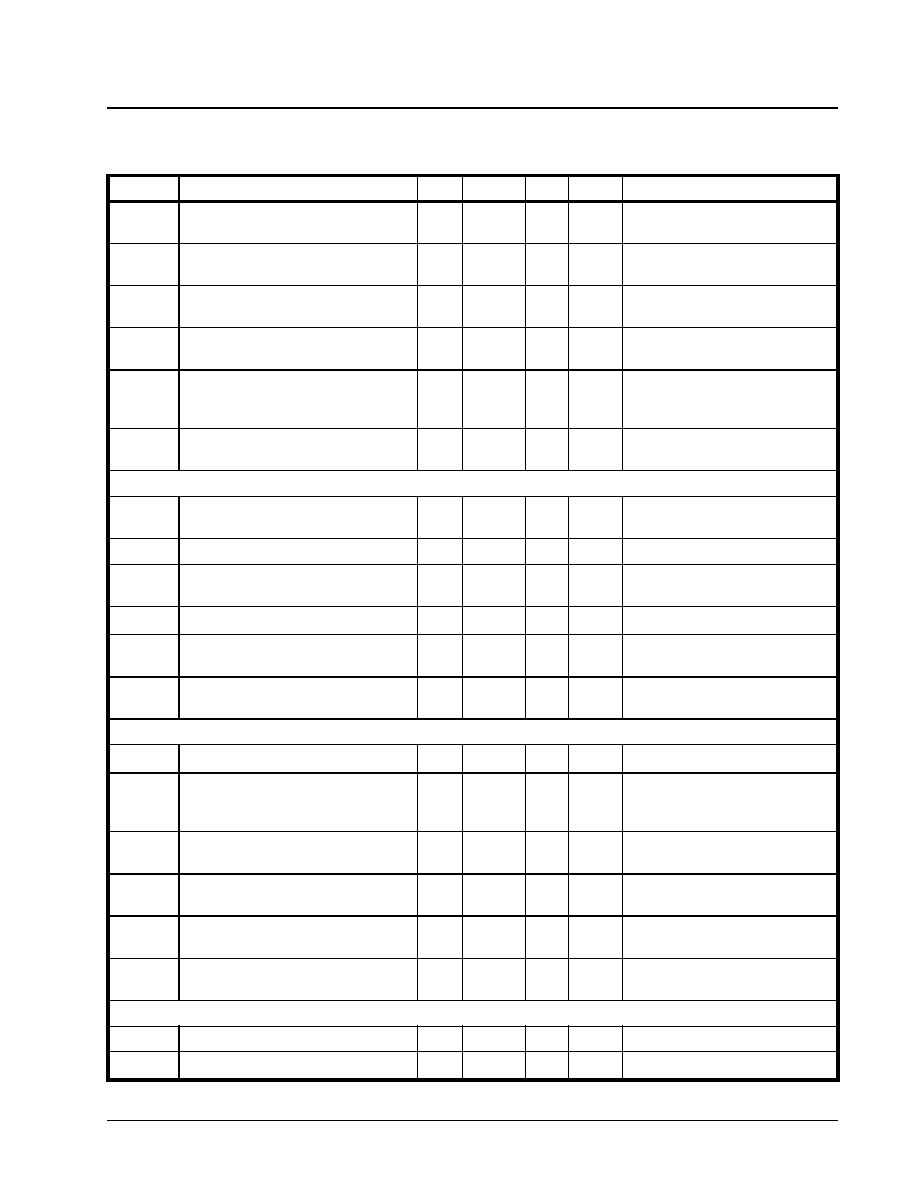

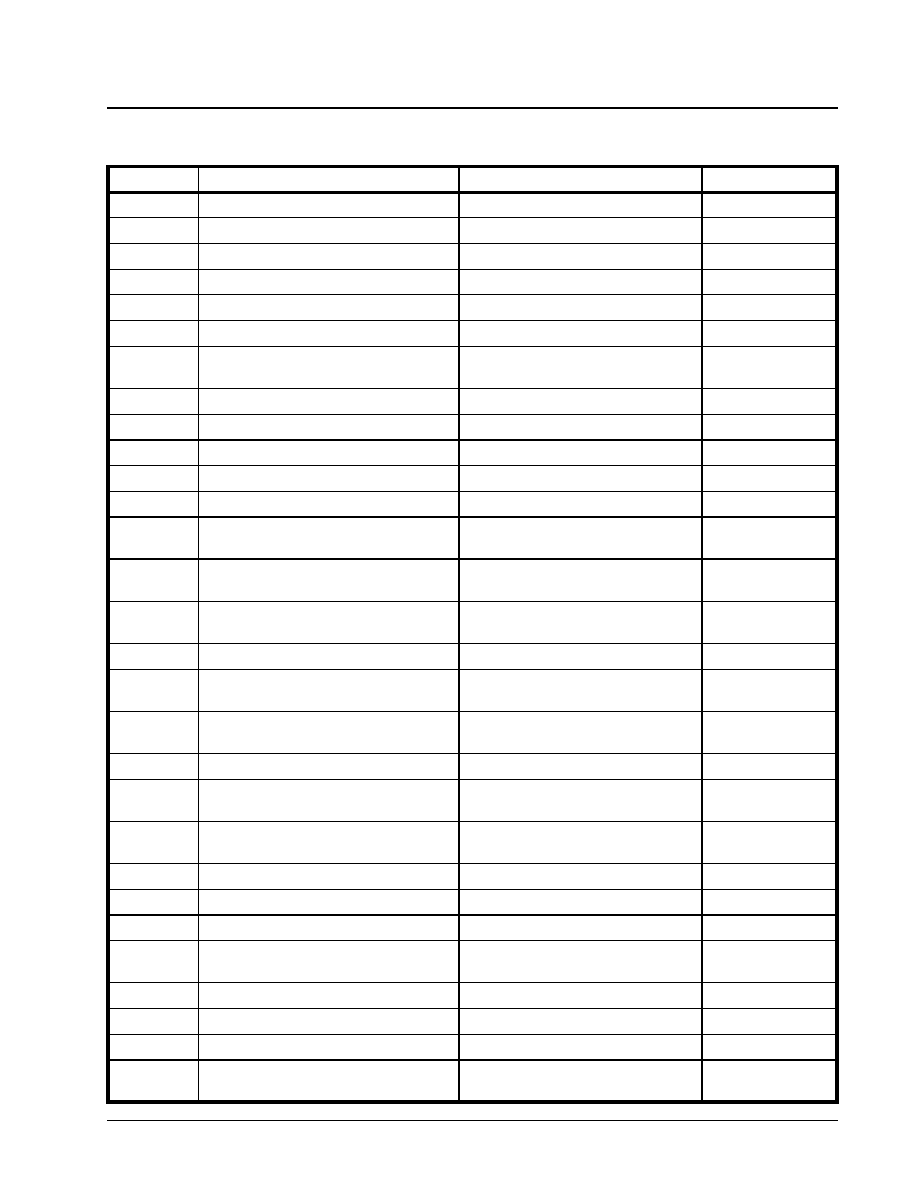

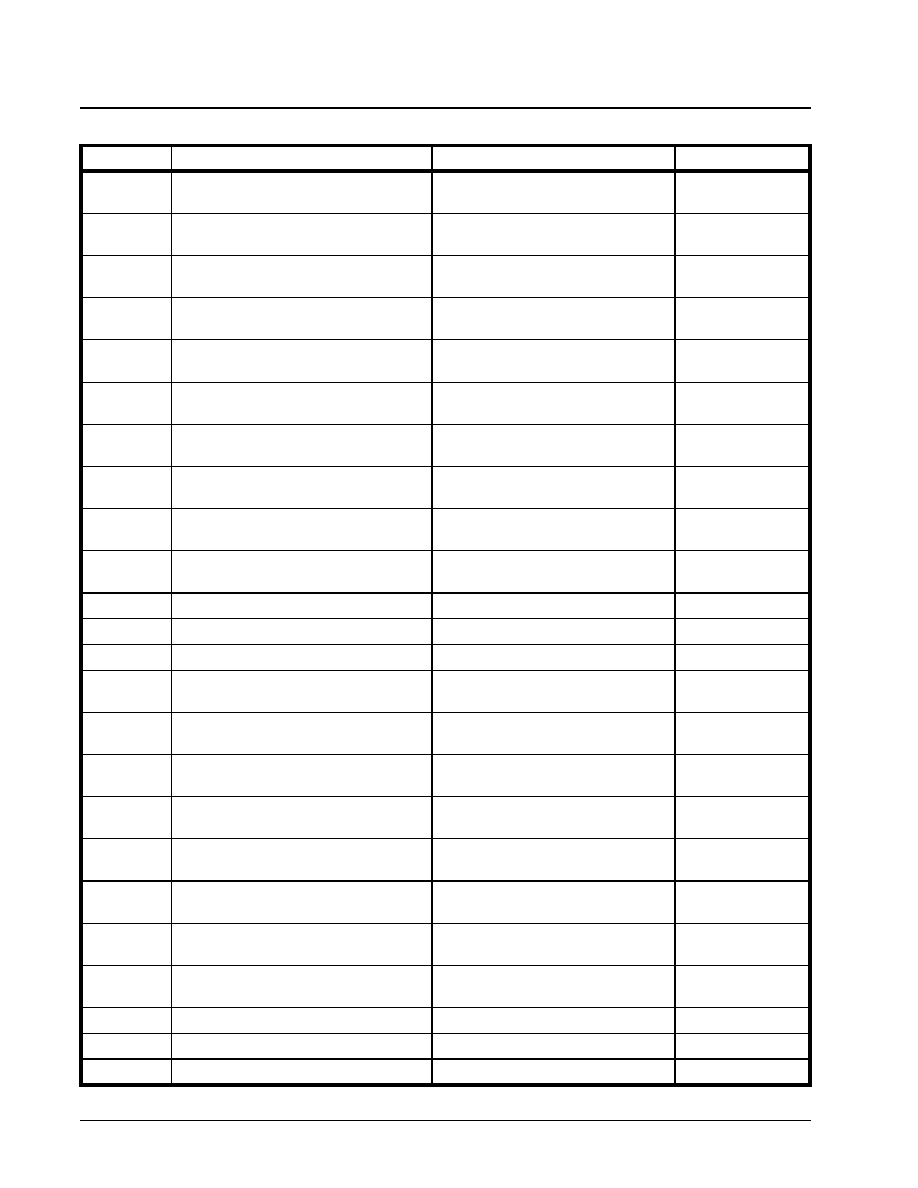

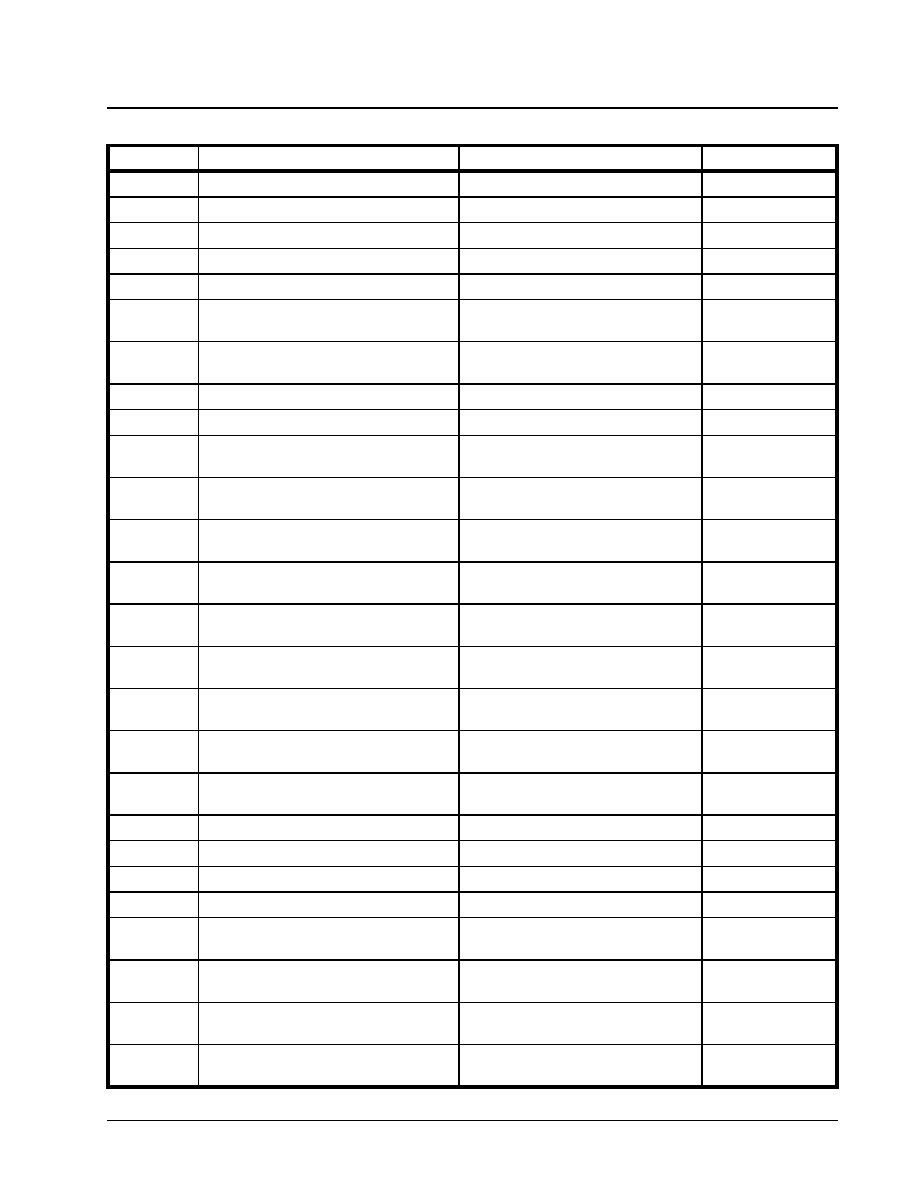

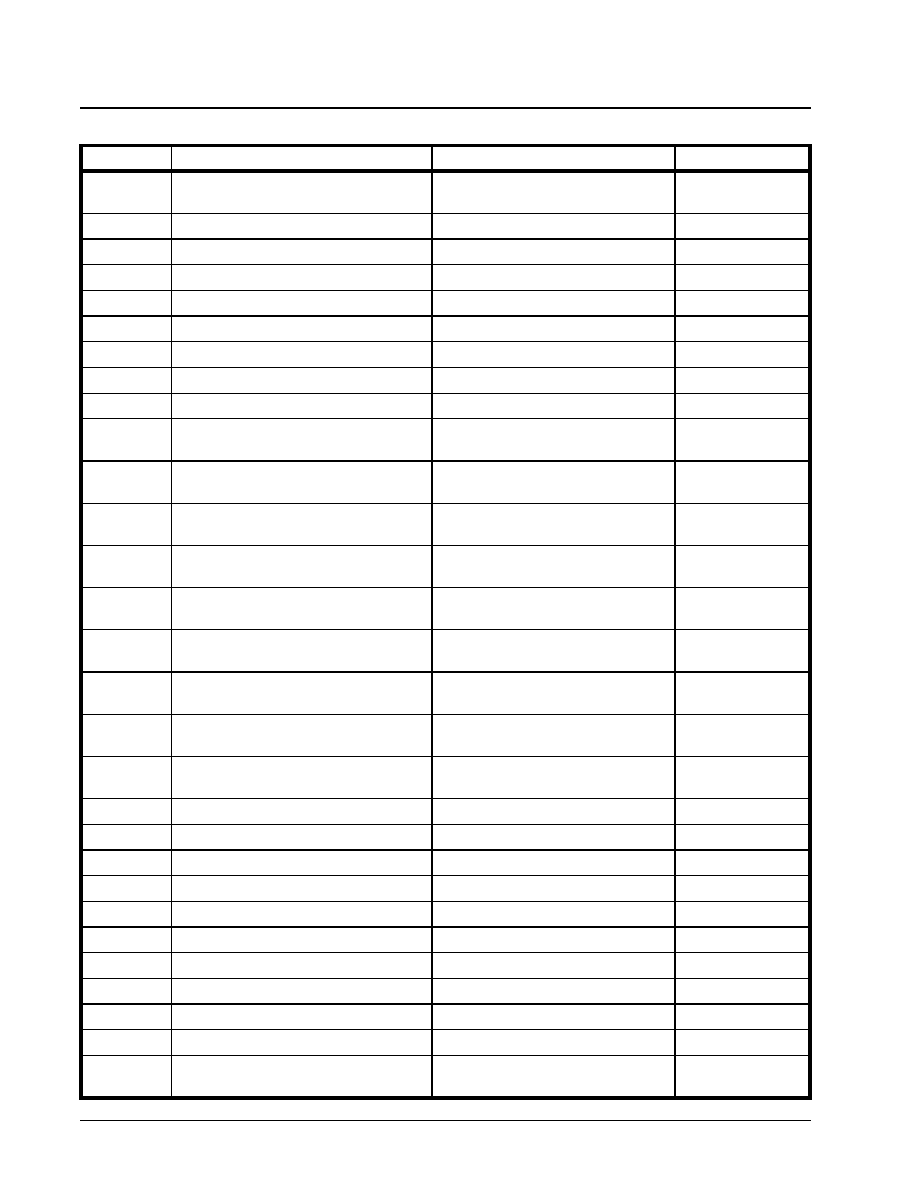

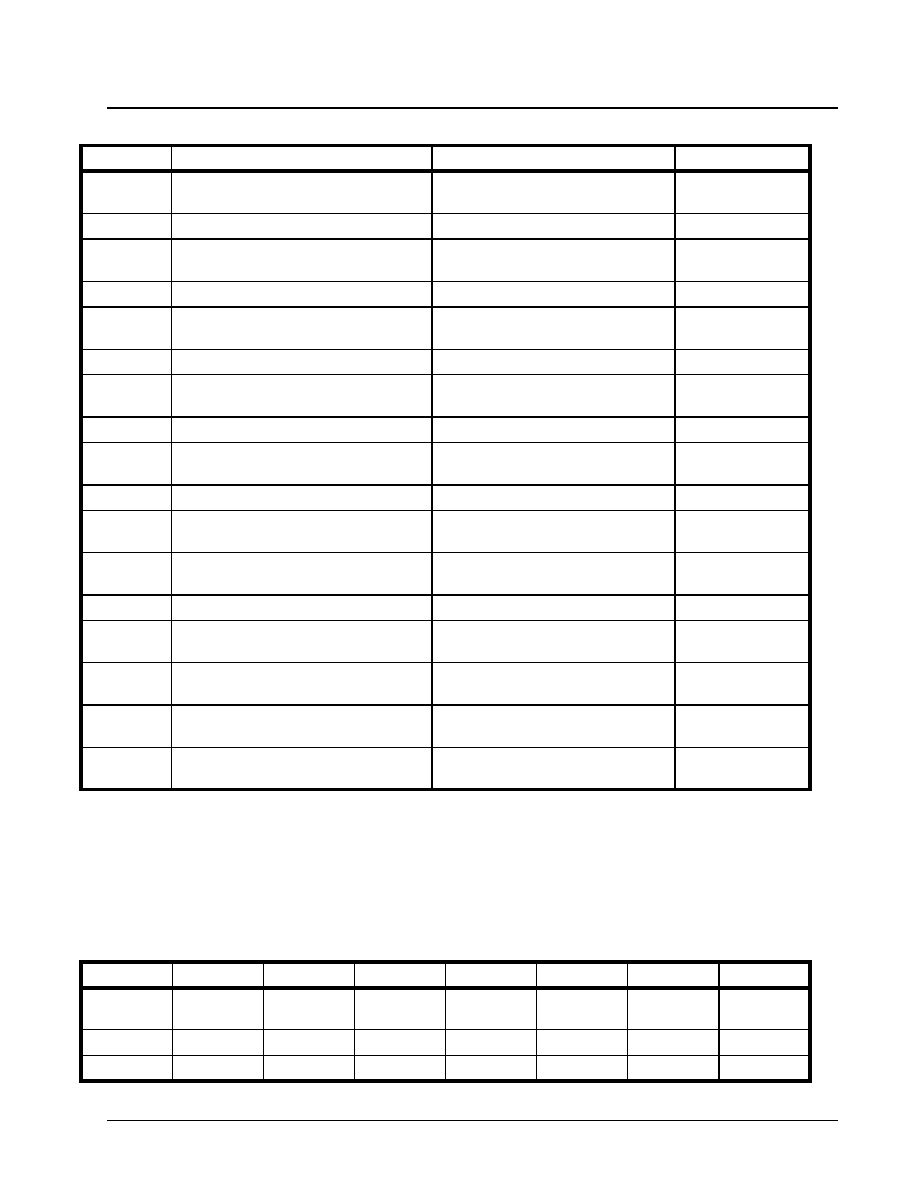

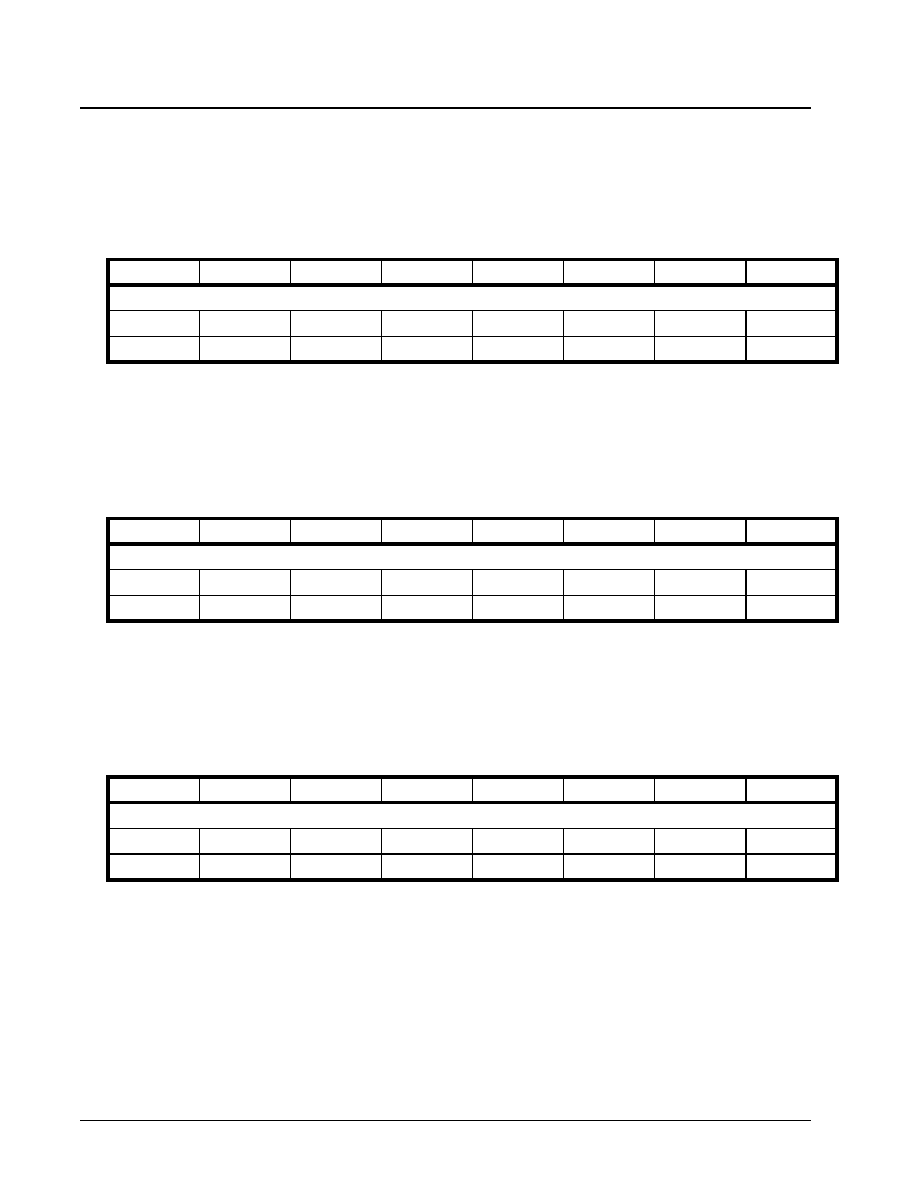

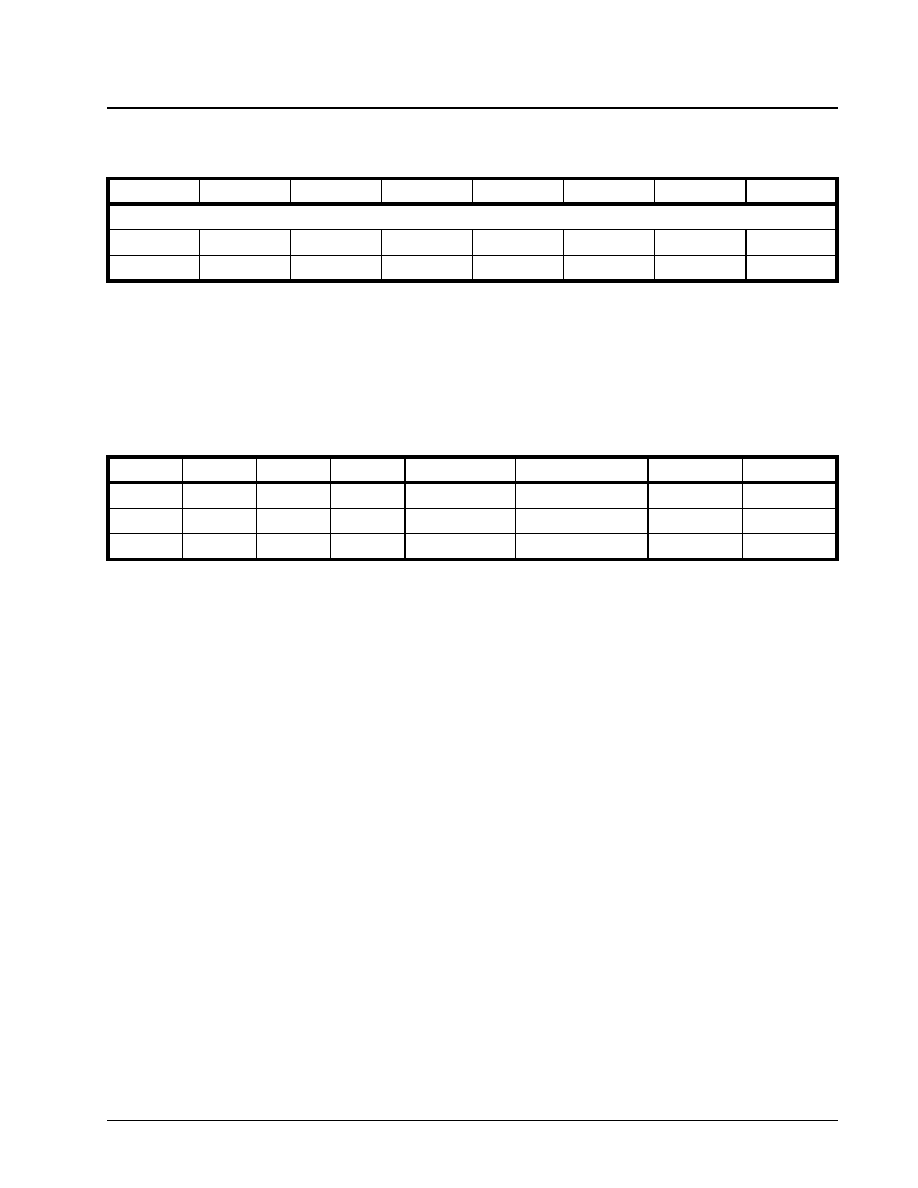

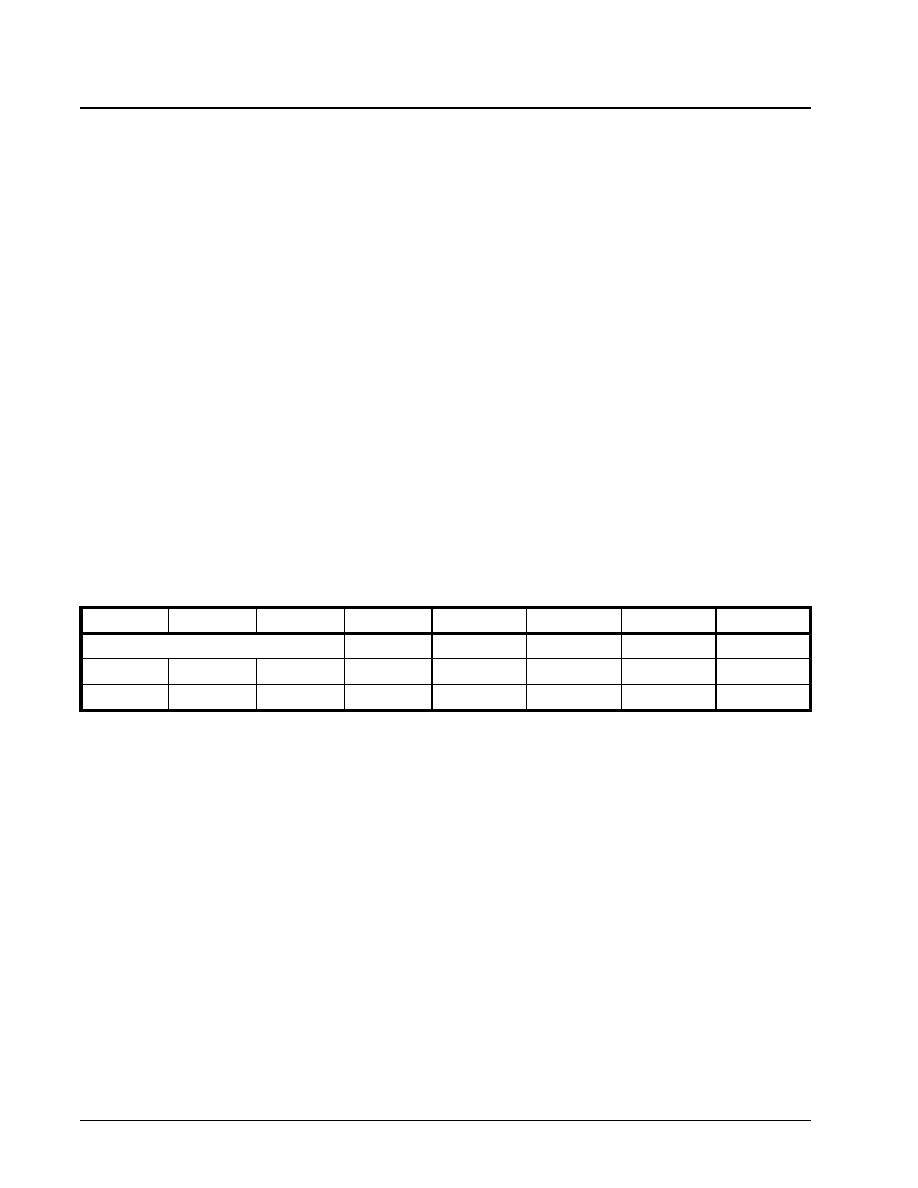

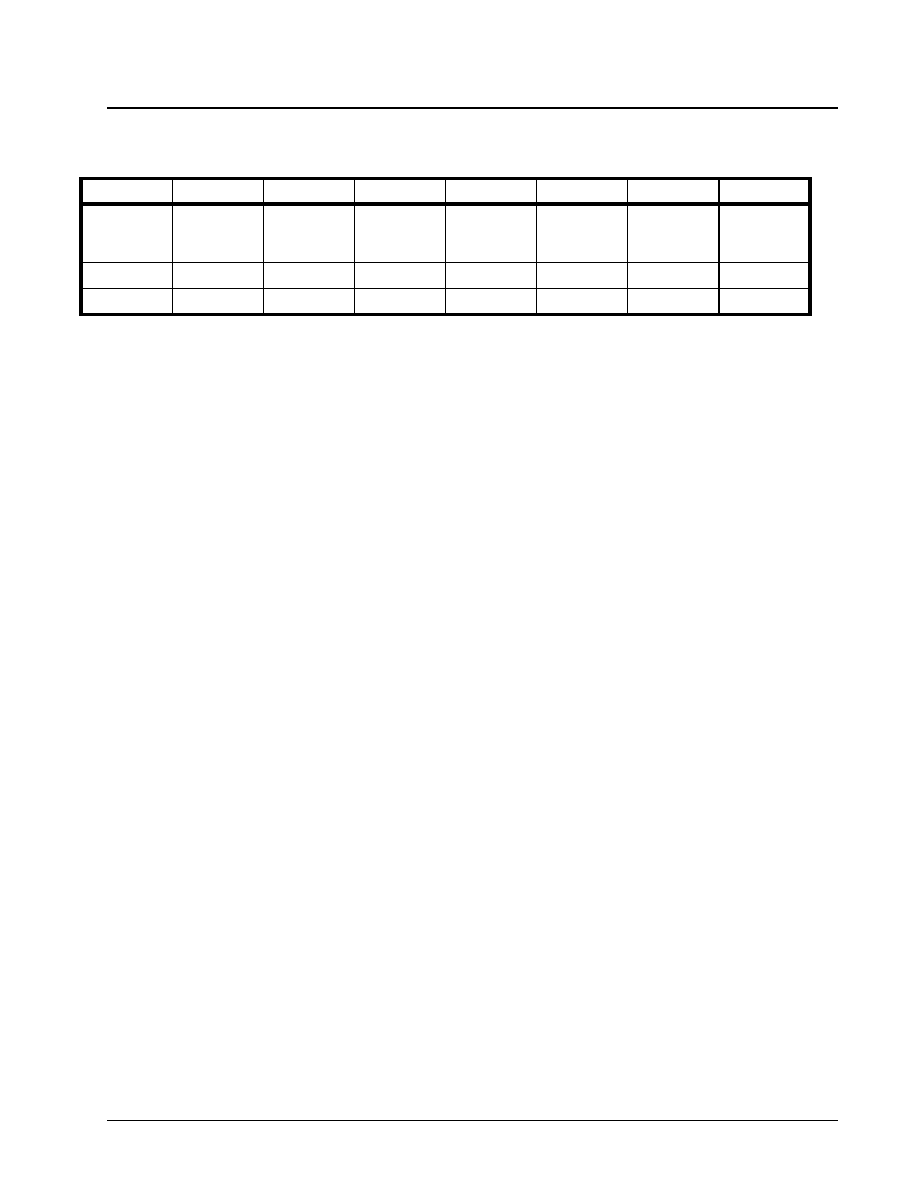

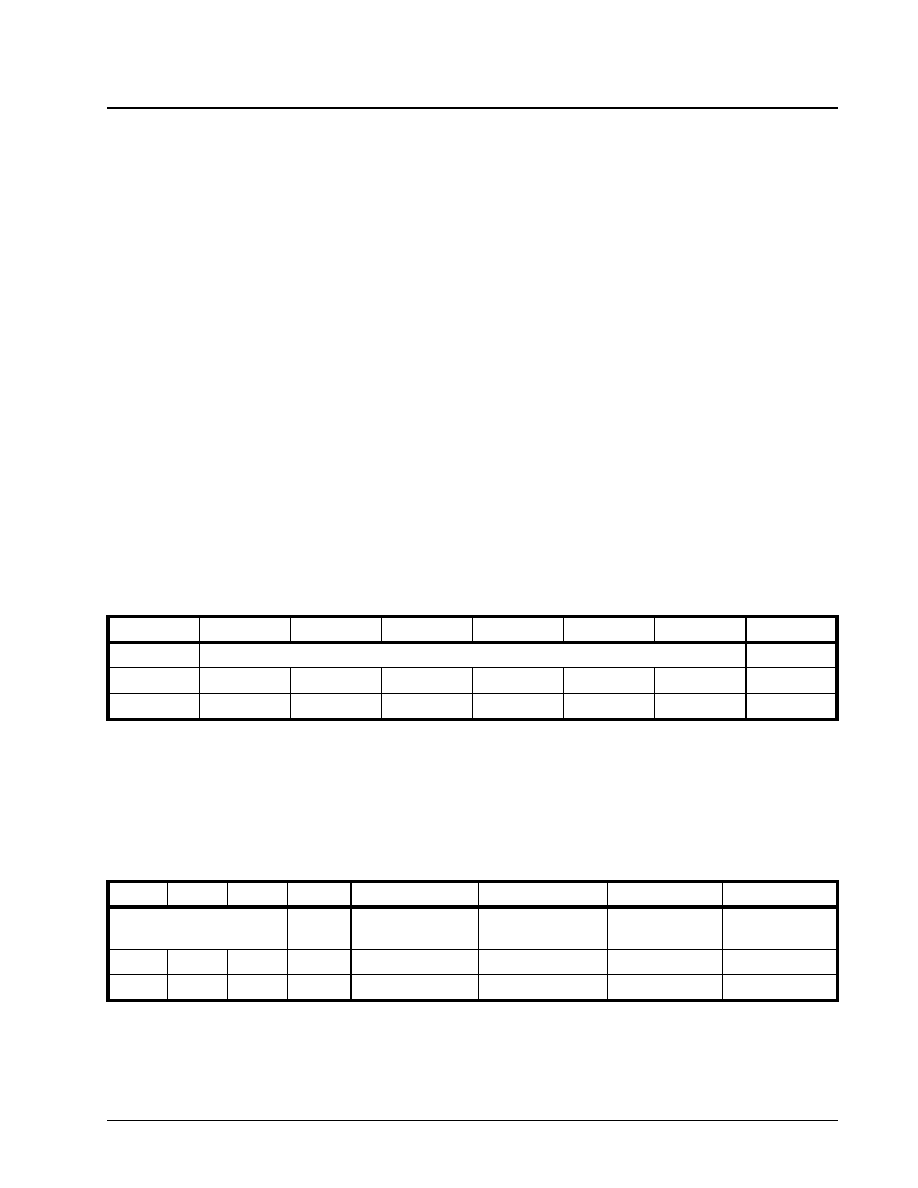

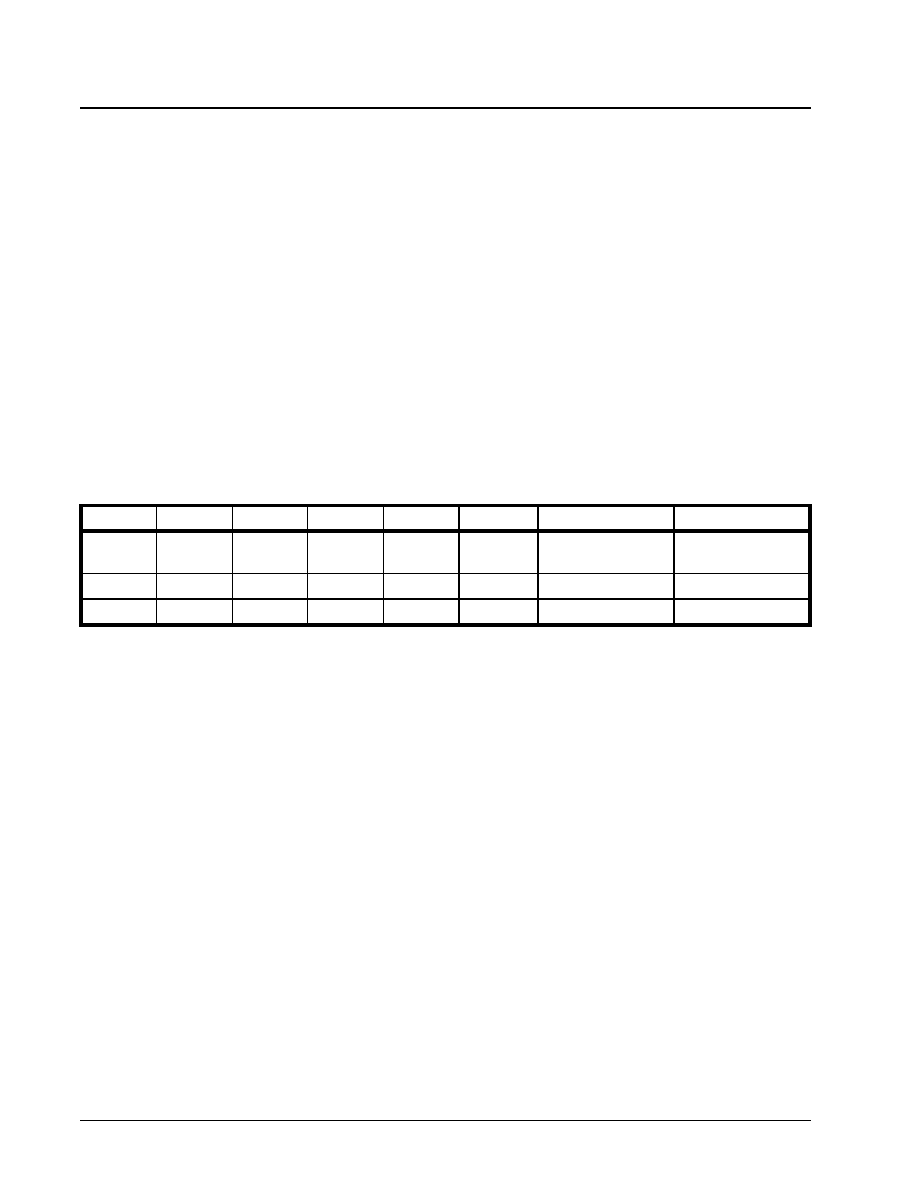

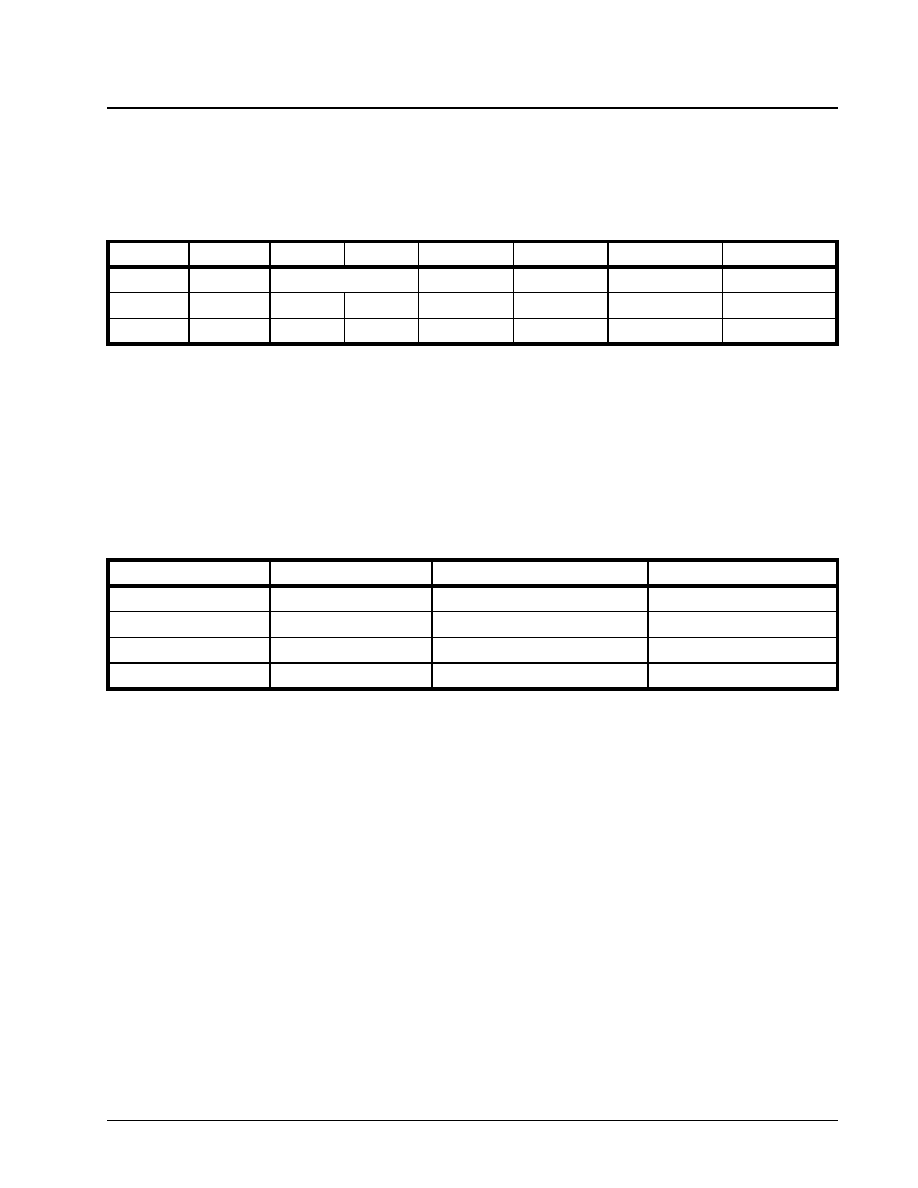

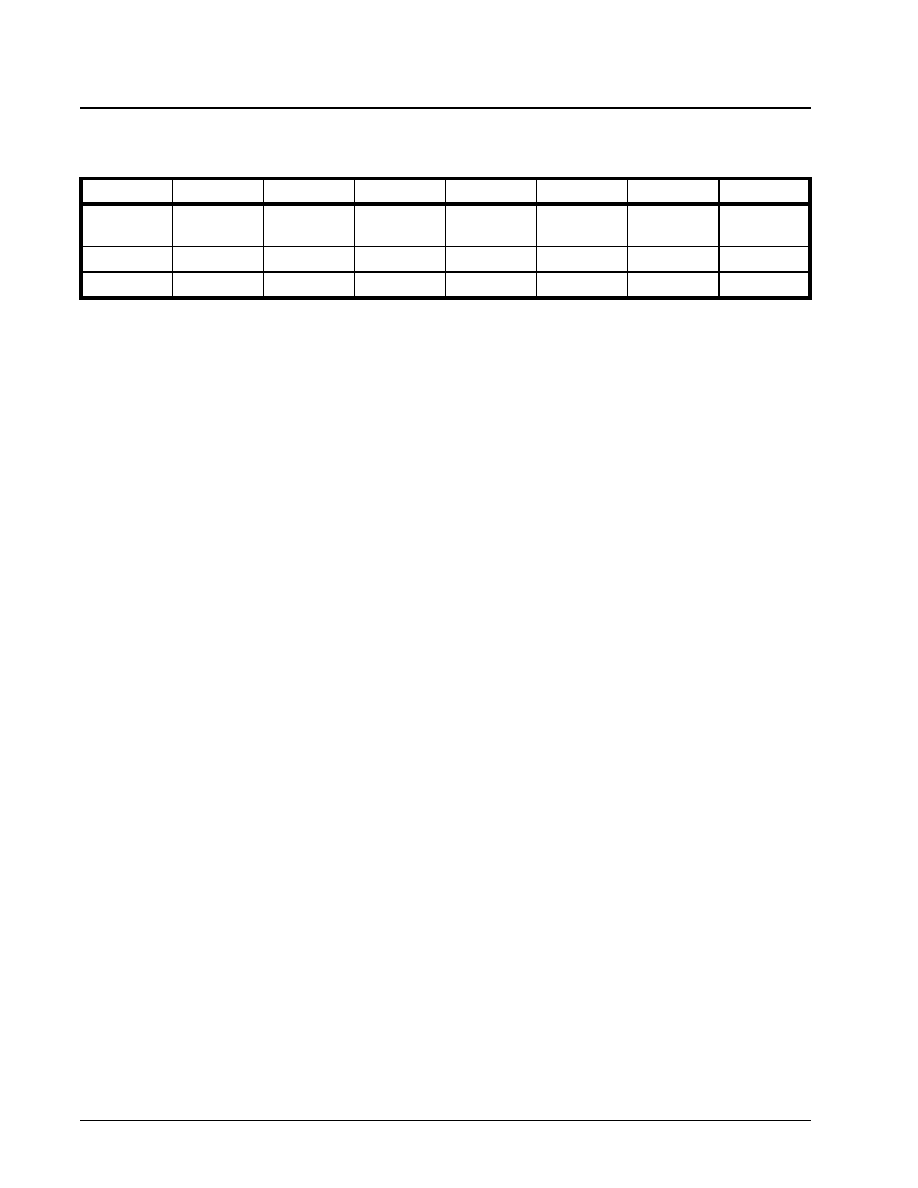

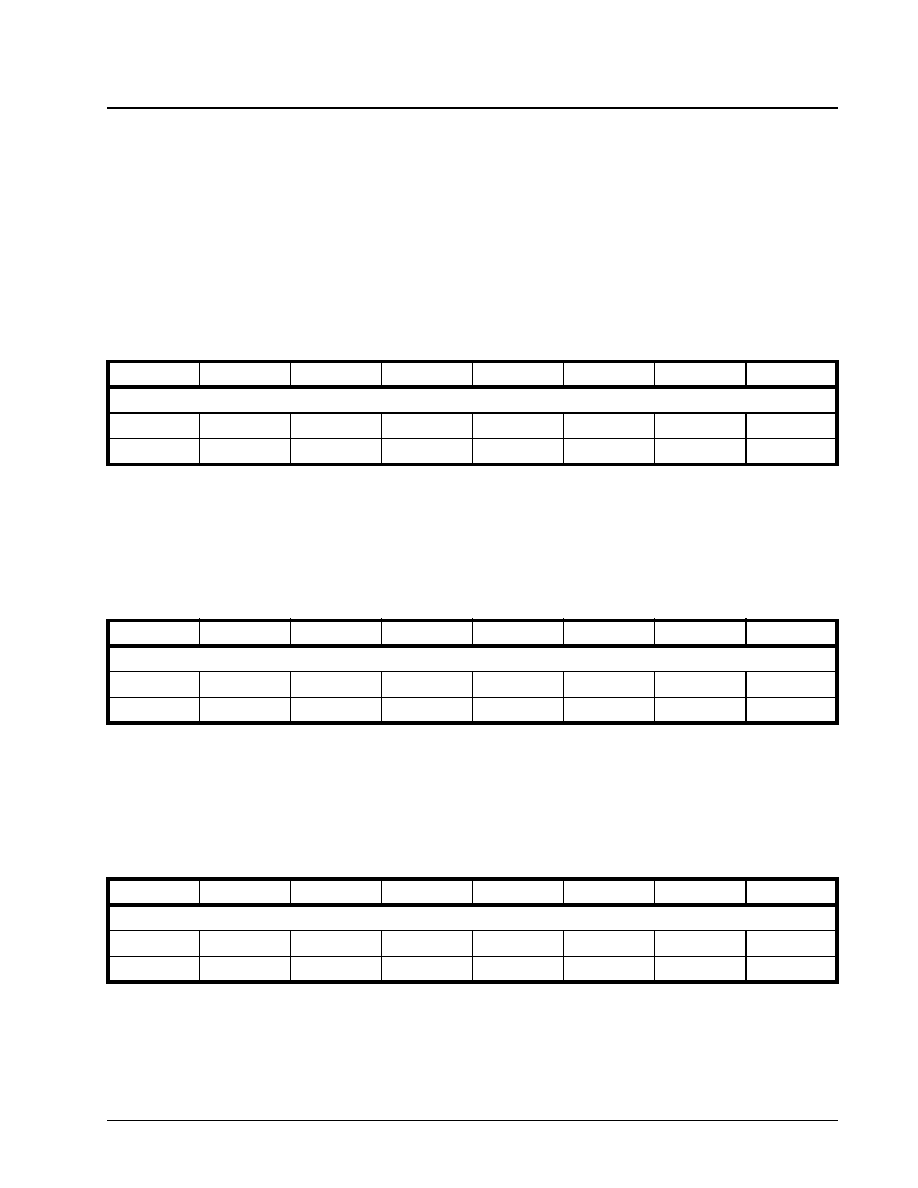

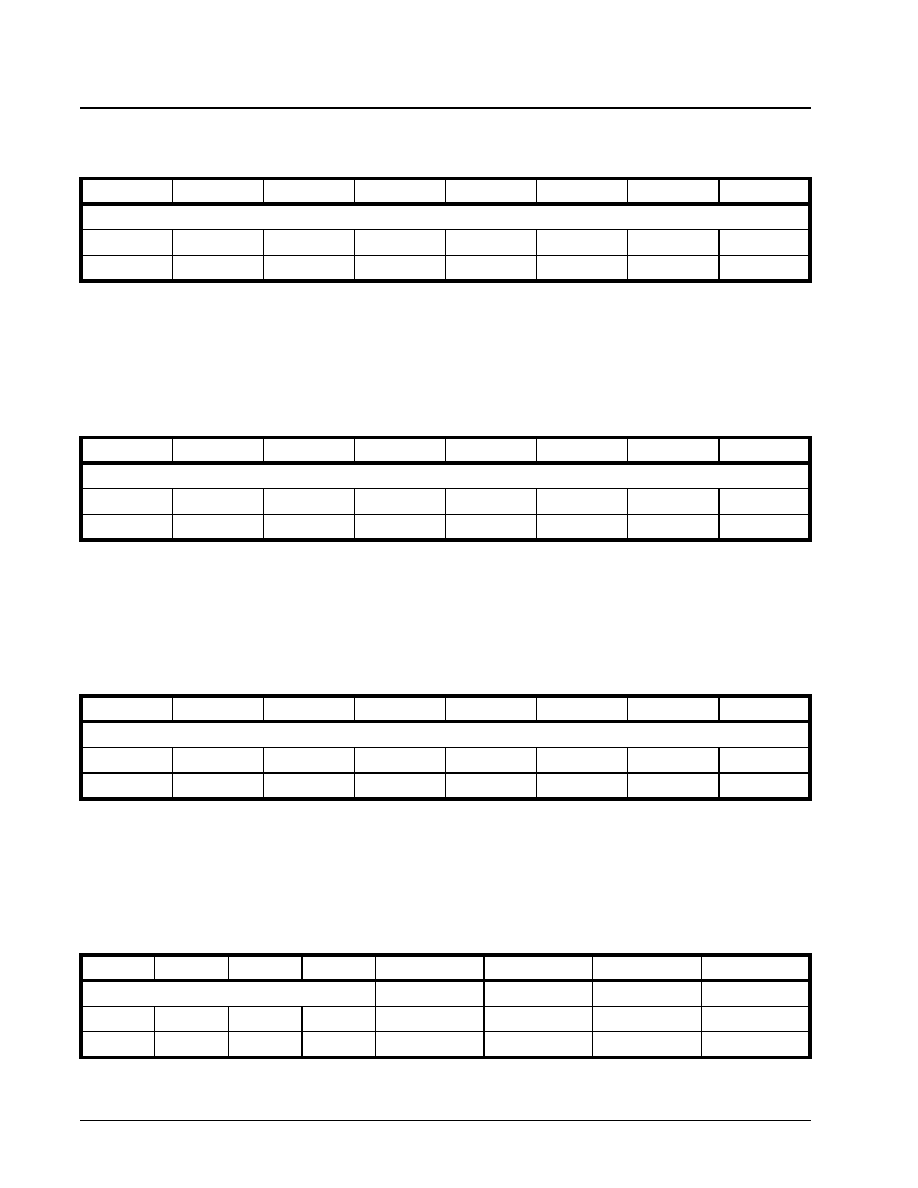

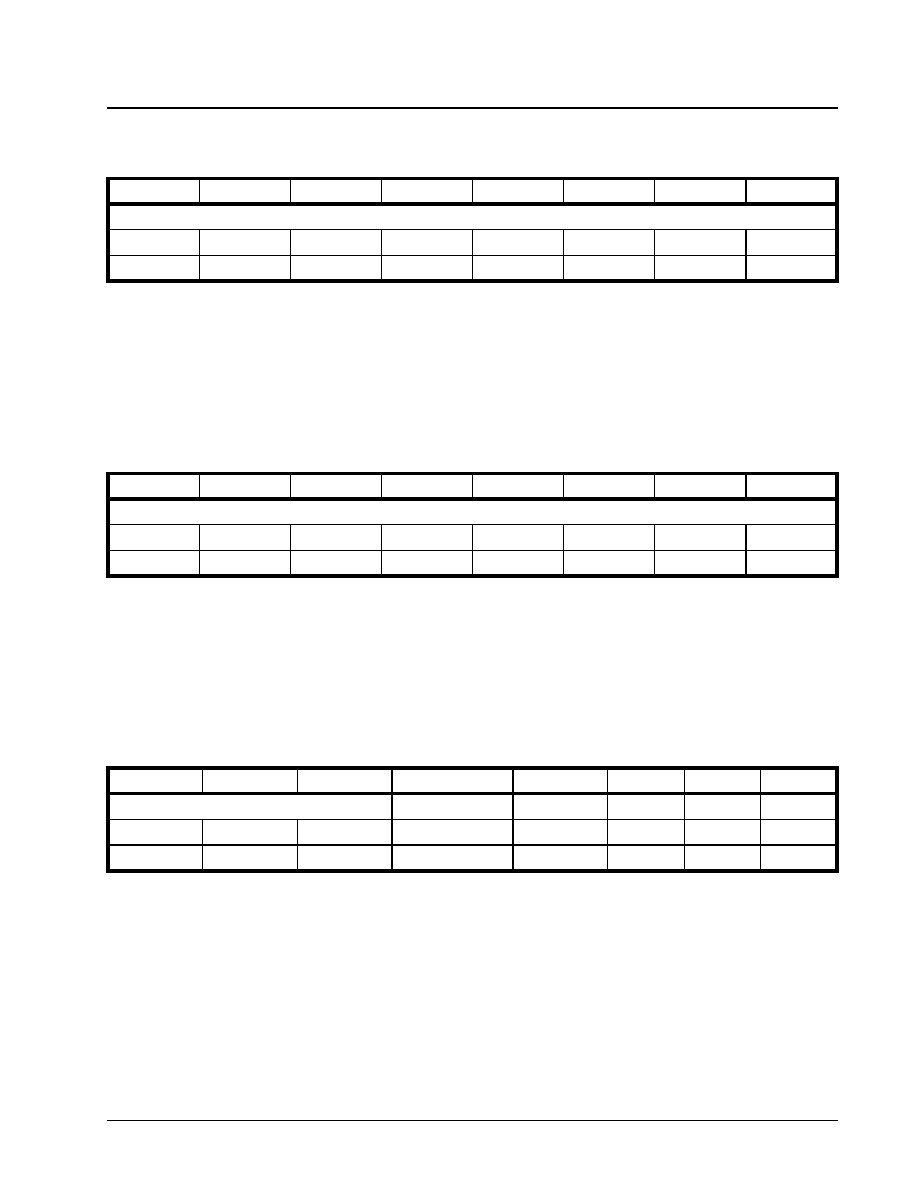

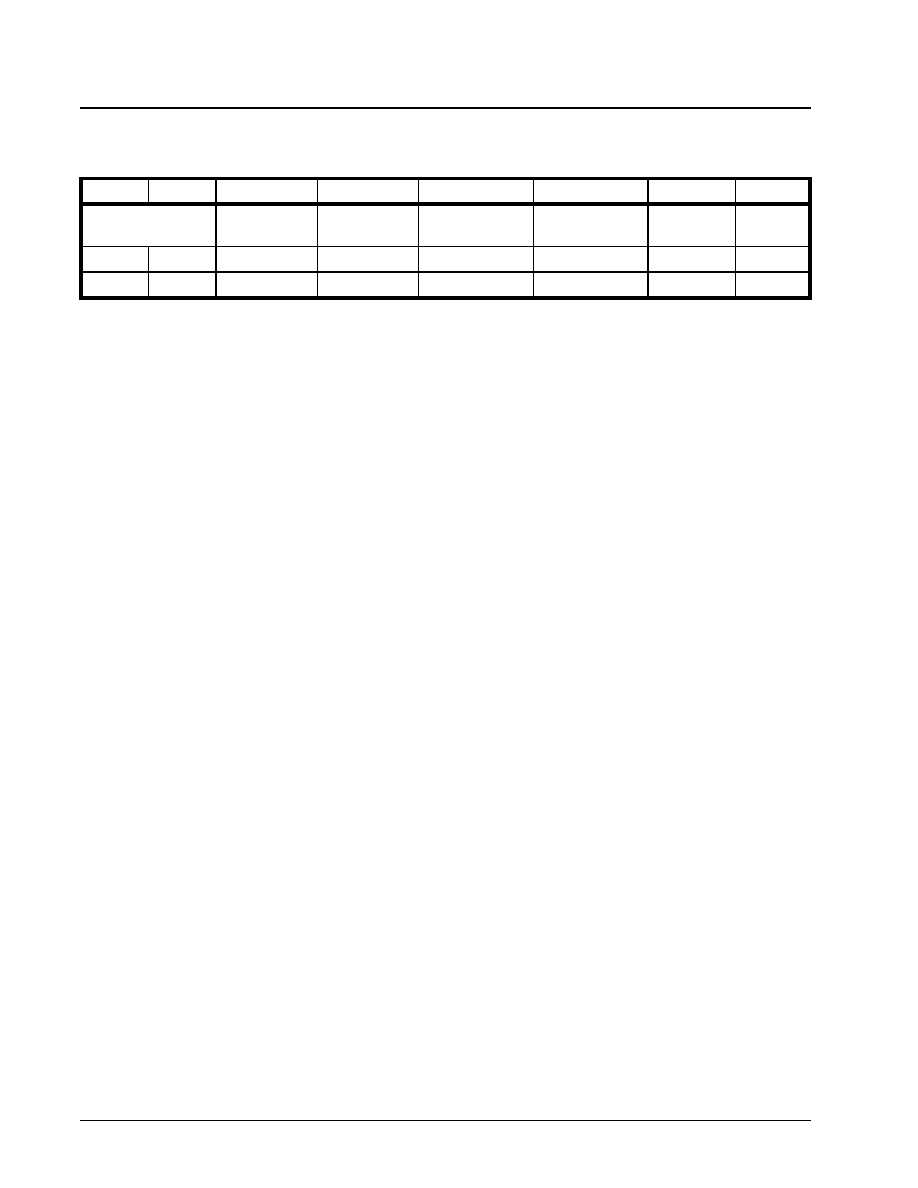

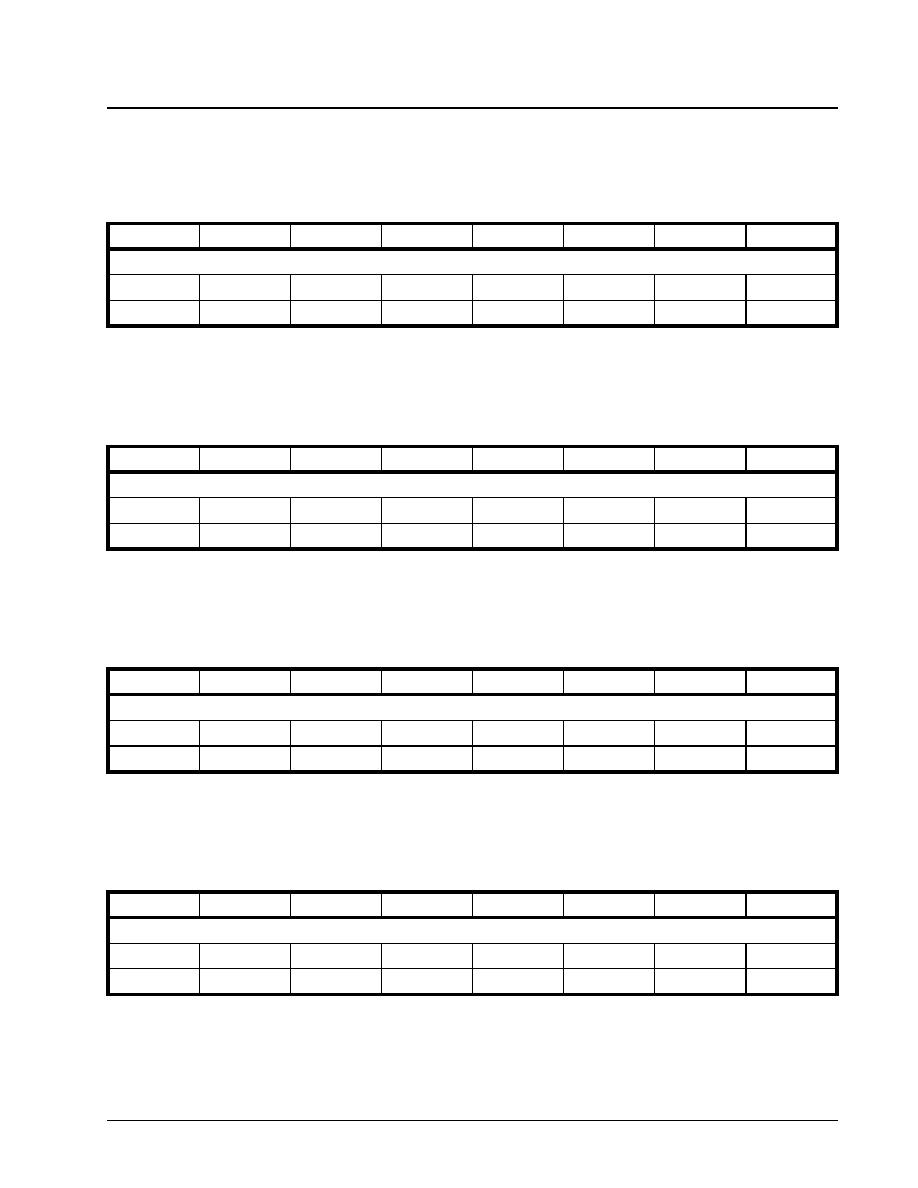

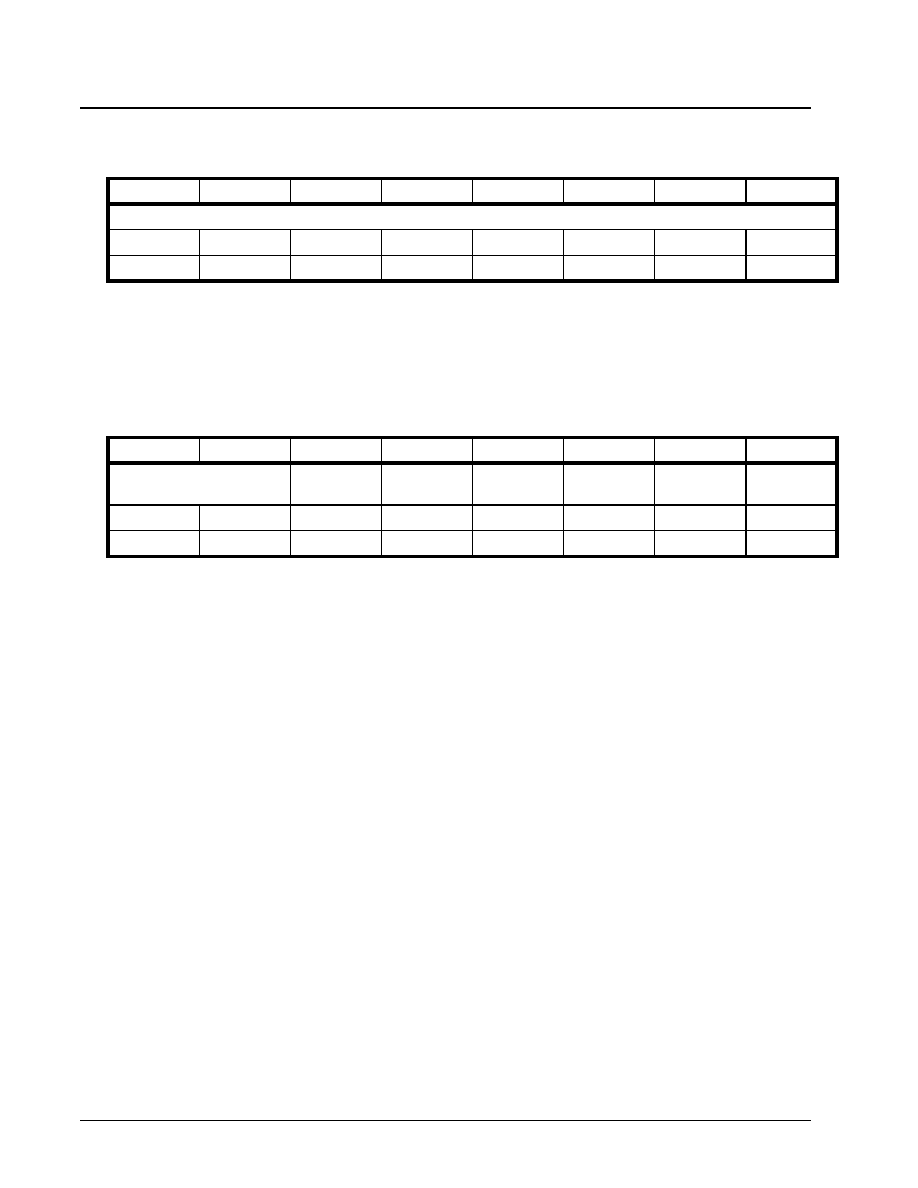

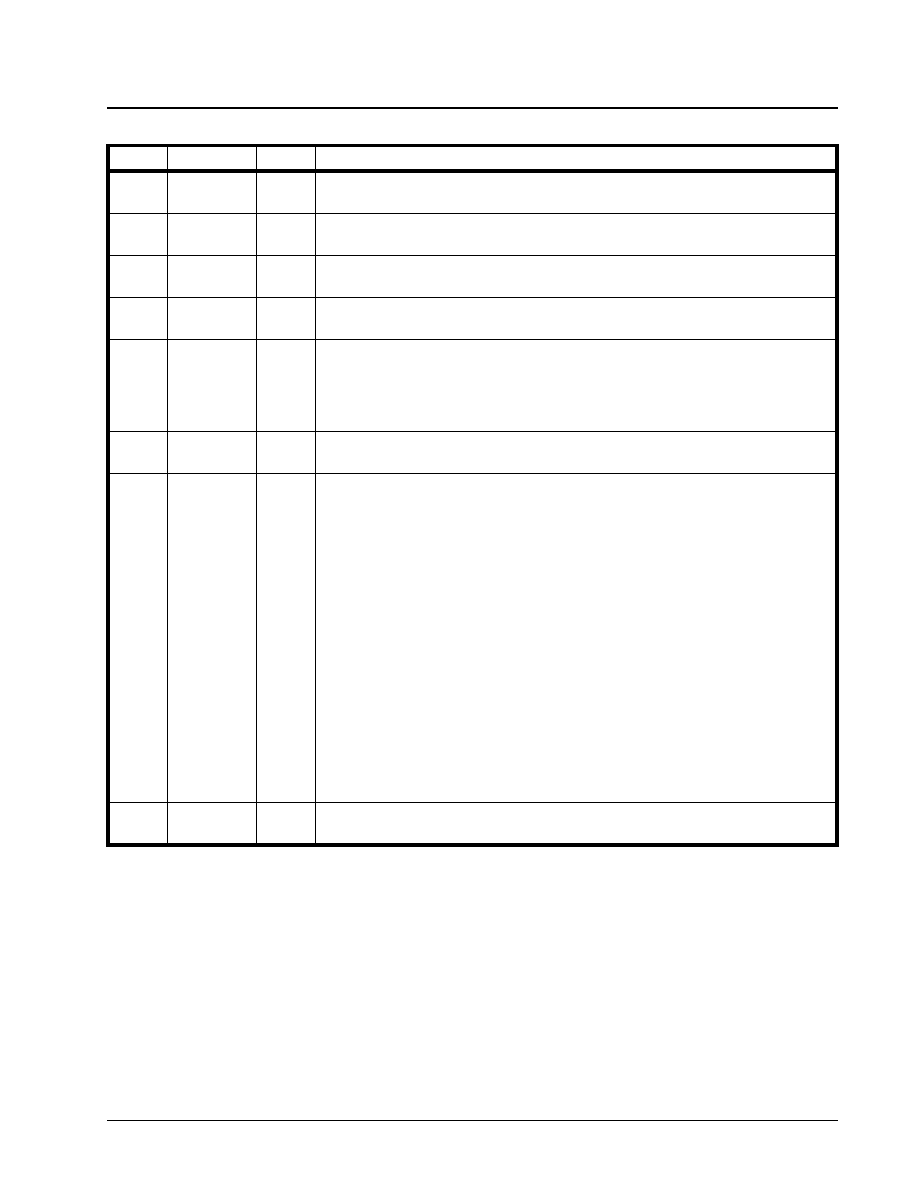

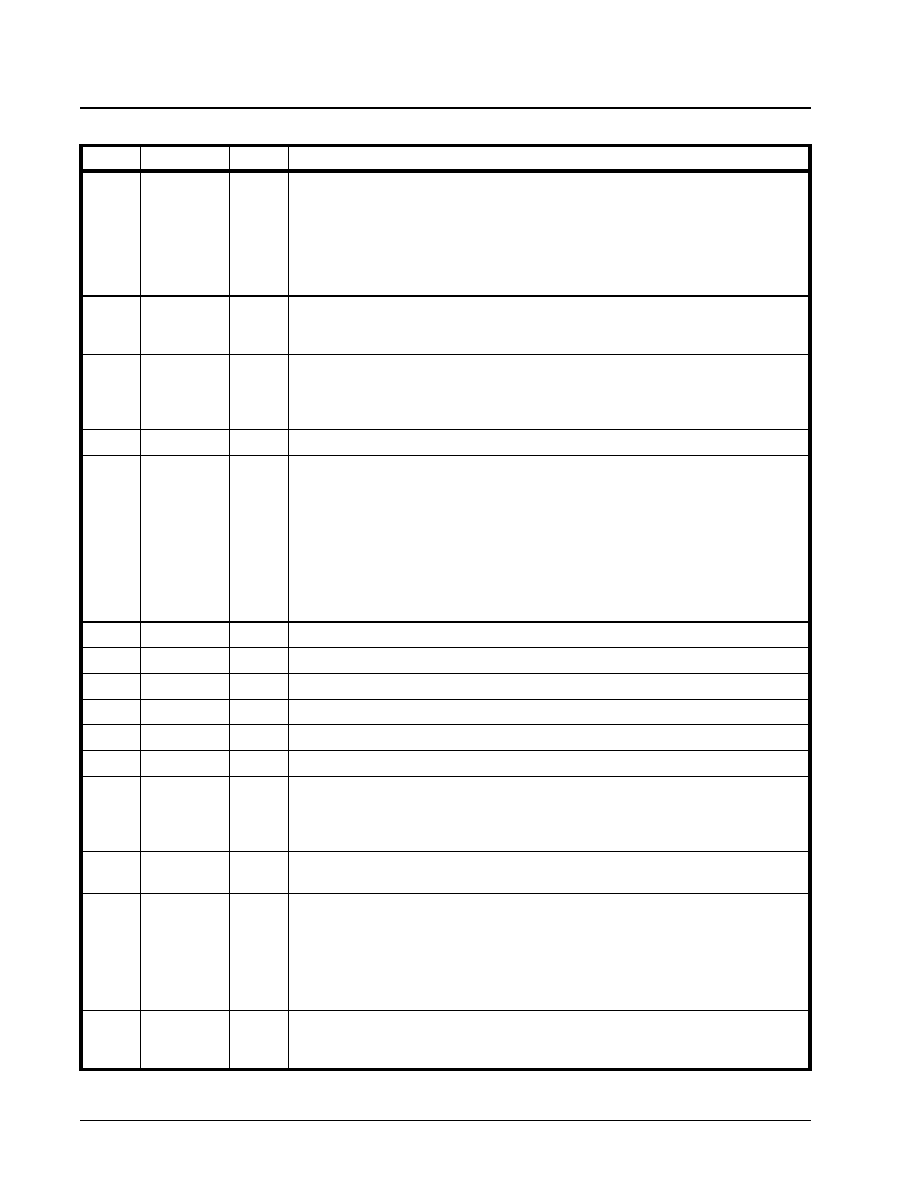

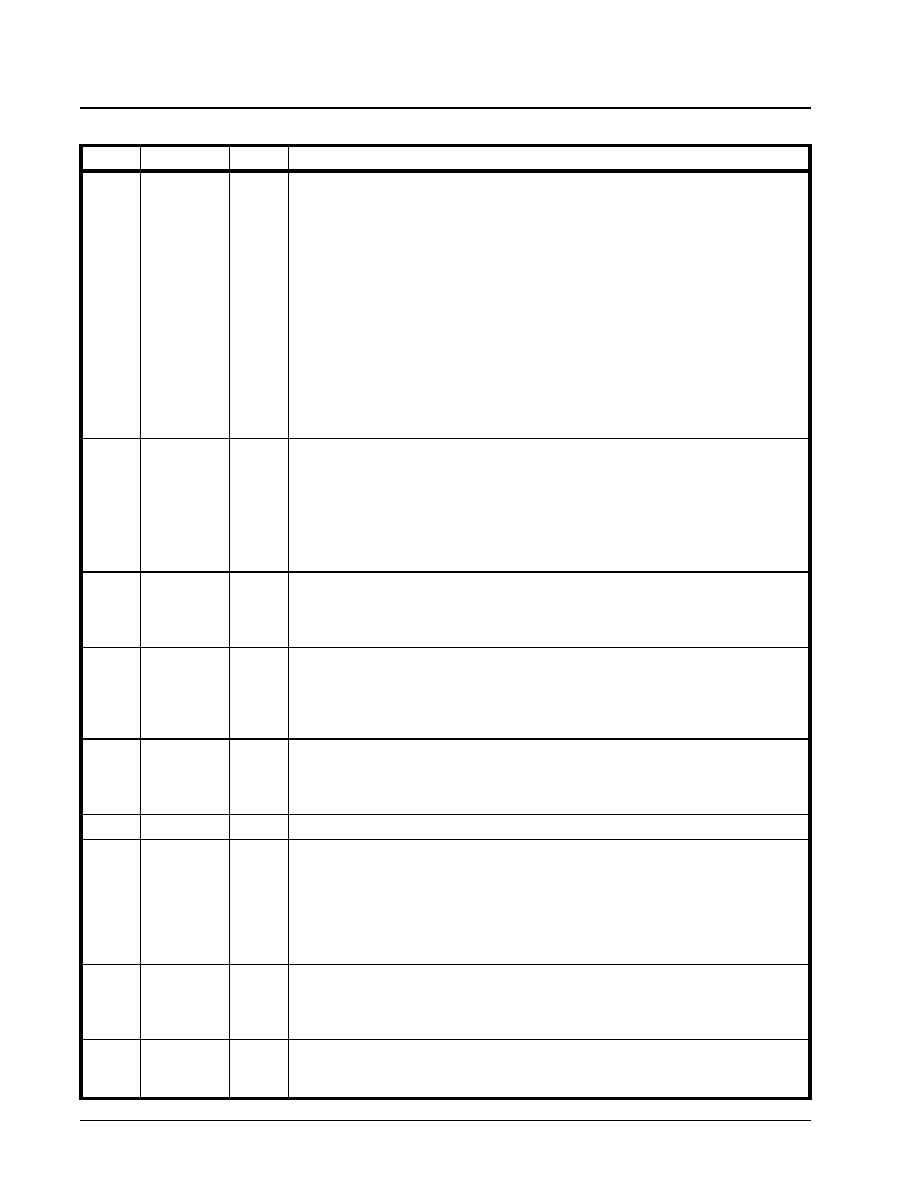

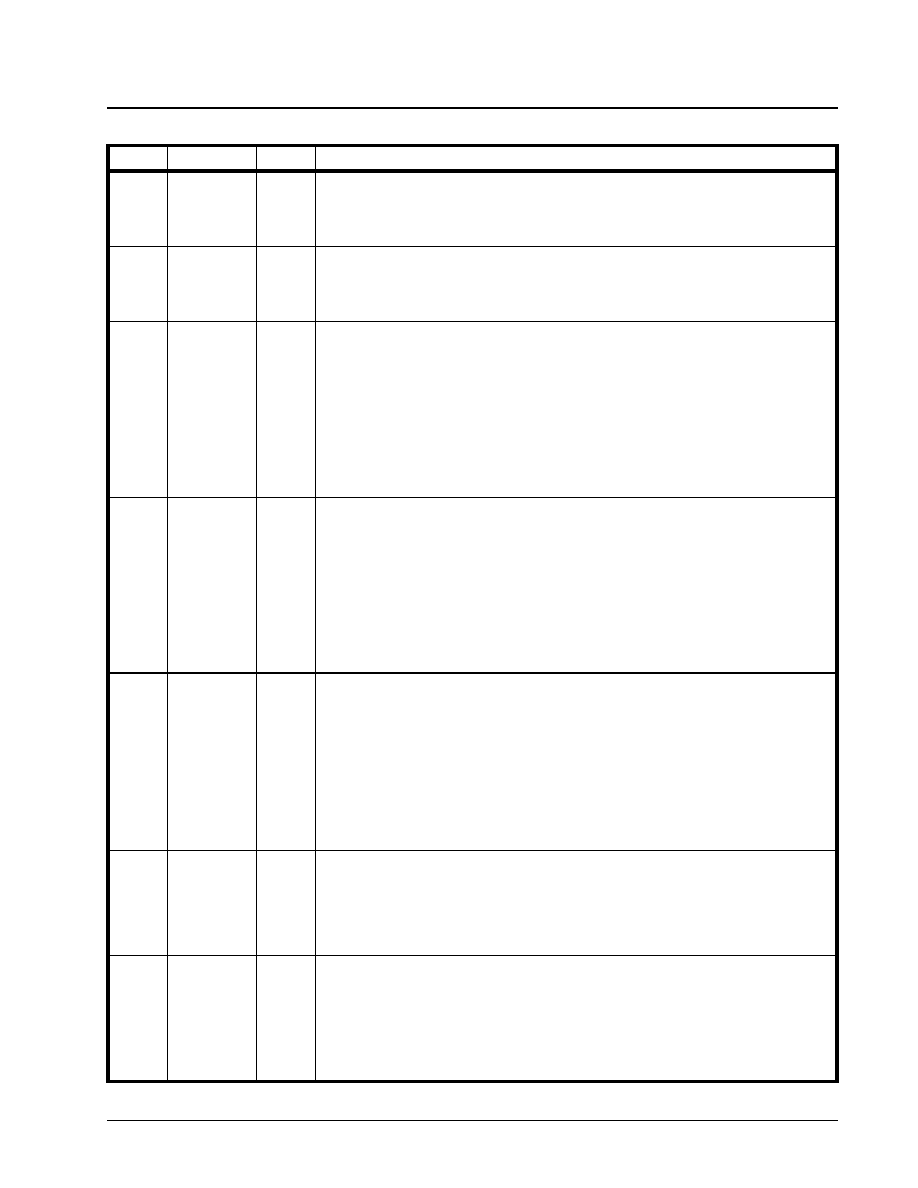

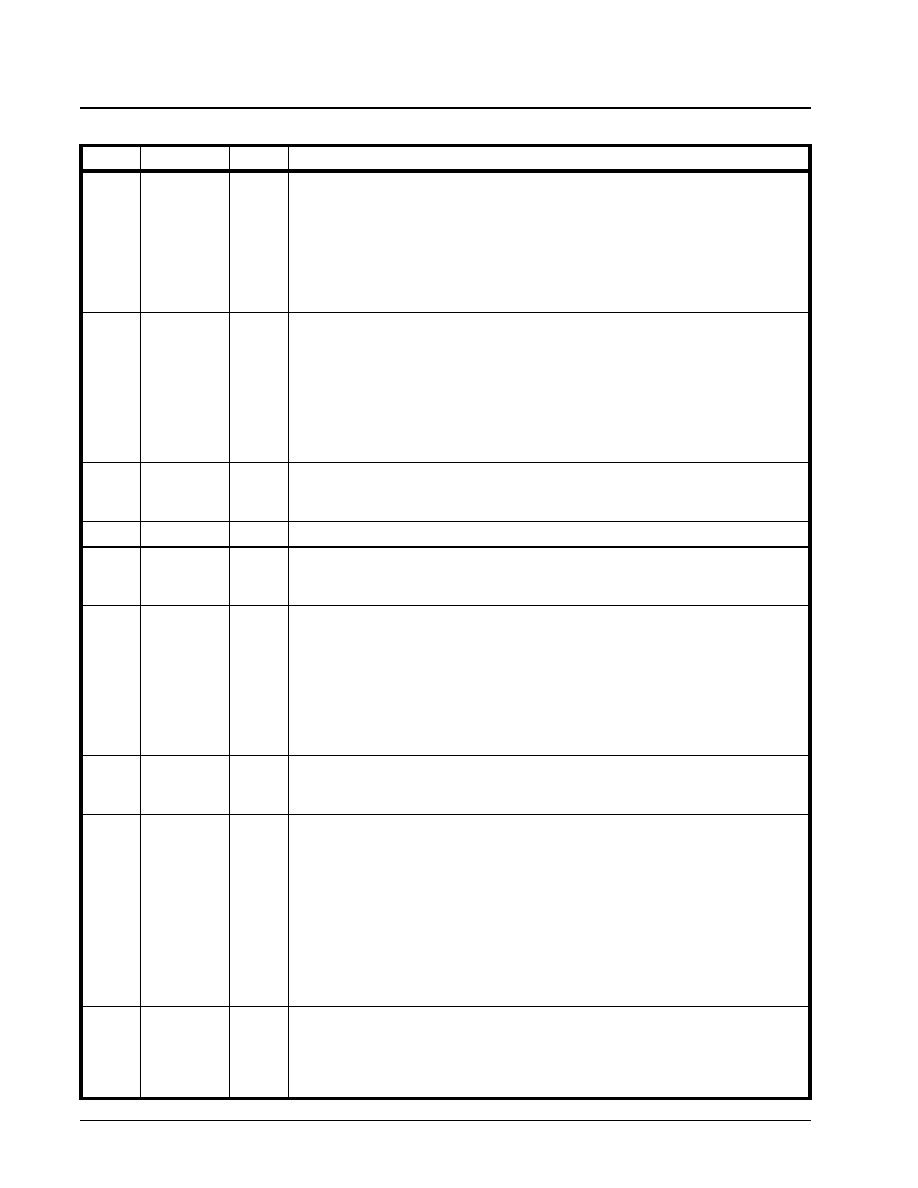

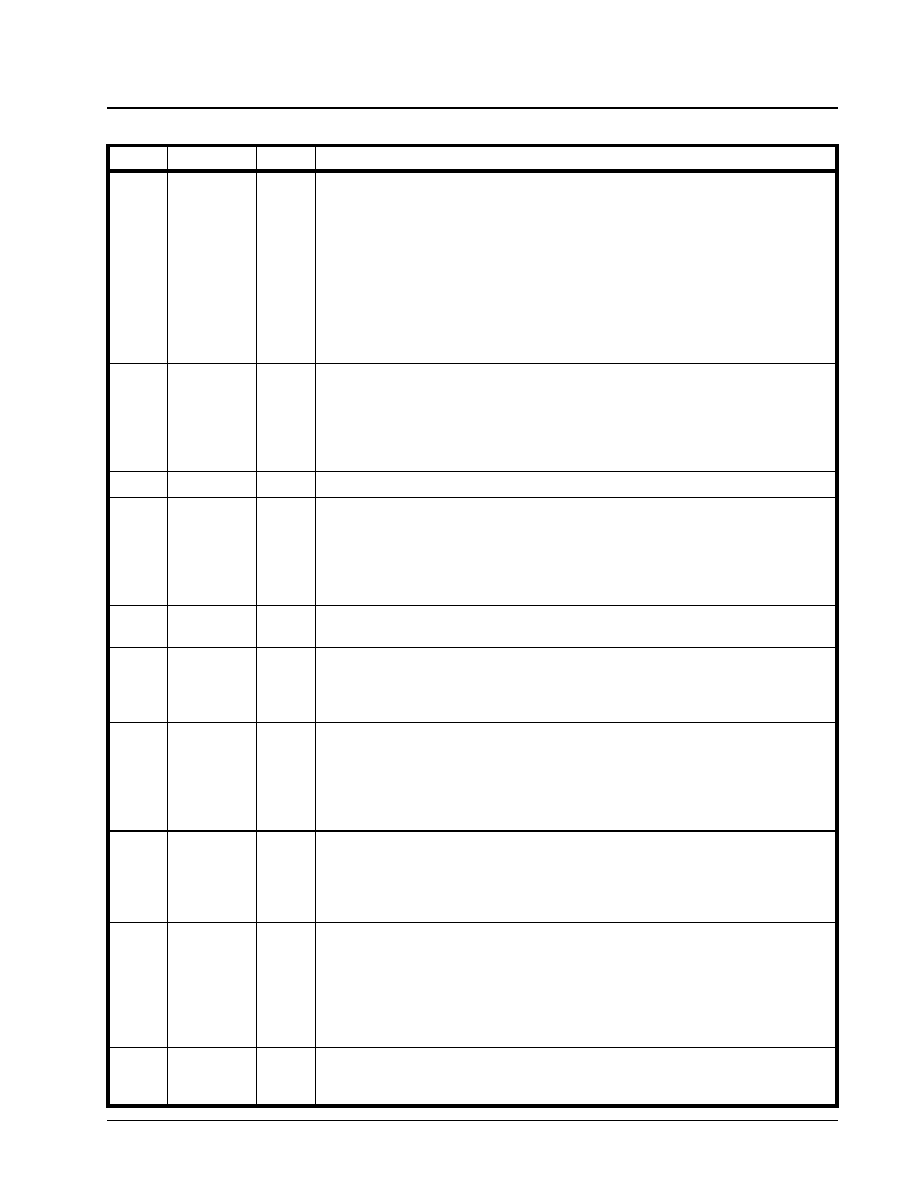

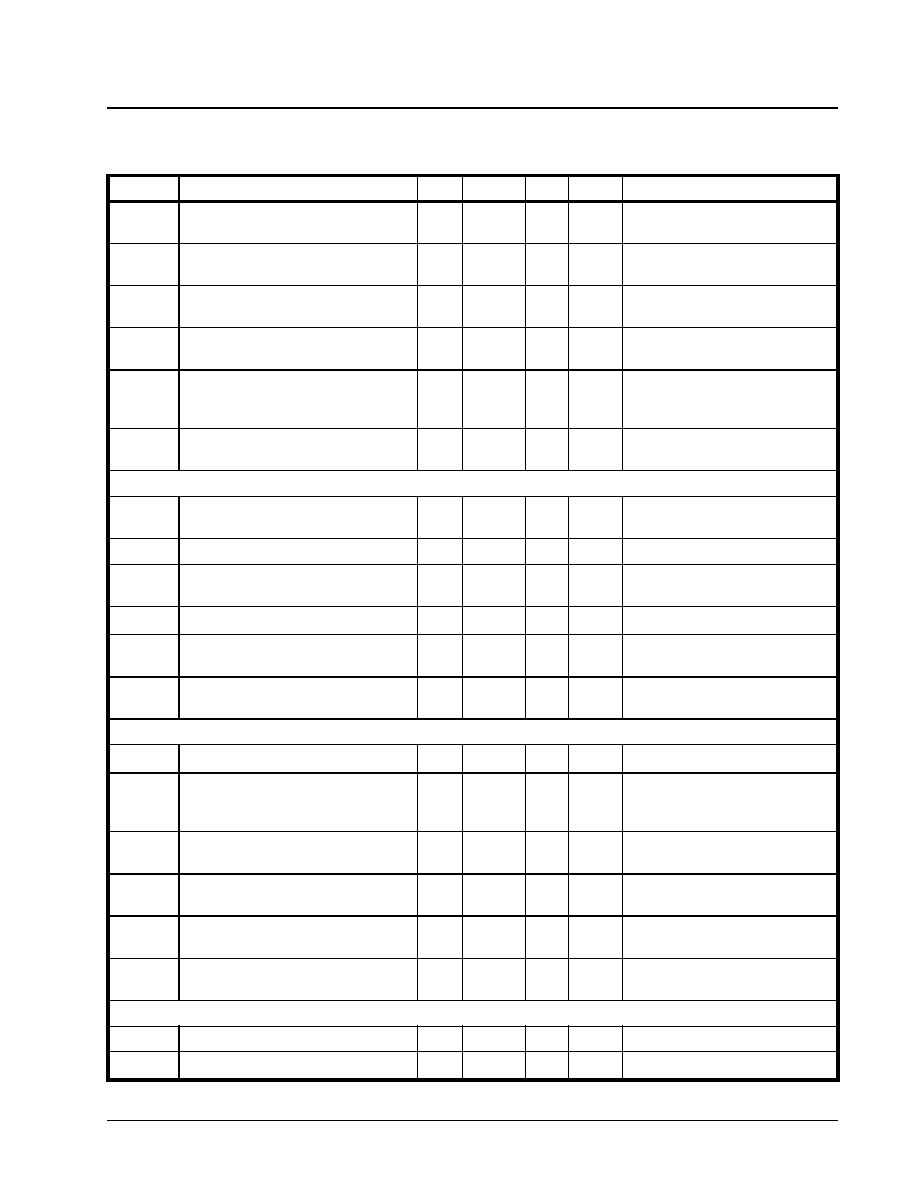

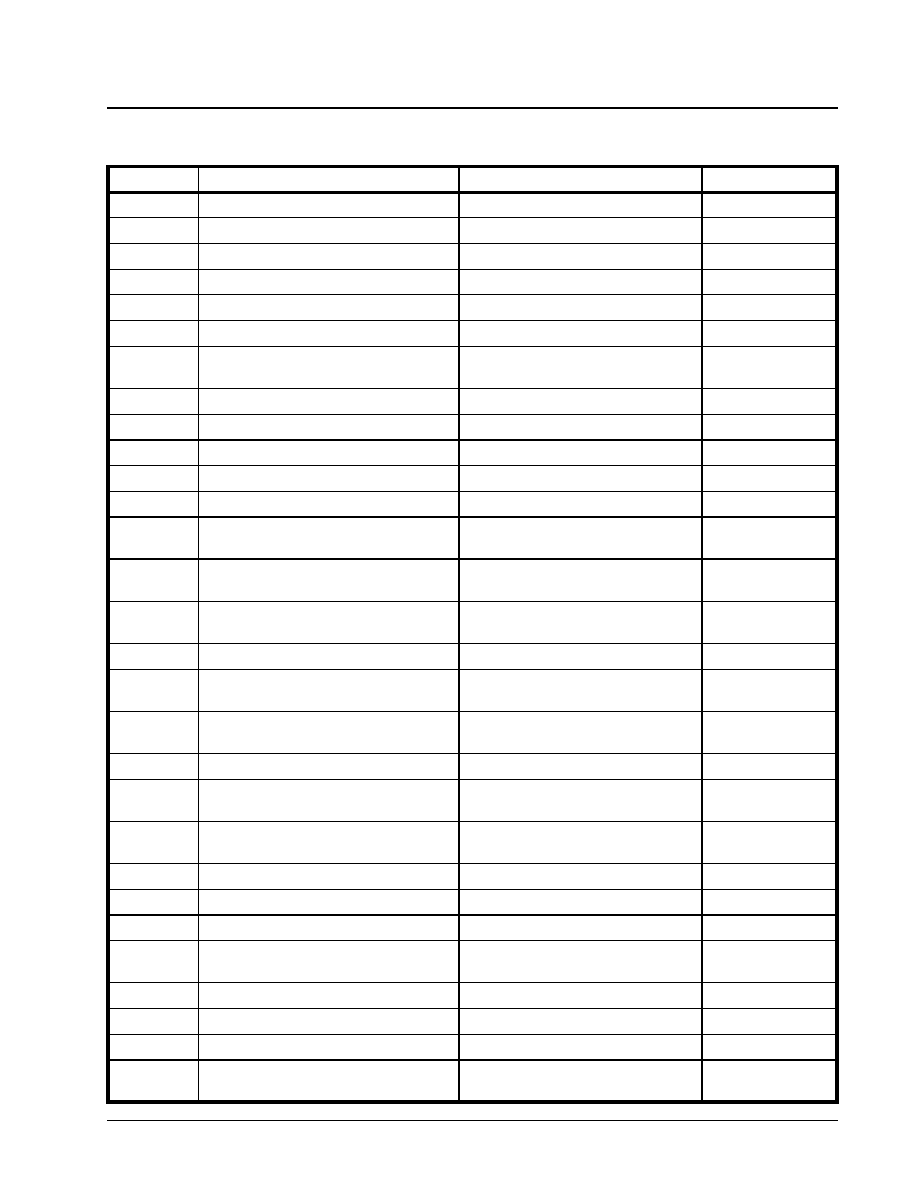

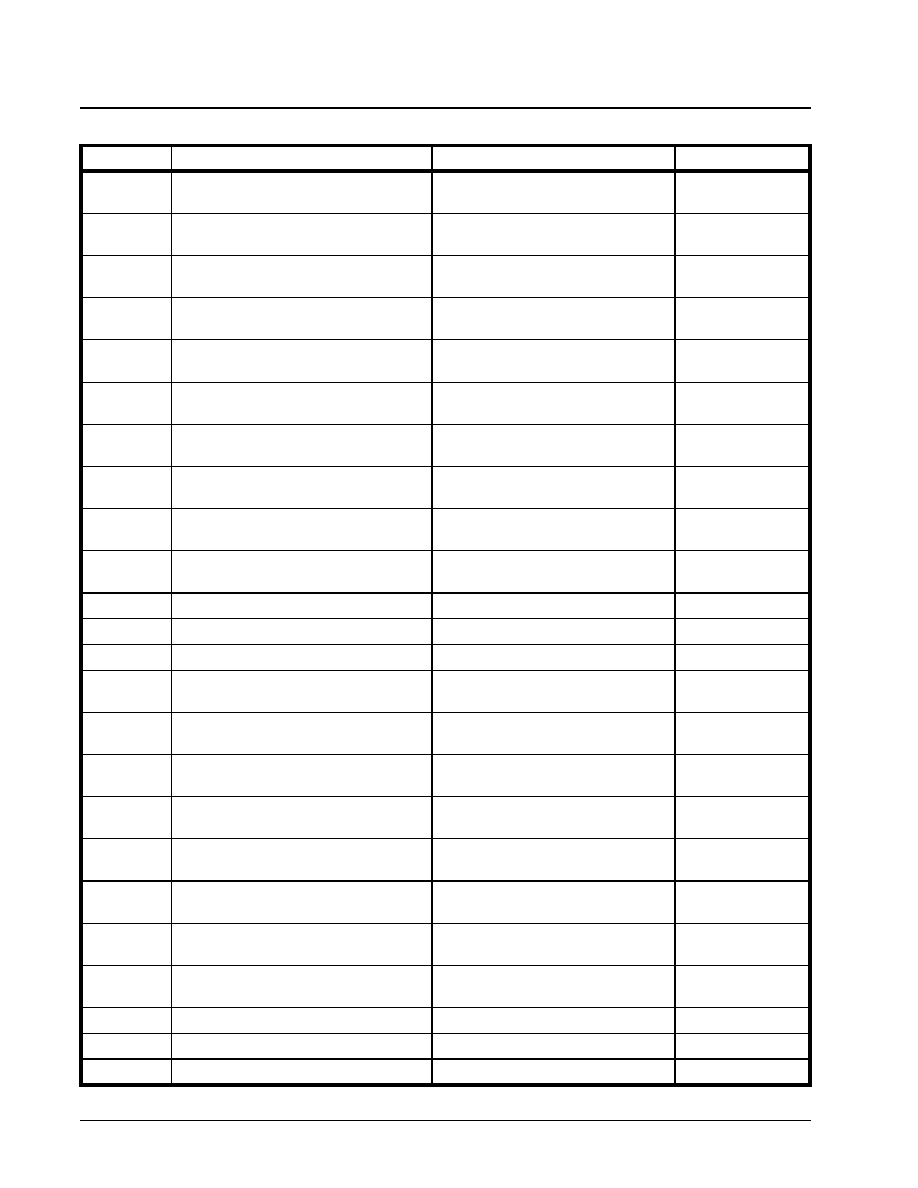

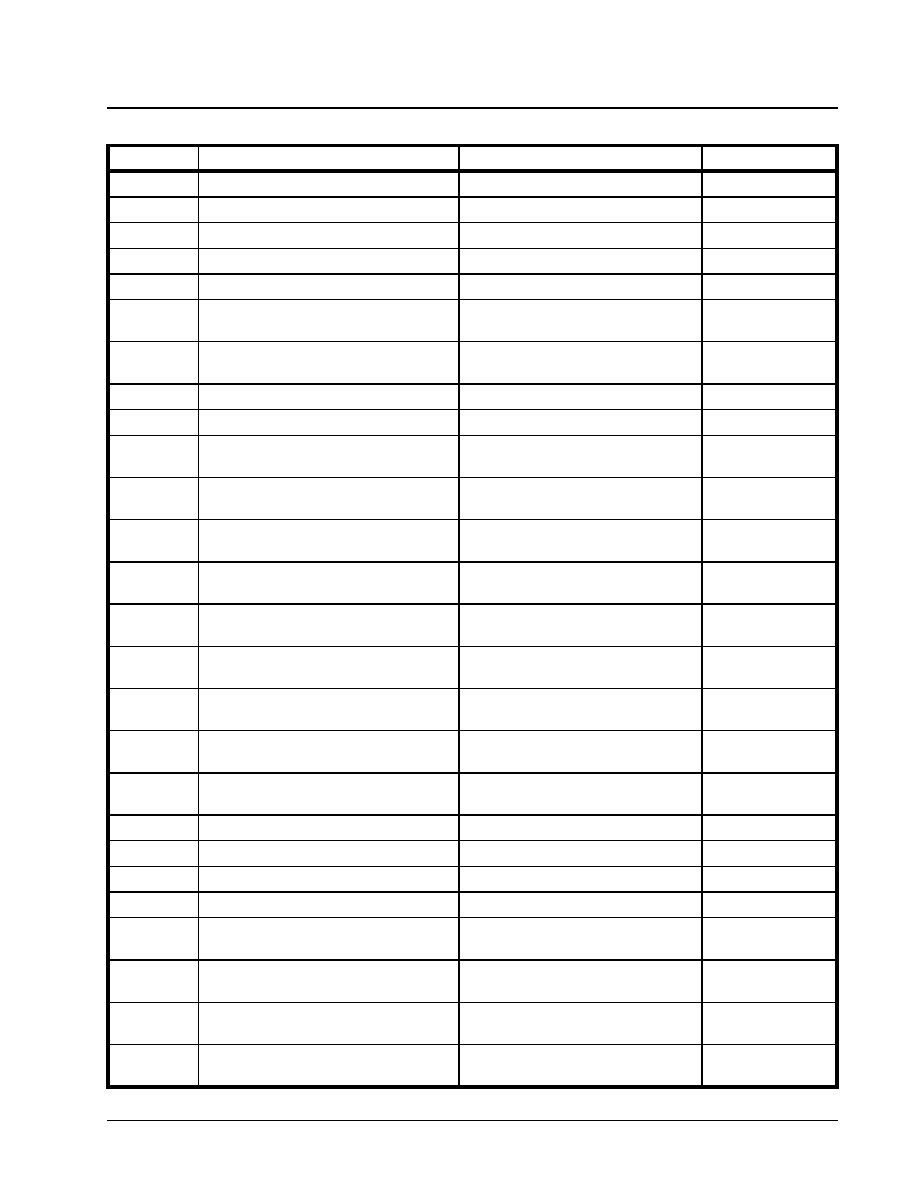

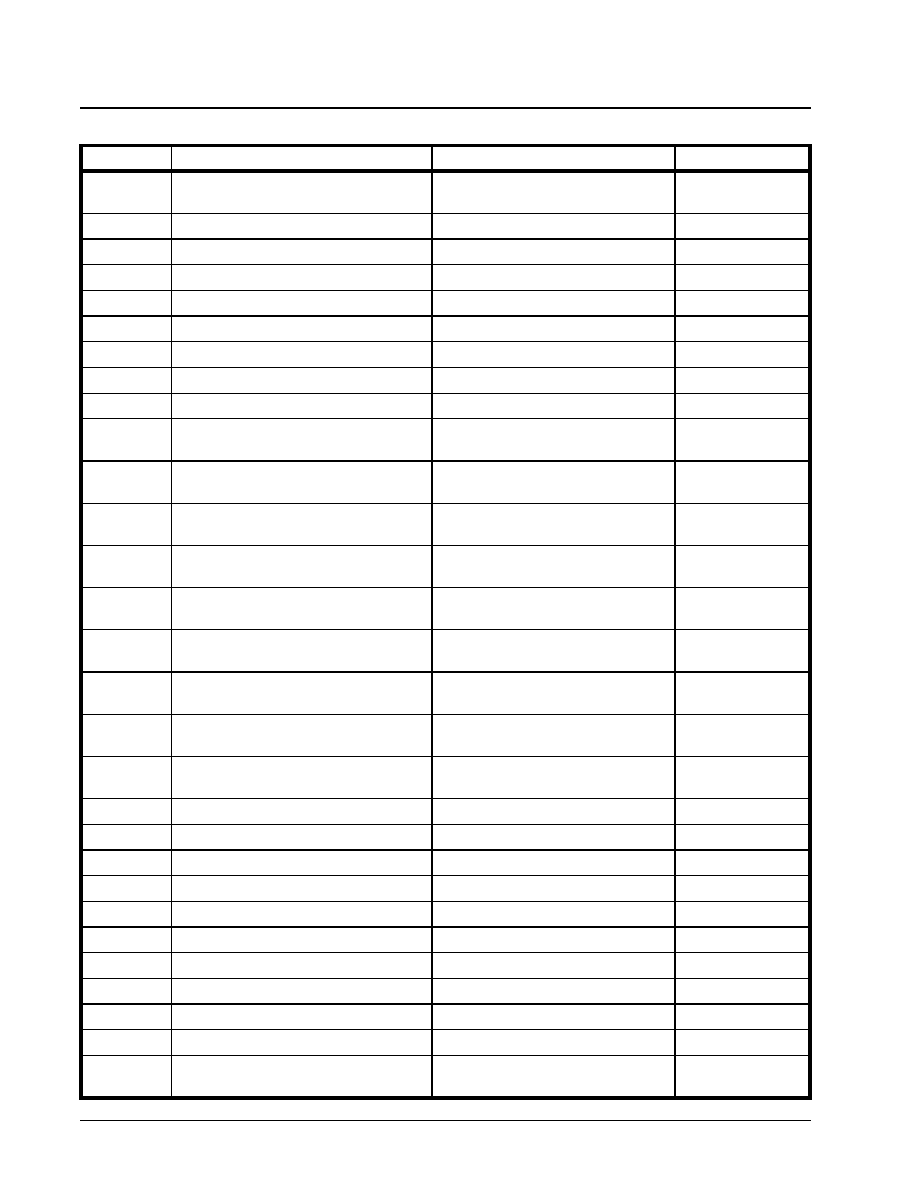

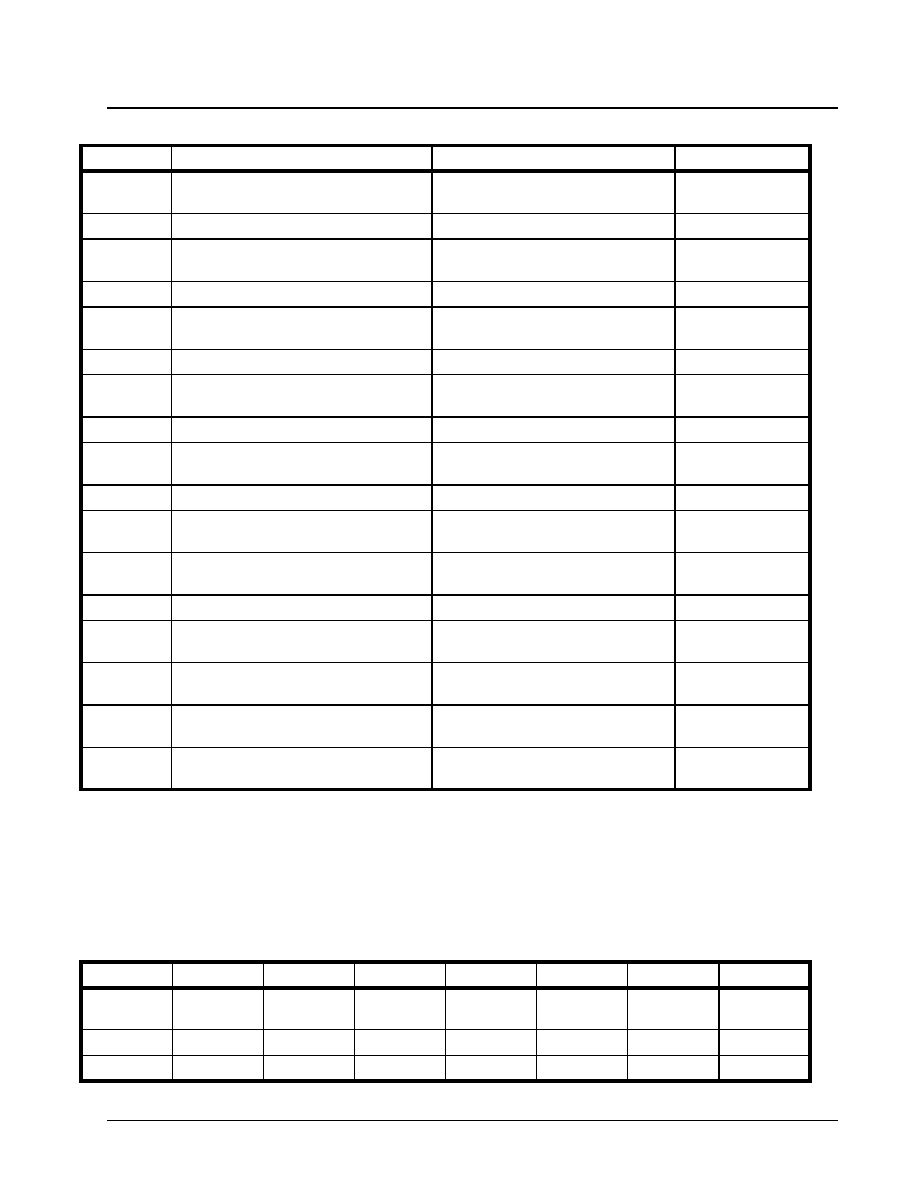

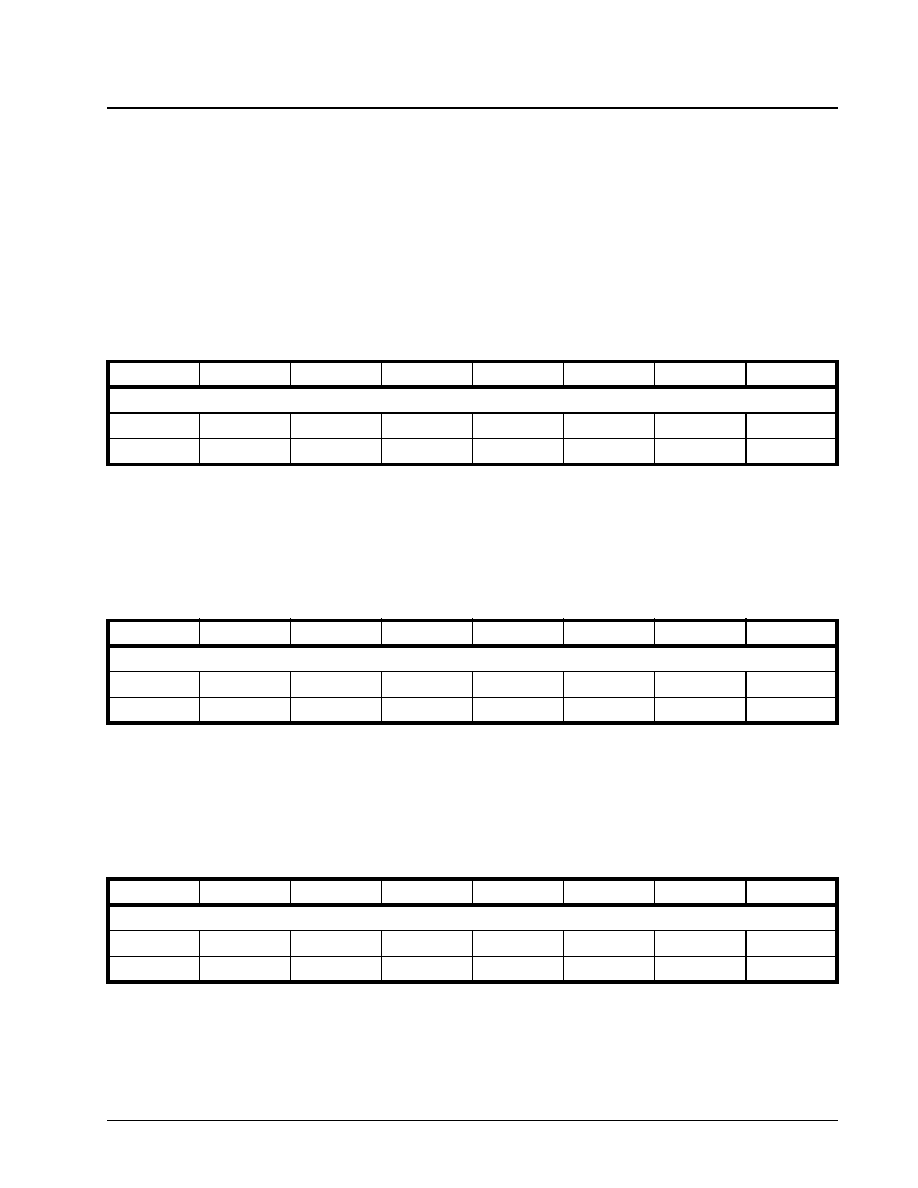

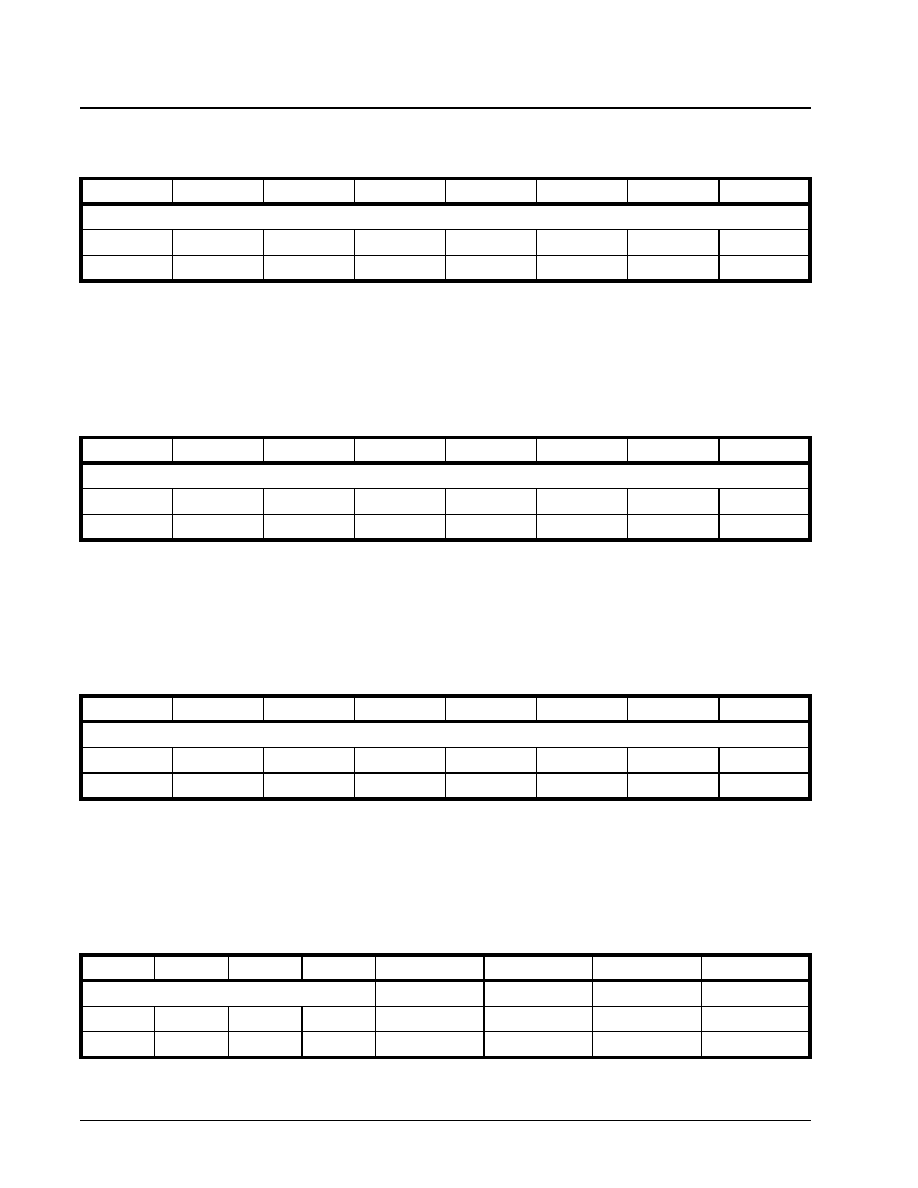

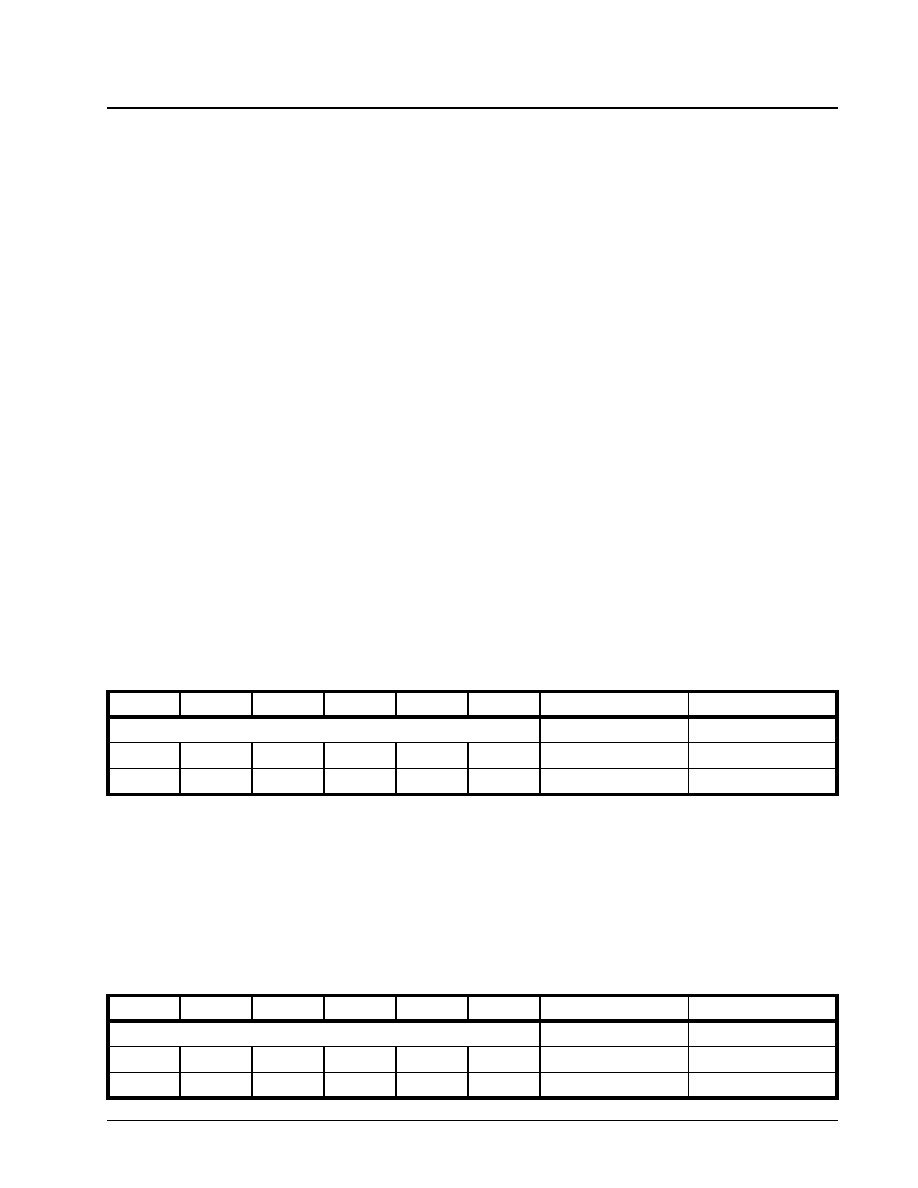

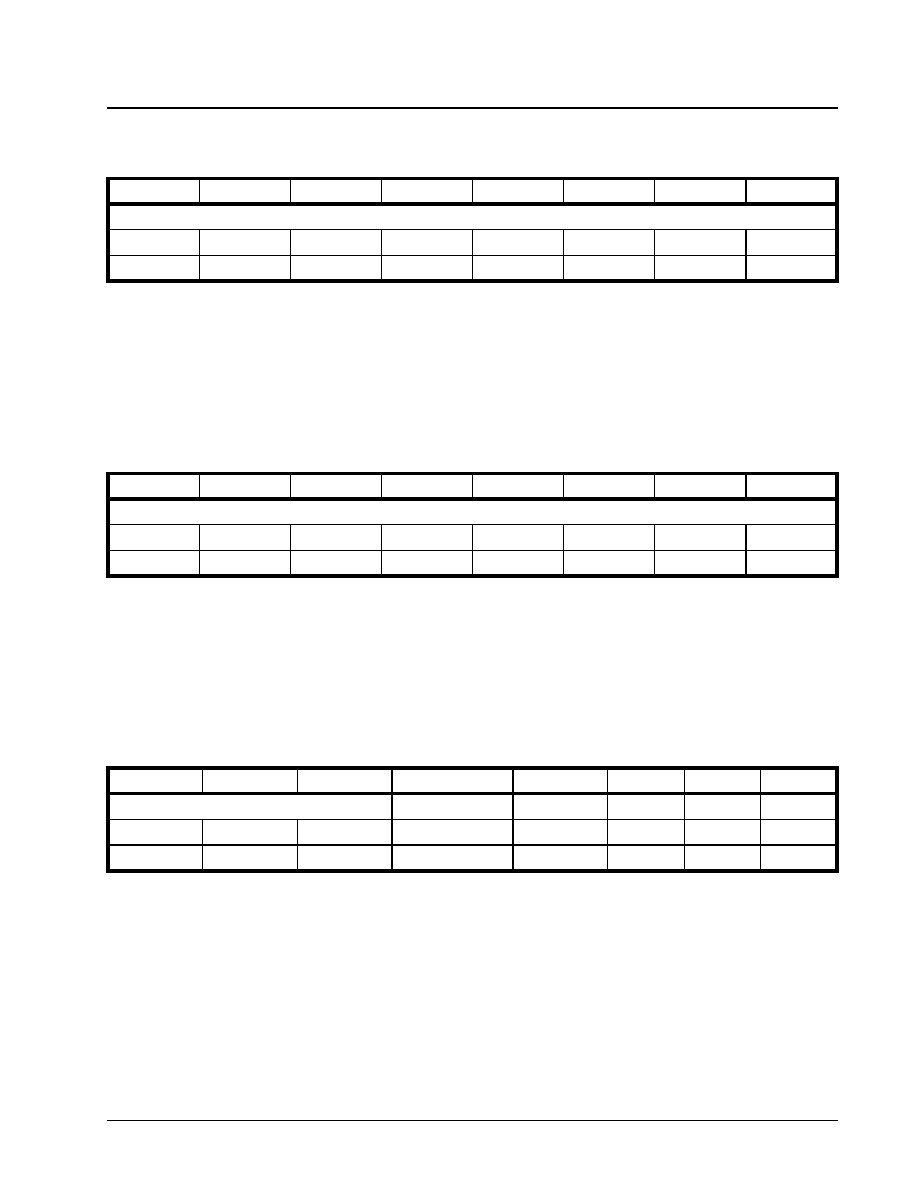

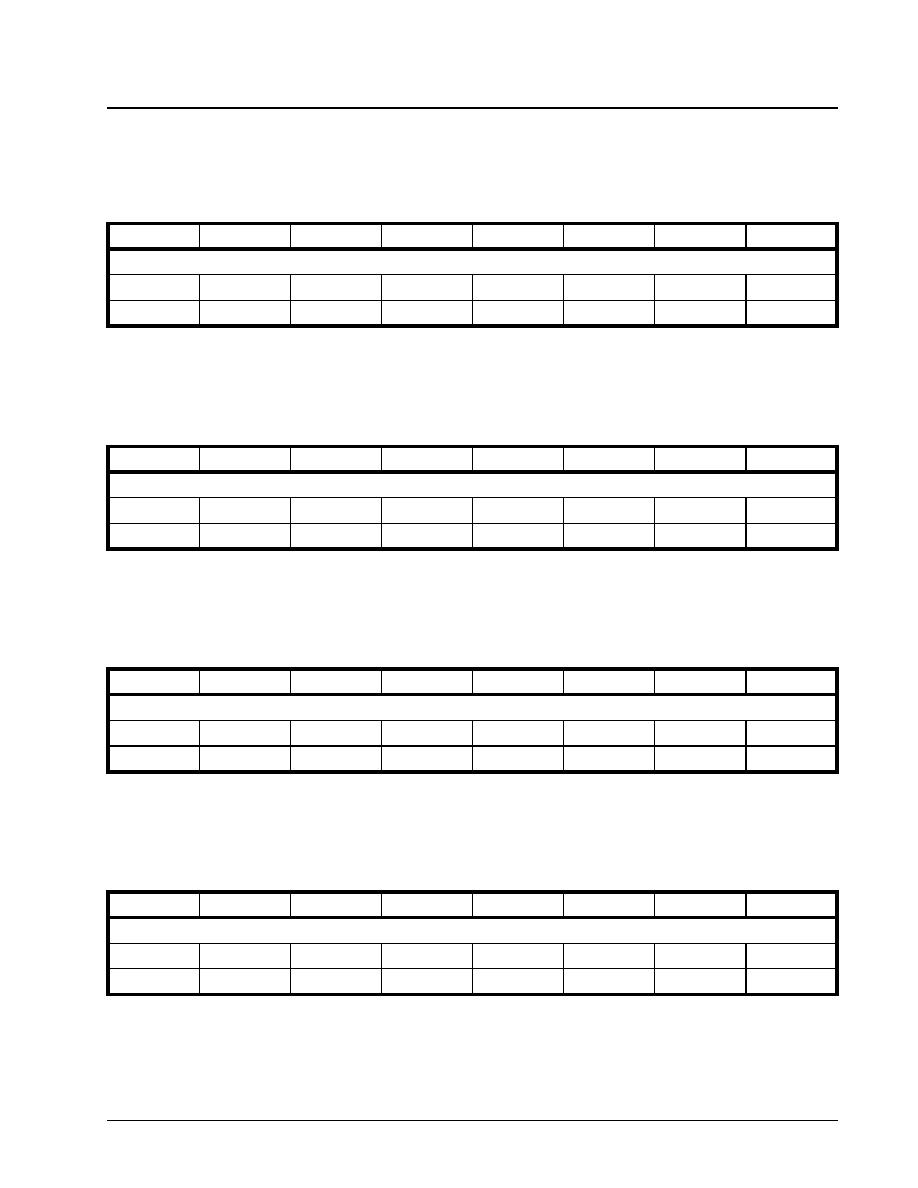

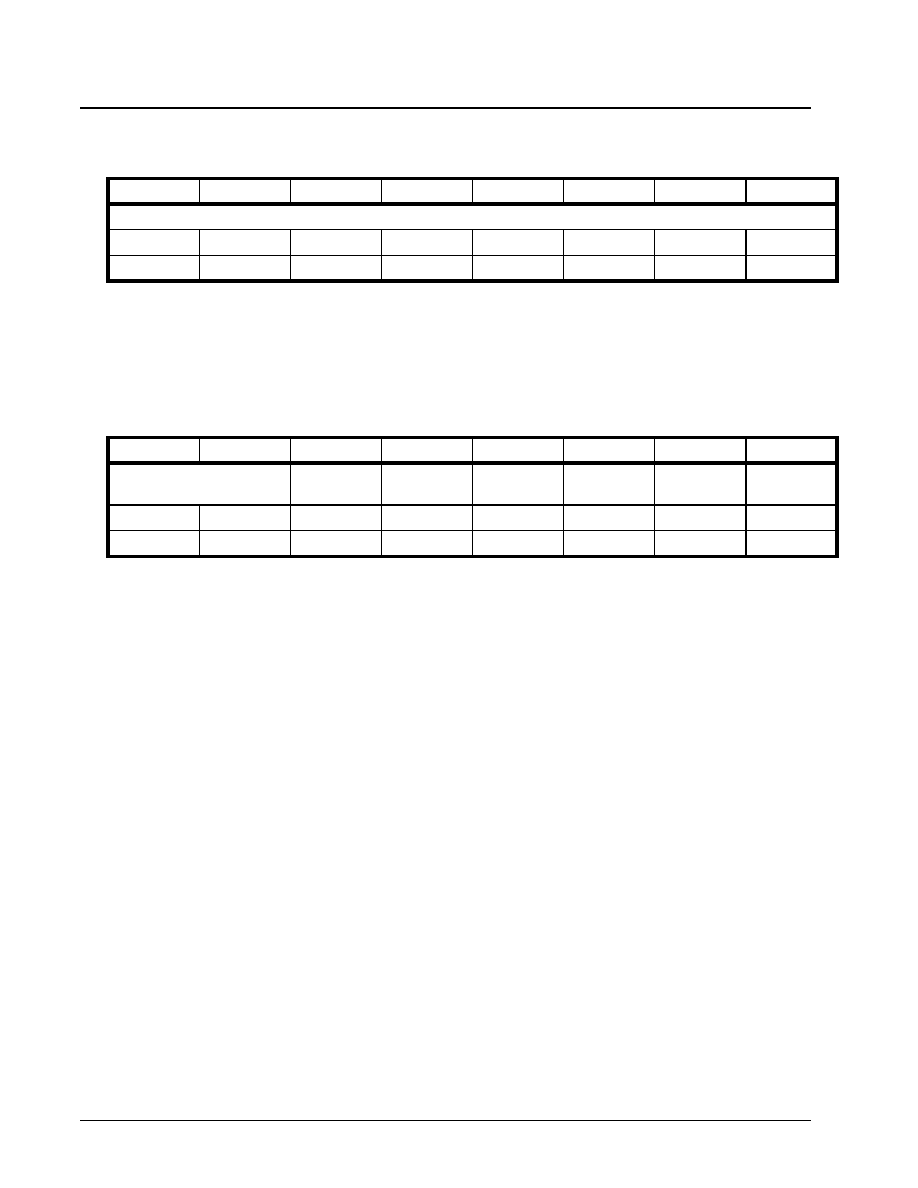

- PIN DESCRIPTION�

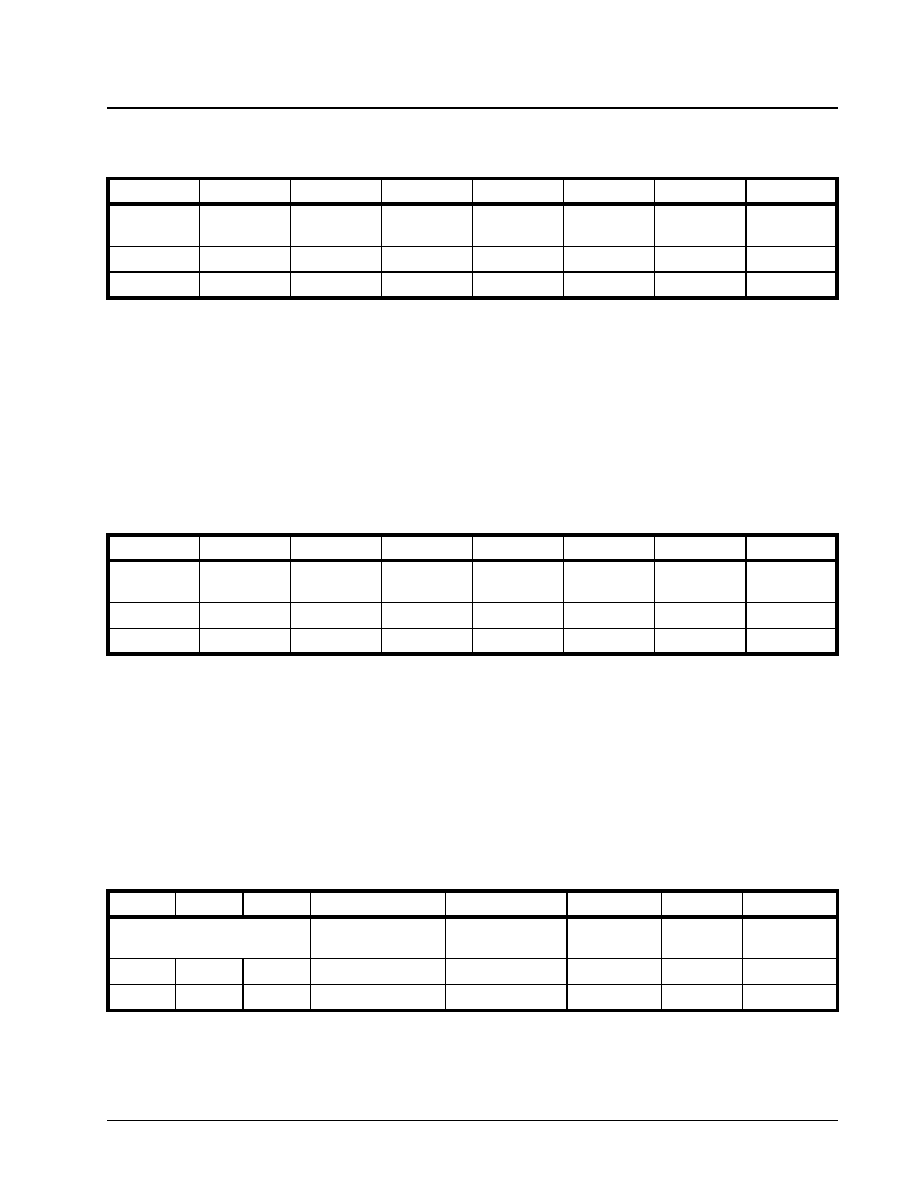

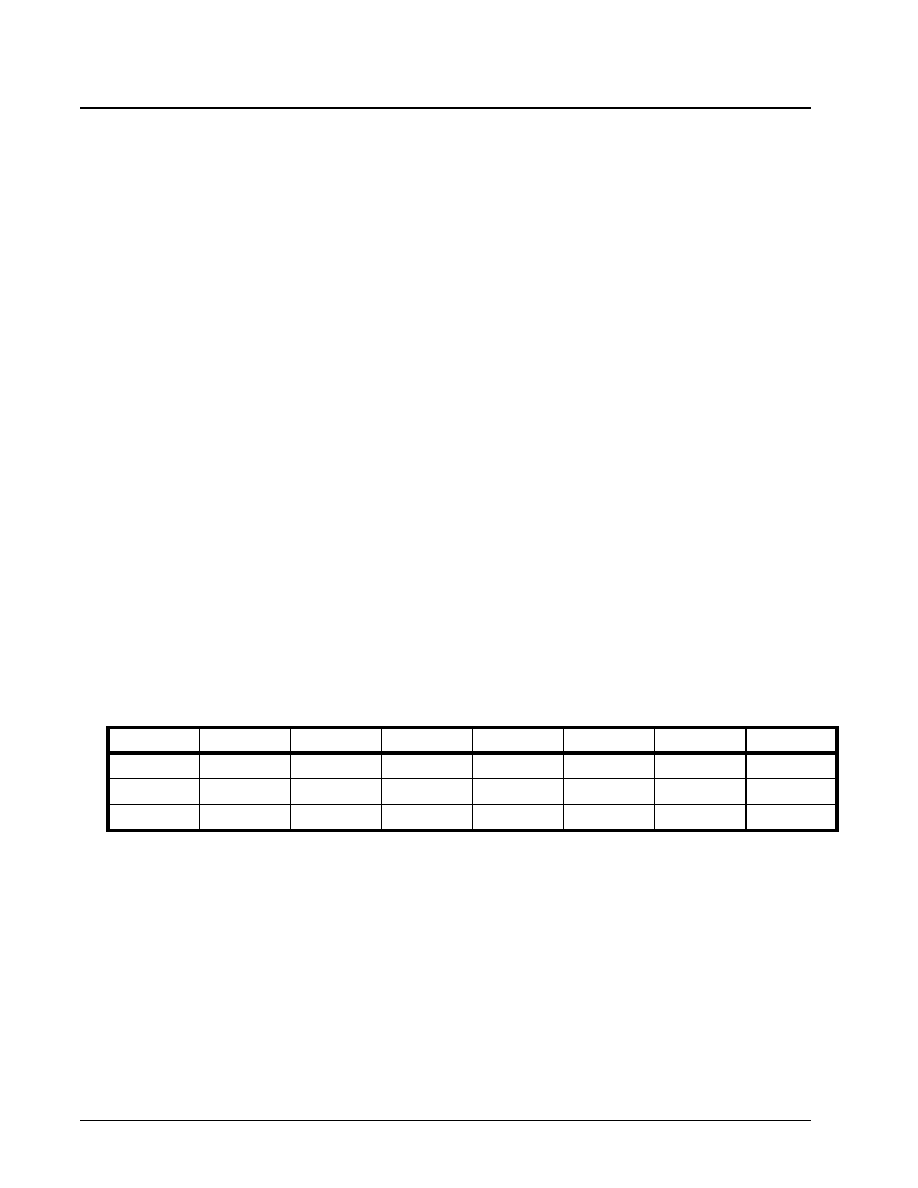

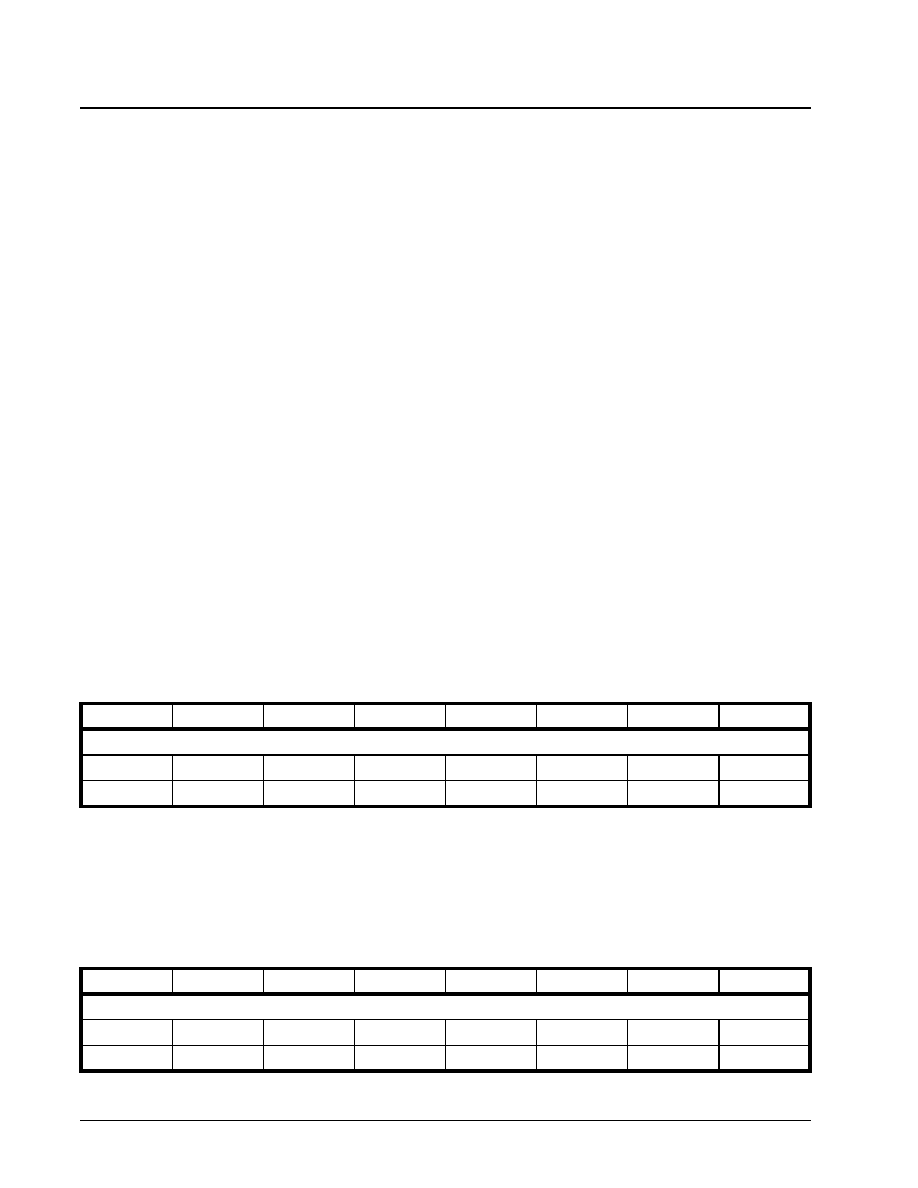

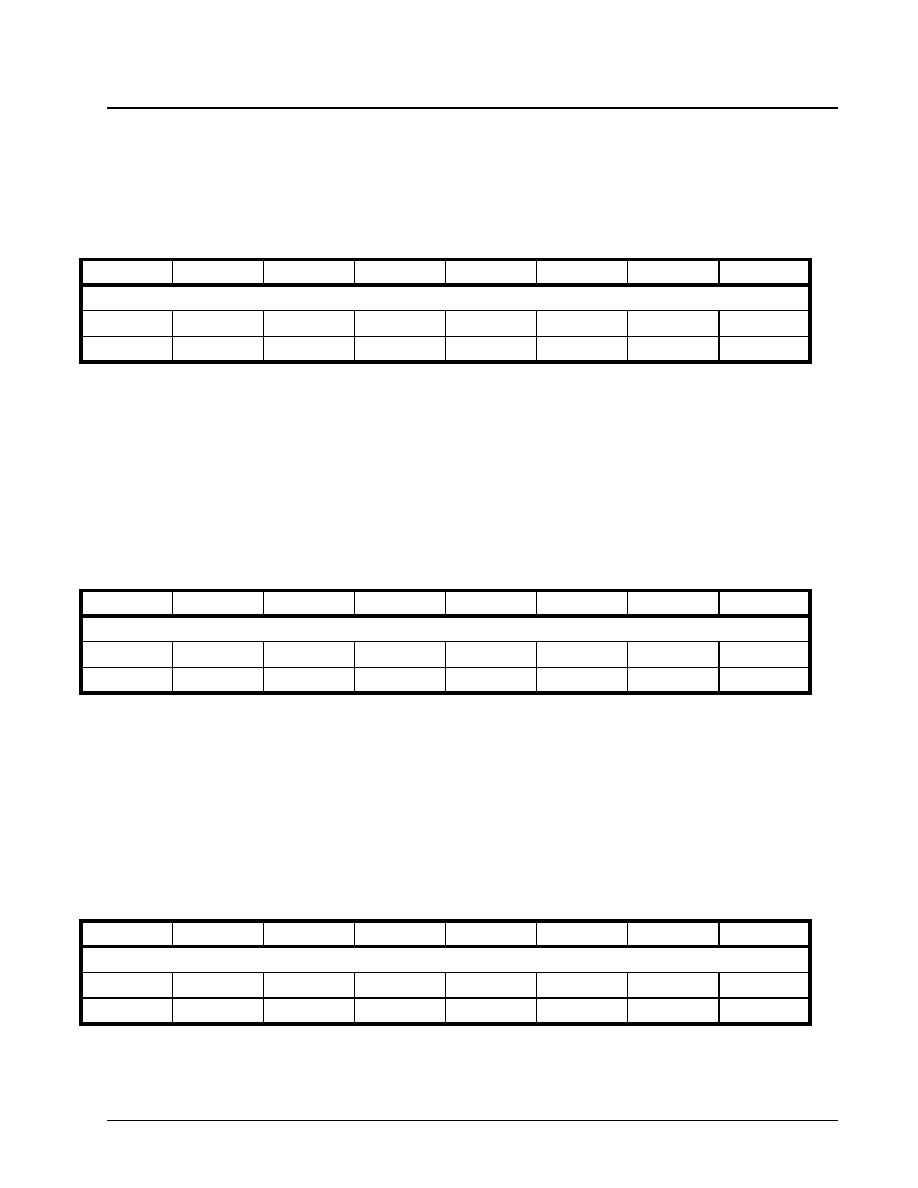

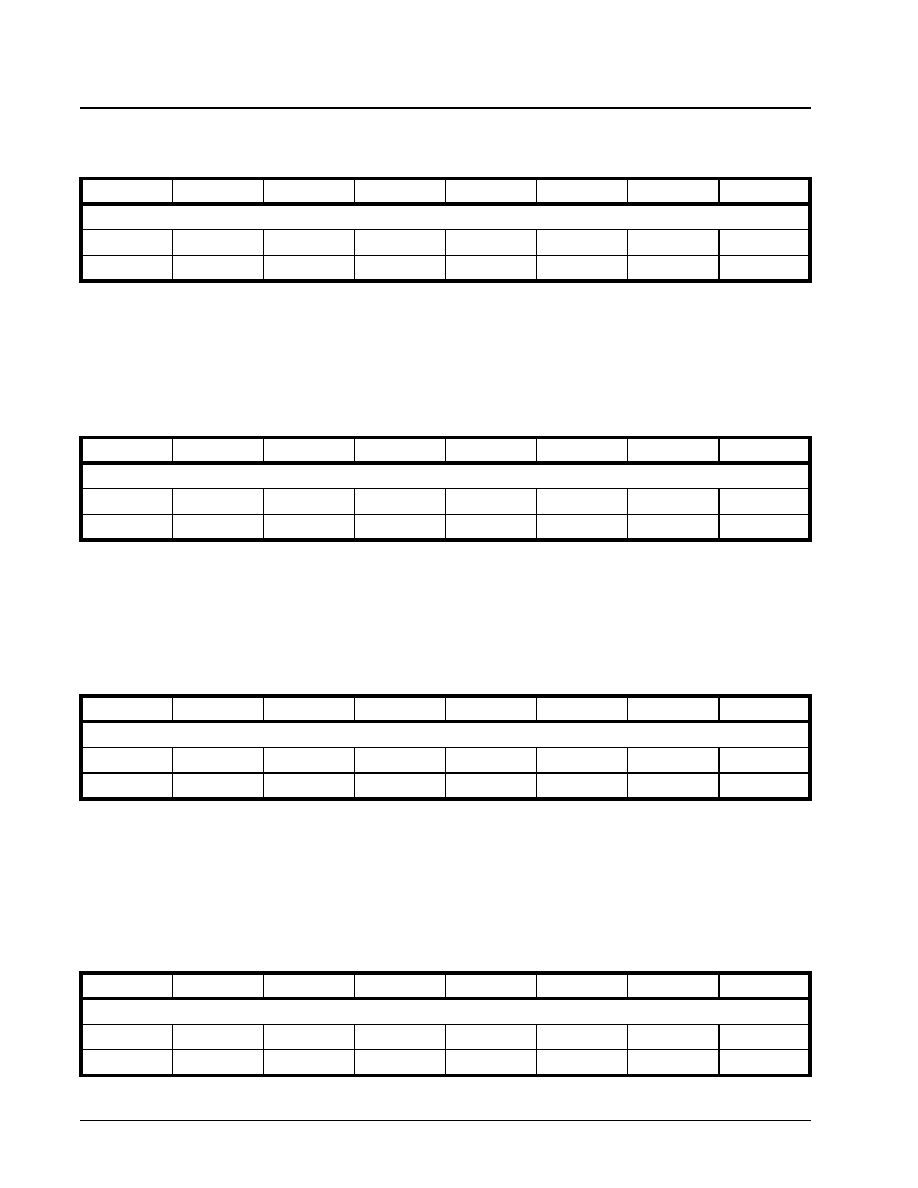

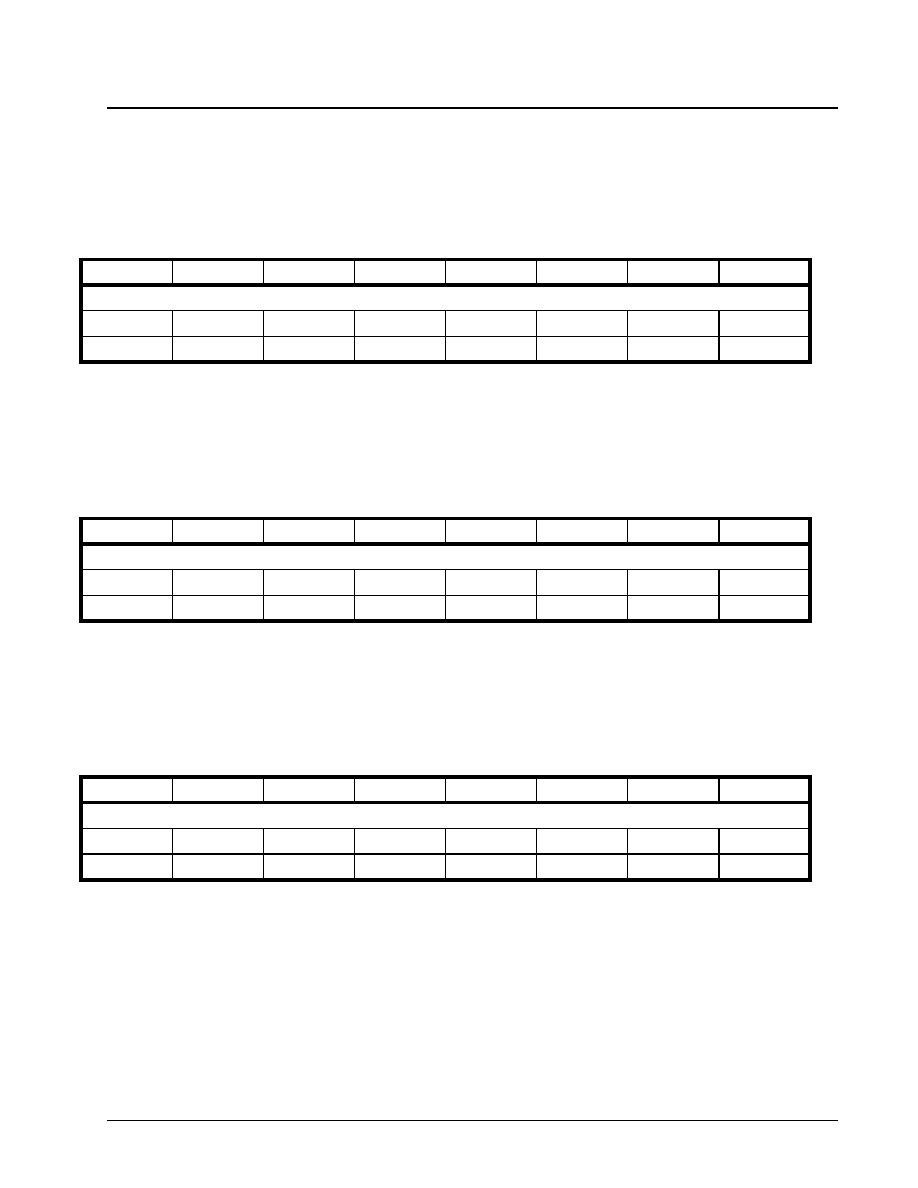

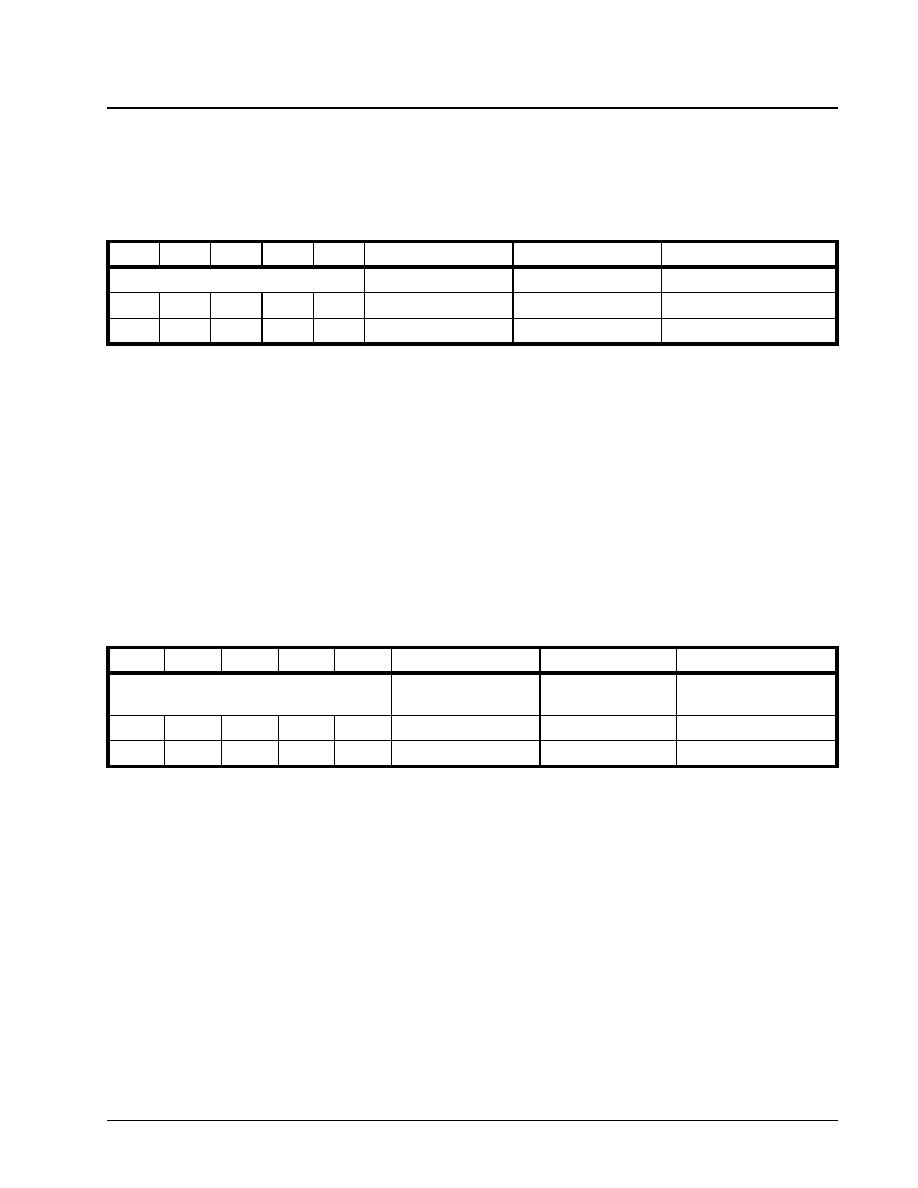

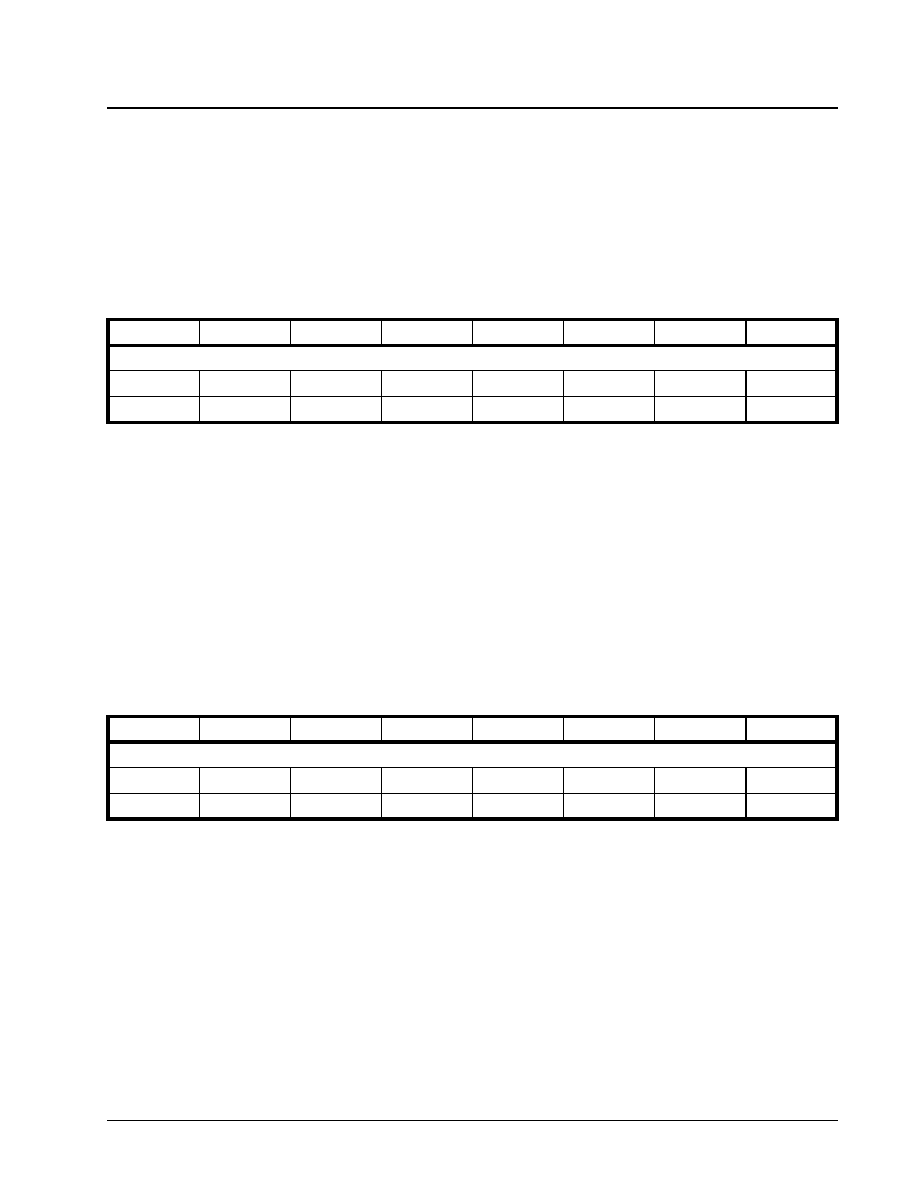

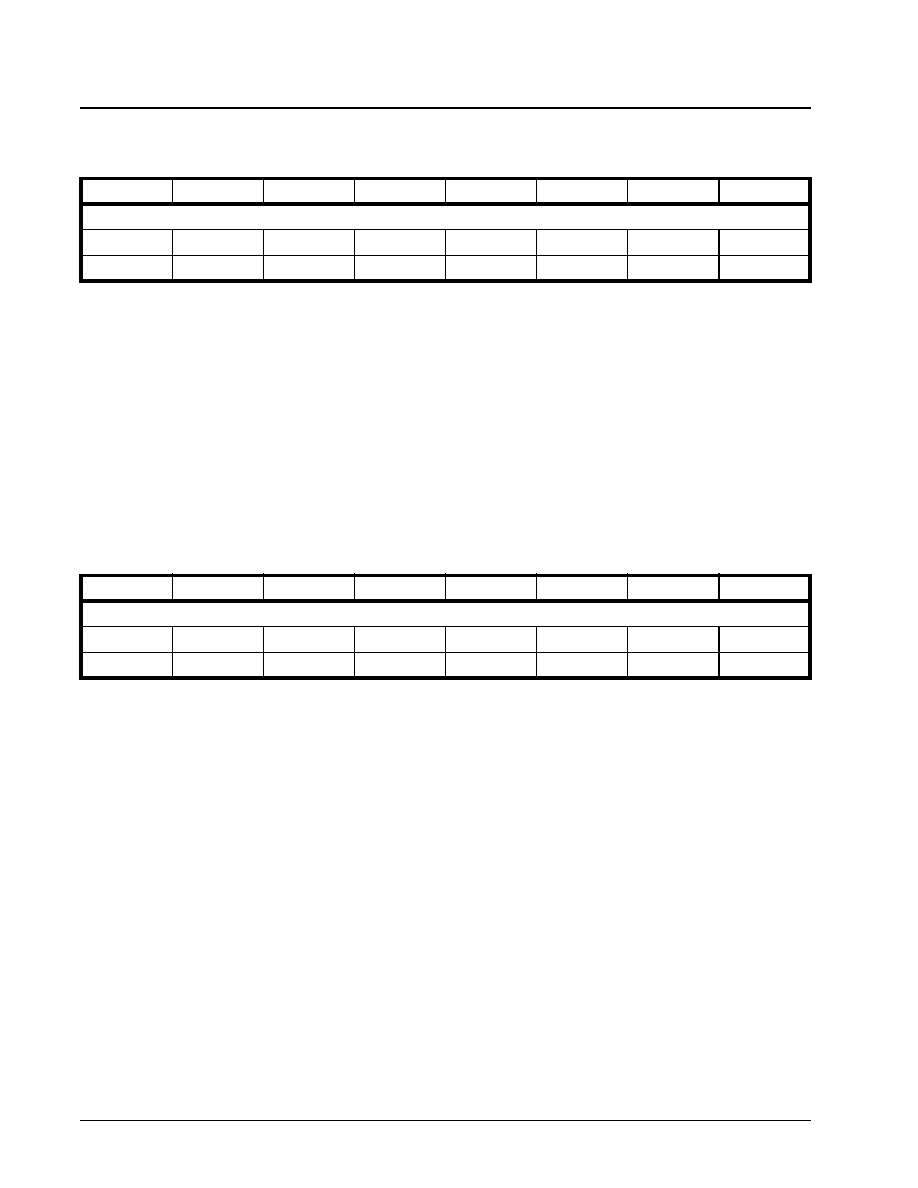

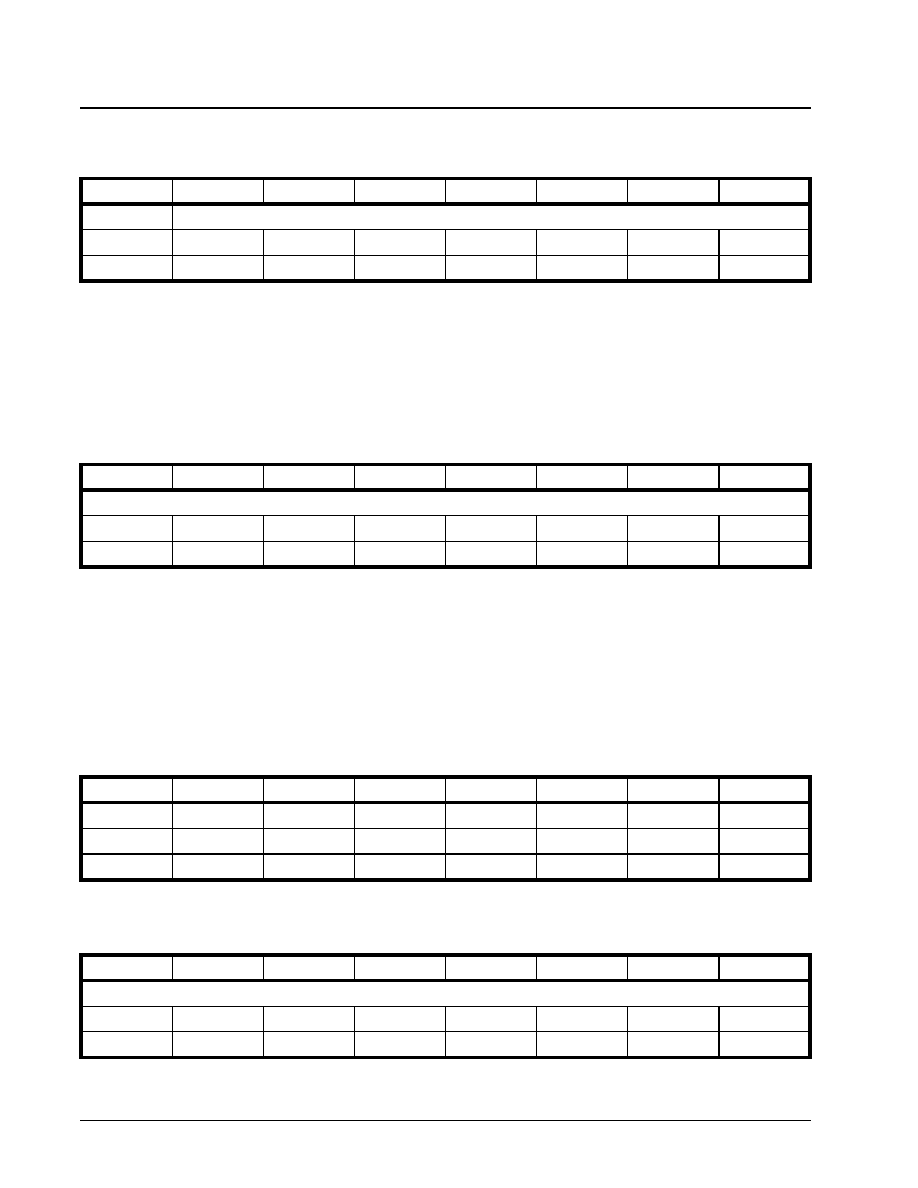

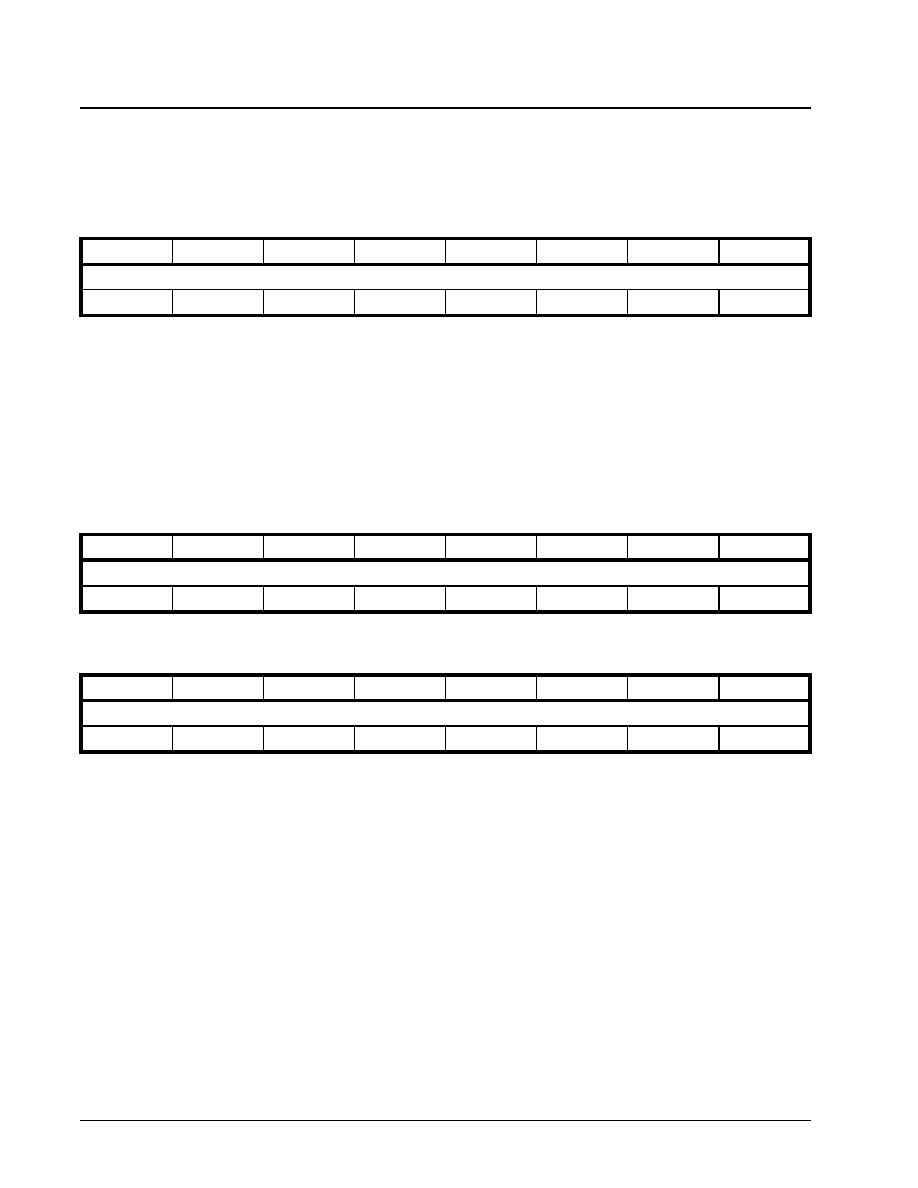

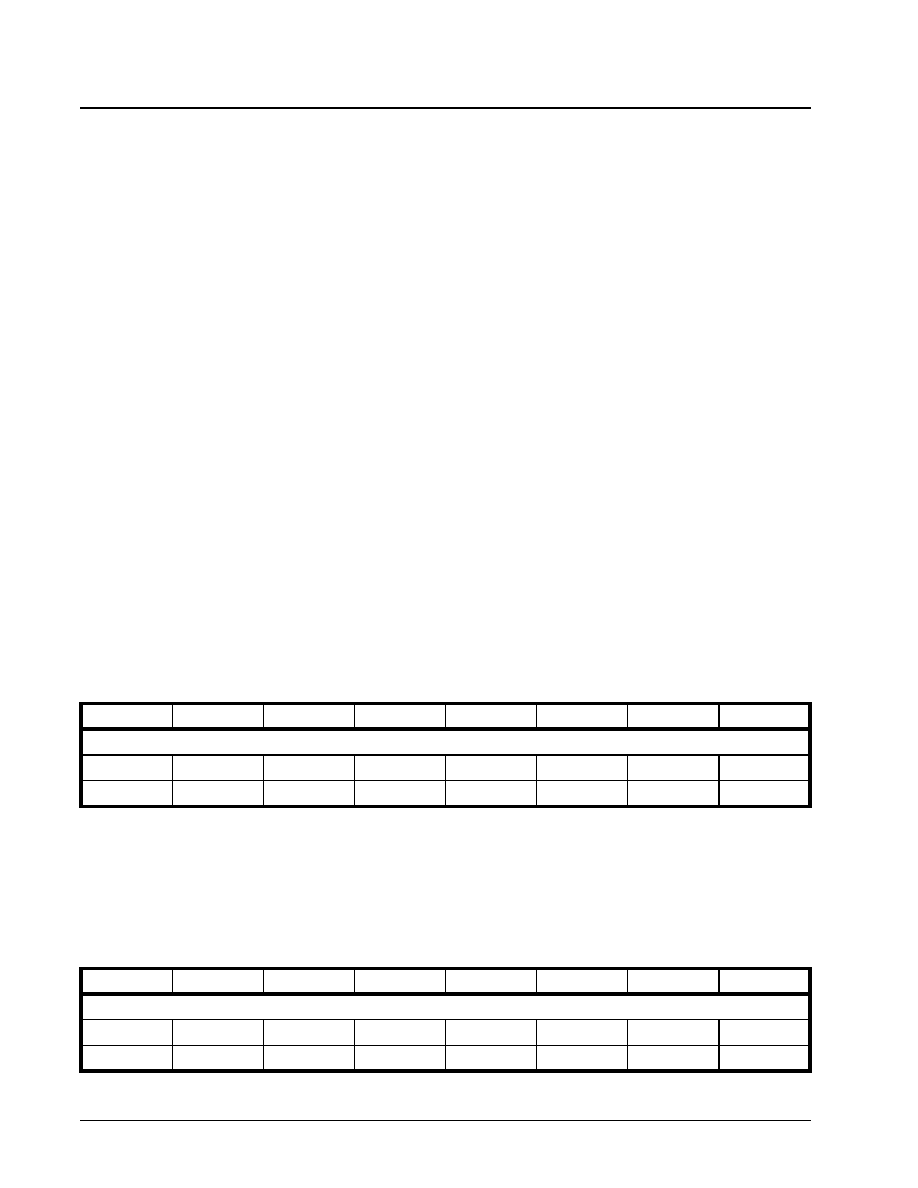

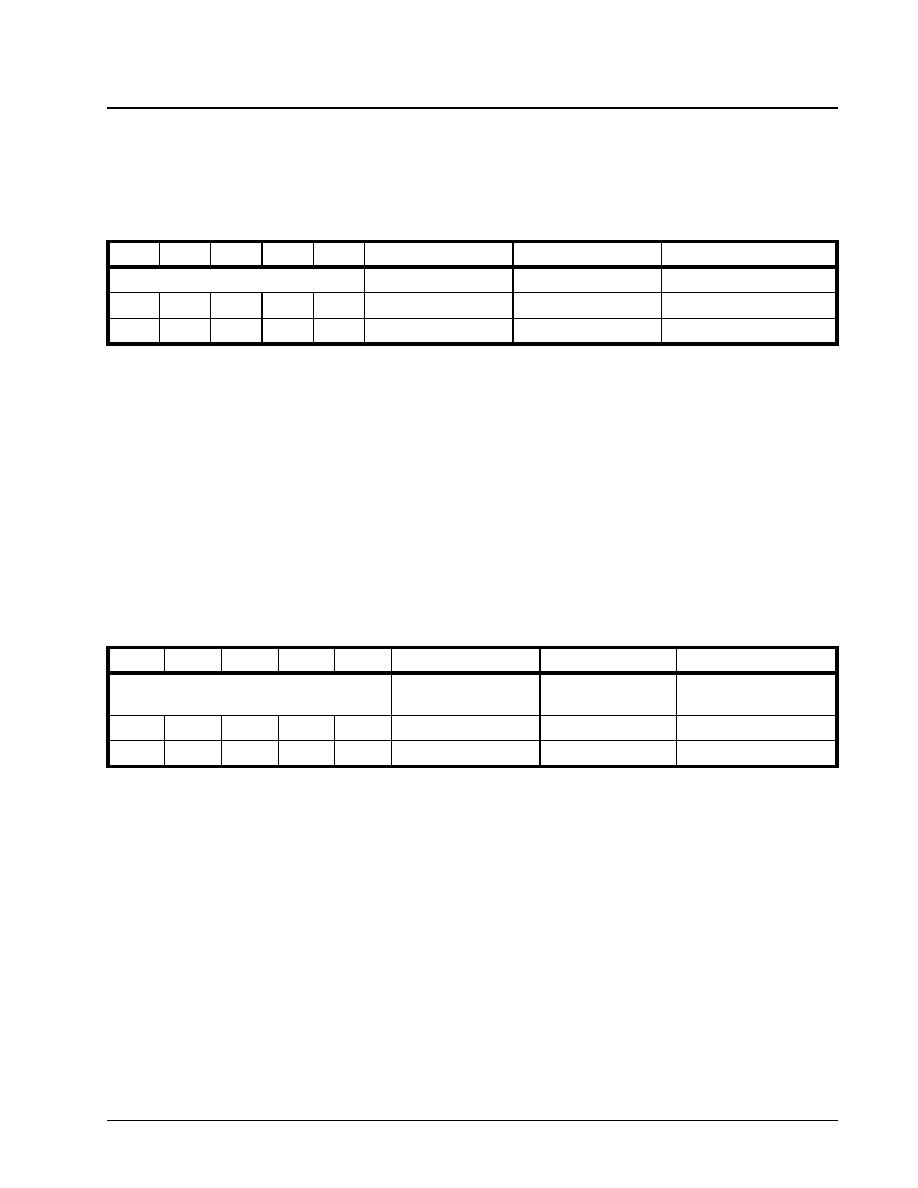

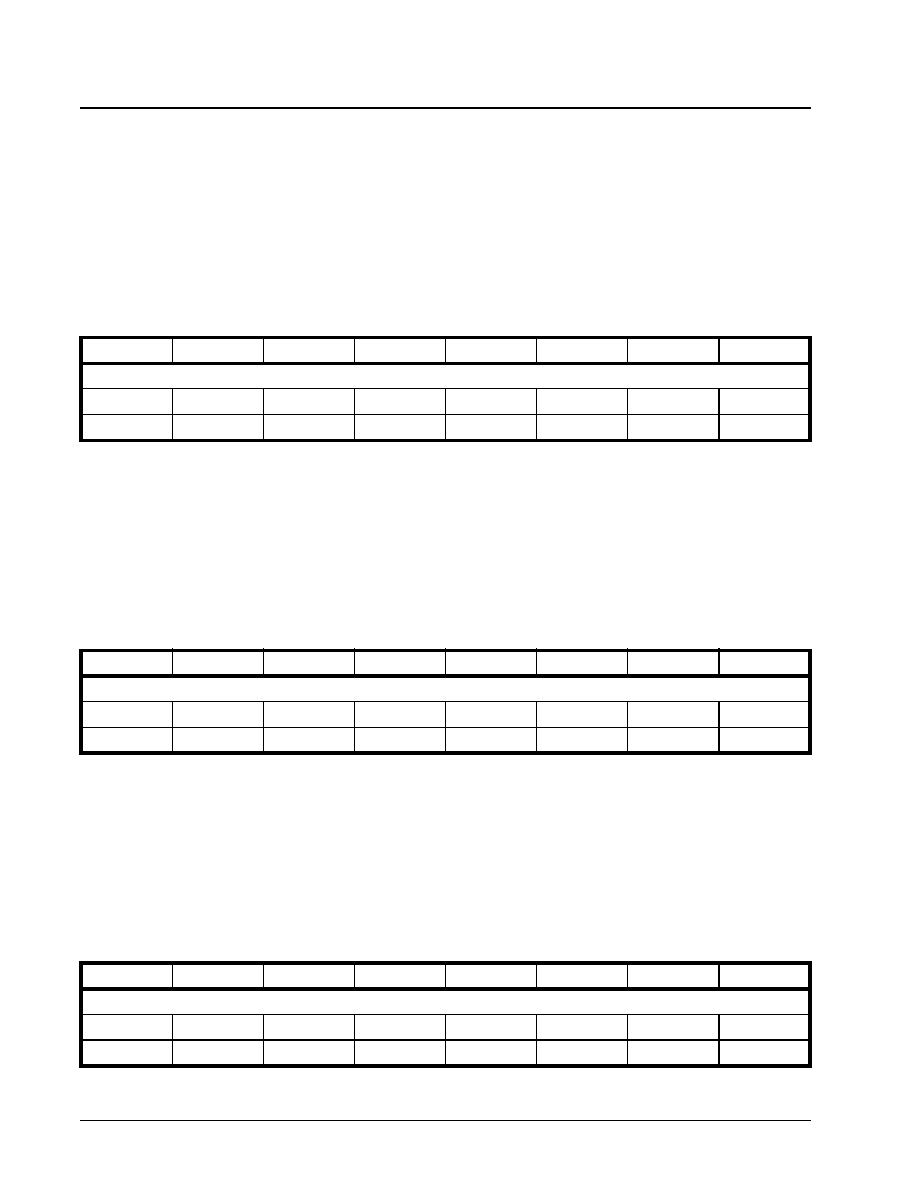

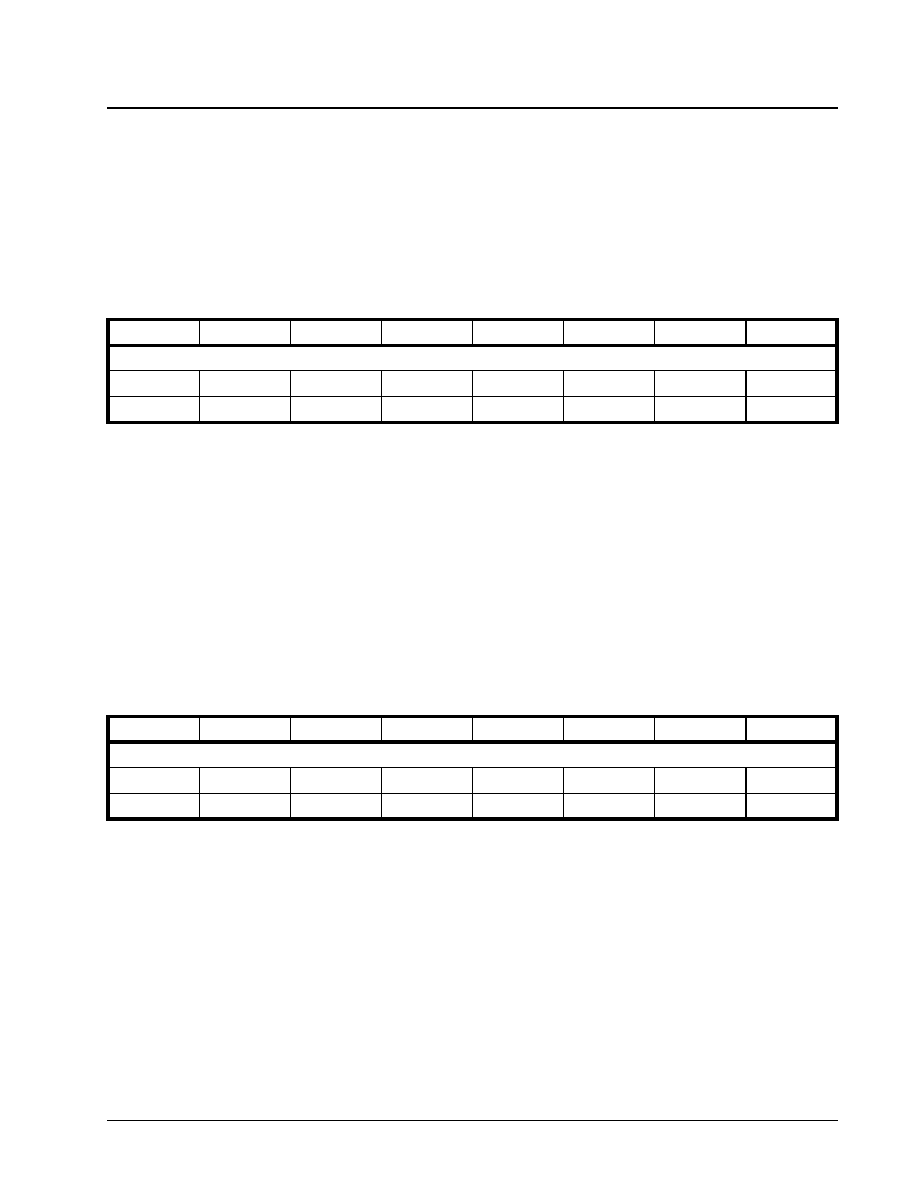

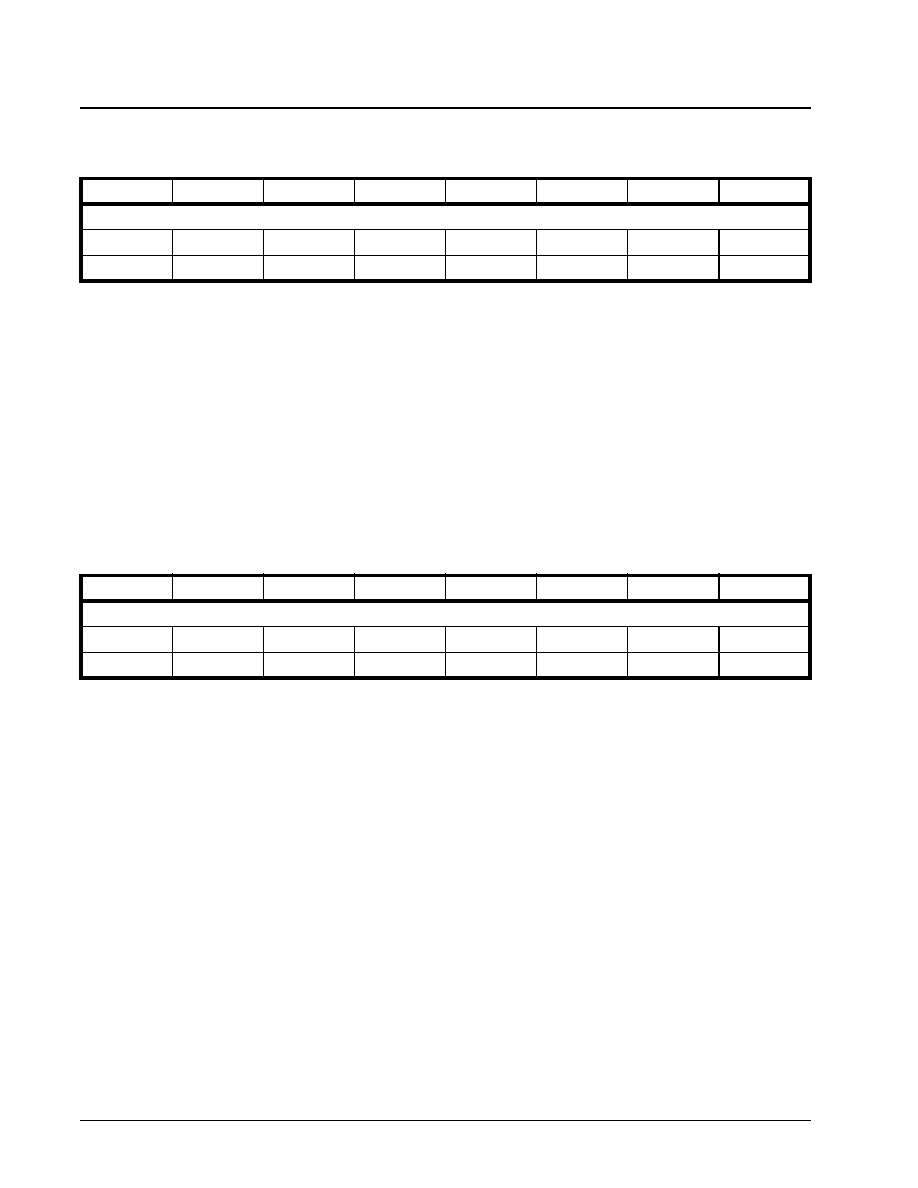

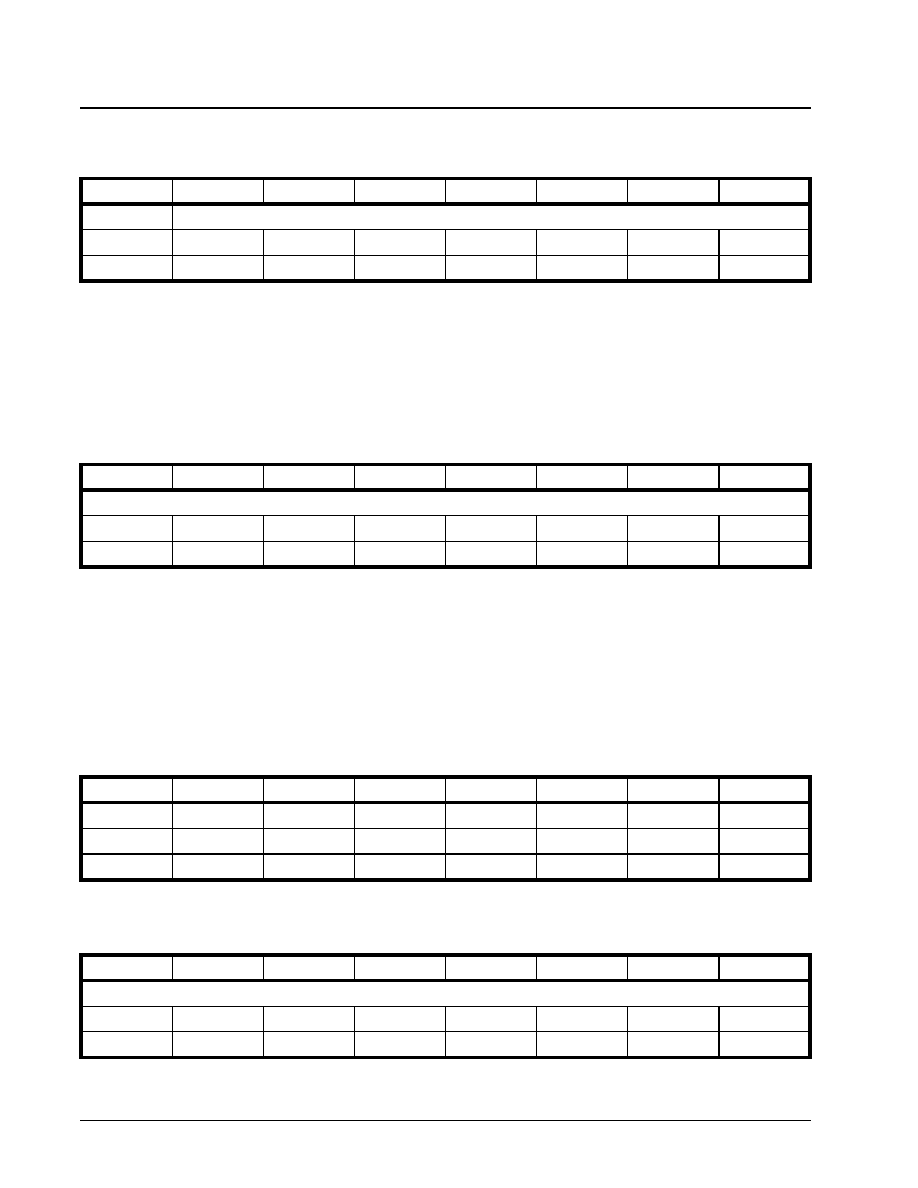

- DC ELECTRICAL CHARACTERISTICS

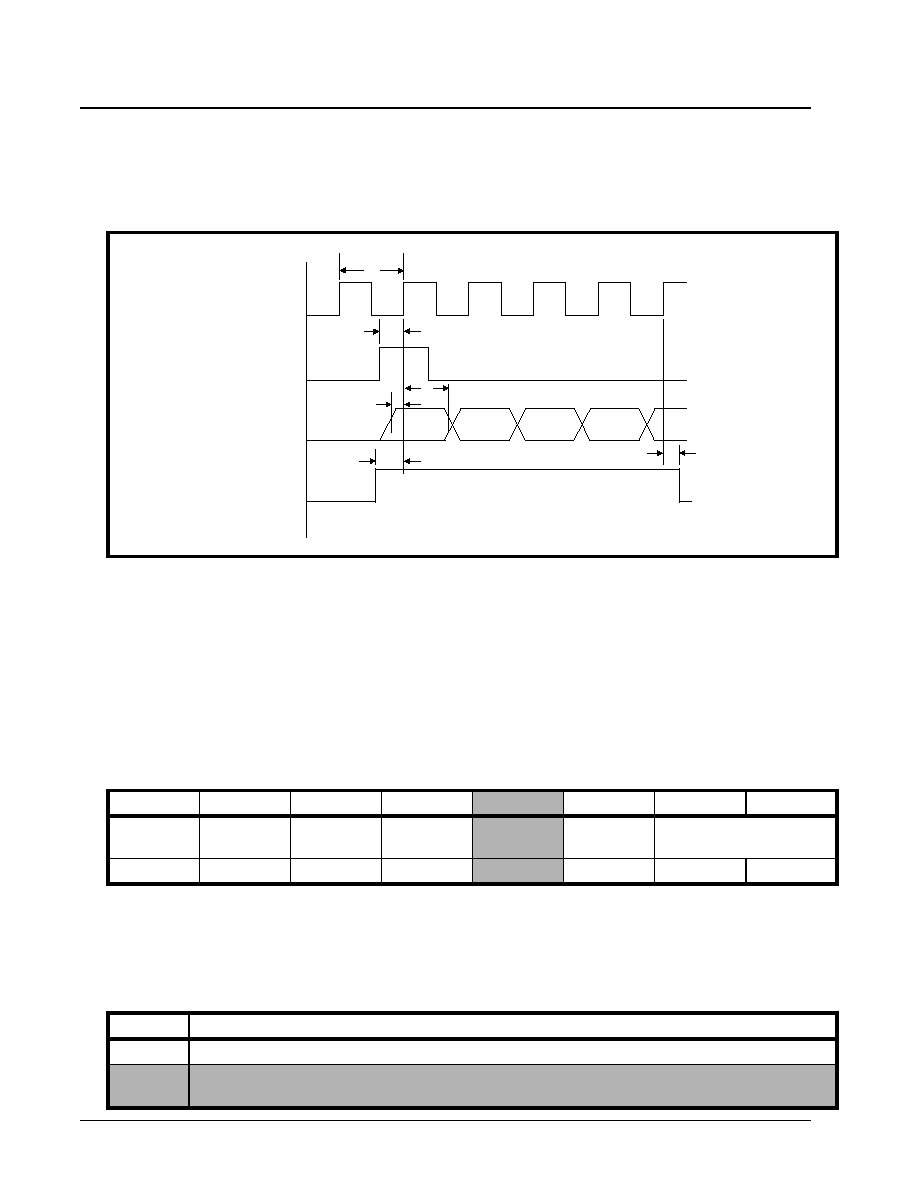

- AC ELECTRICAL CHARACTERISTICS�

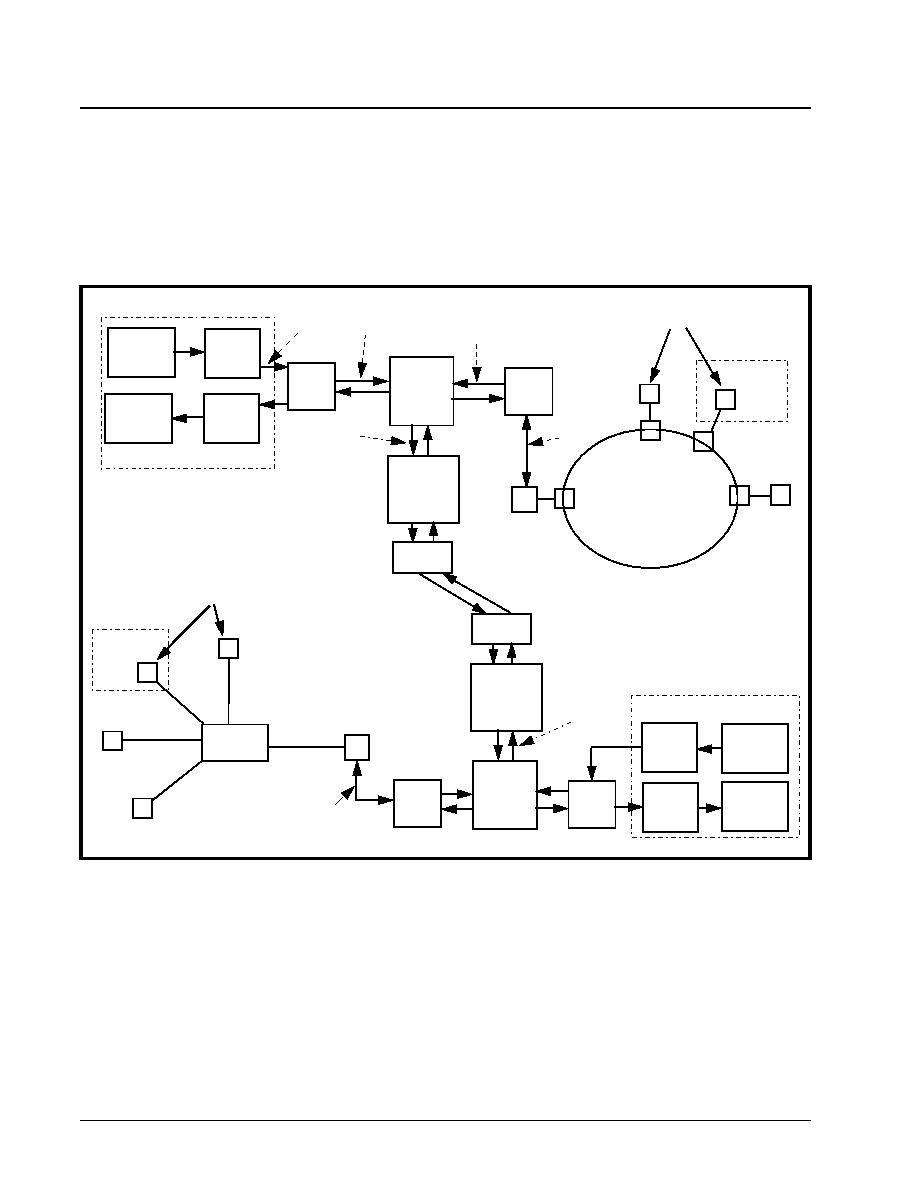

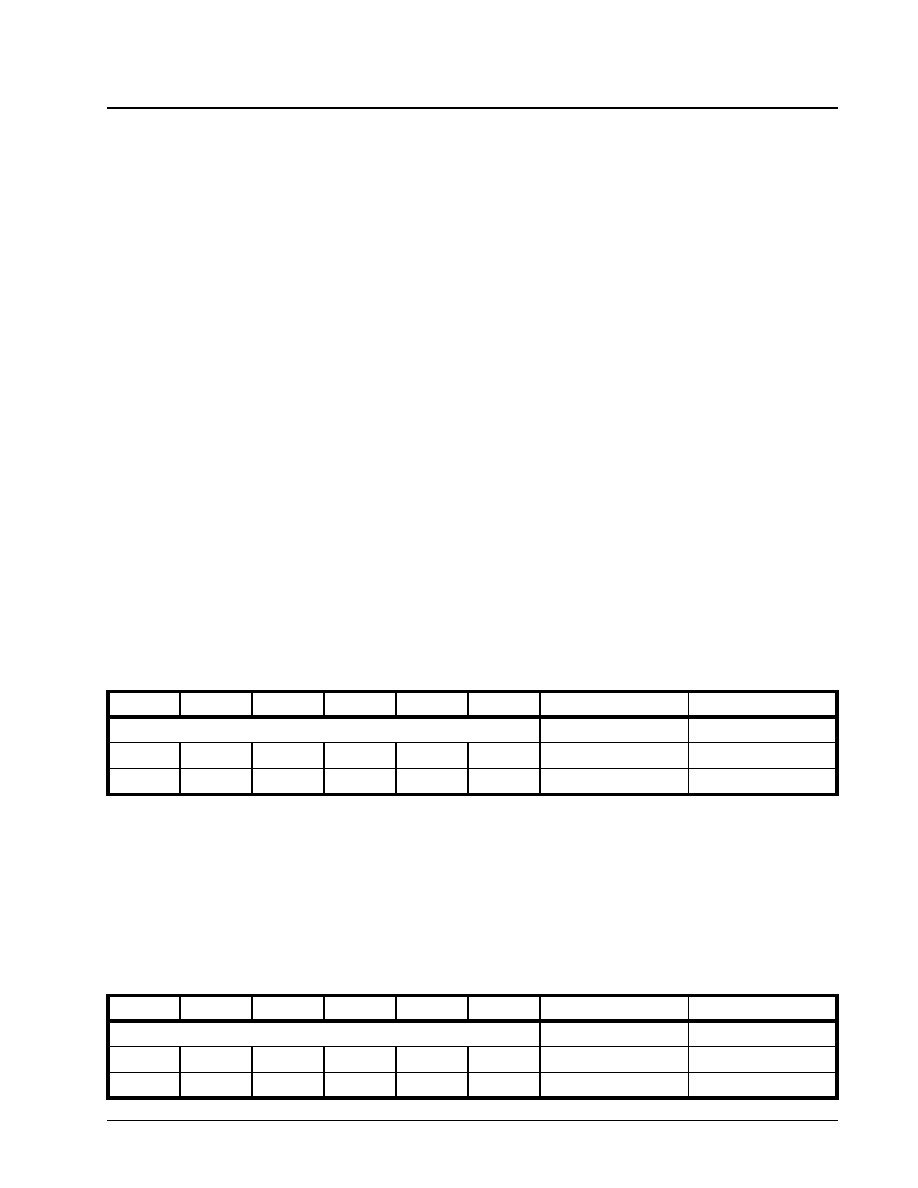

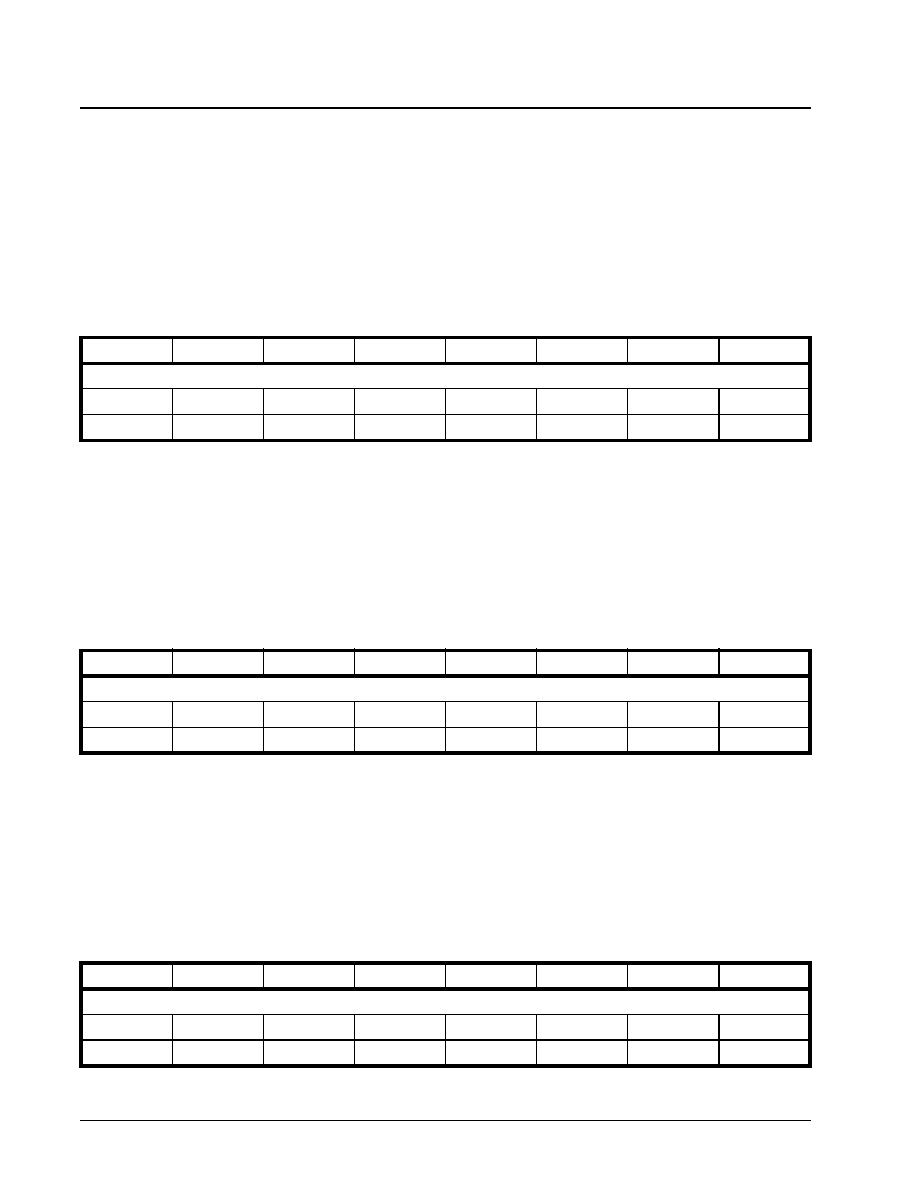

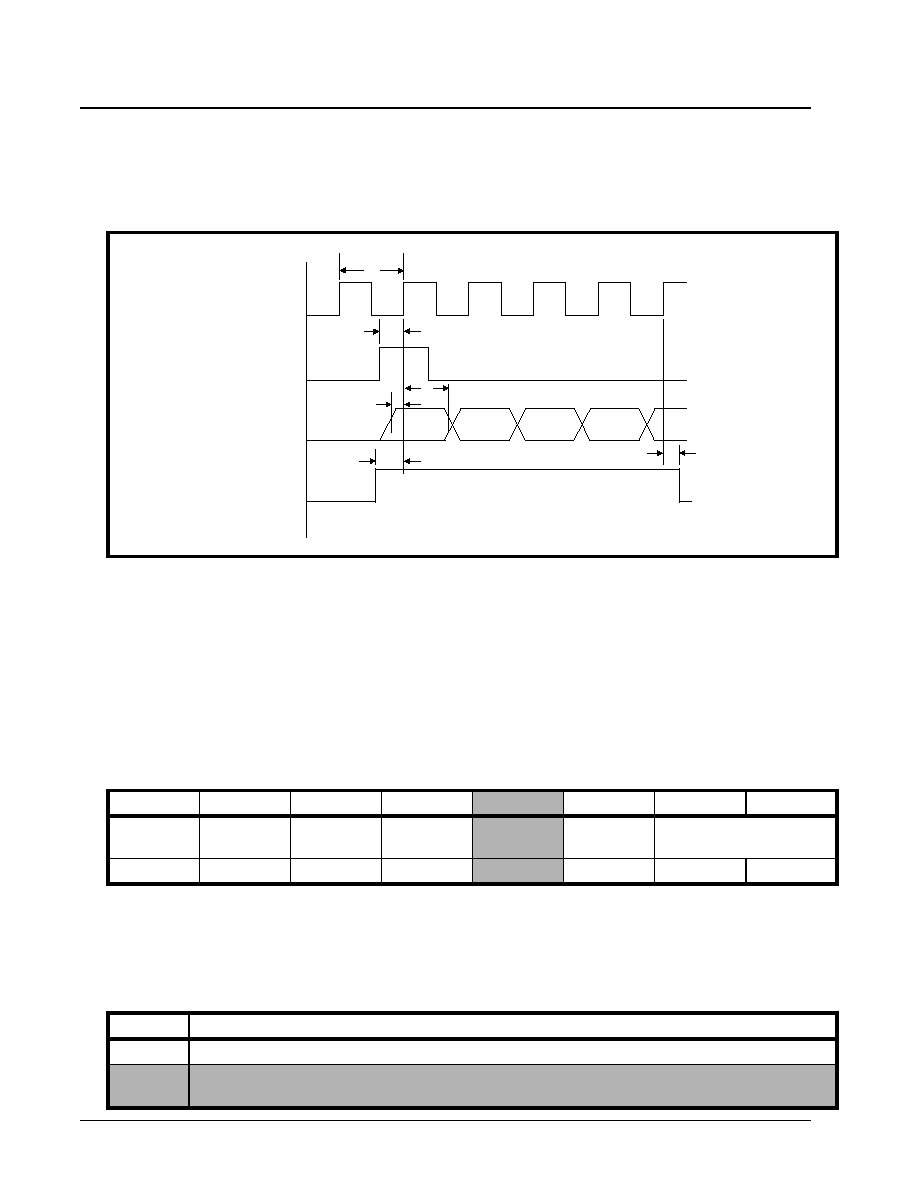

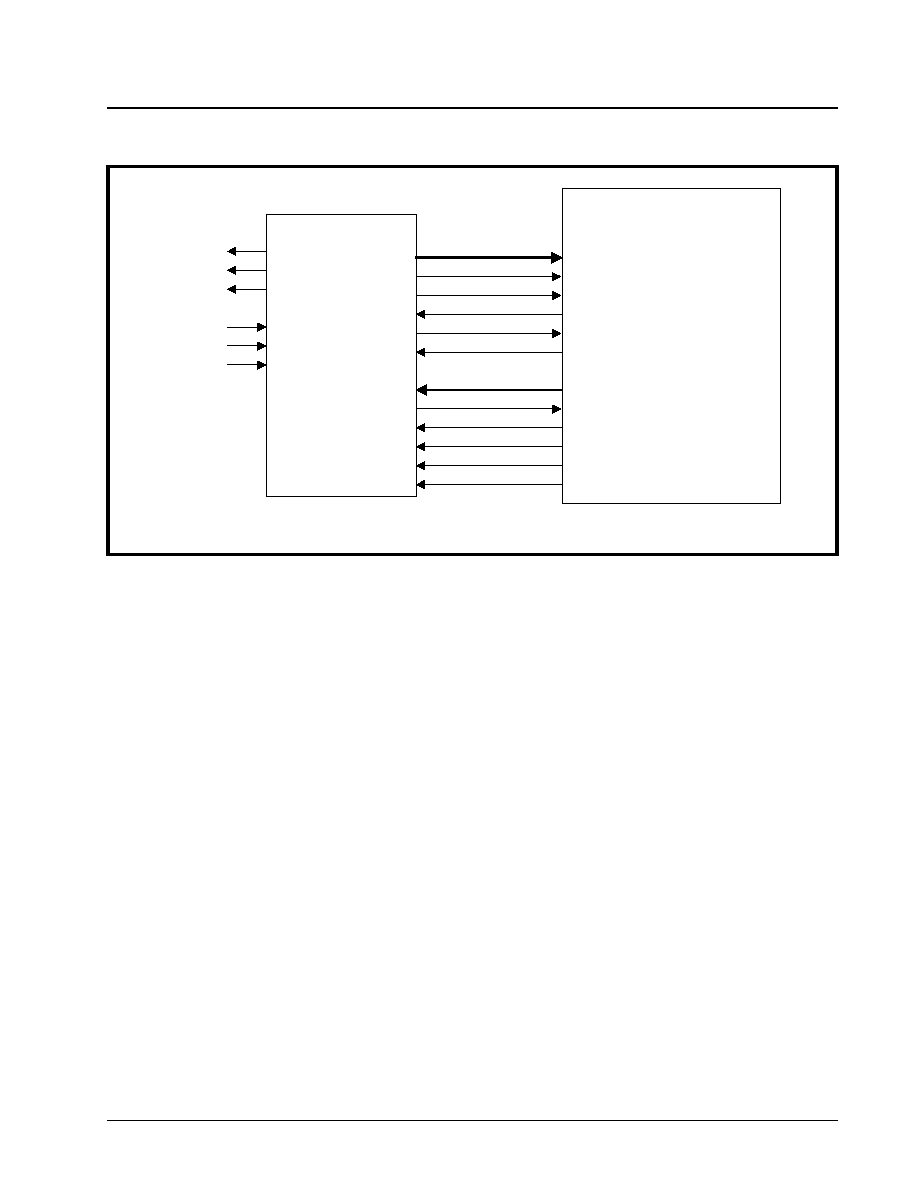

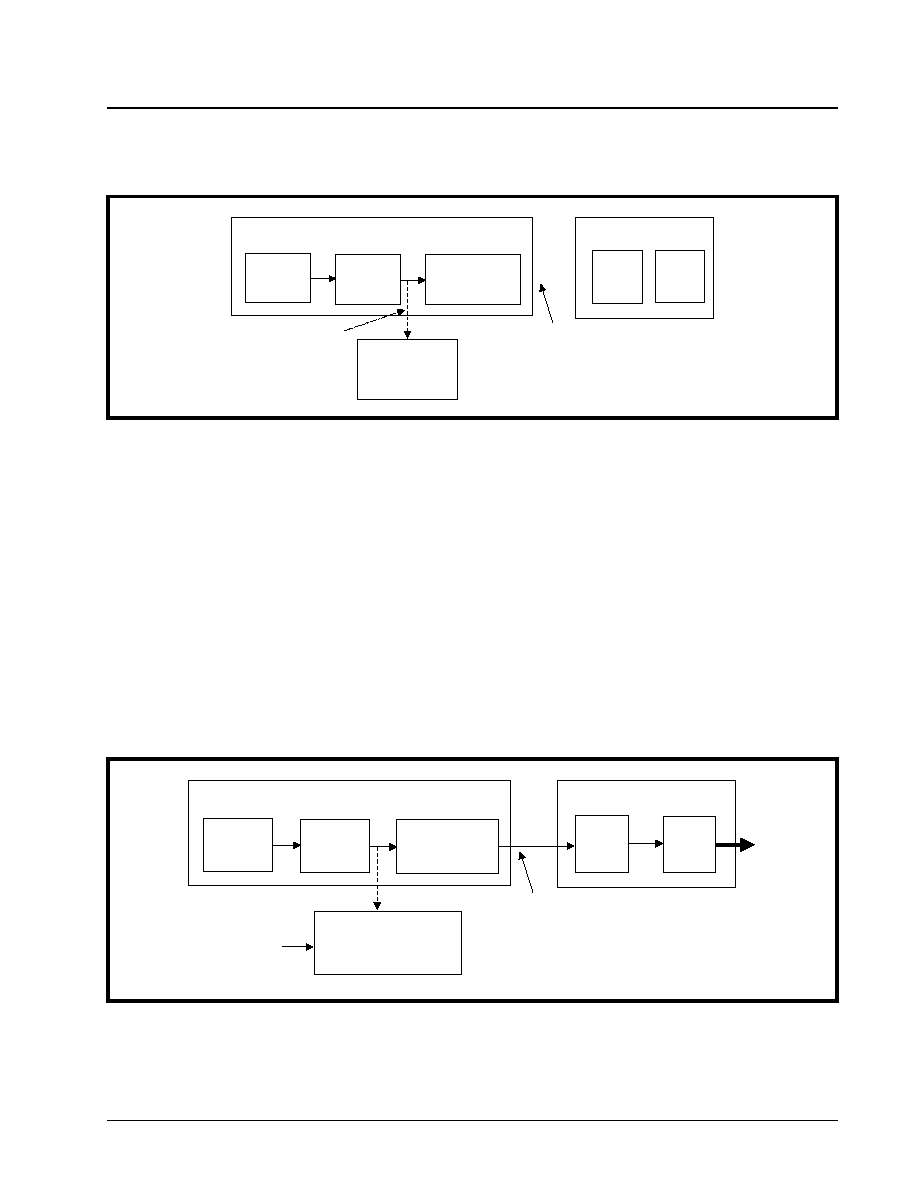

- Interfacing to the ATM Switch (ATM Layer �Processor)

- Interfacing to the Local Microprocessor

- Interfacing the UNI to the DS3 Line

- PRINCIPLE OF OPERATION

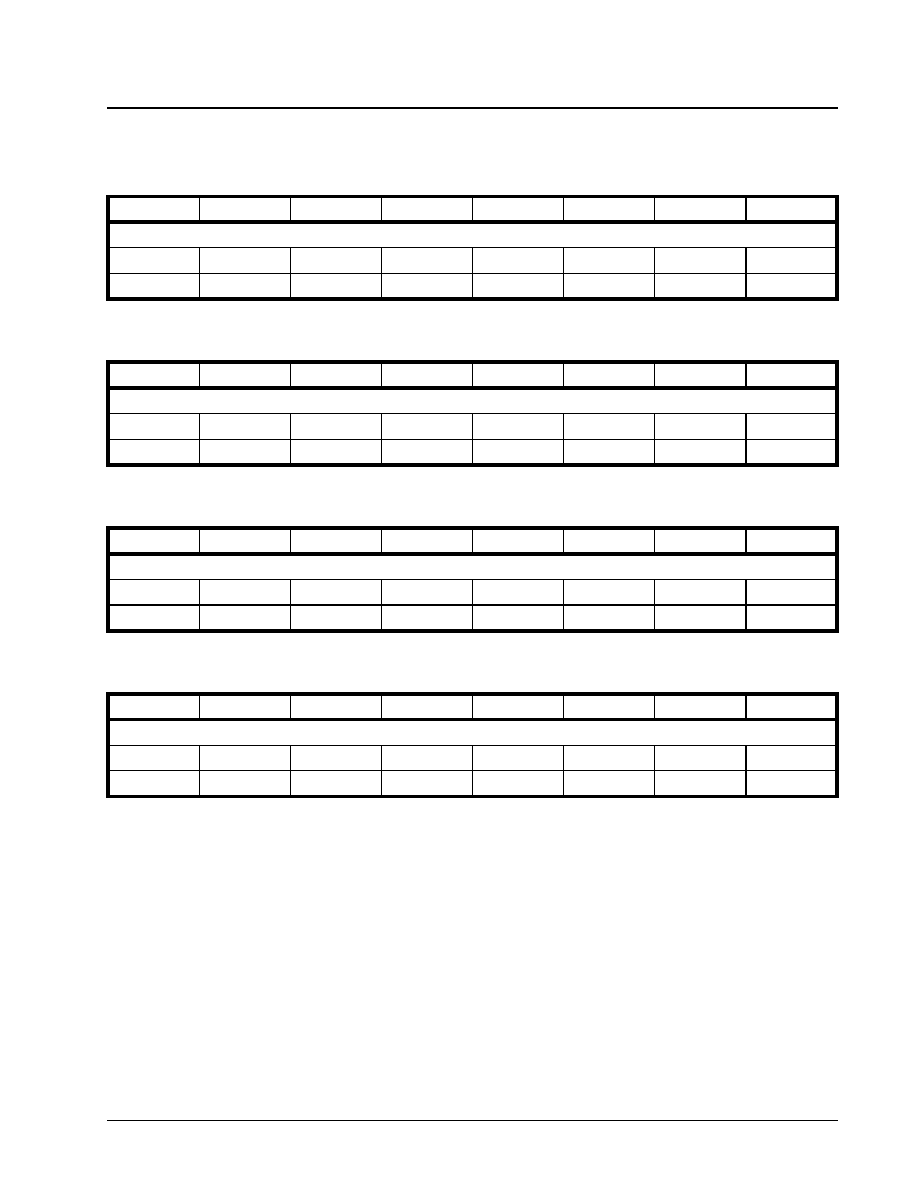

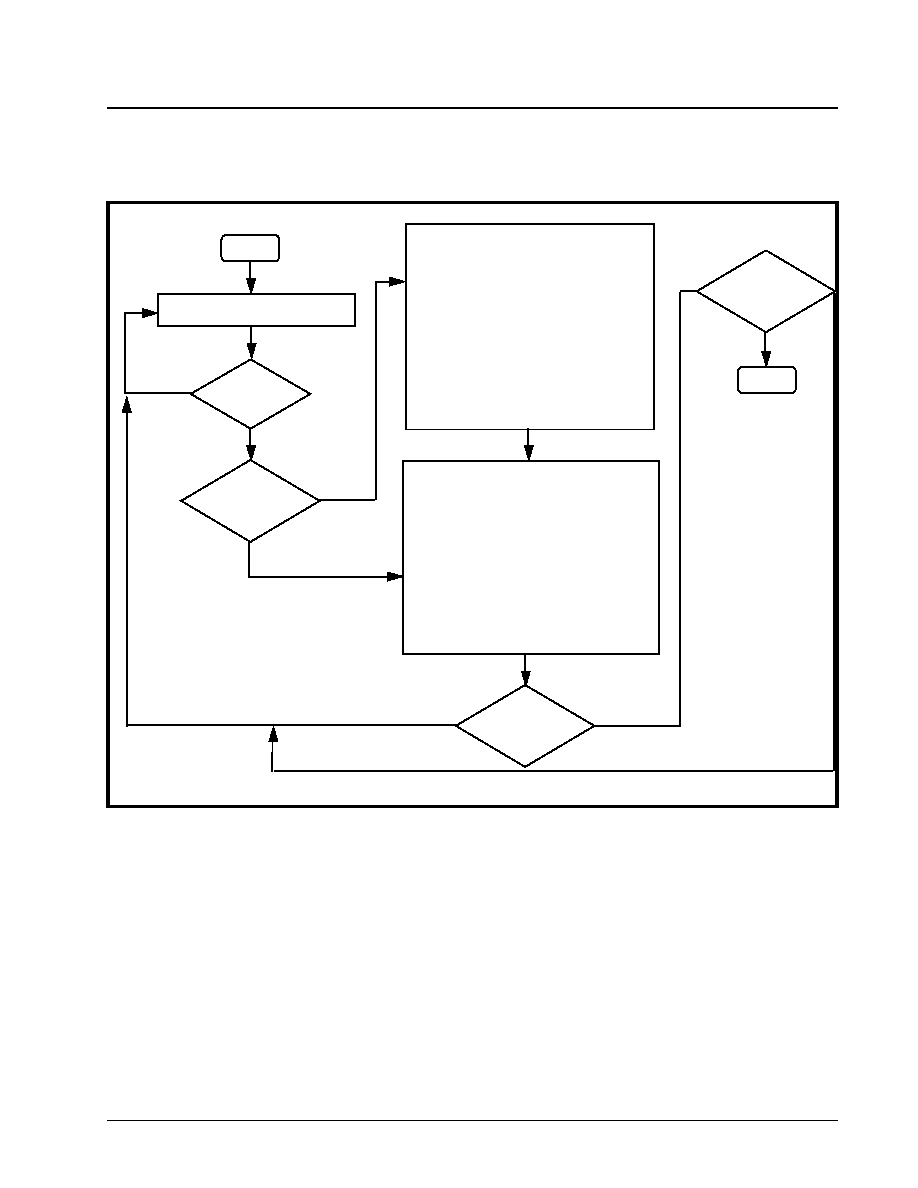

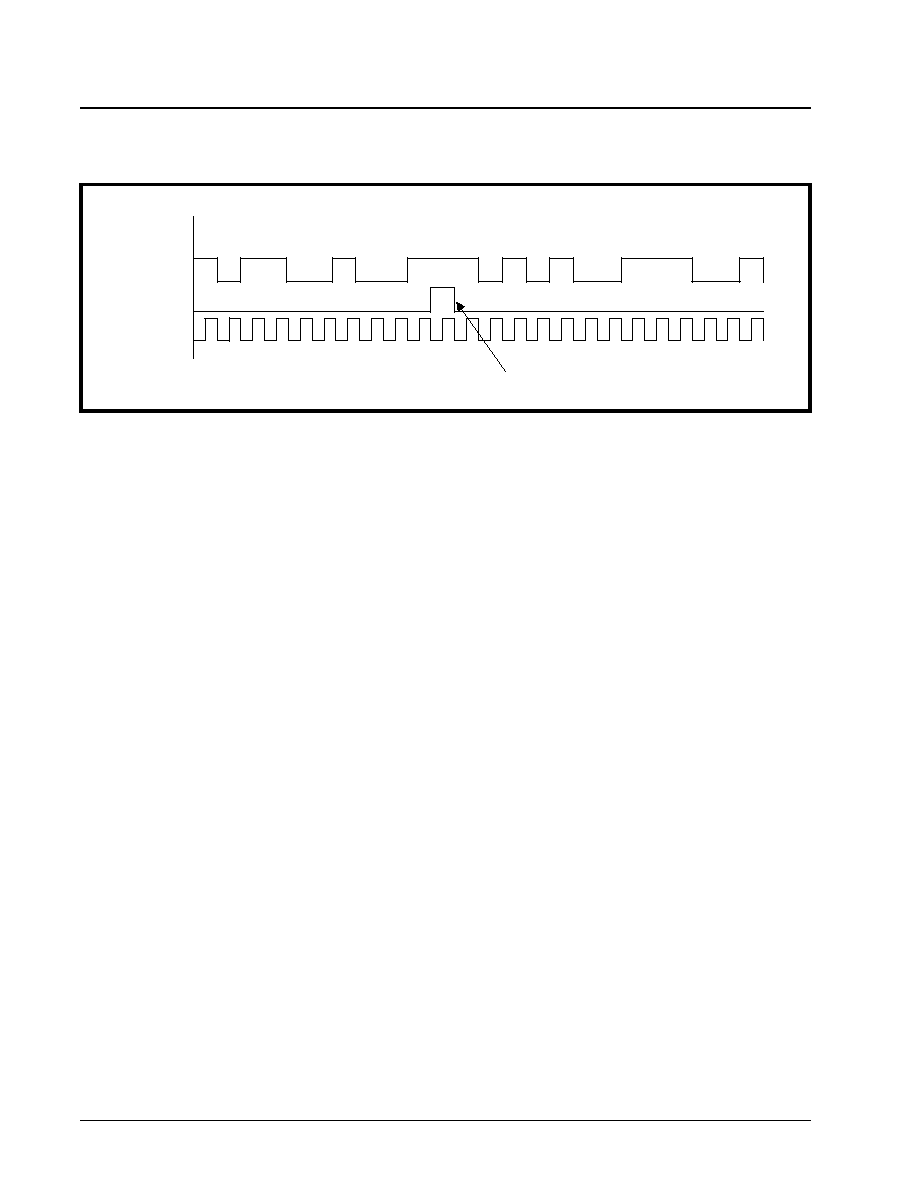

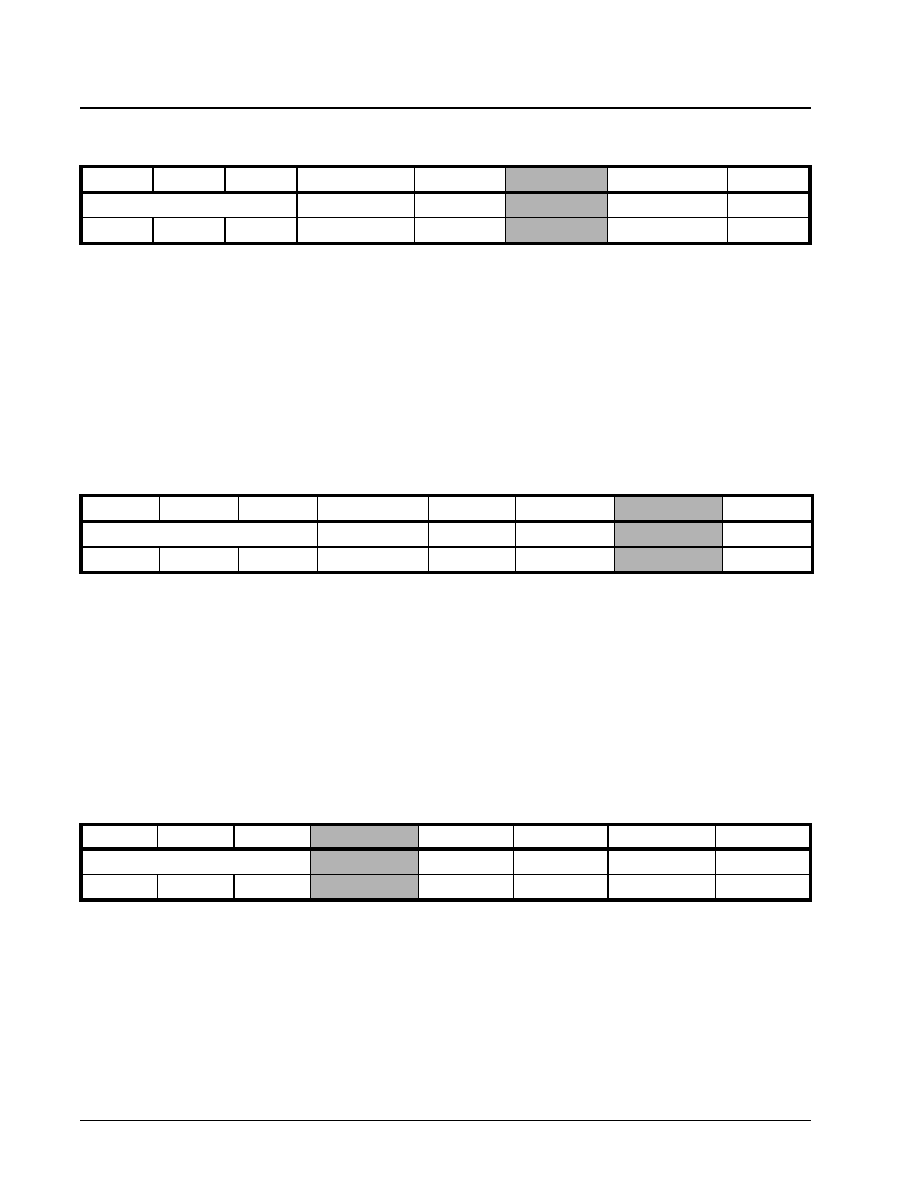

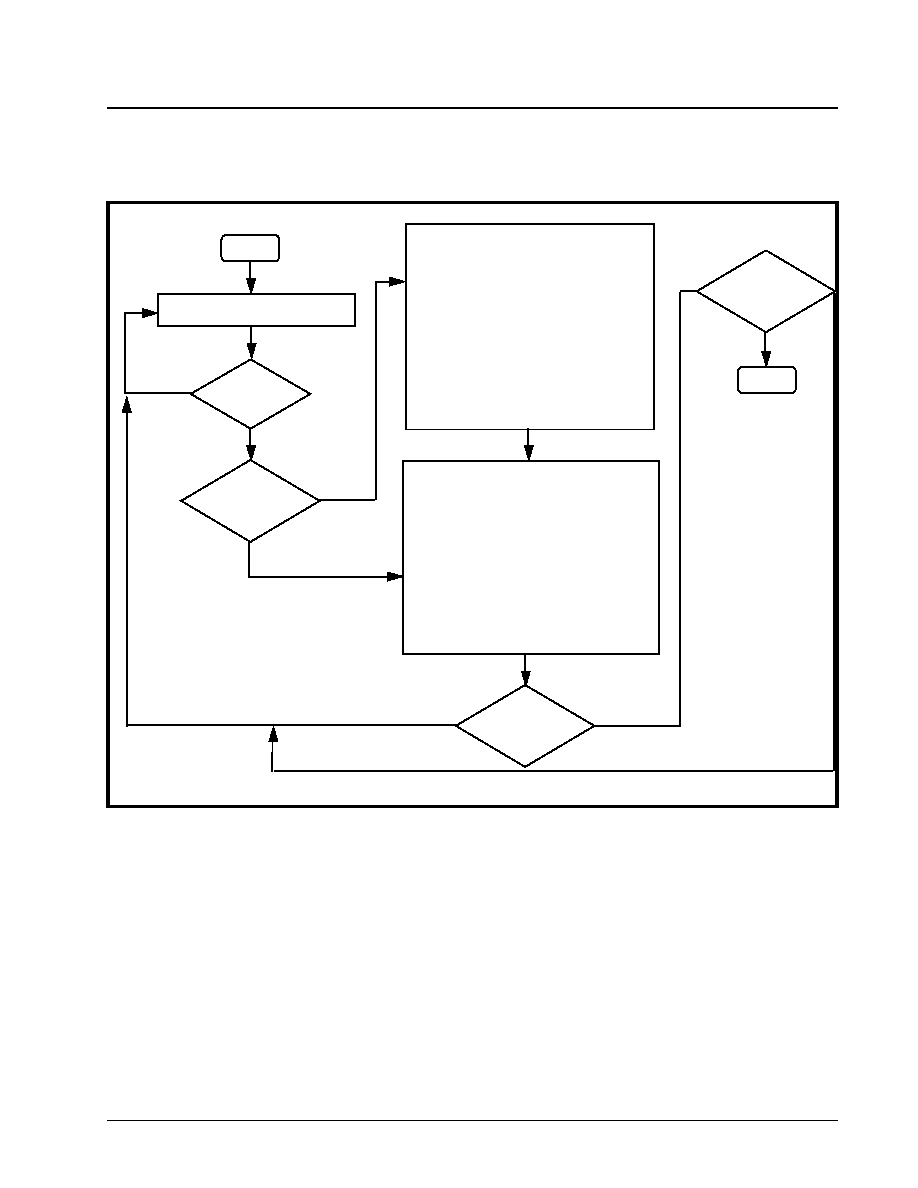

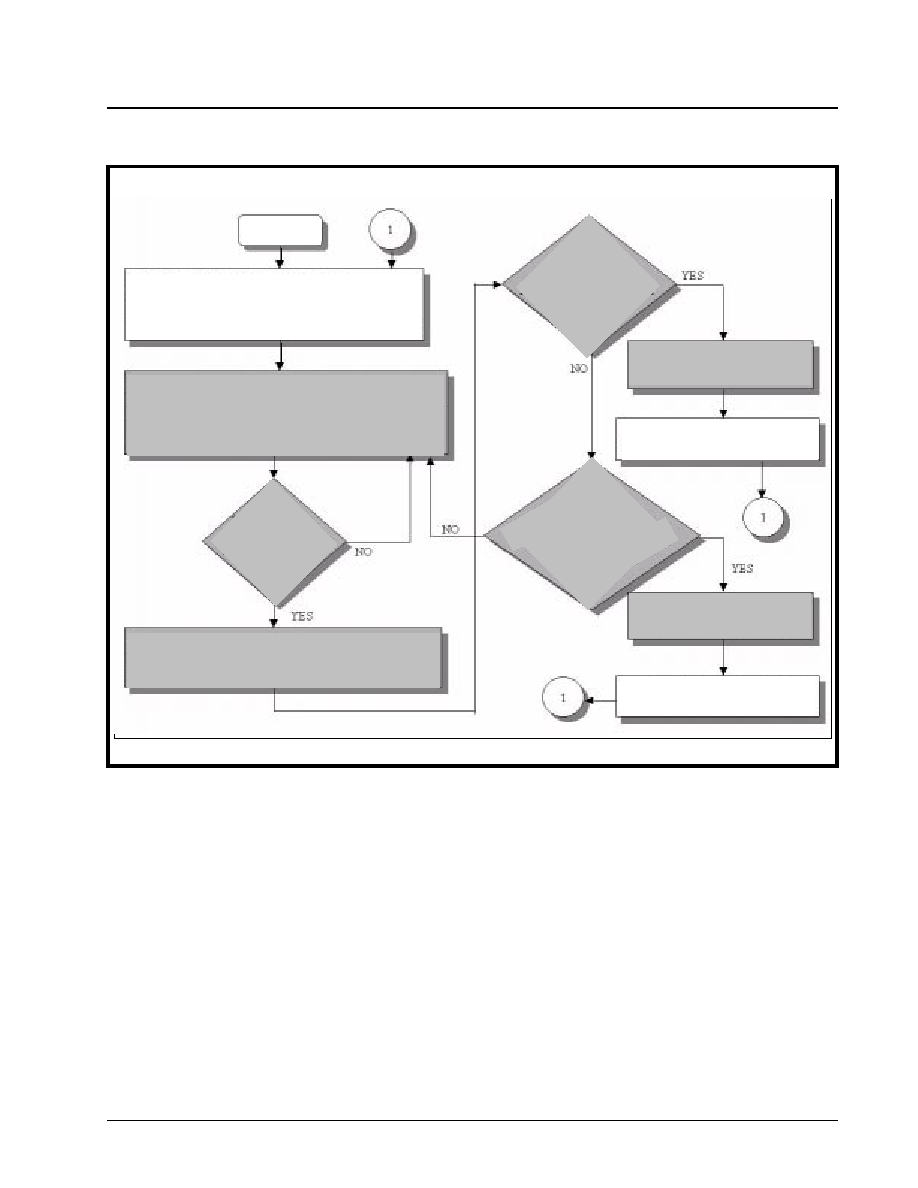

- Reading Performance Monitor (PMON) �Registers

- For Example

- The PMON Holding Register

- In Summary: Whenever an ç8-bité µC/µP needs to read a PMON Register, it must execute the followin...

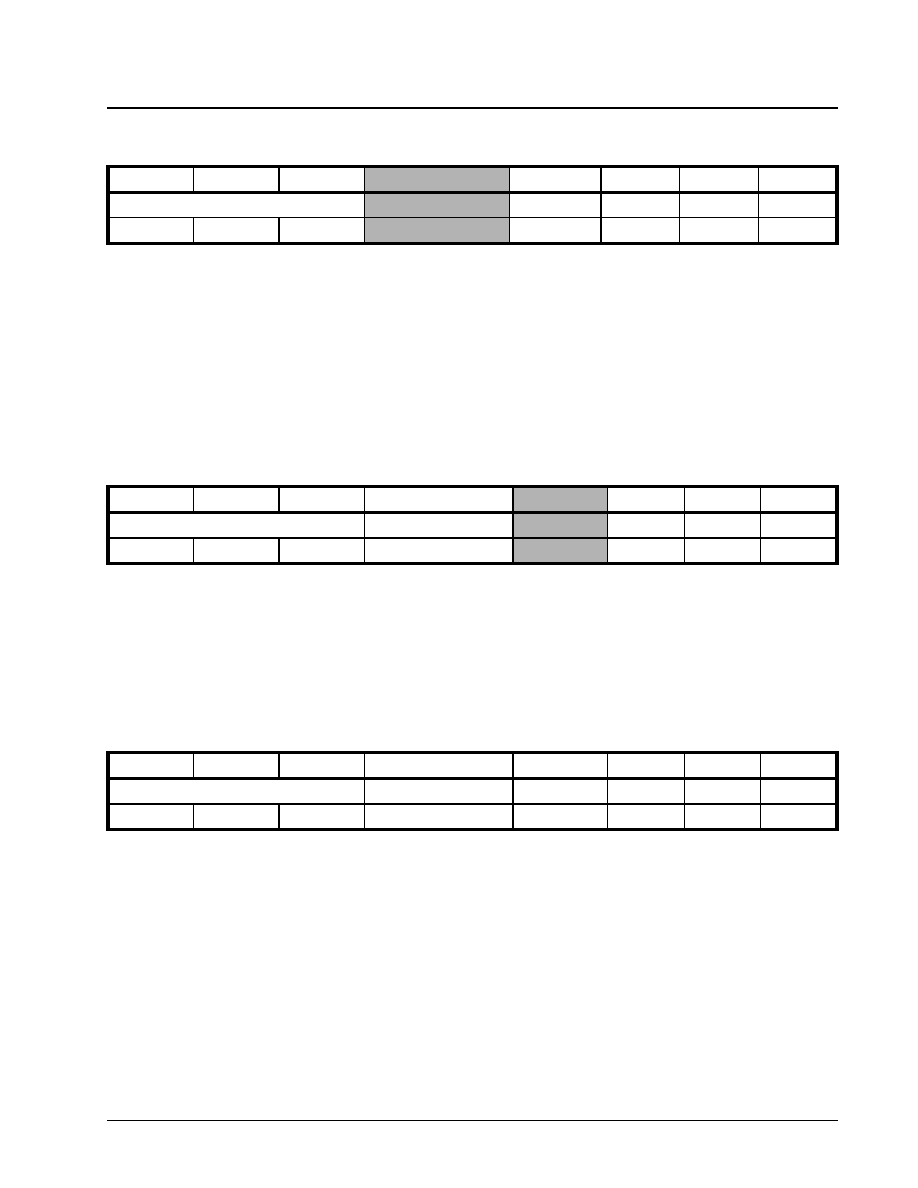

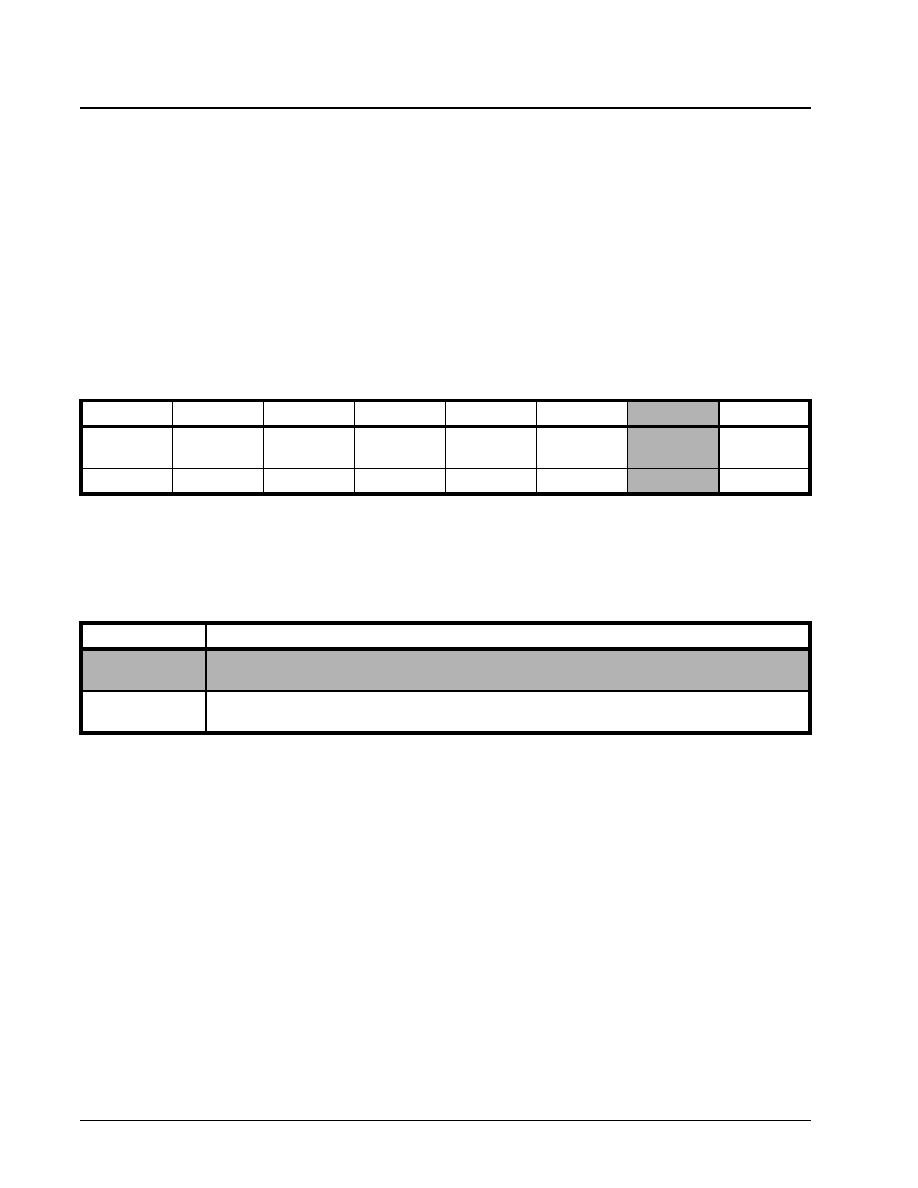

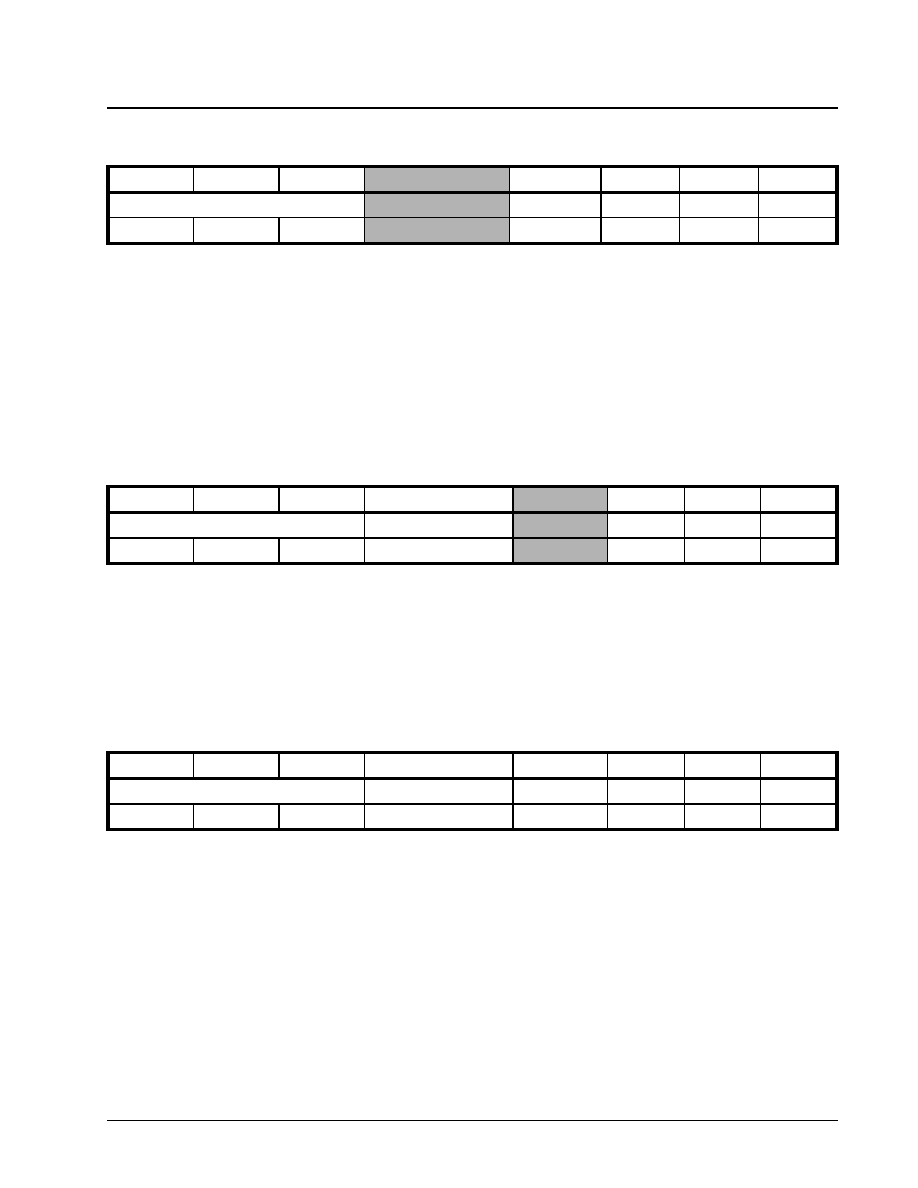

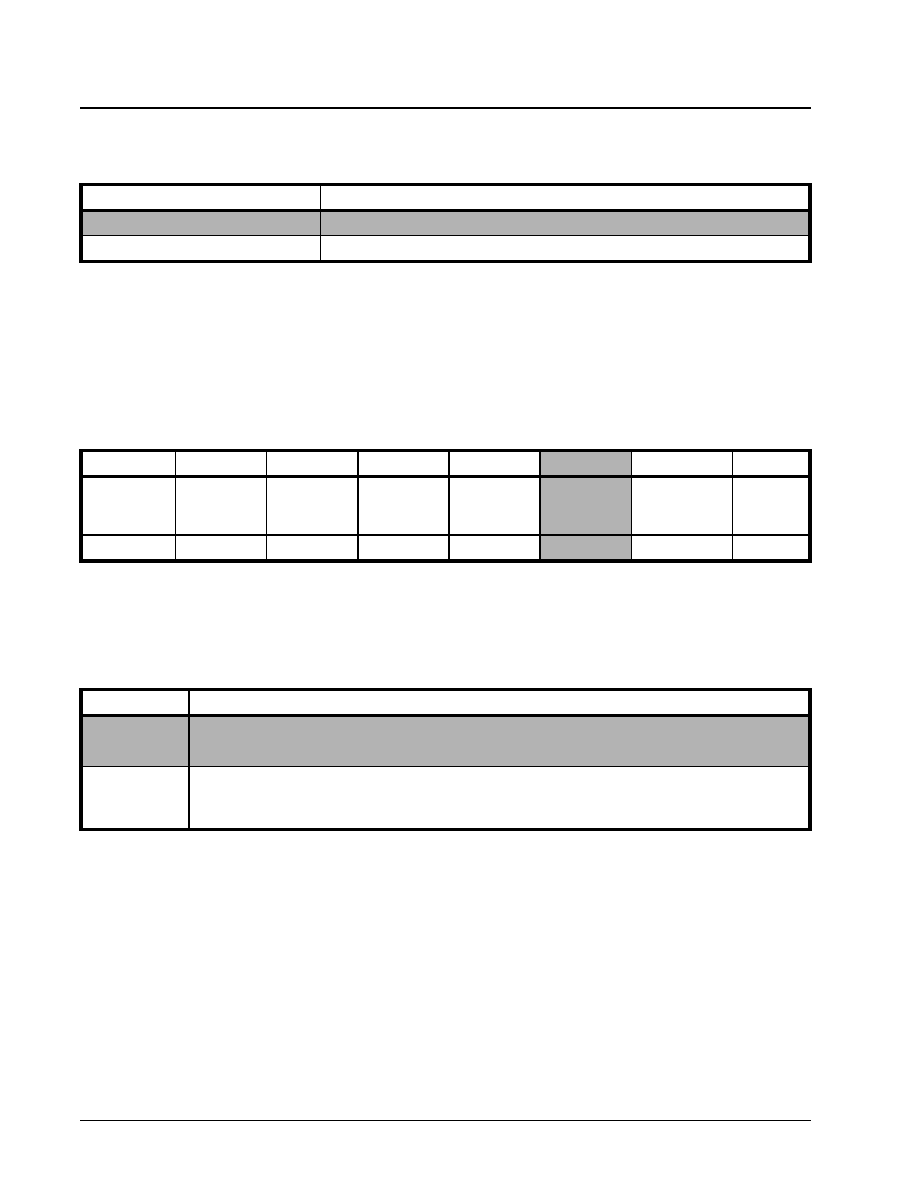

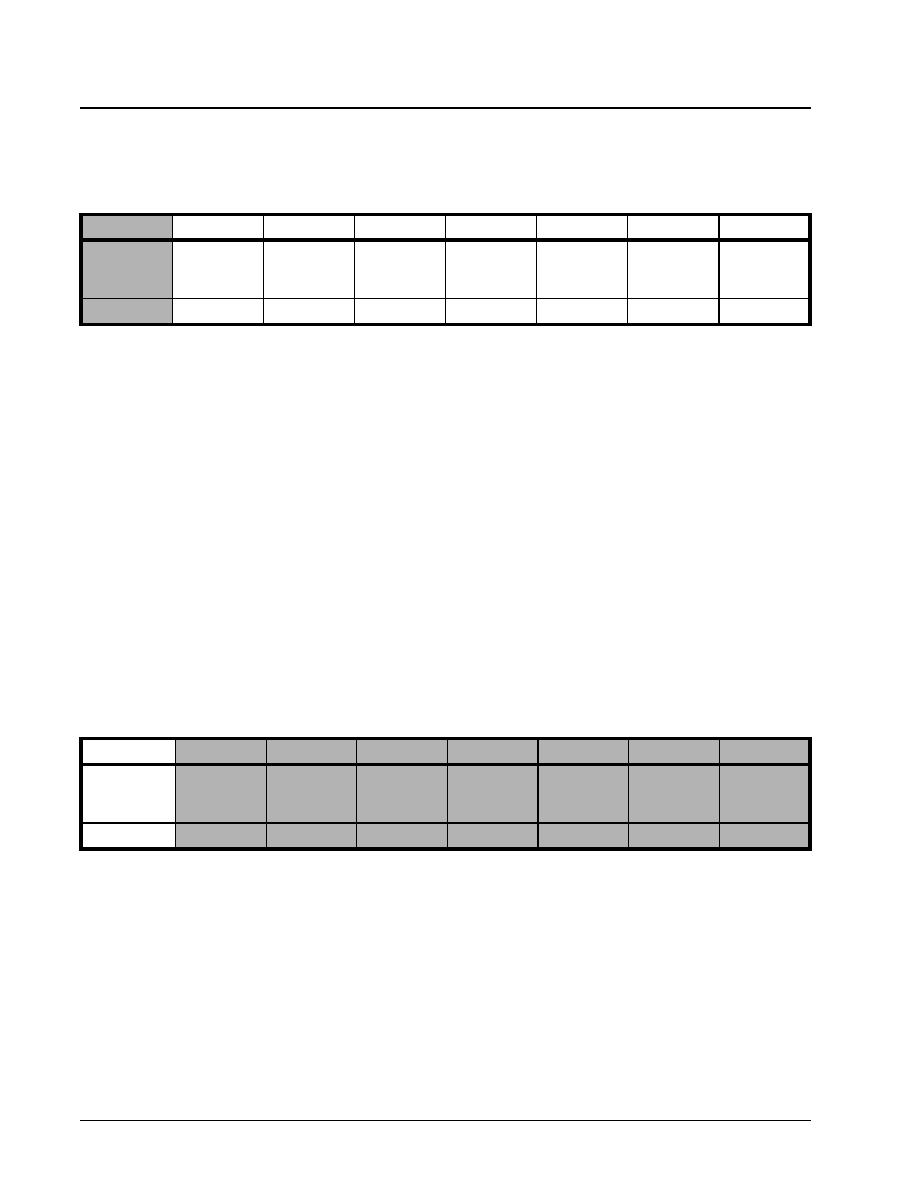

- 3.2.2 Data Access Modes

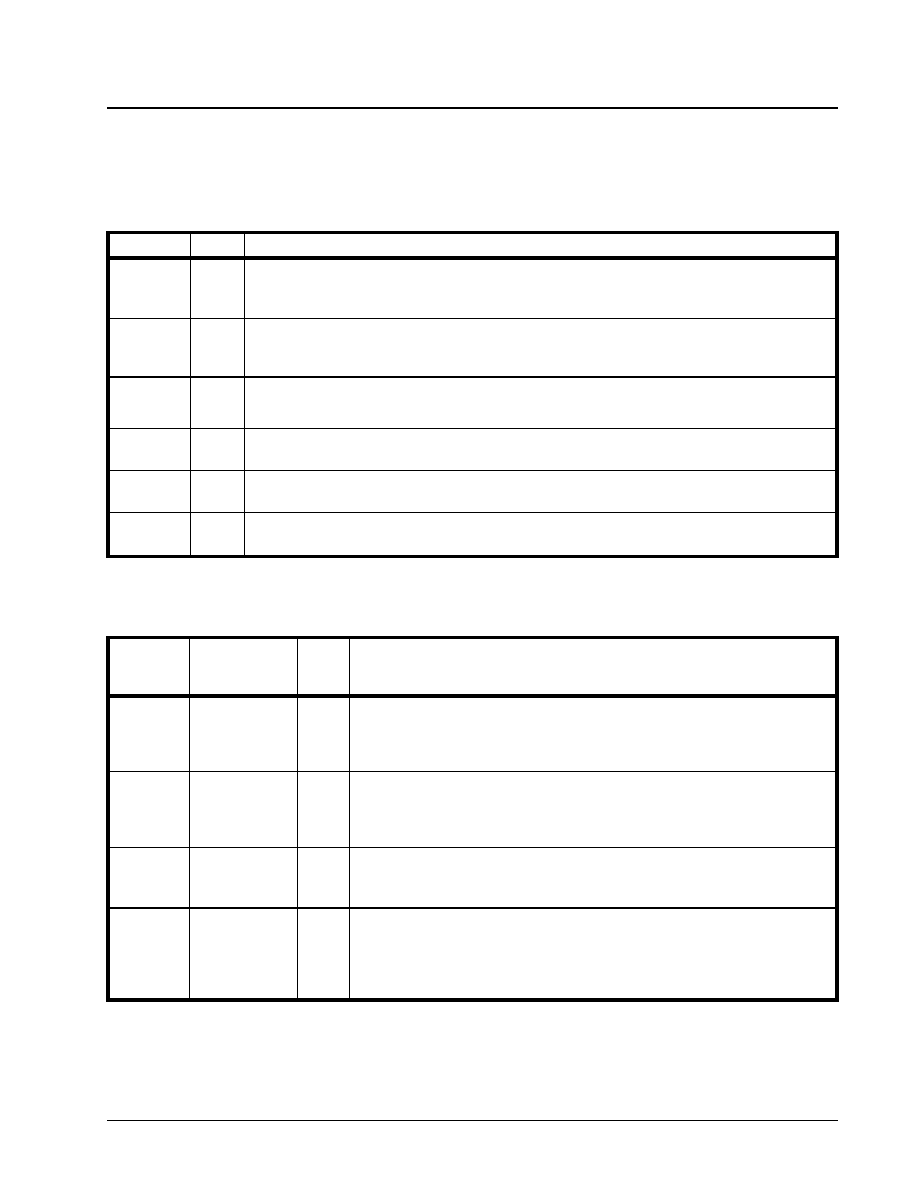

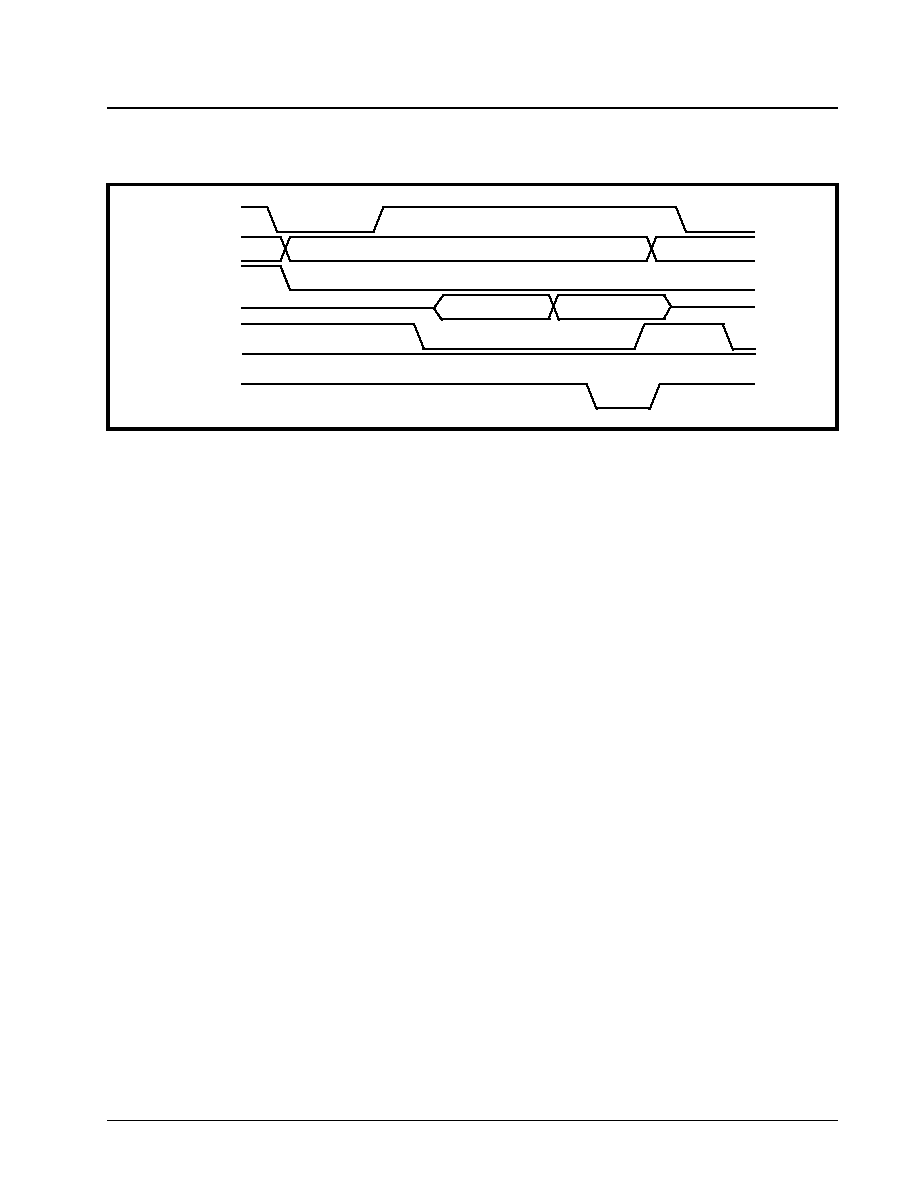

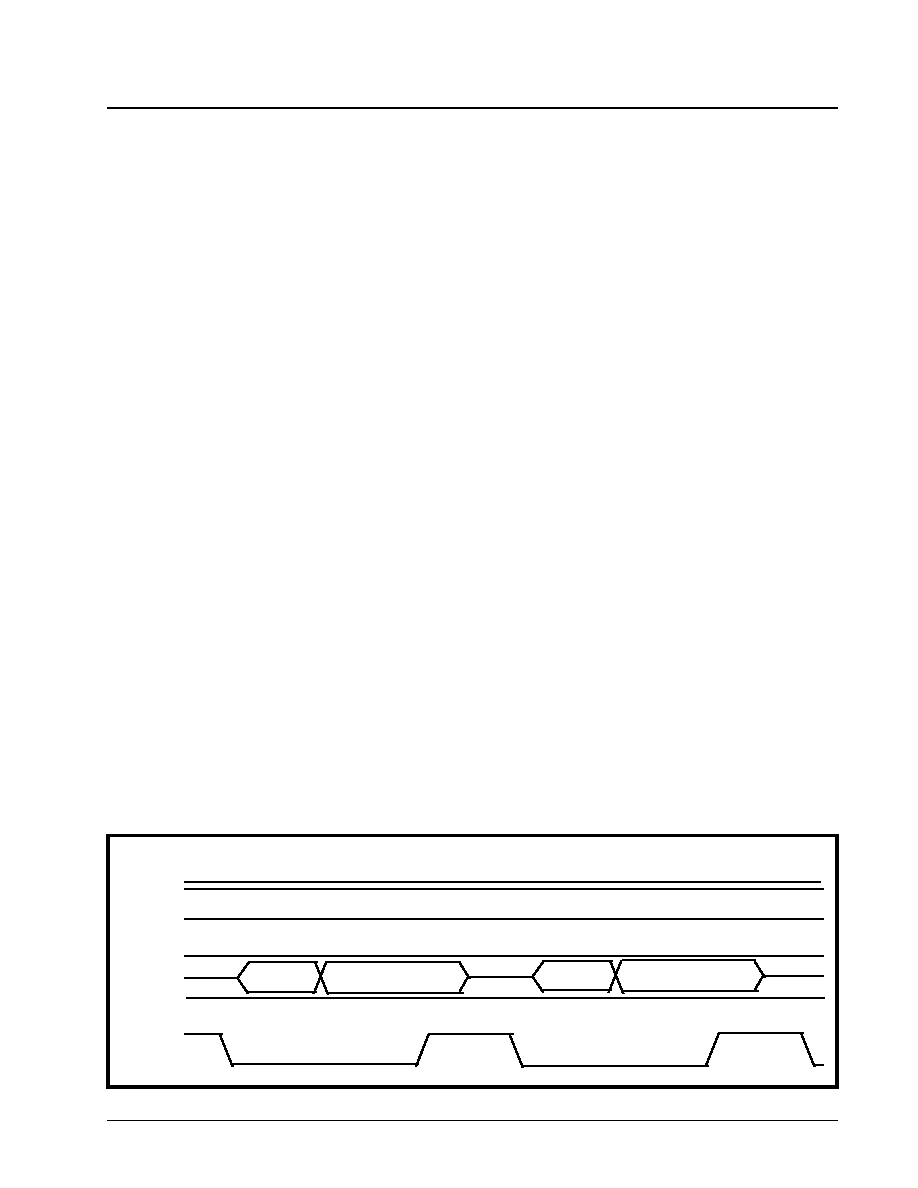

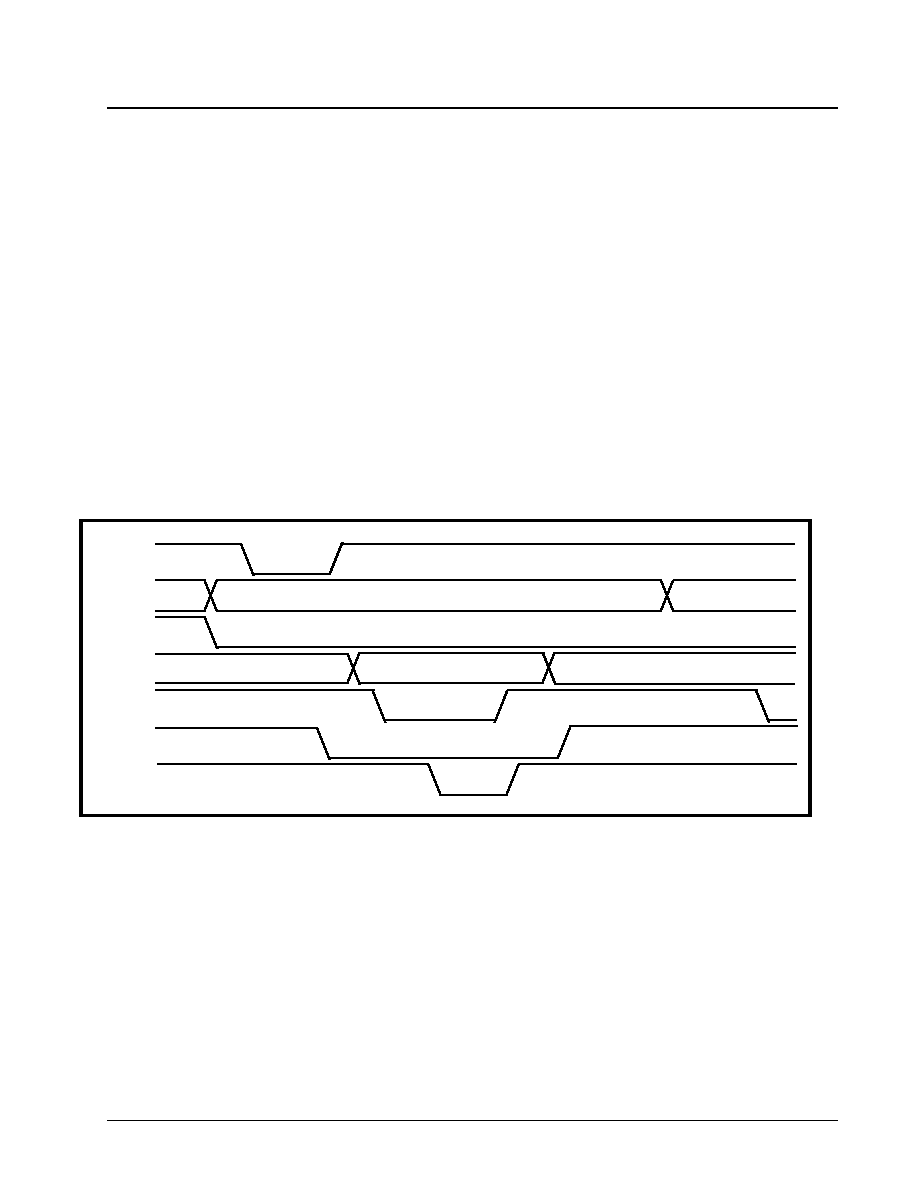

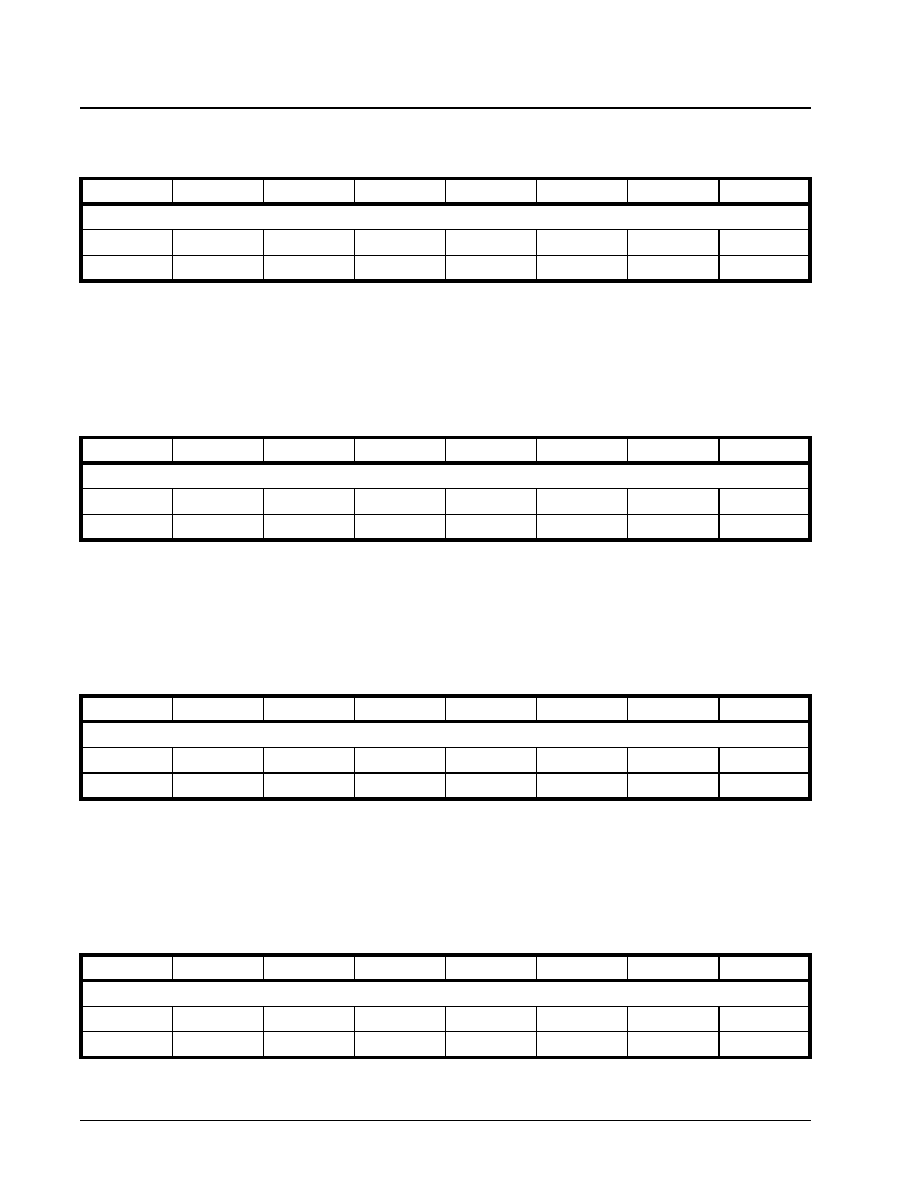

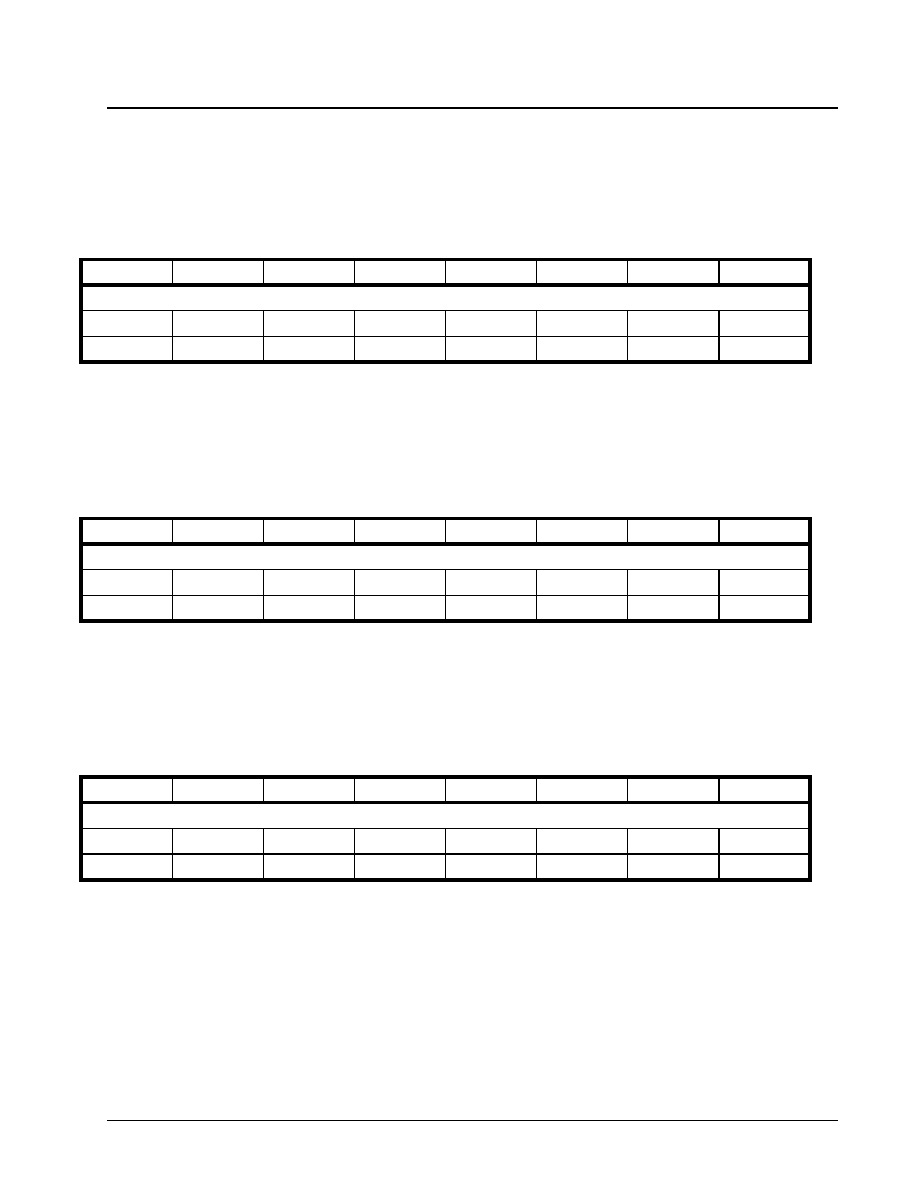

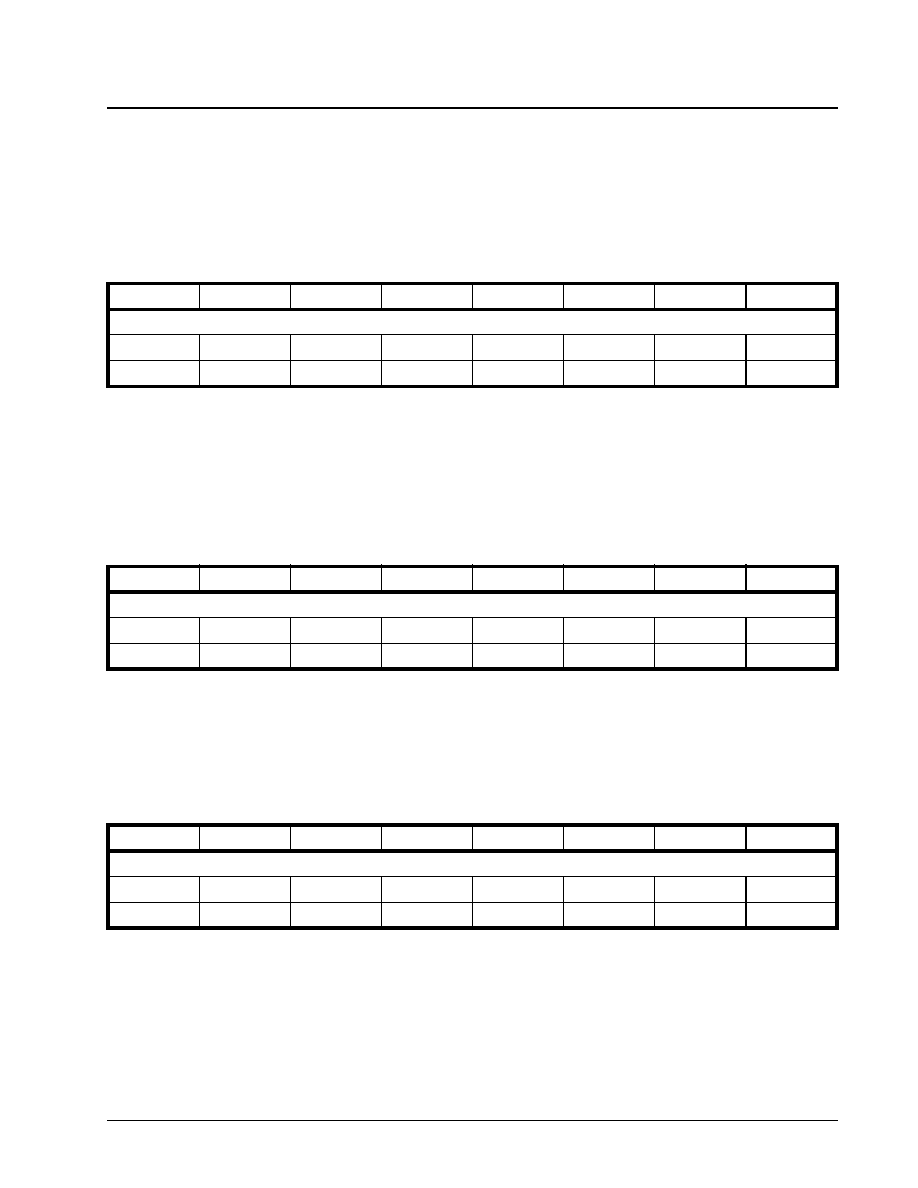

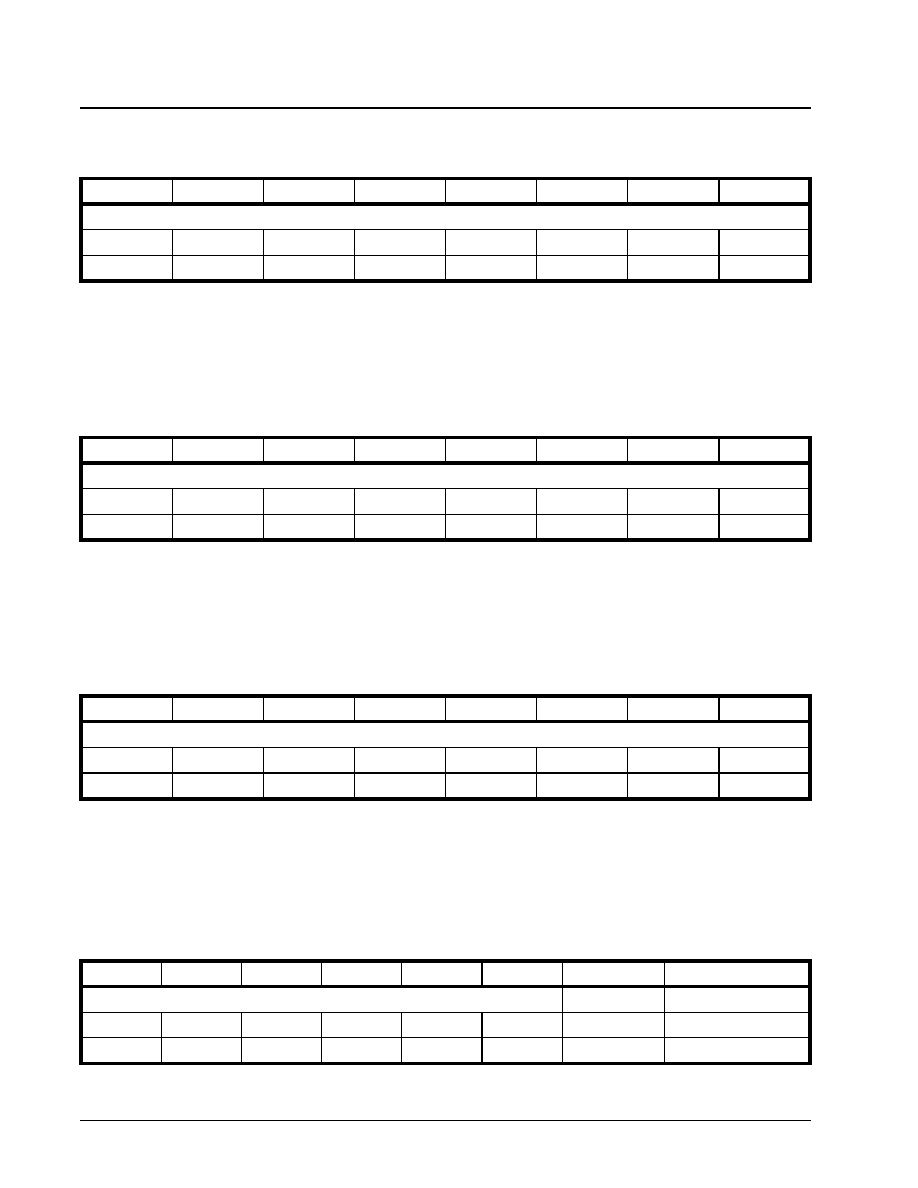

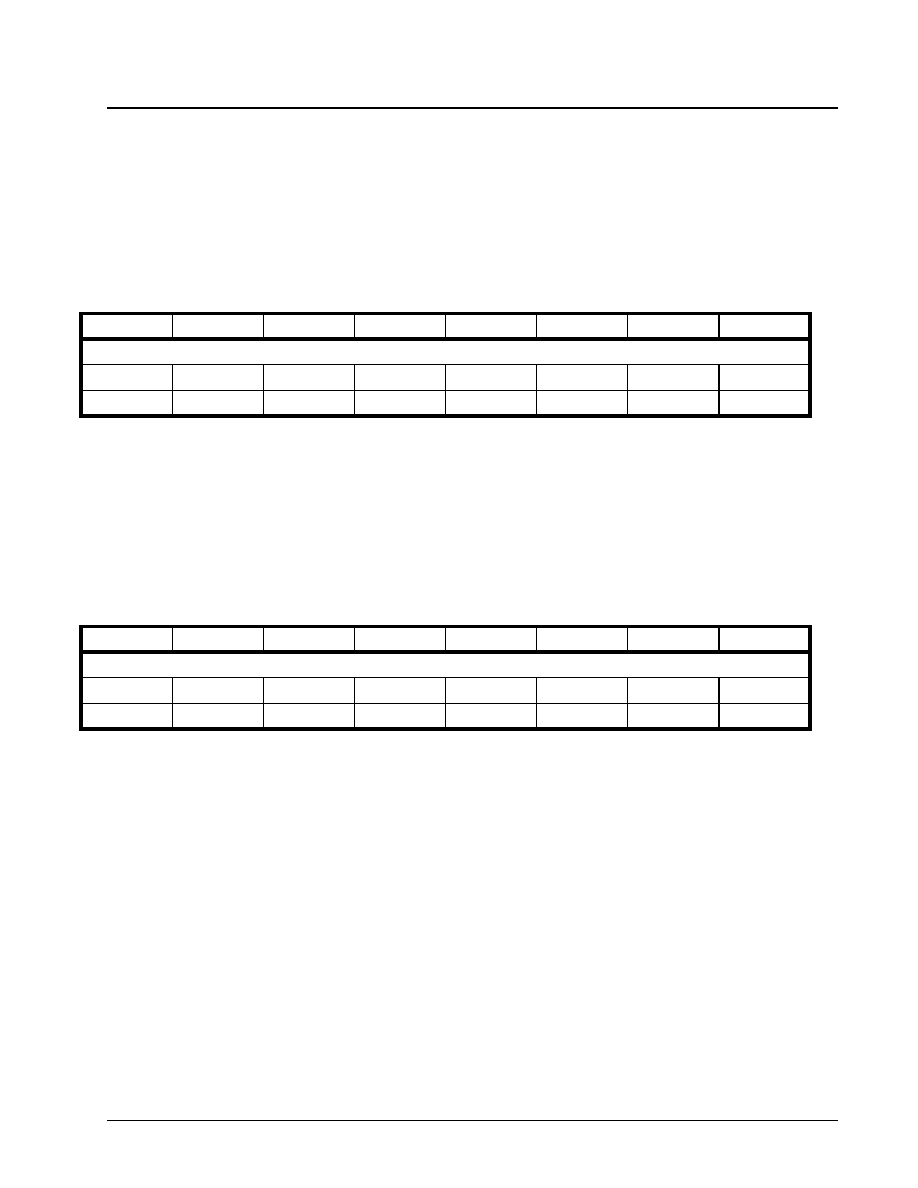

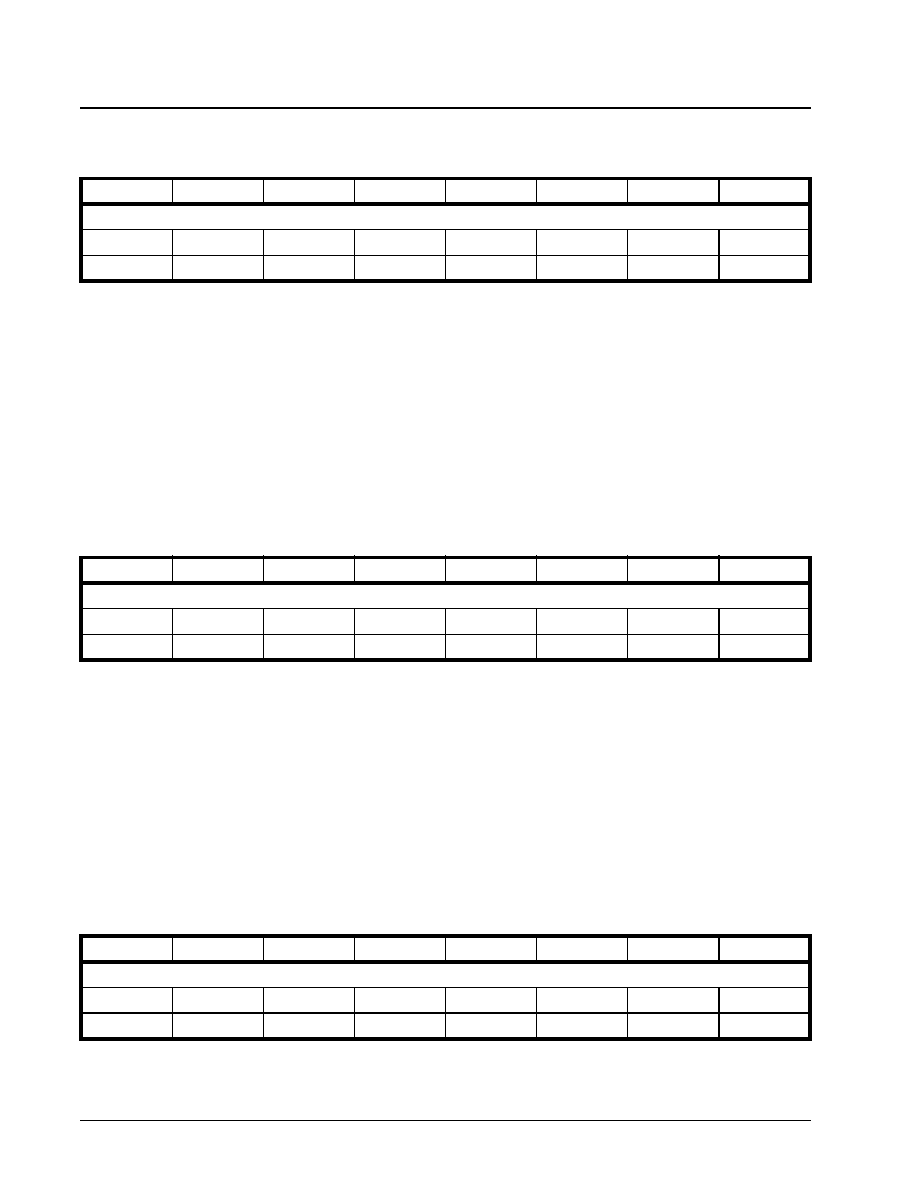

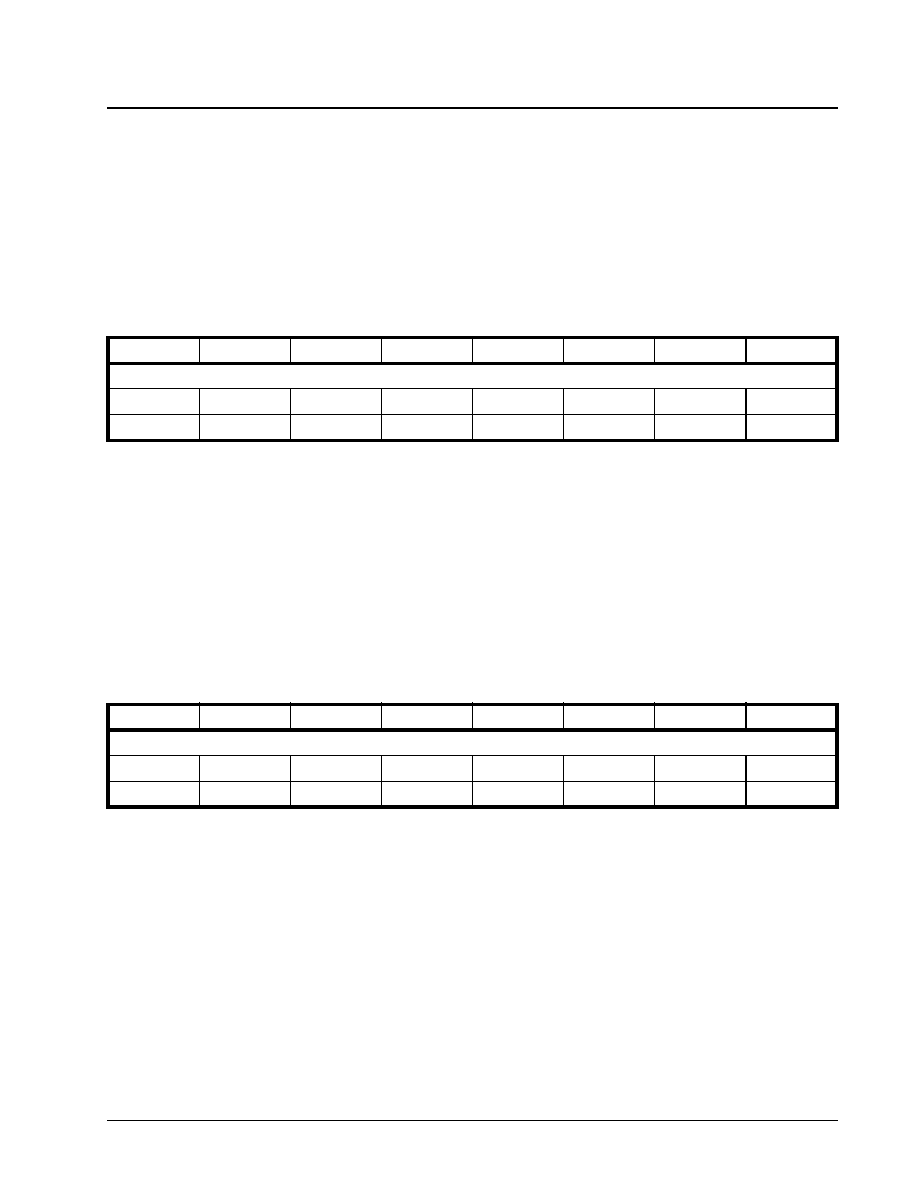

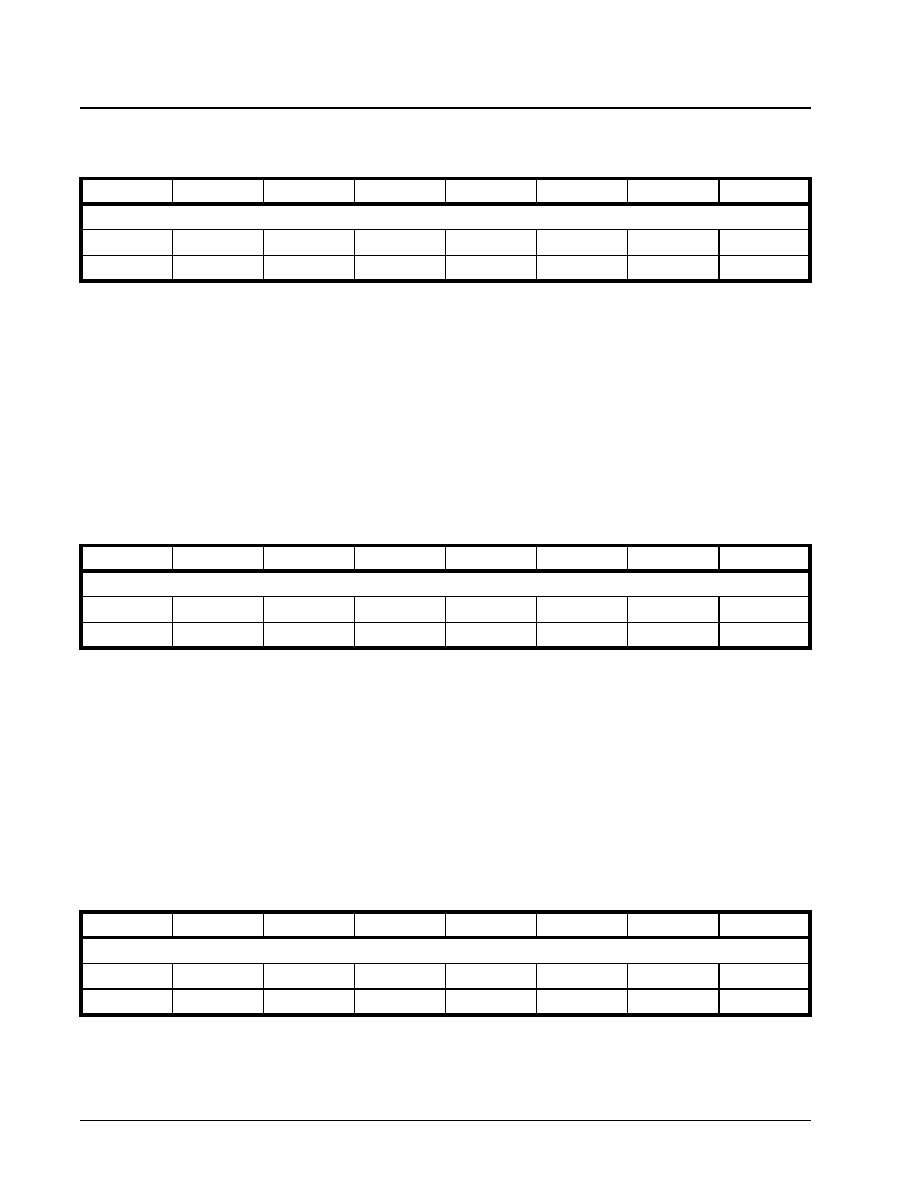

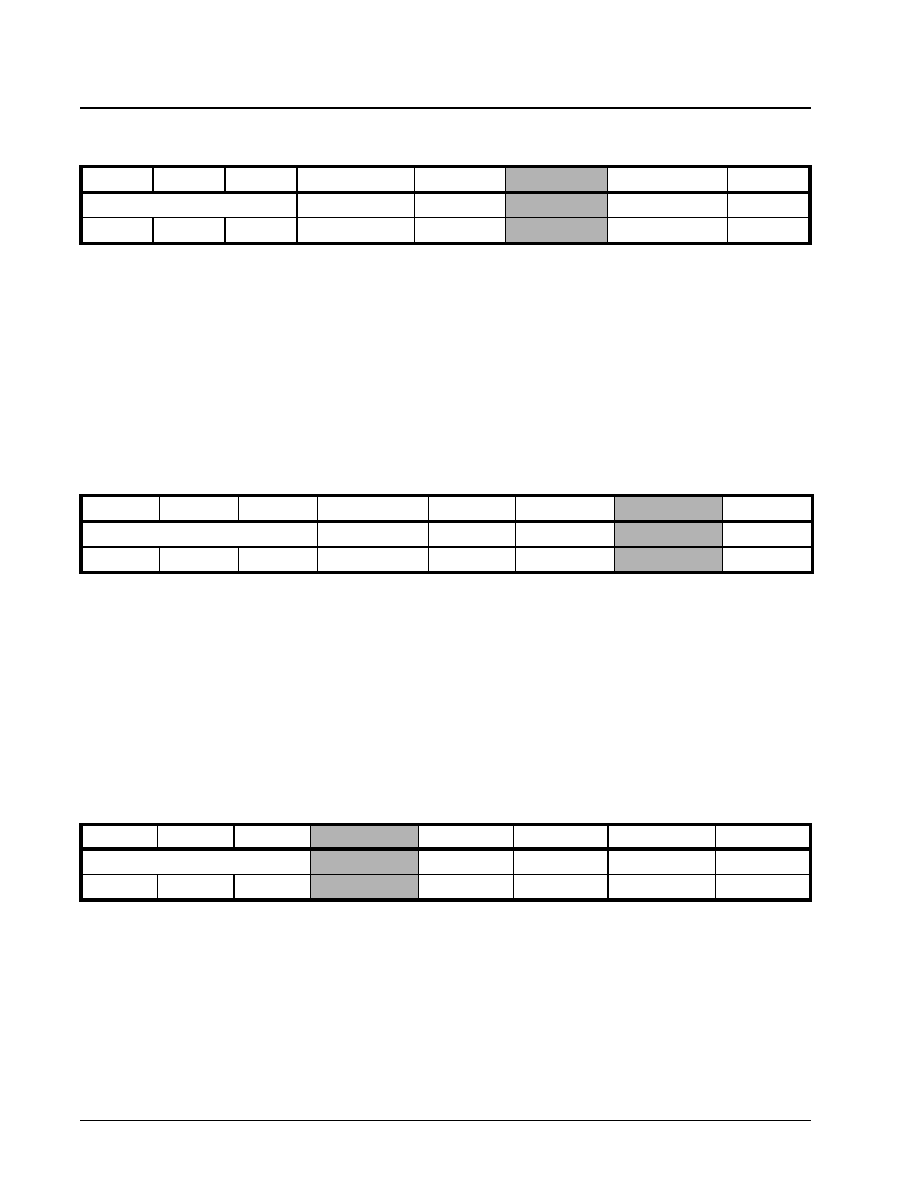

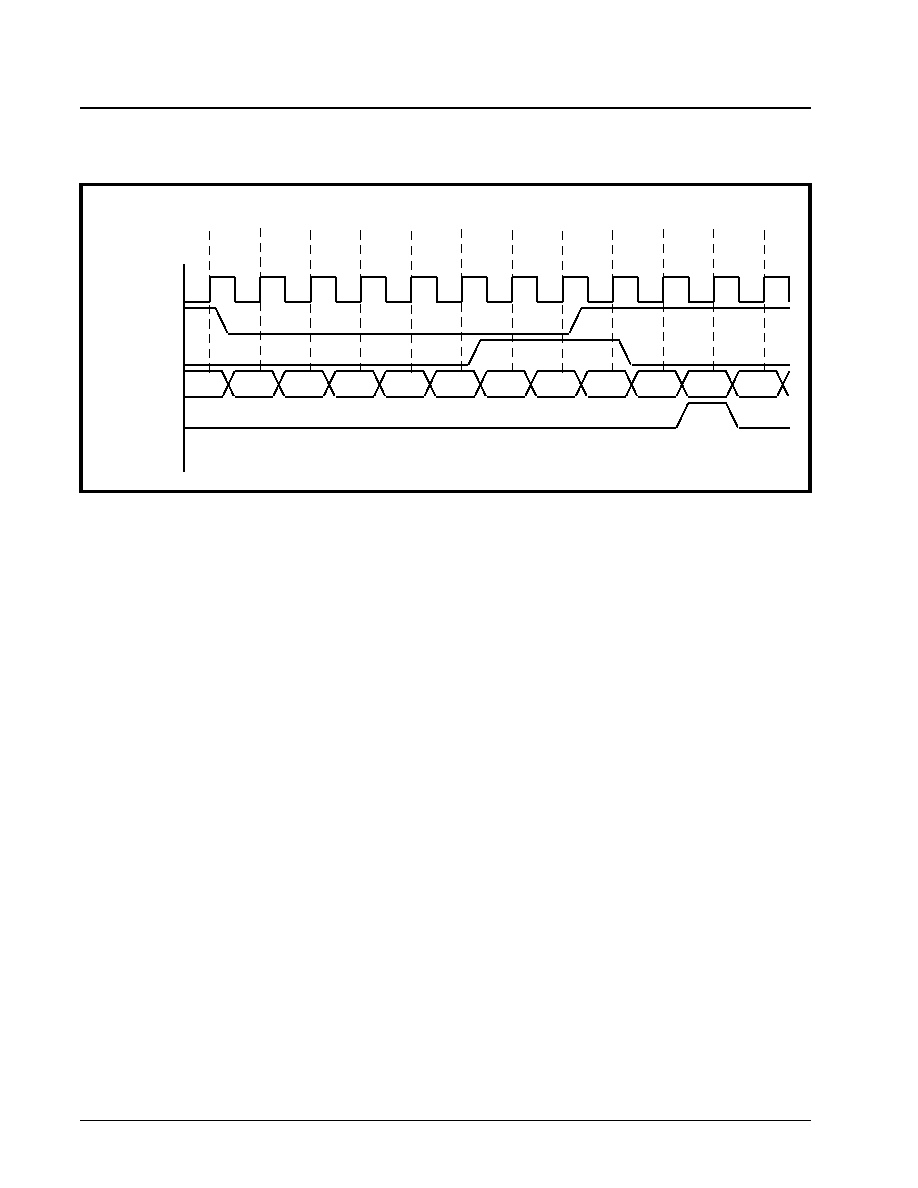

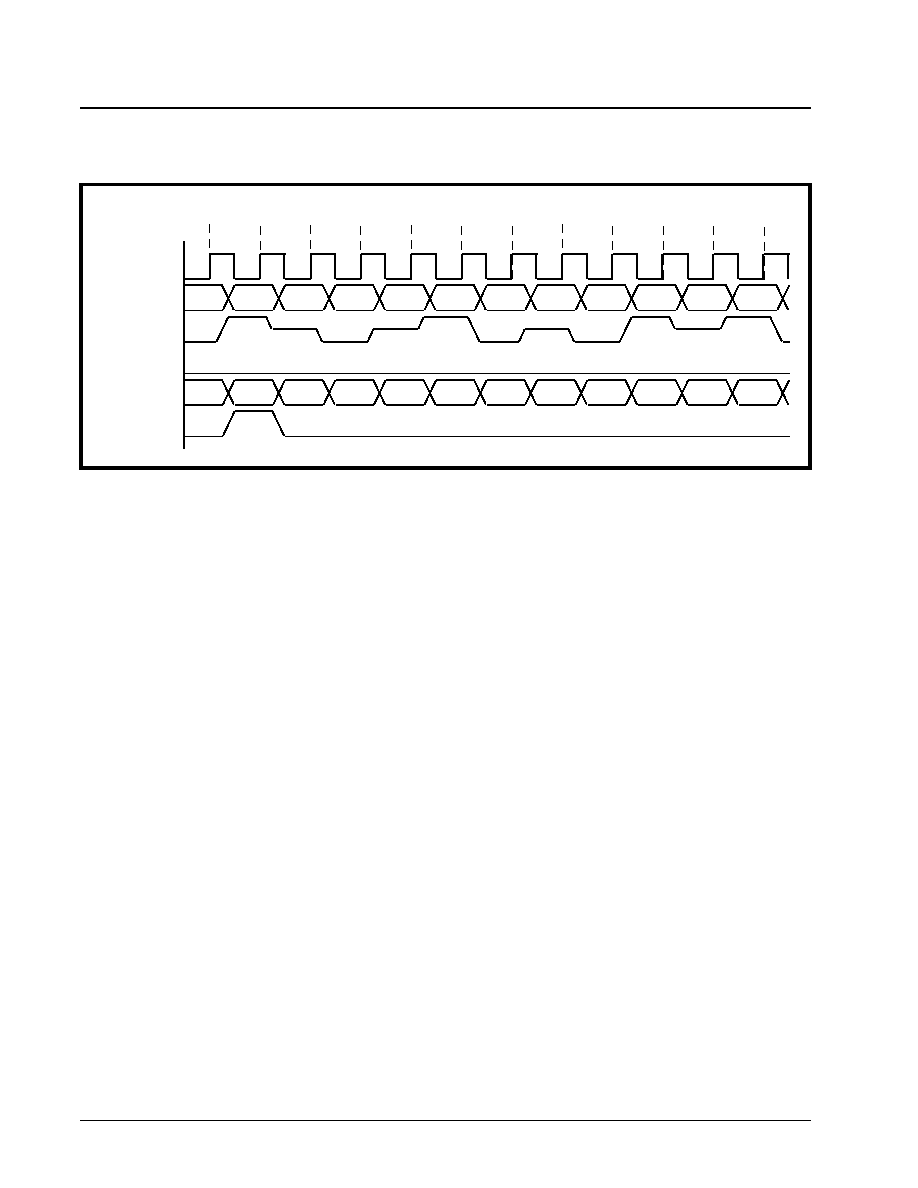

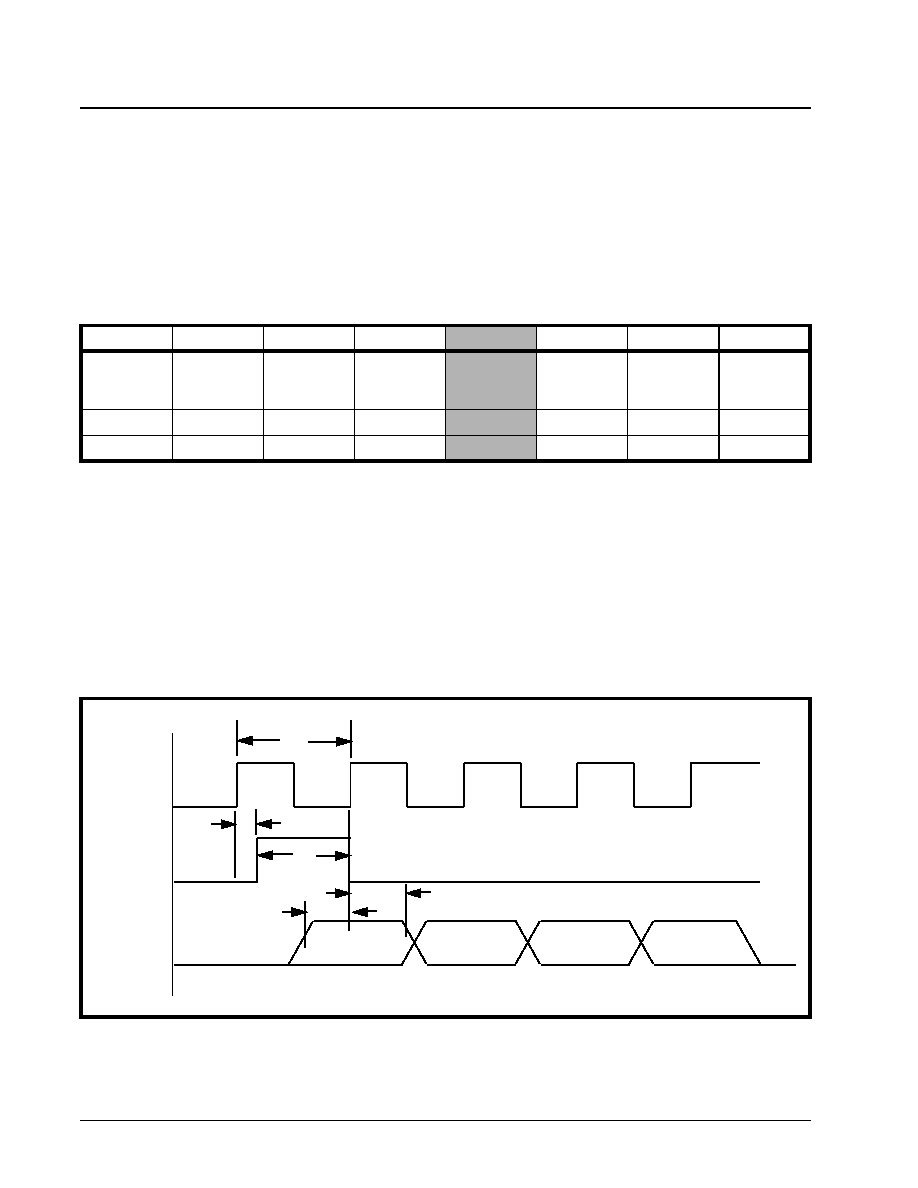

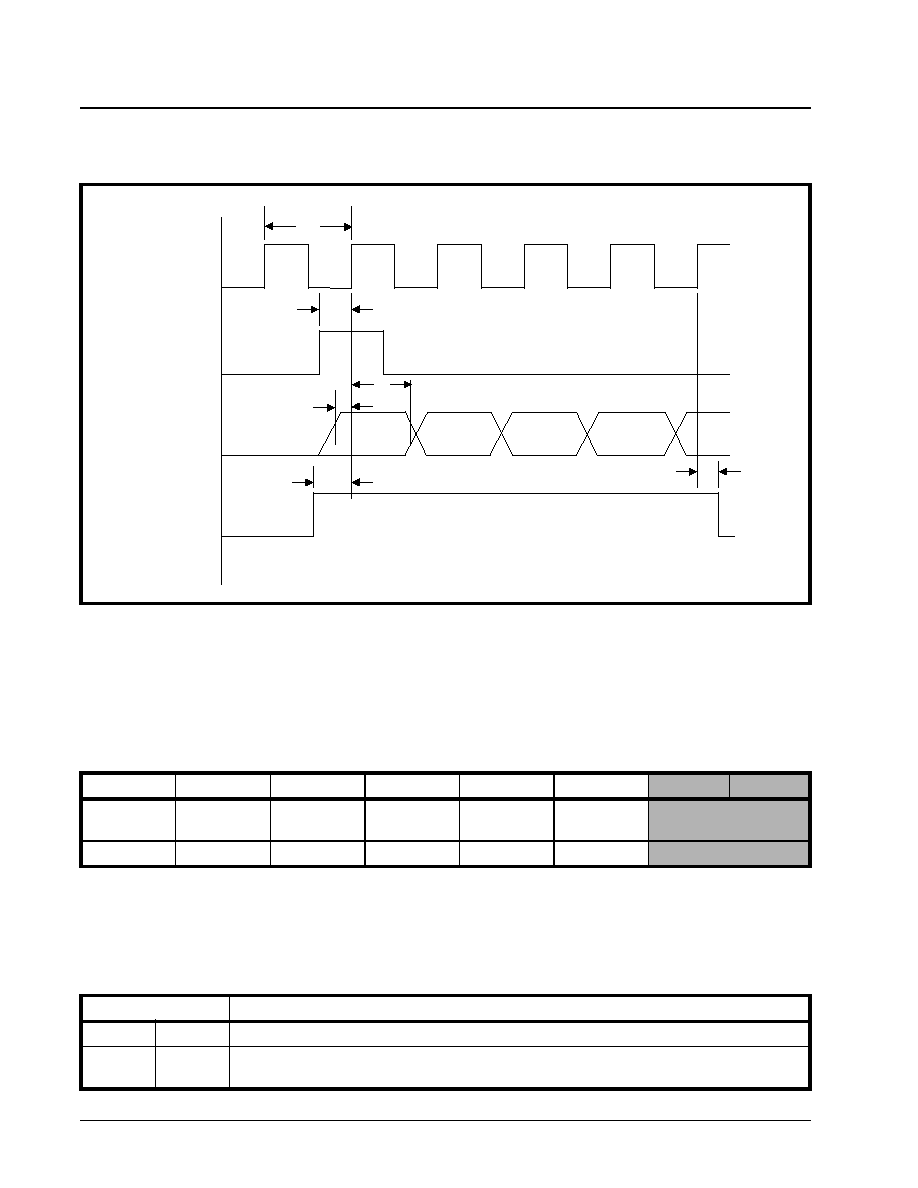

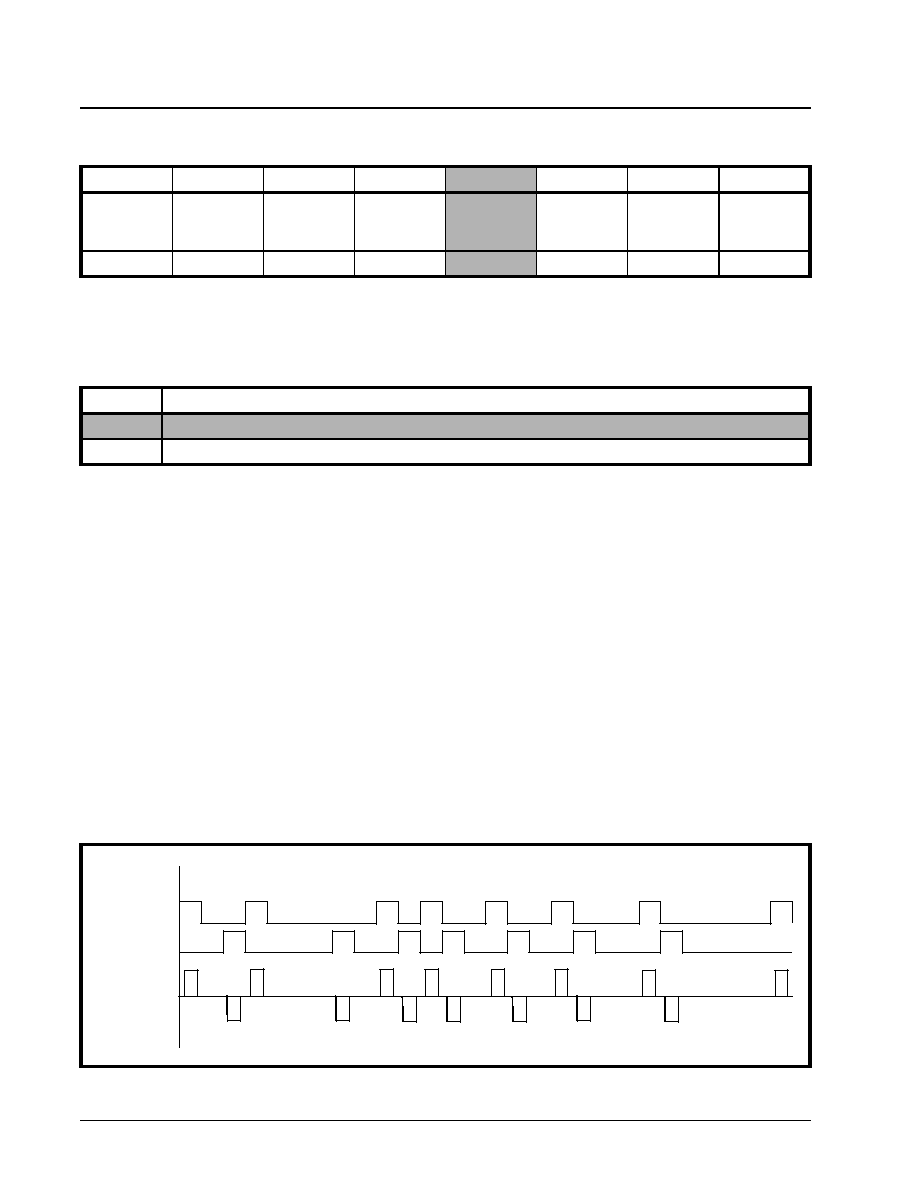

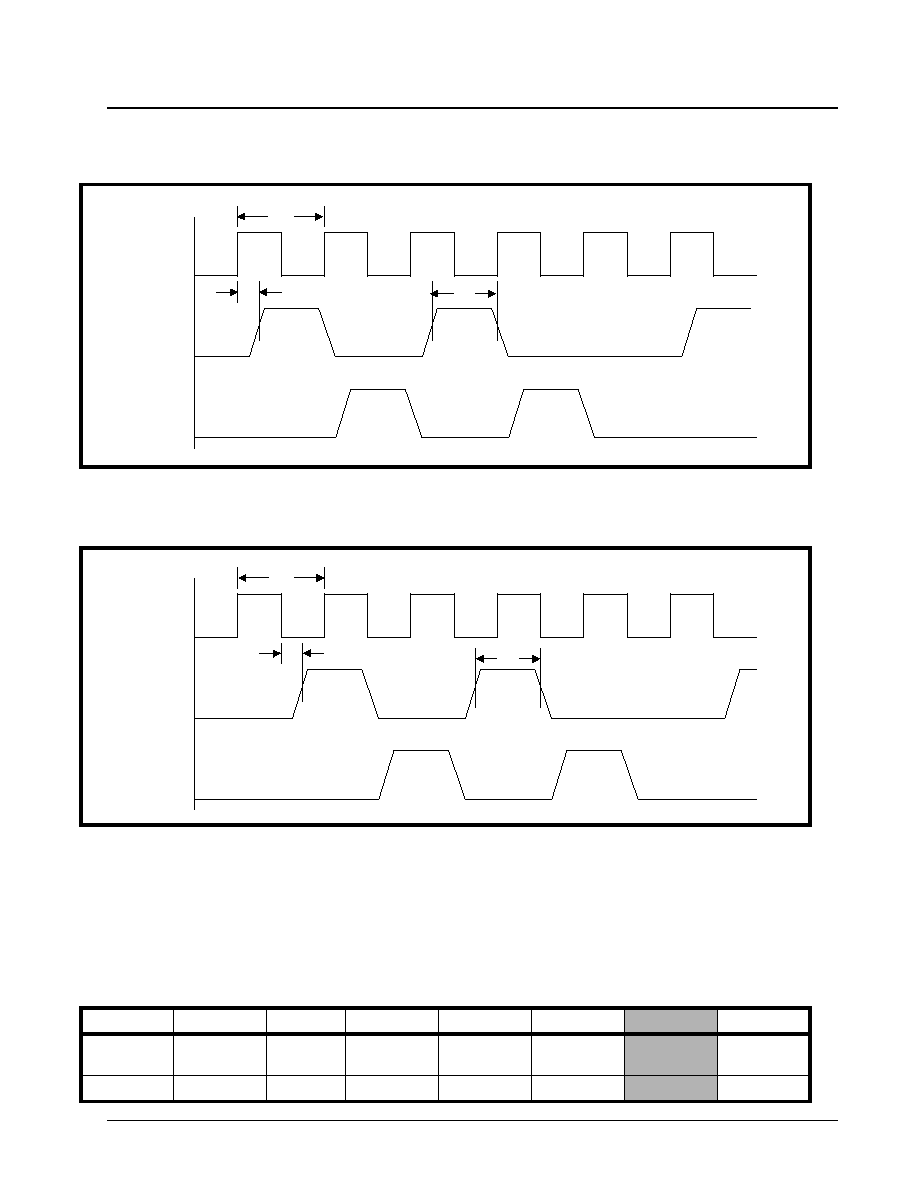

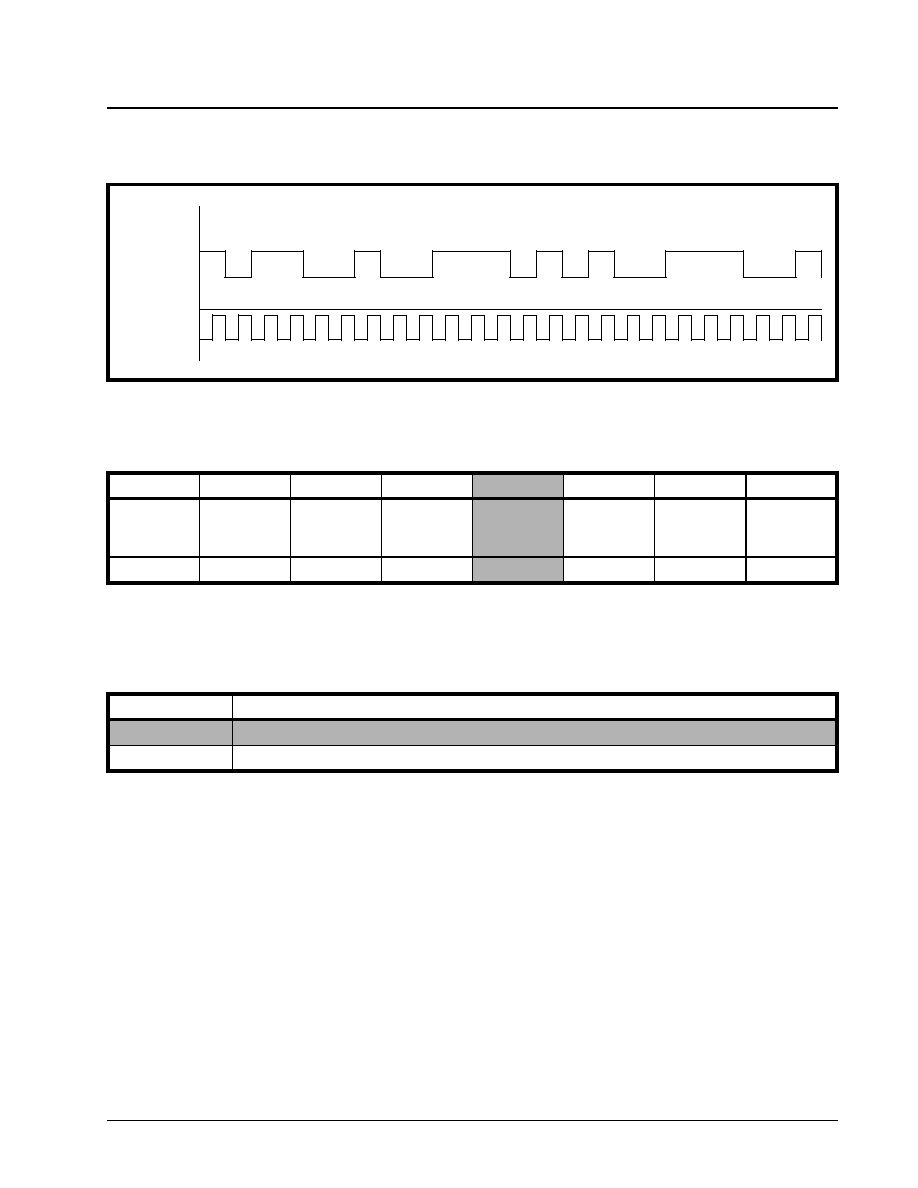

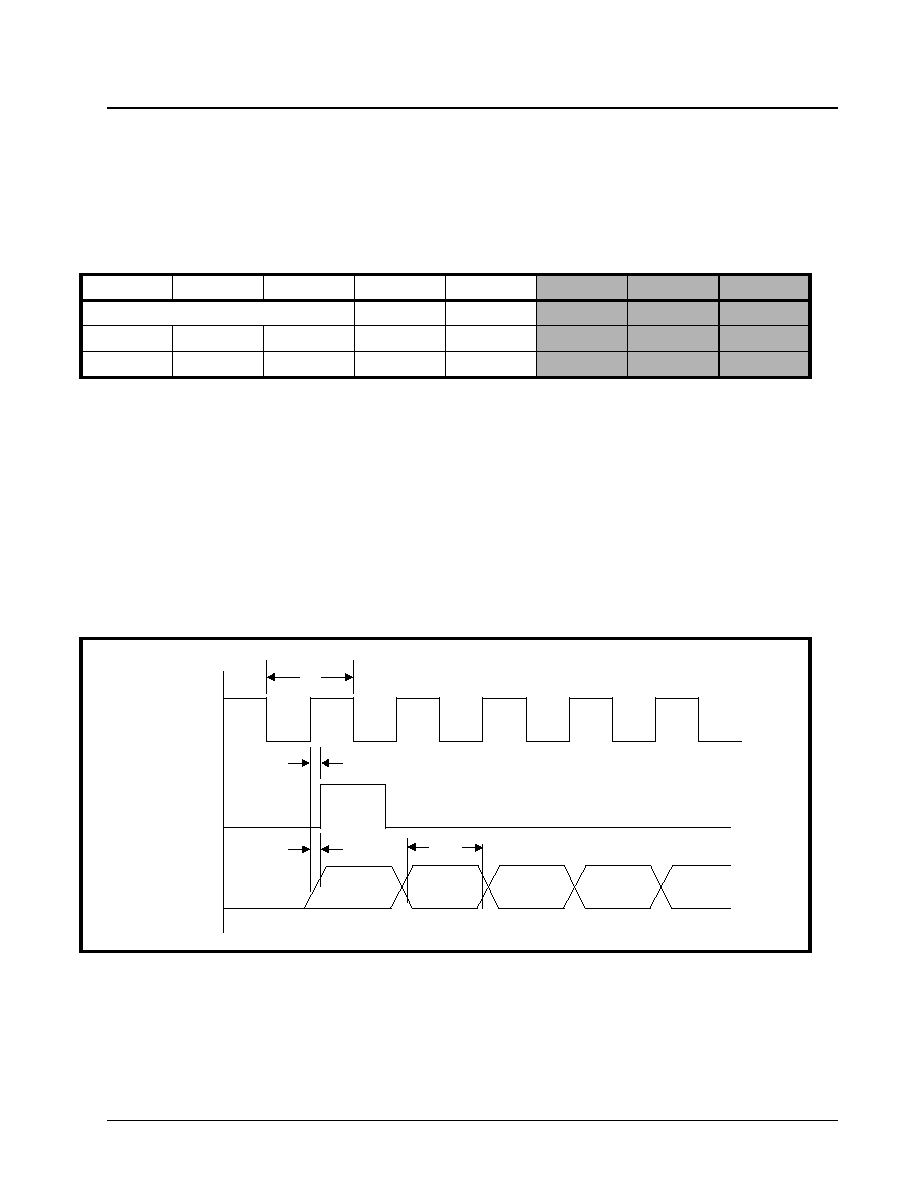

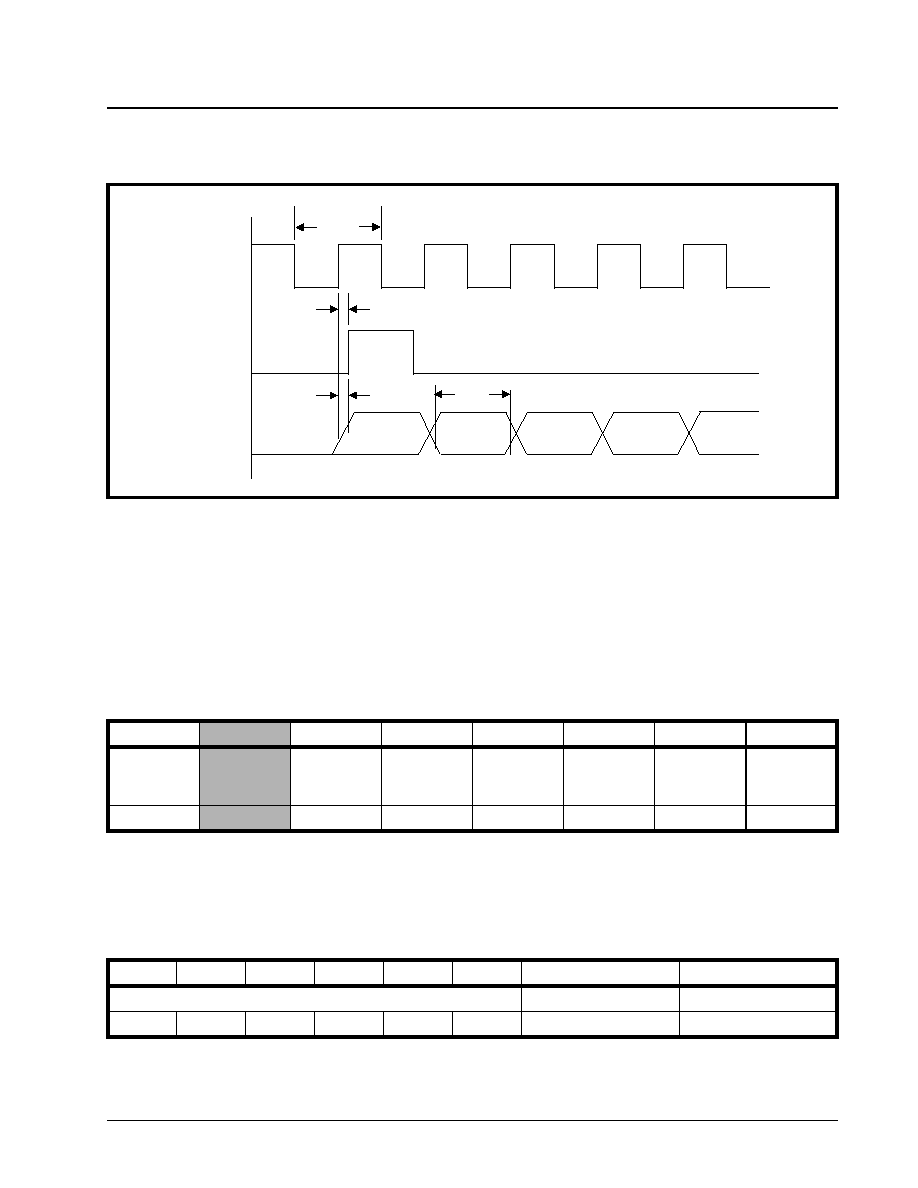

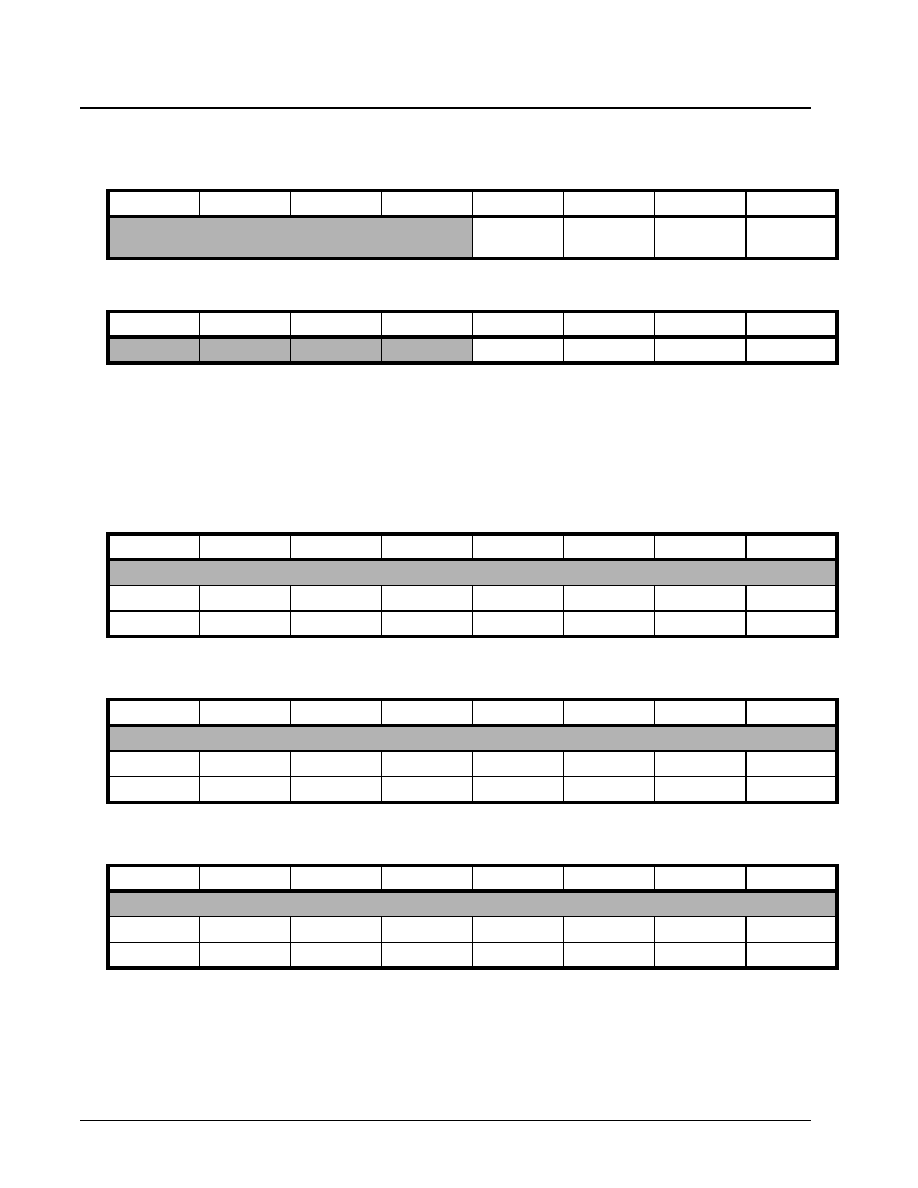

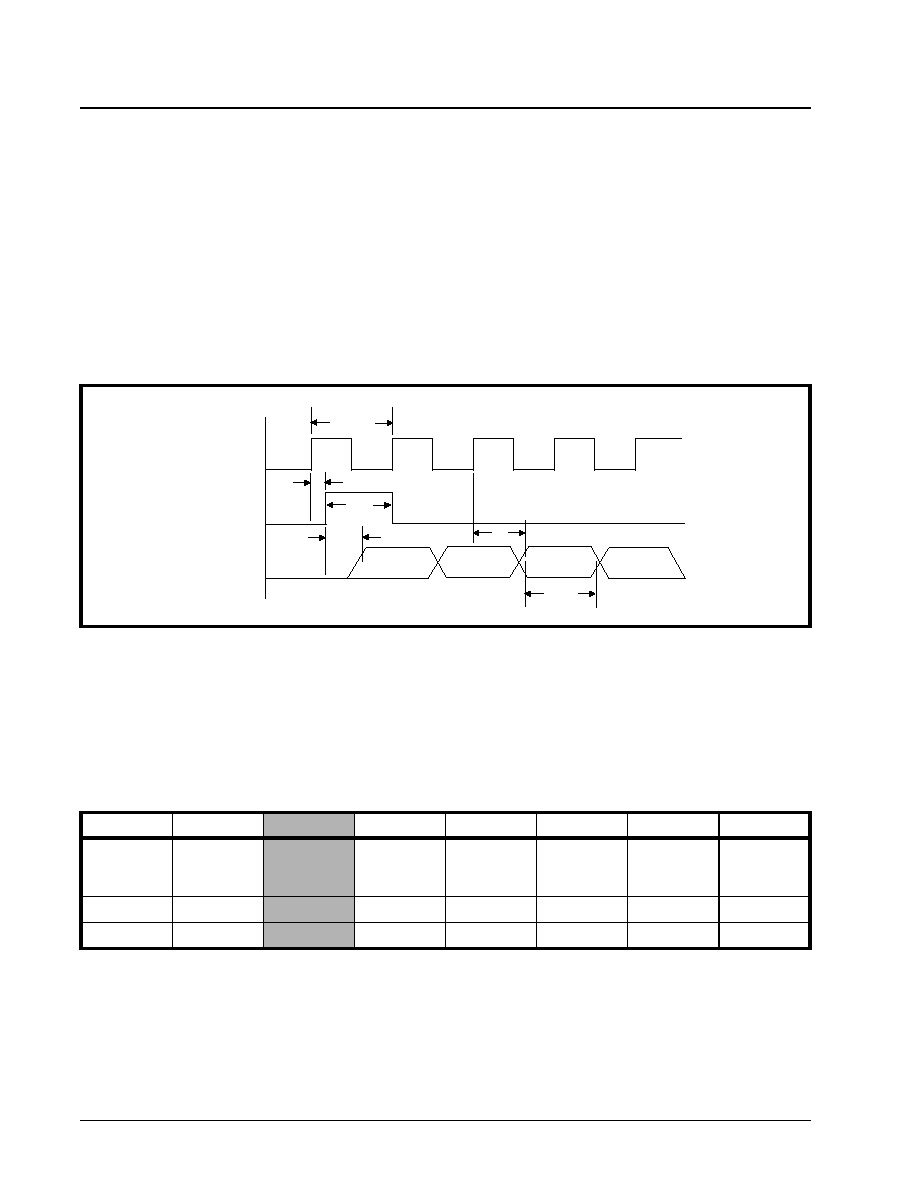

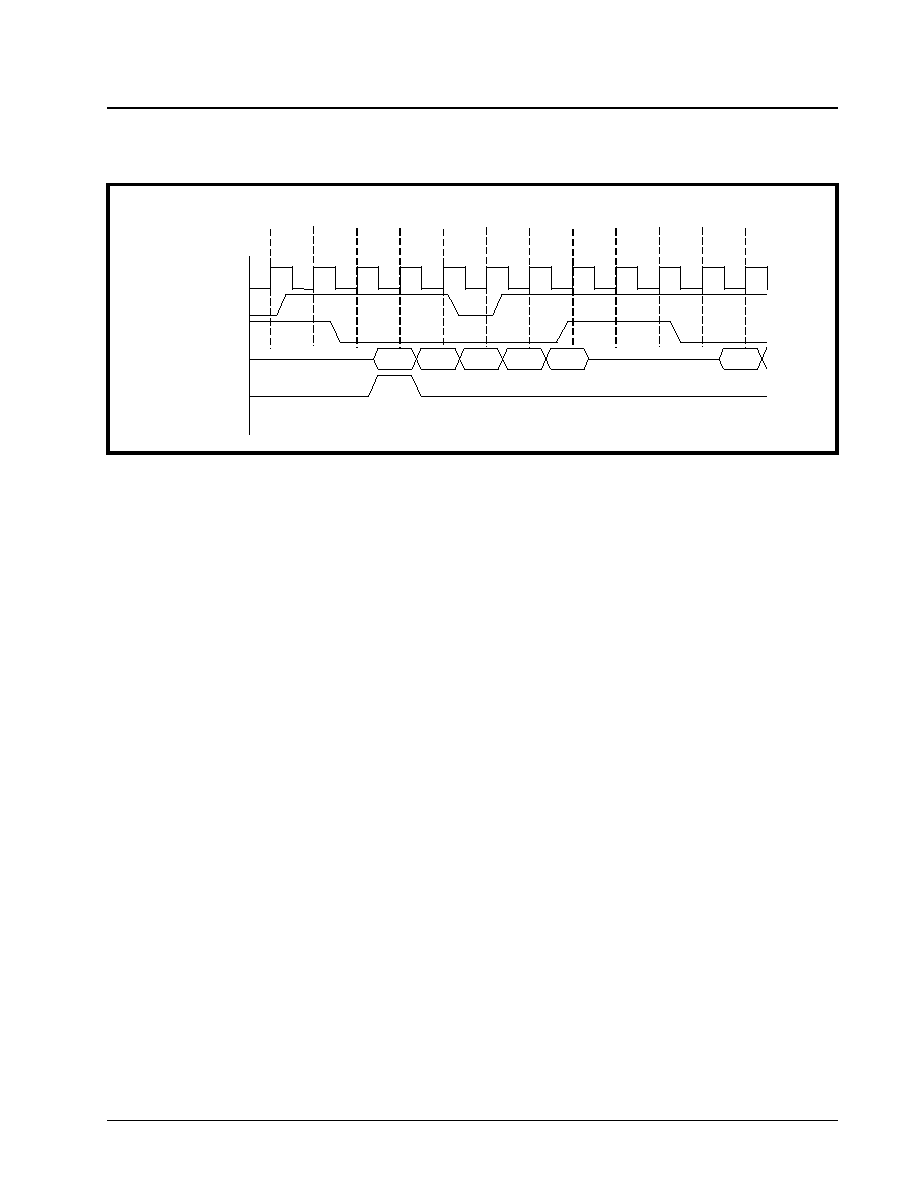

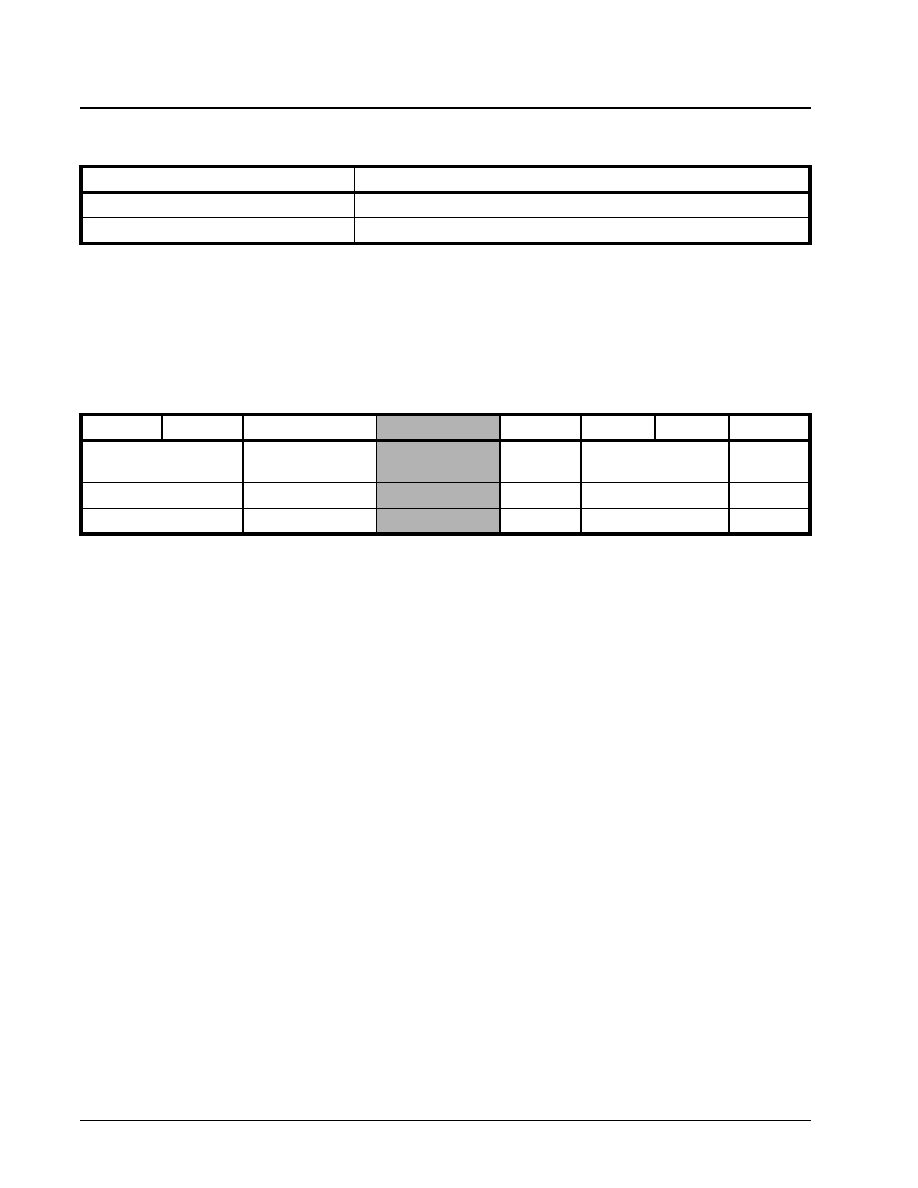

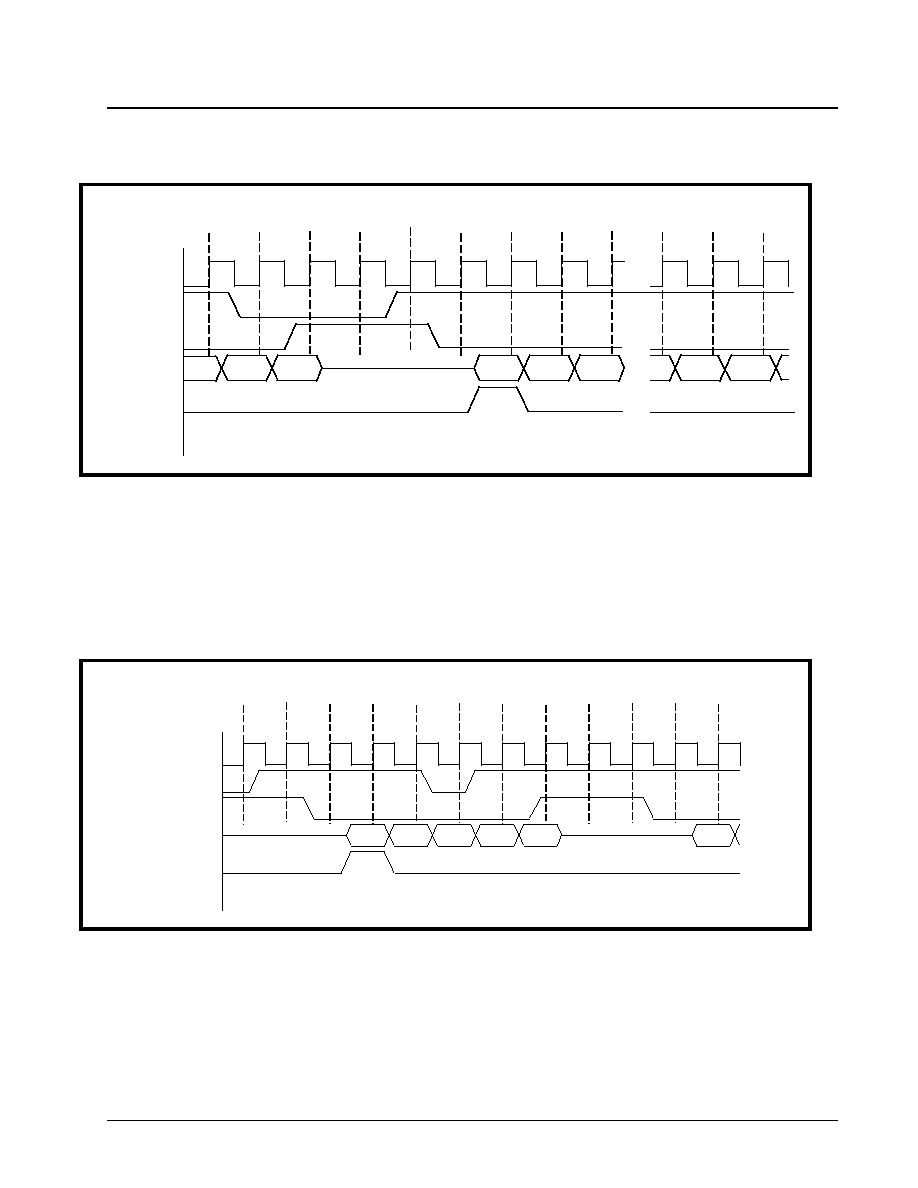

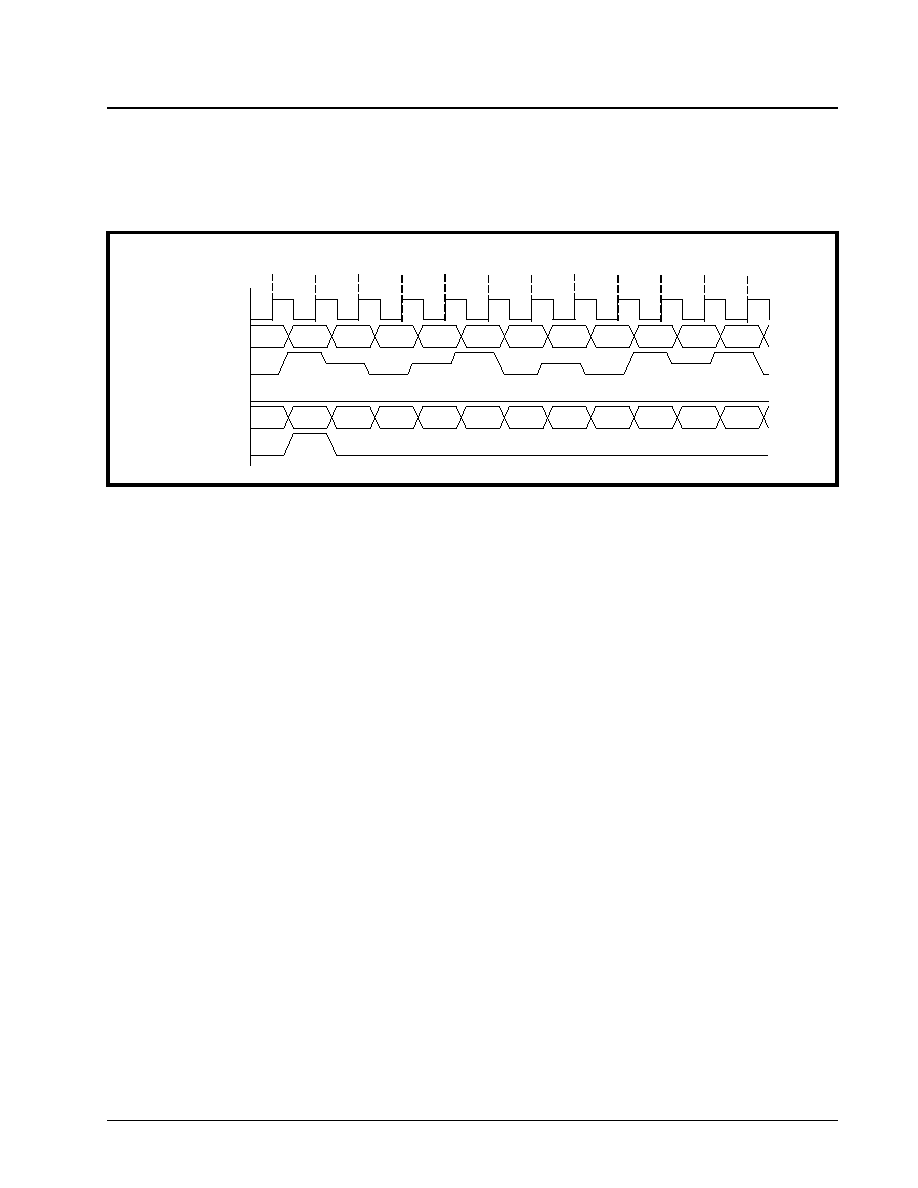

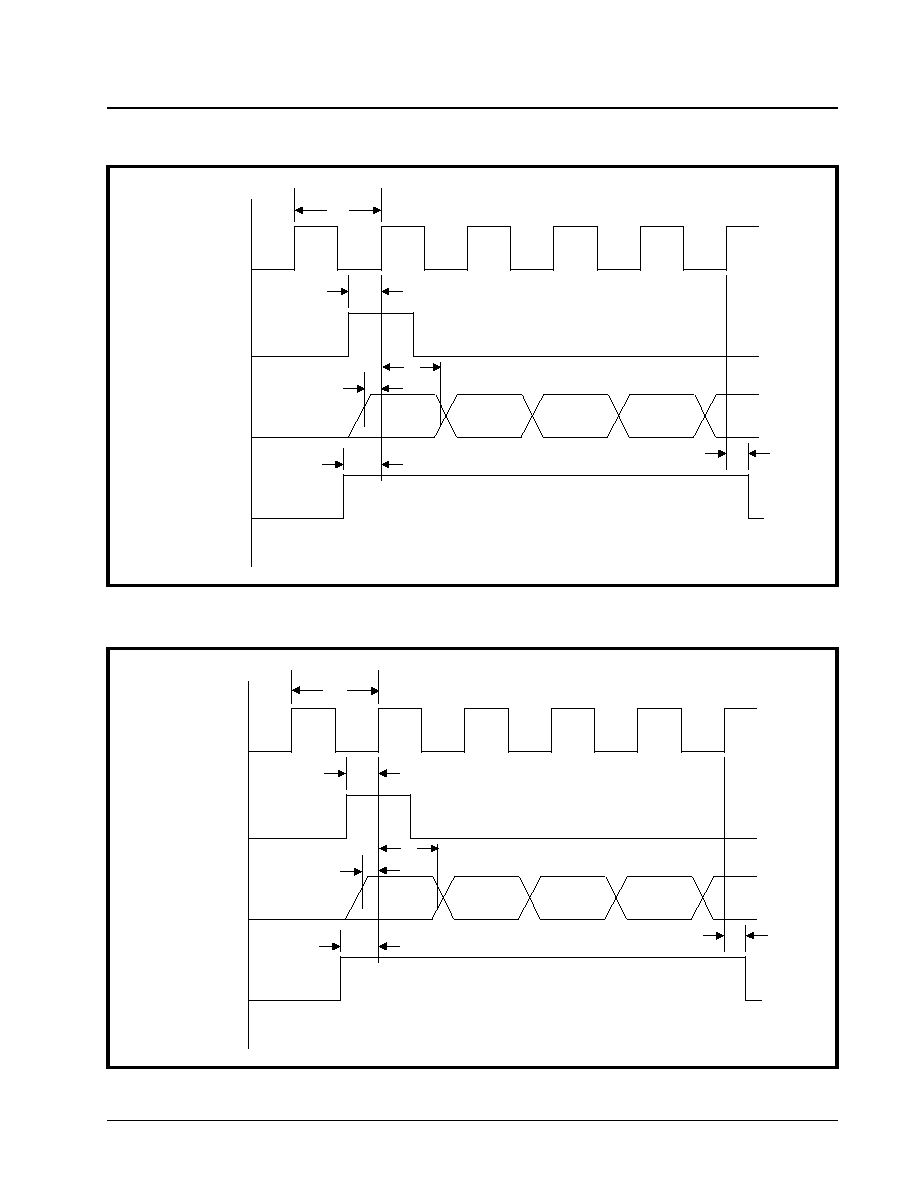

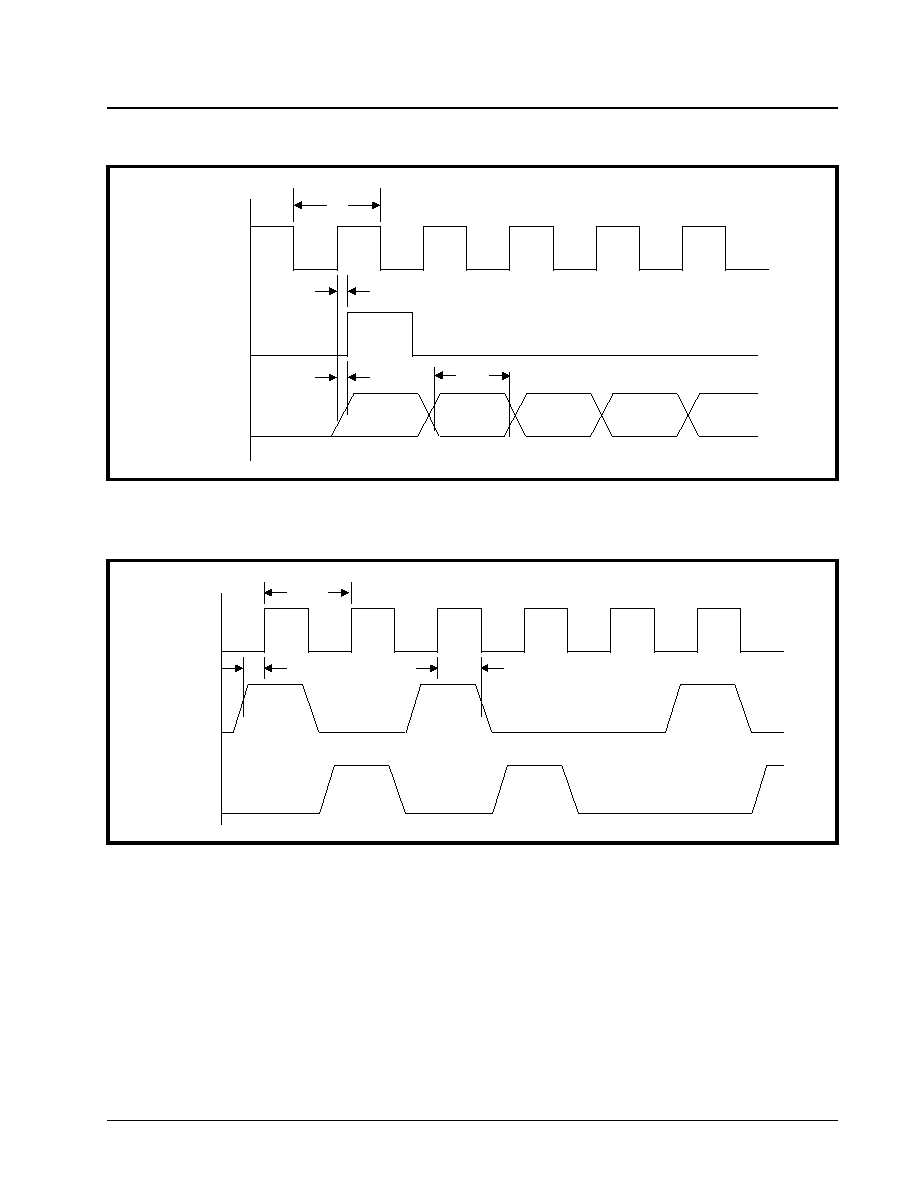

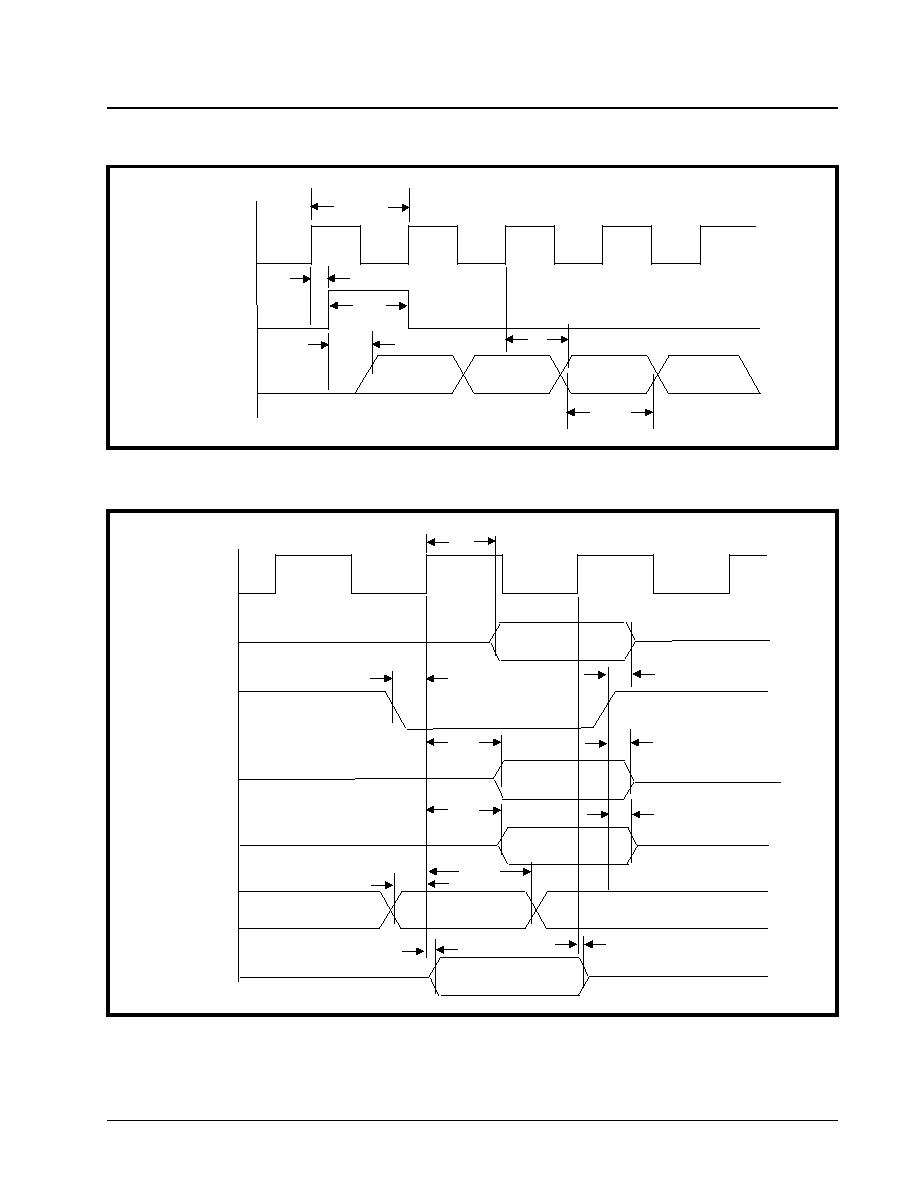

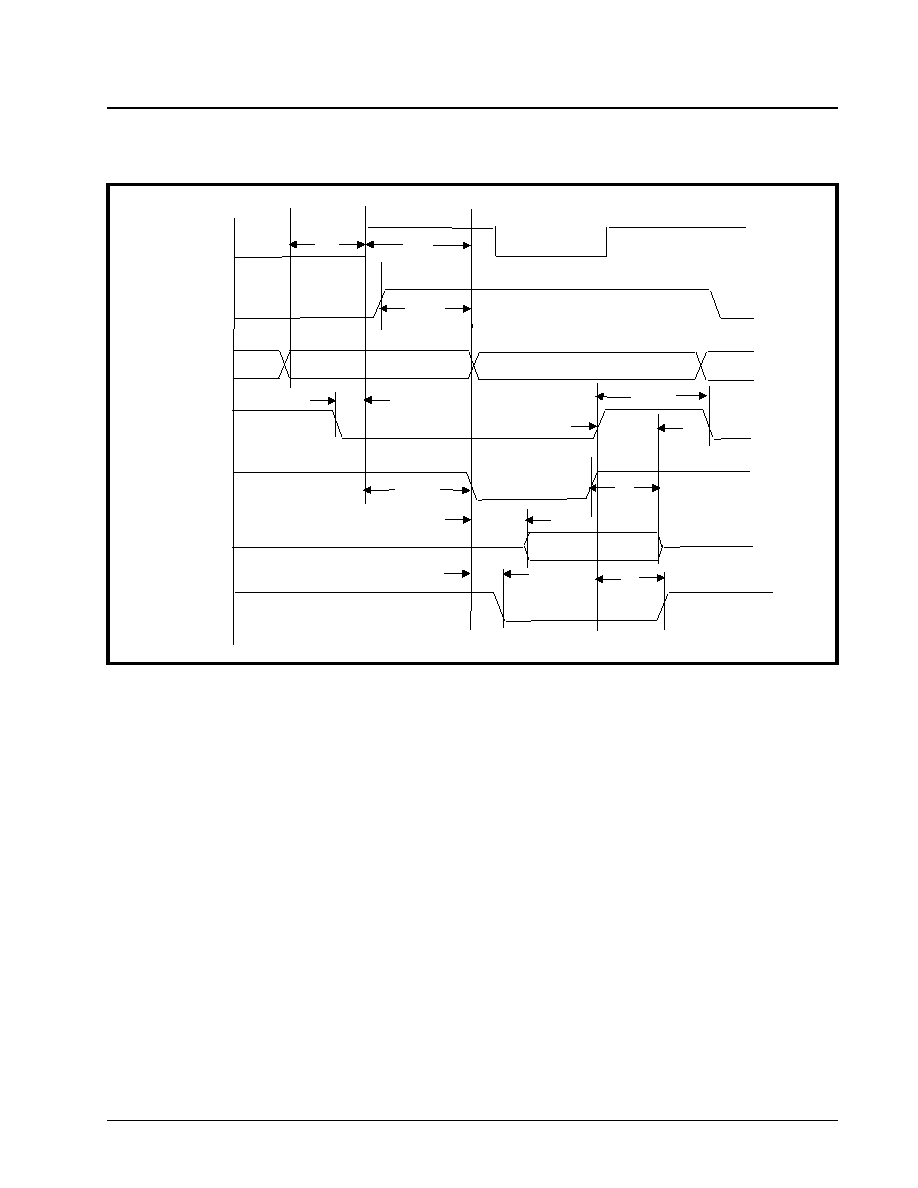

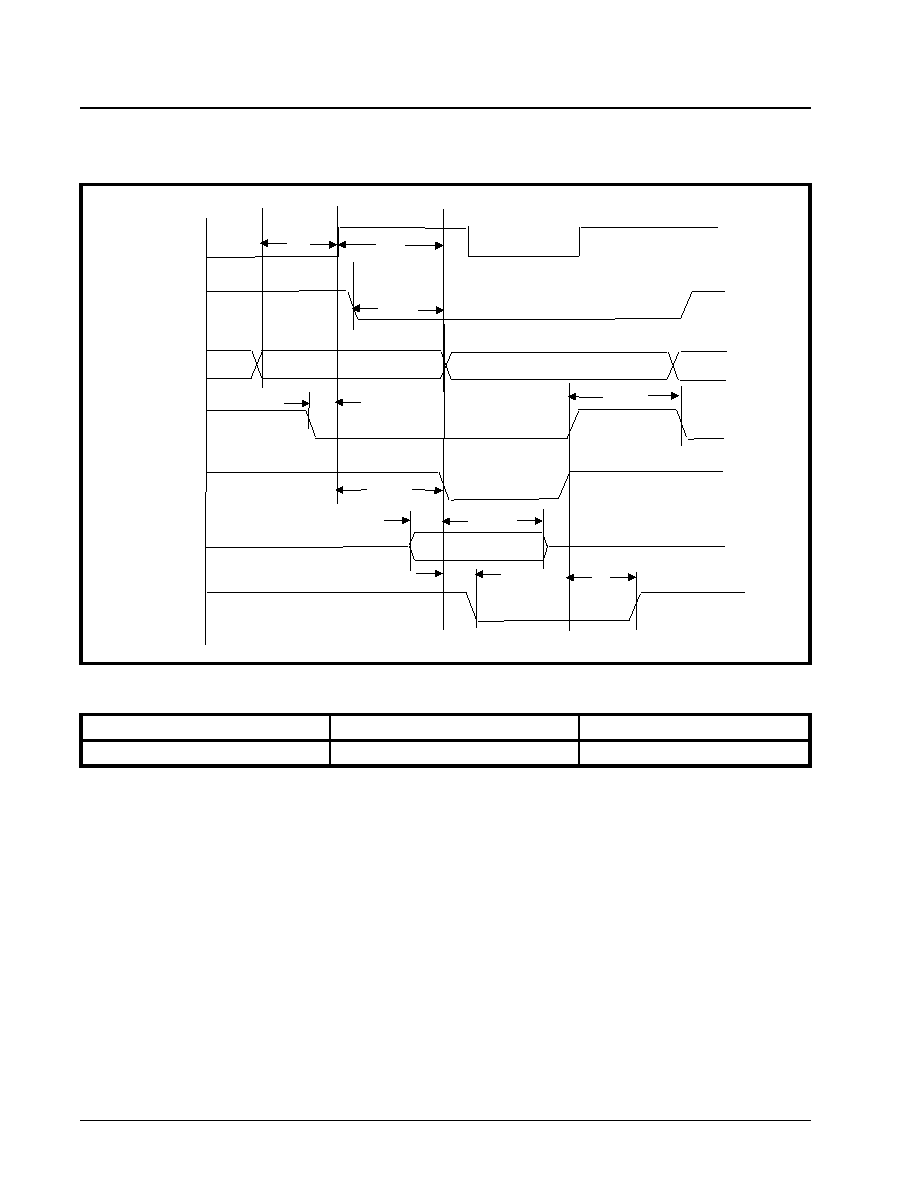

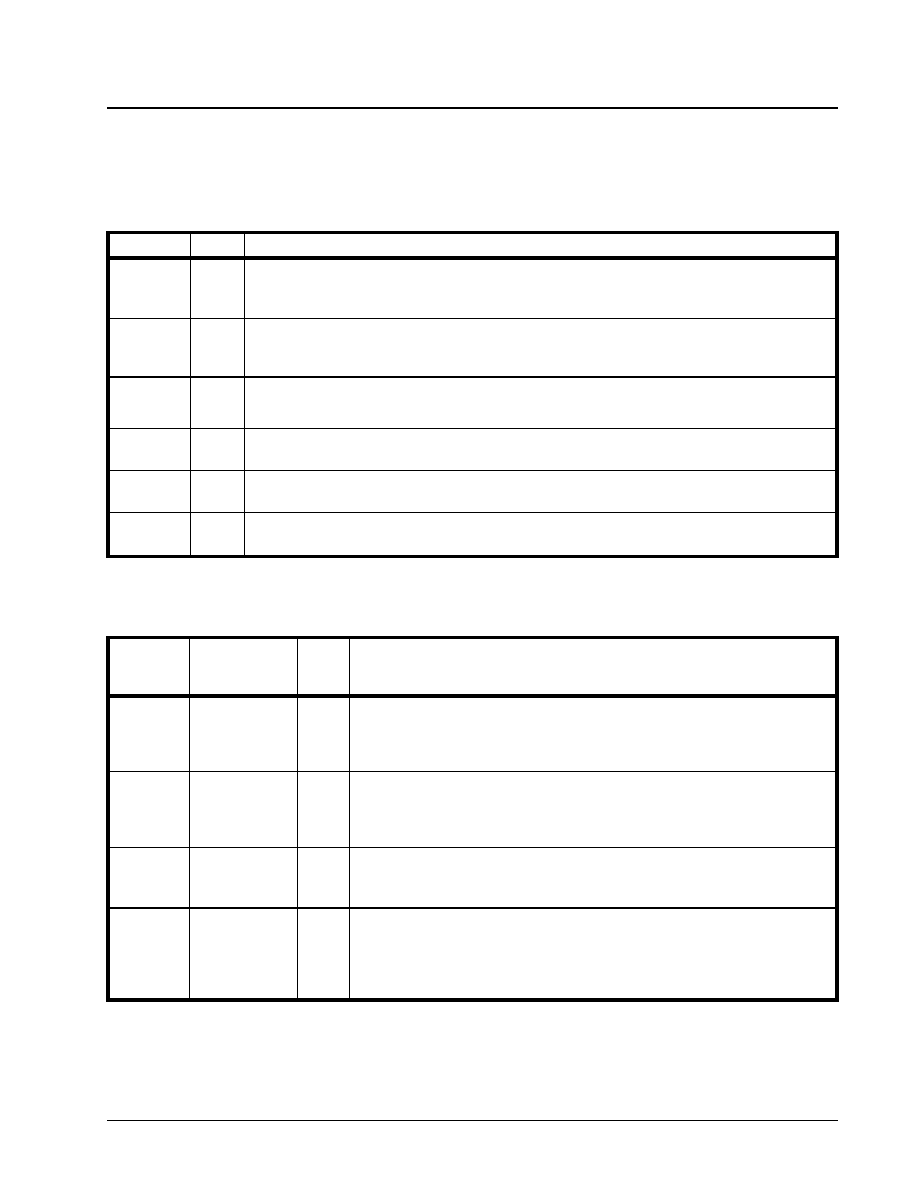

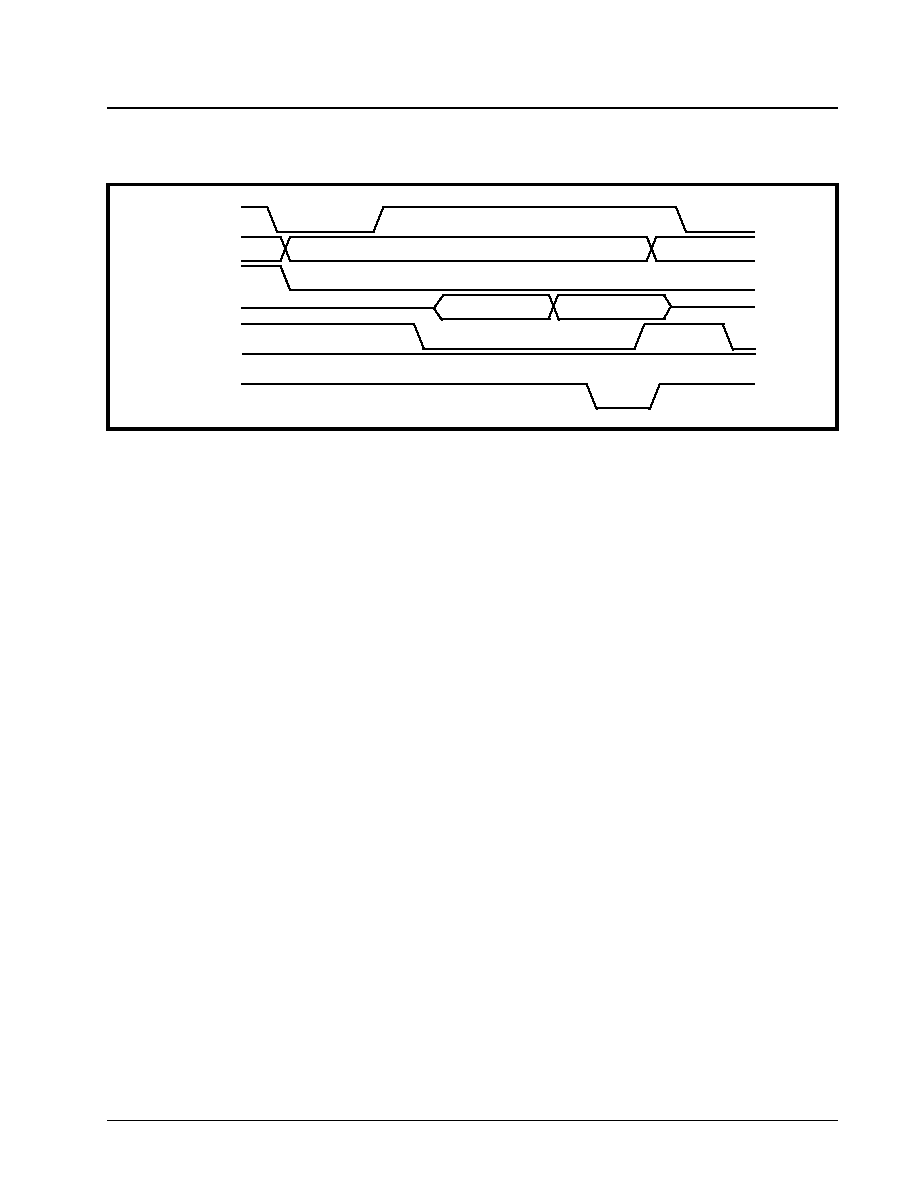

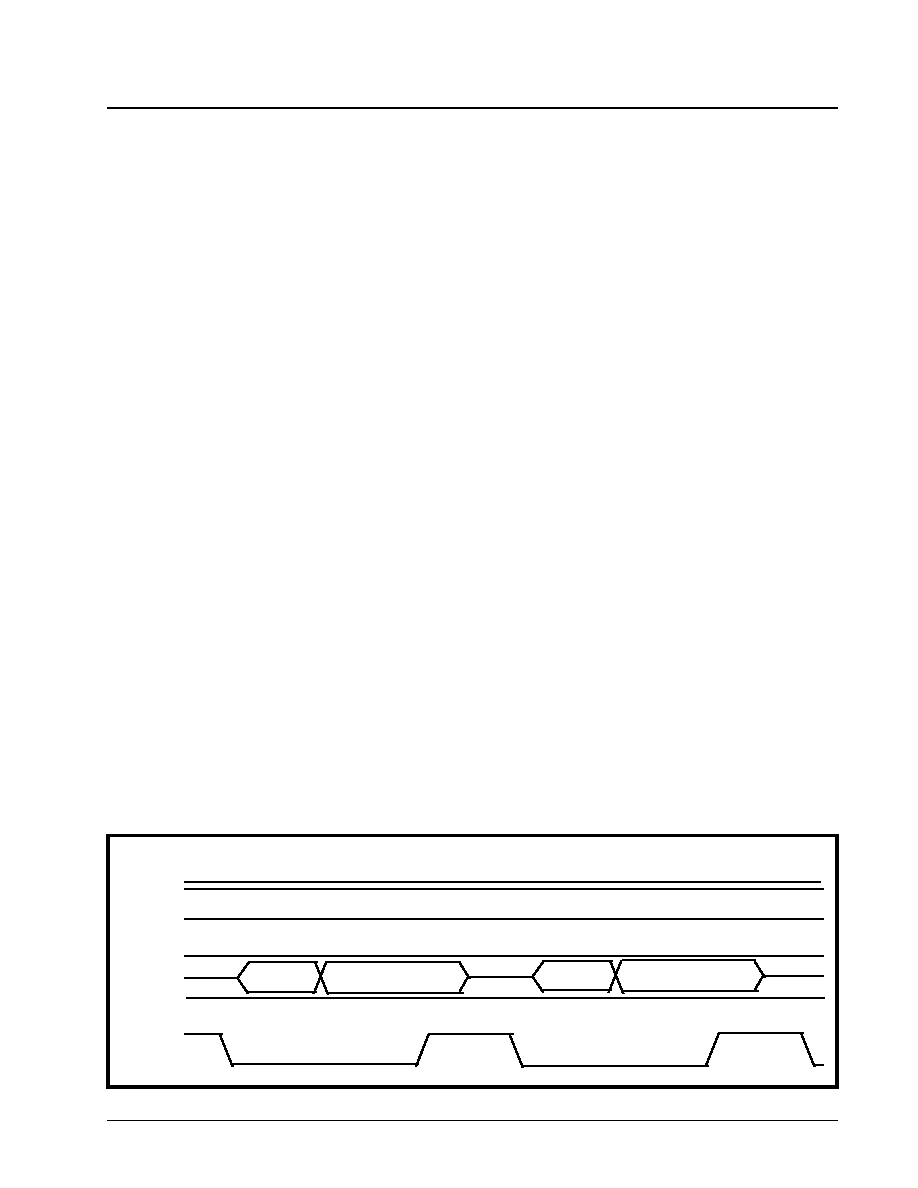

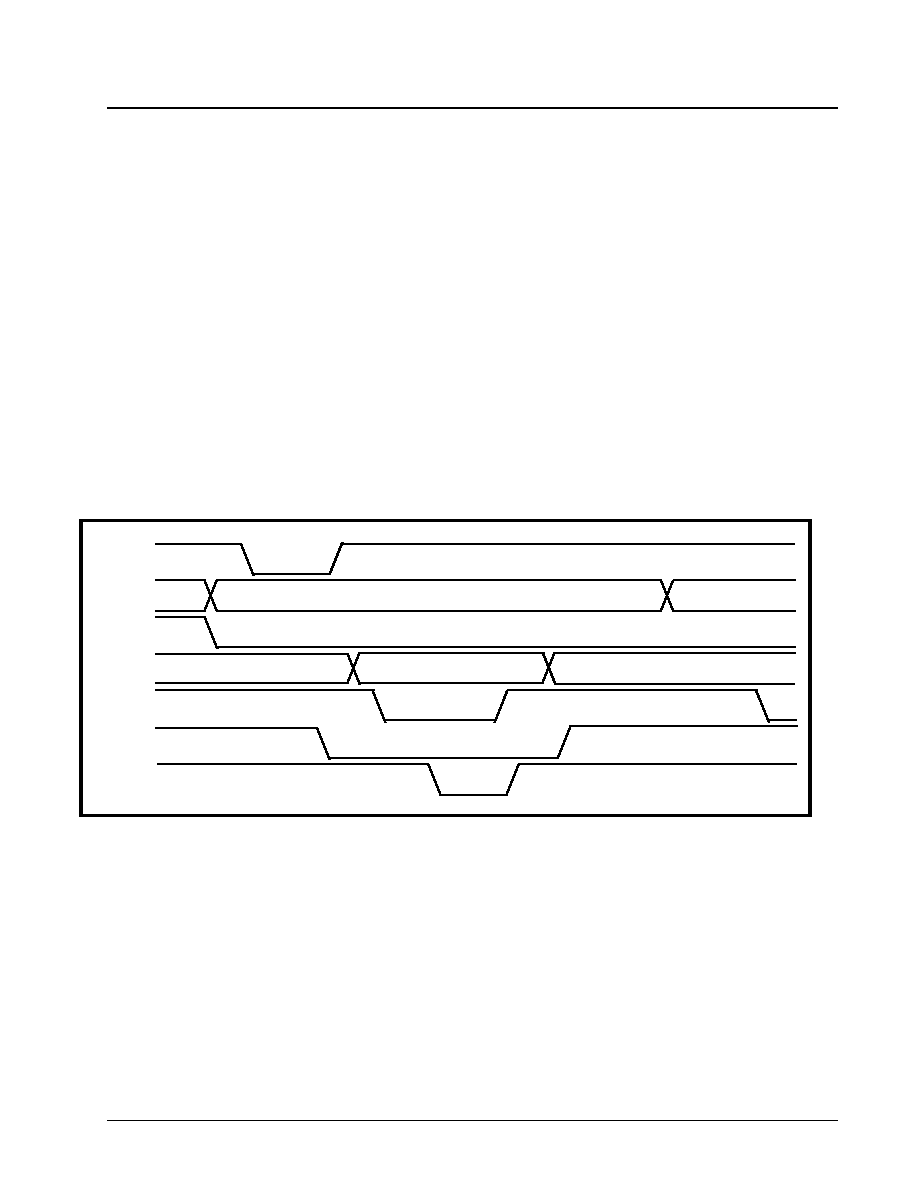

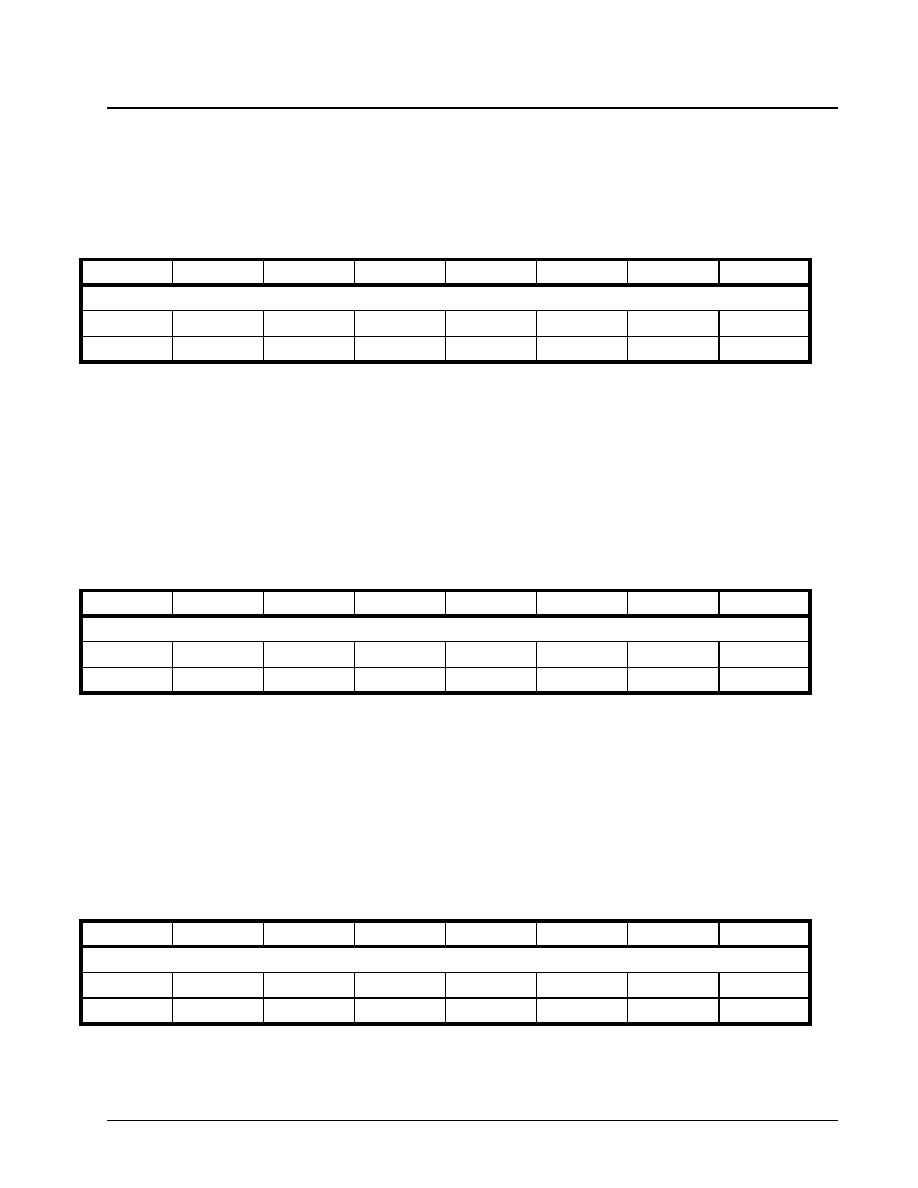

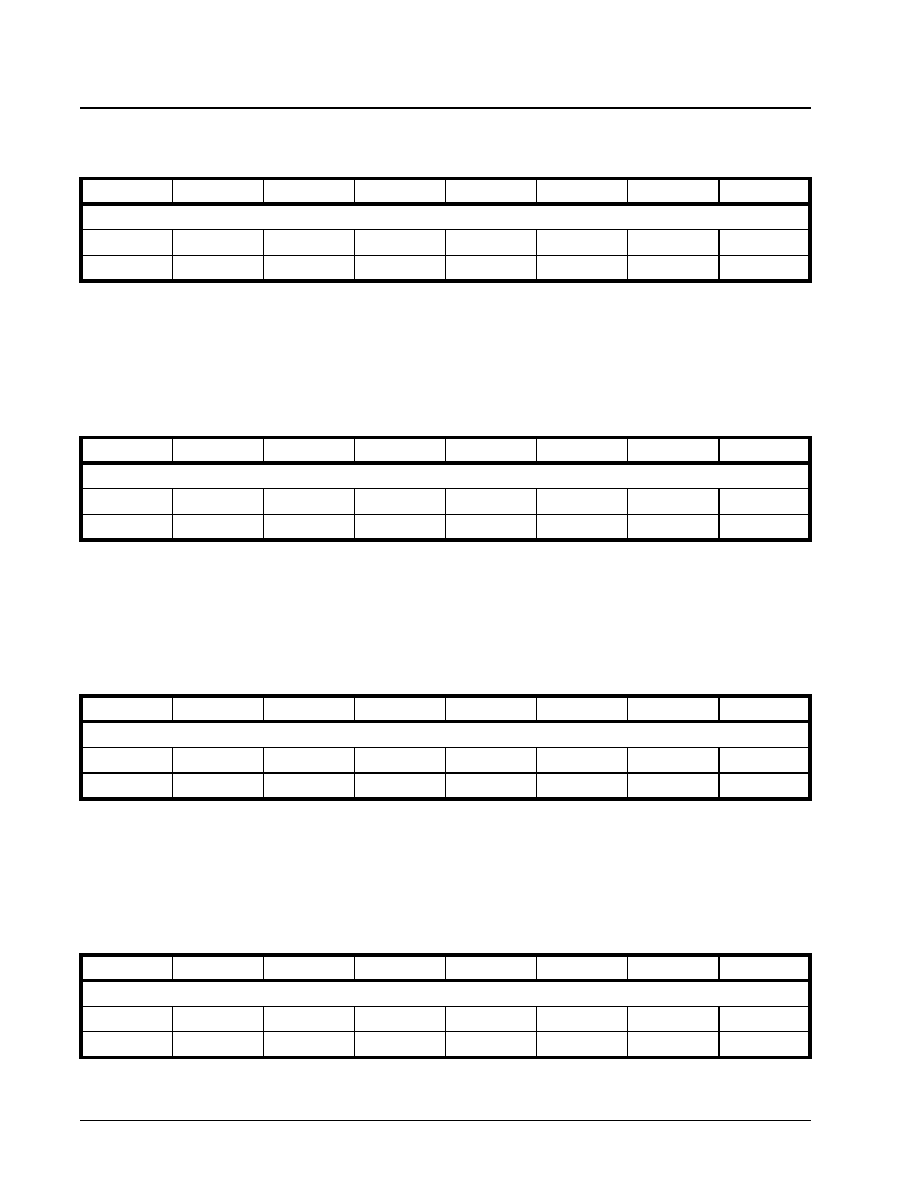

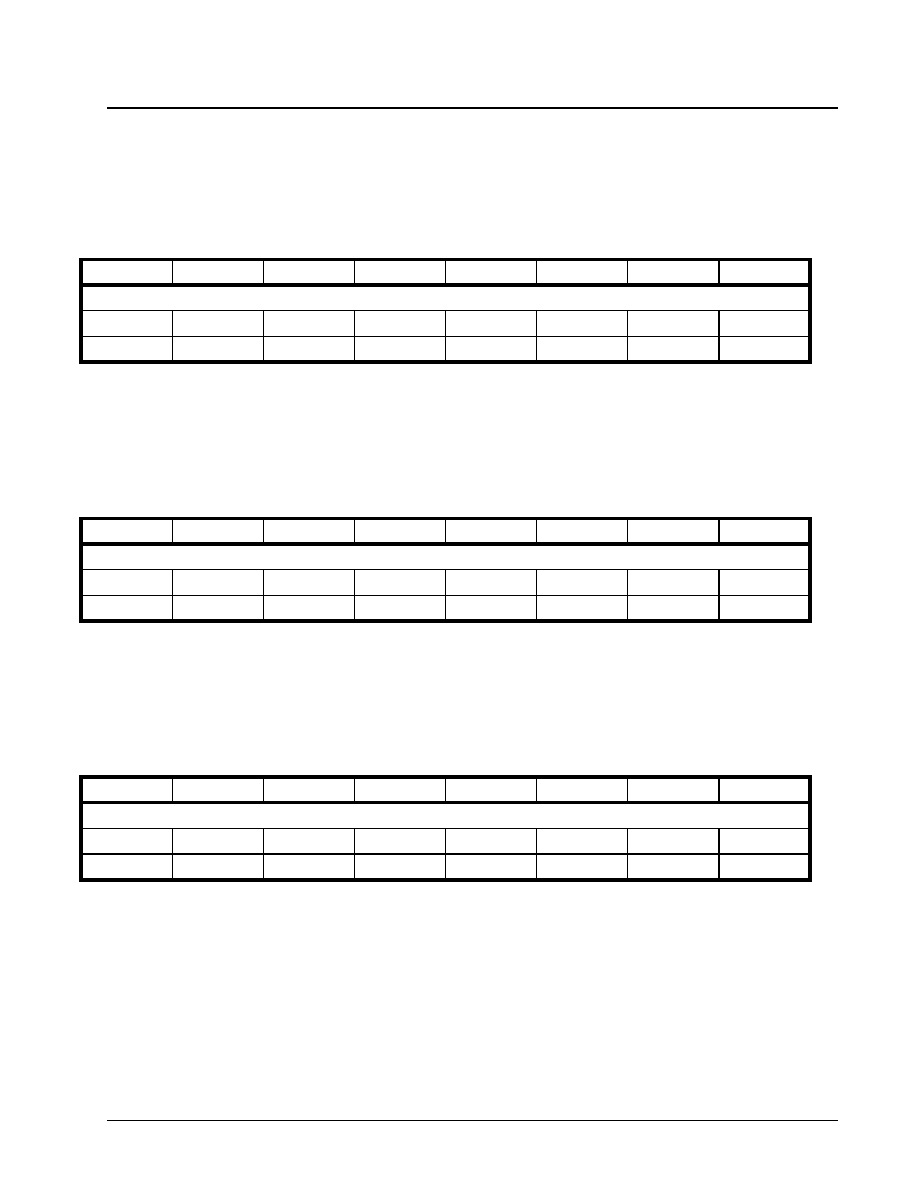

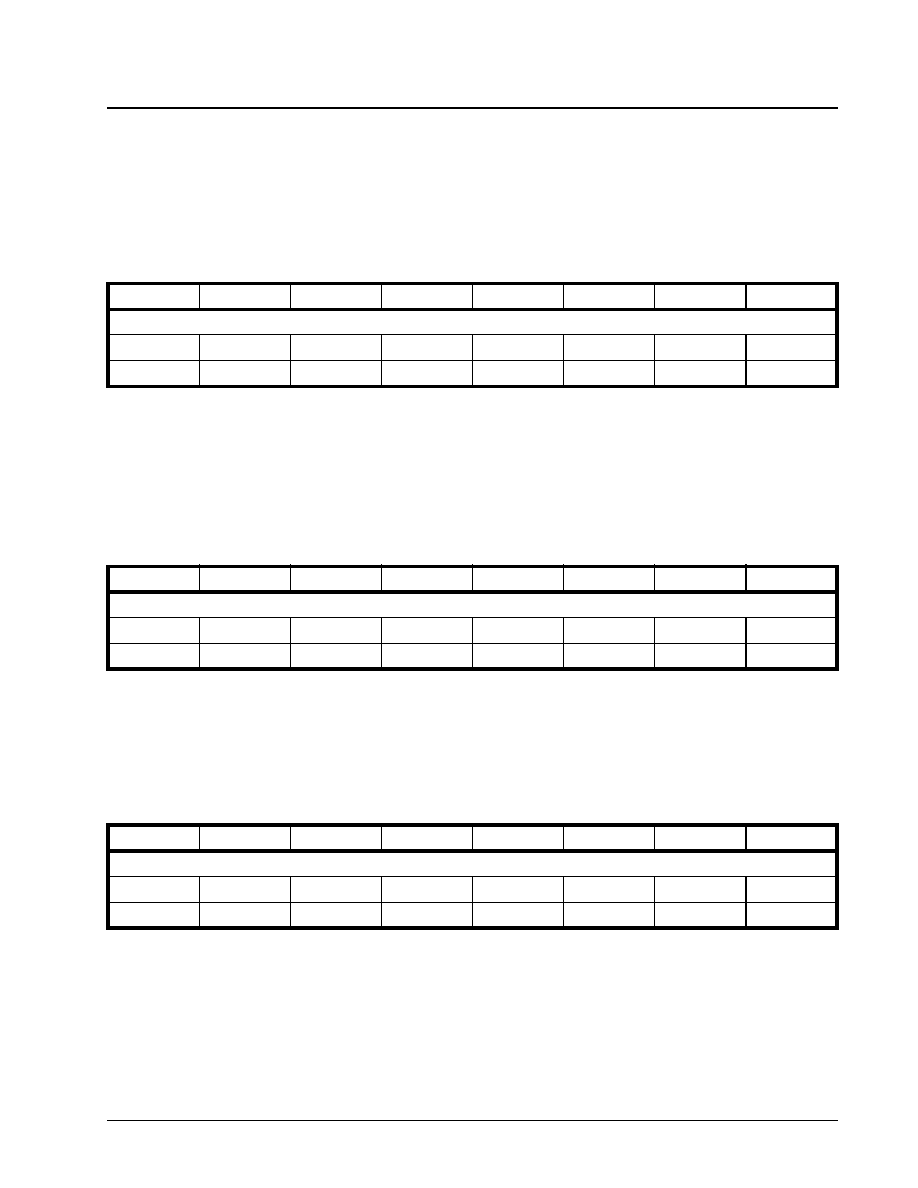

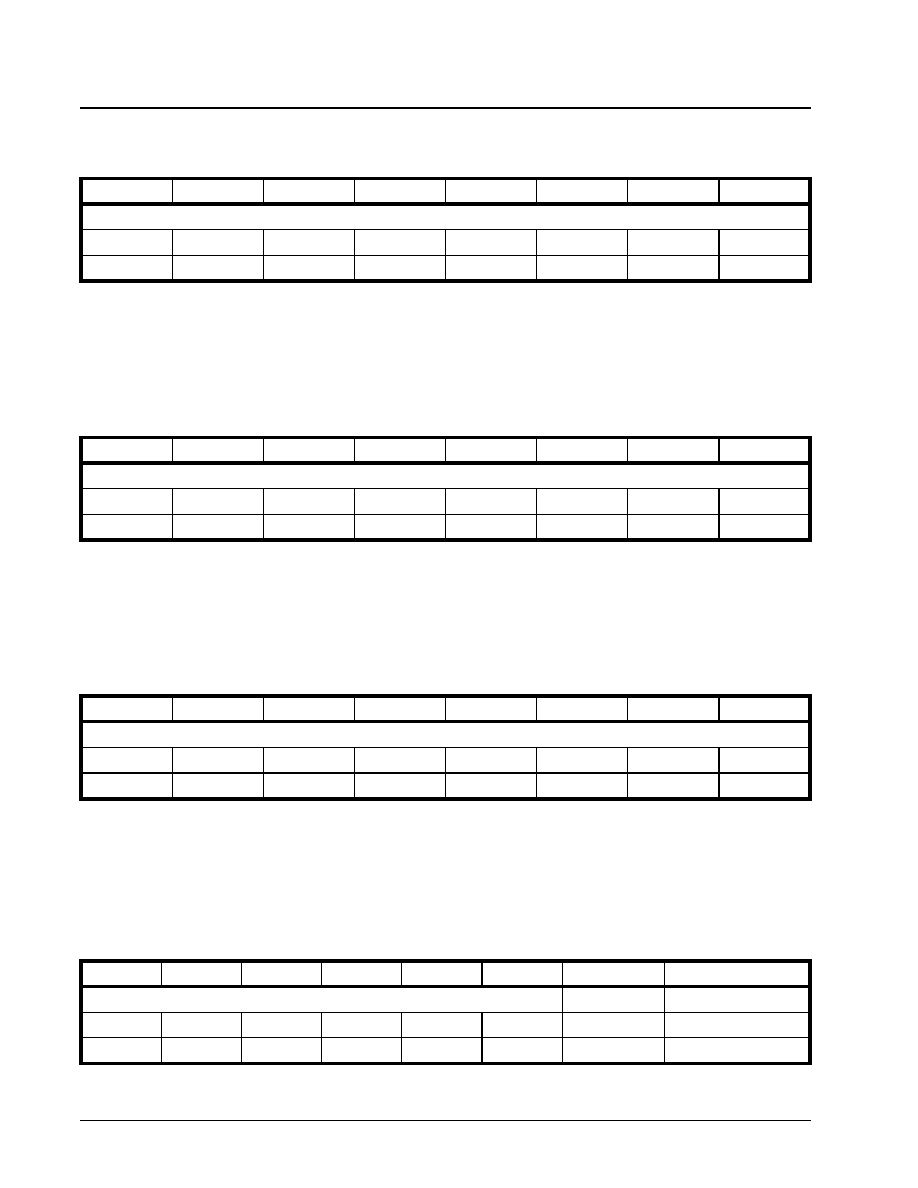

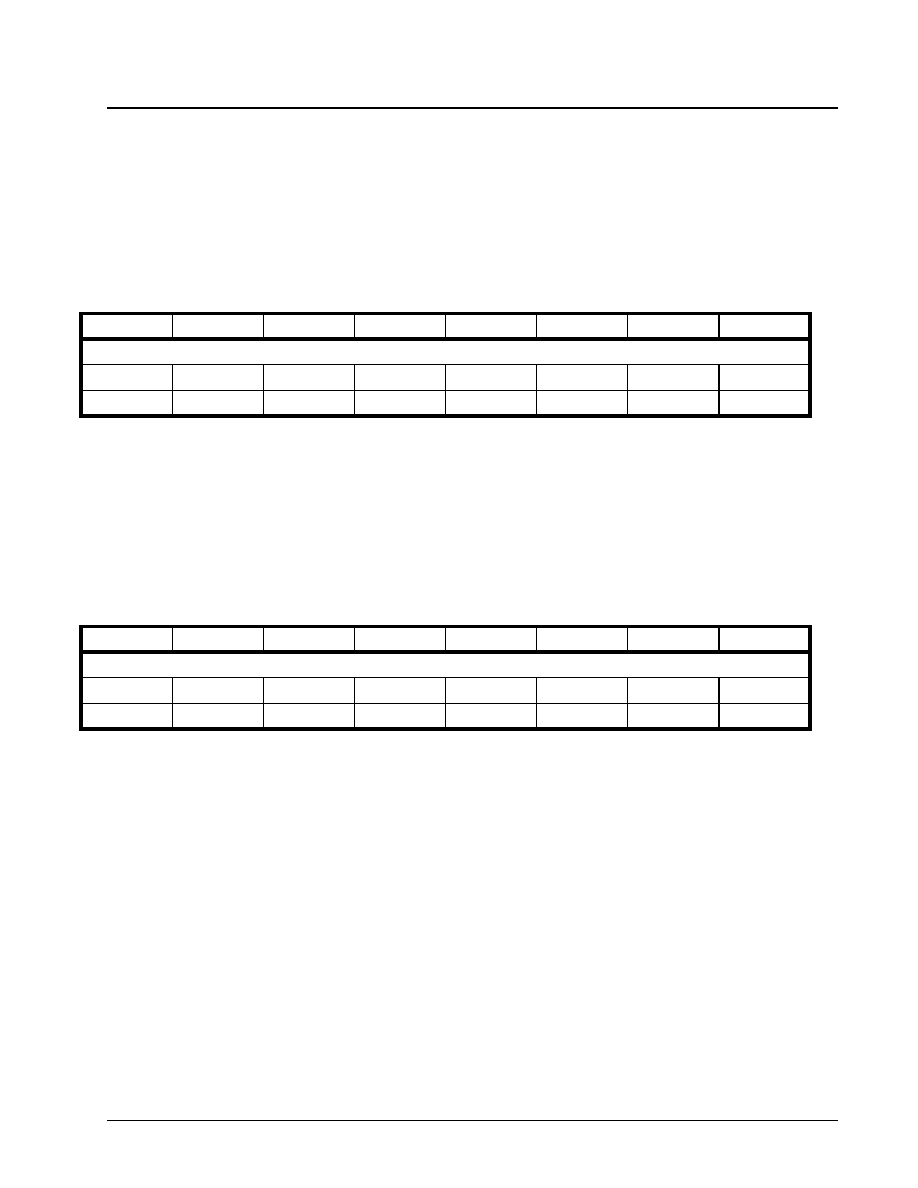

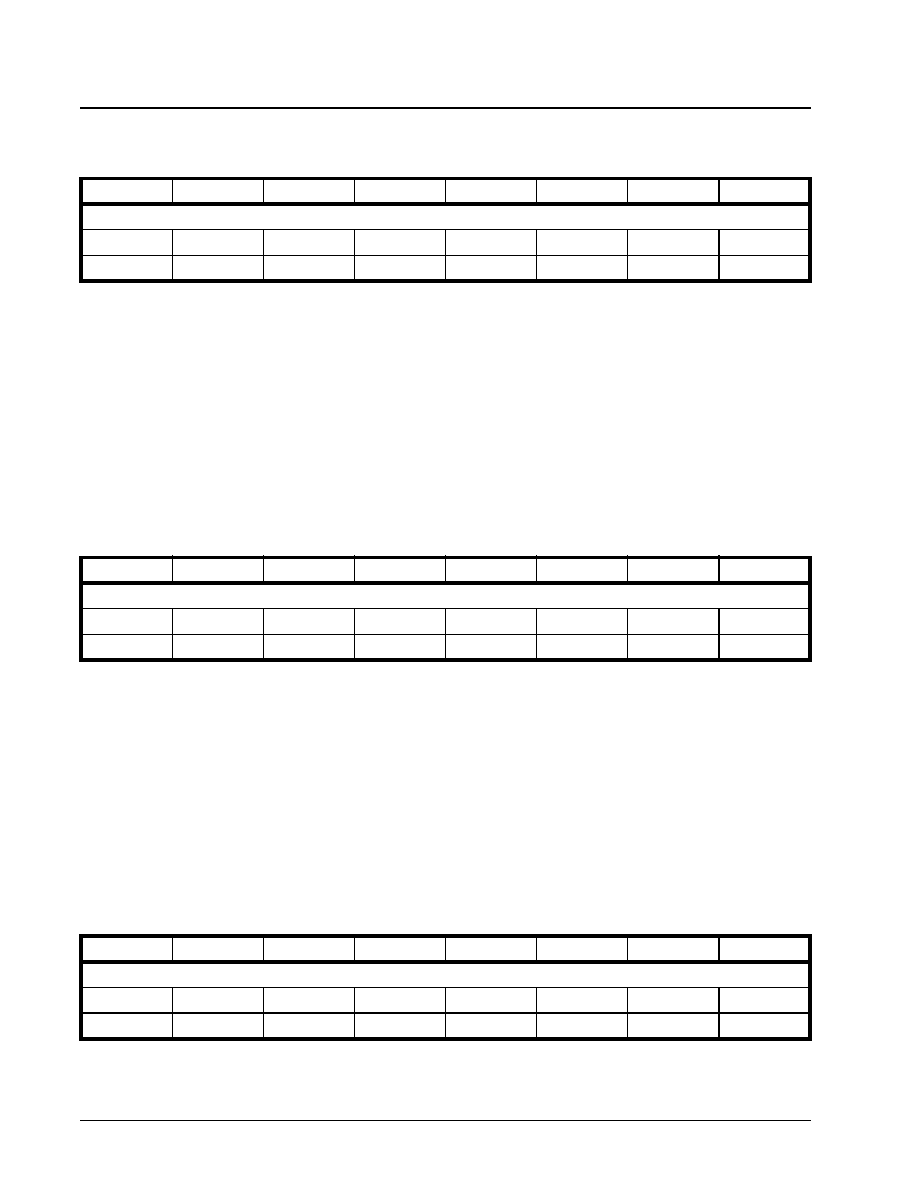

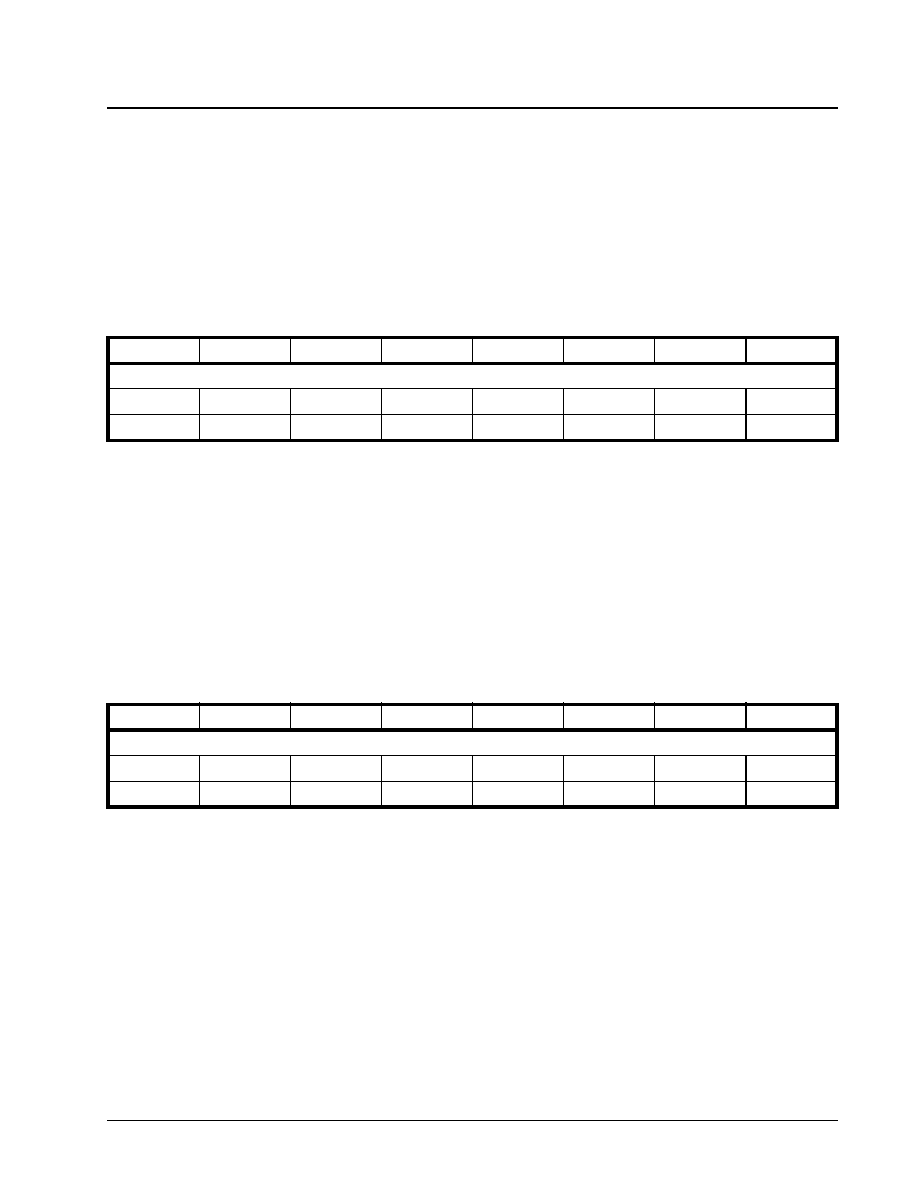

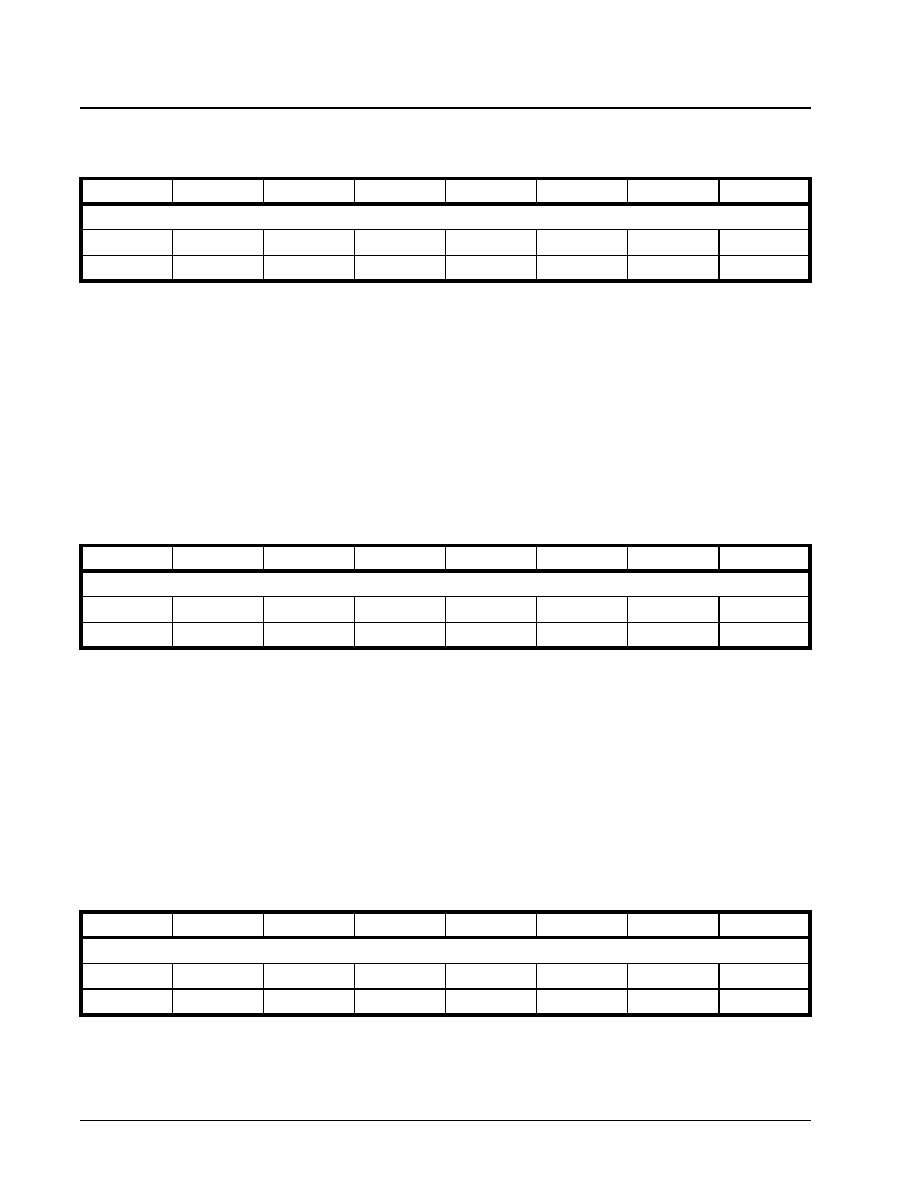

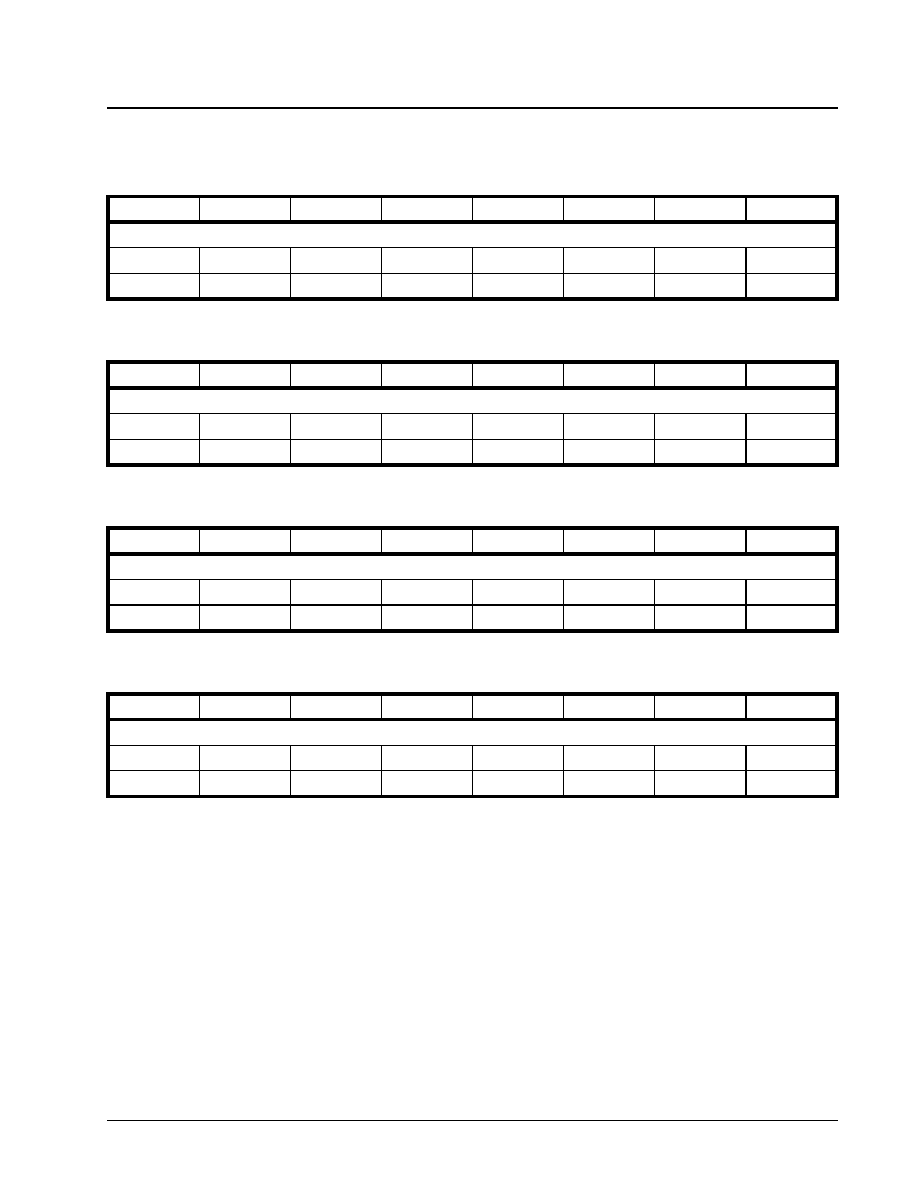

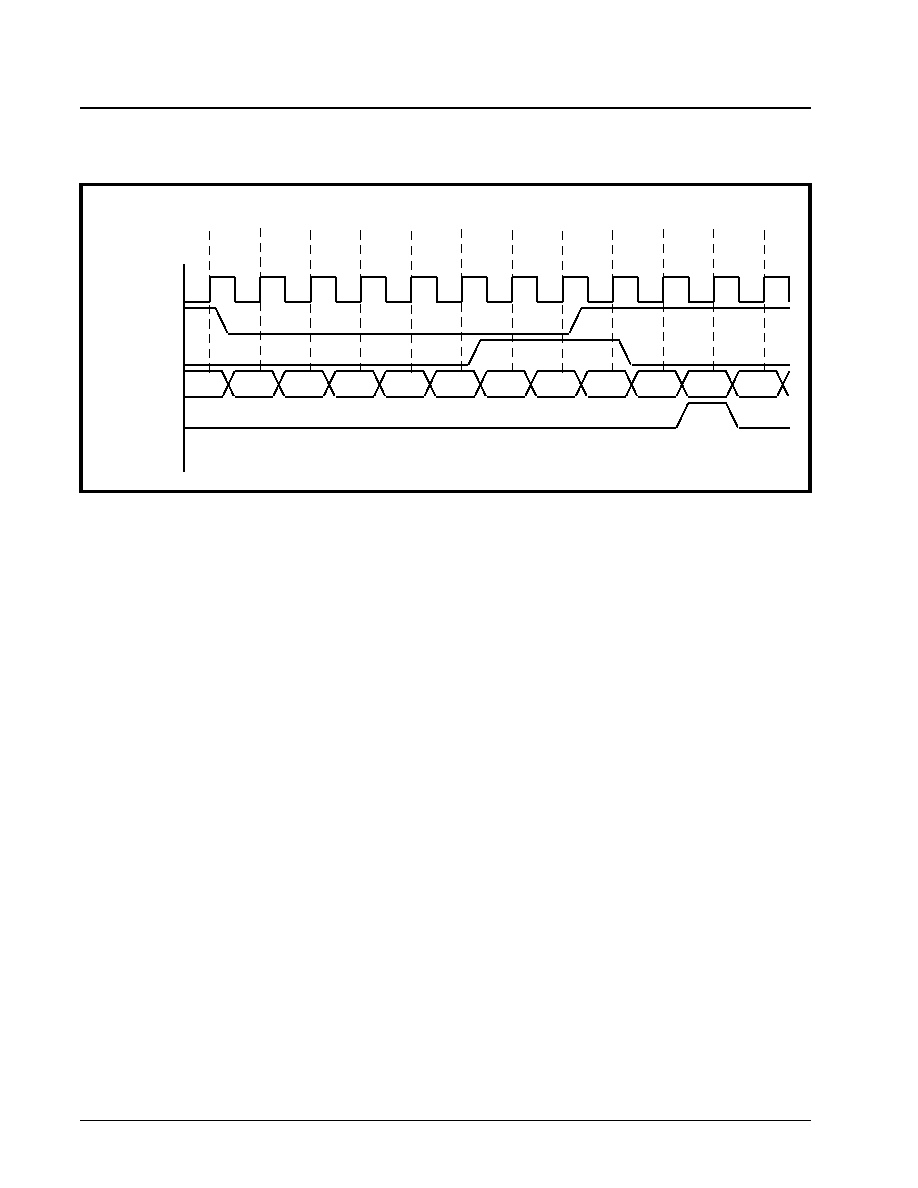

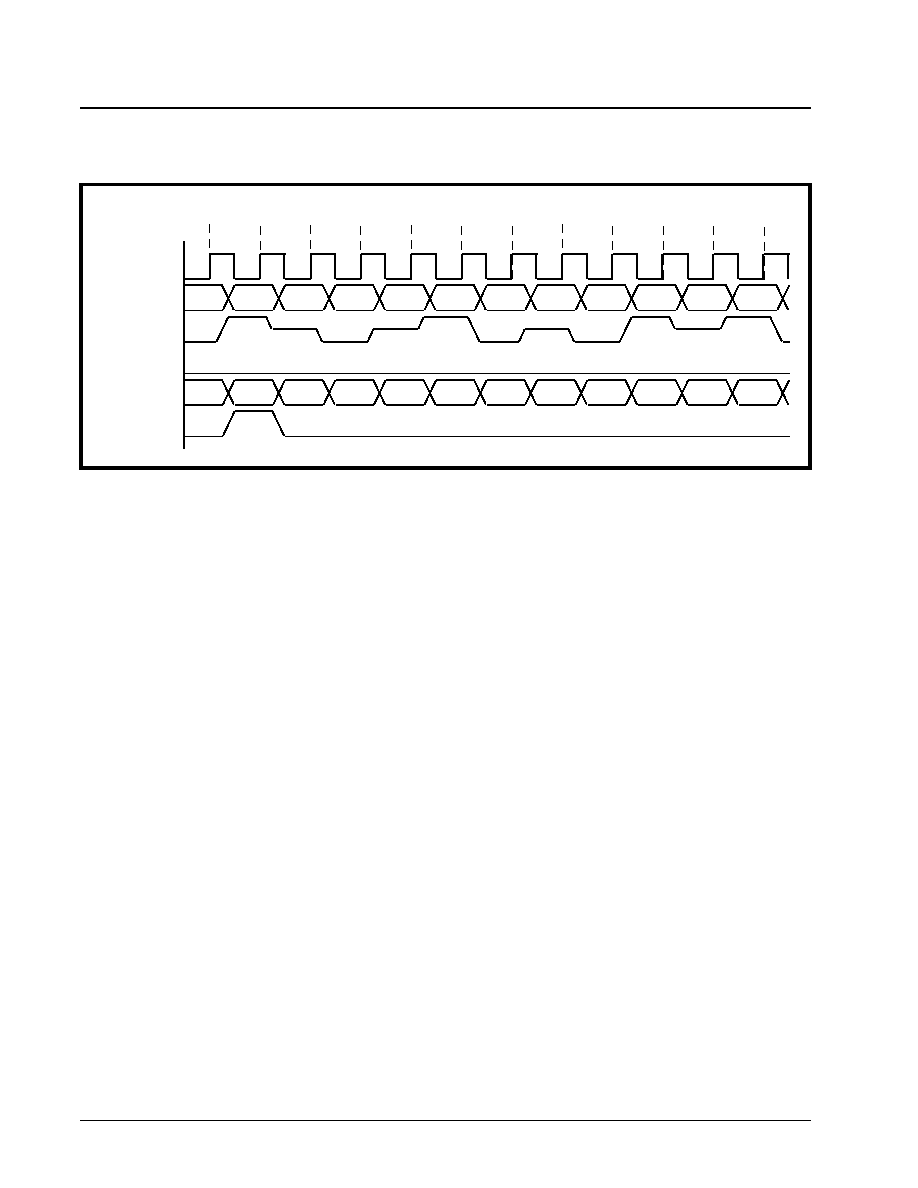

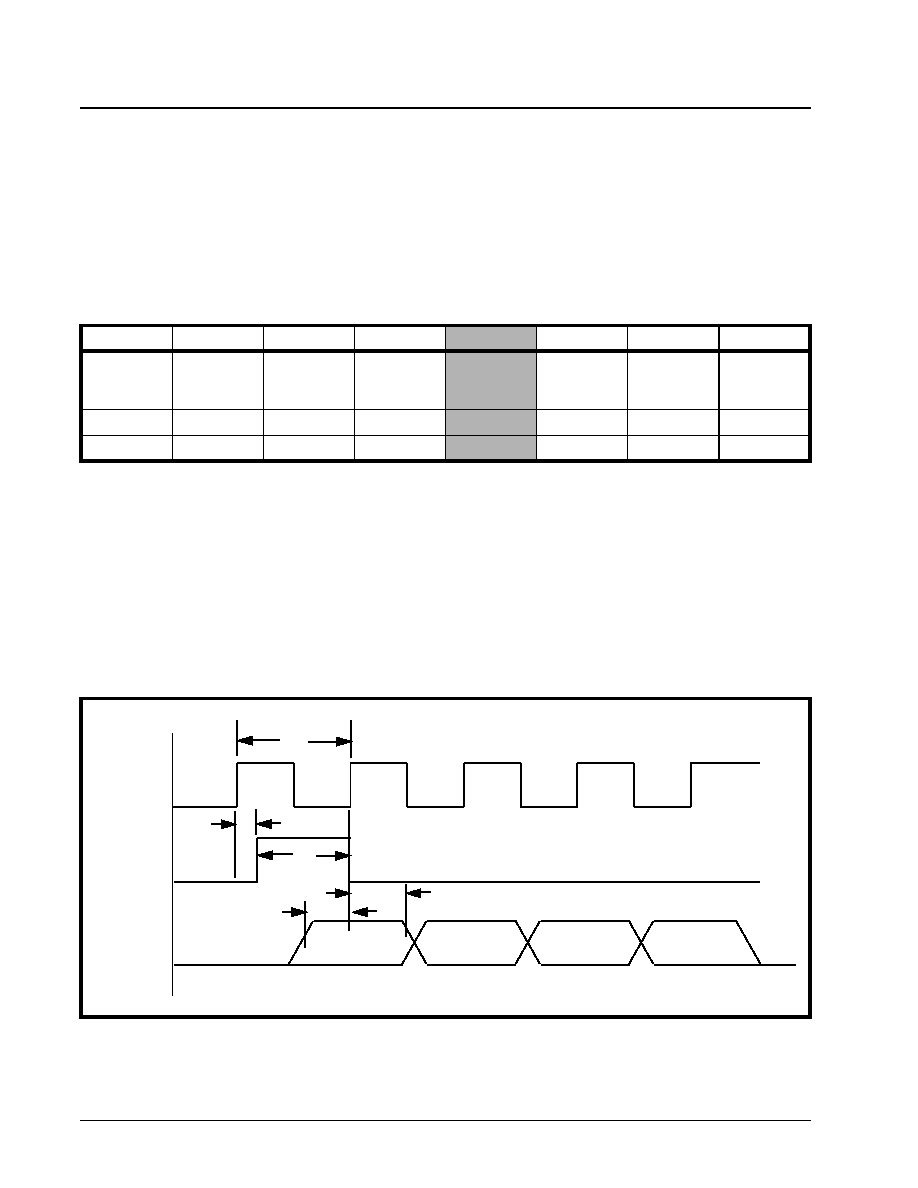

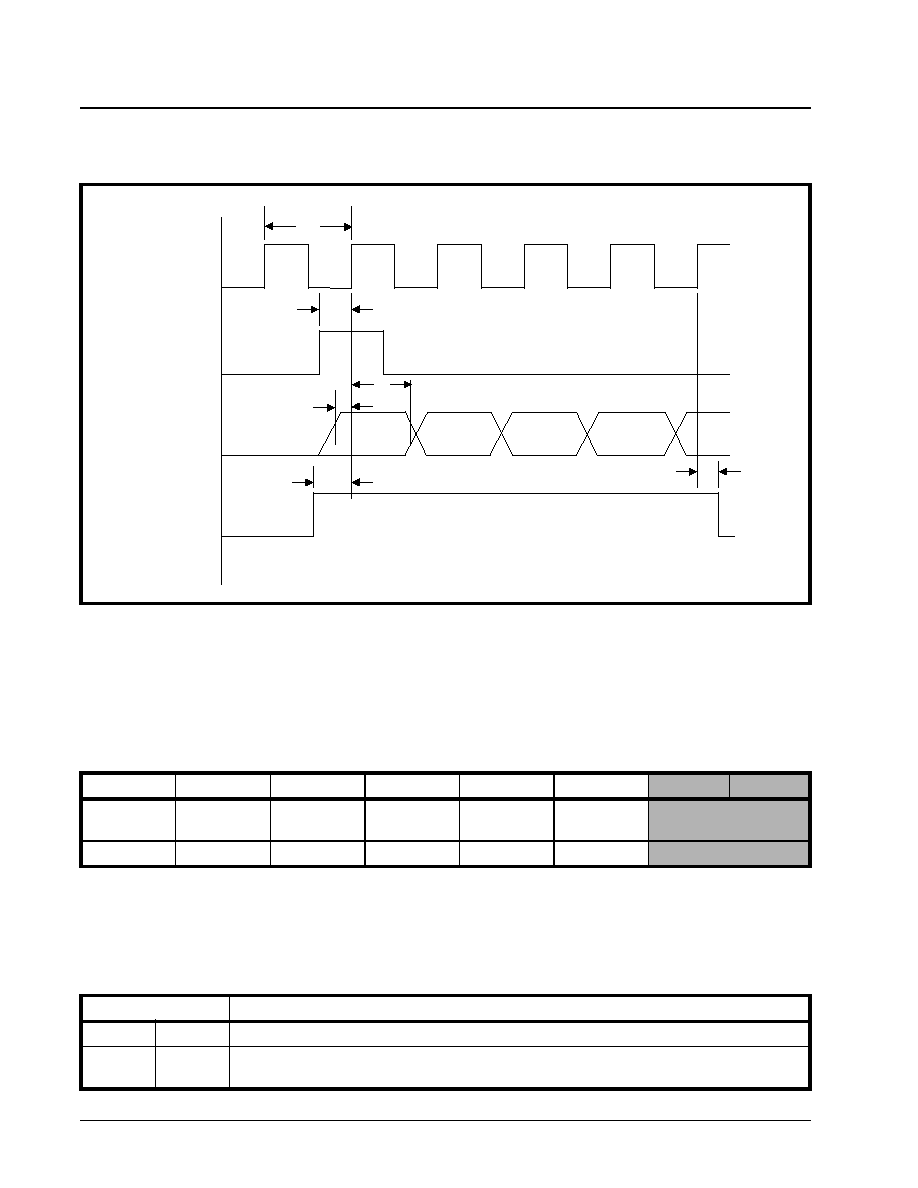

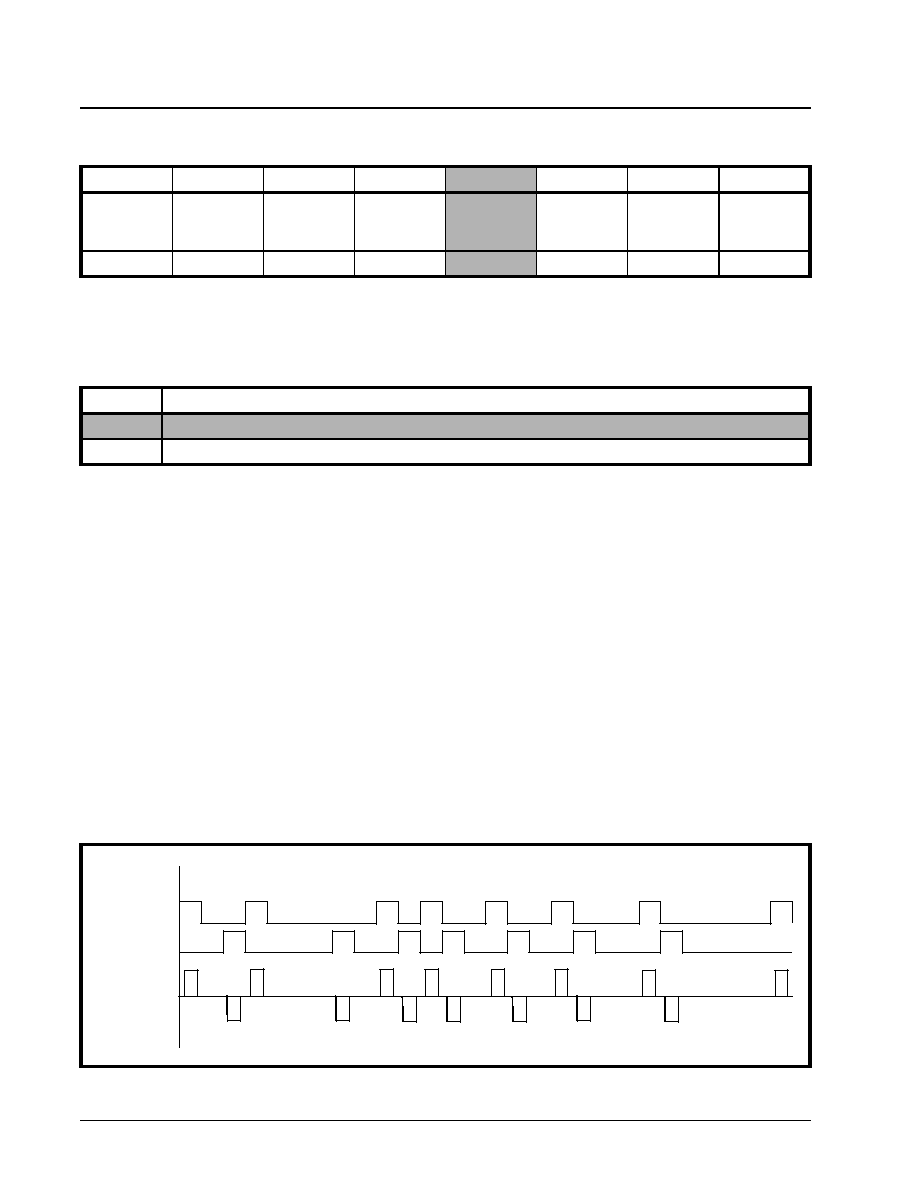

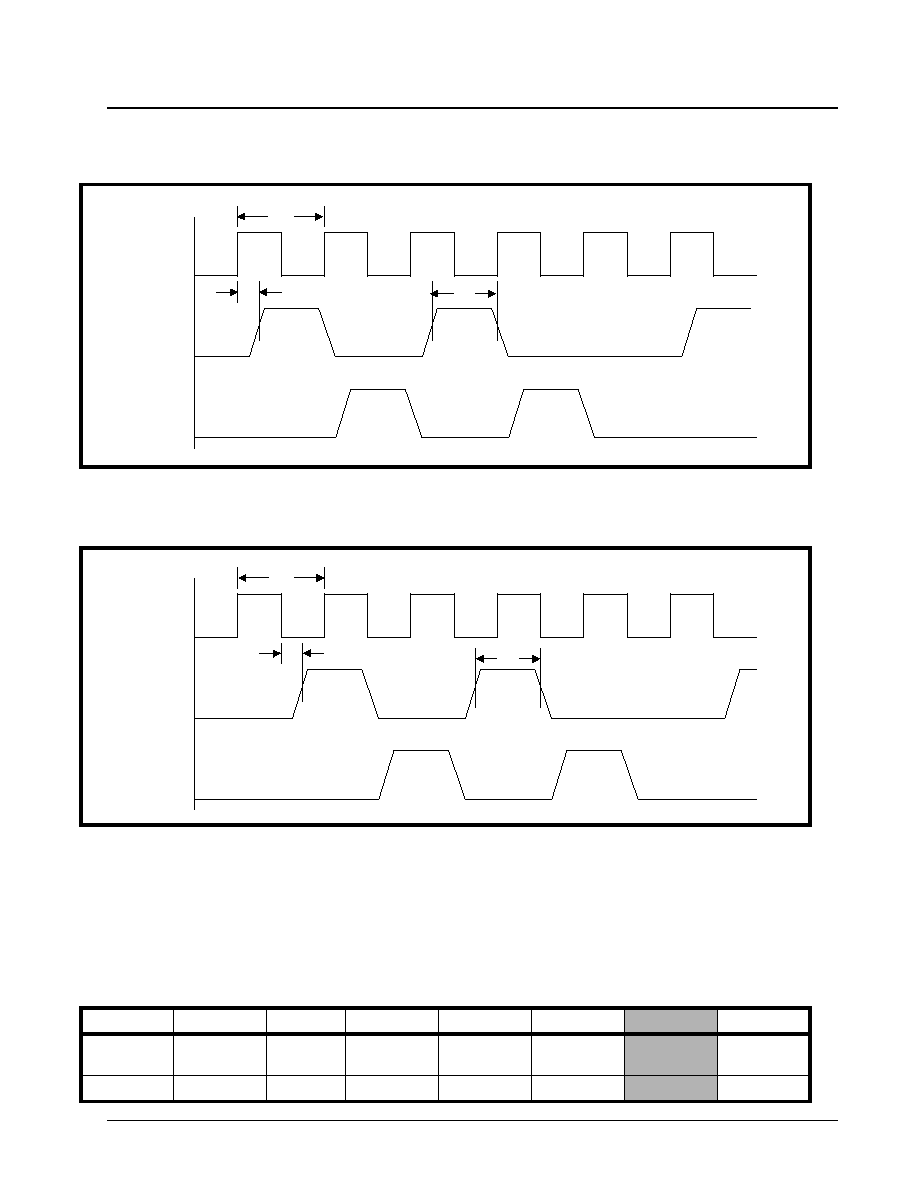

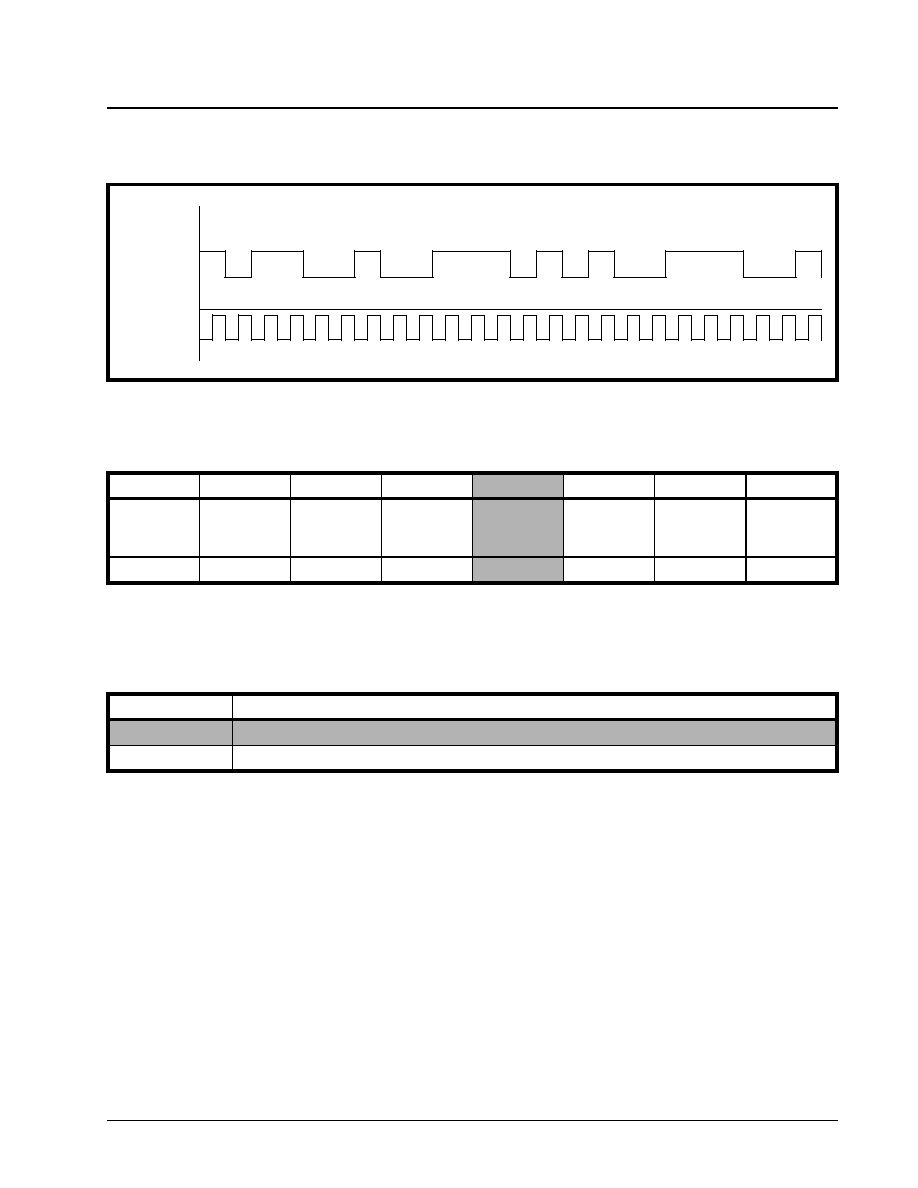

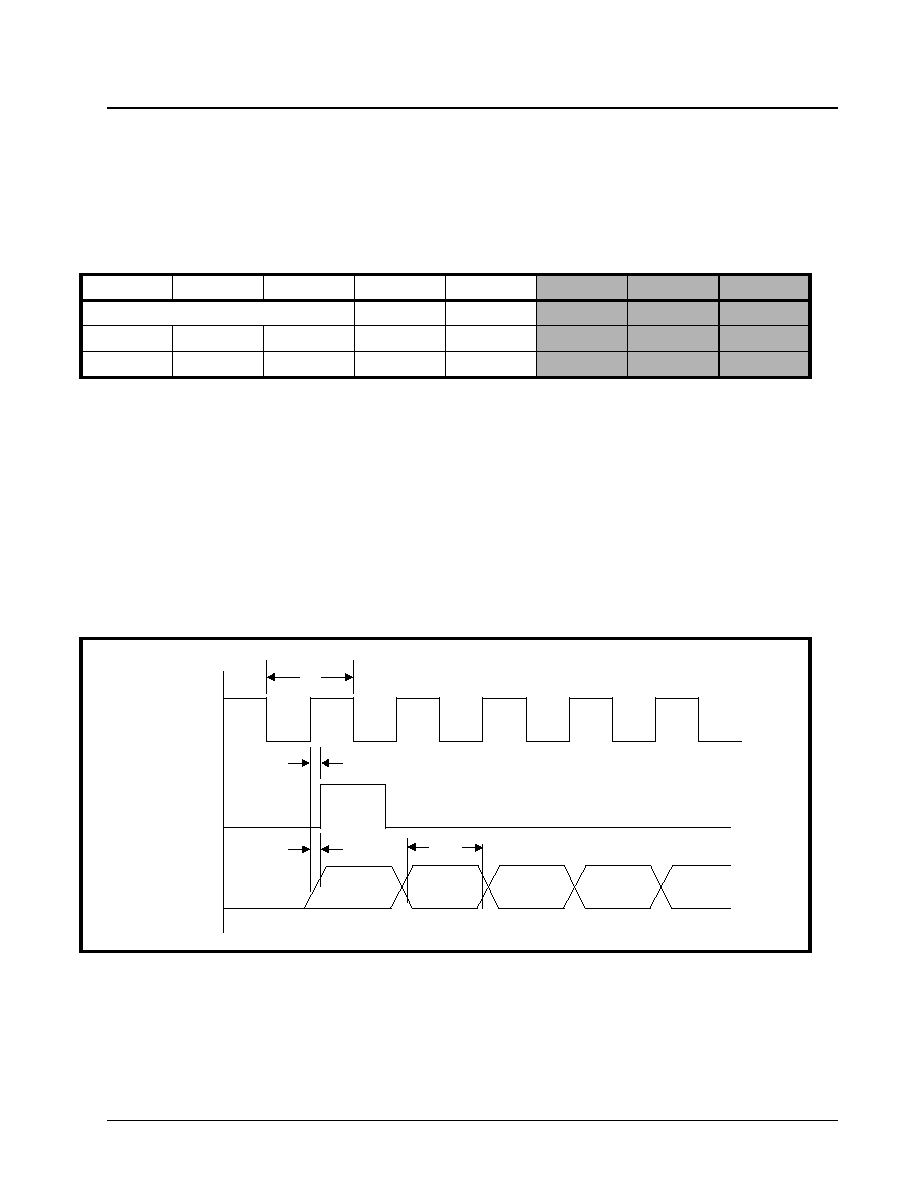

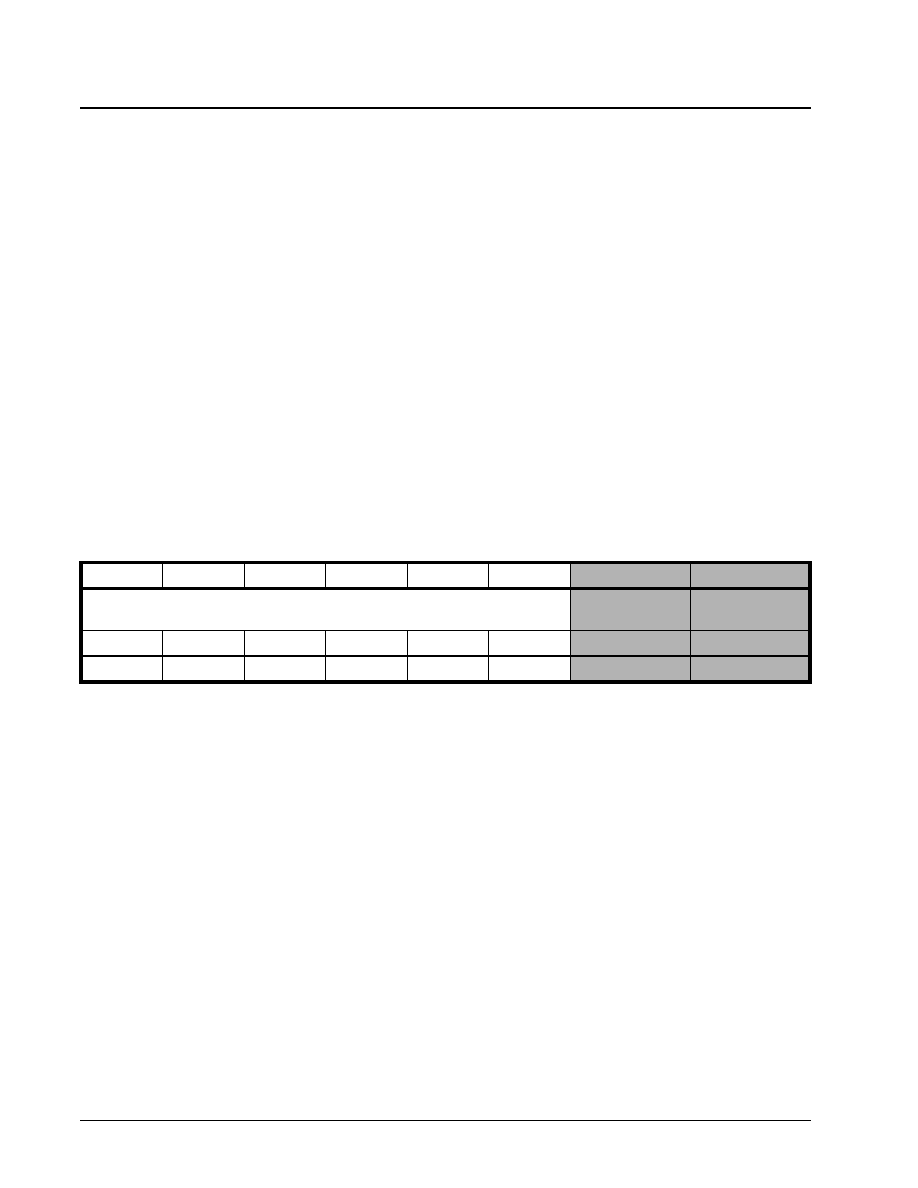

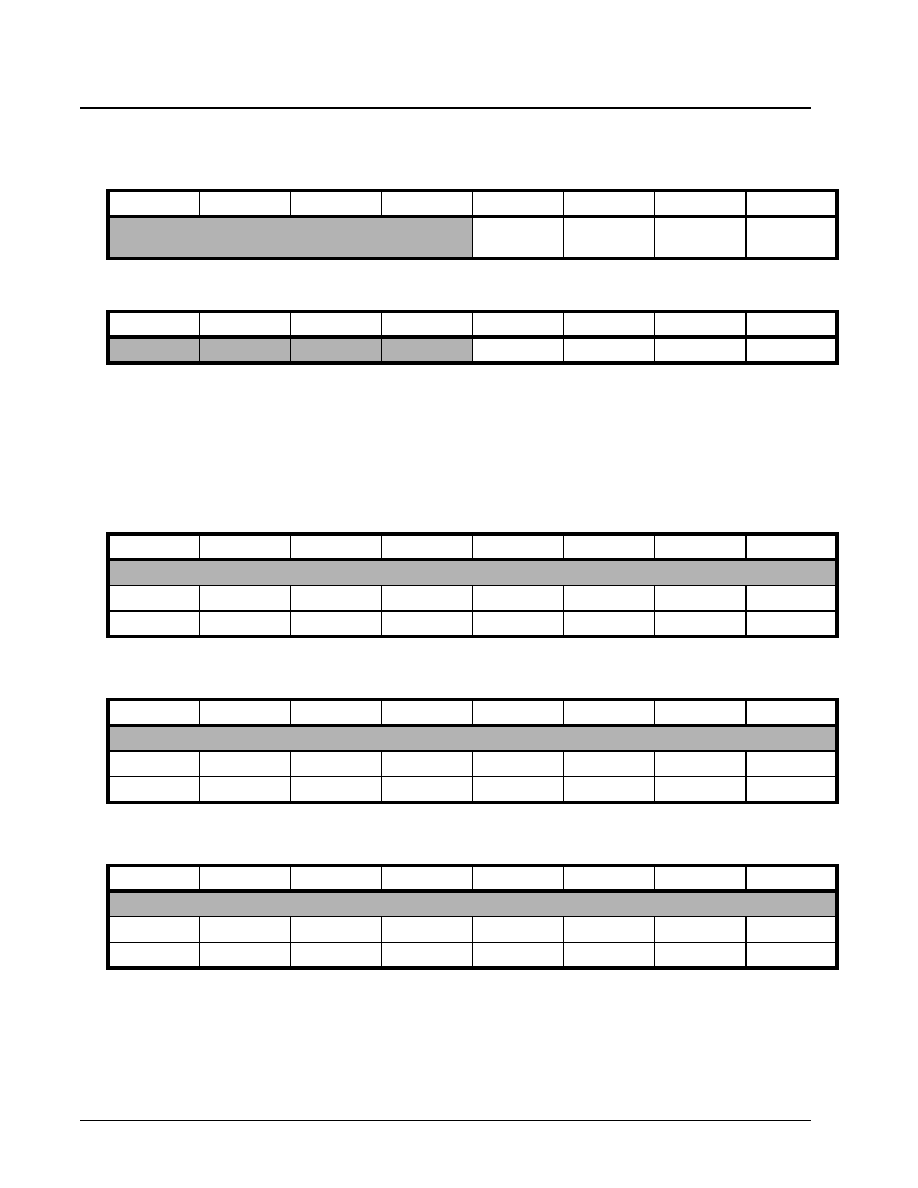

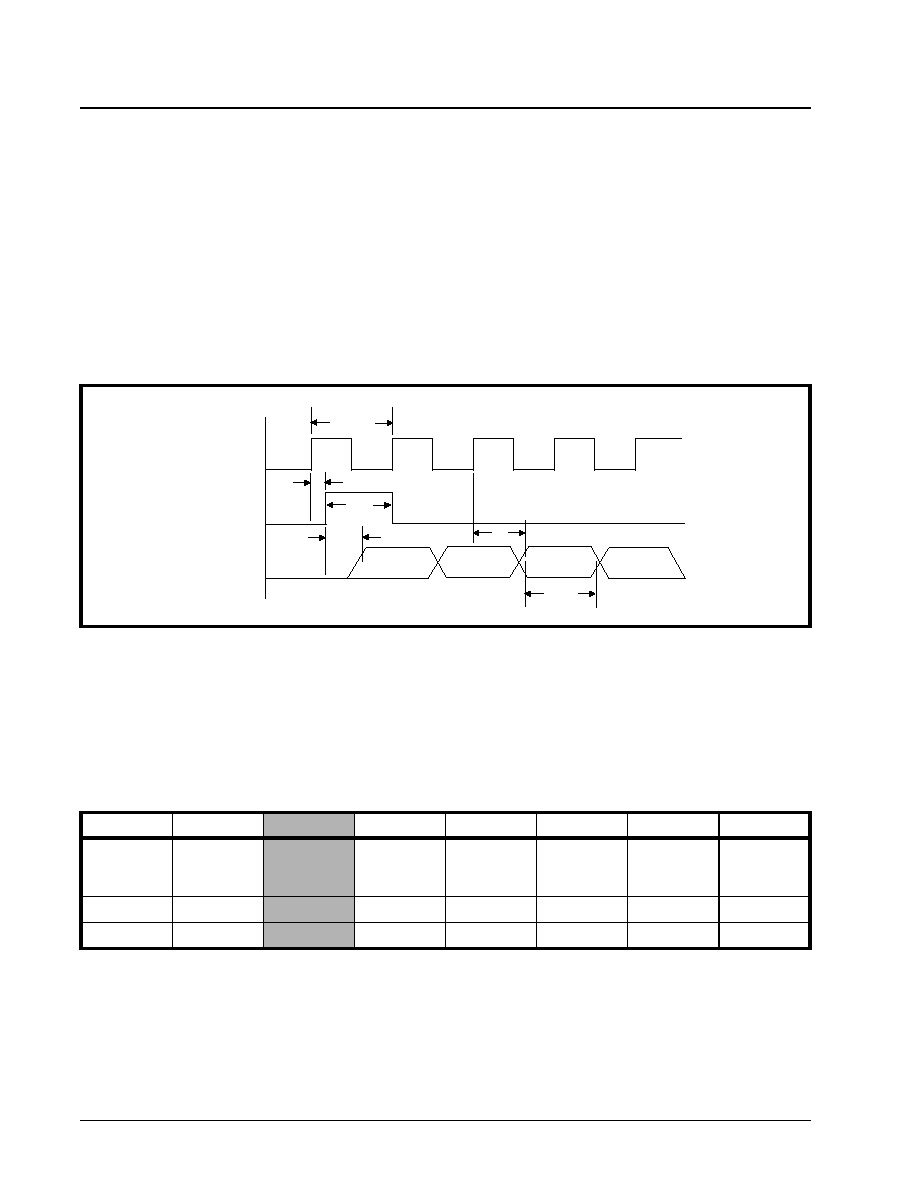

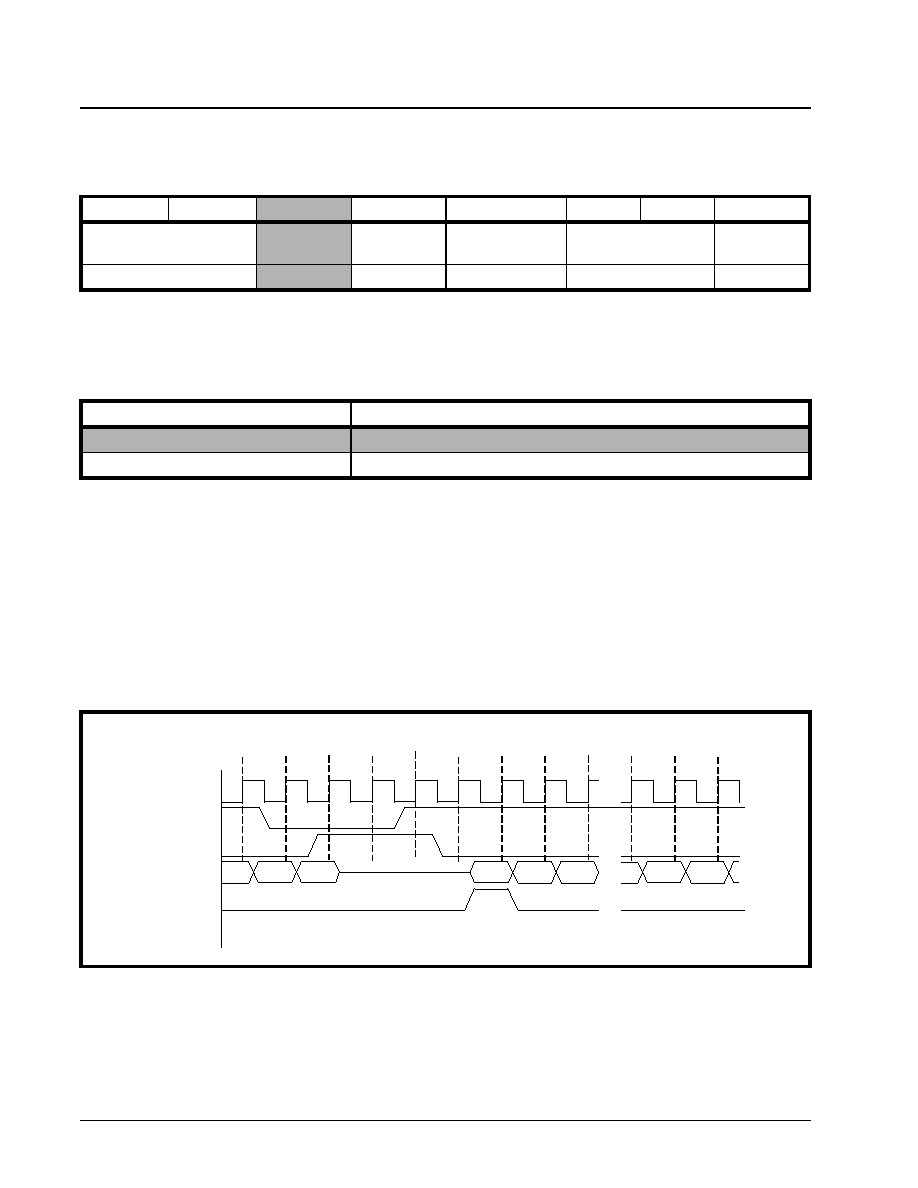

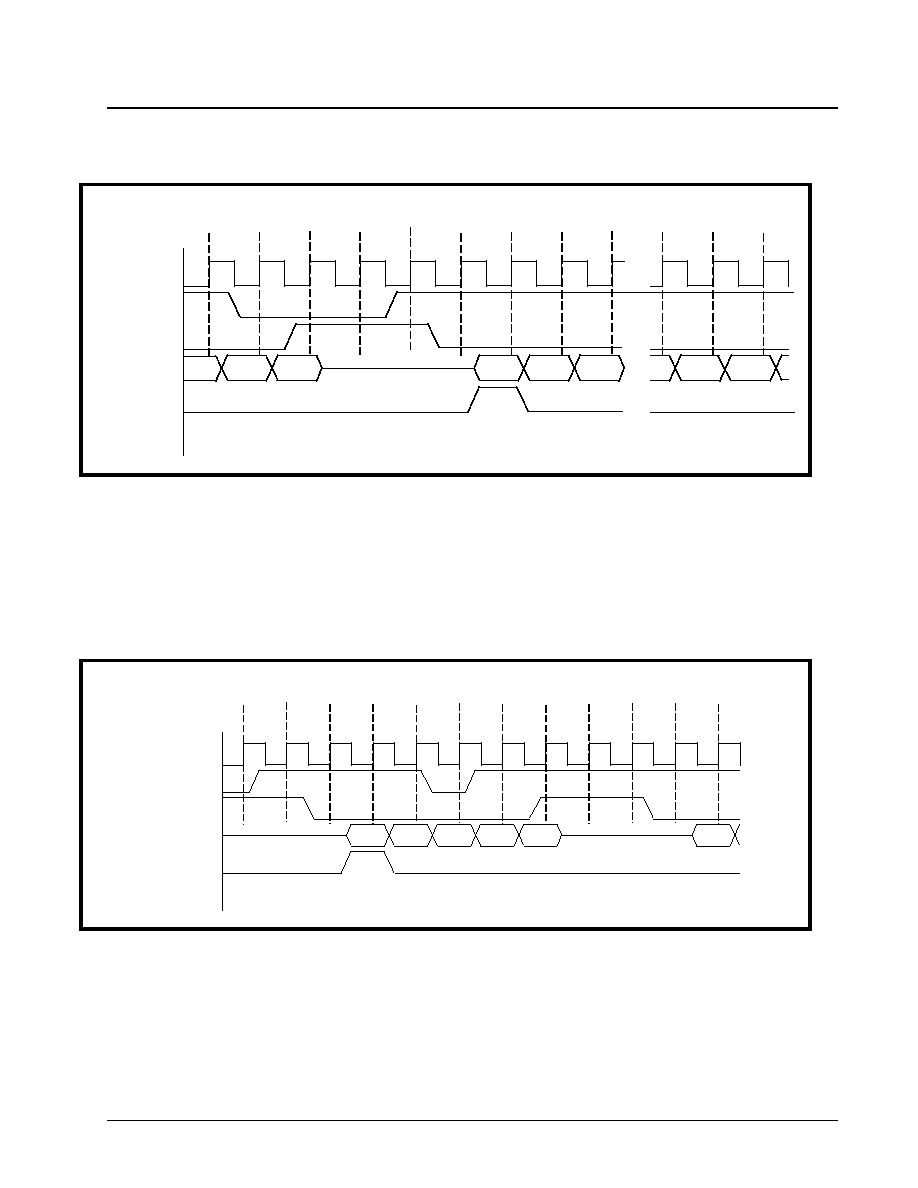

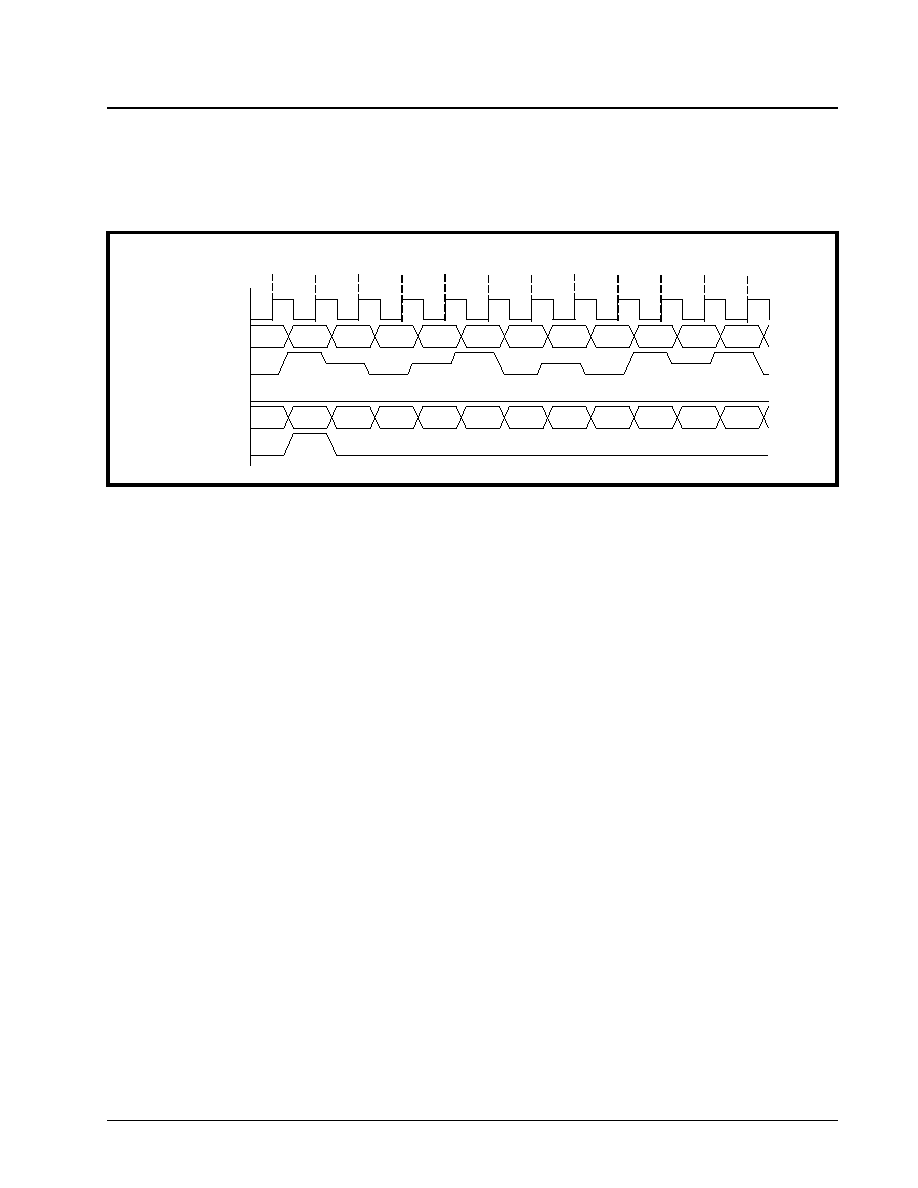

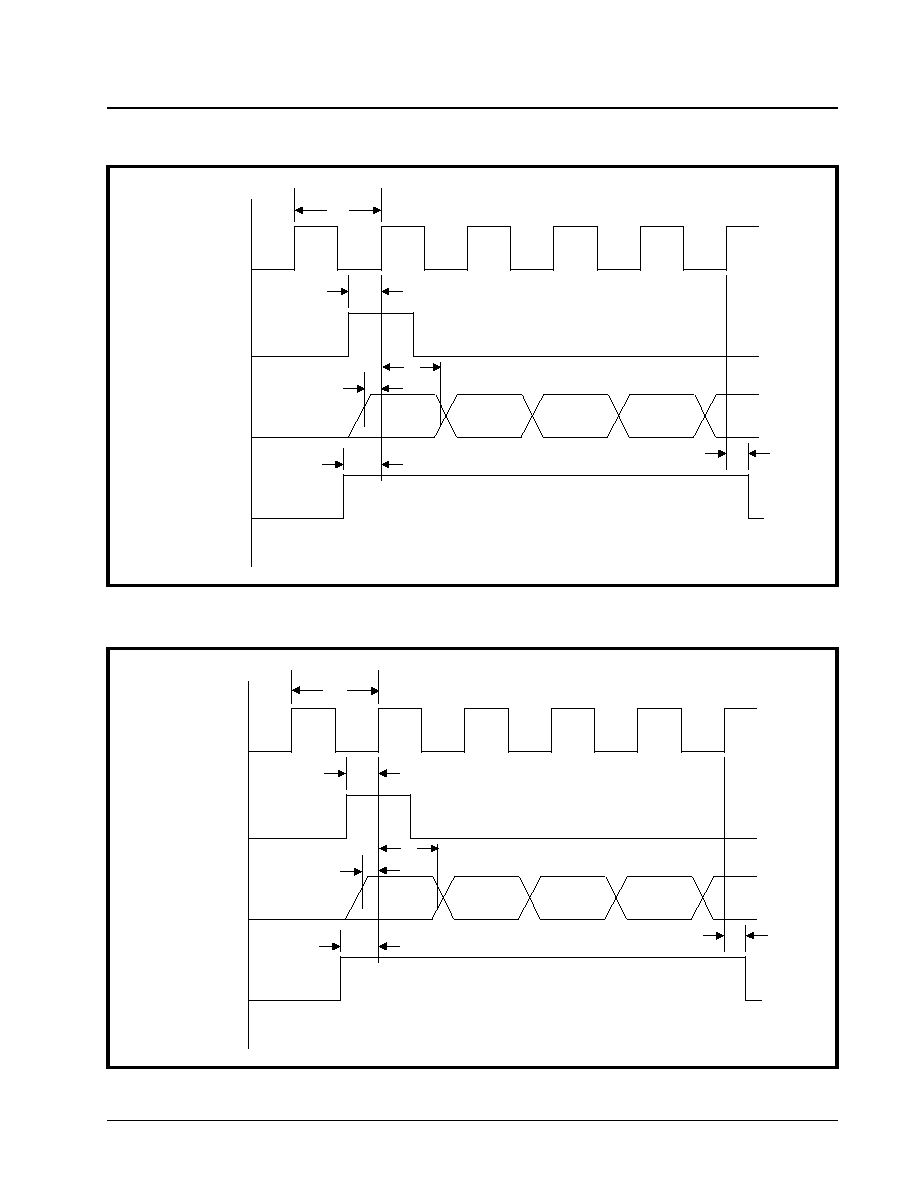

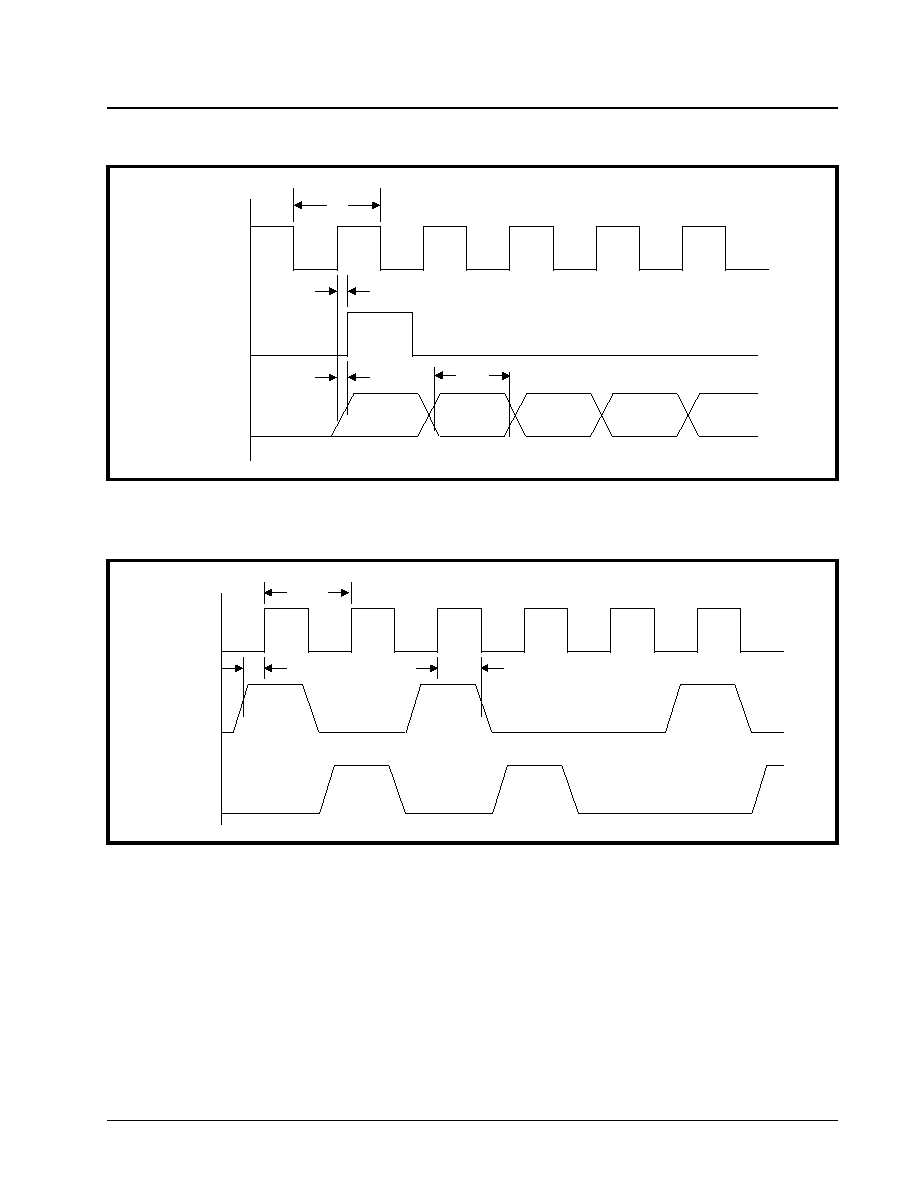

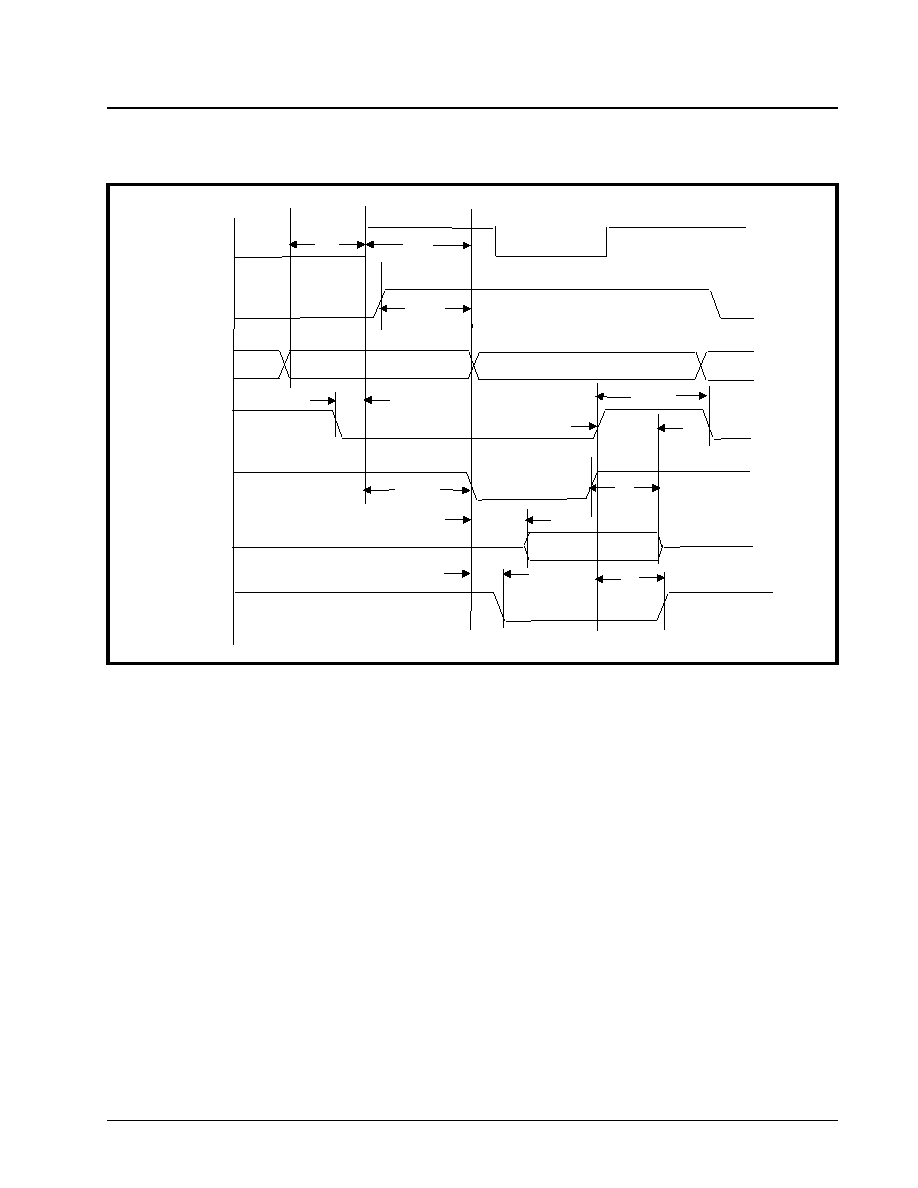

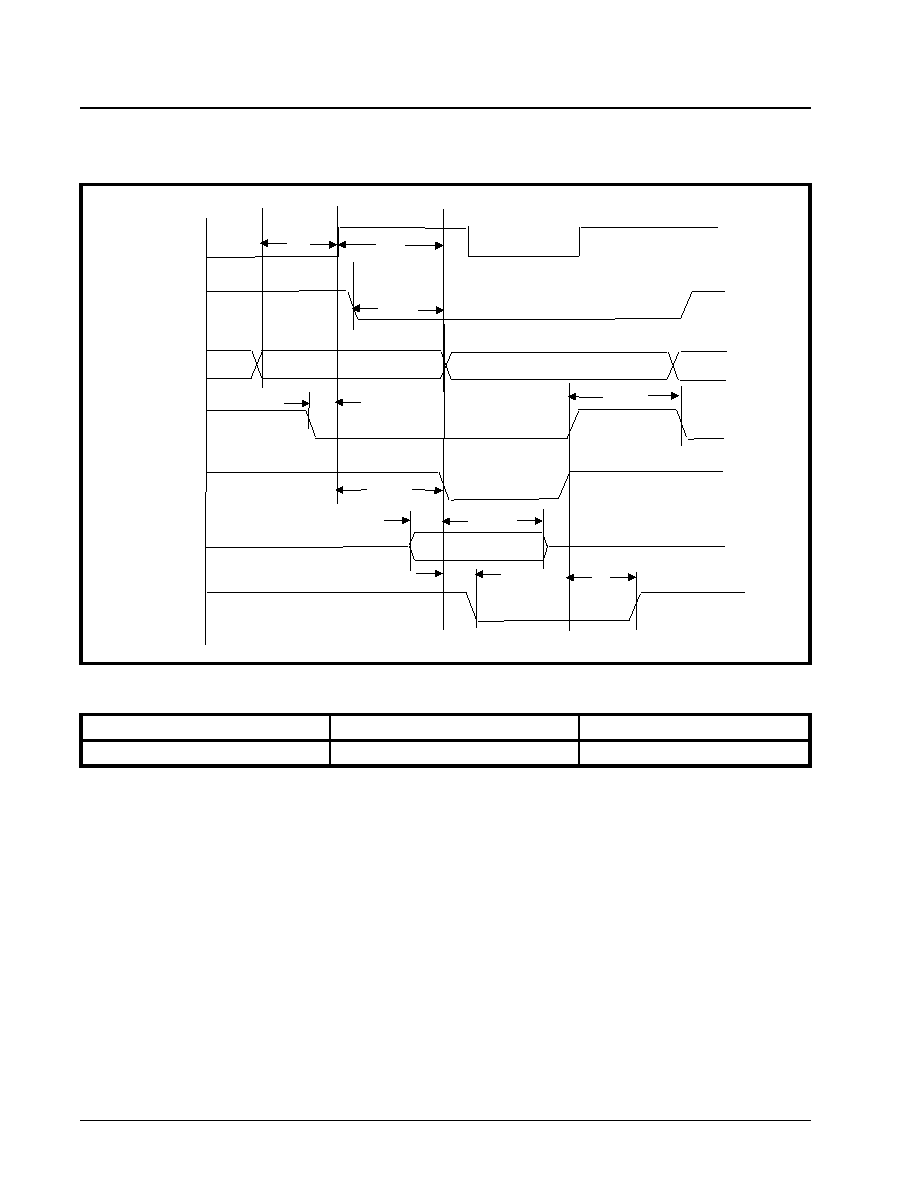

- Figure 8. Behavior of Microprocessor Interface signals during an çIntel-typeé Programmed I/O Read...

- Figure 9. Behavior of the Microprocessor Interface Signals, during an çIntel-typeé Programmed I/O...

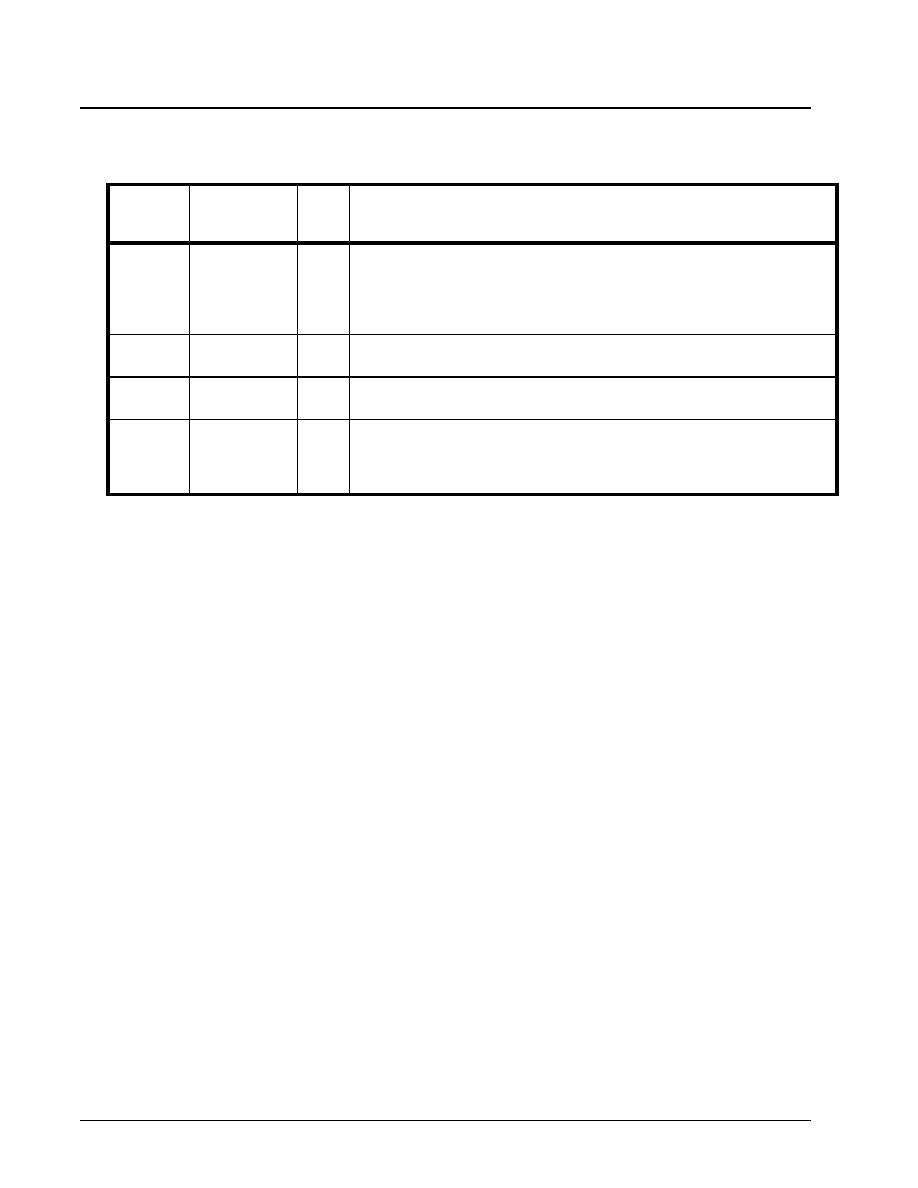

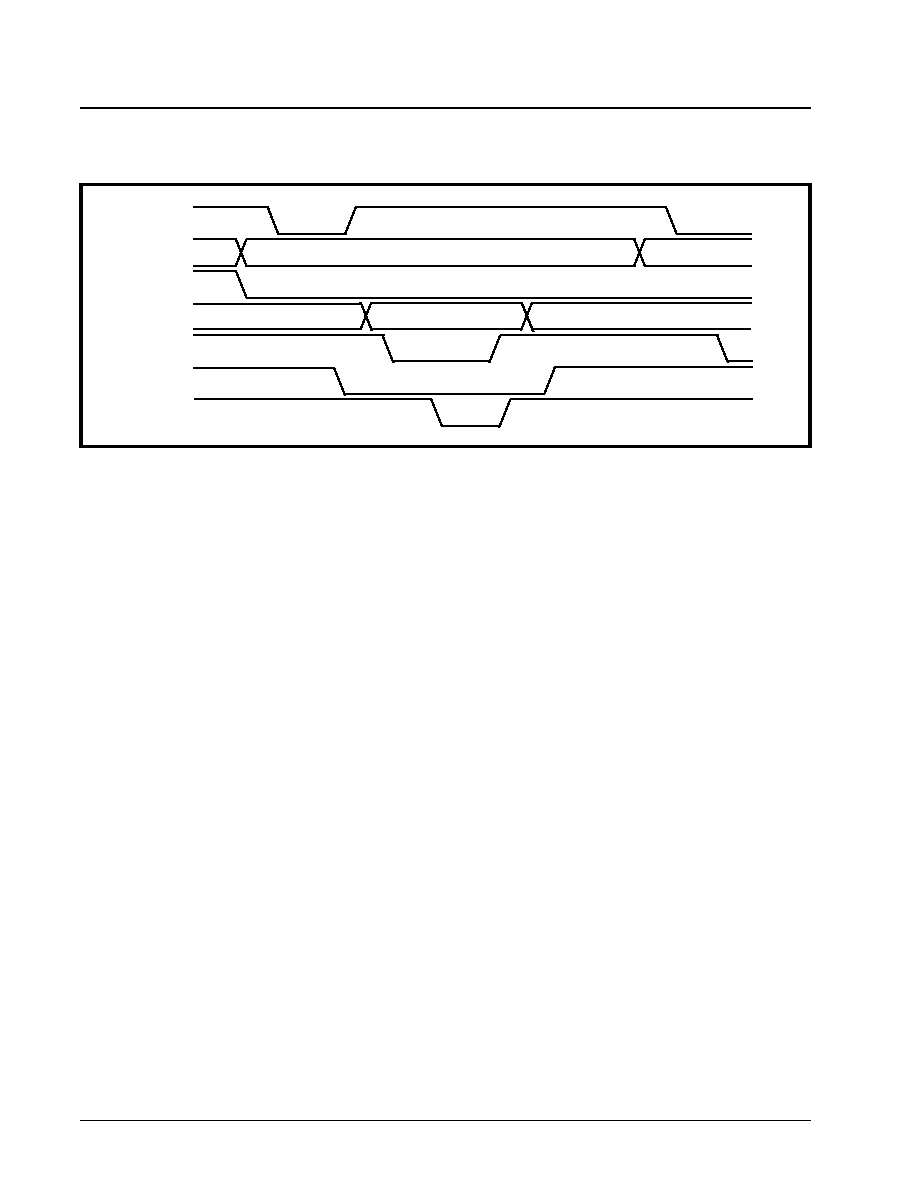

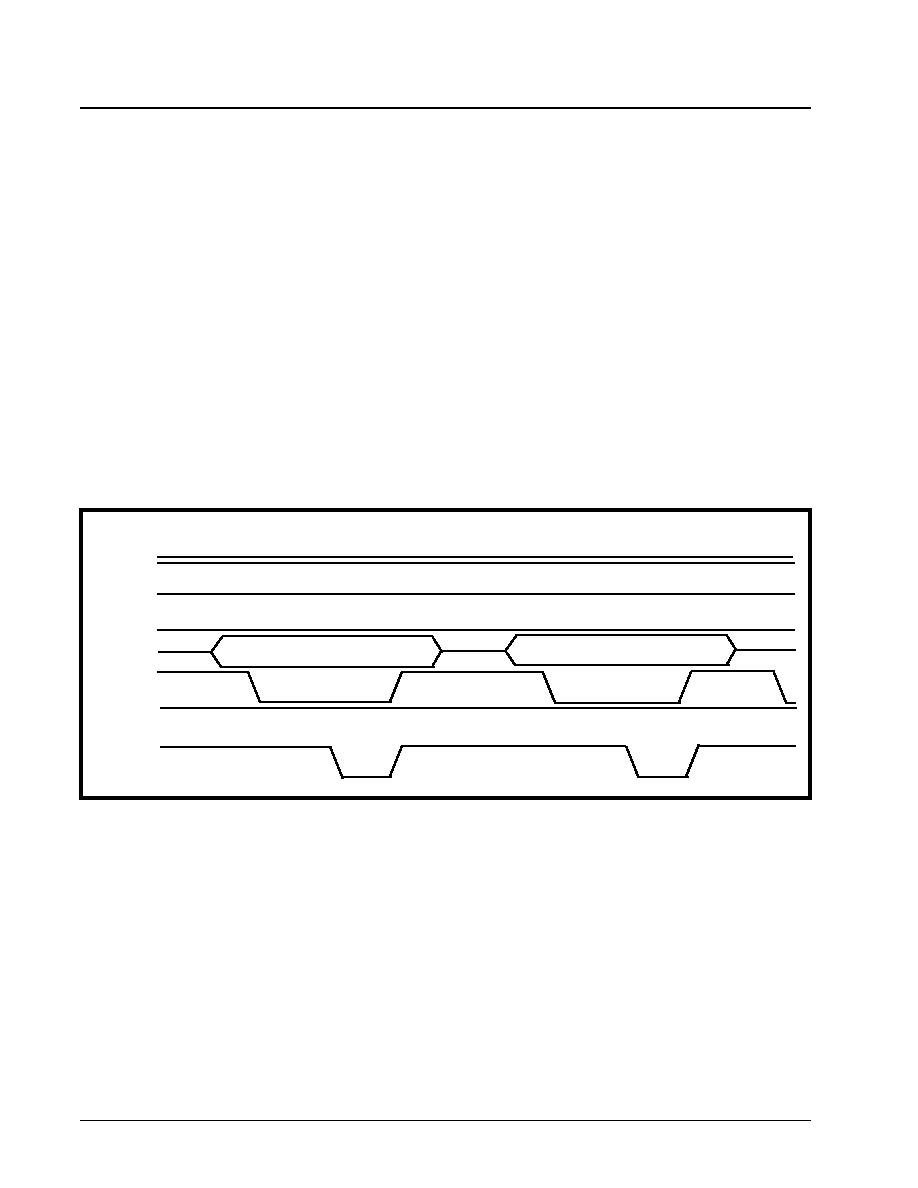

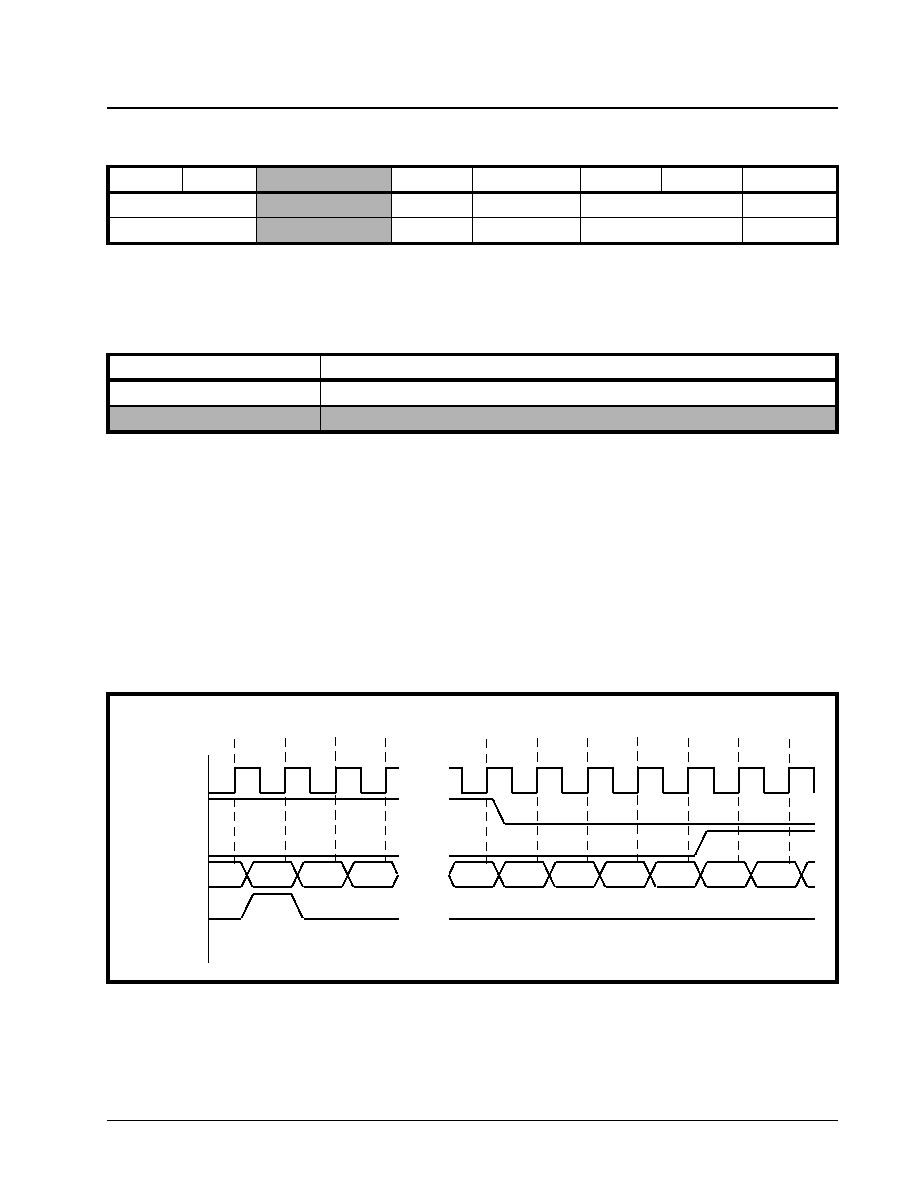

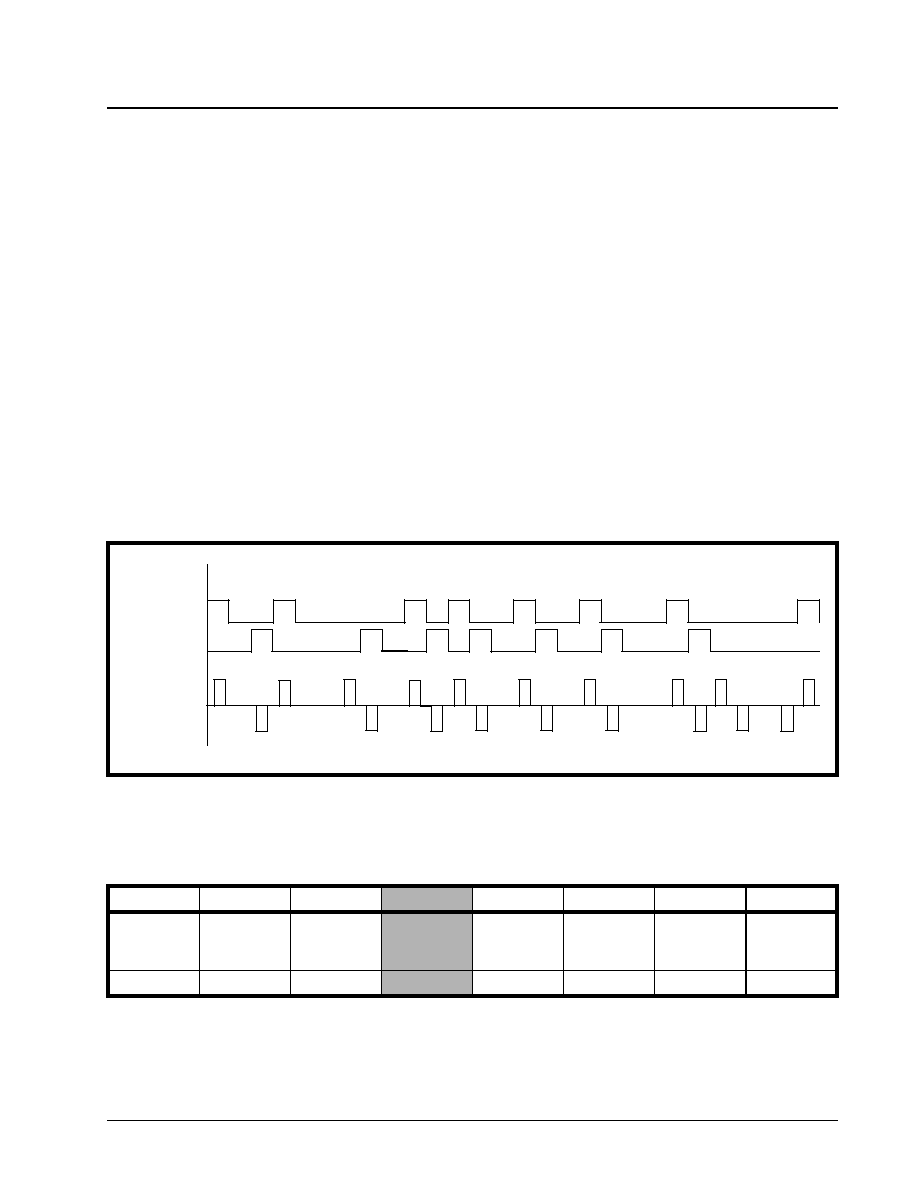

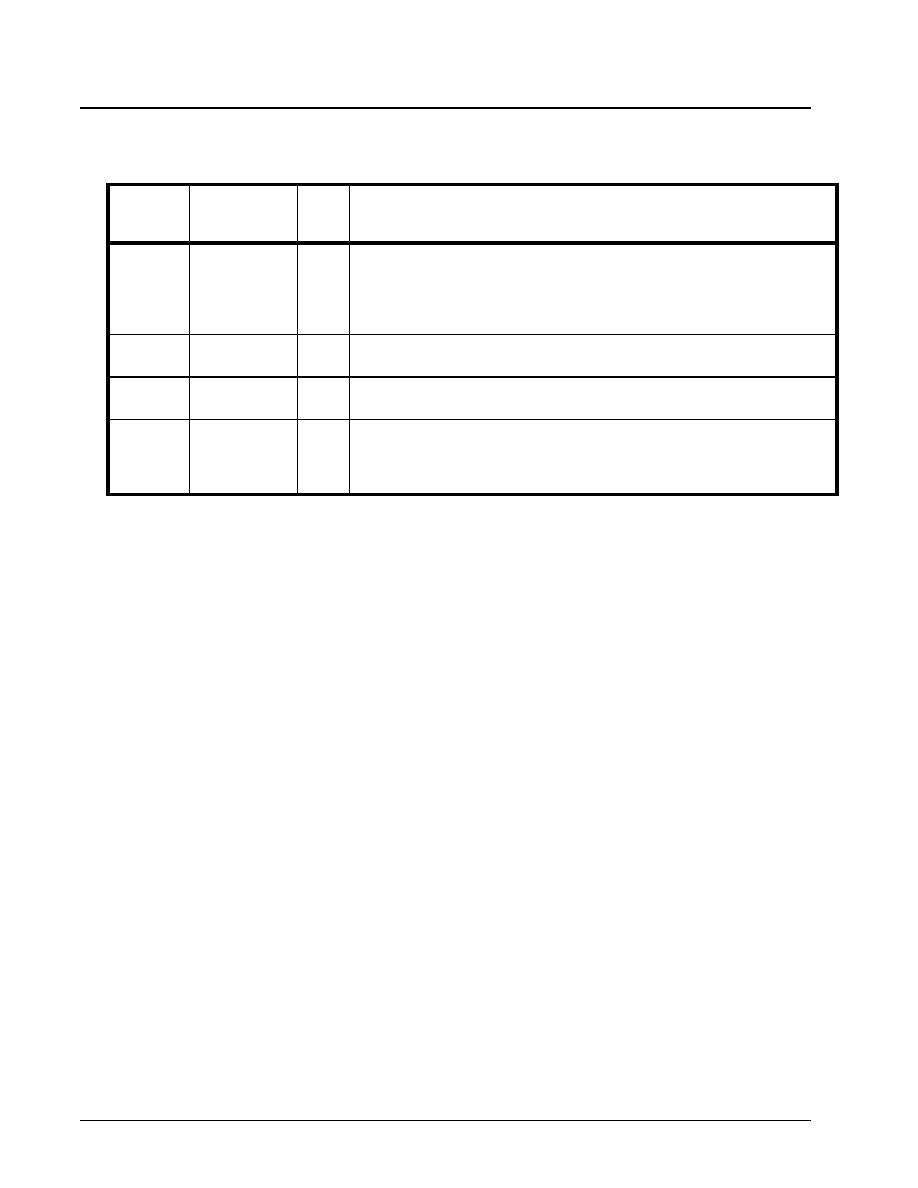

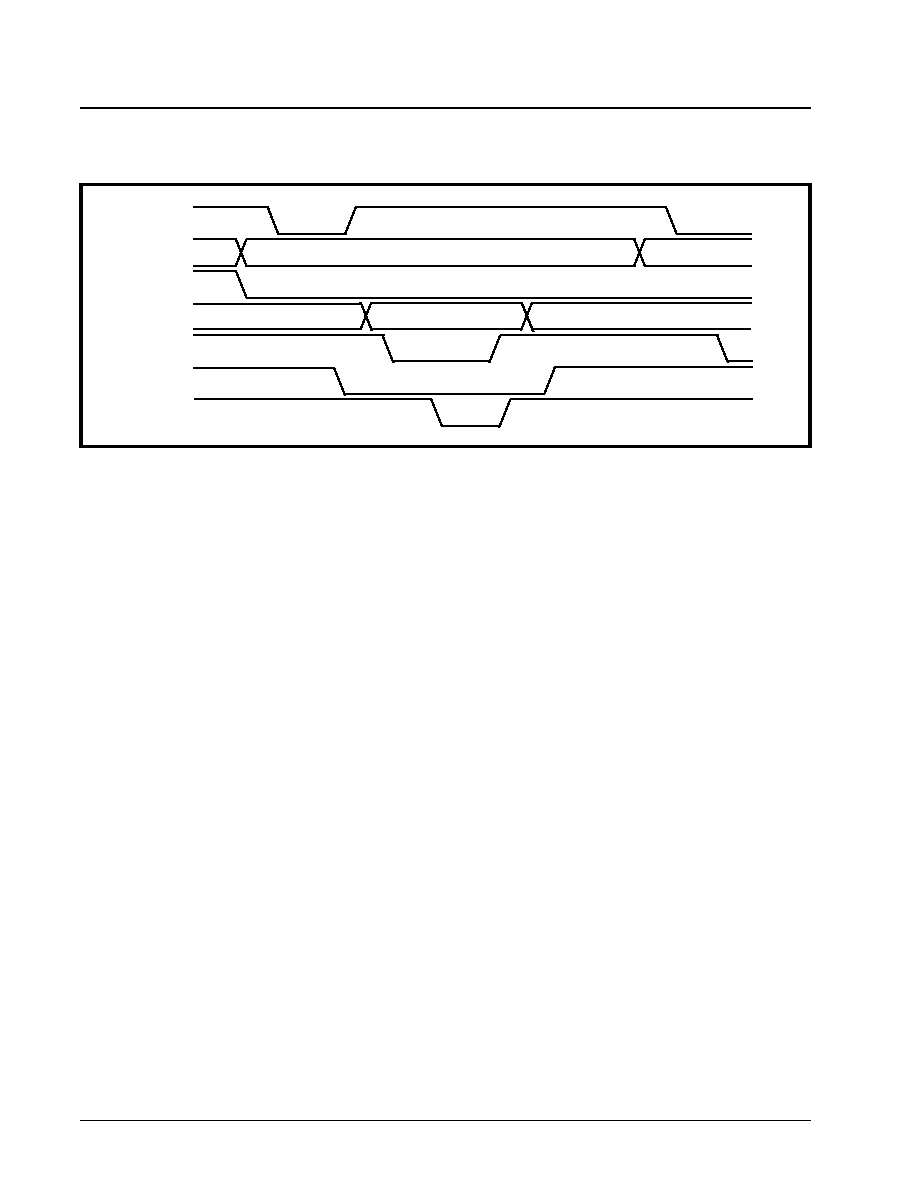

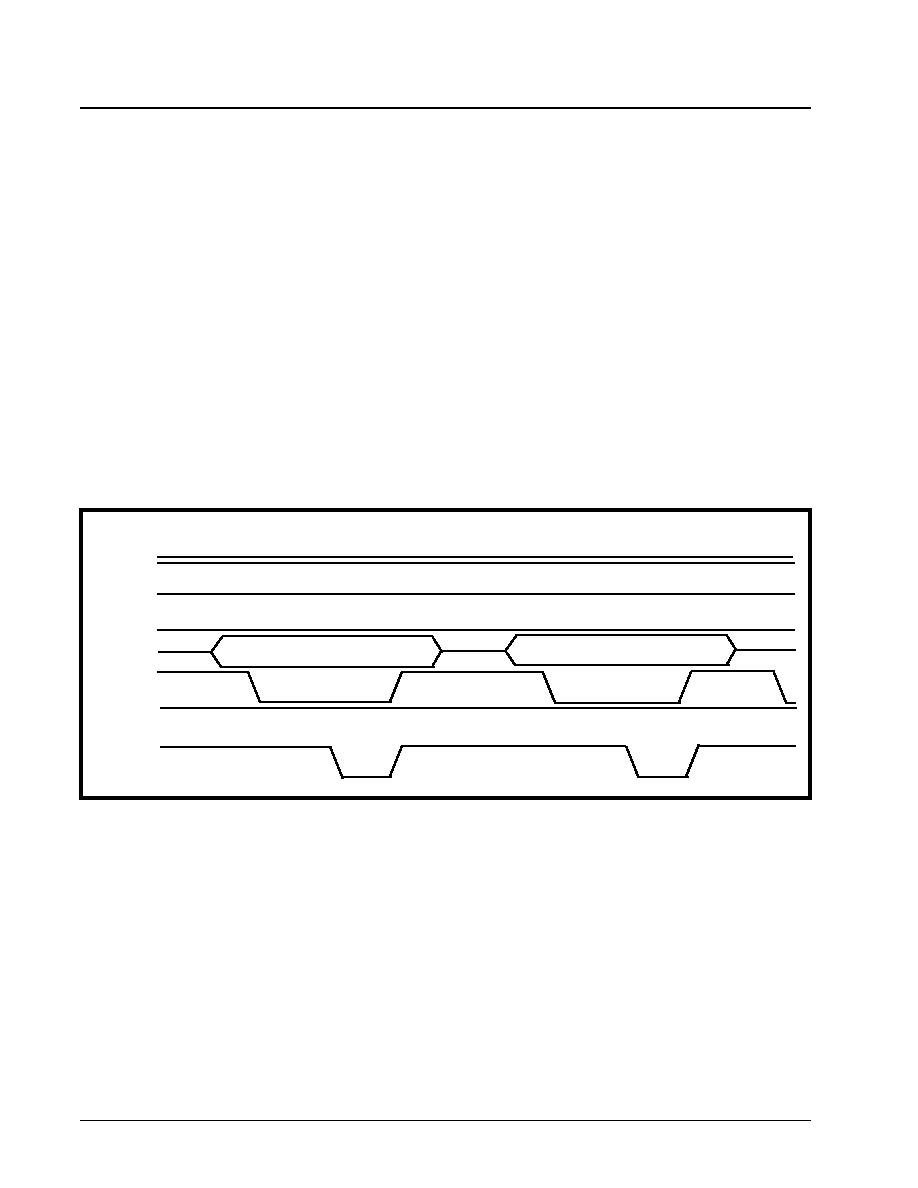

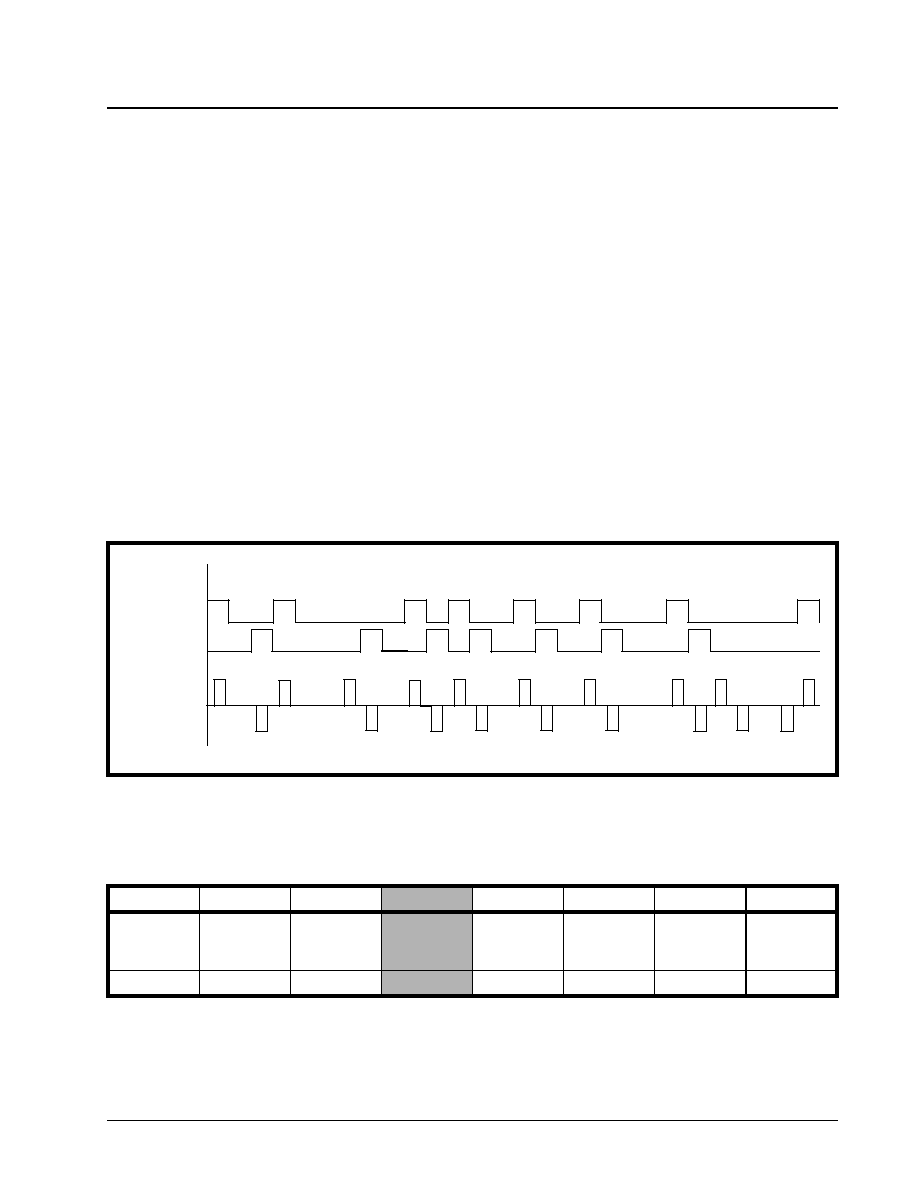

- Figure 10. Illustration of the Behavior of Microprocessor Interface signals, during a çMotorola- ...

- Figure 11. Illustration of the Behavior of the Microprocessor Interface signal, during a �çMotoro...

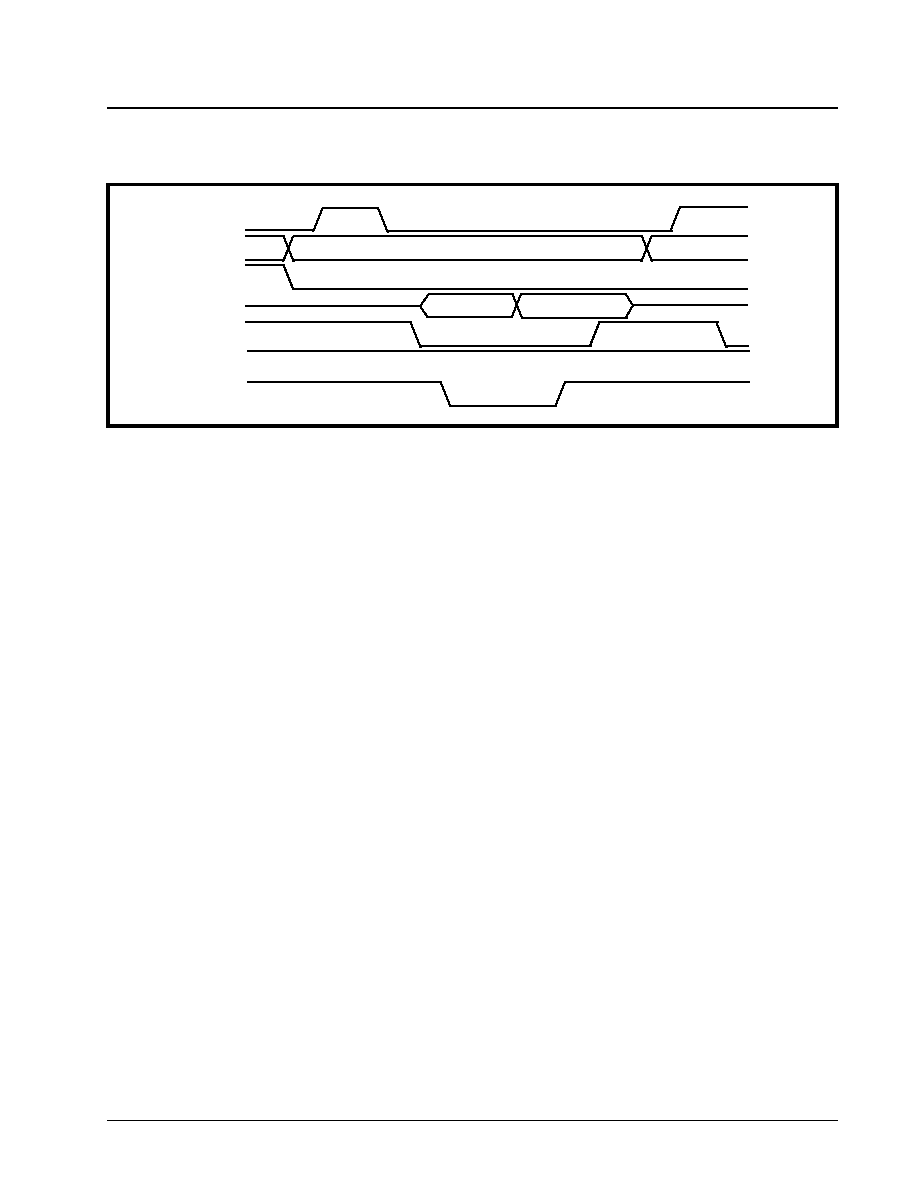

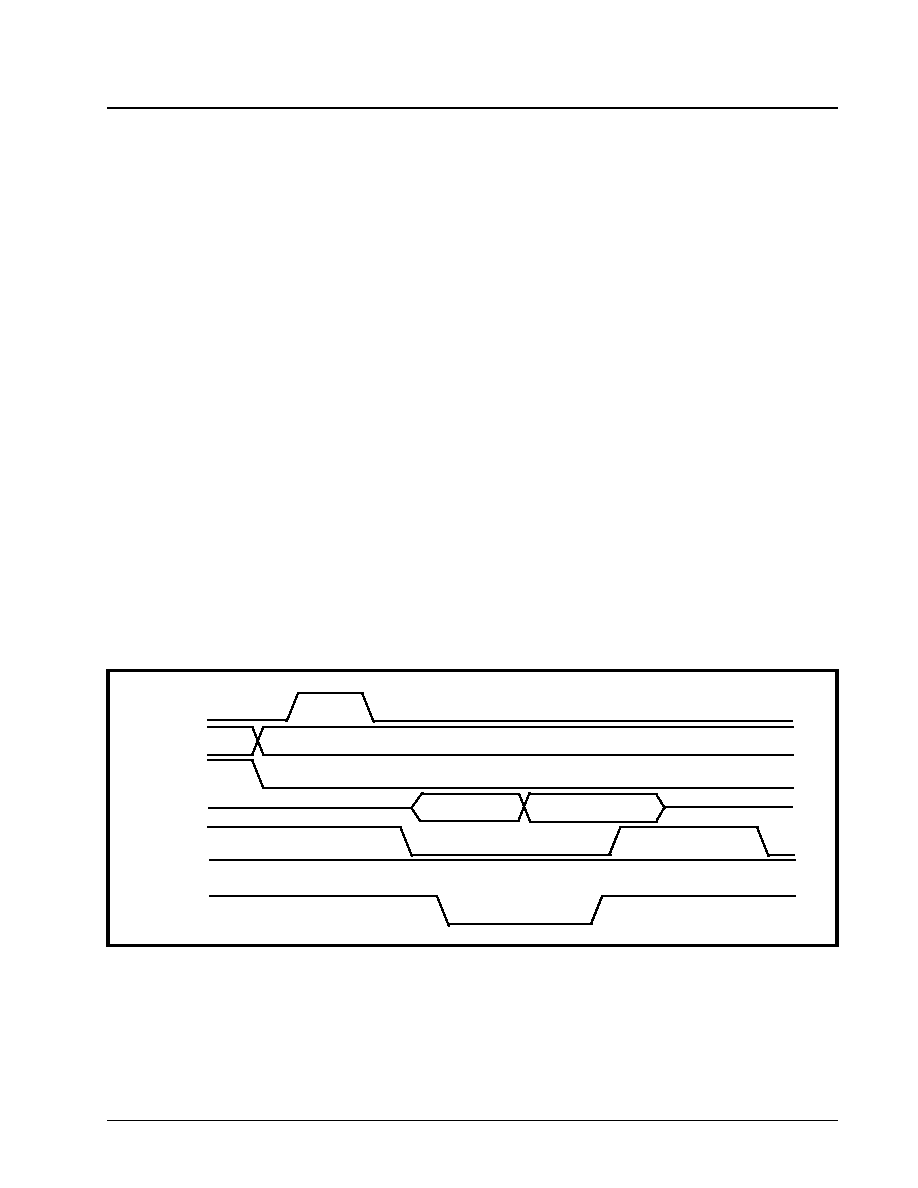

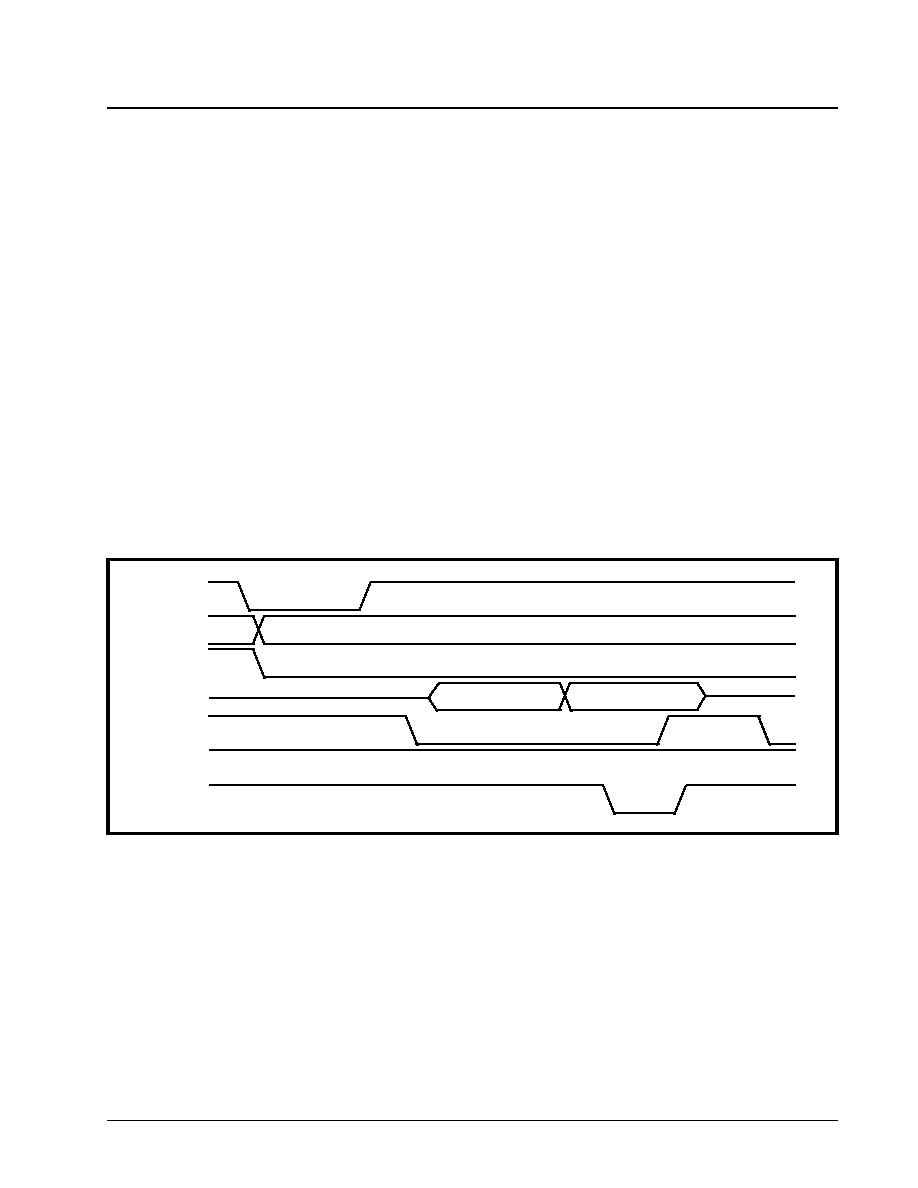

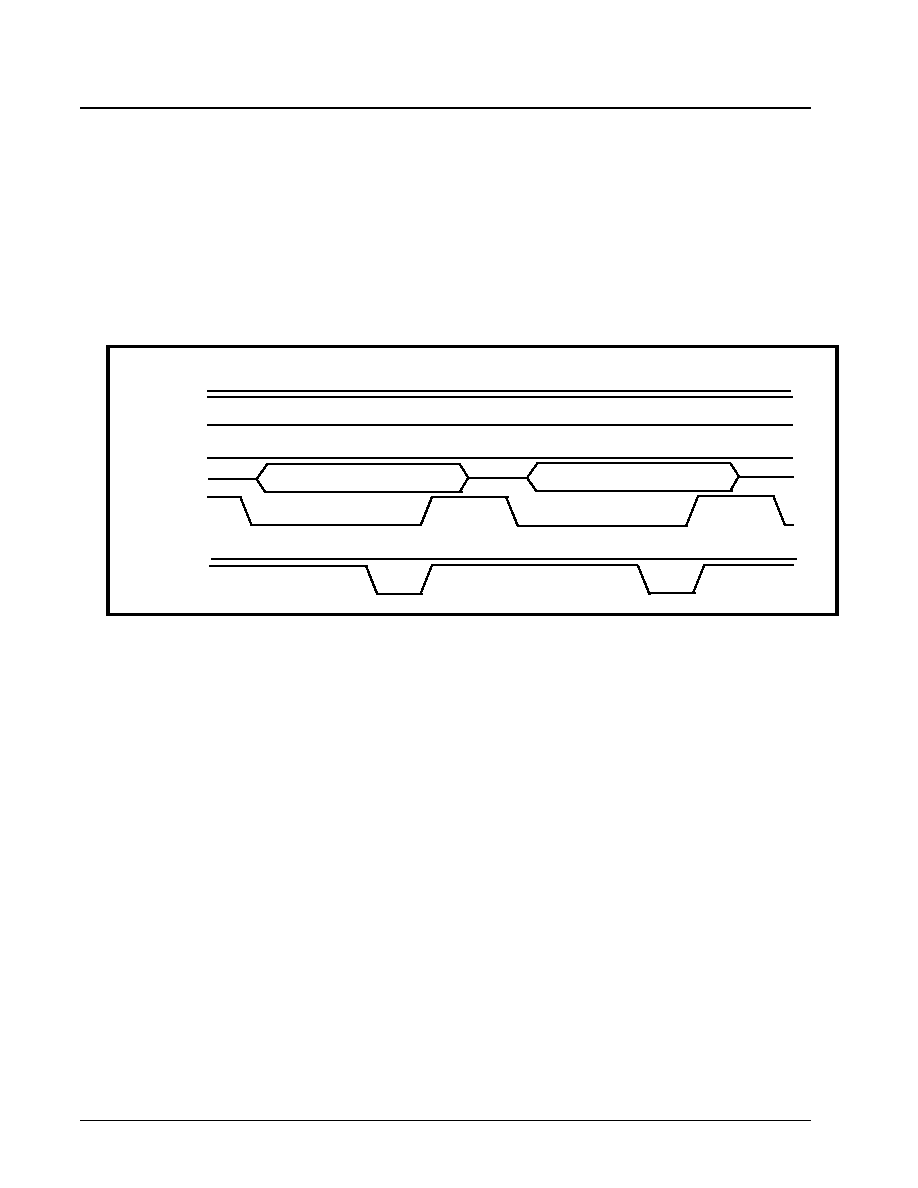

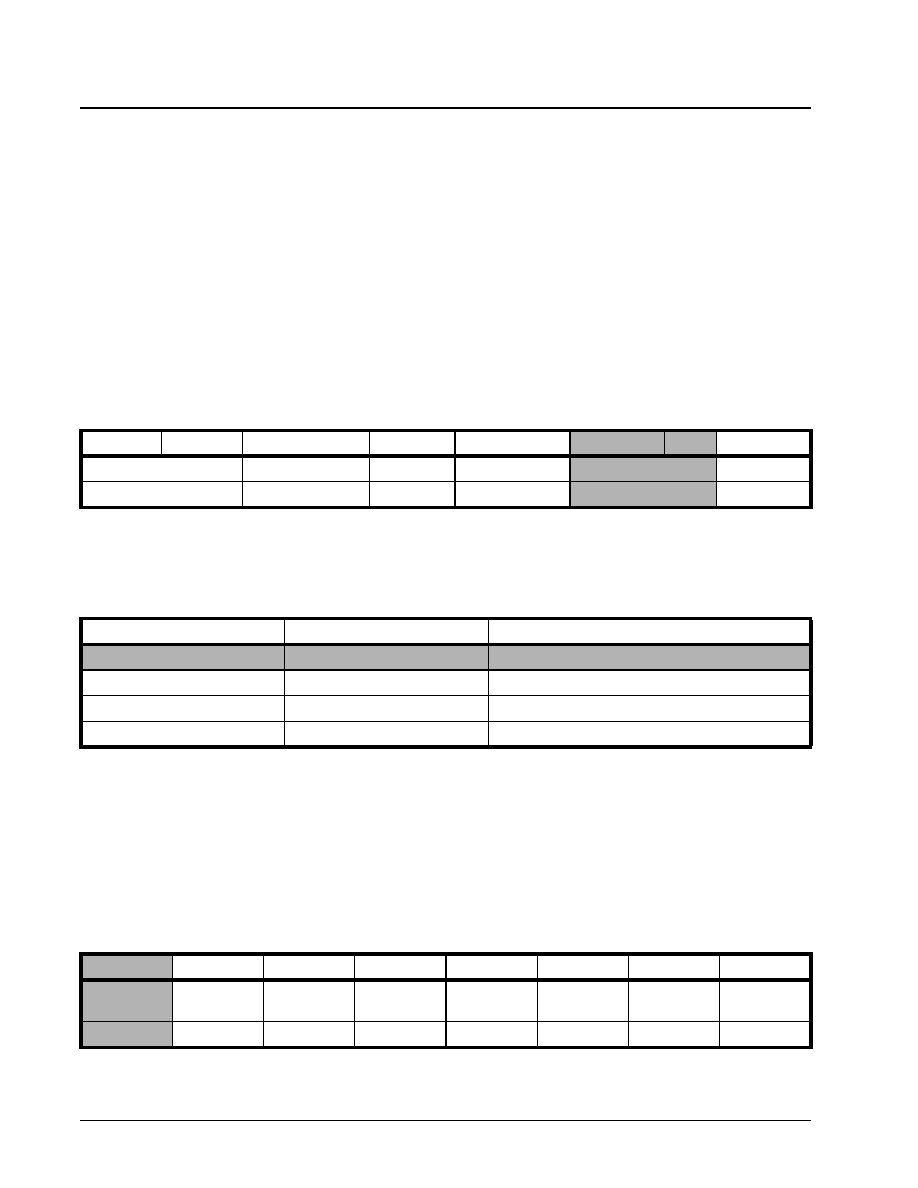

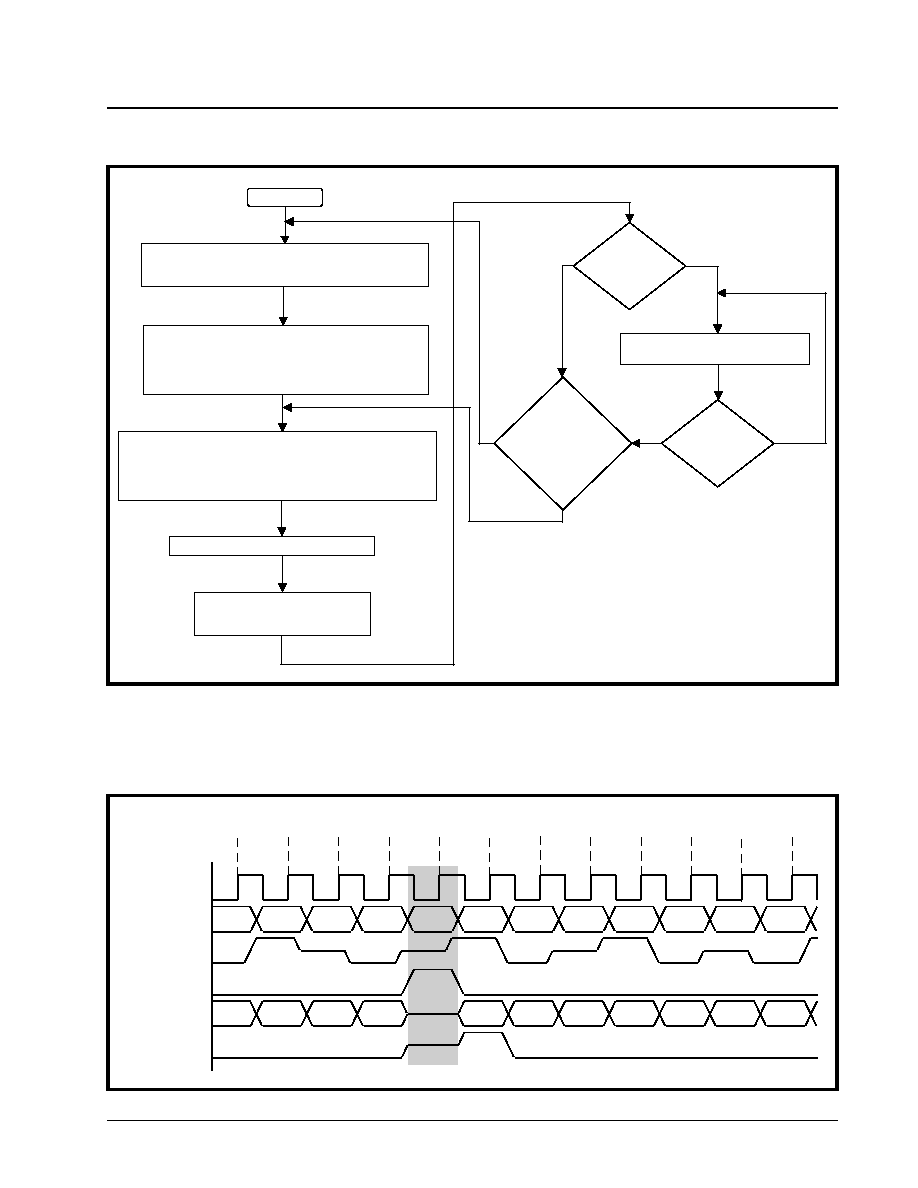

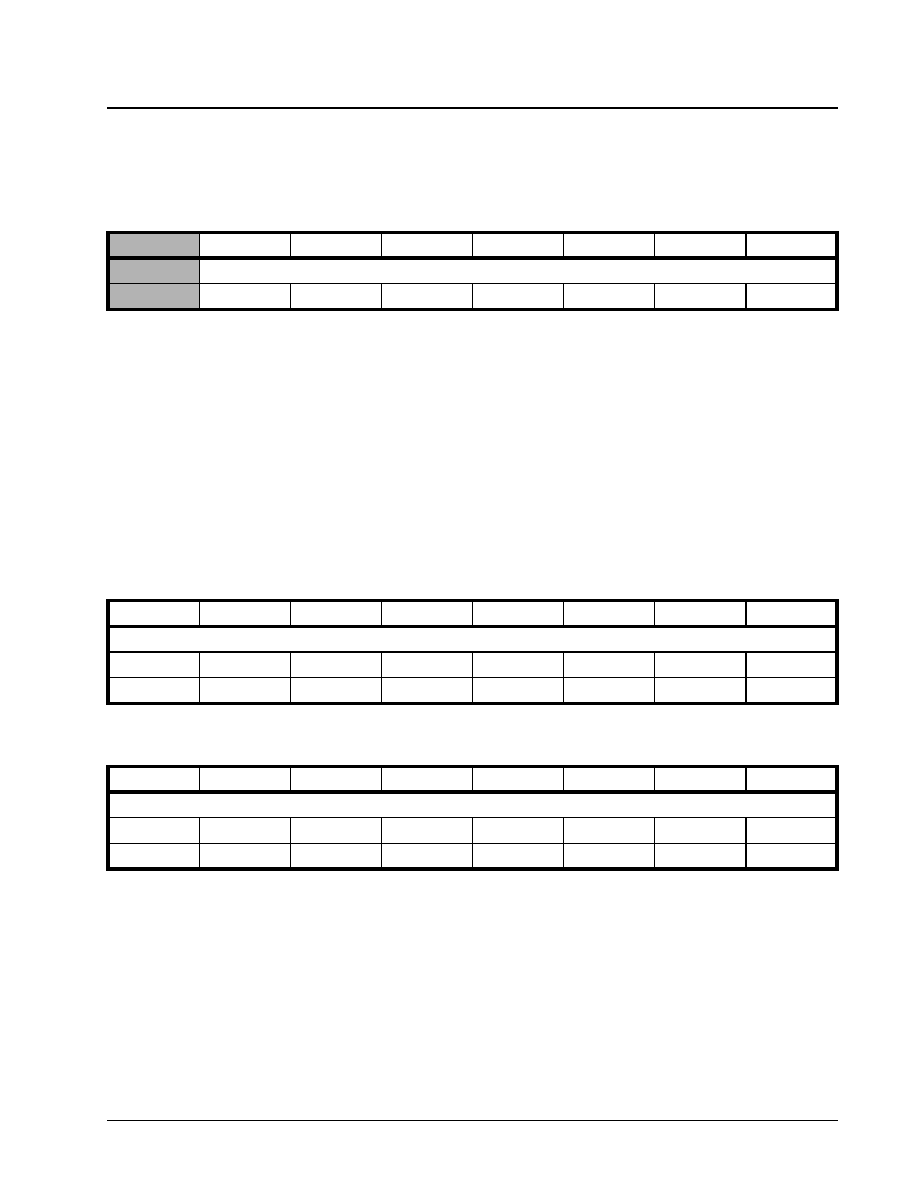

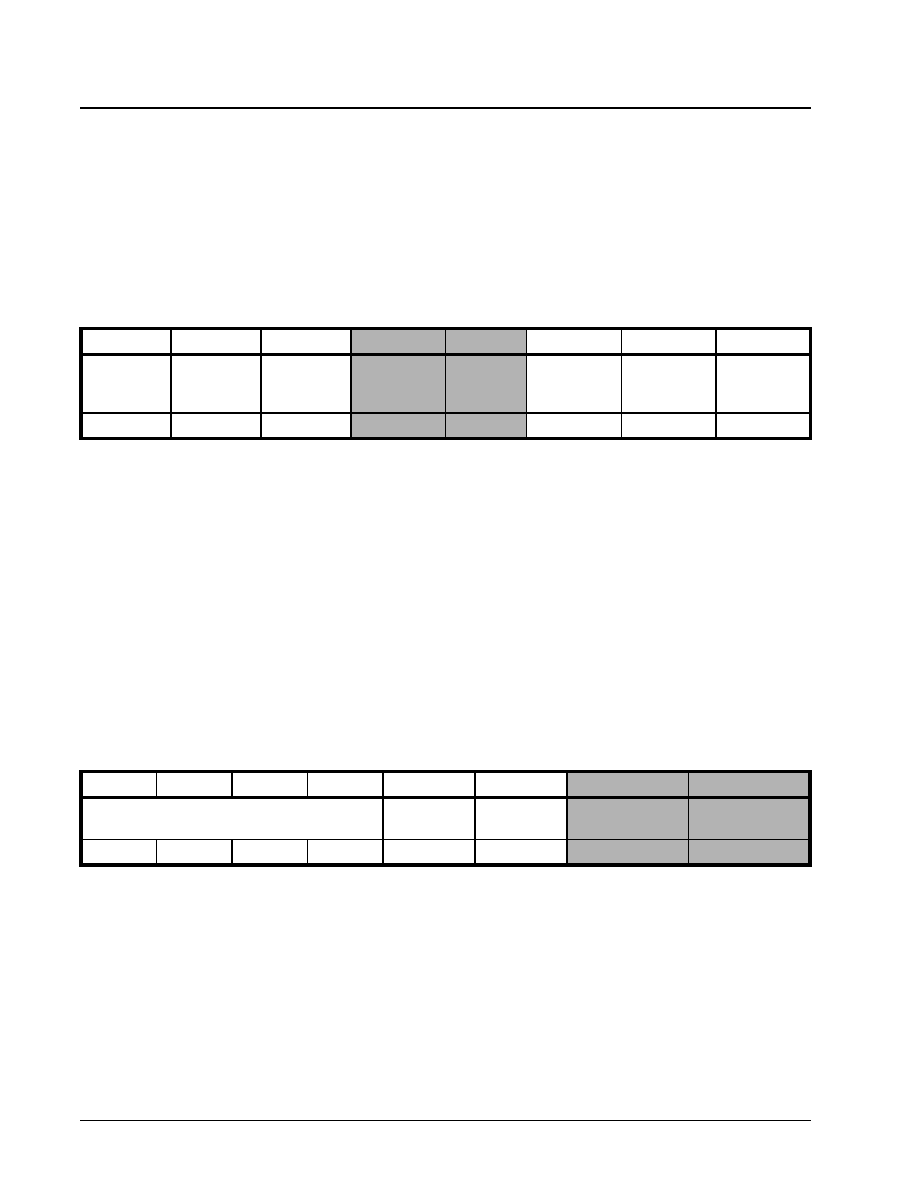

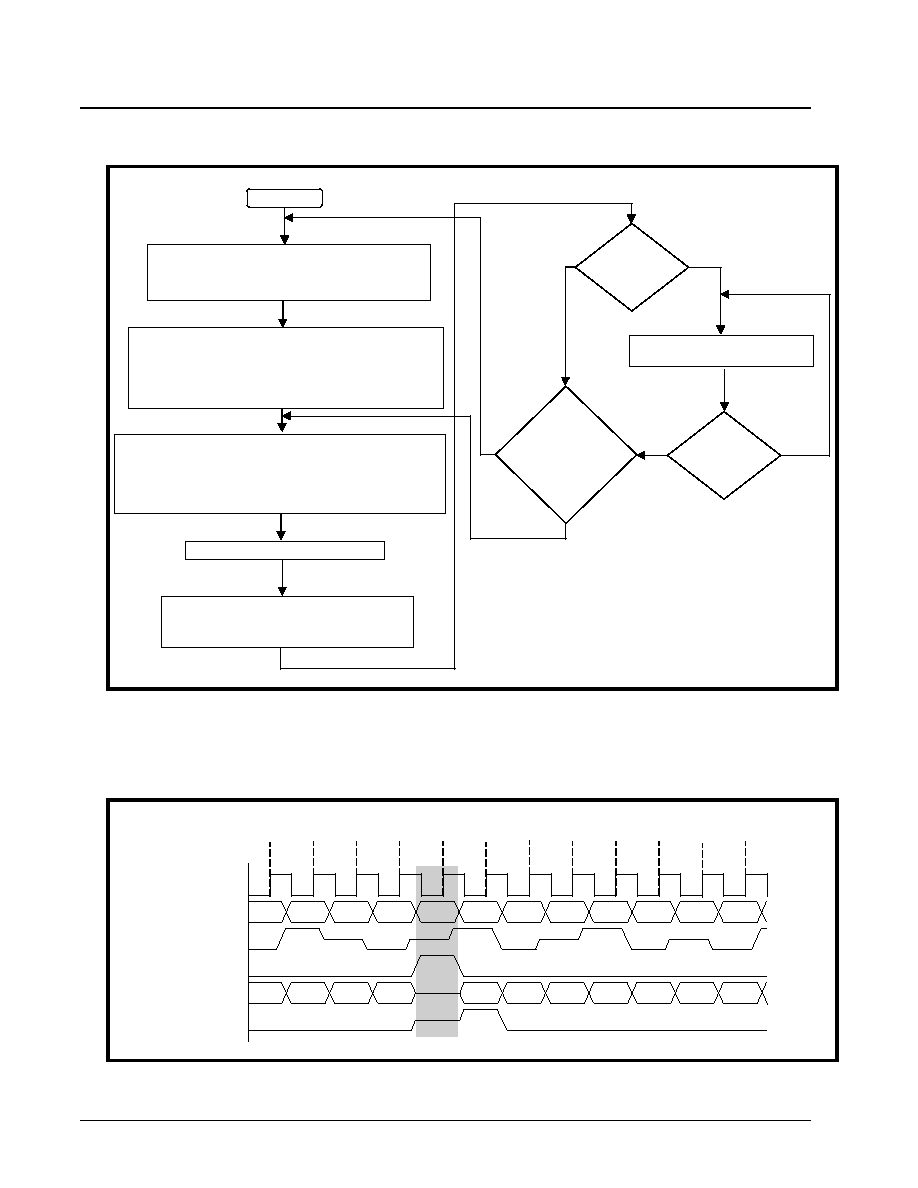

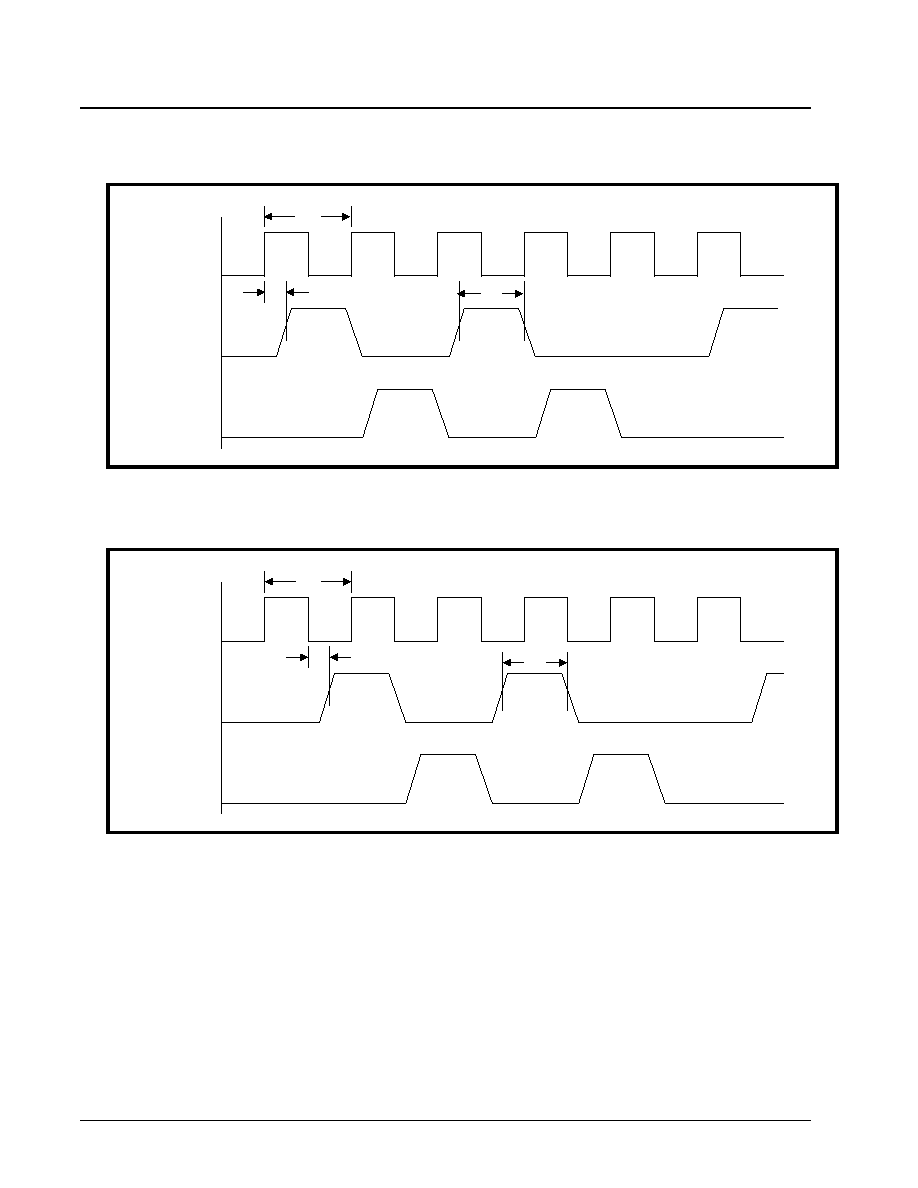

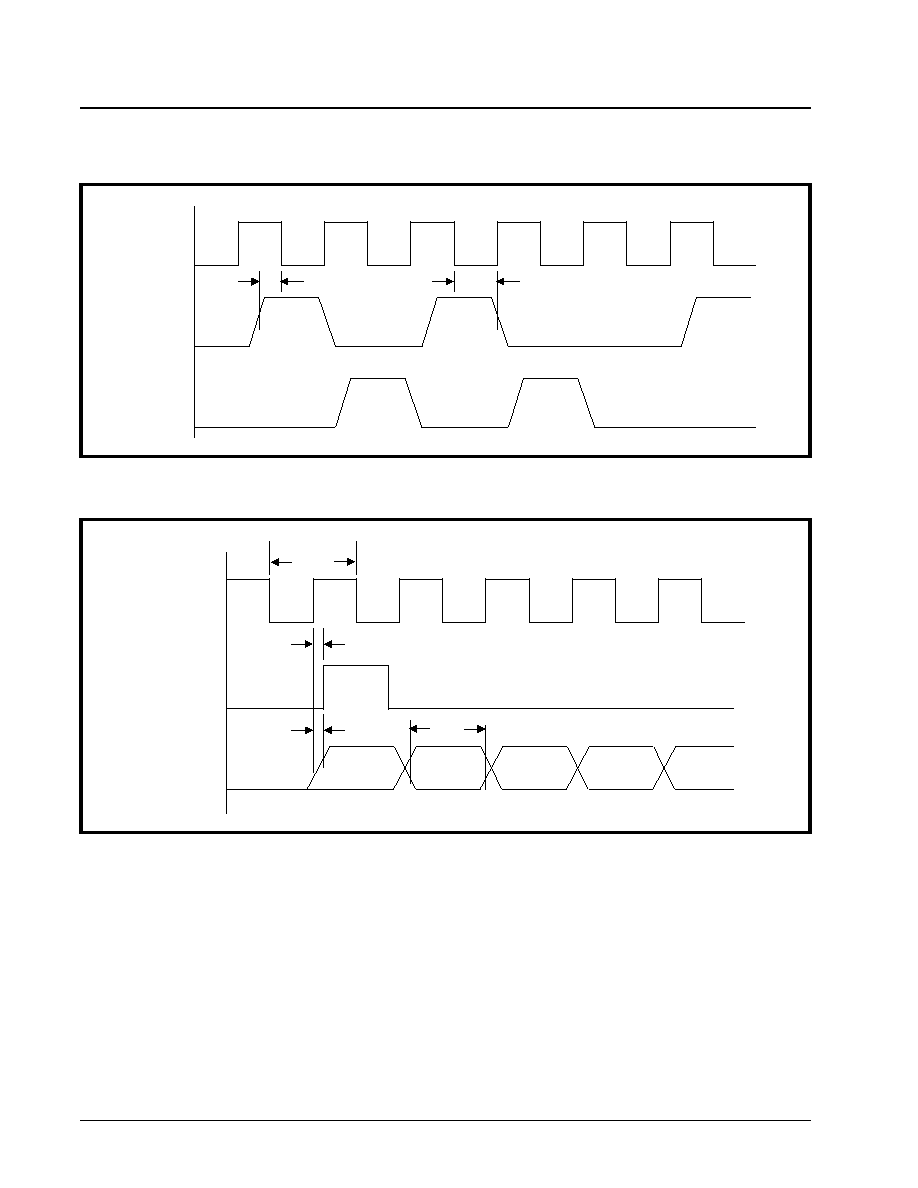

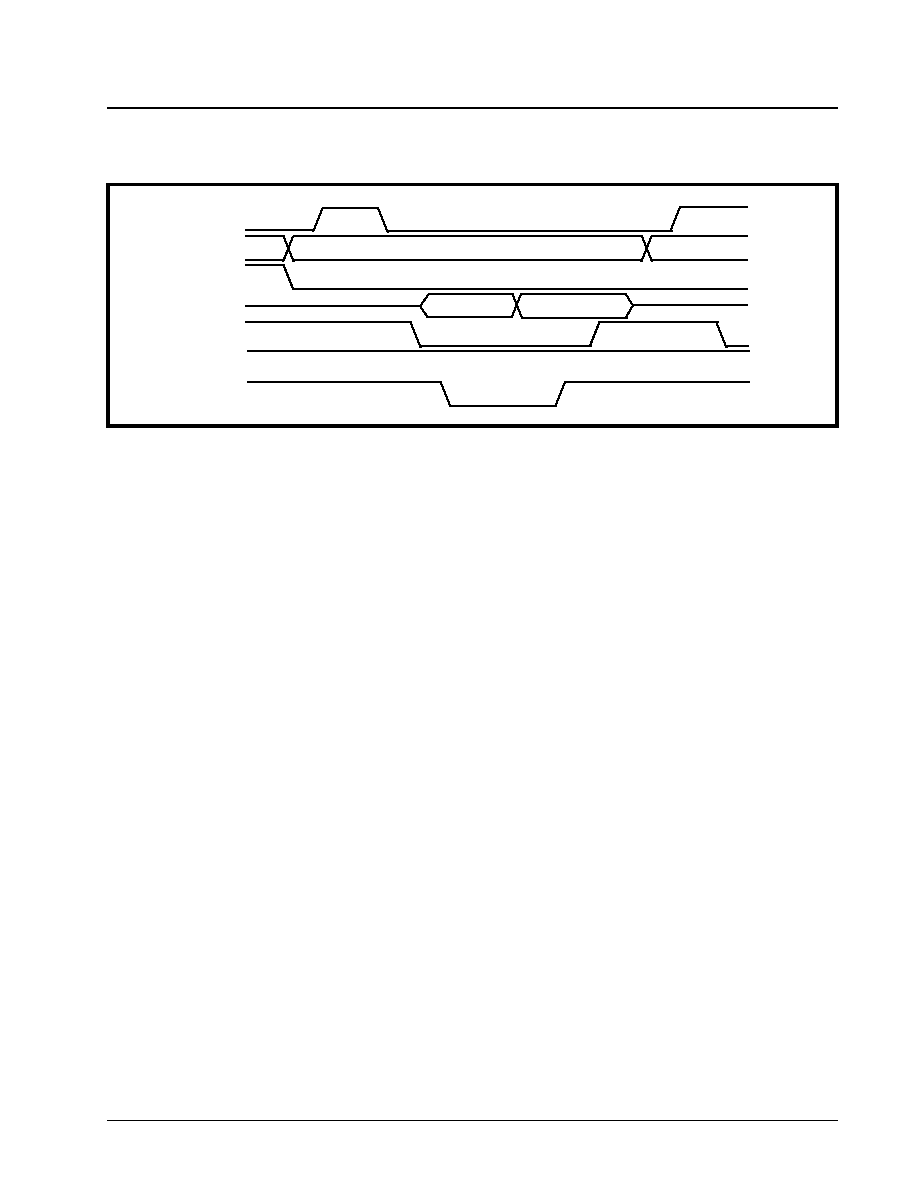

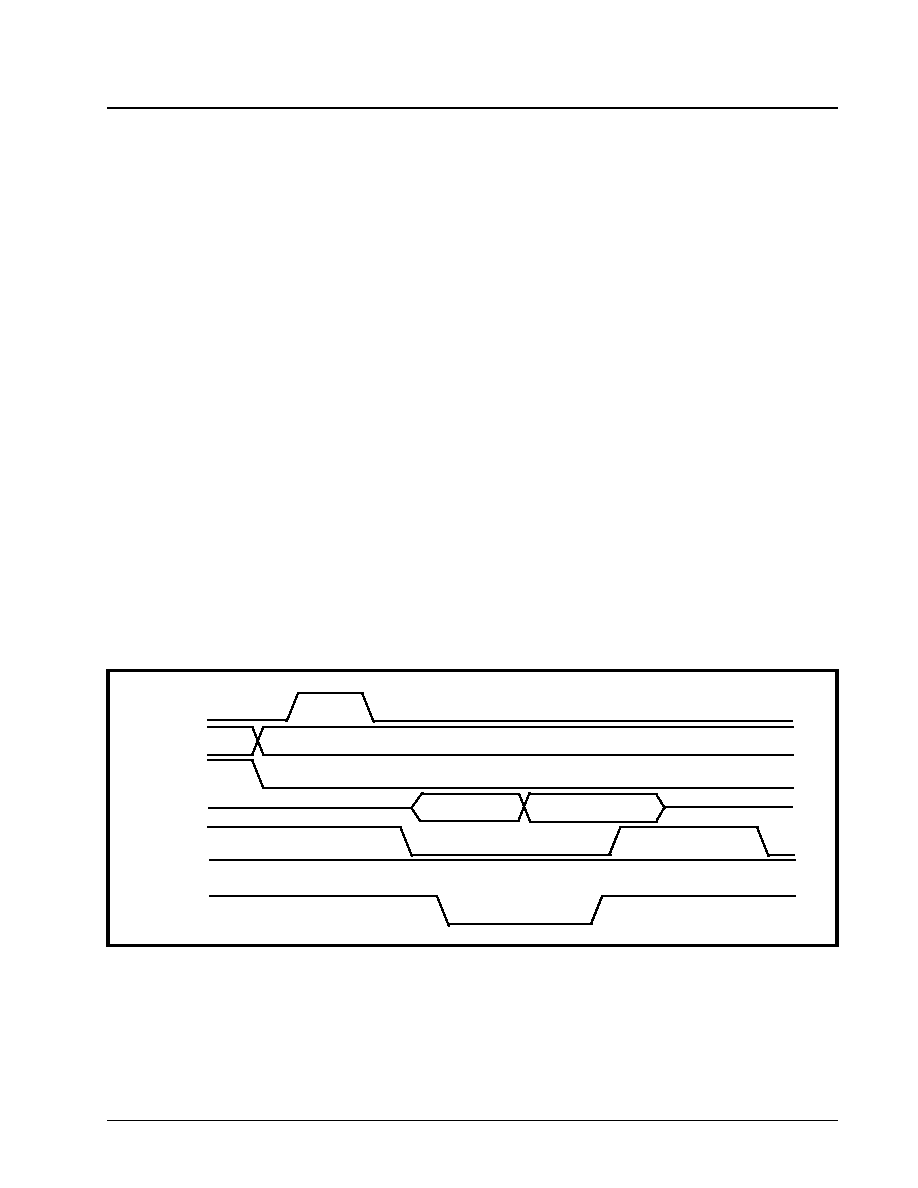

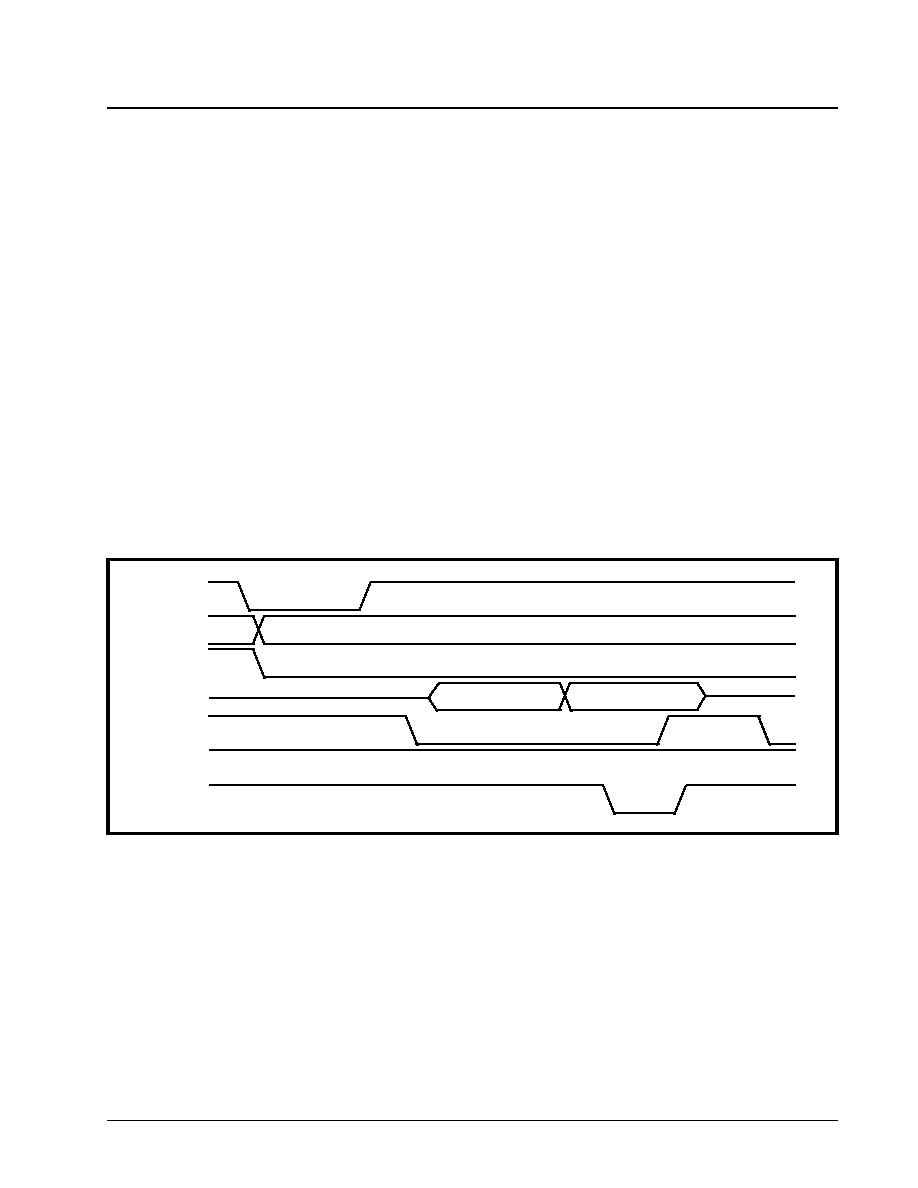

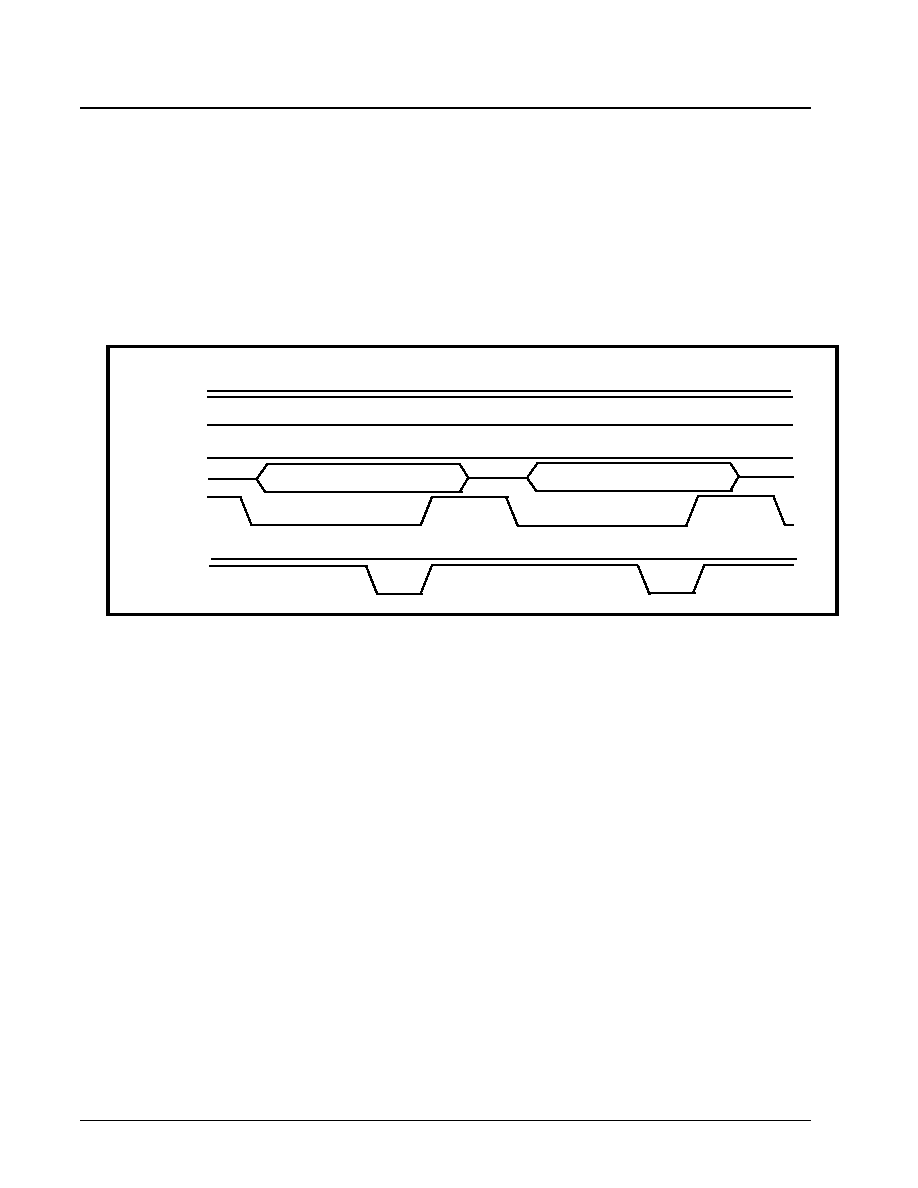

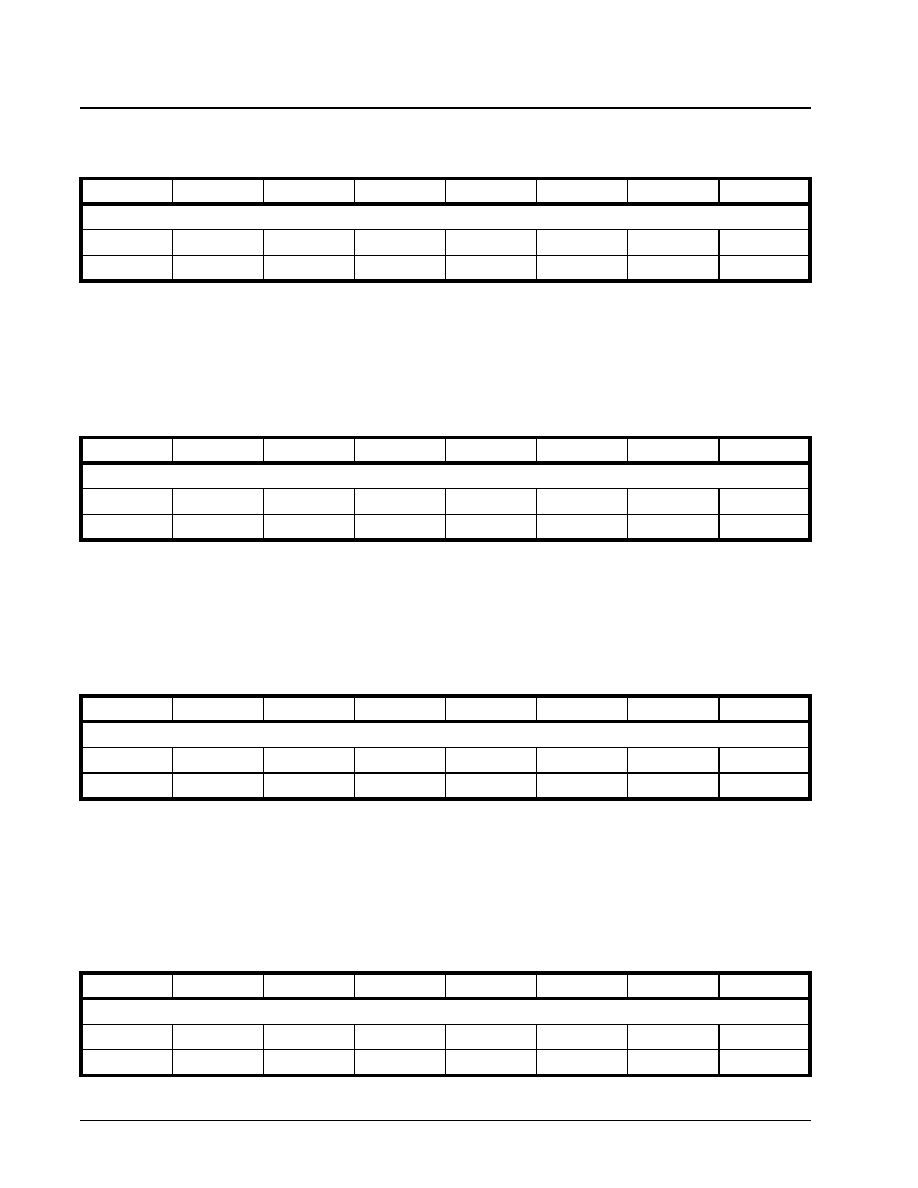

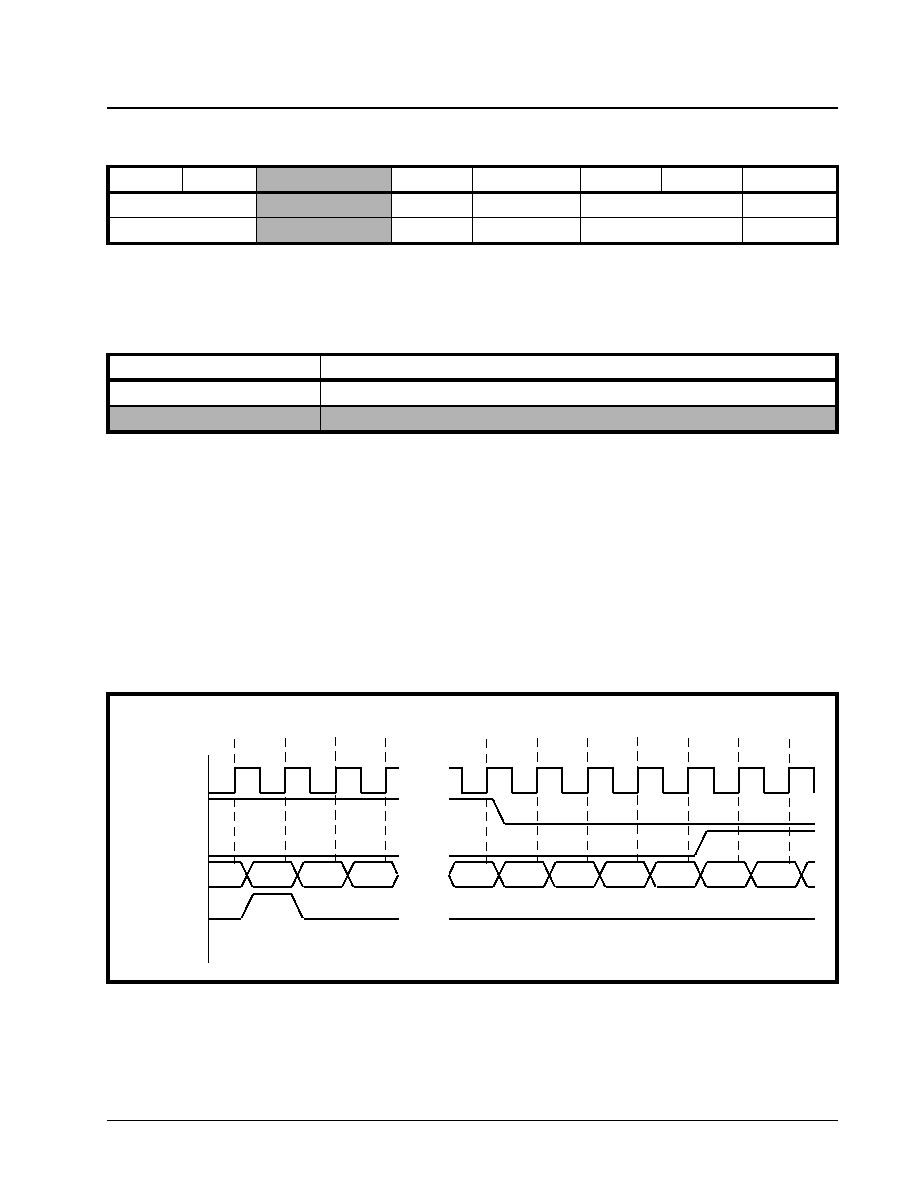

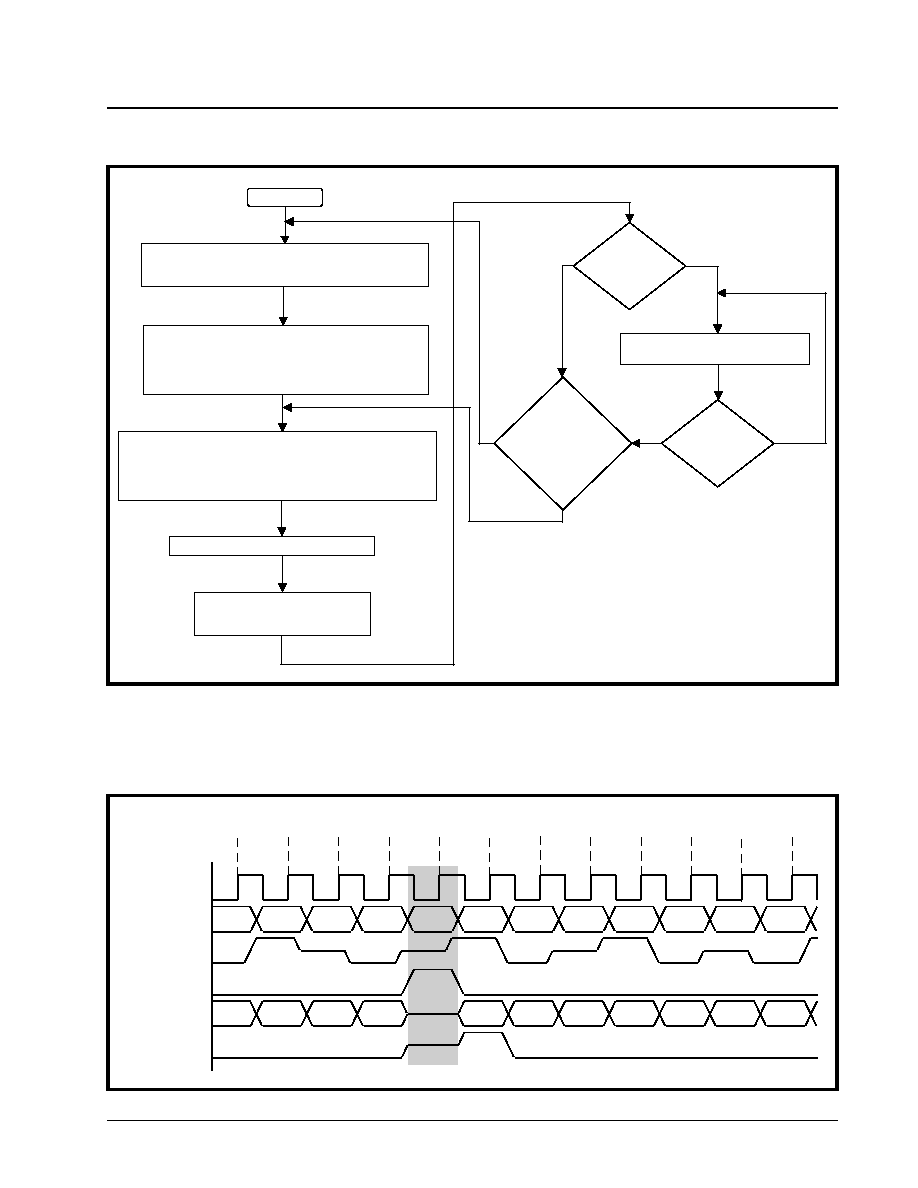

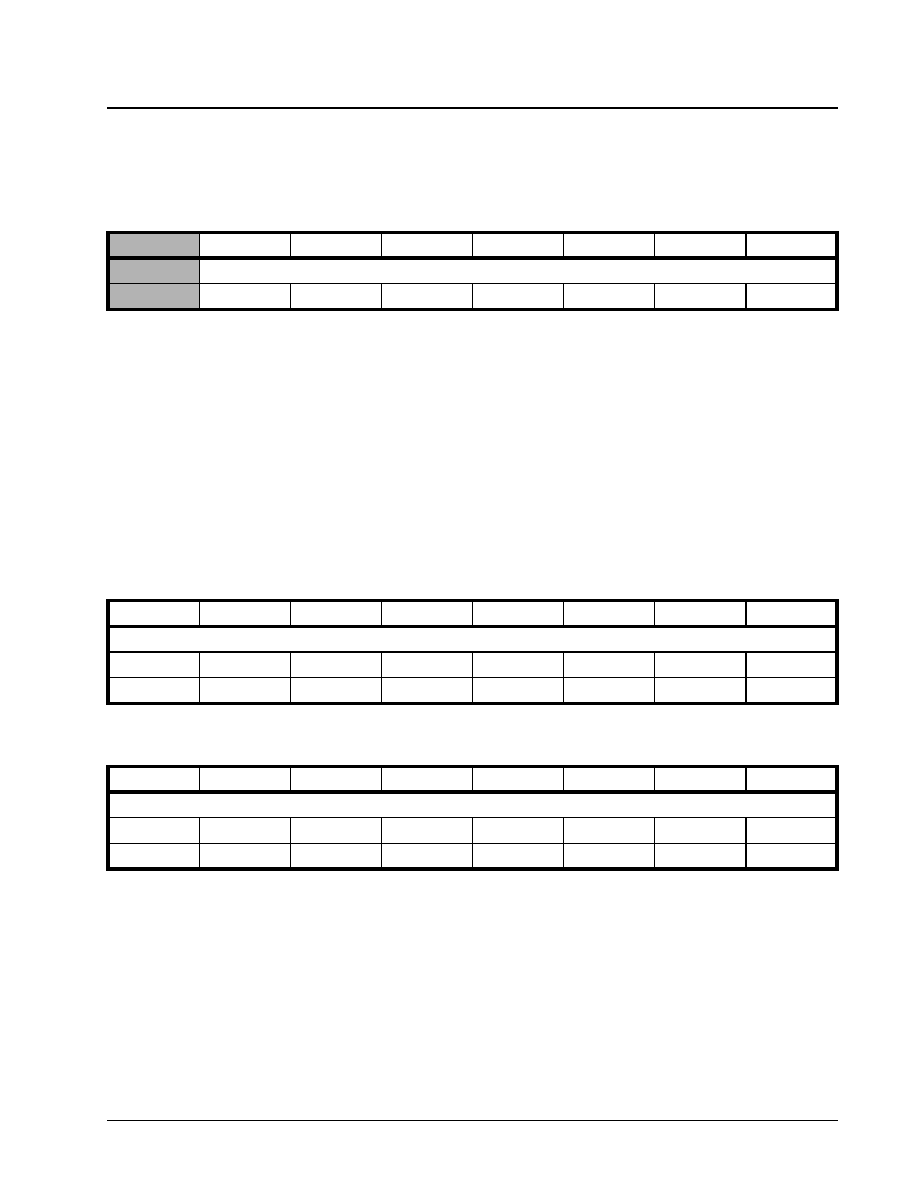

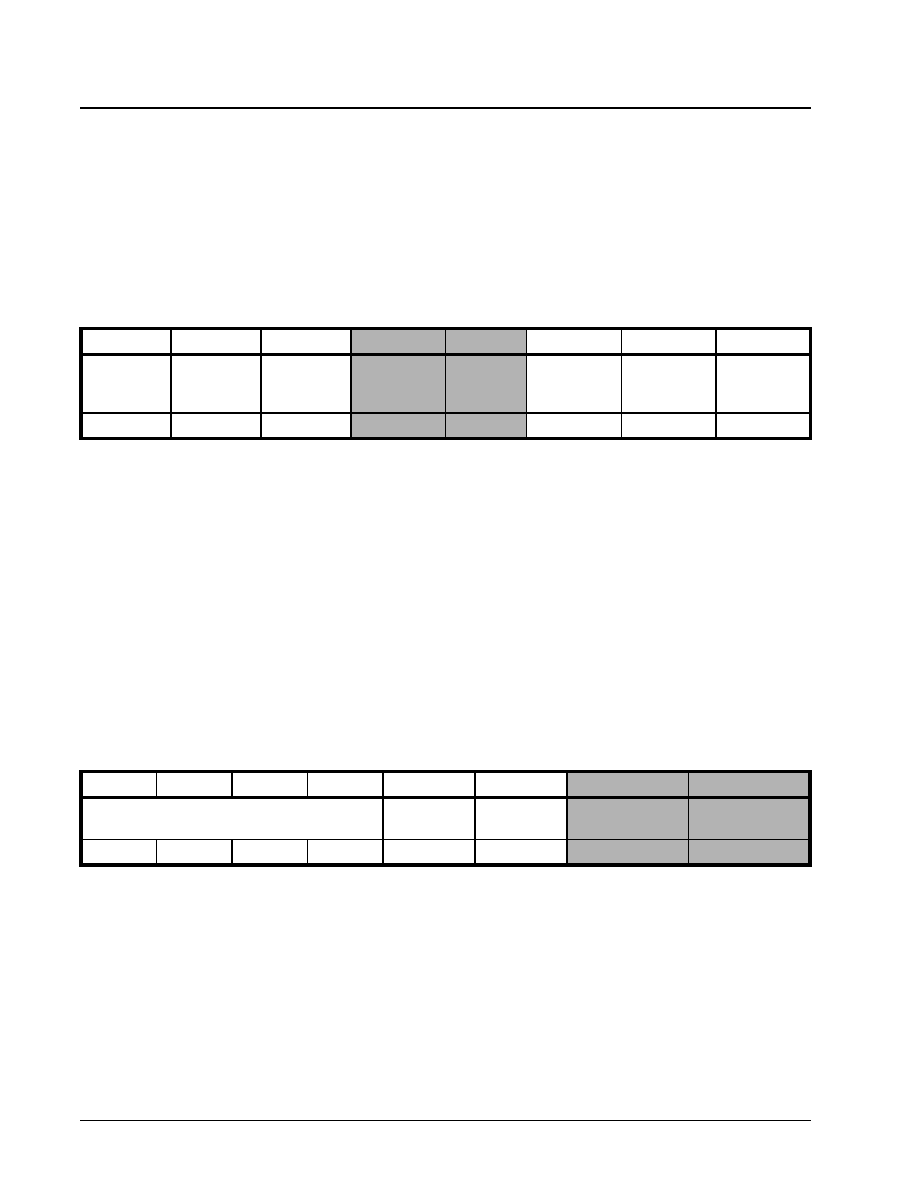

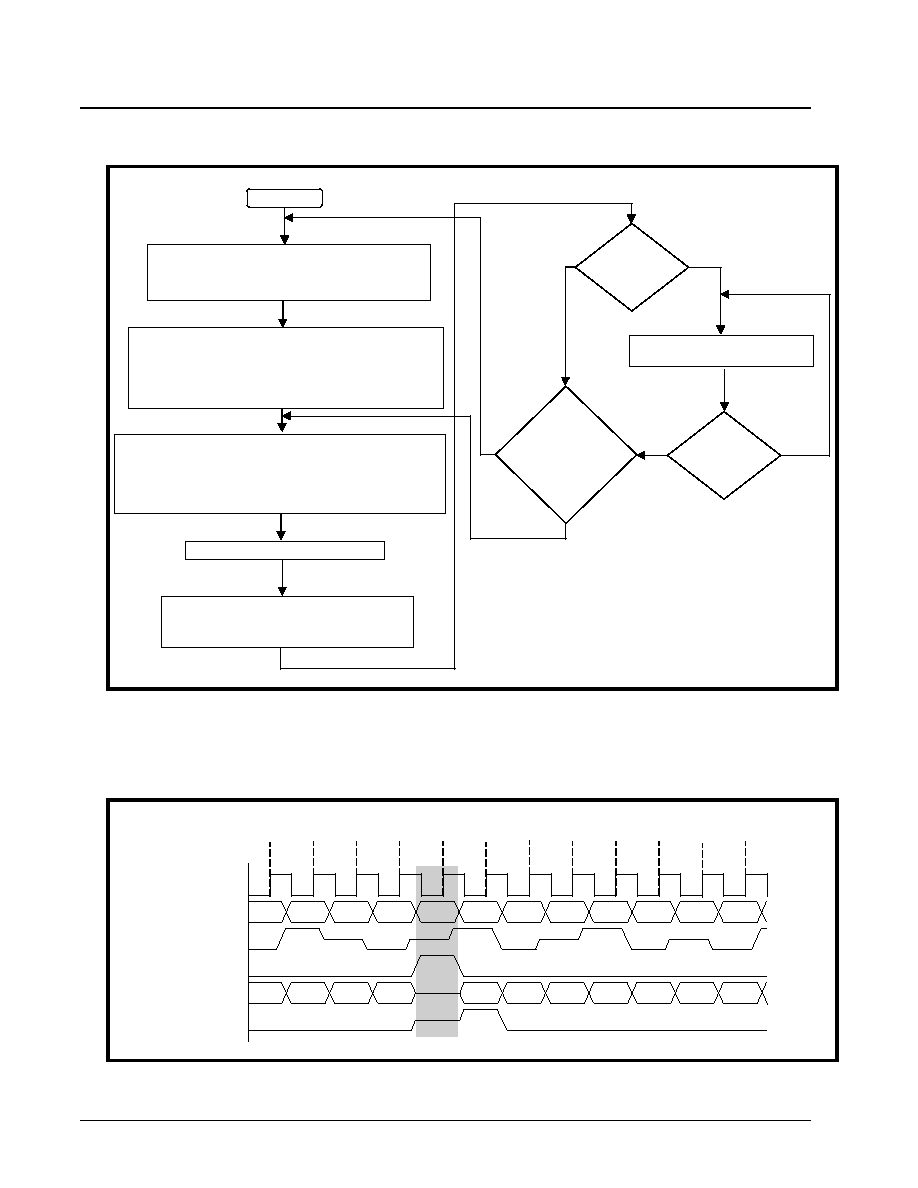

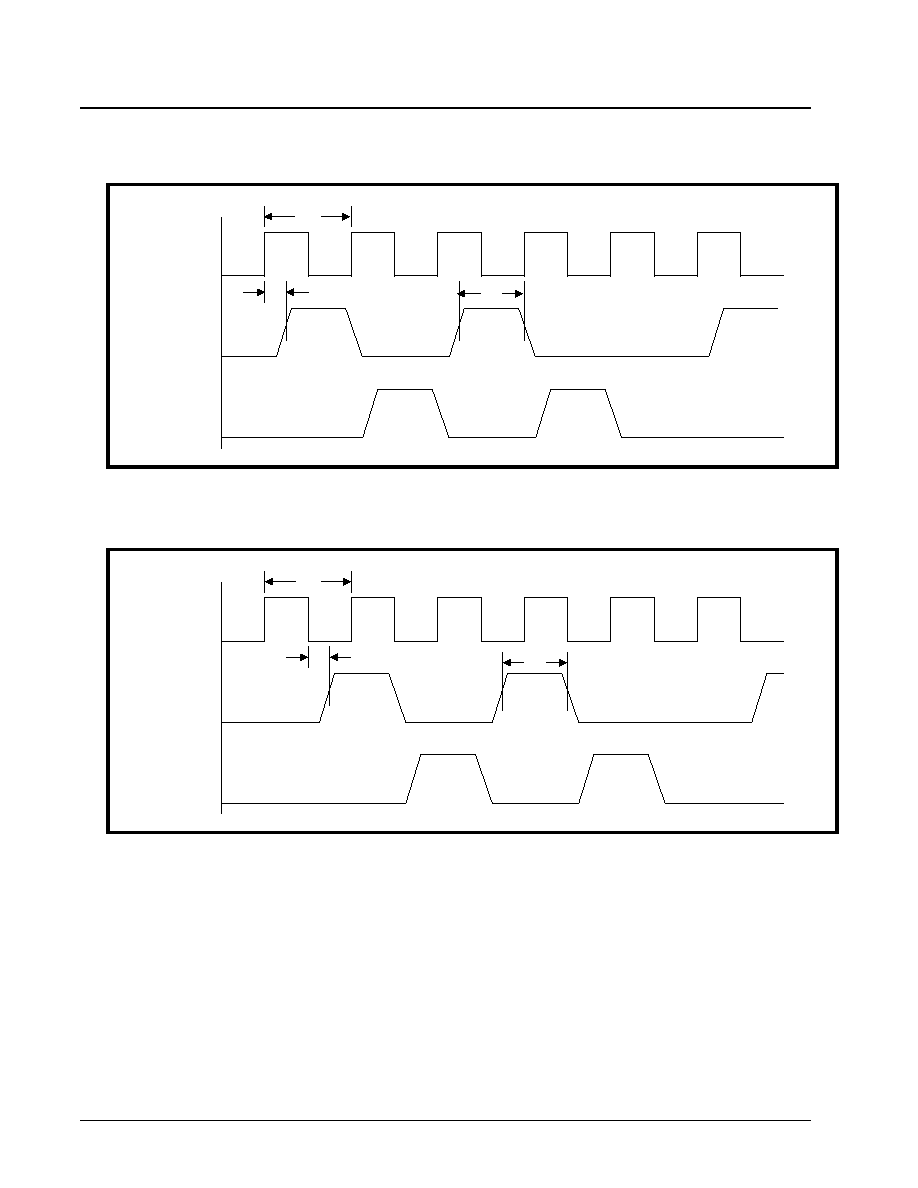

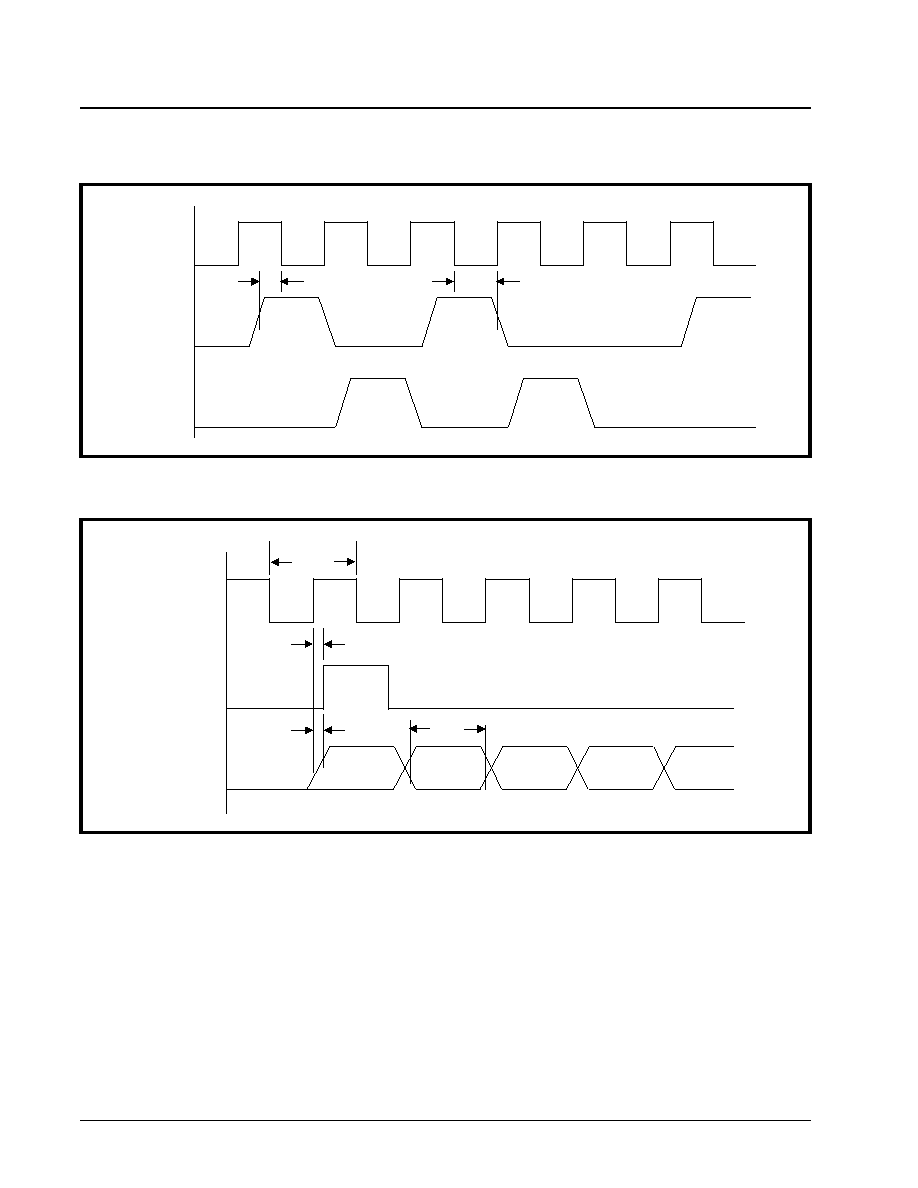

- Figure 12. Behavior of the Microprocessor Interface Signals, during the çInitialé Read Operation ...

- Figure 13. Behavior of the Microprocessor Interface Signals, during subsequent çReadé Operations ...

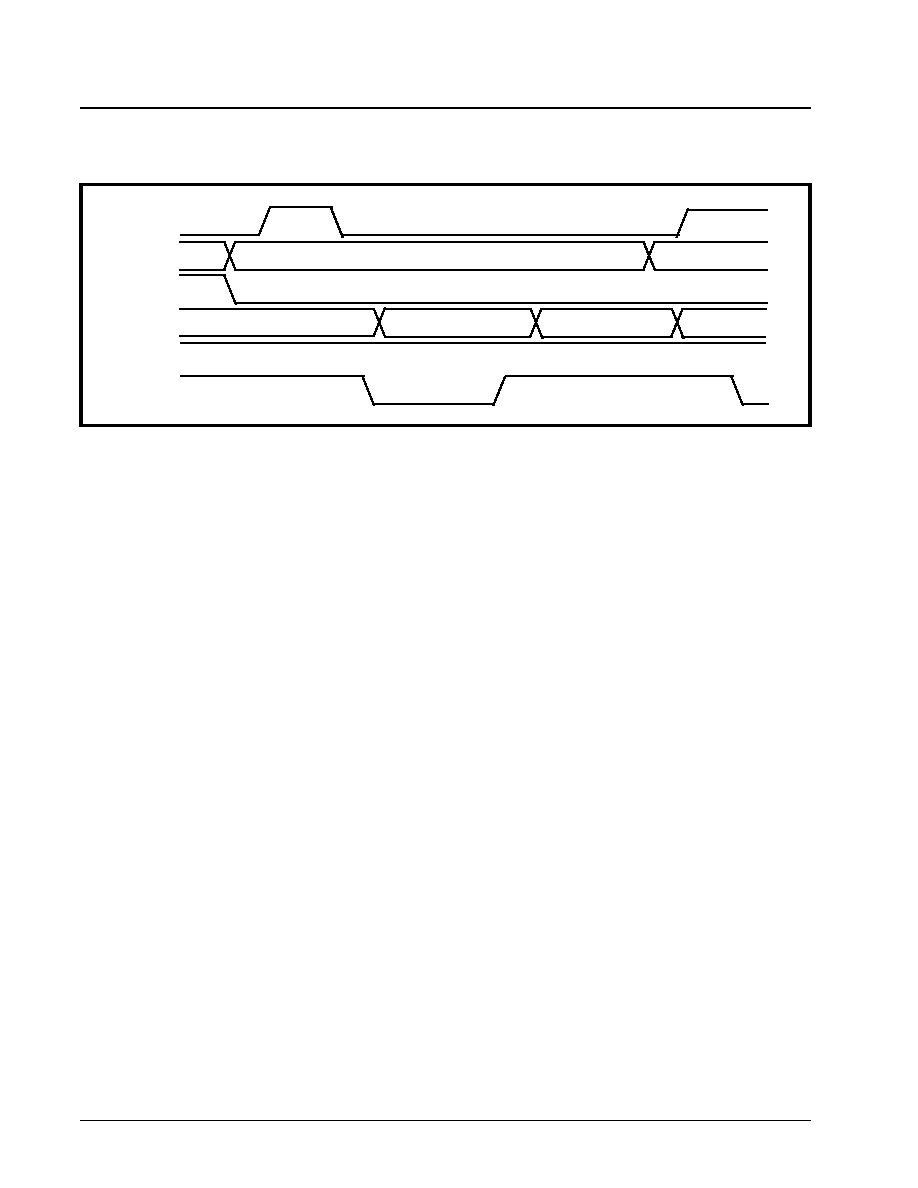

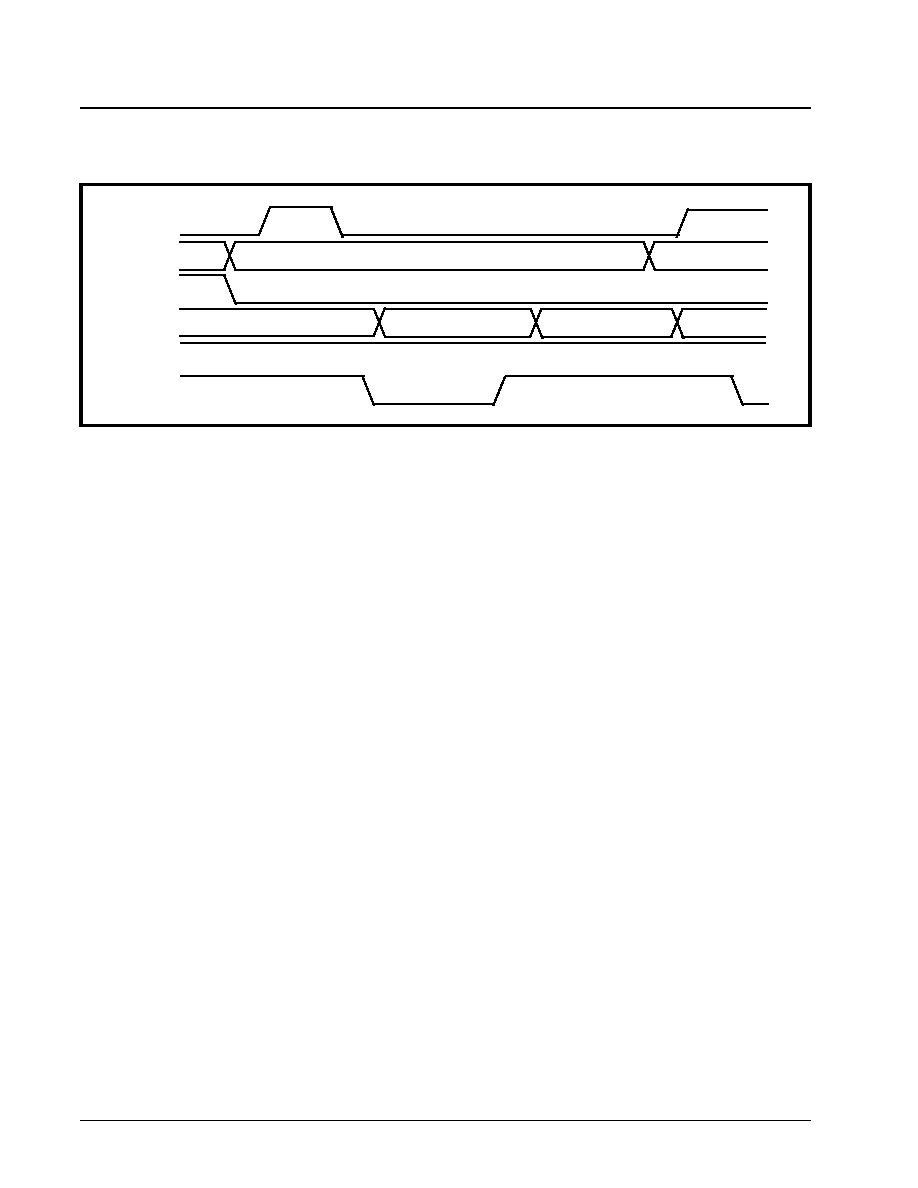

- Figure 14. Behavior of the Microprocessor Interface signals, during the çInitialé Write Operation...

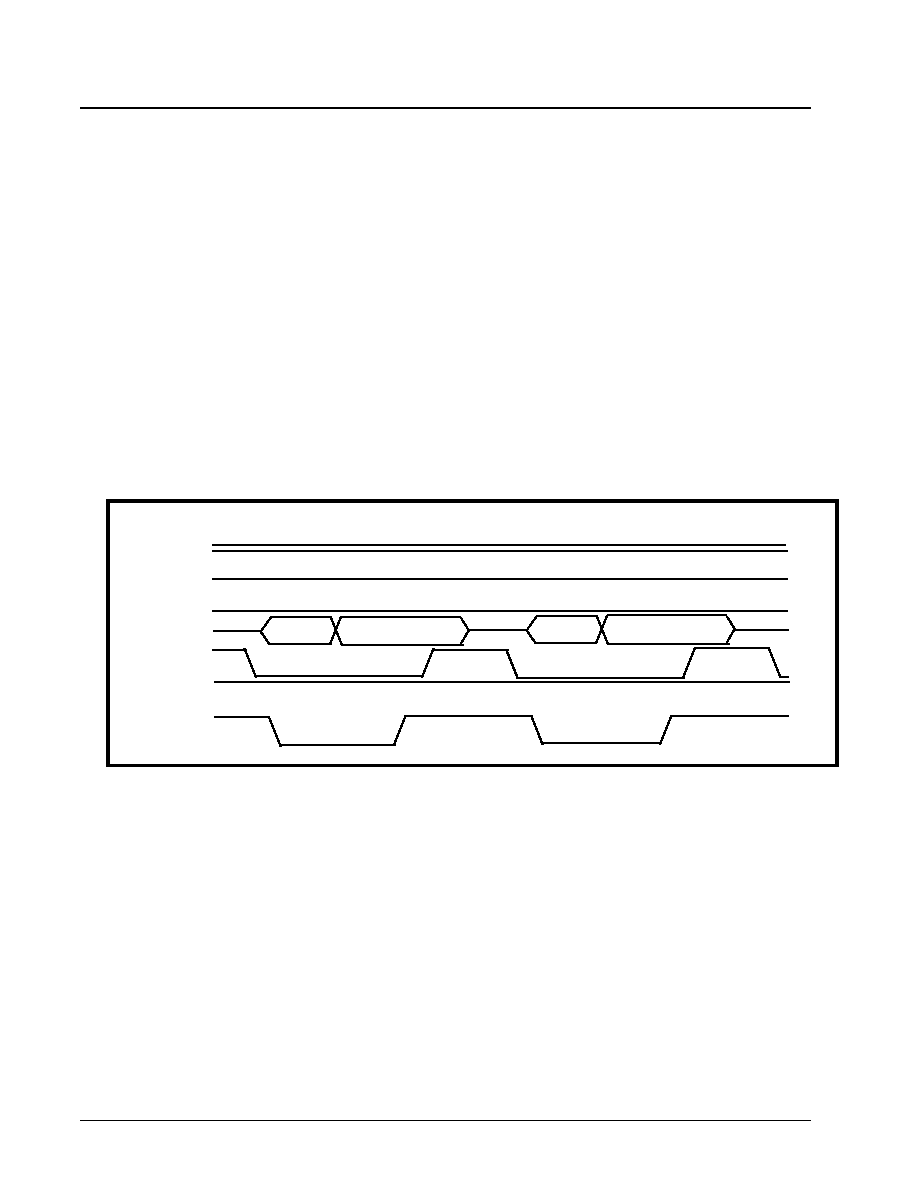

- Figure 15. Behavior of the Microprocessor Interface Signals, during subsequent çWriteé �Operation...

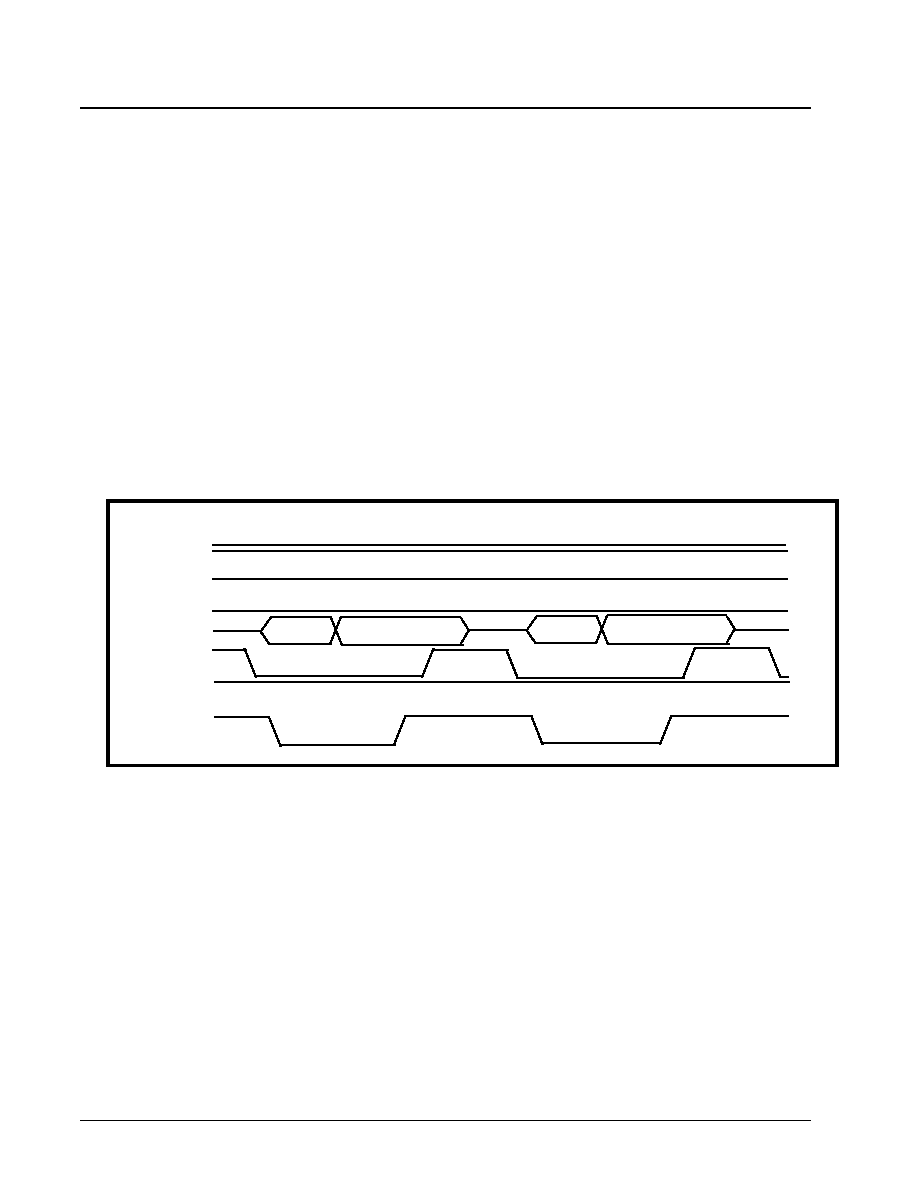

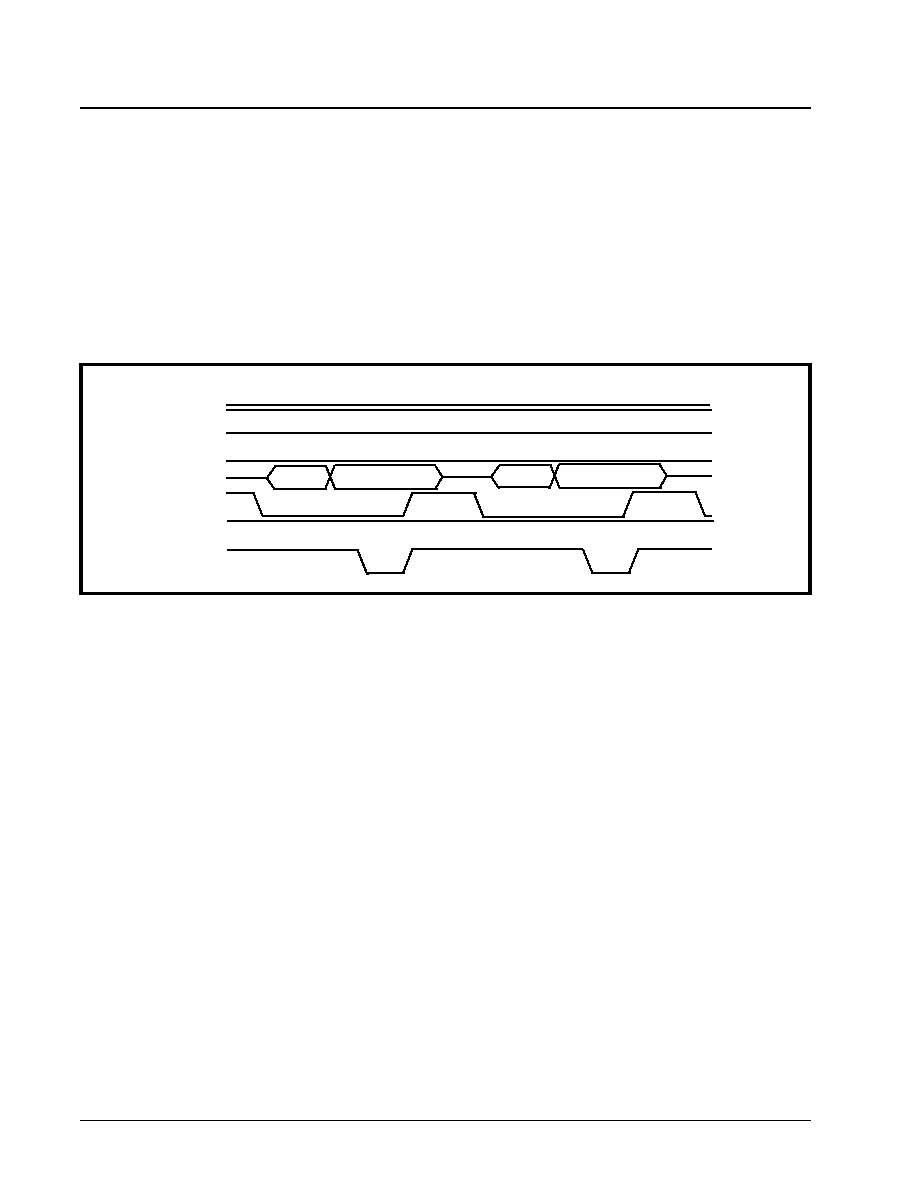

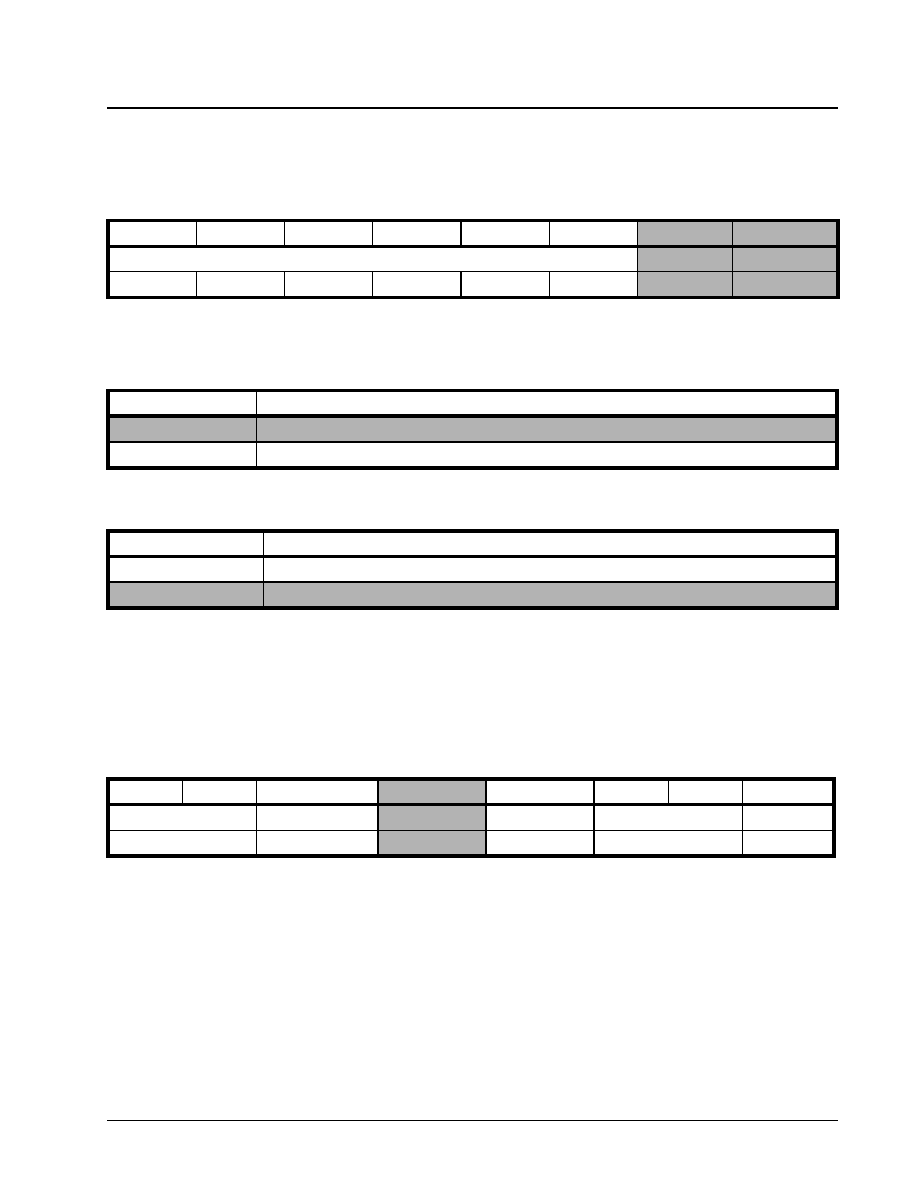

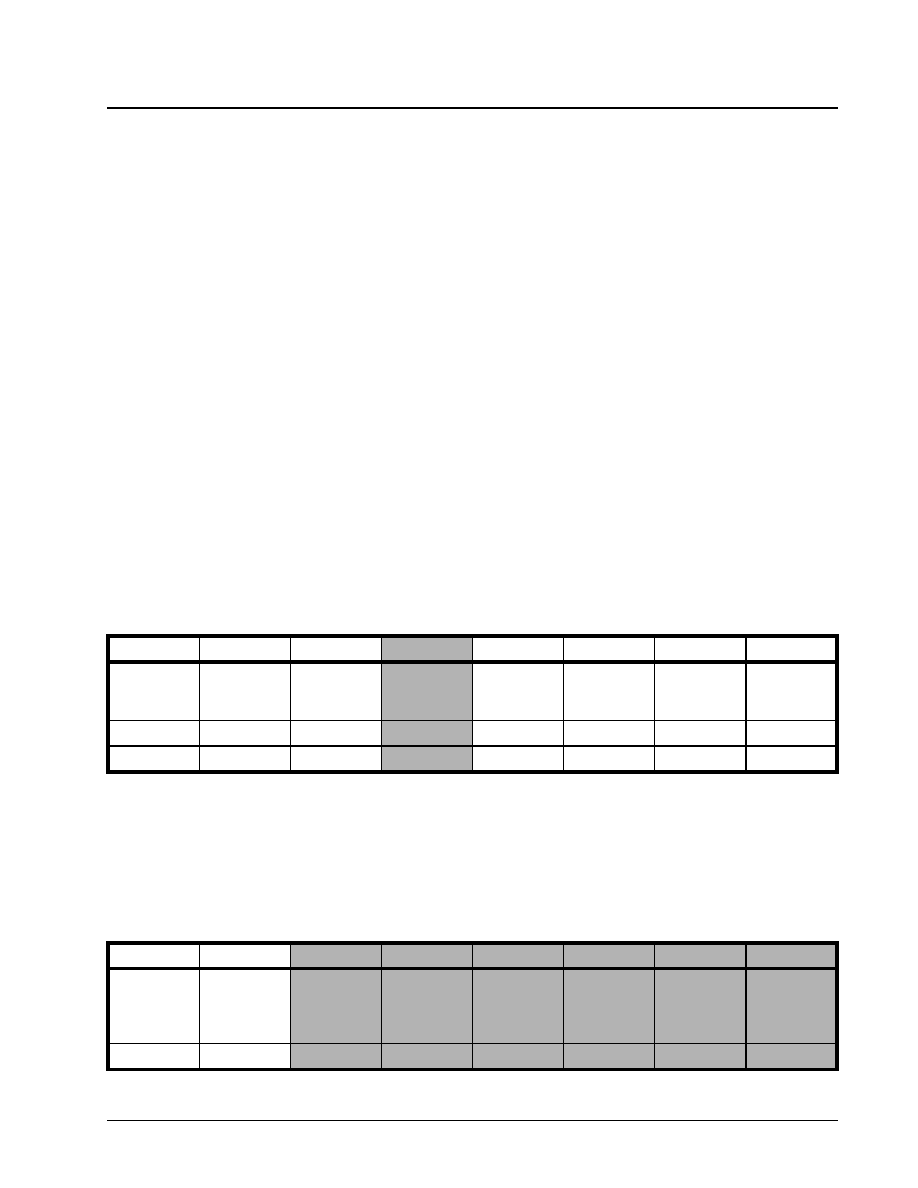

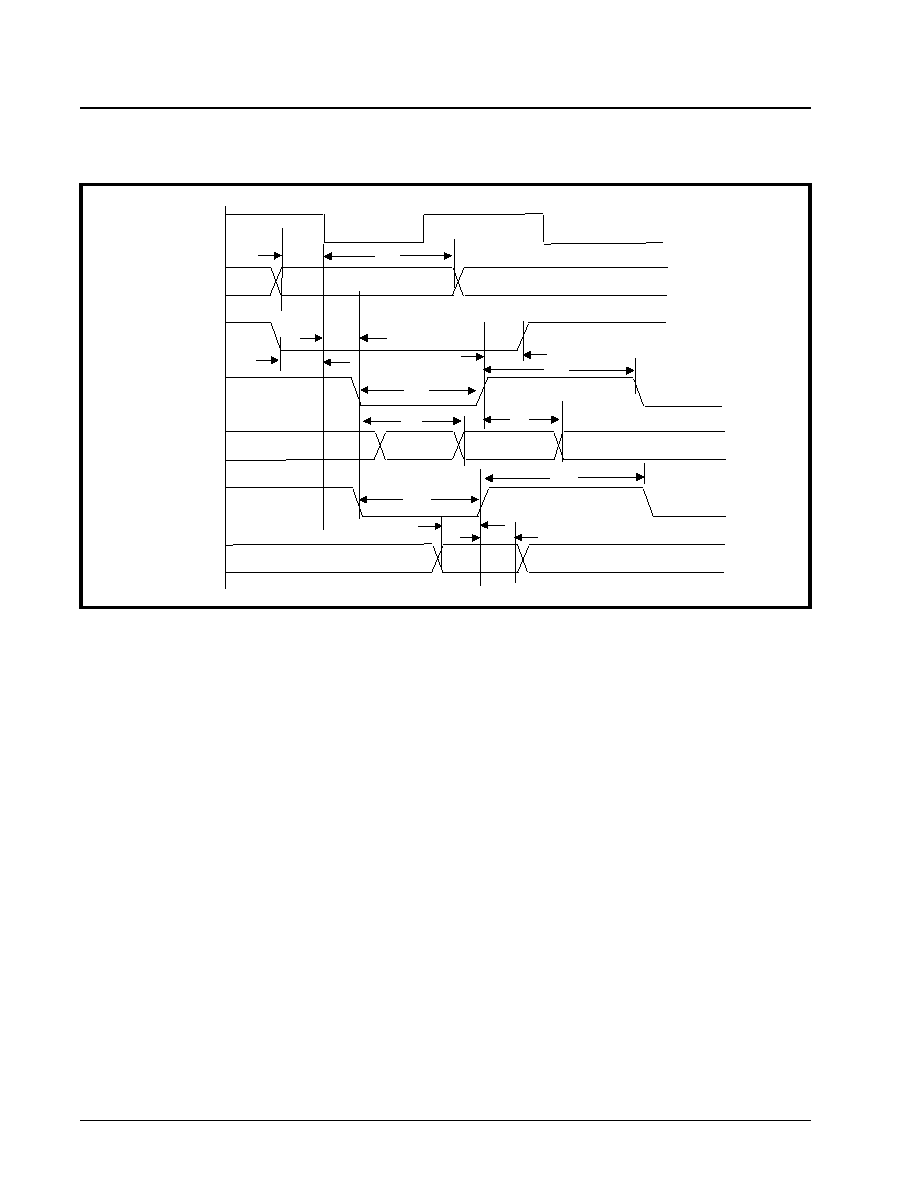

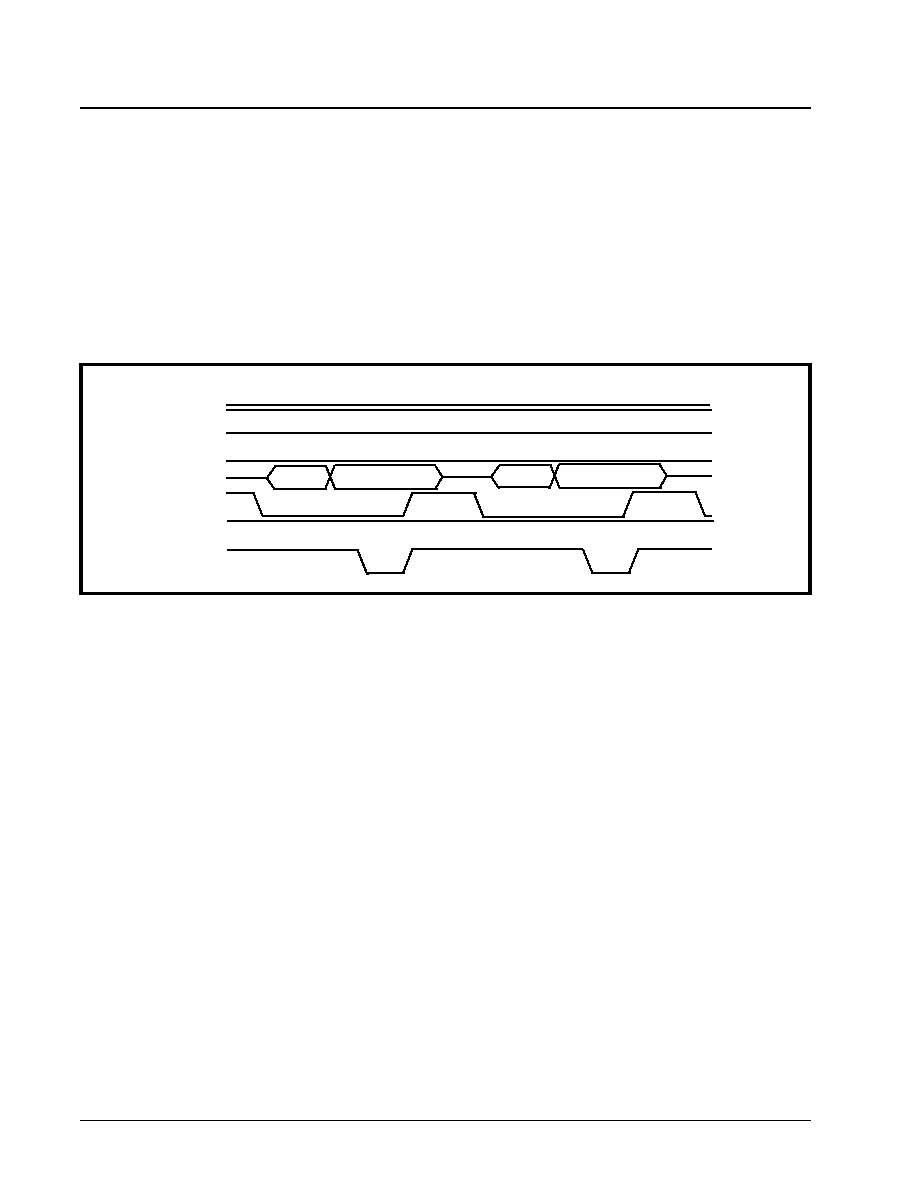

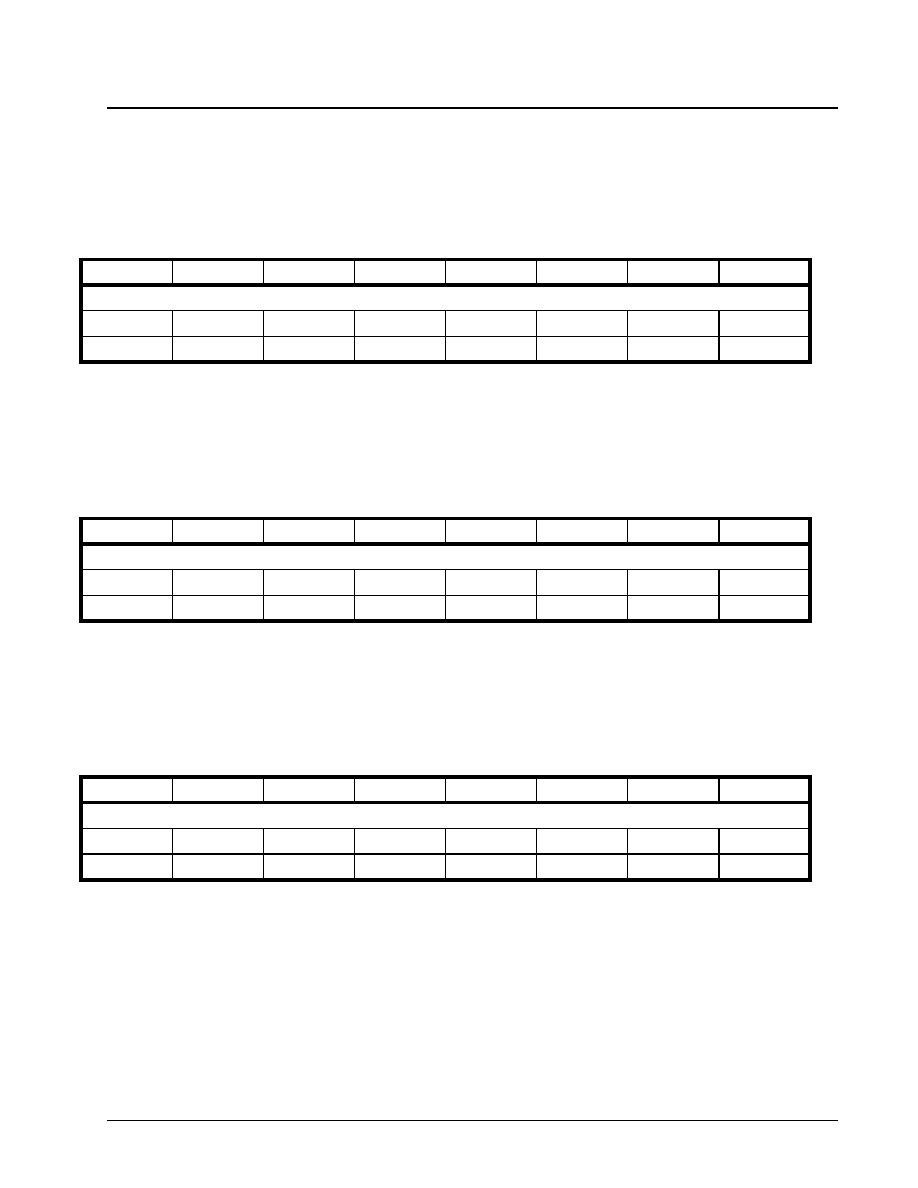

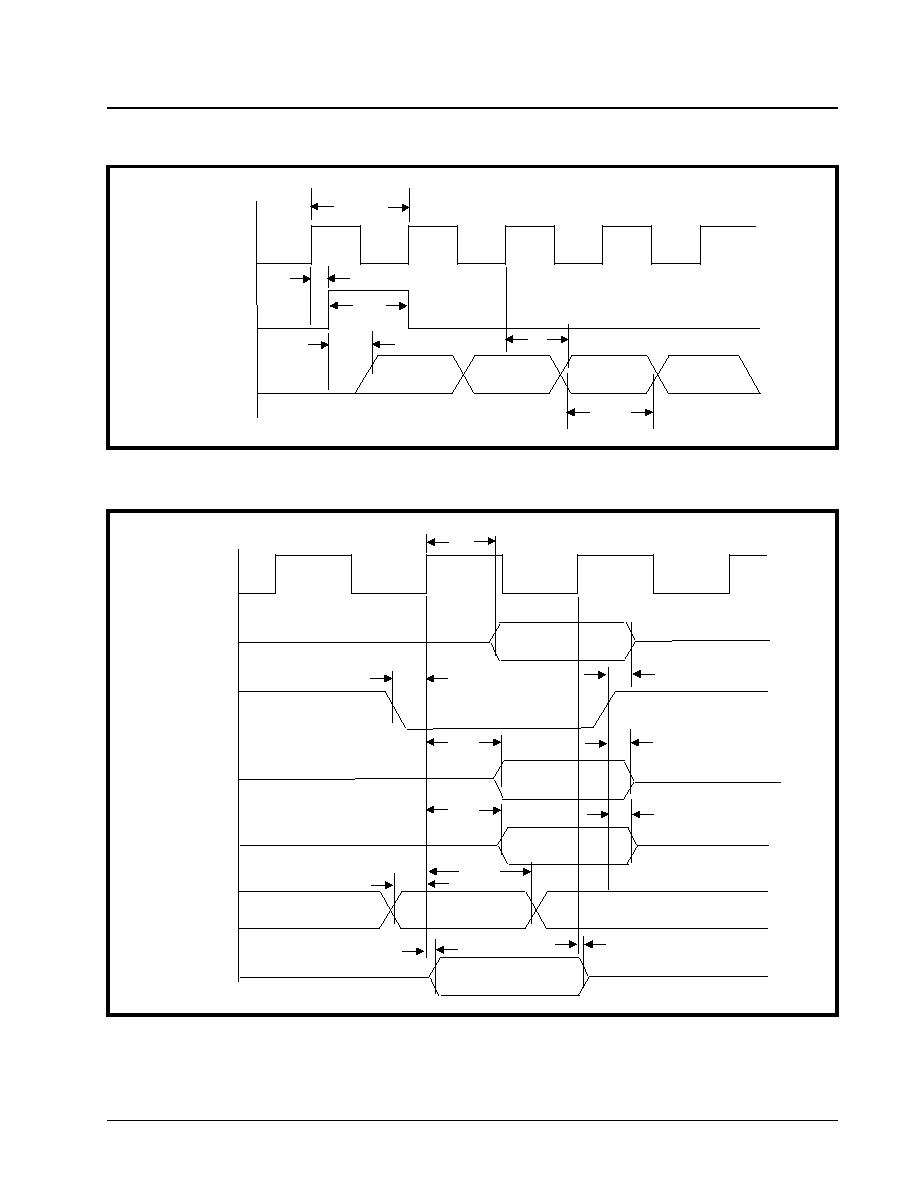

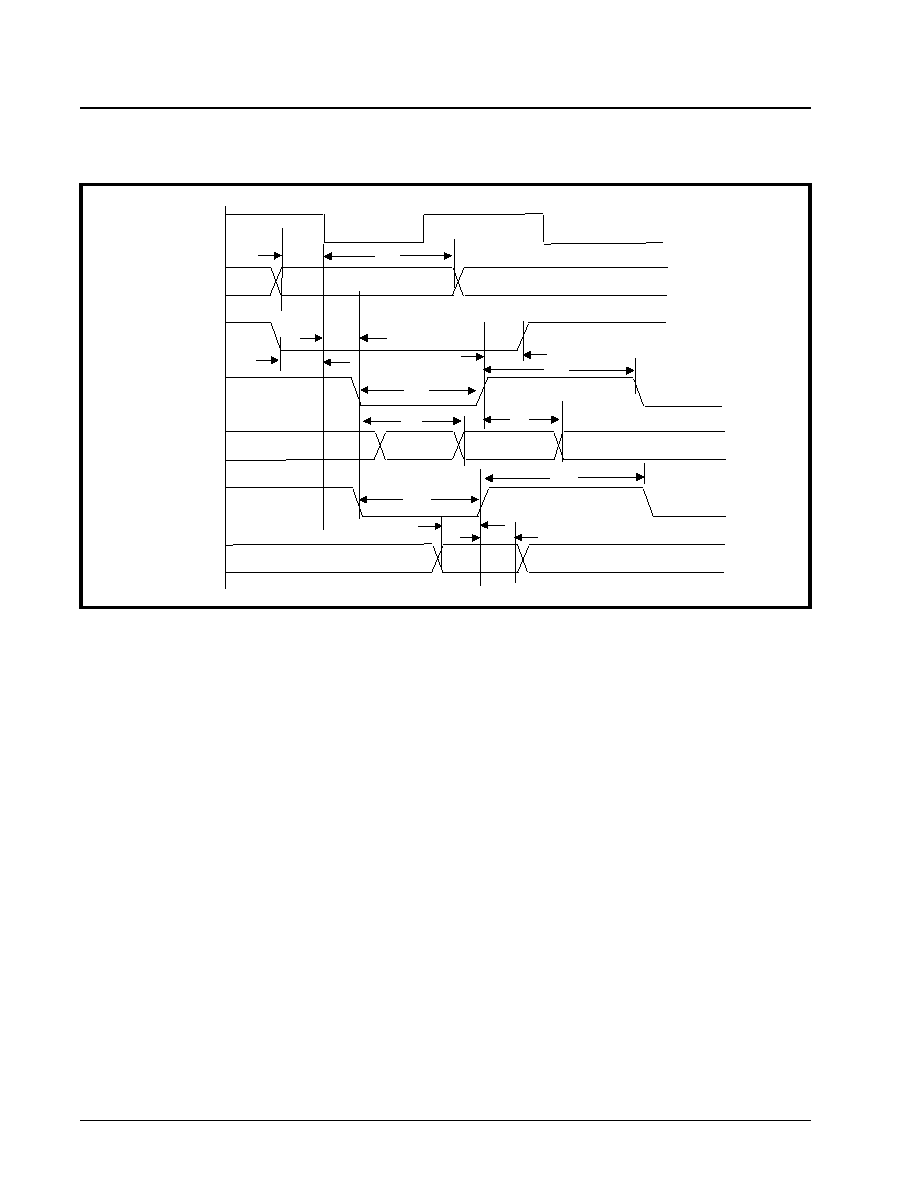

- Figure 16. Behavior of the Microprocessor Interface Signals, during the çInitialé Read Operation ...

- Figure 17. Behavior the Microprocessor Interface Signals, during subsequent çReadé Operations wit...

- Figure 18. Behavior of the Microprocessor Interface signals, during the çInitialé Write Operation...

- Figure 19. Behavior of the Microprocessor Interface Signals, during subsequent çWriteé �Operation...

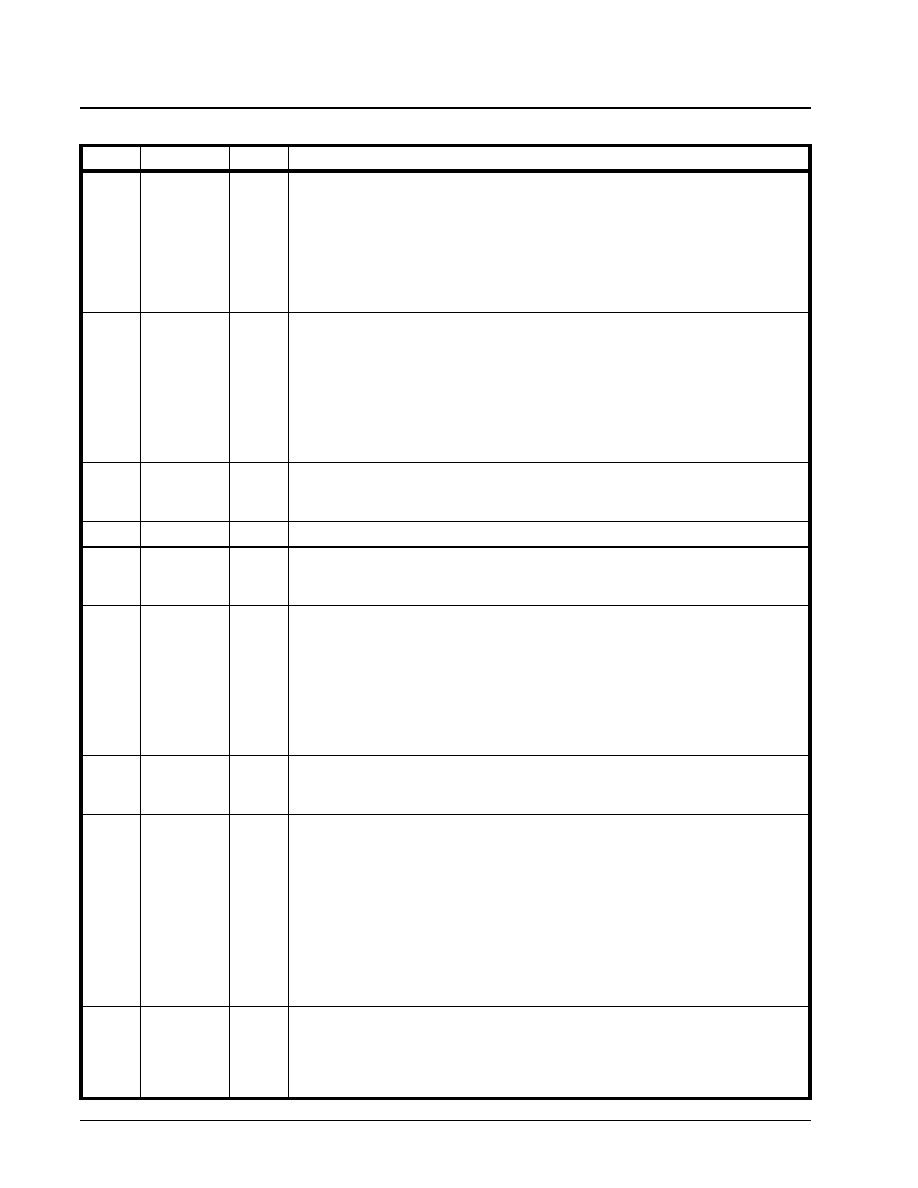

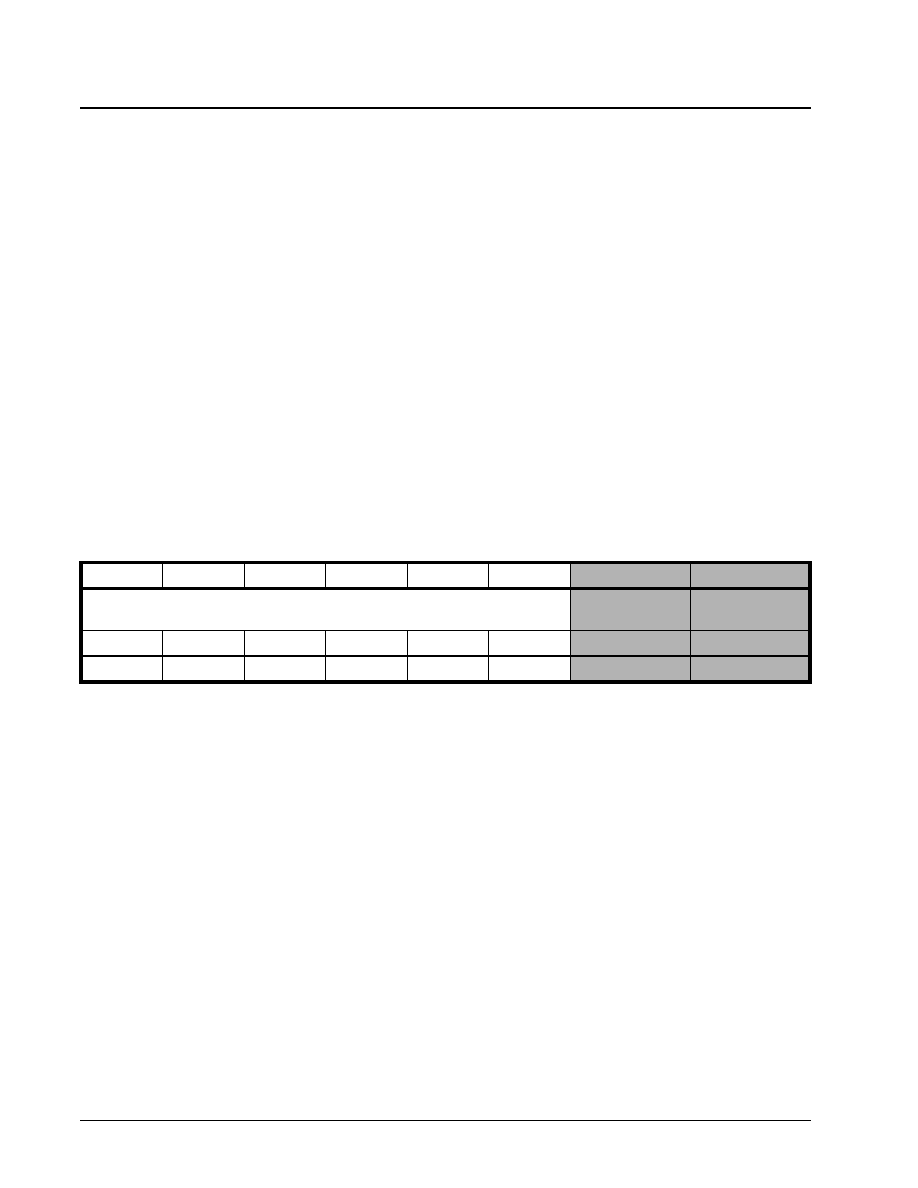

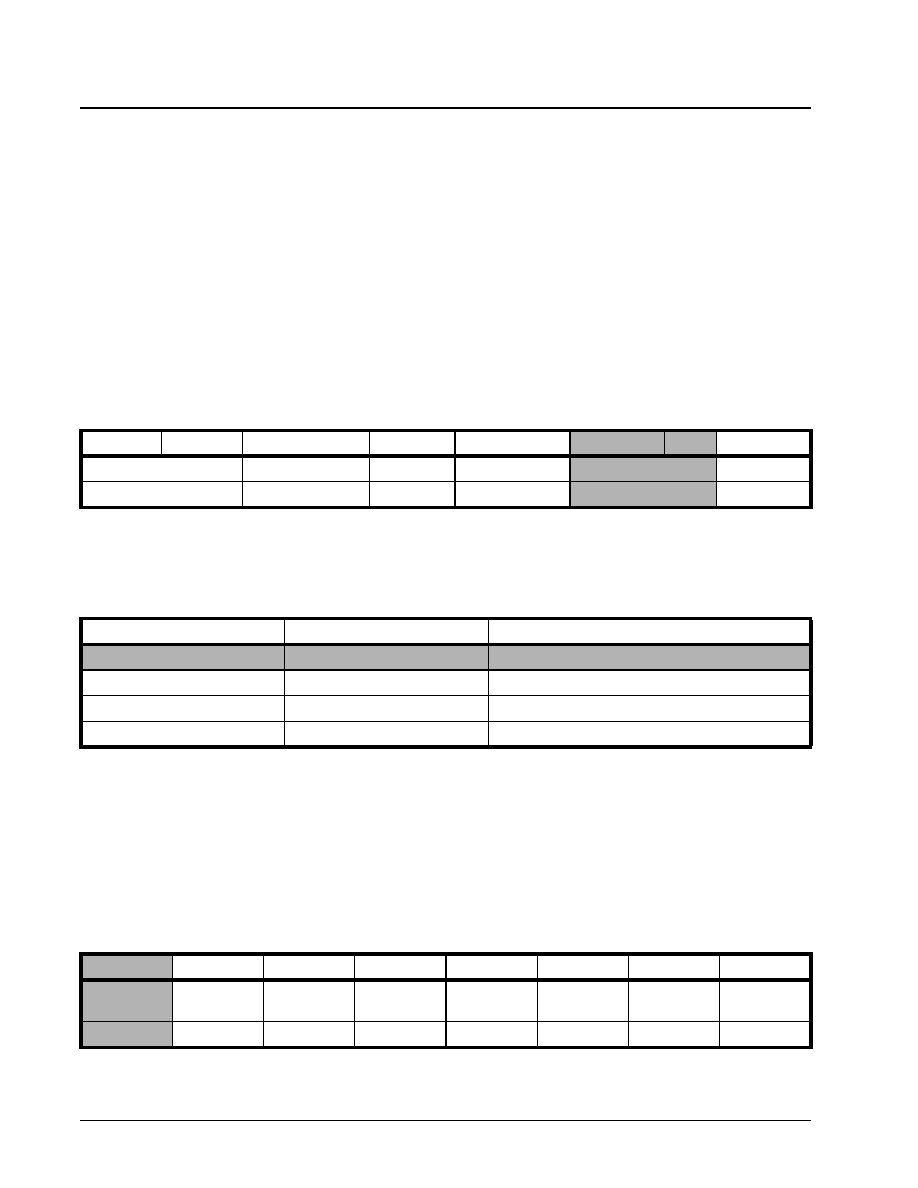

- 3.3 On-Chip Register Organization

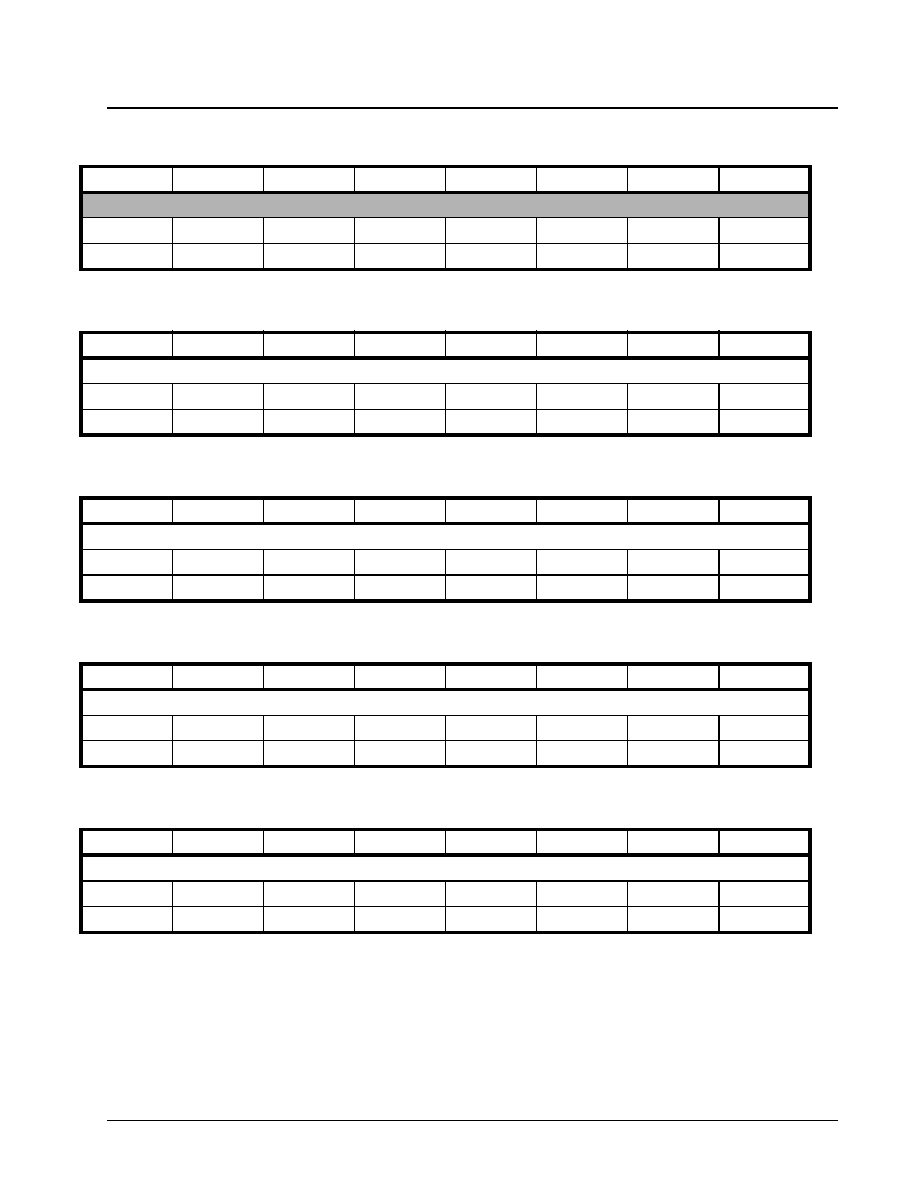

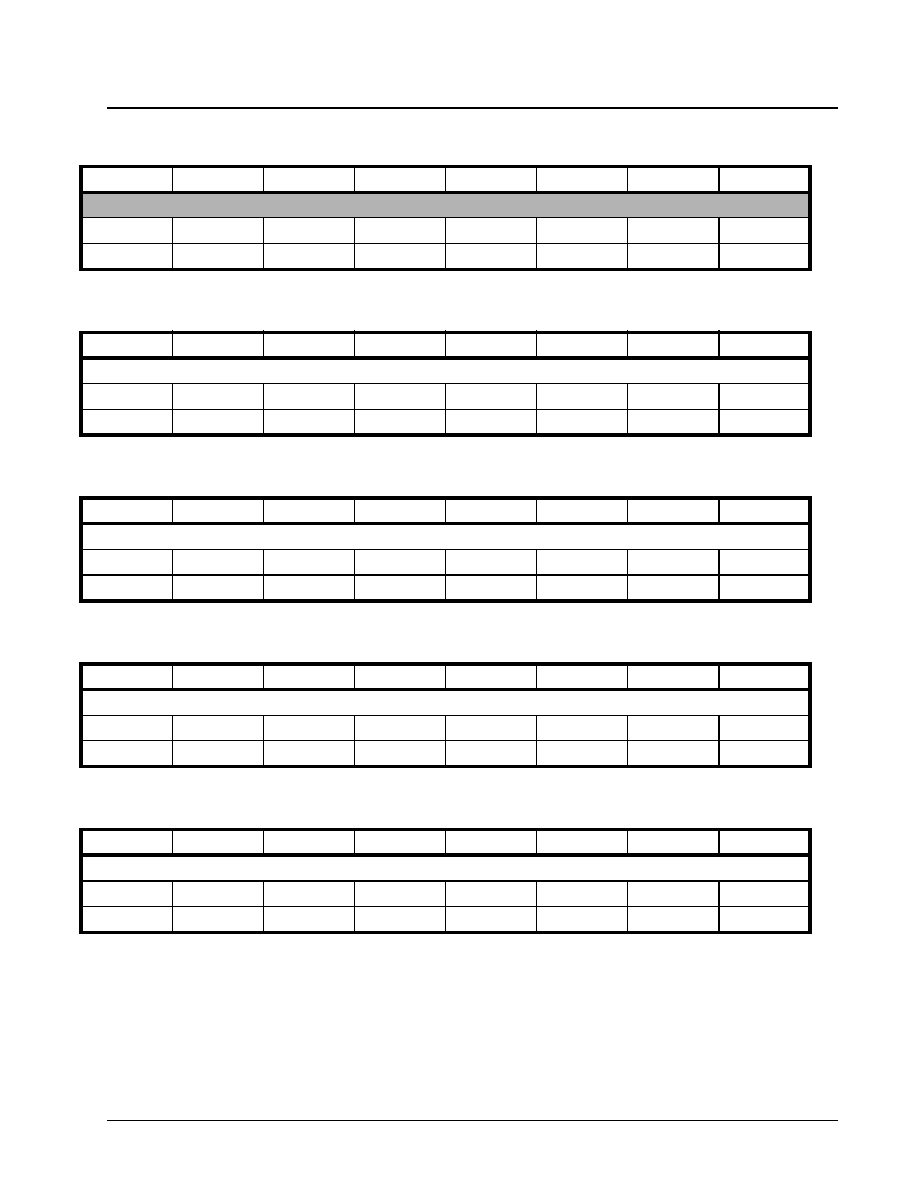

- Address = 00h, UNI Operating Mode Register

- Bit 7ÑLine Loop Back Mode

- Bit 6ÑCell Loop Back Mode

- Bit 5ÑPLCP Loop Back Mode

- Bit 4ÑReset

- Bit 3ÑDirect Mapped ATM/PLCP Mode* Selection

- Bit 2ÑM13/C-Bit* (DS3 Frame Format) Selection

- Bits 1, 0ÑTimRefSel[1, 0] (Timing Reference �SelectÑTransmit PLCP Processor and Transmit DS3 Framer)

- Address = 01h, UNI I/O Control Register

- Bit 7ÑLOC (Loss of Clock)Enable

- Bit 6ÑTest PMON

- Bit 5ÑInt En Reset (Automatic Reset of Interrupt Enable Bits) Select

- Bit 4ÑAMI/B3ZS* (Line Code)

- Bit 3ÑUnipolar/Bipolar* (Line Code)

- Bit 2ÑTxLineClk Inv

- Bit 1ÑRxLineClk Inv

- Bit 0ÑReframe (Receive DS3 Framer)

- Address = 02h, Part Number Register

- Address = 03h, Version Number Register

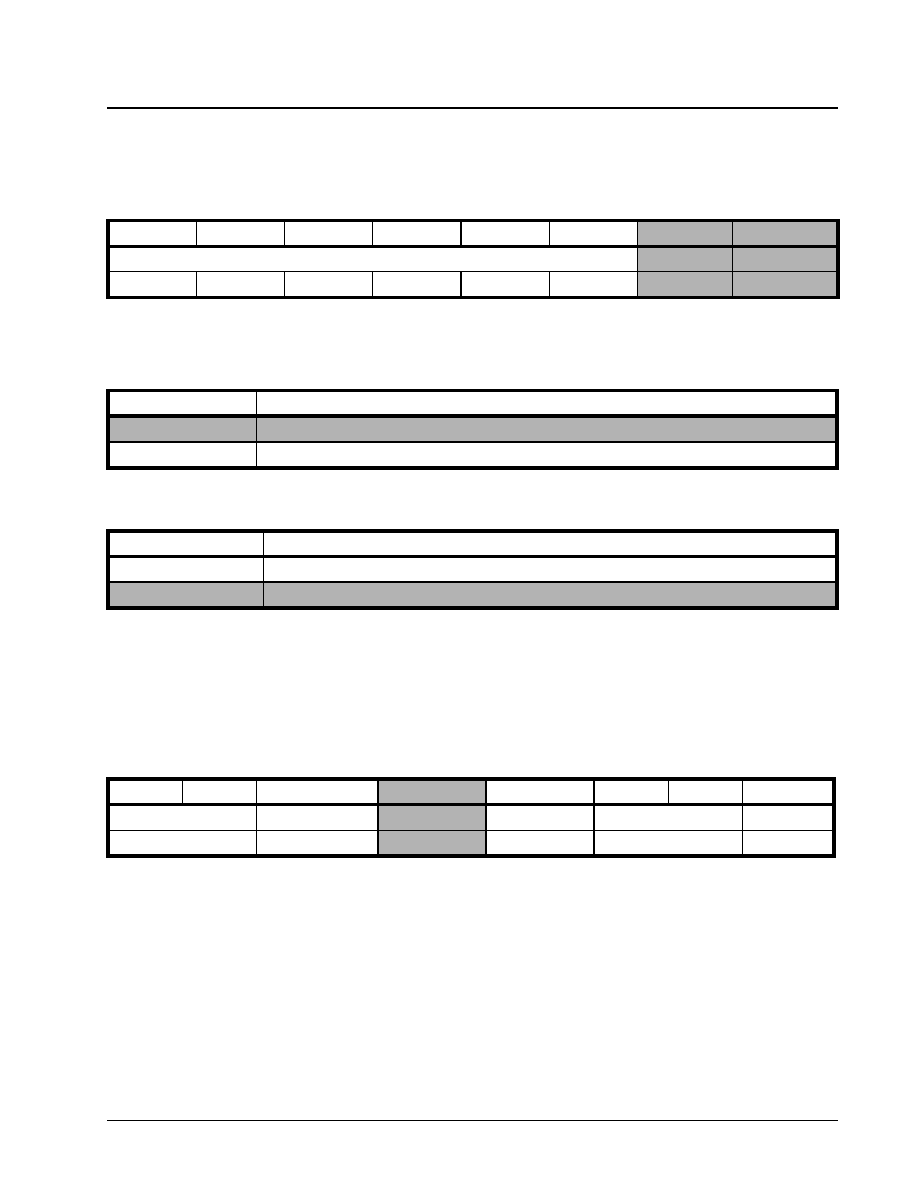

- Address = 04h, UNI Interrupt Enable Register

- Bit 7ÑRx DS3 Interrupt Enable

- Bit 6ÑRx PLCP Interrupt Enable

- Bit 5ÑRx CP Interrupt Enable

- Bit 4ÑRx UTOPIA Interrupt Enable

- Bit 3ÑTx UTOPIA Interrupt Enable

- Bit 2ÑTx CP Interrupt Enable

- Bit 1ÑTx DS3 Framer Interrupt Enable

- Bit 0ÑOne Second Interrupt Enable

- Address = 05h, UNI Interrupt Status Register

- Bit 7ÑRx DS3 (Framer) Interrupt Status

- Bit 6ÑRx PLCP Interrupt Status

- Bit 5ÑRx CP (Cell Processor) Interrupt Status

- Bit 4ÑRx UTOPIA Interrupt Status

- Bit 3ÑTx UTOPIA Interrupt Status

- Bit 2ÑTx CP (Cell Processor) Interrupt Status

- Bit 1ÑTx DS3 (Framer) Interrupt Status

- Bit 0ÑOne Second Interrupt Status

- Address = 06h, Test Cell Control and Status Register

- Bit 4ÑTest Cell (Generator/Receiver) Enable

- Bit 3ÑLine*/System (Side Testing)

- Bit 2ÑOne Shot Test

- Bit 1ÑOne Shot Done

- Bit 0ÑPRBS (Pseudo-Random Byte Sequence) Lock

- Address = 07h, Future Use

- Address = 08h, Test Cell Header Byte-1

- Address = 09h, Test Cell Header Byte-2

- Address = 0Ah, Test Cell Header Byte-3

- Address = 0Bh, Test Cell Header Byte-4

- Address = 0Ch, Test Cell Error AccumulatorÑMSB

- Address = 0Dh, Test Cell Error AccumulatorÑLSB

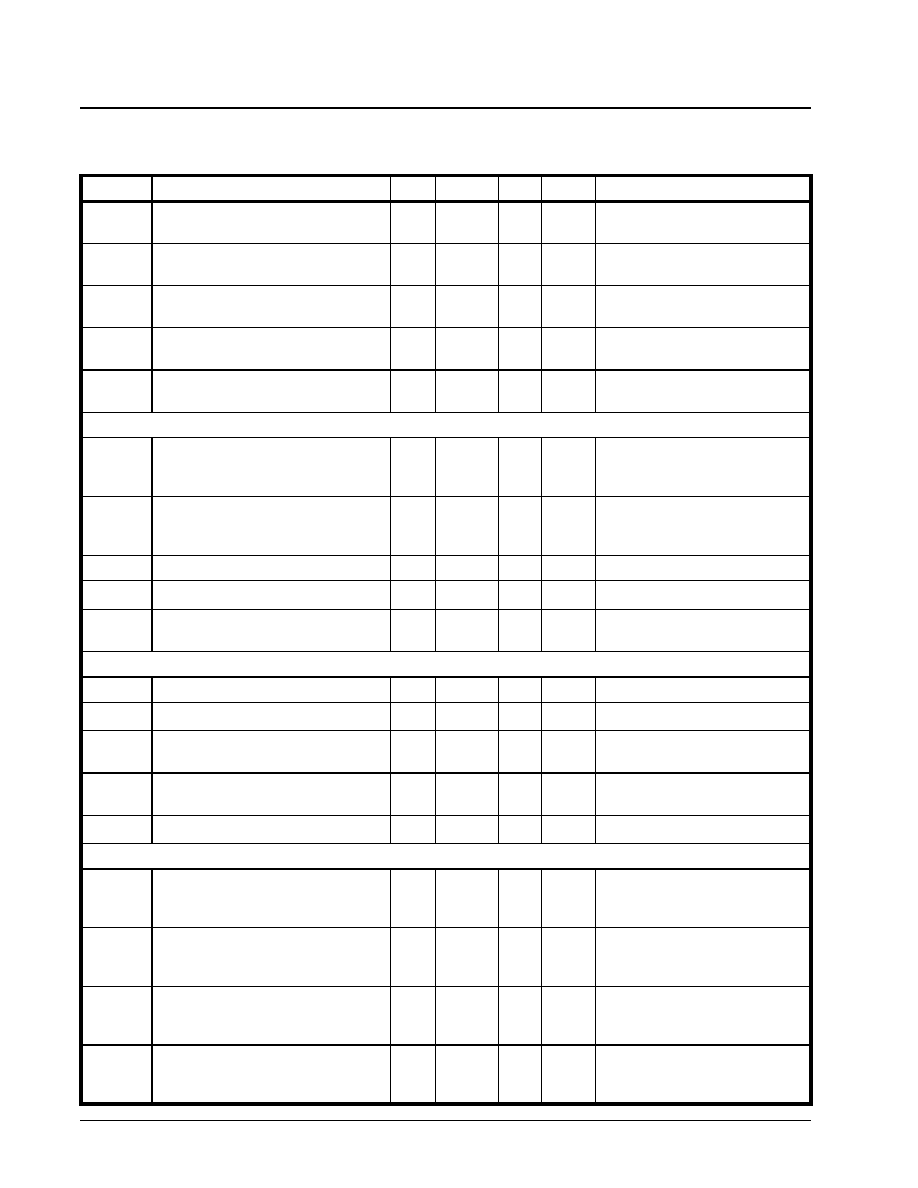

- Address = 0Eh, Rx DS3 Configuration and Status Register

- Bit 7ÑRxAISÑReceive AIS Signal

- Bit 6ÑRxLOSÑReceive LOS Condition

- Bit 5ÑRxIdleÑReceive Idle Condition

- Bit 4ÑRxOOFÑOut of Frame Condition

- Bit 3ÑInt (Receive DS3 Framer) LOS Disable

- Bit 2ÑFraming On Parity

- Bit 1ÑFSync Algo

- Bit 0ÑMSync Algo

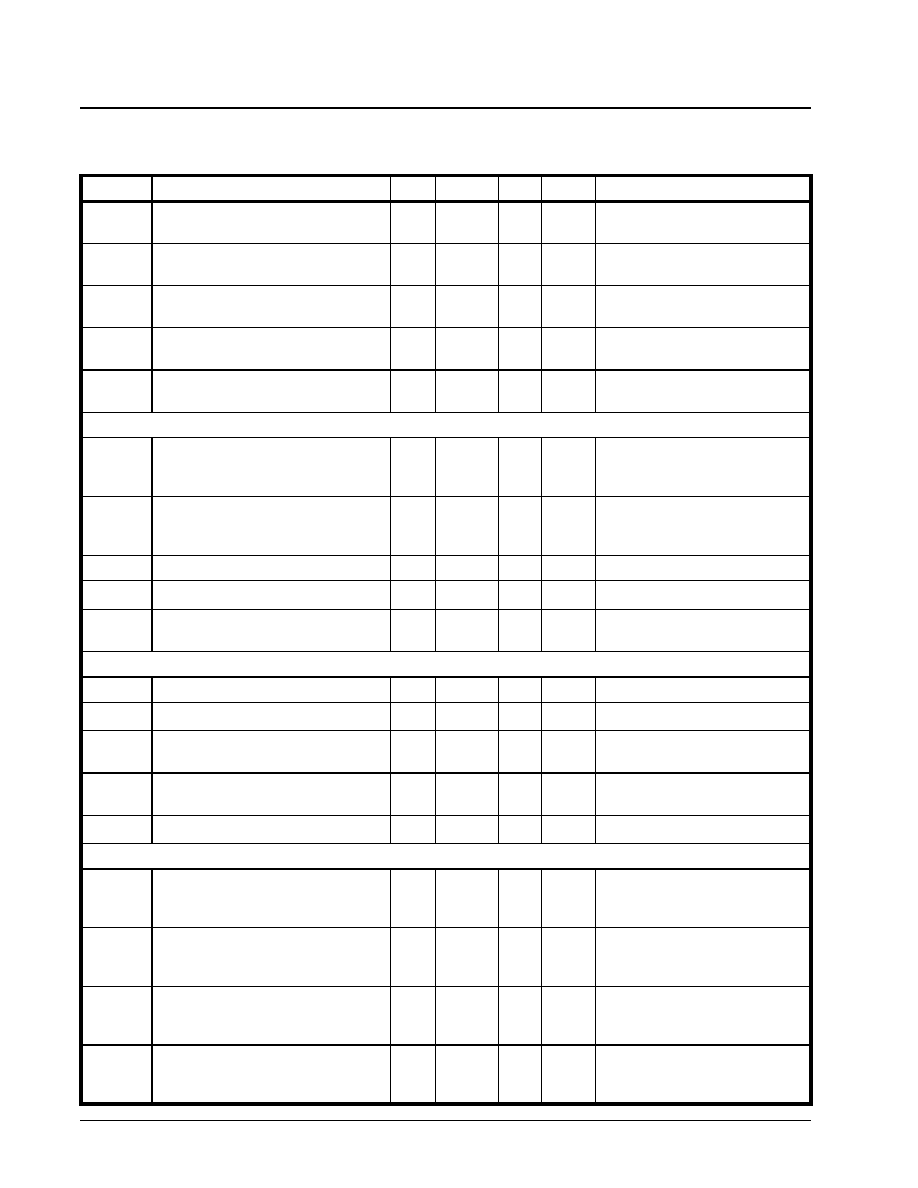

- Address = 0Fh, Rx DS3 Status Register

- Bit 4ÑRxFERF (Far End Receive Failure)

- Bit 3ÑRxAIC

- Bits 2-0 RxFEBE[2:0]

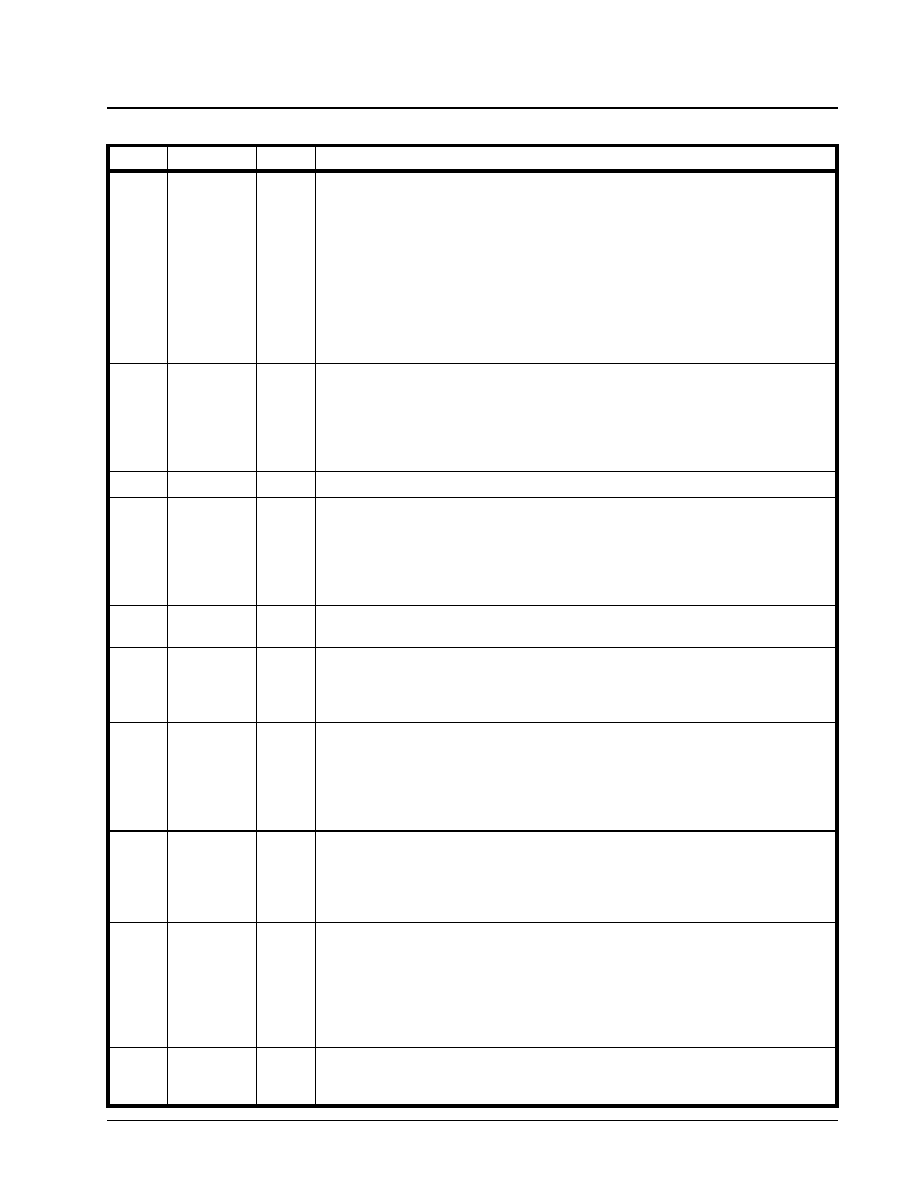

- Address = 10h, Rx DS3 Interrupt Enable Register

- Bit 7ÑCP Bit Error Interrupt Enable

- Bit 6ÑLOS Interrupt Enable

- Bit 5ÑAIS Interrupt Enable

- Bit 4ÑIdle (Condition) Interrupt Enable

- Bit 3ÑFERF Interrupt Enable

- Bit 2ÑAIC Interrupt Enable

- Bit 1ÑOOF Interrupt Enable

- Bit 0ÑParity Error Interrupt Enable

- Address = 11h, RxDS3 Interrupt Status Register

- Bit 7ÑCP Bit Error Interrupt Status

- Bit 6ÑLOS Interrupt Status

- Bit 5ÑAIS Interrupt Status

- Bit 4ÑIdle Interrupt Status

- Bit 3ÑFERF Interrupt Status

- Bit 2Ñ(Change in) AIC Interrupt Status

- Bit 1ÑOOF (Receive DS3 Framer) Interrupt Status

- Bit 0ÑP-Bit Error (Receive DS3 Framer) Interrupt Status

- Address = 12h, RxDS3 FEAC Register

- Address = 13h, RxDS3 FEAC Interrupt Enable/Status Register

- Bit 4ÑFEAC Valid

- Bit 3ÑRxFEAC Remove Interrupt Enable

- Bit 2ÑRxFEAC Remove Interrupt Status

- Bit 1ÑRxFEAC Valid Interrupt Enable

- Bit 0ÑRxFEAC Valid Interrupt Status

- Address = 14h, RxDS3 LAPD Control Register

- Bits 7Ö3 Enable5 F(4)ÖF(0)

- Bit 2 RxLAPD Enable

- Bit 1 RxLAPD (Message Frame Reception �Complete) Interrupt Enable

- Bit 0 RxLAPD (Message Reception Complete) �Interrupt Status

- Address = 15h, Rx DS3 LAPD Status Register

- Bit 6ÑRxAbort (Receive Abort Sequence)

- Bits, 5 and 4ÑRxLAPDType[1, 0]

- Bit 3ÑRxCR (Command/Response) Type

- Bit 2ÑRx FCS (Frame Check Sequence) Error

- Bit 1ÑEnd Of Message

- Bit 0ÑFlag Present

- Address = 16h, Tx DS3 Configuration Register

- Bit 7ÑTx Yellow Alarm

- Bit 6ÑTx X-Bit (Force X bits to ç1é)

- Bit 5ÑTx Idle (Pattern)

- Bit 4ÑTx AIS (Pattern)

- Bit 3ÑTx LOS (Loss of Signal)

- Bit 2ÑFERF on LOS

- Bit 1ÑFERF on OOF

- Bit 0ÑFERF on AIS

- Address = 17h, Tx DS3 M-Bit Mask Register

- Bit 7-5: TxFEBEDat[2:0]

- Bit 4ÑFEBE Register Enable

- Bit 3ÑTransmit Erred P-Bit

- Bit 2Ö0 M-Bit Mask[2:0]

- Address = 18h, Tx DS3 F-Bit Mask1 Register

- Bits 3Ö0 F-Bit Mask[27:24]

- Address = 19h, Tx DS3 F-Bit Mask2 Register

- Bits 7Ö0 F-Bit Mask[23:16]

- Address = 1Ah, Tx DS3 F-Bit Mask3 Register

- Bits 7Ö0 F-Bit Mask[15:8]

- Address = 1Bh, Tx DS3 F-Bit Mask4 Register

- Bits 7Ö0 F-Bit Mask[7:0]

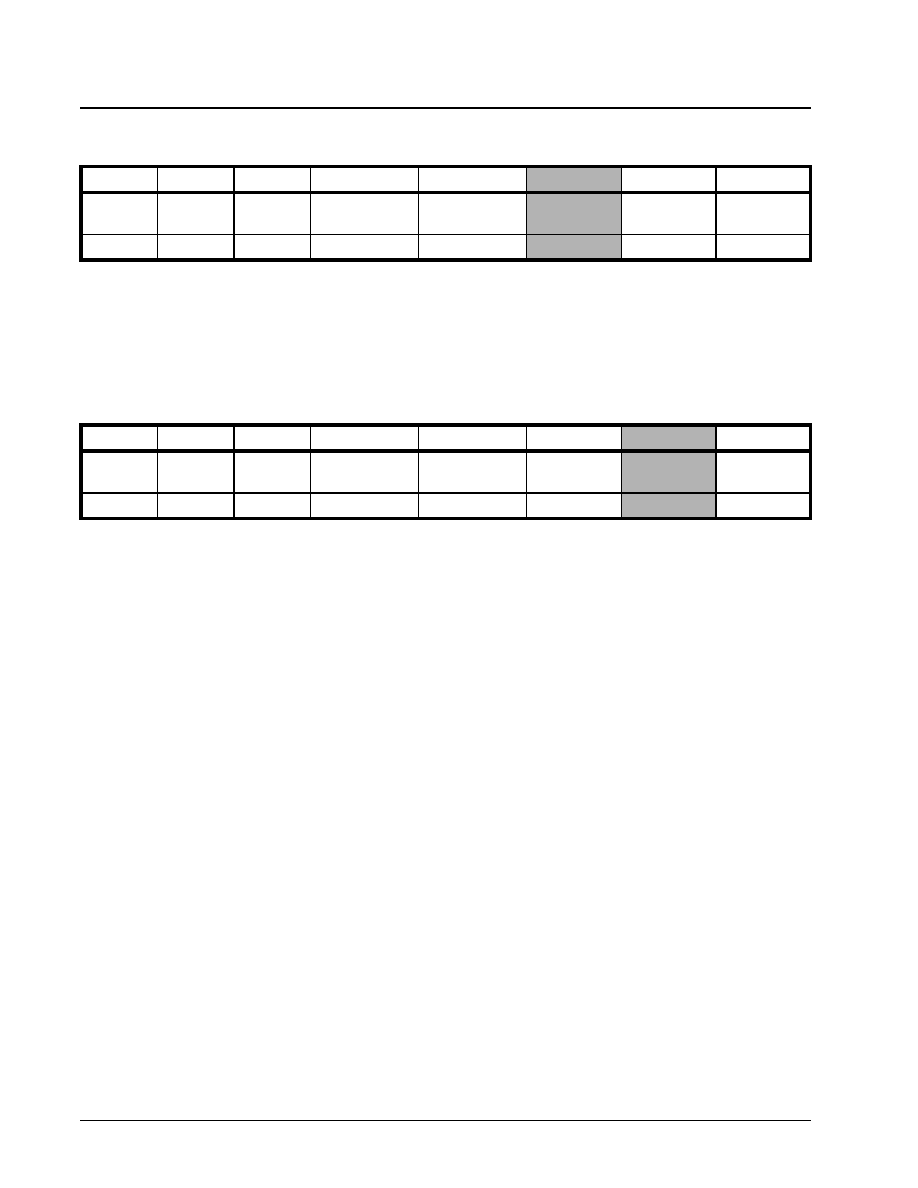

- Address = 1Ch, Tx DS3 FEAC Configuration and Status Register

- Bit 4ÑTxFEAC Interrupt Enable

- Bit 3ÑTxFEAC Interrupt Status

- Bit 2ÑTxFEAC Enable

- Bit 1ÑTxFEAC Go

- Bit 0ÑTxFEAC Busy

- Address = 1Dh, Tx DS3 FEAC Register

- Address = 1Eh, Tx DS3 LAPD Configuration Register

- Bit 3ÑAuto Retransmit

- Bit 2:1 = TxLAPD Type[1, 0]

- Bit 0ÑTxLAPD Enable

- Address = 1Fh, Tx DS3 LAPD Status/Interrupt Register

- Bit 3ÑTxDL Start

- Bit 2ÑTxDL Busy

- Bit 1ÑTxLAPD Interrupt Enable

- Bit 0ÑTxLAPD Interrupt Status

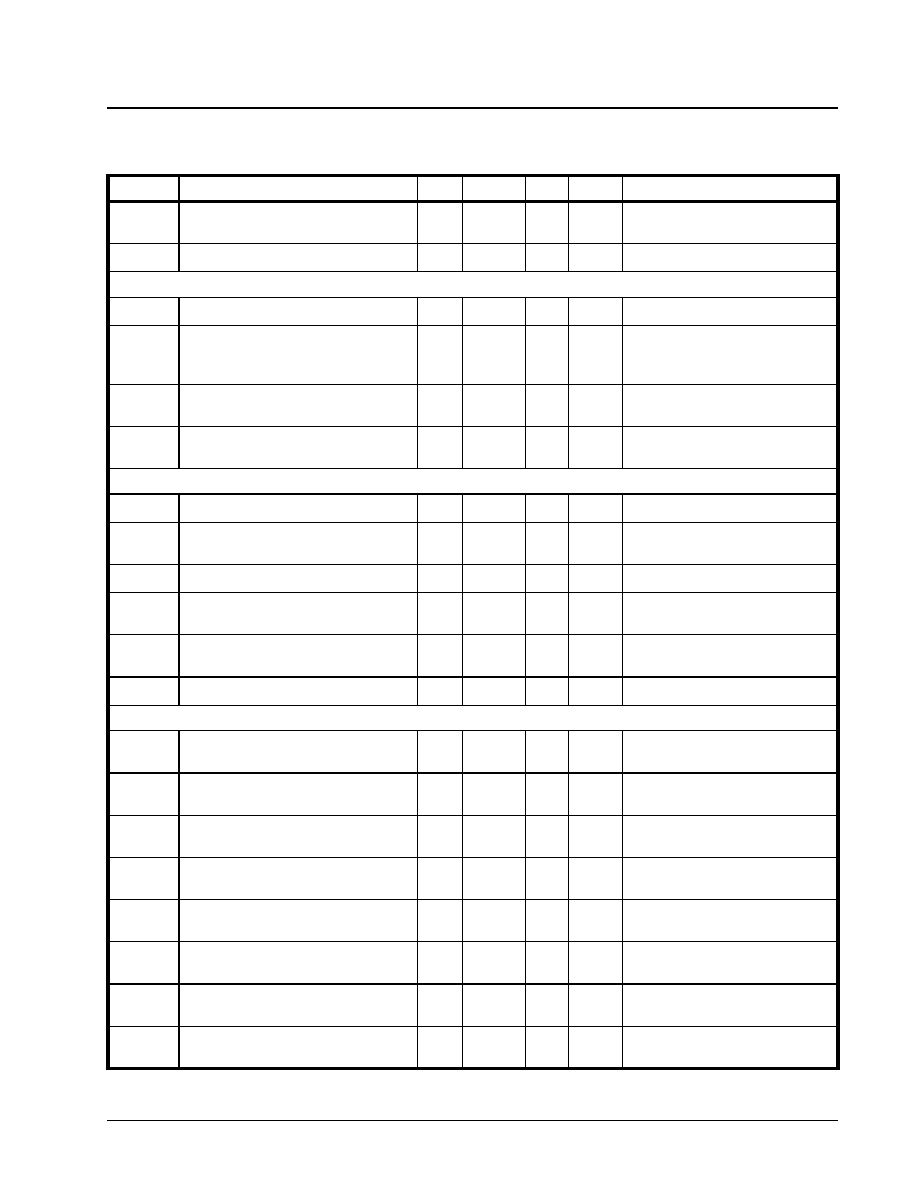

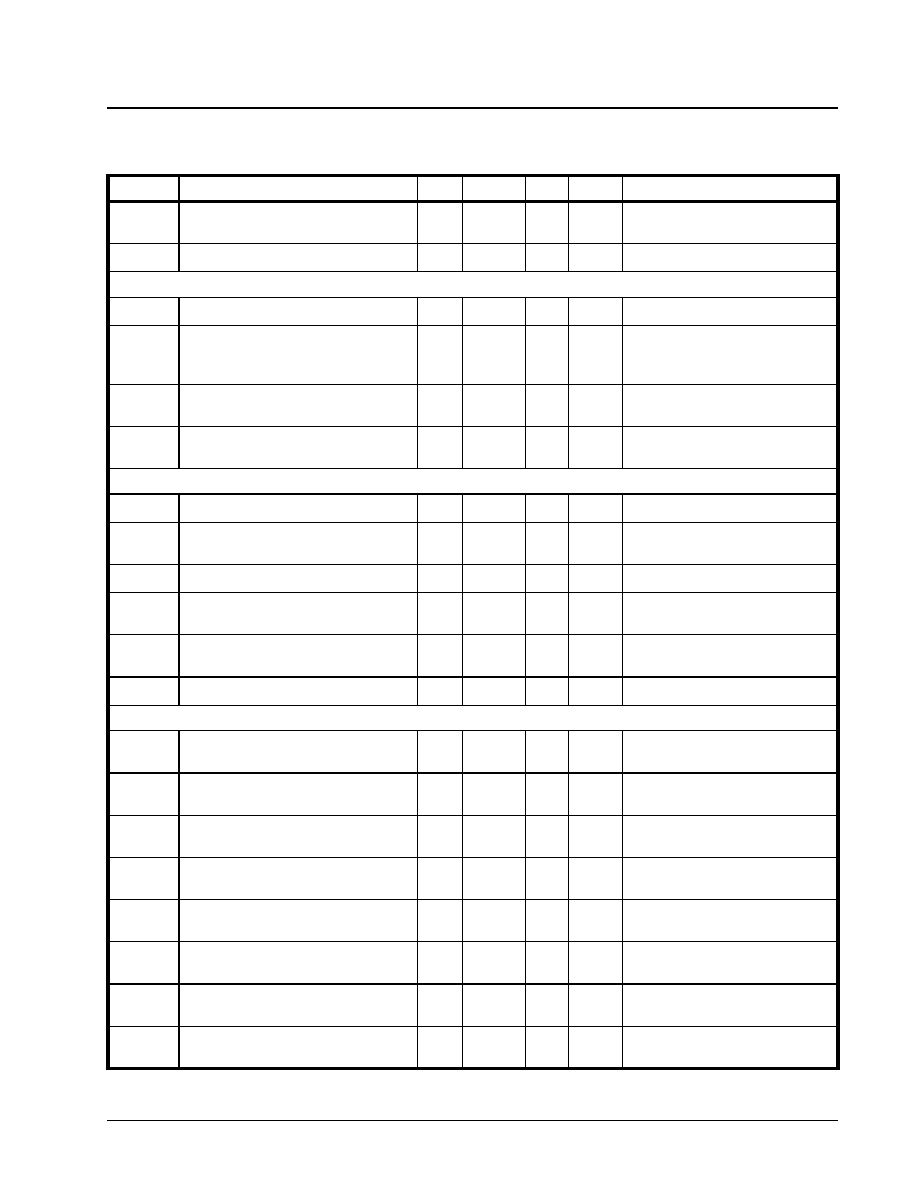

- Address = 20h, PMON LCV Event Count RegisterÑMSB

- Address = 21h, PMON LCV Event Count RegisterÑLSB

- Address = 22h, PMON Framing Bit Error Event Count RegisterÑMSB

- Address = 23h, PMON Framing Bit Error Event Count RegisterÑLSB

- Address = 24h, PMON Parity Error Event Count RegisterÑMSB

- Address = 25h, PMON Parity Error Event Count RegisterÑLSB

- Address = 26h, PMON FEBE Event Count RegisterÑMSB

- Address = 27h, PMON FEBE Event Count RegisterÑLSB

- Address = 28h, PMON BIP-8 Error Count RegisterÑMSB

- Address = 29h, PMON BIP-8 Error Count RegisterÑLSB

- Address = 2Ah, PMON PLCP Framing Byte Error Count RegisterÑMSB

- Address = 2Bh, PMON PLCP Framing Byte Error Count RegisterÑLSB

- Address = 2Ch, PMON PLCP FEBE Count RegisterÑMSB

- Address = 2Dh, PMON PLCP FEBE Count RegisterÑLSB

- Address = 2Eh, PMON Received Single HEC Error CountÑMSB

- Address = 2Fh, PMON Received Single HEC Error CountÑLSB

- Address = 30h, PMON Received Multiple-Bit HEC ErrorÑMSB

- Address = 31h, PMON Received Multiple-Bit HEC ErrorÑLSB

- Address = 32h, PMON Received Idle Cell CountÑMSB

- Address = 33h, PMON Received Idle Cell CountÑLSB

- Address = 34h, PMON Received Valid Cell CountÑMSB

- Address = 35h, PMON Received Valid Cell CountÑLSB

- Address = 36h, PMON Discarded Cell CountÑMSB

- Address = 37h, PMON Discarded Cell CountÑLSB

- Address = 38h, PMON Transmitted Idle Cell CountÑMSB

- Address = 39h, PMON Transmitted Idle Cell CountÑLSB

- Address = 3Ah, PMON Transmitted Valid Cell CountÑMSB

- Address = 3Bh, PMON Transmitted Valid Cell CountÑLSB

- Address = 3Ch, PMON Holding Register

- Address = 3Dh, One Second Error Status Register

- Bit 1ÑErrored Second

- Bit 0ÑSevere Errored Second

- Address = 3Eh, LCVÑOne Second Accumulator RegisterÑMSB

- Address = 3Fh, LCVÑOne Second Accumulator RegisterÑLSB

- Address = 40h, Frame Parity ErrorsÑOne Second Accumulator RegisterÑMSB

- Address = 41h, Frame Parity ErrorsÑOne Second Accumulator RegisterÑLSB

- Address = 42h, HEC ErrorsÑOne Second Accumulator RegisterÑMSB

- Address = 43h, HEC ErrorsÑOne Second Accumulator RegisterÑLSB

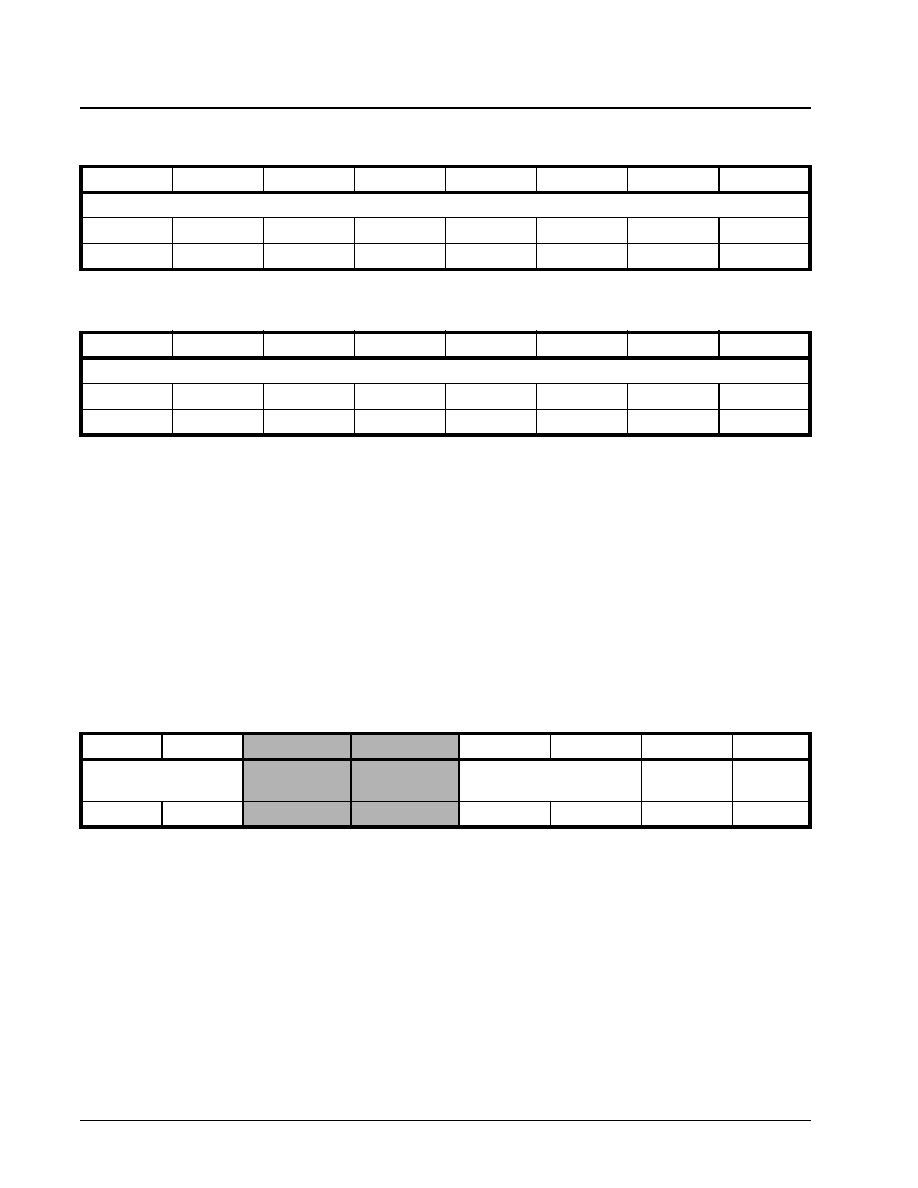

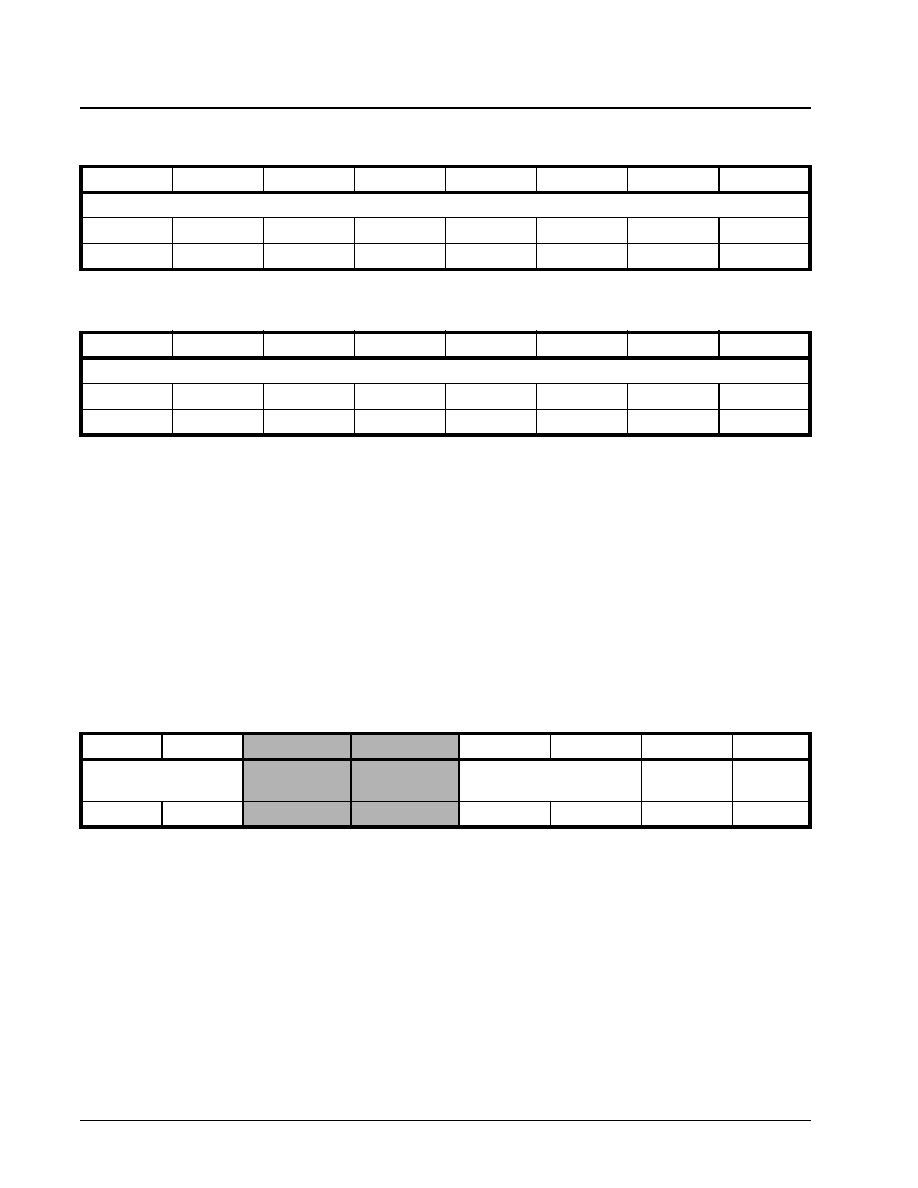

- Address = 44h, Rx PLCP Configuration/Status Register

- Bit 3ÑReframe (Receive PLCP Processor)

- Bit 2ÑPOOF (Receive PLCP OOF Condition) Status

- Bit 1ÑPLOF (Receive PLCP LOF Condition) Status

- Bit 0ÑYellow Status

- Address = 45h, Rx PLCP Interrupt Enable Register

- Bit 1ÑPOOF Interrupt Enable

- Bit 0ÑPLOF Interrupt Enable

- Address = 46h, Rx PLCP Interrupt Status Register

- Bit 1ÑPOOF Interrupt Status

- Bit 0ÑPLOF Interrupt Status

- Address = 47h, Future Use

- Address = 48h, Tx PLCP A1 Byte Error Mask

- Address = 49h, Tx PLCP A2 Byte Error Mask

- Address = 4Ah, Tx PLCP B1 Byte (BIP-8) Error Mask

- Address = 4Bh, Tx PLCP G1 Byte Register

- Bit 4ÑTxFEBE Mask

- Bit 3ÑYellow Alarm

- Bit 2Ñ0ÑLSS(2:0)

- Address = 4Ch, Rx CP Configuration Register

- Bit 7ÑRxLCD (Loss of Cell Delineation)

- Bit 6ÑRDPChk (Receive çData Path Integrity Checké)Pattern

- Bit 5ÑRDPChk (Receive çData Path Integrity Checké) Pattern Enable

- Bit 4ÑIC (Idle Cell) Discard

- Bit 3ÑOAM Check Bit

- Bit 2ÖDe-Scramble Enable

- Bit 1ÑRx Coset Enable

- Bit 0ÑHEC Error Ignore

- Address = 4Dh, Rx CP Additional Configuration Register

- Bit 5ÑUser Cell Filter Discard

- Bit 4ÑUser Cell Filter Enable

- Bits 3 and 2ÑCorrection Threshold[1, 0]

- Bit 1ÑCorrection Enable

- Address = 4Eh, Rx CP Interrupt Enable Register

- Bit 2ÑOAM (Cell Received) Interrupt Enable

- Bit 1ÑLCD (Loss of Cell Delineation) Interrupt Enable

- Bit 0ÑHEC Byte Error Interrupt Enable

- Address = 4Fh, Rx CP Interrupt Status Register

- Bit 2ÑOAM (Cell Received) Interrupt Status

- Bit 1ÑLCD (Loss of Cell Delineation) Interrupt Status

- Bit 0ÑHEC Byte Error Interrupt Status

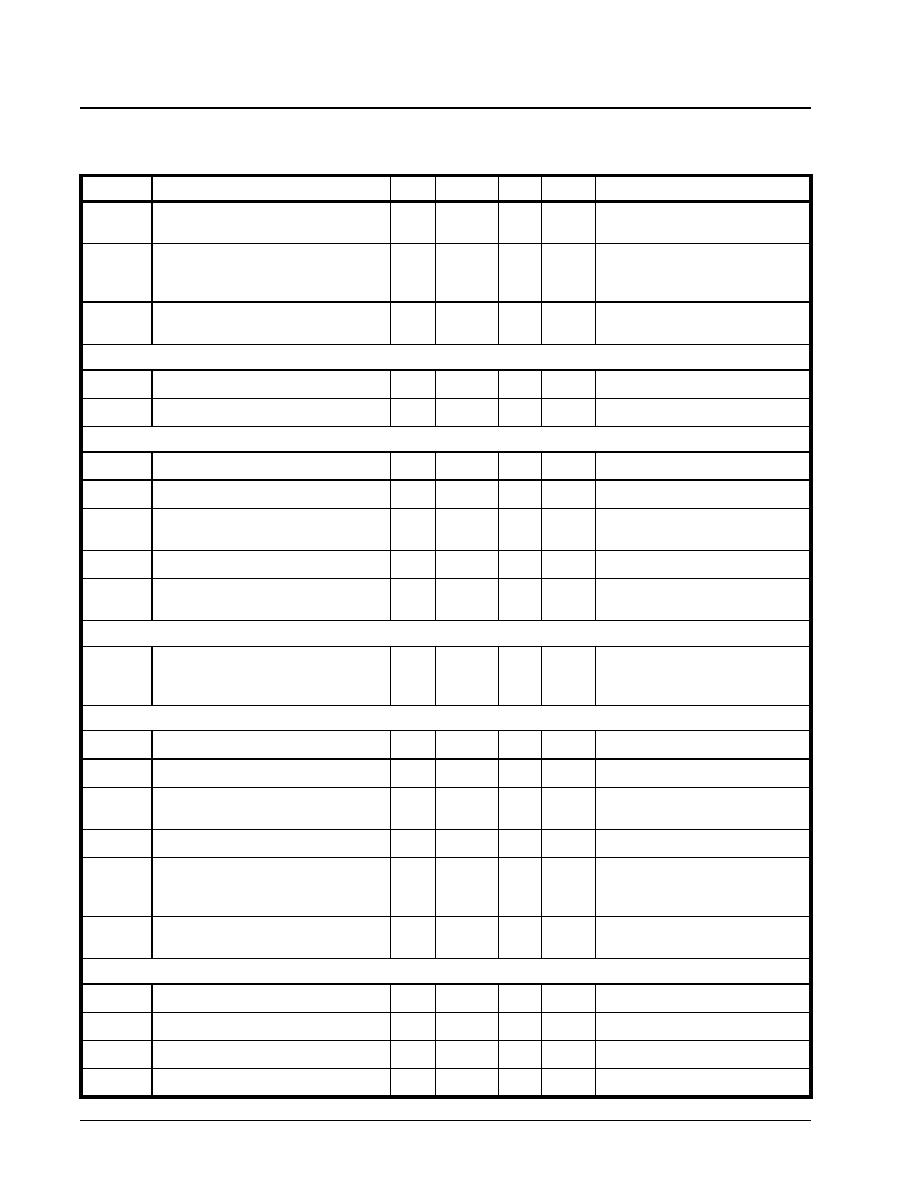

- Address = 50h, Rx CP Idle Cell Pattern HeaderÑByte 1

- Address = 51h, Rx CP Idle Cell Pattern HeaderÑByte 2

- Address = 52h, Rx CP Idle Cell Pattern HeaderÑByte 3

- Address = 53h, Rx CP Idle Cell Pattern HeaderÑByte 4

- Address = 54h, Rx CP Idle Cell Mask HeaderÑByte 1

- Address = 55h, Rx CP Idle Cell Mask HeaderÑByte 2

- Address = 56h, Rx CP Idle Cell Mask HeaderÑByte 3

- Address = 57h, Rx CP Idle Cell Mask HeaderÑByte 4

- Address = 58h, Rx CP User Cell Filter Pattern HeaderÑByte 1

- Address = 59h, Rx CP User Cell Filter Pattern HeaderÑByte 2

- Address = 5Ah, Rx CP User Cell Filter Pattern HeaderÑByte 3

- Address = 5Bh, Rx CP User Cell Filter Pattern HeaderÑByte 4

- Address = 5Ch, Rx CP User Cell Filter Mask HeaderÑByte 1

- Address = 5Dh, Rx CP User Cell Filter Mask HeaderÑByte 2

- Address = 5Eh, Rx CP User Cell Filter Mask HeaderÑByte 3

- Address = 5Fh, Rx CP User Cell Filter Mask HeaderÑByte 4

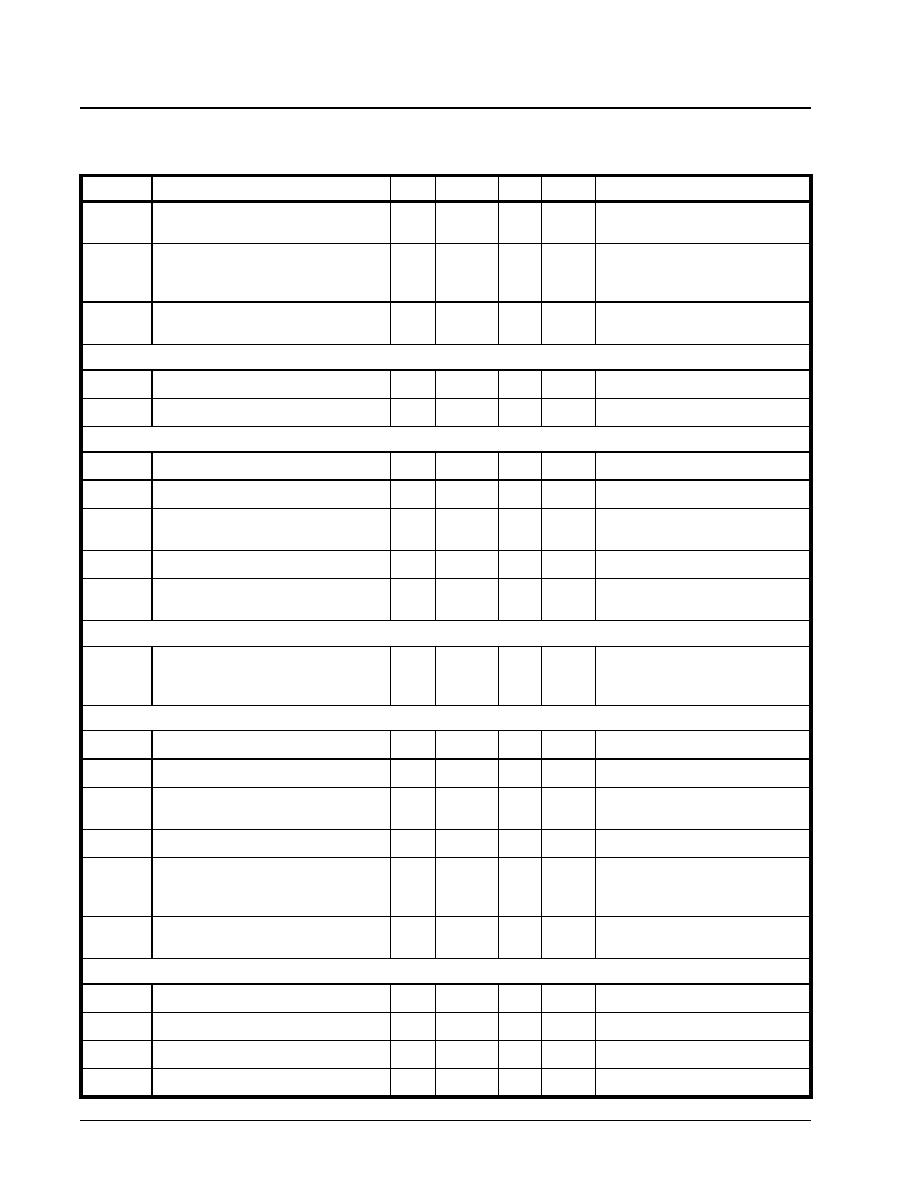

- Address = 60h, Tx CP Control Register

- Bit 7ÑScrambler Enable

- Bit 6ÑCoset Enable

- Bit 5ÑHEC Byte Insert EnableÑAssigned Cells

- Bit 4ÑTDPChk Pat (Transmit Data Path Integrity Check Pattern Selection)

- Bit 3ÑGFC Nibble-Field Insert Enable

- Bit 2ÑTDP (Transmit Data Path Integrity Test) �Error Interrupt Enable

- Bit 1ÑIC (Idle Cell) HEC Byte Calculation Enable

- Bit 0ÑTDP (Transmit Data Path Integrity Check) Error Interrupt Status

- Address = 61h, Tx CP OAM Cell Register

- Bit 7ÑSend OAM (Cell)

- Address = 62h, Tx CP HEC Byte Error Mask Register

- Address = 63h, Future Use

- Address = 64h, Tx CP Idle Cell Pattern HeaderÑByte 1

- Address = 65h, Tx CP Idle Cell Pattern HeaderÑByte 2

- Address = 66h, Tx CP Idle Cell Pattern HeaderÑByte 3

- Address = 67h, Tx CP Idle Cell Pattern HeaderÑByte 4

- Address = 68h, Tx CP Idle Cell Pattern HeaderÑByte 5

- Address = 69h, Tx CP Idle Cell Payload Register

- Address = 6Ah, UTOPIA Configuration Register

- Bit 5ÑHandshake Mode

- Bit 4ÑM-PHY/S-PHY* (UTOPIA Operating Mode)

- Bit 3ÑCellOf52Bytes

- Bits 2, 1,ÑTFIFODepth[1, 0]

- Bit 0ÑUtWidth16ÑUTOPIA Data Width

- Address = 6Bh, Receive UTOPIA Interrupt Enable/Status Register

- Bit 6ÑRxFIFO Reset

- Bit 5ÑRxFIFO Overrun Interrupt Enable

- Bit 4ÑRxFIFO Underrun Interrupt Enable

- Bit 3ÑRxFIFO Change of Cell Alignment Interrupt Enable

- Bit 2ÑRxFIFO Overrun Interrupt Status

- Bit 1ÑRxFIFO Underrun Interrupt Status

- Bit 0ÑRxFIFO Change of Cell Alignment Interrupt Status

- Address = 6Ch, Receive UTOPIA Address Register

- Address = 6Dh, Receive UTOPIA FIFO Status Register

- Bit 1ÑRxFIFO Full

- Bit 0ÑRxFIFO Empty

- Address = 6Eh, Transmit UTOPIA Interrupt/Status Register

- Bit 7ÑTxFIFO Reset

- Bit 6ÑDiscard (Cell) Upon Parity Error (Transmit UTOPIA Interface block)

- Bit 5ÑTx Parity Interrupt Enable (Transmit UTOPIA Interface block)

- Bit 4ÑTxFIFO Overrun Interrupt Enable

- Bit 3ÑTxFIFO Change of Cell Alignment Interrupt Enable

- Bit 2ÑTx Parity Interrupt Status

- Bit 1ÑTxFIFO Overrun Interrupt Status

- Bit 0ÑTxFIFO Change of Cell Alignment Interrupt Status

- Address = 6Fh, Transmit UTOPIA UDF2 Register

- Address = 70h, Transmit UTOPIA Address Register

- Address = 71h, Transmit UTOPIA FIFO Status Register

- Bit 1ÑTxFIFO Full

- Bit 0ÑTxFIFO Empty

- Address = 72h, Line Interface Drive Register

- Bit 5ÑREQB (Receive Equalization Bypass �Control)

- Bit 4ÑTAOS (Transmit All Ones Signal)

- Bit 3ÑEncodis (B3ZS Encoder Disable)

- Bit 2ÑTxLev (Transmit Output Line Build-Out �Select Output)

- Bit 1ÑRLOOP (Remote Loop-back)

- Bit 0ÑLLOOP

- Address = 73h, Line Interface Scan Register

- Bit 2ÑDMO (Drive Monitor Output)

- Bit 1ÑRLOL (Receive Loss of Lock)

- Bit 0ÑRLOS (Receive Loss of Signal)

- Address = 74h, PMON CP Bit Error CountÑMSB

- Address = 72h, Line Interface Drive Register

- Address = 01h, UNI I/O Control Register

- UNI Interrupt Status Register: Address = 05h

- UNI Interrupt Enable Register: Address = 04h

- Address = 01h, UNI I/O Control Register

- The 8051 Microcontroller

- Port 0 (P0.0ÖP0.7)

- Port 1 (P1.0ÖP1.7)

- Port 2 (P2.0ÖP2.7)

- Port 3

- ALEÑAddress Latch Enable

- INT0* (P3.2) and INT1* (P3.3)

- Functional Description of Circuit in Figure 22.

- UNI Operating Mode Register (Address = 00h)

- UNI Operating Mode Register (Address = 00h)

- UNI Operating Mode Register (Address = 00h)

- Test Cell Control and Status Register (Address = 06h)

- Test Cell Header Byte-1 Register (Address = 08h)

- Test Cell Header Byte-2 Register (Address = 09h)

- Test Cell Header Byte-3 Register (Address = 0Ah)

- Test Cell Header Byte-4 Register (Address = 0Bh)

- Test Cell Control and Status Register (Address = 06h)

- Test Cell Control and Status Register (Address = 06h)

- Test Cell Control and Status Register (Address = 06h)

- Test Cell Control and Status Register (Address = 06h)

- Test Cell Error AccumulatorÑMSB (Address = 0Ch)

- Test Cell Error AccumulatorÑLSB (Address = 0Dh)

- Line Interface Drive Register (Address = 72h)

- Bit 5ÑREQB (Receive Equalization Enable/ �Disable Select)

- Bit 4ÑTAOS (Transmit All Ones Signal)

- Bit 3ÑEncodis (B3ZS Encoder Disable)

- Bit 2ÑTxLev (Transmit Line Build-Out Enable/ Disable Select)

- Bit 1ÑRLOOP (Remote Loop-back Select)

- Bit 0ÑLLOOP (Local Loop-back Select)

- Address = 73h, Line Interface Scan Register

- Bit 2ÑDMO (Drive Monitor Output)

- Bit 1ÑRLOL (Receive Loss of Lock)

- Bit 0ÑRLOS (Receive Loss of Signal)

- TxData[15:0] ÑTransmit UTOPIA Data Bus inputs

- TxAddr[4:0]ÑTransmit UTOPIA Address Bus �inputs

- TxClkÑTransmit UTOPIA Interface Block Clock signal input pin

- TxEnB*ÑTransmit UTOPIA Data BusÑWrite �Enable input

- TxPrtyÑTransmit UTOPIAÑOdd Parity Bit Input�Pin

- TxSoCÑTransmit UTOPIAÑçStart of Cellé �Indicator

- Example-1

- Example-2

- TxClav/TFullB*ÑTx FIFO Cell Available/TxFIFO Full*

- Selecting the UTOPIA Data Bus Width

- UTOPIA Configuration Register: Address = 6Ah

- UTOPIA Configuration Register: Address = 6Ah

- Transmit UTOPIA Interrupt/Status Register (Address = 6Eh)

- Transmit UTOPIA FIFO Manager Features and�Options

- UTOPIA Configuration Register: Address = 6Ah

- UTOPIA Configuration Register: Address = 6Ah

- Transmit UTOPIAÑInterrupt/Status Register (AddressÑ6Eh)

- Transmit UTOPIA FIFO Status Register (Address = 71h)

- TxFIFO Full

- Tx FIFO Empty

- UTOPIA Configuration Register: Address = 6Ah

- Final Comments on Single-PHY Operation

- Tx UTOPIA Address Register (Address = 70h)

- Rx UTOPIA Address Register (Address = 6Ch)

- Polling Operation

- The ATM Layer Processorês Role in the çPollingé Operation

- The UNI Devices Role in the çPollingé Operation

- UNI Interrupt Status Register (Address = 05h)

- Tx UT Interrupt Enable /Status Register (Address-6Eh)

- Bit 0ÑTCOCA Interrupt StatusÑTransmit UTOPIA Change of Cell Alignment Condition

- Tx UT Interrupt Enable /Status Register (Address-6Eh)

- Bit 1ÑTx FIFO Overrun Interrupt Status

- Transmit UTOPIA Interrupt Enable /Status Register (AddressÑ6Eh)

- Bit 2ÑTPErr Interrupt StatusÑDetection of Parity Error via the Transmit UTOPIA Interface Block

- Transmit UTOPIA Interrupt Enable /Status Register (Address-6Eh)

- Bit 3ÑTCOCA Interrupt EnableÑTransmit UTOPIA Change of Cell Alignment Interrupt Enable

- Tx UT Interrupt Enable/Status Register (Address-6Eh)

- Bit 4ÑTx FIFO ErrInt EnableÑTx FIFO Overrun Condition Interrupt Enable

- Tx UT Interrupt Enable/Status Register (Address-6Eh)

- Bit 5ÑTPerr Interrupt EnableÑDetection of Parity Error in Transmit UTOPIA Block Interrupt Enable

- Tx UT Interrupt Enable /Status Register (Address-6Eh)

- TxCP Control Register (Address = 60h)

- TxCP Control Register (Address = 60h)

- TxCP Control Register (Address = 60h)

- TxCP Error Mask Register; (Address = 62h)

- TxCP Control Register (Address = 60h)

- TxCP Control Register (Address = 60h)

- TxCP OAM Register (Address = 61h)

- PMON Transmitted Valid Cell CountÑMSB (Address = 3Ah)

- PMON Transmitted Valid Cell CountÑLSB (Address = 3Bh)

- PMON Transmitted Idle Cell CountÑMSB (Address = 38h)

- PMON Transmitted Idle Cell CountÑLSB (Address = 39h)

- Tx CP Control Register (Address = 60h)

- Bit 4ÑTDPChk PatÑTest Data Path Integrity Check Pattern

- UNI Interrupt Status Register (Address = 05h)

- Transmit Cell Processor Control Register (Address = 60h)

- Bit 2Ñ TDPErrIntEnÑçTest Data Path Integrity Checké Interrupt Enable

- Bit 0ÑTDPErrIntStatÑçTest Data Path Integrity Checké Interrupt Status

- UNI Operating Mode Register: Address = 00h

- Far-End Block Error (FEBE)

- RAI (Yellow Alarm)

- Tx PLCP BIP-8 Error Mask Register, Address = 4Ah

- Tx PLCP A1 Byte Error Mask Register (Address = 48h)

- Tx PLCP A2 Byte Error Mask Register (Address = 49h)

- Tx PLCP G1 Byte Register (Address = 4Bh)

- Tx PLCP G1 Byte Register (Address = 4Bh)

- Tx PLCP G1 Byte Register (Address = 4Bh)

- UNI Operating Mode Register: Address = 00h

- Final Notes about the Transmit PLCP Processor

- UNI Operating Mode Register: Address = 00h

- Differences Between the M13 and C-Bit Parity Frame Formats

- Definition of the DS3 Frame Overhead Bits

- P-Bits (Applies to M13 and C-Bit Parity Frame Formats)

- Alarm Indication Signal (AIS) Detection (C-Bit Parity Framing Format only)

- IDLE Condition Signal

- FEAC (Only available for the C-bit Parity Frame Format)

- FEBE (Only available for the C-bit Parity Frame Format)

- Transmit Yellow Alarm (X-bits)

- UDL: User Data Link (C-bit Parity Frame Format�Only)

- DL: Path Maintenance Data Link (C-bit Parity Frame Format Only)

- Tx DS3 M-Bit Mask Register, Address = 17h

- Bit 3ÑTx Err (Transmit Errored) P-Bit

- Bits 2Ñ0: M-Bit Mask[2:0]

- Tx DS3 F-Bit Mask1 Register, Address = 18h

- Tx DS3 F-Bit Mask2 Register, Address = 19h

- Tx DS3 F-Bit Mask3 Register, Address = 1Ah

- Tx DS3 F-Bit Mask4 Register, Address = 1Bh

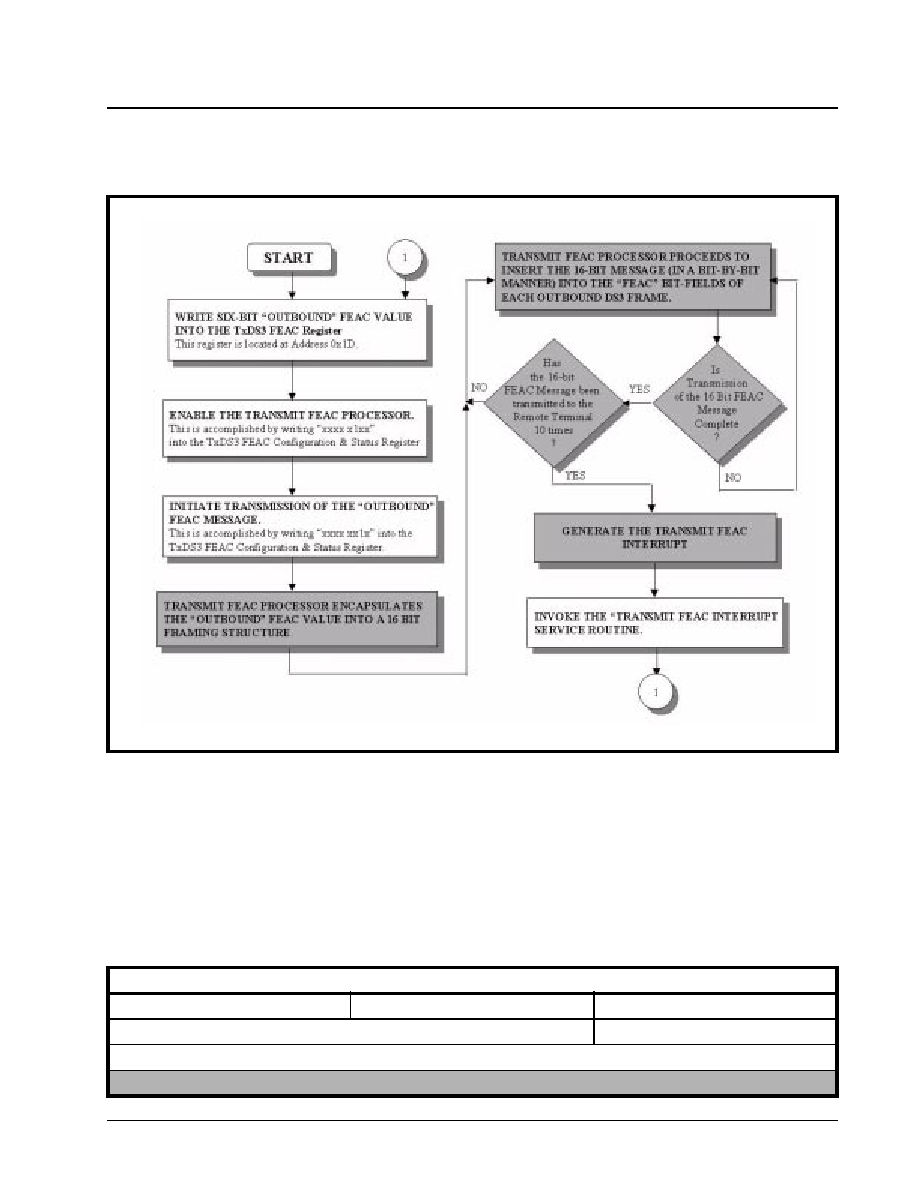

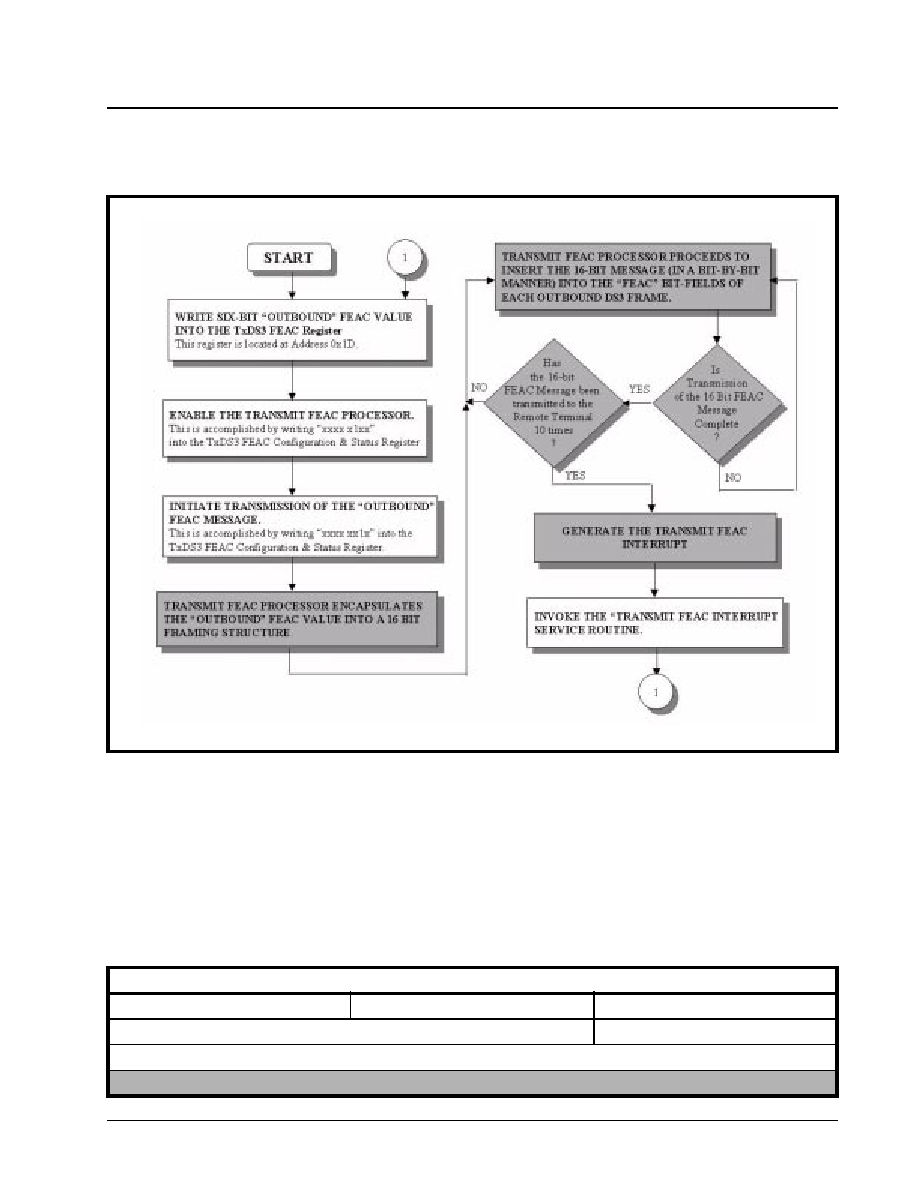

- Tx DS3 FEAC RegisterÑAddress: 1Dh

- Transmit DS3 FEAC Configuration and Status RegisterÑAddress: 1Ch

- Transmit DS3 FEAC Configuration and Status RegisterÑAddress: 1Ch

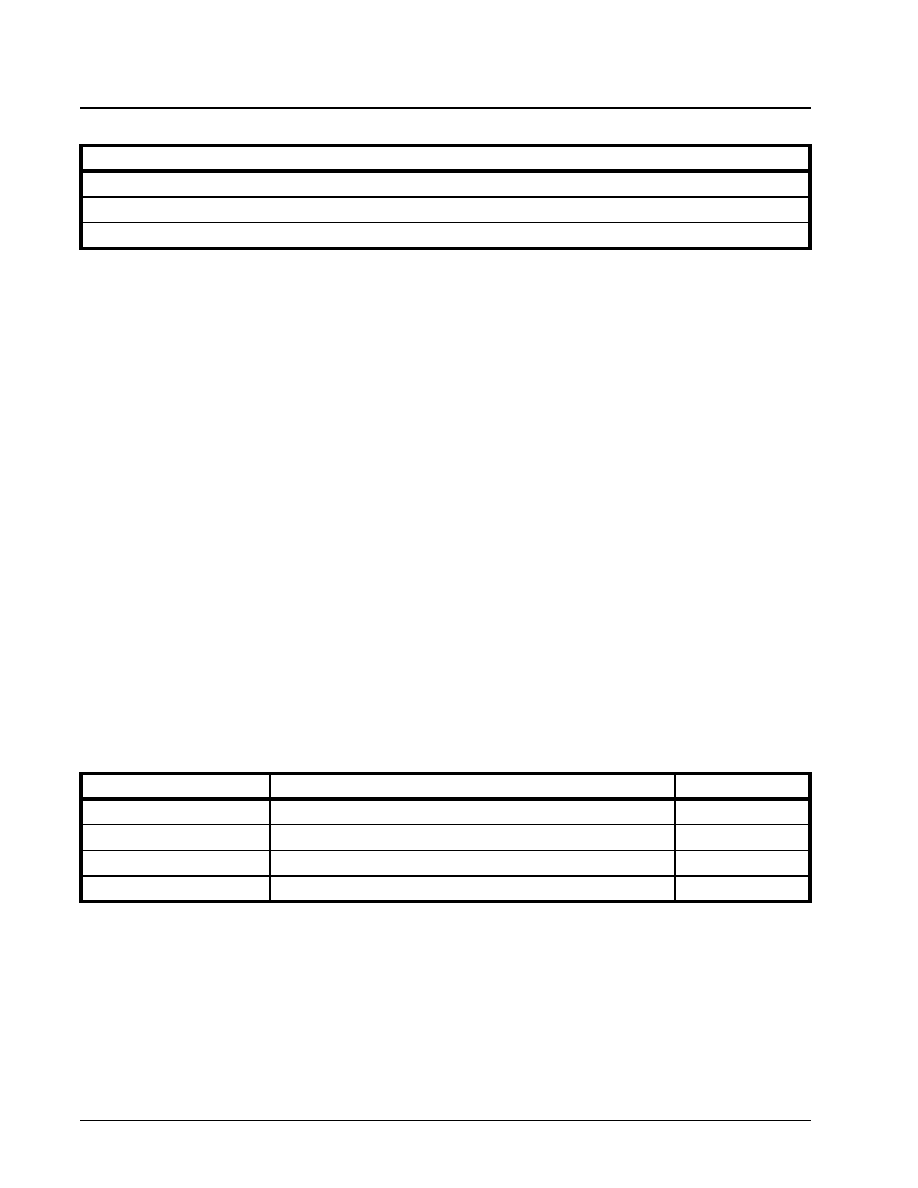

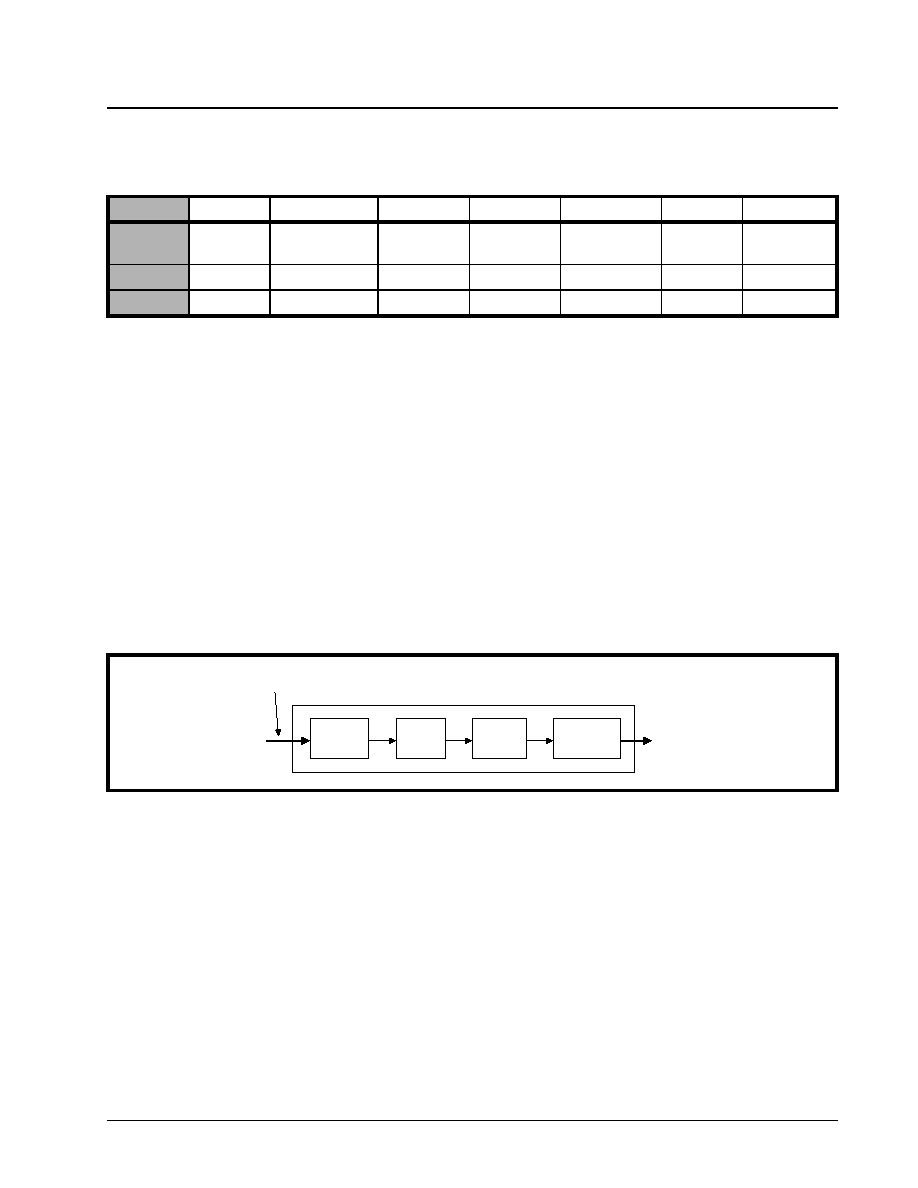

- Flag Sequence Byte

- SAPIÑService Access Point Identifier

- TEIÑTerminal Endpoint Identifier

- Control

- Information Payload

- Frame Check Sequence Bytes

- Operation of the LAPD Transmitter

- Specifying the Type of LAPD Message

- Transmit DS3 LAPD Configuration Register (Address = 1Eh)

- Enabling the LAPD Transmitter

- Transmit DS3 LAPD Configuration Register (Address = 1Eh)

- Bit 0ÑTxLAPD Enable

- Tx DS3 LAPD Status/Interrupt Register (Address = 1Fh)

- Address = 01h, UNI I/O Control Register

- Address = 04h, UNI Interrupt Enable Register

- Tx DS3 M-Bit Mask Register, Address = 17h

- Bit 4ÑFEBE Register Enable

- Tx DS3 Configuration Register (Address = 16h)

- UNI Operating Mode Register: Address = 00h

- UNI I/O Control Register (Address = 01h)

- UNI I/O Control Register (Address = 01h)

- UNI I/O Control Register (Address = 01h)

- UNI Interrupt Status Register (Address = 05h)

- Tx DS3 FEAC Configuration and Status Register

- Tx DS3 FEAC Configuration and Status Register (Address = 1Ch)

- Bit 3ÑTx FEAC Interrupt Status

- Bit 4ÑTx FEAC Interrupt Enable

- Tx DS3 LAPD Status/Interrupt Register (Address = 1Fh)

- Bit-0ÑTxLAPD Interrupt Status

- Bit-1ÑTxLAPD Interrupt Enable

- UNI I/O Control Register (Address = 01h)

- UNI I/O Control Register (Address = 01h)

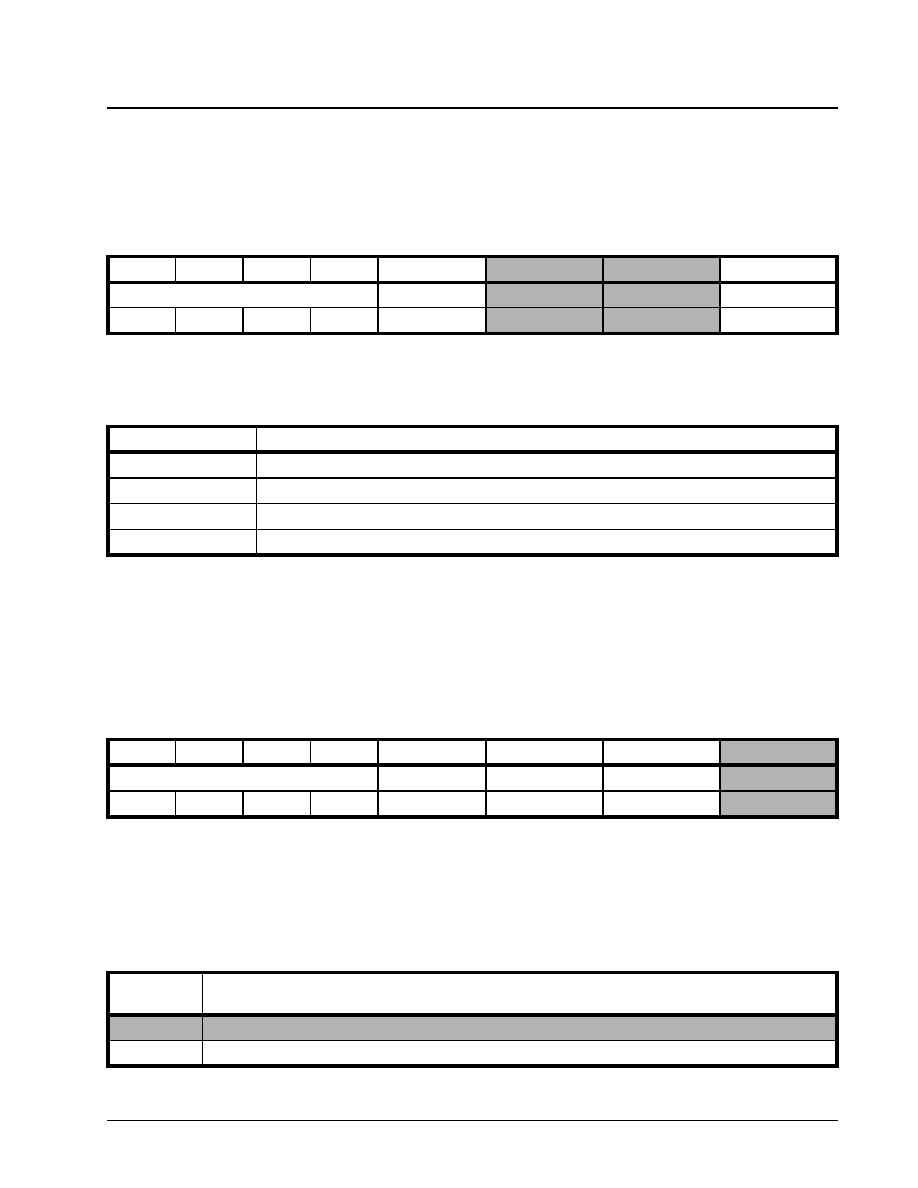

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- The çFraming on Parityé Option

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- UNI I/O Control Register (Address = 01h)

- Address = 22h, PMON Framing Bit Error Event Count RegisterÑMSB

- Address = 23h, PMON Framing Bit Error Event Count RegisterÑLSB

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Rx DS3 Configuration and Status Register, (Address = 0Eh)

- Address = 0Fh, Rx DS3 Status Register

- Rx DS3 Interrupt Status Register (Address = 11h)

- Address = 24h, PMON Parity Error Event Count RegisterÑMSB

- Address = 25h, PMON Parity Error Event Count RegisterÑLSB

- Operation of the Receive DS3 FEAC Processor

- FEAC Code Validation

- Rx DS3 FEAC Interrupt Enable/Status Register (Address = 13h)

- Rx DS3 FEAC Register (Address = 12h)

- FEAC Code Removal

- Rx DS3 FEAC Interrupt Enable/Status Register (Address = 13h)

- Operation of the LAPD Receiver

- Rx DS3 LAPD Control Register (Address = 14h)

- Rx DS3 LAPD Status Register (Address = 15h)

- Bit 3ÑRxCR TypeÑC/R (Command/Response) Type

- Bit 4, 5ÑRxLAPD Type[1, 0]ÑLAPD Message Type

- Bit 1ÑEndOfMessageÑEnd of LAPD Message Frame

- Bit 2ÑRxFCSErrÑFrame Check Sequence Error Indicator

- Address = 0Fh, RxDS3 Status Register

- UNI Interrupt Status Register (Address = 05h)

- Rx DS3 Interrupt Status Register

- Rx DS3 Interrupt Status Register (Address = 11h)

- Bit 0ÑParity (P-Bit) Error Interrupt Status

- Bit 1ÑChange in OOF Statusé Interrupt Status

- Bit 2ÑAIC Interrupt Status (C-Bit Parity Mode Only)

- Bit 3ÑFERF (Far-End Receive Failure) Interrupt Status

- Bit 4ÑçChange in IDLE Statusé Interrupt Status

- Bit 5ÑçChange in AIS Statusé Interrupt Status

- Bit 6ÑçChange in LOS (Loss of Signal) Statusé Interrupt Status

- Rx DS3 Interrupt Enable Register (Address = 10h)

- Rx DS3 FEAC Interrupt Enable/Status Register

- Rx DS3 FEAC Interrupt Enable/Status Register (Address = 13h)

- Bit 0ÑRx FEAC Valid Interrupt Status

- Bit 1ÑRx FEAC Valid Interrupt Enable

- Bit 2ÑRx FEAC Removal Interrupt Status

- Bit 3ÑRx FEAC Removal Interrupt Enable

- Rx DS3 LAPD Control Register

- Rx DS3 LAPD Control Register (Address = 14h)

- Bit 0ÑRxLAPD Interrupt Status

- Bit 1ÑRxLAPD Interrupt Enable

- Rx PLCP Configuration/Status Register (Address = 44h)

- Address = 2Ah, PMON PLCP Framing Byte Error Count RegisterÑMSB

- Address = 2Bh, PMON PLCP Framing Byte Error Count RegisterÑLSB

- Rx PLCP Configuration/Status Register (Address = 44h)

- Bit 1ÑPLOF Status

- Bit 2ÑPOOF Status

- Rx PLCP Configuration/Status Register (Address = 44h)

- Address = 28h, PMON BIP-8 Error Count RegisterÑMSB

- Address = 29h, PMON BIP-8 Error Count RegisterÑLSB

- Bit 3ÑRAIÑYellow Alarm Indicator

- Rx PLCP Configuration/Status Register (Address = 44h)

- Bits 4 through 7ÑFEBE

- Address = 2Ch, PMON PLCP FEBE Count RegisterÑMSB

- Address = 2Dh, PMON PLCP FEBE Count RegisterÑLSB

- UNI Interrupt Status Register (Address = 05h)

- Rx PLCP Interrupt Status Register (Address = 46h)

- Bit 0ÑçPLOF Interrupt Status

- Bit 1ÑPOOF Interrupt Status

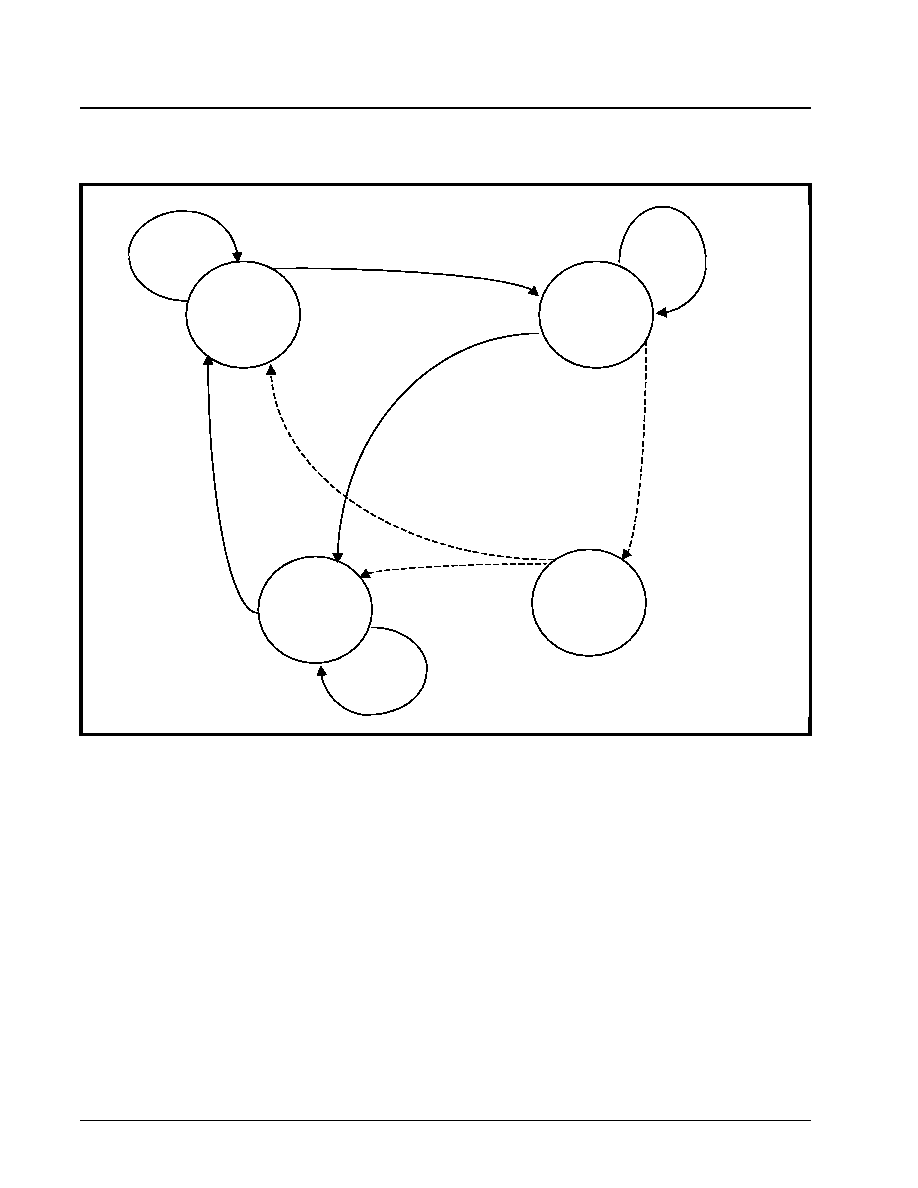

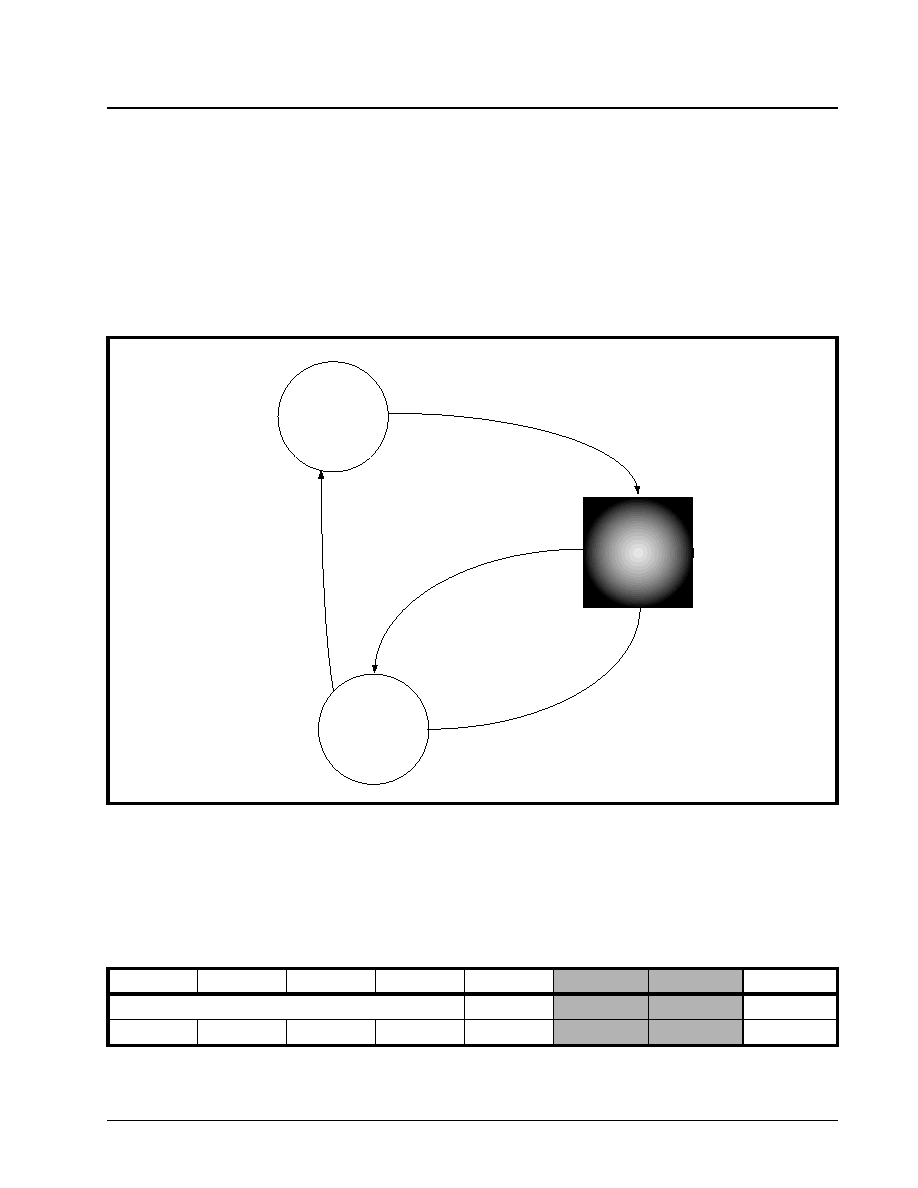

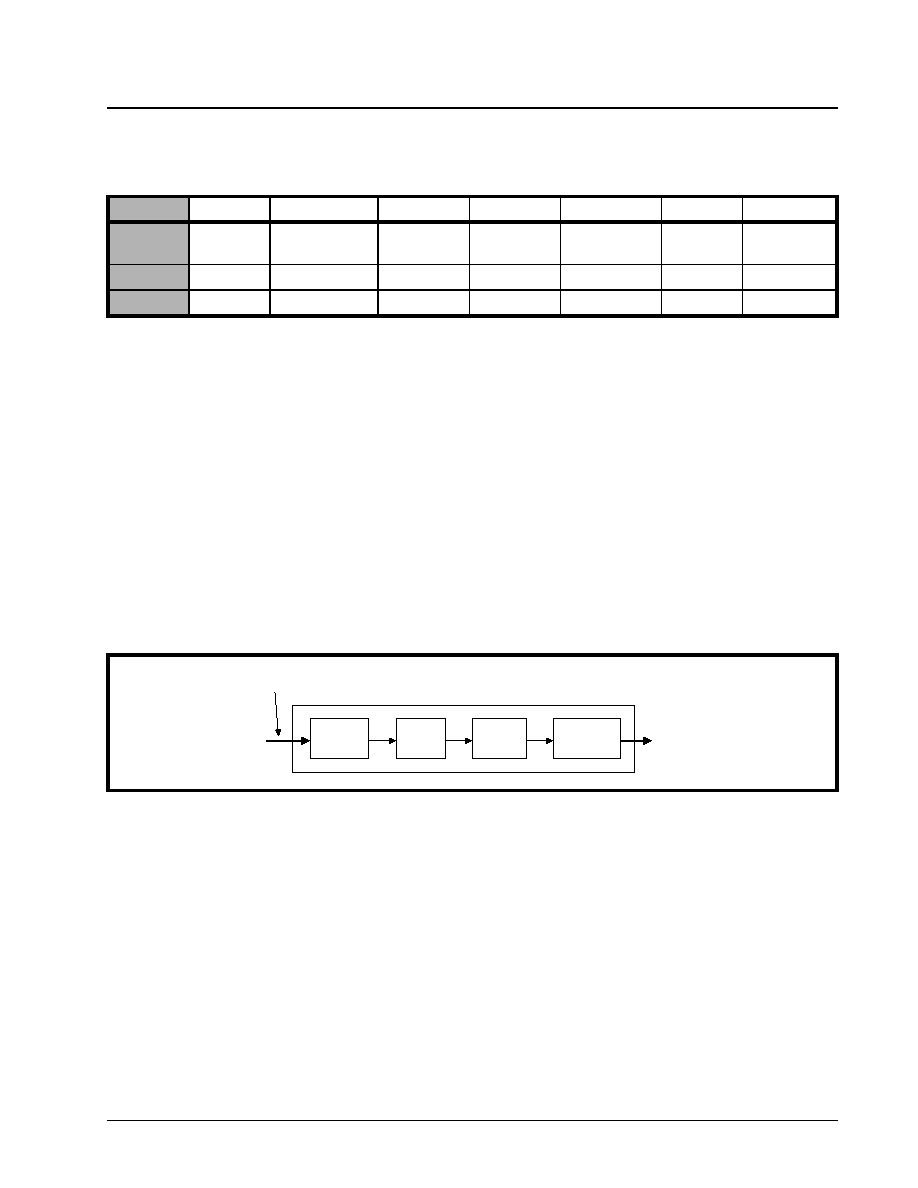

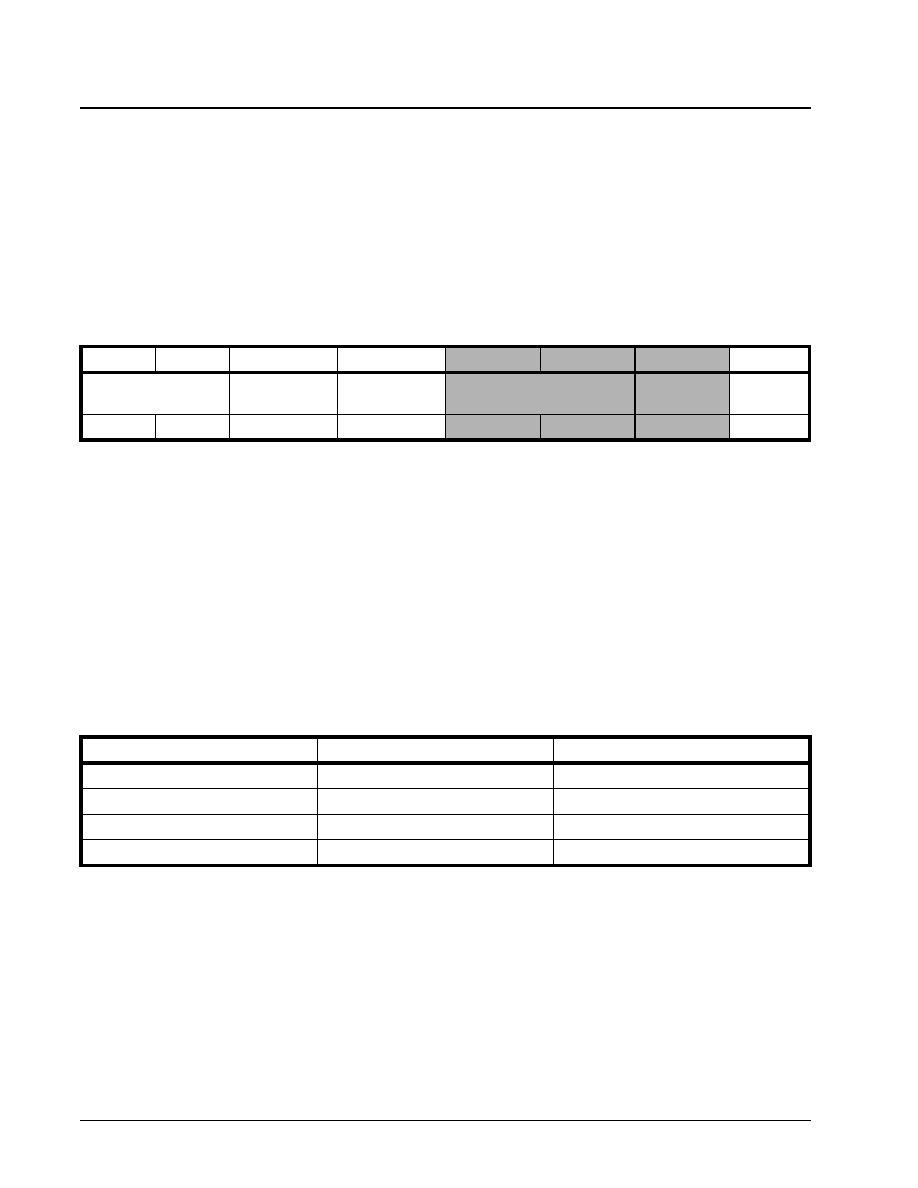

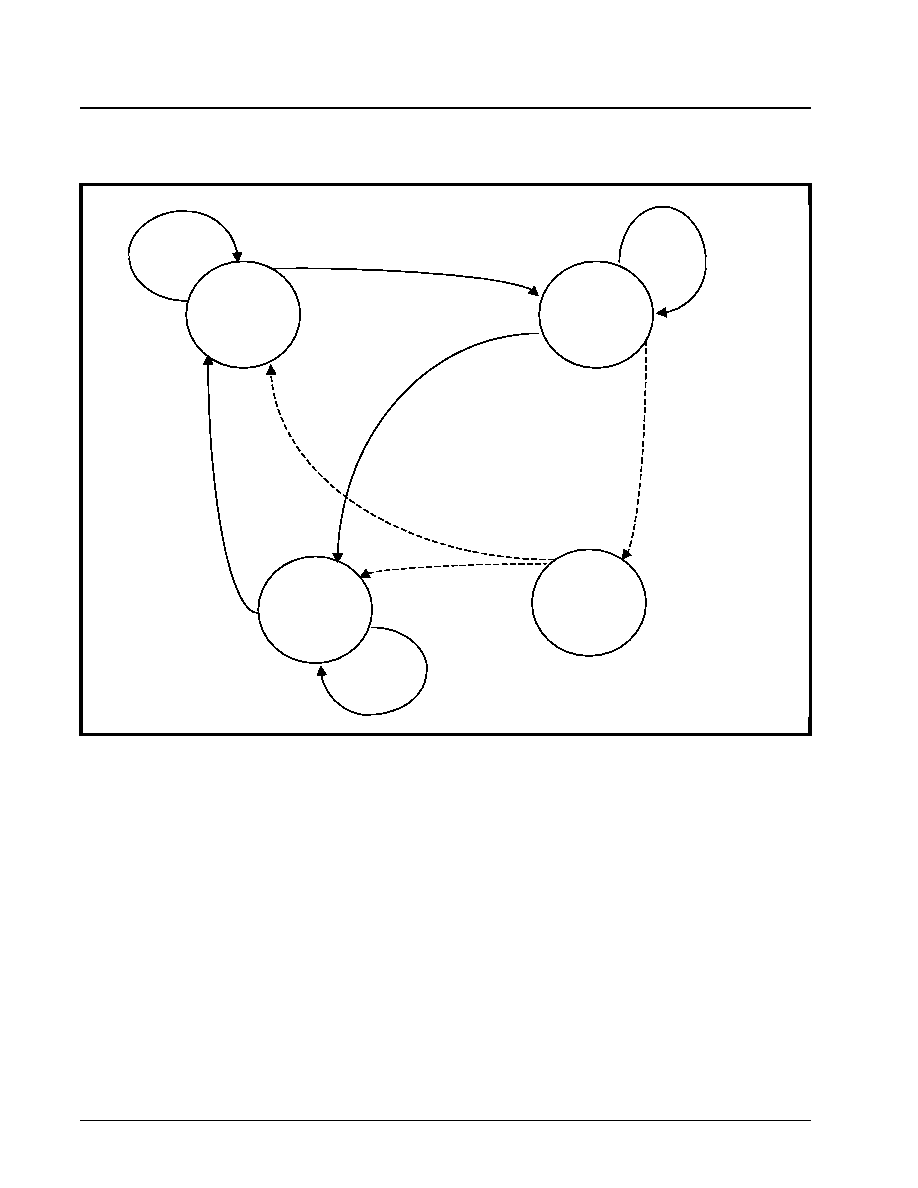

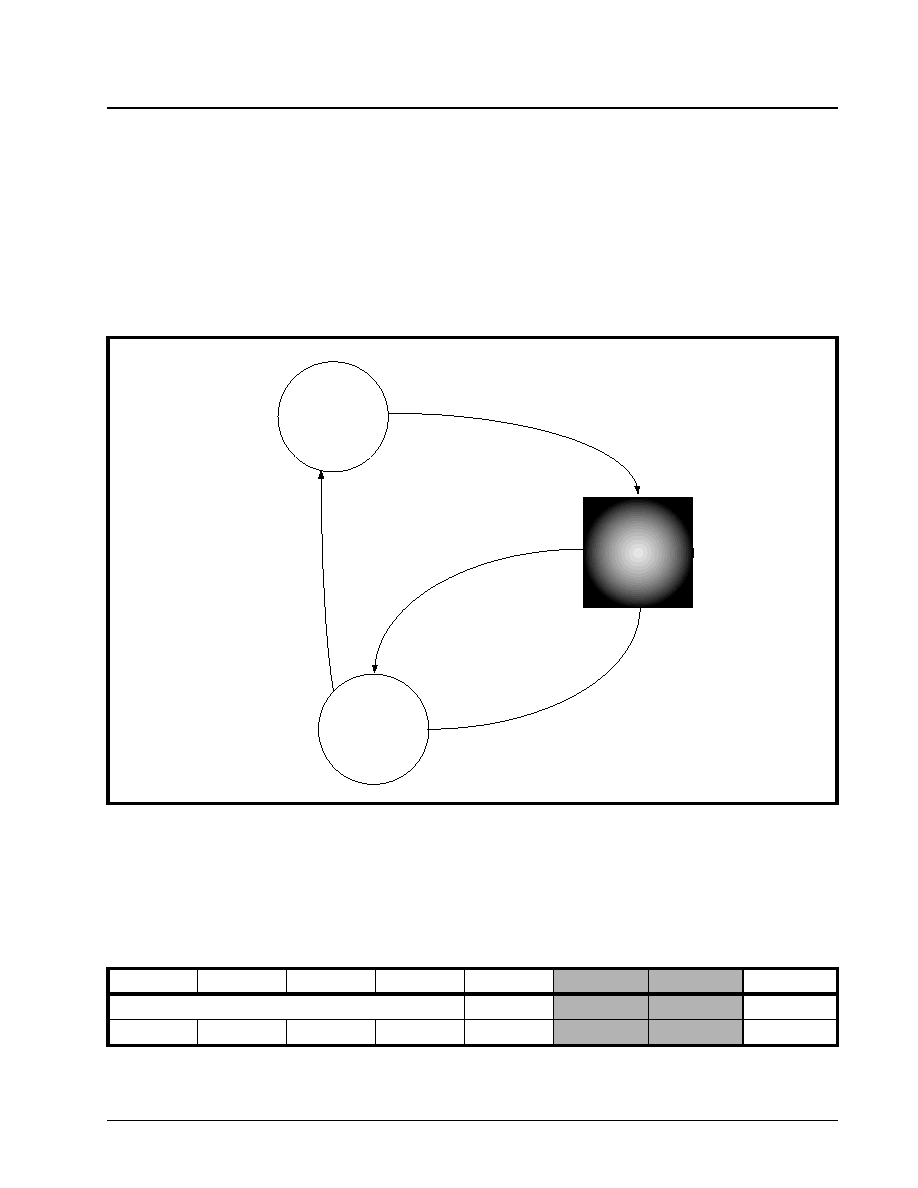

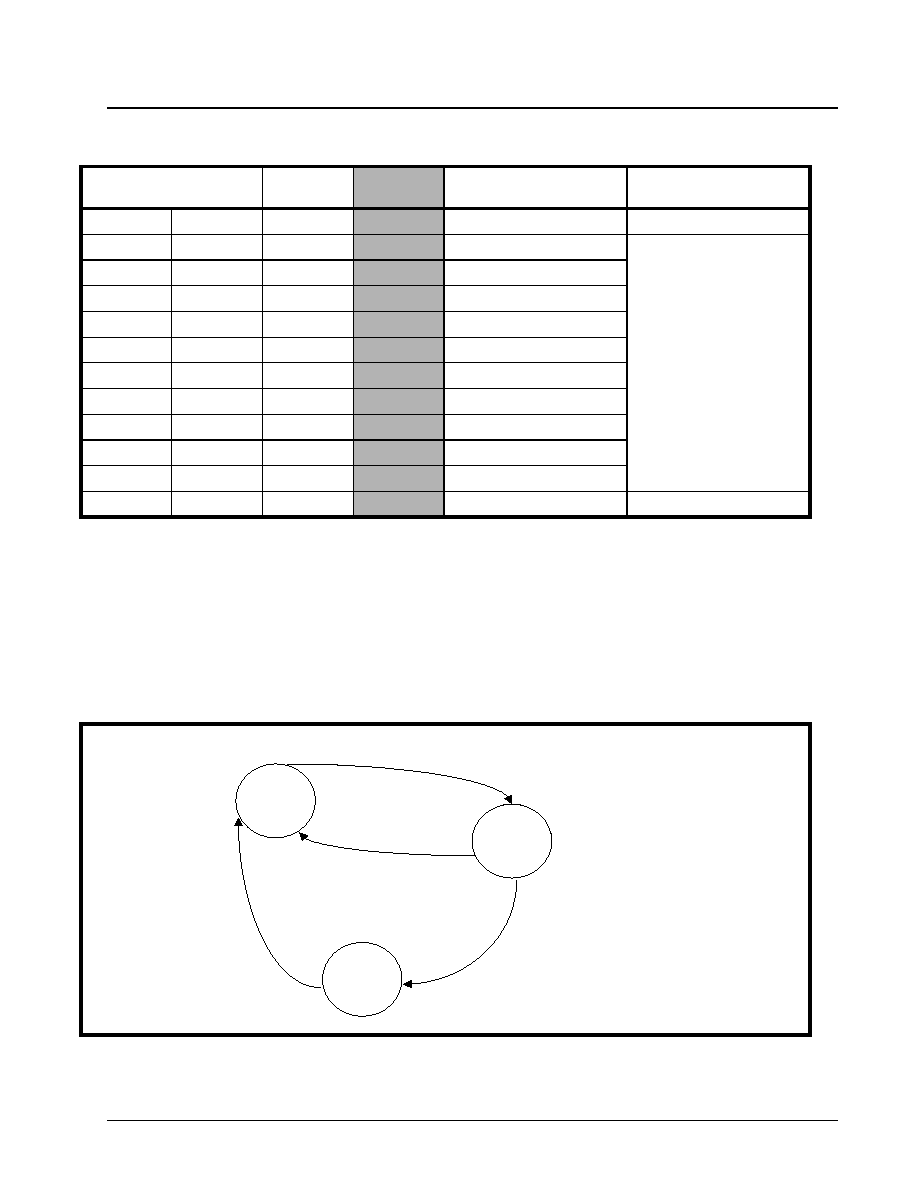

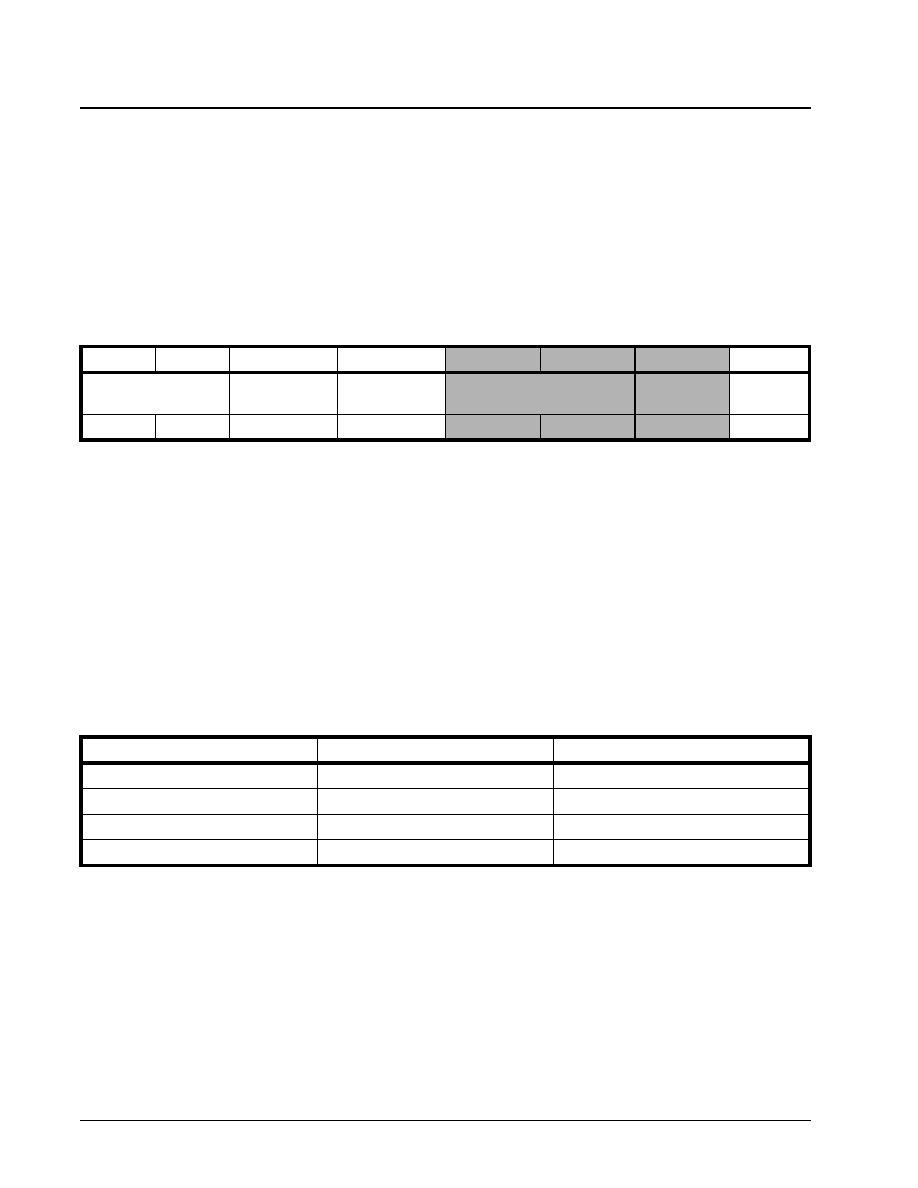

- The HUNT State

- The PRE-SYNC State

- The SYNC State

- Rx CP Interrupt Status Register (Address = 4Eh)

- The SYNC State

- RxCP Configuration Register (Address = 4Ch)

- The Overall Cell Filtering/Processing Approach within the Receive Cell Processor block

- RxCP Configuration Register (Address = 4Ch)

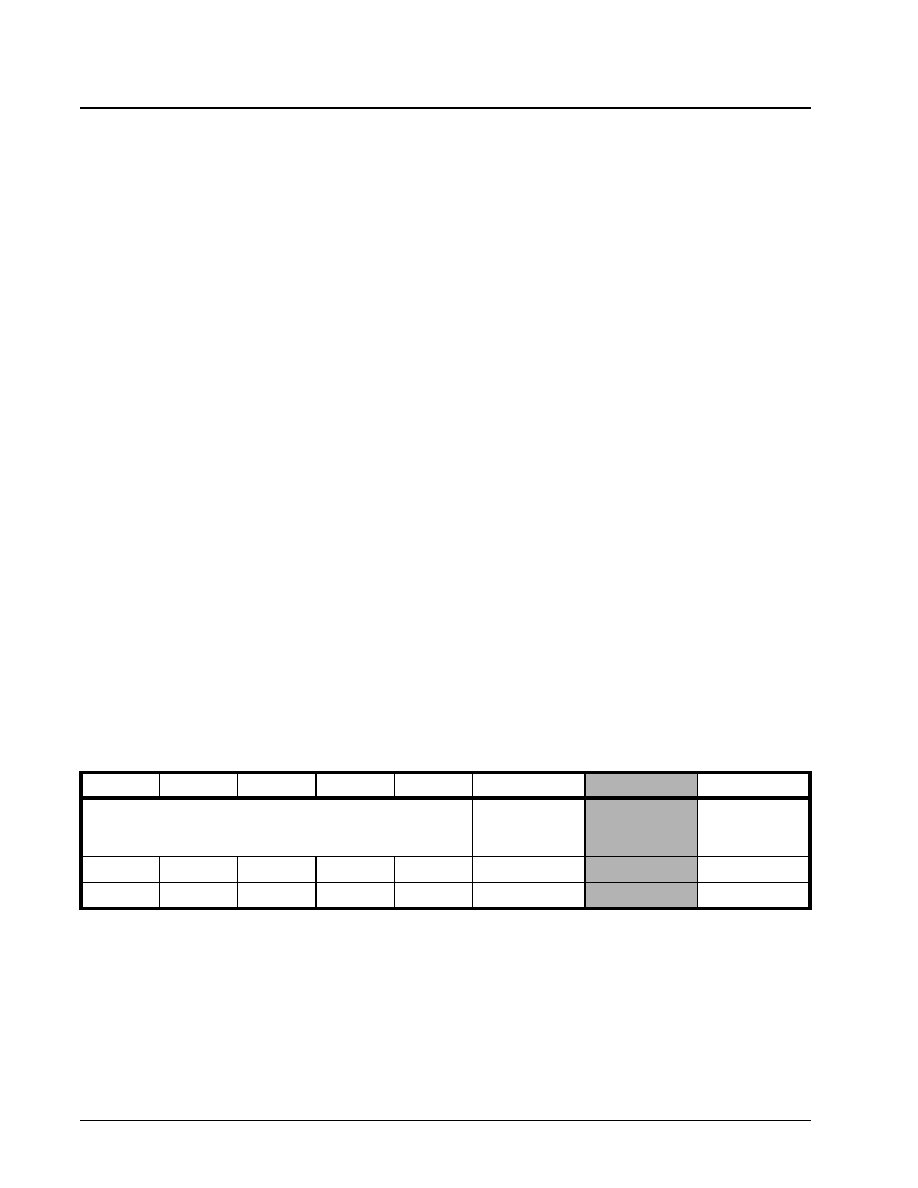

- The çHEC Byte Error Correction/Detectioné �Algorithm

- The çCorrectioné State

- RxCP Configuration Register (Address = 4Ch)

- Monitoring of Single-Bit Errors, during HEC Byte Verification.

- PMON Received Single HEC Error CountÑMSB (Address = 2Eh)

- PMON Received Single HEC Error CountÑLSB (Address = 2Fh)

- Monitoring of Multi-Bit Errors, during HEC Byte Verification

- PMON Received Multiple-Bit HEC ErrorÑMSB (Address = 30h)

- PMON Received Multiple-Bit HEC ErrorÑLSB (Address = 31h)

- The çDetectioné State

- RxCP Additional Configuration Register (Address = 4Dh)

- Bit 1ÑCorrection (Mode) Enable

- Bits 2 and 3ÑCorrection Threshold [1, 0]

- Filtering of Cells with HEC Byte Errors

- RxCP Configuration Register (Address = 4Ch)

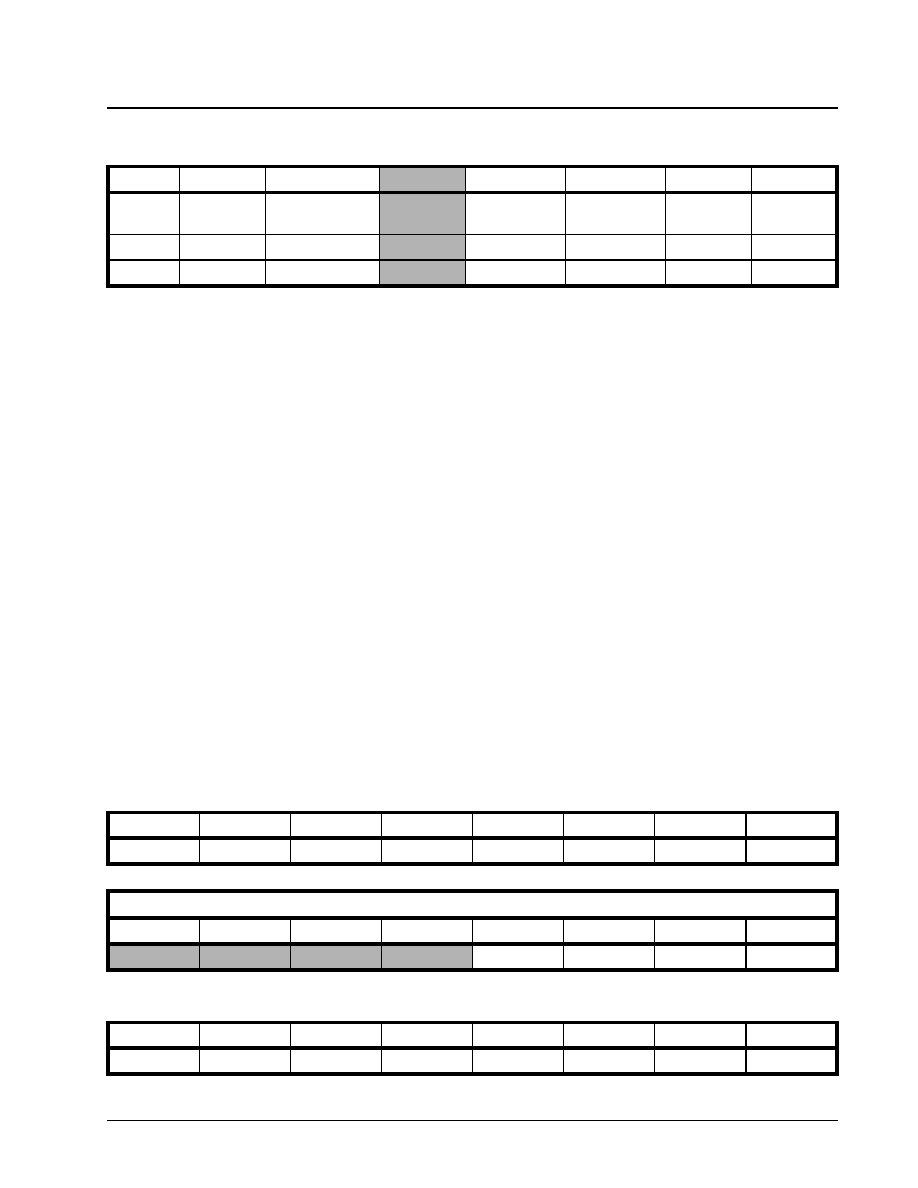

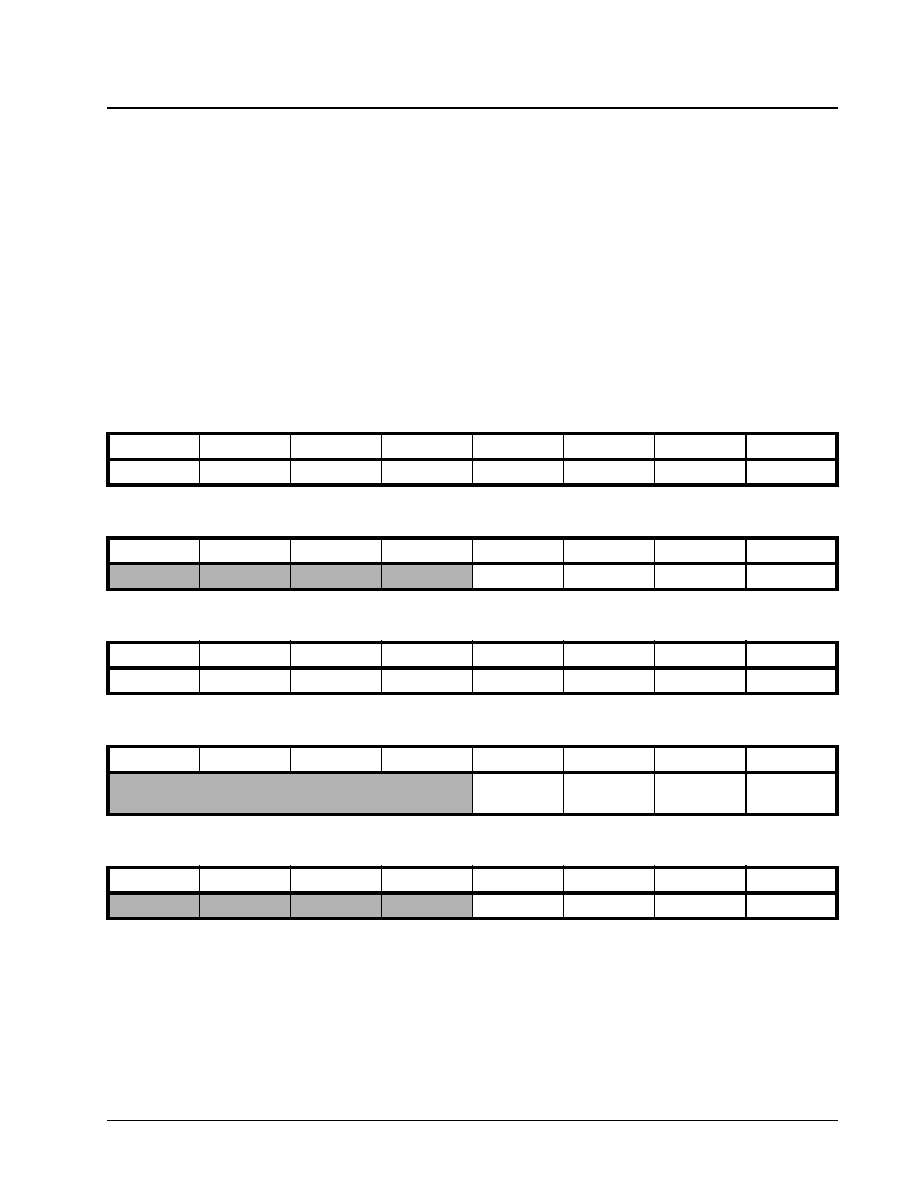

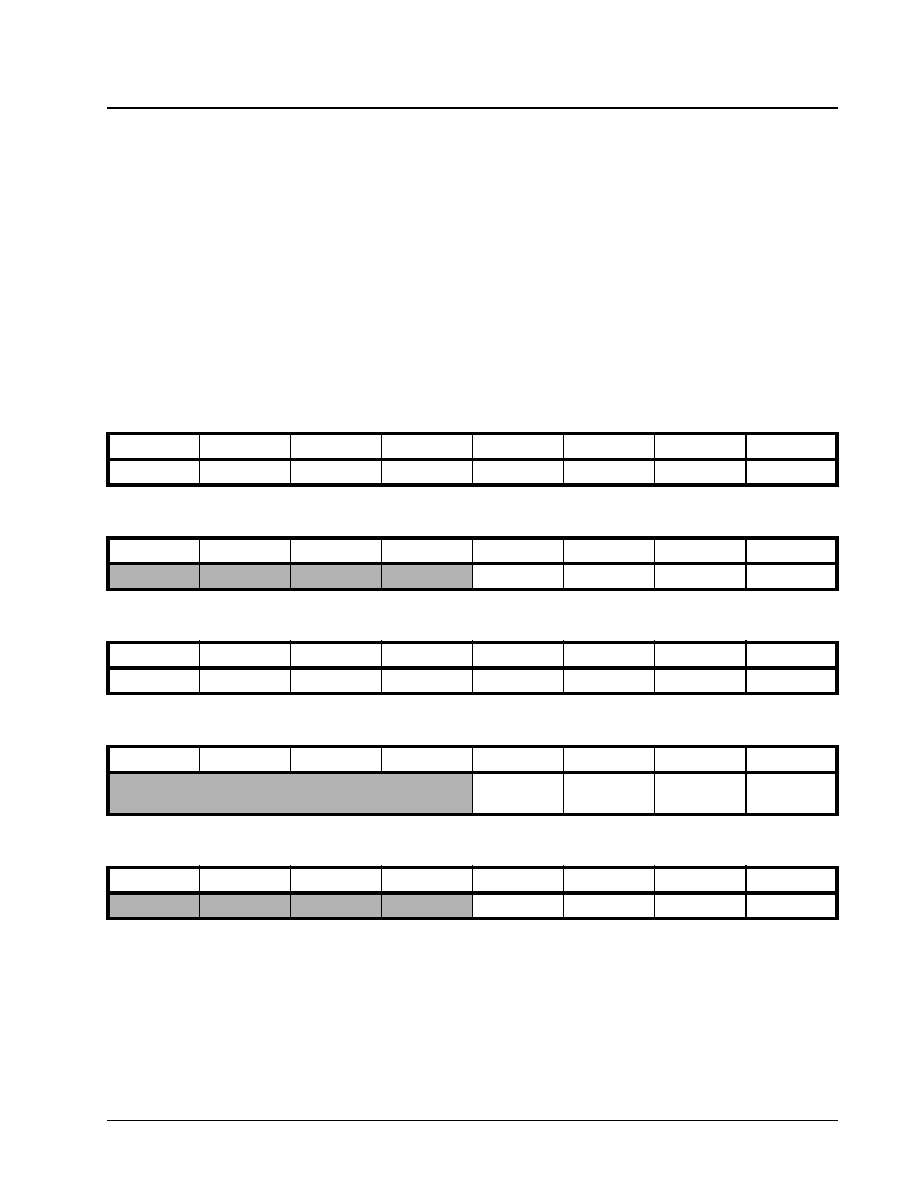

- ExampleÑIdle Cell Filtering

- Content of Header Byte-1 (of Incoming Cell)

- Content of çRx CP Idle Cell Mask Header Byte-1 Register

- Content of çRx CP Idle Cell Header Byte-1 Register

- Comments

- Results of Comparison

- Rx CP Idle Cell Pattern Header Byte-1 Register (Address = 50h)

- Rx CP Idle Cell Pattern Header Byte-2 Register (Address = 51h)

- Rx CP Idle Cell Pattern Header Byte-3 Register (Address = 52h)

- Rx CP Idle Cell Pattern Header Byte-4 Register (Address = 53h)

- Rx CP Idle Cell Mask HeaderÑByte 1 (Address = 54h)

- Rx CP Idle Cell Mask HeaderÑByte 2 (Address = 55h)

- Rx CP Idle Cell Mask HeaderÑByte 3 (Address = 56h)

- Rx CP Idle Cell Mask HeaderÑByte 4 (Address = 57h)

- PMON Received Idle Cell CountÑMSB (Address = 32h)

- PMON Received Idle Cell CountÑLSB (Address = 33h)

- Disable the User-Cell Filter

- RxCP Additional Configuration Register (Address = 4Dh)

- Enable the User Cell Filter

- ExampleÑUser Cell Filtering

- Content of Header Byte-1 (of Incoming User Cell)

- Content of çRx CP User Cell Filter Mask Header Byte-1 Register

- Content of çRx CP User Cell Filter Pattern Header Byte-1 Register

- Comments

- Resulting çUser Cell Fiilteré Pattern for Header Byte-1

- User Cell Filter Header Byte Pattern Registers

- User Cell Filter Mask Registers

- How the Receive Cell Processor handles Segment Type OAM Cells

- RxCP Configuration Register (Address = 4Ch)

- How the Receive Cell Processor Handles End-to- End type OAM Cells

- Monitoring the Number of User/OAM Cells

- PMON Received Valid Cell CountÑMSB (Address = 34h)

- PMON Received Valid Cell CountÑLSB (Address = 35h)

- PMON Discarded Cell CountÑMSB (Address = 36h)

- PMON Discarded Cell CountÑLSB (Address = 37h)

- RxCP Configuration Register (Address = 4Ch)

- The Receive Cell Processorês Handling of the �Data Path Integrity Test pattern

- RxCP Configuration Register (Address = 4Ch)

- UNI Interrupt Status Register (Address = 05h)

- Rx CP Interrupt Status Register (Address = 4Ch)

- Bit 0ÑHEC Byte Error Interrupt Status

- Bit 1ÑçChange in LCD (Loss of Cell Delineation) Stateé Interrupt Status

- Bit 2ÑReceived OAM Cell Interrupt Status

- RxData[15:0]ÑReceive UTOPIA Data Bus Outputs

- RxAddr[4:0]ÑReceive UTOPIA Address Bus Inputs

- RxClkÑReceive UTOPIA Interface BlockÑClock Signal Input Pin

- RxEnB*ÑReceive UTOPIA Data BusÑOutput �Enable Input

- RxPrtyÑReceive UTOPIAÑOdd Parity Bit Output�Pin

- RxSoCÑReceive UTOPIAÑçStart of Cellé �Indicator Output Pin

- RxClav/RxEmptyB*ÑRx FIFO Cell Available/ �RxEmpty*

- UTOPIA Configuration Register: (Address = 6Ah)

- UTOPIA Configuration Register: (Address = 6Ah)

- An Advisory to Users

- Receive UTOPIA FIFO Manager Features and �Options

- UTOPIA Configuration Register: Address = 6Ah

- Receive UTOPIAÑInterrupt/Status Register (AddressÑ6Bh)

- Receive UTOPIA FIFO Status Register (Address = 6Dh)

- RxFIFO Full

- Rx FIFO Empty

- UTOPIA Configuration Register: Address = 6Ah

- Final Comments on Single-PHY Mode

- Receive UTOPIA Address Register: (Address = 6Ch)

- Tx UTOPIA Address Register (Address = 70h)

- Polling Operation

- UNI Interrupt Status Register (Address = 05h)

- Address = 6Bh, Rx UT Interrupt Enable/Status Register

- Bit 0ÖÑRCOCA Interrupt StatusÑReceive UTOPIA Change of Cell Alignment Condition

- Address = 6Bh, Rx UT Interrupt Enable/Status Register

- Bit 1ÑRx FIFO Underflw Interupt StatusÑRxFIFO Underrun Condition

- Address = 6Bh, Rx UT Interrupt Enable/Status Register

- Bit 2ÑRx FIFO Overflw Interrupt StatusÑRxFIFO Overrun Condition

- Address = 6Bh, Rx UT Interrupt Enable/Status Register

- Bit 3ÑRCOCA Interrupt EnableÑReceive UTOPIA Change of Cell Alignment Interrupt Enable

- Bit 4ÑRxFIFO Underflw Interrupt EnableÑ Rx�FIFO Underrun Condition Interrupt Enable

- Bit 5ÑRxFIFO Overflw Interrupt EnableÑRx FIFO Overrun Condition Interrupt Enable

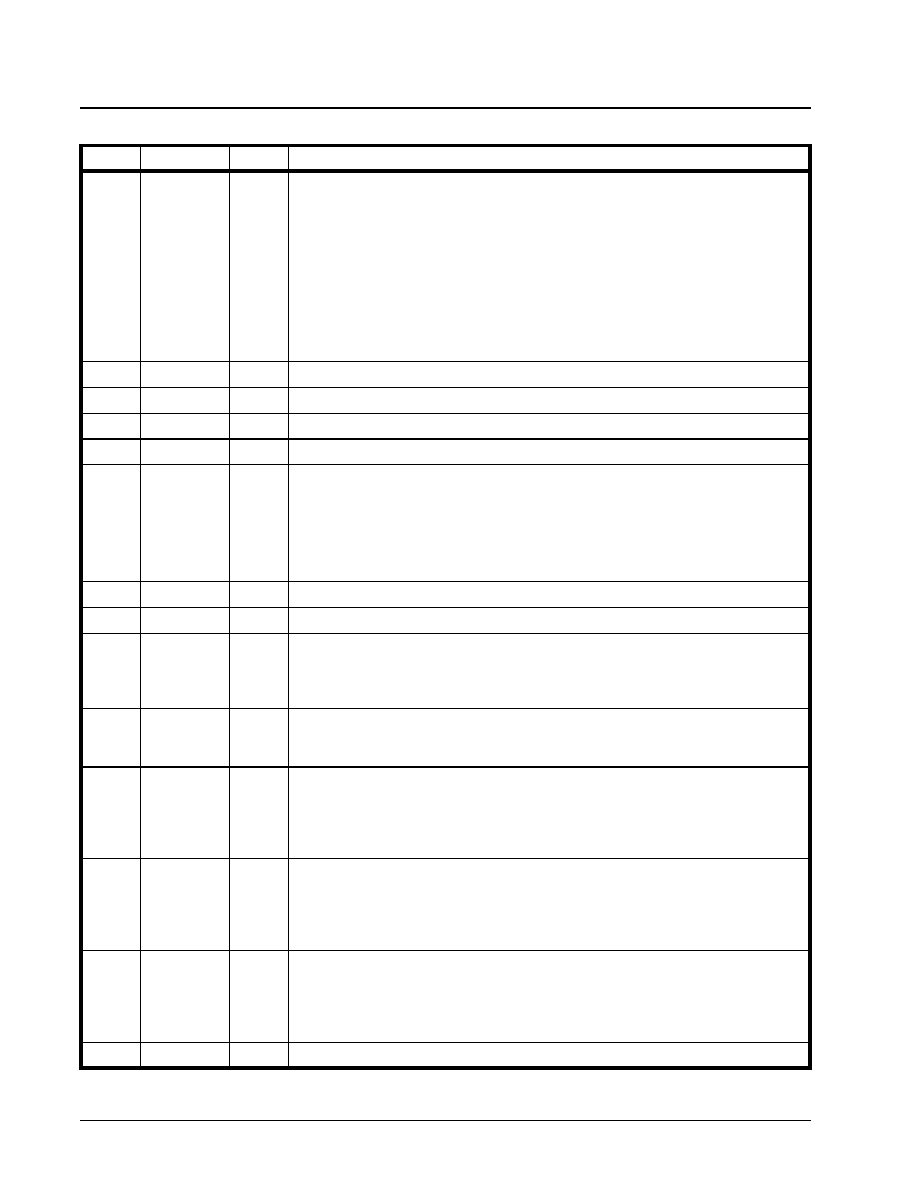

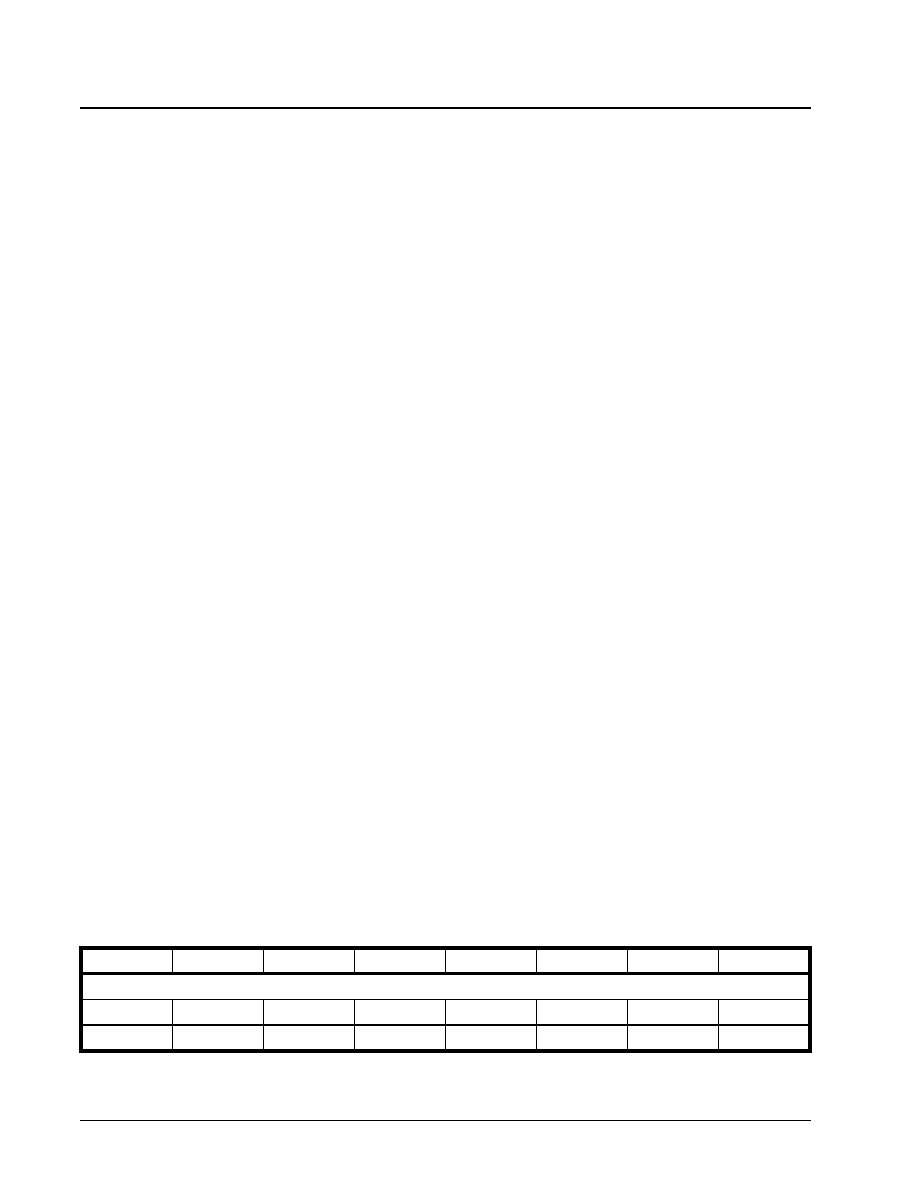

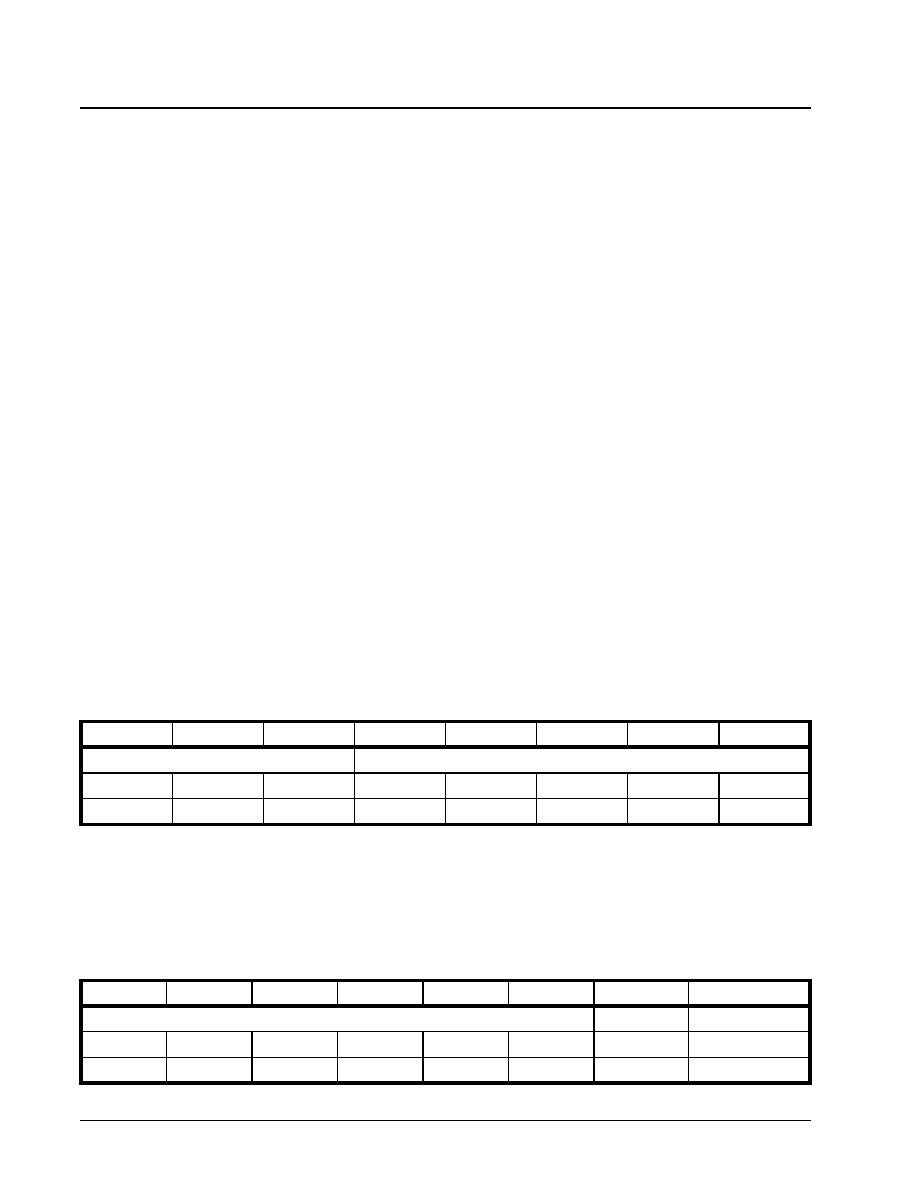

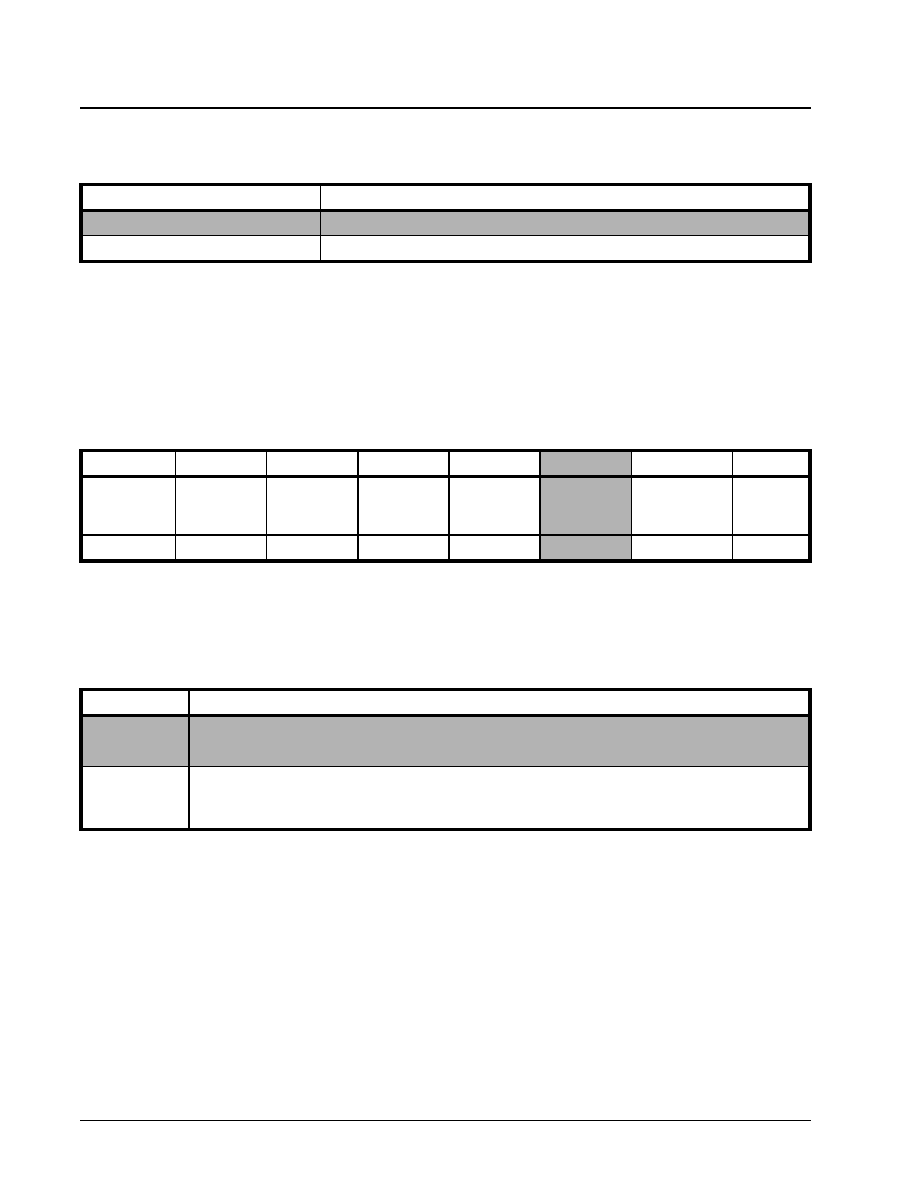

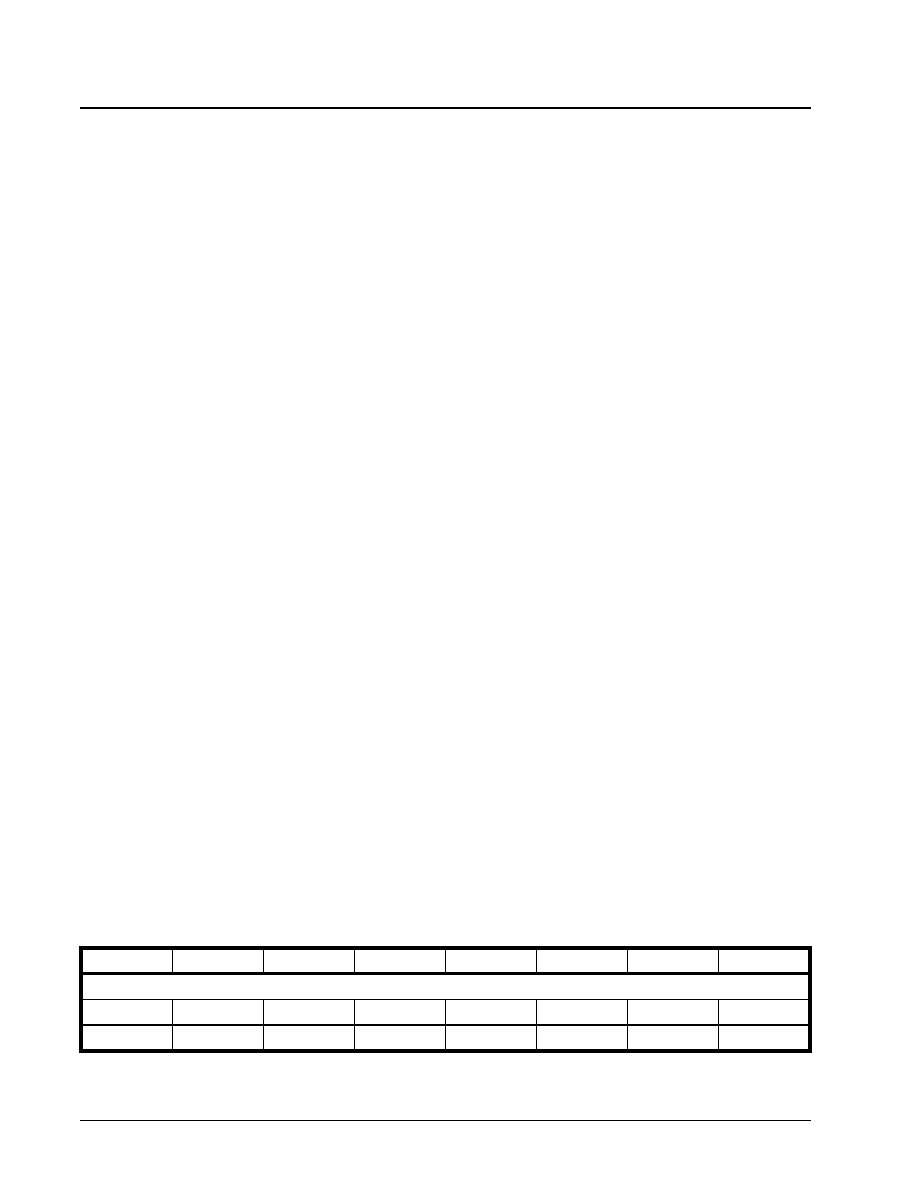

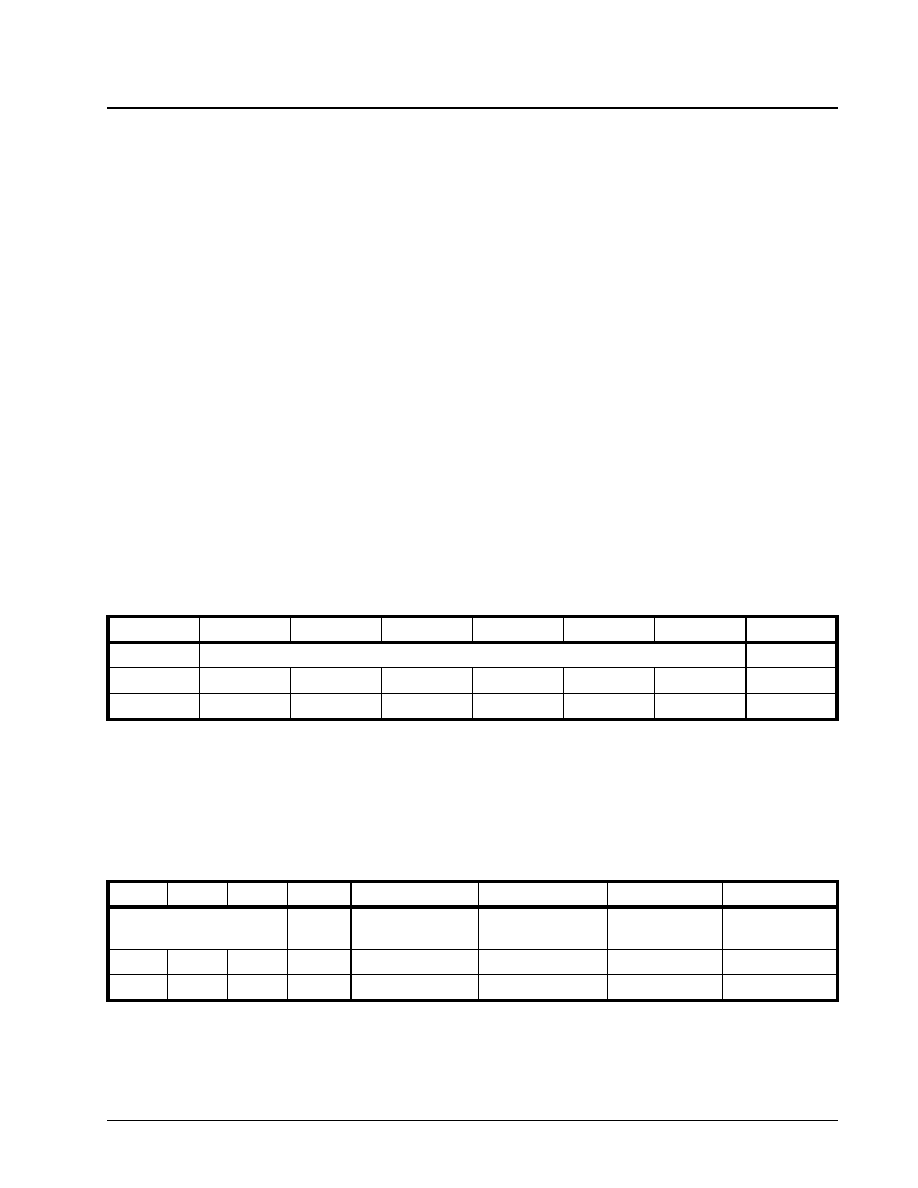

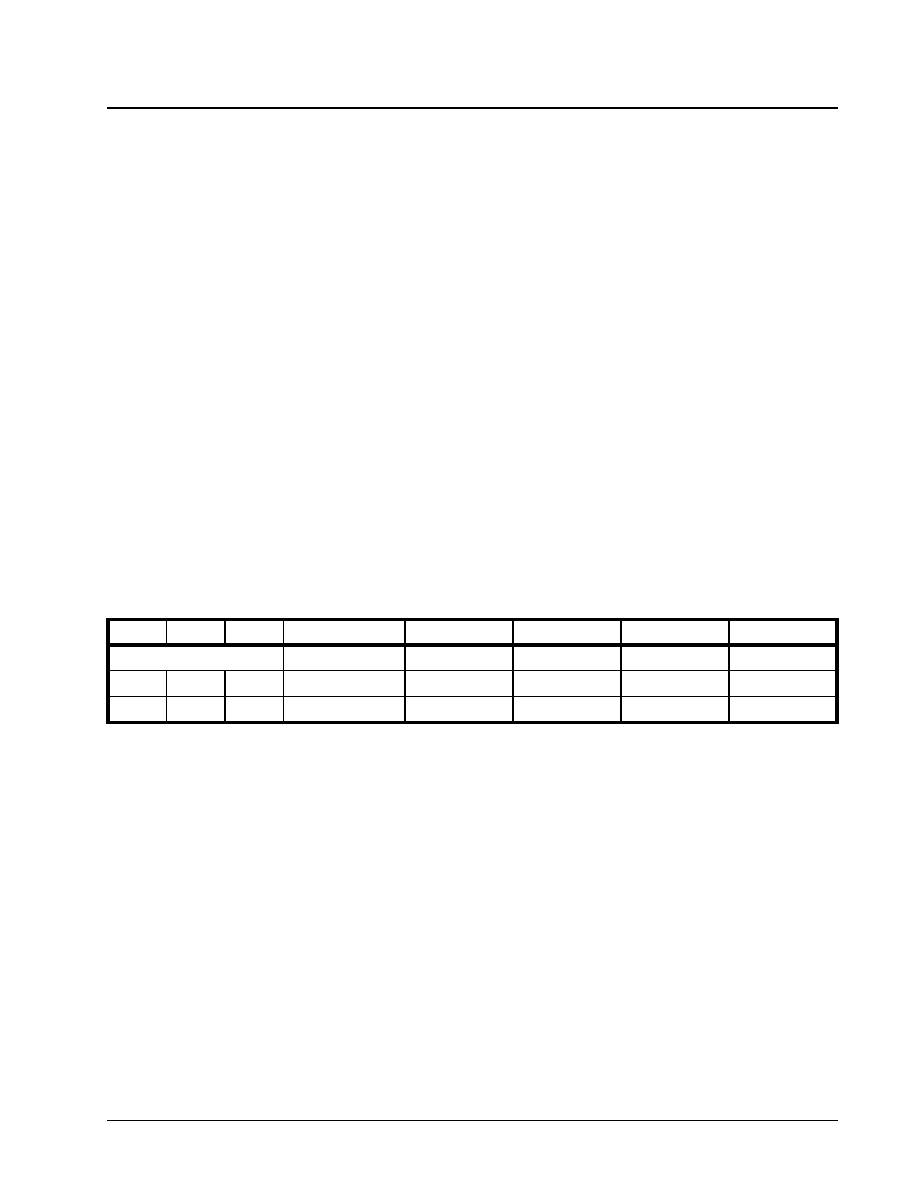

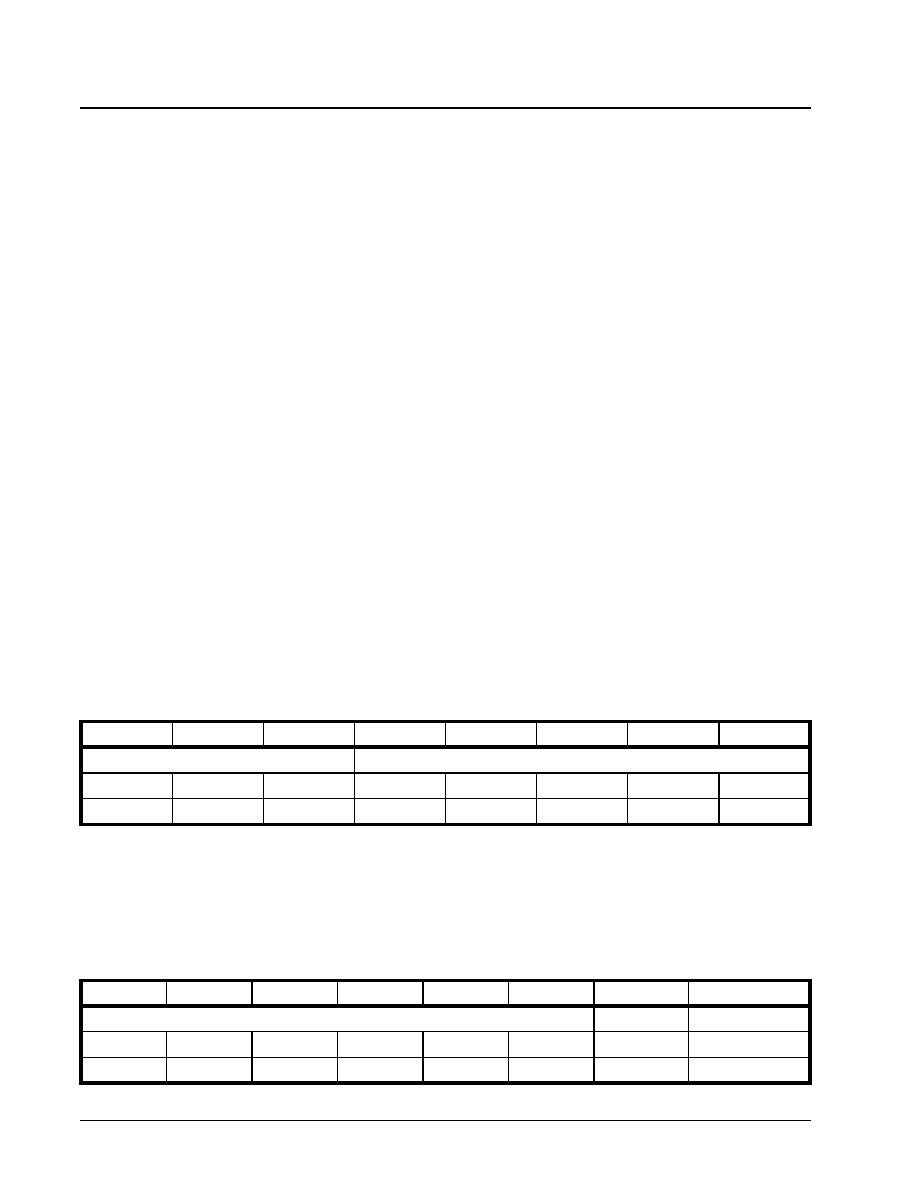

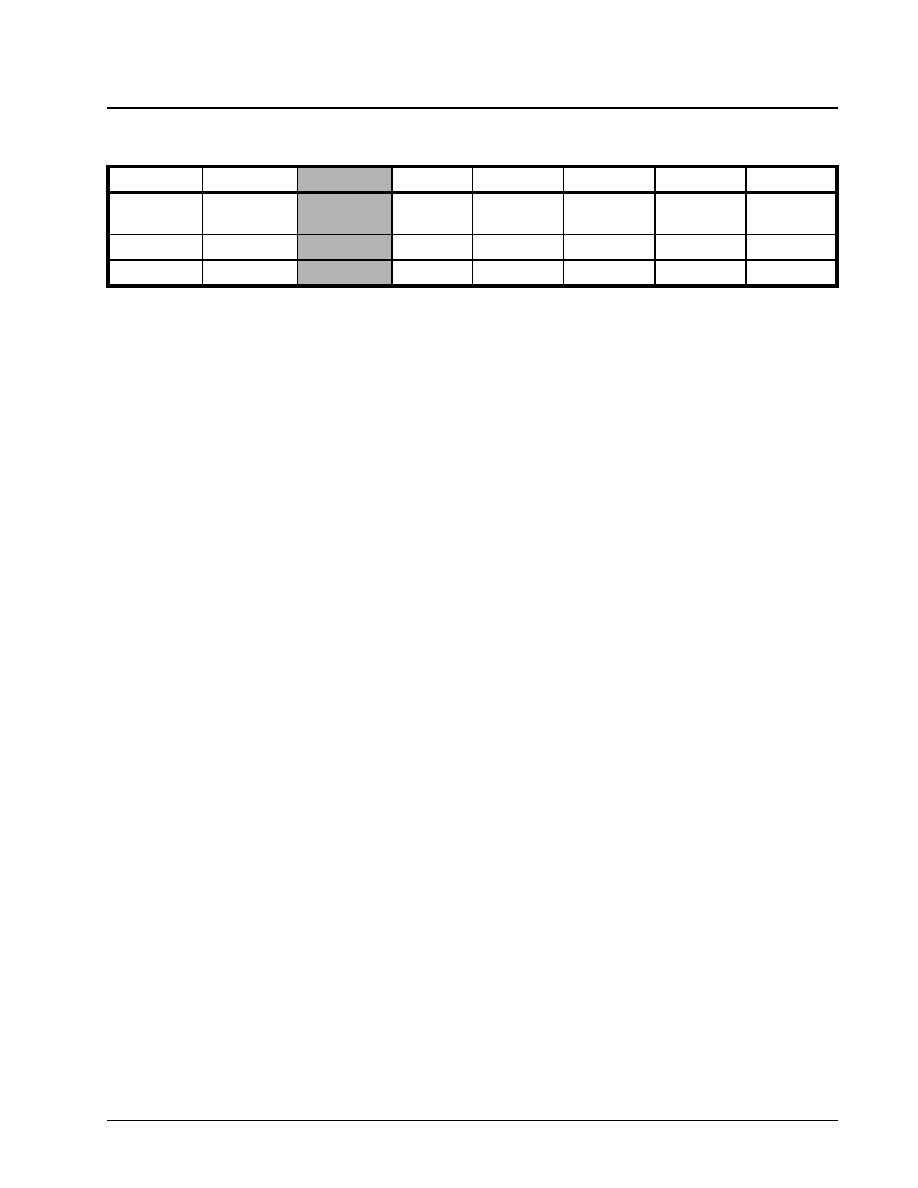

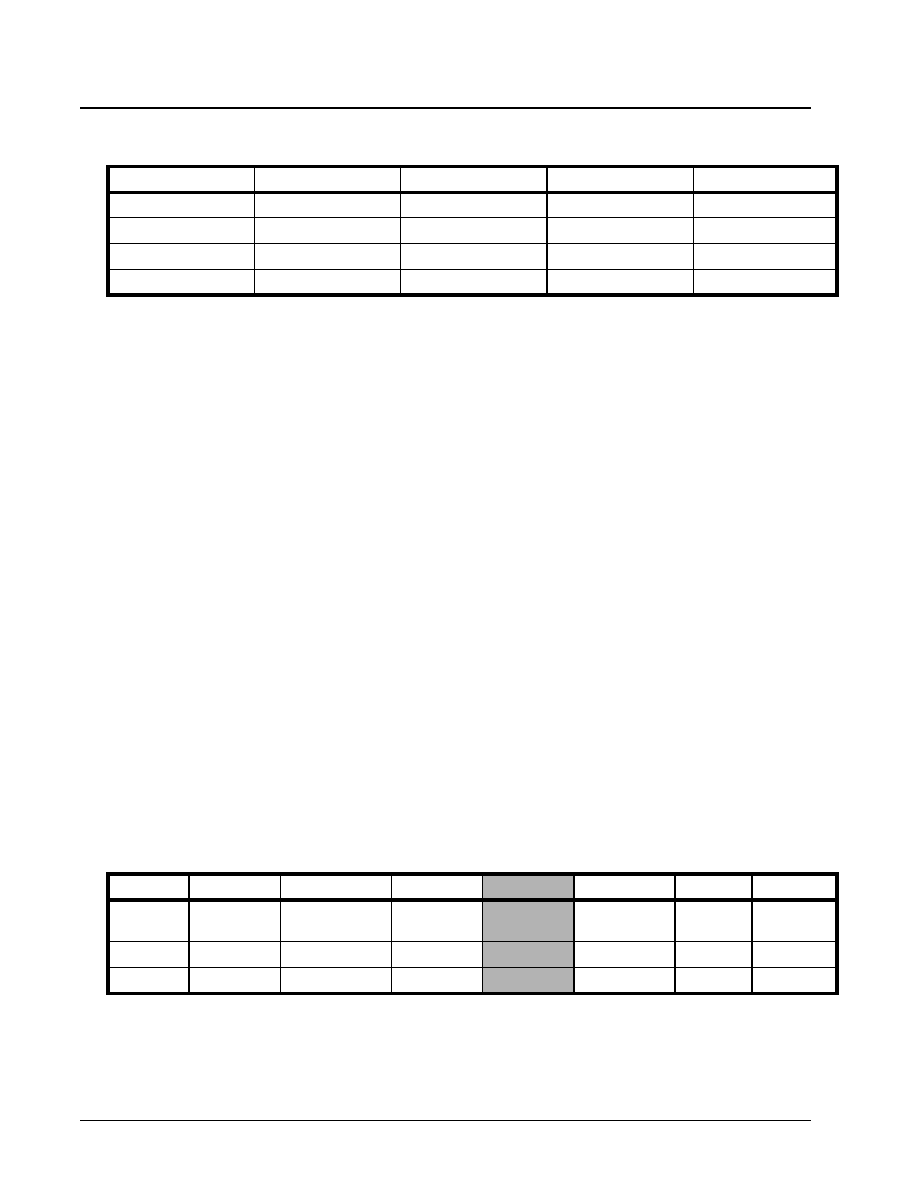

- Ordering Information

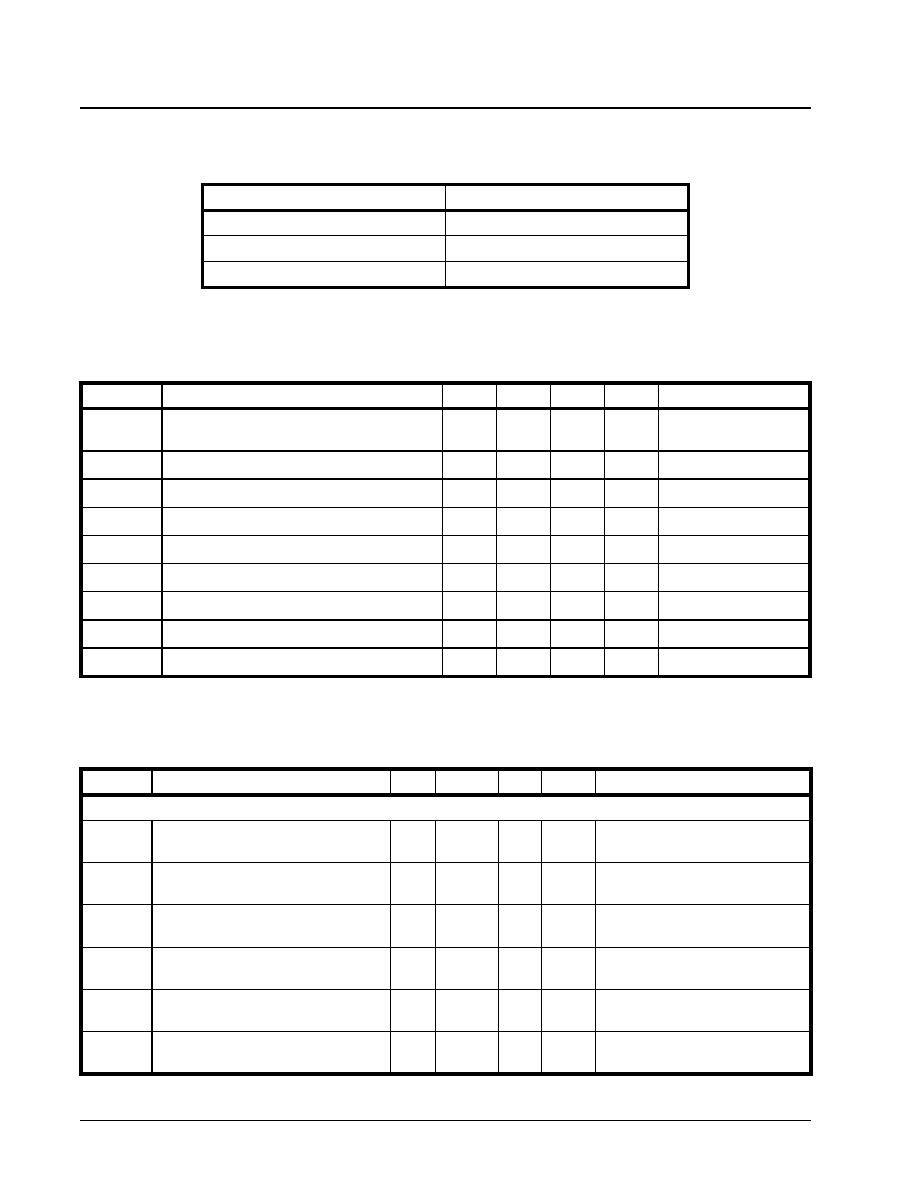

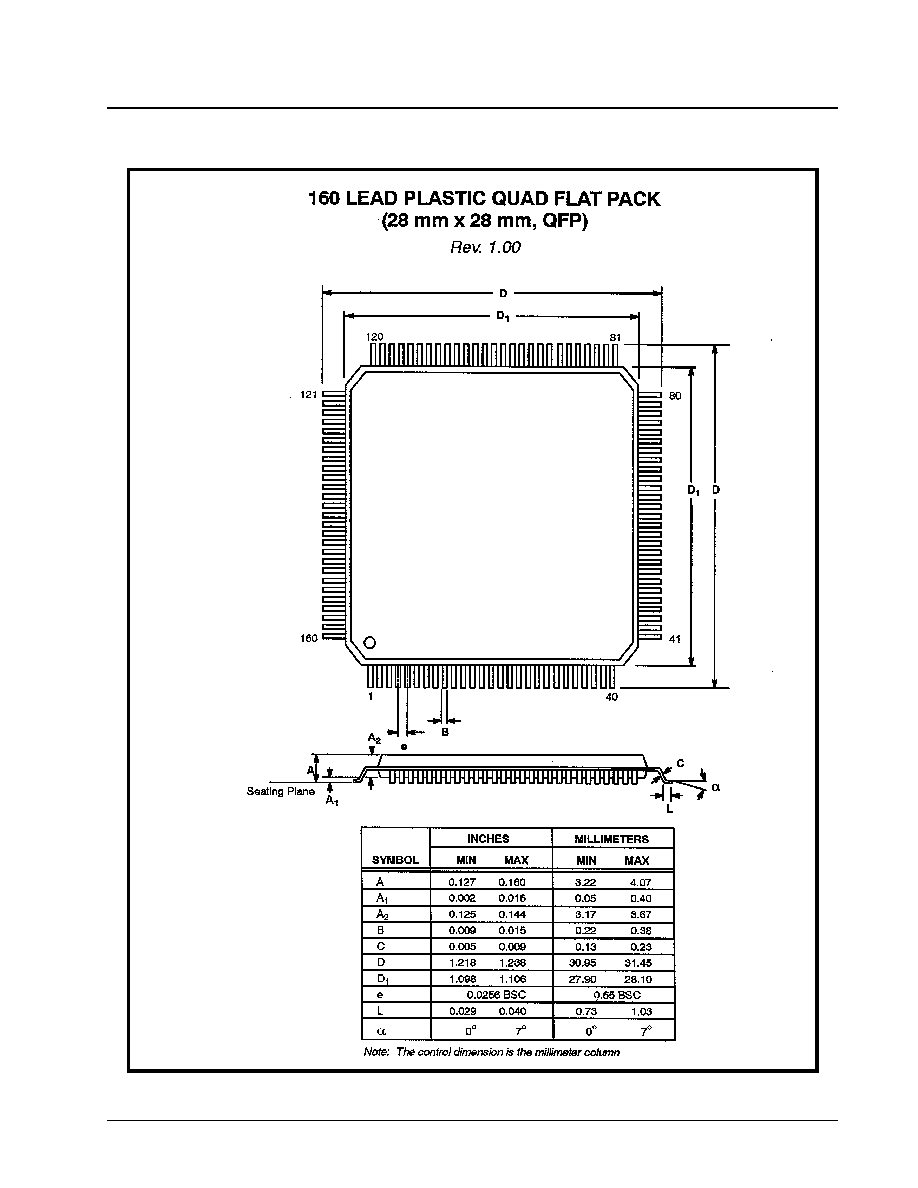

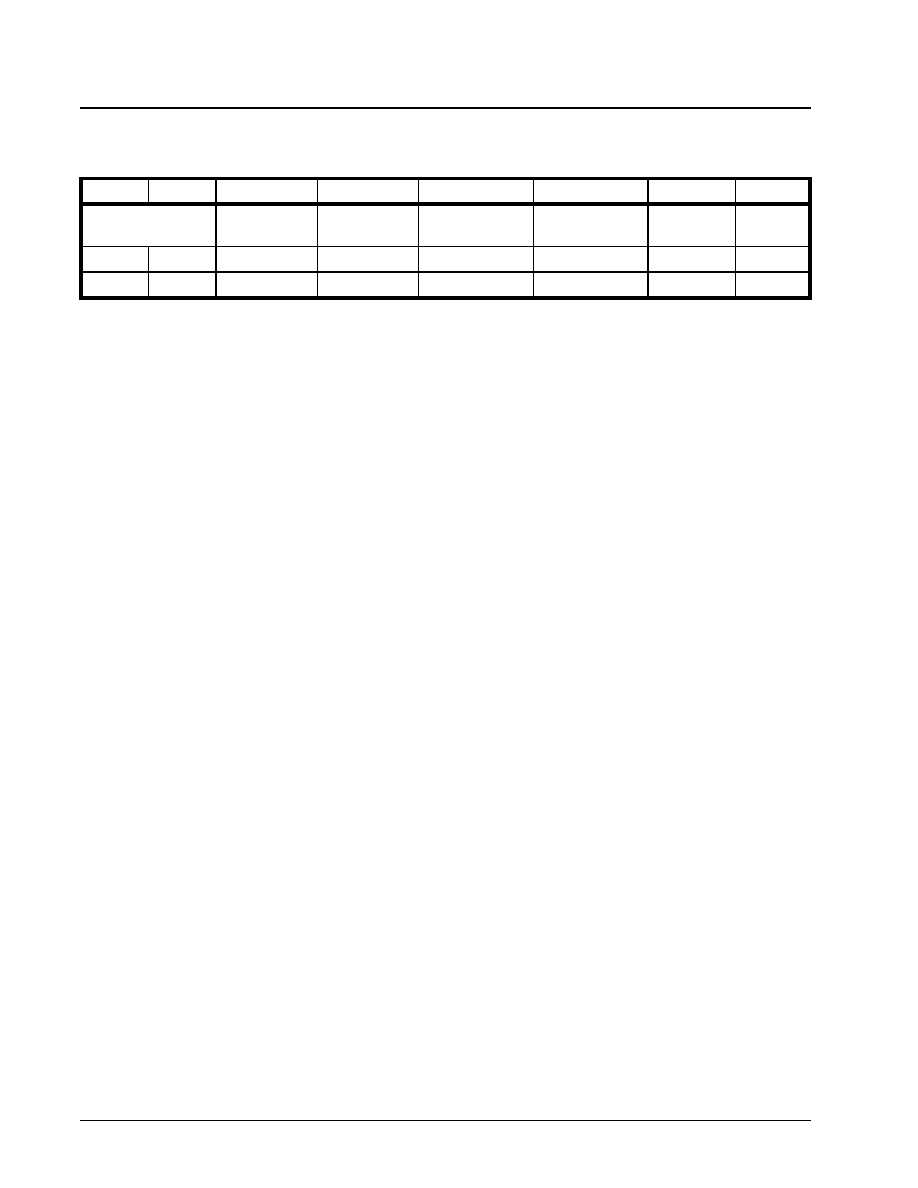

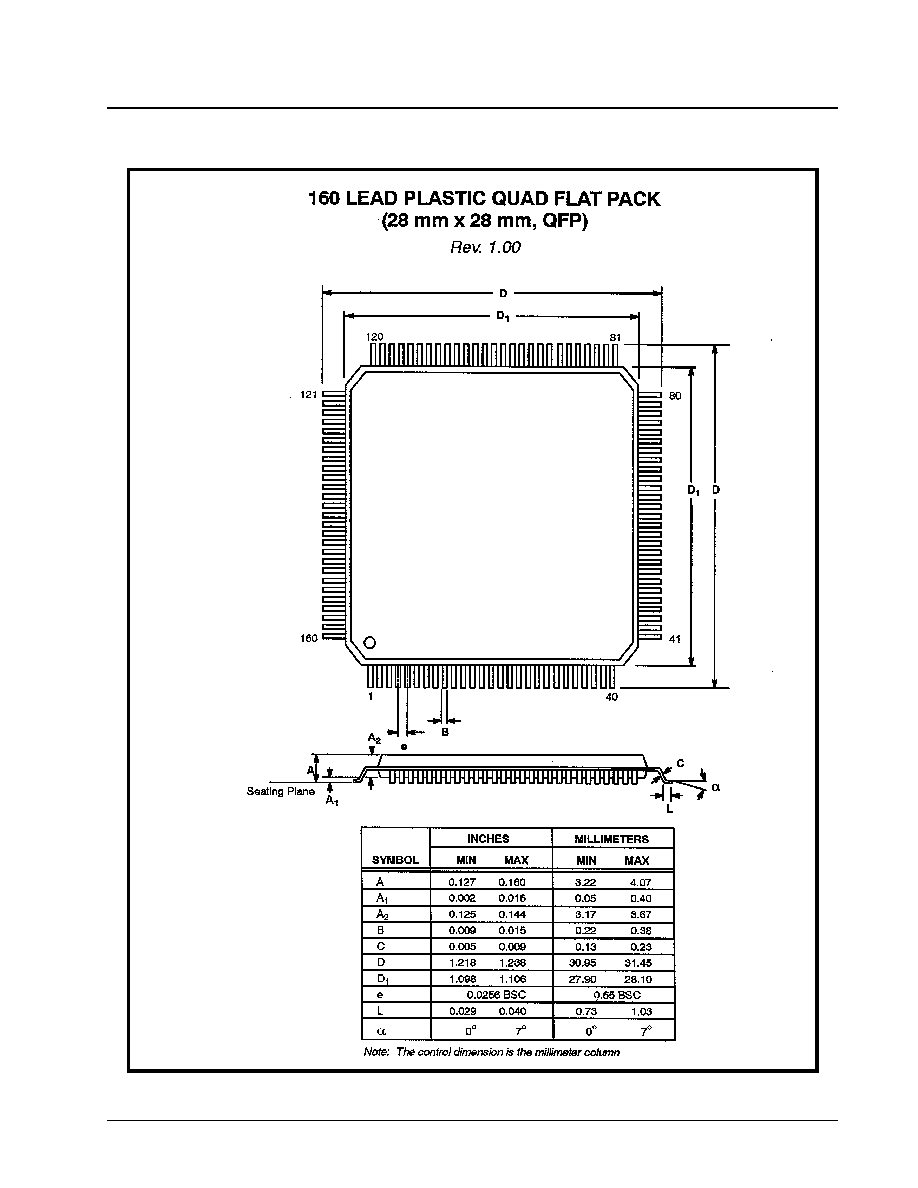

- Package Dimensions

Exar Coporation 48720 Kato Road, Fremont CA, 94538 ∑ (510) 668-7000 ∑ FAX (510) 668-7200 ∑ www.exar.com

·Á

·Á

·Á

·Á

PRELIMINARY

XRT7245

DS3 UNI FOR ATM

DECEMBER 1999

REV. 1.03

GENERAL DESCRIPTION

The XRT7245 DS3 ATM User Network Interface

(UNI) device is designed to provide the ATM Physical

Layer (Physical Medium Dependent and Transmis-

sion Convergence sub-layers) interface for the public

and private networks at DS3 rates. This device pro-

vides full-duplex data flow between two ATM Layer

devices (e.g., ATM Switching equipment) and/or ATM

Adaptation Layer (AAL) devices; over a DS3 Transport

Medium.

The XRT7245 DS3 UNI for ATM incorporates Receive,

Transmit, Microprocessor Interface, Performance Moni-

tor, Test and Diagnostic and Line Interface Unit Scan

Drive functional sections.

FEATURES

∑

Compliant with UTOPIA Level 1and 2, 8 or 16 Bit,

Interface Specification and supports UTOPIA Bus

operating at 25, 33 or 50 MHz

∑

Contains on-chip 16 cell FIFO (configurable in

depths of4, 8, 12 or 16 cells), in the transmit Direc-

tion (TxFIFO)

∑

Contains on-chip Receive OAM Cell Buffer for

reception, filtering and processing of selected User

and OAM Cells

∑

Supports PLCP or ATM Direct Mapping modes

∑

Supports M13 and C-Bit Parity Framing Formats

∑

Supports Line, Cell, and PLCP Loop-backs

∑

Interfaces to 8 or 16 Bit wide Motorola and Intel µPs

and µCs

∑

Available in 160 pin PQFP Package

APPLICATIONS

∑

Private User Network Interfaces

∑

ATM Switches

∑

ATM Routers and Bridges

∑

ATM Concentrators

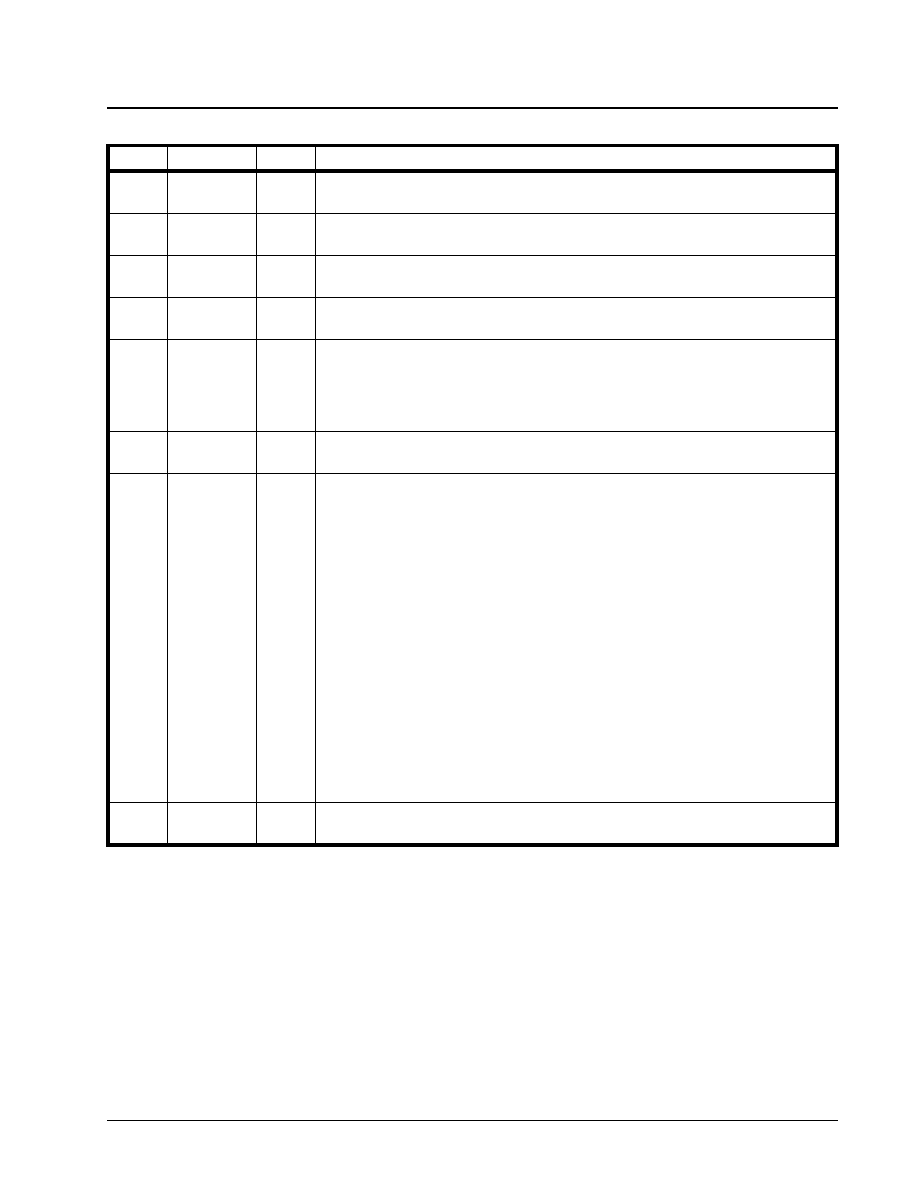

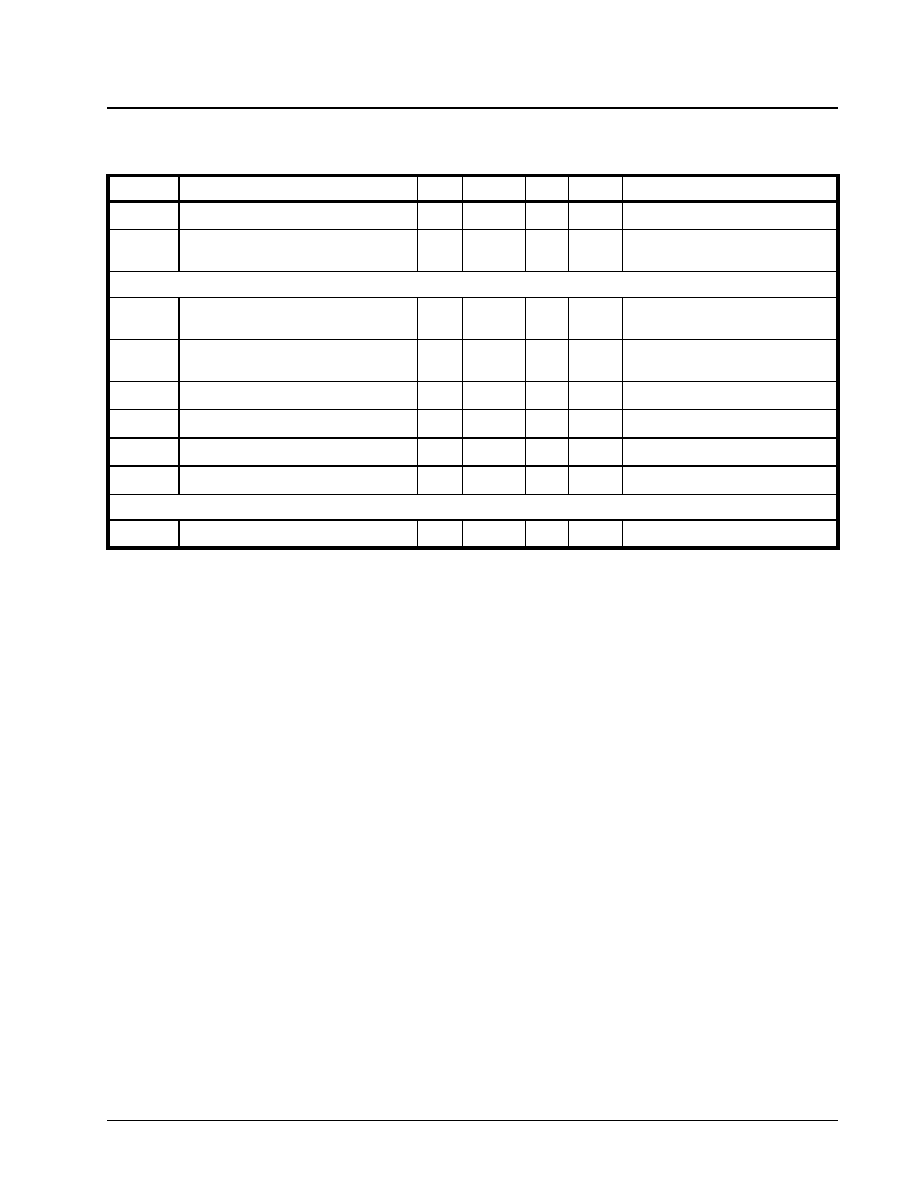

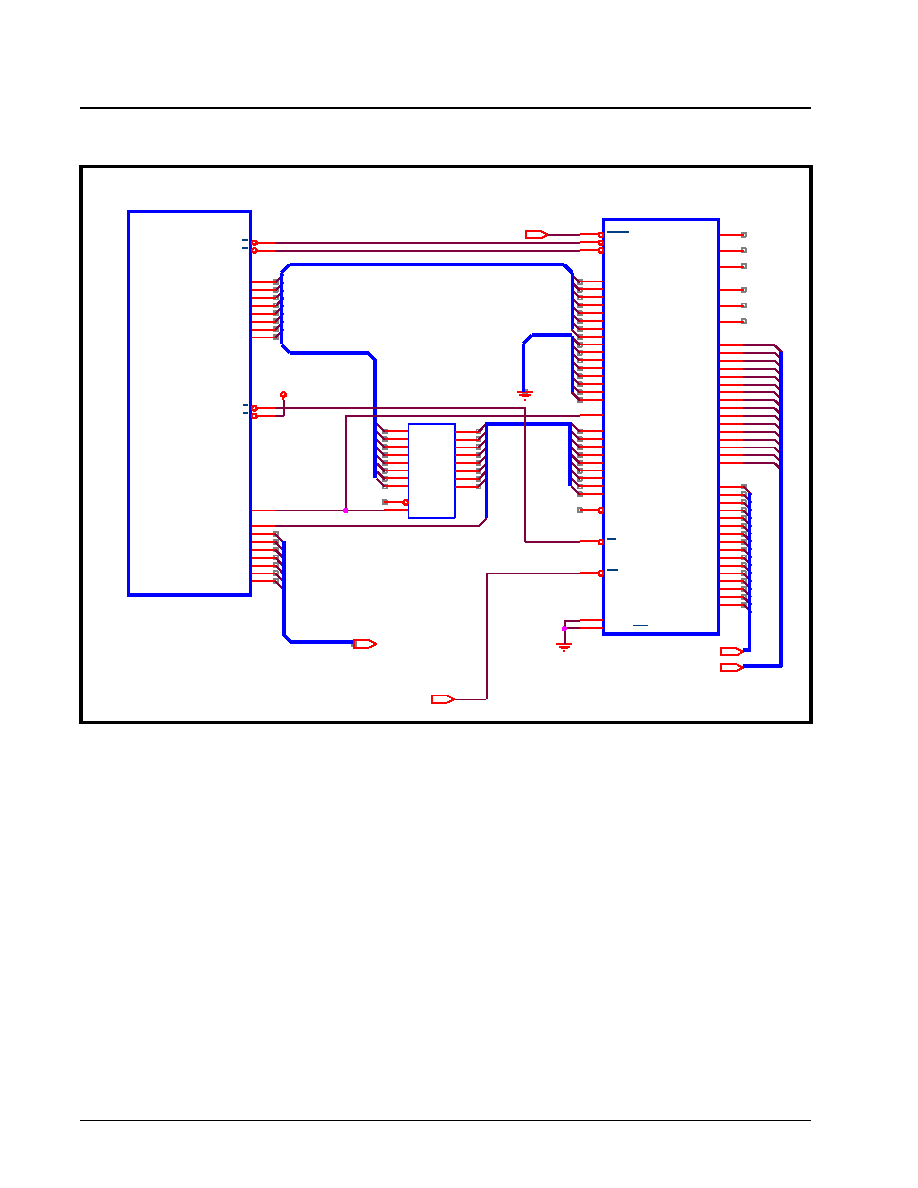

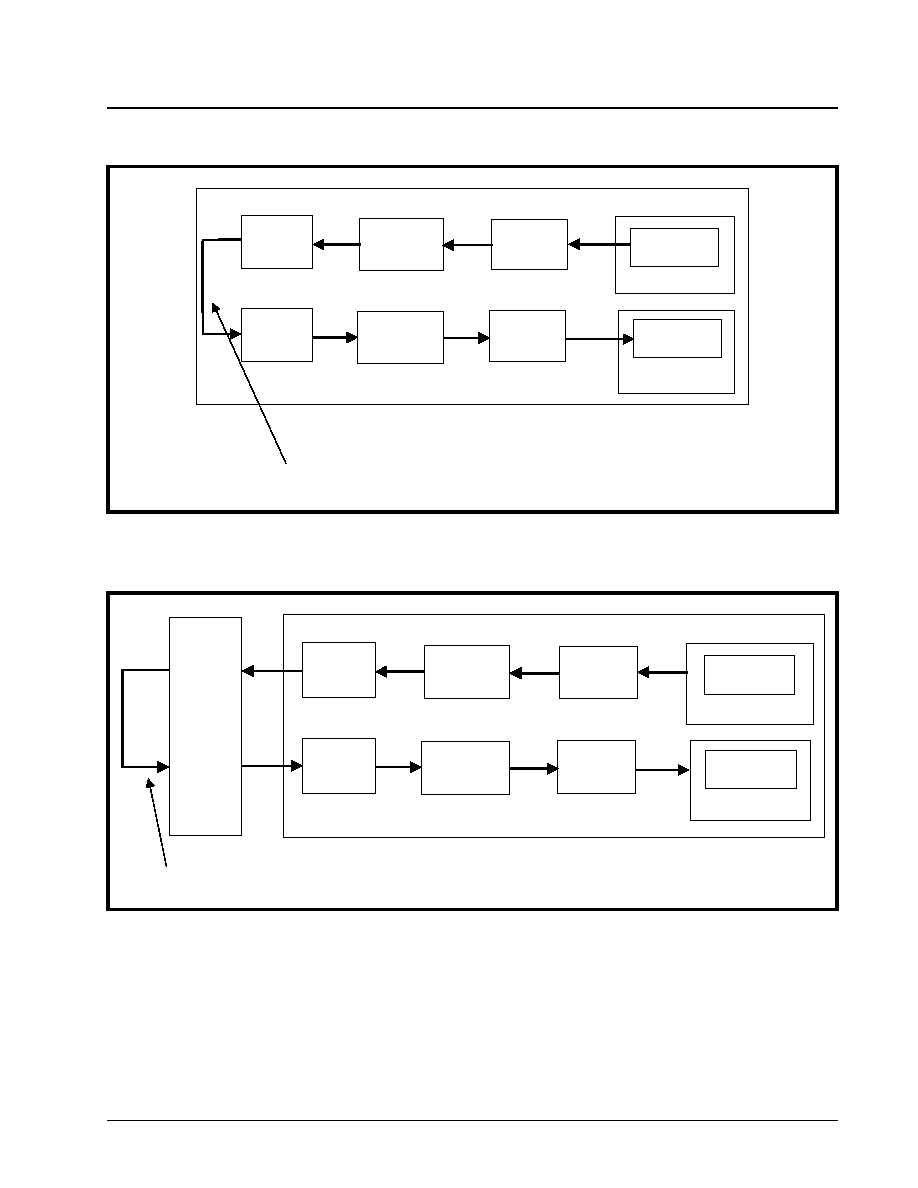

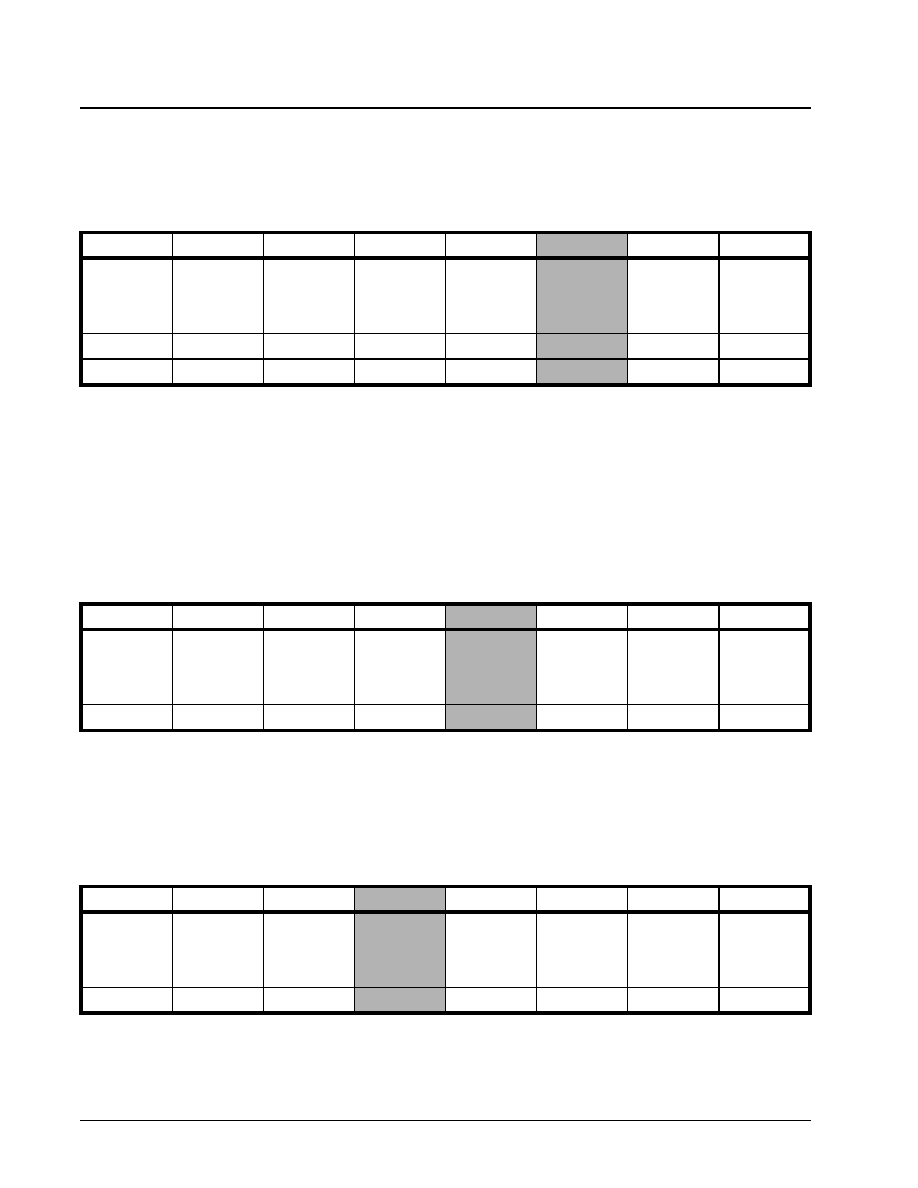

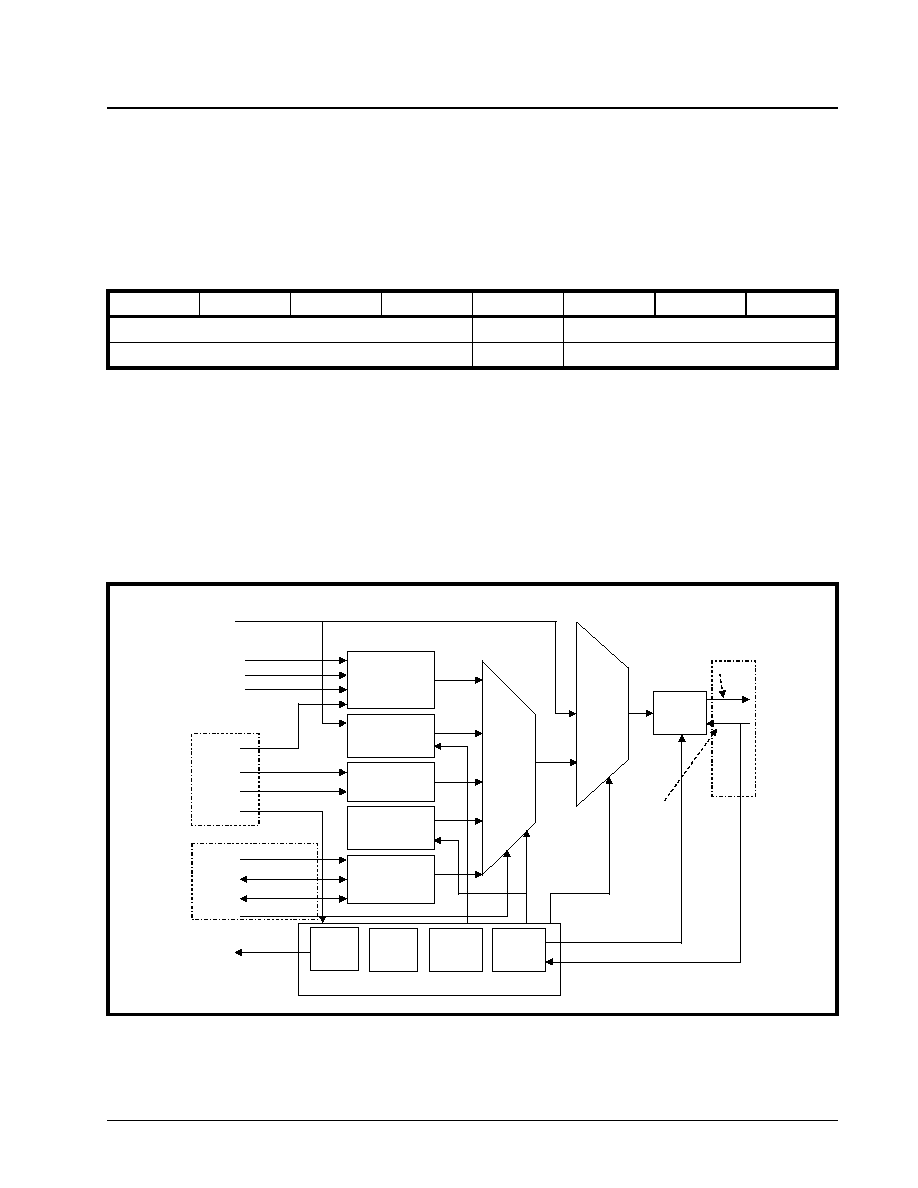

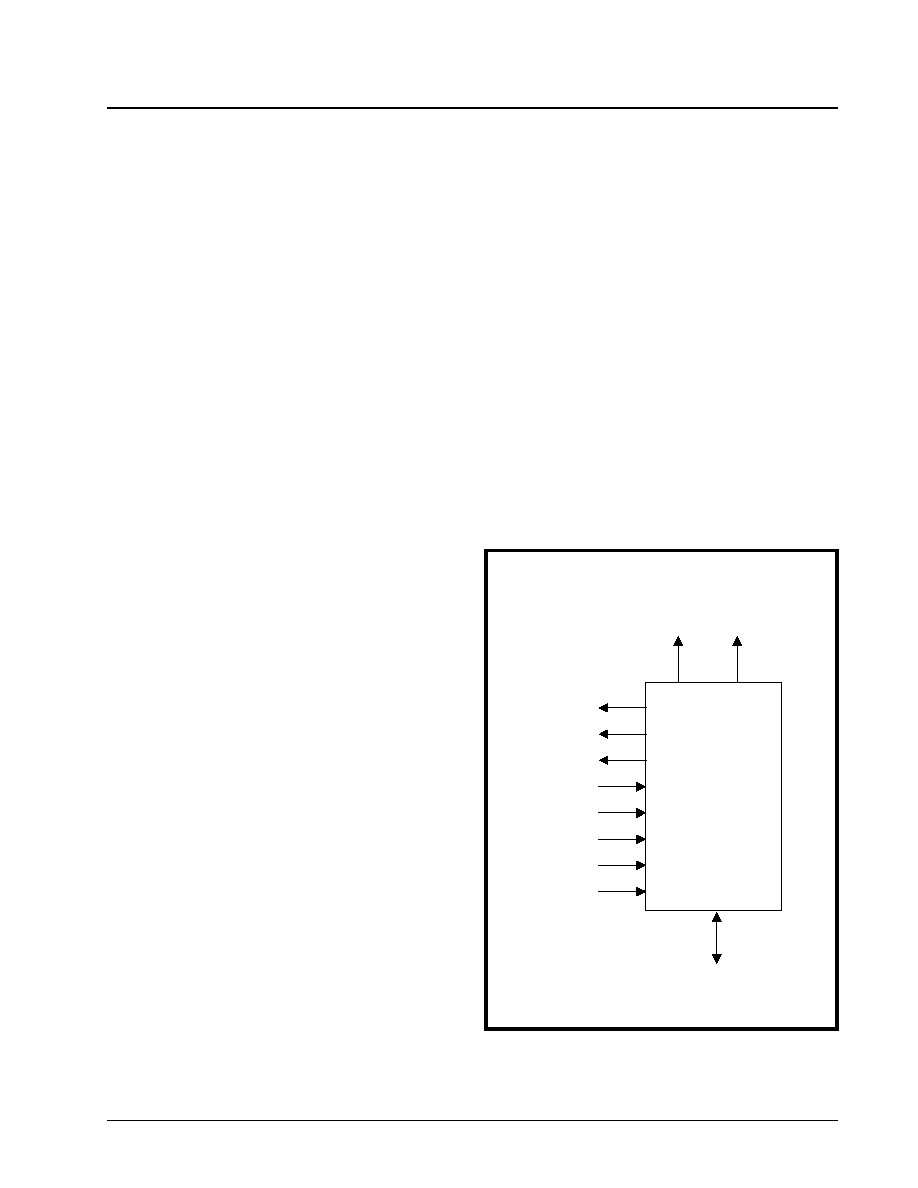

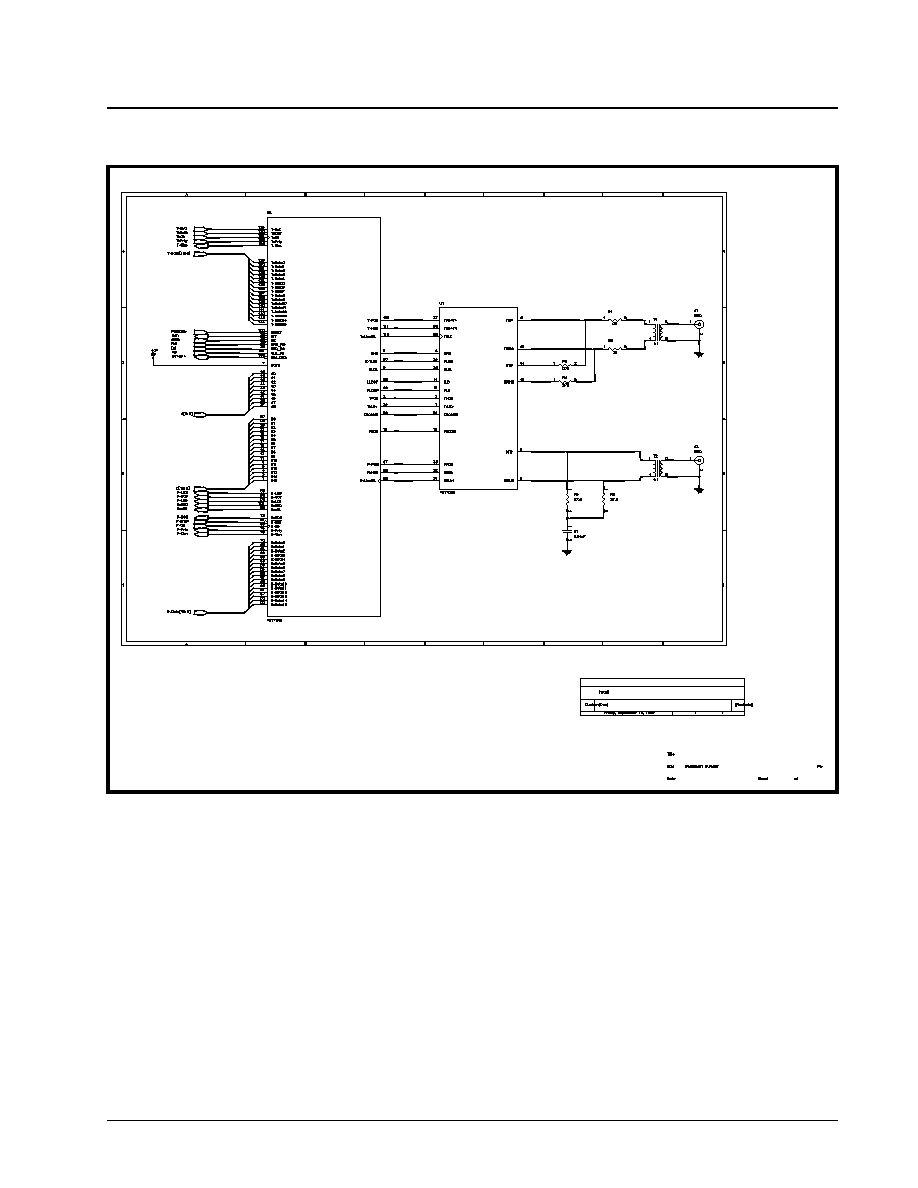

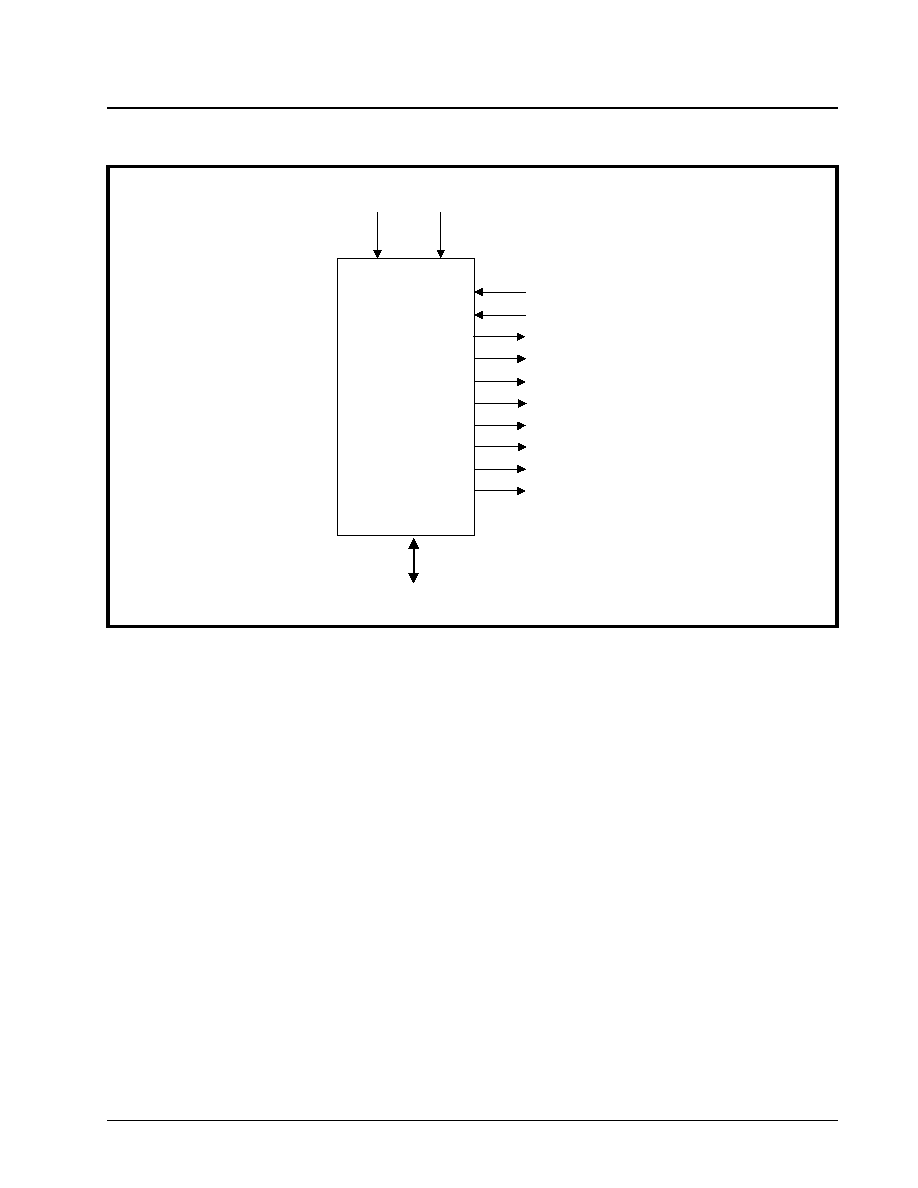

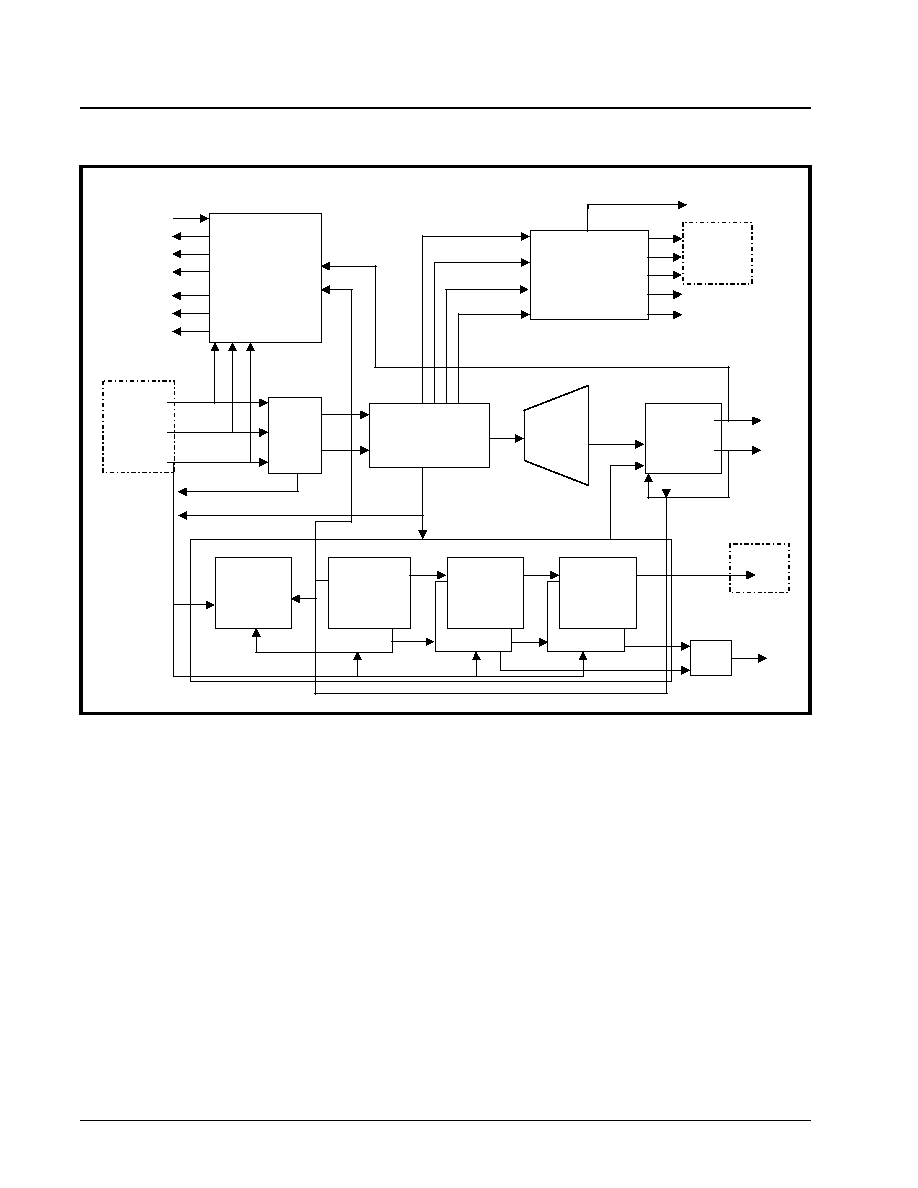

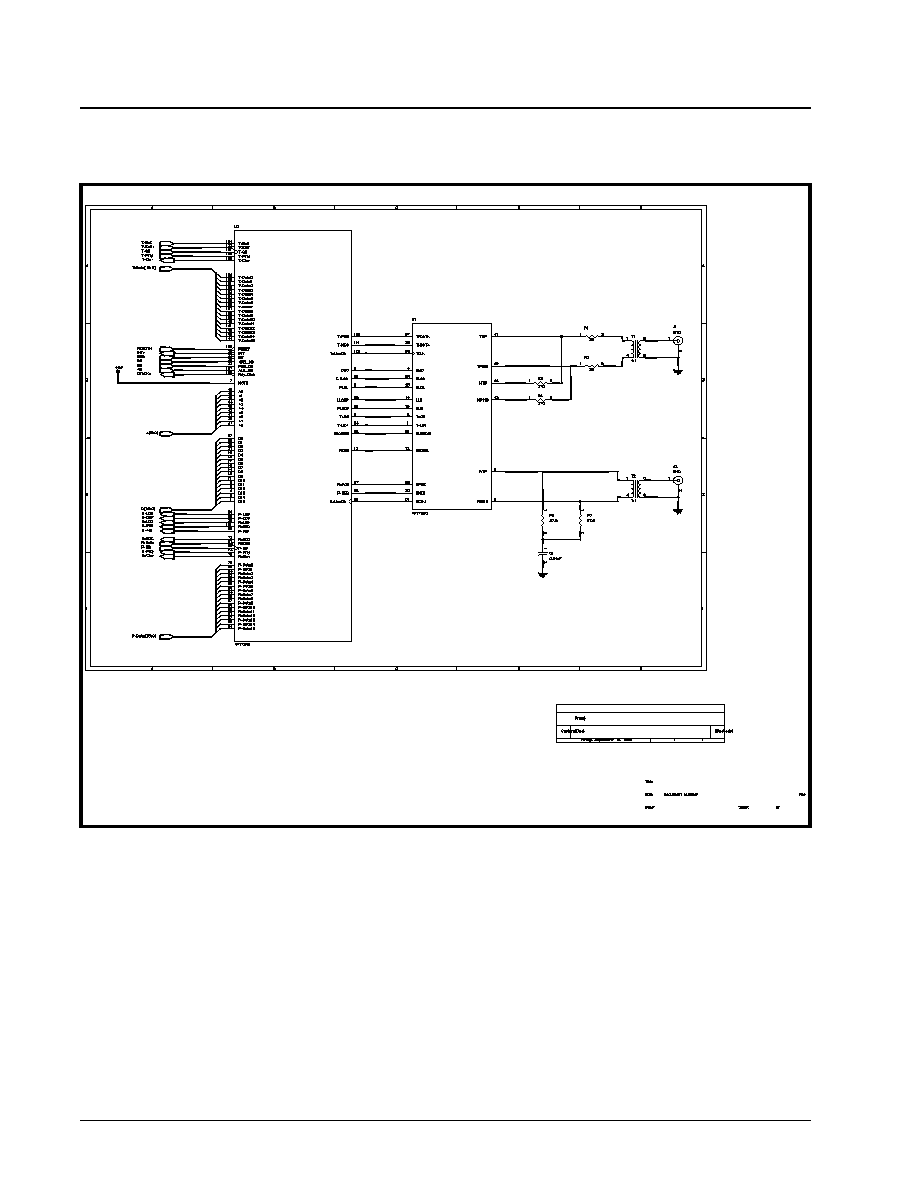

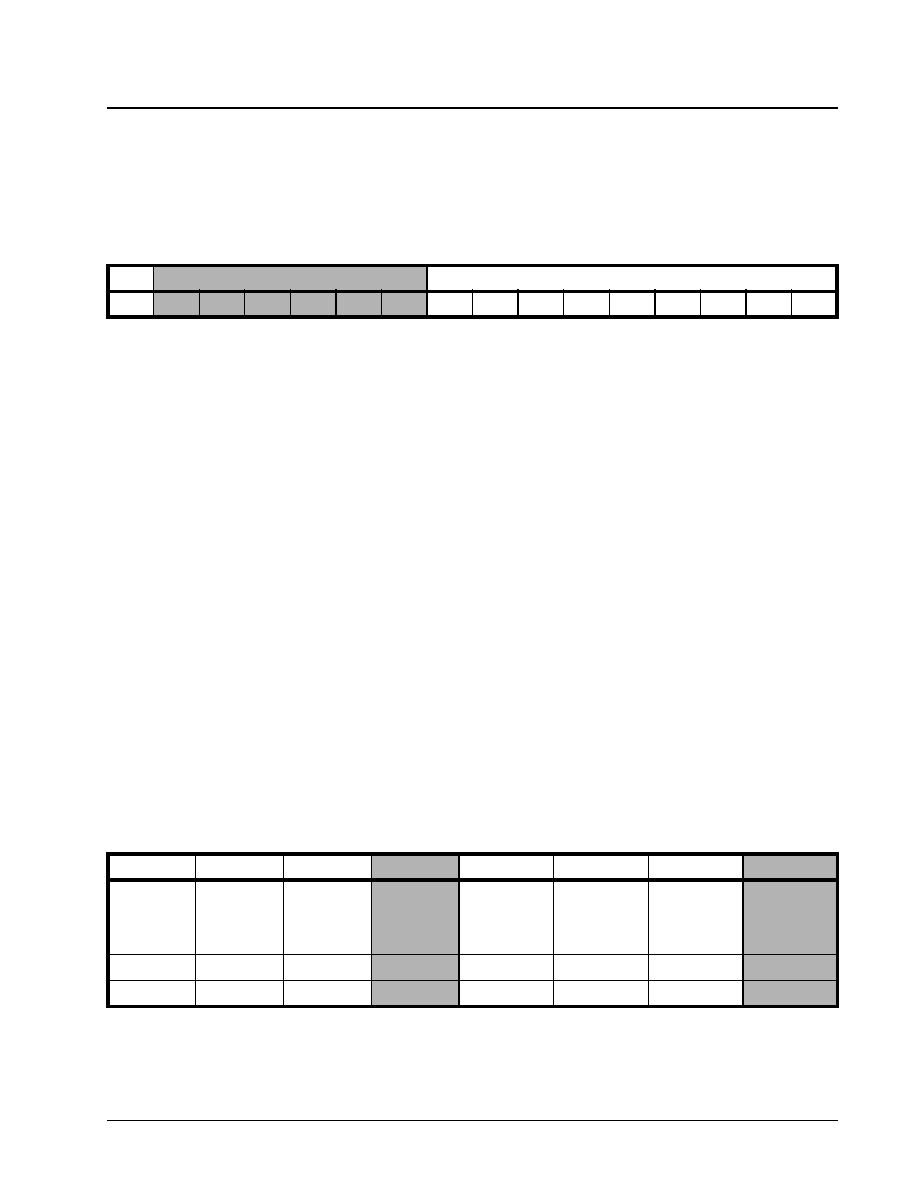

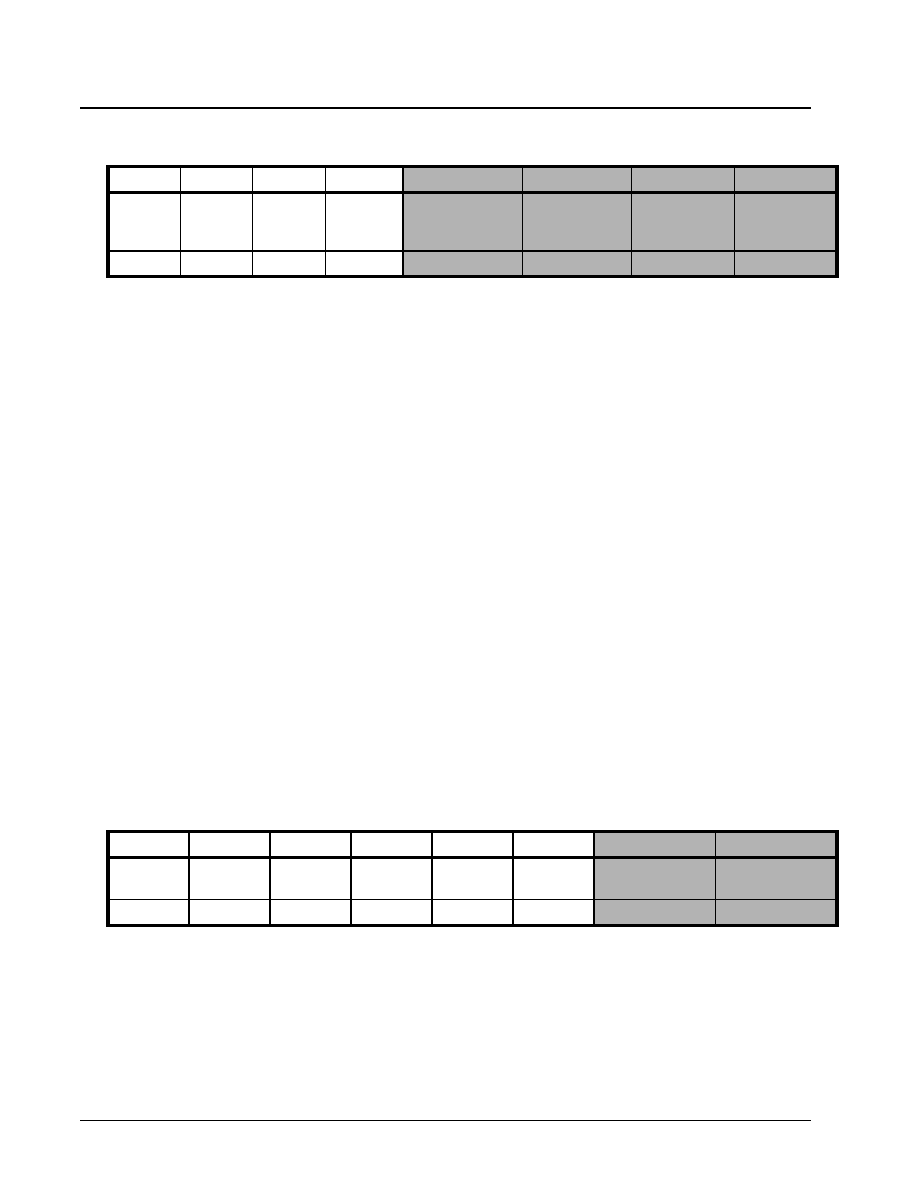

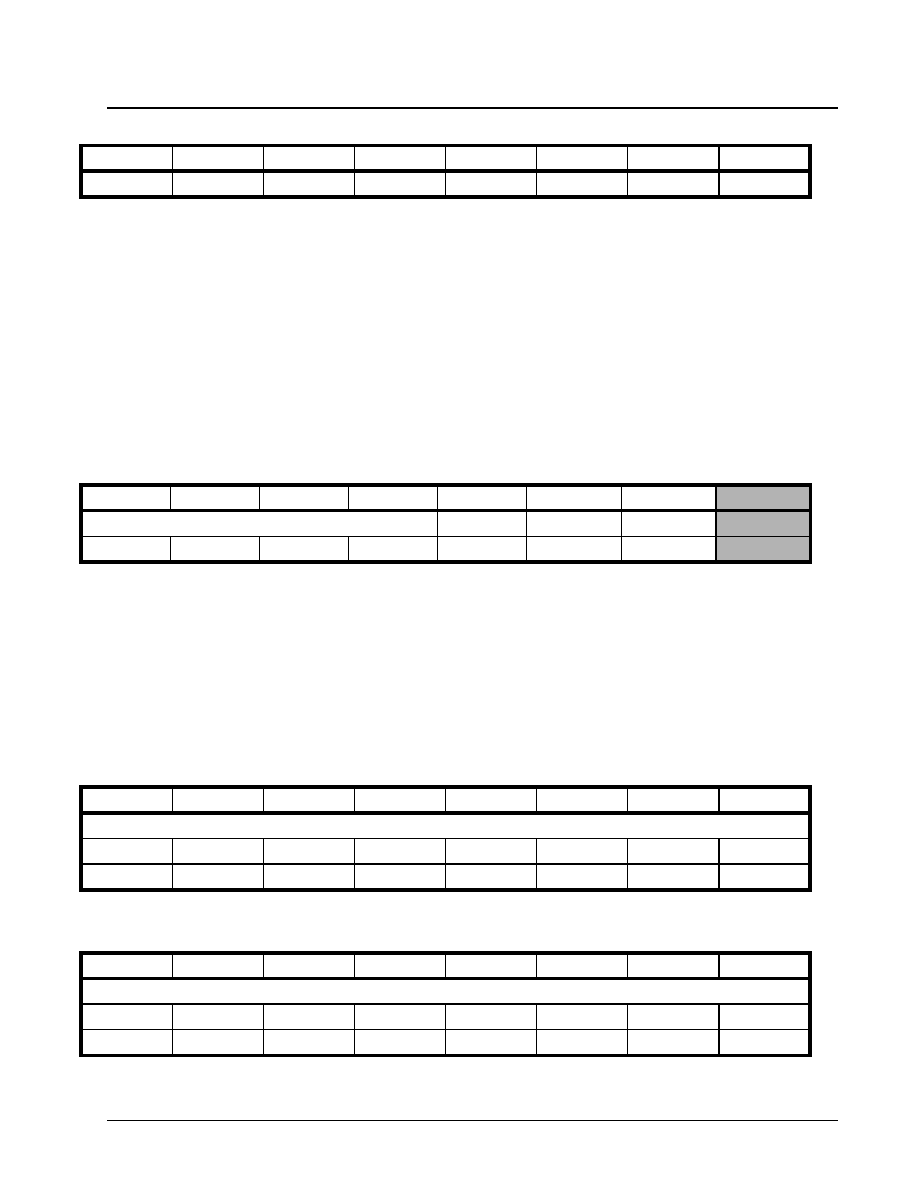

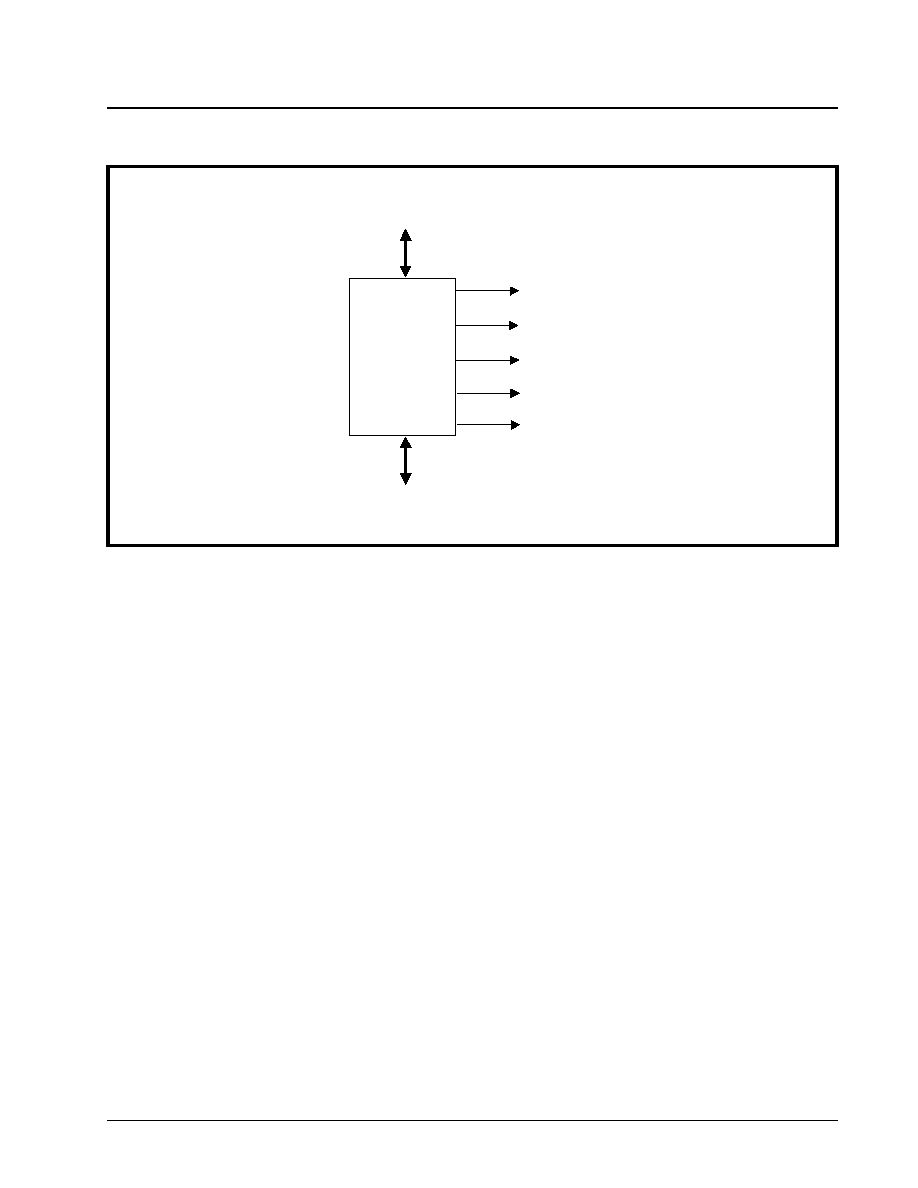

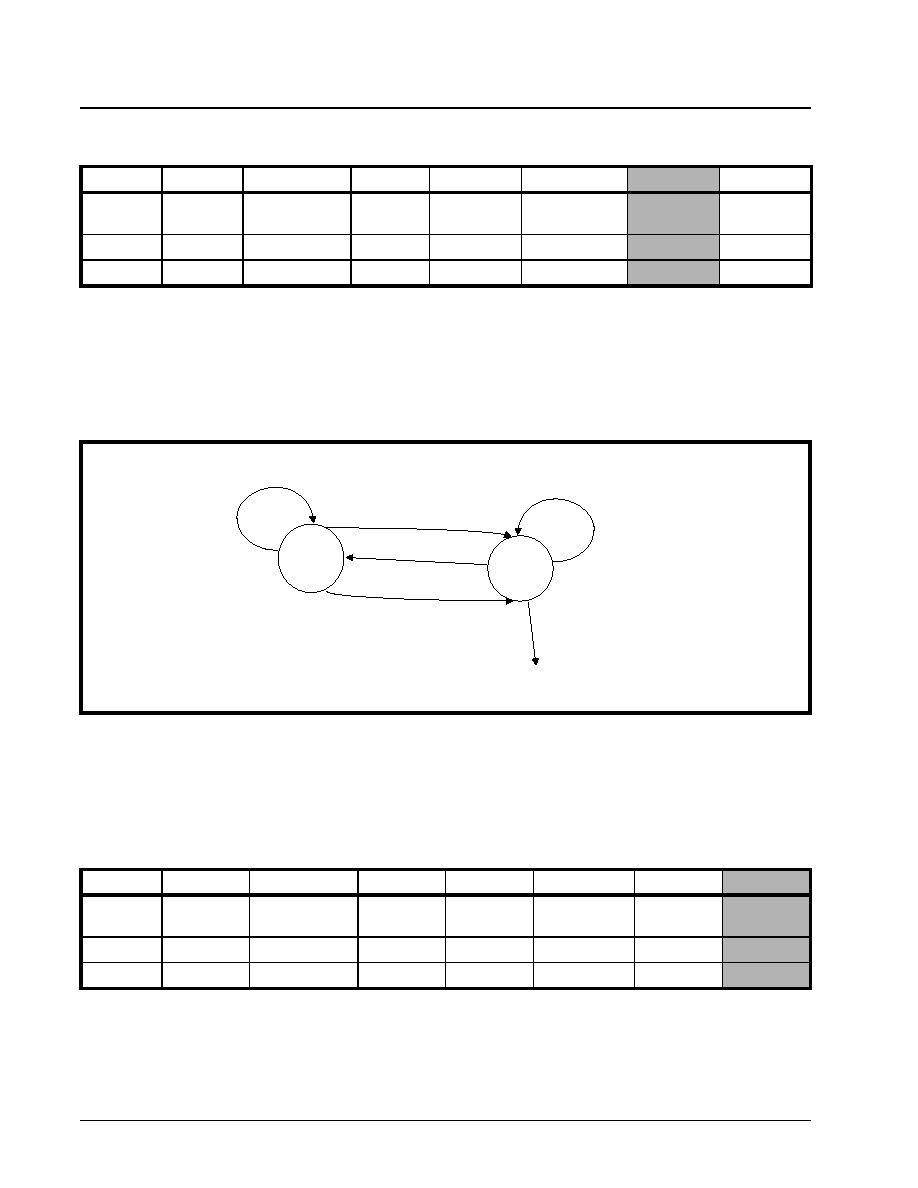

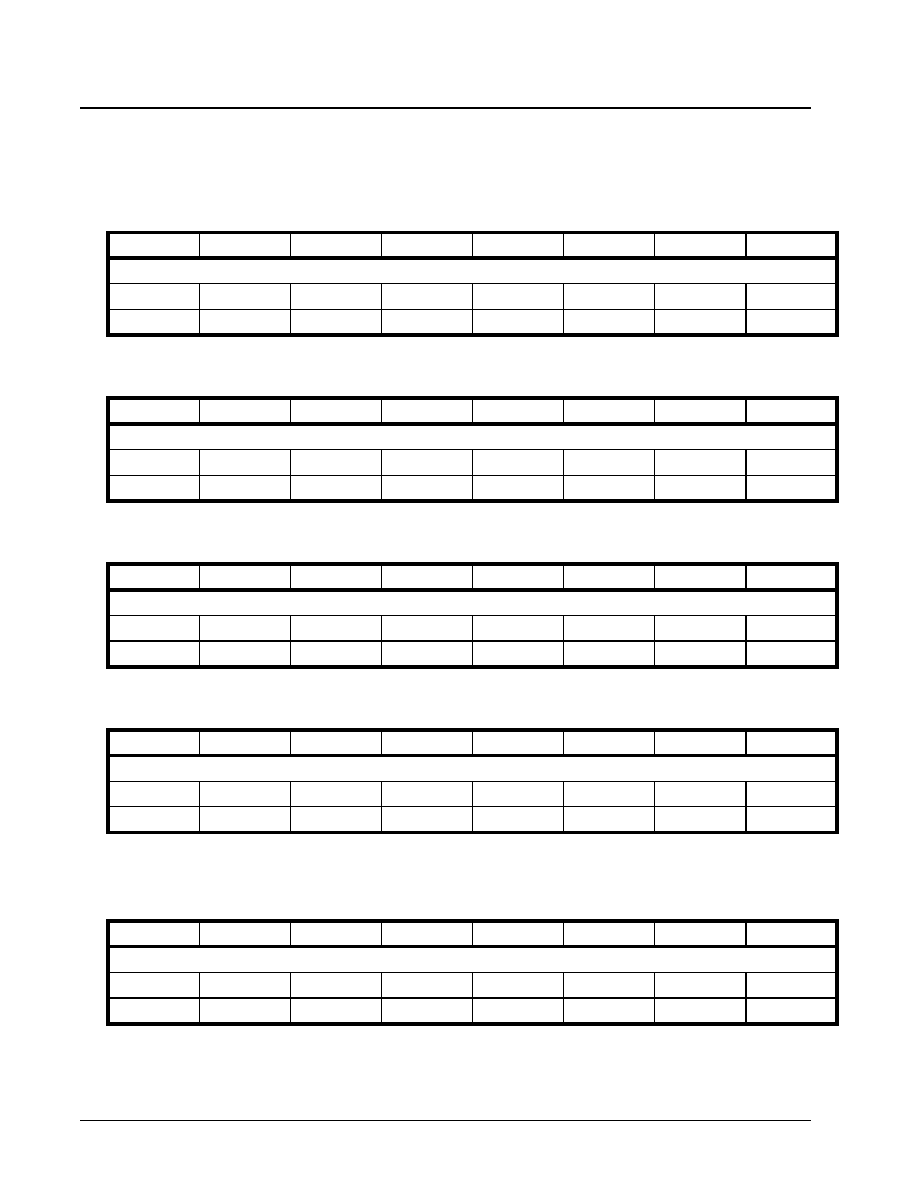

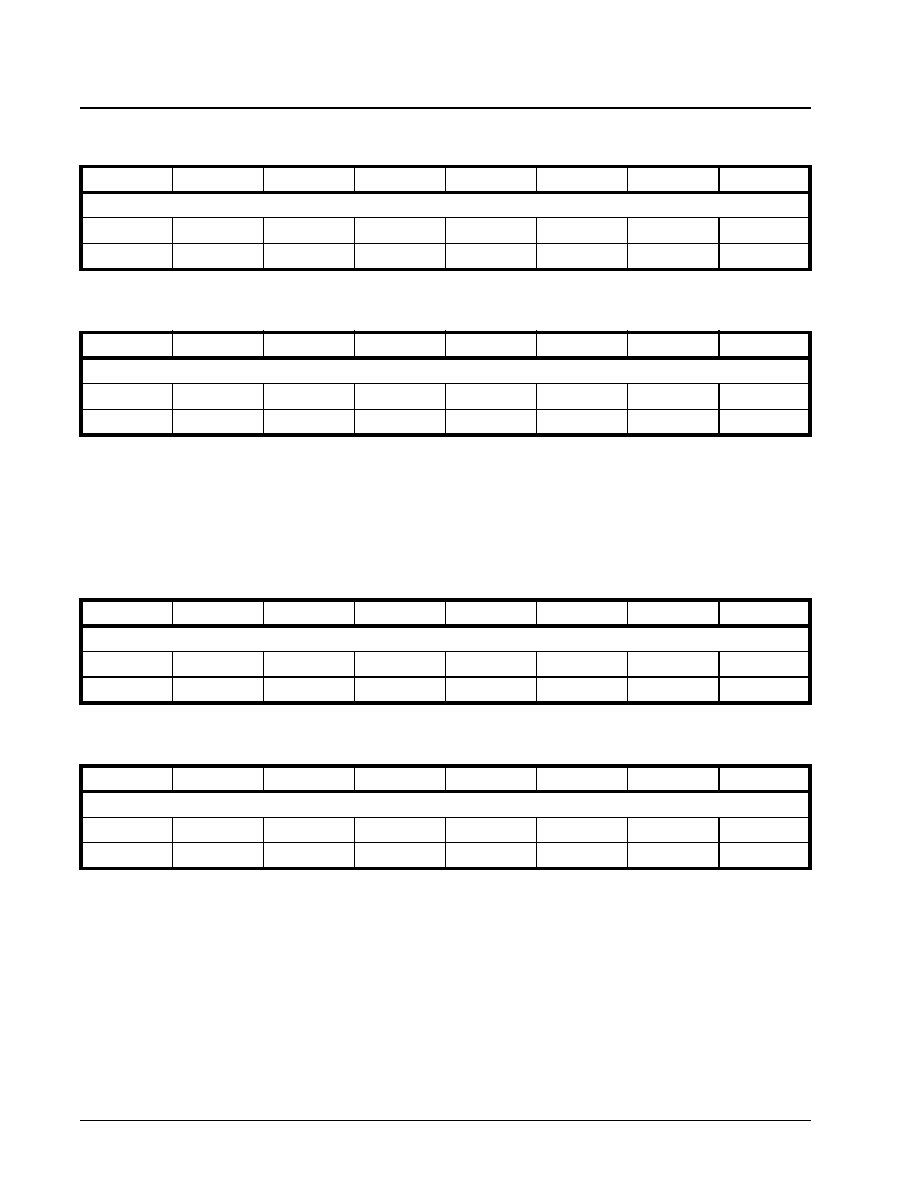

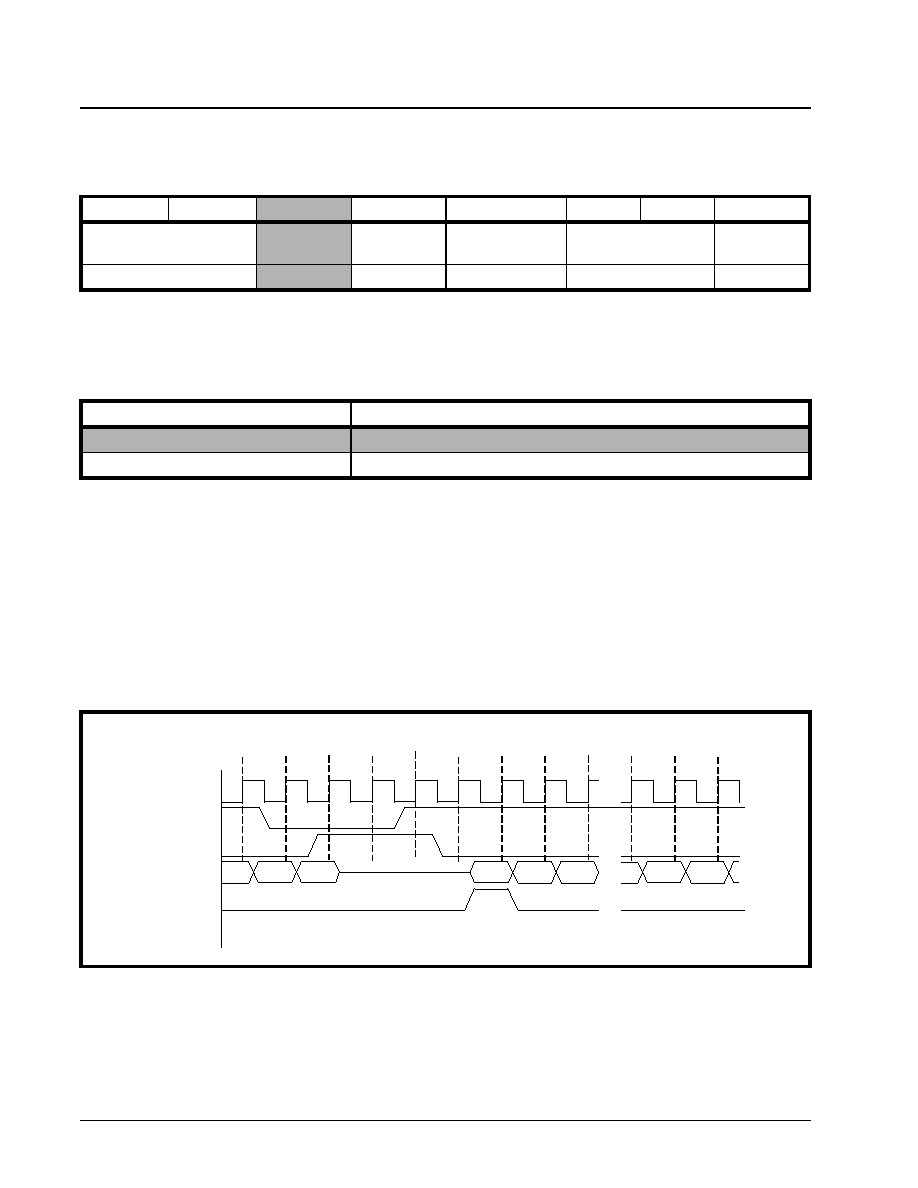

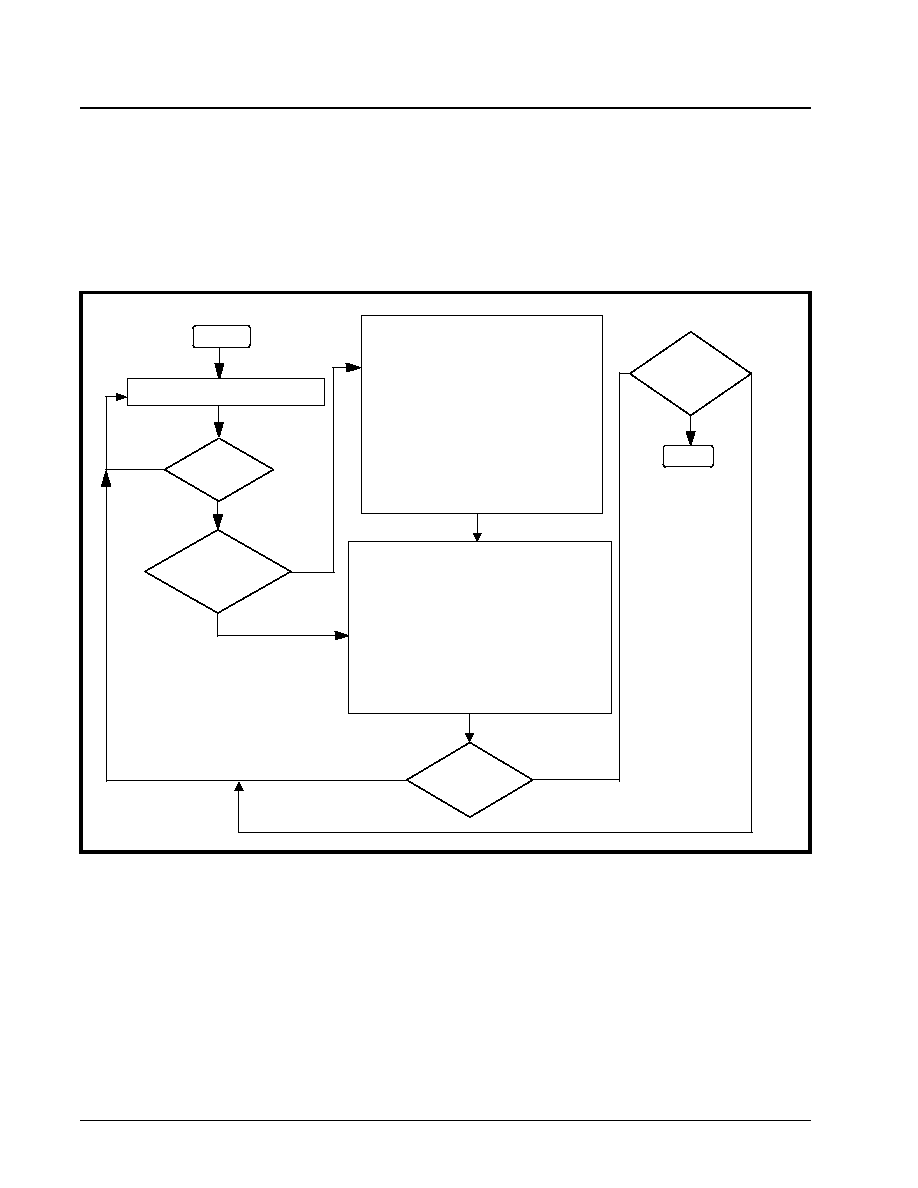

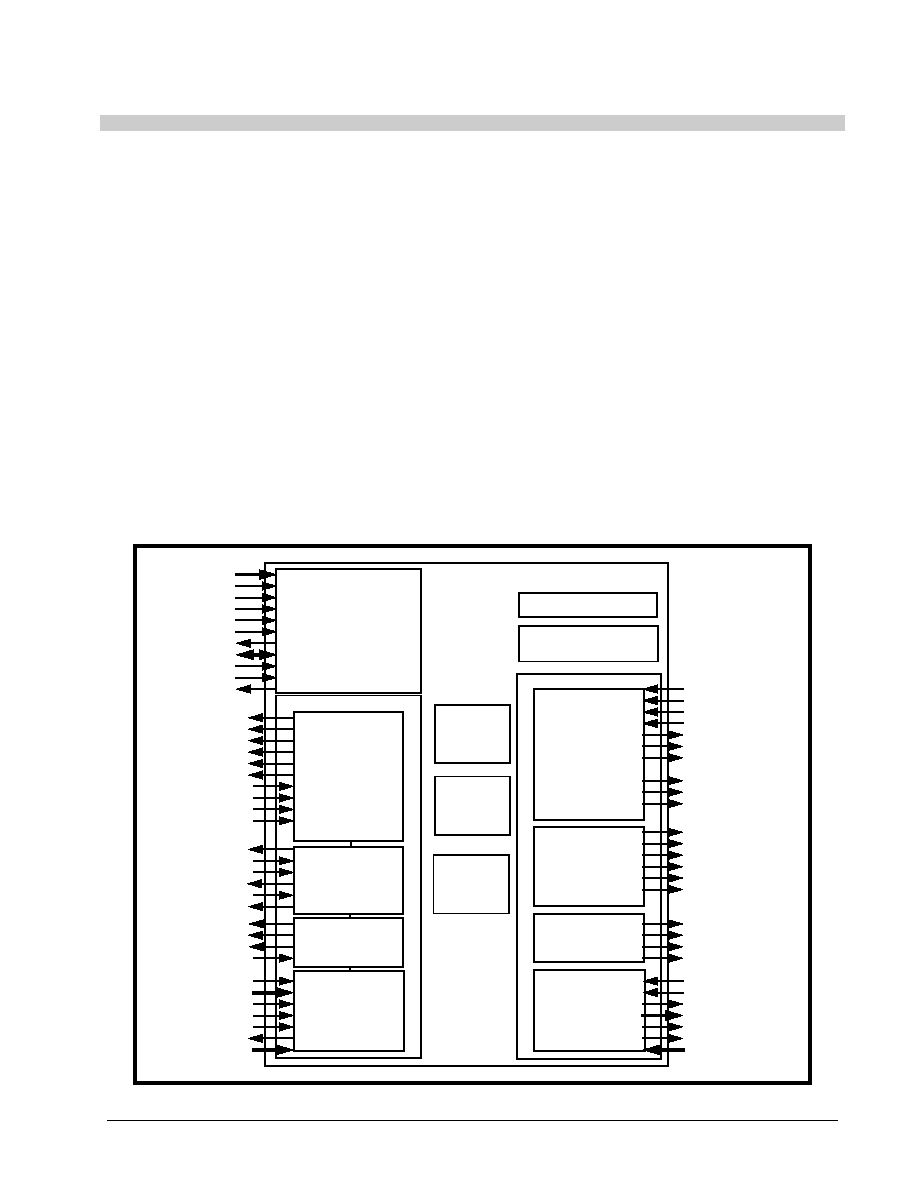

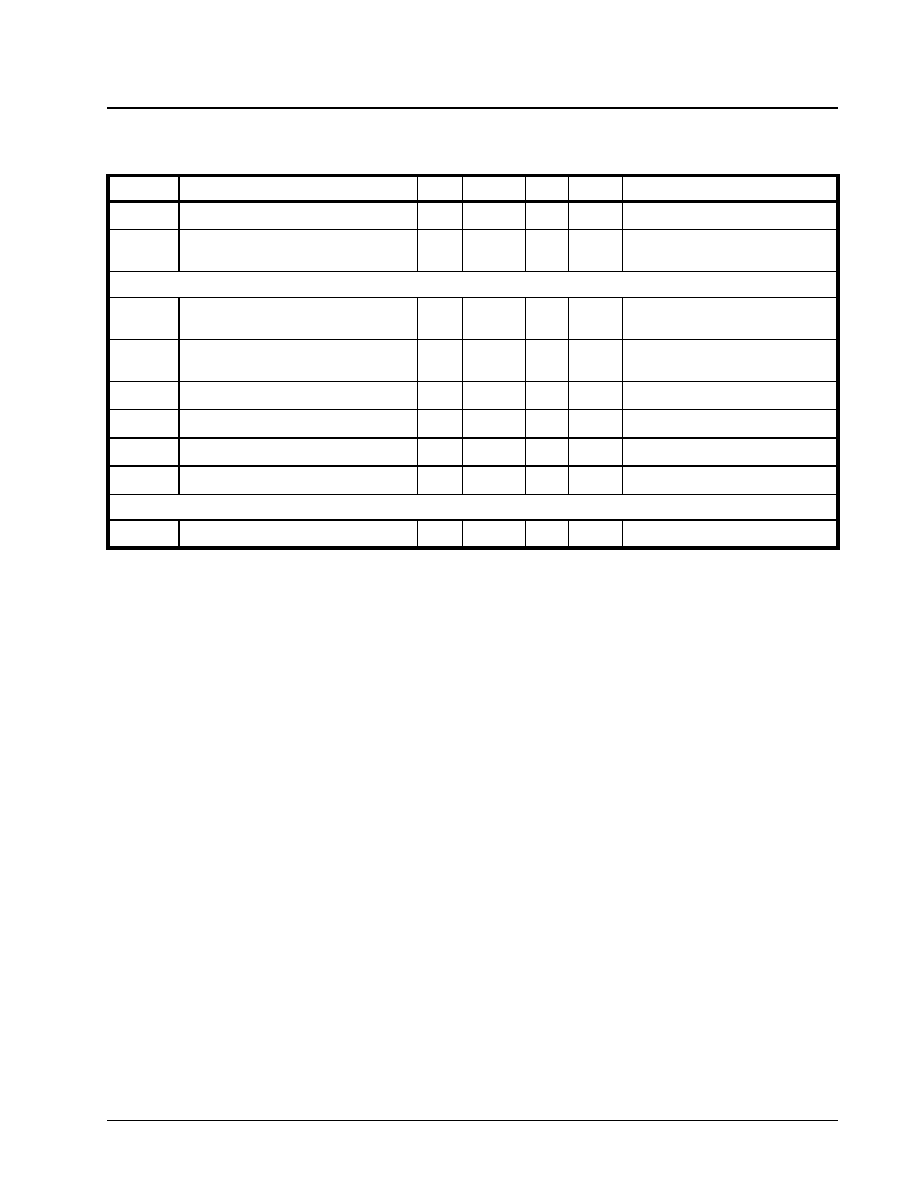

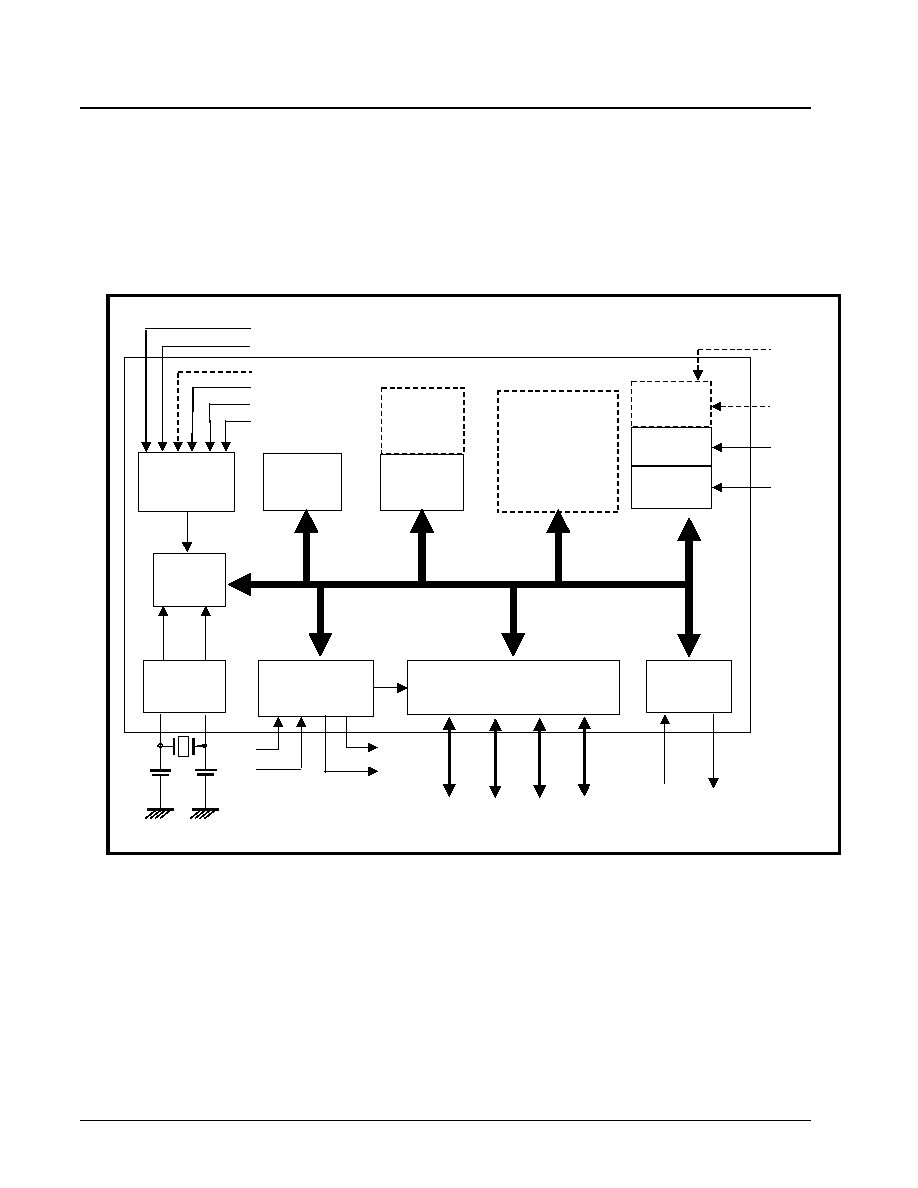

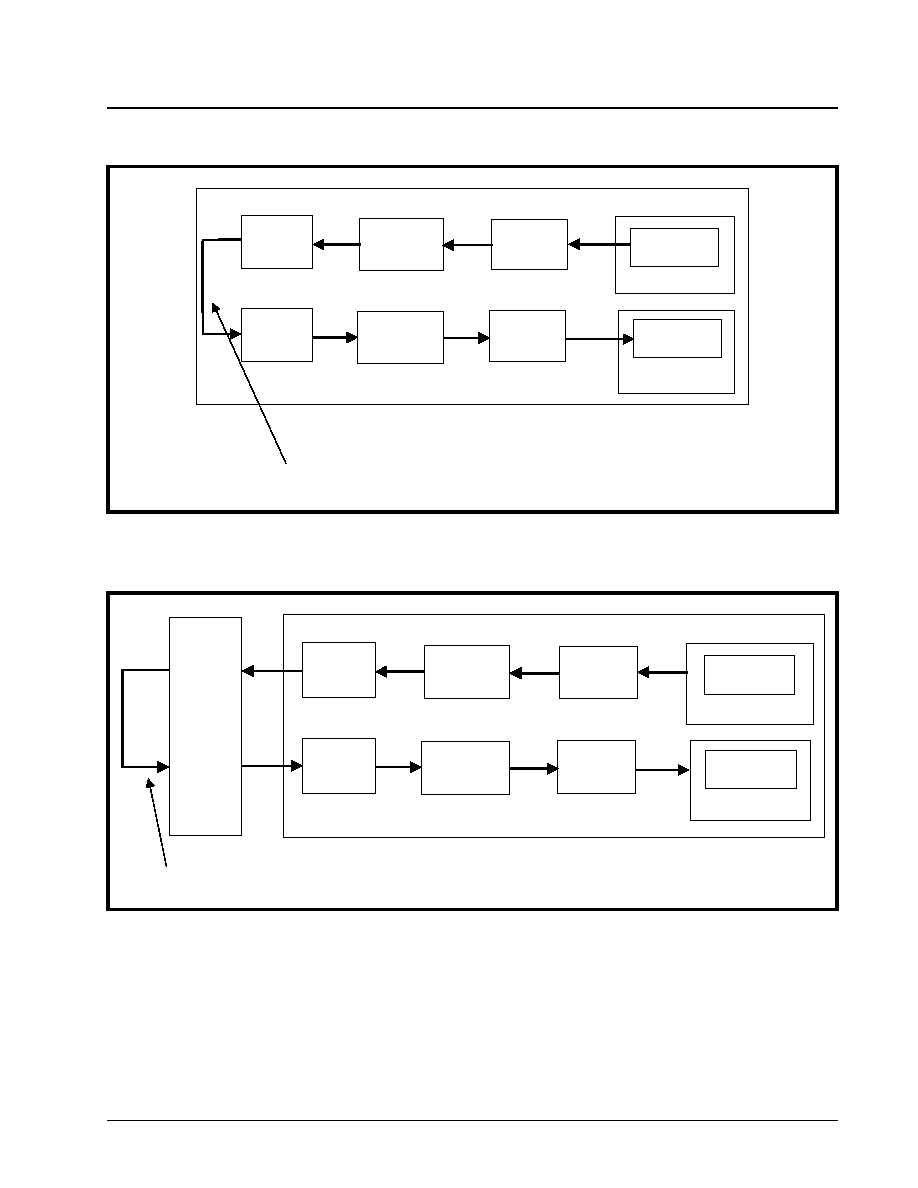

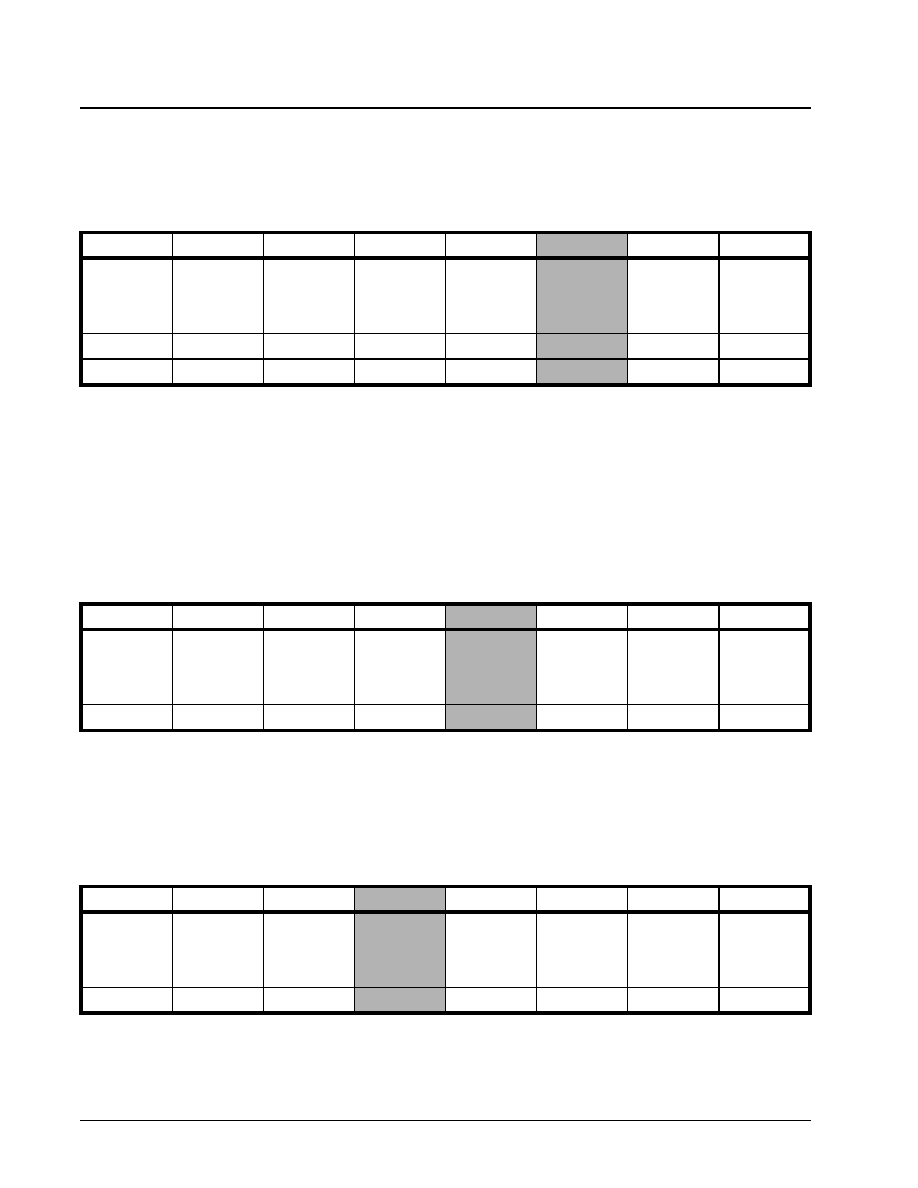

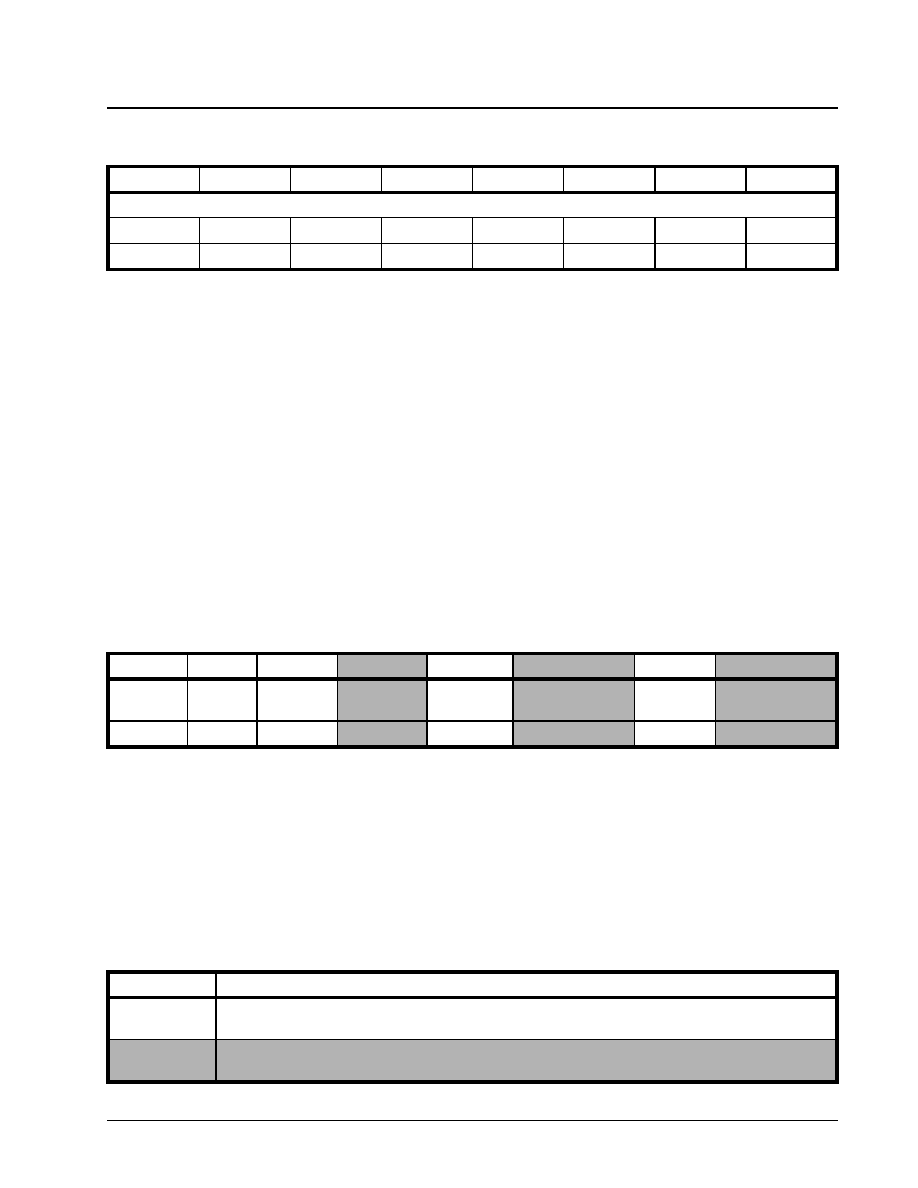

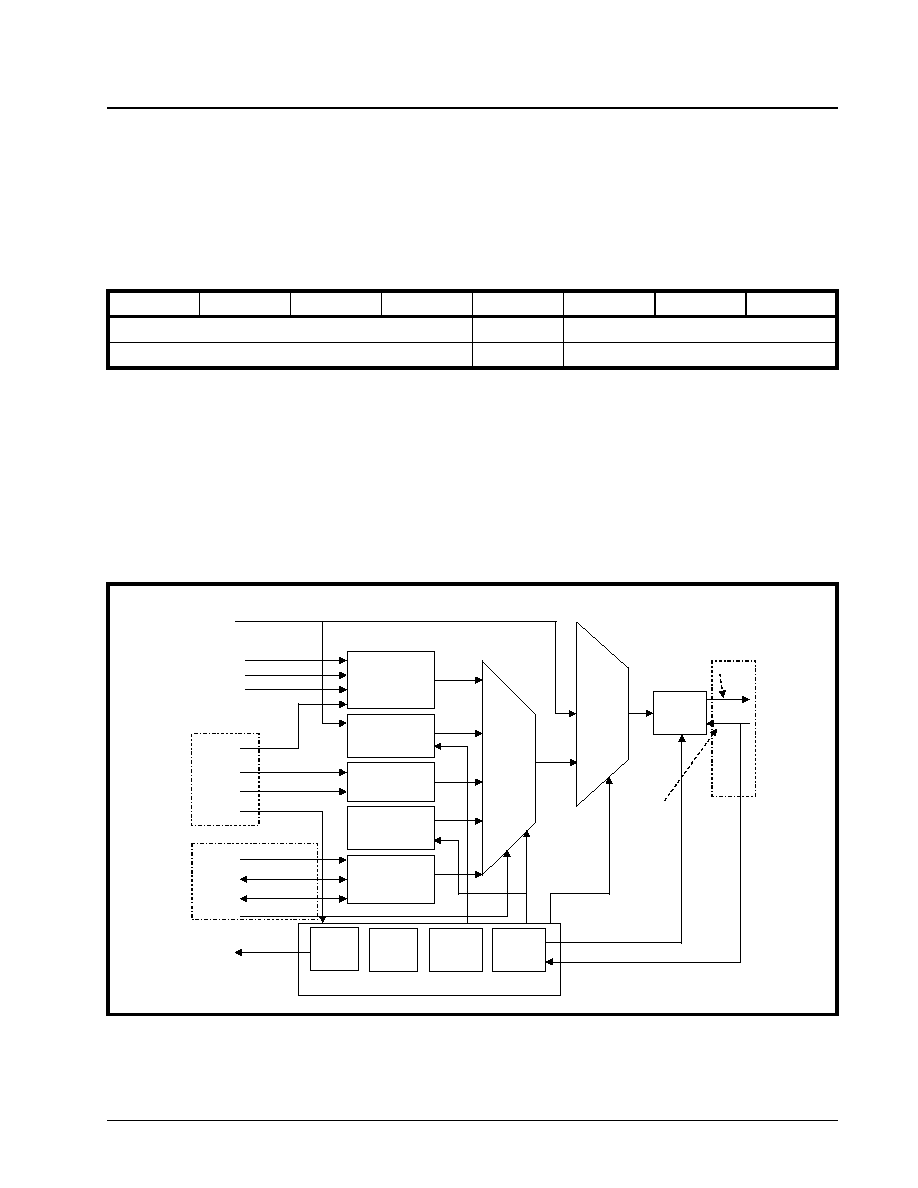

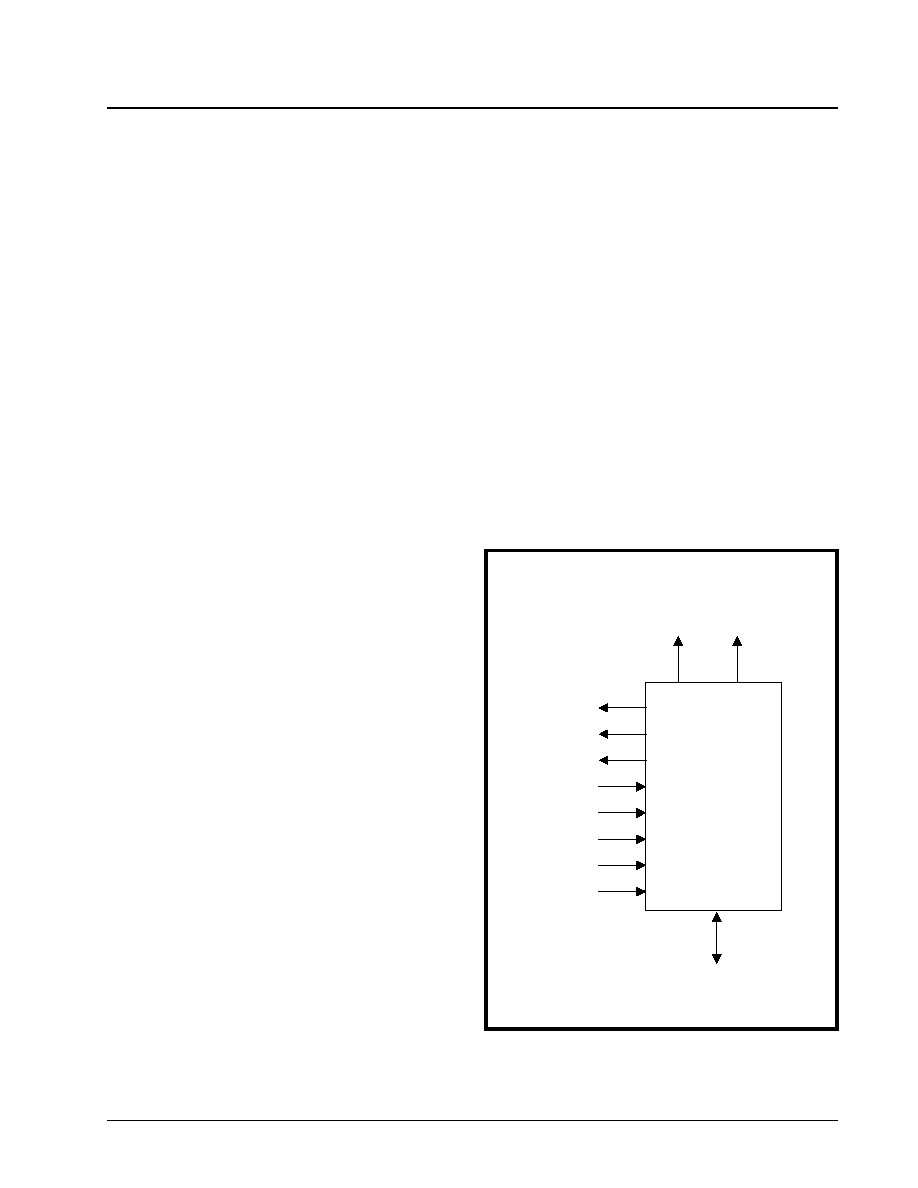

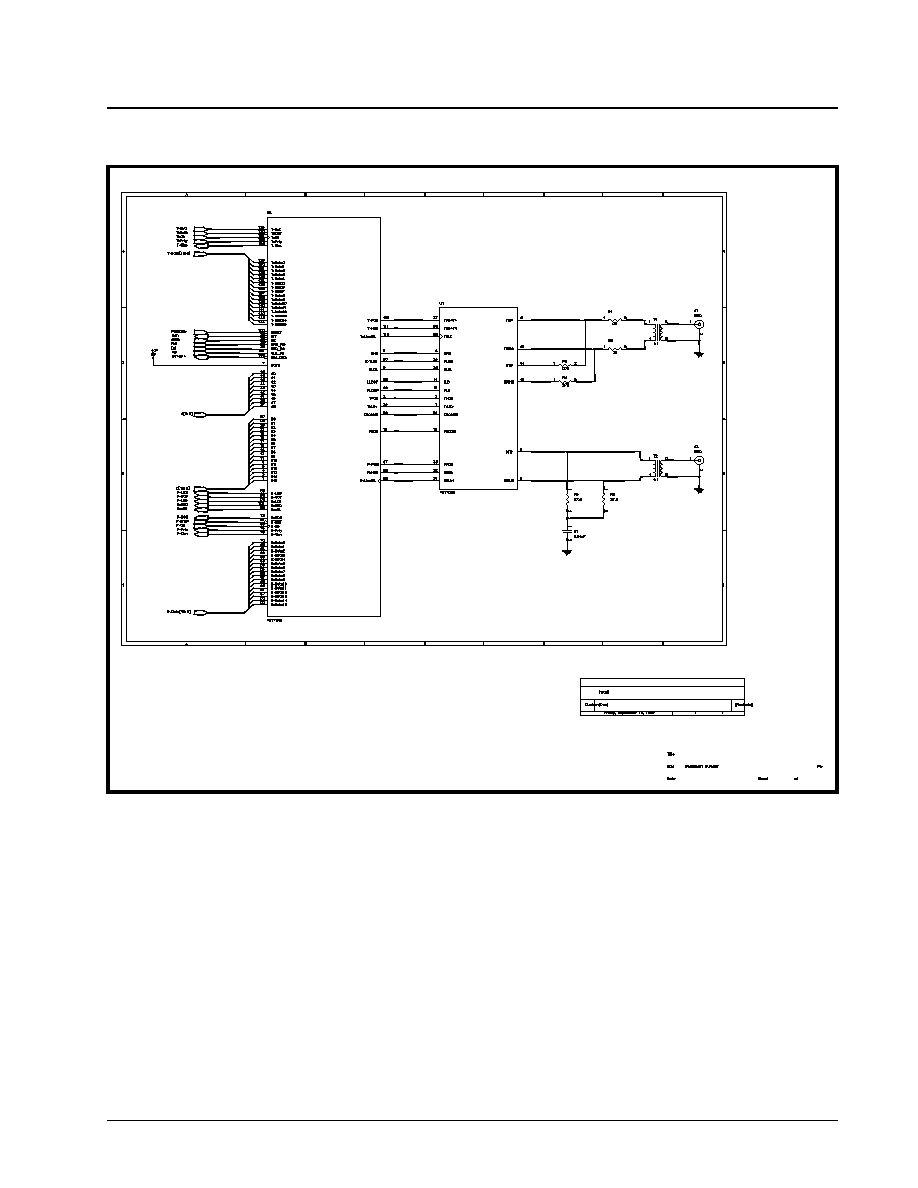

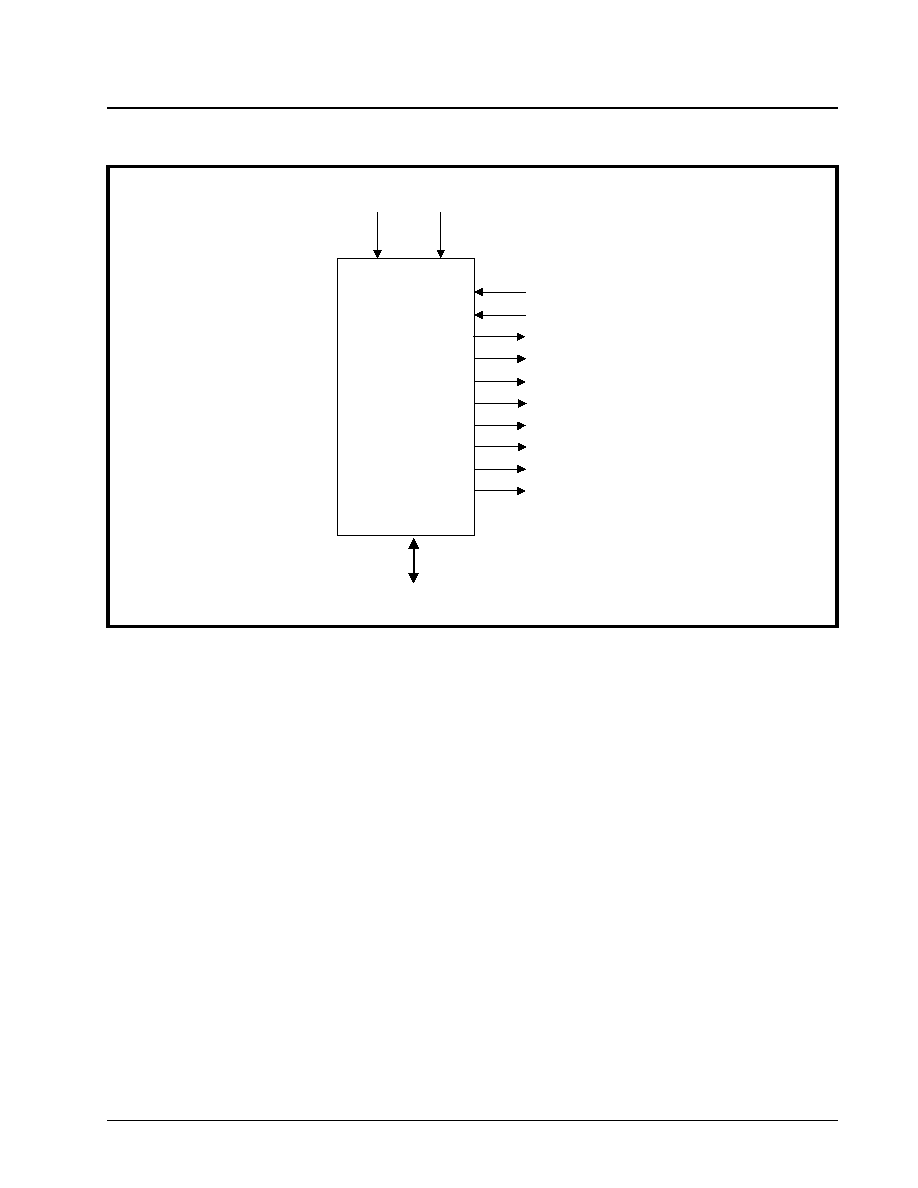

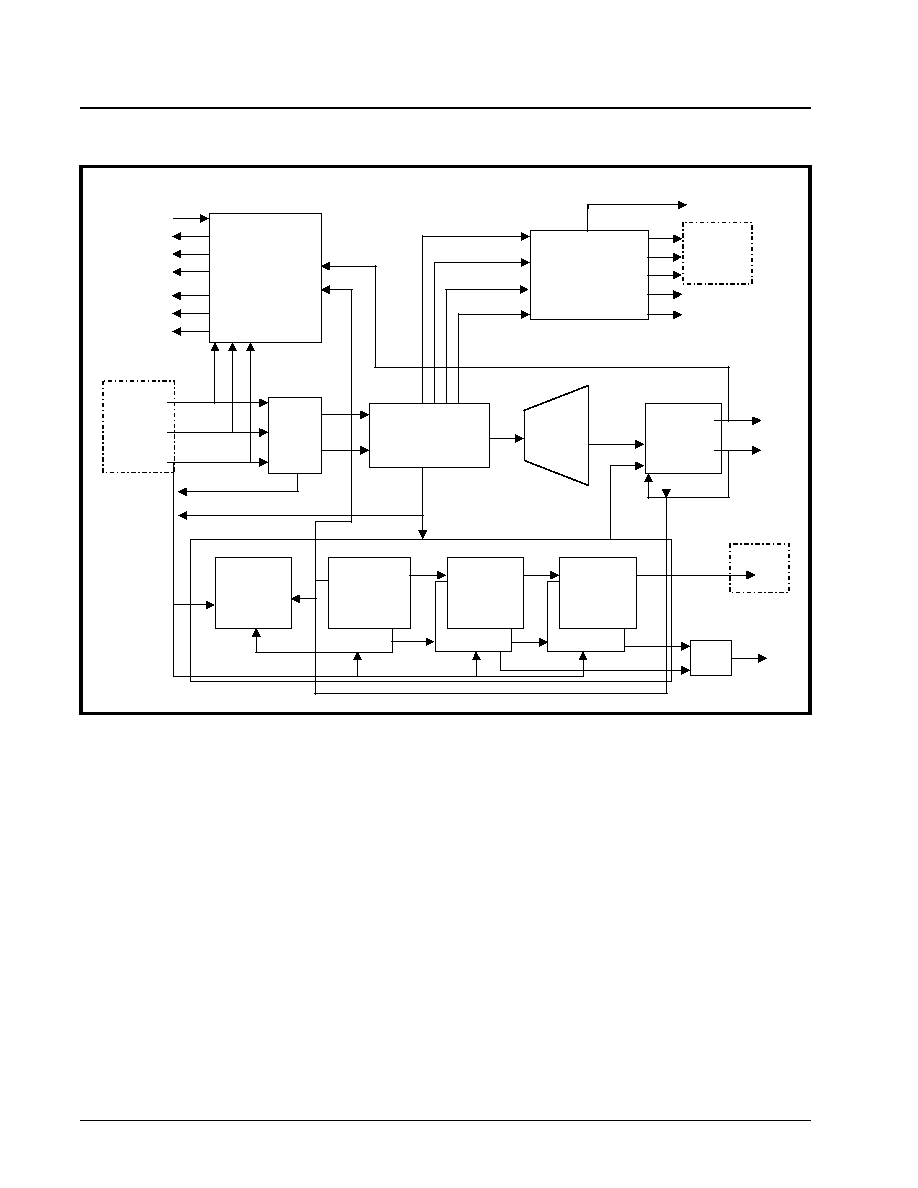

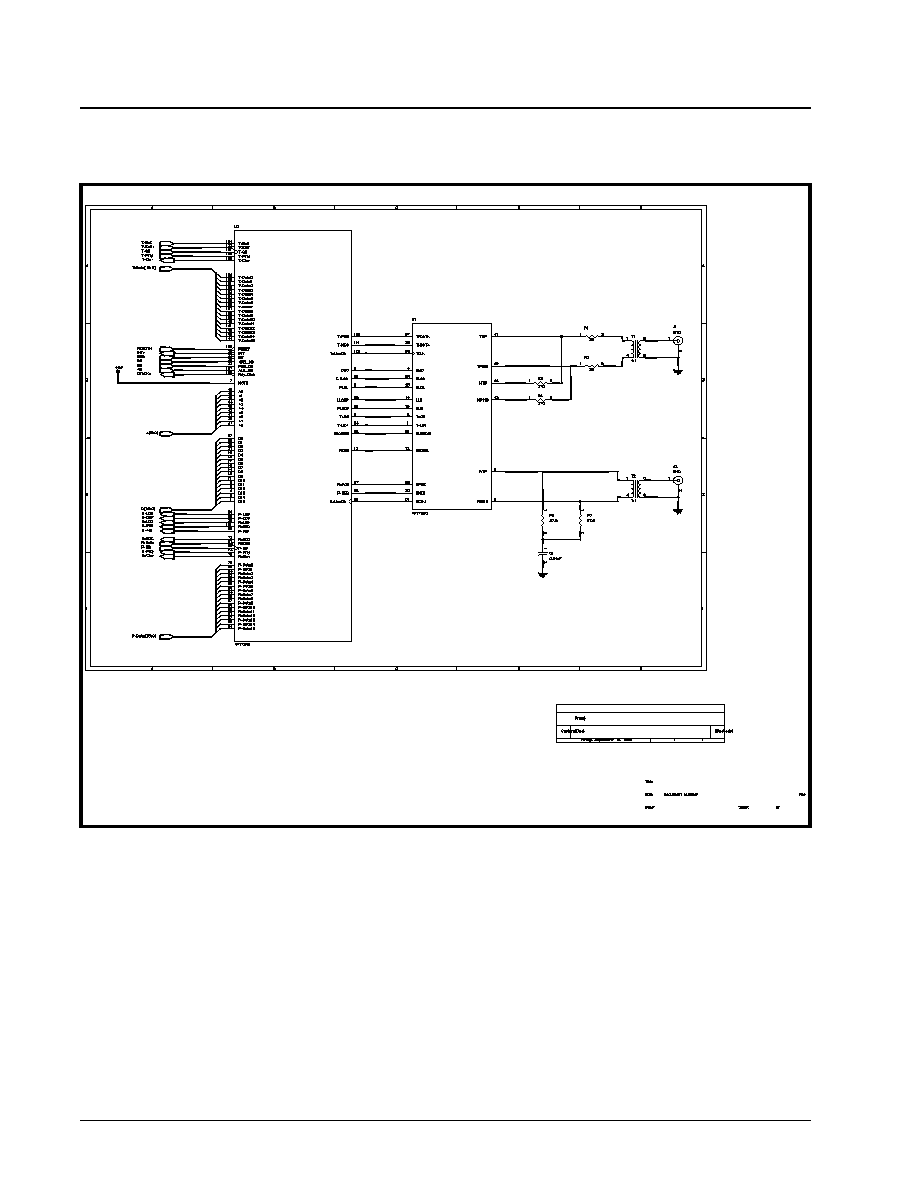

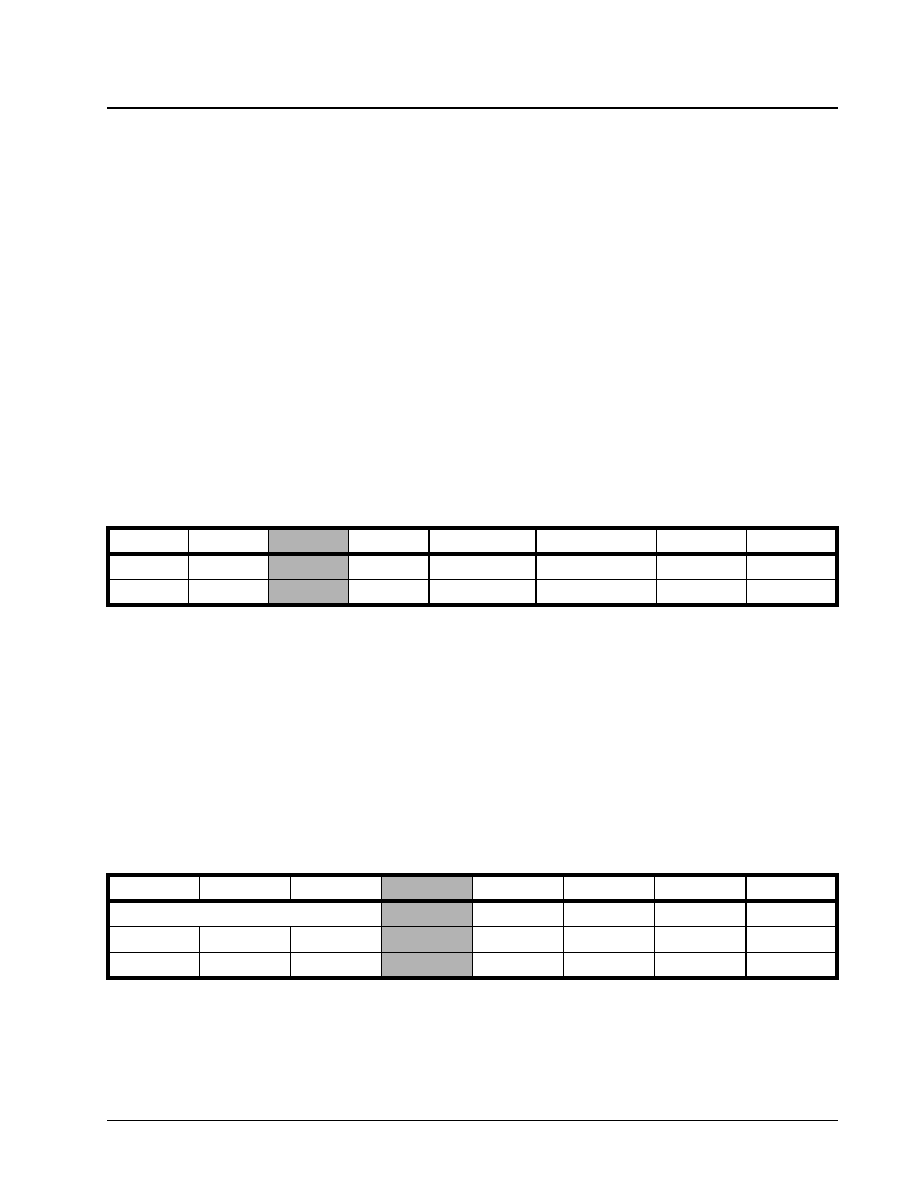

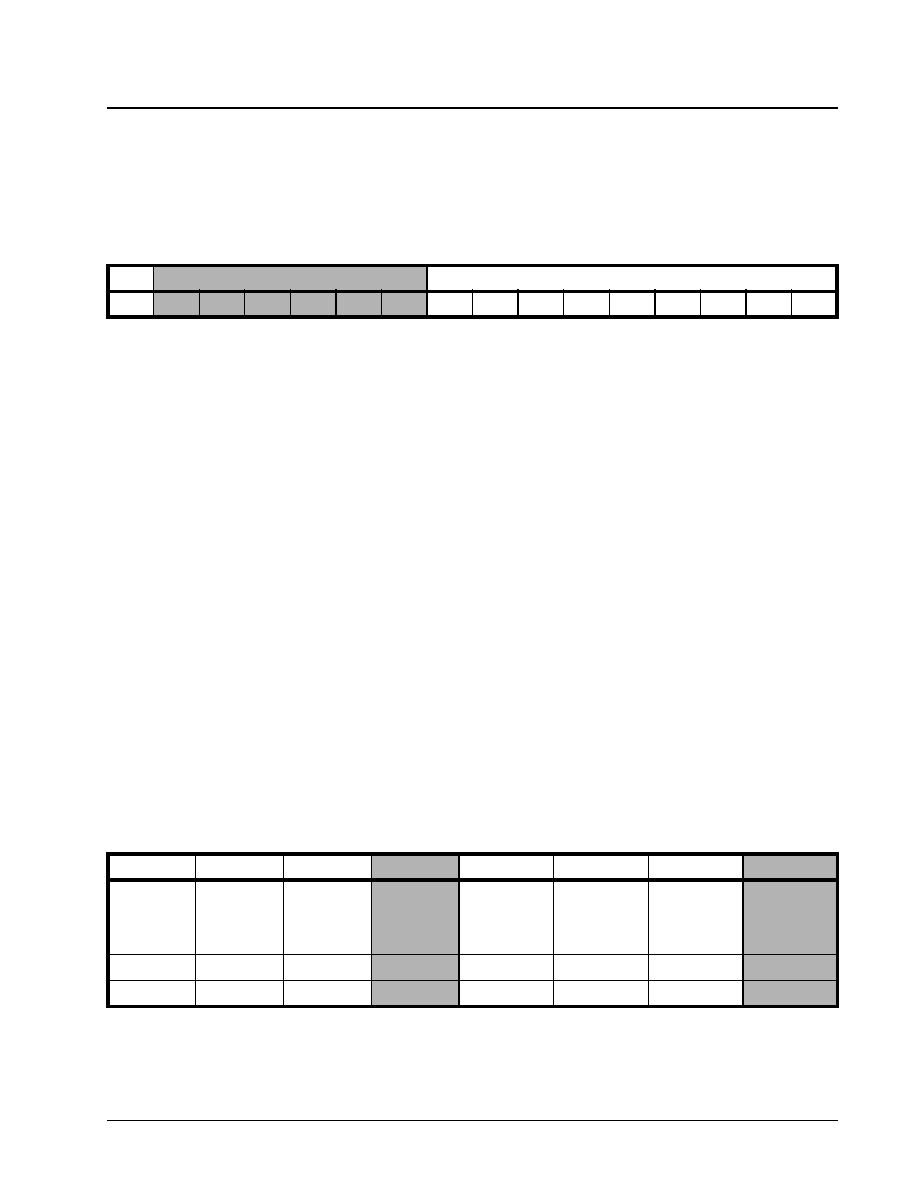

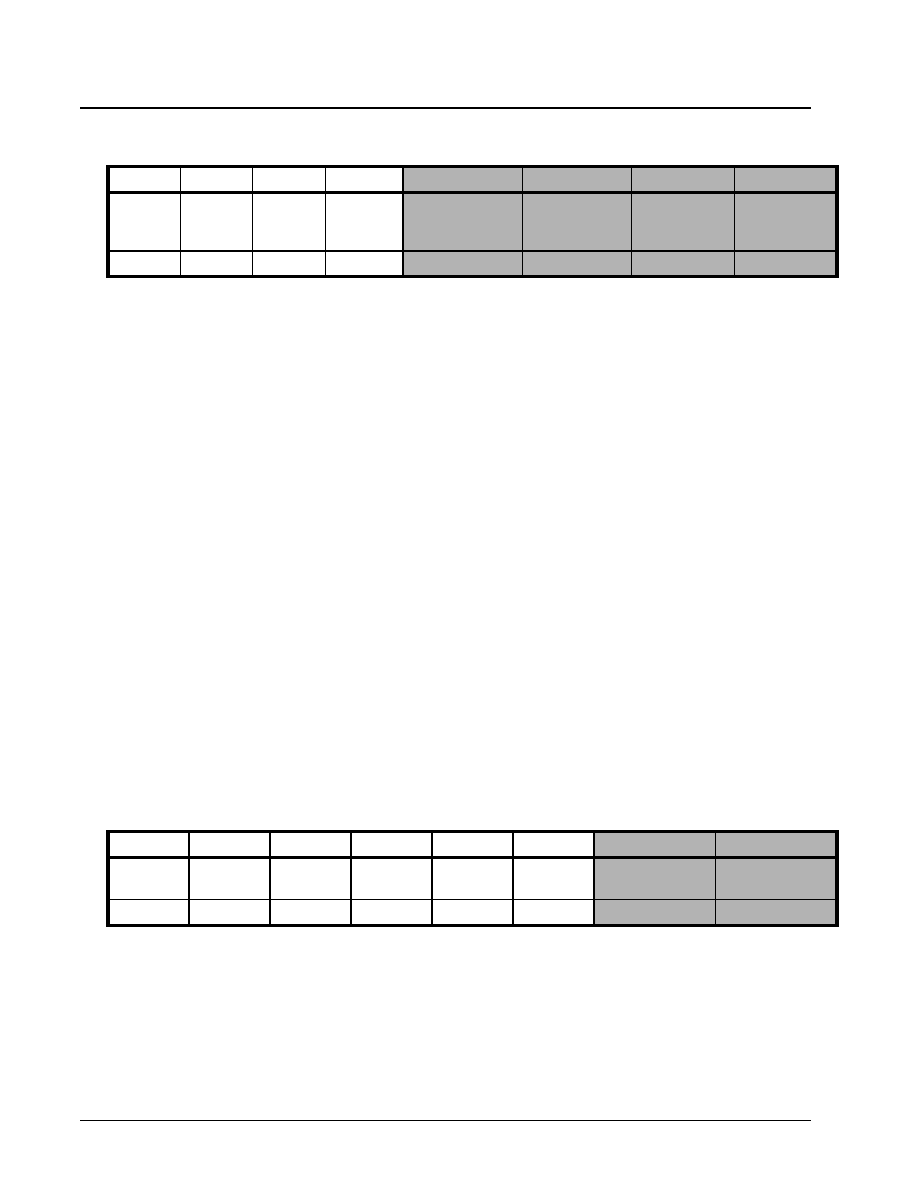

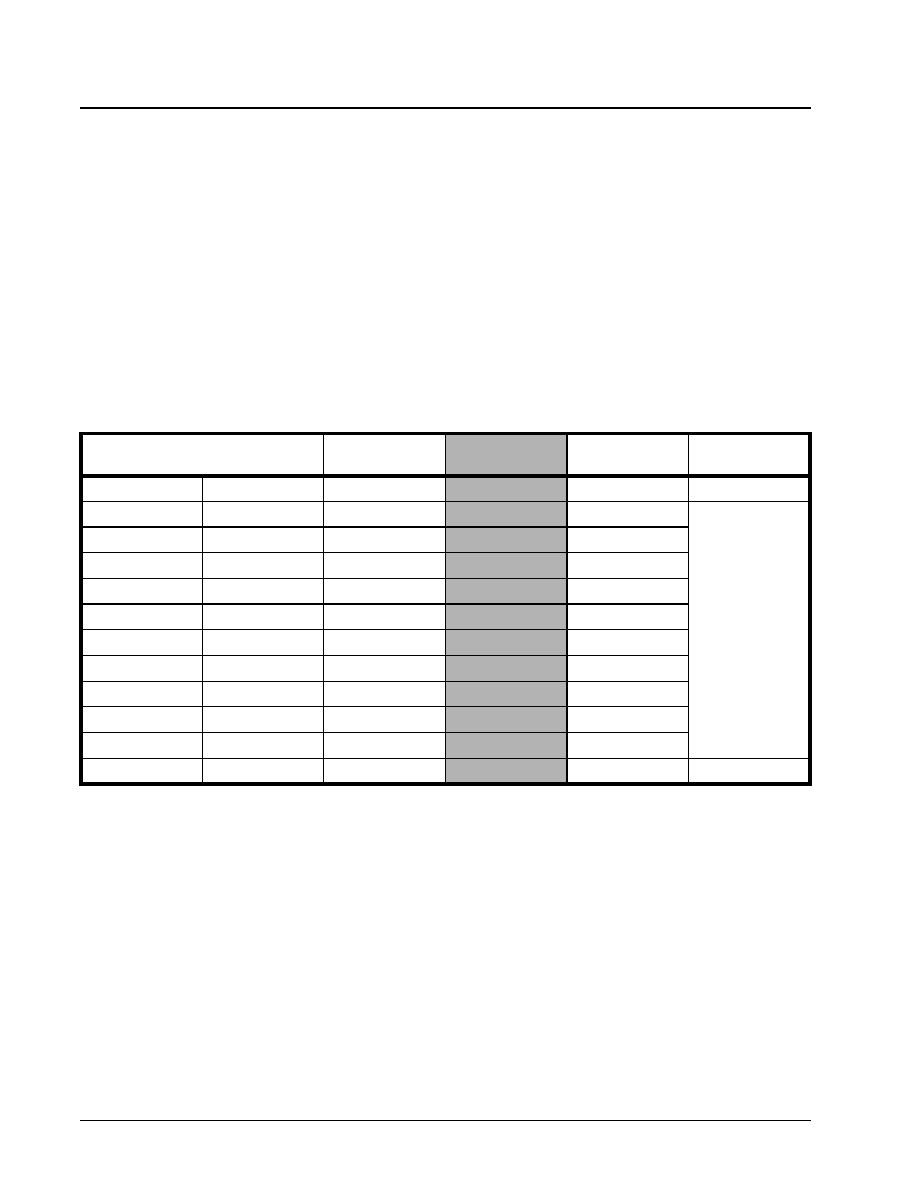

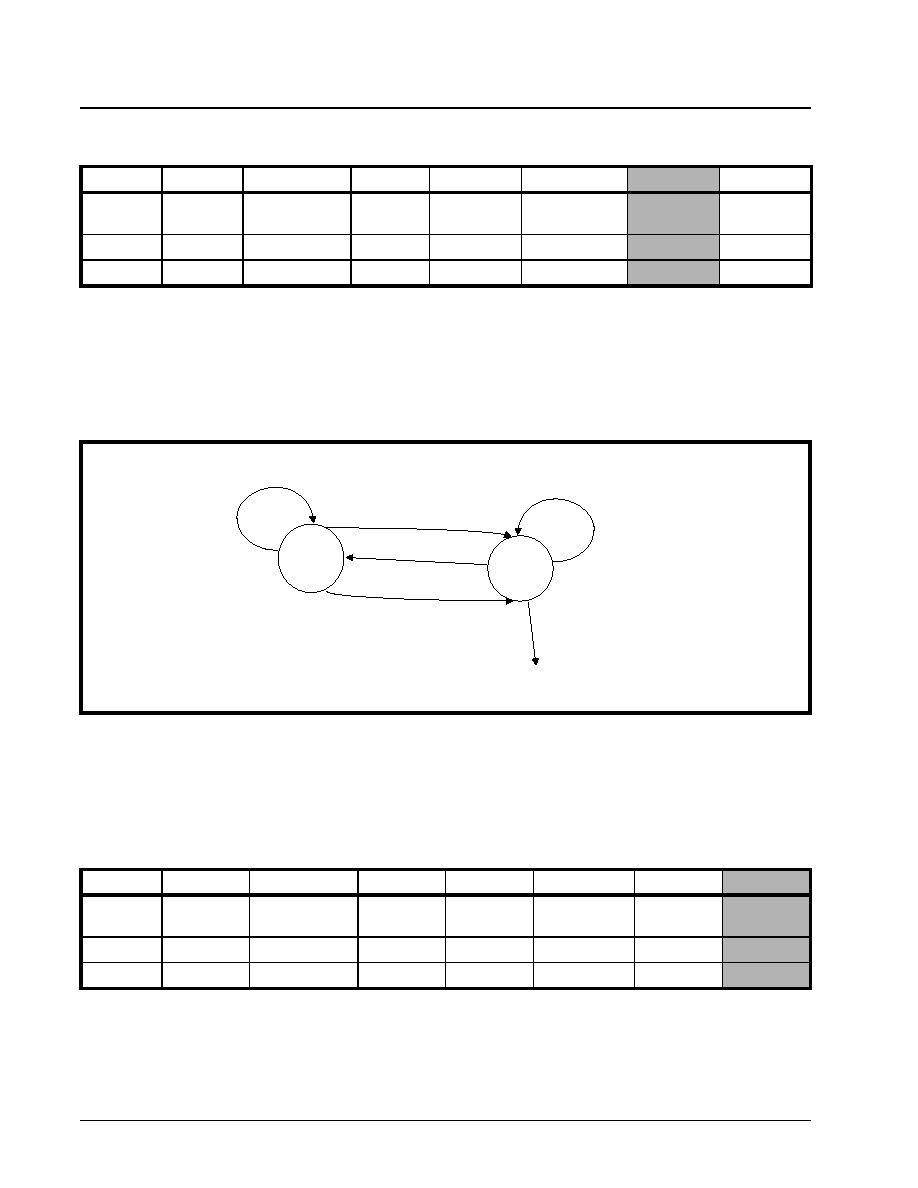

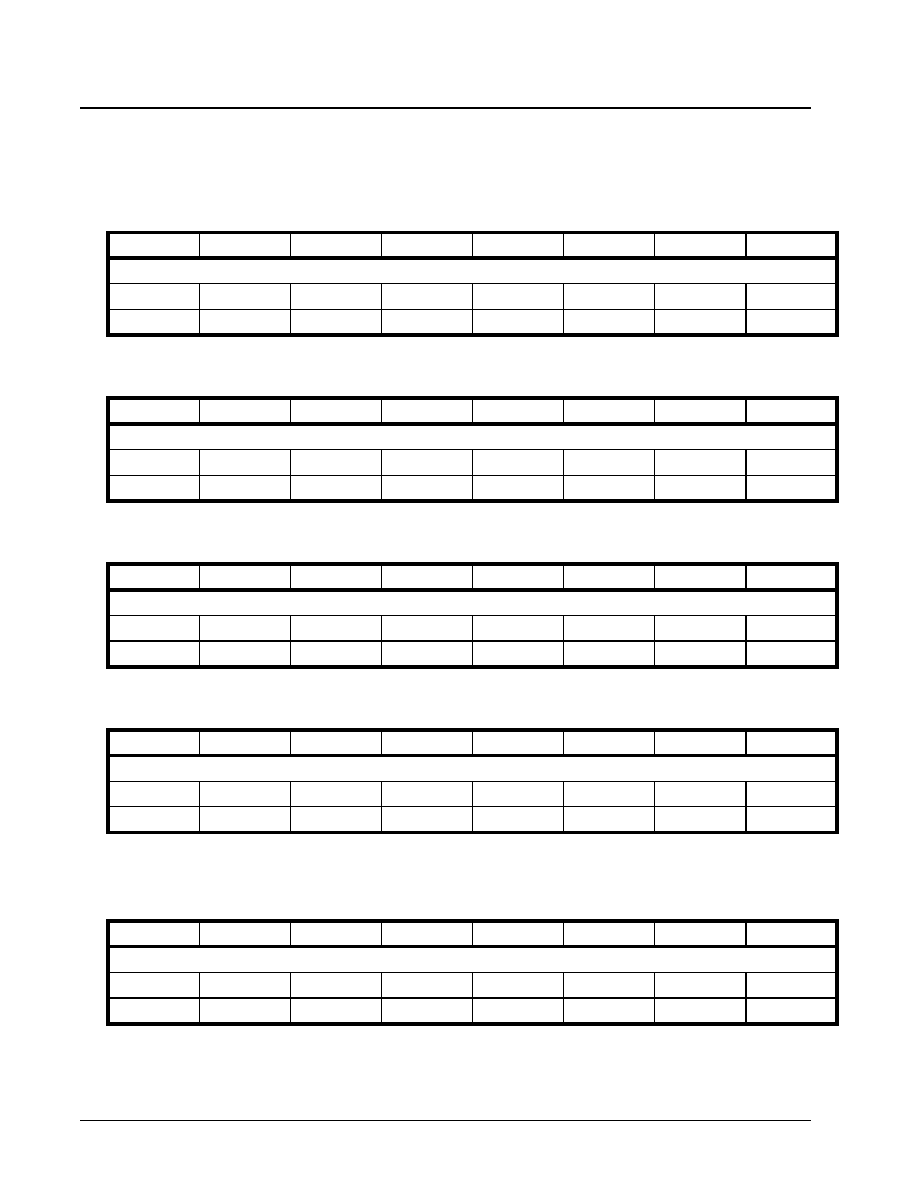

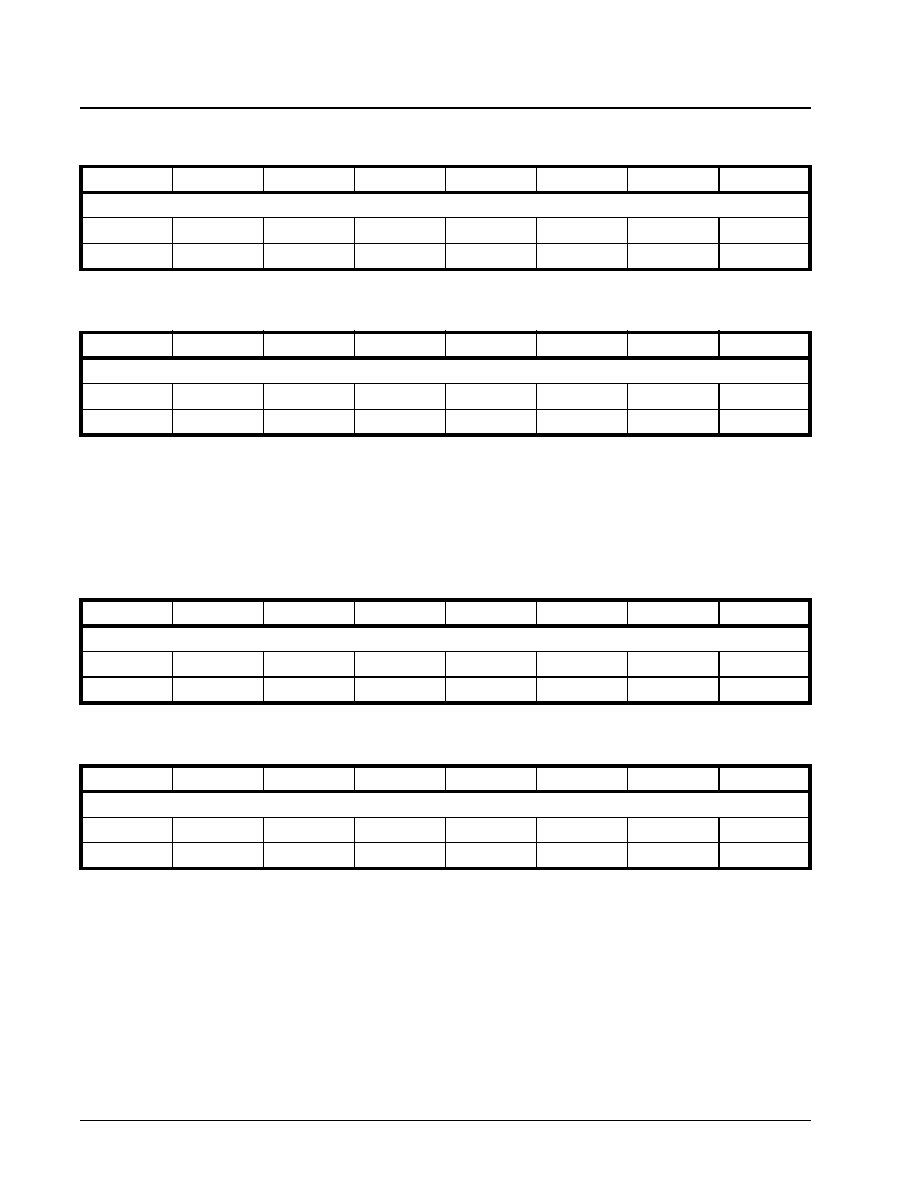

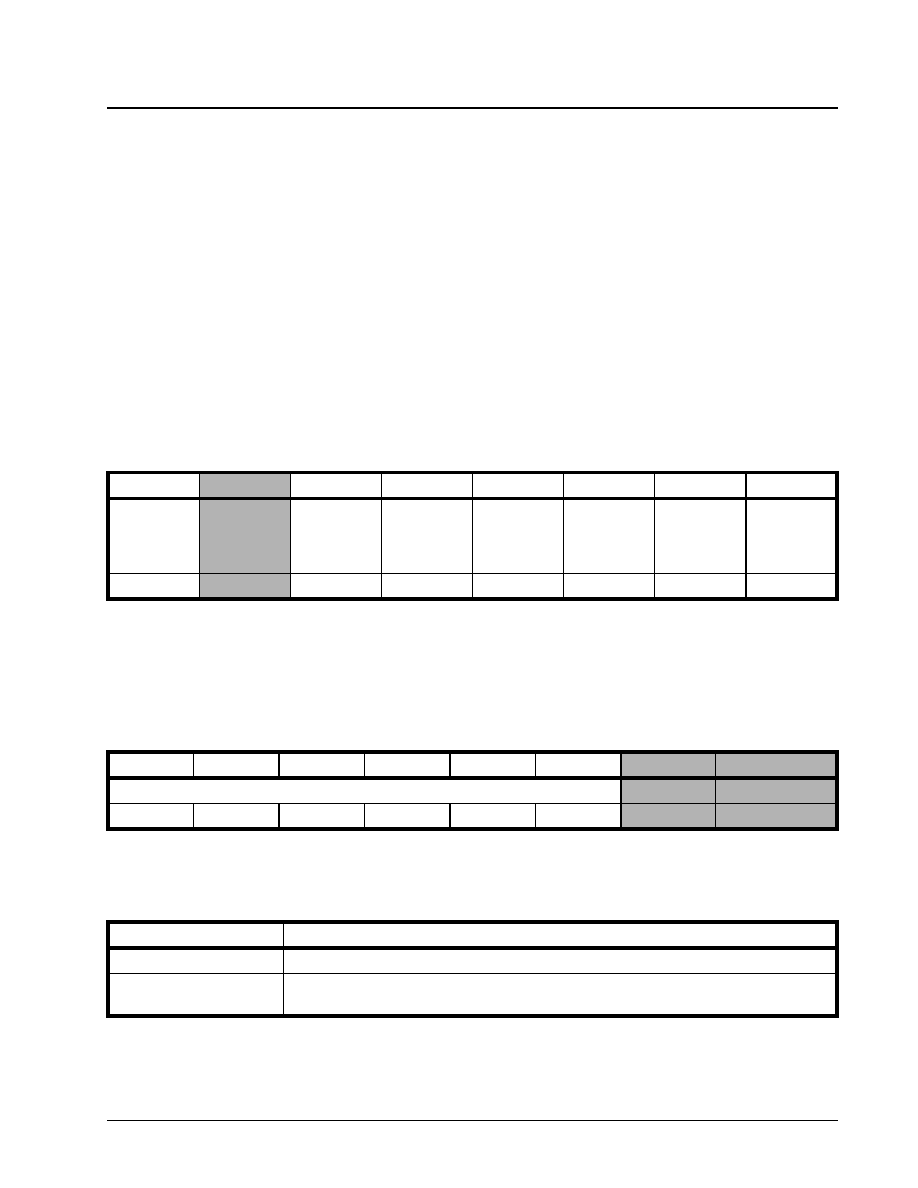

F

IGURE

1. B

LOCK

D

IAGRAM

OF

THE

XRT7245 DS3 UNI IC

Microprocessor Interface

(Programmable

Registers and Interrupt

Block)

Line I/F Drive and Scan

Transmit

DS3

Framer

Transmitter

Receiver

Receive

DS3

Framer

Performance

Monitor

Transmit

PLCP

Processor

Transmit Cell

Processor

Tx Utopia

Interface

Receive

PLCP

Processor

Receive Cell

Processor

Rx Utopia

Interface

A[8:0]

WrB_RW

RdB_DS

CSB*

ALE_AS

Reset

IntB*

D[15:0]

Width16

MOTO/Intel*

Rdy_Dtck

TxPOS

TxNEG

TxFrame

TxOHClk

TxLineClk

TxAISEn

TxFrameRef

TxInClk

TxOHIns

TxOH

TxPFrame

8kRef

StuffCtl

TxPOHFrame

TxPOH

TxPOHClk

TxCellTxed

TxGFCClk

TxGFCMSB

TxGFC

TxClk

TxData[15:0]

TxPrty

TxSoC

TxEnB

RxLineClk

RxNEG

RxPOS

RLOS

RxAIS

RxOHClk

RxOH[7:0]

RxLOS

RxFrame

RxOOF

RxPOHClk

RxPOH

RxPFrame

RxPLOF

RxPOOF

RxPOHFrame

RxCellRxed

RxGFCClk

RxGFCMSB

RxGFC

TxClav/TFullB

RFClk

RxEnB

RxPrty

RxData[15:0]

RxSoC

RxClav/RxEmpty

RxAddr[4:0]

TxAddr[4:0]

Transmit

DS3

Framer

Test and Diagnostic

FEAC

Processor

LAPD

Transceiver

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

2

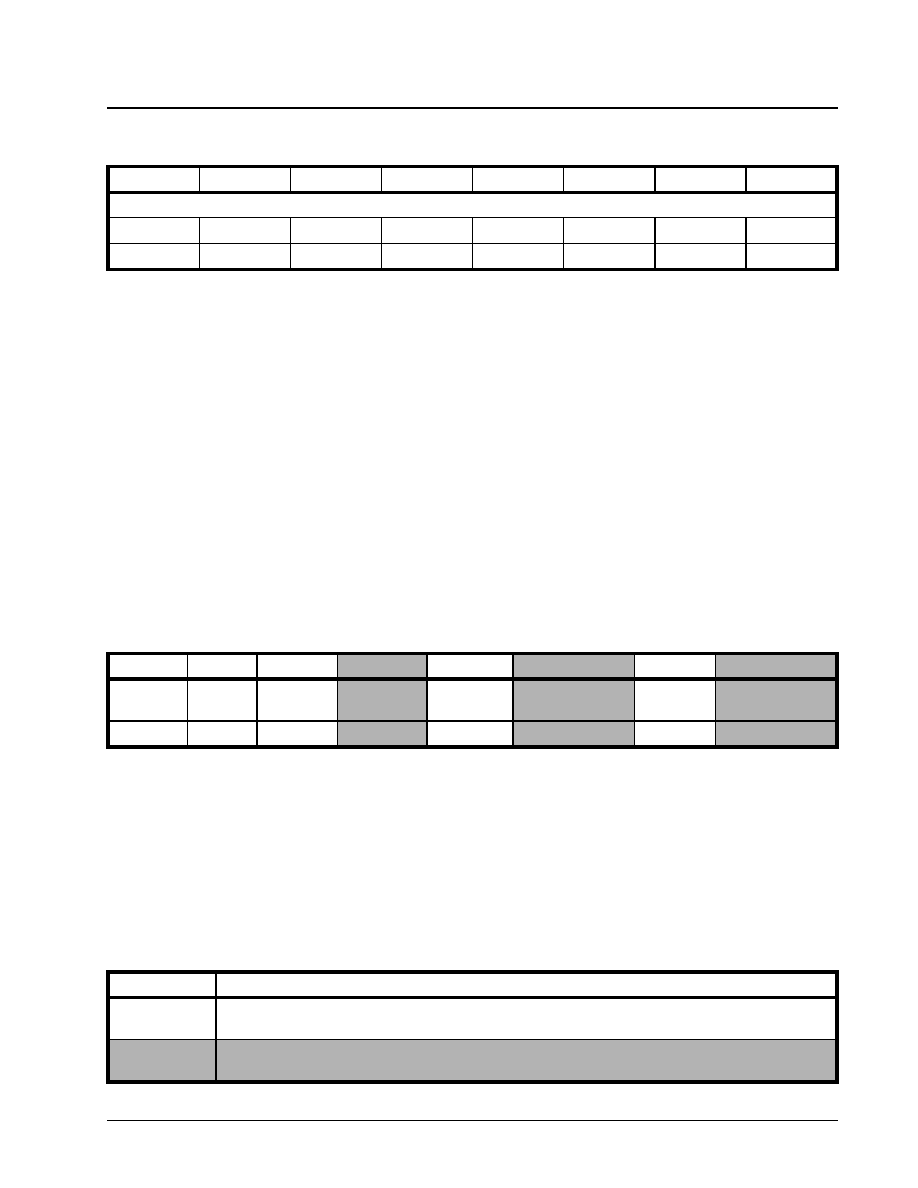

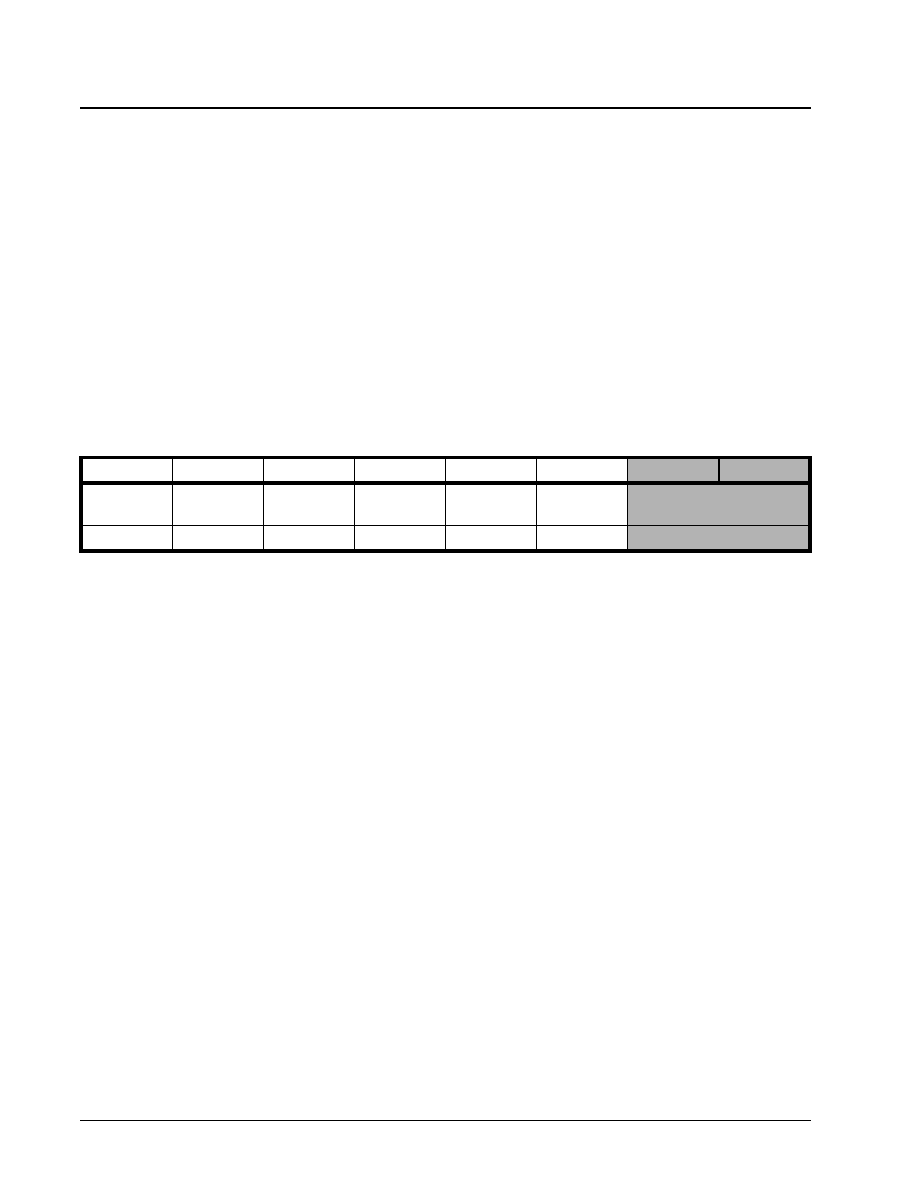

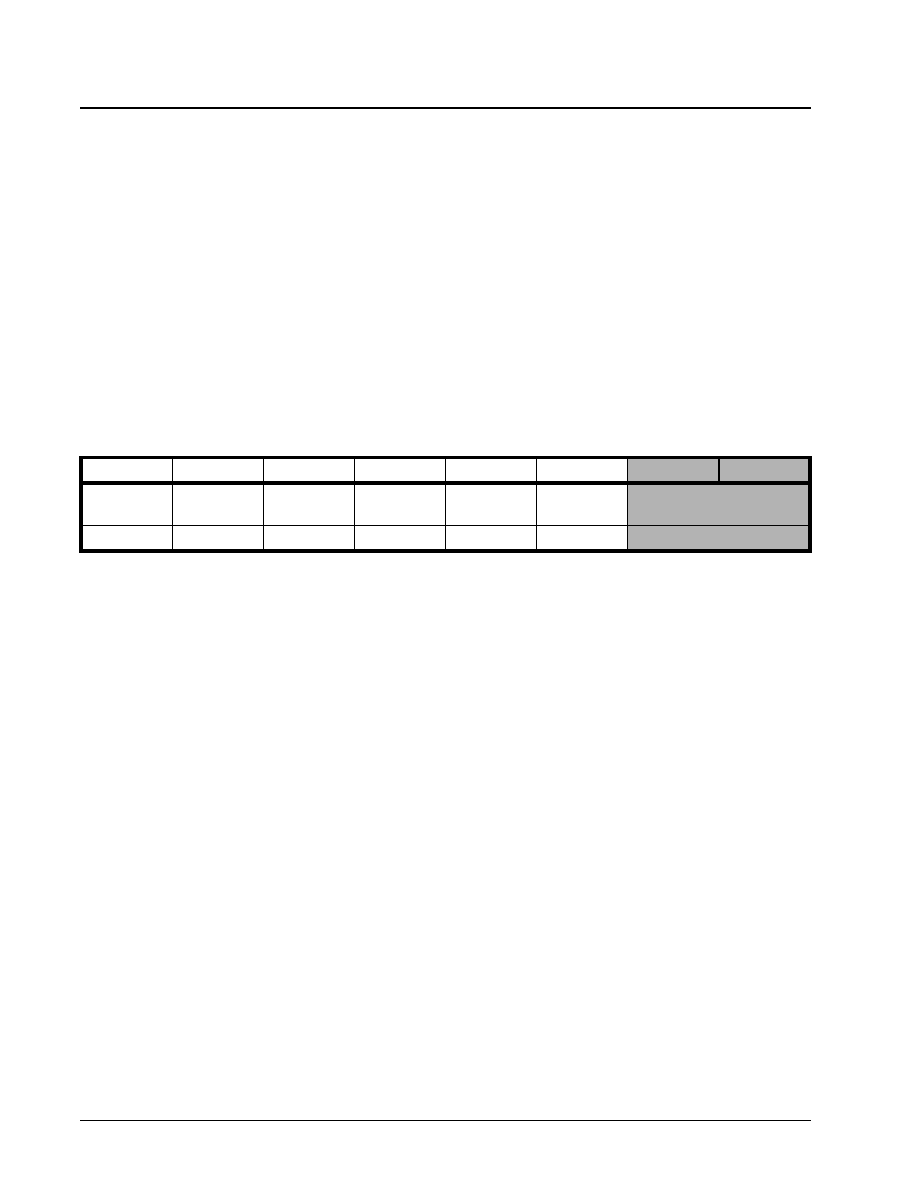

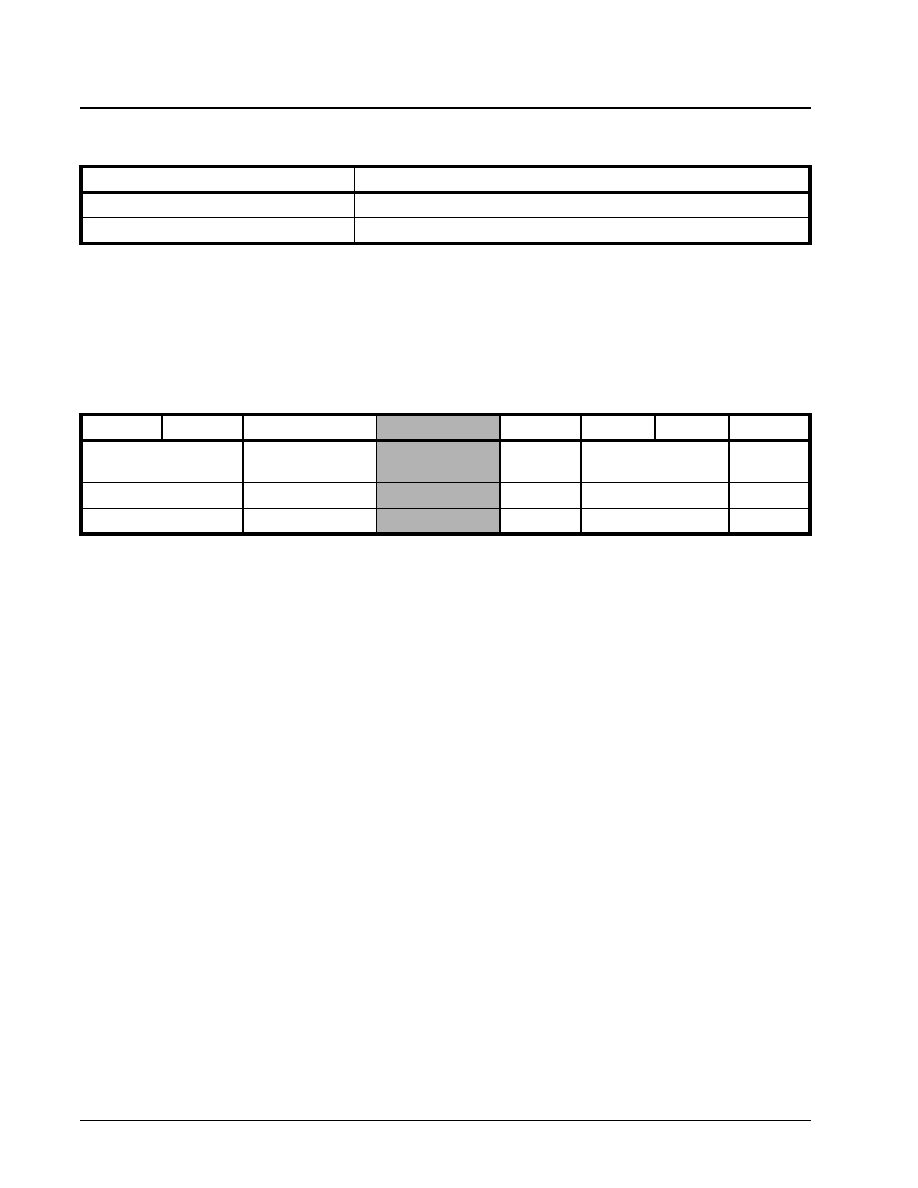

ORDERING INFORMATION

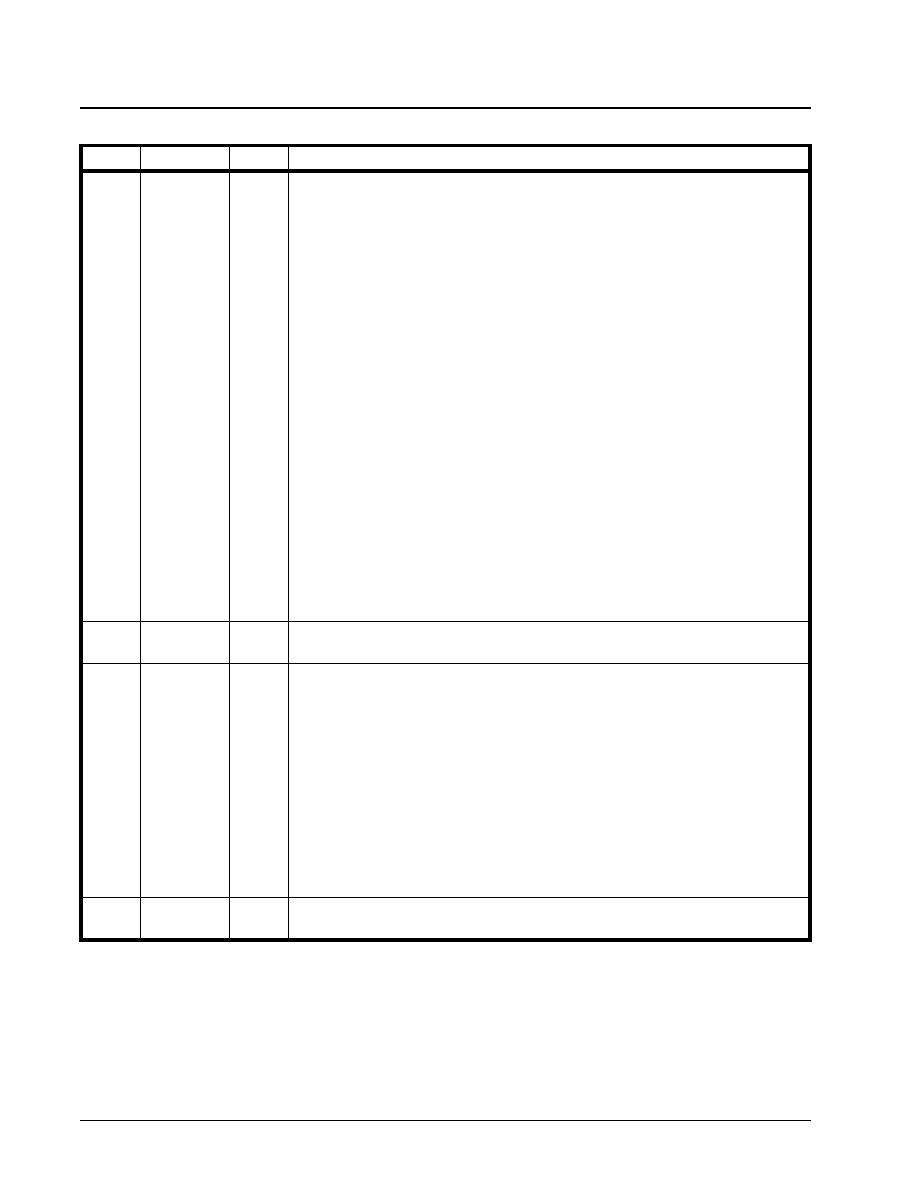

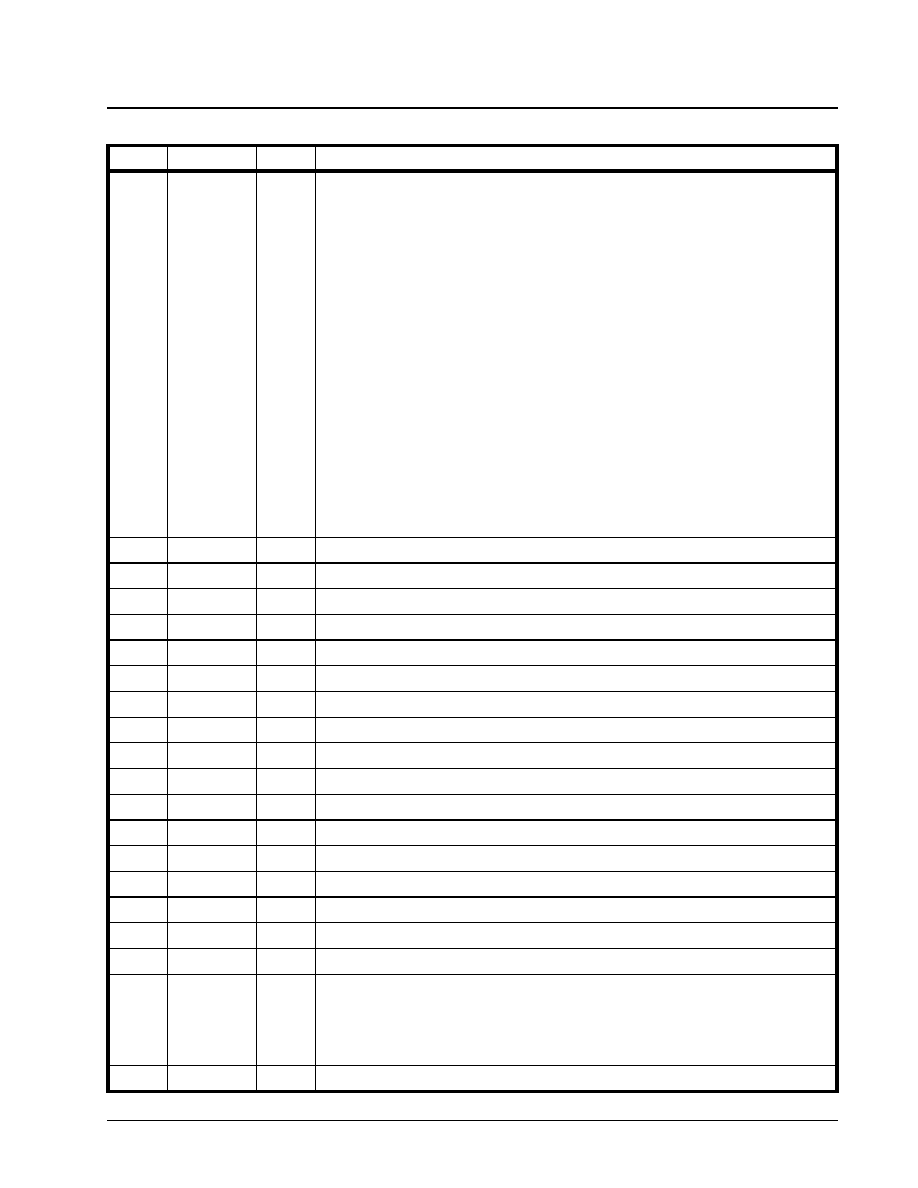

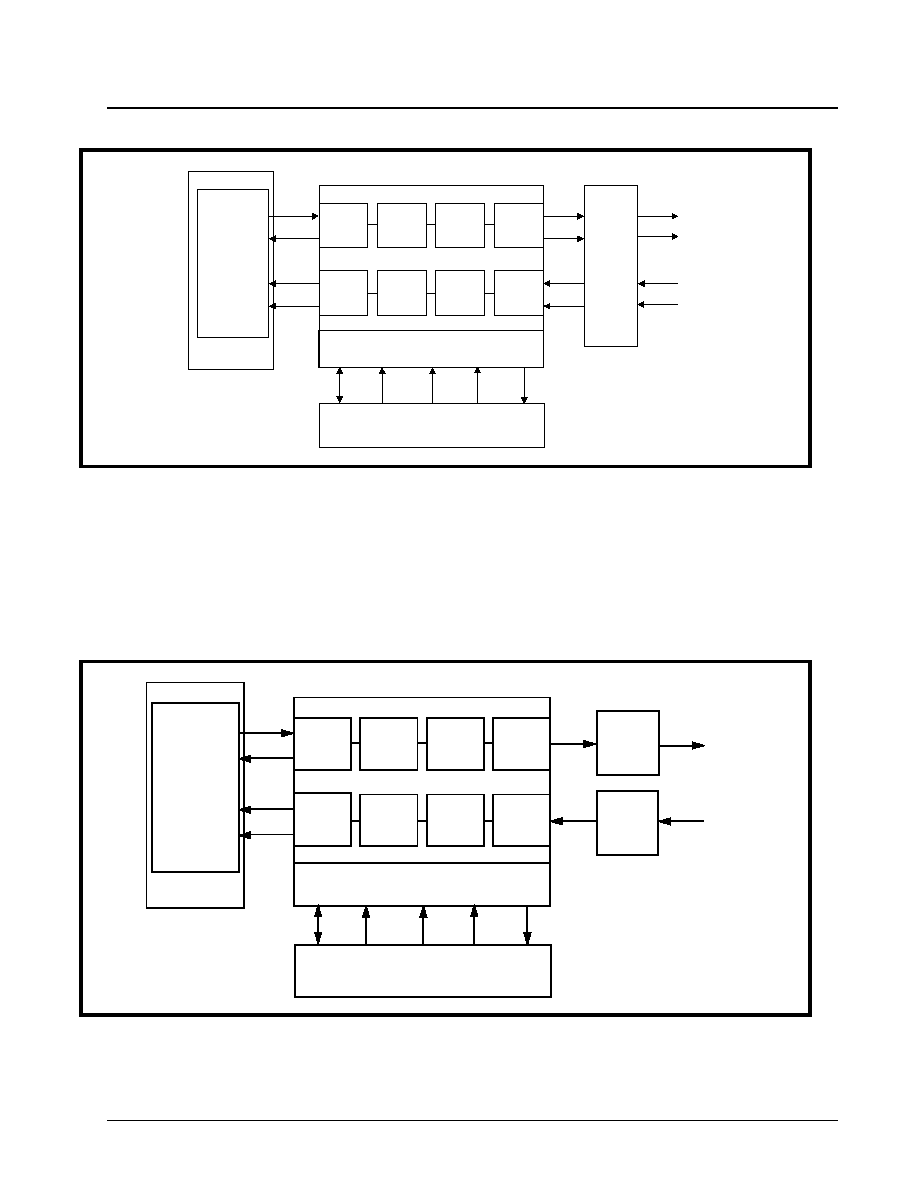

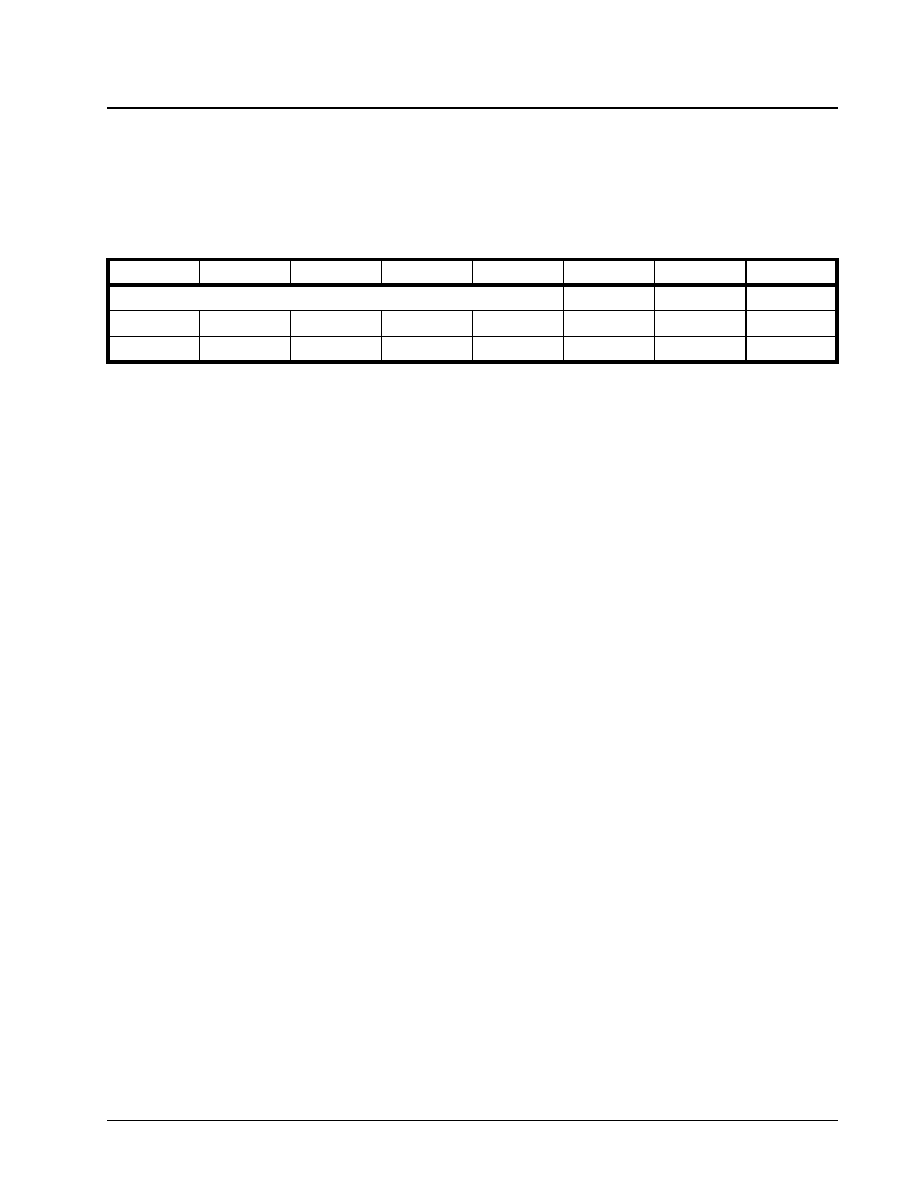

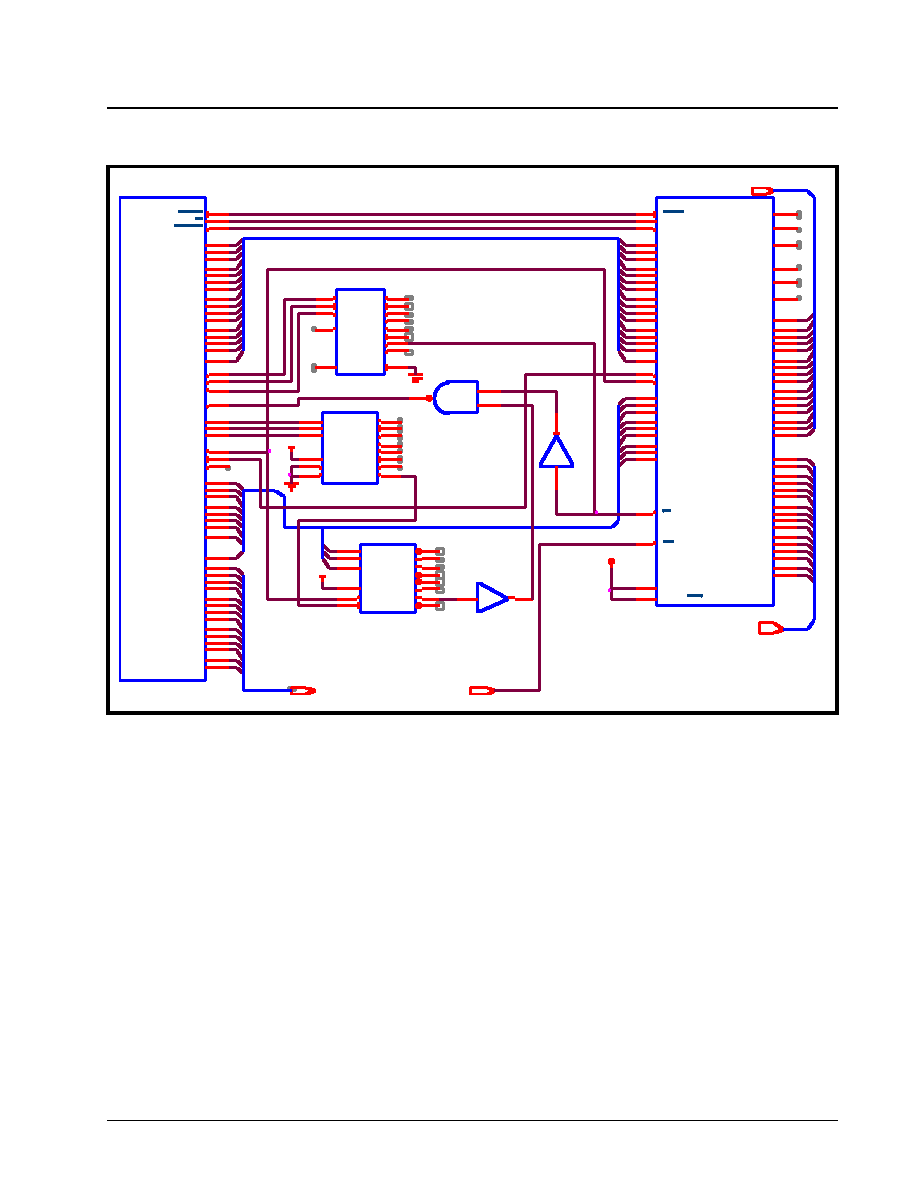

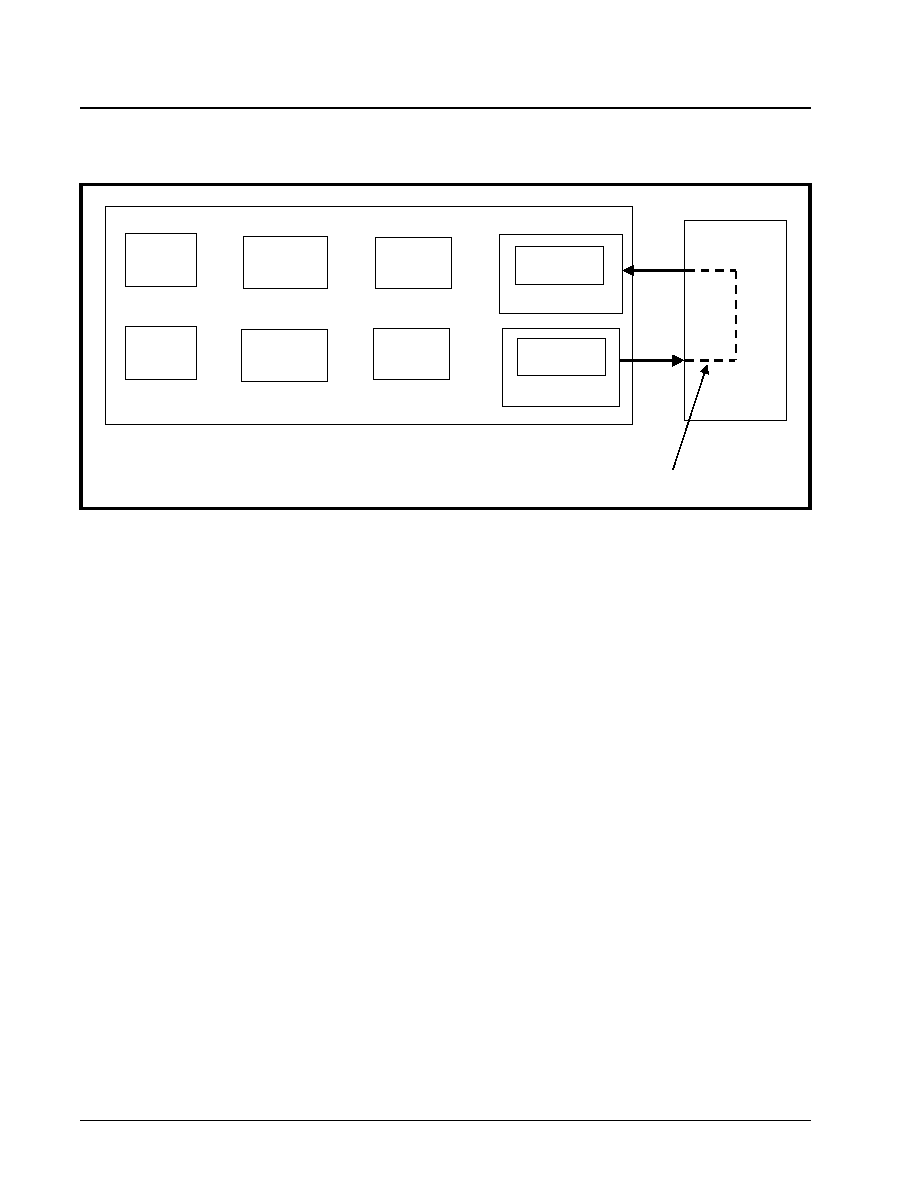

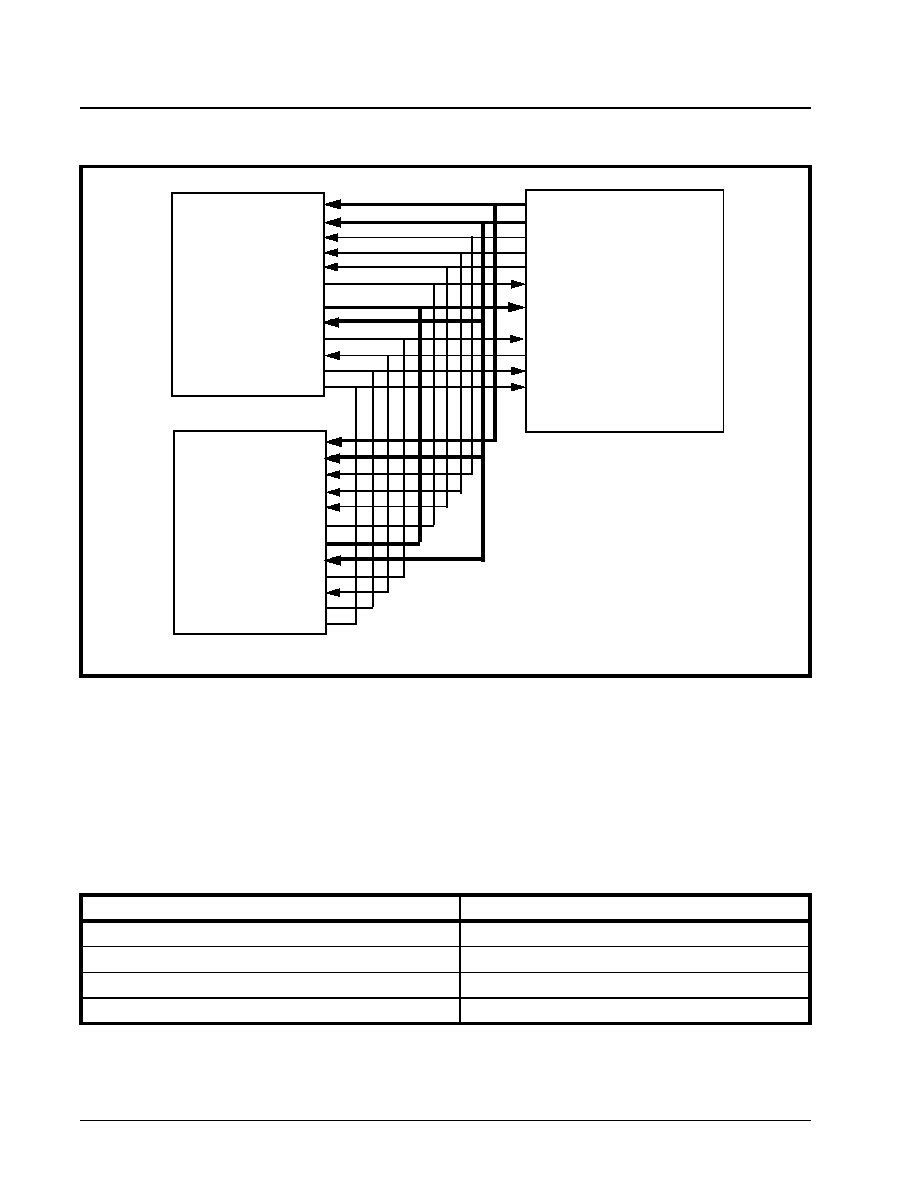

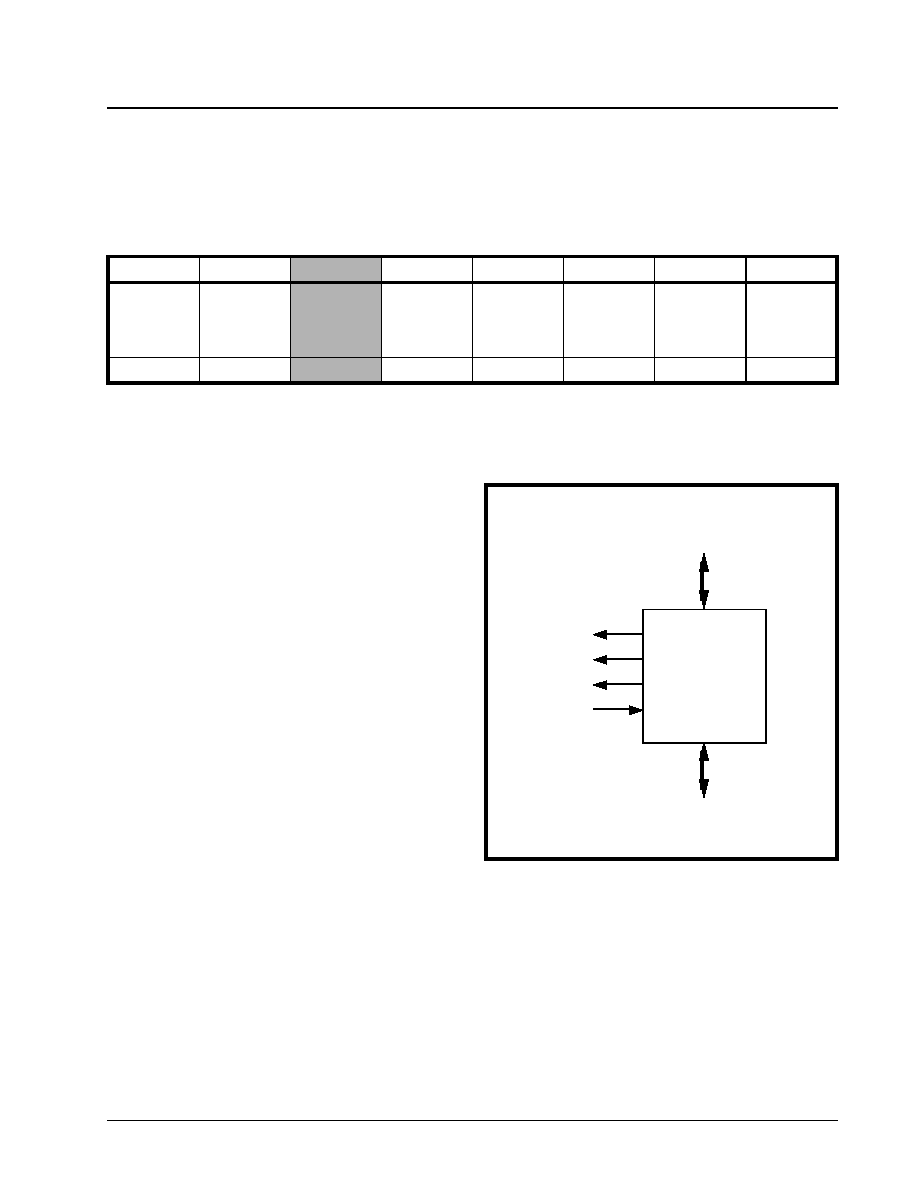

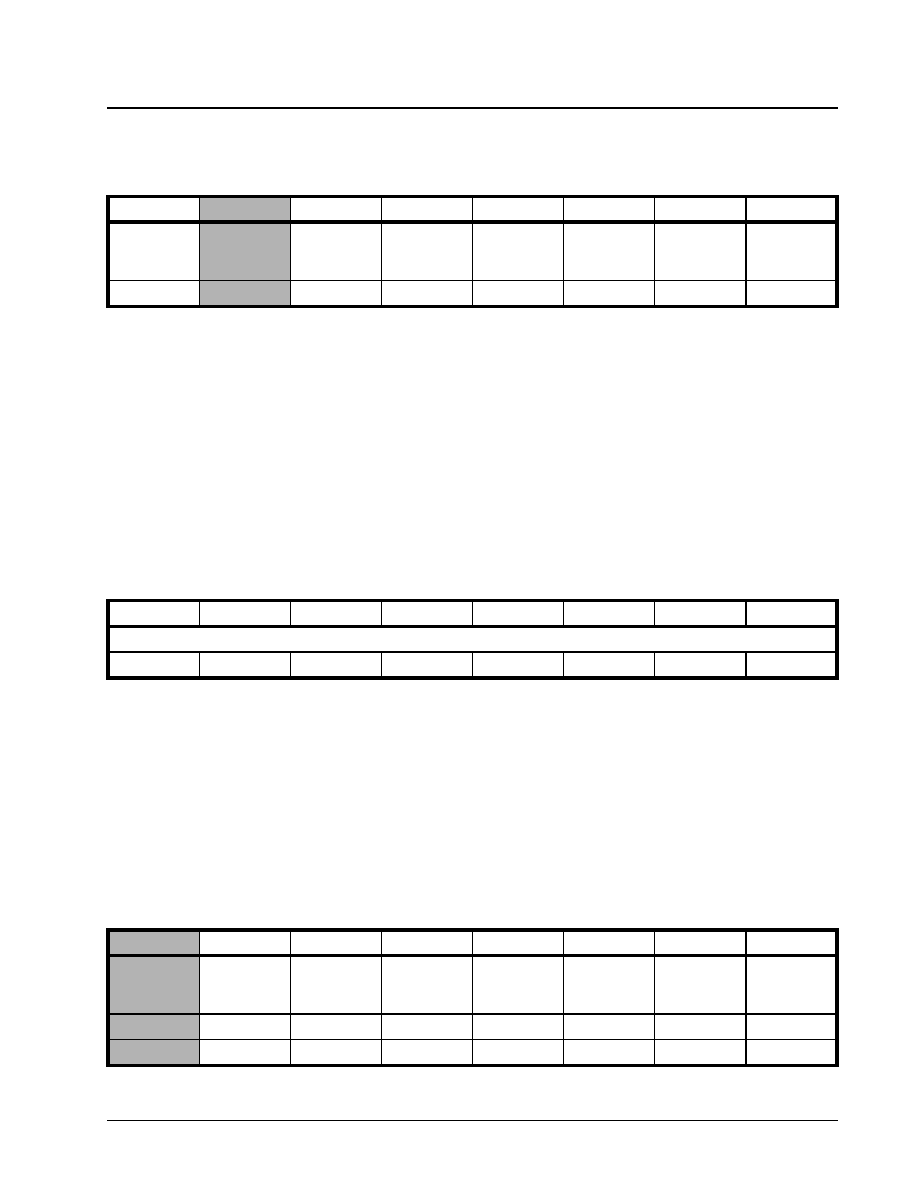

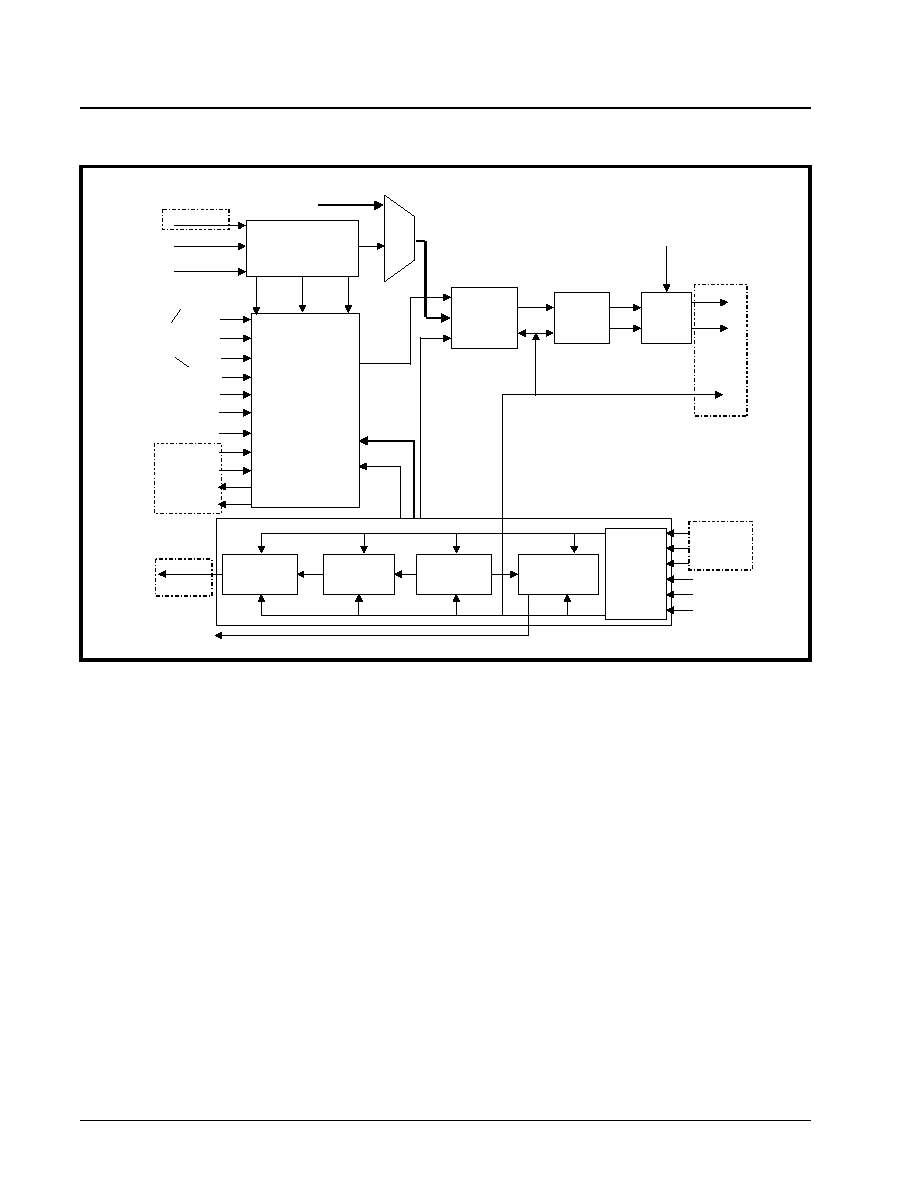

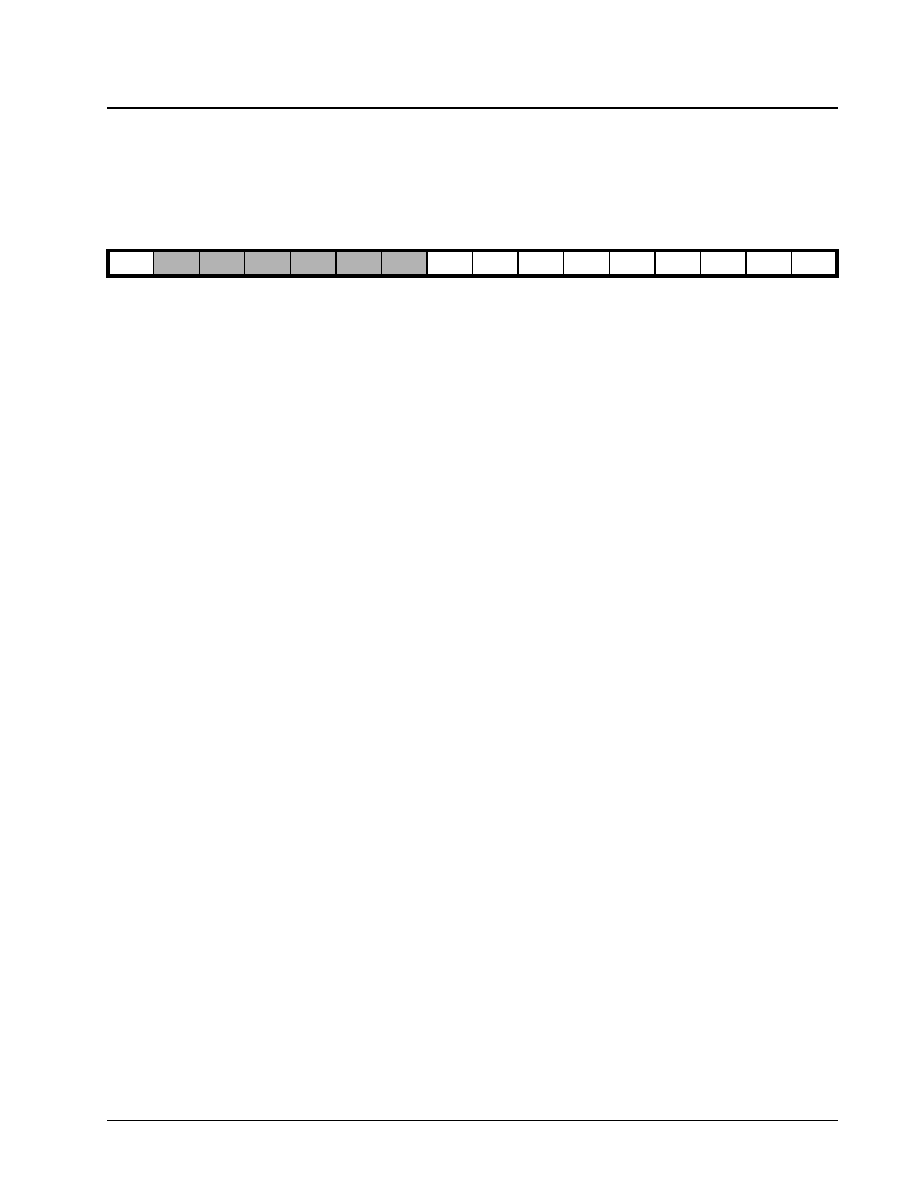

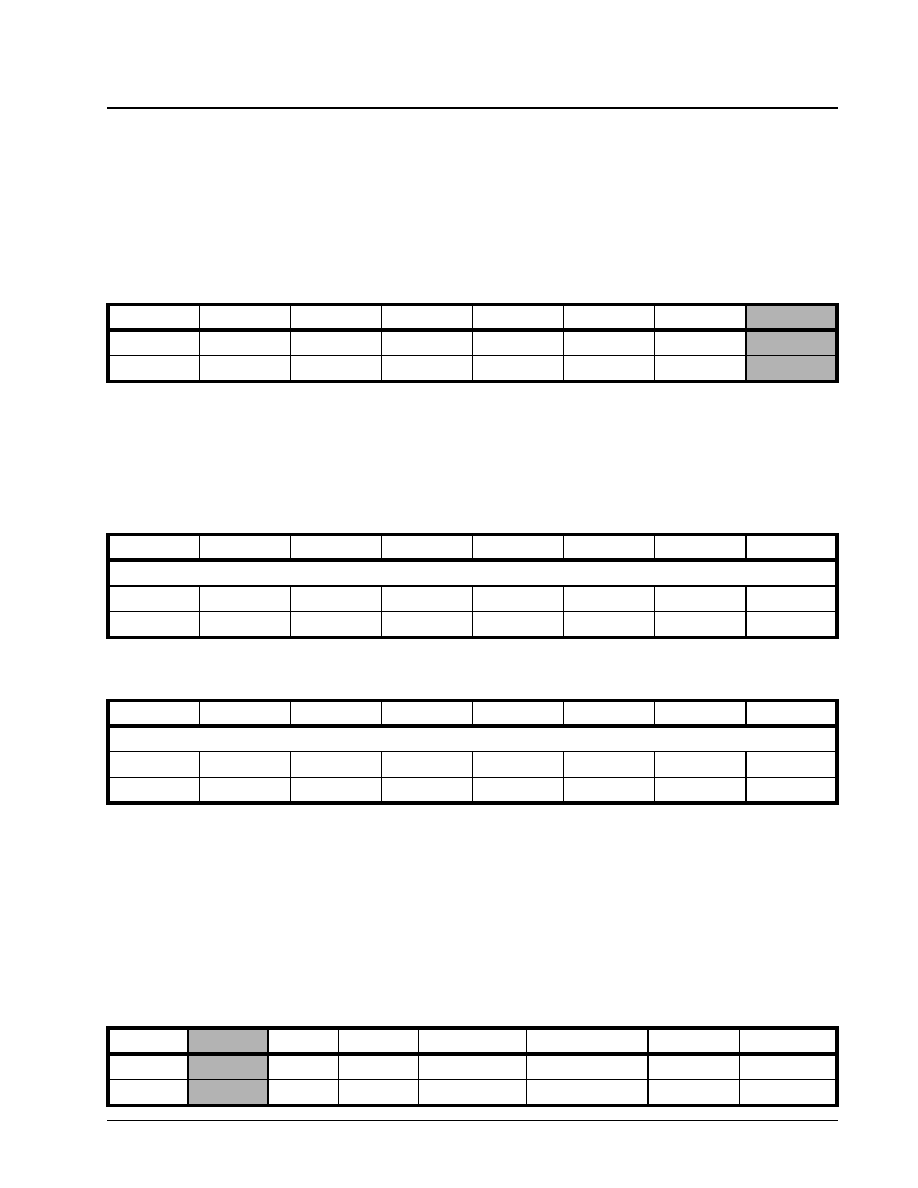

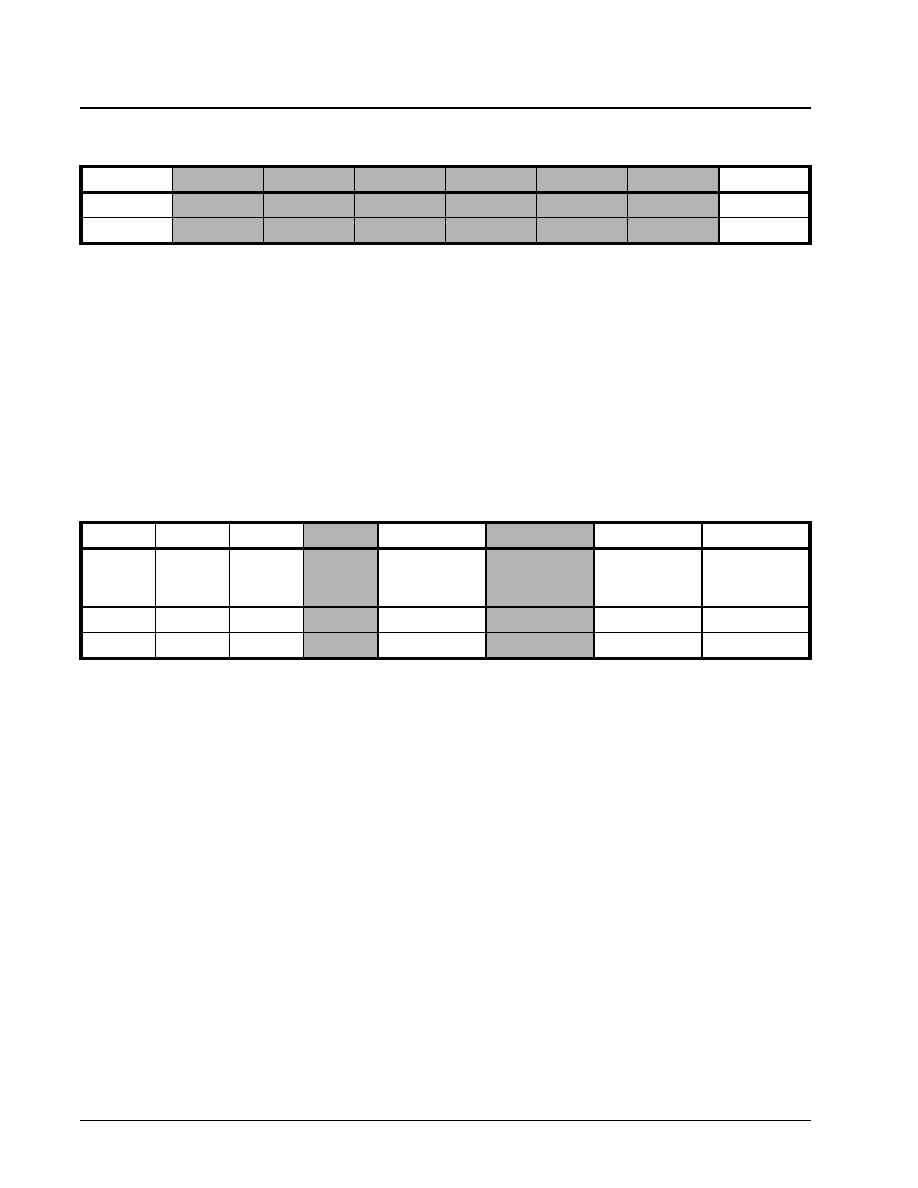

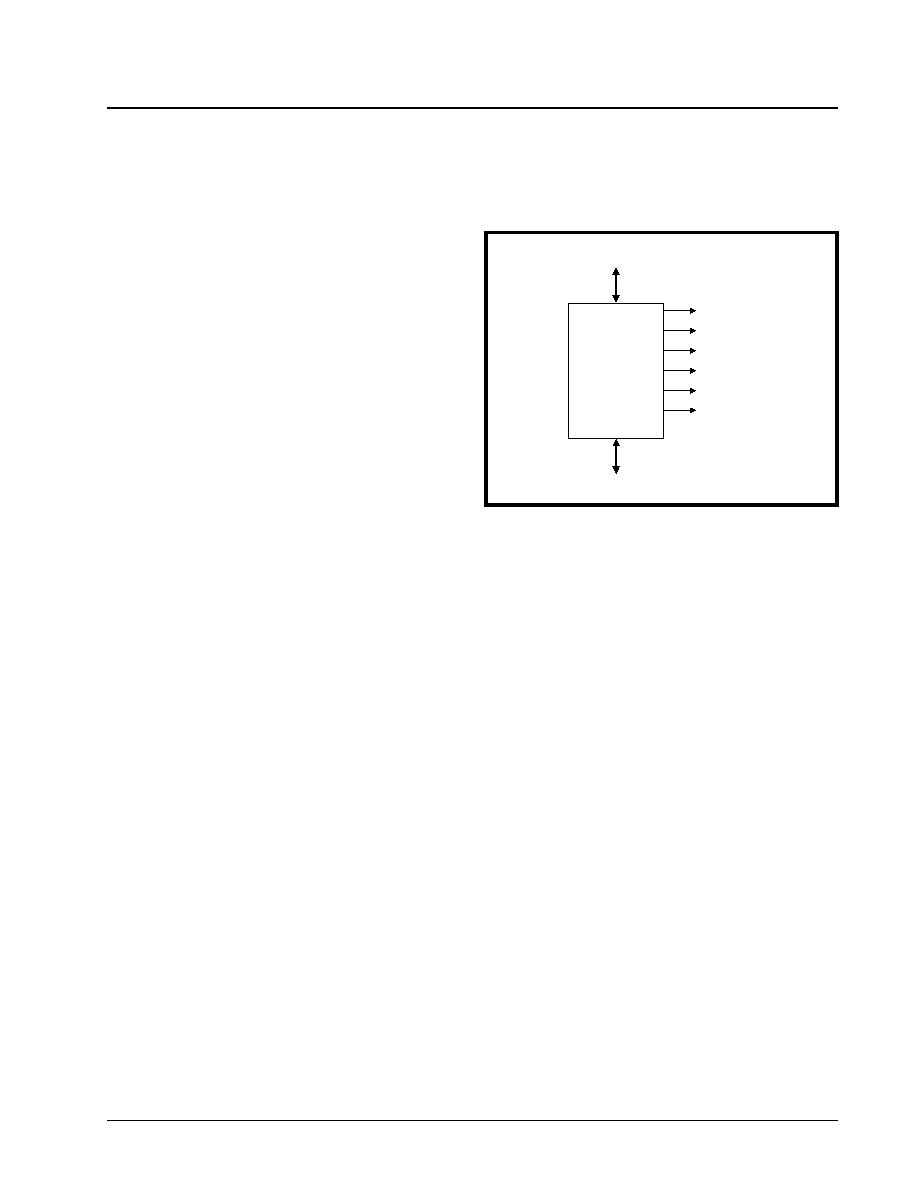

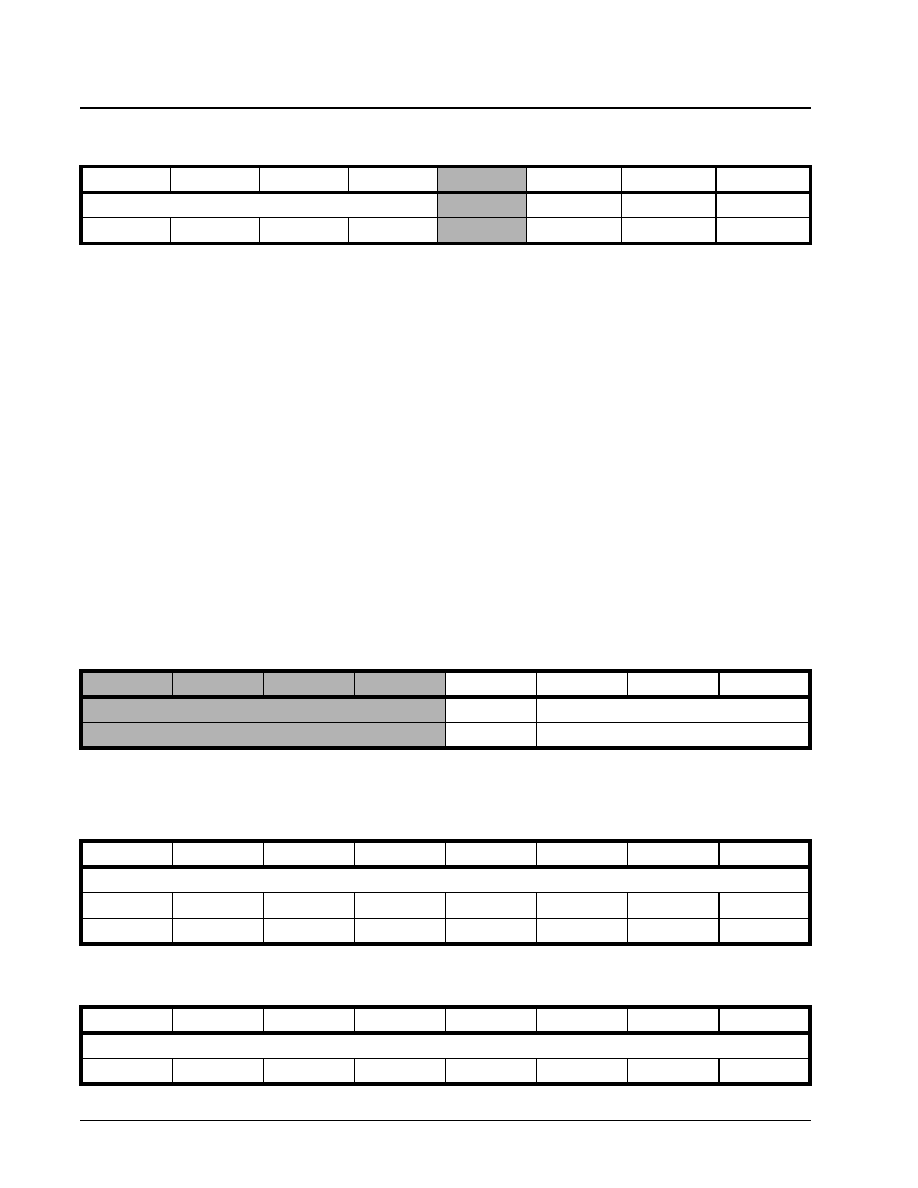

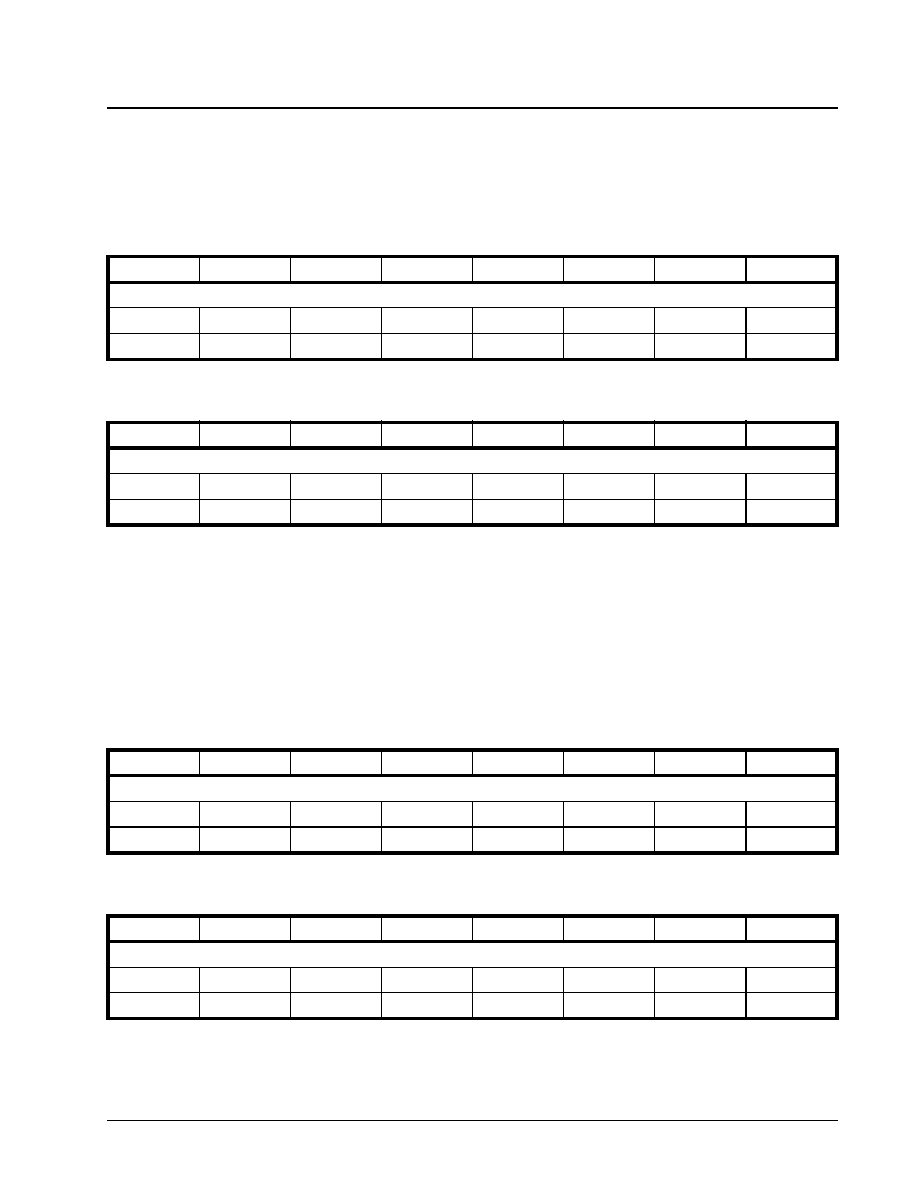

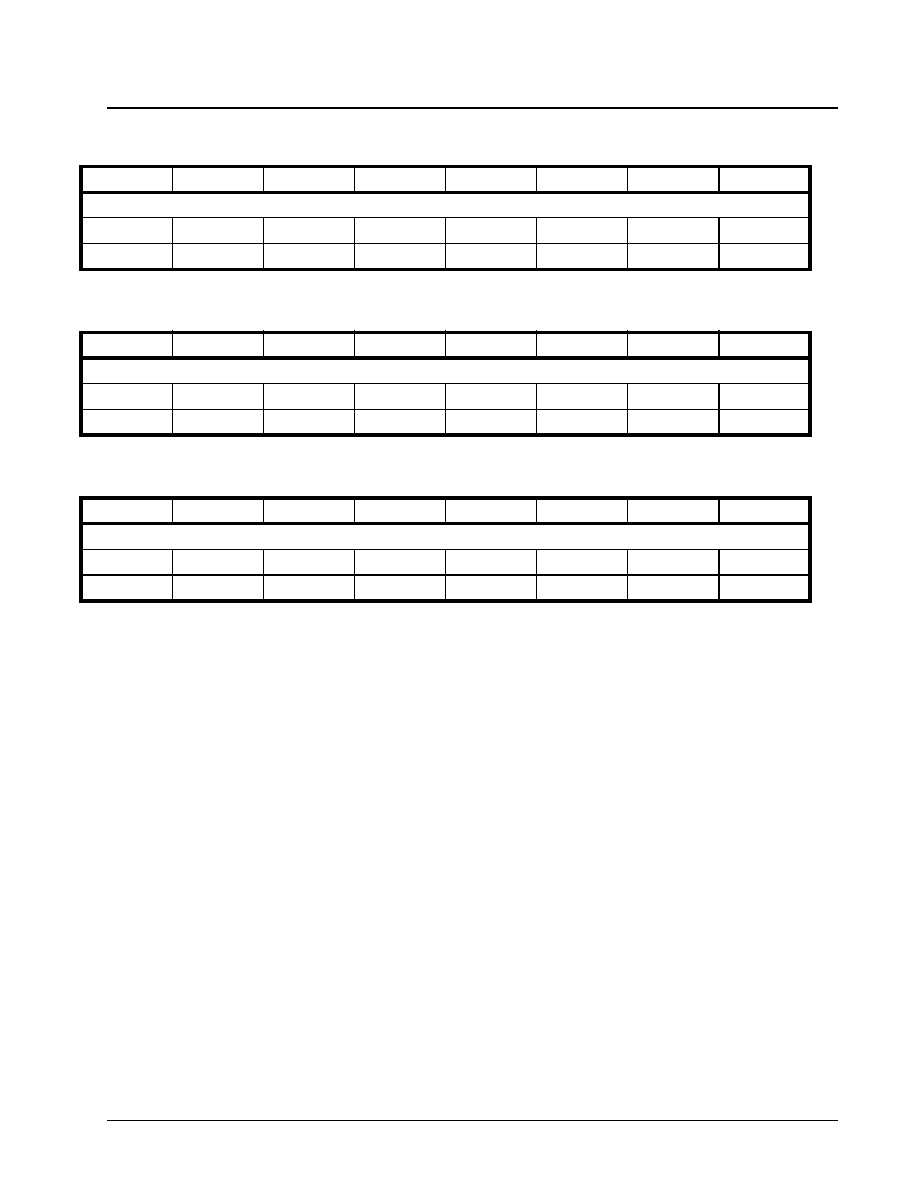

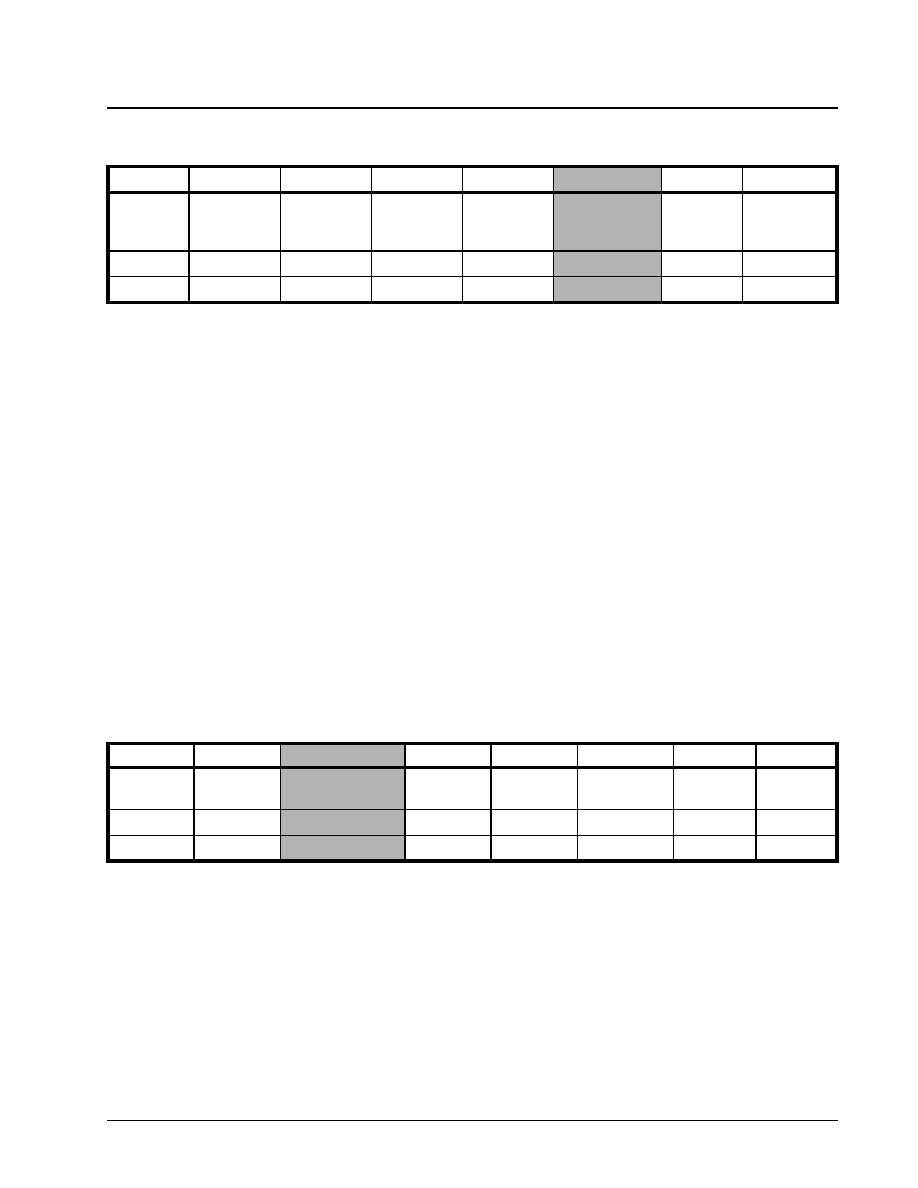

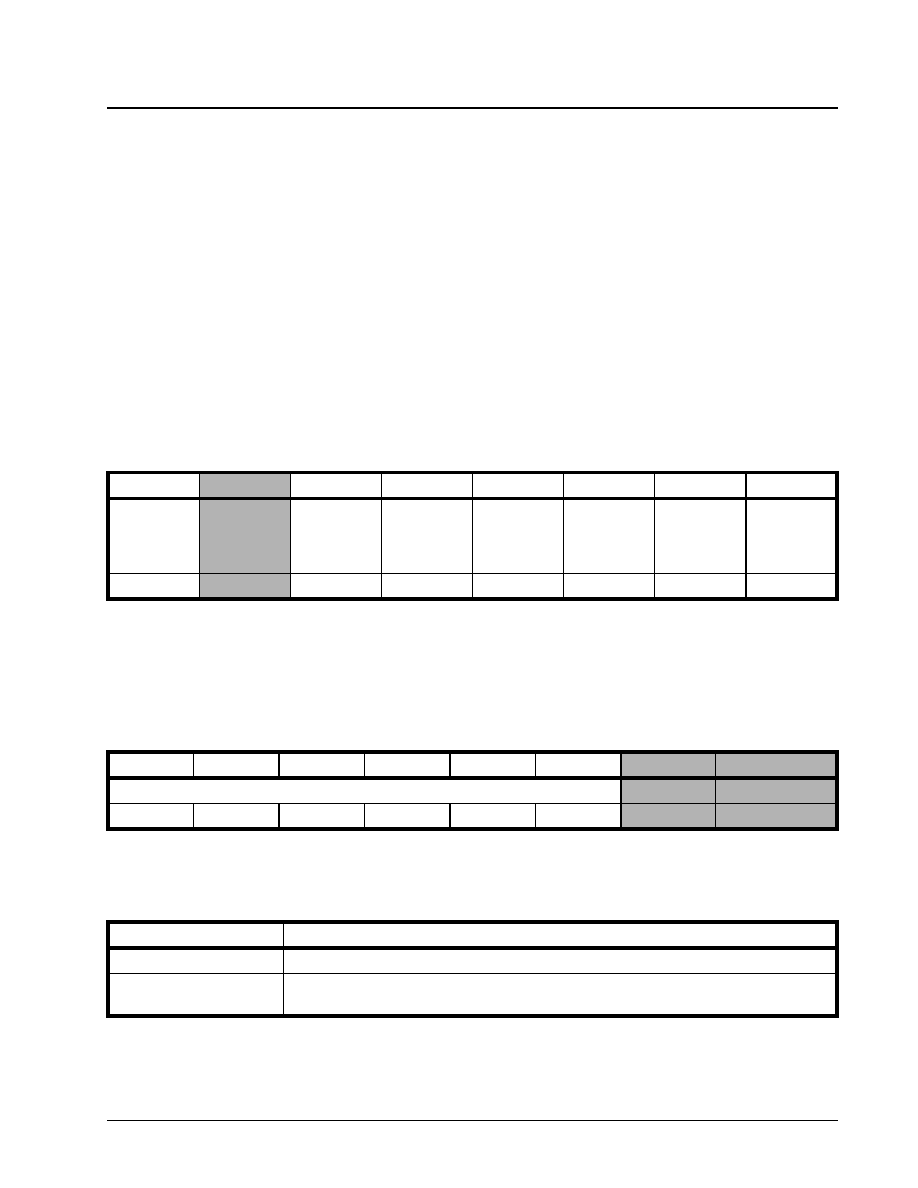

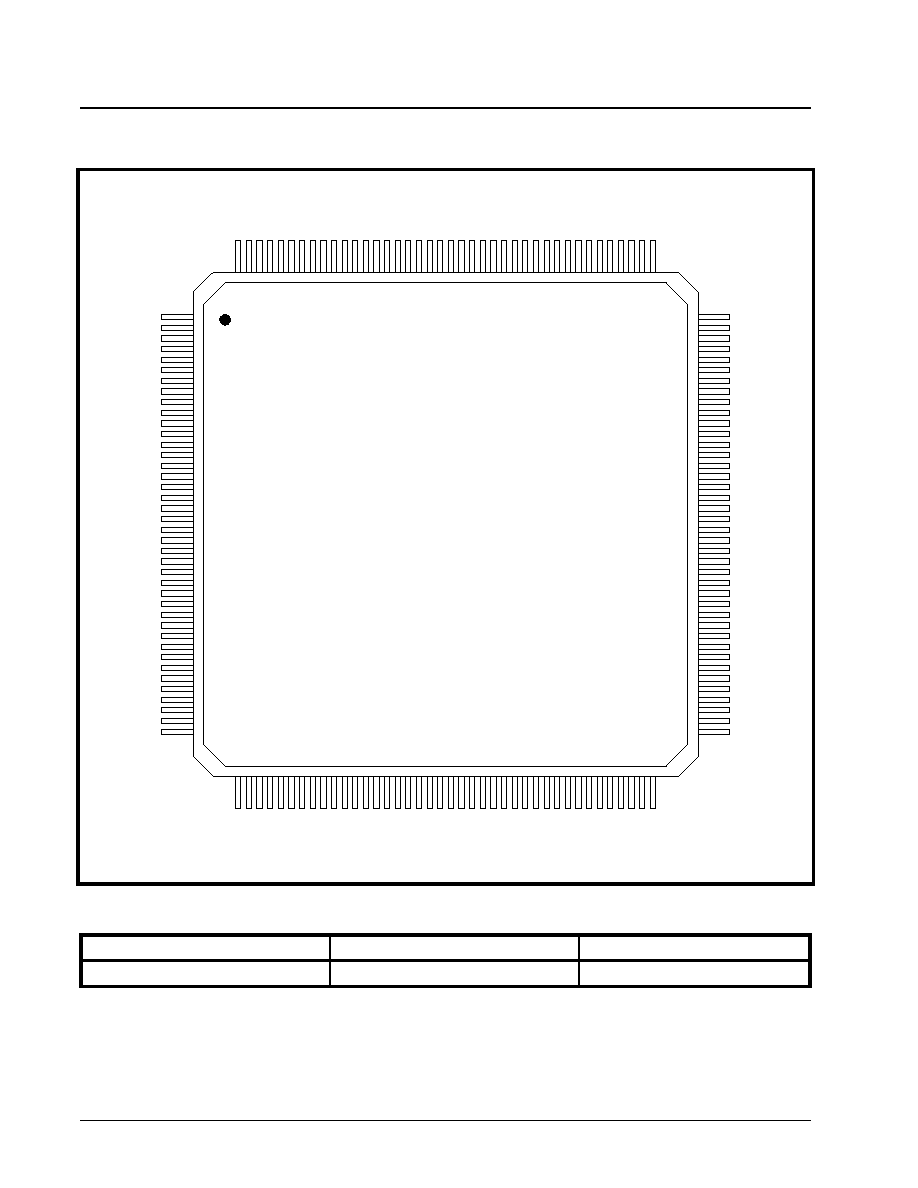

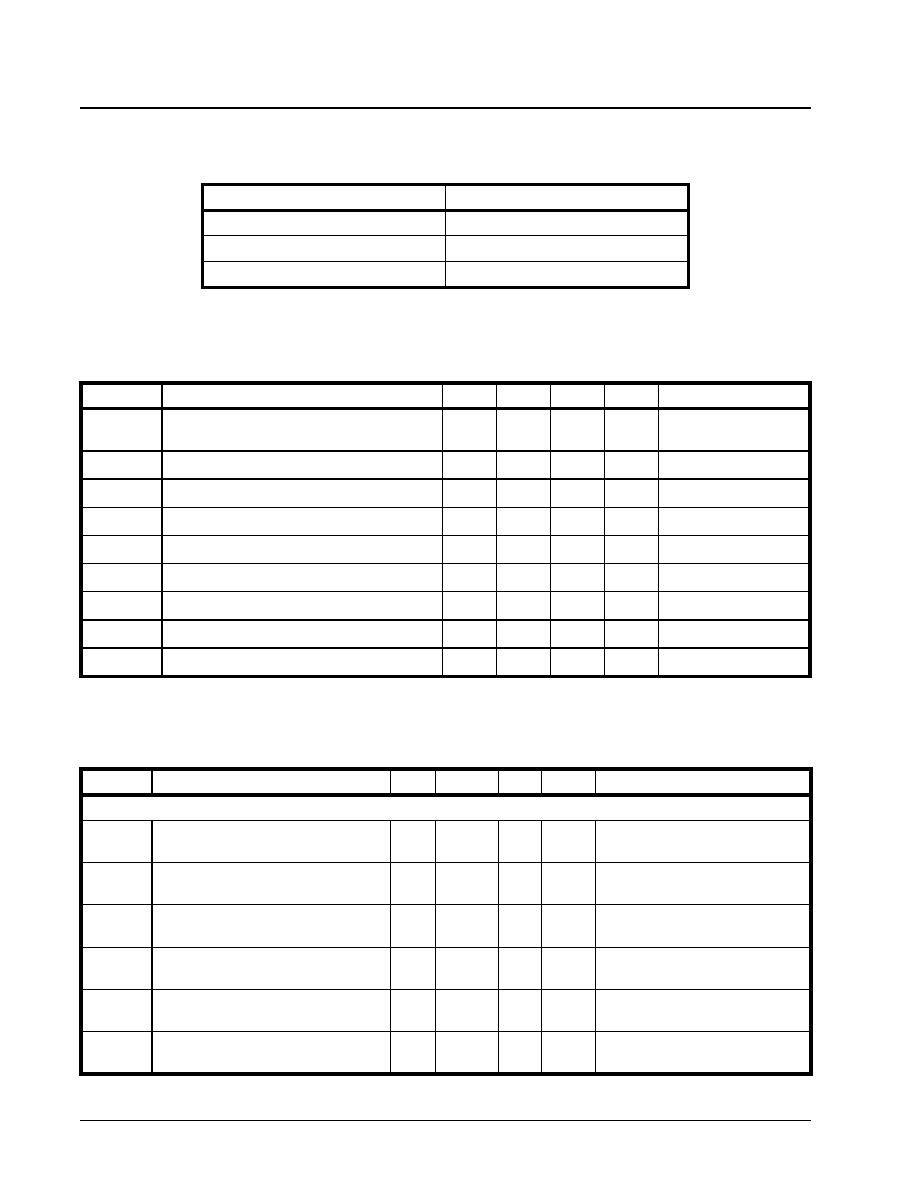

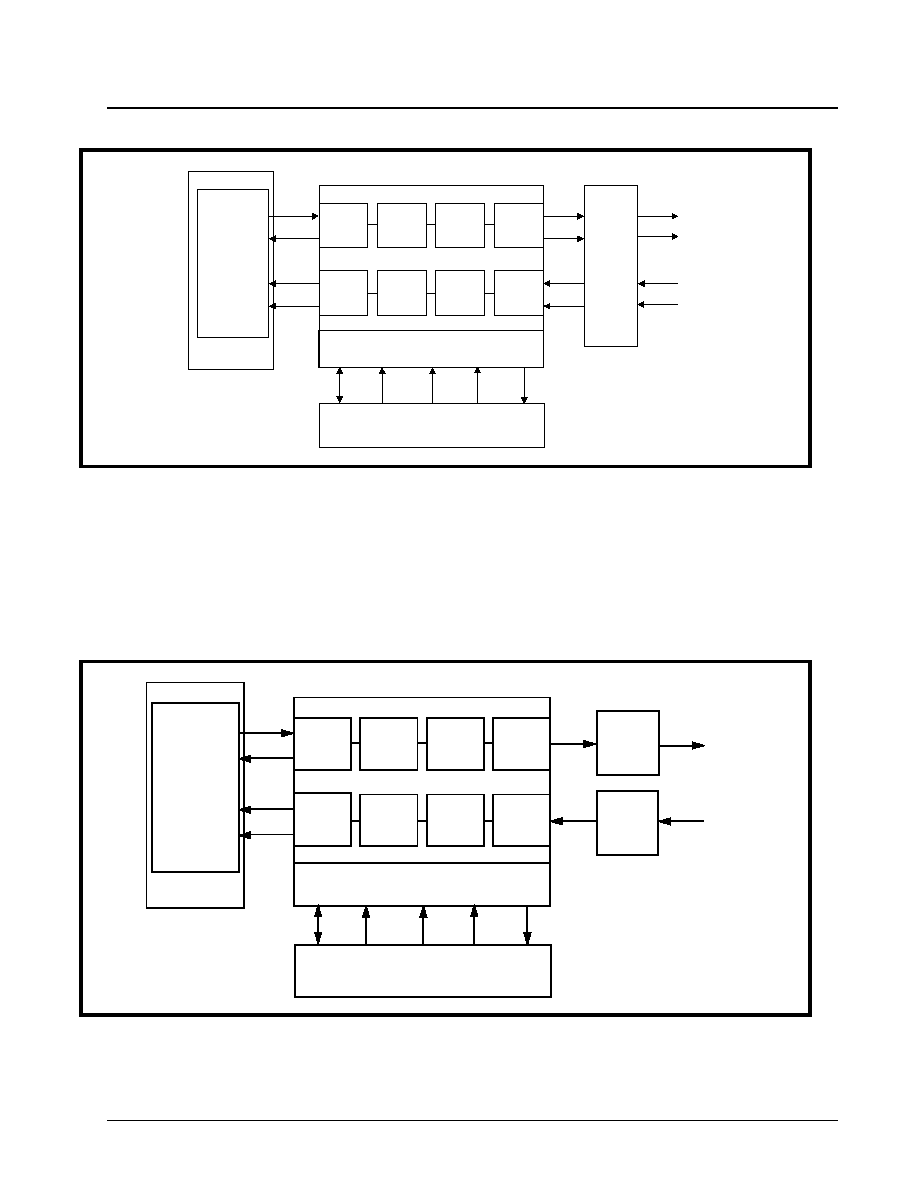

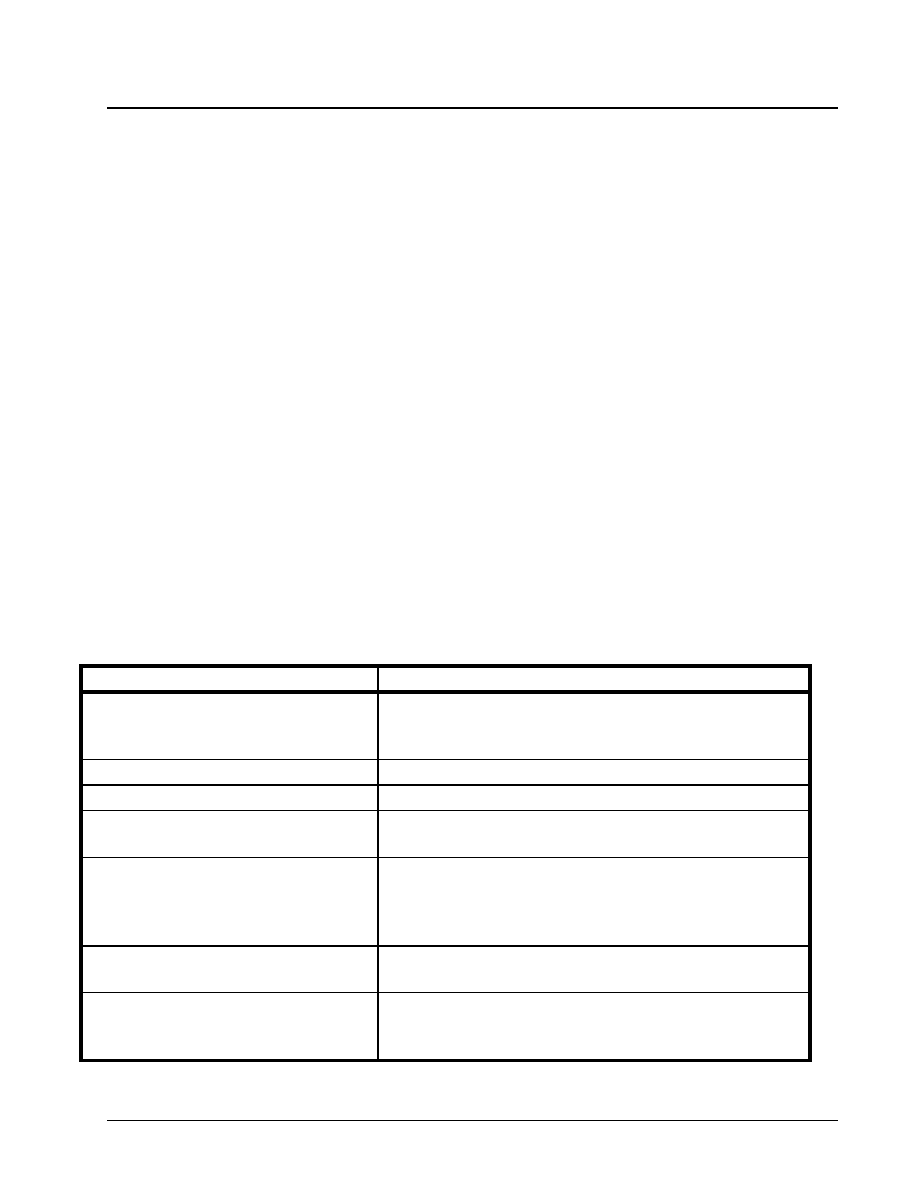

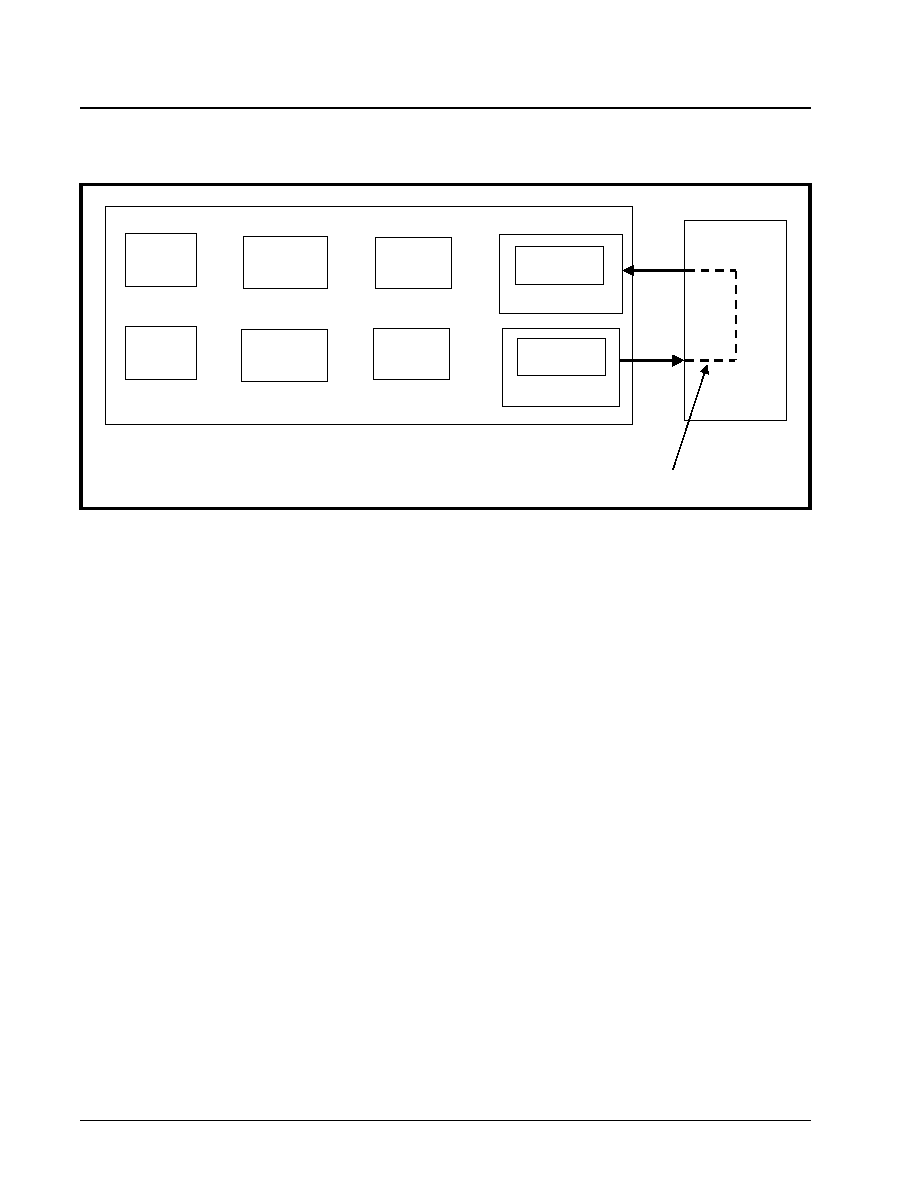

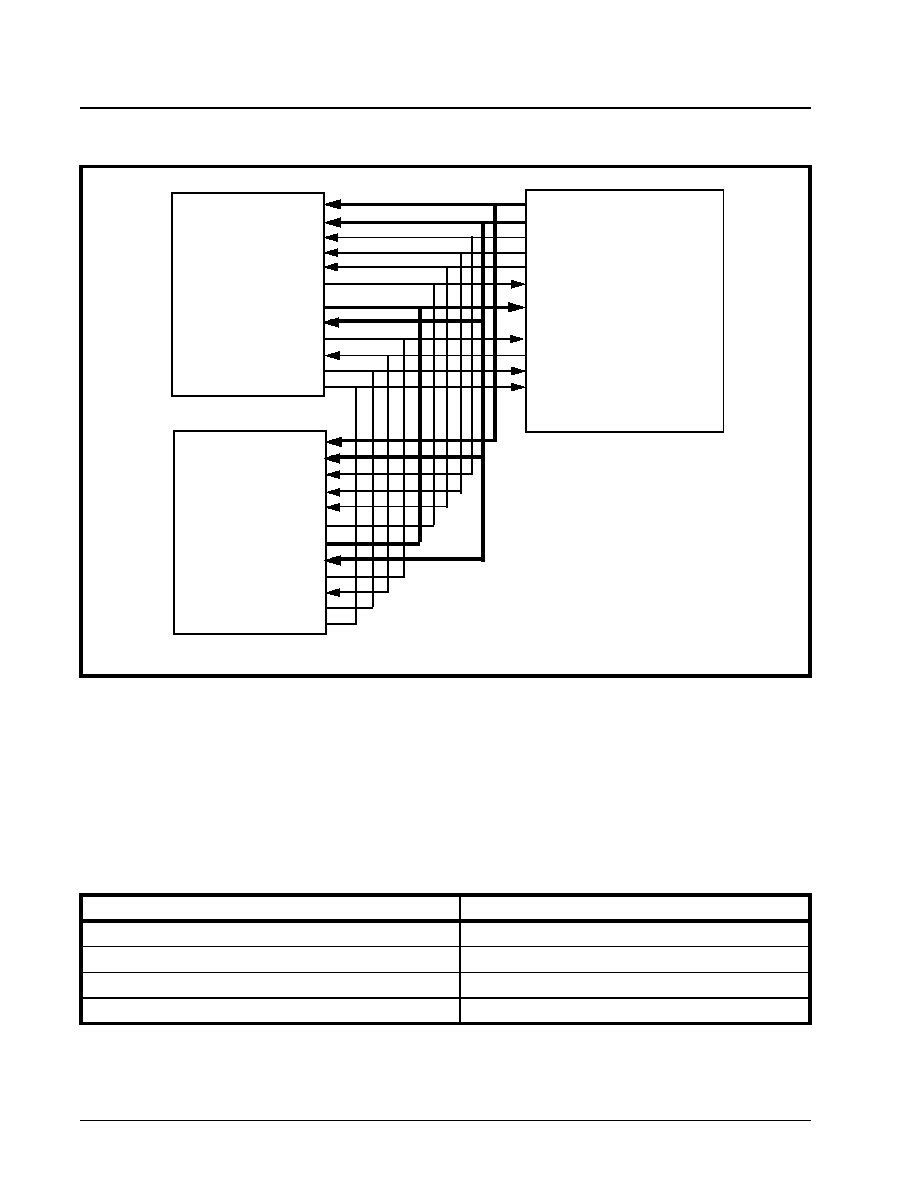

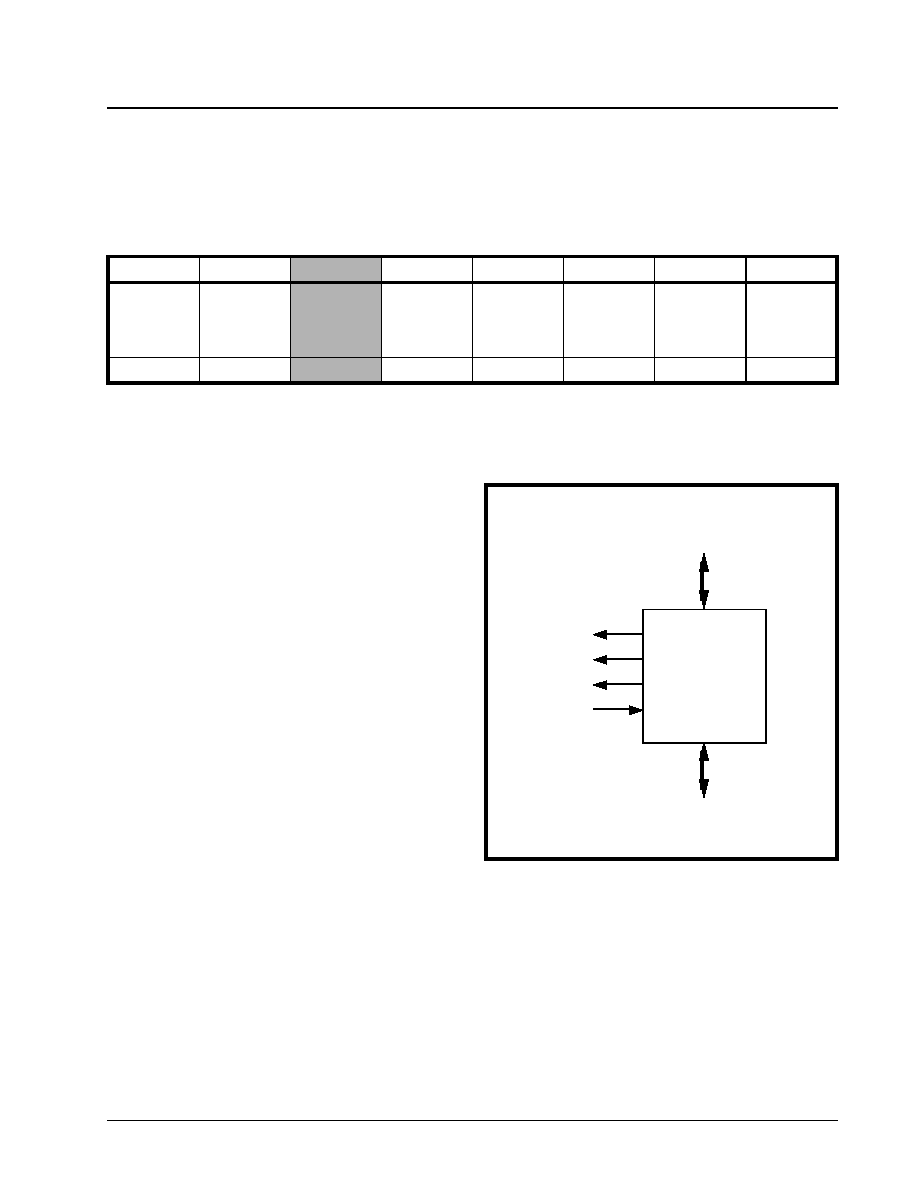

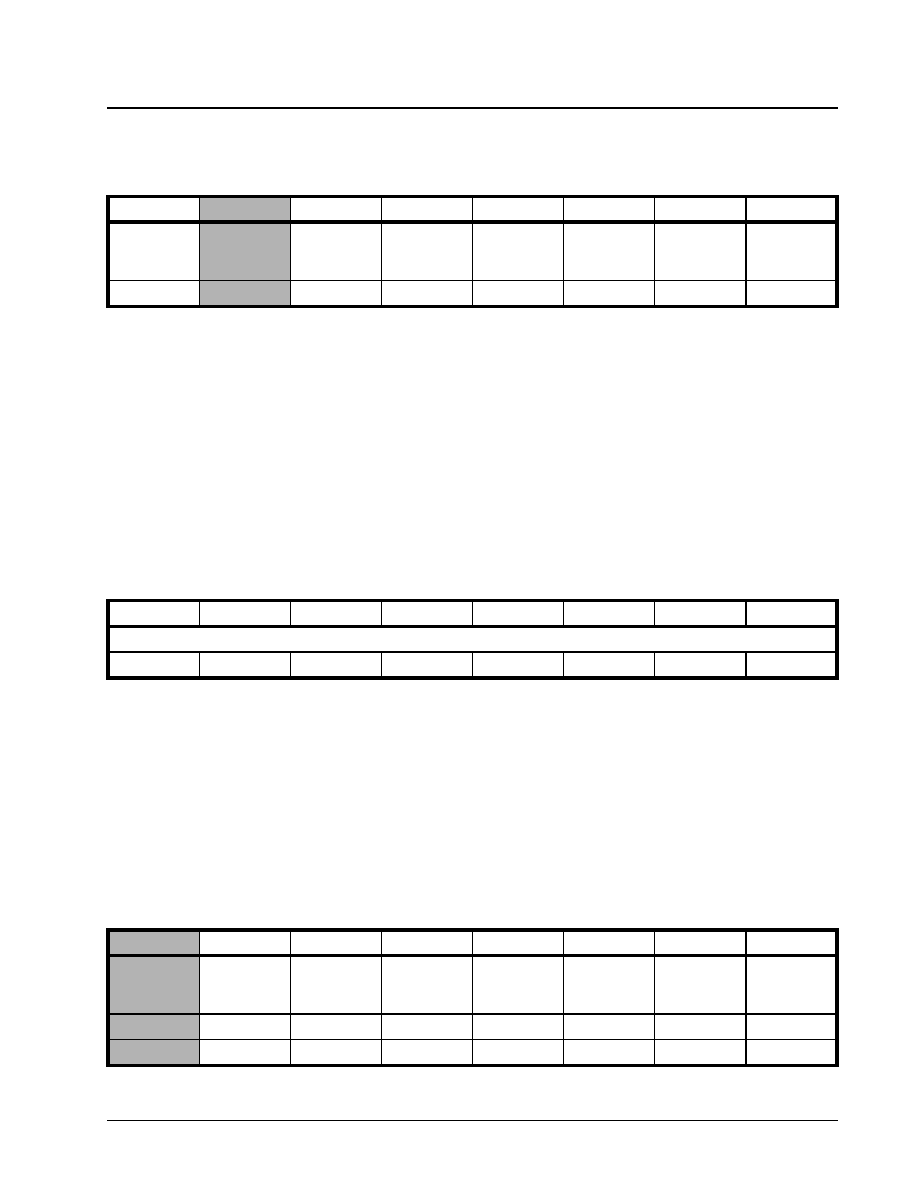

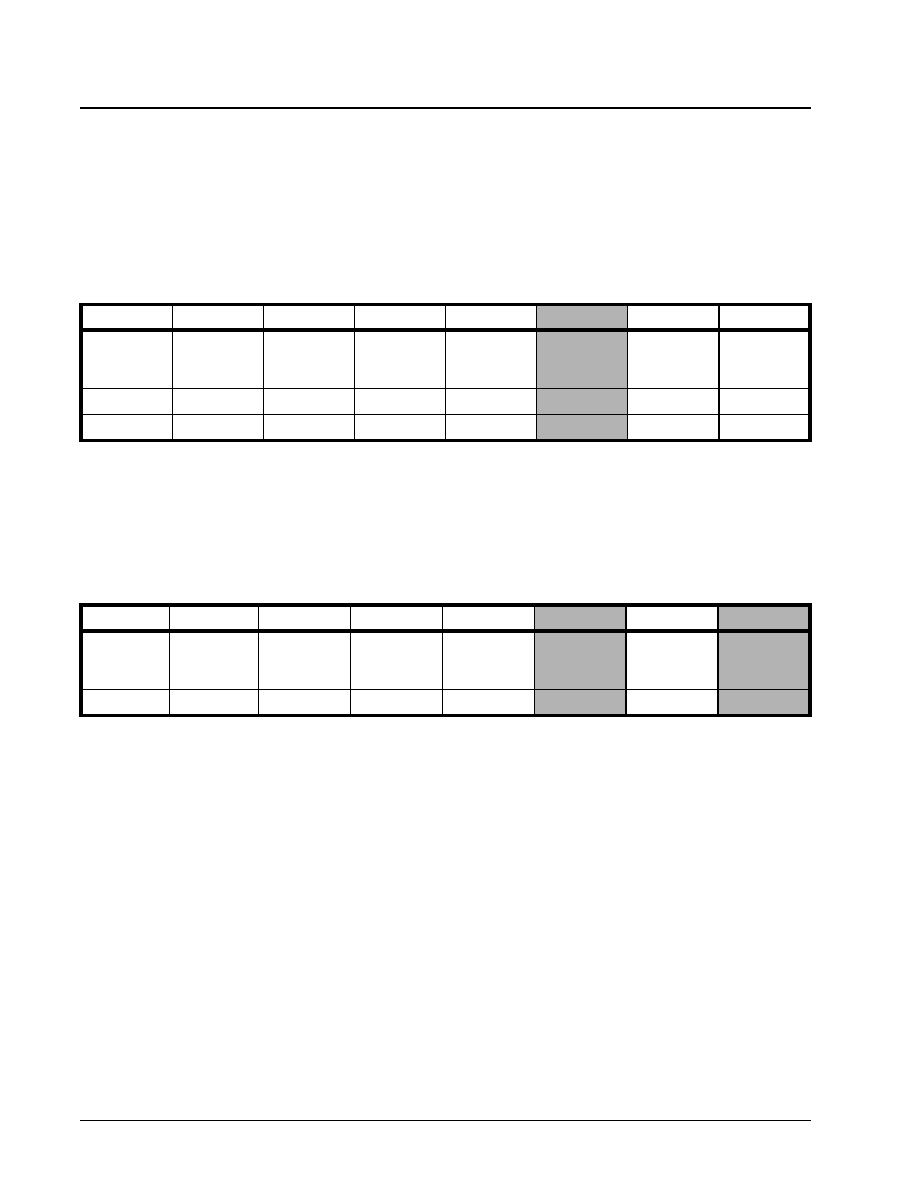

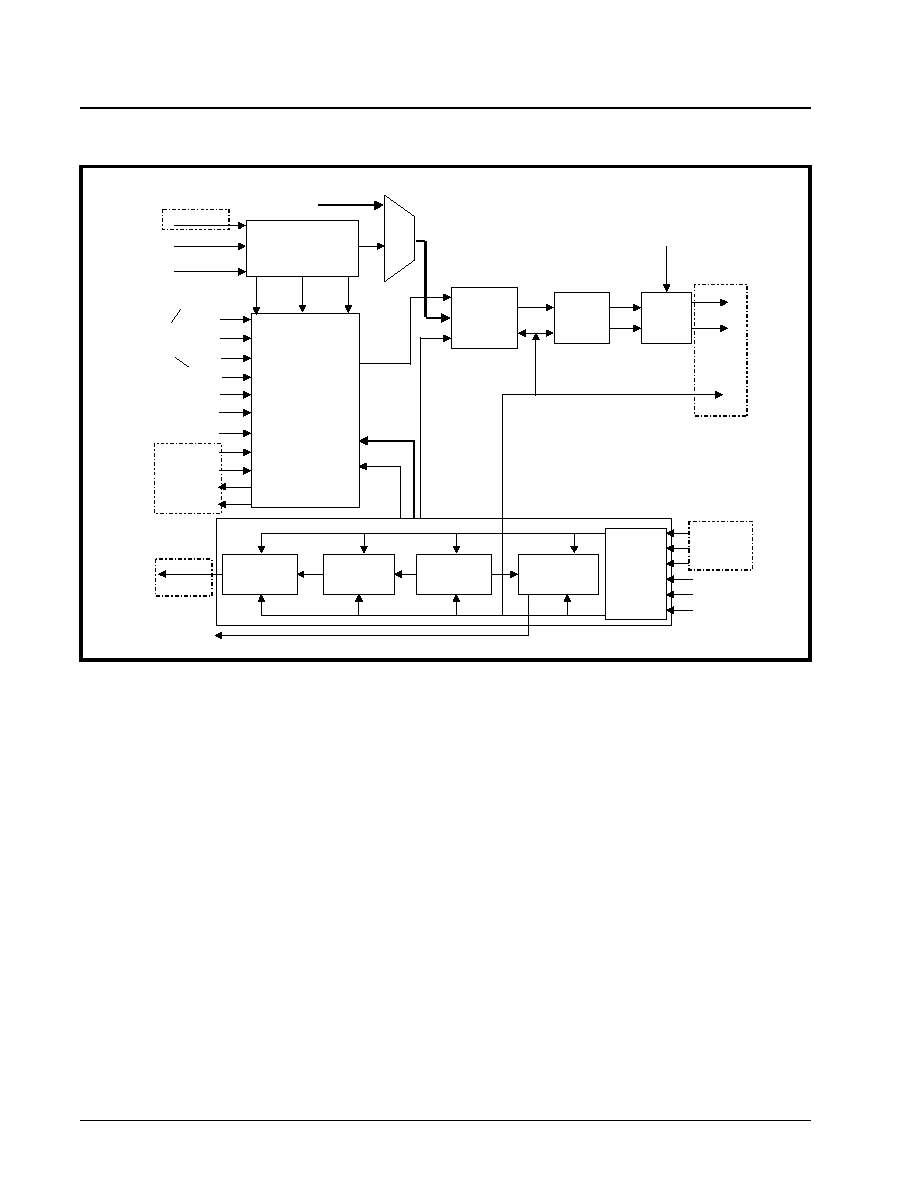

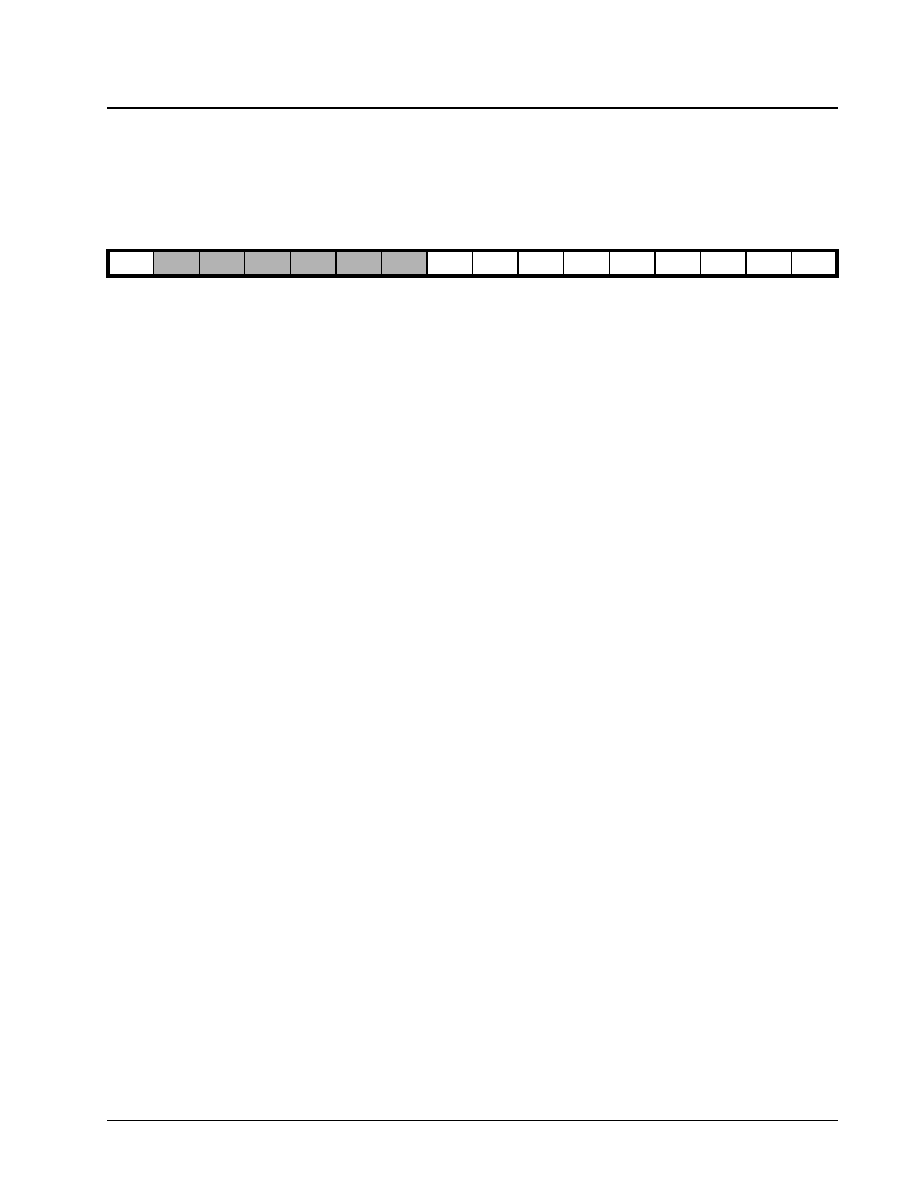

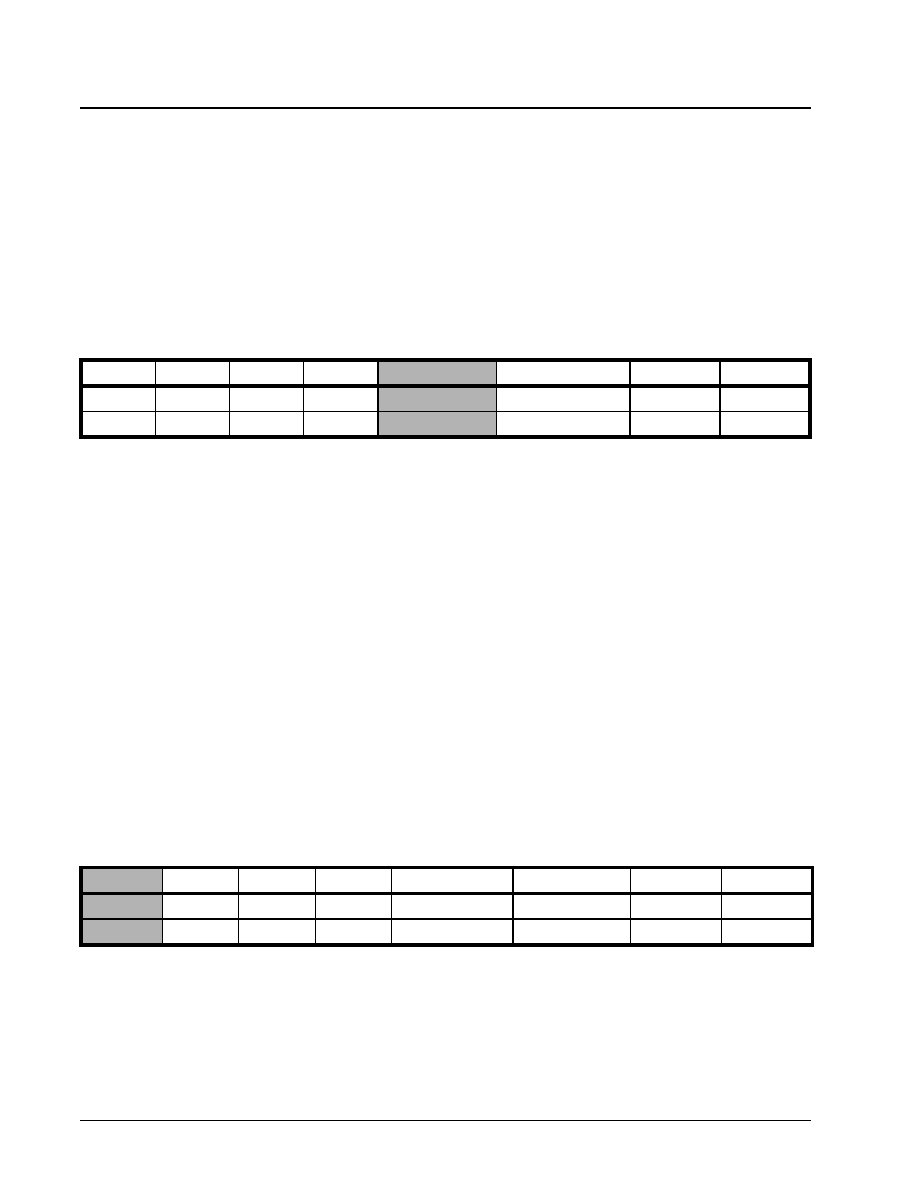

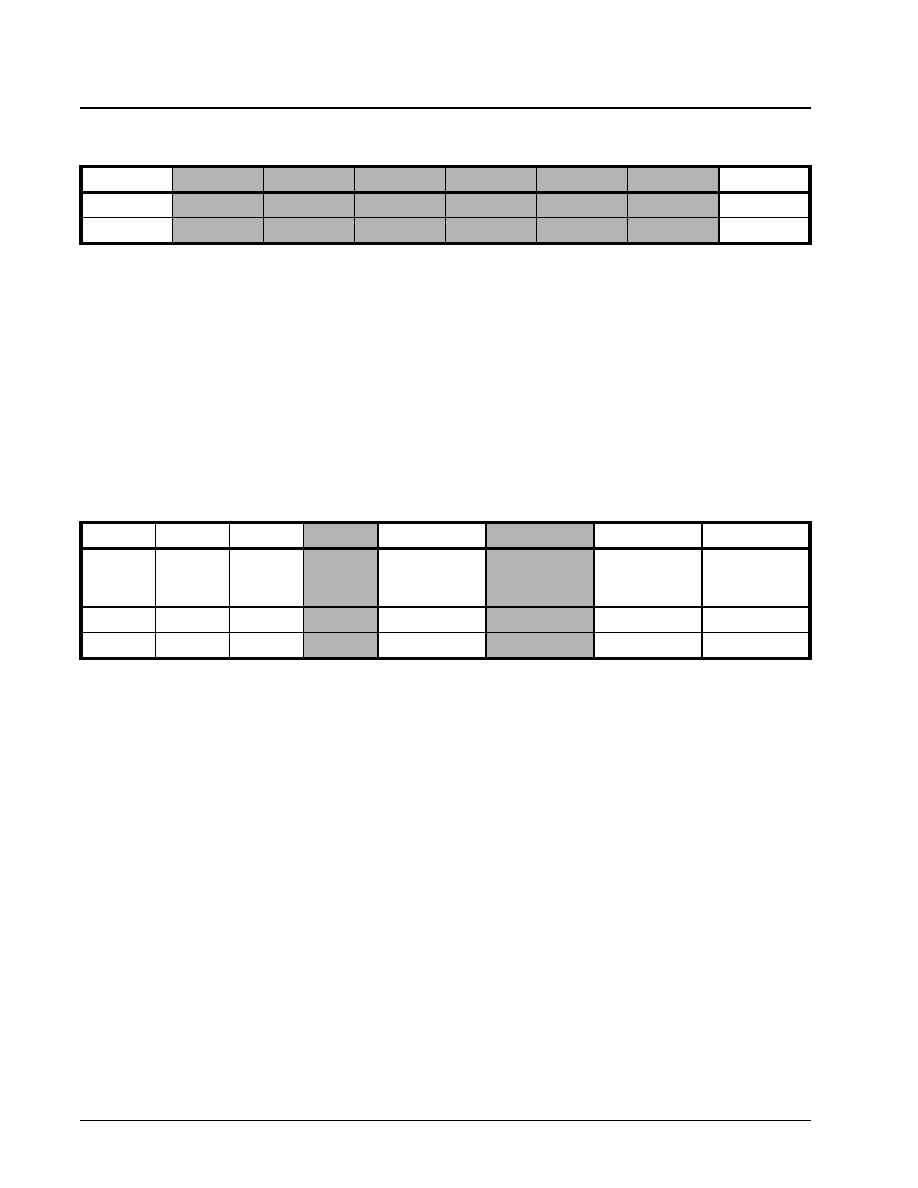

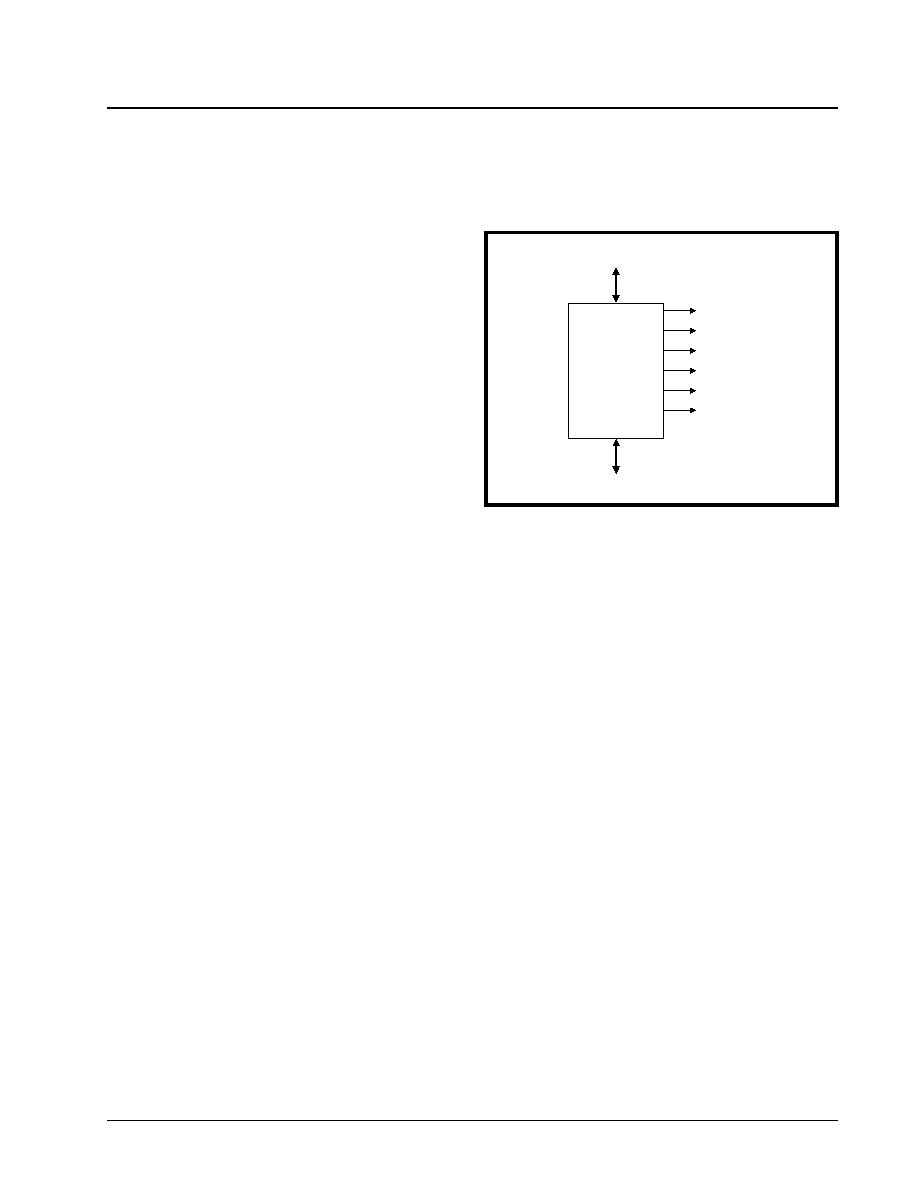

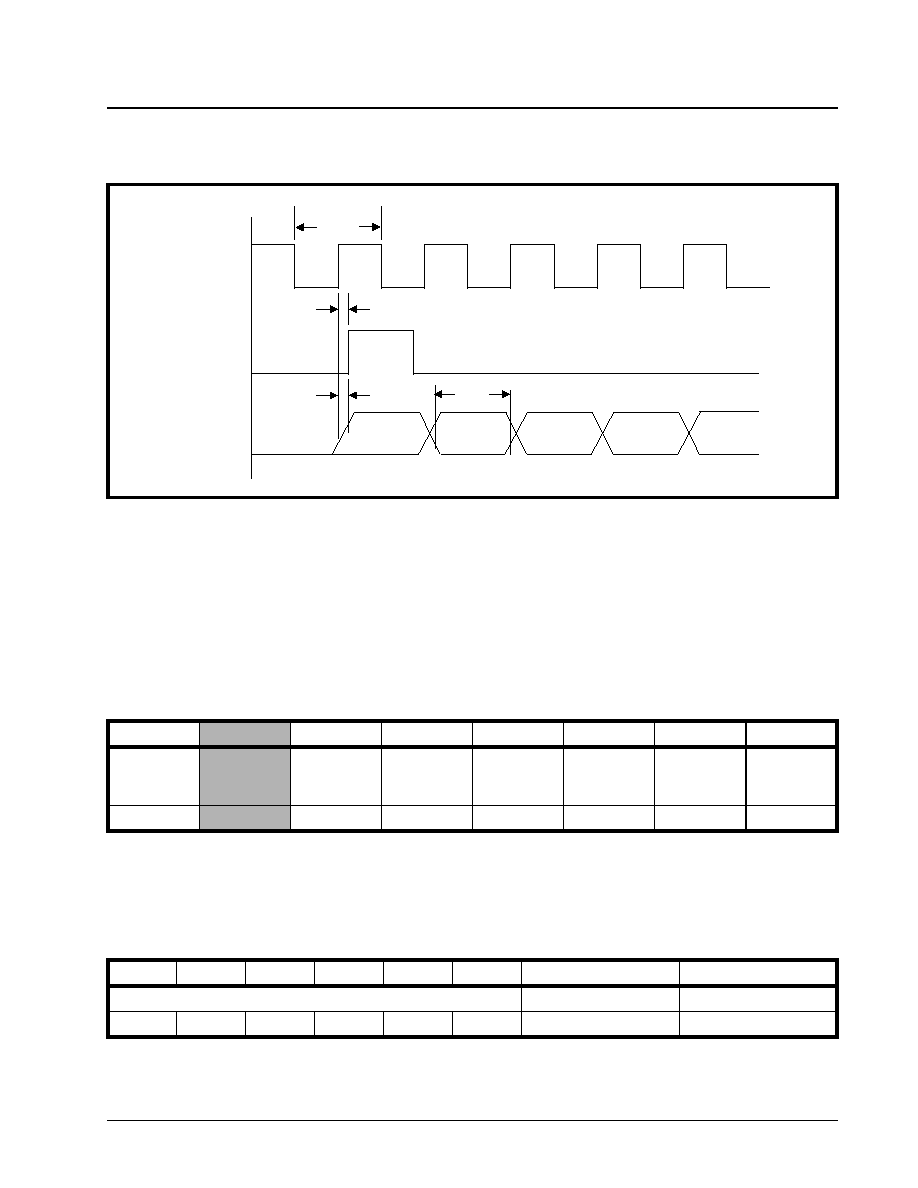

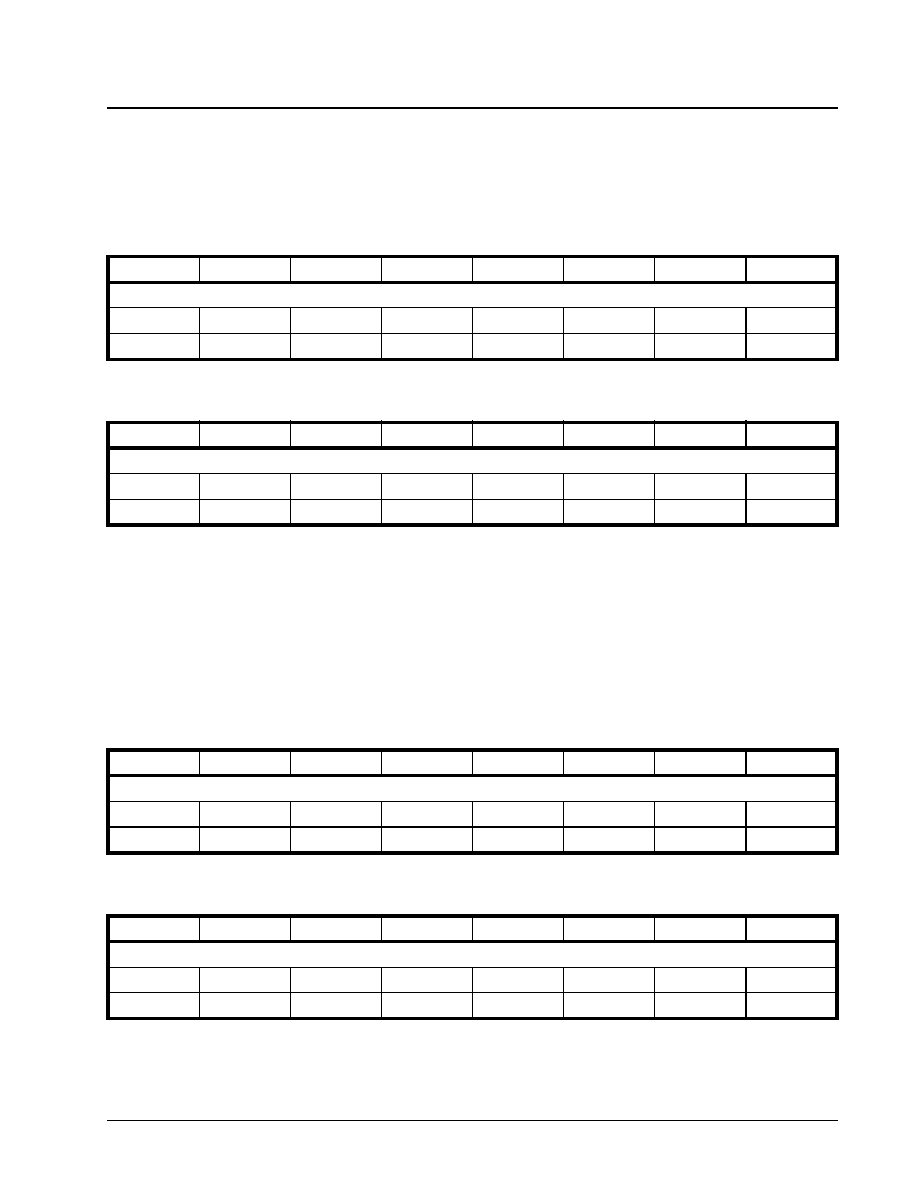

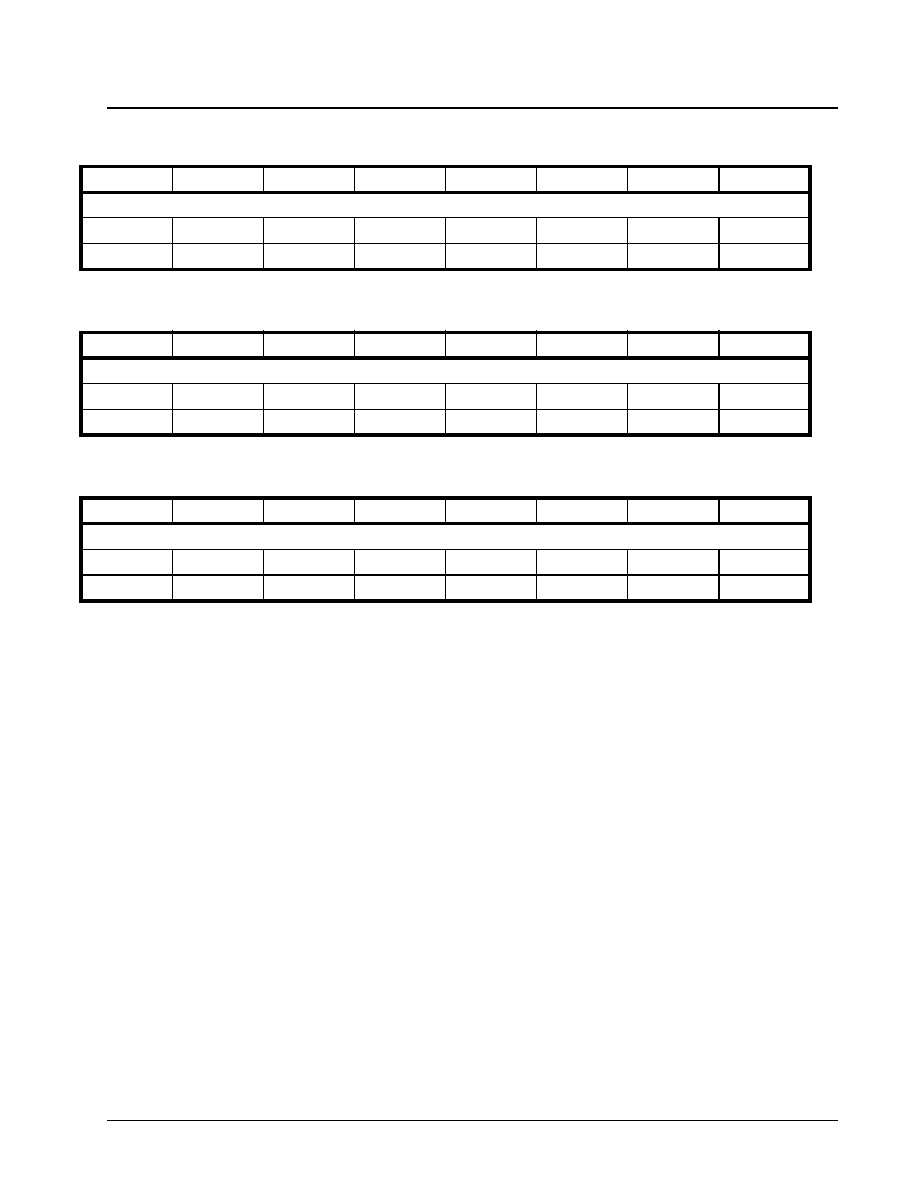

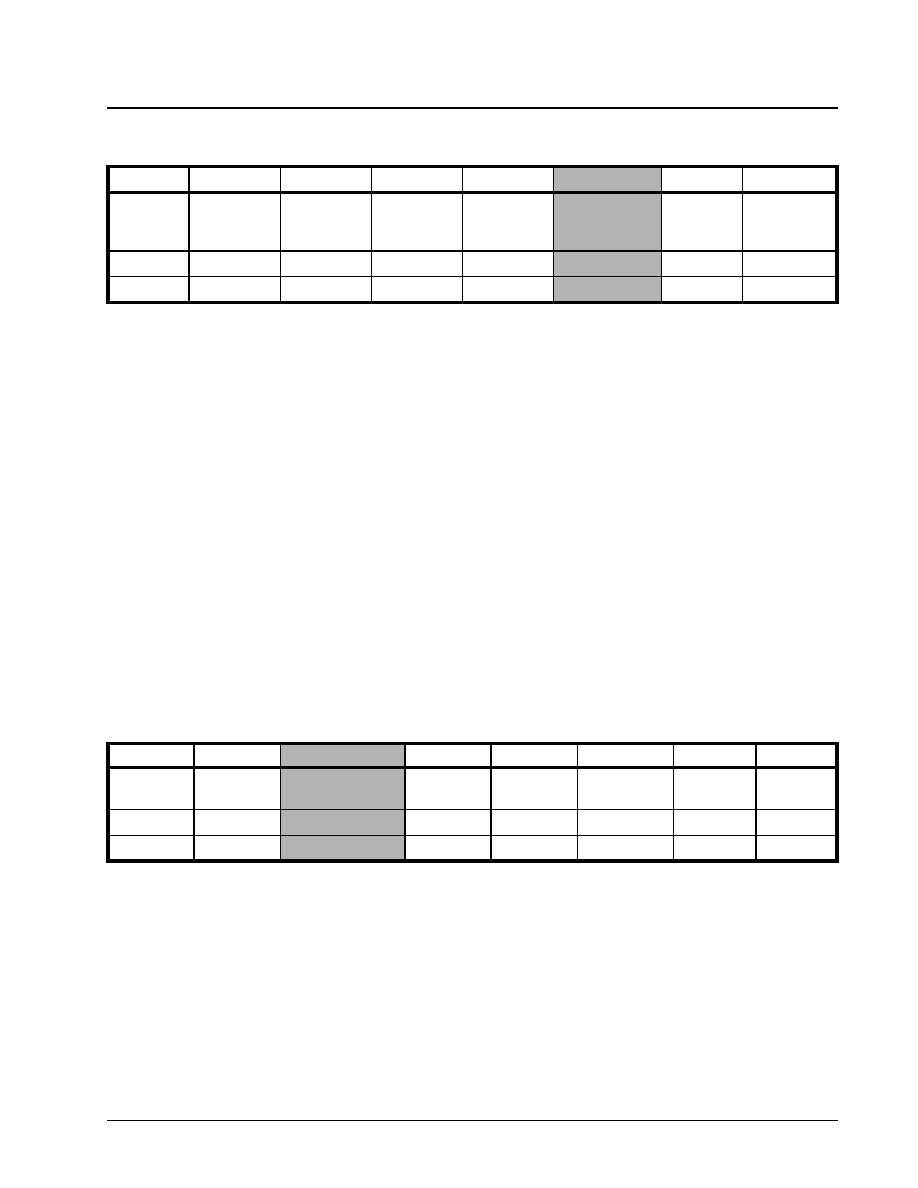

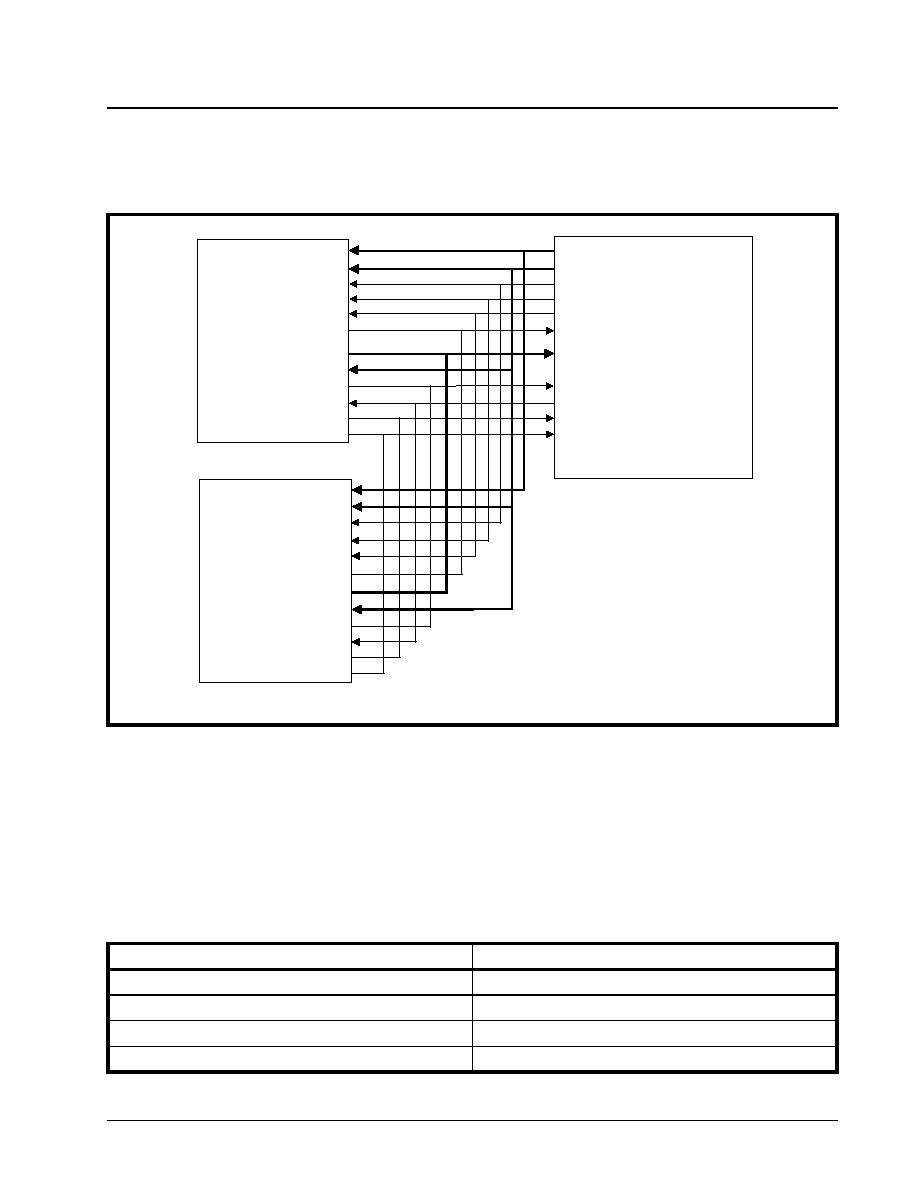

F

IGURE

2. P

IN

O

UT

OF

THE

XRT7245 DS3 UNI

FOR

ATM (160

PIN

QFP)

D 1 5

T A O S

D 1 4

D 1 3

D 1 2

D M O

M O T O / I n t e l

R L O L

D 1 1

T x F r a m e

D 1 0

R E Q B

D 9

D 8

V D D

D 7

D 6

D 5

D 4

W i d t h 1 6

D 3

E n c o D i s

D 2

T x L e v

D 1

R L O O P

D 0

L L O O P

IntB

R x L C D

G N D

C S B

R D _ D S

R x G F C

W R B _ R W

R x P O H

A 8

R x P O H C l k

A 7

R x P O H F r a m e

A6

A5

A4

A3

A2

A1

RxGFCMSB

A0

RxGFClk

RxClk

RxCellRxed

GND

RxData15

RxData7

RxData14

RxData6

RxData13

RxData5

VDD

RxData4

RxData12

RxData3

RxData11

RxData2

RxData10

VDD

RxData9

RxData1

RxData8

RxData0

GND

RxSoC

RxAddr4

RxPrty

RxAddr3

RxClav

RxAddr2

VDD

RxAddr0

RxAddr1

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

X R T 7 2 4 5

Rdy_Dtck

GND

TxGFC

ALE_AS

TxGFCClk

ResetB

TxGFCMSB

GND

GND

TxClk

TxAddr2

TxAddr1

TxAddr3

TxAddr0

TxAddr4

VDD

TxData15

TxData7

TxData14

TxData6

TxData13

TxData5

TxData12

TxData4

VDD

TxData3

TxData11

TxData2

TxData10

TxData1

TxData9

TxData0

TxData8

GND

TxClav

TxPrty

TxSoC

TxEnB

TxOHFrame

TxOHClk

T C e l l T x e d

T x O H

T x P O H C l k

T x O H I n s

T x P O H I n s

T x A I S E n

T x P O H

V D D

T x L i n e C l k

T x N E G

T x P O H F r a m e

T x P O S

T x P F r a m e

T x F r a m e R e f

R x P O O F

G N D

R x P L O F

T x L n C l k

StuffCtl

R x R e d

R x P R e d

R x L i n e C l k

R x N E G

R x P O S

R x F r a m e

R x O H F r a m e

R x P F r a m e

R x O H C l k

R x A I S

G N D

R x O O F

R x O H

R x L O S

EightKRef

R L O S

V D D

N C

G N D

G N D

R x E n B

1 6 0 L e a d P Q F P

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

2 9

3 0

3 1

3 2

3 3

3 4

3 5

3 6

3 7

3 8

3 9

4 0

1 2 0

1 1 9

1 1 8

1 1 7

1 1 6

1 1 5

1 1 4

1 1 3

1 1 2

1 1 1

1 1 0

1 0 9

1 0 8

1 0 7

1 0 6

1 0 5

1 0 4

1 0 3

1 0 2

1 0 1

1 0 0

9 9

9 8

9 7

9 6

9 5

9 4

9 3

9 2

9 1

9 0

8 9

8 8

8 7

8 6

8 5

8 4

8 3

8 2

8 1

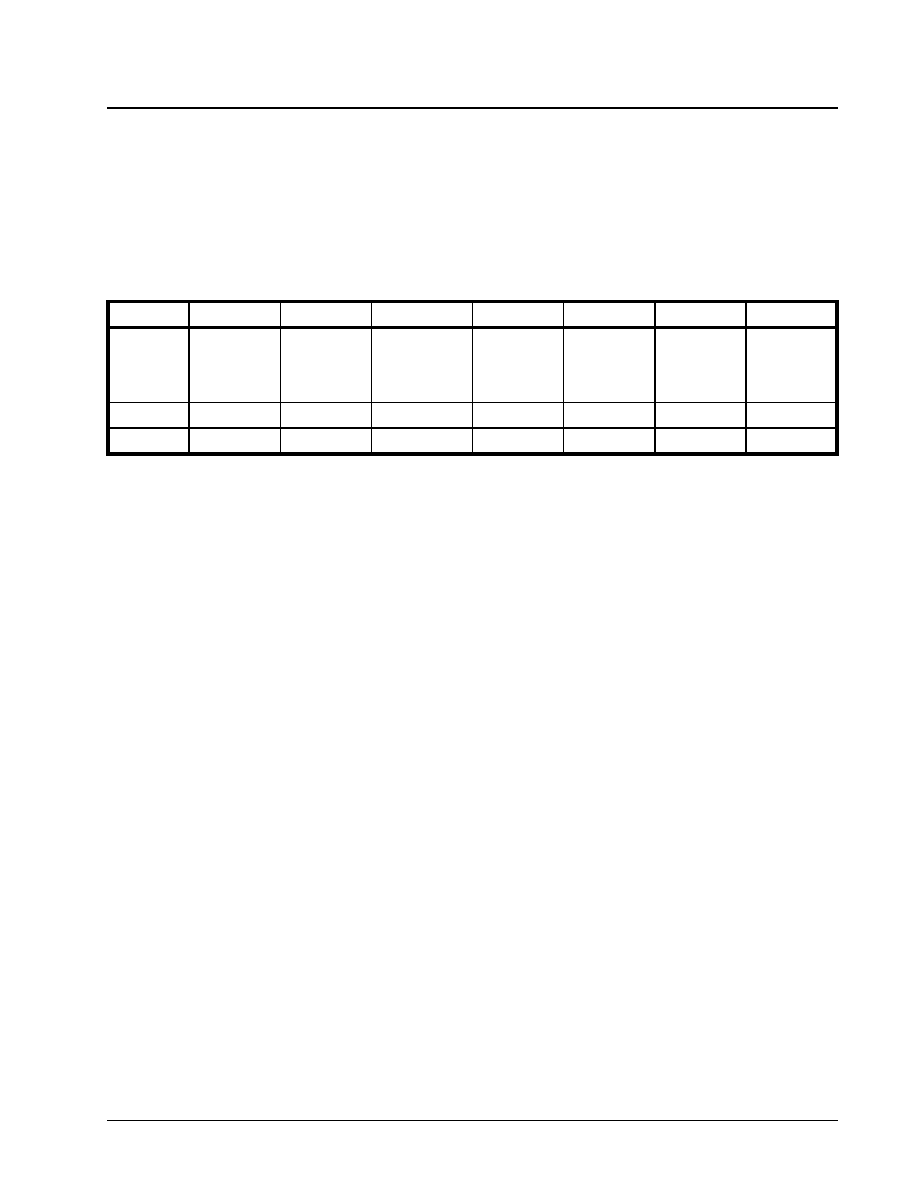

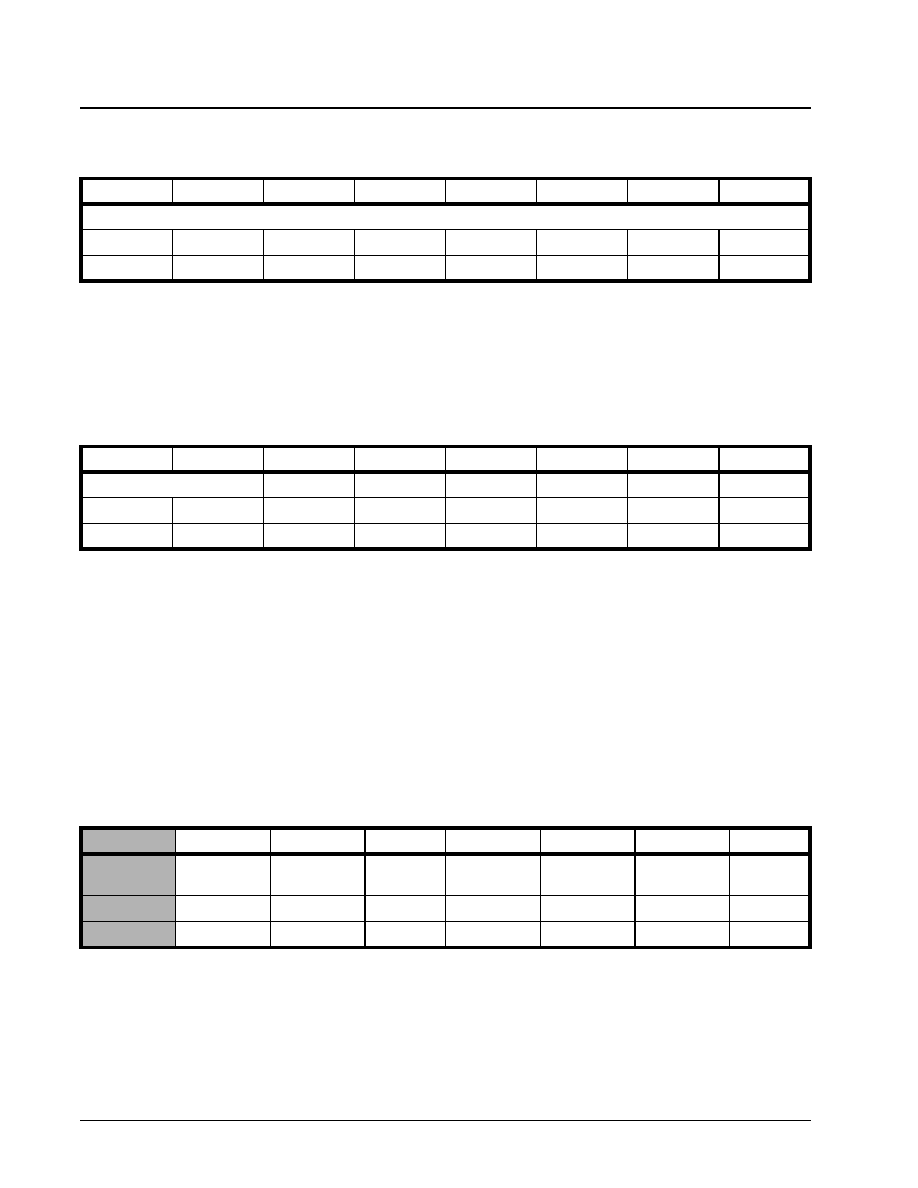

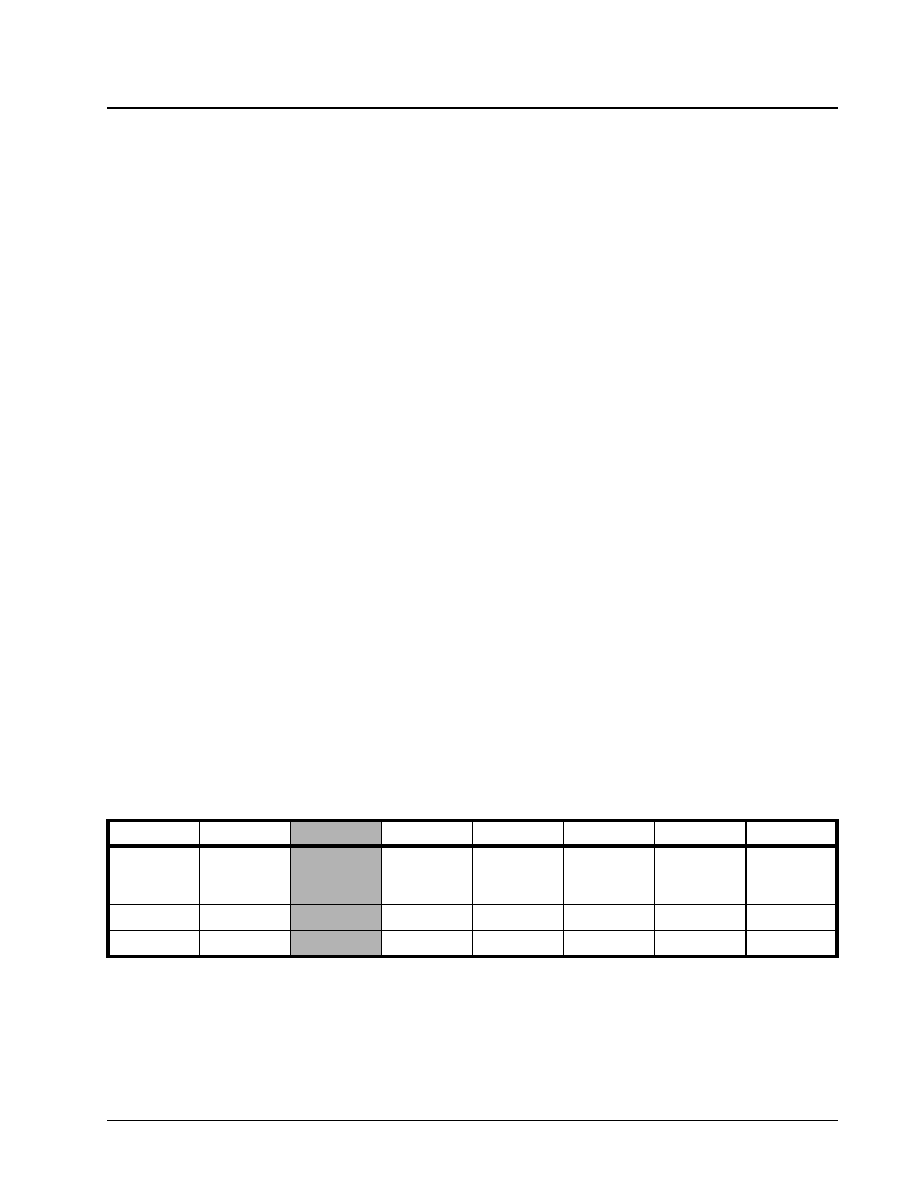

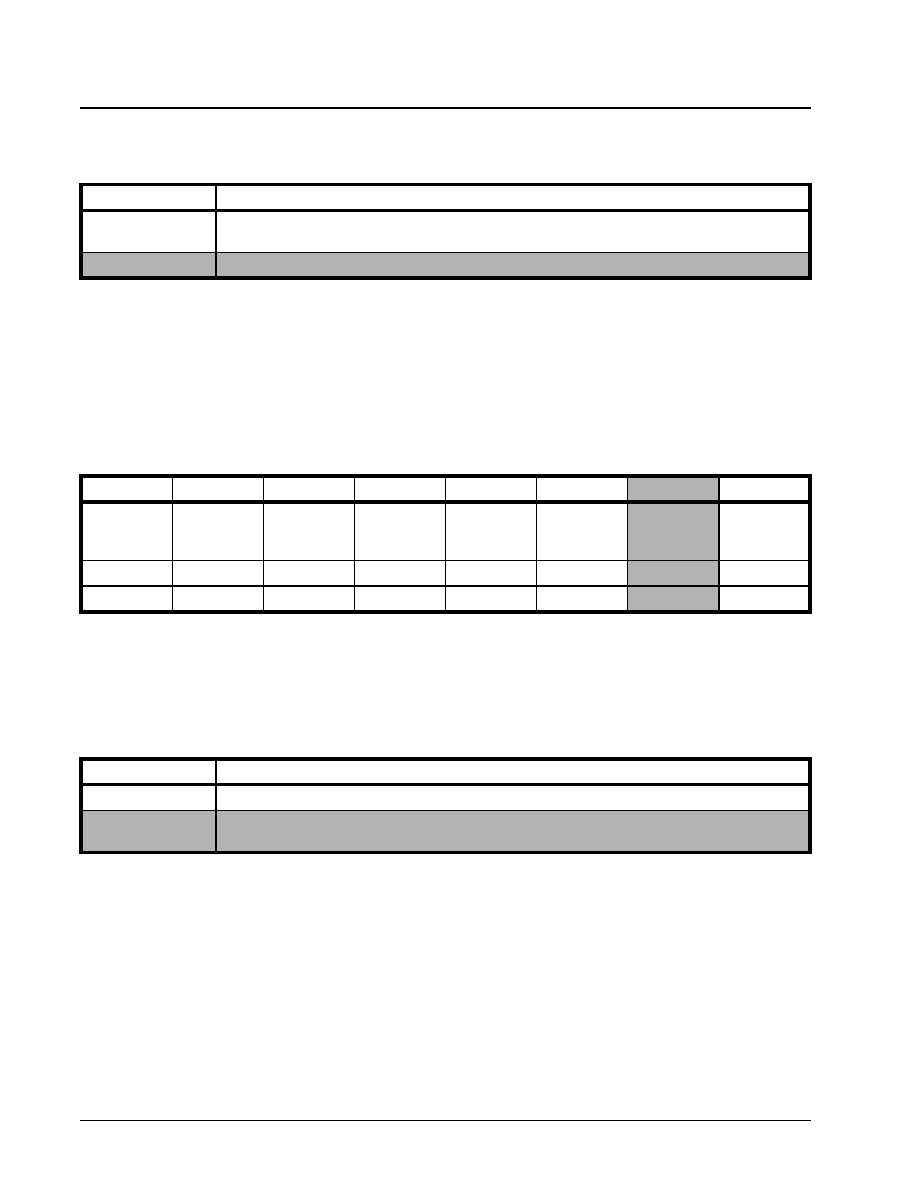

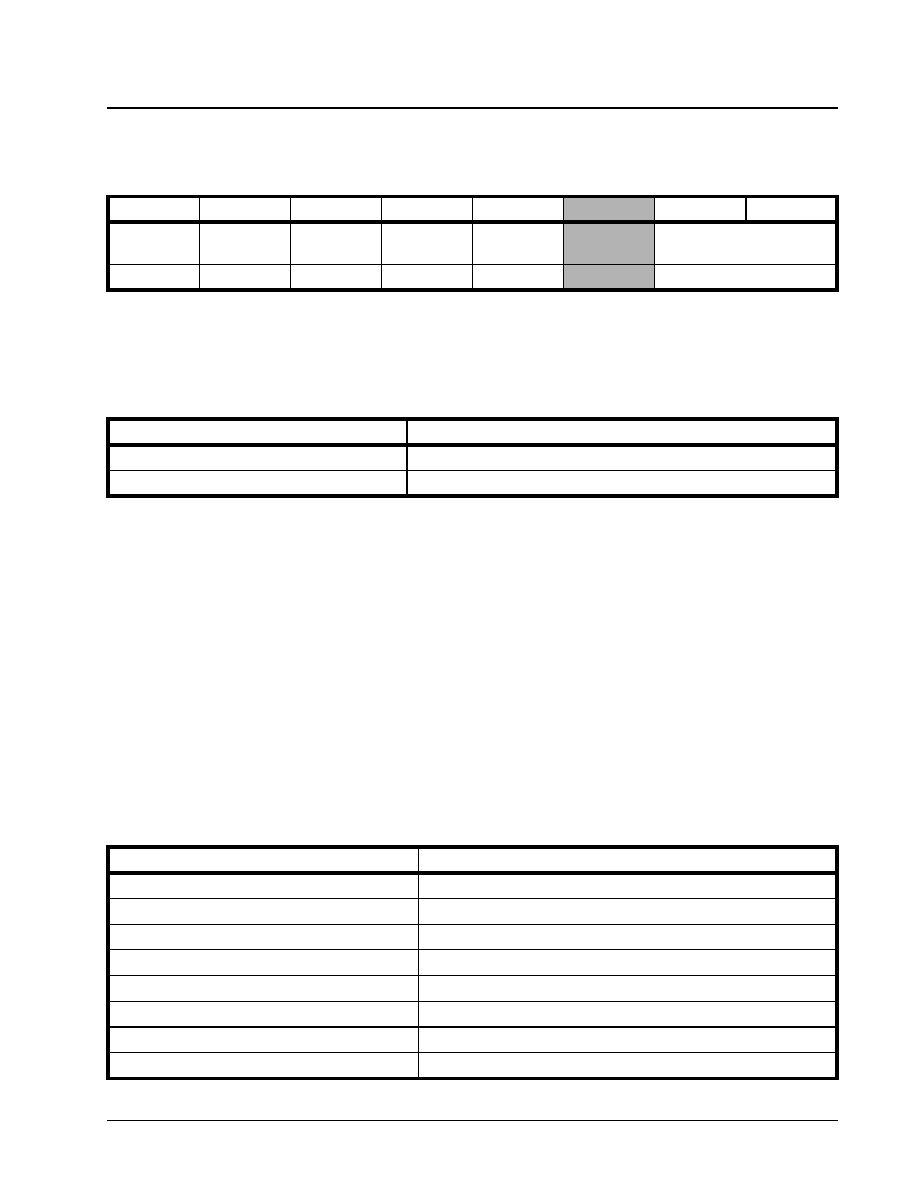

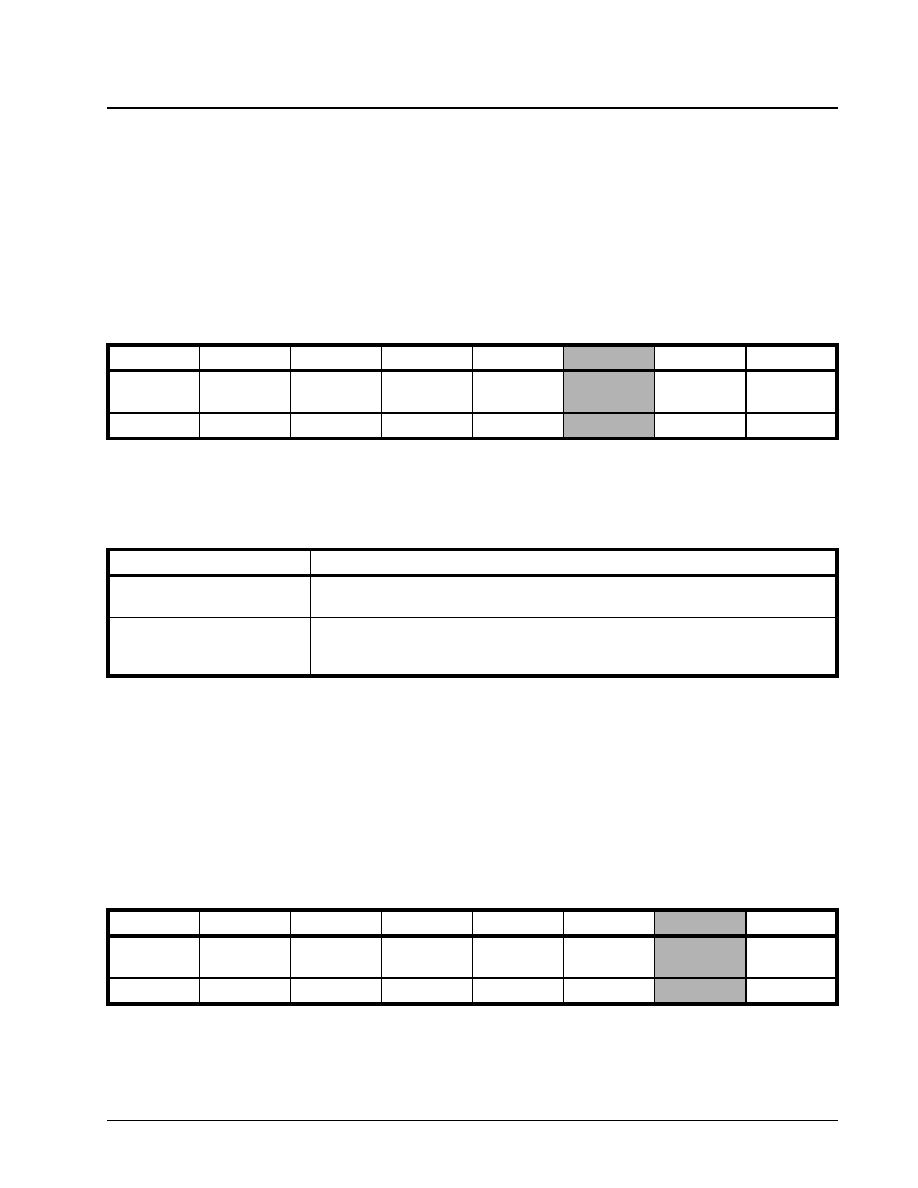

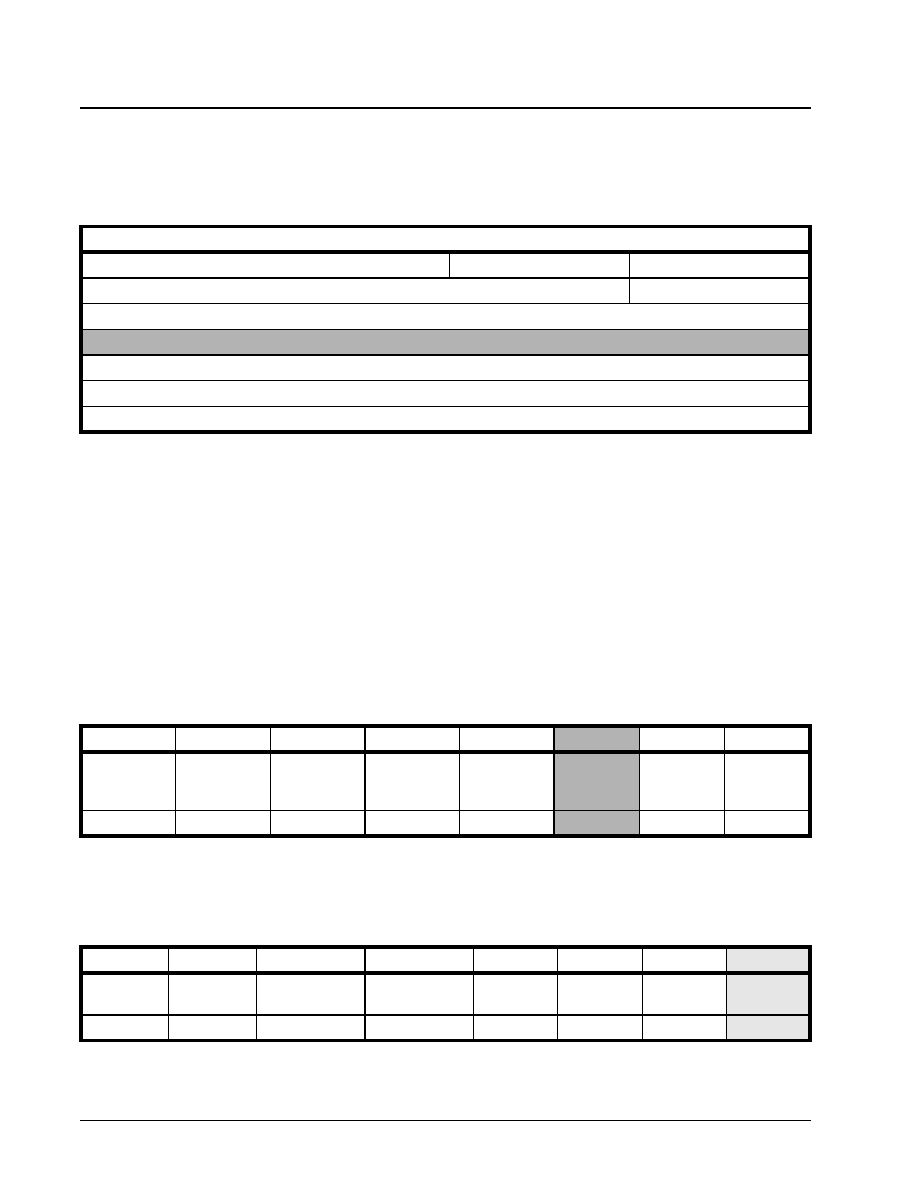

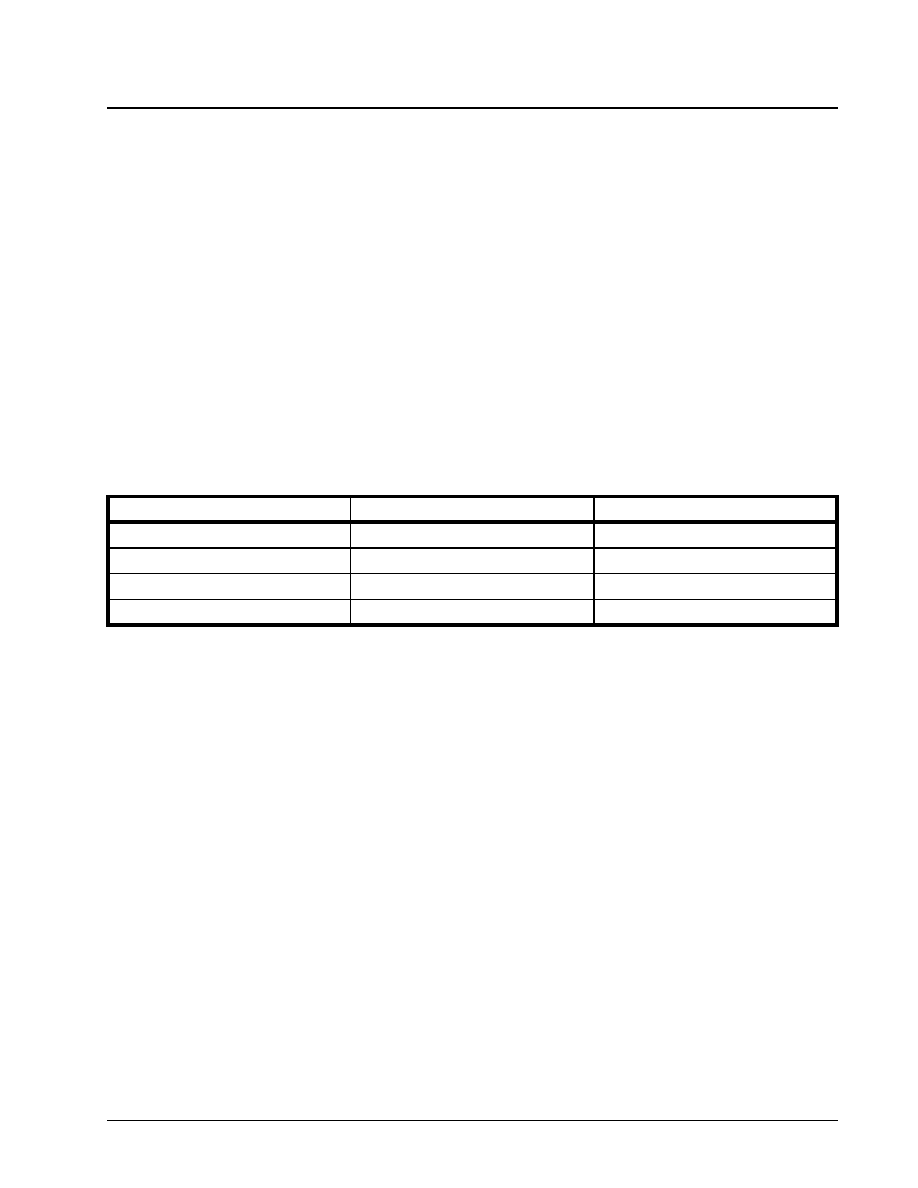

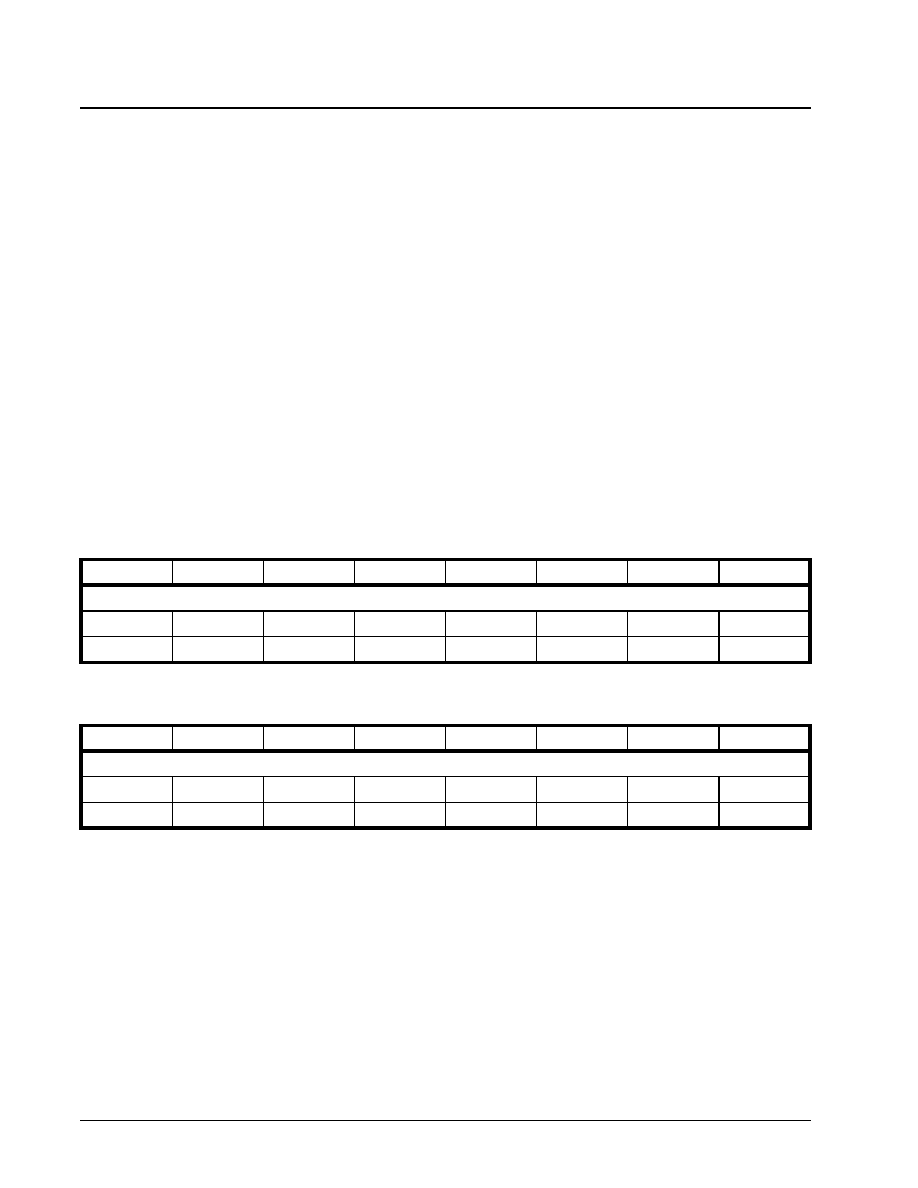

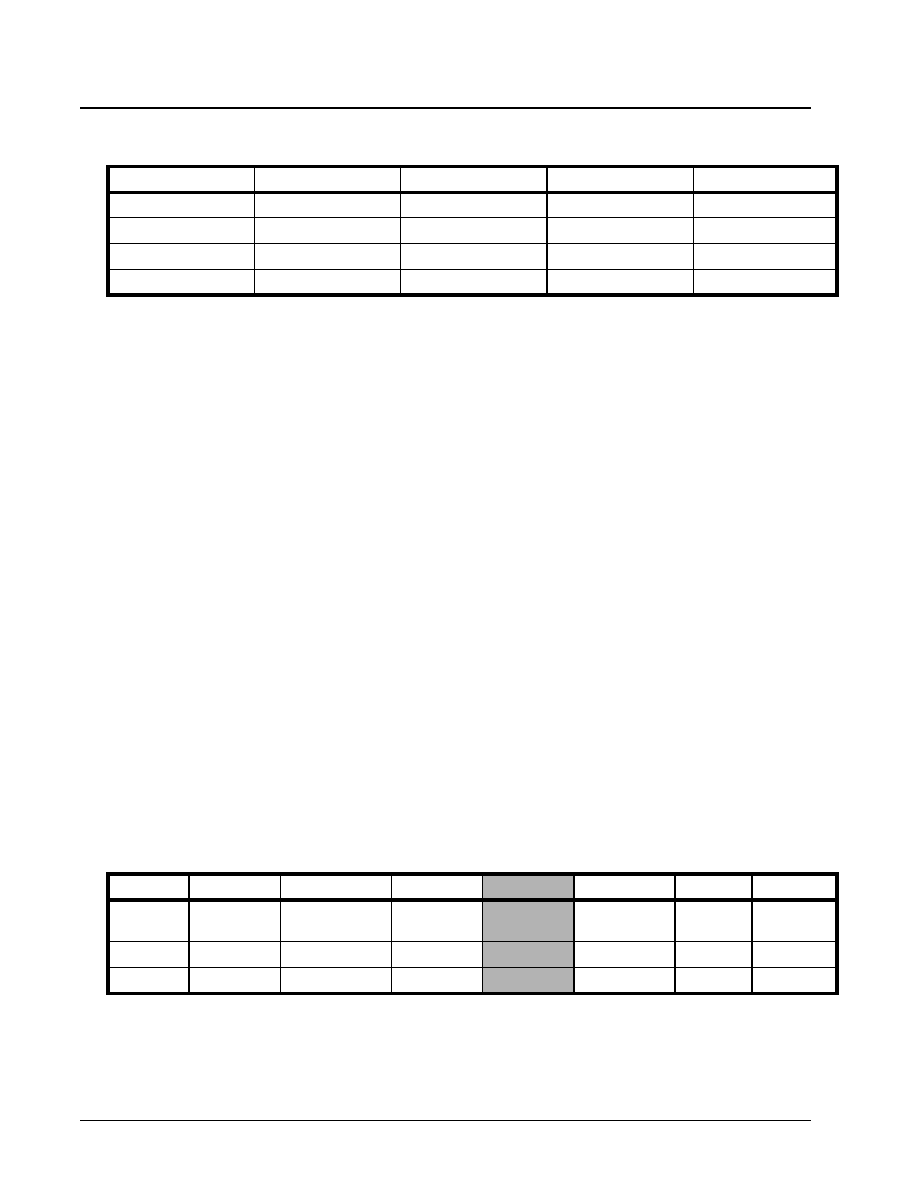

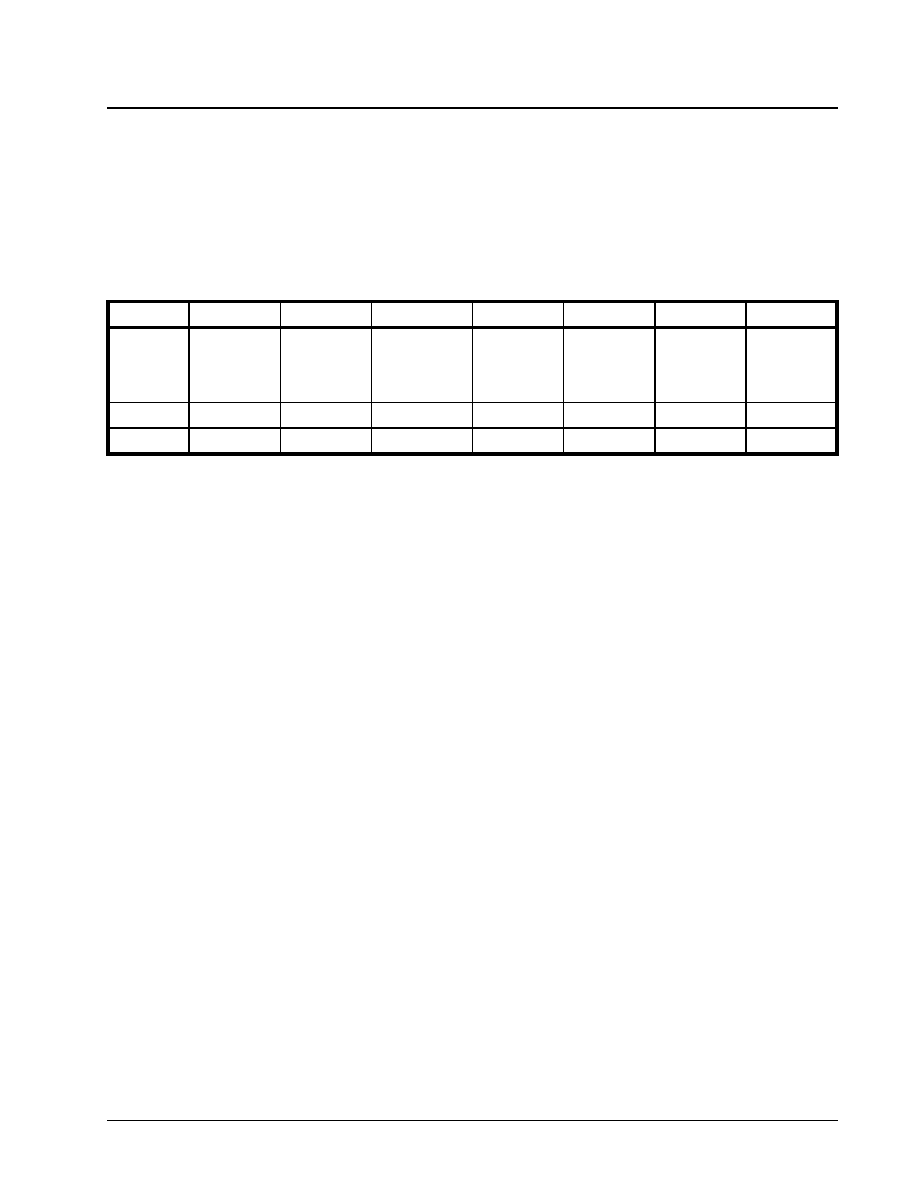

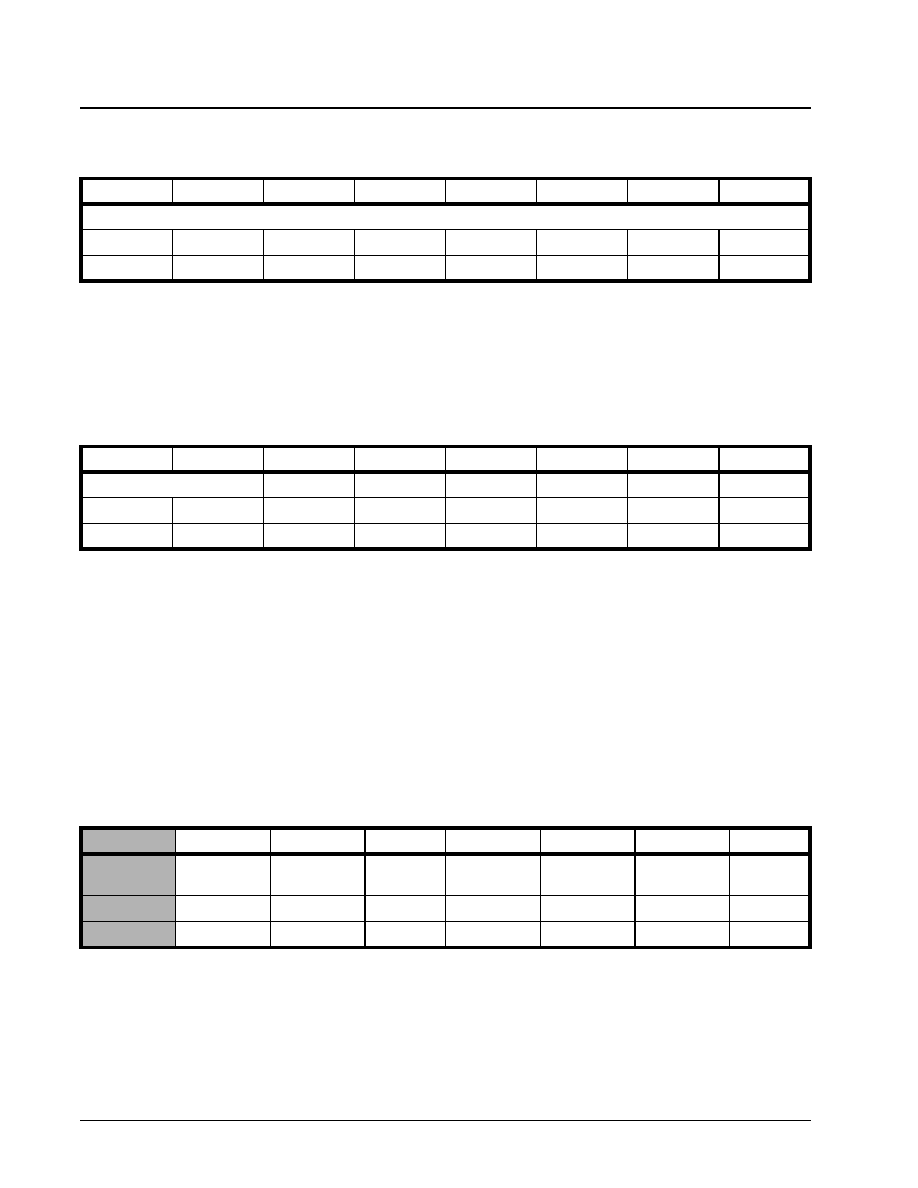

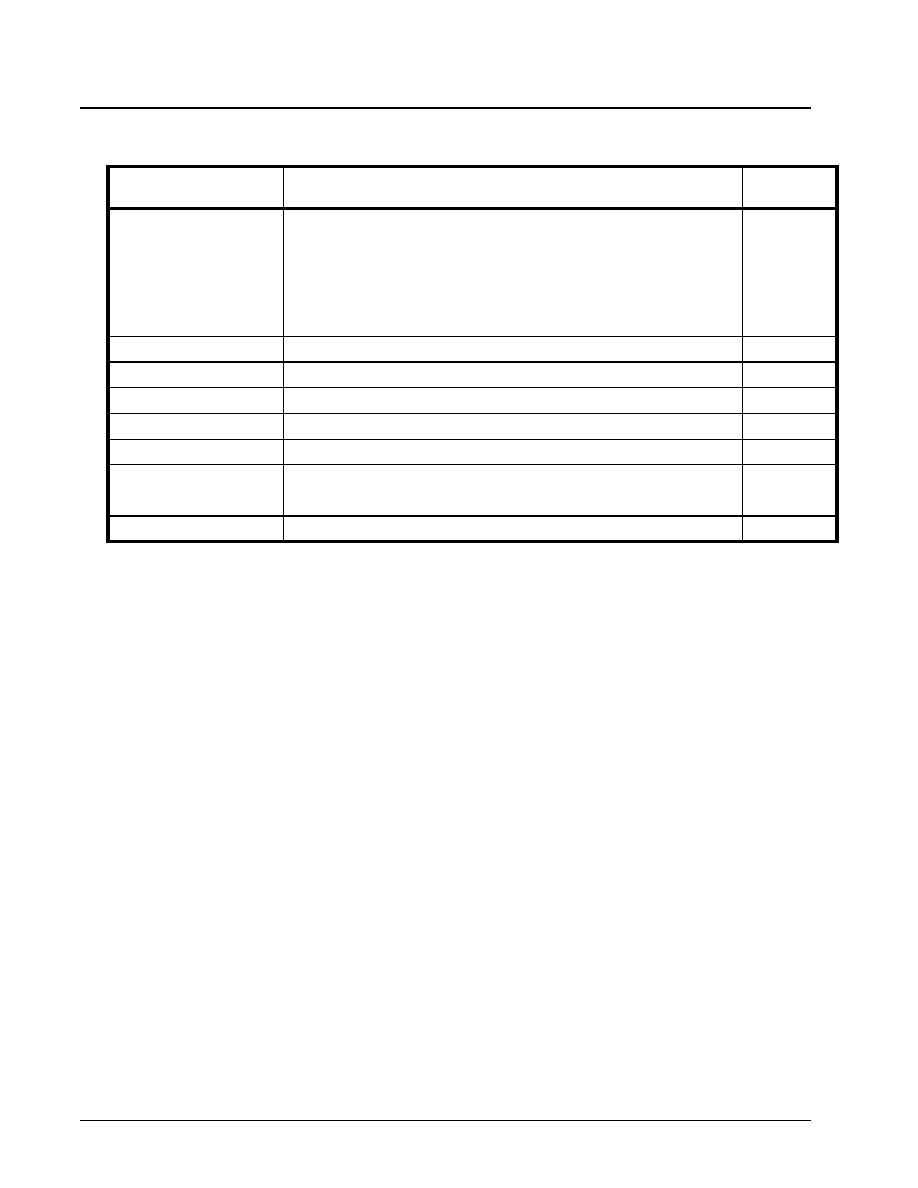

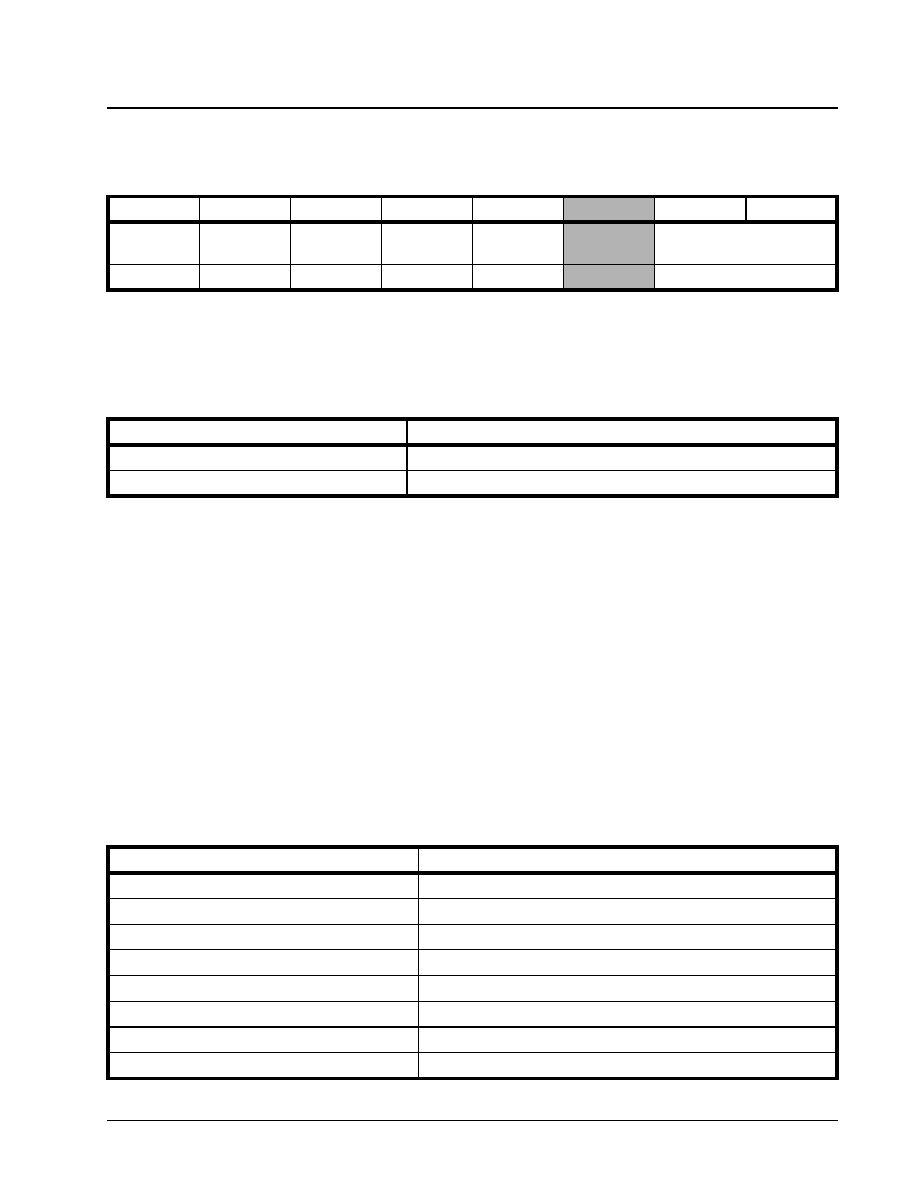

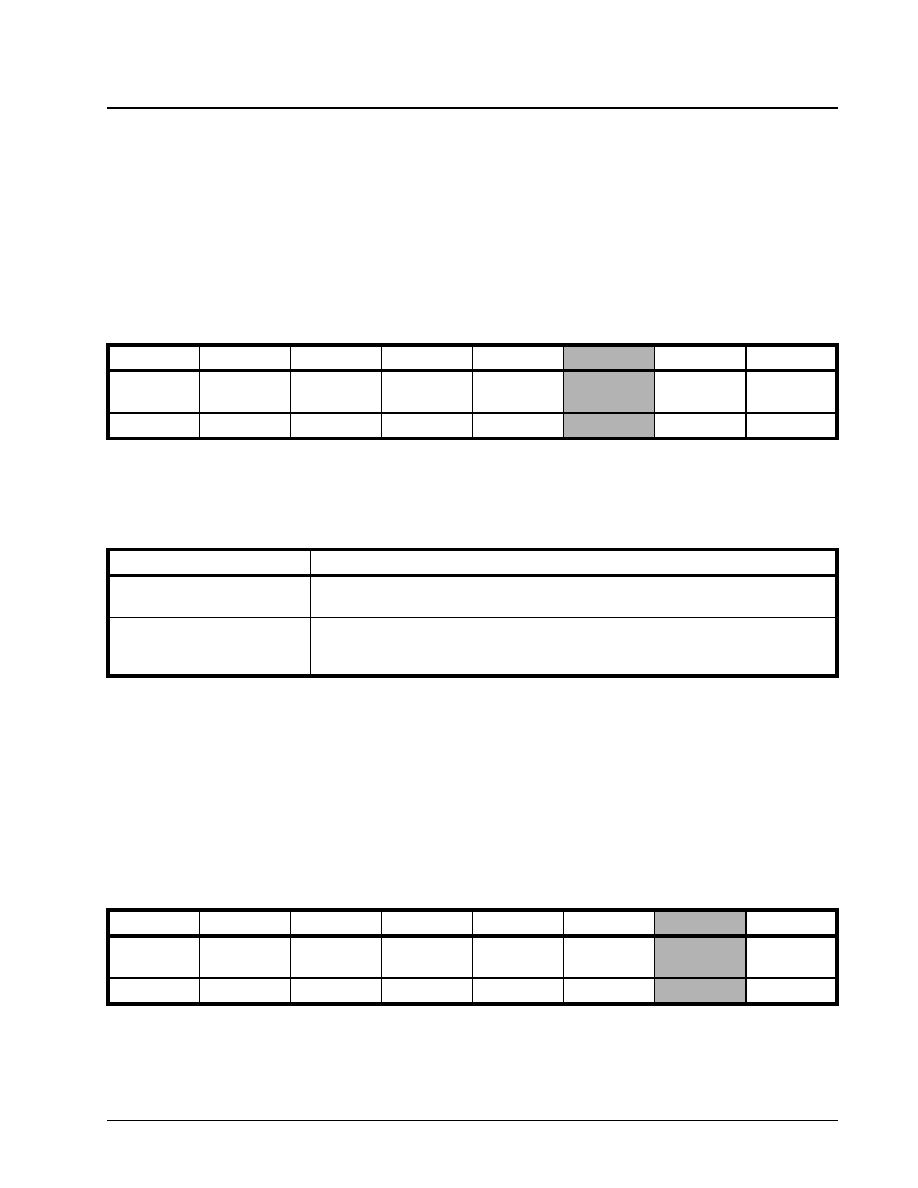

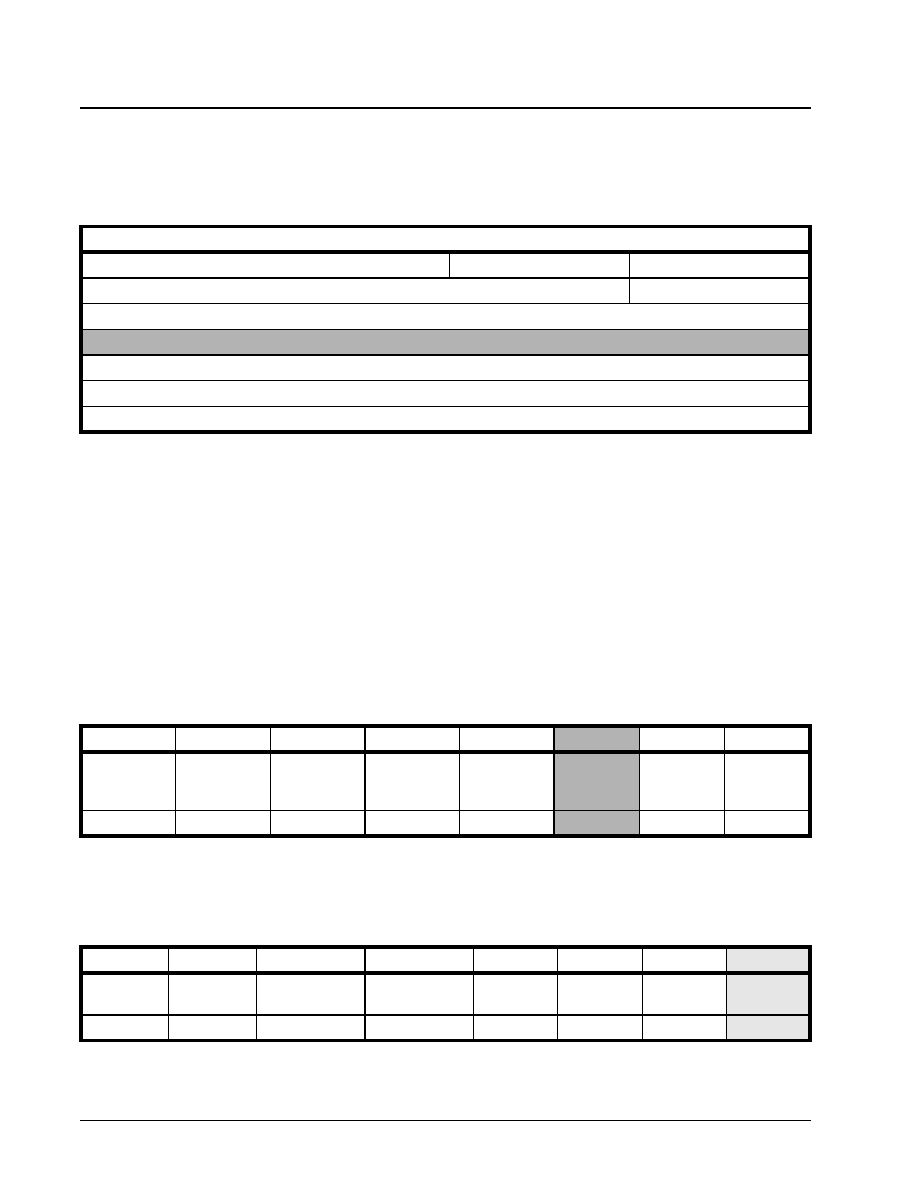

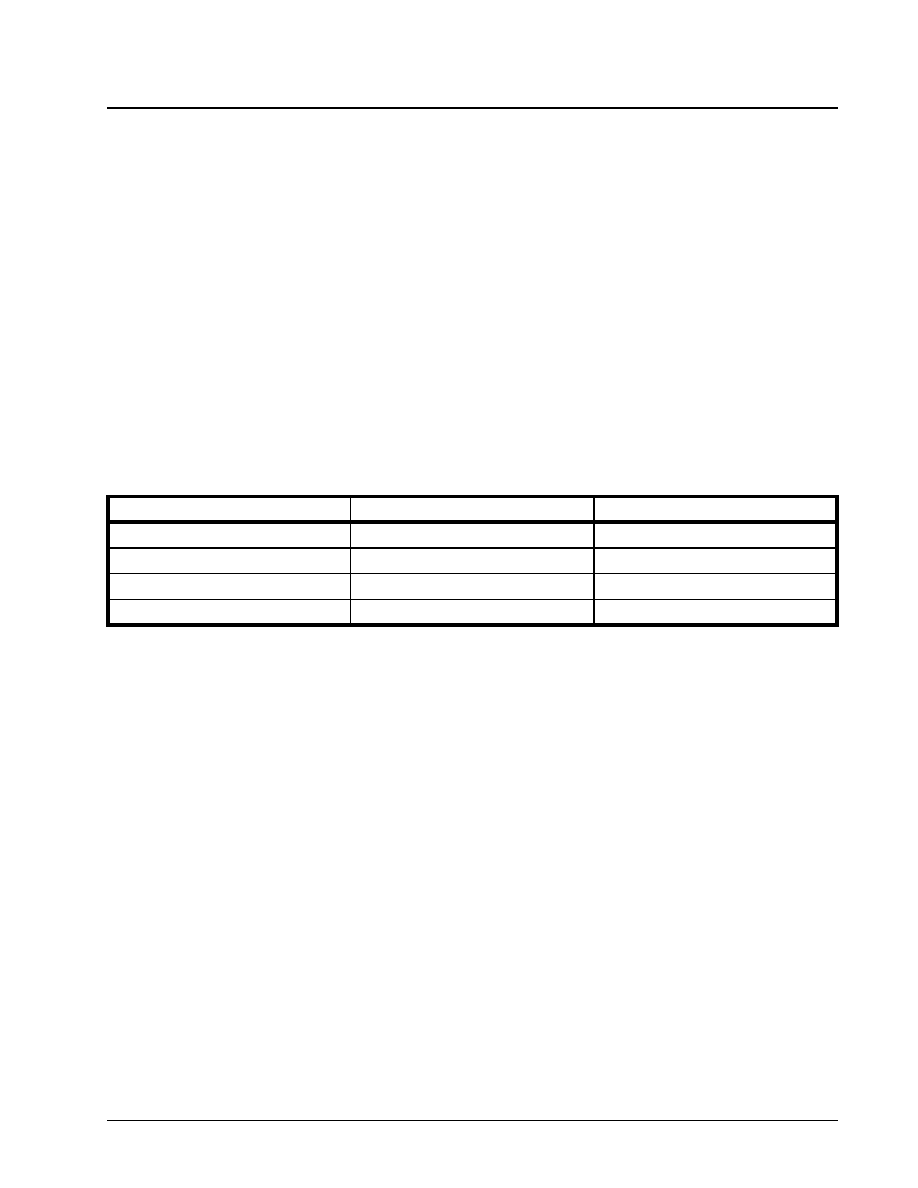

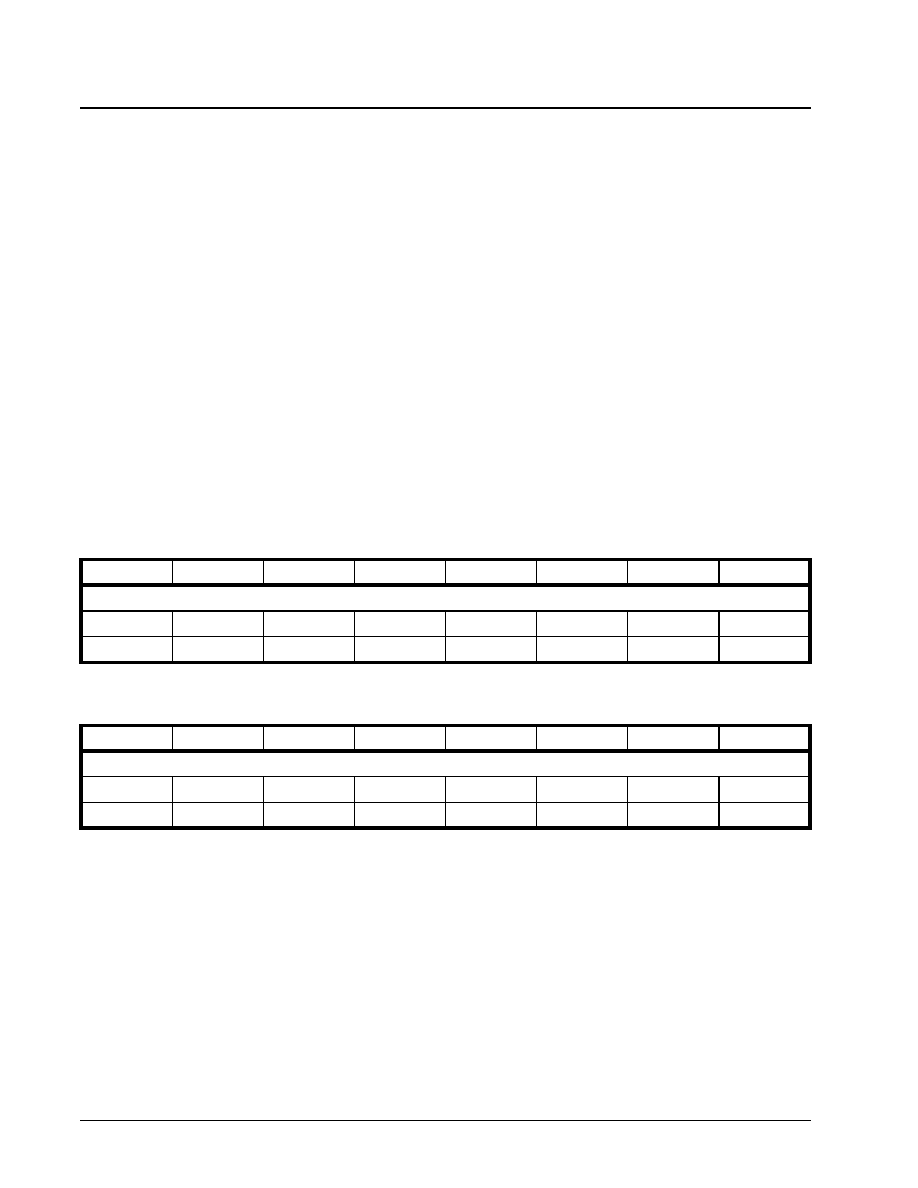

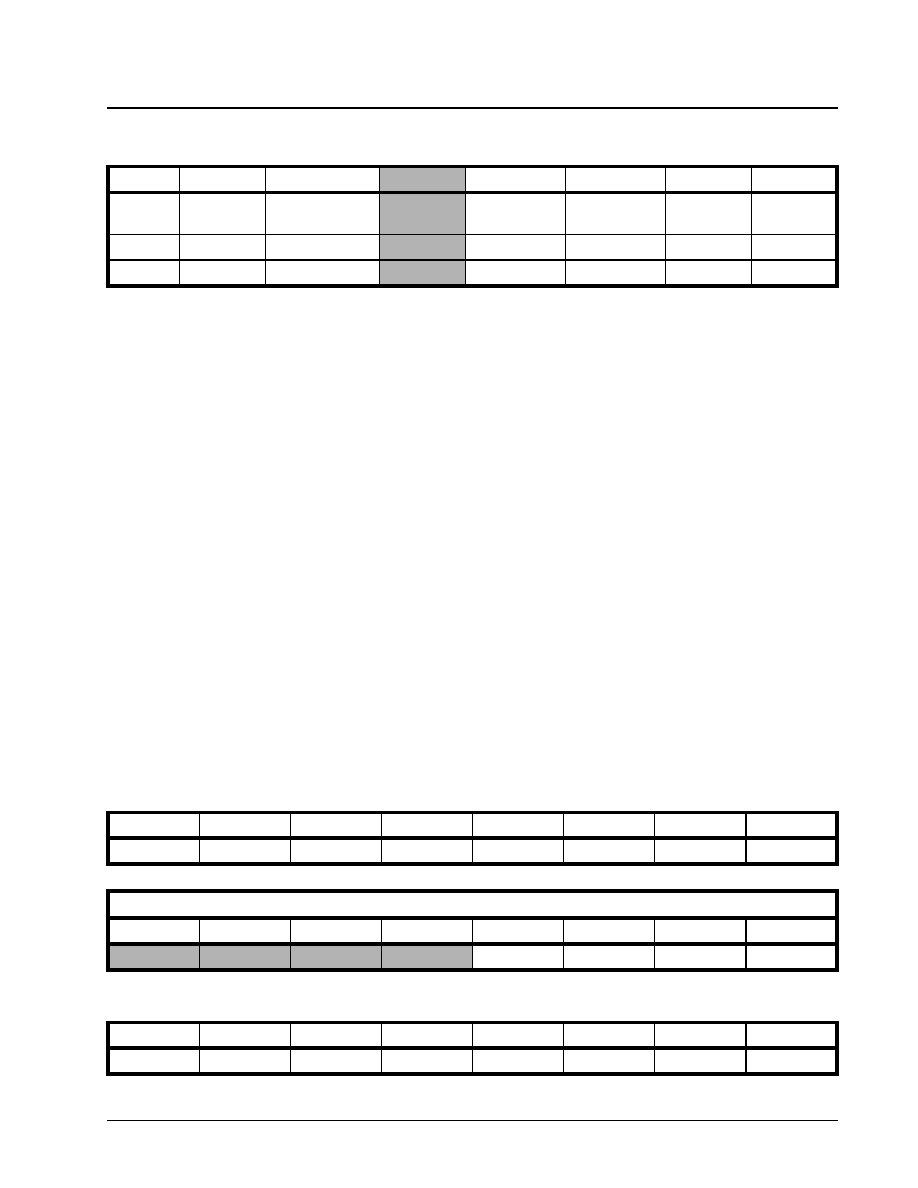

P

ART

N

UMBER

P

ACKAGE

O

PERATING

T

EMPERATURE

R

ANGE

XRT7245SIQ160

28 x28 mm Plastic QFP

-40∞C to +85∞C

·Á

·Á

·Á

·Á

DS3 UNI FOR ATM

XRT7245

PRELIMINARY

REV. 1.03

3

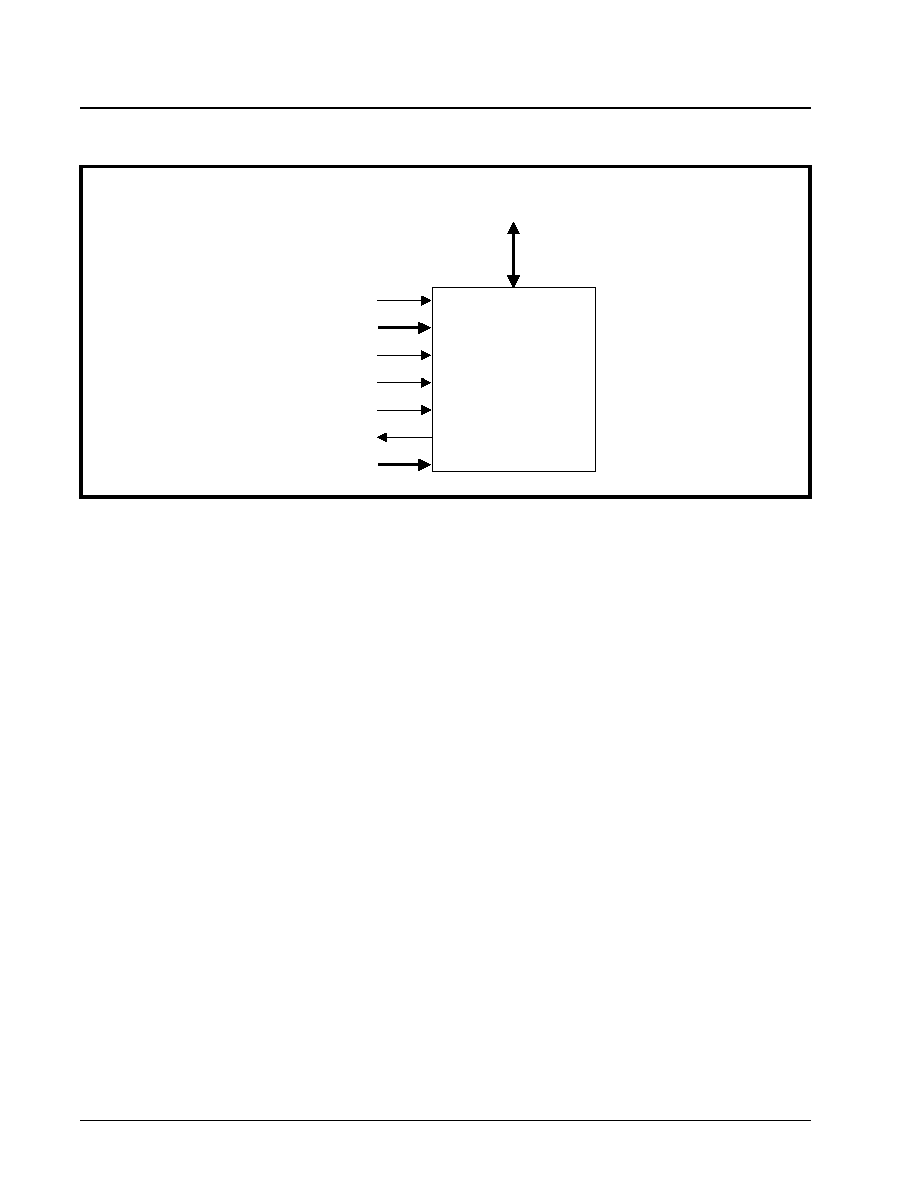

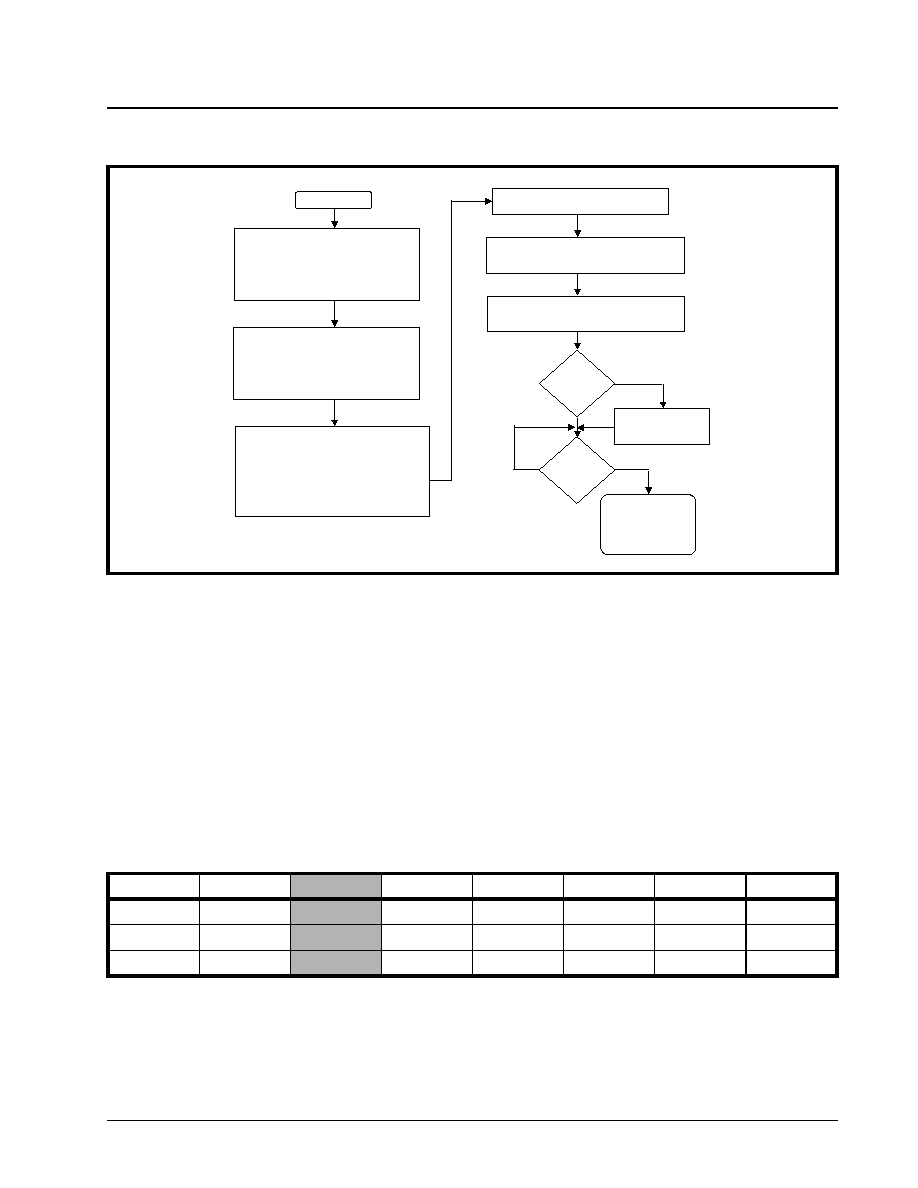

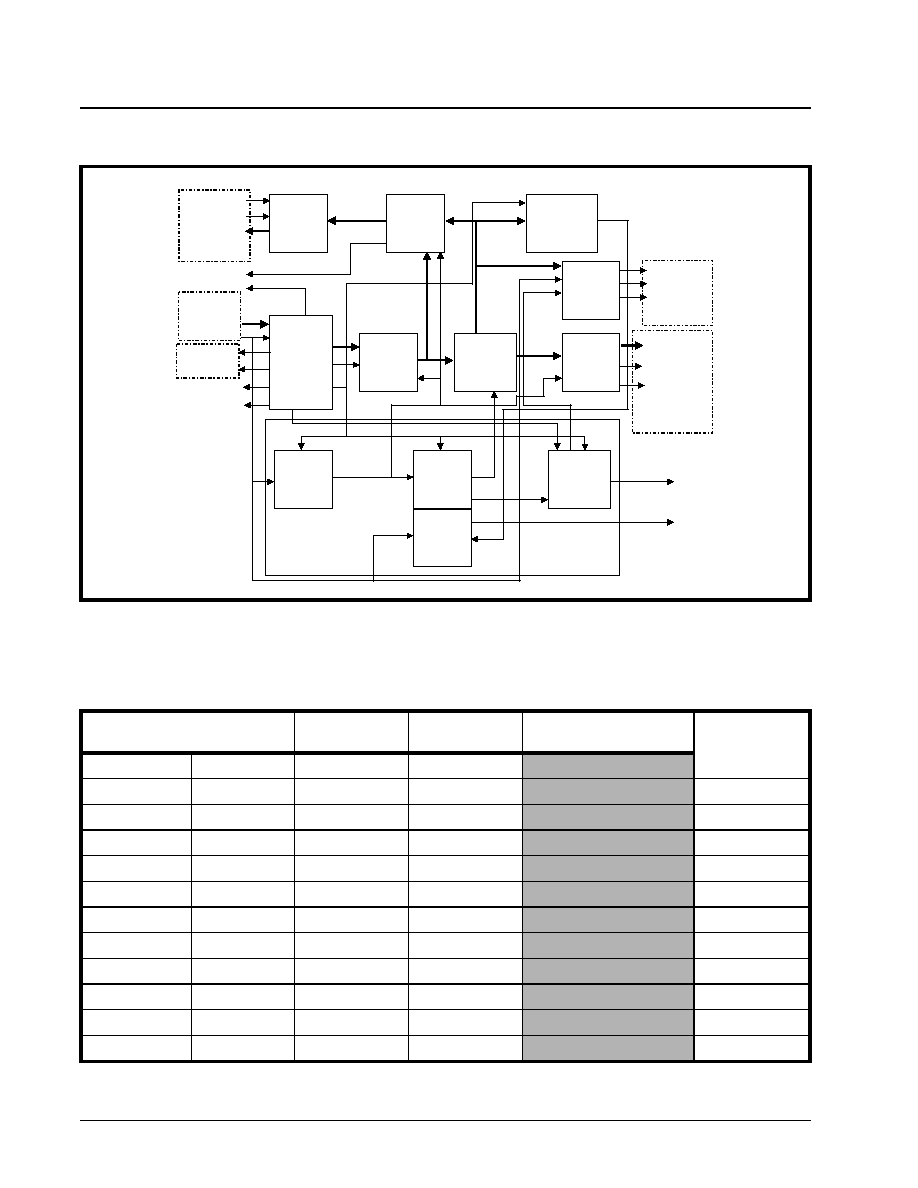

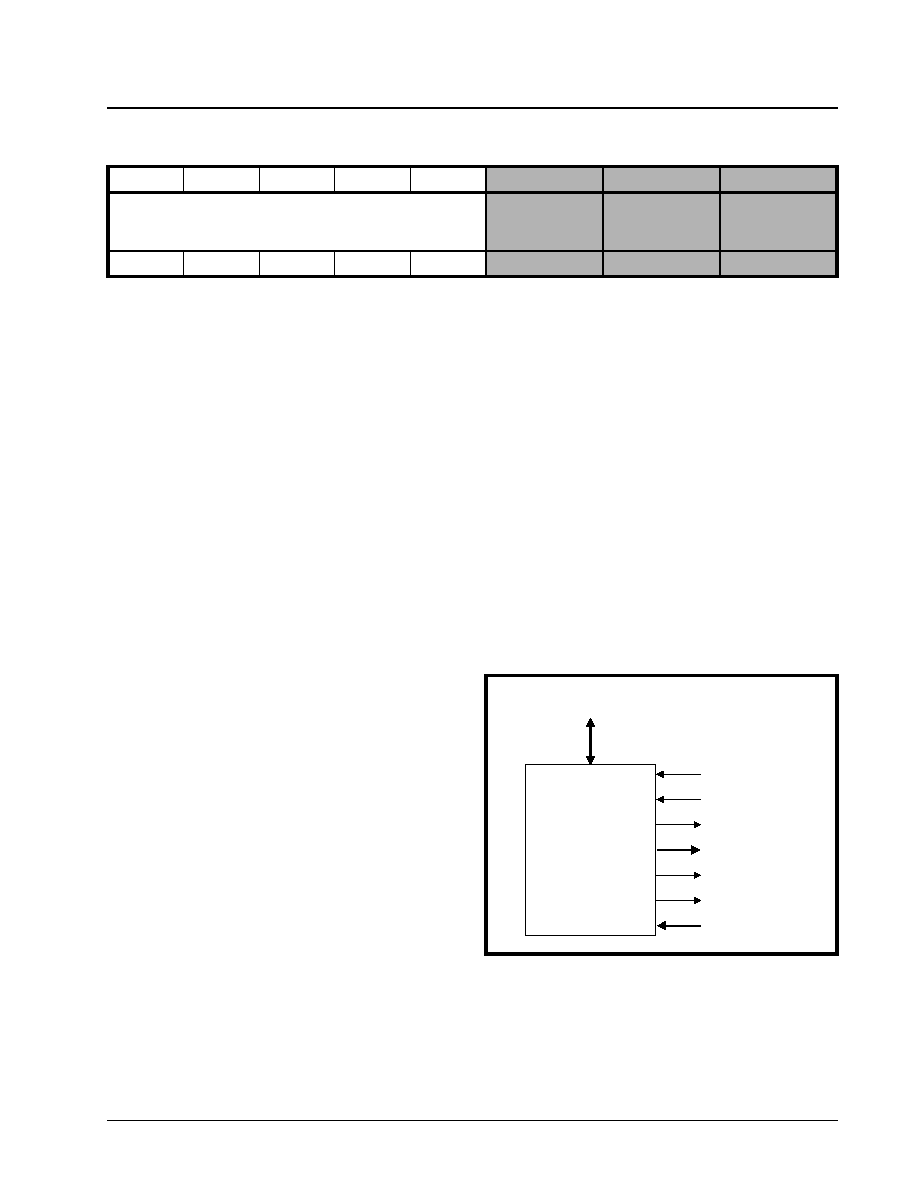

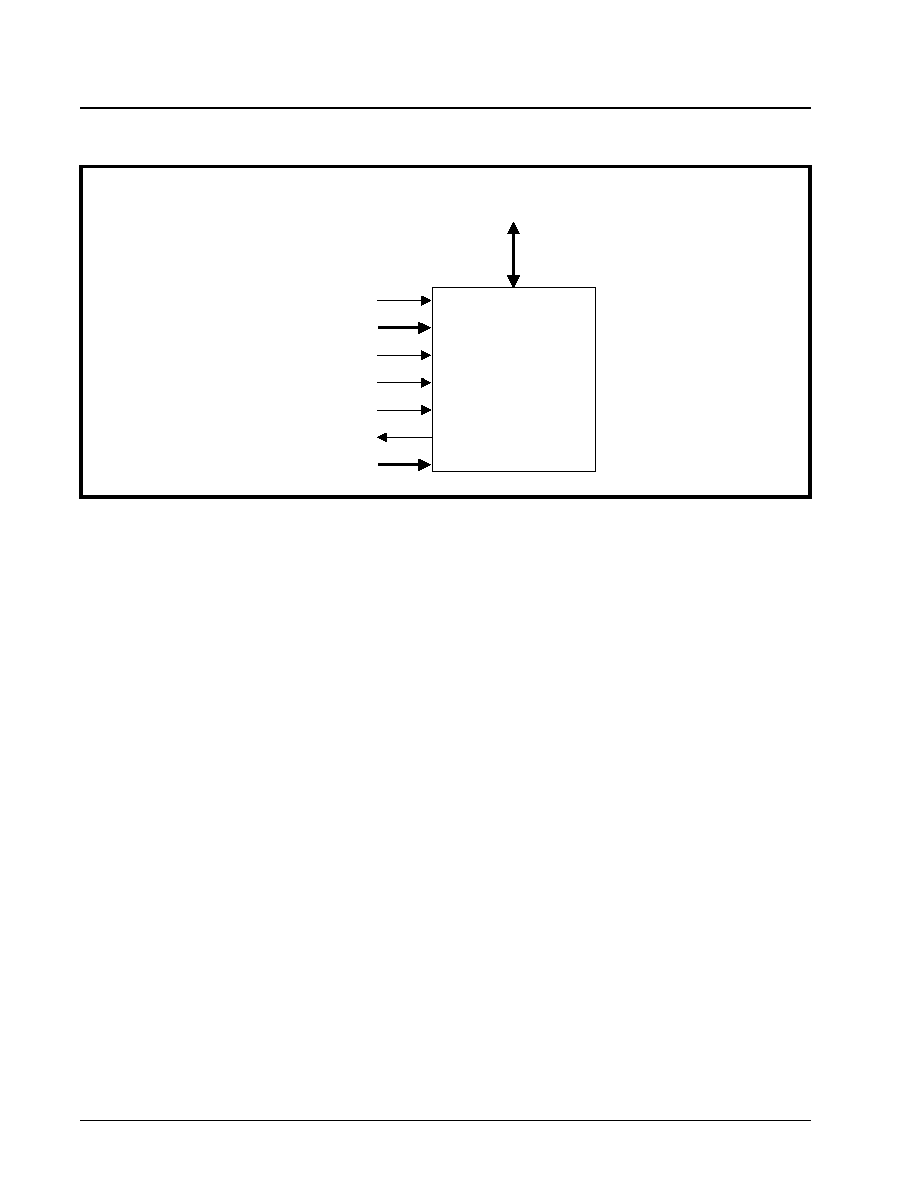

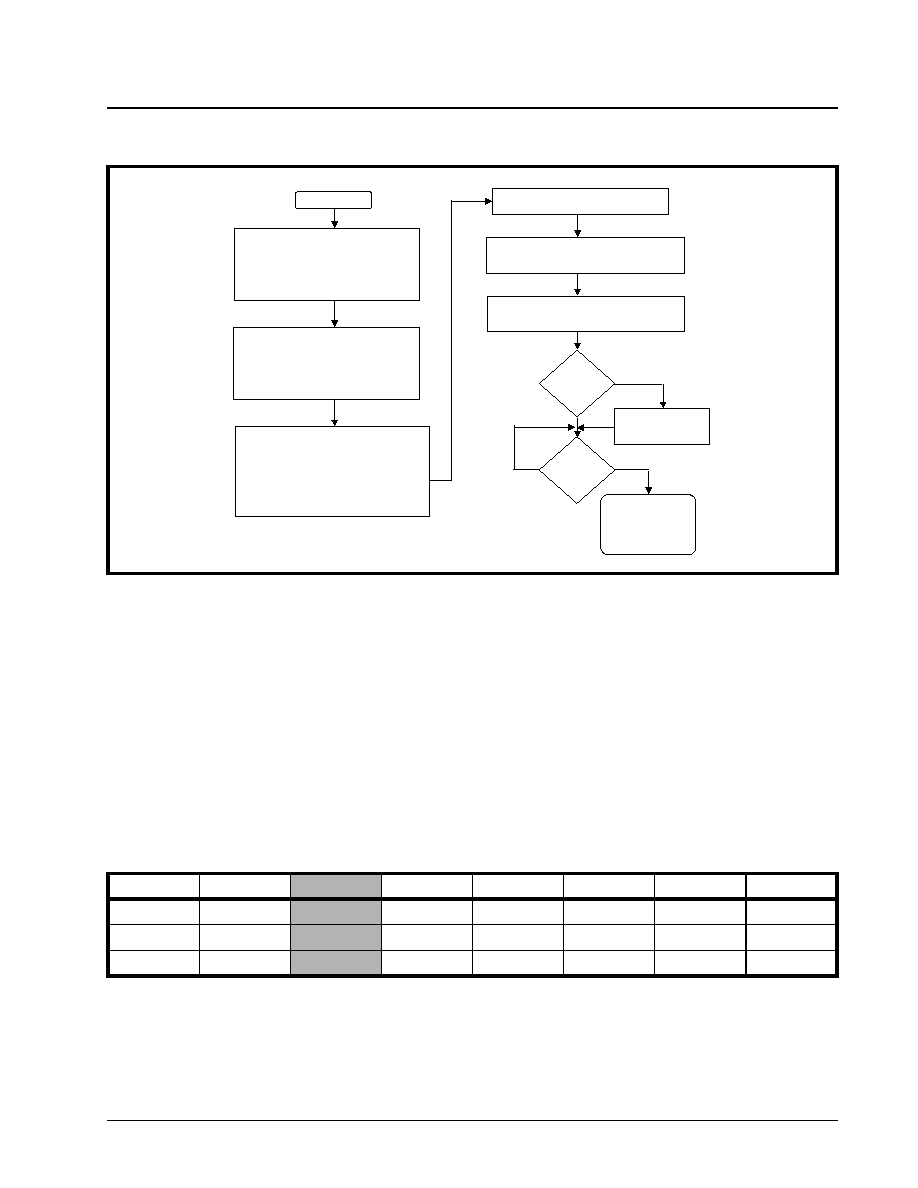

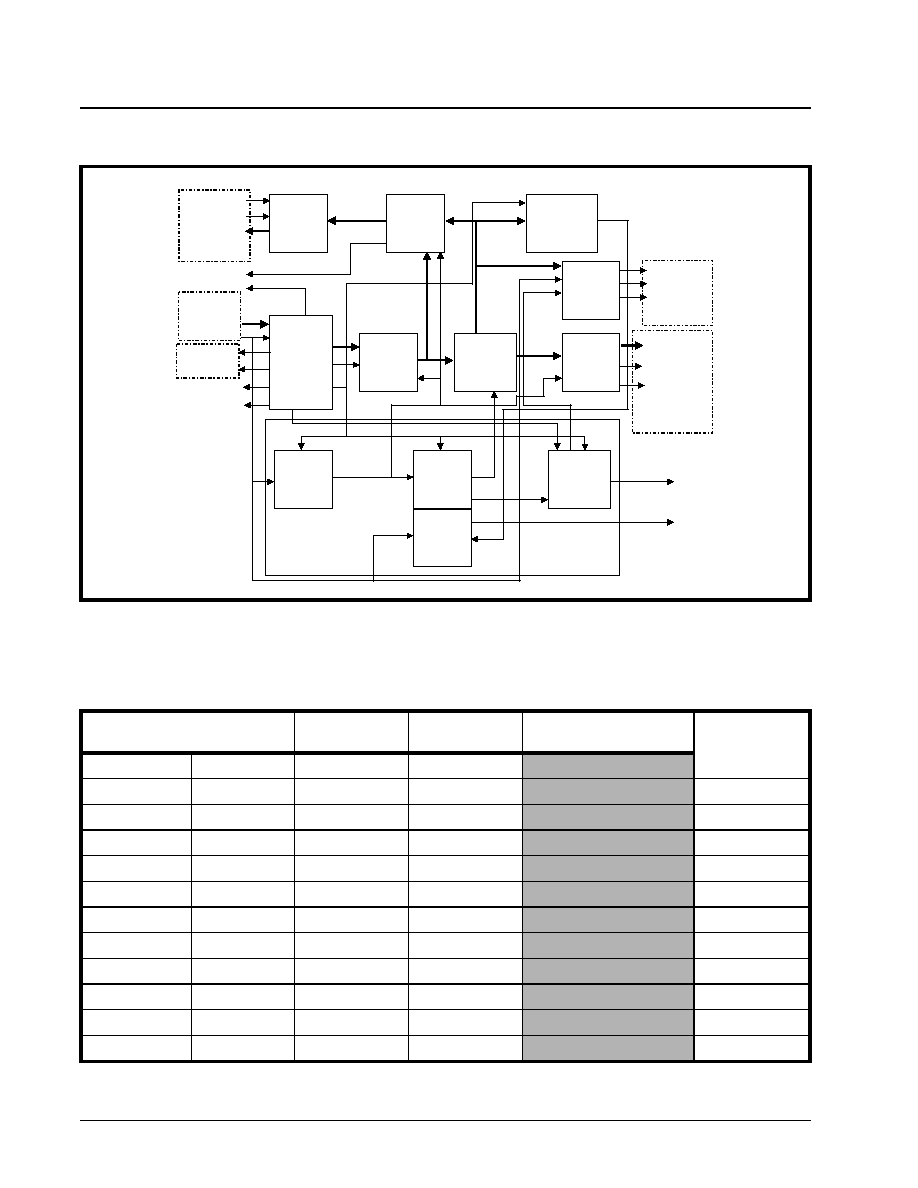

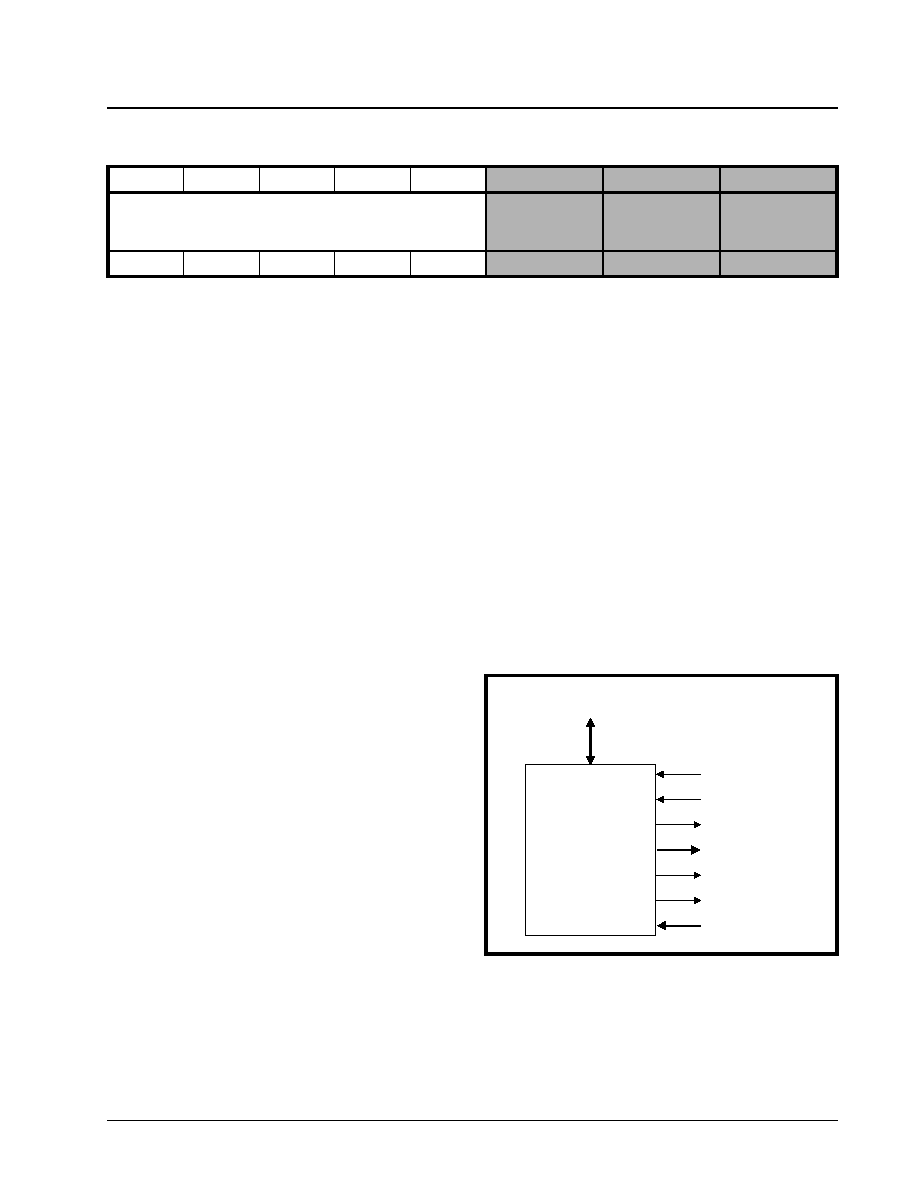

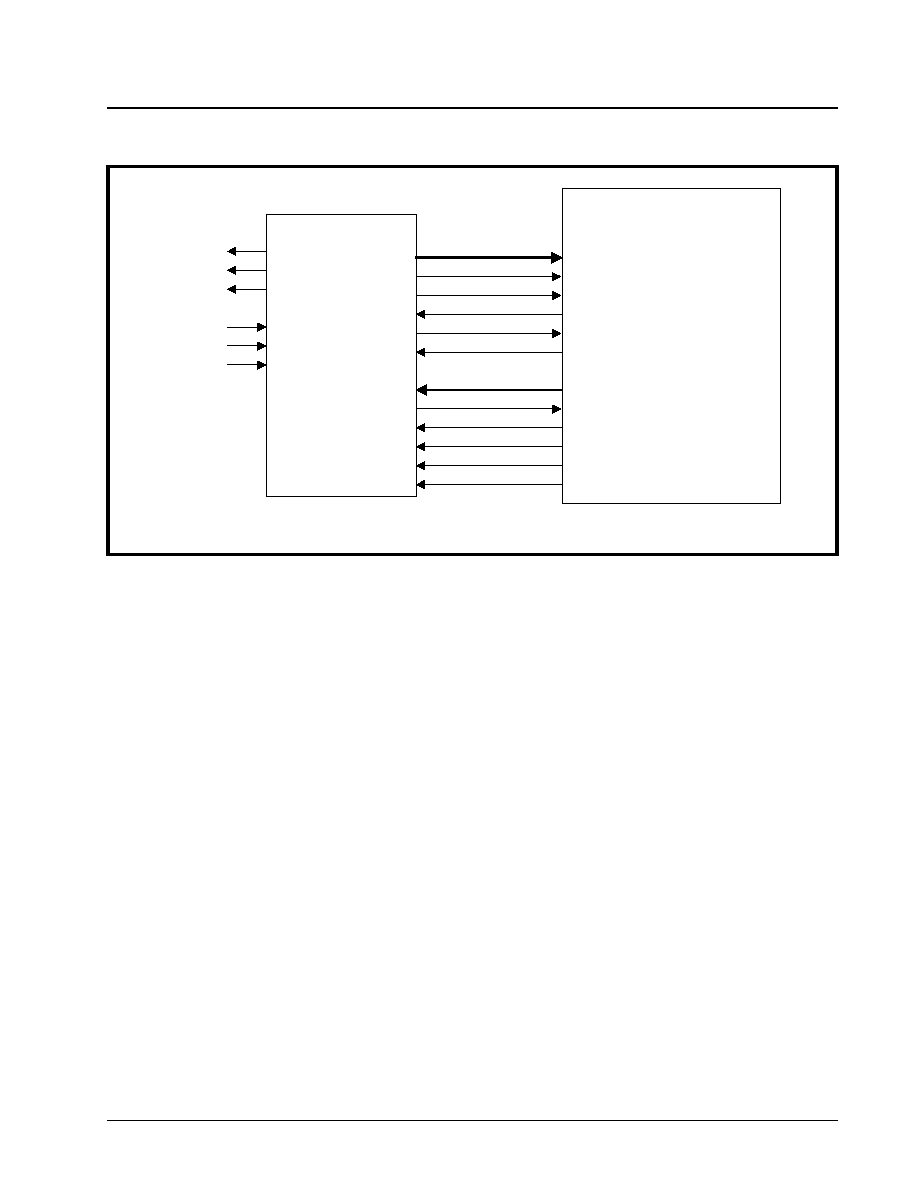

FUNCTIONAL DESCRIPTION

The XRT7245 UNI can functionally be subdivided in-

to 6 different sections, as shown in Figure 1.

∑

Receive Section

∑

Transmit Section

∑

Microprocessor Interface Section

∑

Performance Monitor Section

∑

Test and Diagnostic Section

∑

Line Interface Unit Scan Drive Section

The features of each of these functional sections are

briefly outlined below.

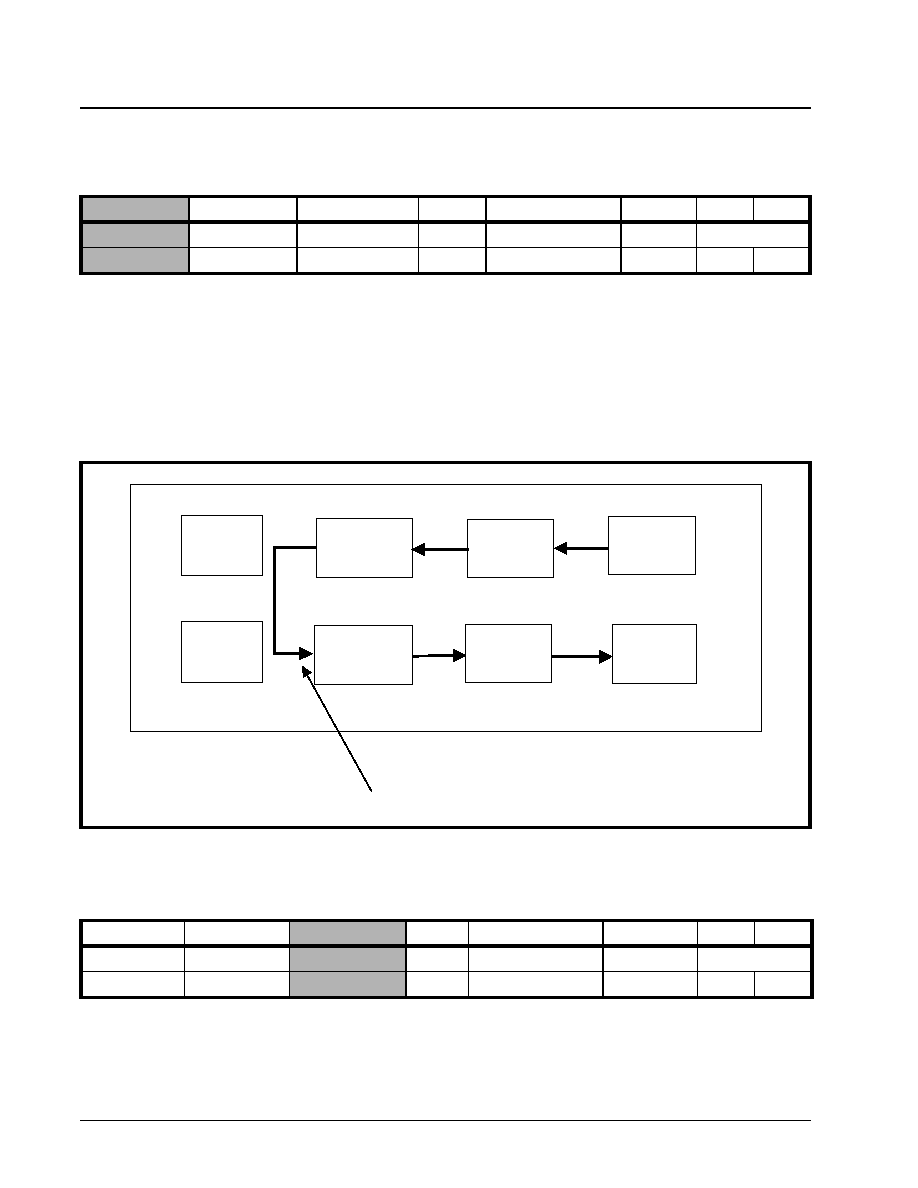

THE RECEIVE SECTION

The purpose of the Receiver Section of the XRT7245

DS3 ATM UNI device is to allow a local ATM Layer (or

ATM Adaptation Layer) processor to receive ATM cell

data from a remote piece of equipment via a public or

leased DS3 transport medium.

The Receive Section of the XRT7245 DS3 UNI con-

sists of the following functional blocks.

∑

Receive DS3 Framer Block

∑

Receive PLCP (Physical Layer Convergence Proto-

col) Processor Block

∑

Receive Cell Processor Block

∑ Receive UTOPIA Interface Block

The Receive Section of the UNI device will:

∑ The Receive DS3 Framer will synchronize to the

incoming DS3 data stream and remove or process

the DS3 Framing/Overhead Bits. This procedure

will result in either extracting PLCP frame data or

"Direct-Mapped" ATM Cell data, from the payload

portion of the incoming DS3 data stream. The

Receive DS3 Framer can used to receive FEAC

(Far End Alarm & Control) messages via an on-

chip FEAC Transceiver.

Additionally, the Receive DS3 Framer includes an on-

chip LAPD Receiver that can receive incoming path

maintenance data link messages from the far-end

Transmit DS3 Framer of the "Far End" Terminal.

Note: The Receive DS3 Framer supports both M13 and C-

bit Parity Frame Formats.

∑

The Receive PLCP Processor will identify the

frame boundary of each incoming PLCP frame,

extract and process the overhead bytes of these

PLCP frames (applies only if the UNI is operating in

the PLCP Mode). The Receive PLCP Processor

will also perform some error checking on the

incoming PLCP frames. The Receive PLCP Pro-

cessor will inform the Far-End (Transmitting UNI) of

the results of this error-checking by internally rout-

ing these results to the "Near-End" Transmit PLCP

Processor, for transmission back out to the Far-End

Terminal.

∑

The Receive Cell Processor will perform the follow-

ing functions:

≠ Cell Delineation

≠ HEC Byte Verification of incoming cells

(optional)

≠ Cell-payload de-scrambling (optional)

≠ Idle cell detection and removal (optional)

≠ User and OAM Cell Filtering (optional)

≠ OAM Cell Processing (optional)

∑

The UNI provides 54 bytes of on-chip RAM that

allows for the reception and processing of selected

OAM cells.

∑ The RxFIFO, within the Receive UTOPIA Interface

block will temporarily hold any ATM cells that pass

through the Receive Cell Processor, where they can

be read out by the ATM Layer processor, over the

Receive UTOPIA Data Bus.

THE TRANSMIT SECTION

The purpose of the Transmit section of the XRT7245

DS3 ATM UNI device is to allow a local ATM Layer (or

ATM Adaptation Layer) processor to transmit ATM

Cell data to a remote piece of equipment via a public

or leased DS3 transport medium.

The Transmit Section of the XRT7245 DS3 UNI con-

sists of the following functional blocks.

∑

Transmit UTOPIA Interface Block

∑

Transmit Cell Processor Block

∑

Transmit PLCP Processor Block

∑ Transmit DS3 Framer Block

The Transmit Section of the UNI device will:

∑

Allow the ATM Layer processor to write ATM cells

into the Transmit FIFO (within the Transmit UTOPIA

Interface block) via a standard UTOPIA Level 2

interface.

∑

The Transmit Cell Processor will read in these cells

from the Transmit FIFO (if available) for further

processing. If no cell is available within the Trans-

mit FIFO, then the Transmit Cell Processor will

automatically generate an Idle cell. The UNI is

equipped with on-chip registers to allow for the

generation of customized Idle cells.

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

4

∑

The UNI provides 54 bytes of on-chip RAM that

allows for the generation and transmission of "user-

specified" OAM cells. The Transmit Cell Processor

will generate and transmit these OAM cells upon

software command.

∑

The Transmit Cell Processor will (optionally) scramble

the Cell Payload bytes and (optionally) compute

and insert the HEC (Header Error Check) byte.

This HEC byte will be inserted into the fifth octet of

each cell prior to being transferred to the Transmit

PLCP Processor (or the Transmit DS3 Framer).

∑

The Transmit PLCP Processor will pack 12 ATM cells

into each PLCP frame and automatically determine

the nibble-stuffing option of the current PLCP frame.

These PLCP frames will also include an overhead

byte that reflect BIP-8 (Bit Interleaved Parity) calcu-

lation results, a byte that reflects the current stuffing

option status of the current PLCP frame, Path

Overhead and Identifier bytes, and diagnostic-

related bytes reflecting any detected BIP-8 errors

and alarm conditions detected in the Receive section

of the UNI chip.

∑ These PLCP frames (or "Direct Mapped" ATM

cells) will be inserted into the payload of an outgo-

ing DS3 frame, for transmission to the "Far-End" Ter-

minal, by the Transmit DS3 Framer. The Transmit

DS3 Framer will transmit FEAC (Far End Alarm &

Control) messages to the Far-End Receiver via an

on-chip FEAC Transceiver.Additionally, the Trans-

mit DS3 Framer can transmit path maintenance

data link messages to the Far-End Terminal via the

on-chip LAPD Transmitter.

Note: The Transmit DS3 Framer will support either M13 or

C-bit Parity Framing Formats.

THE MICROPROCESSOR INTERFACE SECTION

The Microprocessor Interface Section allows a user (or

a local "housekeeping" processor) to do the following:

∑

To configure the UNI IC into a wide variety of oper-

ating modes; by writing data into any one of a large

number of "read/write" registers.

∑

To monitor many aspects of the UNI's performance

by reading data from any one of a large number of

"read/write" and "read-only" registers.

∑

To run in a "polling" or "interrupt-driven" environment.

The UNI IC contains an extensive interrupt structure

consisting of a wide range of interrupt enable and

interrupt status registers.

∑

To command the UNI IC to transmit OAM cells,

FEAC messages and/or LAPD Messages frames,

upon software command.

∑

To read in and process received OAM cells, FEAC

messages and/or Path Maintenance Data Link

Messages from the UNI IC.

∑

The Microprocessor Interface allows the user to

interface the XRT7245 DS3 UNI to either an Intel

type or Motorola type processor. Additionally, the

Microprocessor Interface can be configured to

operate over an 8-bit or 16-bit data bus.

∑ The Microprocessor Interface section includes a

"Loss of Clock Signal" protection feature that auto-

matically completes (or terminates) a "Read/Write"

operation, should a "Loss of Clock Signal" event

occur.

PERFORMANCE MONITOR SECTION

The Performance Monitor Section of the XRT7245

DS3 UNI consists of a large number of "Reset-upon-

Read" and "Read-Only" registers that contains cumu-

lative and "one-second" statistics that reflect the per-

formance/health of the UNI chip/system. These cu-

mulative and "one-second" statistics are kept on

some of the following parameters.

∑

Number of Line Code Violation events detected by

the Receive DS3 Framer

∑

Number of Framing Bit (F- and M-bit) errors

detected by the Receive DS3 Framer

∑

Number of P-bit Errors detected by the Receive

DS3 Framer

∑

Number of FEBE Events detected by the Receive

DS3 Framer

∑

Cumulative number of BIP-8 errors, detected by

the Receive PLCP Processor

∑

Number of PLCP framing errors, detected by the

Receive PLCP Processor

∑

Cumulative sum of the FEBE value, in the incoming

G1 bytes (within each PLCP frame), received by

the Receive PLCP Processor

∑

Number of Single-bit HEC byte Errors detected

∑

Number of Multi-bit HEC byte Errors detected

∑

Number of Received Idle Cells

∑

Number of Received Valid (User and OAM) cells

discarded

∑

Number of Discarded Cells

∑

Number of Transmitted Idle Cells

∑ Number of Transmitted Valid Cells

TEST AND DIAGNOSTIC SECTION

The Test and Diagnostic Section allows the user to

perform a series of tests in order to verify proper

functionality of the UNI chip and/or the user's system.

·Á

·Á

·Á

·Á

DS3 UNI FOR ATM

XRT7245

PRELIMINARY

REV. 1.03

5

The "Test and Diagnostic" section provides the UNI

IC with the following capabilities.

∑

Allows the UNI to operate in the Line, Cell, and

PLCP Loop-back Modes

∑

Contains an internal Test Cell Generator and an

internal Test Cell Receiver. The Test Cell Generator

will generate Test Cells with "user-defined" header

byte patterns. The Test Cell Generator will also fill

the payload portion of these test cells with bytes

from an on-chip PRBS generator.

∑

The Test Cell Generator can generate test cells in

"One Shot" Mode (e.g., a burst of 1024 test cells) or in

"Continuous" Mode (e.g., a continuous stream of

test cells).

∑ The Test Cell Receiver will identify and collect the

Test Cells for further analyses, based upon the

"user-defined" header byte patterns. Additionally,

the Test Cell Receiver will report the occurrence of

any errors by incrementing an on-chip register.

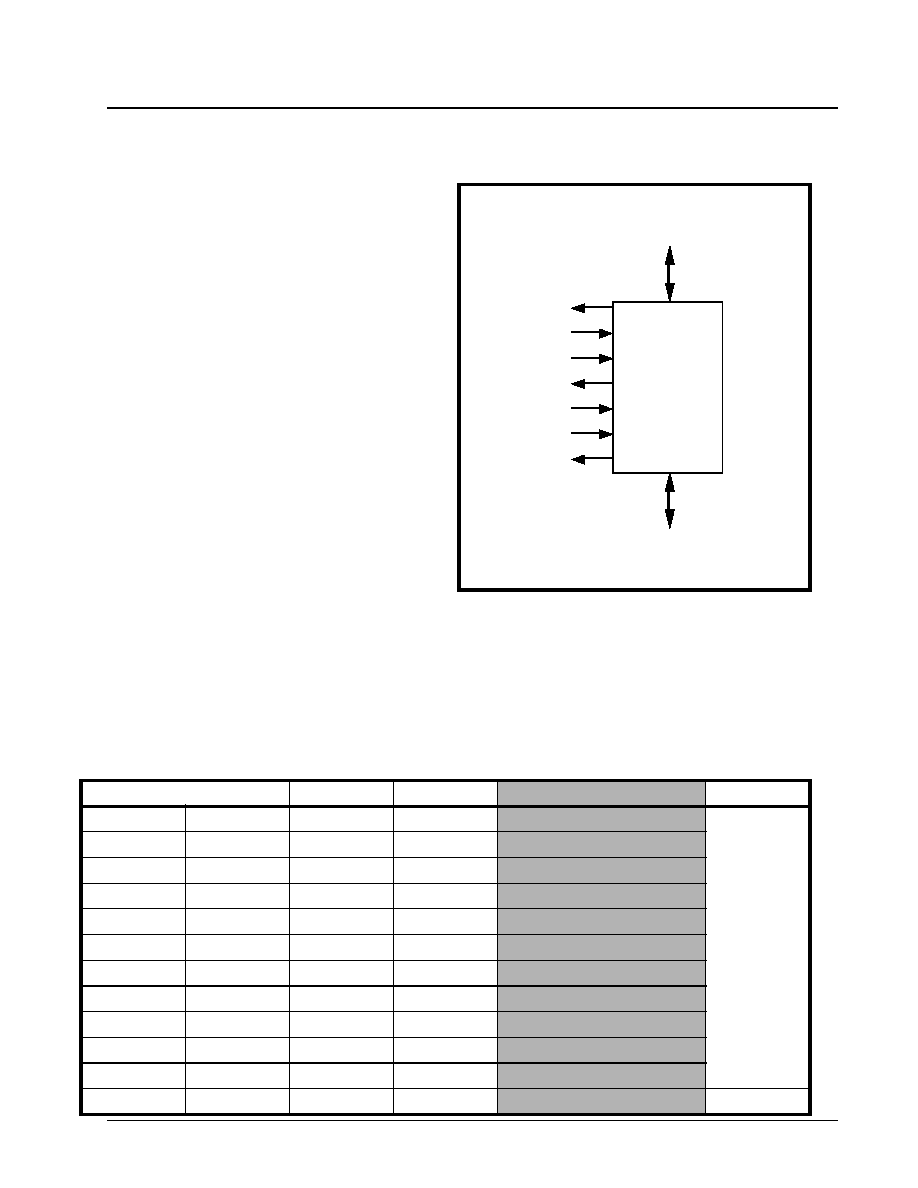

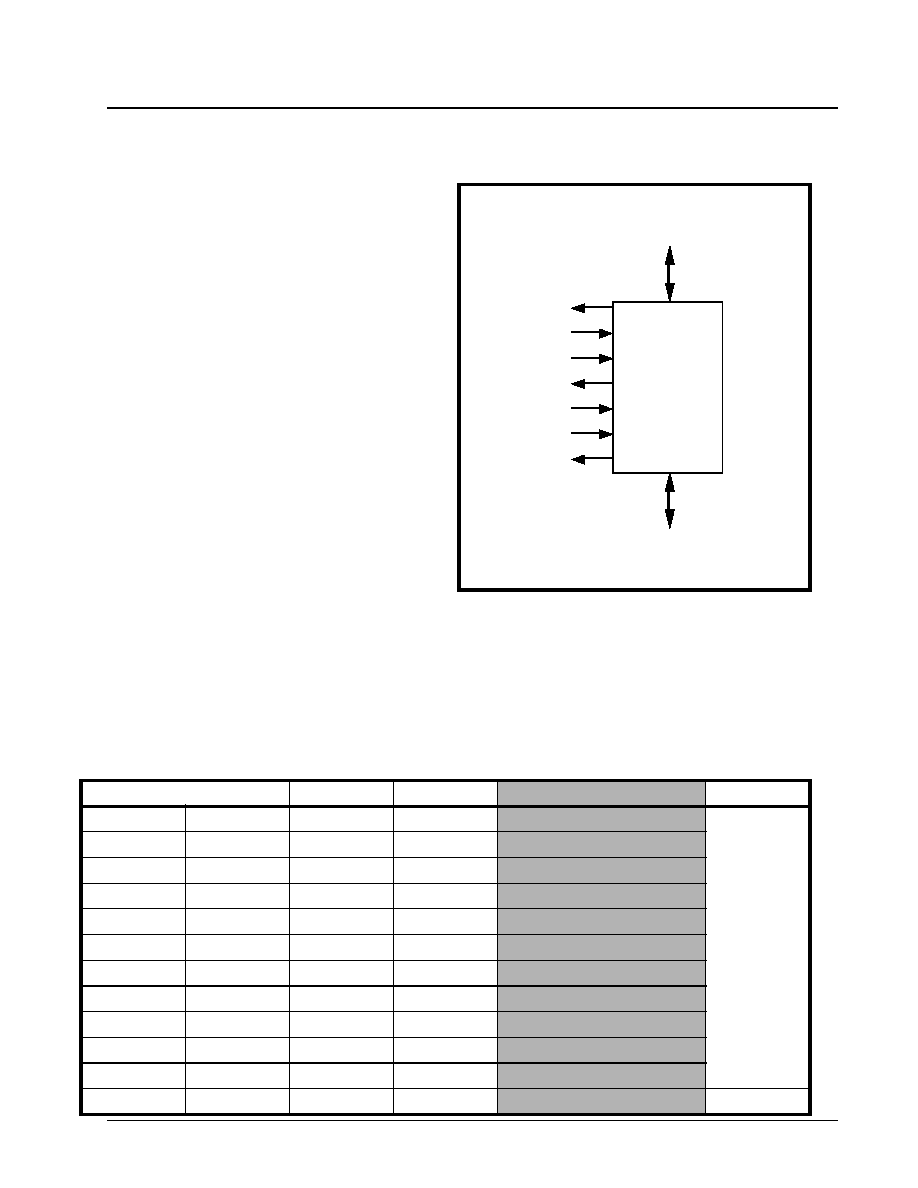

LINE INTERFACE DRIVE AND SCAN SECTION

The Line Interface Drive and Scan Section allows the

user to monitor and control many aspects of the

XRT7295 DS3 Line Receiver IC and the XRT7296

DS3 Line Transmitter IC, via on-chip registers, within

the UNI IC. This feature eliminates the need for glue

logic to interface the XRT7245 DS3 UNI to the

XRT7295/XRT7296 DS3 Line Interface Unit ICs.

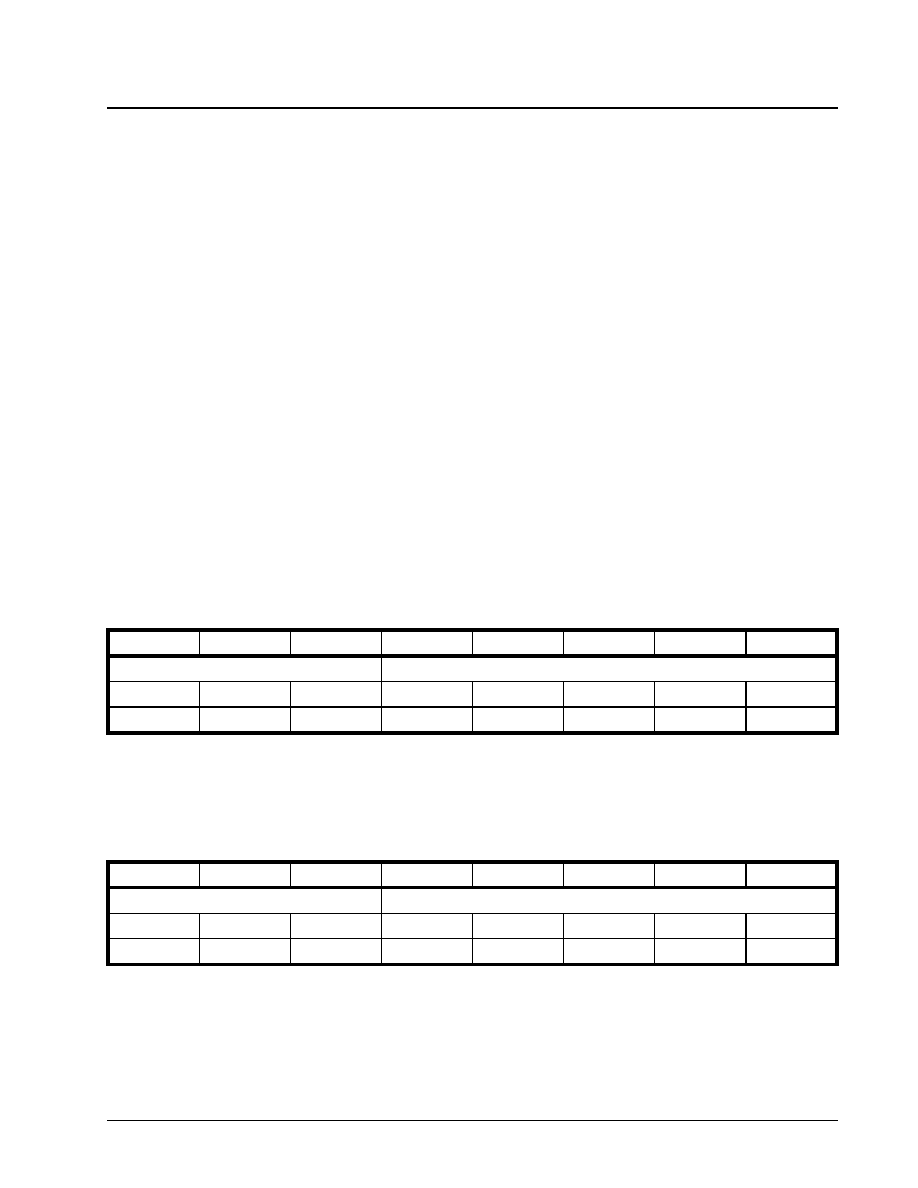

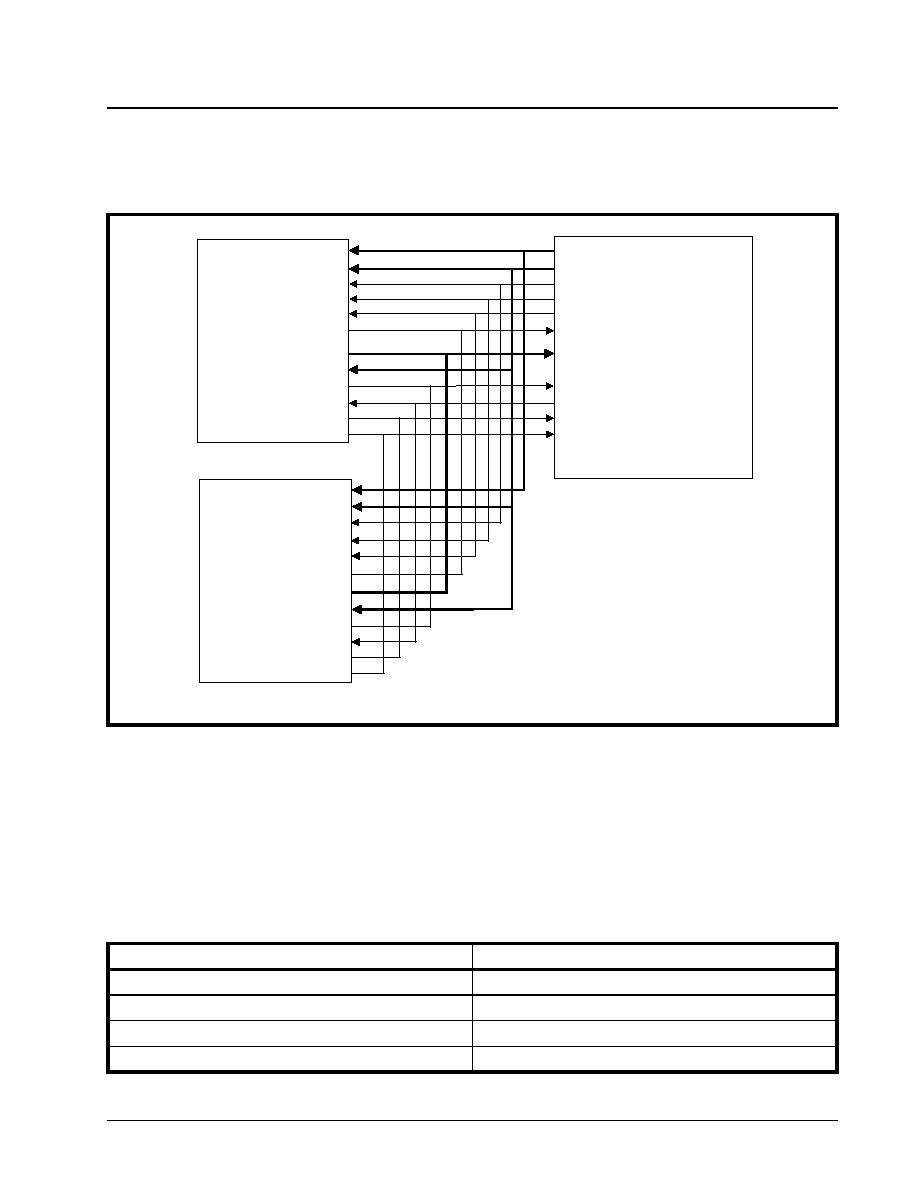

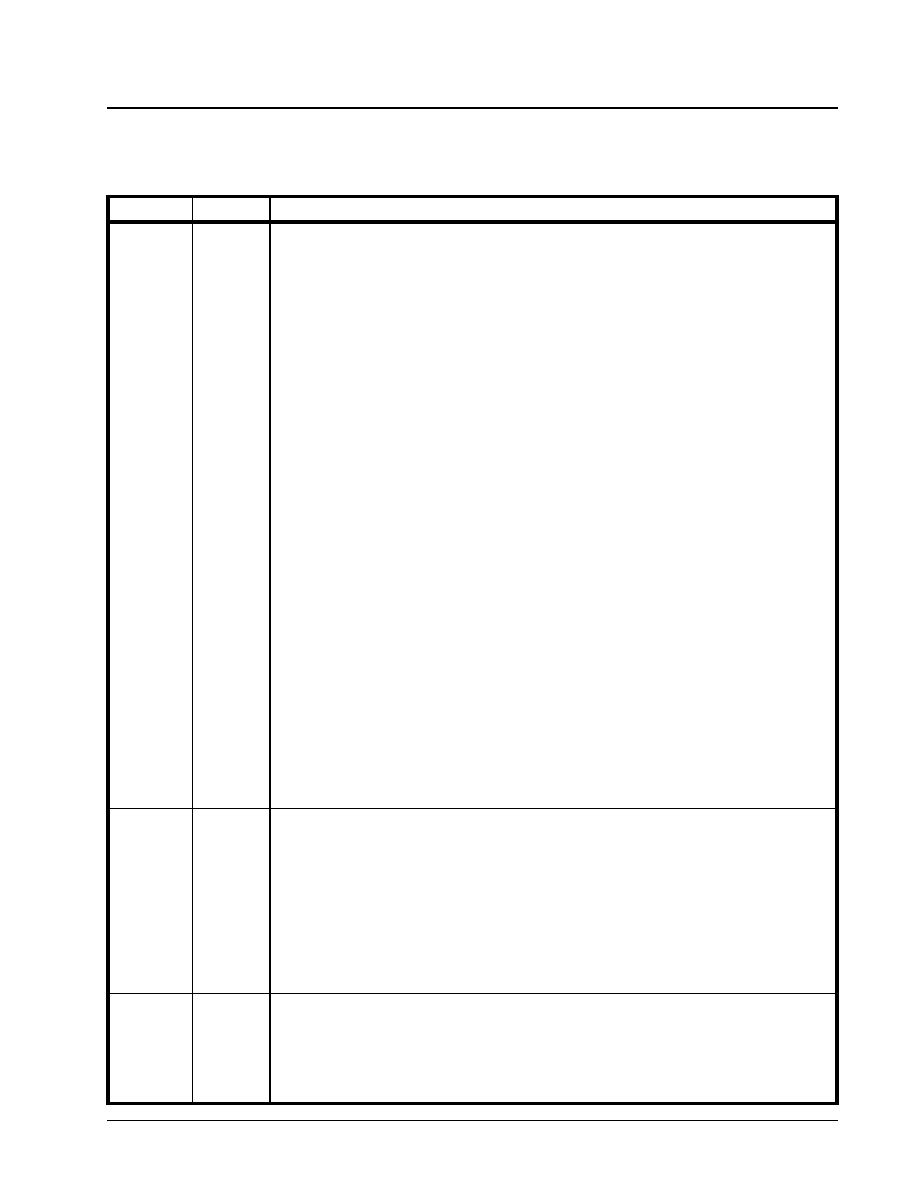

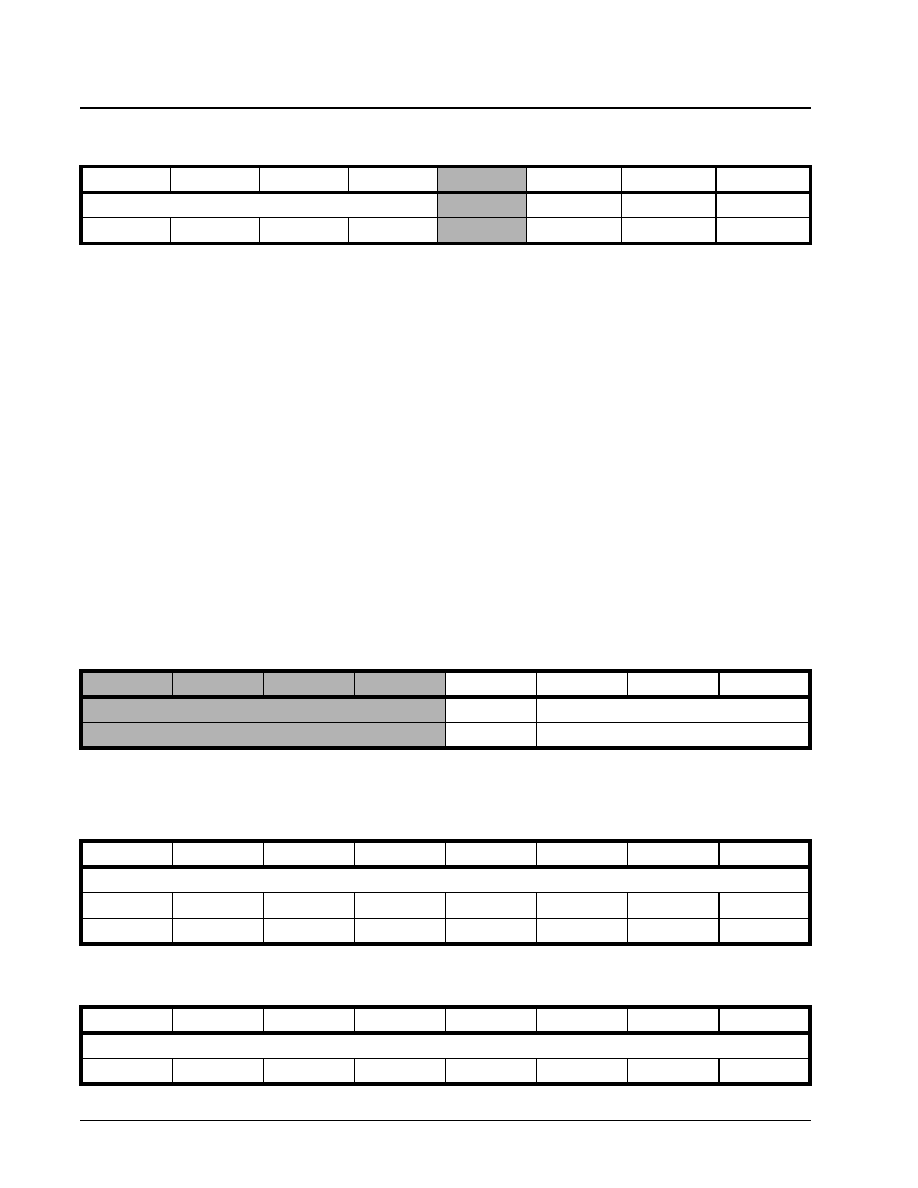

∑ The On-Chip Line Interface Drive register allows

the user to control the state of 6 output pins. The

function of these output pins, when asserted, are

tabulated below.

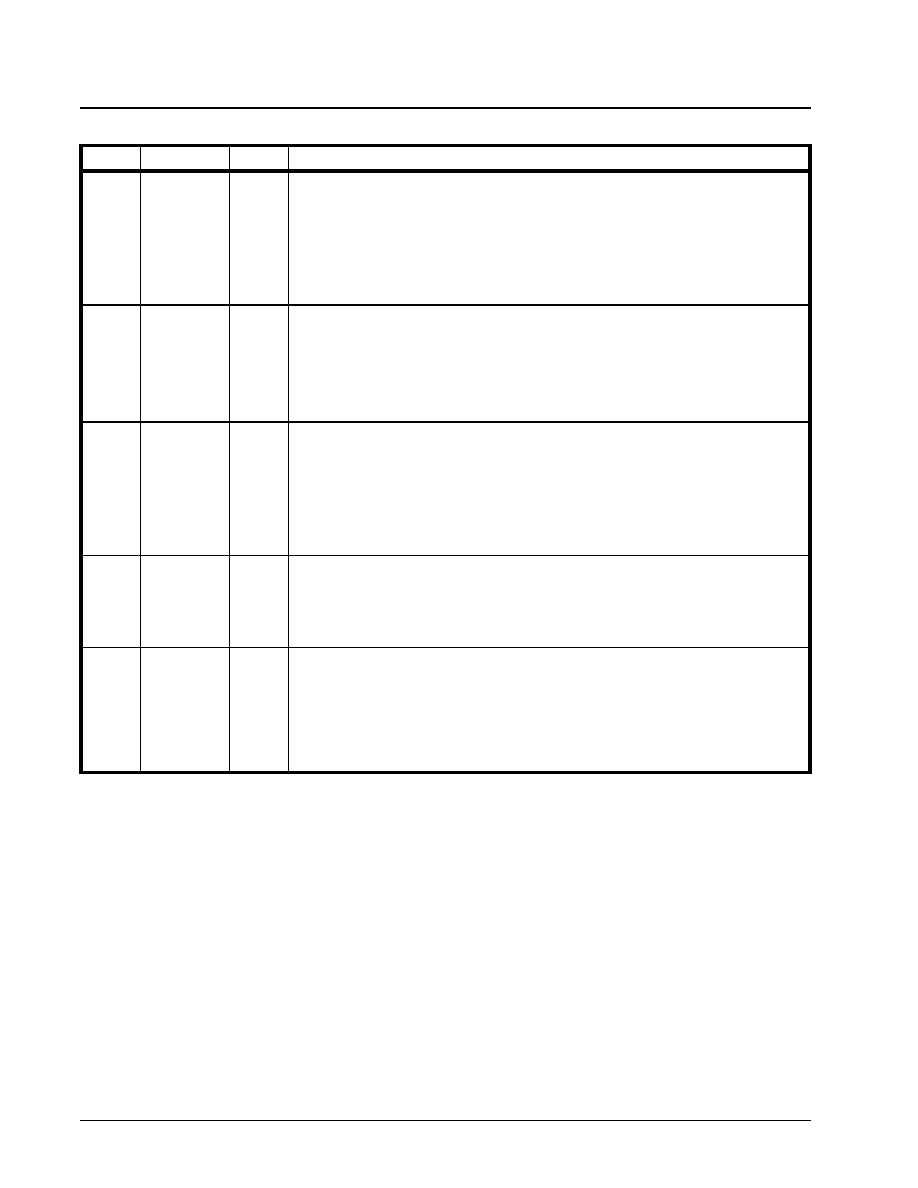

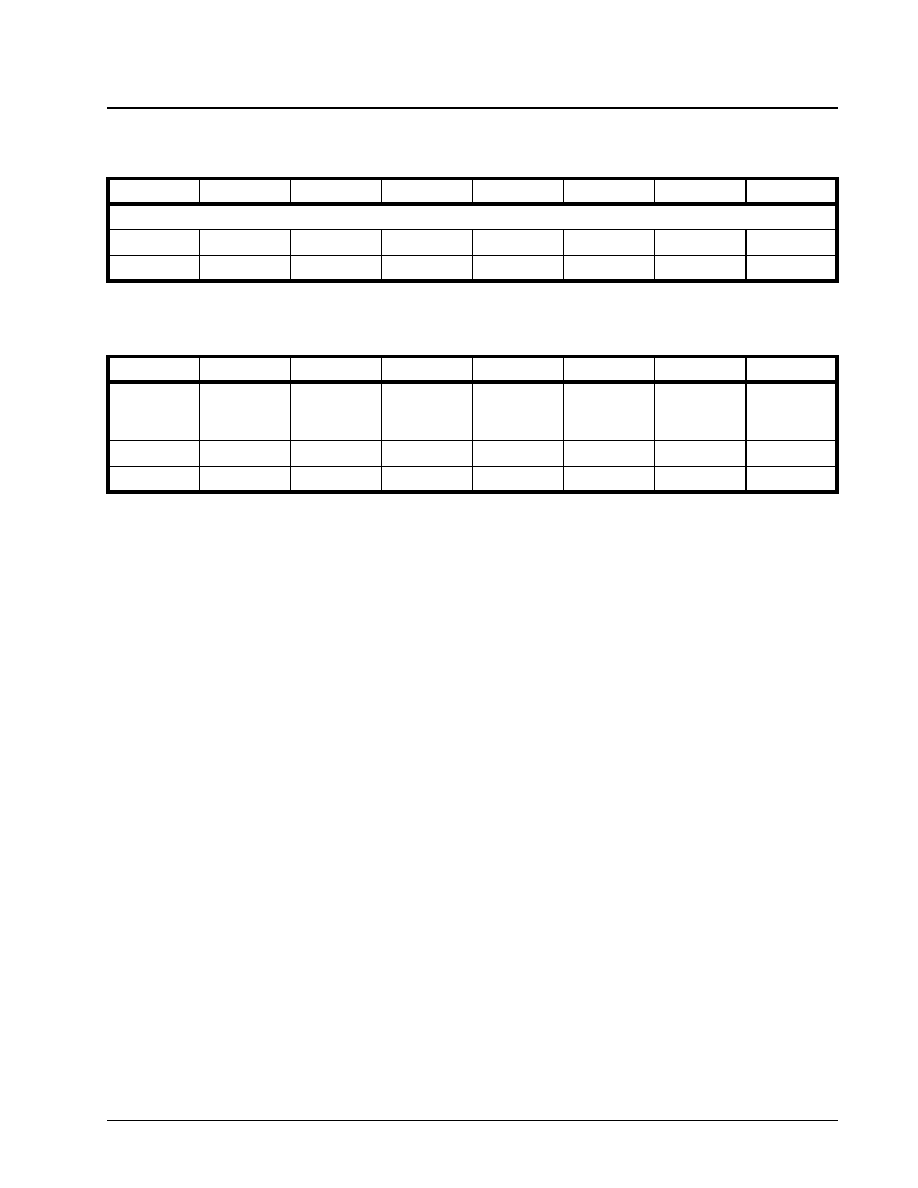

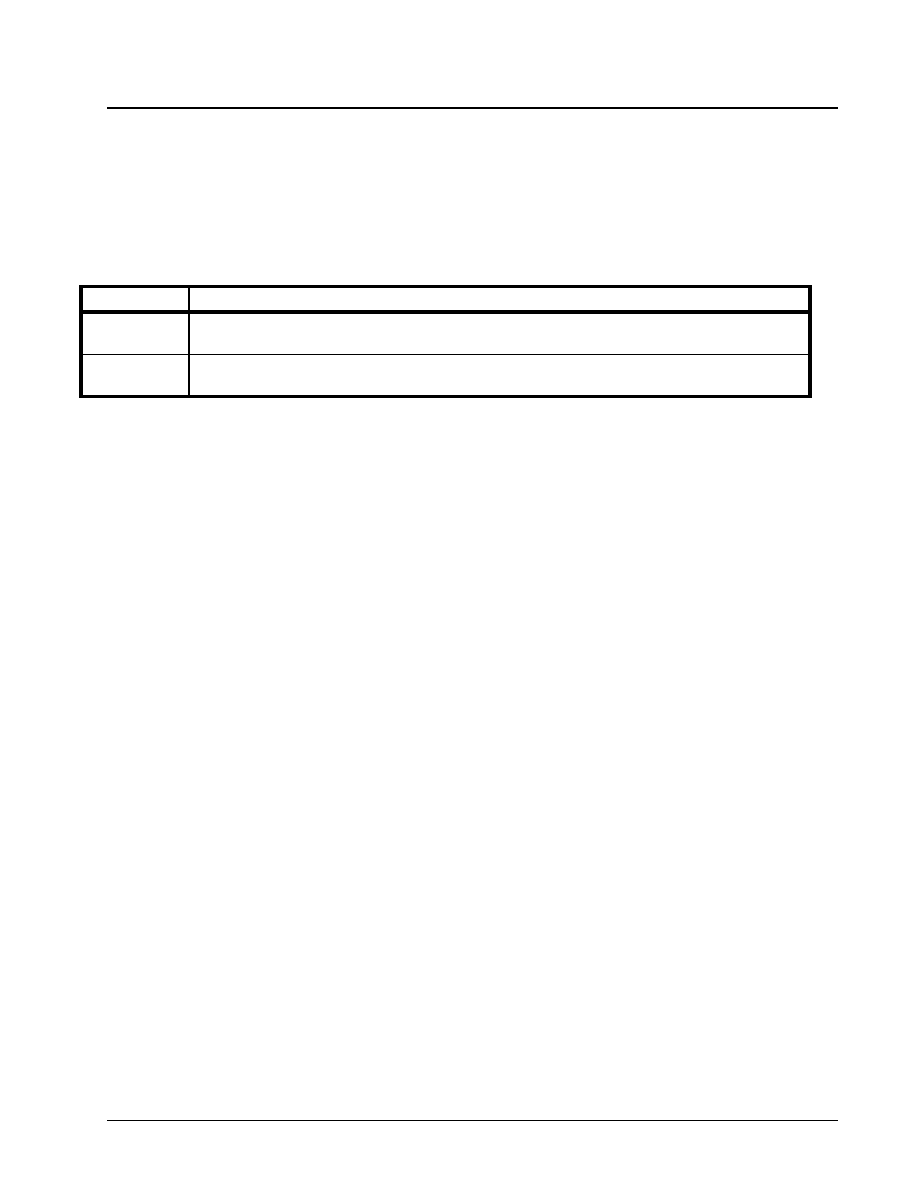

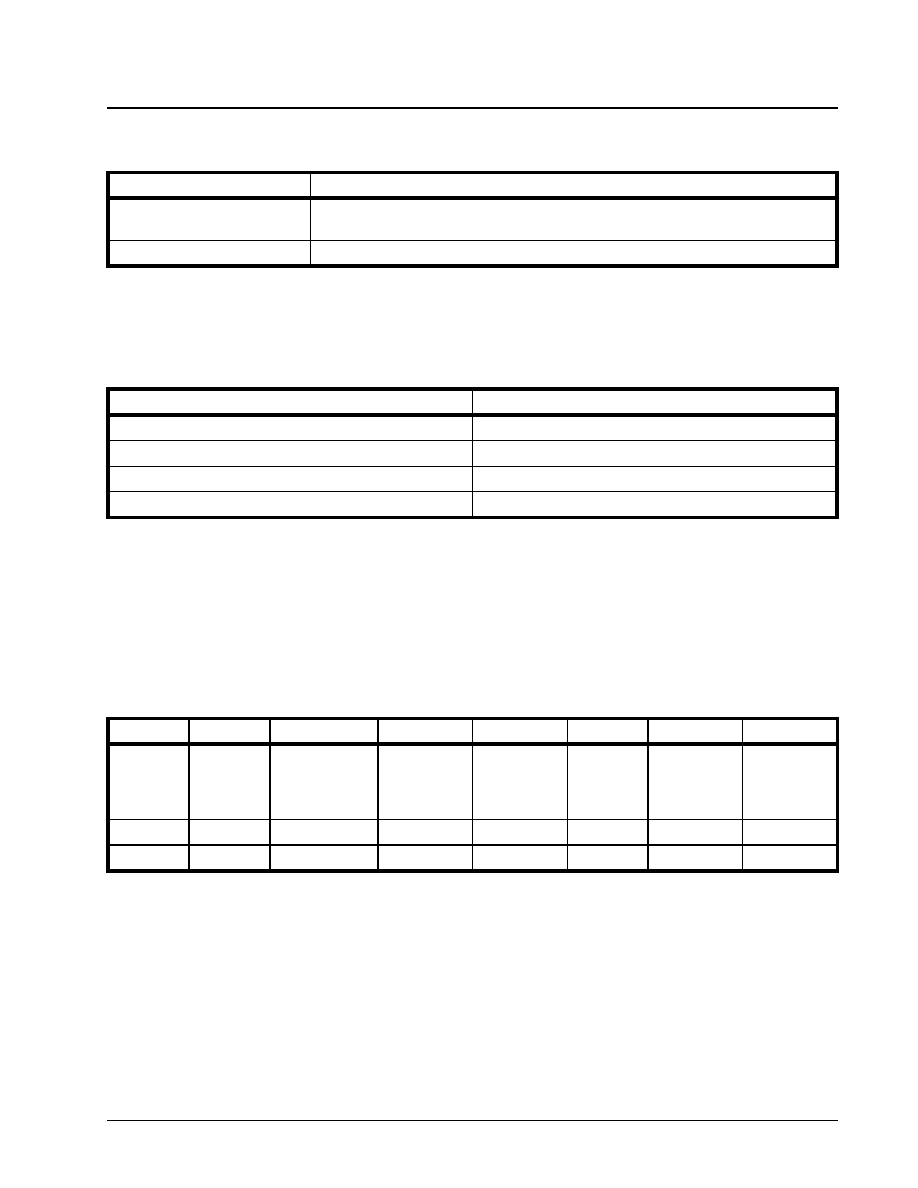

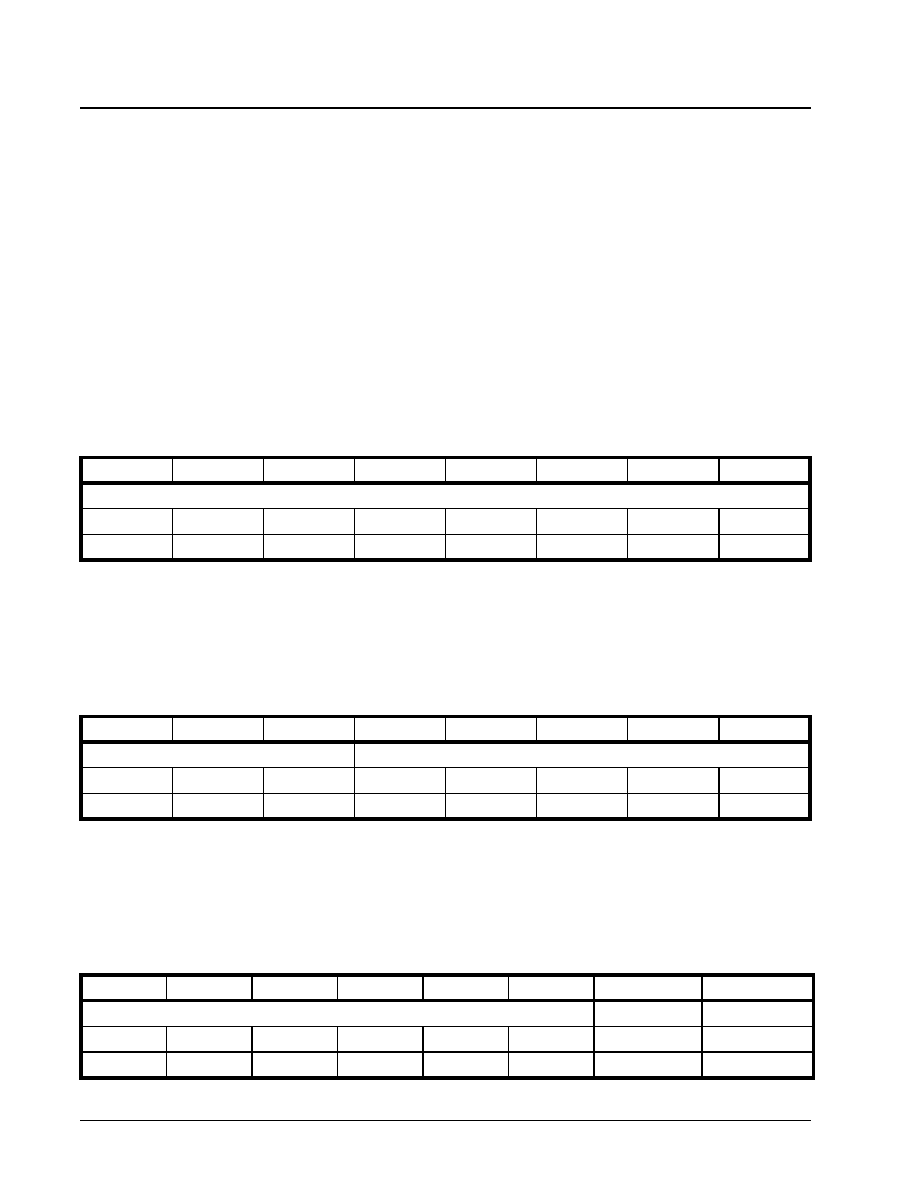

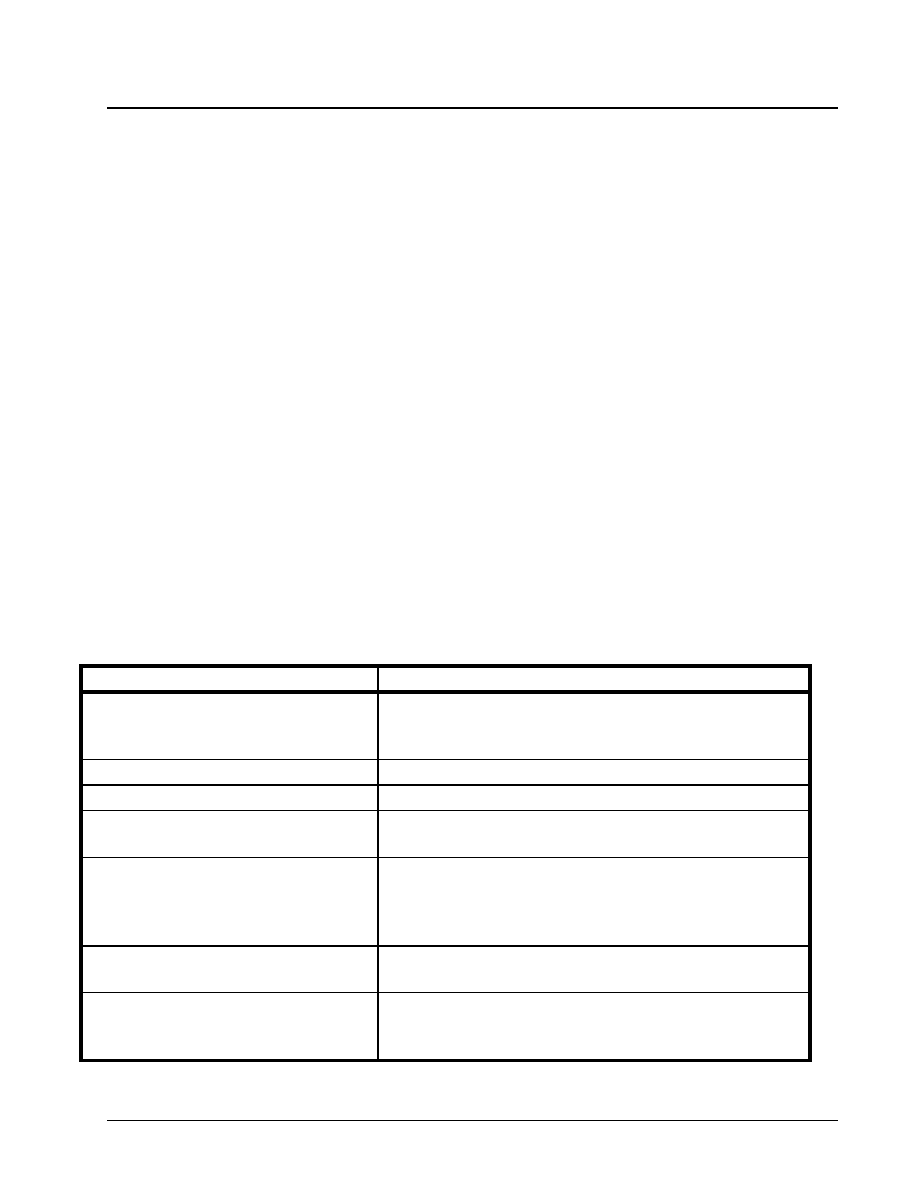

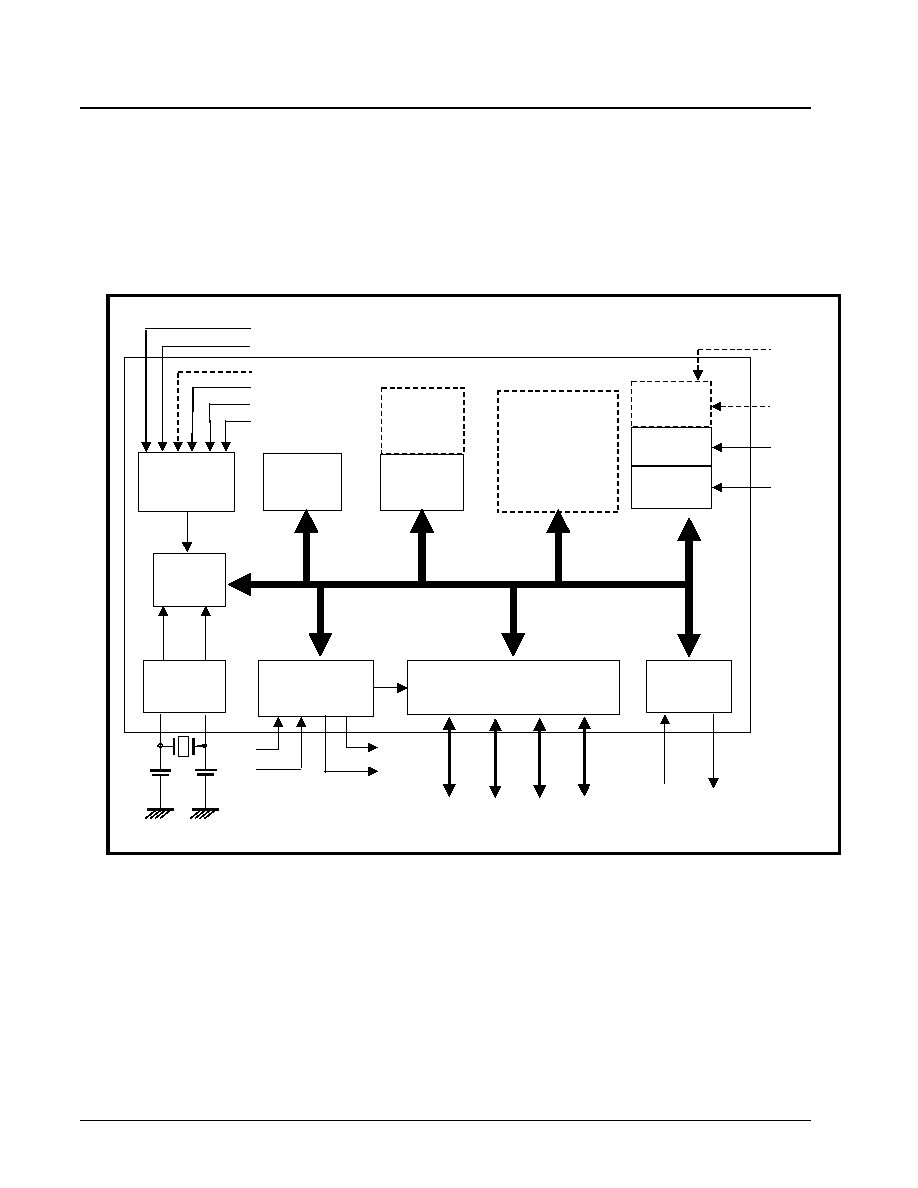

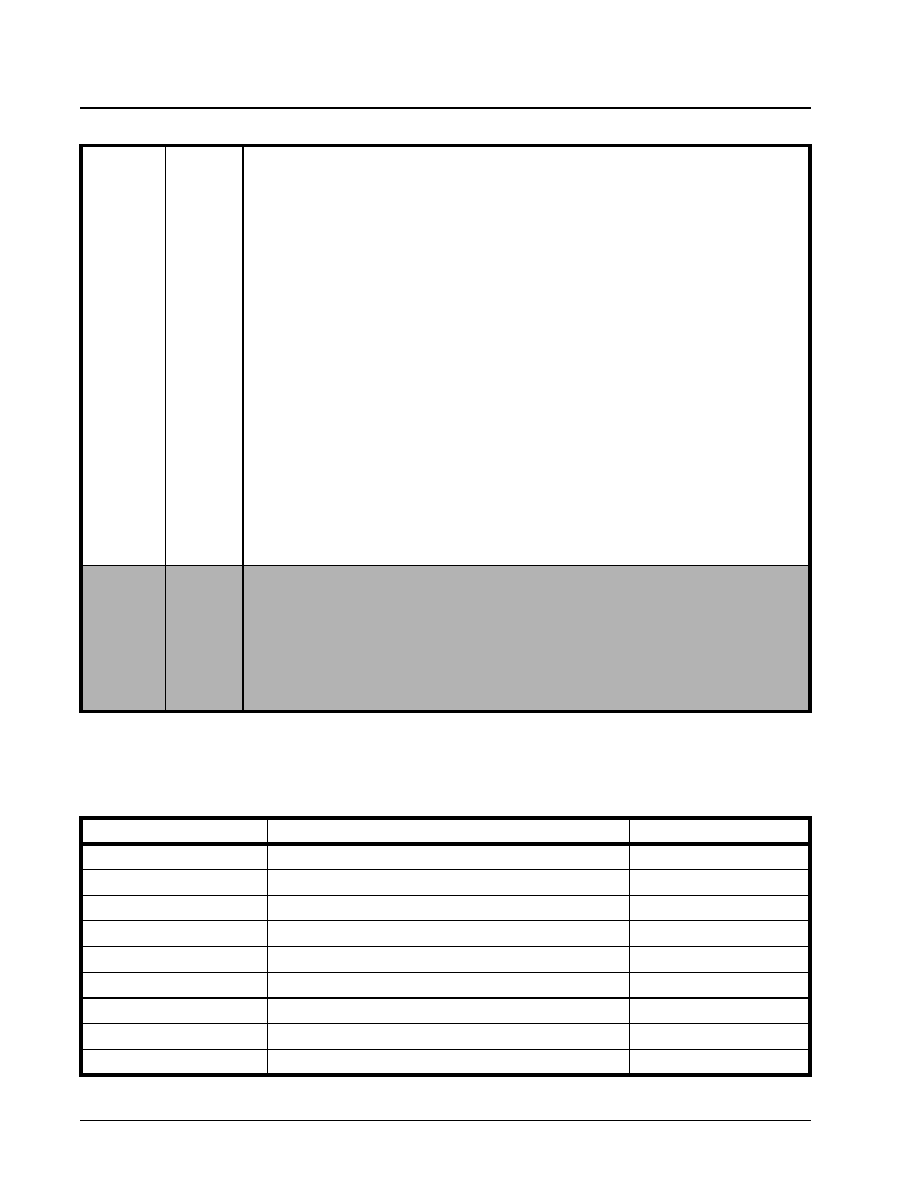

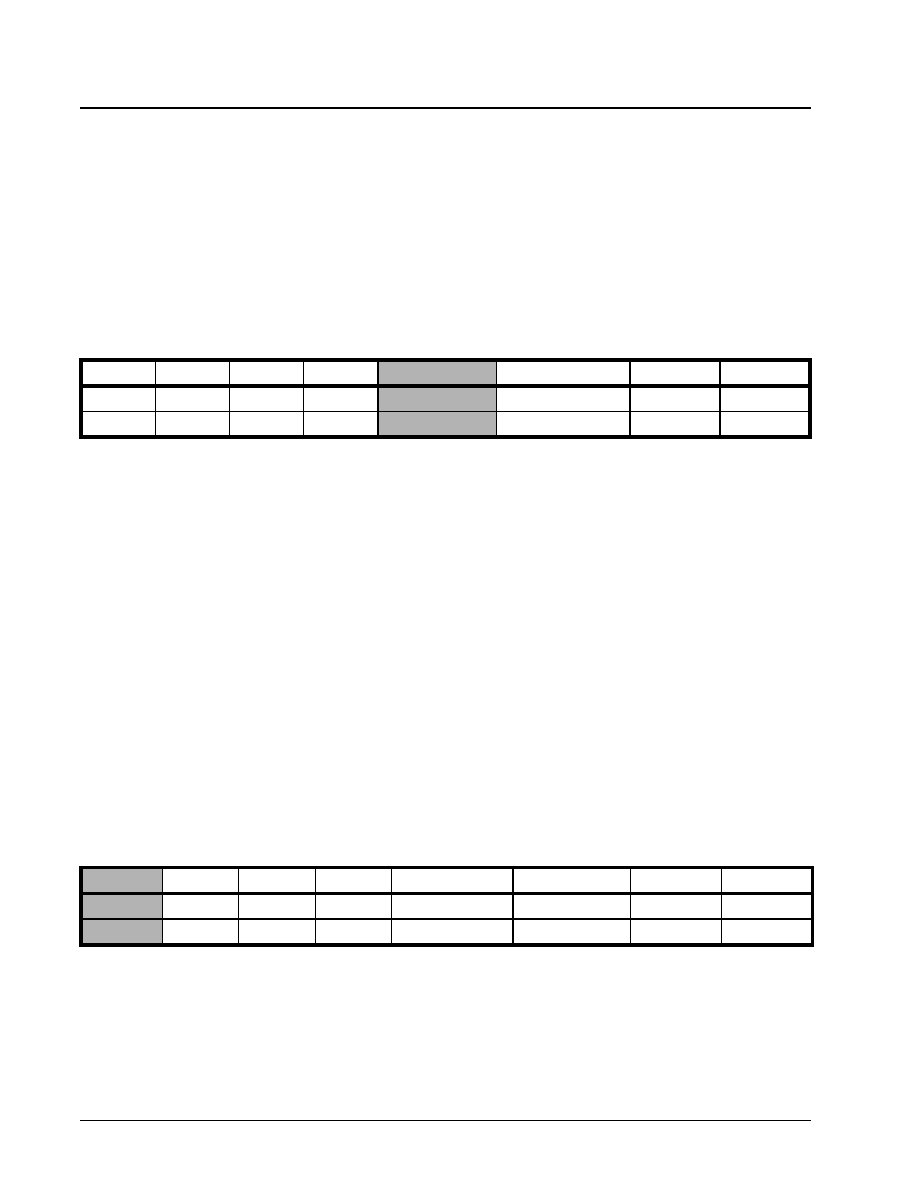

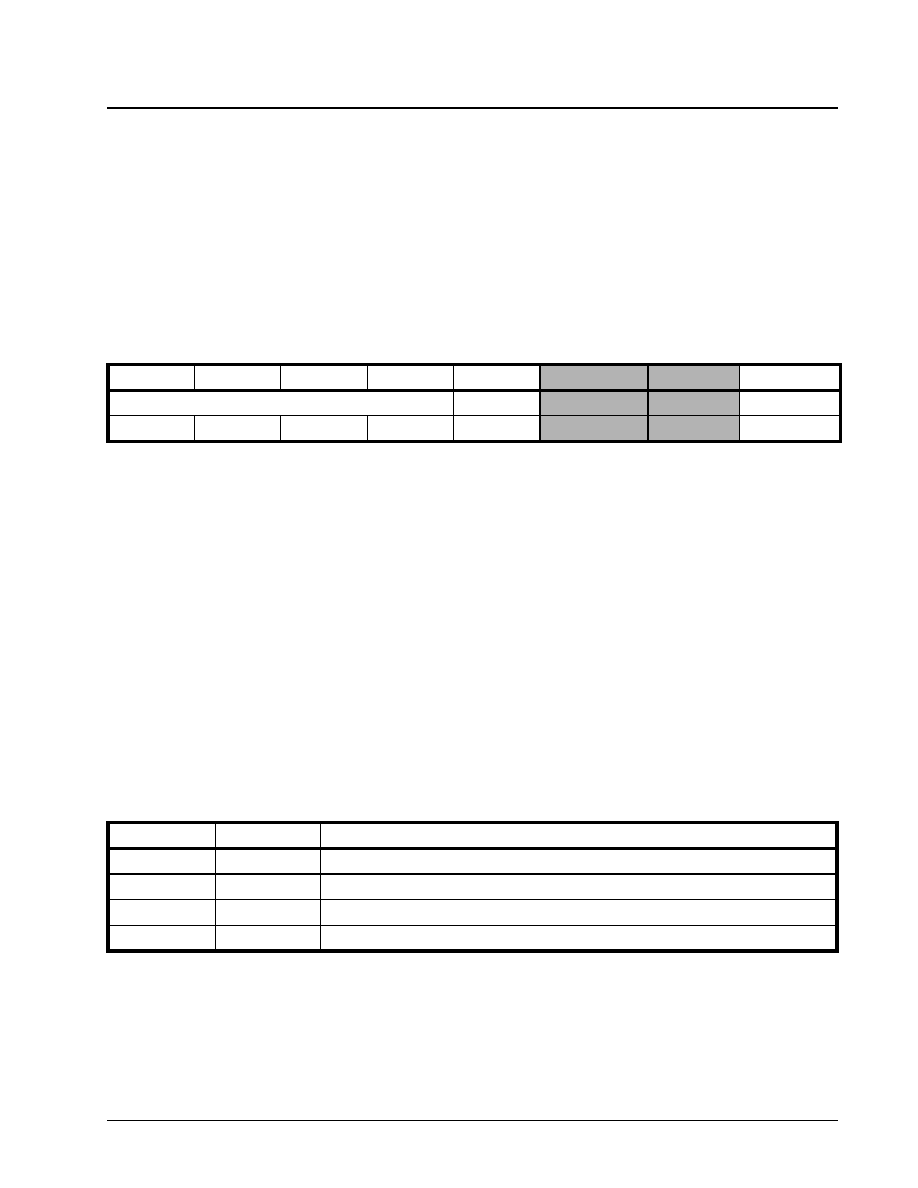

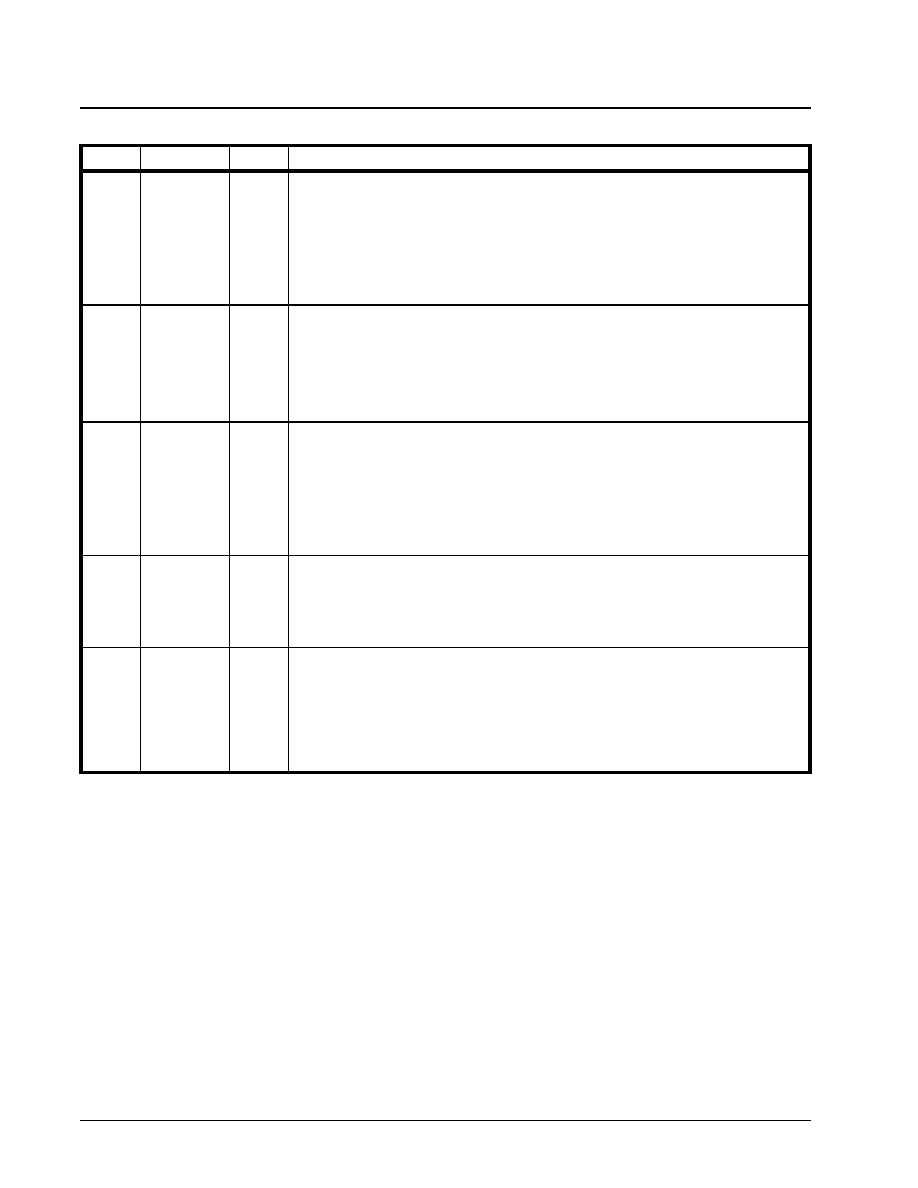

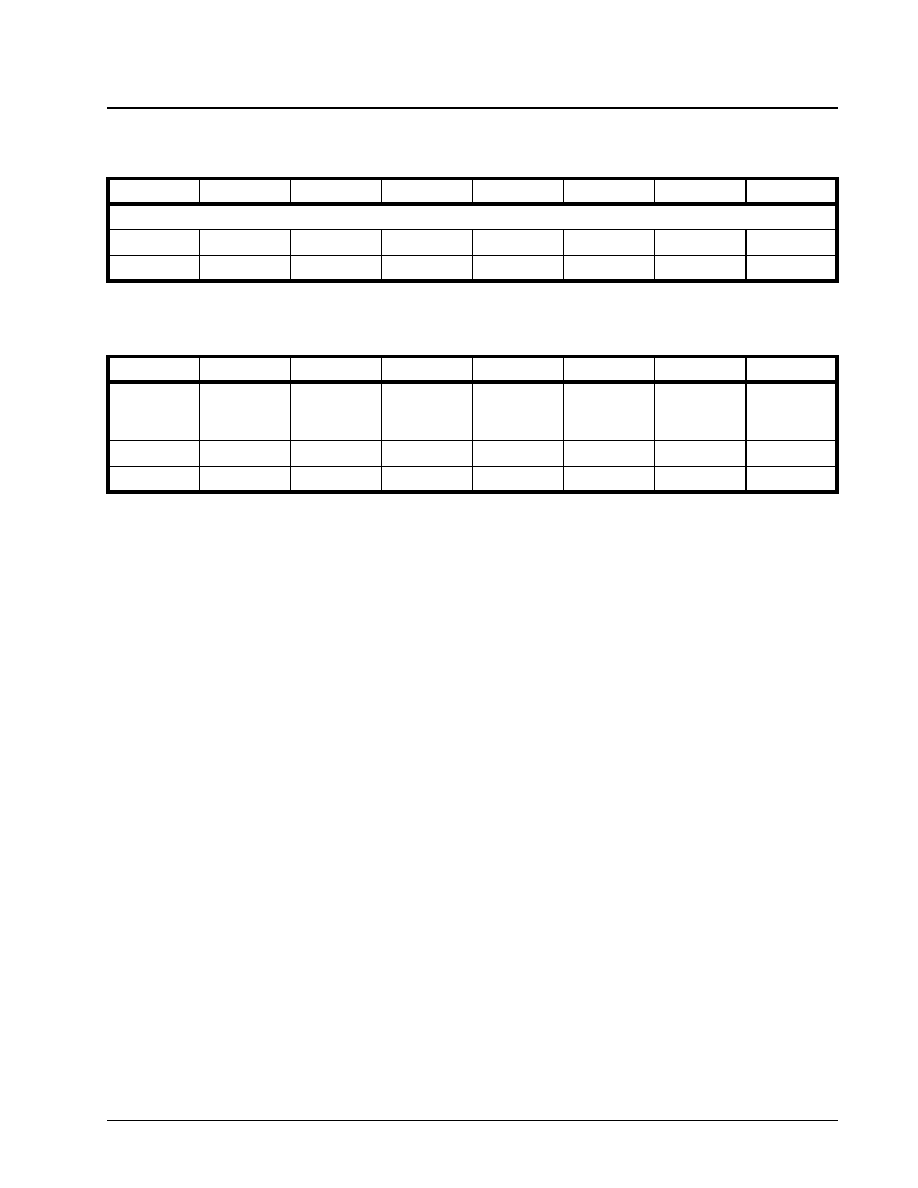

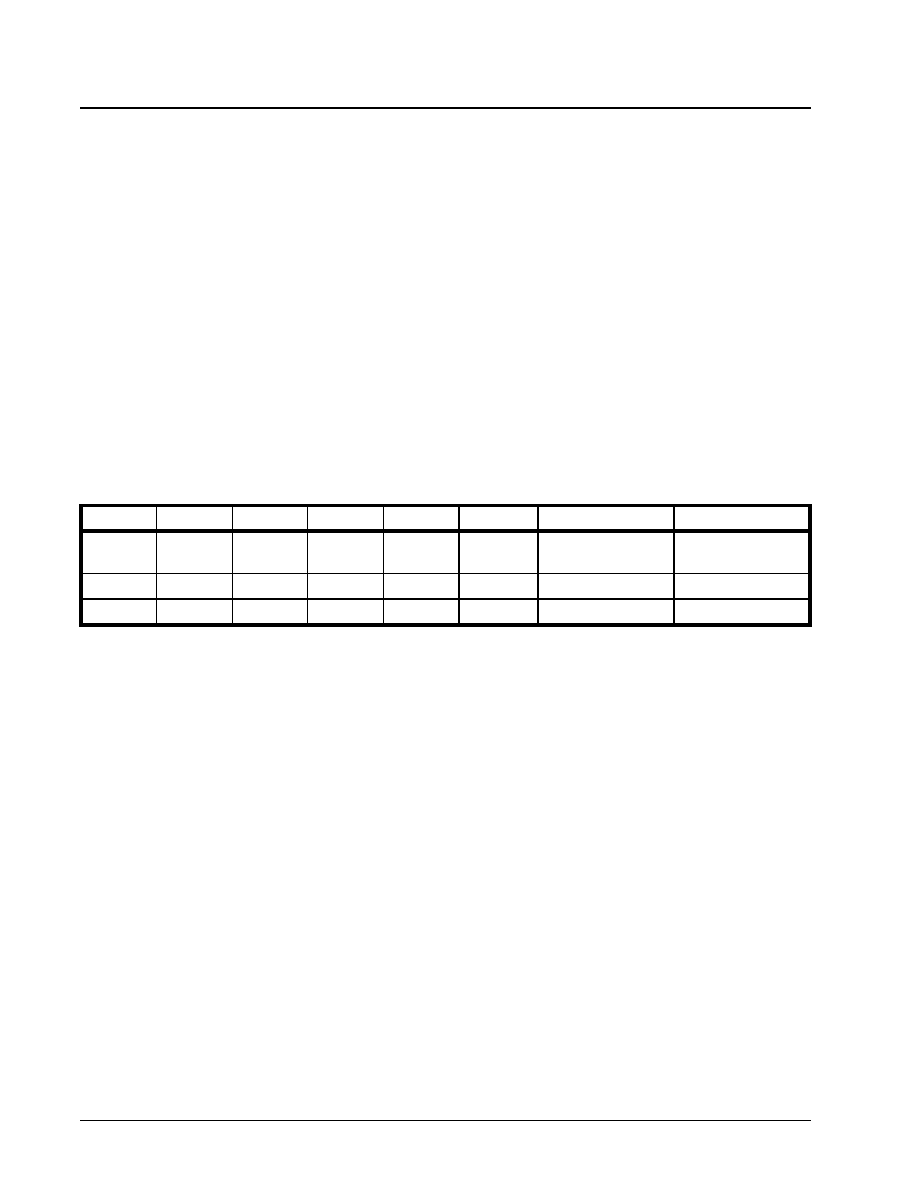

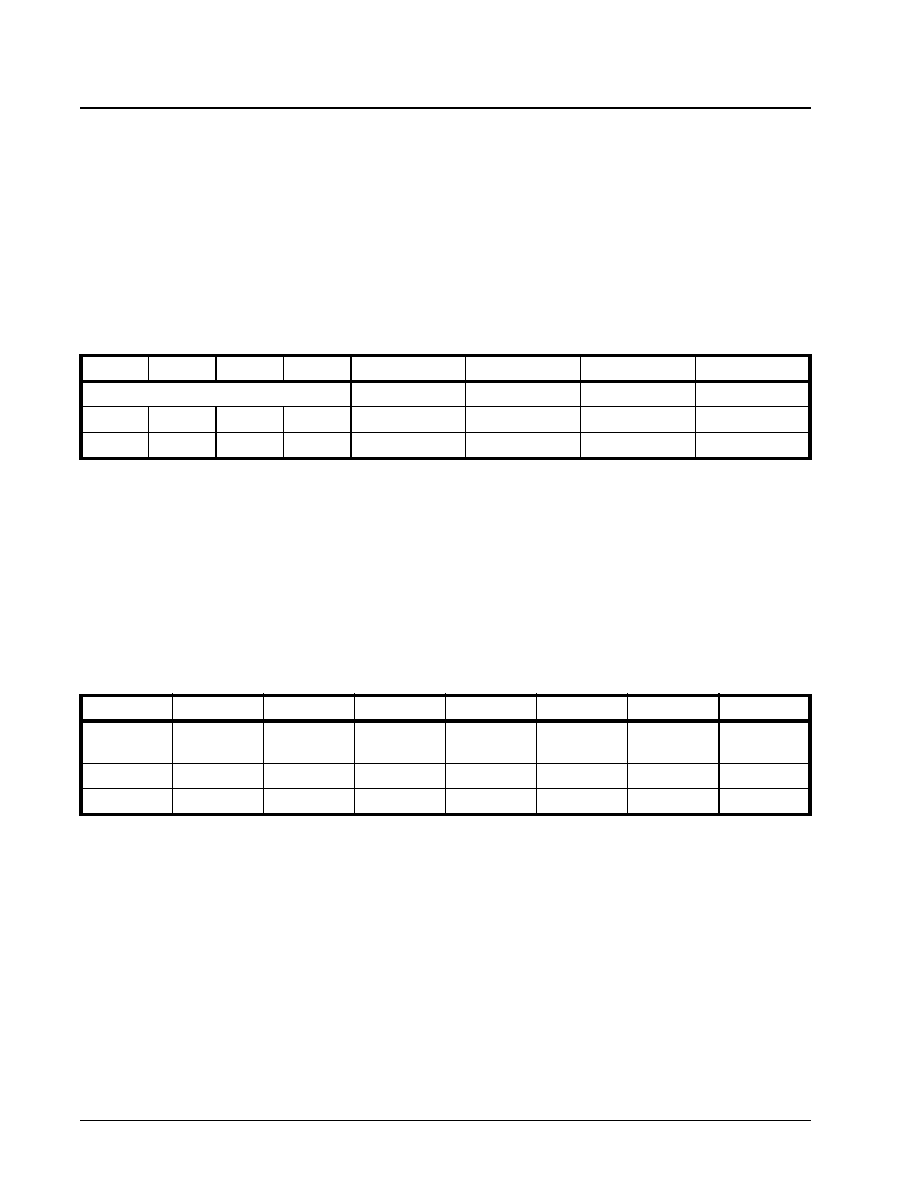

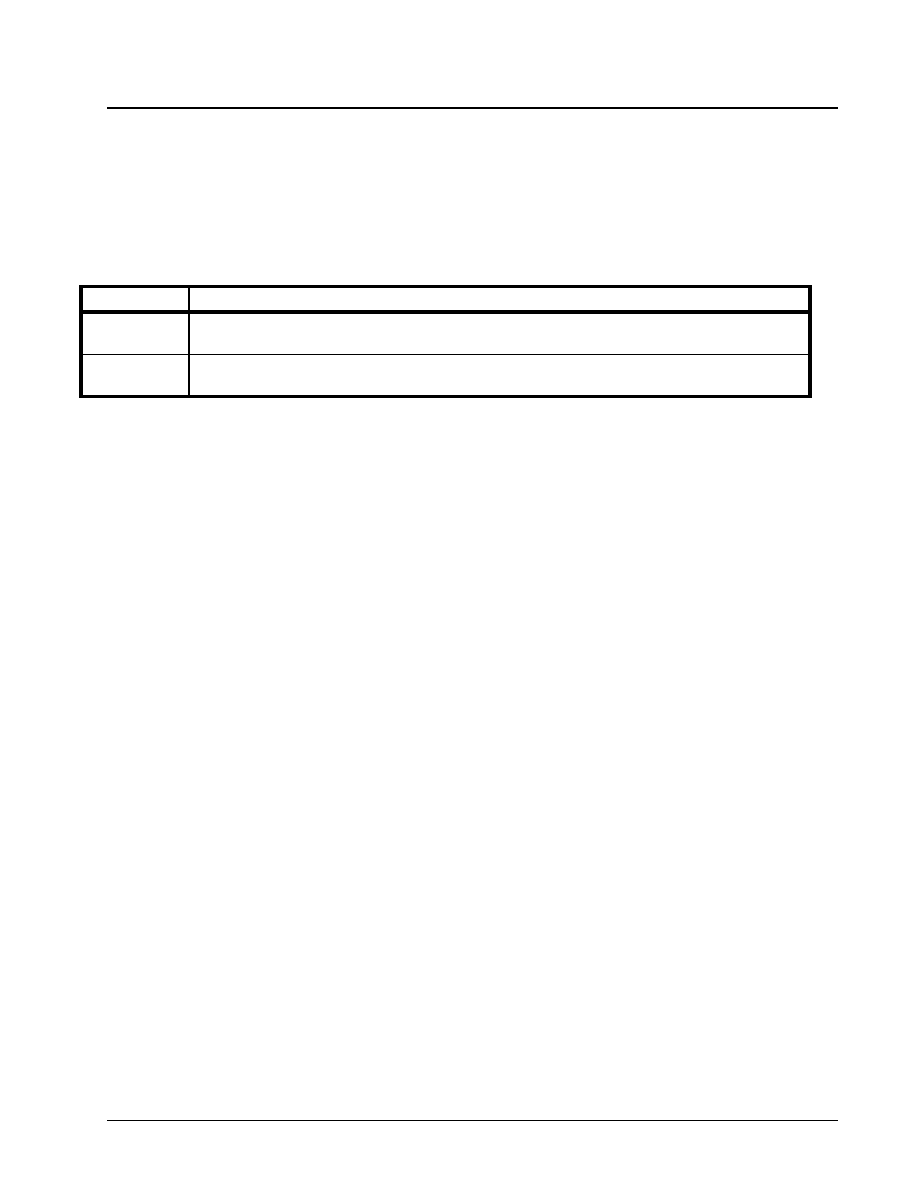

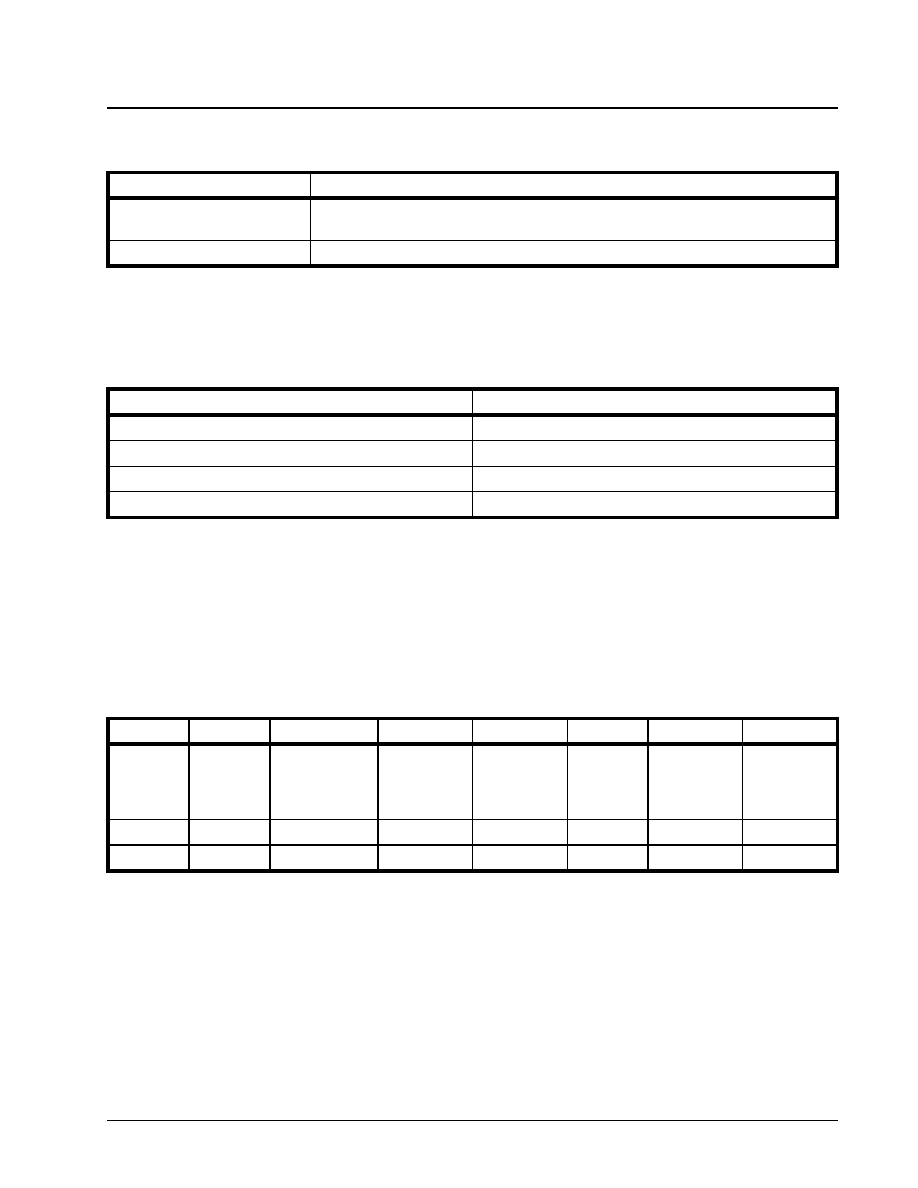

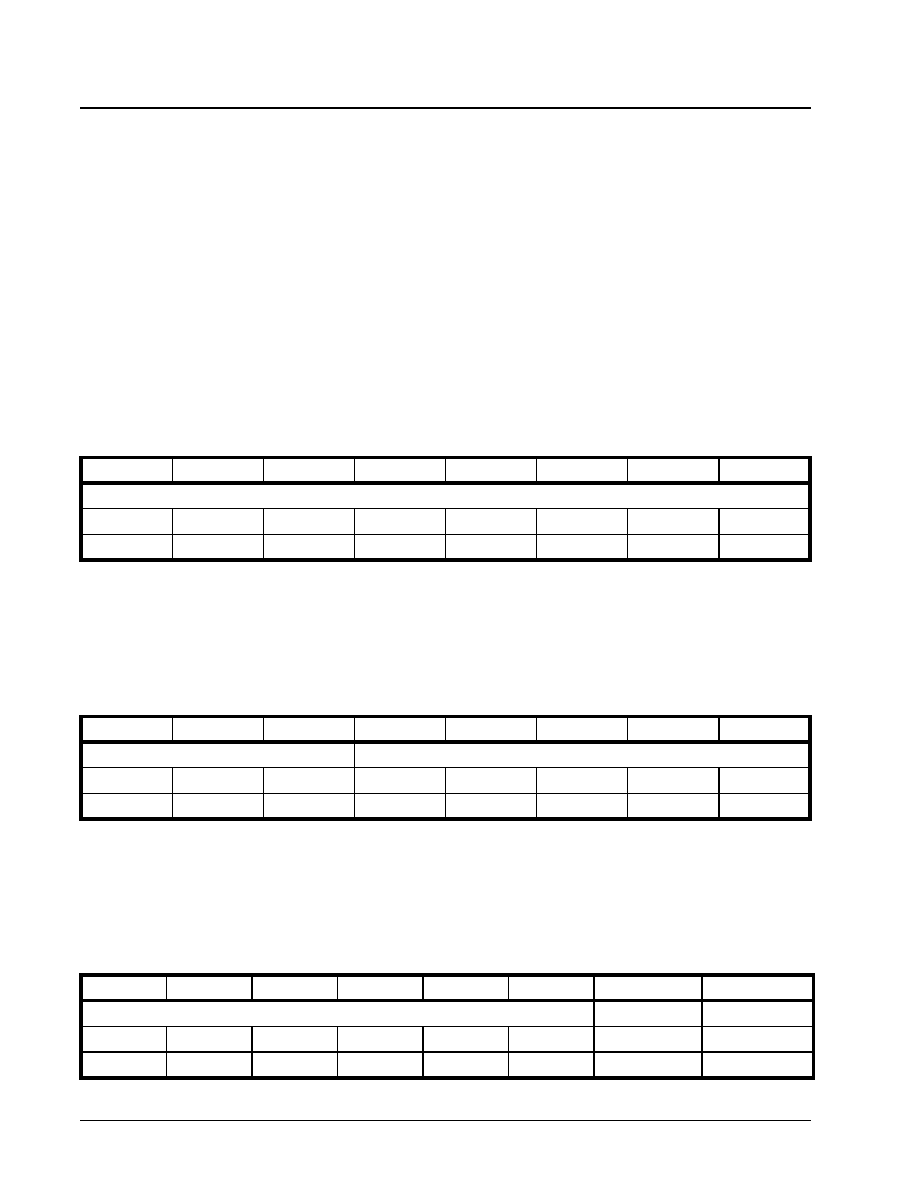

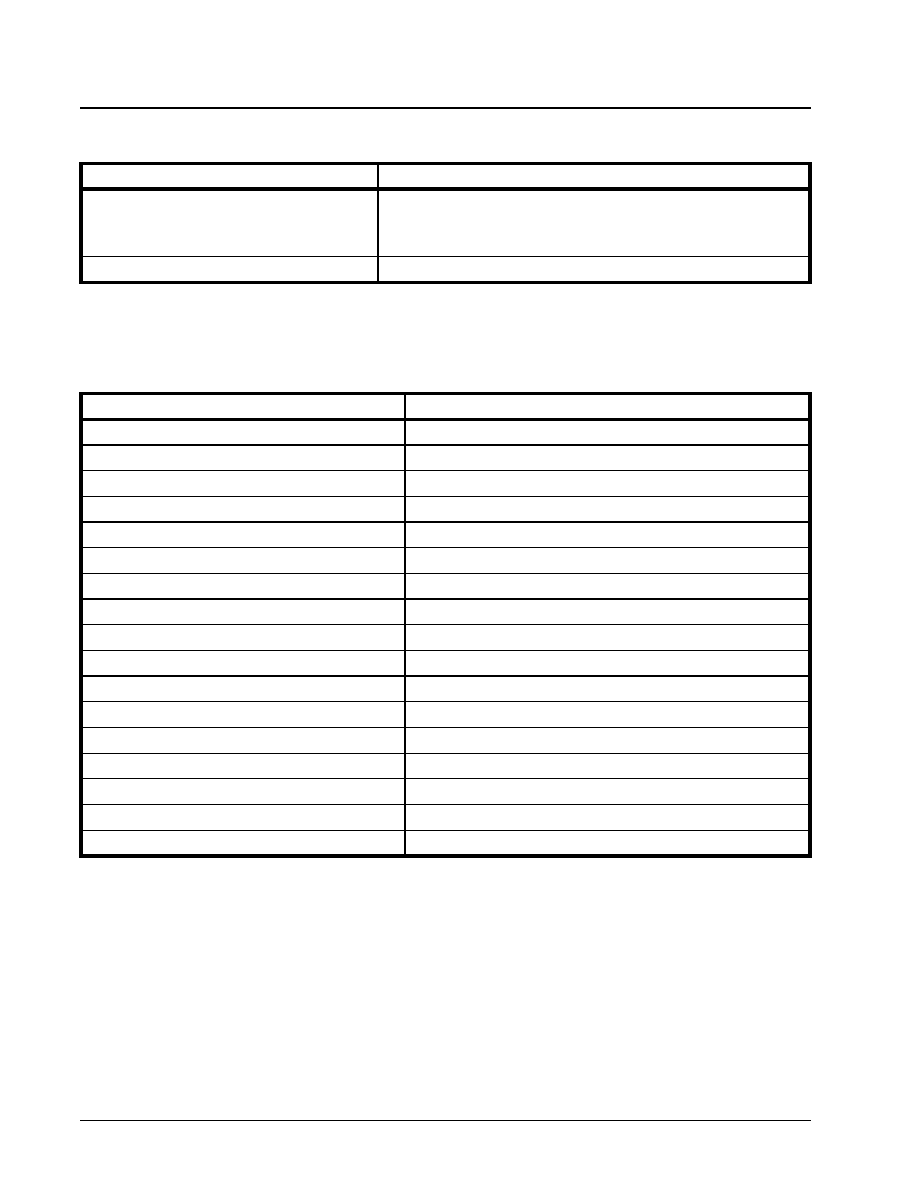

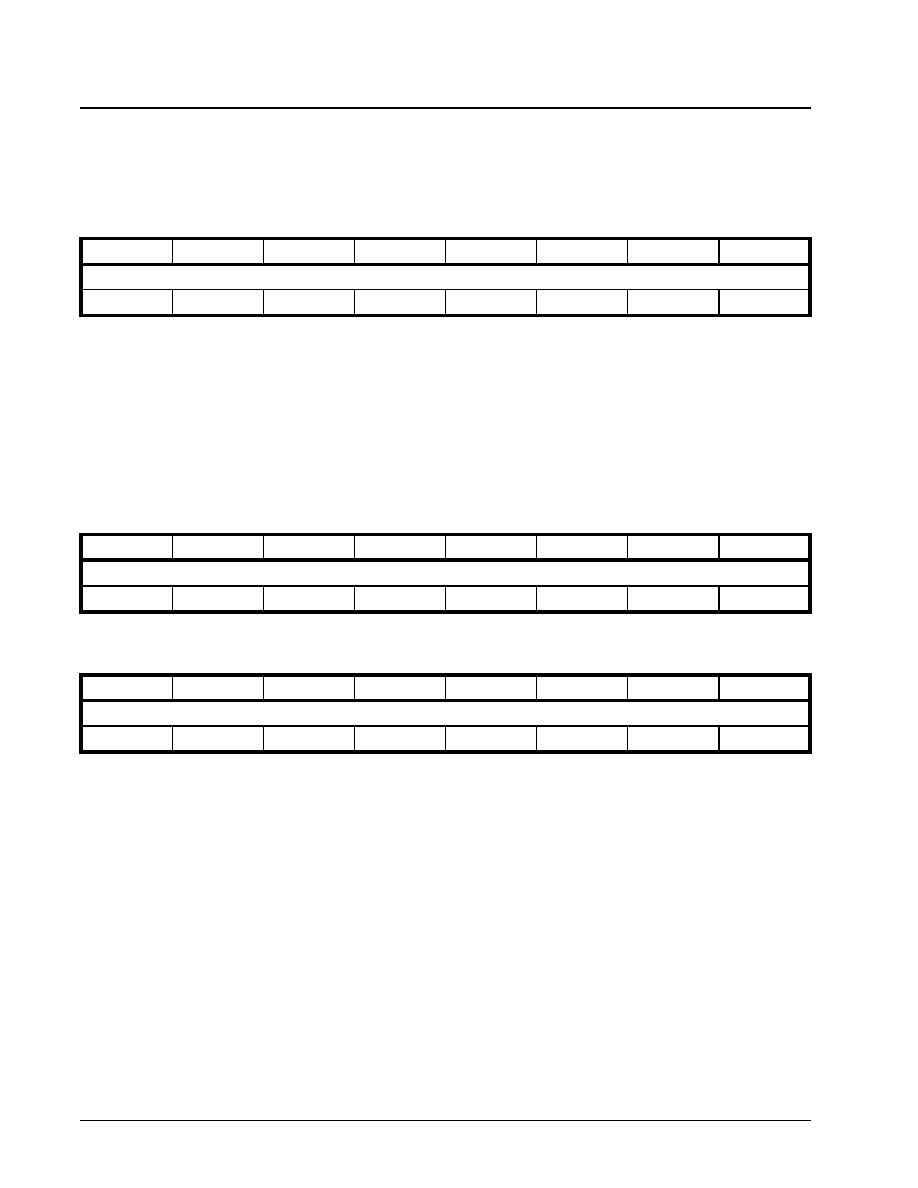

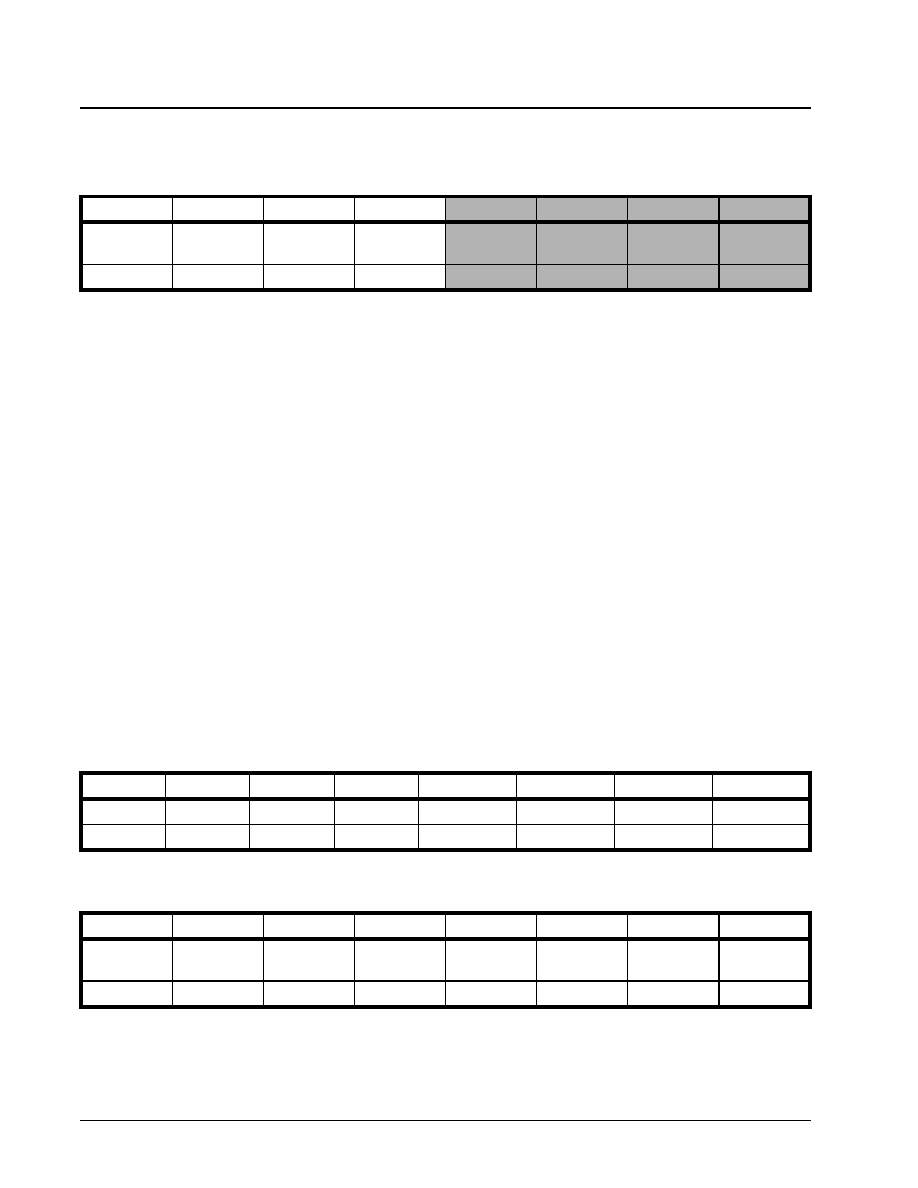

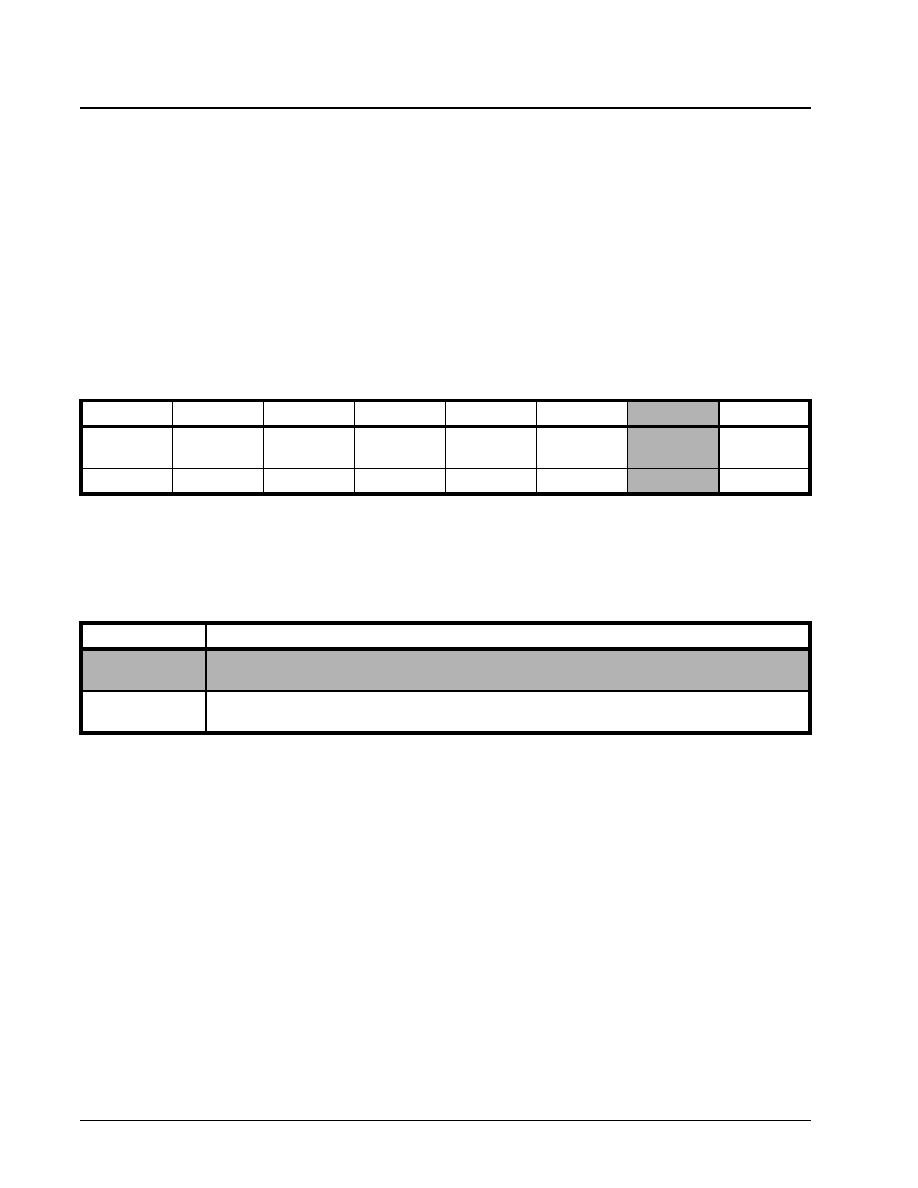

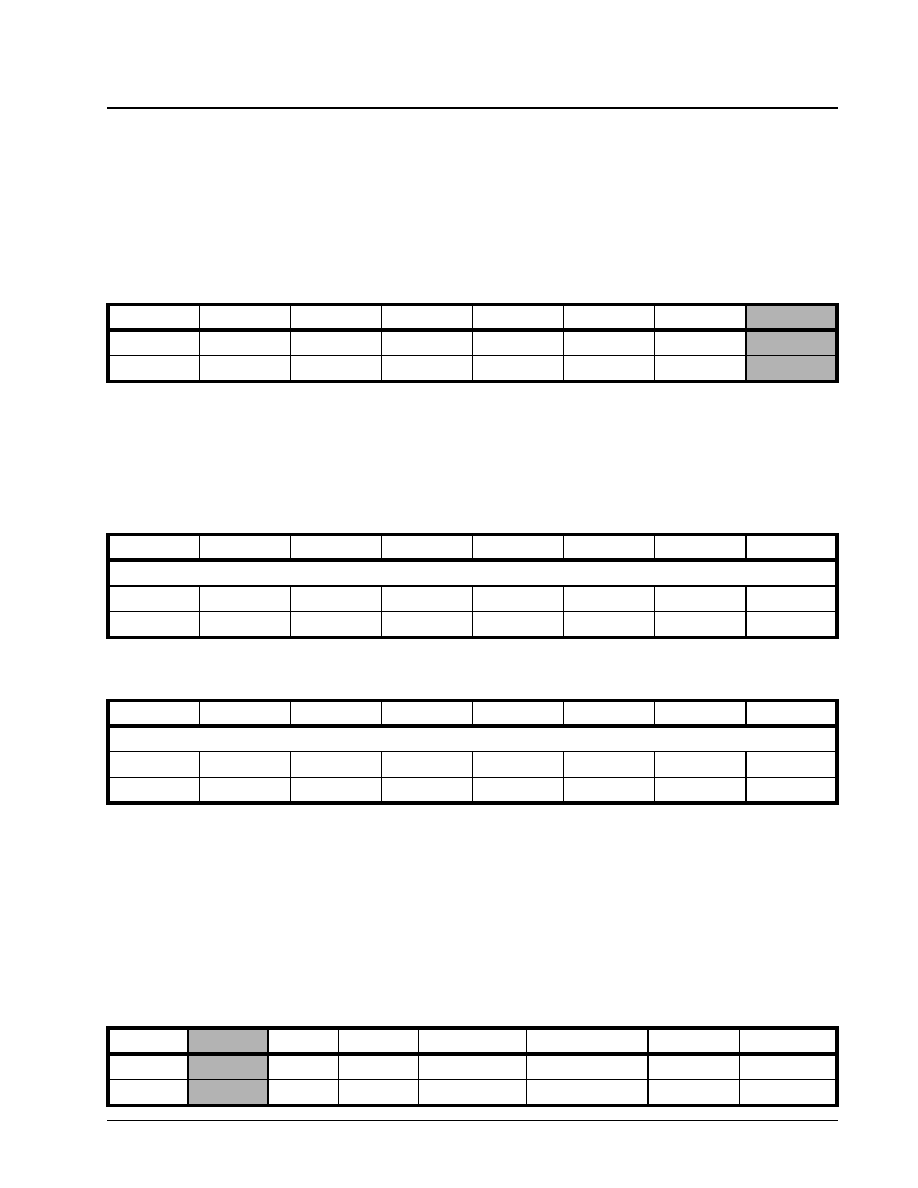

Signal Name

Function of Output Pin

REQB

Receive Equalizer By-Pass:

Setting this bit-field to "1" configures the XRT7300 device to shut off its internal Receive Equalizer.

Setting this bit-field to "0" configures the XRT7300 device to enable its internal Receive Equalizer.

TAOS

Transmit "All Ones" Pattern.

Setting this bit-field to "1" configures the XRT7300 LIU IC to overwrite the DS3 data that is output via

the TxPOS and TxNEG outputs, and transmit an "All Ones" pattern onto the line.

Setting this bit-field to "0" configures the XRT7300 LIU IC to transmit data, as is applied to it via the

TPDATA and TNDATA input pins.

ENCODIS

B3ZS Encoder Disable/Enable Select.

Setting this bit-field to "1" disables the B3ZS Encoder, within the XRT7300 device.

Setting this bit-field to "0" enables the B3ZS Decoder within the XRT7300 device.

TxLev

Transmit Output Signal Line Build Out Select.

Setting this bit-field to "1" disables the Transmit Line Build Out circuitry within the XRT7300 device. In

this case, the XRT7300 will generate an "unshaped" square wave signal out onto the line (via the TTIP

and TRING output pins).

Note: In order to configure the XRT7300 device to generate a line signal that complies with the Transmit

Output Pulse Template Requirements (per GR-499-CORE), this setting is advised if the cable length

between the Transmit Output of the XRT7300 device and the Cross-Connect is greater than 225 feet.

Setting this bit-field to "0" enables the Transmit Line Build Out circuitry within the XRT7300 device. In

this case, the XRT7300 device will generate a "shaped" square wave out onto the line (via the TTIP and

TRING output pins).

Note: In order to configure the XRT7300 device to generate a line signal that complies with the Transmit

Output Pulse Template Requirements (per GR-499-CORE), this setting is advised if the cable length

between the Transmit Output of the XRT7300 device and the Cross-Connect is less than 225 feet.

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

6

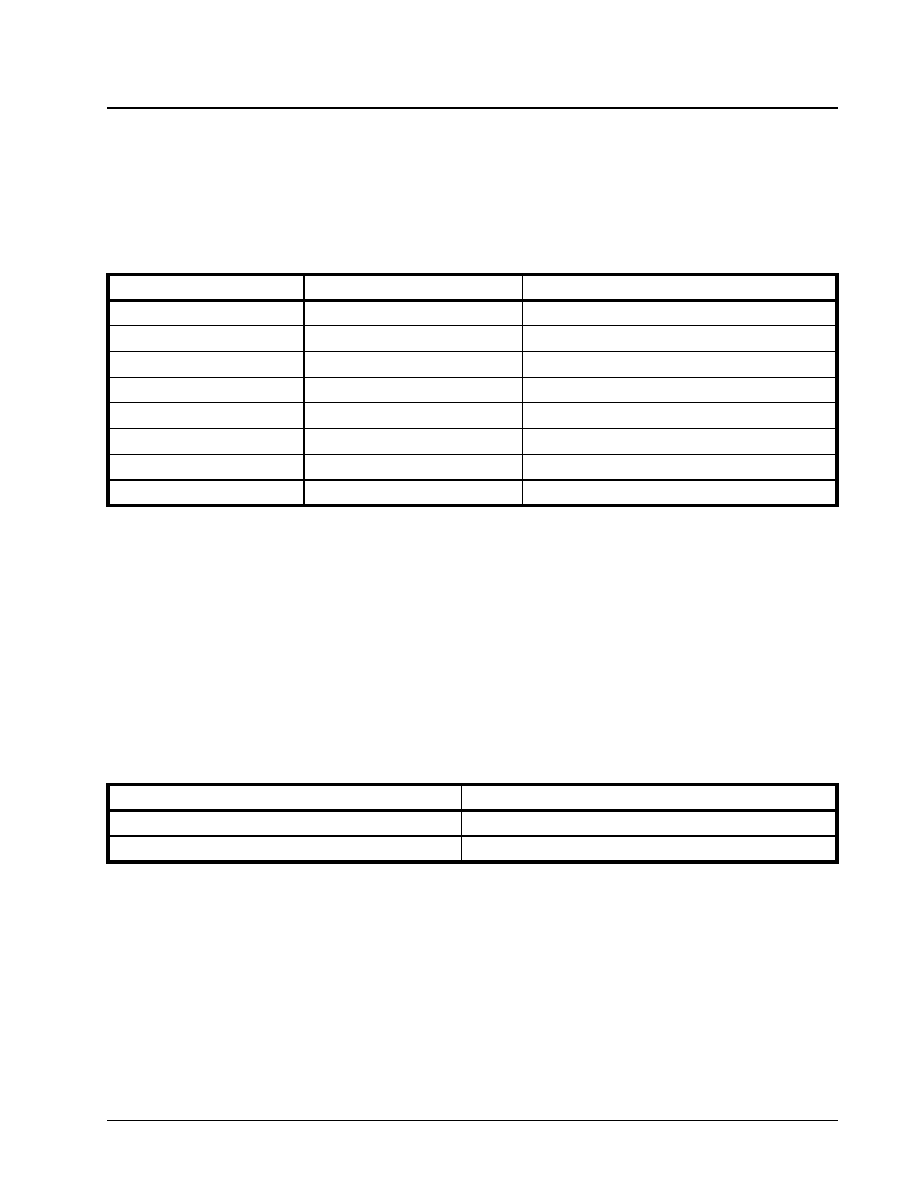

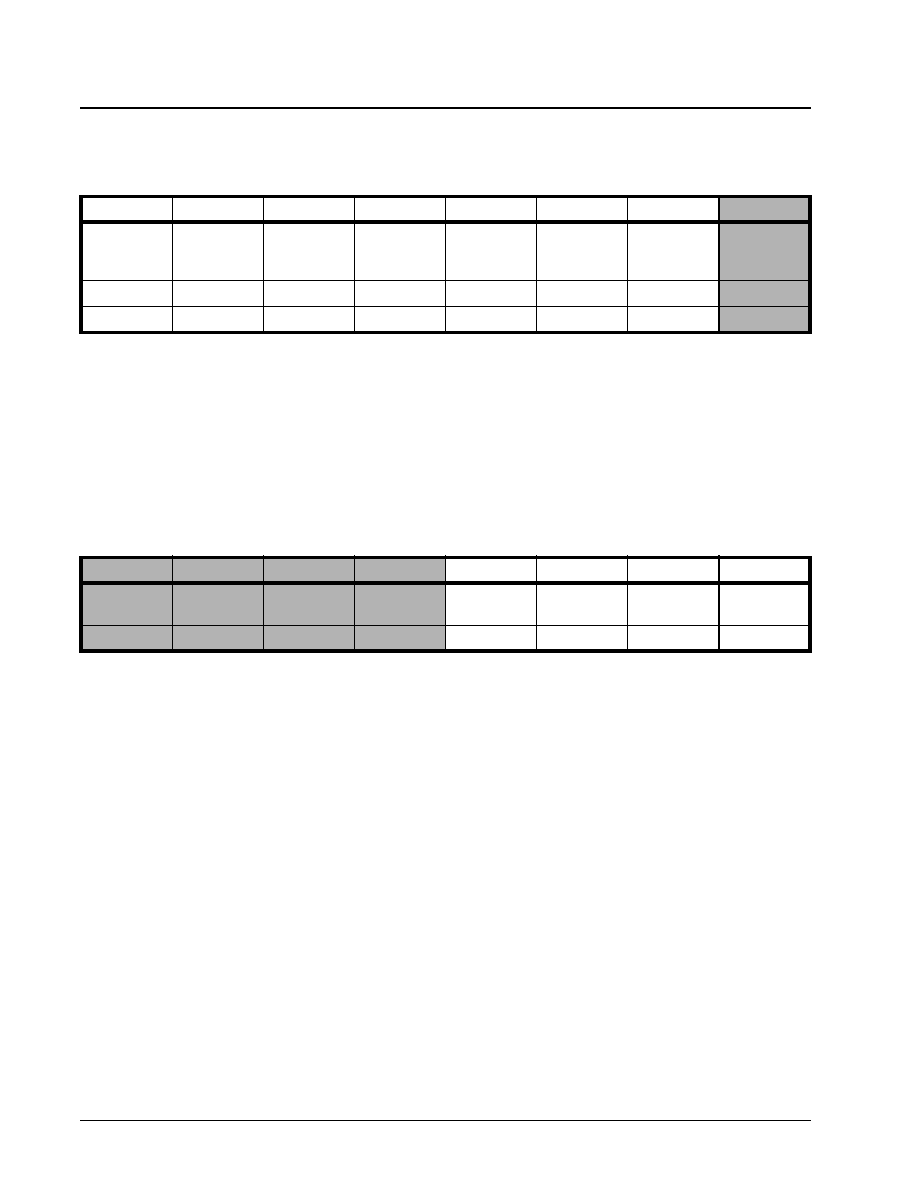

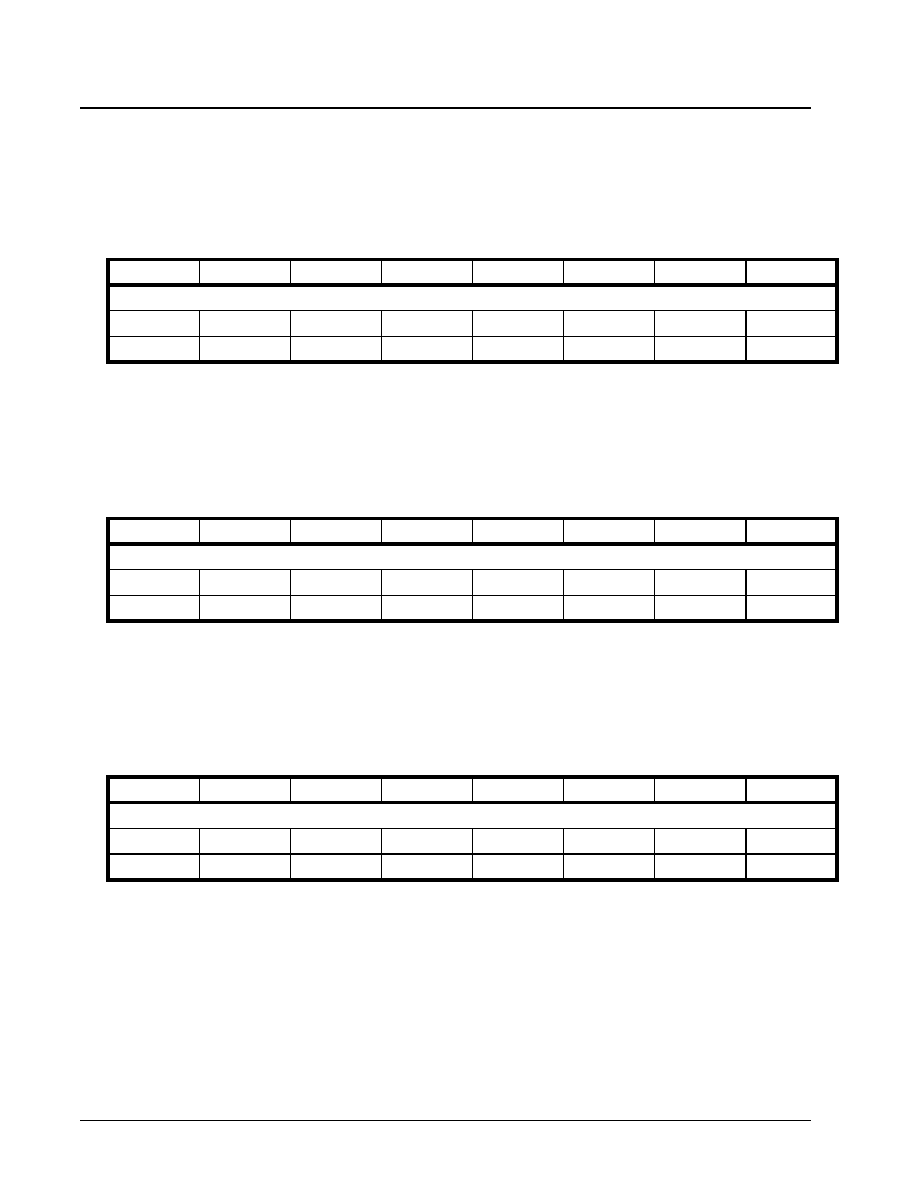

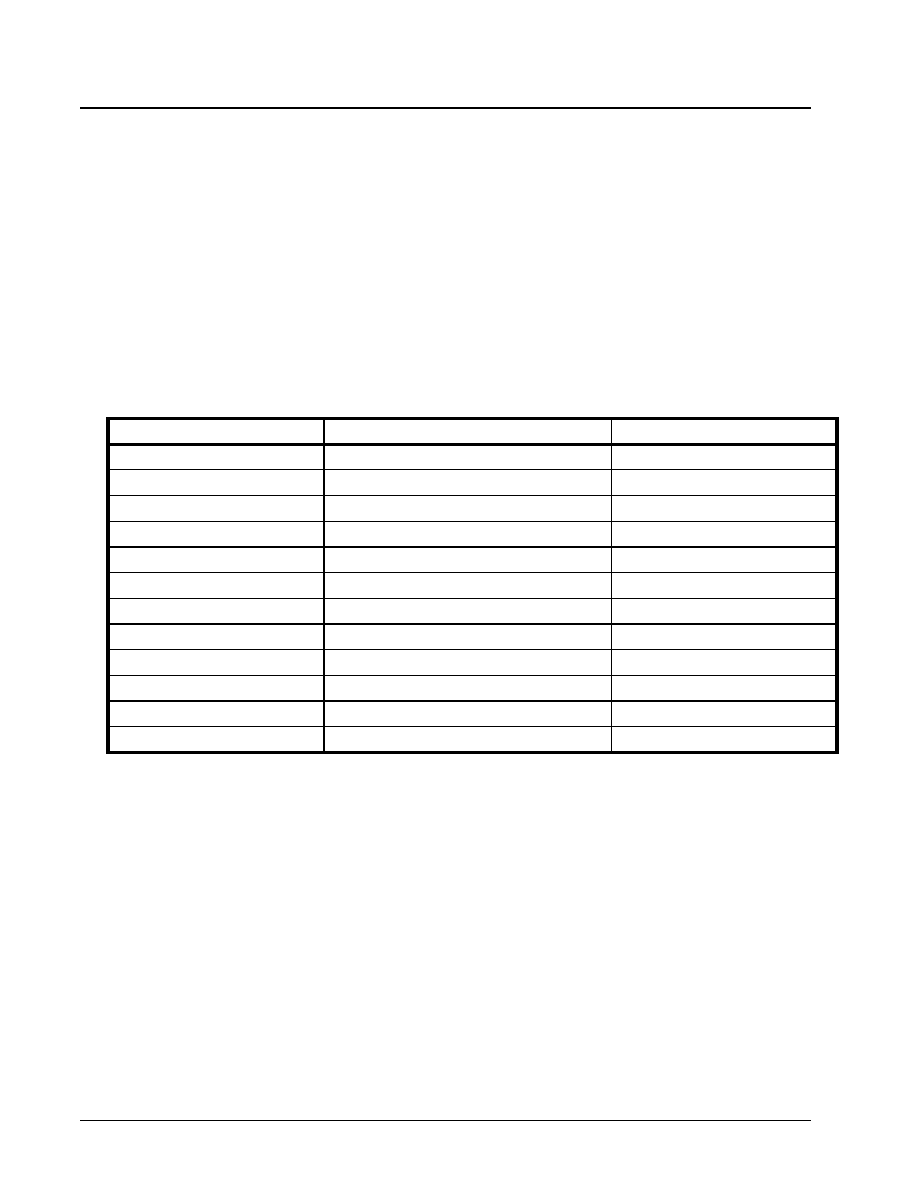

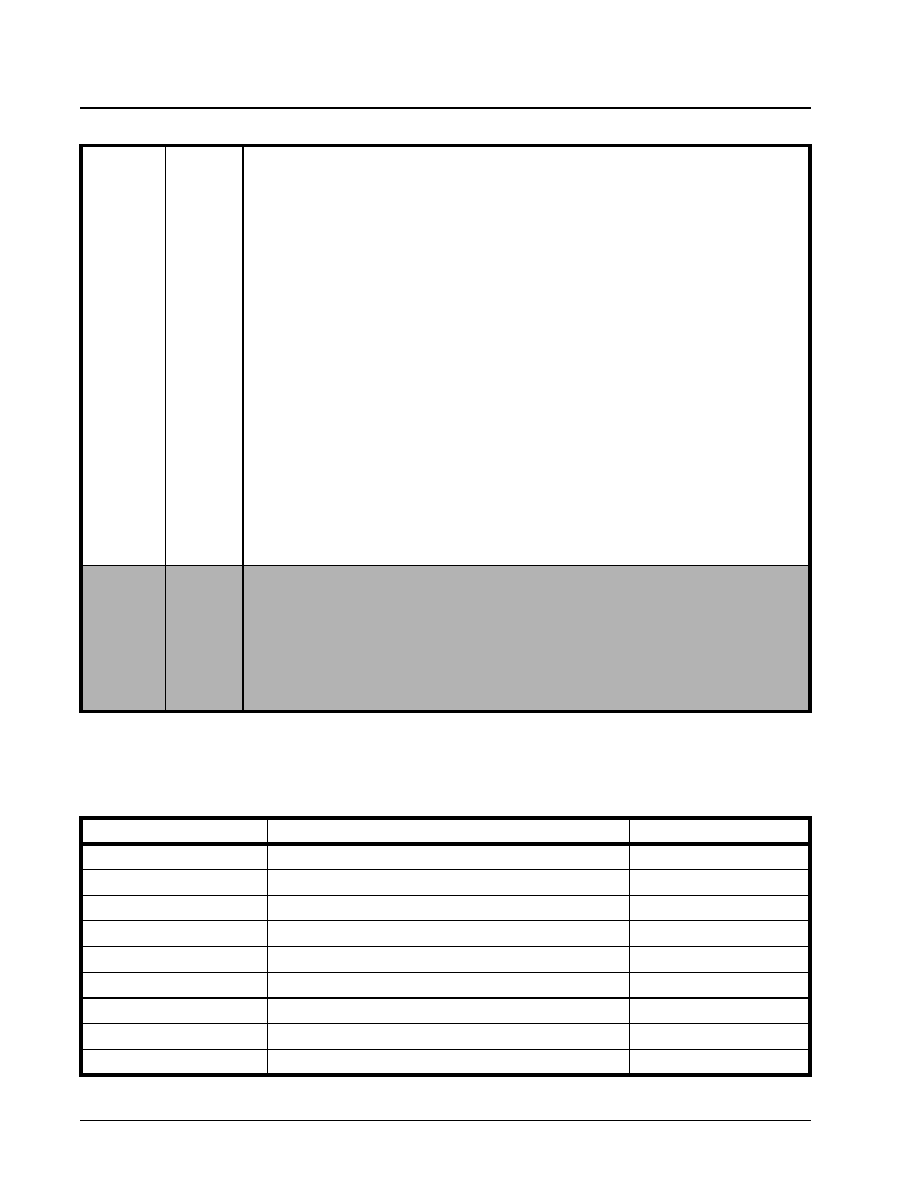

∑

The On-Chip Line Interface Scan Register allows

the user to monitor the state of 3 input pins. The

function of these input pins, when asserted, are

tabulated below.

FEATURES

TRANSMIT AND RECEIVE SECTIONS

UTOPIA I

NTERFACE

B

LOCKS

∑

Compliant with UTOPIA Level 2 Interface Specifi-

cation (e.g., supports Single-PHY or Multi-PHY

operation).

∑

8-bit or 16-bit wide UTOPIA Data Bus operation in

the Transmit and Receive Directions.

∑

The UTOPIA Data Bus runs at clock rates of 25

MHz, 33 MHz and 50 MHz

∑

Supports Octet-Level and Cell-Level Handshaking

between the UNI and the ATM Layer processor.

∑

The Transmit UTOPIA Interface block performs par-

ity checking of ATM cell data that is written into it,

by the ATM Layer processor. Will optionally discard

errored cells.

∑

Contains on-chip 16 cell FIFO in the Transmit

Direction (TxFIFO)

∑

The TxFIFO can be configured to operate with

depths of 4, 8, 12 or 16 cells

∑ Contains on-chip 4 cell FIFO in the Receive

Direction (RxFIFO)

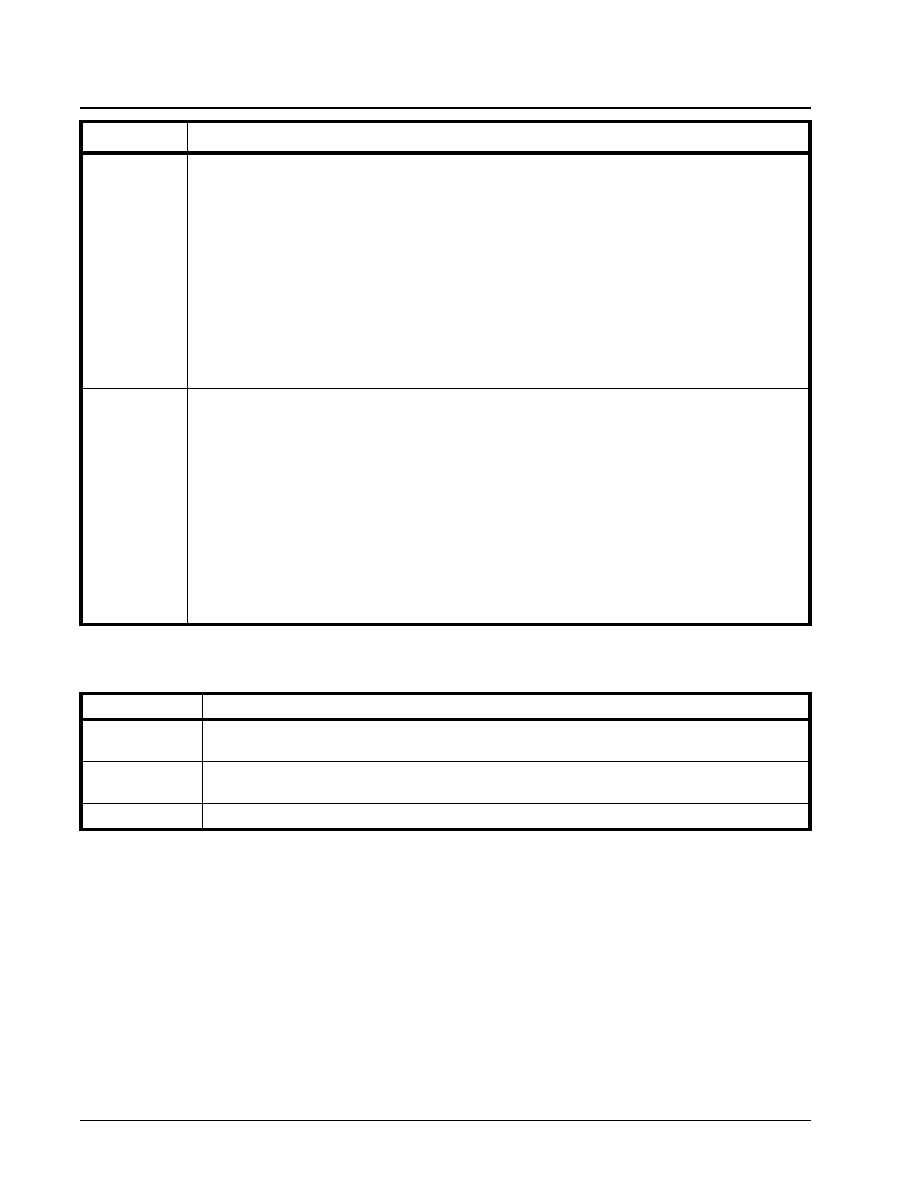

RLOOP

Remote Loop-Back Mode Select:

This bit-field, along with LLOOP can be used to configure the XRT7300 device into one of four different

loop-back modes.

Setting RLOOP to "1" (with LLOOP = 0) configures the XRT7300 device to operate in the Remote

Loop-Back Mode.

Setting RLOOP to "1" (with LLOOP = 1) configures the XRT7300 device to operate in the "Digital Local

Loop-Back" Mode.

Setting RLOOP to "0" (with LLOOP = 1) configures the XRT7300 device to operate in the "Analog Local

Loop-Back" Mode.

Setting RLOOP to "0" (with LLOOP = 0) configures the XRT7300 device to operate in the "Normal"

(No-Loop-back) Mode.

LLOOP

Local Loop-Back Mode Select:

This bit-field along with RLOOP can be used to configure the XRT7300 device into one of four different

loop-back modes.

Setting LLOOP to "1" (with RLOOP = 0) configures the XRT7300 device to operate in the "Analog Local

Loop-back" Mode.

Setting LLOOP to "1" (with RLOOP = 1) configures the XRT7300 device to operate in the "Digital Local

Loop-back" Mode.

Setting LLOOP to "0" (with RLOOP = 0) configures the XRT7300 device to operate in the "Normal"

(No-Loop-back) Mode.

Setting LLOOP to "0" (with RLOOP = 1) configures the XRT7300 device to operate in the "Remote

Loop-back" Mode.

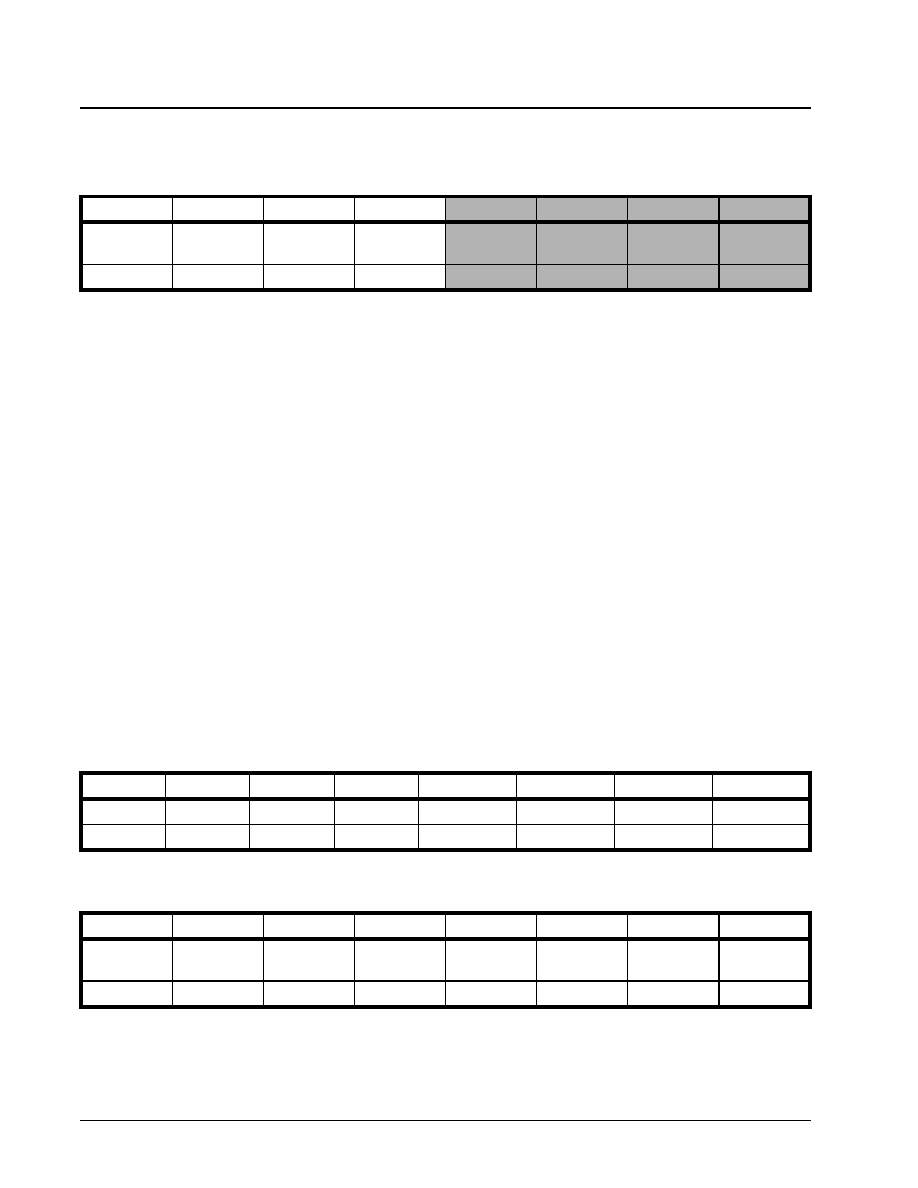

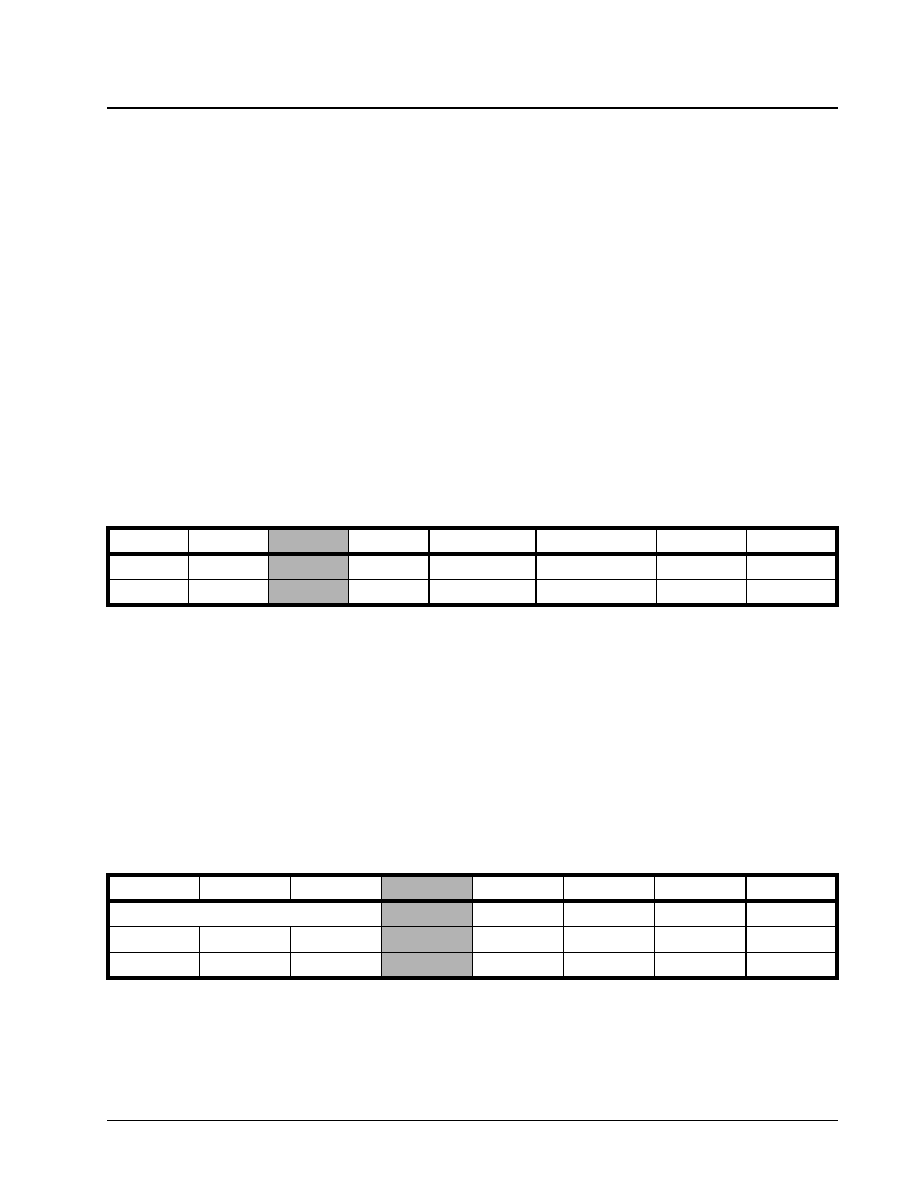

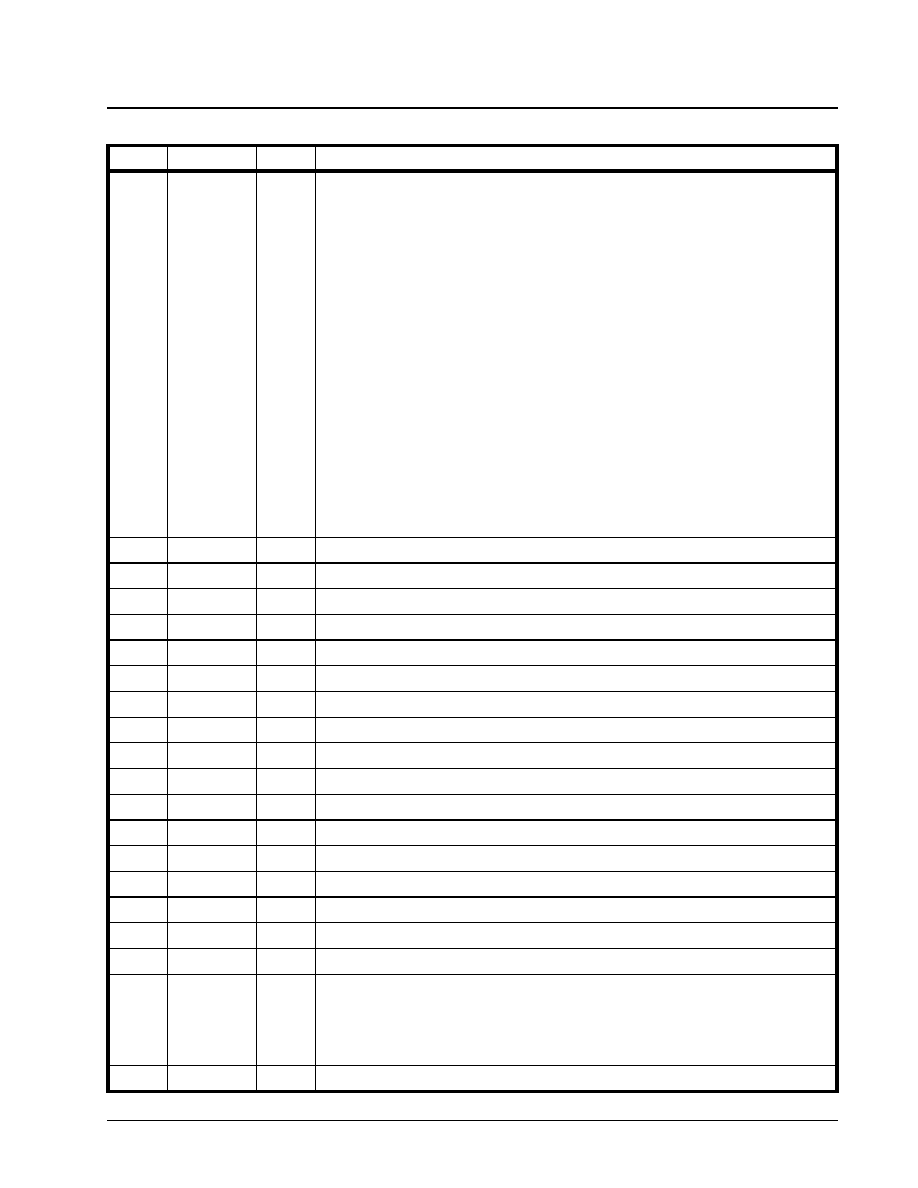

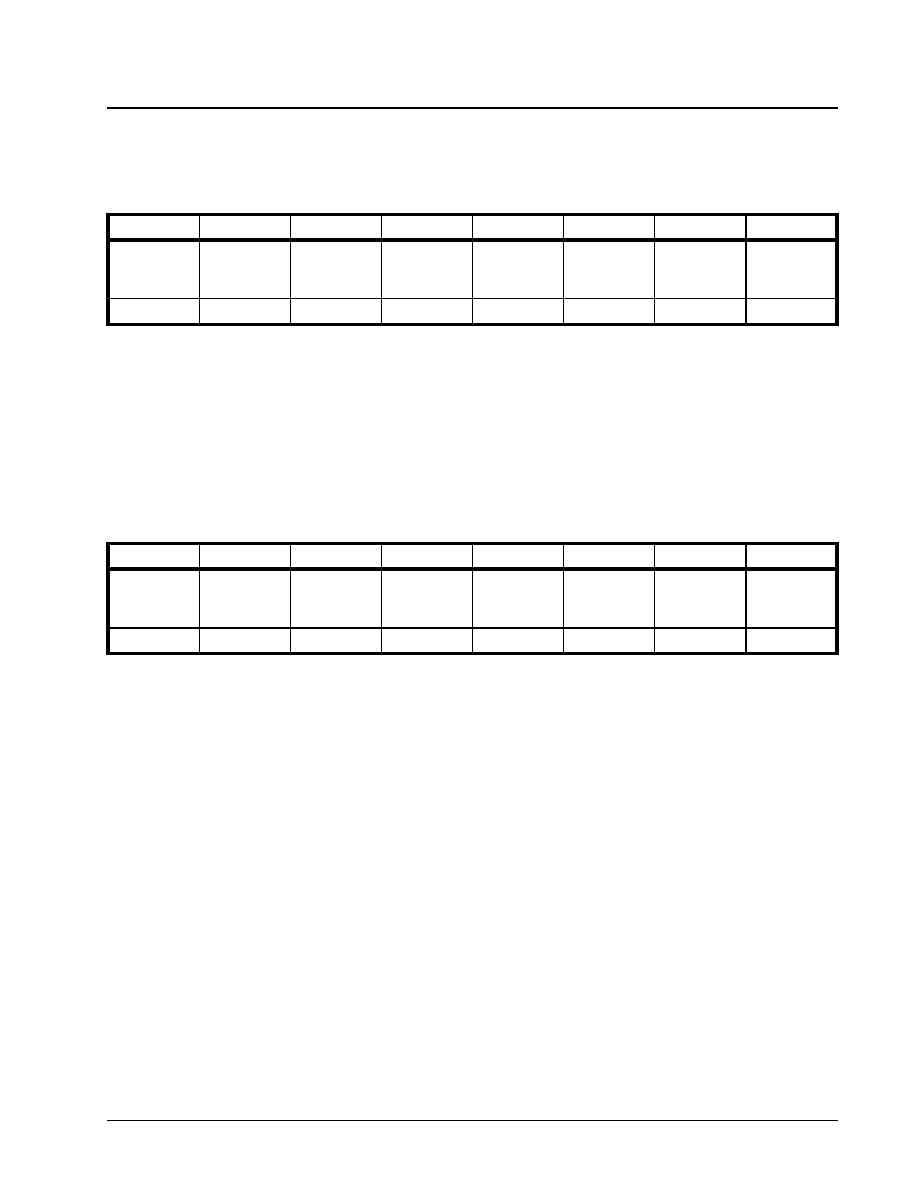

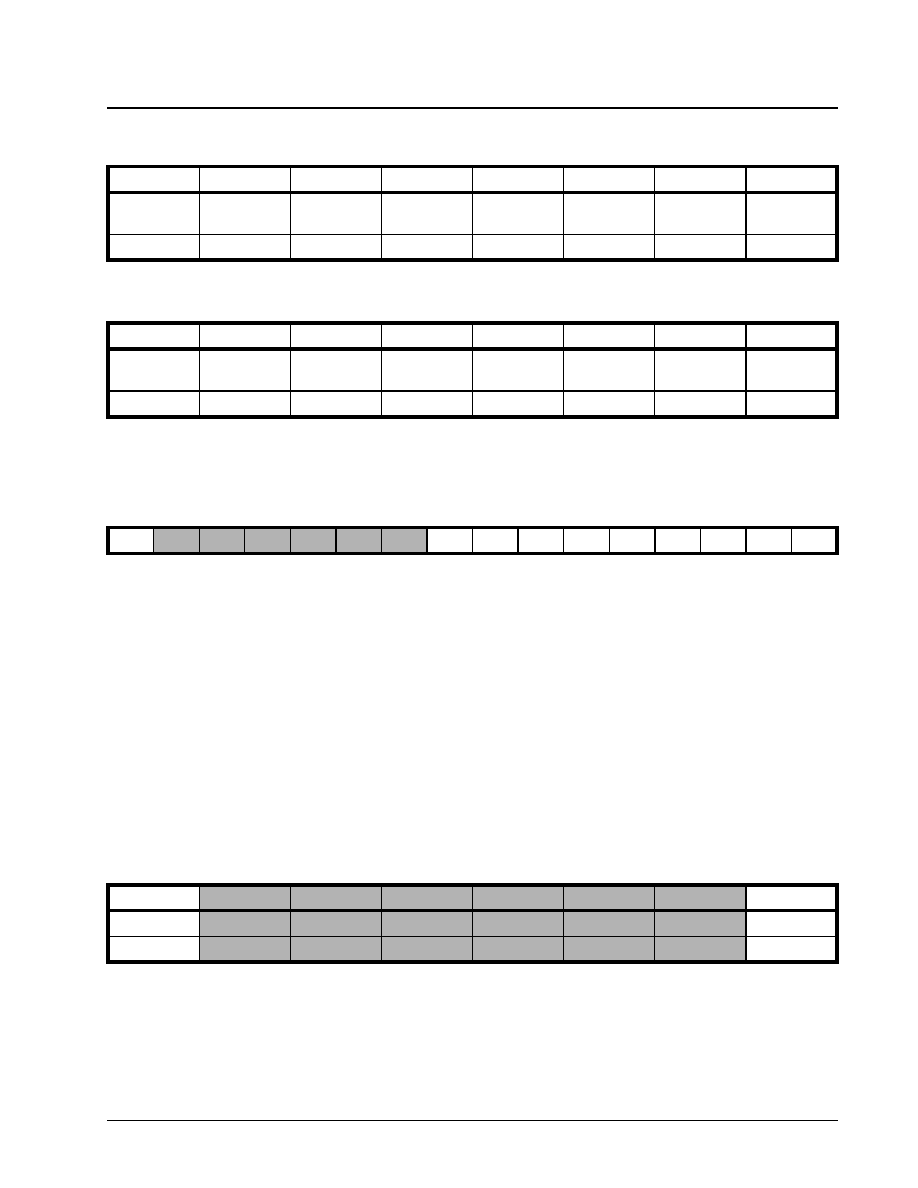

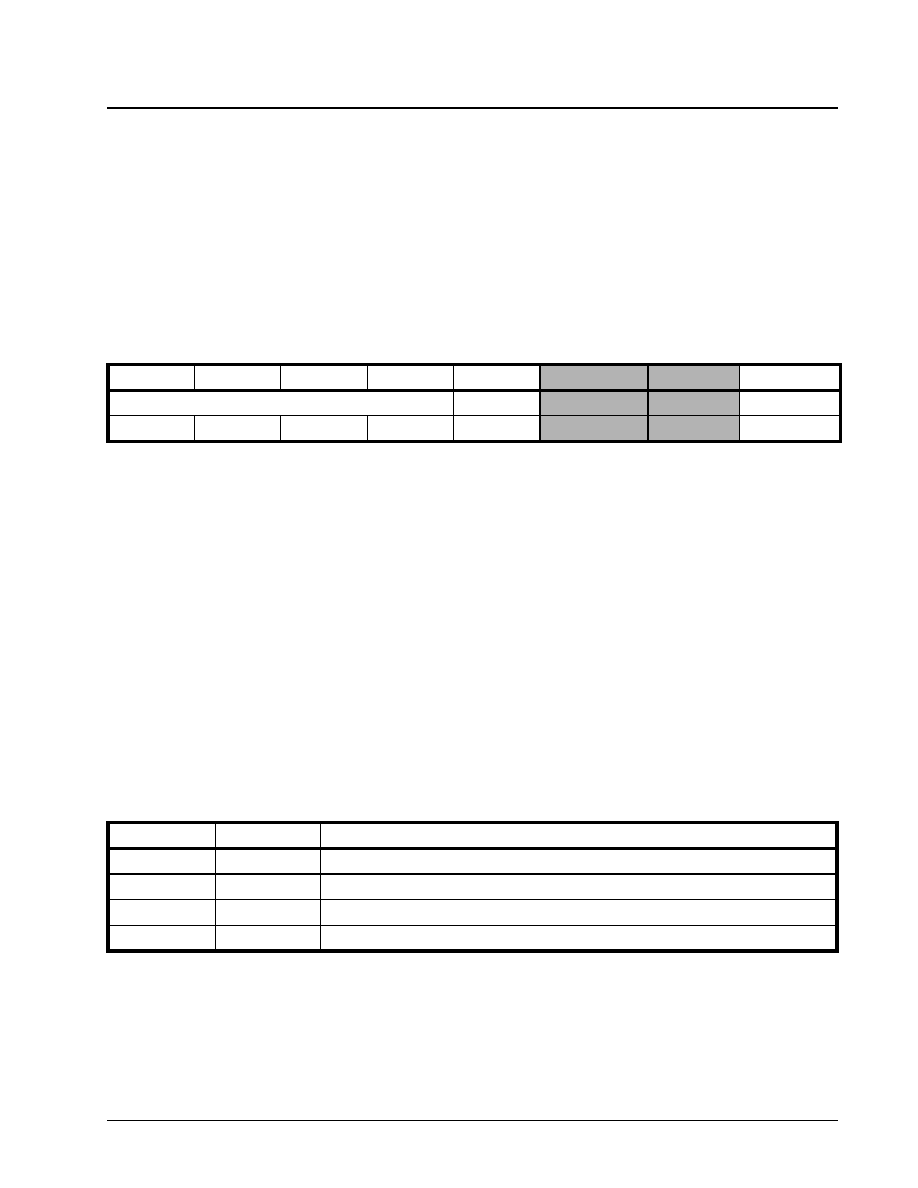

Signal Name

Function of Output Pin

S

IGNAL

N

AME

F

UNCTION

OF

I

NPUT

P

IN

IF

ASSERTED

DMO

Indicates that the "Drive Monitor" circuitry within the XRT7300 has not detected any bipolar signals

within the last 128 ± 32 bit periods.

RLOL

Indicates that the "Clock Recovery" circuit, within the XRT7300 has lost "lock" with the incoming DS3

line signal.

RLOS

Indicates that the XRT7300 device is declaring an LOS (Loss of Signal) Condition.

·Á

·Á

·Á

·Á

DS3 UNI FOR ATM

XRT7245

PRELIMINARY

REV. 1.03

7

T

RANSMIT

C

ELL

P

ROCESSOR

B

LOCK

∑

Optionally computes and inserts HEC byte into all

cells (user, OAM and Idle).

∑

Optionally scrambles the payload of each cell.

∑

Idle cells are automatically generated when no

user cells are available in the TxFIFO.

∑

UNI contains on-chip registers that support the

generation/transmission of default or custom Idle

cells.

∑

UNI contains the on-chip "Transmit OAM Cell" buffer

(54 bytes) that allows the user to write in and store

the contents of OAM cells, in preparation for trans-

mission.

∑

OAM cells are transmitted upon software command.

∑

Performs "Data Path Integrity" check on all incoming

cell data, originating from the ATM Layer processor.

∑ Provides a serial input port to allow the user to

insert the GFC (Generic Flow Control) field exter-

nally into the GFC nibble field of an outbound (e.g.,

Transmit direction) valid ATM Cell.

R

ECEIVE

C

ELL

P

ROCESSOR

B

LOCK

∑

Performs cell delineation on either "Direct Mapped"

ATM cell data or PLCP frames.

∑

Verifies the HEC bytes of incoming cells and cor-

rects most cells with single bit errors. Cells with

multi-bit errors are detected and are optionally dis-

carded.

∑

(Optionally) Performs filtering of Idle Cells.

∑

(Optionally) Performs filtering of User and OAM cells.

∑

UNI contains on-chip buffer space ("Receive OAM

Cell" buffer) that allows for the reception and pro-

cessing of selected OAM cells.

∑

Optionally de-scrambles the payload of each cell.

∑

Provides a serial output port that allows the user to

read the GFC value of an incoming (e.g., Receive

direction) ATM Cell.

∑ Inserts the "Data Path Integrity Check" patterns in

all cells that are written to the RxFIFO.

T

RANSMIT

PLCP P

ROCESSOR

B

LOCK

∑

Can be disabled to support the "Direct Mapped"

ATM mode.

∑

Packs 12 ATM cells into each PLCP frame along

with various other overhead bytes.

∑

The Transmit PLCP Processor will automatically

determine its own stuffing options.

∑

Overhead bytes include those that support BIP-8

calculations (B1), indicator of stuff-option status for

current PLCP frame (C1), diagnostic byte that

reflects alarms conditions that were detected in the

Receive Section of the UNI (G1); and Path Over-

head bytes.

∑ Provides a serial input port for user to insert PLCP

Overhead Bytes externally.

R

ECEIVE

PLCP P

ROCESSOR

B

LOCK

∑

Can be disabled to support the "Direct Mapped"

ATM mode.

∑

Determines the frame boundaries of incoming

PLCP frames (from the Receive DS3 Framer).

∑

Extracts and processes the PLCP frame overhead

bytes.

∑

Provides a serial output port for user to read in the

contents of the PLCP Overhead Bytes from the

incoming data.

T

RANSMIT

/R

ECEIVE

DS3 F

RAMER

B

LOCK

∑

Supports the M13 and C-bit Parity Framing Formats.

∑

Transmit and Receive DS3 Framers can transmit/

receive data in the Unipolar or the Bipolar (AMI or

B3ZS line codes) format.

∑

The Transmit DS3 Framer provides a serial input

port that allows the user to insert his/her own

values for the overhead bits of the "outbound"

DS3 frames.

∑

The Receive DS3 Framer provides a serial output

port that allows the user access to the values of the

overhead bits of the "incoming" DS3 frames.

∑

The Receive DS3 Framer can be configured to

sample the incoming DS3 data (at the RxPOS and

RxNEG input pins) via the rising edge or falling

edge of the Receive Line Clock (RxLineClk) input.

∑

The Transmit DS3 Framer can be configured to

update the "outbound" DS3 data (at the TxPOS and

TxNEG output pins) at the rising edge or falling

edge of the Transmit Line Clock (TxLineClk) output.

∑

UNI includes on-chip RAM space to support the

transmission and reception of path maintenance data

link messages via an on-chip LAPD Transceiver

∑

UNI includes on-chip registers to support the trans-

mission and reception of FEAC (Far End Alarm &

Control) messages via an on-chip FEAC Transceiver.

∑

Contains on-chip FEAC Transceiver.

∑ Contains on-chip LAPD Transceiver.

M

ICROPROCESSOR

I

NTERFACE

S

ECTION

∑

Can be interfaced to Motorola or Intel type of

microprocessors/microcontrollers

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

8

∑

Microprocessor interface supports 8 bit wide or 16-

bit wide read/write accesses.

∑

Supports polled or interrupt-driven environments.

∑

Supports burst mode "Read and Write" operations

between the "local" microprocessor and the UNI on-

chip registers and RAM locations.

∑ Includes a "Loss of Clock Signal" protection feature

that terminates "Read/Write" cycles with the local

µ

P, during a "Loss of Clock signal" event.

P

ERFORMANCE

M

ONITOR

S

ECTION

Contains numerous on-chip "Read-Only" registers

that allows the user to monitor the overall "health" of

the system.

T

EST

AND

D

IAGNOSTIC

S

ECTION

∑

Supports Line, PLCP, and Cell Loop-back Modes

∑

Supports Line-Side Testing

∑

Contains an on-chip Test Cell Generator and an

on-chip Test Cell Receiver

∑

Test Cell Generator can generate a "continuous"

stream of test cells, or a "one-shot" burst of 1024

test cells.

∑

The Test Cell Receiver identifies, collects and eval-

uates Test Cells for errors.

∑ The Test Cell Receiver also reports the occurrence

of errors to the user.

L

INE

I

NTERFACE

D

RIVE

AND

S

CAN

S

ECTION

∑

Consists of an on-chip "Read/Write" register that

allows the user to control the state of 6 output pins.

∑ Consists of an on-chip "Read-Only" register that

allows the user to monitor the state of 3 input pins.

·Á

·Á

·Á

·Á

DS3 UNI FOR ATM

XRT7245

PRELIMINARY

REV. 1.03

9

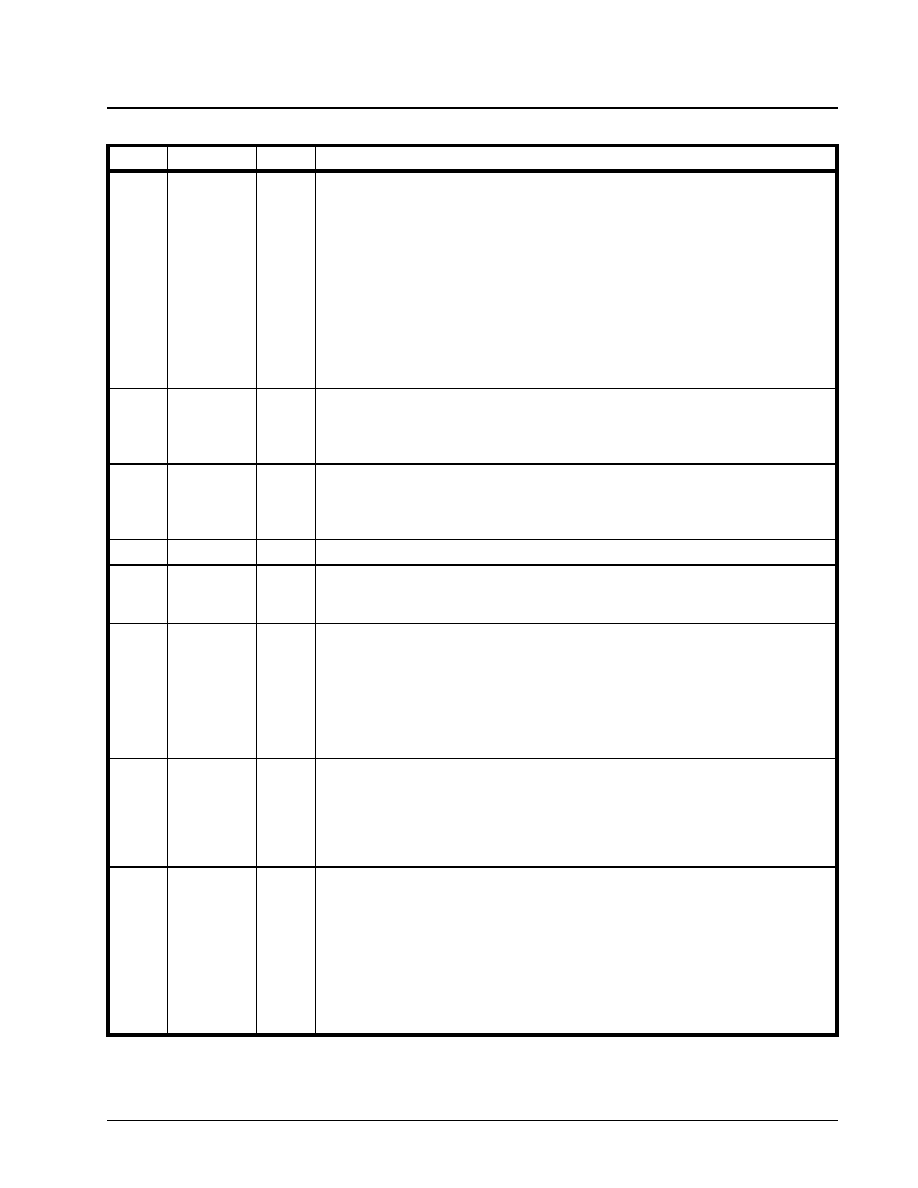

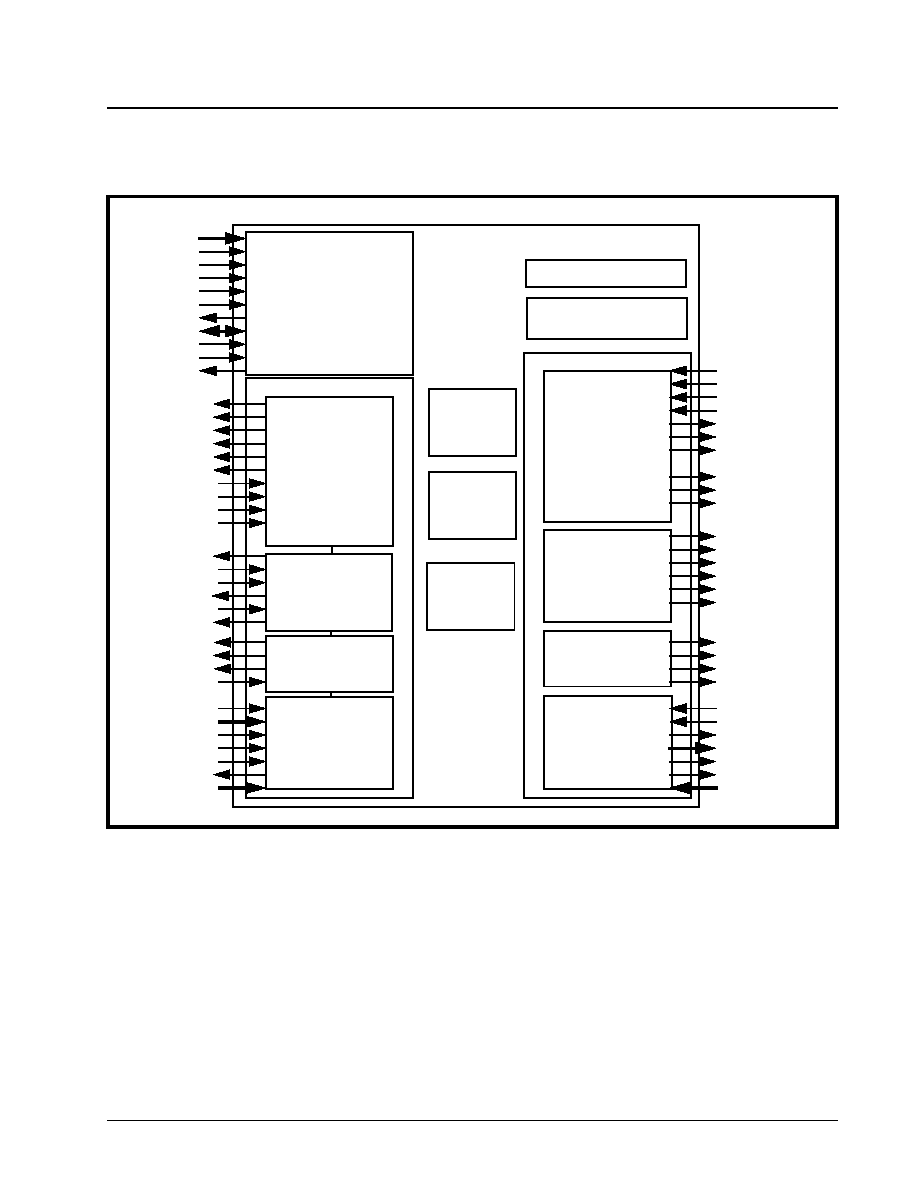

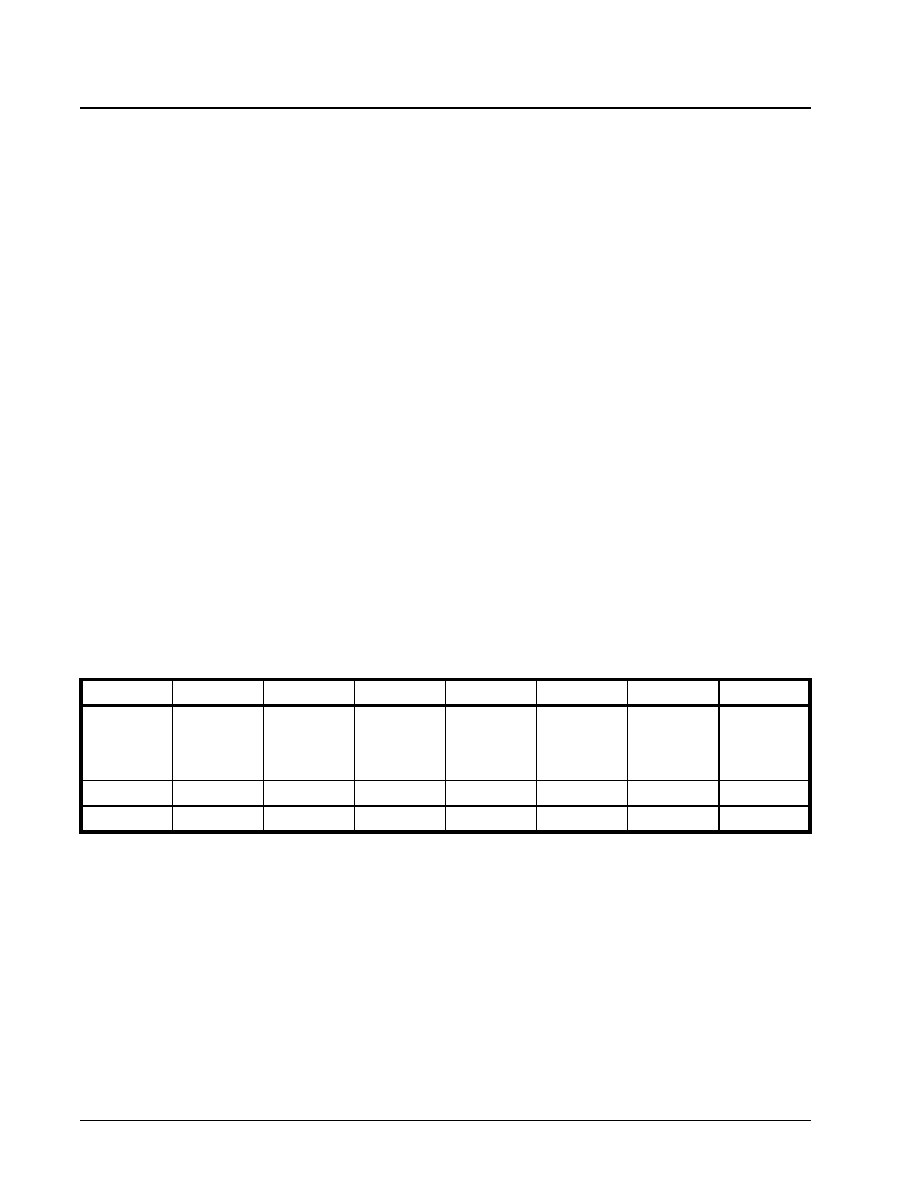

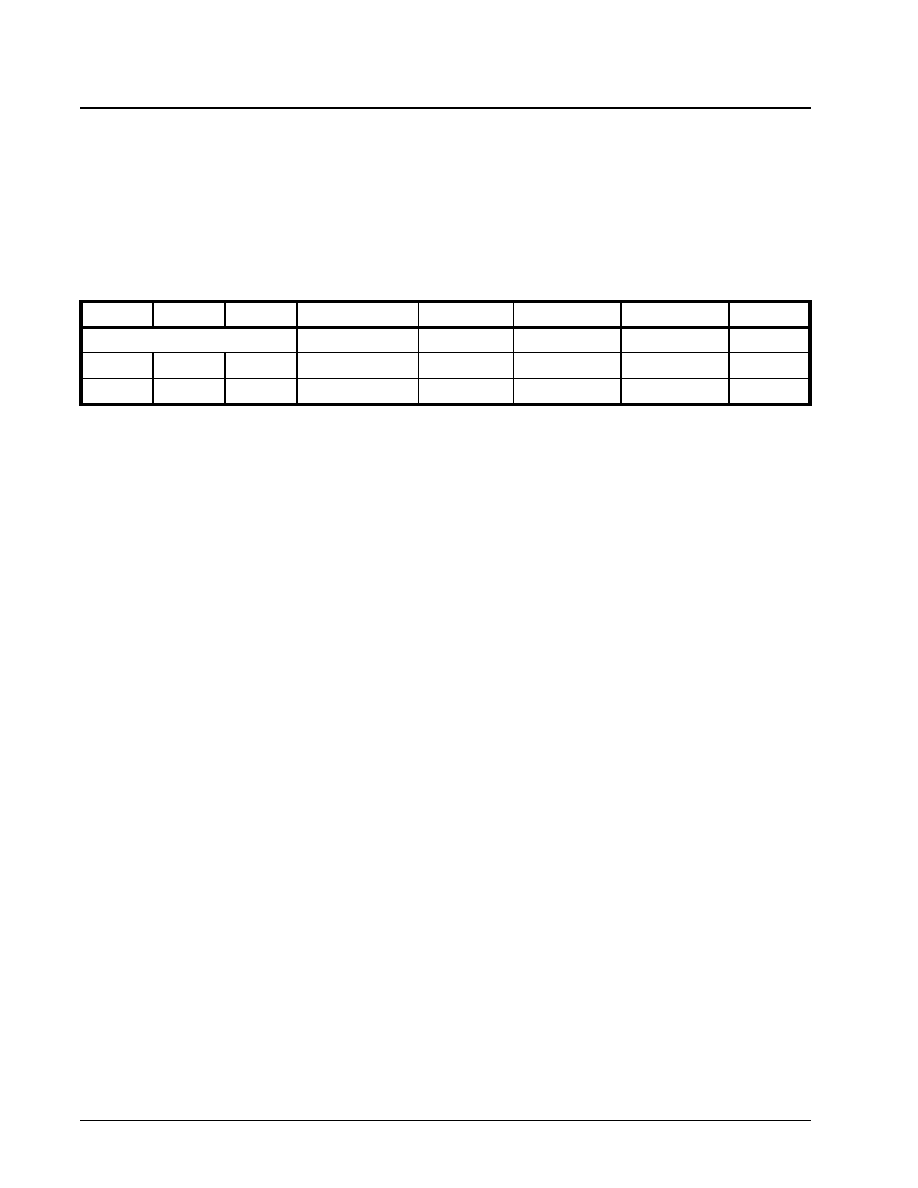

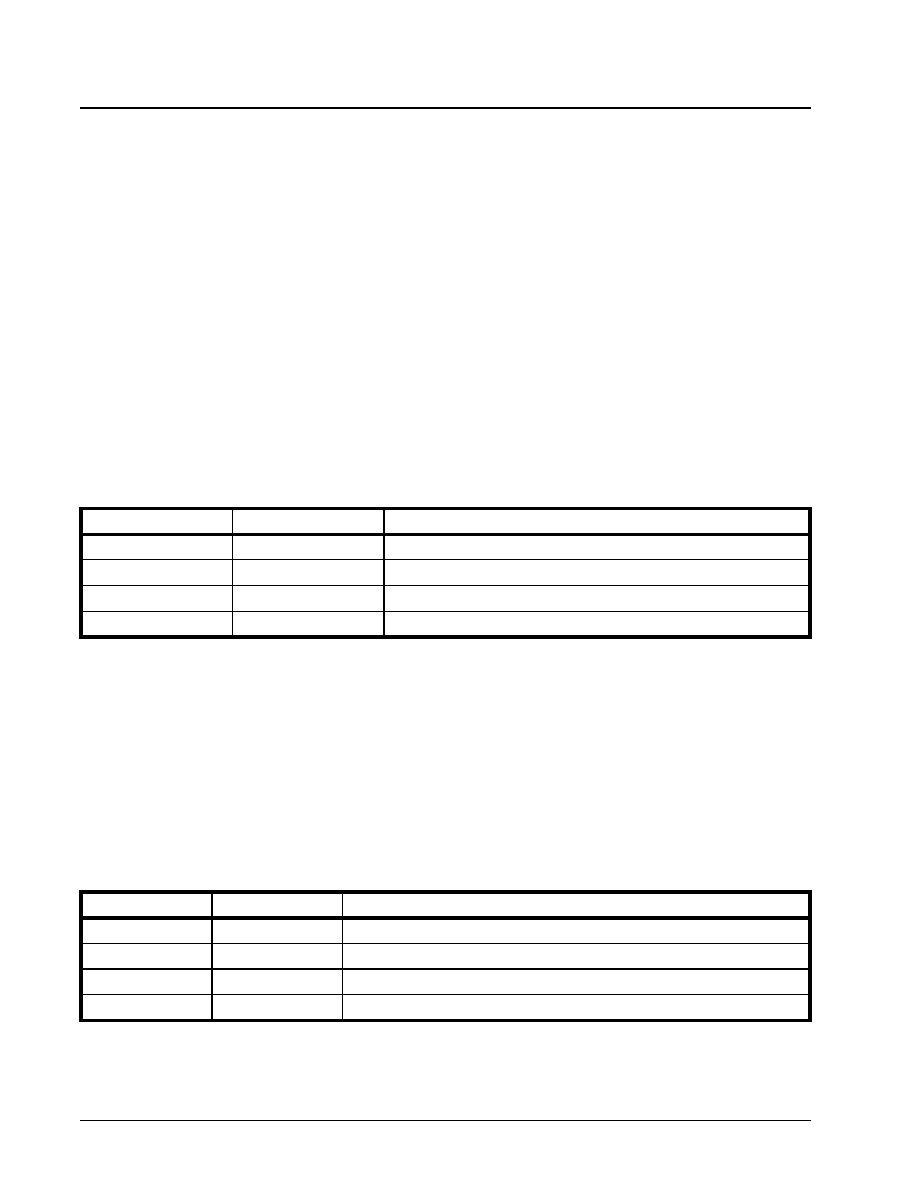

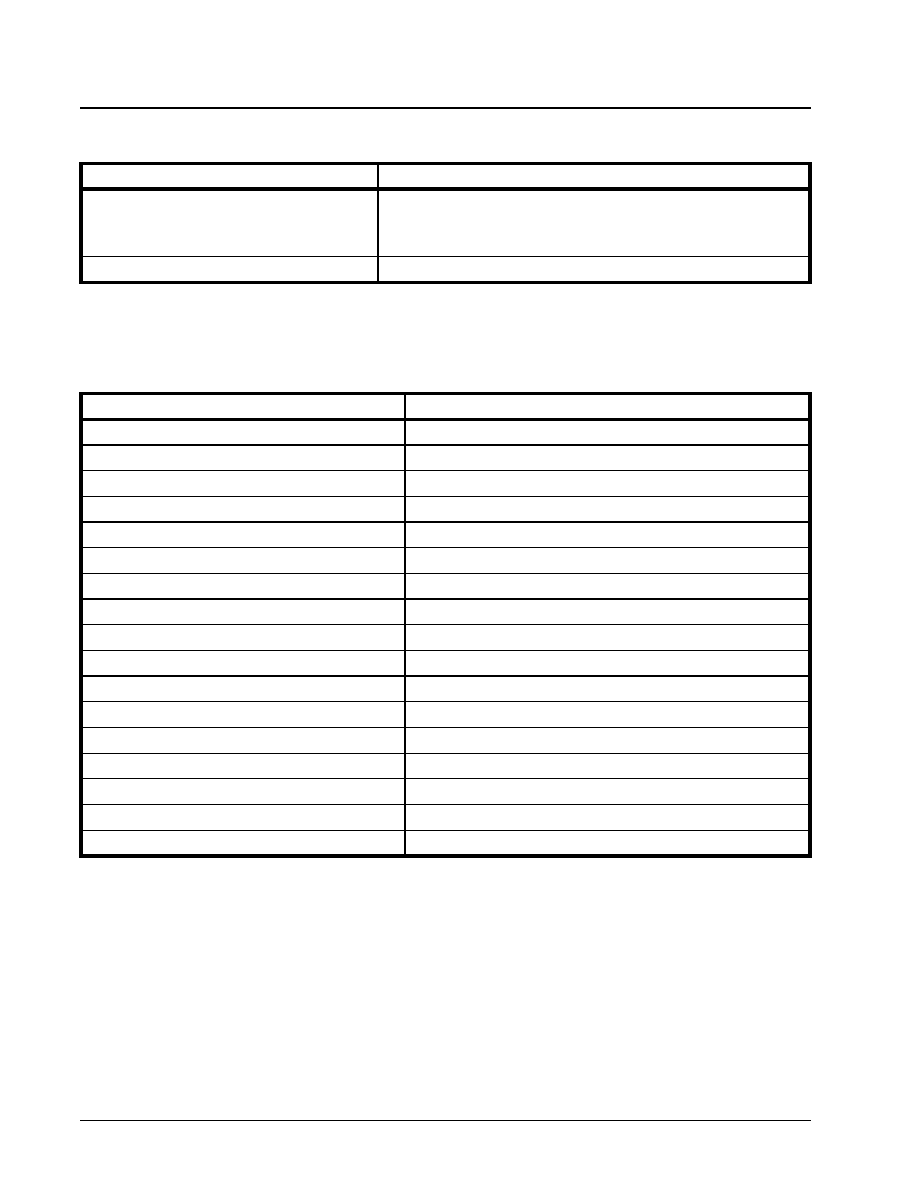

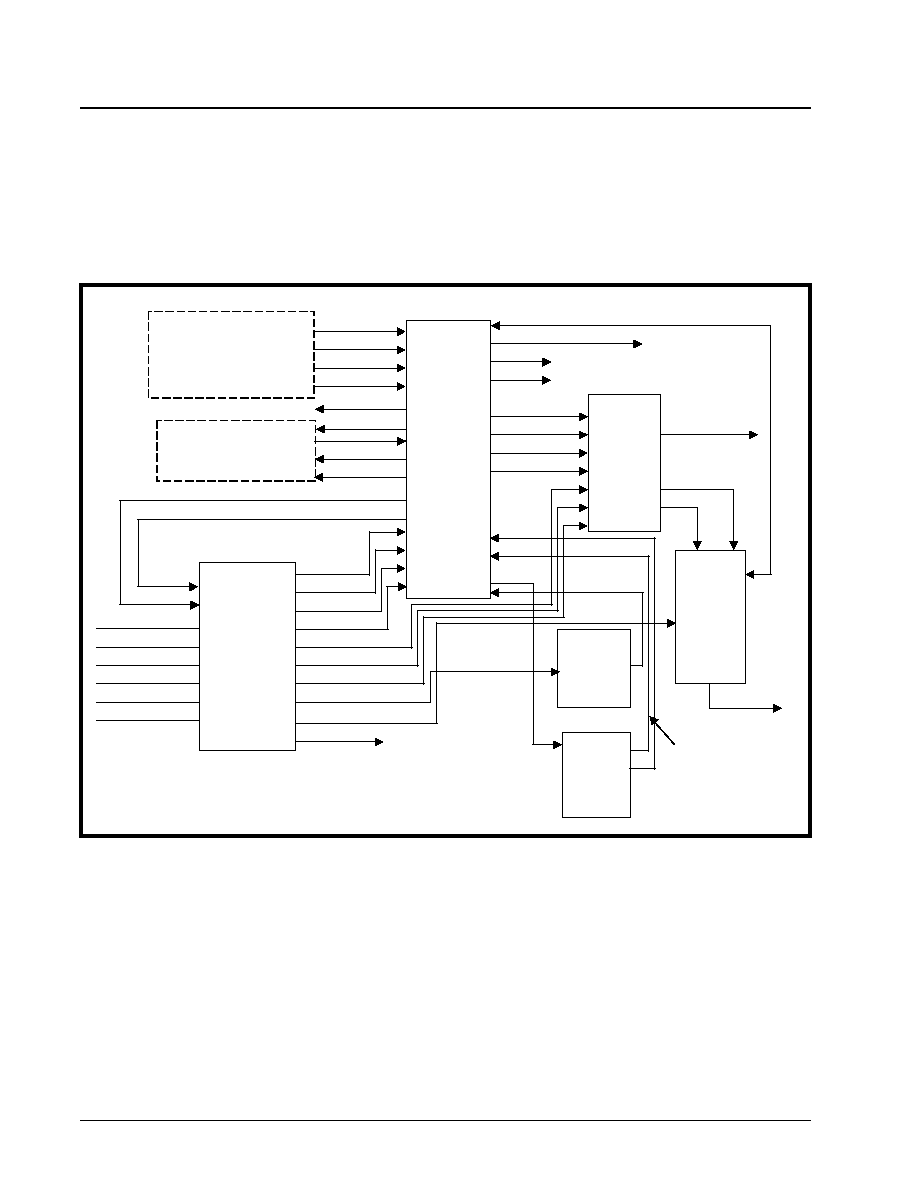

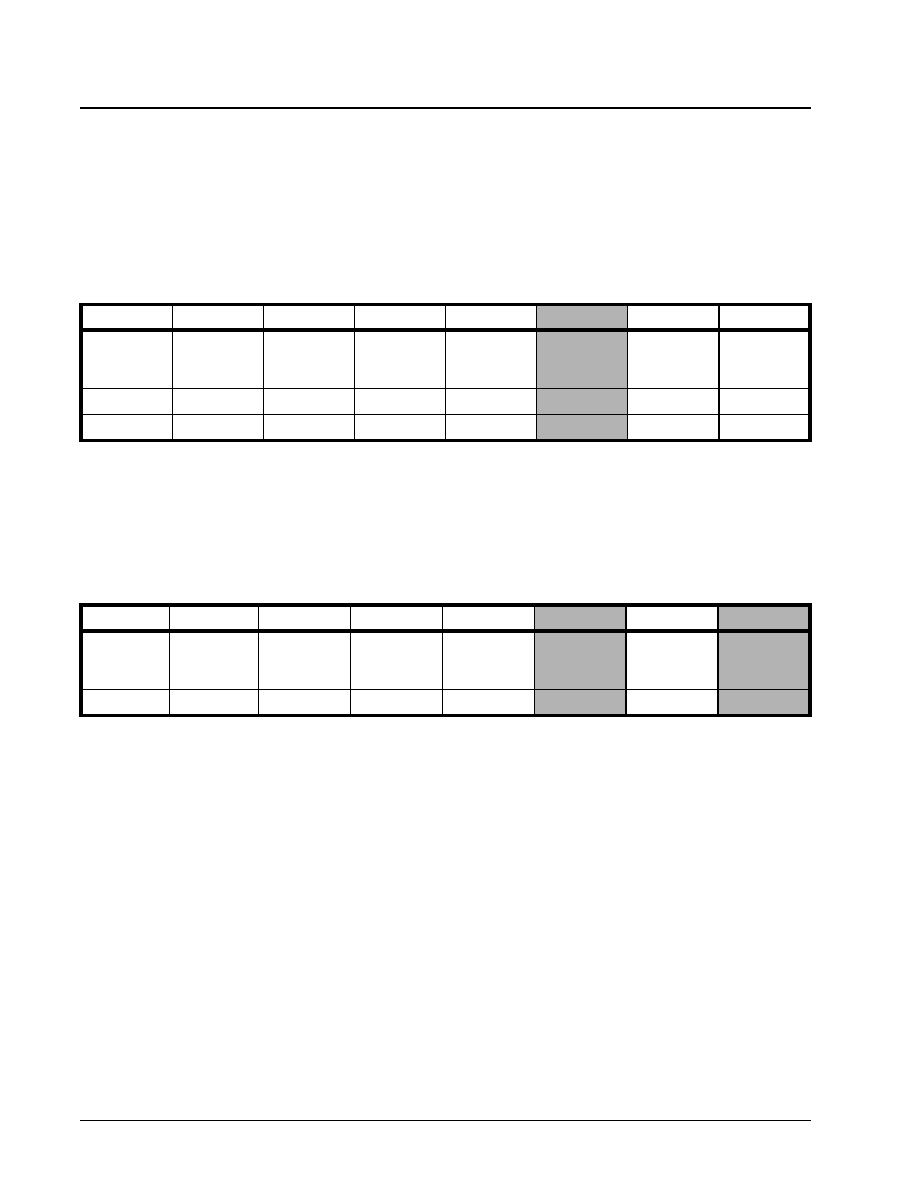

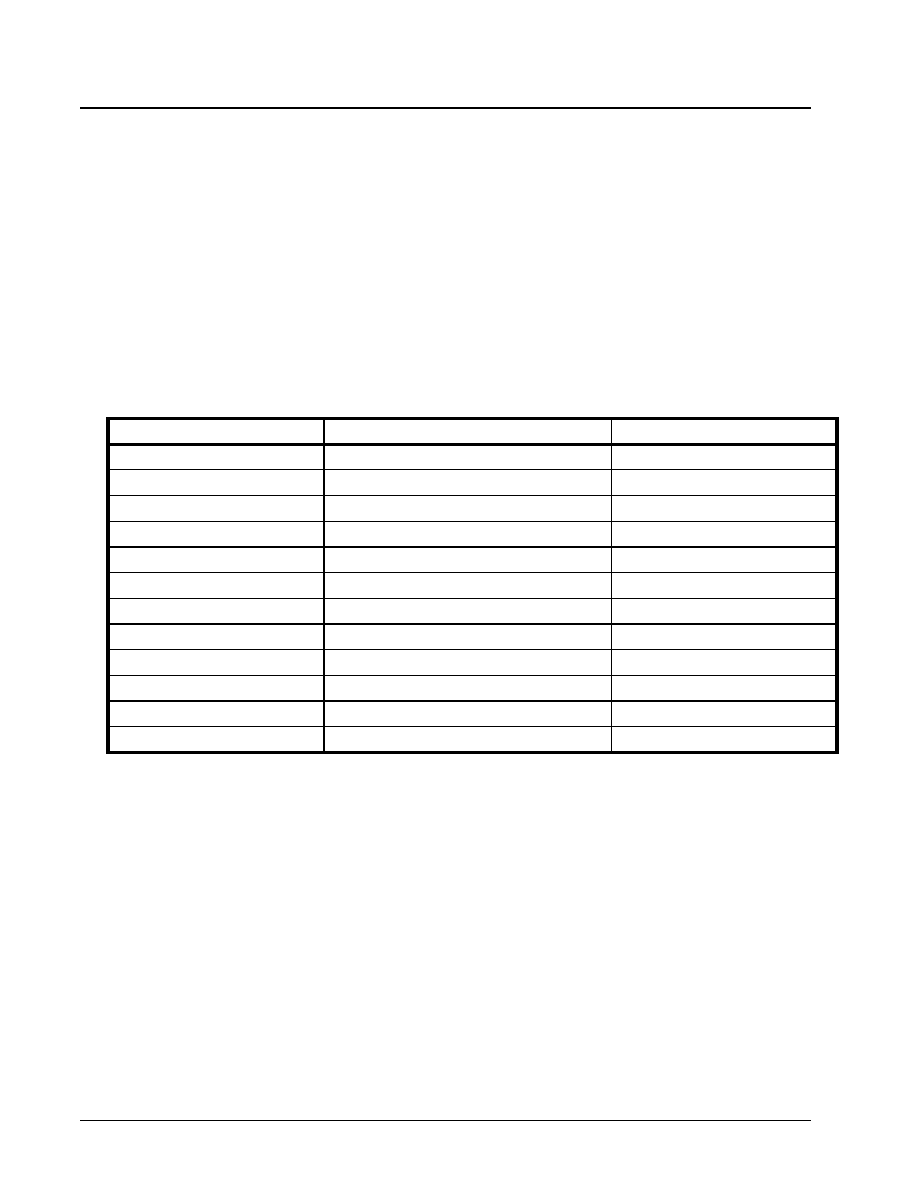

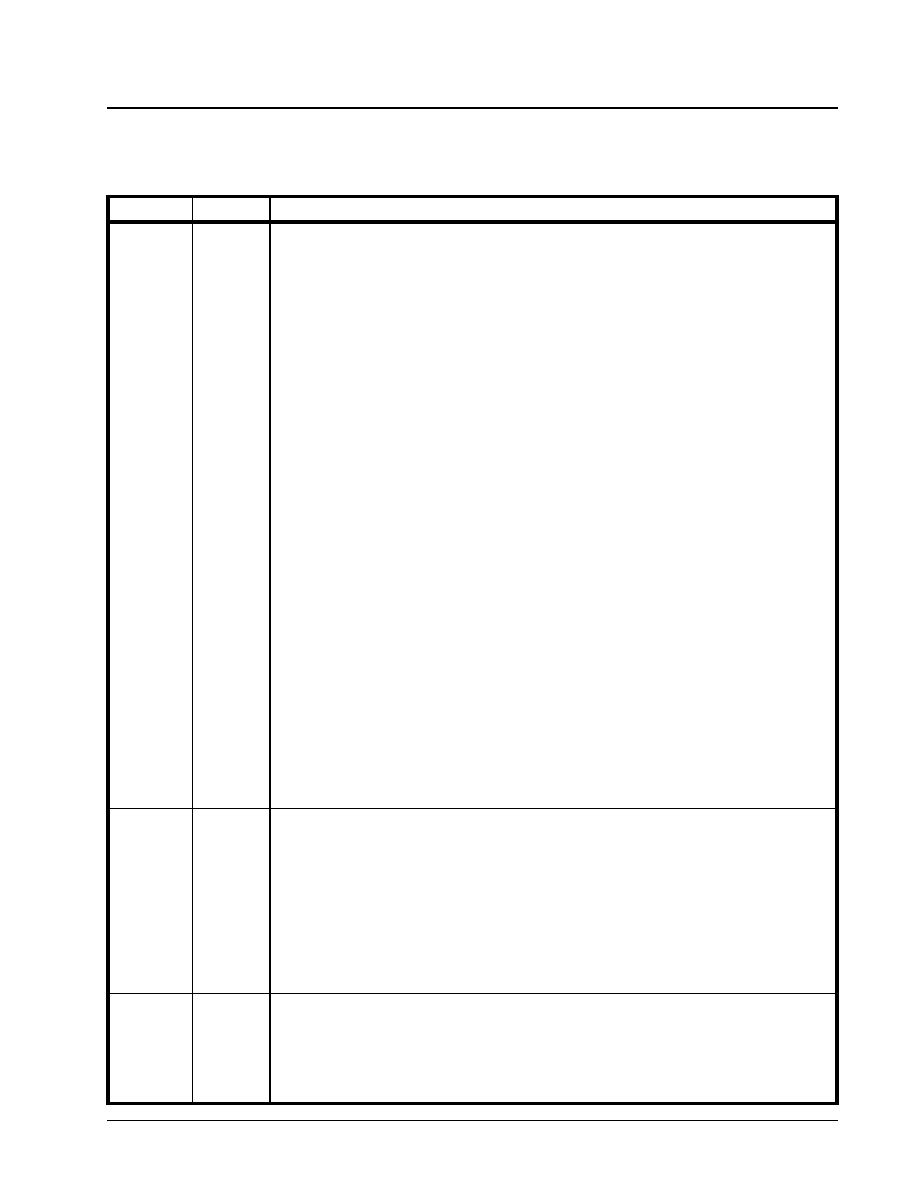

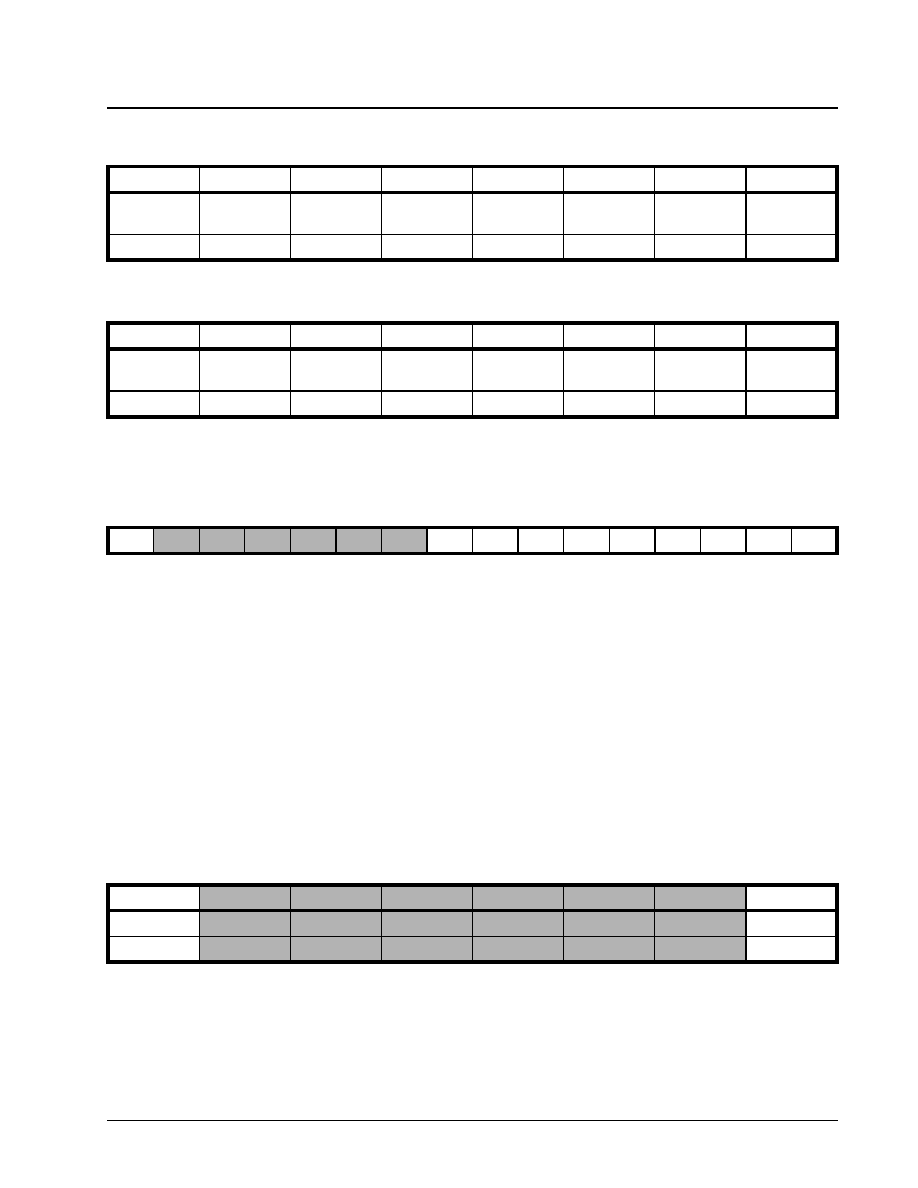

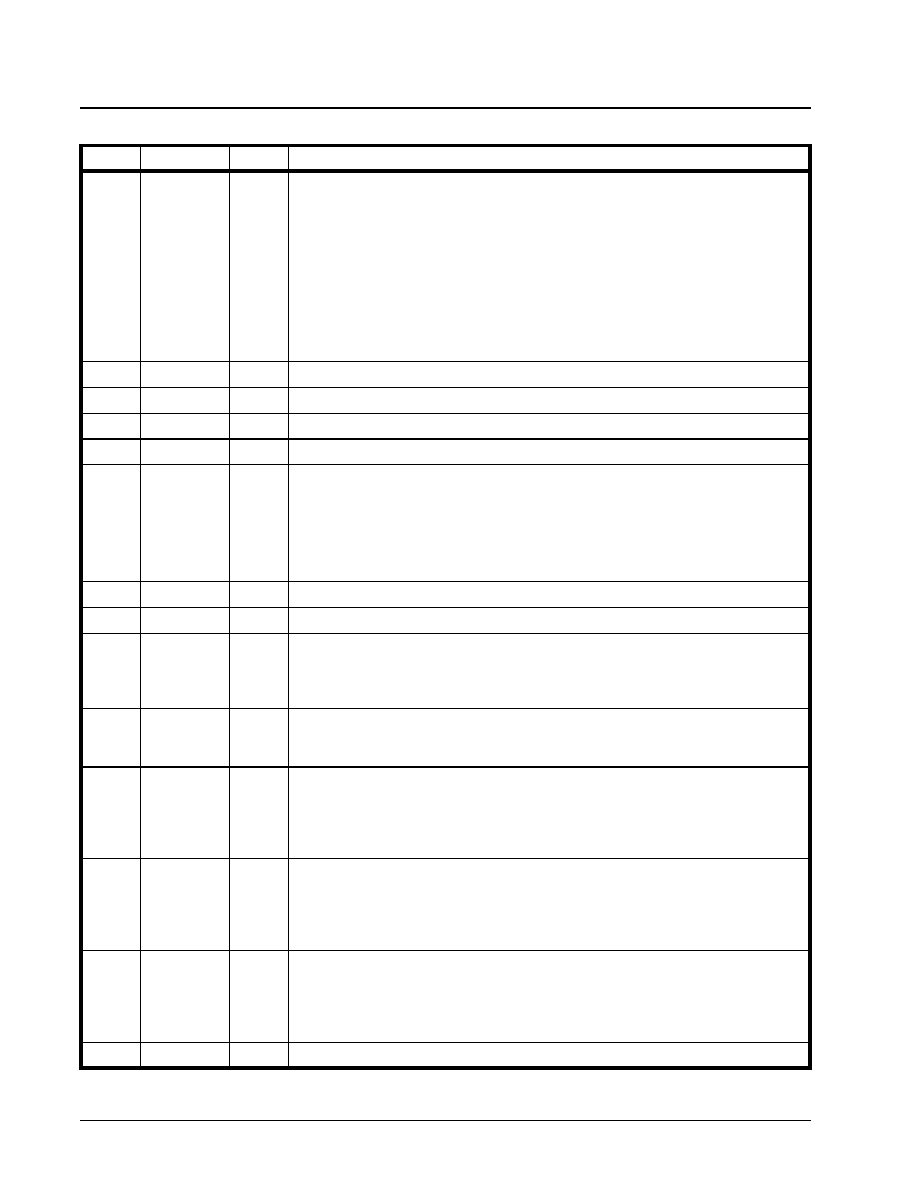

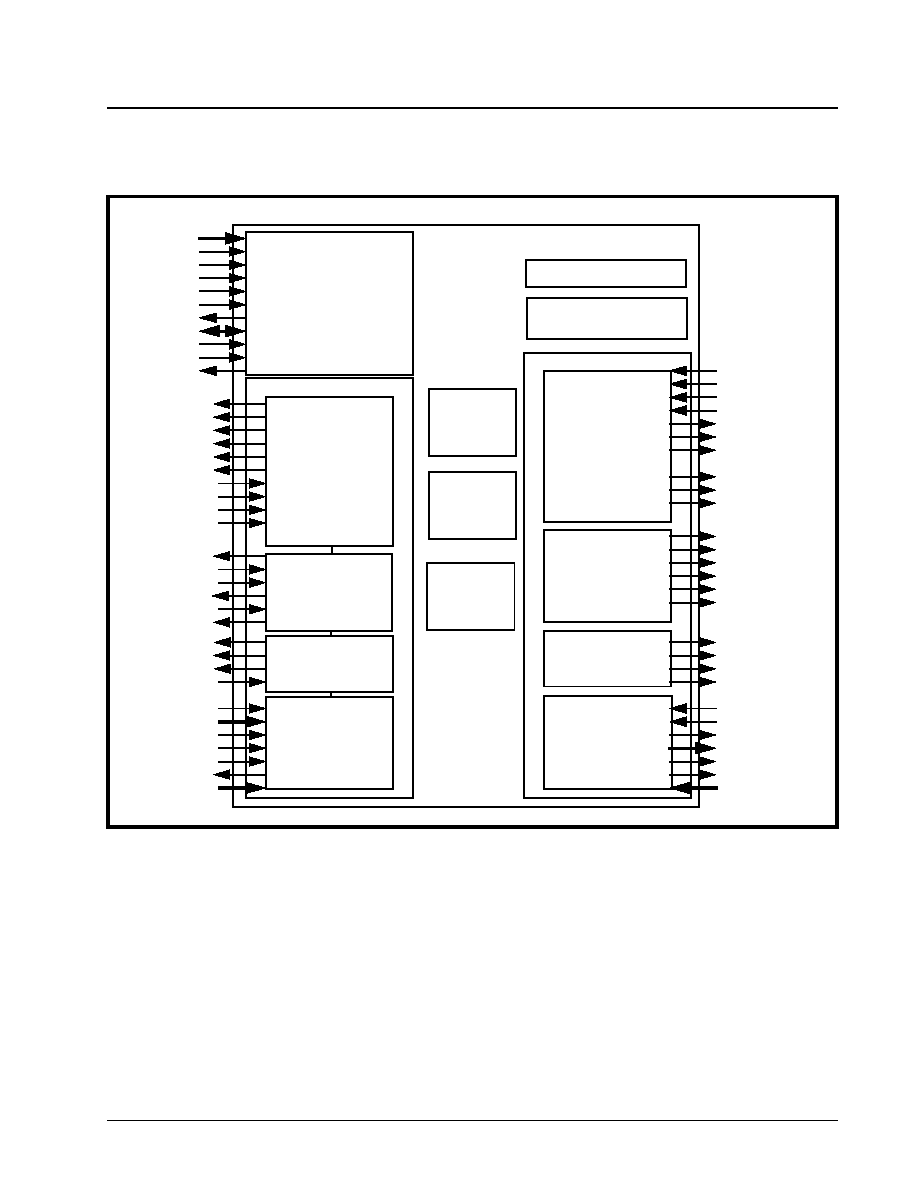

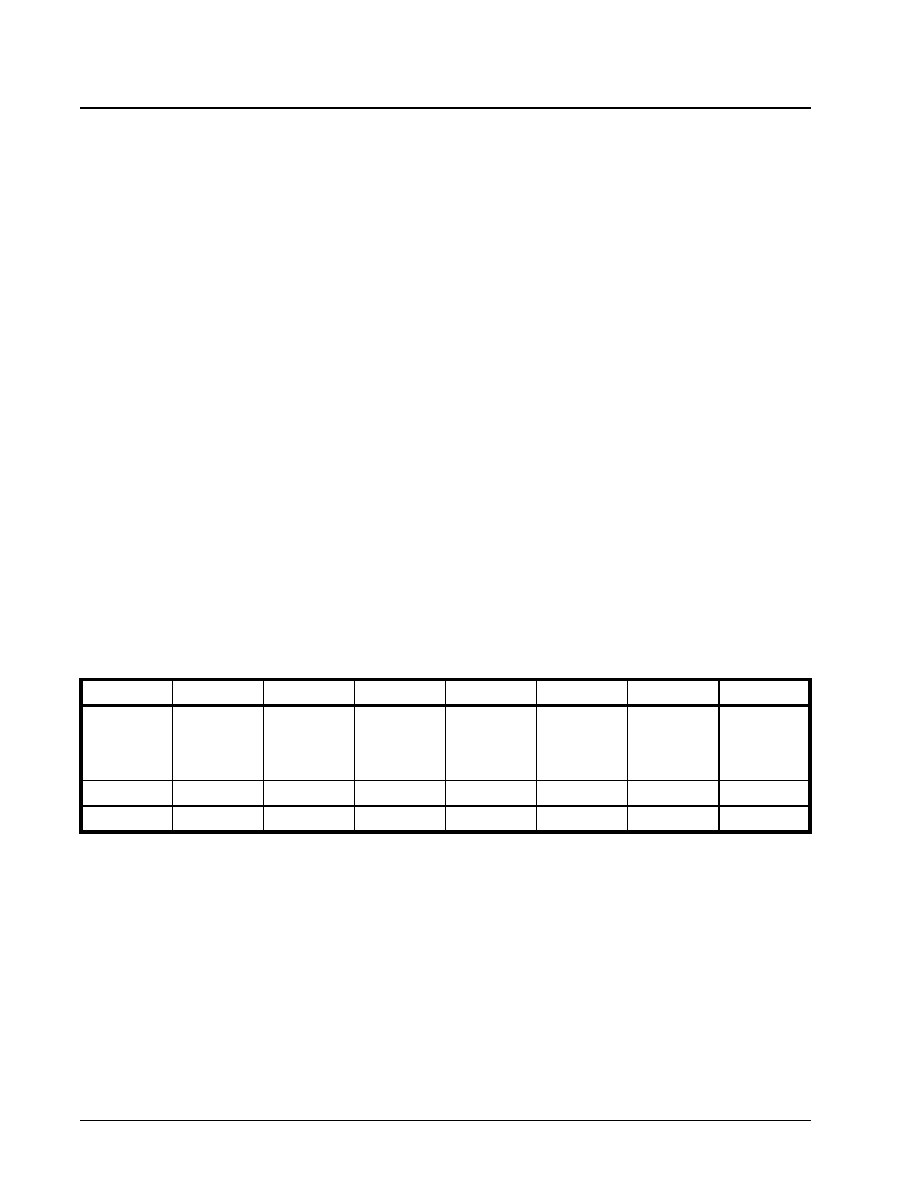

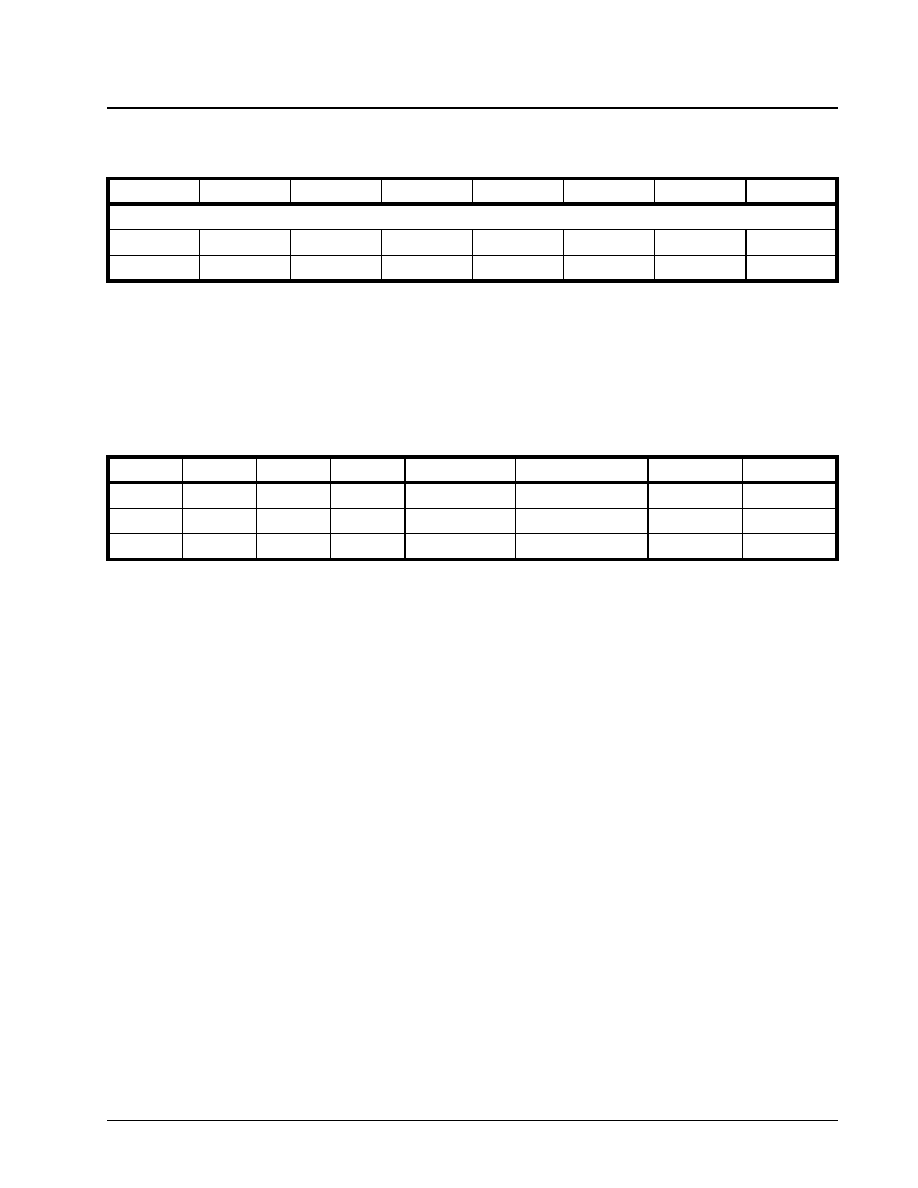

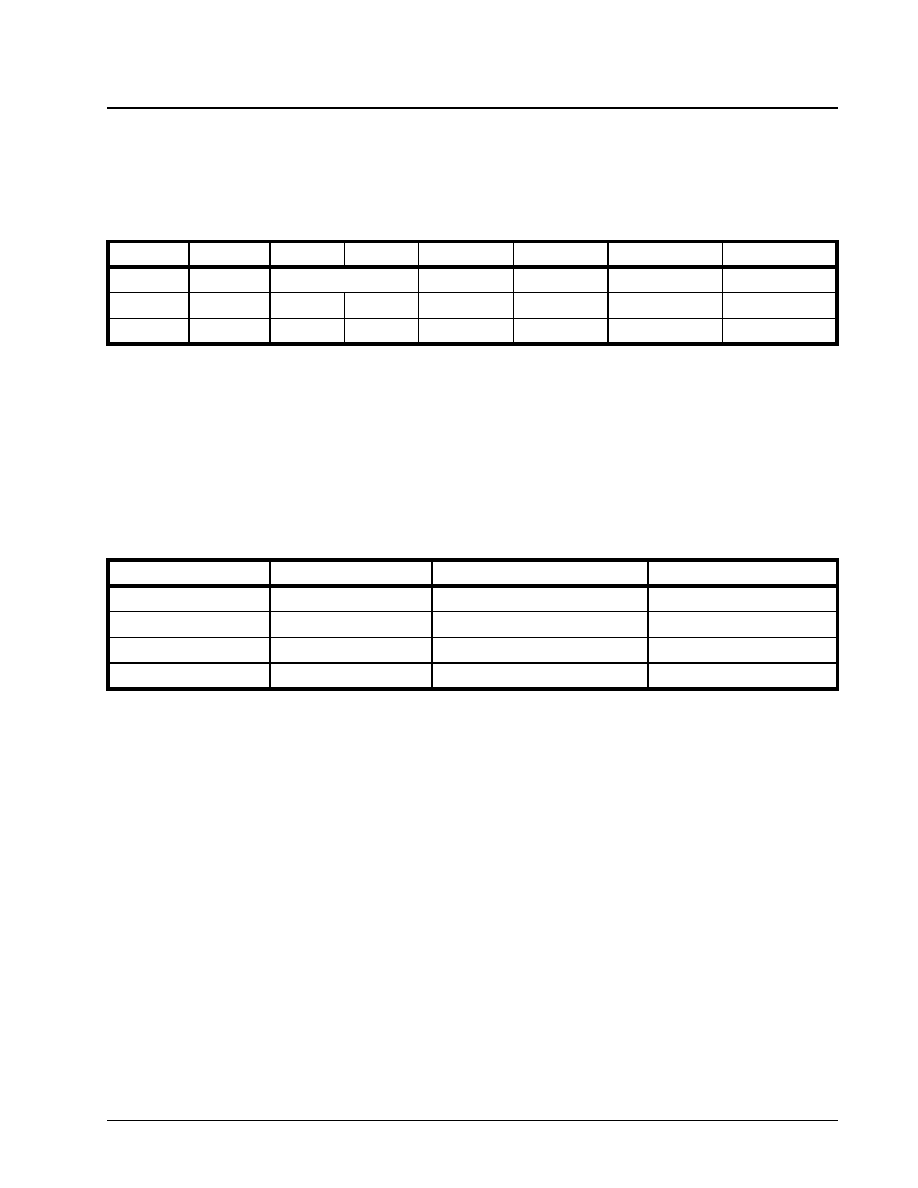

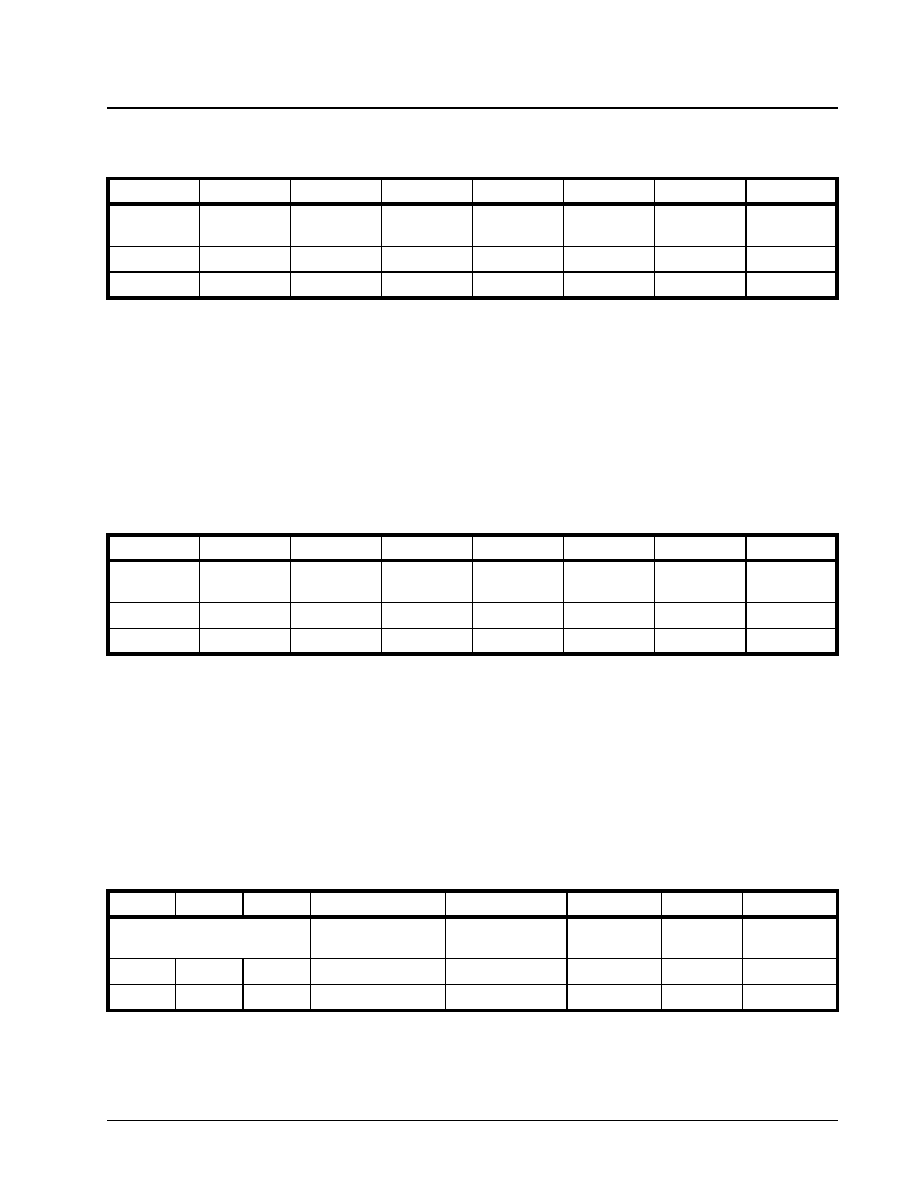

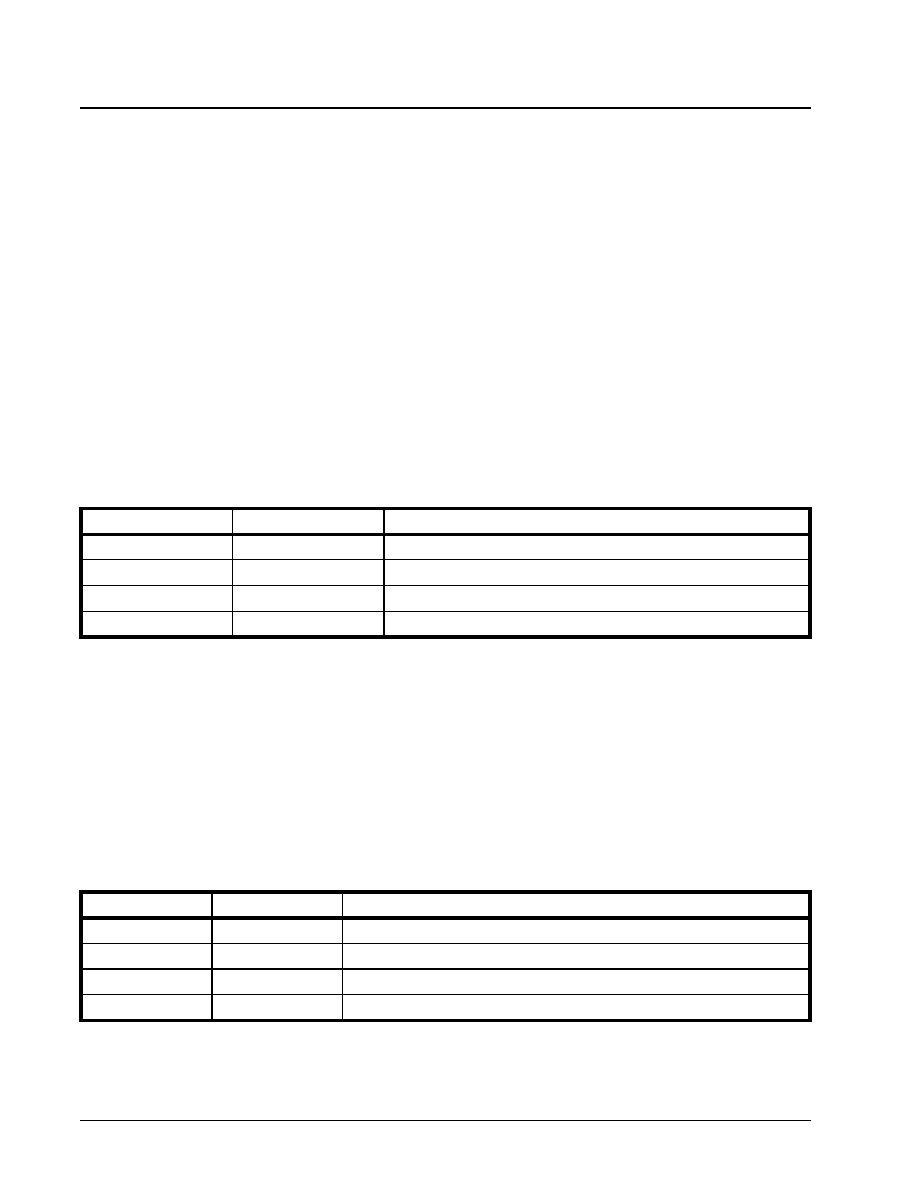

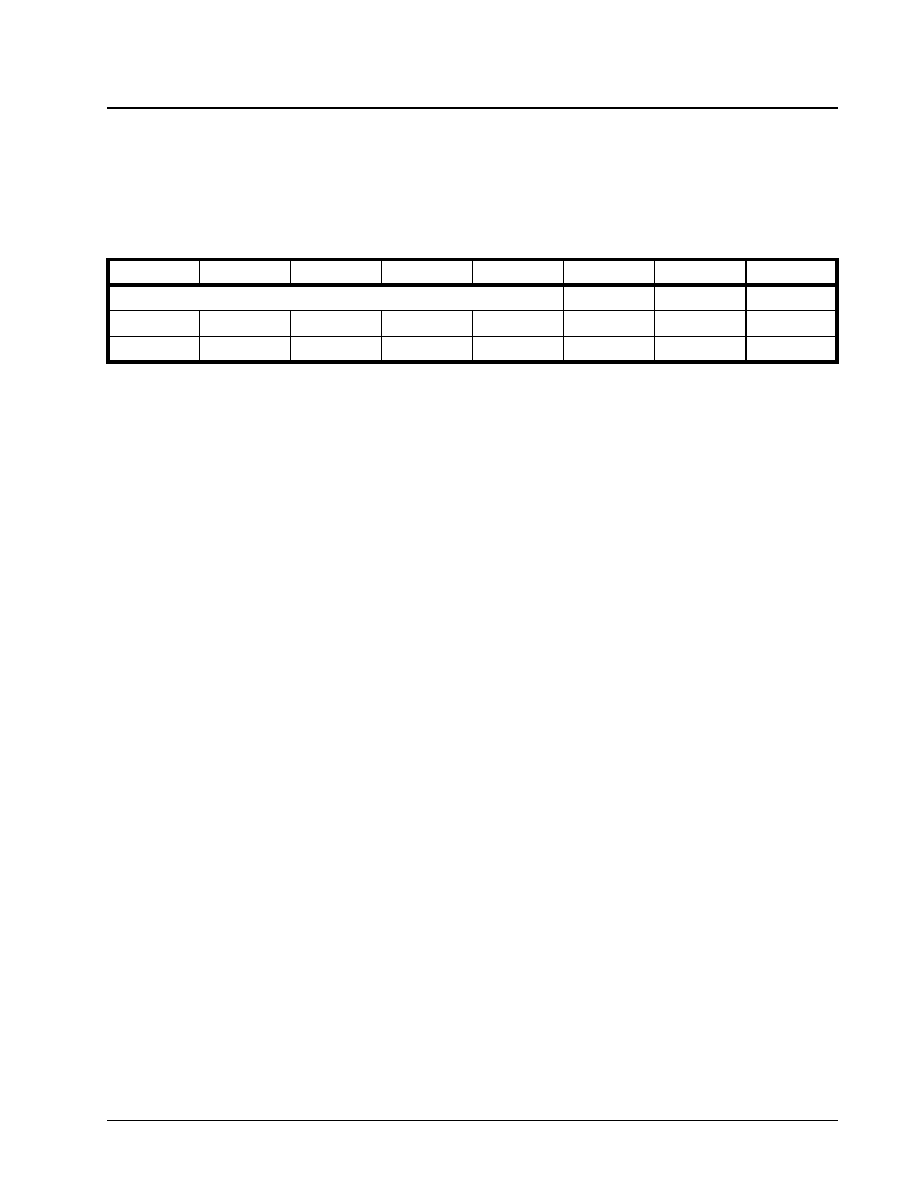

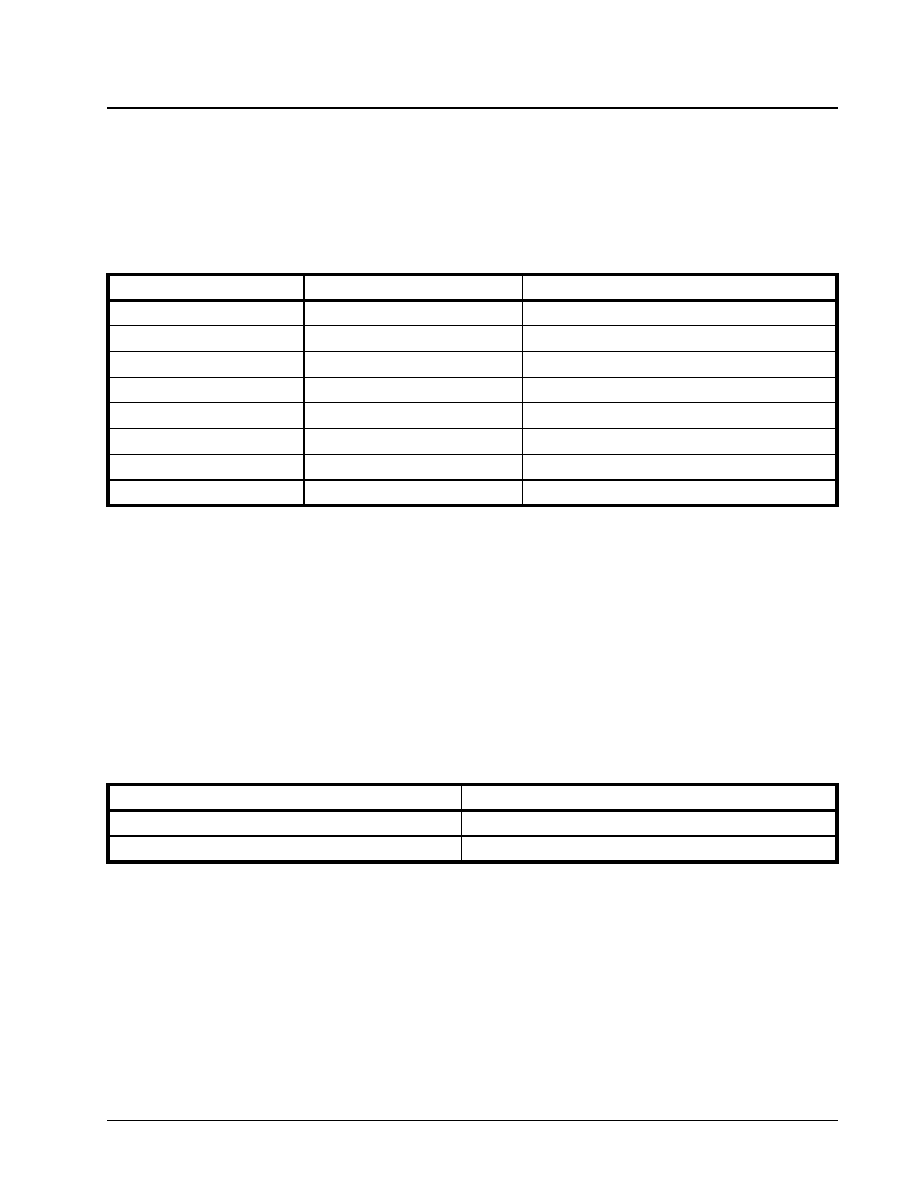

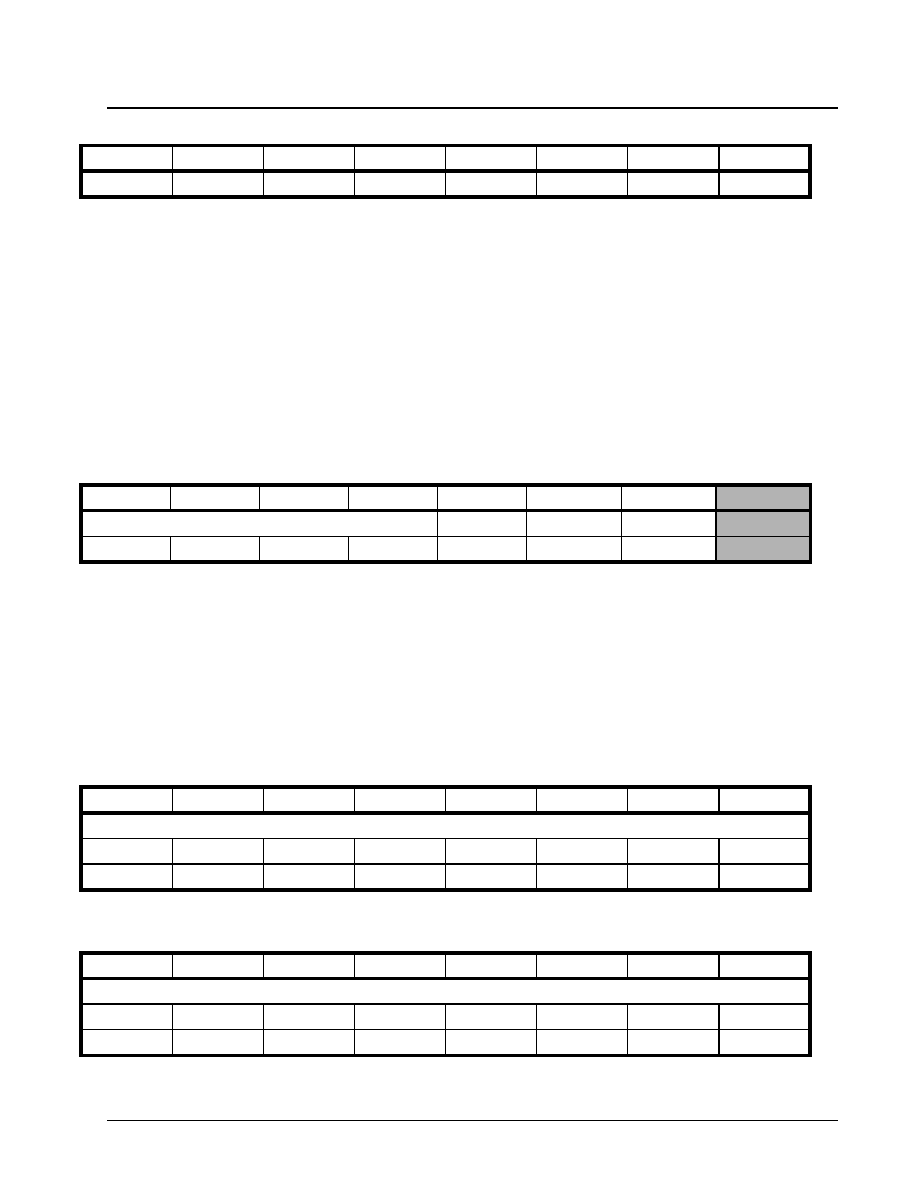

)Pin Descriptions (see Figure 2)

PIN DESCRIPTION

P

IN

N

O

. S

YMBOL

T

YPE

D

ESCRIPTION

1

D15

I/O

MSB of Bi-Directional Data Bus (Microprocessor Interface Section): This pin,

along with pins D0 - D14, function as the Microprocessor Interface bi-directional data

bus, and is intended to be interfaced to the "local" microprocessor. This pin is inactive

if the Microprocessor Interface block is configured to operate over an 8 bit data bus.

2

TAOS

O

"Transmit All Ones Signal" (TAOS) Command (for the XR-T7296 DS3 Line

Transmitter IC).

This output pin is intended to be connected to the TAOS input pin of the XR-T7296

DS3 Line Transmitter IC. The user can control the state of this output pin by writing a

`0' or `1' to Bit 4 (TAOS) of the Line Interface Drive Register (Address = 72h). If the

user commands this signal to toggle "high" then it will force the XR-T7296 DS3 Line

Transmitter IC to transmit an "All Ones" pattern onto the line. Conversely, if the user

commands this output signal to toggle "low" then the XR-T7296 DS3 Line Transmitter

IC will proceed to transmit data based upon the pattern that it receives via the TxPOS

and TxNEG output pins.

Writing a "1" to Bit 4 of the Line Interface Drive Register (Address = 72h) will cause this

output pin to toggle "high". Writing a "0" to this bit-field will cause this output pin to toggle

"low".

Note: If the customer is not using the XR-T7296 DS3 Line Transmitter IC, then he/she

can use this output pin for a variety of other purposes.

3

D14

I/O

Bi-directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

4

D13

I/O

Bi-directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

5

D12

I/O

Bi-directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

6 DMO

I

"Drive Monitor Output" Input (from the XRT7300 LIU IC).

This input pin is intended to be tied to the DMO output pin of the XRT7300 DS3/E3

LIU IC. The user can determine the state of this input pin by reading Bit 2 (DMO)

within the Line Interface Scan Register (Address = 73h). If this input signal is "high",

then it means that the drive monitor circuitry (within the XRT7300 LIU IC) has not

detected any bipolar signals at the MTIP and MRING inputs within the last 128 ± 32

bit-periods. If this input signal is "low", then it means that bipolar signals are being

detected at the MTIP and MRING input pins of the XRT7300 device.

Note: If this customer is not using the XRT7300 DS3 LIU IC, then he/she can use this

input pin for a variety of other purposes.

7

MOTO

I

Motorola/Intel Processor Interface Select Mode: This input pin allows the user to

configure the Microprocessor Interface to interface with either a "Motorola-type" or

"Intel-type" microprocessor/microcontroller. Tying this input pin to VCC, configures the

microprocessor interface to operate in the Motorola mode (e.g., the UNI device can be

readily interfaced to a "Motorola type" local microprocessor). Tying this input pin to

GND configures the microprocessor interface to operate in the Intel Mode (e.g., the

UNI device can be readily interfaced to an "Intel type" local microprocessor).

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

10

8

RLOL

I

Receive Loss of Lock Indicator--from the XRT7300 DS3/E3 LIU IC.

This input pin is intended to be connected to the RLOL (Receive Loss of Lock) output

pin of the XRT7300 LIU IC. The user can monitor the state of this pin by reading the

state of Bit 1 (RLOL) within the Line Interface Scan Register (Address = 73h). If this

input pin is "low", then it means that the phase-locked-loop circuitry, within the XRT7300

device is properly locked onto the incoming DS3 data-stream; and is properly recover-

ing clock and data from this DS3 data-stream. However, if this input pin is "high", then

it means that the phase-locked-loop circuitry, within the XRT7300 device has lost lock

with the incoming DS3 data-stream, and is not properly recovering clock and data.

For more information on the operation of the XRT7300 DS3/E3/STS-1 LIU IC, please

consult the "XRT7300 DS3/E3/STS-1 LIU IC" data sheet.

Note: If the customer is not using the XRT7300 LIU IC, he/she can use this input pin

for other purposes.

9

D11

I/O

Bi-Directional Data bus (Microprocessor Interface Section):

10

TxFrame

O

Transmit End of DS3 Frame Indicator: This output pin indicates that the last bit of an

outbound DS3 frame is being transmitted from the TxPOS and TxNEG output pins.

This pin marks the end of DS3 frame by pulsing "high" for one bit period at the end of each

frame.

11

D10

I/O

Bi-Directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

12

REQB

O

Receive Equalization Bypass Control Output Pin--(to be connected to the

XRT7300 DS3/E3 LIU IC):

This output pin is intended to be connected to the REQB input pin of the XRT7300 DS3/

E3 LIU IC. The user can control the state of this output pin by writing a `0' or `1' to Bit 5

(REQB) of the Line Interface Driver Register (Address = 72h). If the user commands

this signal to toggle "high" then it will cause the incoming DS3 line signal to "by-pass"

equalization circuitry, within the XRT7300 Device. Conversely, if the user commands

this output signal to toggle "low", then the incoming DS3 line signal with be routed

through the equalization circuitry. For information on the criteria that should be used

when deciding whether to bypass the equalization circuitry or not, please consult the

"XRT7300 DS3/E3/STS-1 LIU IC" data sheet.

Writing a "1" to Bit 5 of the Line Interface Drive Register (Address = 72h) will cause this

output pin to toggle "high". Writing a "0" to this bit-field will cause this output pin to toggle

"low".

Note: If the customer is not using the XRT7300 DS3/E3/STS-1 LIU IC, then he/she

can use this output pin for a variety of other purposes.

13

D9

I/O

Bi-Directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

14

D8

I/O

Bi-Directional Data bus (Microprocessor Interface Section): This pin is inactive if

the Microprocessor Interface block is configured to operate over an 8 bit data bus.

(Please see description for D15)

15

VDD

***

Power Supply Pin

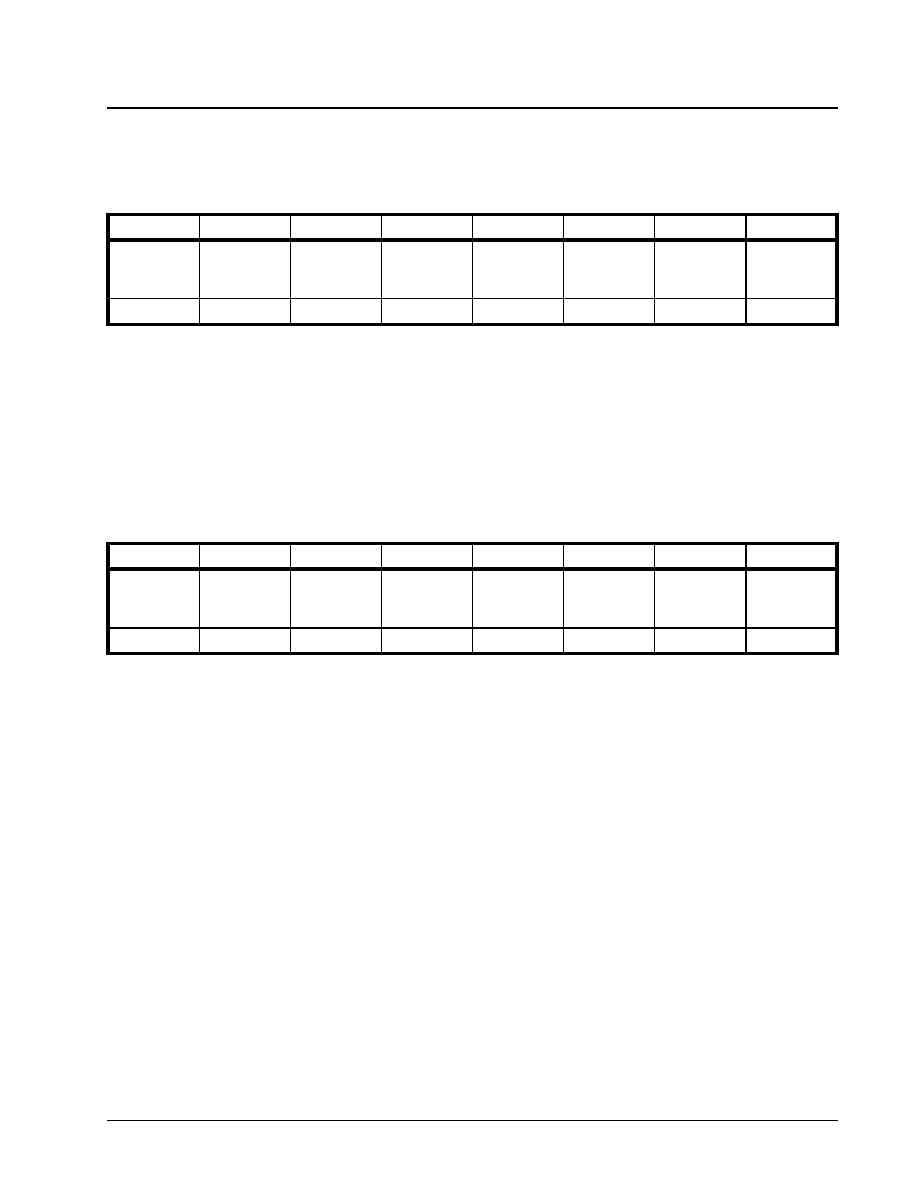

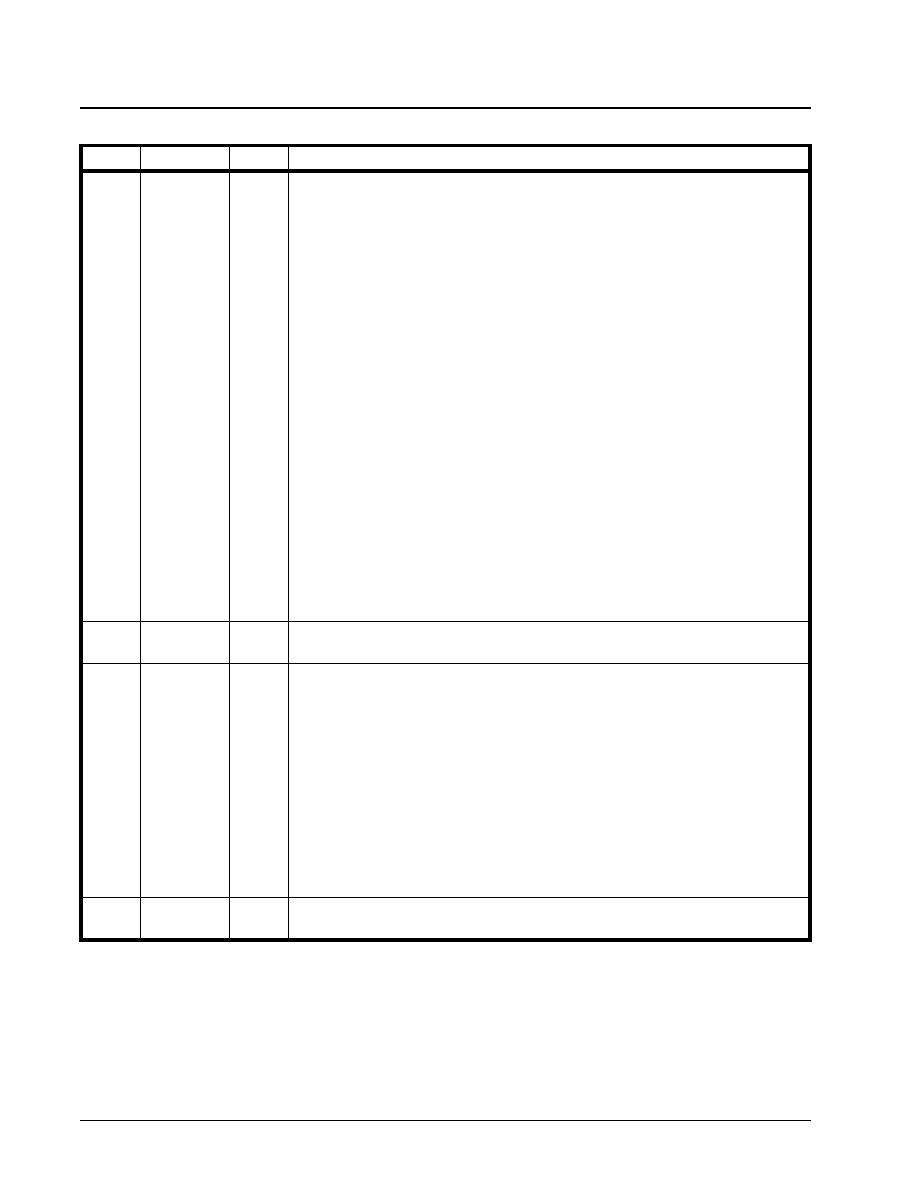

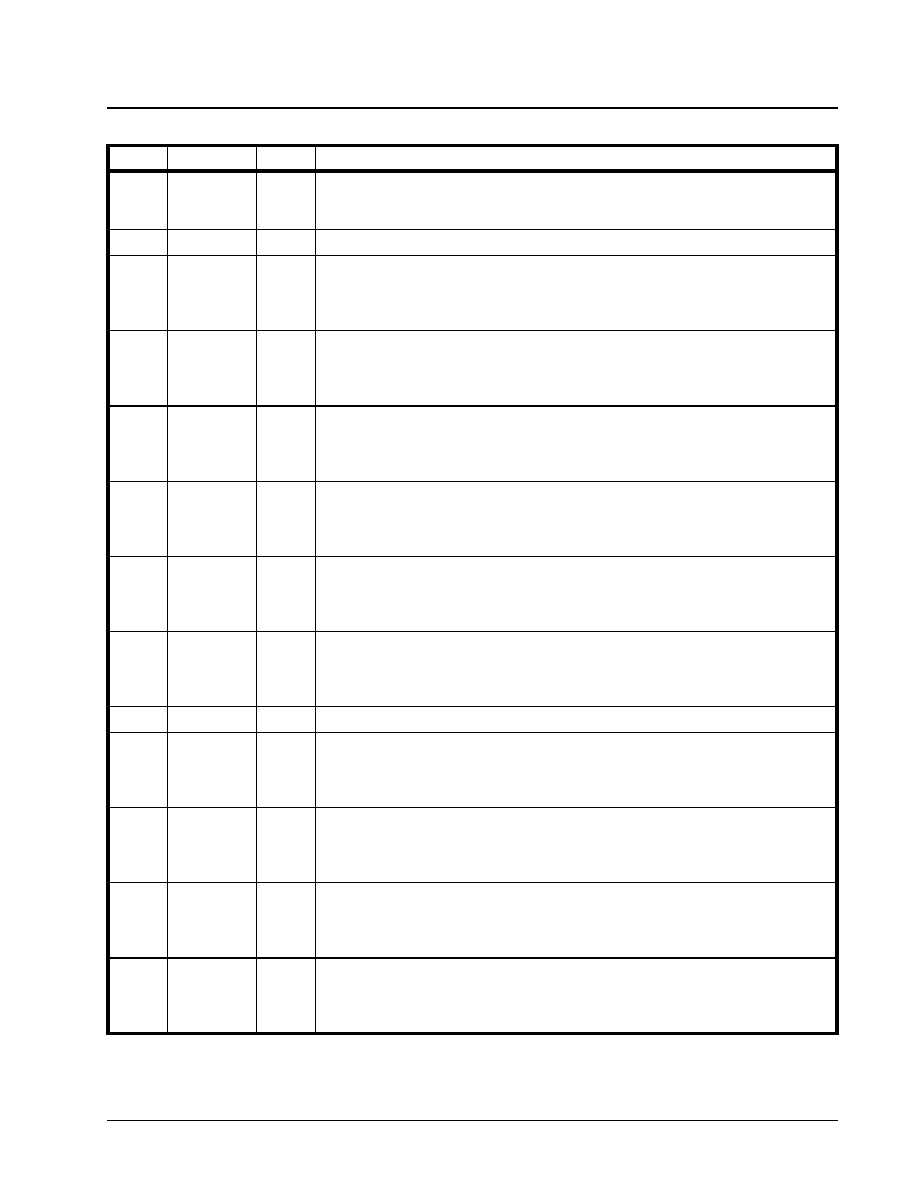

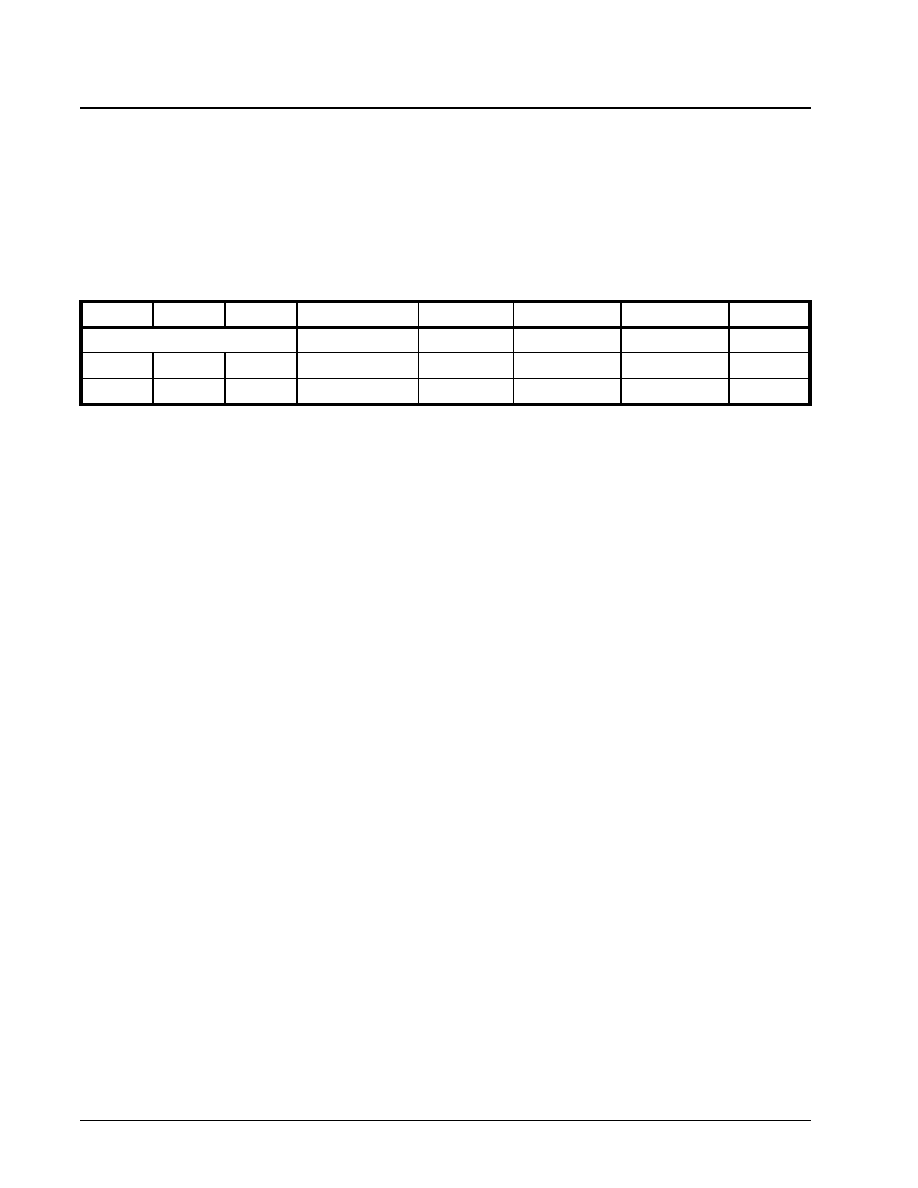

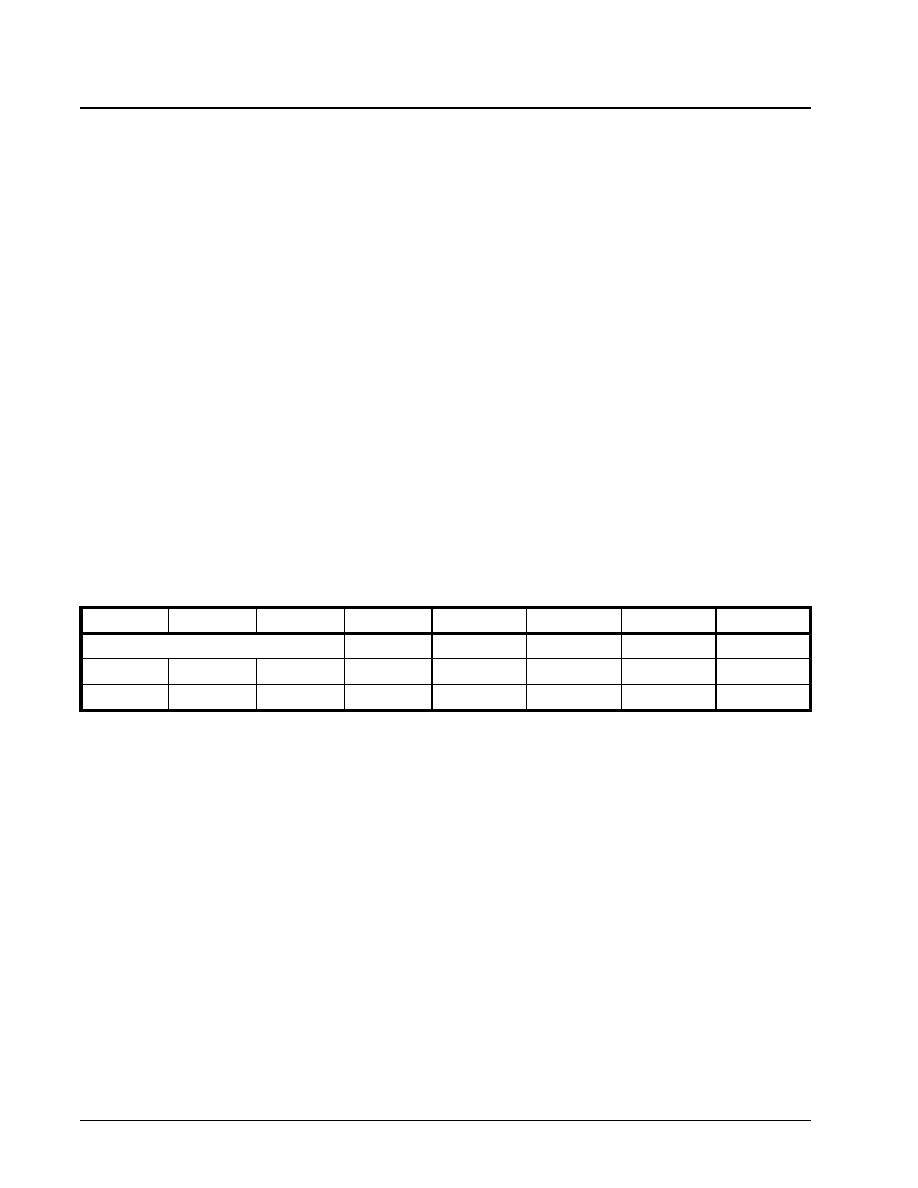

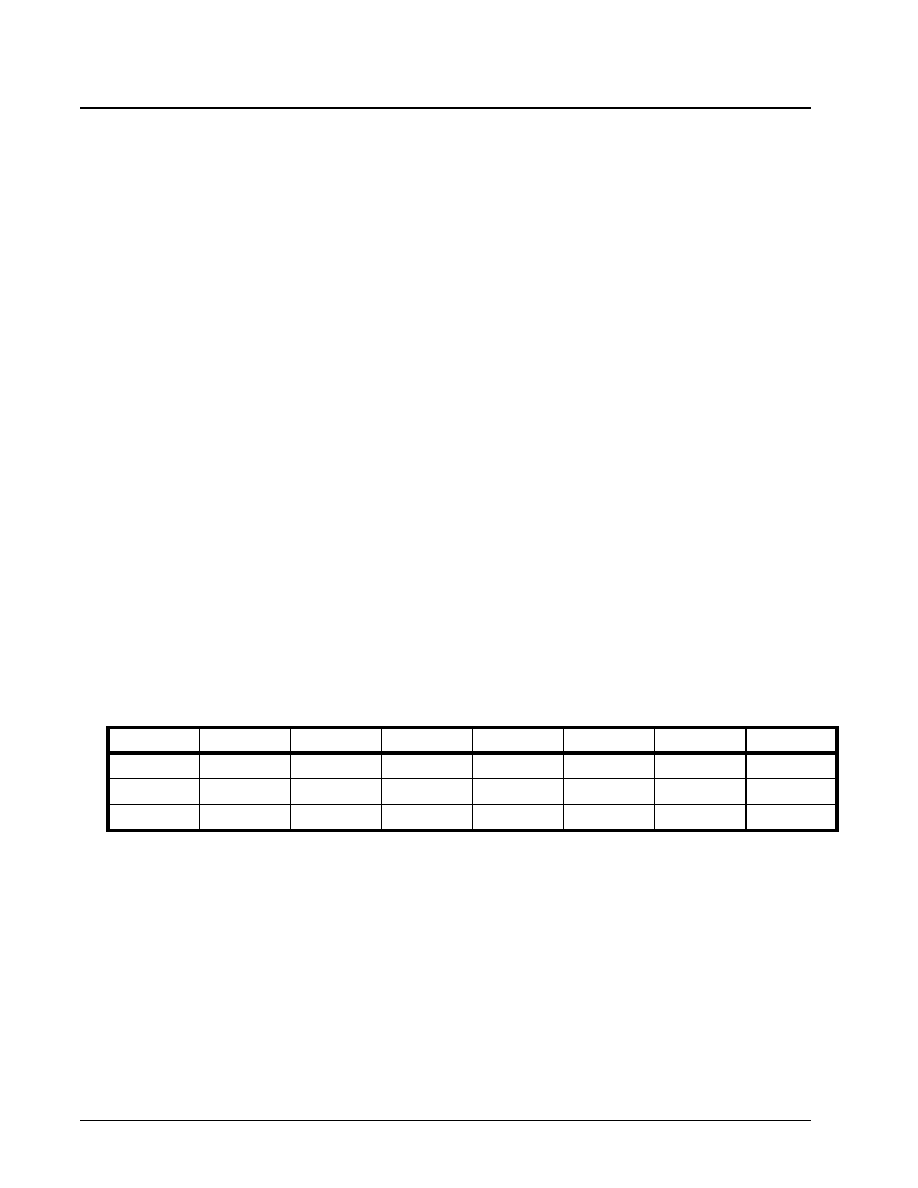

PIN DESCRIPTION (CONT'D)

P

IN

N

O

. S

YMBOL

T

YPE

D

ESCRIPTION

·Á

·Á

·Á

·Á

DS3 UNI FOR ATM

XRT7245

PRELIMINARY

REV. 1.03

11

16

D7

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

17

D6

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

18

D5

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

19

D4

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

20

Width16

I

Microprocessor Interface Block Data Bus Width Selector: This input pin allows the

user to configure the microprocessor interface of the UNI, to operate over either an 8

or 16 bit wide data bus. Tying this pin to VCC configures the Microprocessor Interface

Data Bus width to be 16 bits. Tying this pin to GND configures the Microprocessor

Interface Data Bus width to be 8 bits.

21

D3

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

22

Encodis

O

Encoder (B3ZS) Disable Output pin (intended to be connected to the XRT7300

DS3/E3 LIU IC).

This output pin is intended to be connected to the Encodis input pin of the XRT7300

LIU IC. The user can control the state of this output pin by writing a "0" or "1" to Bit 3

(Encodis) of the Line Interface Driver Register (Address = 72h). If the user commands

this signal to toggle "high" then it will disable the B3ZS encoder circuitry within the

XRT7300 IC. Conversely, if the user commands this output signal to toggle "low", then

the B3ZS Encoder circuitry, within the XRT7300 IC will be enabled.

Writing a "1" to Bit 3 of the Line Interface Driver Register (Address = 72h) will cause this

output pin to toggle "high". Writing a "0" to this bit-field will cause this output pin to toggle

"low".

Notes:

1. The user is advised to disable the B3ZS encoder (within the XRT7300 IC) if the

Transmit and Receive DS3 Framers (within the UNI) are configured to operate

in the B3ZS line code.

2. If the customer is not using the XRT7300 DS3 Line Transmitter IC, then he/

she can use this output pin for a variety of other purposes.

23

D2

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

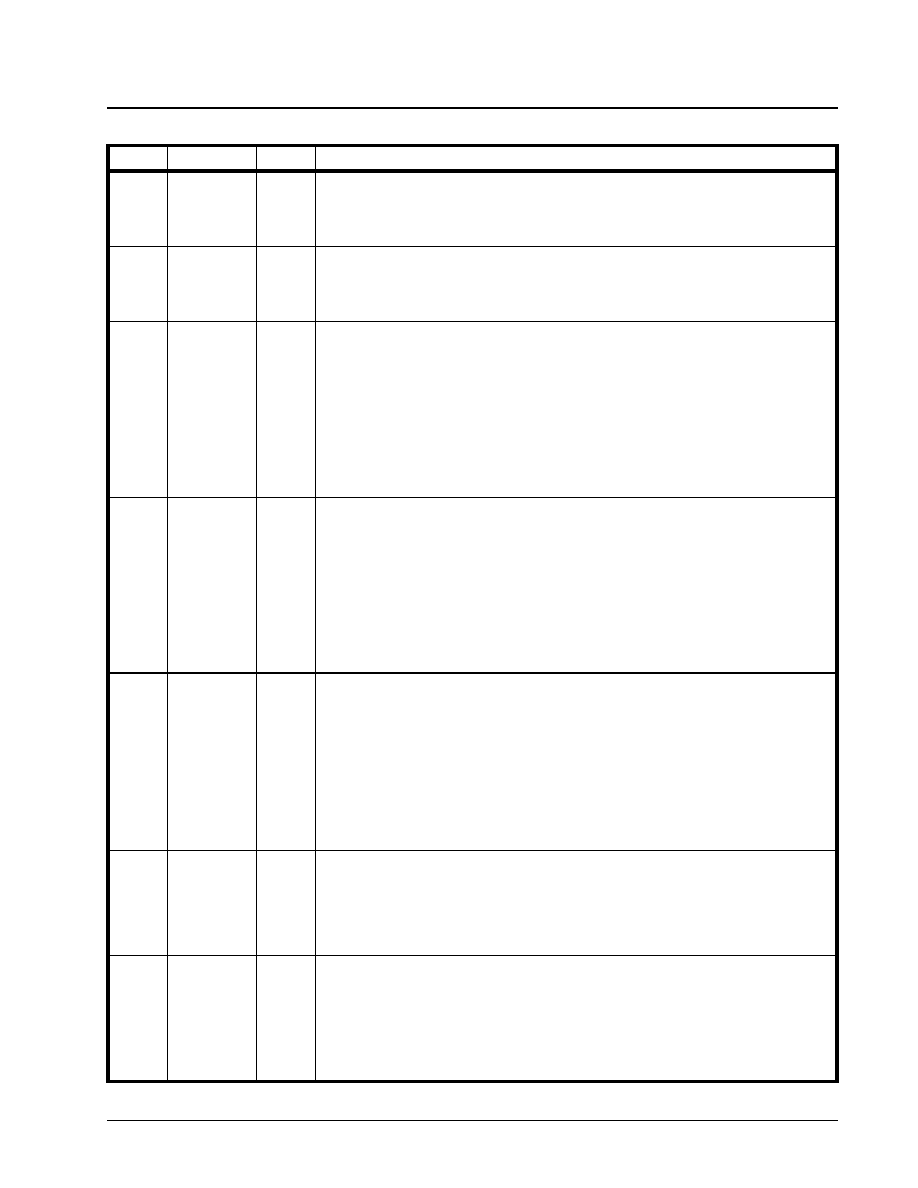

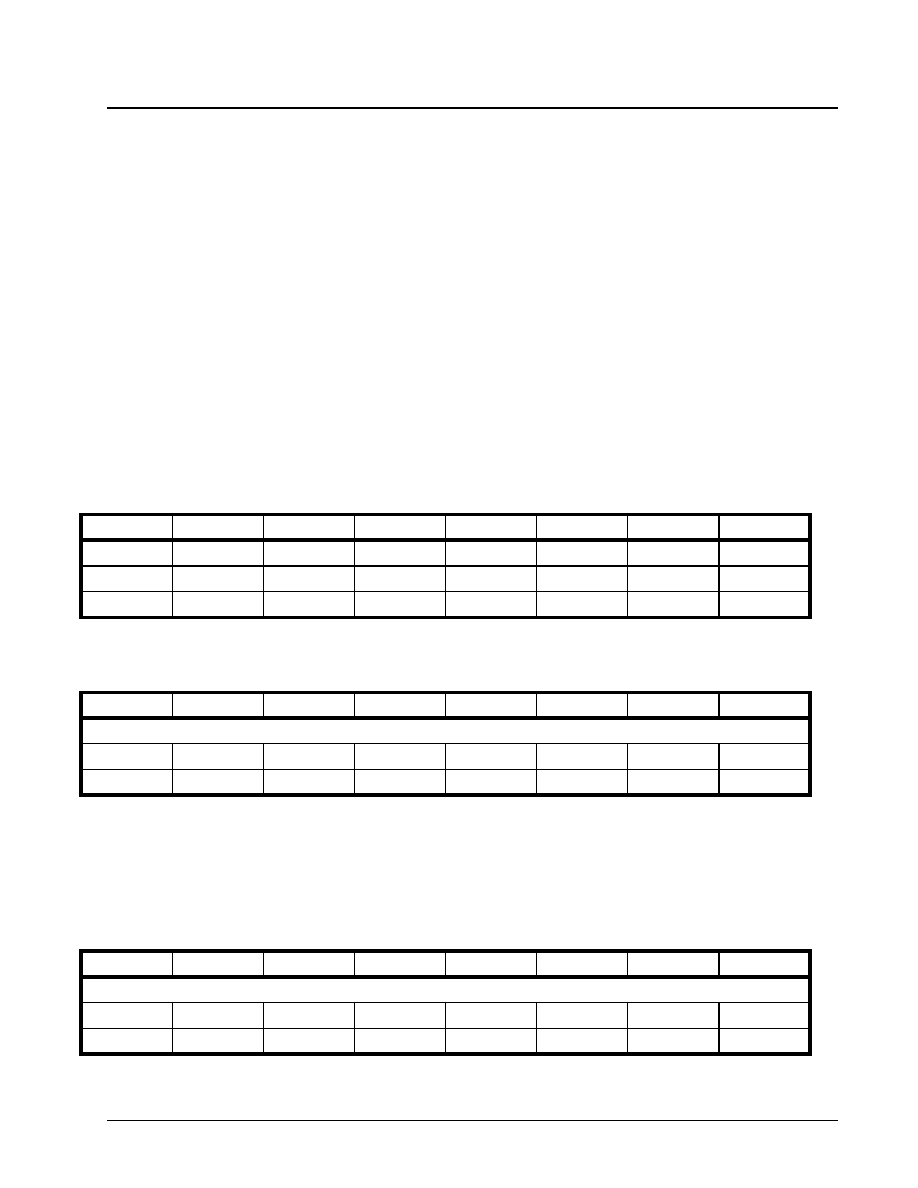

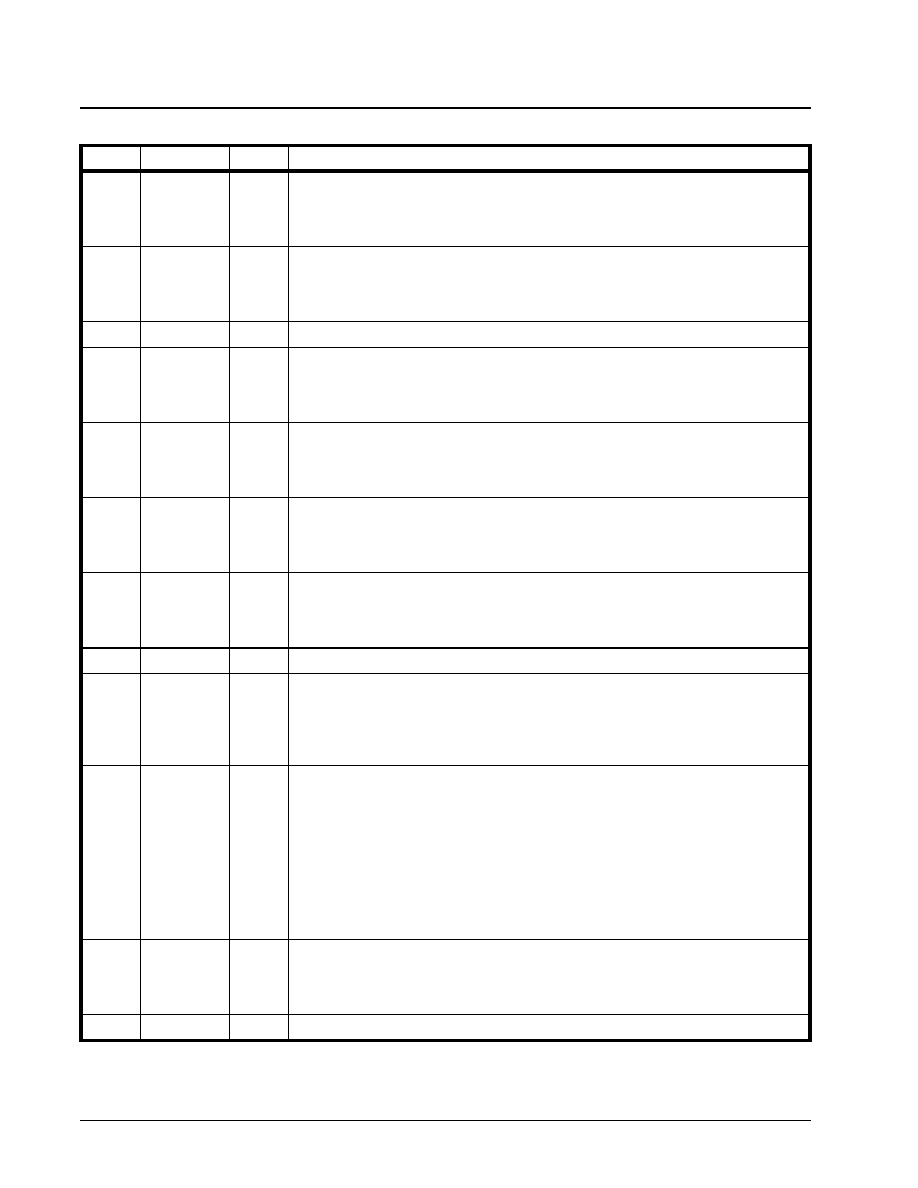

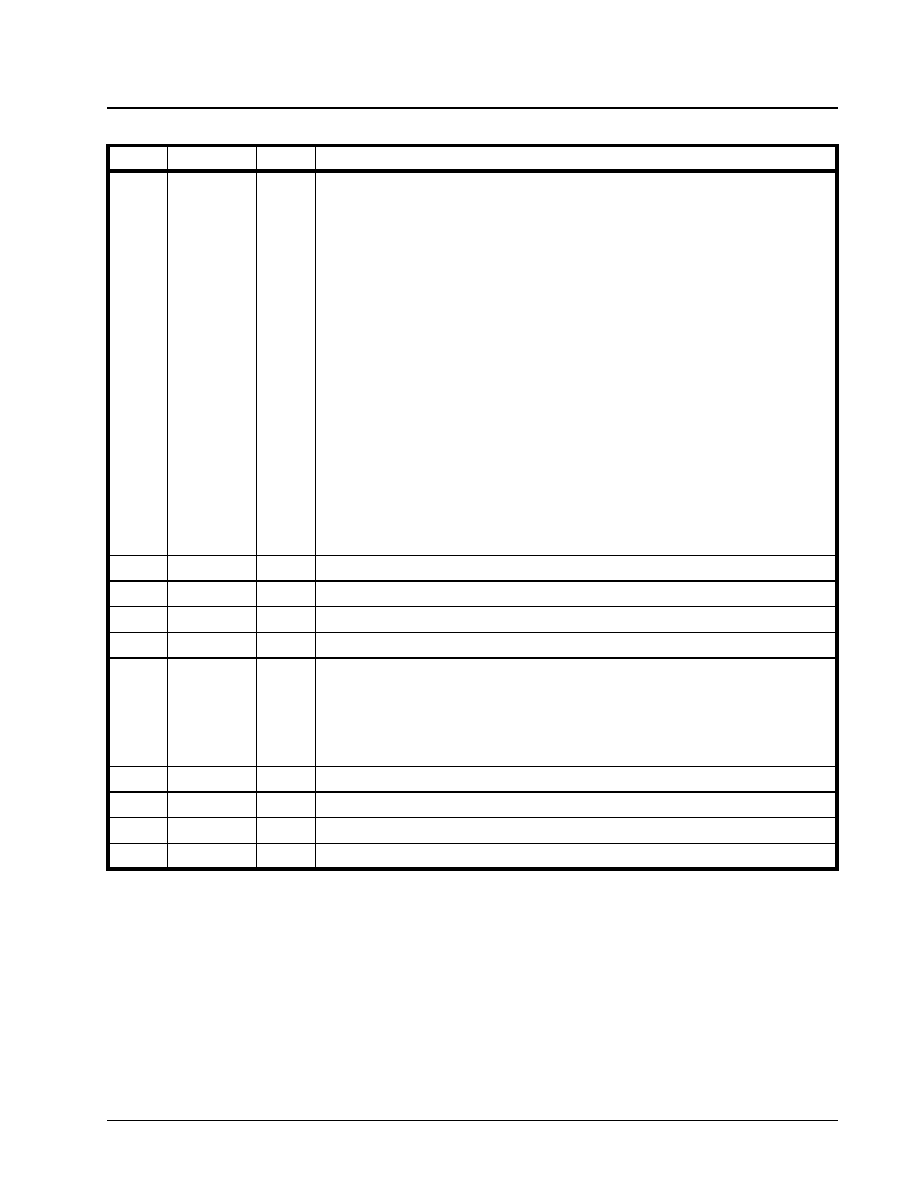

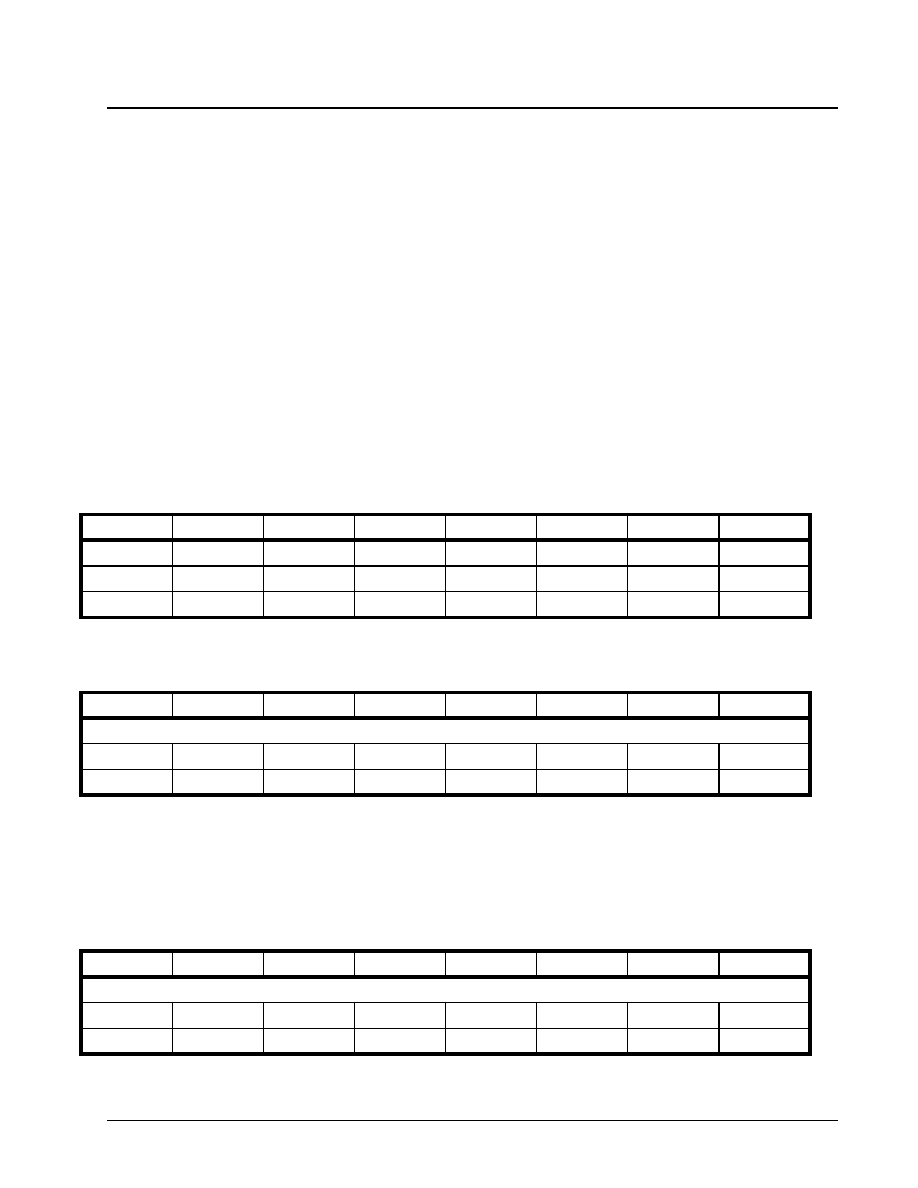

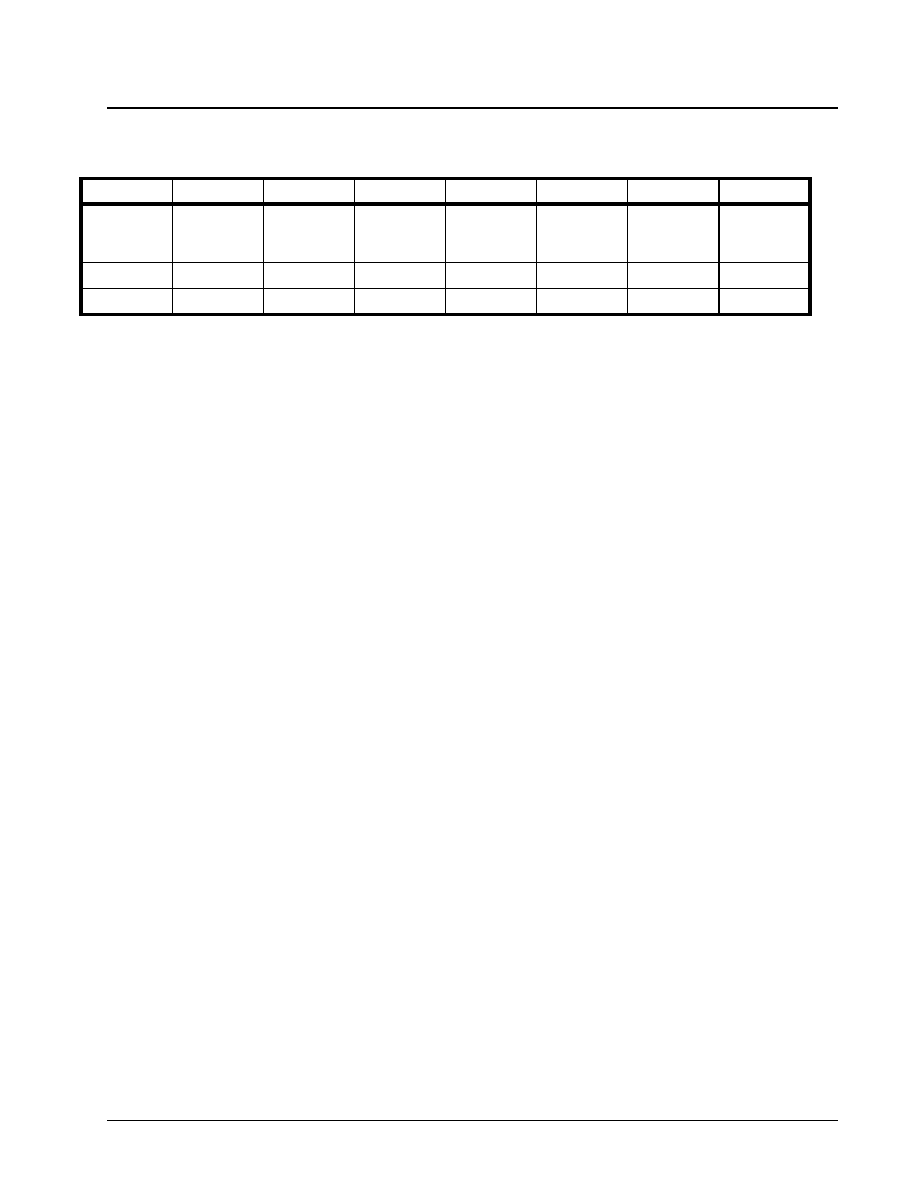

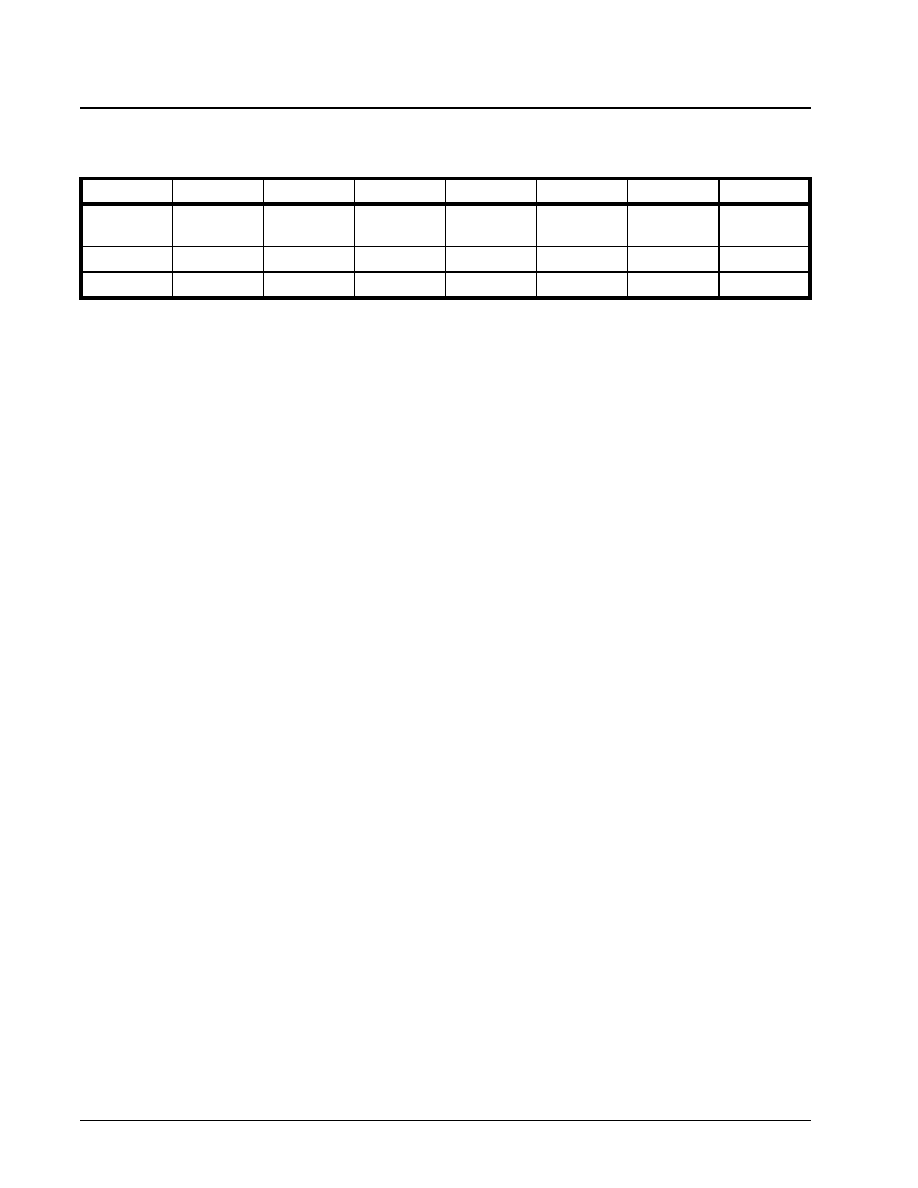

PIN DESCRIPTION (CONT'D)

P

IN

N

O

. S

YMBOL

T

YPE

D

ESCRIPTION

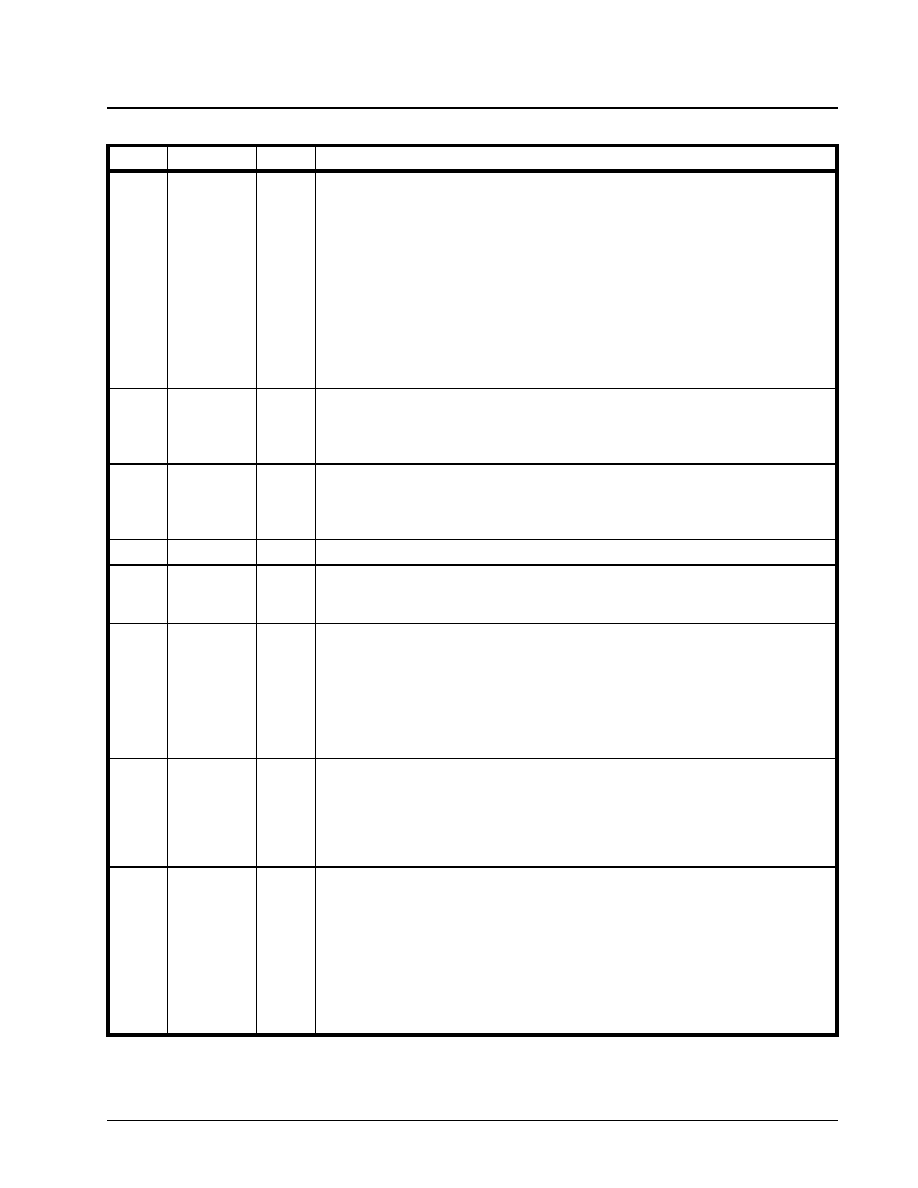

XRT7245

DS3 UNI FOR ATM

·Á

·Á

·Á

·Á

PRELIMINARY

REV. 1.03

12

24

TxLev

O

Transmit Line Build Enable/Disable Select (to be connected to the TxLev input

pin of the XRT7300 DS3/E3 LIU IC).

This output pin is intended to be connected to the TxLev input pin of the XRT7300 DS3/

E3 LIU IC. The user can control the state of this output pin by writing a "0" or a "1" to Bit

2 (TxLev) within the Line Interface Driver Register (Address = 72h).

If the user commands this signal to toggle "high" then it will disable the "Transmit Line

Build-Out" circuitry within the XRT7300 device. In this case, the XRT7300 device will

output unshaped (square-wave) pulses onto the "Transmit Line Signal". In order to

insure that the XRT7300 device generates a line signal that is compliant with the

Bellcore GR-499-CORE Pulse Template requirements (at the Cross-Connect), the

user is advised to set this output pin high, if the cable length (between the Transmit

Output of the XRT7300 device and the Cross-Connect) is greater than 225 feet.

Conversely, if the user commands this signal to toggle "high", then it will enable the

"Transmit Line Build-Out" circuitry within the XRT7300 device. In this case, the

XRT7300 device will output shaped pulses onto the "Transmit Line Signal". In order to

ensure that the XRT7300 device generates a line signal that is compliant with the

Bellcore GR-499-CORE Pulse Template requirements (at the Cross-Connect), the

user is advised to set this output pin low, if the cable length (between the Transmit

Output of the XRT7300 device and the Cross Connect) is less than 225 ft. of cable.

Writing a "1" to Bit 2 of the Line Interface Drive Register (Address = 72h) will cause this

output pin to toggle "high". Writing a "0" to this bit-field will cause this output pin to toggle

"low".

Note: If the customer is not using the XRT7300 DS3/E3 LIU IC, then he/she can use

this output pin for a variety of other purposes.

25

D1

I/O

Bi-Directional Data bus (Microprocessor Interface Section): (Please see descrip-

tion for D15)

26

RLOOP

O

Remote Loop-back Output Pin (to the XRT7300 DS3/E3 LIU IC).

This output pin is intended to be connected to the RLOOP input pin of the XRT7300 LIU

IC. The user can command this signal to toggle "high" and, in turn, force the XRT7300