Exar

Corporation 48720 Kato Road, Fremont CA, 94538

·

(510) 668-7000

·

FAX (510) 668-7017

·

www.exar.com

áç

áç

áç

áç

PRELIMINARY

XRT72L52

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

JANUARY 2001

REV. P1.1.3

GENERAL DESCRIPTION

The XRT72L52, 2 Channel DS3/E3 Framer IC is de-

signed to accept "User Data" from the Terminal

Equipment and insert this data into the "payload" bit-

fields within an "outbound" DS3/E3 Data Stream. Fur-

ther, the Framer IC is also designed to receive an "in-

bound" DS3/E3 Data Stream (from the Remote Ter-

minal Equipment) and extract out the "User Data".

The XRT72L52 DS3/E3 Framer device is designed to

support full-duplex data flow between Terminal Equip-

ment and an LIU (Line Interface Unit) IC. The Framer

Device will transmit, receive and process data in the

DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and E3-

ITU-T G.832 Framing Formats.

The XRT72L52 DS3/E3 Framer IC consists of two

Transmit sections, two Receiver sections, two Perfor-

mance Monitor Sections and a Microprocessor inter-

face.

The Transmit Sections, include a Transmit Payload

Data Input Interface, a Transmit Overhead data Input

Interface Section, a Transmit HDLC Controller, a

Transmit DS3/E3 Framer block and a Transmit LIU In-

terface Block which permits the Terminal Equipment

to transmit data to a remote terminal.

The Receive Sections, consist of a Receive LIU Inter-

face, a Receive DS3/E3 Framer, a Receive HDLC

Controller, a Receive Payload Data Output Interface,

and a Receive Overhead Data Interface which allows

the local terminal equipment to receive data from re-

mote terminal equipment.

The Microprocessor Interface is used to configure the

Framer IC in different operating modes and monitor

the performance of the Framer.

The Performance Monitor Sections consist of a large

number of "Reset-upon-Read" and "Read-Only" reg-

isters that contain cumulative and "one-second" sta-

tistics that reflect the performance/health of the two

channels of the Framer IC/system.

FEATURES

· Transmits, Receives and Processes data in the

DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and

E3-ITU-T G.832 Framing Formats.

· 2 Channel HDLC Controller - Tx and Rx

· Interfaces to all Popular Microprocessors

· Integrated Framer Performance Monitor

· Available in a 160 Pin PQFP package

· 3.3V Power Supply with 5V Tolerant I/O

· Operating Temperature -40°C to +85°C

APPLICATIONS

· Network Interface Units

· CSU/DSU Equipment.

· PCM Test Equipment

· Fiber Optic Terminals

· DS3/E3 Frame Relay Equipment

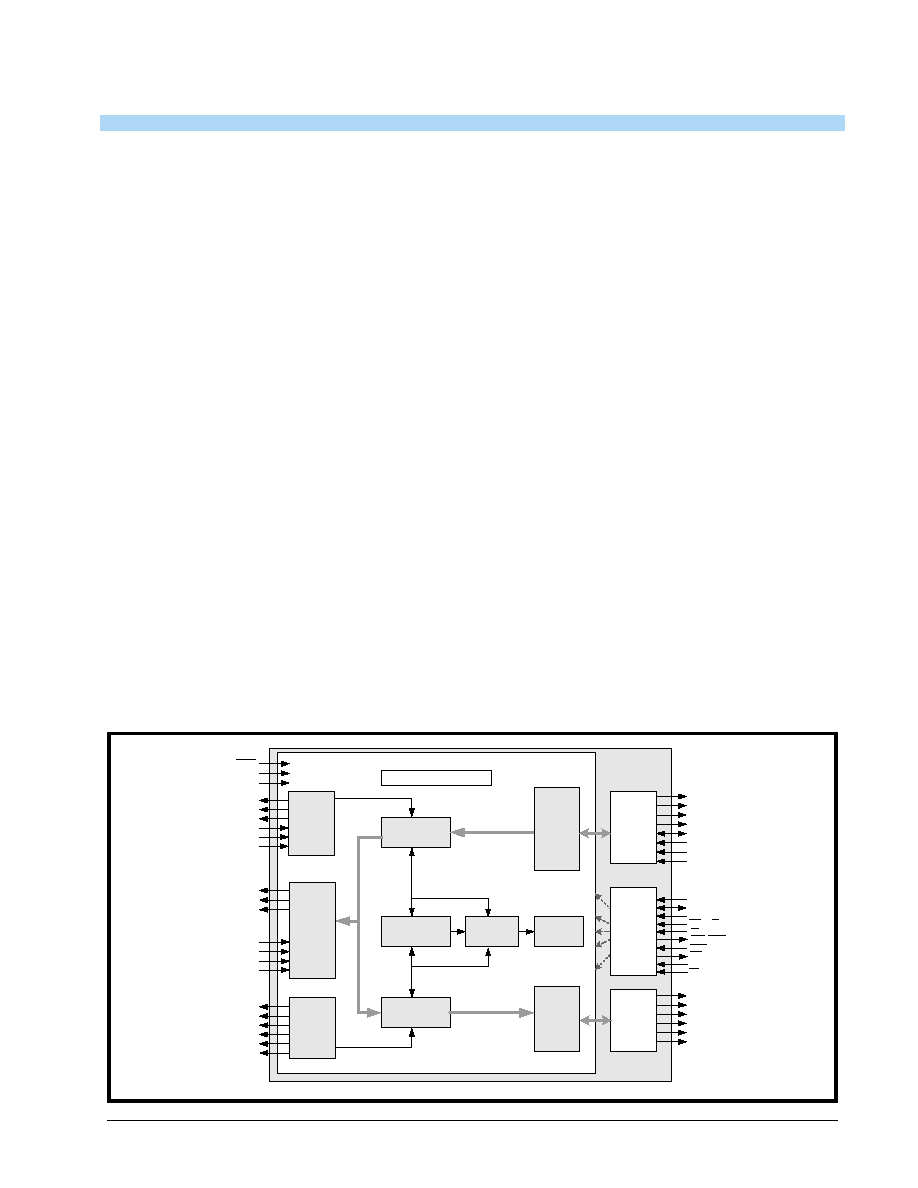

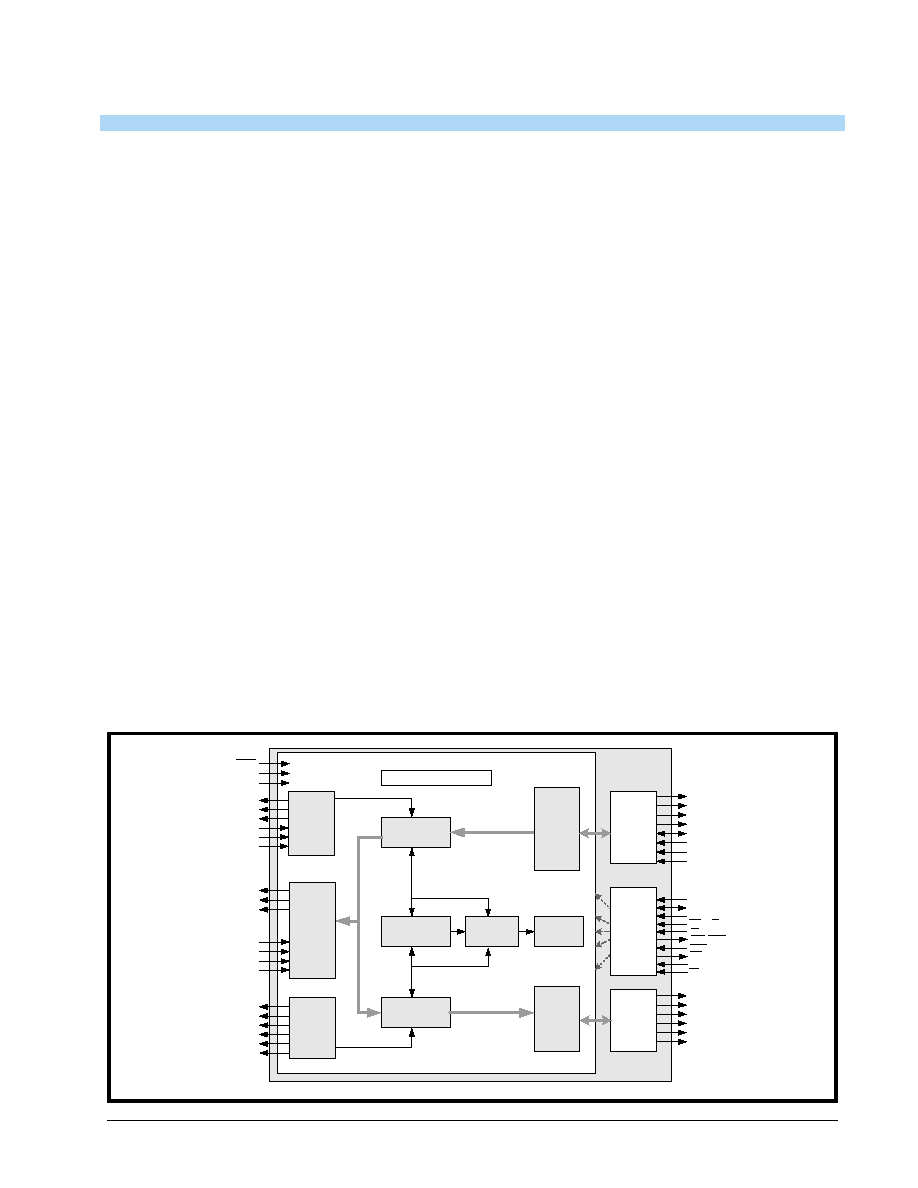

F

IGURE

1. B

LOCK

D

IAGRAM

OF

THE

XRT72L52

T3/E3 Transmit

Framer

T3 FEAC & Data

Link Controller

T3/E3 Receive

Framer

Performance

Monitor

Interrupt

Controller

TxOHInd[n:0]

TxNibFrame[n:0]

TxFrame[n:0]

TxNibClk[n:0]

TxLnClk[n:0]

TxFrameRef[n:0]

TxNib[n:0]

TxSer[n:0]

T3/E3

transmit

Input

RxClk[n:0]

RxOHind[n:0]

RxFrame[n:0]

RxNib[n:0]

RxSer[n:0]

RxOUTClk[n:0]

T3/E3

Receive

Output

uP

Interface

Typical Channel n

Where n = 0 or 1

TxLineClk[n:0]

TxPOS[n:0]

TxNEG[n:0]

RxLineClk[n:0]

RxPOS[n:0]

RxNEG[n:0]

ExtLOS

LIU

Interface/

Controller

TxOHEnable

TxOHClk

TxOHFrame

TxAISEn

TxOH

TxOHIns

T3/E3

Transmit

Overhead

Interface

RxOHEnable[n:0]

RxOHClk[n:0]

RxOH[n:0]

RxRed[n:0]

RxOHFrame[n:0]

RxOOF[n:0]

T3/E3

Receive

Overhead

Interface

HDLC

controller

HDLC

controller

Reset

TestMode

NibbleLnTF

A(11:0)

D(7:0)

ALE_AS

WR_R/W

CS

RDY_DTCK

Reset

INT

MOTO

RD_DS

XRT72L52

áç

áç

áç

áç

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

REV. P1.1.3

PRELIMINARY

2

ORDERING INFORMATION

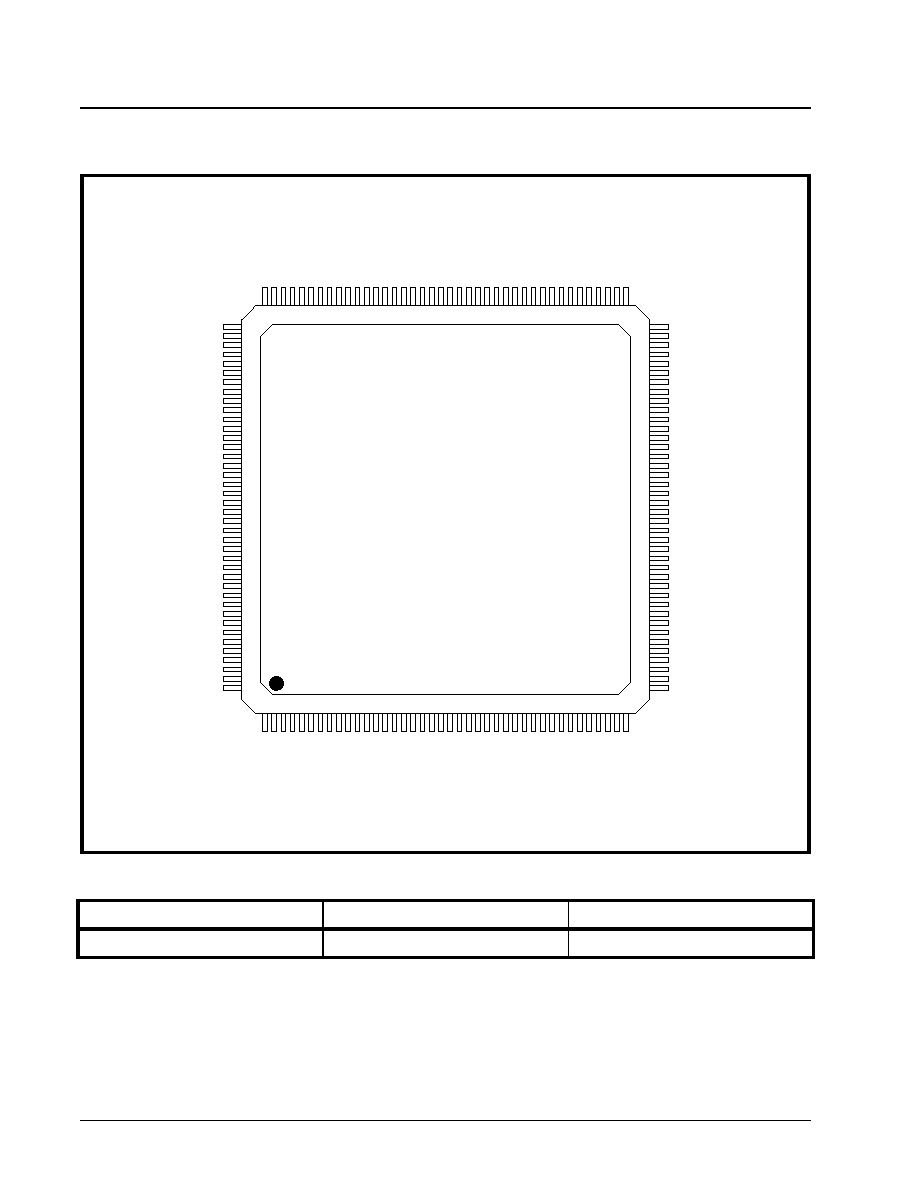

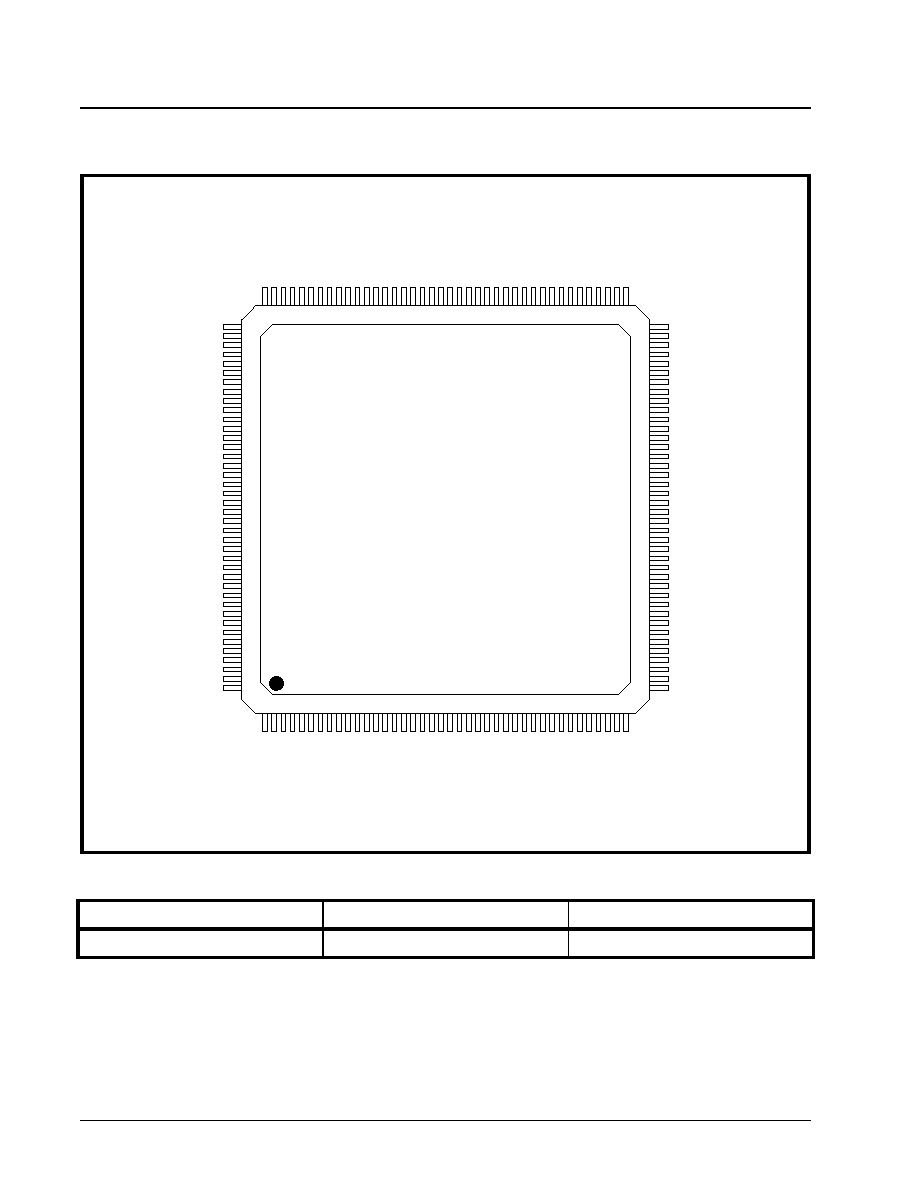

F

IGURE

2. P

IN

O

UT

OF

THE

XRT72L52

XRT72L52

R x N i b 0 [ 0 ] / R x H D L C D a t 0 [ 0 ]

R x F r a m e [ 0 ]

V D D

R x O H I n d [ 0 ]

RxSer[0]/RxIdle[0]

R x C l k [ 0 ]

G N D

T x F r a m e [ 0 ]

T x N i b F r a m e [ 0 ] / V a l F C S [ 0 ]

T x N I B C l k [ 0 ] / S n d F C S [ 0 ]

T x O H I n d [ 0 ] / T x H D L C D a t 6 [ 0 ]

G N D

T x S e r [ 0 ] / S n d M s g [ 0 ]

T x N i b 3 [ 0 ] / T x H D L C D a t 3 [ 0 ]

T x N i b 2 [ 0 ] / T x H D L C D a t 2 [ 0 ]

T x N i b 1 [ 0 ] / T x H D L C D a t 1 [ 0 ]

T x N i b 0 [ 0 ] / T x H D L C D a t 0 [ 0 ]

T x A I S E n [ 0 ]

T x O H [ 0 ] / T x H D L C D a t 5 [ 0 ]

T x O H I n s [ 0 ] / T x H D L C D a t 4 [ 0 ]

V D D

T x O H E n a b l e [ 0 ] / T x H D L C D a t 7 [ 0 ]

T x O H C l k [ 0 ]

T x O H F r a m e [ 0 ] / T x H D L C C l k [ 0 ]

R x O H E n a b l e [ 0 ] / R x H D L C D a t 5 [ 0 ]

R x O H F r a m e [ 0 ] / R x H D L C D a t 4 [ 0 ]

R x O H C l k [ 0 ] / R x H D L C C l k [ 0 ]

R x O H [ 0 ] / R x H D L C D a t 6 [ 0 ]

G N D

D M O [ 0 ]

E x t L O S [ 0 ]

R L O L [ 0 ]

G N D

N C

R L O O P [ 0 ]

L L O O P [ 0 ]

R e q [ 0 ]

T A O S [ 0 ]

R x R e d [ 0 ]

R x A I S [ 0 ]

T x N i b 3 [ 1 ] / T x H D L C D a t 3 [ 1 ]

T x S e r [ 1 ] / S n d M s g [ 1 ]

G N D

T x O H I n d [ 1 ] / T x H D L C D a t 6 [ 1 ]

T x N I B C l k [ 1 ] / S n d F C S [ 1 ]

T x F r a m e [ 1 ]

T x N i b F r a m e [ 1 ] / V a l F C S [ 1 ]

R x F r a m e [ 1 ]

RxSer[1]/RxIdle[1]

V D D

R x C l k [ 1 ]

R x N i b 0 [ 1 ] / R x H D L C D a t 0 [ 1 ]

R x N i b 1 [ 1 ] / R x H D L C D a t 1 [ 1 ]

R x N i b 2 [ 1 ] / R x H D L C D a t 2 [ 1 ]

R x N i b 3 [ 1 ] / R x H D L C D a t 3 [ 1 ]

R x O H I n d [ 1 ]

G N D

R x O H C l k [ 1 ] / R x H D L C C l k [ 1 ]

R x O H E n a b l e [ 1 ] / R x H D L C D a t 5 [ 1 ]

R x O H F r a m e [ 1 ] / R x H D L C D a t 4 [ 1 ]

R x O H [ 1 ] / R x H D L C D a t 6 [ 1 ]

T x O H C l k [ 1 ]

T x O H F r a m e [ 1 ] / T x H D L C C l k [ 1 ]

T x O H E n a b l e [ 1 ] / T x H D L C D a t 7 [ 1 ]

V D D

T x O H I n s [ 1 ] / T x H D L C D a t 4 [ 1 ]

T x O H [ 1 ] / T x H D L C D a t 5 [ 1 ]

T x A I S E n [ 1 ]

G N D

T x L e v [ 1 ]

E n c o D i s [ 1 ]

R x L O S [ 1 ]

R x O O F [ 1 ]

R x A I S [ 1 ]

R x R e d [ 1 ]

T A O S [ 1 ]

R e q [ 1 ]

L L O O P [ 1 ]

R L O O P [ 1 ]

G N D

RxNib1[0]/RxHDLCDat1[0]

RxNib2[0]/RxHDLCDat2[0]

RxNib3[0]/RxHDLCDat3[0]

NC

Int

Rdy_Dtck

GND

D(7)

D(6)

D(5)

D(4)

VDD

D(3)

D(2)

D(1)

D(0)

GND

A(9)

A(8)

A(7)

A(6)

A(5)

A(4)

A(3)

A(2)

A(1)

A(0)

NC

ALE_AS

WR_RW

CS

MOTO

Reset

NibbleIntf

TestMode

Rd_DS

NC

TxNib0[1]/TxHDLCDat0[1]

TxNib1[1]/TxHDLCDat1[1]

TxNib2[1]/TxHDLCDat2[1]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

1 2 1

1 2 2

1 2 3

1 2 4

1 2 5

1 2 6

1 2 7

1 2 8

1 2 9

1 3 0

1 3 1

1 3 2

1 3 3

1 3 4

1 3 5

1 3 6

1 3 7

1 3 8

1 3 9

1 4 0

1 4 1

1 4 2

1 4 3

1 4 4

1 4 5

1 4 6

1 4 7

1 4 8

1 4 9

1 5 0

1 5 1

1 5 2

1 5 3

1 5 4

1 5 5

1 5 6

1 5 7

1 5 8

1 5 9

1 6 0

8 0

7 9

7 8

7 7

7 6

7 5

7 4

7 3

7 2

7 1

7 0

6 9

6 8

6 7

6 6

6 5

6 4

6 3

6 2

6 1

6 0

5 9

5 8

5 7

5 6

5 5

5 4

5 3

5 2

5 1

5 0

4 9

4 8

4 7

4 6

4 5

4 4

4 3

4 2

4 1

12

0

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

VDD

RxOOF[0]

RxLOS[0]

EncoDis[0]

TxLev[0]

GND

NC

TDI

TCK

NC

TRST

TMS

GND

TDO

RxOutClk[0]RxHDLCDat7[0]

TxNEG[0]

TxPOS[0]

TxLineClk[0]

VDD

TxFrameRef[0]

RxNEG[0]

TxInClk[0]

RxPOS[0]

RxLineClk[0]

NC

TxFrameRef[1]

RxNEG[1]

TxInClk[1]

RxPOS[1]

RxLineClk[1]

GND

TxLineClk[1]

TxPOS[1]

TxNEG[1]

RxOutClk[1]/RxHDLCDat7[1]

VDD

NC

DMO[1]

ExtLOS[1]

RLOL[1]

P

ART

N

UMBER

P

ACKAGE

T

YPE

O

PERATING

T

EMPERATURE

R

ANGE

XRT72L52

28x28mm 160 lead QFP

-40°C to +85°C

áç

áç

áç

áç

XRT72L52

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

PRELIMINARY

REV. P1.1.3

I

TABLE OF CONTENTS

GENERAL DESCRIPTION ............................................................................................... 1

FEATURES

................................................................................................................................................. 1

APPLICATIONS

........................................................................................................................................... 1

Figure 1. Block Diagram of the XRT72L52 ............................................................................................ 1

Figure 2. Pin Out of the XRT72L52 ........................................................................................................ 2

ORDERING INFORMATION ............................................................................................ 2

PIN DESCRIPTIONS ........................................................................................................ 3

ELECTRICAL CHARACTERISTICS .............................................................................. 24

A

BSOLUTE

M

AXIMUMS

............................................................................................................................. 24

DC E

LECTRICAL

C

HARACTERISTICS

......................................................................................................... 24

AC E

LECTRICAL

C

HARACTERISTICS

......................................................................................................... 24

AC E

LECTRICAL

C

HARACTERISTICS

(C

ONT

.) ............................................................................................ 26

1.0 Timing Diagrams ................................................................................................................................. 30

Figure 3. Timing Diagram for Transmit Payload Input Interface, when the XRT72L52 Device is operating in

both the DS3 and Loop-Timing Modes ................................................................................................. 30

Figure 4. Timing Diagram for the Transmit Payload Input Interface, when the XRT72L52 Device is operating

in both the DS3 and Local-Timing Modes ............................................................................................. 30

Figure 5. Timing Diagram for the Transmit Payload Data Input Interface, when the XRT72L52 Device is

operating in both the DS3/Nibble and Looped-Timing Modes .............................................................. 31

Figure 6. Timing Diagram for the Transmit Payload Data Input Interface, when the XRT72L52 Device is

operating in the DS3/Nibble and Local-Timing Modes .......................................................................... 31

Figure 7. Timing Diagram for the Transmit Overhead Data Input Interface (Method 1 Access) .......... 32

Figure 8. Timing Diagram for the Transmit Overhead Data Input Interface (Method 2 Access) .......... 32

Figure 9. Transmit LIU Interface Timing - Framer is configured to update "TxPOS" and "TxNEG" on the

rising edge of "TxLineClk" ..................................................................................................................... 33

Figure 10. Transmit LIU Interface Timing - Framer is configured to update "TxPOS" and "TxNEG" on the

falling edge of "TxLineClk" .................................................................................................................... 33

Figure 11. Receive LIU Interface Timing - Framer is configured to sample "RxPOS" and "RxNEG" on the

rising edge of "RxLineClk" ..................................................................................................................... 34

Figure 12. Receiver LIU Interface Timing - Framer is configured to sample "RxPOS" and "RxNEG" on the

falling edge of "RxLineClk" .................................................................................................................... 34

Figure 13. Receive Payload Data Output Interface Timing .................................................................. 35

Figure 14. Receive Payload Data Output Interface Timing (Nibble Mode Operation) ......................... 35

Figure 15. Receive Overhead Data Output Interface Timing (Method 1 - Using RxOHClk) ................ 36

Figure 16. Receive Overhead Data Output Interface Timing (Method 2 - Using RxOHEnable) .......... 36

Figure 17. Microprocessor Interface Timing - Intel Type Programmed I/O Read Operations .............. 37

Figure 18. Microprocessor Interface Timing - Intel Type Programmed I/O Write Operations .............. 37

Figure 19. Microprocessor Interface Timing - Intel Type Read Burst Access Operation ..................... 38

Figure 20. Microprocessor Interface Timing - Intel type Write Burst Access Operation ....................... 38

Figure 21. Microprocessor Interface Timing - Motorola Type Programmed I/O Read Operation ........ 39

Figure 22. Microprocessor Interface Timing - Motorola Type Programmed I/O Write Operation ......... 39

Figure 23. Microprocessor Interface Timing - Reset Pulse Width ........................................................ 40

2.0 The Microprocessor Interface Block ................................................................................................. 41

2.1 C

HANNEL

S

ELECTION

WITHIN

THE

XRT72L52 D

EVICE

.......................................................................................... 41

T

ABLE

1: T

HE

R

ELATIONSHIP

BETWEEN

A

DDRESS

B

ITS

A(9)

AND

THE

S

ELECTED

C

ONFIGURATION

R

EGISTER

B

ANK

...................................................................................................................................................... 41

Figure 24. Simple Block Diagram of the Microprocessor Interface Block, within the Framer IC .......... 42

2.2 T

HE

M

ICROPROCESSOR

I

NTERFACE

B

LOCK

S

IGNAL

.............................................................................................. 42

T

ABLE

2: D

ESCRIPTION

OF

THE

M

ICROPROCESSOR

I

NTERFACE

S

IGNALS

THAT

EXHIBIT

CONSTANT

ROLES

IN

BOTH

THE

I

NTEL

AND

M

OTOROLA

M

ODES

.......................................................................................................... 43

T

ABLE

3: P

IN

D

ESCRIPTION

OF

M

ICROPROCESSOR

I

NTERFACE

S

IGNALS

- W

HILE

THE

M

ICROPROCESSOR

I

NTER

-

FACE

IS

O

PERATING

IN

THE

I

NTEL

M

ODE

.................................................................................................. 43

XRT72L52

áç

áç

áç

áç

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

REV. P1.1.3

PRELIMINARY

II

T

ABLE

4: P

IN

D

ESCRIPTION

OF

THE

M

ICROPROCESSOR

I

NTERFACE

S

IGNALS

WHILE

THE

M

ICROPROCESSOR

I

N

-

TERFACE

IS

OPERATING

IN

THE

M

OTOROLA

M

ODE

..................................................................................... 44

2.3 I

NTERFACING

THE

XRT72L52 DS3/E3 F

RAMER

TO

THE

L

OCAL

µC/µP

VIA

THE

M

ICROPROCESSOR

I

NTERFACE

B

LOCK

44

2.3.1 Interfacing the XRT72L52 DS3/E3 Framer to the Microprocessor over an 8 bit wide bi-directional Data Bus

44

2.3.2 Data Access Modes ................................................................................................................................ 45

Figure 25. Behavior of Microprocessor Interface signals during an Intel-type Programmed I/O Read Oper-

ation ....................................................................................................................................................... 46

Figure 26. Behavior of the Microprocessor Interface Signals, during an Intel-type Programmed I/O Write

Operation ............................................................................................................................................... 47

Figure 27. Illustration of the Behavior of Microprocessor Interface signals, during a Motorola-type Pro-

grammed I/O Read Operation ............................................................................................................... 48

Figure 28. Illustration of the Behavior of the Microprocessor Interface signal, during a Motorola-type Pro-

grammed I/O Write Operation ............................................................................................................... 49

Figure 29. Behavior of the Microprocessor Interface Signals, during the Initial Read Operation of a Burst

Cycle (Intel Type Processor) ................................................................................................................. 50

Figure 30. Behavior of the Microprocessor Interface Signals, during subsequent Read Operations within

the Burst I/O Cycle ................................................................................................................................ 51

Figure 31. Behavior of the Microprocessor Interface signals, during the Initial Write Operation of a Burst

Cycle (Intel-type Processor) .................................................................................................................. 53

Figure 32. Behavior of the Microprocessor Interface Signals, during subsequent Write Operations within

the Burst I/O Cycle ................................................................................................................................ 54

Figure 33. Behavior of the Microprocessor Interface Signals, during the Initial Read Operation of a Burst

Cycle (Motorola Type Processor) .......................................................................................................... 55

Figure 34. Behavior the Microprocessor Interface Signals, during subsequent Read Operations within the

Burst I/O Cycle (Motorola-type µC/µP) .................................................................................................. 56

Figure 35. Behavior of the Microprocessor Interface signals, during the Initial Write Operation of a Burst

Cycle (Motorola-type Processor) ........................................................................................................... 57

Figure 36. Behavior of the Microprocessor Interface Signals, during subsequent Write Operations with the

Burst I/O Cycle (Motorola-type µC/µP) .................................................................................................. 58

2.4 O

N

-C

HIP

R

EGISTER

O

RGANIZATION

...................................................................................................................... 58

2.4.1 Framer Register Addressing .................................................................................................................... 58

T

ABLE

5: R

EGISTER

A

DDRESSING

OF

THE

F

RAMER

P

ROGRAMMER

R

EGISTERS

......................................... 59

2.4.2 Framer Register Description .................................................................................................................... 62

P

ART

N

UMBER

R

EGISTER

(A

DDRESS

= 0

X

02) .......................................................................................... 65

V

ERSION

N

UMBER

R

EGISTER

(A

DDRESS

= 0

X

03) ..................................................................................... 65

B

LOCK

I

NTERRUPT

E

NABLE

R

EGISTER

(A

DDRESS

= 0

X

04) ........................................................................ 65

B

LOCK

I

NTERRUPT

S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

05) ........................................................................ 66

TEST R

EGISTER

(A

DDRESS

= 0

X

0C) ....................................................................................................... 67

R

X

DS3 C

ONFIGURATION

& S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

10) ........................................................... 68

R

X

DS3 S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

11) ........................................................................................ 69

R

X

DS3 I

NTERRUPT

E

NABLE

R

EGISTER

(A

DDRESS

= 0

X

12) ....................................................................... 70

R

X

DS3 I

NTERRUPT

S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

13) ....................................................................... 71

R

X

DS3 SYNC D

ETECT

E

NABLE

R

EGISTER

(A

DDRESS

= 0

X

14) ................................................................ 73

R

X

DS3 FEAC I

NTERRUPT

E

NABLE

/S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

17) ............................................... 73

R

X

DS3 LAPD C

ONTROL

R

EGISTER

(A

DDRESS

= 0

X

18) ........................................................................... 74

R

X

DS3 LAPD S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

19) .............................................................................. 75

2.4.3 Receive E3 Framer Configuration Registers (ITU-T G.832) .................................................................... 75

R

X

E3 C

ONFIGURATION

& S

TATUS

R

EGISTER

1 (A

DDRESS

= 0

X

10) ........................................................... 76

R

X

E3 C

ONFIGURATION

& S

TATUS

R

EGISTER

2 (A

DDRESS

= 0

X

11) ........................................................... 77

R

X

E3 I

NTERRUPT

E

NABLE

R

EGISTER

- 1 (A

DDRESS

= 0

X

12) .................................................................... 78

R

X

E3 I

NTERRUPT

E

NABLE

R

EGISTER

- 2 (A

DDRESS

= 0

X

13) .................................................................... 79

R

X

E3 I

NTERRUPT

S

TATUS

R

EGISTER

- 1 (A

DDRESS

= 0

X

14) .................................................................... 79

R

X

E3 I

NTERRUPT

S

TATUS

R

EGISTER

- 2 (A

DDRESS

= 0

X

15) .................................................................... 81

áç

áç

áç

áç

XRT72L52

TWO CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

PRELIMINARY

REV. P1.1.3

III

R

X

E3 LAPD C

ONTROL

R

EGISTER

(A

DDRESS

= 0

X

18) ............................................................................. 82

R

X

E3 LAPD S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

19) ................................................................................ 82

R

X

E3 NR B

YTE

R

EGISTER

(A

DDRESS

= 0

X

1A) ........................................................................................ 83

R

X

E3 GC B

YTE

R

EGISTER

(A

DDRESS

= 0

X

1B) ....................................................................................... 83

R

X

E3 TTB-0 R

EGISTER

(A

DDRESS

= 0

X

1C) ............................................................................................ 84

R

X

E3 TTB-1 R

EGISTER

(A

DDRESS

= 0

X

1D) ............................................................................................ 84

R

X

E3 TTB-2 R

EGISTER

(A

DDRESS

= 0

X

1E) ............................................................................................ 84

R

X

E3 TTB-3 R

EGISTER

(A

DDRESS

= 0

X

1F) ............................................................................................ 85

R

X

E3 TTB-4 R

EGISTER

(A

DDRESS

= 0

X

20) ............................................................................................ 85

R

X

E3 TTB-5 R

EGISTER

(A

DDRESS

= 0

X

21) ............................................................................................ 85

R

X

E3 TTB-6 R

EGISTER

(A

DDRESS

= 0

X

22) ............................................................................................ 85

R

X

E3 TTB-7 R

EGISTER

(A

DDRESS

= 0

X

23) ............................................................................................ 86

R

X

E3 TTB-8 R

EGISTER

(A

DDRESS

= 0

X

24) ............................................................................................ 86

R

X

E3 TTB-9 R

EGISTER

(A

DDRESS

= 0

X

25) ............................................................................................ 86

R

X

E3 TTB-10 R

EGISTER

(A

DDRESS

= 0

X

26) .......................................................................................... 87

R

X

E3 TTB-11 R

EGISTER

(A

DDRESS

= 0

X

27) .......................................................................................... 87

R

X

E3 TTB-12 R

EGISTER

(A

DDRESS

= 0

X

28) .......................................................................................... 87

R

X

E3 TTB-13 R

EGISTER

(A

DDRESS

= 0

X

29 ........................................................................................... 87

R

X

E3 TTB-14 R

EGISTER

(A

DDRESS

= 0

X

2A) .......................................................................................... 88

R

X

E3 TTB-15 R

EGISTER

(A

DDRESS

= 0

X

2B) .......................................................................................... 88

R

X

E3

SSM

R

EGISTER

(A

DDRESS

= 0

X

2B) ................................................................................................ 88

2.4.4 Receive E3 Framer Configuration Registers (ITU-T G.751) ................................................................... 89

R

X

E3 C

ONFIGURATION

& S

TATUS

R

EGISTER

- 1 G.751 (A

DDRESS

= 0

X

10) ............................................. 89

R

X

E3 C

ONFIGURATION

& S

TATUS

R

EGISTER

- 2 (A

DDRESS

= 0

X

11) ........................................................ 89

R

X

E3 I

NTERRUPT

E

NABLE

R

EGISTER

- 1 (A

DDRESS

= 0

X

12) ................................................................... 90

R

X

E3 I

NTERRUPT

E

NABLE

R

EGISTER

- 2 (A

DDRESS

= 0

X

13) ................................................................... 91

R

X

E3 I

NTERRUPT

S

TATUS

R

EGISTER

- 1 (A

DDRESS

= 0

X

14) ................................................................... 91

R

X

E3 I

NTERRUPT

S

TATUS

R

EGISTER

- 2 (A

DDRESS

= 0

X

15) ................................................................... 92

R

X

E3 LAPD C

ONTROL

R

EGISTER

(A

DDRESS

= 0

X

18) ............................................................................. 93

R

X

E3 LAPD S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

19) ................................................................................ 93

R

X

E3 S

ERVICE

B

IT

R

EGISTER

(A

DDRESS

= 0

X

1A) ................................................................................... 94

2.4.5 Transmit DS3 Configuration Registers .................................................................................................... 94

T

RANSMIT

DS3 C

ONFIGURATION

R

EGISTER

(A

DDRESS

= 0

X

30) ............................................................... 95

T

RANSMIT

DS3 FEAC C

ONFIGURATION

& S

TATUS

R

EGISTER

(A

DDRESS

= 0

X

31) .................................... 96

T

X

DS3 FEAC R

EGIS

T

ER

(A

DDRESS

= 0

X

32) .......................................................................................... 97

T

X

DS3 LAPD C

ONFIGURATION

R

EGISTER

(A

DDRESS

= 0

X

33) ................................................................. 97

T

X

DS3 LAPD S

TATUS

AND

I

NTERRUPT

R

EGISTER

(A

DDRESS

= 0

X

34) ..................................................... 98

T

X

DS3 M-B

IT

M

ASK

R

EGISTER

(A

DDRESS

= 0

X

35) ................................................................................. 98

T

X

DS3 F-B

IT

M

ASK

R

EGISTER

- 1 (A

DDRESS

= 0

X

36) ............................................................................. 99

T

X

DS3 F-B

IT

M

ASK

R

EGISTER

- 2 (A

DDRESS

= 0

X

37) ........................................................................... 100

T

X

DS3 F-B

IT

M

ASK

R

EGISTER

- 3 (A

DDRESS

= 0

X

38) ........................................................................... 100

T

X

DS3 F-B

IT

M

ASK

R

EGISTER

- 4 (A

DDRESS

= 0

X

39) ........................................................................... 100

2.4.6 Transmit E3 (ITU-T G.832) Configuration Registers ............................................................................. 100

T

X

E3 C

ONFIGURATION

R

EGISTER

(A

DDRESS

= 0

X

30) ............................................................................ 101

T

X

E3 LAPD C

ONFIGURATION

R

EGISTER

(A

DDRESS

= 0

X

33) ................................................................. 102

T

X

E3 LAPD S

TATUS

AND

I

NTERRUPT

R

EGISTER

(A

DDRESS

= 0

X

34) ...................................................... 102

T

X

E3 GC B

YTE

R

EGISTER

(A

DDRESS

= 0

X

35) ...................................................................................... 103

T

X

E3 MA B

YTE

R

EGISTER

(A

DDRESS

= 0

X

36) ...................................................................................... 104

T

X

E3 MA B

YTE

R

EGISTER

(A

DDRESS

= 0

X

36) ...................................................................................... 104

T

X

E3 NR B

YTE

R

EGISTER

(A

DDRESS

= 0

X

37) ...................................................................................... 104

T

X

E3 TTB-0 R

EGISTER

(A

DDRESS

= 0

X

38) ........................................................................................... 105

T

X

E3 TTB-1 R

EGISTER

(A

DDRESS

= 0

X

39) ........................................................................................... 105

T

X

E3 TTB-2 R

EGISTER

(A

DDRESS

= 0

X

3A) .......................................................................................... 105

T

X

E3 TTB-3 R

EGISTER

(A

DDRESS

= 0

X

3B) .......................................................................................... 106

T

X

E3 TTB-4 R

EGISTER

(A

DDRESS

= 0

X

3C) .......................................................................................... 106