Exar

Corporation 48720 Kato Road, Fremont CA, 94538

·

(510) 668-7000

·

FAX (510) 668-7017

·

www.exar.com

áç

áç

áç

áç

PRELIMINARY

XRT73L04

4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

SEPTEMBER 2000

REV. P1.0.5

GENERAL DESCRIPTION

The XRT73L04, 4-Channel, DS3/E3/STS-1 Line In-

terface Unit consists of four independent line trans-

mitters and receivers integrated on a single chip de-

signed for DS3, E3 or SONET STS-1 applications.

Each channel of the XRT73L04 can be configured to

support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or

the SONET STS-1 (51.84 Mbps) rates. Each channel

can be configured to operate in a mode/data rate that

is independent of the other channels.

In the transmit direction, each channel encodes input

data to either B3ZS (DS3/STS-1) or HDB3 (E3) for-

mat and converts the data into the appropriate pulse

shapes for transmission over coaxial cable via a 1:1

transformer.

In the receive direction, the XRT73L04 performs

equalization on incoming signals, performs Clock Re-

covery, decodes data from either B3ZS or HDB3 for-

mat, converts the receive data into TTL/CMOS for-

mat, checks for LOS or LOL conditions and detects

and declares the occurrence of Line Code Violations.

FEATURES

· Meets E3/DS3/STS-1 Jitter Tolerance Require-

ments

· Contains a 4-Wire Microprocessor Serial Interface

· Full Loop-Back Capability

· Transmit and Receive Power Down Modes

· Full Redundancy Support

· Uses Minimum External components

· Single +3.3V Power Supply

· 5V tolerant I/O

· -40°C to +85°C Operating Temperature Range

· Available in a Thermally Enhanced 144 pin TQFP

package

APPLICATIONS

· Digital Cross Connect Systems

· CSU/DSU Equipment

· Routers

· Fiber Optic Terminals

· Multiplexers

· ATM Switches

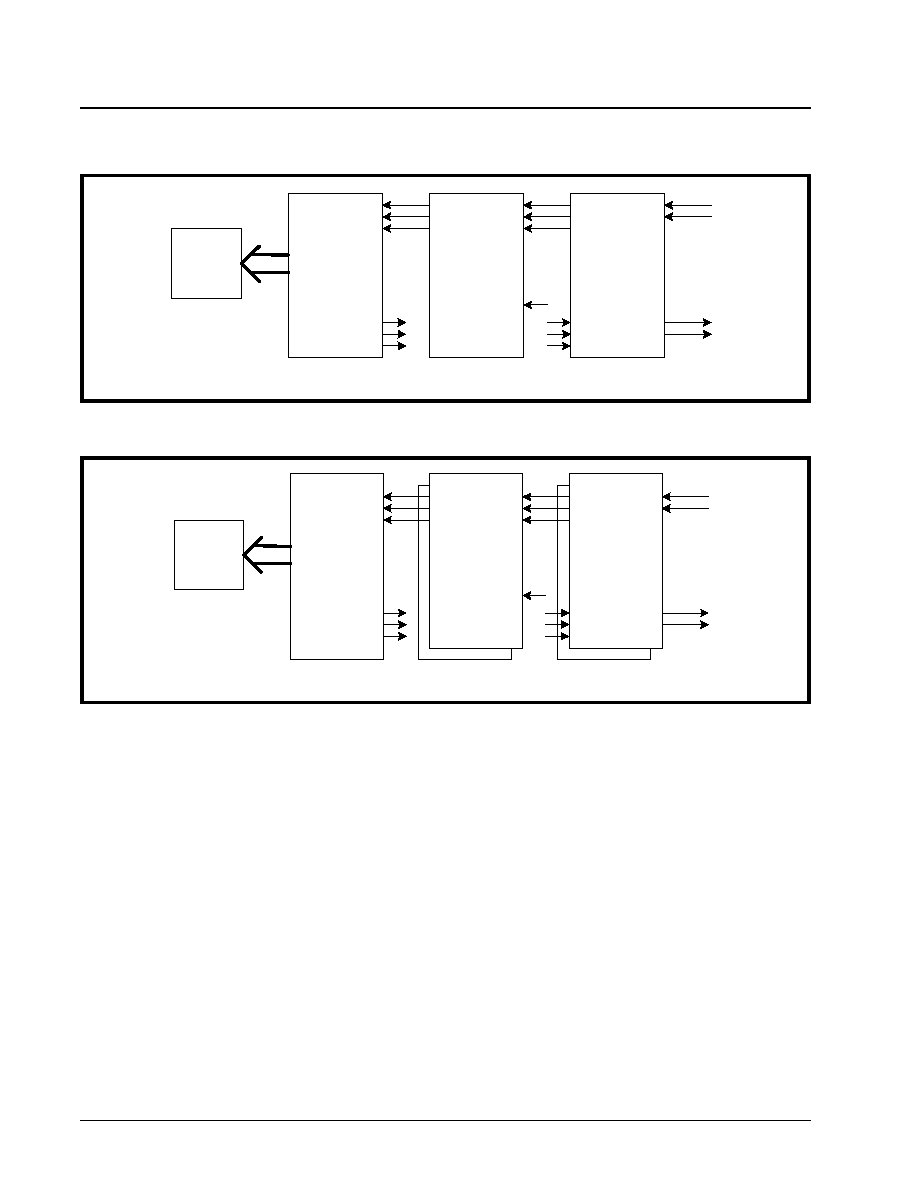

F

IGURE

1. XRT73L04 B

LOCK

D

IAGRAM

RLOS(n)

LLB(n)

RLB(n)

TAOS(n)

TPData(n)

TNData(n)

TxClk(n)

TxLEV(n)

TxOFF

Channel 2

AGC/

Equalizer

Serial

Processor

Interface

Peak

Detector

LOS Detector

Slicer

Clock

Recovery

Data

Recovery

Invert

Loop MUX

HDB3/

B3ZS

Decoder

LOSTHR

SDI

SDO

SClk

CS/(SR/DR)

REGR

RTIP(n)

RRing(n)

REQEN(n)

Channel 0

Channel 1

Notes: 1. (n) = 0, 1, 2 , or 3 for respective Channels

2. Serial Processor Interface input pins are shared by the four Channels in HOST Mode and redefined in

Hardware Mode.

Device

Monitor

MTIP(n)

MRing(n)

DMO(n)

Transmit

Logic

Duty Cycle Adjust

TTIP(n)

TRing(n)

Pulse

Shaping

HDB3/

B3ZS

Encoder

E3_Ch(n)

STS-1/DS3_Ch(n)

Host/(HW)

RLOL(n)

EXClk(n)

RxOFF

RxClkINV

RxClk(n)

RPOS(n)

RNEG(n)/

(LCV(n))

Channel 3

Tx

Control

XRT73L04

áç

áç

áç

áç

4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

REV. P1.0.5

PRELIMINARY

2

TYPICAL APPLICATIONS

TRANSMIT INTERFACE CHARACTERISTICS:

· Accepts either Single-Rail or Dual-Rail data from

Terminal Equipment and generates a bipolar signal

from the line

· Integrated Pulse Shaping Circuit

· Built-in B3ZS/HDB3 Encoder (which can be dis-

abled)

· Contains Transmit Clock Duty Cycle Correction Cir-

cuit on-chip

· Generates pulses that comply with the ITU-T G.703

pulse template (E3 applications)

· Generates pulses that comply with the DSX-3 pulse

template as specified in Bellcore GR-499

-CORE

and ANSI T1.102_1993

· Generates pulses that comply with the STSX-1

pulse template as specified in Bellcore GR-253-

CORE

· Transmitter can be turned off in order to support

redundancy designs

RECEIVE INTERFACE CHARACTERISTICS:

· Integrated Adaptive Receive Equalization (optional)

and Timing Recovery

· Declares and Clears the LOS defect per ITU-T

G.775 requirements (E3 and DS3 applications)

· Meets Jitter Tolerance Requirements as specified in

ITU-T G.823_1993 (E3 Applications)

· Meets Jitter Tolerance Requirements as specified in

Bellcore GR-499-CORE (DS3 Applications)

· Declares Loss of Signal (LOS) and Loss of Lock

(LOL) Alarms

· Built-in B3ZS/HDB3 Decoder (which can be dis-

abled)

· Recovered Data can be muted while the LOS Con-

dition is declared

· Outputs either Single-Rail or Dual-Rail data to the

Terminal Equipment

· Receiver can be powered down in order to con-

serve power in redundancy designs

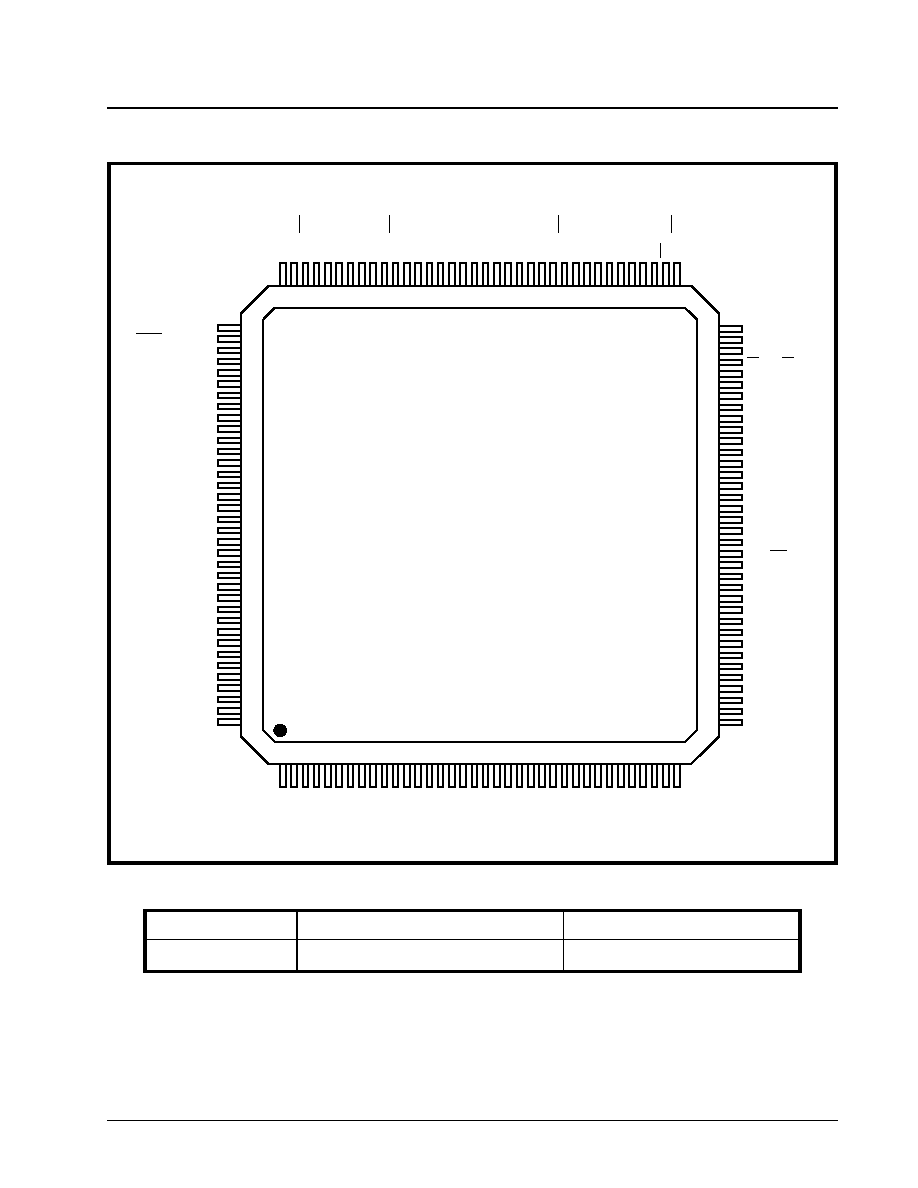

F

IGURE

2. M

ULTI

C

HANNEL

ATM A

PPLICATION

ATM

Switch/

SAR

XRT72L74

RPOS

RNEG

RxLineClk

XRT71D04

XRT73L04

RRPOS

RRNEG

RRClk

RPOS

RNEG

RxClk

RPOS

RNEG

RxClk

RTIP

RRing

TTIP

TRing

TPOS

TNEG

TxLineClk

MClk

TPOS

TNEG

TxClk

4 Channel DS3 ATM UNI

4 Channel E3/DS3 J/A

4 Channel E3/DS3 LIU

F

IGURE

3. M

ULTI

S

ERVICE

- F

RAME

R

ELAY

A

PPLICATION

Frame

Relay

XRT72L58

RPOS

RNEG

RxLineClk

XRT71D04

XRT73L04

RRPOS

RRNEG

RRClk

RPOS

RNEG

RxClk

RPOS

RNEG

RxClk

RTIP

RRing

TTIP

TRing

TPOS

TNEG

TxLineClk

MClk

TPOS

TNEG

TxClk

8 Channel E3/DS3 Framer

2 x 4 Channel E3/DS3 J/A

2 x 4 Channel E3/DS3 LIU

XRT73L04

áç

áç

áç

áç

4 CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

REV. P1.0.5

PRELIMINARY

I

TABLE OF CONTENTS

GENERAL DESCRIPTION ................................................................................................. 1

F

EATURES

.................................................................................................................................................... 1

APPLICATIONS ......................................................................................................................................... 1

T

YPICAL

A

PPLICATIONS

................................................................................................................................. 2

T

RANSMIT

I

NTERFACE

C

HARACTERISTICS

: ..................................................................................................... 2

R

ECEIVE

I

NTERFACE

C

HARACTERISTICS

: ....................................................................................................... 2

ORDERING INFORMATION ............................................................................................... 3

PIN DESCRIPTIONS .......................................................................................................... 4

ELECTRICAL CHARACTERISTICS ................................................................................ 14

A

BSOLUTE

M

AXIMUM

R

ATINGS

.................................................................................................................... 20

SYSTEM DESCRIPTION .................................................................................................. 22

T

HE

T

RANSMIT

S

ECTION

- C

HANNELS

0, 1, 2,

AND

3 .................................................................................... 22

T

HE

R

ECEIVE

S

ECTION

- C

HANNELS

0, 1, 2

AND

3 ....................................................................................... 22

T

HE

M

ICROPROCESSOR

S

ERIAL

I

NTERFACE

................................................................................................. 22

1.0 Selecting the Data Rate .................................................................................................................... 23

1.1 C

ONFIGURING

C

HANNEL

(

N

) ............................................................................................................................... 23

C

OMMAND

R

EGISTER

, CR4-(

N

) ...................................................................................................... 25

2.0 The Transmit Section ....................................................................................................................... 26

2.1 T

HE

T

RANSMIT

L

OGIC

B

LOCK

............................................................................................................................ 26

2.1.1 Accepting Dual-Rail Data from the Terminal Equipment ...................................................................... 26

2.1.2 Accepting Single-Rail Data from the Terminal Equipment ................................................................... 27

C

OMMAND

R

EGISTER

CR3-(

N

) ....................................................................................................... 27

2.2 T

HE

T

RANSMIT

C

LOCK

D

UTY

C

YCLE

A

DJUST

C

IRCUITRY

................................................................................... 27

2.3 T

HE

HDB3/B3ZS E

NCODER

B

LOCK

.................................................................................................................. 28

2.3.1 B3ZS Encoding .................................................................................................................................... 28

2.3.2 HDB3 Encoding .................................................................................................................................... 28

2.3.3 Disabling the HDB3/B3ZS Encoder ..................................................................................................... 29

C

OMMAND

R

EGISTER

CR3-(

N

) ....................................................................................................... 29

2.4 T

HE

T

RANSMIT

P

ULSE

S

HAPING

C

IRCUITRY

....................................................................................................... 29

2.4.1 Enabling the Transmit Line Build-Out Circuit ....................................................................................... 31

C

OMMAND

R

EGISTER

, CR1-(

N

) ...................................................................................................... 31

2.4.2 Disabling the Transmit Line Build-Out Circuit ....................................................................................... 31

C

OMMAND

R

EGISTER

, CR1-(

N

) ...................................................................................................... 32

2.4.3 Design Guideline for Setting the Transmit Line Build-Out Circuit ......................................................... 32

2.4.4 The Transmit Line Build-Out Circuit and E3 Applications .................................................................... 32

2.5 I

NTERFACING

THE

T

RANSMIT

S

ECTIONS

OF

THE

XRT73L04

TO

THE

L

INE

........................................................... 32

TRANSFORMER VENDOR INFORMATION ........................................................................................... 33

3.0 The Receive Section ......................................................................................................................... 33

3.1 I

NTERFACING

THE

R

ECEIVE

S

ECTIONS

OF

THE

XRT73L04

TO

THE

L

INE

............................................................. 33

3.2 T

HE

R

ECEIVE

E

QUALIZER

B

LOCK

...................................................................................................................... 34

C

OMMAND

R

EGISTER

CR-2 (

N

) ...................................................................................................... 36

3.3 C

LOCK

R

ECOVERY

PLL .................................................................................................................................... 36

3.3.1 The Training Mode ............................................................................................................................... 36

3.3.2 The Data/Clock Recovery Mode .......................................................................................................... 36

3.4 T

HE

HDB3/B3ZS D

ECODER

............................................................................................................................. 36

3.4.1 B3ZS Decoding (DS3/STS-1 Applications) .......................................................................................... 36

3.4.2 HDB3 Decoding (E3 Applications) ....................................................................................................... 37

3.4.3 Configuring the HDB3/B3ZS Decoder .................................................................................................. 37

C

OMMAND

R

EGISTER

CR3-(

N

) ....................................................................................................... 38

3.5 LOS D

ECLARATION

/C

LEARANCE

....................................................................................................................... 38

3.5.1 The LOS Declaration/Clearance Criteria for E3 Applications ............................................................... 38

3.5.2 The LOS Declaration/Clearance Criteria for DS3 and STS-1 Applications .......................................... 39

C

OMMAND

R

EGISTER

CR0-(

N

) ....................................................................................................... 40

C

OMMAND

R

EGISTER

CR2-(

N

) ....................................................................................................... 40

áç

áç

áç

áç

XRT73L04

4 CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

PRELIMINARY

REV. P1.0.5

II

C

OMMAND

R

EGISTER

CR0-(

N

) ...................................................................................................... 41

C

OMMAND

R

EGISTER

CR2-(

N

) ...................................................................................................... 41

3.5.3 Muting the Recovered Data while the LOS is being Declared ............................................................. 41

C

OMMAND

R

EGISTER

CR3-(

N

) ...................................................................................................... 41

3.6 R

OUTING

THE

R

ECOVERED

T

IMING

AND

D

ATA

I

NFORMATION

TO

THE

R

ECEIVING

T

ERMINAL

E

QUIPMENT

.............. 41

3.6.1 Routing Dual-Rail Format Data to the Receiving Terminal Equipment ................................................ 41

C

OMMAND

R

EGISTER

CR3-(

N

) ...................................................................................................... 43

3.6.2 Routing Single-Rail Format (Binary Data Stream) data to the Receive Terminal Equipment .............. 43

C

OMMAND

R

EGISTER

CR3-(

N

) ...................................................................................................... 43

3.7 S

HUTTING

OFF

THE

R

ECEIVE

S

ECTION

............................................................................................................. 44

C

OMMAND

R

EGISTER

CR3-(

N

) ...................................................................................................... 44

4.0 Diagnostic Features of the XRT73L04 ............................................................................................ 45

4.1 T

HE

A

NALOG

L

OCAL

L

OOP

-B

ACK

M

ODE

............................................................................................................ 45

4.2 T

HE

D

IGITAL

L

OCAL

L

OOP

-B

ACK

M

ODE

. ........................................................................................................... 46

C

OMMAND

R

EGISTER

CR4-(

N

) ...................................................................................................... 46

C

OMMAND

R

EGISTER

CR4-(

N

) ...................................................................................................... 46

4.3 T

HE

R

EMOTE

L

OOP

-B

ACK

M

ODE

...................................................................................................................... 47

C

OMMAND

R

EGISTER

CR4-(n) ...................................................................................................... 47

4.4 T

X

OFF F

EATURES

........................................................................................................................................... 48

C

OMMAND

R

EGISTER

CR1-(

N

) ...................................................................................................... 48

4.5 T

HE

T

RANSMIT

D

RIVE

M

ONITOR

F

EATURES

....................................................................................................... 48

4.6 T

HE

TAOS (T

RANSMIT

A

LL

O

NE

S) F

EATURE

.................................................................................................... 49

5.0 The Microprocessor Serial Interface .............................................................................................. 49

5.1 D

ESCRIPTION

OF

THE

C

OMMAND

R

EGISTERS

.................................................................................................... 49

C

OMMAND

R

EGISTER

CR1-(

N

) ...................................................................................................... 49

5.2 D

ESCRIPTION

OF

B

IT

-F

IELDS

FOR

EACH

C

OMMAND

R

EGISTER

........................................................................... 51

5.2.1 Command Register - CR0-(n) .............................................................................................................. 51

C

OMMAND

R

EGISTER

CR

0-(

N

) ....................................................................................................... 51

C

OMMAND

R

EGISTER

CR1-(

N

) ...................................................................................................... 52

5.2.3 Command Register CR2-(n) ................................................................................................................ 52

C

OMMAND

R

EGISTER

CR2-(

N

) ...................................................................................................... 52

C

OMMAND

R

EGISTER

CR3-(

N

) ...................................................................................................... 53

C

OMMAND

R

EGISTER

CR4-(

N

) ...................................................................................................... 54

5.3 O

PERATING

THE

M

ICROPROCESSOR

S

ERIAL

I

NTERFACE

. ................................................................................... 54

ORDERING INFORMATION ............................................................................................ 57

PACKAGE DIMENSIONS ................................................................................................. 57

R

EVISION

H

ISTORY

..................................................................................................................................... 58