| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: XRT74L73 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Exar

Corporation 48720 Kato Road, Fremont CA, 94538

∑

(510) 668-7000

∑

FAX (510) 668-7017

∑

www.exar.com

PRELIMINARY

XRT74L73

3 CHANNEL, ATM UNI/PPP DS3/E3 FRAMING CONTROLLER

OCTOBER 2003

REV. P1.0.1

GENERAL DESCRIPTION

The XRT74L73 3 Channel, ATM UNI/PPP Physical

Layer Processor with integrated DS3/E3 framing con-

troller is designed to support ATM direct mapping and

cell delineation as well as PPP mapping and Frame

processing. For ATM UNI applications, this device

provides the ATM Physical Layer (Physical Medium

Dependent and Transmission Convergence sub-lay-

ers) interface for the public and private networks at

DS3/E3 rates. For Clear-Channel Framer applica-

tions, this device supports the transmission and re-

ception of "user data" via the DS3/E3 payload.

The XRT74L73 DS3 ATM UNI/Clear-Channel Framer

incorporates Receive, Transmit, Microprocessor Inter-

face, Performance Monitor, Test and Diagnostic and

Line Interface Unit Scan Drive functional sections.

FEATURES

∑ Compliant with 8/16 bit UTOPIA Level I and II and

PPP Multi-PHY Interface Specifications and sup-

ports UTOPIA Bus operating at 25, 33 or 50 MHz

∑ Contains on-chip 16 cell FIFO (configurable in

depths of 4, 8, 12 or 16 cells), in both the Transmit

(TxFIFO) and Receive Directions (RxFIFO)

∑ Contains on-chip 54 byte Transmit and Receive

OAM Cell Buffer for transmission, reception and

processing of OAM Cells

∑ Supports ATM cell or PPP Packet Mapping

∑ Supports M13 and C-Bit Parity Framing Formats

∑ Supports DS3/E3 Clear-Channel Framing Applica-

tions

∑ Includes PRBS Generator and Receiver

∑ Supports Line, Cell, and PLCP Loop-backs

∑ Interfaces to 8 Bit wide Intel, Motorola, PowerPC,

and Mips µPs

∑ HDLC controller per channel for Tx and Rx

∑ Low power 3.3V, 5V Input Tolerant, CMOS

∑ Available in 388 pin PBGA Package

APPLICATIONS

∑ Digital Access and Cross Connect Systems

∑ Digital, ATM, WAN and LAN Switches

∑ Network Interface Service Units

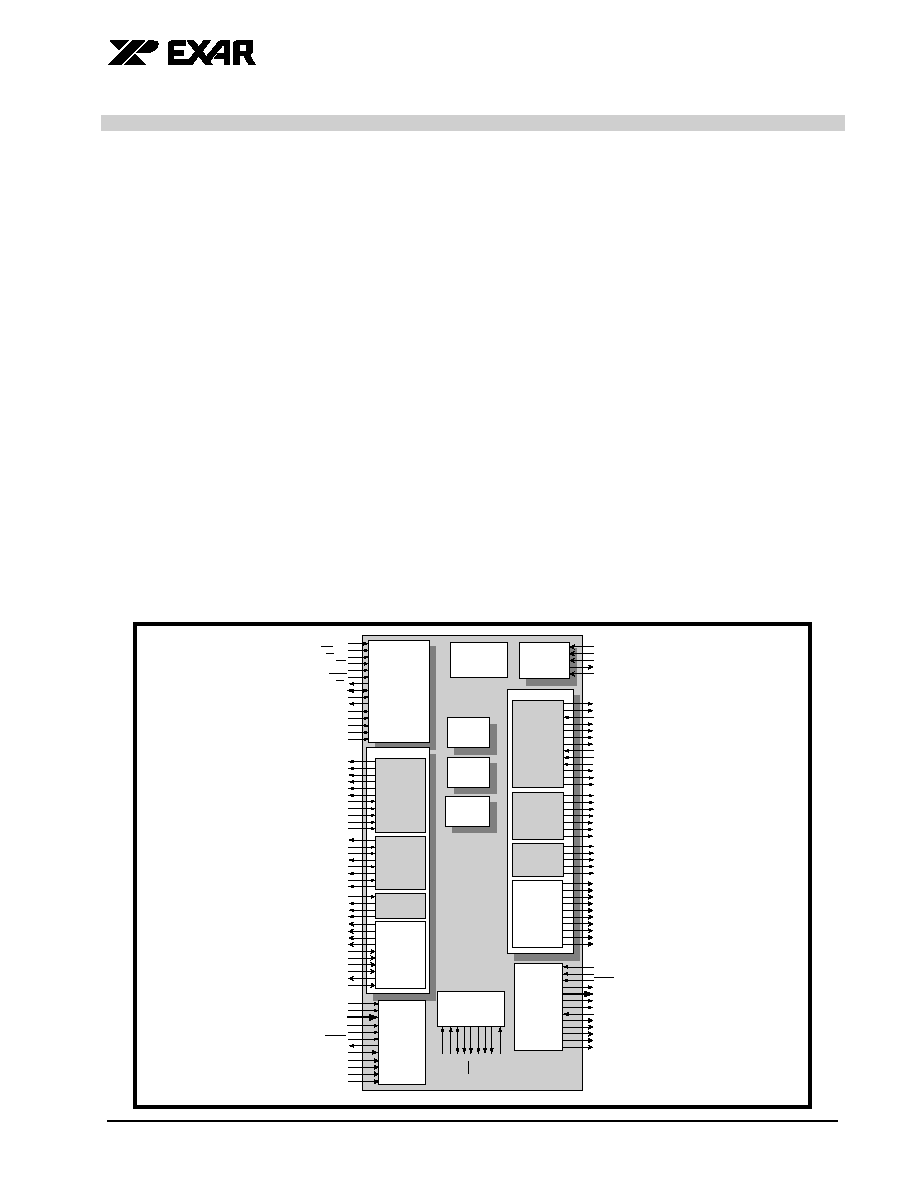

F

IGURE

1. B

LOCK

D

IAGRAM

OF

THE

XRT74L73 ATM UNI/PPP DS3/E3 F

RAMING

C

ONTROLLER

JTAG

JTAG

Microprocessor

Interface

(Programmable

Registers and

Interrupt Block)

Microprocessor

Interface

(Programmable

Registers and

Interrupt Block)

A[6:0]

WR_RW

RD_DS

ALE_AS

Reset

D[7:0]

µ

PClk

RDY_DTCK

CS

INT

Type

Type_0

Type_1

Pblast

PDBEN

Transmitter_n

Transmitter_n

Receiver_n

Receiver_n

Performance

Monitor

Channel (n)

Performance

Monitor

Channel (n)

LAPD

Transceiver

Channel (n)

LAPD

Transceiver

Channel (n)

FEAC

Processor

Channel (n)

FEAC

Processor

Channel (n)

Note: Typical

channel (n) shown,

where;

n = 0, 1, 2 or 3.

Receive Cell

Processor

RxCellRxed_n

RxGFCClk_n

RxGFCMS_n

RxGFC_n

RxLCD_n

Receive PLCP

Processor/

Clear Channel

Rx Serial Data

Processor

RxPOH_n

RxPOHFrame_n

RxPOHClk_n

RxPFrame_n

RxPLOF_n

RxPOOF_n

RxPRed_n

HDLC

CONTROLLER

RXOHInd_n

RxFrame_n

RxClk_n

RxOutClk_n

RxNib_[3:0]_n

RxSerData_n

TDI

TCK

TMS

TDO

TRST

ValidFCS_n

RxIdle_n

RxHDLCDat_[7:0]_n

RxHDLCClk_n

Rx Utopia/PPP

Interface

RxUClk

RxUClkO

RxUEn/RxPEnb

RxUPrty

RxUData[15:0]/RxPData[15:0]

RxUSoC/RxPSOP

RxUClav

RxUAddr[4:0]

RxTSX/RxPSOF

RxPDVAL

RxPERR

RxPEOP

RxMOD_n

TA

O

S

_n

Tx

Le

v

_

n

RL

OO

P_

n

RL

OL

_

n

Line Interface

Drive and Scan

N

i

b

b

le

In

tf

DM

O_

n

GP

I

O

_

n

LL

O

O

P

_

n

Re

q

_

n

Tx Utopia/PPP

Interface

TxUClk

TxUClkO

TxUData[15:0]/TxPData[15:0]

TxUPrty

TxUSoC/TxPSOP

TxUEn

TxUClav

TxUAddr[4:0]

TxPEOP

TxMod_n

TxTSX/TxPOSF

TxPERR

HDLC

CONTROLLER

TXOHInd_n

TxNibFrame_n

Transmit Cell

Processor

TxGFCClk

TxGFCMS_n

TxGFC_n

TxCellTxed_n

TxNibClk_n

TxFrameRef_n

TxNib_[3:0]_n

TxSerData_n

TxHDLCClk_n

TxHDLCDat_[7:0]_n

SendFCS_n

SendMSG_n

Transmit PLCP

Processor/

Clear Channel

Tx Serial Data

Processor

TxStuffCtl_n

8KRef_n

TxPOHClk_n

TxPFrame_n

TxPOH_n

TxPOHFrame_n

TxPOHIns_n

EncoDis_n

TxOH_n

TxOHEnable_n

Transmit

DS3/E3

Framer

TxPOS_n

TxNEG_n

TxFrame_n

TxOHClk_n

TxLineClk_n

TxAISEn_n

TxInClk_n

TxOHIns_n

TxOHFrame_n

Receive

DS3/E3

Framer

RxLineClk_n

RxNEG_n

RxPOS_n

RxSerClk_n

RxOHEnable_n

RxAIS_n

RxOHClk_n

RxOH_n

RxLOS_n

RxOOF_n

EXTLOS_n

RxOHFrame_n

RxRed_n

XRT74L73

3 CHANNEL, ATM UNI/PPP DS3/E3 FRAMING CONTROLLER

REV. P1.0.1

PRELIMINARY

2

ORDERING INFORMATION

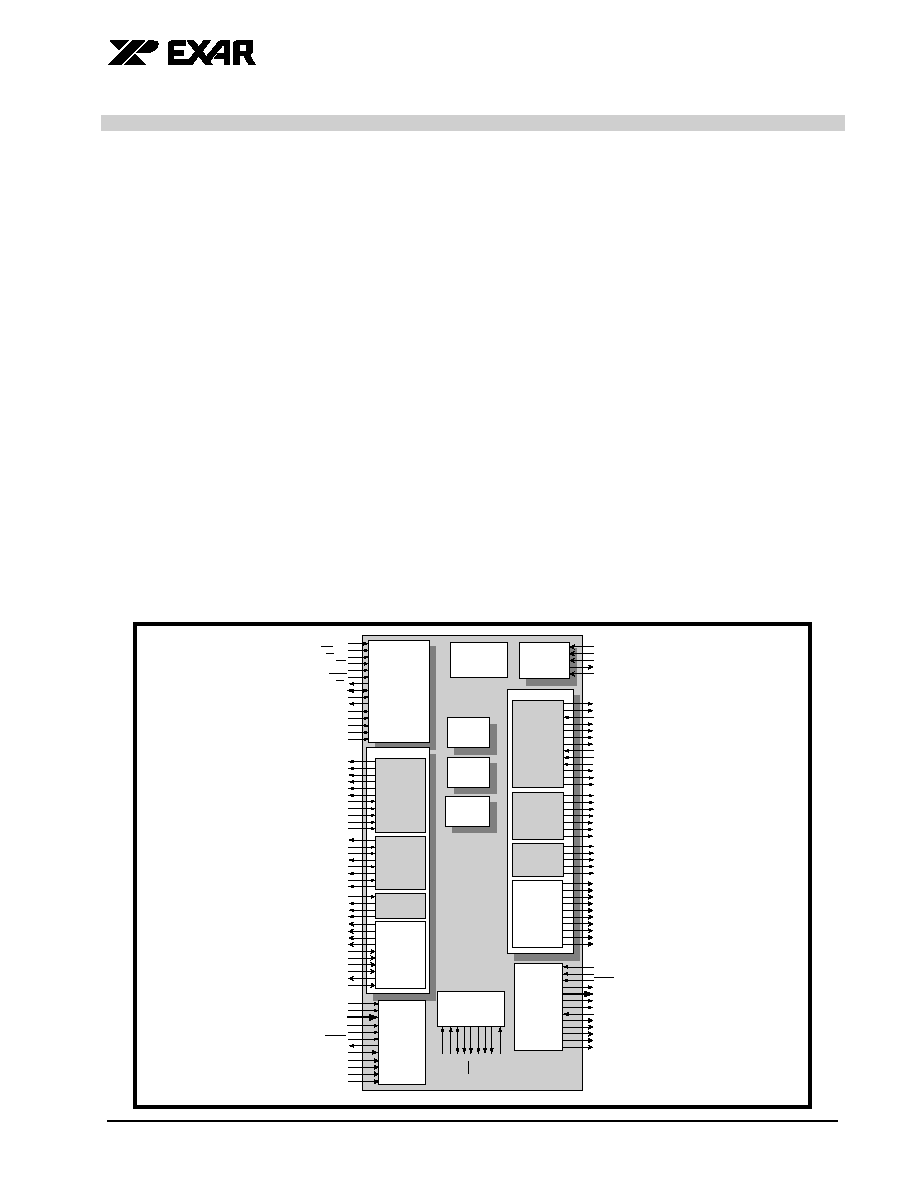

F

IGURE

2. P

IN

O

UT

OF

THE

XRT74L73 DS3/E3 ATM UNI/PPP (388 BALL PBGA)

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

21

22

19

20

23

24

25

26

1

2

3

4

5

6

7

8

17

18

13

14

15

16

9

10

11

12

A

26

D

23

D

26

AC

1

AC

4

AC

23

AC

26

AF

1

AF

26

AE

1

AD

1

A1

D4

D4

C1

B1

L4

T4

E1

F1

G1

H1

J1

K1

L1

M1

AA

1

AB

1

U1

V1

W1

Y1

N1

P1

R1

T1

L2

T2

L3

T3

L

26

T

26

L

23

T

23

L

24

T

24

L

25

T

25

XRT74L73

(See pin list for pin names and function)

V3

V1

V1

V1

V1

G

V1

V1

G

G

G

G

G

G

G

G

G

G

G

V2

G

G

V1

V1

V3

V3

V3

V3

V3

V2

V2

V2

V2

V2

V2

V2

P

ART

N

UMBER

P

ACKAGE

O

PERATING

T

EMPERATURE

R

ANGE

XRT74L73IB

35 x 35 mm, 388 Plastic Ball Grid Array

-40∞C to +85∞C

XRT74L73

3 CHANNEL, ATM UNI/PPP DS3/E3 FRAMING CONTROLLER

PRELIMINARY

REV. P1.0.1

I

TABLE OF CONTENTS

1.0 REGISTER MAP OF THE XRT74L73 ................................................................................................. 47

2.0 TRANSMIT SECTION .......................................................................................................................... 82

2.1 TRANSMIT UTOPIA INTERFACE BLOCK .................................................................................................... 82

2.1.1 BRIEF DESCRIPTION OF THE TRANSMIT UTOPIA INTERFACE........................................................................... 82

2.1.2 FUNCTIONAL DESCRIPTION OF THE TRANSMIT UTOPIA INTERFACE .............................................................. 83

2.2 TRANSMIT CELL PROCESSOR .................................................................................................................. 104

2.2.1 BRIEF DESCRIPTION OF THE TRANSMIT CELL PROCESSOR .......................................................................... 104

2.2.2 FUNCTIONAL DESCRIPTION OF TRANSMIT CELL PROCESSOR ...................................................................... 104

2.3 TRANSMIT PLCP PROCESSOR ................................................................................................................. 113

2.3.1 BRIEF DESCRIPTION OF THE TRANSMIT PLCP PROCESSOR .......................................................................... 113

2.3.2 DESCRIPTION OF THE PLCP FRAME AND THE PATH OVERHEAD (POH) BYTES .......................................... 114

2.3.3 FUNCTIONAL DESCRIPTION OF THE TRANSMIT PLCP PROCESSOR BLOCK ................................................ 116

2.4 TRANSMIT DS3 FRAMER ............................................................................................................................ 124

2.4.1 BRIEF DESCRIPTION OF THE TRANSMIT DS3 FRAMER .................................................................................... 124

2.5 TRANSMIT E3 FRAMER .............................................................................................................................. 124

2.5.1 BRIEF DESCRIPTION OF THE TANSMIT E3 FRAMER.......................................................................................... 124

3.0 THE RECEIVE SECTION ................................................................................................................... 125

3.1 RECEIVE DS3 FRAMER .............................................................................................................................. 125

3.1.1 BRIEF DESCRIPTION OF THE RECEIVE DS3 FRAMER ....................................................................................... 125

3.2 RECEIVE PLCP PROCESSOR .................................................................................................................... 127

3.2.1 OPERATION OF THE RECEIVE PLCP PROCESSOR ............................................................................................ 127

3.2.2 FUNCTIONAL DESCRIPTION OF THE RECEIVE PLCP PROCESSOR ................................................................ 128

3.3 RECEIVE CELL PROCESSOR .................................................................................................................... 137

3.3.1 BRIEF DESCRIPTION OF THE RECEIVE CELL PROCESSOR ............................................................................. 137

3.3.2 FUNCTIONAL DESCRIPTION OF RECEIVE CELL PROCESSOR ......................................................................... 137

3.4 RECEIVE UTOPIA INTERFACE BLOCK ..................................................................................................... 157

3.4.1 BRIEF DESCRIPTION OF THE RECEIVE UTOPIA INTERFACE BLOCK.............................................................. 157

3.4.2 FUNCTIONAL DESCRIPTION OF RECEIVE UTOPIA............................................................................................. 157

4.0 DS3 OPERATION OF THE XRT74L73 .............................................................................................. 178

4.1 DESCRIPTION OF THE DS3 FRAMES AND ASSOCIATED OVERHEAD BITS ........................................ 178

4.1.1 FRAME SYNCHRONIZATION BITS (APPLIES TO BOTH M13 AND C-BIT PARITY FRAMING FORMATS)....... 180

4.1.2 PERFORMANCE MONITORING/ERROR DETECTION BITS (PARITY)................................................................. 181

4.1.3 ALARM AND SIGNALING-RELATED OVERHEAD BITS ....................................................................................... 181

4.1.4 THE DATA LINK RELATED OVERHEAD BITS....................................................................................................... 182

4.2 THE TRANSMIT SECTION OF THE XRT74L73 (DS3 MODE OPERATION) .............................................. 182

4.2.1 THE TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK ........................................................................... 183

4.2.2 THE TRANSMIT OVERHEAD DATA INPUT INTERFACE ...................................................................................... 200

4.2.3 THE TRANSMIT DS3 HDLC CONTROLLER ........................................................................................................... 211

4.2.4 THE TRANSMIT DS3 FRAMER BLOCK .................................................................................................................. 219

4.2.5 THE TRANSMIT DS3 LINE INTERFACE BLOCK.................................................................................................... 225

4.2.6 TRANSMIT SECTION INTERRUPT PROCESSING................................................................................................. 230

4.3 THE RECEIVE SECTION OF THE XRT74L73 (DS3 MODE OPERATION) ................................................ 233

4.3.1 THE RECEIVE DS3 LIU INTERFACE BLOCK......................................................................................................... 234

4.3.2 THE RECEIVE DS3 FRAMER BLOCK..................................................................................................................... 239

4.3.3 THE RECEIVE HDLC CONTROLLER BLOCK ........................................................................................................ 250

4.3.4 THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE ..................................................................................... 257

4.3.5 THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE ........................................................................................ 267

4.3.6 RECEIVE SECTION INTERRUPT PROCESSING.................................................................................................... 274

5.0 E3/ITU-T G.751 OPERATION OF THE XRT74L73 ........................................................................... 288

5.1 DESCRIPTION OF THE E3, ITU-T G.751 FRAMES AND ASSOCIATED OVERHEAD BITS .................... 288

5.1.1 DEFINITION OF THE OVERHEAD BITS.................................................................................................................. 288

5.2 THE TRANSMIT SECTION OF THE XRT74L73 (E3, ITU-T G.751 MODE OPERATION) .......................... 289

5.2.1 THE TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK ........................................................................... 289

5.2.2 THE TRANSMIT OVERHEAD DATA INPUT INTERFACE ...................................................................................... 306

5.2.3 THE TRANSMIT E3 HDLC CONTROLLER.............................................................................................................. 315

5.2.4 THE TRANSMIT E3 FRAMER BLOCK..................................................................................................................... 323

5.2.5 THE TRANSMIT E3 LINE INTERFACE BLOCK ...................................................................................................... 328

5.2.6 TRANSMIT SECTION INTERRUPT PROCESSING................................................................................................. 333

5.3 THE RECEIVE SECTION OF THE XRT74L73 (E3 MODE OPERATION) ................................................... 335

5.3.1 THE RECEIVE E3 LIU INTERFACE BLOCK ........................................................................................................... 335

XRT74L73

3 CHANNEL, ATM UNI/PPP DS3/E3 FRAMING CONTROLLER

REV. P1.0.1

PRELIMINARY

II

5.3.2 THE RECEIVE E3 FRAMER BLOCK ....................................................................................................................... 341

5.3.3 THE RECEIVE HDLC CONTROLLER BLOCK ........................................................................................................ 355

5.3.4 THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE ..................................................................................... 360

5.3.5 THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE ........................................................................................ 366

5.3.6 RECEIVE SECTION INTERRUPT PROCESSING.................................................................................................... 371

6.0 E3/ITU-T G.832 OPERATION OF THE XRT74L73 ............................................................................382

6.1 DESCRIPTION OF THE E3, ITU-T G.832 FRAMES AND ASSOCIATED OVERHEAD BYTES ................. 382

6.1.1 DEFINITION OF THE OVERHEAD BYTES .............................................................................................................. 382

6.2 THE TRANSMIT SECTION OF THE XRT74L73 (E3 MODE OPERATION) ................................................ 385

6.2.1 THE TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK ........................................................................... 386

6.2.2 THE TRANSMIT OVERHEAD DATA INPUT INTERFACE ...................................................................................... 400

6.2.3 THE TRANSMIT E3 HDLC CONTROLLER .............................................................................................................. 413

6.2.4 THE TRANSMIT E3 FRAMER BLOCK..................................................................................................................... 421

6.2.5 THE TRANSMIT E3 LINE INTERFACE BLOCK ...................................................................................................... 424

6.2.6 TRANSMIT SECTION INTERRUPT PROCESSING ................................................................................................. 430

6.3 THE RECEIVE SECTION OF THE XRT74L73 (E3 MODE OPERATION) ................................................... 432

6.3.1 THE RECEIVE E3 LIU INTERFACE BLOCK ........................................................................................................... 432

6.3.2 THE RECEIVE E3 FRAMER BLOCK ....................................................................................................................... 438

6.3.3 THE RECEIVE HDLC CONTROLLER BLOCK ........................................................................................................ 453

6.3.4 THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE ..................................................................................... 460

6.3.5 THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE ........................................................................................ 469

6.3.6 RECEIVE SECTION INTERRUPT PROCESSING.................................................................................................... 475

XRT74L73

3 CHANNEL, ATM UNI/PPP DS3/E3 FRAMING CONTROLLER

PRELIMINARY

REV. P1.0.1

6

PIN DESCRIPTION

P

IN

#

N

AME

T

YPE

D

ESCRIPTION

Microprocessor Interface

AB3

AA4

AA1

AA2

Y1

Y2

Y3

A0

A1

A2

A3

A4

A5

A6

I

Address Bus Input (Microprocessor Interface):

These pins are used to select the on-chip Framer/UNI registers and RAM space

for READ/WRITE operations with the "local" microprocessor.

V4

NibbleIntf

I

Nibble Interface Select Input pin:

This input pin permits the user to configure the Transmit Payload Data Input

Interface and the Receive Payload Data Output Interface blocks to operate in

either the "Serial" or the "Nibble-Parallel" Mode.

Setting this input pin "high" configures each of these blocks to operate in the Nib-

ble-Parallel Mode. In this mode, the "Transmit Payload Data Input Interface"

block will accept the "outbound" payload data (from the local terminal equip-

ment) in a "nibble-parallel" manner via the "TxNib[2:0]" input pins. Further, the

Receive Payload Data Output Interface block will output "inbound" payload data

(to the local terminal equipment) in a "nibble-parallel" via the "RxNib[2:0] output

pins.

Setting this input pin "low" configures each of these blocks to operate in the

Serial Mode. In this mode, the Transmit Payload Data Input Interface block will

accept the "outbound" payload data (from the local terminal equipment) in a

"serial" manner via the "TxSer_n" input pin. Further, the Receive Payload Data

Output Interface block will output the "inbound" payload data (to the local termi-

nal equipment) in a serial manner, via the "RxSer_n" output pin.

N

OTE

: This input pin is only active if the XRT74L73 device has been configured

to operate in the Clear-Channel Framer Mode.

AC7

AD6

AE5

AF4

AC5

AD4

AE3

AF2

D0

D1

D2

D3

D4

D5

D6

D7

I/O

Bi-Directional Data Bus (Microprocessor Interface Section):

These pins function as the Microprocessor Interface bi-directional data bus and is

intended to be interfaced to the "local" microprocessor. This pin is inactive if the

Microprocessor Interface block is configured to operate over an 8 bit data bus.

AE2

ALE_AS

I

Address Latch Enable/Address Strobe:

This input is used to latch the address (present at the Microprocessor Interface

Address Bus, A[6:0]) into the Framer/UNI Microprocessor Interface circuitry and

to indicate the start of a READ or WRITE cycle. This input is active-"High" in the

Intel Mode (MOTO = "Low") and active-"Low" in the Motorola Mode (MOTO =

"High").

AB1

CS

I

Chip Select Input:

This active-"Low" input signal selects the Microprocessor Interface Section of the

UNI/Framer and enables Read/Write operations between the "local" micropro-

cessor and the UNI/Framer on-chip registers and RAM locations.