QUAD E1 FRAMER IC

XRT84V24

PRELIMINARY

REV. 1.0.1

1

GENERAL DESCRIPTION

The XRT84V24 Quad E1 Framer IC contains four in-

dependent E1 Framer blocks. Each E1 Framer block

contains its own Transmit and Receive E1 Framin

function, Transmit HDLC Controller (which encapsu-

lates contents of Transmit HDLC Buffers into LAPD

Message frames) and Receiver HDLC Controller

(which extracts payload content of "Receive LAPD

Message" frames from the incoming E1 data stream

and writes it into the Receive HDLC Buffer). Each

framer also contains a Transmit and Overhead Input

port, which permits "Data Link" Terminal equipment

direct access to the outbound E1 frames and a Re-

ceive Overhead Output port, which permits "Data

Link" Terminal equipment direct access to the "Data

Link" bits within the inbound E1 frames.

FEATURES

∑ Four independent, ITU-T G.704 compliant Trans-

ceiver E1 Framers

∑ Supports Channel Associated Signalin

∑ Supports Common-Channel and Primary Rate

ISDN Signalin

∑ Supports FAS, CRC-Multiframe and CAS Multi-

frame framing stuctures

∑ Contains two 96 byte Transmit HDLC Buffers and

two 96 byte Receive HDLC buffers for each channel

∑ Contains Microprocessor Interface for popular

types of Microprocessors and supports Pro-

grammed I/O, Burst and DMA modes of Read/Write

access

∑ Each framer block can encode or decode the E

Frame data into/from the Single-Rail or Dual-Rail

(AMI or HDB3 encoded) formats

∑ Detects and forces RAI and AIS Alarms

∑ Detects LOF, COFA and LOS conditions

∑ Each Framer Contains a 512 bit Elastic Store Buffer

∑ Uses a Single +3.3V Power Supply

∑ Available in either a 160 pin PQFP and 208 pin

PQFP package

APPLICATIONS

∑ SDH terminal or add/drop multiplexers supporting

E1 framing

∑ E1 multiplexers

∑ Channel Service Units (CSUs)

∑ LAN routers with integrated E1 interfaces

∑ E1 Frame Relay Interface

∑ ISDN Primary Rate Interfaces

∑ Test Equipment

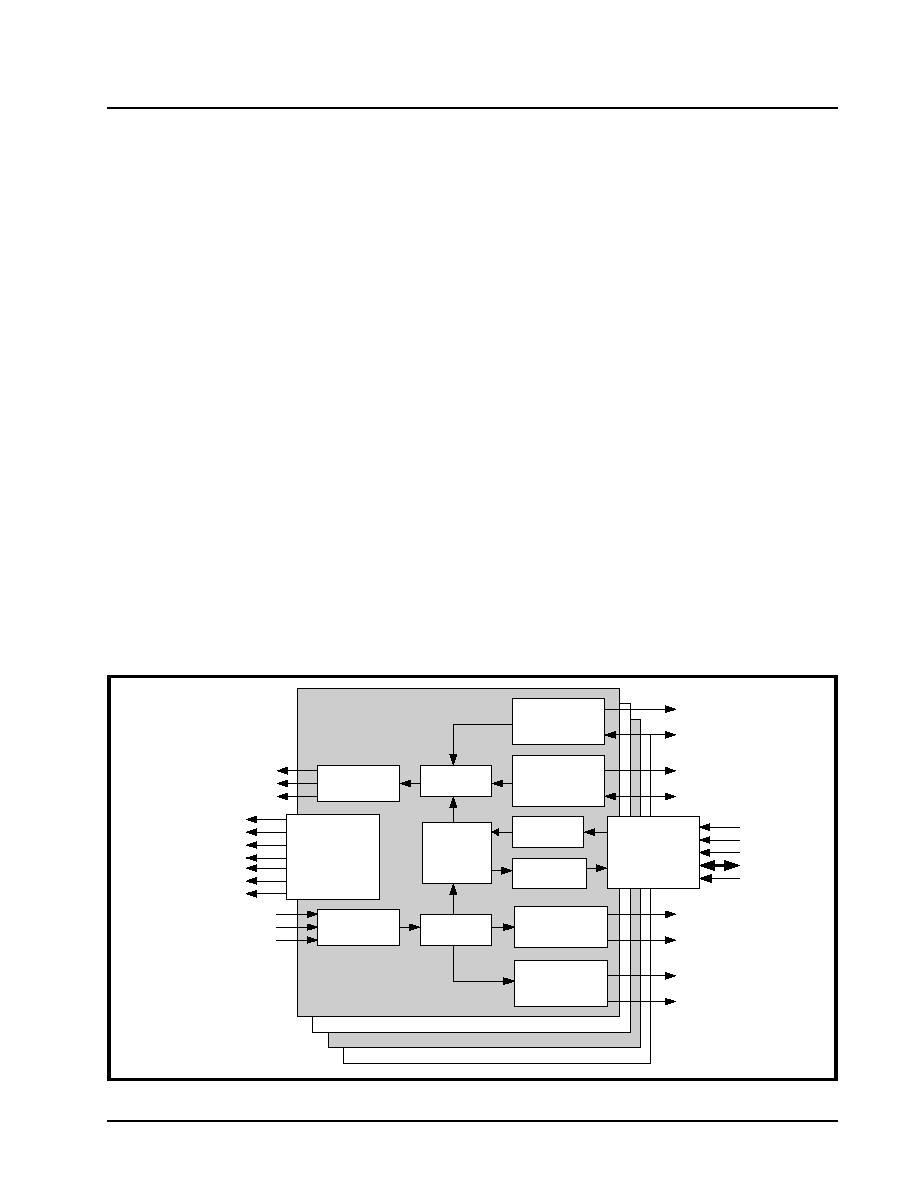

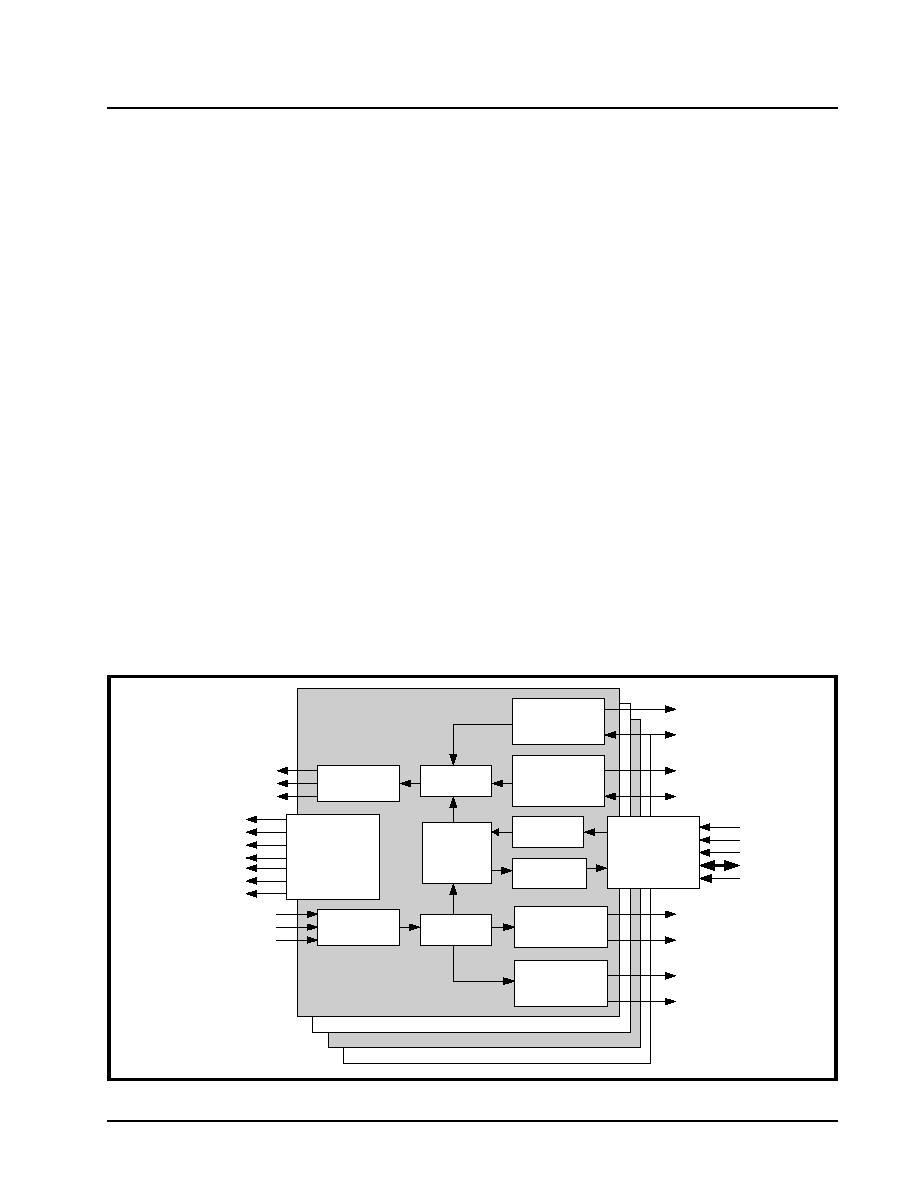

F

IGURE

1. B

LOCK

D

IAGRAM

OF

THE

XRT84V24

TxPOS_0

TxNEG_0

TxLineClk_0

RxPOS_0

RxNEG_0

RxLineClk_0

Microprosser

Interface Block

PCS_L

PWR_L

PRD_L

PD[7:0]

PA[5:0]

RxSER_0

RxSERClk_0

RxOH_0

RxOHClk_0

TxOH_0

TxOHClk_0

TxSER_0

TxSERClk_0

Framer Block 1

Framer Block 2

Framer Block 3

Transmit E1

LIU Interface

Transmit E1

Framer

Receive E1

Framer

HDLC

Controller

Transmit E1

Overhead Input

Interface

Transmit E1

Serial Input

Interface

TxLAPD

Buffer

Rx LAPD

Buffer

Receive E1

Serial Output

Interface

Receive E1

Overhead Output

Interface

Framer Block 0

LIU

Controller

Block

GPO_6_CS_L_3

GPO_5_CS_L_2

GPO_4_CS_L_1

GPO_3_CS_L_0

GPO_2_SClK_L

GPO_1_SDI

GPO_0_SDO

Receive E1

LIU Interface

XRT84V24

QUAD E1 FRAMER IC

PRELIMINARY

REV. 1.0.1

2

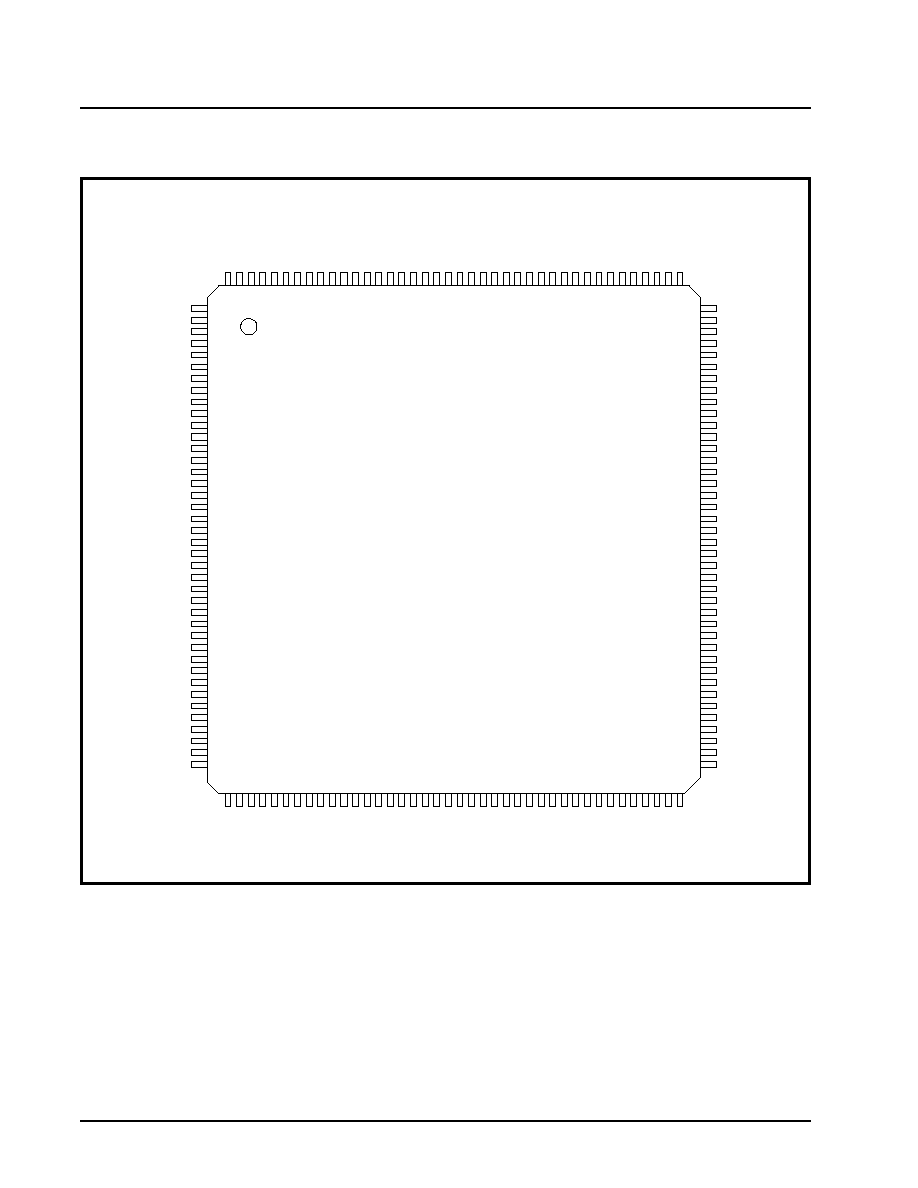

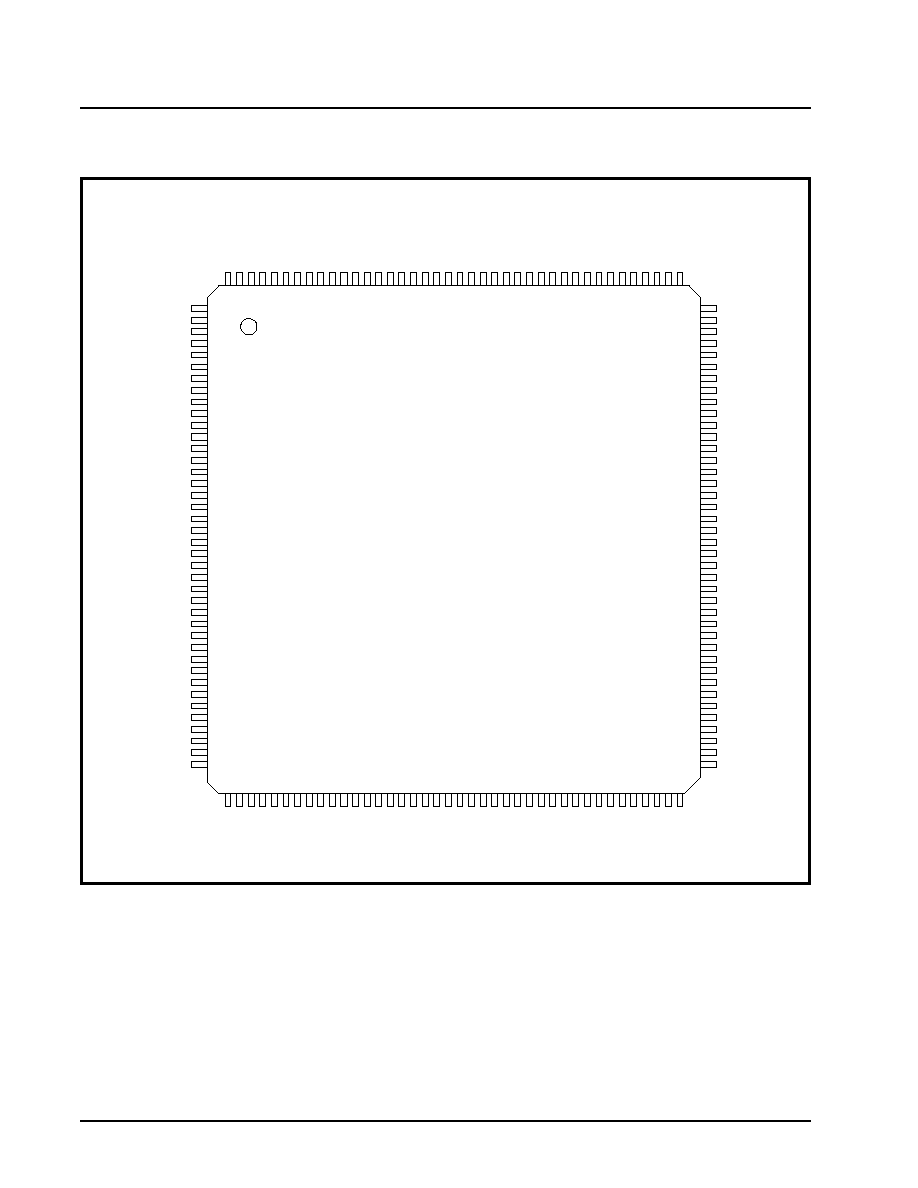

F

IGURE

2. P

IN

OUT

OF

THE

XRT84V24

IN

THE

160

PIN

PQFP

PACKAGE

T x C h C l k _ 3

T x O H C l k _ 3

T x O H _ 3

T x M S y n c _ 3

T x S y n c _ 3

G N D

T x S e r C l k _ 3

TxSer_3

R x L O S _ 3

R x O H C l k _ 3

R x O H _ 3

R x C H C l k _ 3

R x C A S M S y n c _ 3

V D D

R x C R C M S y n c _ 3

R x S y n c _ 3

R x S e r C l k _ 3

R x S e r _ 3

T C K

T M S

T D I

T D O

G N D

TxSer_2

T x S e r C l k _ 2

T x S y n c _ 2

T x M S y n c _ 2

T x O H _ 2

T x O H C l k _ 2

R x S e r _ 2

T x C h C l k _ 2

R x S e r C l k _ 2

V D D

R x S y n c _ 2

R x C R C M S y n c 2

R x C A S M S y n c _ 2

R x C h C l k _ 2

R x O H _ 2

R x O H C l k _ 2

R x L O S _ 2

NC

PACK_L_0

PBLAST_L

VDD

PACK_L_1

PData_0

PREQ_L_0

PDATA_1

VDD

PREQ_L_1

PData_2

PINT_L

PData_3

GND

PData

PData_4

PTYPE_0

PData_5

VDD

PTYPE_1

PData_6

PTYPE_2

PData_7

GND

PDACK_L

PAddr_0

PDBEN_L

PAddr_1

VDD

PAS_L

PAddr_2

PCS_L

PAddr_3

PRD_L

PAddr_4

GND

PWR_L

PAddr_5

NC

NC

T x C h C l k _ 0

T x O H C l k _ 0

T x O H _ 0

T x M S y n c _ 0

T x S y n c _ 0

G N D

T x S e r C l k _ 0

T x S E R _ 0

R x L O S _ 0

R x O H C l k _ 0

R x O H _ 0

R x C H C l k _ 0

R x C A S M S y n c _ 0

V D D

R x C R C M S y n c _ 0

R x S y n c _ 0

R x S e r C l k _ 0

R x S e r _ 0

O S C C l k

R E S E T _ L

8 k H z R E F

T E S T M O D E

G N D

TxSer_1

T x S e r C l k _ 1

T x S y n c _ 1

T x M S y n c _ 1

T x O H _ 1

T x O H C l k _ 1

R x S e r _ 1

T x C h C l k _ 1

R x S e r C l k _ 1

V D D

R x S y n c _ 1

R x C R C M S y n c _ 1

R x C A S M S y n c _ 1

R x C H C l k _ 1

R x O H _ 1

R x O H C l k _ 1

R x L O S _ 1

LOS_0

TxPOS_0

TxNEG_0

TxLineClk_0

RxPOS_0

RxNEG_0

RxLineClk_0

LOS_1

GND

TxPOS_1

TxNEG_1

TxLineClk_1

RxPOS_1

RxNEG_1

RxLineClk_1

VDD

GPO_6_CS_L_3

GPO_5_CS_L_2

GPO_4_CS_L_1

GPO_3_CS_L_0

GPO_2_SClk

GPO_1_SDI

GPO_0_SDO

VDD

RxLineClk_2

RxNEG_2

RxPOS_2

TxLineClk_2

TxNEG_2

TxPOS_2

GND

LOS_2

RxLineClk_3

RxNEG_3

RxPOS_3

TxLineClk_3

TxNEG_3

TxPOS_3

LOS_3

NC

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

2 9

3 0

3 1

3 2

3 3

3 4

3 5

3 6

3 7

3 8

3 9

4 0

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

1 2 0

1 1 9

1 1 8

1 1 7

1 1 6

1 1 5

1 1 4

1 1 3

1 1 2

1 1 1

1 1 0

1 0 9

1 0 8

1 0 7

1 0 6

1 0 5

1 0 4

1 0 3

1 0 2

1 0 1

1 0 0

9 9

9 8

9 7

9 6

9 5

9 4

9 3

9 2

9 1

9 0

8 9

8 8

8 7

8 6

8 5

8 4

8 3

8 2

8 1

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

160 Lead PQFP

QUAD E1 FRAMER IC

XRT84V24

PRELIMINARY

REV. 1.0.1

3

ORDERING INFORMATION

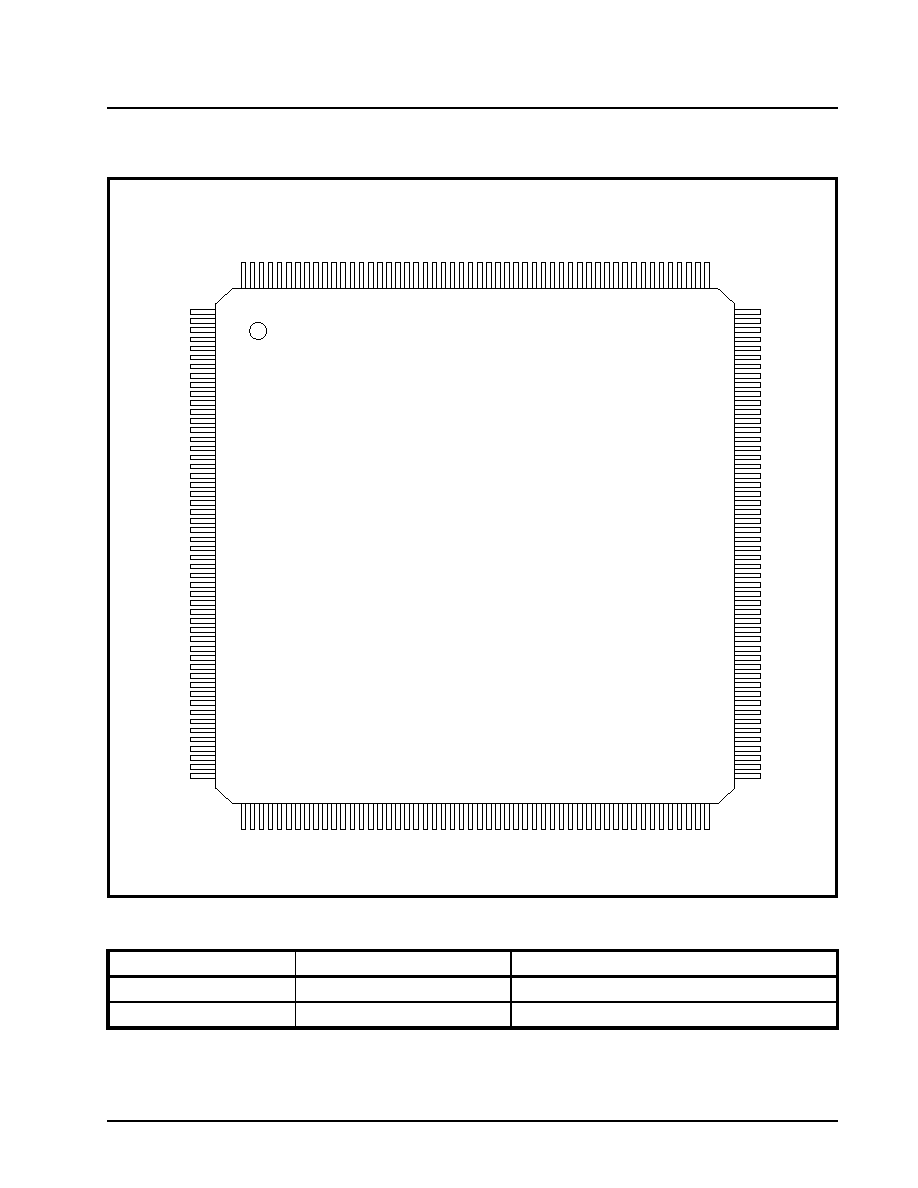

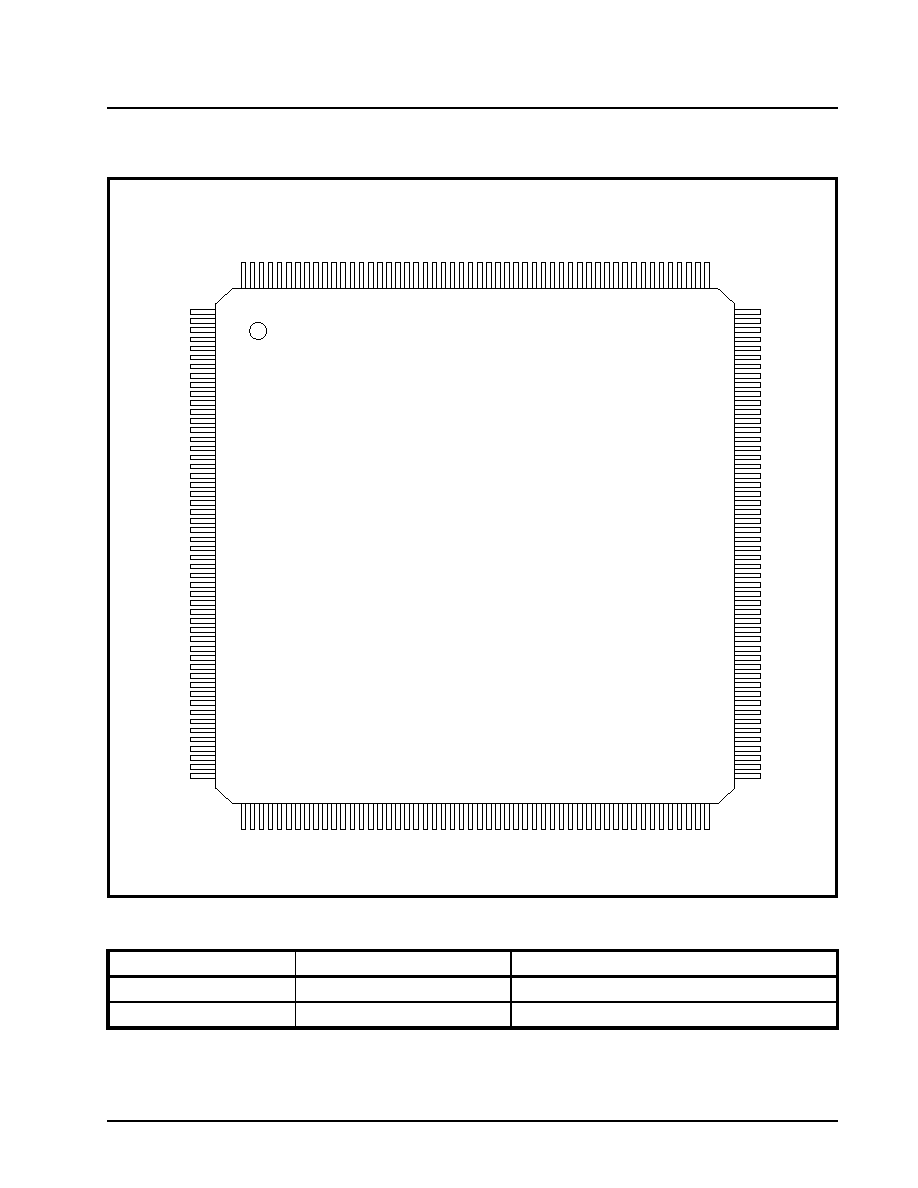

F

IGURE

3. P

IN

O

UT

OF

THE

XRT84V24

IN

THE

20

PIN

PQFP

PACKAGE

N C

TxChClk_3

TxOHClk_3

R x C H N 3 _ 0

T x O H _ 3

R x C H N 3 _ 1

T x M S y n c _ 3

R x C H N _ 3 _ 2

T x S y n c _ 3

R x C H N _ 3 _ 3

V S S

TxSerClk_3

R x C H N _ 3 _ 4

T x S e r _ 3

R x L O S _ 3

R x O H C l k _ 3

R x O H _ 3

R x C H C l k _ 3

R x C A S M S y n c _ 3

V D D

R x C R C M S y n c _ 3

R x S y n c _ 3

R x S e r C l k _ 3

R x S e r _ 3

T C K

T M S

TDI

T D O

G N D

T x S e r _ 2

TxSerClk_2

T x S y n c _ 2

T x M S y n c _ 2

T x O H _ 2

TxOHClk_2

R x S e r _ 2

TxChClk_2

R x S e r C l k _ 2

V D D

R x S y n c _ 2

T x C H N _ 2 _ 4

R x C R C M S y n c 2

T x C H N _ 2 _ 3

R x C A S M S y n c _ 2

R x C h C l k _ 2

T x C H N _ 2 _ 2

R x O H _ 2

T x C H N _ 2 _ 1

G N D

R x O H C l k _ 2

T x C H N _ 2 _ 0

R x L O S _ 2

LOS_0

TxPOS_0

TxCHN_0_4

TxNEG_0

TxCHN_0_3

TxLineClk_0

TxCHN_0_2

GND

RxPOS_0

TxCHN_0_1

RxNEG_0

TxCHN_0_0

RxLineClk_0

LOS_1

GND

TxPOS_1

TxNEG_1

TxLineClk_1

RxPOS_1

RxNEG_1

RxLineClk_1

VDD

GPO_6_CS_L_3

GPO_5_CS_L_2

GPO_4_CS_L_1

GPO_3_CS_L_0

GPO_2_SClk

GPO_1_SDI

GPO_0_SDO

VDD

RxLineClk_2

RxNEG_2

RxPOS_2

TxLineClk_2

TxNEG_2

TxPOS_2

GND

LOS_2

RxLineClk_3

TxCHN_3_0

RxNEG_3

TxCHN_3_1

RxPOS_3

GND

TxCHN_3_2

TxLineClk_3

TxCHN_3_3

TxNEG_3

TxCHN_3_4

TxPOS_3

LOS_3

NC

NC

PACK_L_0

PBLAST_L

RxCHN2_4

GND

PACK_L_1

RxCHN_2_3

PData_0

RxCHN_2_2

GND

PREQ_L_0

RxCHN_2_1

PData_1

RxCHN_2_0

VDD

PREQ_L_1

PData_2

PINT_L

PData_3

GND

PClk

PData_4

PType_0

PData_5

VDD

PType_1

PData_6

PType_2

PData_7

GND

PDACK_L

PAddr_0

PDBEN_L

PAddr_1

VDD

PAS_L

PAddr_2

PCS_L

RxCHN_1_0

GND

PAddr_3

RxCHN_1_1

PRD_L

RxCHN_1_2

PAddr_4

GND

RxCHN_1_3

PWR_L

RxCHN_1_4

PAddr_5

NC

NC

N C

TxChClk_0

TxOHClk_0

R x C H N _ 0 _ 0

T x O H _ 0

R x C H N _ 0 _ 1

T x M S y n c _ 0

R x C H N _ 0 _ 2

T x S y n c _ 0

R x C H N _ 0 _ 3

G N D

TxSerClk_0

R x C H N _ 0 _ 4

T x S E R _ 0

R x L O S _ 0

R x O H C l k _ 0

R x O H _ 0

R x C H C l k _ 0

R x C A S M S y n c _ 0

V D D

R x C R C M S y n c _ 0

R x S y n c _ 0

R x S e r C l k _ 0

R x S e r _ 0

O S C C l k

R E S E T _ L

8 k H z R E F

T E S T M O D E

G N D

T x S e r _ 1

TxSerClk_1

T x S y n c _ 1

T x M S y n c _ 1

T x O H _ 1

TxOHClk_1

R x S e r _ 1

TxChClk_1

R x S e r C l k _ 1

V D D

R x S y n c _ 1

T x C H N _ 1 _ 4

R x C R C M S y n c _ 1

T x C H N _ 1 _ 3

R x C A S M S y n c _ 1

R x C H C l k _ 1

T x C H N _ 1 _ 2

R x O H _ 1

T x C H N _ 1 _ 1

G N D

R x O H C l k _ 1

T x C H N _ 1 _ 0

R x L O S _ 1

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

2 9

3 0

3 1

3 2

3 3

3 4

3 5

3 6

3 7

3 8

3 9

4 0

4 1

4 2

4 3

4 4

4 5

4 6

4 7

4 8

4 9

5 0

5 1

5 2

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

1 5 6

1 5 5

1 5 4

1 5 3

1 5 2

1 5 1

1 5 0

1 4 9

1 4 8

1 4 7

1 4 6

1 4 5

1 4 4

1 4 3

1 4 2

1 4 1

1 4 0

1 3 9

1 3 8

1 3 7

1 3 6

1 3 5

1 3 4

1 3 3

1 3 2

1 3 1

1 3 0

1 2 9

1 2 8

1 2 7

1 2 6

1 2 5

1 2 4

1 2 3

1 2 2

1 2 1

1 2 0

1 1 9

1 1 8

1 1 7

1 1 6

1 1 5

1 1 4

1 1 3

1 1 2

1 1 1

1 1 0

1 0 9

1 0 8

1 0 7

1 0 6

1 0 5

2 0 8 L e a d P Q F P

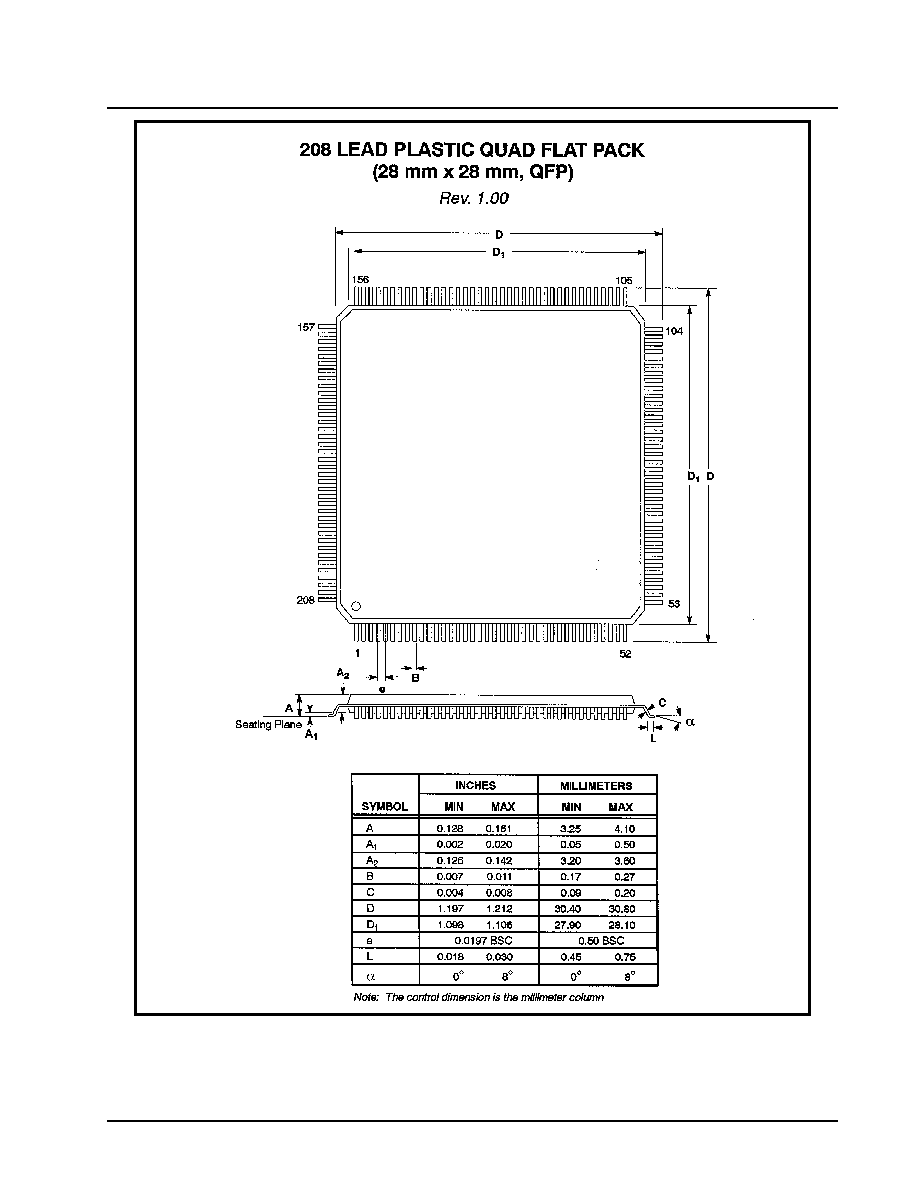

P

ART

N

UMBER

P

ACKAGE

O

PERATING

T

EMPERATURE

R

ANGE

XRT84V24IV-208

208 Lead PQFP

-40

∞

C to +85

∞

C

XRT84V24IV-160

160 Lead PQFP

-40

∞

C to +85

∞

C