Exar

Corporation 48720 Kato Road, Fremont CA, 94538

·

(510) 668-7000

·

FAX (510) 668-7017

·

www.exar.com

PRELIMINARY

XRT86L30

PRELIMINARY

SINGLE T1/E1/J1 FRAMER/LIU COMBO

MAY 2004

REV. P1.0.1

GENERAL DESCRIPTION

The XRT86L30 is a single channel 1.544 Mbit/s or

2.048 Mbit/s DS1/E1/J1 framer and LIU integrated

solution featuring R

3

technology (Relayless, Recon-

figurable, Redundancy). The physical interface is op-

timized with internal impedance, and with the patent-

ed pad structure, the XRT86L30 provides protection

from power failures and hot swapping.

The XRT86L30 contains an integrated DS1/E1/J1

framer and LIU which provide DS1/E1/J1 framing and

error accumulation in accordance with ANSI/ITU_T

specifications. The framer has a framing synchronizer

and transmit-receive slip buffers. The slip buffers can

be independently enabled or disabled as required

and can be configured to frame to the common DS1/

E1/J1 signal formats.

The Framer block contains a Transmit and Receive

T1/E1/J1 Framing function. There are 3 Transmit

HDLC controllers which encapsulate contents of the

Transmit HDLC buffers into LAPD Message frames.

There are 3 Receive HDLC controllers which extract

the payload content of Receive LAPD Message

frames from the incoming T1/E1/J1 data stream and

write the contents into the Receive HDLC buffers.

The framer also contains a Transmit and Overhead

Data Input port, which permits Data Link Terminal

Equipment direct access to the outbound T1/E1/J1

frames. Likewise, a Receive Overhead output data

port permits Data Link Terminal Equipment direct ac-

cess to the Data Link bits of the inbound T1/E1/J1

frames.

The XRT86L30 fully meets all of the latest T1/E1/J1

specifications: ANSI T1/E1.107-1988, ANSI T1/

E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/

E1.408-1990, AT&T TR 62411 (12-90) TR54016, and

ITU G-703, G.704, G706 and G.733, AT&T Pub.

43801, and ETS 300 011, 300 233, JT G.703, JT

G.704, JT G706, I.431. Extensive test and diagnostic

functions include Loop-backs, Boundary scan, Pseu-

do Random bit sequence (PRBS) test pattern gener-

ation, Performance Monitor, Bit Error Rate (BER)

meter, forced error insertion, and LAPD unchannel-

ized data payload processing according to ITU-T

standard Q.921.

Applications and Features (next page)

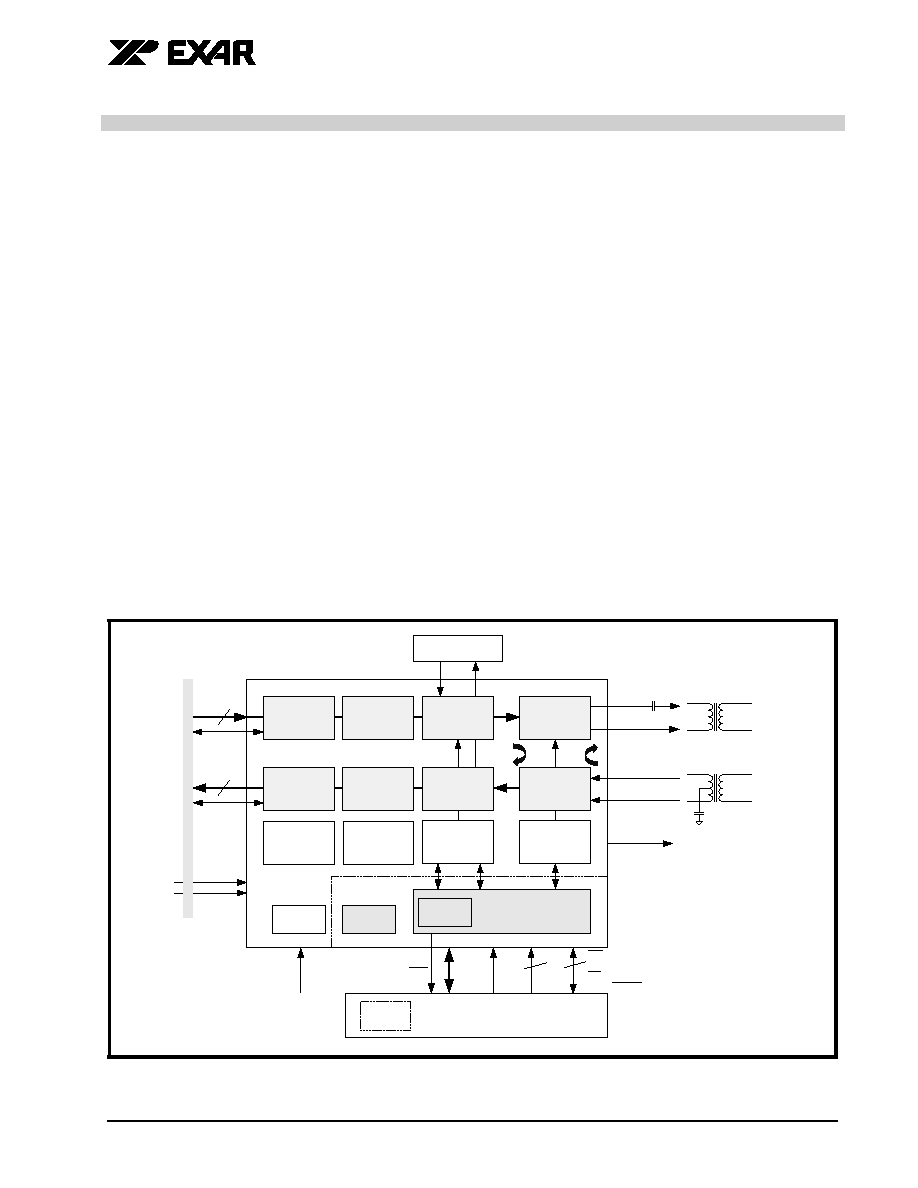

F

IGURE

1. XRT86L30 1-

CHANNEL

DS1 (T1/E1/J1) F

RAMER

/LIU C

OMBO

Performance

Monitor

PRBS

Generator &

Analyser

HDLC/LAPD

Controllers

LIU &

Loopback

Control

DMA

Interface

Signaling &

Alarms

JTAG

WR

ALE_AS

RD

RDY_DTACK

µ

P

Select

A[11:0]

D[7:0]

Microprocessor

Interface

4

3

Tx Serial

Clock

Rx Serial

Clock

8kHz sync

OSC

Back Plane

1.544-16.384 Mbit/s

Local PCM

Highway

ST

-B

US

2-Frame

Slip Buffer

Elastic Store

Tx Serial

Data In

Tx LIU

Interface

2-Frame

Slip Buffer

Elastic Store

Rx LIU

Interface

Rx Framer

Rx Serial

Data Out

RTIP

RRING

TTIP

TRING

External Data

Link Controller

Tx Overhead In

Rx Overhead Out

XRT86L30

Tx Framer

LLB

LB

System (Terminal) Side

Line Side

1:1 Turns Ratio

1:2 Turns Ratio

Memory

Intel/Motorola µP

Configuration, Control &

Status Monitor

RxLOS

TxON

INT

XRT86L30

SINGLE T1/E1/J1 FRAMER/LIU COMBO

REV. P1.0.1

PRELIMINARY

2

APPLICATIONS

· High-Density T1/E1/J1 interfaces for Multiplexers,

Switches, LAN Routers and Digital Modems

· SONET/SDH terminal or Add/Drop multiplexers

(ADMs)

· T1/E1/J1 add/drop multiplexers (MUX)

· Channel Service Units (CSUs): T1/E1/J1 and Frac-

tional T1/E1/J1

· Digital Access Cross-connect System (DACs)

· Digital Cross-connect Systems (DCS)

· Frame Relay Switches and Access Devices

(FRADS)

· ISDN Primary Rate Interfaces (PRA)

· PBXs and PCM channel bank

· T3 channelized access concentrators and M13

MUX

· Wireless base stations

· ATM equipment with integrated DS1 interfaces

· Multichannel DS1 Test Equipment

· T1/E1/J1 Performance Monitoring

· Voice over packet gateways

· Routers

FEATURES

· Full duplex DS1 Tx and Rx Framer/LIU

· Two 512-bit (two-frame) elastic store, PCM frame

slip buffers (FIFO) on TX and Rx provide up to

8.192 MHz asynchronous back plane connections

with jitter and wander attenuation

· Supports input PCM and signaling data at 1.544,

2.048, 4.096 and 8.192 Mbits. Also supports 4-

channel multiplexed 12.352/16.384 (HMVIP/H.100)

Mbit/s on the back plane bus (with stuffed don't

care bits for the other 3 channels)

· Programmable output clocks for Fractional T1/E1/

J1

· Supports Channel Associated Signaling (CAS)

· Supports Common Channel Signalling (CCS)

· Supports ISDN Primary Rate Interface (ISDN PRI)

signaling

· Extracts and inserts robbed bit signaling (RBS)

· 3 Integrated HDLC controllers for transmit and

receive, each controller having two 96-byte buffers

(buffer 0 / buffer 1)

· HDLC Controllers Support SS7

· Timeslot assignable HDLC

· V5.1 or V5.2 Interface

· Automatic Performance Report Generation (PMON

Status) can be inserted into the transmit LAPD

interface every 1 second or for a single transmis-

sion

· Alarm Indication Signal with Customer Installation

signature (AIS-CI)

· Remote Alarm Indication with Customer Installation

(RAI-CI)

· Gapped Clock interface mode for Transmit and

Receive.

· Intel/Motorola and Power PC interfaces for configu-

ration, control and status monitoring

· Parallel search algorithm for fast frame synchroni-

zation

· Wide choice of T1 framing structures: SF/D4, ESF,

SLC®96, T1DM and N-Frame (non-signaling)

· Direct access to D and E channels for fast trans-

mission of data link information

· PRBS, QRSS, and Network Loop Code generation

and detection

· Programmable Interrupt output pin

· Supports programmed I/O and DMA modes of

Read-Write access

· Each framer block encodes and decodes the T1/

E1/J1 Frame serial data

· Detects and forces Red (SAI), Yellow (RAI) and

Blue (AIS) Alarms

· Detects OOF, LOF, LOS errors and COFA condi-

tions

· Loopbacks: Local (LLB) and Line remote (LB)

· Facilitates Inverse Multiplexing for ATM

· Performance monitor with one second polling

· Boundary scan (IEEE 1149.1) JTAG test port

· Accepts external 8kHz Sync reference

· 3.3V CMOS operation with 5V tolerant inputs

· 128-pin TQFP package with

-40

°

C to +85

°

C

opera-

tion

XRT86L30

PRELIMINARY

REV. P1.0.1

SINGLE T1/E1/J1 FRAMER/LIU COMBO

I

LIST OF PARAGRAPHS

1.0 PIN LIST .................................................................................................................................................10

2.0 PIN DESCRIPTIONS ..............................................................................................................................11

3.0 MICROPROCESSOR INTERFACE BLOCK ..........................................................................................24

3.0.1 THE MICROPROCESSOR INTERFACE BLOCK SIGNALS ....................................................................................... 24

3.1 INTEL MODE PROGRAMMED I/O ACCESS (ASYNCHRONOUS) .................................................................. 27

3.2 MOTOROLA MODE PROGRAMMED I/O ACCESS (SYNCHRONOUS) .......................................................... 29

3.2.1 DMA READ/WRITE OPERATIONS .............................................................................................................................. 31

3.3 MEMORY MAPPED I/O ADDRESSING ............................................................................................................ 33

3.4 DESCRIPTION OF THE CONTROL REGISTERS ............................................................................................ 34

3.4.1 REGISTER DESCRIPTIONS ......................................................................................................................................... 40

3.5 PROGRAMMING THE LINE INTERFACE UNIT (LIU SECTION) ................................................................... 124

3.6 THE INTERRUPT STRUCTURE WITHIN THE FRAMER ............................................................................... 143

3.6.1 CONFIGURING THE INTERRUPT SYSTEM, AT THE FRAMER LEVEL .................................................................. 146

4.0 GENERAL DESCRIPTION AND INTERFACE .....................................................................................149

4.1 PHYSICAL INTERFACE .................................................................................................................................. 149

4.2 R3 TECHNOLOGY (RELAYLESS / RECONFIGURABLE / REDUNDANCY) ................................................ 150

4.2.1 LINE CARD REDUNDANCY ....................................................................................................................................... 150

4.2.2 TYPICAL REDUNDANCY SCHEMES ........................................................................................................................ 150

4.2.3 1:1 AND 1+1 REDUNDANCY WITHOUT RELAYS .................................................................................................... 150

4.2.4 TRANSMIT INTERFACE WITH 1:1 AND 1+1 REDUNDANCY .................................................................................. 150

4.2.5 RECEIVE INTERFACE WITH 1:1 AND 1+1 REDUNDANCY ..................................................................................... 151

4.3 POWER FAILURE PROTECTION ................................................................................................................... 152

4.4 OVERVOLTAGE AND OVERCURRENT PROTECTION ................................................................................ 152

4.5 NON-INTRUSIVE MONITORING ..................................................................................................................... 152

4.6 T1/E1 SERIAL PCM INTERFACE ................................................................................................................... 153

4.7 T1/E1 FRACTIONAL INTERFACE .................................................................................................................. 154

4.8 T1/E1 TIME SLOT SUBSTITUTION AND CONTROL ..................................................................................... 155

4.9 ROBBED BIT SIGNALING/CAS SIGNALING ................................................................................................. 156

4.10 OVERHEAD INTERFACE .............................................................................................................................. 158

4.11 FRAMER BYPASS MODE ............................................................................................................................. 159

4.12 HIGH-SPEED NON-MULTIPLEXED INTERFACE ........................................................................................ 160

4.13 HIGH-SPEED MULTIPLEXED INTERFACE ................................................................................................. 161

5.0 LOOPBACK MODES OF OPERATION ............................................................................................... 162

5.1 LIU PHYSICAL INTERFACE LOOPBACK DIAGNOSTICS ............................................................................ 162

5.1.1 LOCAL ANALOG LOOPBACK .................................................................................................................................. 162

5.1.2 REMOTE LOOPBACK ................................................................................................................................................ 162

5.1.3 DIGITAL LOOPBACK ................................................................................................................................................. 163

5.1.4 DUAL LOOPBACK ..................................................................................................................................................... 163

5.1.5 FRAMER REMOTE LINE LOOPBACK ...................................................................................................................... 163

5.1.6 FRAMER PAYLOAD LOOPBACK ............................................................................................................................. 164

5.1.7 FRAMER LOCAL LOOPBACK ................................................................................................................................... 164

6.0 HDLC CONTROLLERS AND LAPD MESSAGES ...............................................................................165

6.1 PROGRAMMING SEQUENCE FOR SENDING LESS THAN 96-BYTE MESSAGES .................................... 165

6.2 PROGRAMMING SEQUENCE FOR SENDING LARGE MESSAGES ........................................................... 165

6.3 PROGRAMMING SEQUENCE FOR RECEIVING LAPD MESSAGES ........................................................... 165

6.4 SS7 (SIGNALING SYSTEM NUMBER 7) FOR ESF IN DS1 ONLY ................................................................ 166

6.5 DS1/E1 DATALINK TRANSMISSION USING THE HDLC CONTROLLERS ................................................. 167

6.6 TRANSMIT BOS (BIT ORIENTED SIGNALING) PROCESSOR ..................................................................... 167

6.6.1 DESCRIPTION OF BOS .............................................................................................................................................. 167

6.6.2 PRIORITY CODEWORD MESSAGE .......................................................................................................................... 167

6.6.3 COMMAND AND RESPONSE INFORMATION .......................................................................................................... 167

6.7 TRANSMIT MOS (MESSAGE ORIENTED SIGNALING) PROCESSOR ........................................................ 168

6.7.1 DISCUSSION OF MOS ............................................................................................................................................... 168

6.7.2 PERIODIC PERFORMANCE REPORT ...................................................................................................................... 168

6.7.3 TRANSMISSION-ERROR EVENT .............................................................................................................................. 169

6.7.4 PATH AND TEST SIGNAL IDENTIFICATION MESSAGE ......................................................................................... 169

6.7.5 FRAME STRUCTURE ................................................................................................................................................. 169

6.7.6 FLAG SEQUENCE ...................................................................................................................................................... 169

6.7.7 ADDRESS FIELD ........................................................................................................................................................ 170

6.7.8 ADDRESS FIELD EXTENSION BIT (EA) ................................................................................................................... 170

PRELIMINARY

XRT86L30

SINGLE T1/E1/J1 FRAMER/LIU COMBO

REV. P1.0.1

II

6.7.9 COMMAND OR RESPONSE BIT (C/R) ...................................................................................................................... 170

6.7.10 SERVICE ACCESS POINT IDENTIFIER (SAPI) ...................................................................................................... 170

6.7.11 TERMINAL ENDPOINT IDENTIFIER (TEI) ............................................................................................................... 170

6.7.12 CONTROL FIELD ...................................................................................................................................................... 170

6.7.13 FRAME CHECK SEQUENCE (FCS) FIELD ............................................................................................................. 170

6.7.14 TRANSPARENCY (ZERO STUFFING) ..................................................................................................................... 171

6.8 TRANSMIT SLC®96 DATA LINK CONTROLLER .......................................................................................... 172

6.9 D/E TIME SLOT TRANSMIT HDLC CONTROLLER BLOCK V5.1 OR V5.2 INTERFACE ............................ 173

6.10 AUTOMATIC PERFORMANCE REPORT (APR) .......................................................................................... 173

6.10.1 BIT VALUE INTERPRETATION ............................................................................................................................... 173

7.0 OVERHEAD INTERFACE BLOCK ...................................................................................................... 175

7.1 DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK .......................................................................... 175

7.1.1 DESCRIPTION OF THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK .............................................. 175

7.1.2 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE FACILITY DATA

LINK (FDL) BITS IN ESF FRAMING FORMAT MODE ............................................................................................... 175

7.1.3 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE SIGNALING

FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE ........................................................................ 177

7.1.4 CONFIGURE THE DS1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE REMOTE SIG-

NALING (R) BITS IN T1DM FRAMING FORMAT MODE ........................................................................................... 178

7.2 DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK ......................................................................... 178

7.2.1 DESCRIPTION OF THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK ............................................. 179

7.2.2 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE FACILITY

DATA LINK (FDL) BITS IN ESF FRAMING FORMAT MODE .................................................................................... 179

7.2.3 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE SIGNALING

FRAMING (FS) BITS IN N OR SLC®96 FRAMING FORMAT MODE ........................................................................ 180

7.2.4 CONFIGURE THE DS1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS DESTINATION OF THE REMOTE

SIGNALING (R) BITS IN T1DM FRAMING FORMAT MODE ..................................................................................... 181

7.3 E1 OVERHEAD INTERFACE BLOCK ............................................................................................................ 182

7.4 E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK ............................................................................. 182

7.4.1 DESCRIPTION OF THE E1 TRANSMIT OVERHEAD INPUT INTERFACE BLOCK ................................................. 182

7.4.2 CONFIGURE THE E1 TRANSMIT OVERHEAD INPUT INTERFACE MODULE AS SOURCE OF THE NATIONAL BIT SE-

QUENCE IN E1 FRAMING FORMAT MODE .............................................................................................................. 183

7.5 E1 RECEIVE OVERHEAD INTERFACE ......................................................................................................... 185

7.5.1 DESCRIPTION OF THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE BLOCK ............................................... 185

7.5.2 CONFIGURE THE E1 RECEIVE OVERHEAD OUTPUT INTERFACE MODULE AS SOURCE OF THE NATIONAL BIT

SEQUENCE IN E1 FRAMING FORMAT MODE .......................................................................................................... 186

8.0 LIU TRANSMIT PATH ......................................................................................................................... 188

8.1 TRANSMIT DIAGNOSTIC FEATURES ........................................................................................................... 188

8.1.1 TAOS (TRANSMIT ALL ONES) .................................................................................................................................. 188

8.1.2 ATAOS (AUTOMATIC TRANSMIT ALL ONES) ......................................................................................................... 189

8.1.3 NETWORK LOOP UP CODE ...................................................................................................................................... 189

8.1.4 NETWORK LOOP DOWN CODE ............................................................................................................................... 189

8.1.5 QRSS GENERATION .................................................................................................................................................. 190

8.2 T1 LONG HAUL LINE BUILD OUT (LBO) ...................................................................................................... 190

8.3 T1 SHORT HAUL LINE BUILD OUT (LBO) .................................................................................................... 191

8.3.1 ARBITRARY PULSE GENERATOR ........................................................................................................................... 191

8.3.2 DMO (DIGITAL MONITOR OUTPUT) ......................................................................................................................... 192

8.3.3 TRANSMIT JITTER ATTENUATOR ........................................................................................................................... 192

8.4 LINE TERMINATION (TTIP/TRING) ................................................................................................................ 193

9.0 LIU RECEIVE PATH ............................................................................................................................ 194

9.1 LINE TERMINATION (RTIP/RRING) ............................................................................................................... 194

9.1.1 CASE 1: INTERNAL TERMINATION .......................................................................................................................... 194

9.1.2 CASE 2: INTERNAL TERMINATION WITH ONE EXTERNAL FIXED RESISTOR FOR ALL MODES .................... 194

9.1.3 EQUALIZER CONTROL ............................................................................................................................................. 195

9.1.4 CABLE LOSS INDICATOR ......................................................................................................................................... 195

9.2 RECEIVE SENSITIVITY ................................................................................................................................... 196

9.2.1 AIS (ALARM INDICATION SIGNAL) .......................................................................................................................... 196

9.2.2 NLCD (NETWORK LOOP CODE DETECTION) ......................................................................................................... 196

9.2.3 FLSD (FIFO LIMIT STATUS DETECTION) ................................................................................................................ 197

9.2.4 RECEIVE JITTER ATTENUATOR .............................................................................................................................. 197

9.2.5 RXMUTE (RECEIVER LOS WITH DATA MUTING) ................................................................................................... 197

10.0 THE E1 TRANSMIT/RECEIVE FRAMER .......................................................................................... 199

10.1 DESCRIPTION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK ................ 199

10.1.1 BRIEF DISCUSSION OF THE TRANSMIT/RECEIVE PAYLOAD DATA INPUT INTERFACE BLOCK OPERATING AT