© 2005 Fairchild Semiconductor Corporation

DS500296

www.fairchildsemi.com

August 1999

Revised May 2005

7

4

AC

T1

6245 1

6

-Bi

t

T

r

ansc

eiver

wi

th

3-ST

A

T

E Out

put

s

74ACT16245

16-Bit Transceiver with 3-STATE Outputs

General Description

The ACT16245 contains sixteen non-inverting bidirectional

buffers with 3-STATE outputs and is intended for bus ori-

ented applications. The device is byte controlled. Each has

separate control inputs which can be shorted together for

full 16-bit operation. The T/R inputs determine the direction

of data flow through the device. The OE inputs disable both

the A and B ports by placing them in a high impedance

state.

Features

s

Bidirectional non-inverting buffers

s

Separate control logic for each byte

s

16-bit version of the ACT245

s

Outputs source/sink 24 mA

s

TTL-compatible inputs

Ordering Code:

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

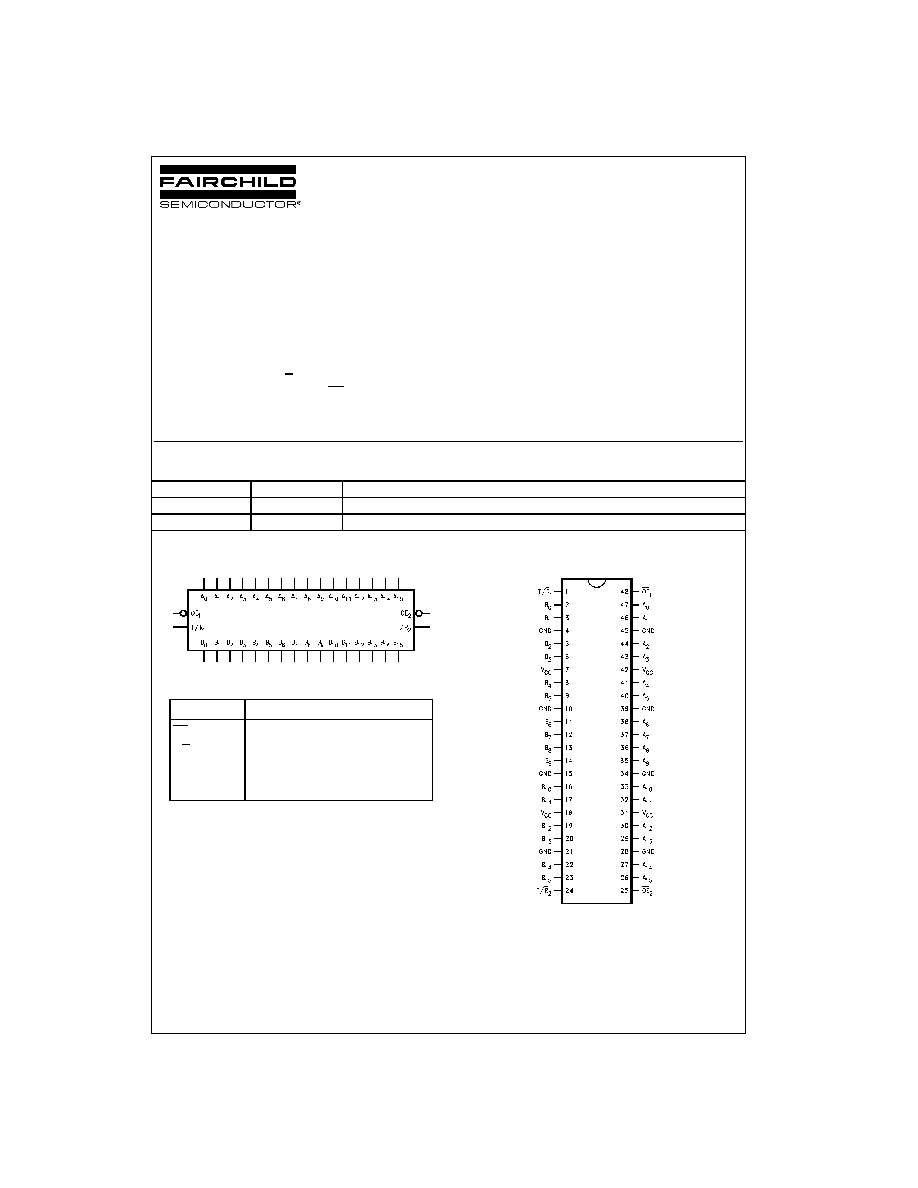

Logic Symbol

Pin Description

Connection Diagram

FACT

•

is a trademark of Fairchild Semiconductor Corporation.

Order Number

Package Number

Package Description

74ACT16245SSC

MS48A

48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

74ACT16245MTD

MTD48

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Pin Names

Description

OE

n

Output Enable Input (Active LOW)

T/R

Transmit/Receive Input

A

0

≠A

15

Side A Inputs/Outputs

B

0

≠B

15

Side B Outputs/Inputs

www.fairchildsemi.com

2

74ACT16245

Functional Description

The ACT16245 contains sixteen non-inverting bidirectional

buffers with 3-STATE outputs. The device is byte controlled

with each byte functioning identically, but independent of

the other. The control pins can be shorted together to

obtain full 16-bit operation. The following description

applies to each byte. When the T/R input is HIGH, then Bus

A data is transmitted to Bus B. When the T/R input is LOW,

Bus B data is transmitted to Bus A. The 3-STATE outputs

are controlled by an Output Enable (OE

n

) input for each

byte. When OE

n

is LOW, the outputs are in 2-state mode.

When OE

n

is HIGH, the outputs are in the high impedance

mode, but this does not interfere with entering new data

into the inputs.

Truth Tables

H

HIGH Voltage Level

L

LOW Voltage Level

X

Immaterial

Z

High Impedance

Logic Diagram

Inputs

Outputs

OE

1

T/R

1

L

L

Bus B

0

≠B

7

Data to Bus A

0

≠A

7

L

H

Bus A

0

≠A

7

Data to Bus B

0

≠B

7

H

X

HIGH-Z State on A

0

≠A

7

, B

0

≠B

7

Inputs

Outputs

OE

2

T/R

2

L

L

Bus B

8

≠B

15

Data to Bus A

8

≠A

15

L

H

Bus A

8

≠A

15

Data to Bus B

8

≠B

15

H

X

HIGH-Z State on A

8

≠A

15

, B

8

≠B

15

3

www.fairchildsemi.com

7

4

AC

T1

6245

Absolute Maximum Ratings

(Note 1)

Recommended Operating

Conditions

Note 1: Absolute maximum ratings are those values beyond which damage

to the device may occur. The databook specifications should be met, with-

out exception to ensure that the system design is reliable over its power

supply, temperature, and output/input loading variables. Fairchild does not

recommend operation of FACT

•

circuits outside databook specifications.

DC Electrical Characteristics

Note 2: All outputs loaded; thresholds associated with output under test.

Note 3: Maximum test duration 2.0 ms; one output loaded at a time.

Supply Voltage (V

CC

)

0.5V to

7.0V

DC Input Diode Current (I

IK

)

V

I

0.5V

20 mA

V

I

V

CC

0.5V

20 mA

DC Output Diode Current (I

OK

)

V

O

0.5V

20 mA

V

O

V

CC

0.5V

20 mA

DC Output Voltage (V

O

)

0.5V to V

CC

0.5V

DC Output Source/Sink Current (I

O

)

r

50 mA

DC V

CC

or Ground Current

per Output Pin

r

50 mA

Storage Temperature

65

q

C to

150

q

C

Supply Voltage (V

CC

)

4.5V to 5.5V

Input Voltage (V

I

)

0V to V

CC

Output Voltage (V

O

)

0V to V

CC

Operating Temperature (T

A

)

40

q

C to

85

q

C

Minimum Input Edge Rate (

'

V/

'

t)

125 mV/ns

V

IN

from 0.8V to 2.0V

V

CC

@ 4.5V, 5.5V

Symbol

Parameter

V

CC

T

A

25

q

C

T

A

40

q

C to

85

q

C

Units

Conditions

(V)

Typ

Guaranteed Limits

V

IH

Minimum HIGH

4.5

1.5

2.0

2.0

V

V

OUT

0.1V

Input Voltage

5.5

1.5

2.0

2.0

or V

CC

0.1V

V

IL

Maximum LOW

4.5

1.5

0.8

0.8

V

V

OUT

0.1V

Input Voltage

5.5

1.5

0.8

0.8

or V

CC

0.1V

V

OH

Minimum HIGH

4.5

4.49

4.4

4.4

V

I

OUT

50

P

A

Output Voltage

5.5

5.49

5.4

5.4

V

IN

V

IL

or V

IH

4.5

3.86

3.76

V

I

OH

=

24 mA

5.5

4.86

4.76

I

OH

=

24 mA (Note 2)

V

OL

Maximum LOW

4.5

0.001

0.1

0.1

V

I

OUT

50

P

A

Output Voltage

5.5

0.001

0.1

0.1

V

IN

V

IL

or V

IH

4.5

0.36

0.44

V

I

OL

= 24 mA

5.5

0.36

0.44

I

OL

= 24 mA (Note 2)

I

OZT

Maximum I/O

5.5

r

0.5

r

5.0

P

A

V

I

V

IL

, V

IH

Leakage Current

V

O

V

CC

, GND

I

IN

Maximum Input

5.5

r

0.1

r

1.0

P

A

V

I

V

CC

, GND

Leakage Current

I

CCT

Maximum I

CC

/Input

5.5

0.6

1.5

mA

V

I

V

CC

2.1V

I

CC

Max Quiescent

5.5

8.0

80.0

P

A

V

IN

V

CC

or GND

Supply Current

I

OLD

Minimum Dynamic

5.5

75

mA

V

OLD

1.65V Max

I

OHD

Output Current (Note 3)

75

mA

V

OHD

3.85V Min

www.fairchildsemi.com

4

74ACT16245

AC Electrical Characteristics

Note 4: Voltage Range 5.0 is 5.0V

r

0.5V.

Capacitance

V

CC

T

A

25

q

C

T

A

40

q

C to

85

q

C

Symbol

Parameter

(V)

C

L

50 pF

C

L

50 pF

Units

(Note 4)

Min

Typ

Max

Min

Max

t

PLH

Propagation

5.0

3.2

5.7

8.4

3.2

9.0

ns

t

PHL

Delay A

n

, B

n

to B

n

, A

n

2.6

5.1

7.9

2.6

8.4

t

PZH

Output Enable

5.0

3.7

6.4

9.4

2.7

10.0

ns

t

PZL

Time

4.1

7.4

10.5

3.4

11.6

t

PHZ

Output Disable

5.0

2.2

5.4

8.7

2.2

9.3

ns

t

PLZ

Time

2.0

5.2

8.2

2.0

8.8

Symbol

Parameter

Typ

Units

Conditions

C

IN

Input Pin Capacitance

4.5

pF

V

CC

5.0V

C

PD

Power Dissipation Capacitance

25

pF

V

CC

5.0V

5

www.fairchildsemi.com

7

4

AC

T1

6245

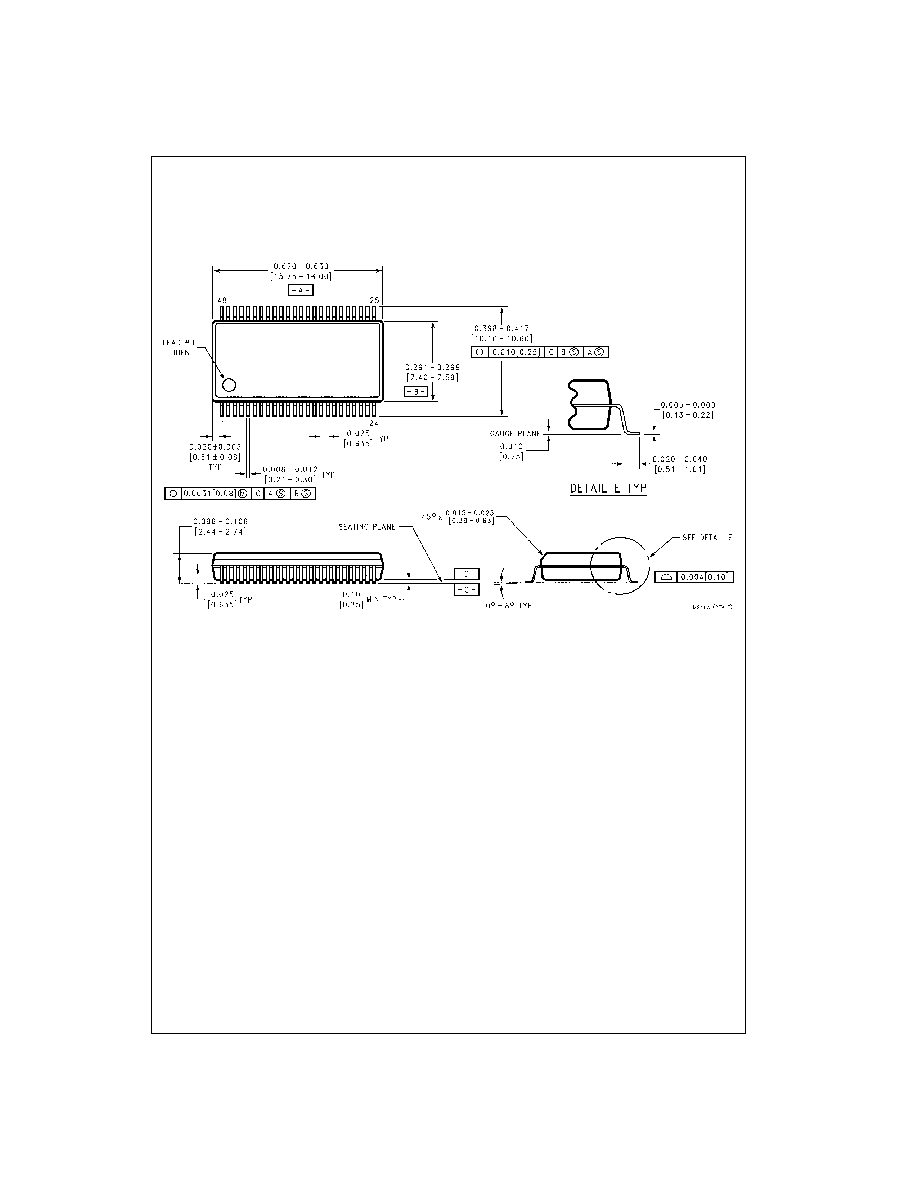

Physical Dimensions

inches (millimeters) unless otherwise noted

48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide

Package Number MS48A