Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

© 2005 Fairchild Semiconductor Corporation

DS011552

www.fairchildsemi.com

February 1993

Revised April 2005

7

4

L

VX24

4

Low V

o

l

t

age Oct

a

l Buff

er/

L

i

ne

Dri

ver

wit

h

3-ST

A

T

E

Out

put

s

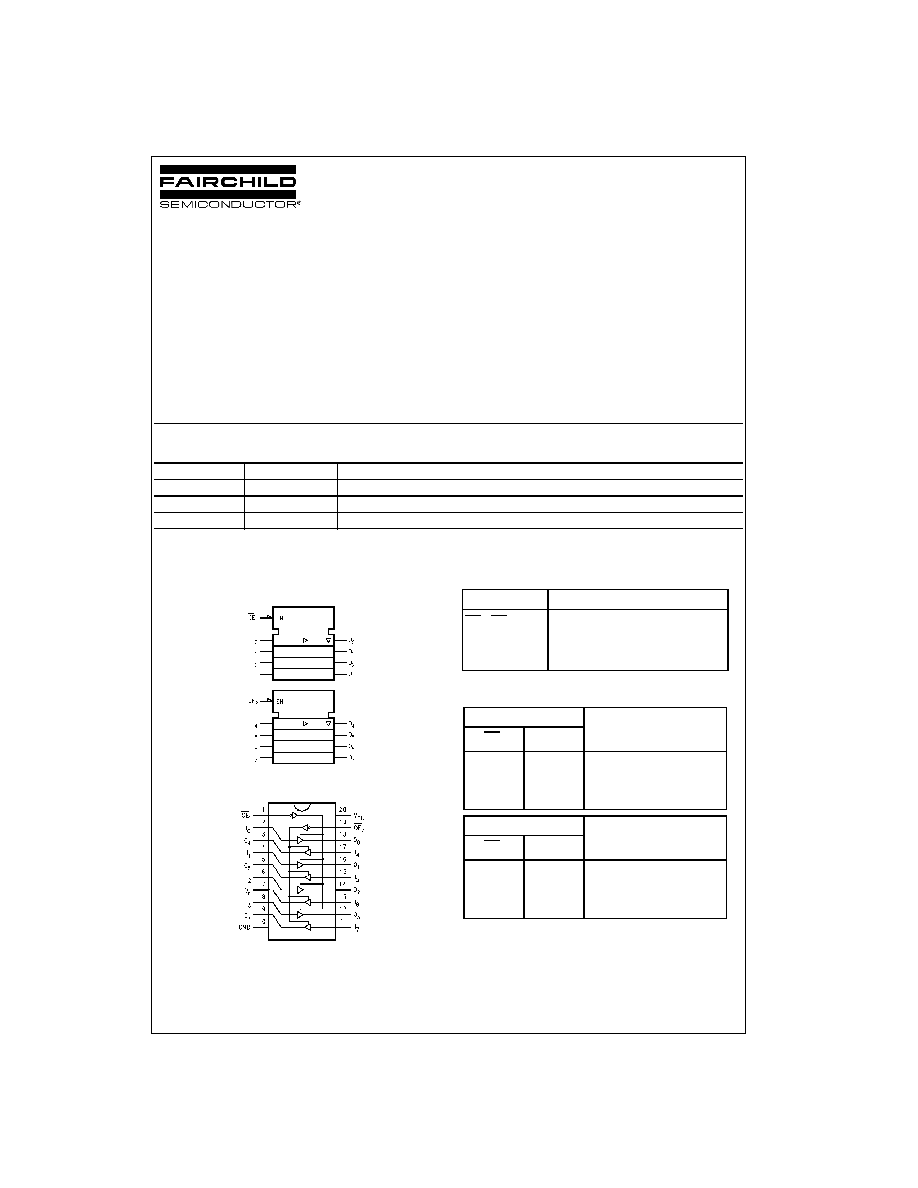

74LVX244

Low Voltage Octal Buffer/Line Driver with

3-STATE Outputs

General Description

The LVX244 is an octal non-inverting buffer and line driver

designed to be employed as a memory address driver,

clock driver and bus oriented transmitter or receiver which

provides improved PC board density. The inputs tolerate up

to 7V allowing interface of 5V systems to 3V systems.

Features

s

Input voltage translation from 5V to 3V

s

Ideal for low power/low noise 3.3V applications

s

Guaranteed simultaneous switching noise level and

dynamic threshold performance

Ordering Code:

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

Pb-Free package per JEDEC J-STD-020B.

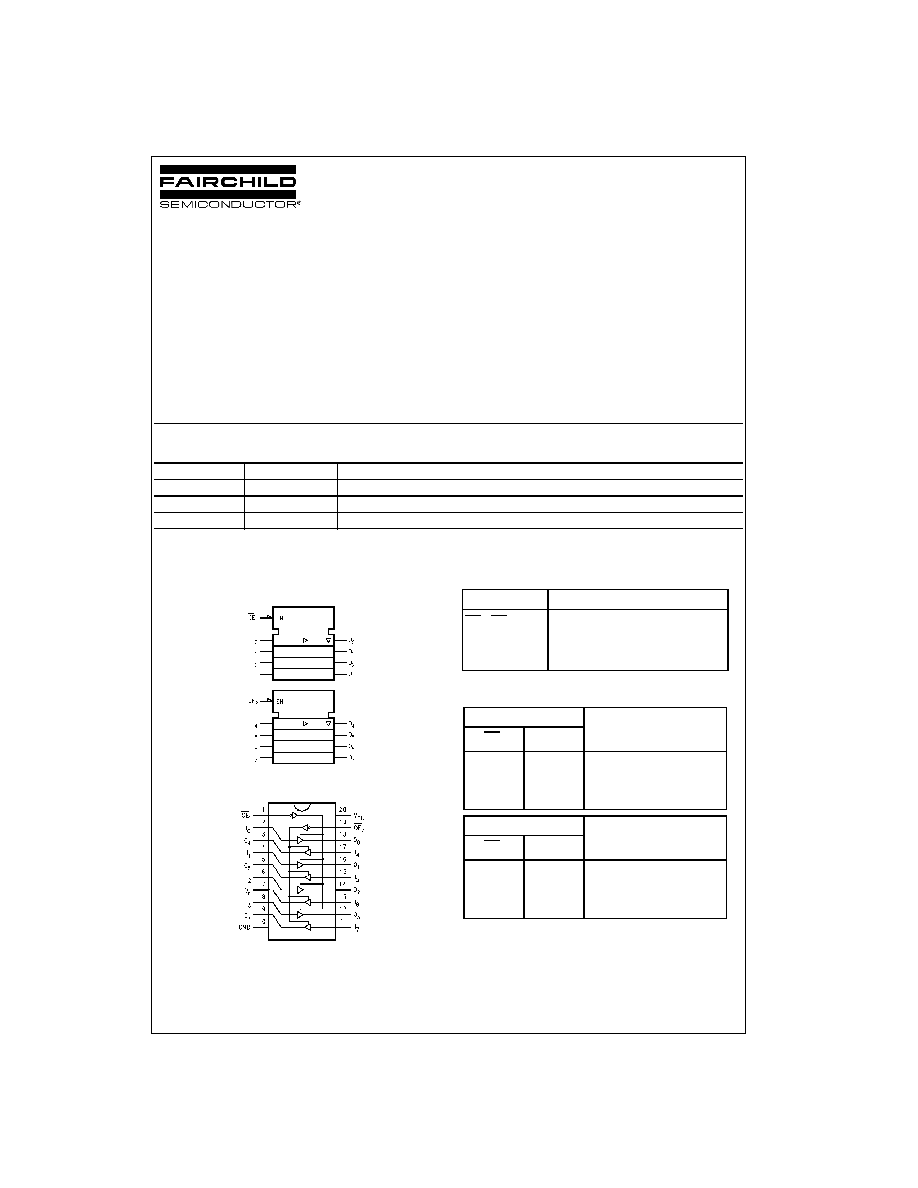

Logic Symbol

IEEE/IEC

Connection Diagram

Pin Descriptions

Truth Tables

H

HIGH Voltage Level

L

LOW Voltage Level

X

Immaterial

Z

High Impedance

Order Number

Package Number

Package Description

74LVX244M

M20B

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

74LVX244SJ

M20D

Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74LVX244MTC

MTC20

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names

Description

OE

1

, OE

2

3-STATE Output Enable Inputs

I

0

I

7

Inputs

O

0

O

7

Outputs

Inputs

Outputs

OE

1

I

n

(Pins 12, 14, 16, 18)

L

L

L

L

H

H

H

X

Z

Inputs

Outputs

OE

2

I

n

(Pins 3, 5, 7, 9)

L

L

L

L

H

H

H

X

Z

www.fairchildsemi.com

2

74

L

VX244

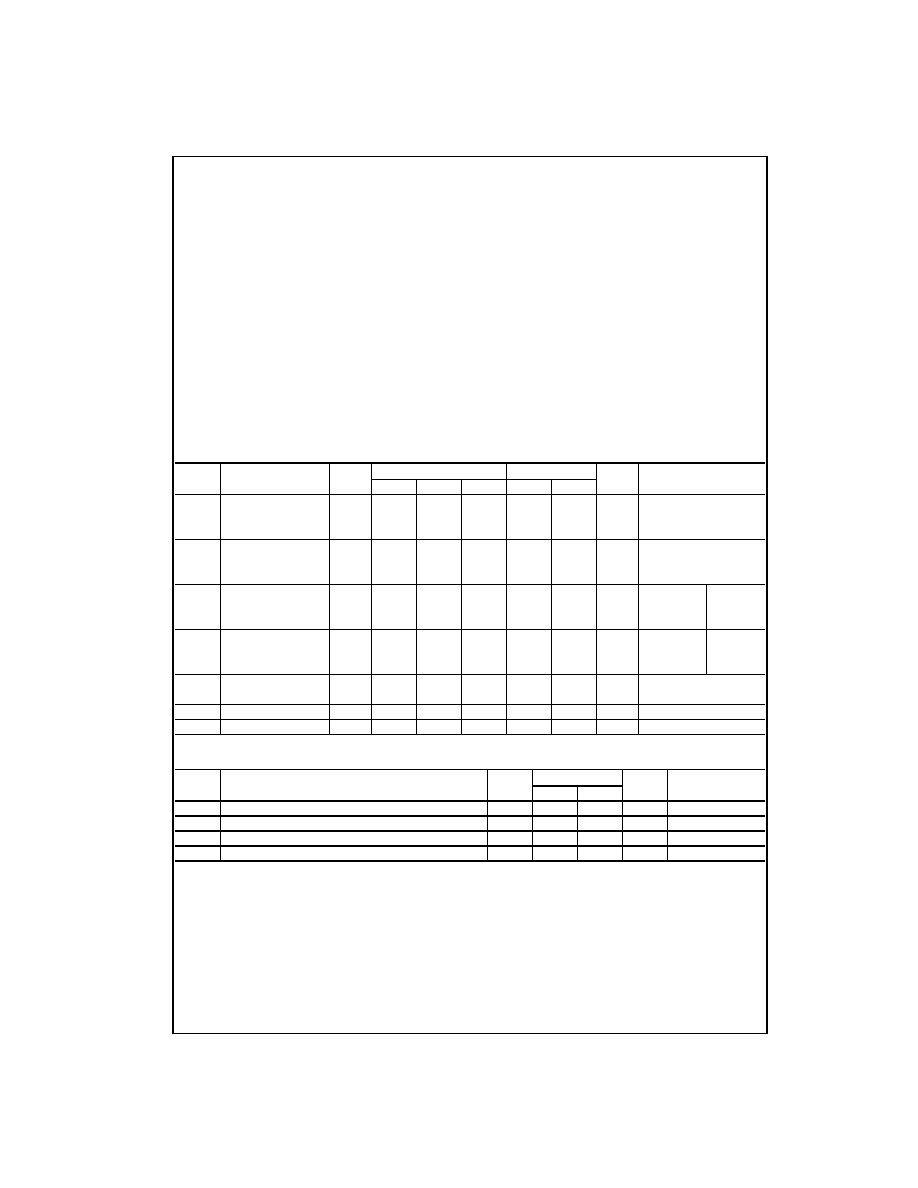

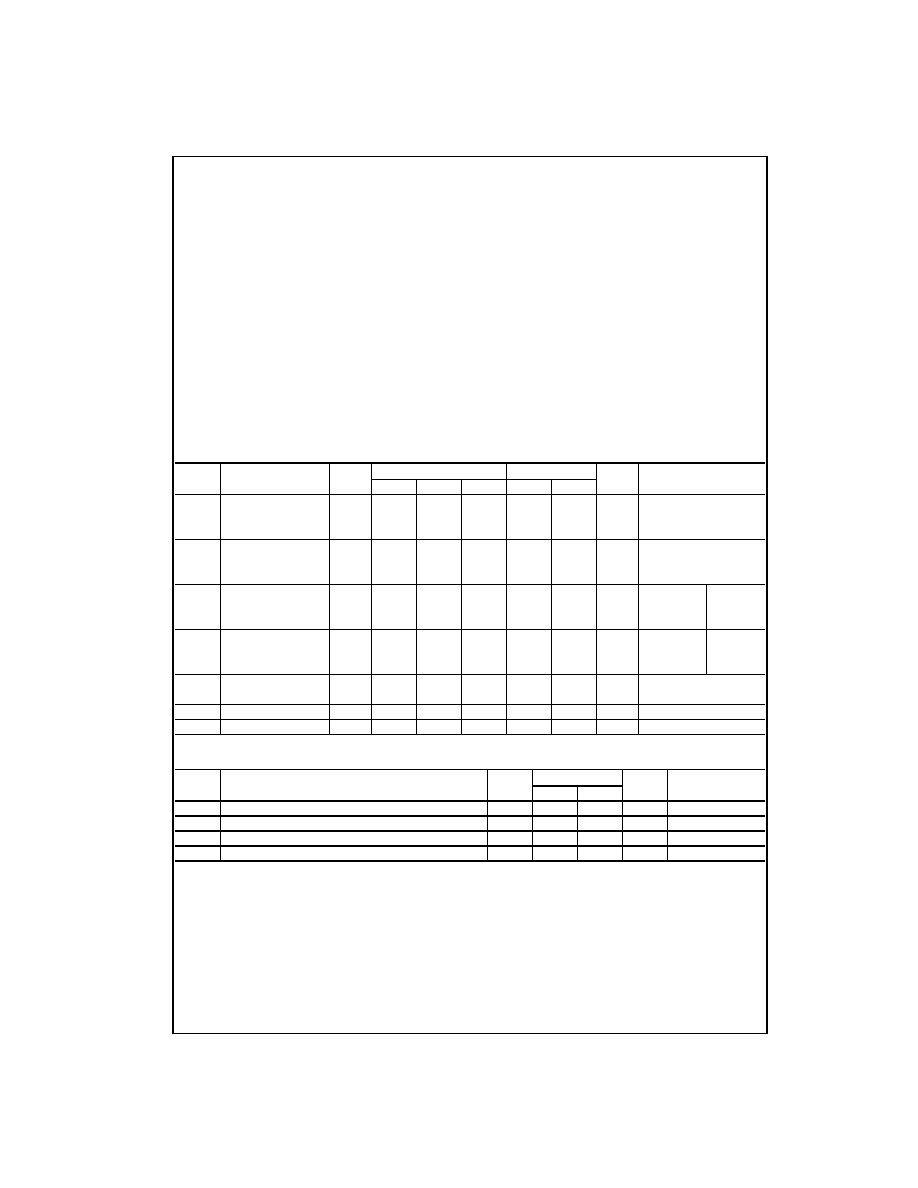

Absolute Maximum Ratings

(Note 1)

Recommended Operating

Conditions

(Note 2)

Note 1: The "Absolute Maximum Ratings" are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The "Recommended Operating Conditions" table will define the conditions

for actual device operation.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

DC Electrical Characteristics

Noise Characteristics

(Note 3)

Note 3: Input t

r

t

f

3 ns

Supply Voltage (V

CC

)

0.5V to

7.0V

DC Input Diode Current (I

IK

)

V

I

0.5V

20 mA

DC Input Voltage (V

I

)

0.5V to 7V

DC Output Diode Current (I

OK

)

V

O

0.5V

20 mA

V

O

V

CC

0.5V

20 mA

DC Output Voltage (V

O

)

0.5V to V

CC

0.5V

DC Output Source

or Sink Current (I

O

)

r

25 mA

DC V

CC

or Ground Current

(I

CC

or I

GND

)

r

75 mA

Storage Temperature (T

STG

)

65

q

C to

150

q

C

Power Dissipation

180 mW

Supply Voltage (V

CC

)

2.0V to 3.6V

Input Voltage (V

I

)

0V to 5.5V

Output Voltage (V

o

)

0V to V

CC

Operating Temperature (T

A

)

40

q

C to

85

q

C

Input Rise and Fall Time (

'

t/

'

V)

0 ns/V to 100 ns/V

Symbol

Parameter

V

CC

T

A

25

q

C

T

A

40

q

C to

85

q

C

Units

Conditions

Min

Typ

Max

Min

Max

V

IH

HIGH Level Input

2.0

1.5

1.5

Voltage

3.0

2.0

2.0

V

3.6

2.4

2.4

V

IL

LOW Level Input

2.0

0.5

0.5

Voltage

3.0

0.8

0.8

V

3.6

0.8

0.8

V

OH

HIGH Level Output

2.0

1.9

2.0

1.9

V

IN

V

IH

or V

IL

I

OH

50

P

A

Voltage

3.0

2.9

3.0

2.9

V

I

OH

50

P

A

3.0

2.58

2.48

I

OH

4 mA

V

OL

LOW Level Output

2.0

0.0

0.1

0.1

V

IN

V

IH

or V

IL

I

OL

50

P

A

Voltage

3.0

0.0

0.1

0.1

V

I

OL

50

P

A

3.0

0.36

0.44

I

OL

4 mA

I

OZ

3-STATE Output

3.6

r

0.25

r

2.5

P

A

V

IN

V

IH

or V

IL

Off-State Current

V

OUT

V

CC

or GND

I

IN

Input Leakage Current

3.6

r

0.1

r

1.0

P

A

V

IN

5.5V or GND

I

CC

Quiescent Supply Current

3.6

4.0

40.0

P

A

V

IN

V

CC

or GND

Symbol

Parameter

V

CC

T

A

25

q

C

Units

C

L

(pF)

(V)

Typ

Limit

V

OLP

Quiet Output Maximum Dynamic V

OL

3.3

0.5

0.8

V

50

V

OLV

Quiet Output Minimum Dynamic V

OL

3.3

0.5

0.8

V

50

V

IHD

Minimum HIGH Level Dynamic Input Voltage

3.3

2.0

V

50

V

ILD

Maximum LOW Level Dynamic Input Voltage

3.3

0.8

V

50

3

www.fairchildsemi.com

74

L

V

X

2

44

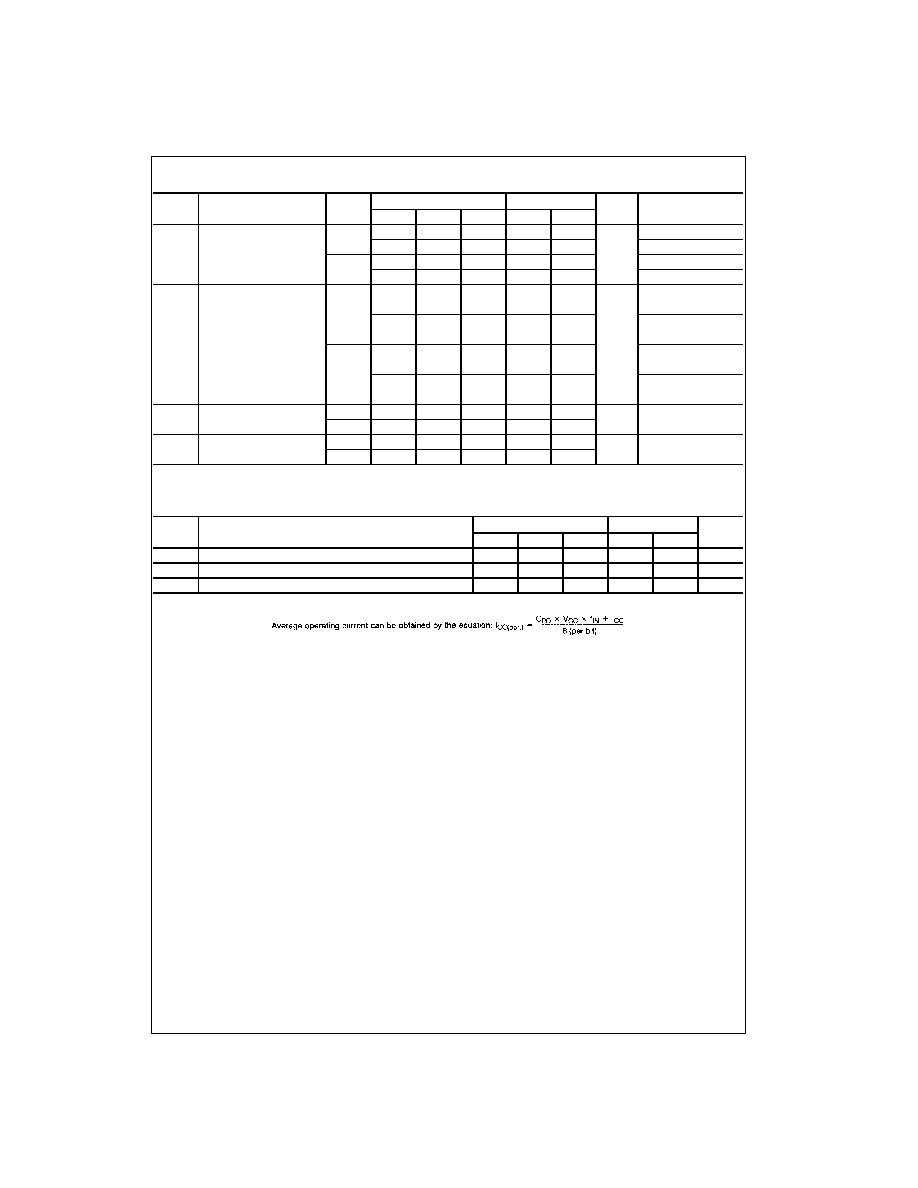

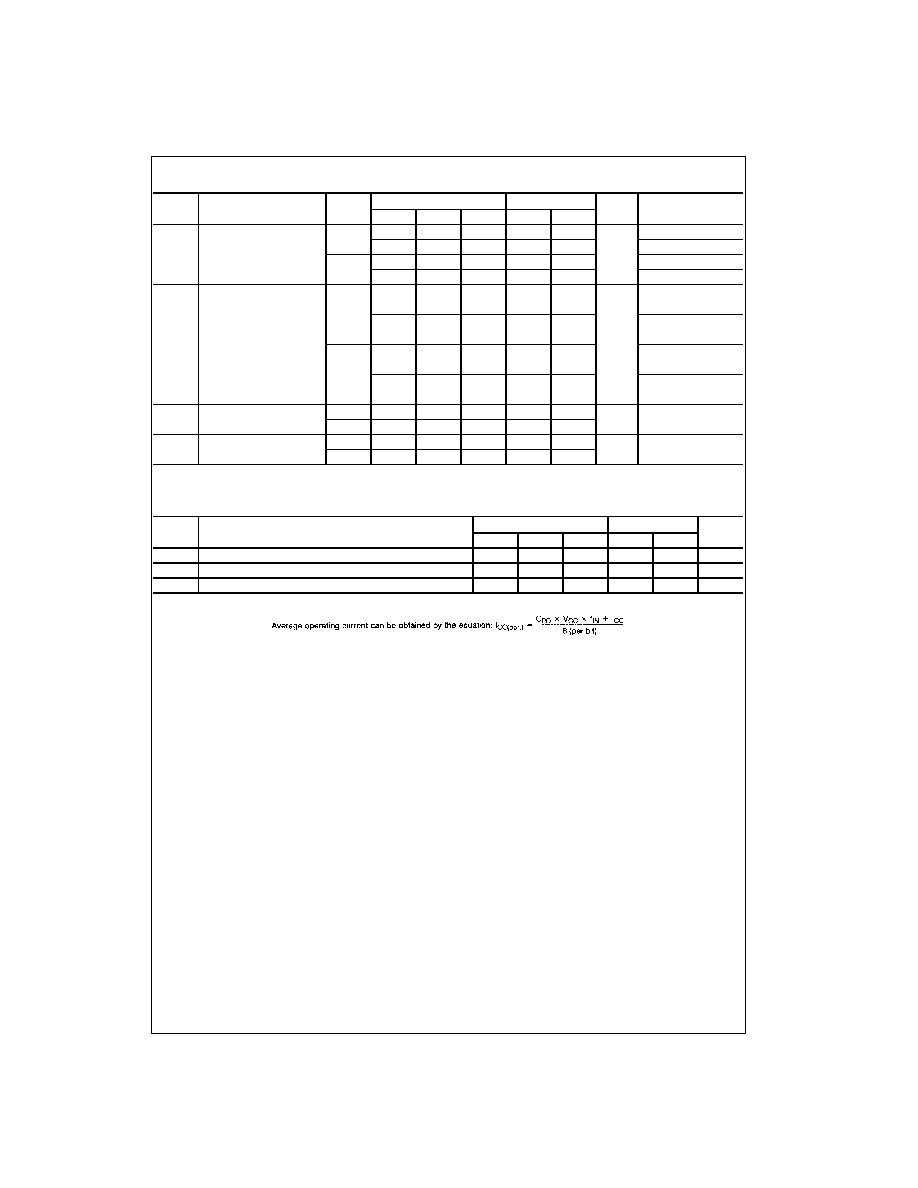

AC Electrical Characteristics

Note 4: Parameter guaranteed by design. t

OSLH

|t

PLHm

t

PLHn

|, t

OSHL

|t

PHLm

t

PHLn

|

Capacitance

Note 5: C

PD

is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Symbol

Parameter

V

CC

T

A

25

q

C

T

A

40

q

C to

85

q

C

Units

Conditions

(V)

Min

Typ

Max

Min

Max

t

PLH

Propagation Delay

2.7

6.1

11.4

1.0

13.5

ns

C

L

15 pF

t

PHL

Time

8.6

14.9

1.0

17.0

C

L

50 pF

3.3

r

0.3

4.7

7.1

1.0

8.5

C

L

15 pF

7.2

10.6

1.0

12.0

C

L

50 pF

t

PZL

3-STATE Output

2.7

7.1

13.8

1.0

16.5

ns

C

L

15 pF,

t

PZH

Enable Time

R

L

1 k

:

9.6

17.3

1.0

20.0

C

L

50 pF,

R

L

1 k

:

3.3

r

0.3

5.5

8.8

1.0

10.5

C

L

15 pF,

R

L

1 k

:

8.0

12.3

1.0

14.0

C

L

50 pF,

R

L

1 k

:

t

PLZ

3-STATE Output

2.7

11.6

16.0

1.0

19.0

ns

C

L

50 pF,

t

PHZ

Disable Time

3.3

r

0.3

9.7

11.4

1.0

13.0

R

L

1 k

:

t

OSLH

Output to Output

2.7

1.5

1.5

ns

C

L

50 pF

t

OSHL

Skew (Note 4)

3.3

1.5

1.5

Symbol

Parameter

T

A

25

q

C

T

A

40

q

C to

85

q

C

Units

Min

Typ

Max

Min

Max

C

IN

Input Capacitance

4

10

10

pF

C

OUT

Output Capacitance

6

pF

C

PD

Power Dissipation Capacitance (Note 5)

19

pF

www.fairchildsemi.com

4

74

L

VX244

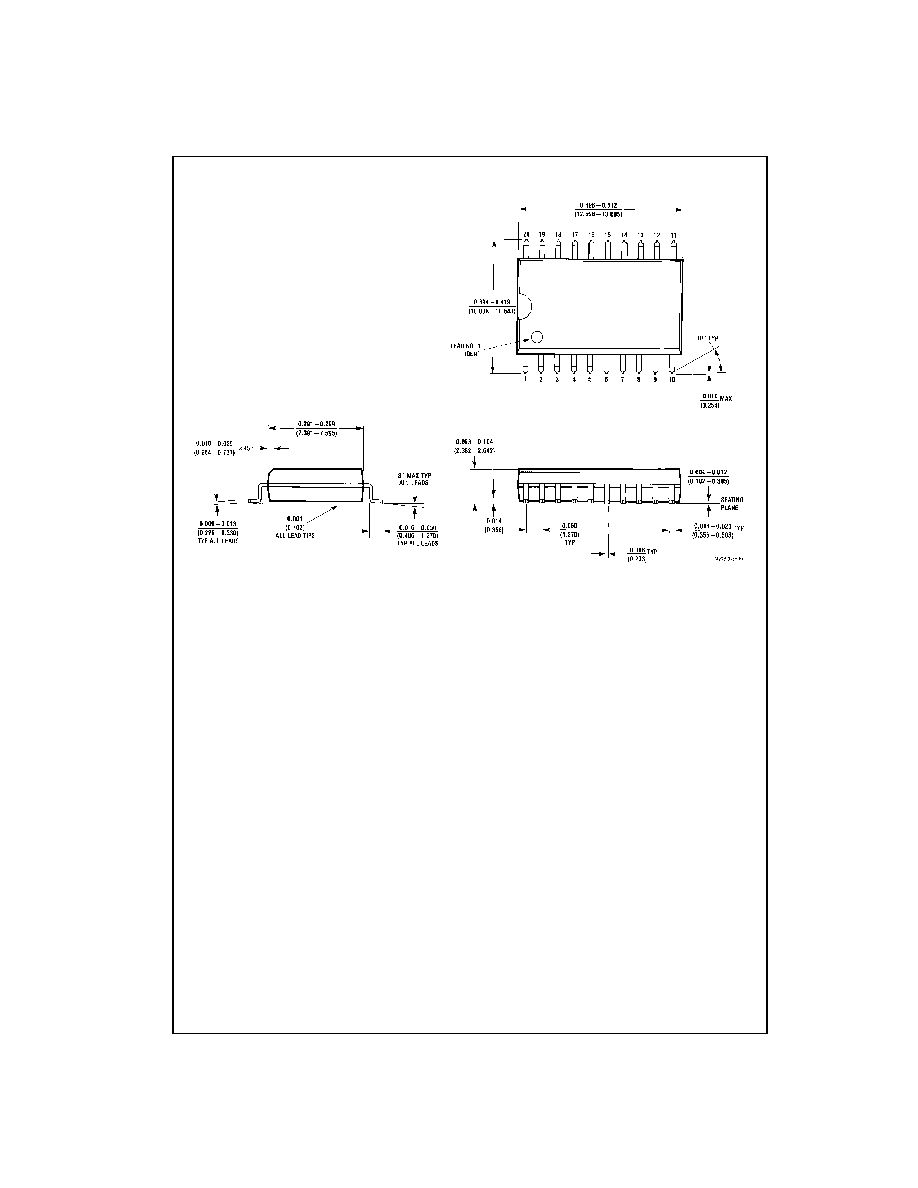

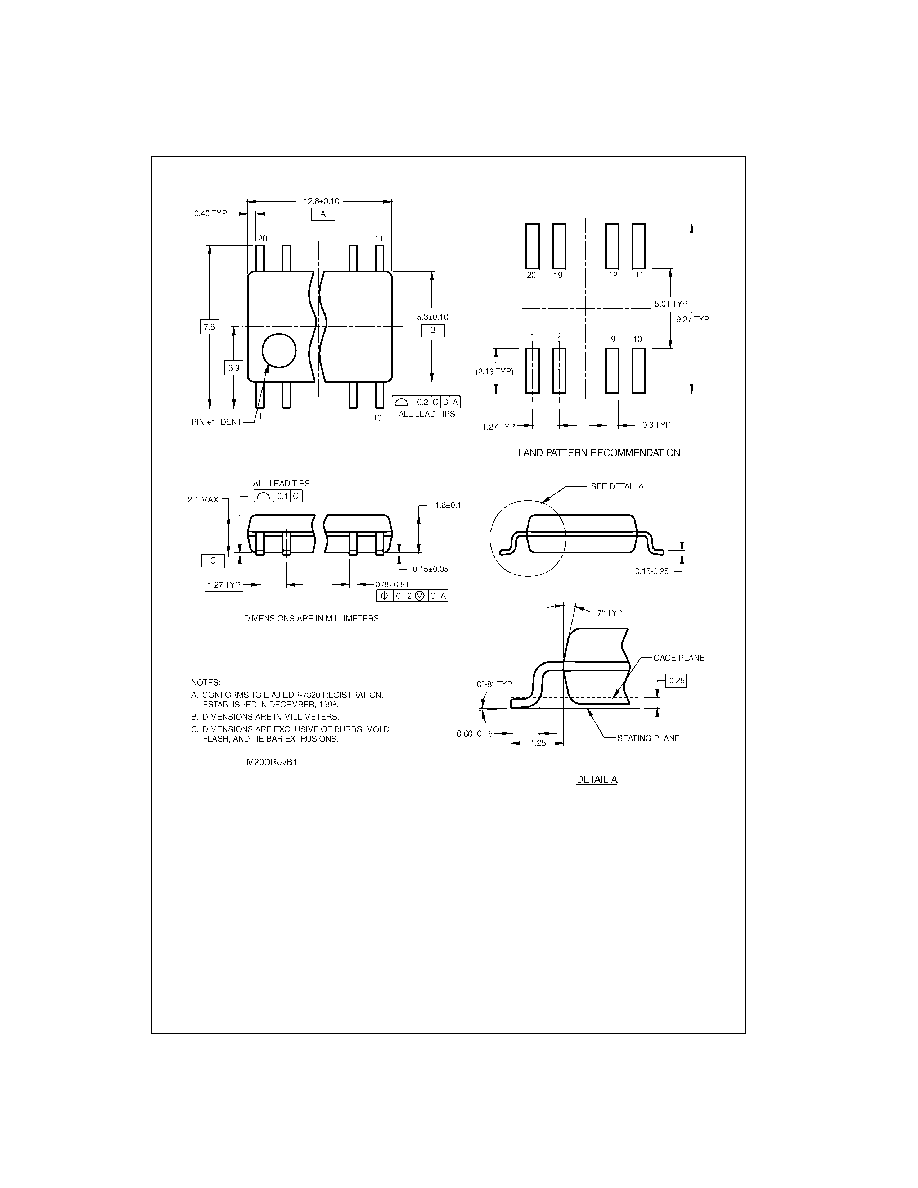

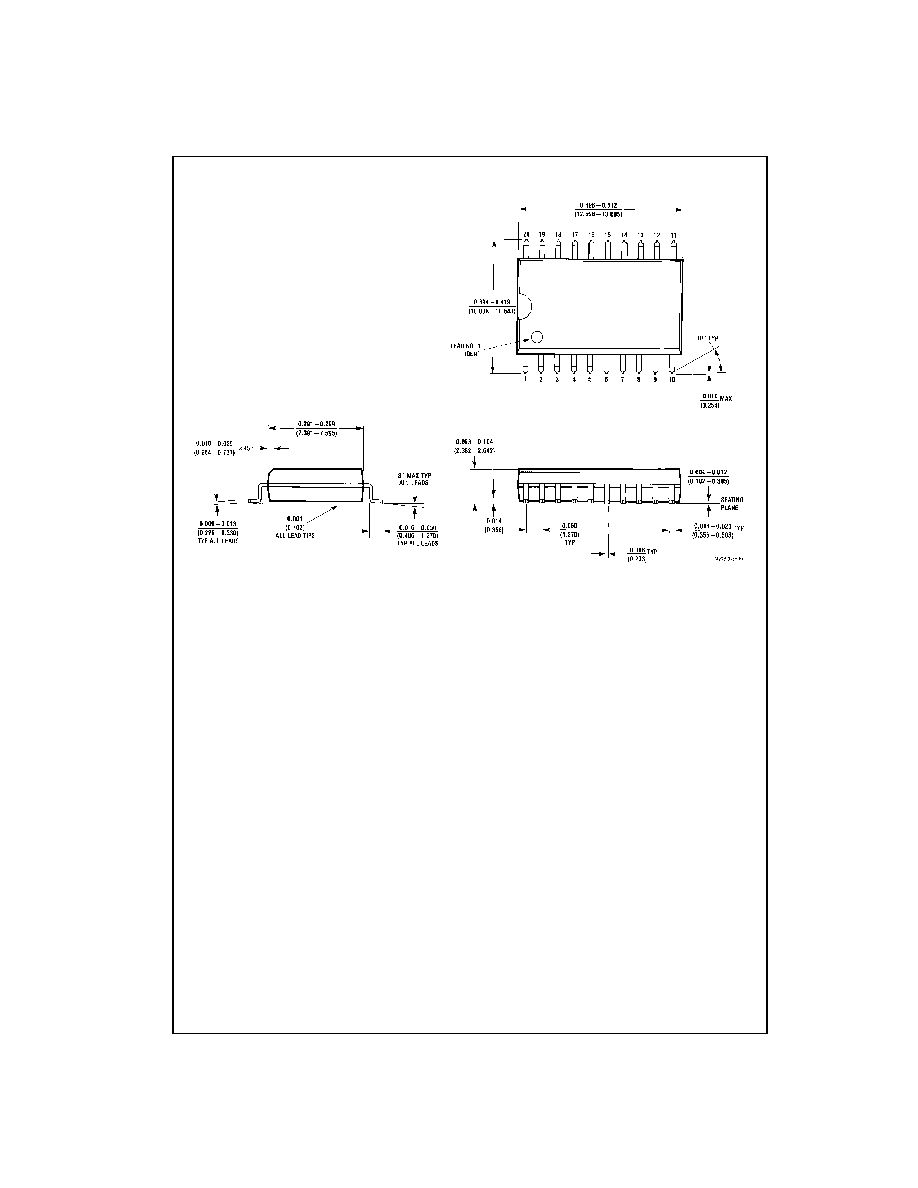

Physical Dimensions

inches (millimeters) unless otherwise noted

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

Package Number M20B

5

www.fairchildsemi.com

74

L

V

X

2

44

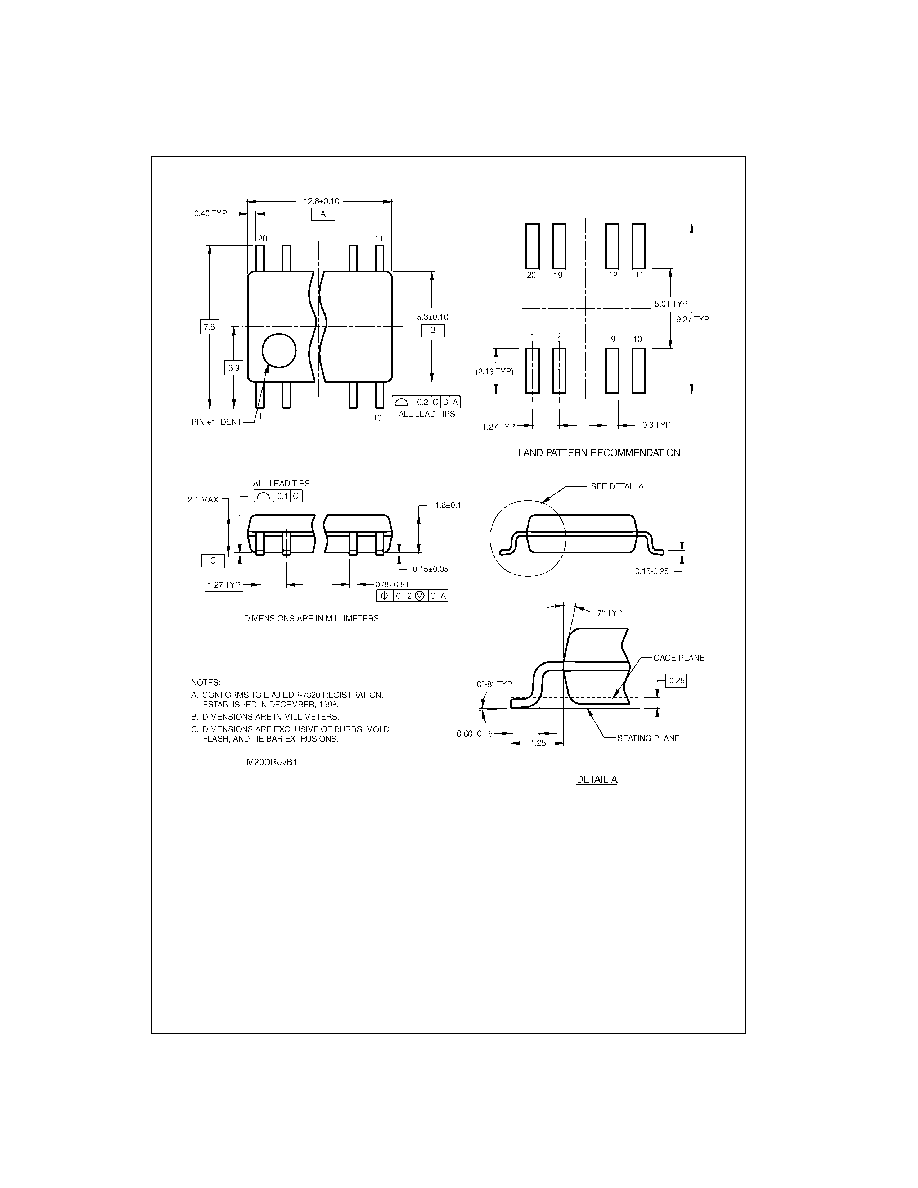

Physical Dimensions

inches (millimeters) unless otherwise noted (Continued)

Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

Package Number M20D