© 2004 Fairchild Semiconductor Corporation

DS500876

www.fairchildsemi.com

October 2003

Revised October 2004

FI

N1217 ∑

FI

N1218 ∑

FI

N1215 ∑

FI

N1216 L

V

DS 21-Bi

t Seri

al

izer

s/De-

S

eri

a

l

i

zer

s

FIN1217 ∑ FIN1218 ∑

FIN1215 ∑ FIN1216

LVDS 21-Bit Serializers/De-Serializers

General Description

The FIN1217 and FIN1215 transform 21-bit wide parallel

LVTTL (Low Voltage TTL) data into 3 serial LVDS (Low

Voltage Differential Signaling) data streams. A phase-

locked transmit clock is transmitted in parallel with the data

stream over a separate LVDS link. Every cycle of transmit

clock 21 bits of input LVTTL data are sampled and trans-

mitted.

The FIN1218 and FIN1216 receive and convert the 3 serial

LVDS data streams back into 21 bits of LVTTL data. Refer

to Table 1 for a matrix summary of the Serializers and De-

serializers available. For the FIN1217, at a transmit clock

frequency of 85 MHz, 21 bits of LVTTL data are transmitted

at a rate of 595 Mbps per LVDS channel.

These chipsets are an ideal solution to solve EMI and

cable size problems associated with wide and high-speed

TTL interfaces.

Features

s

Low power consumption

s

20 MHz to 85 MHz shift clock support

s

50% duty cycle on the clock output of receiver

s

±

1V common-mode range around 1.2V

s

Narrow bus reduces cable size and cost

s

High throughput (up to 1.785 Gbps throughput)

s

Up to 595 Mbps per channel

s

Internal PLL with no external component

s

Compatible with TIA/EIA-644 specification

s

Devices are offered in 48-lead TSSOP packages

Ordering Code:

Devices also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

Order Number

Package Number

Package Description

FIN1215MTD

MTD48

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

FIN1216MTD

MTD48

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

FIN1217MTD

MTD48

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

FIN1218MTD

MTD48

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

www.fairchildsemi.com

2

FIN12

17

∑

FIN12

18

∑

FIN121

5

∑

FIN1216

TABLE 1. Serializers/De-Serializers Chip Matrix

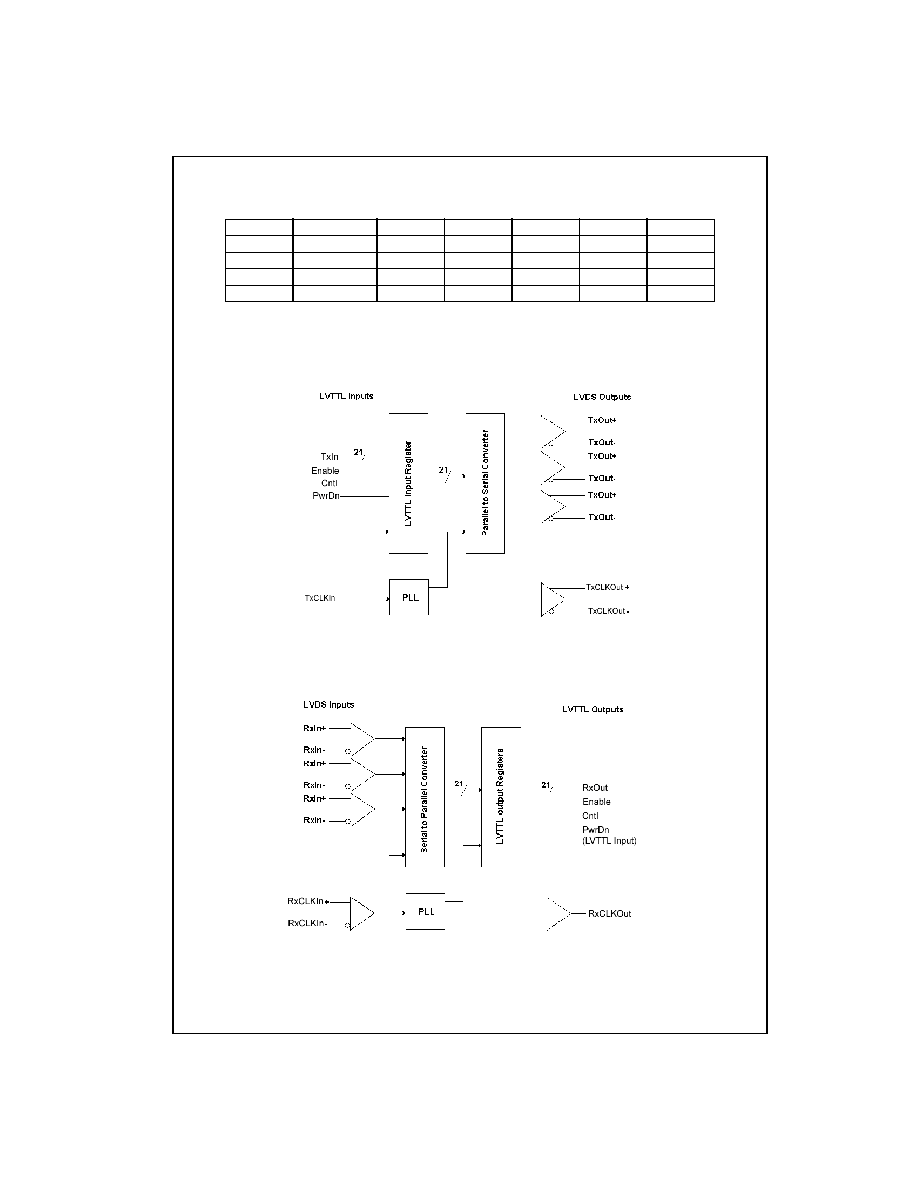

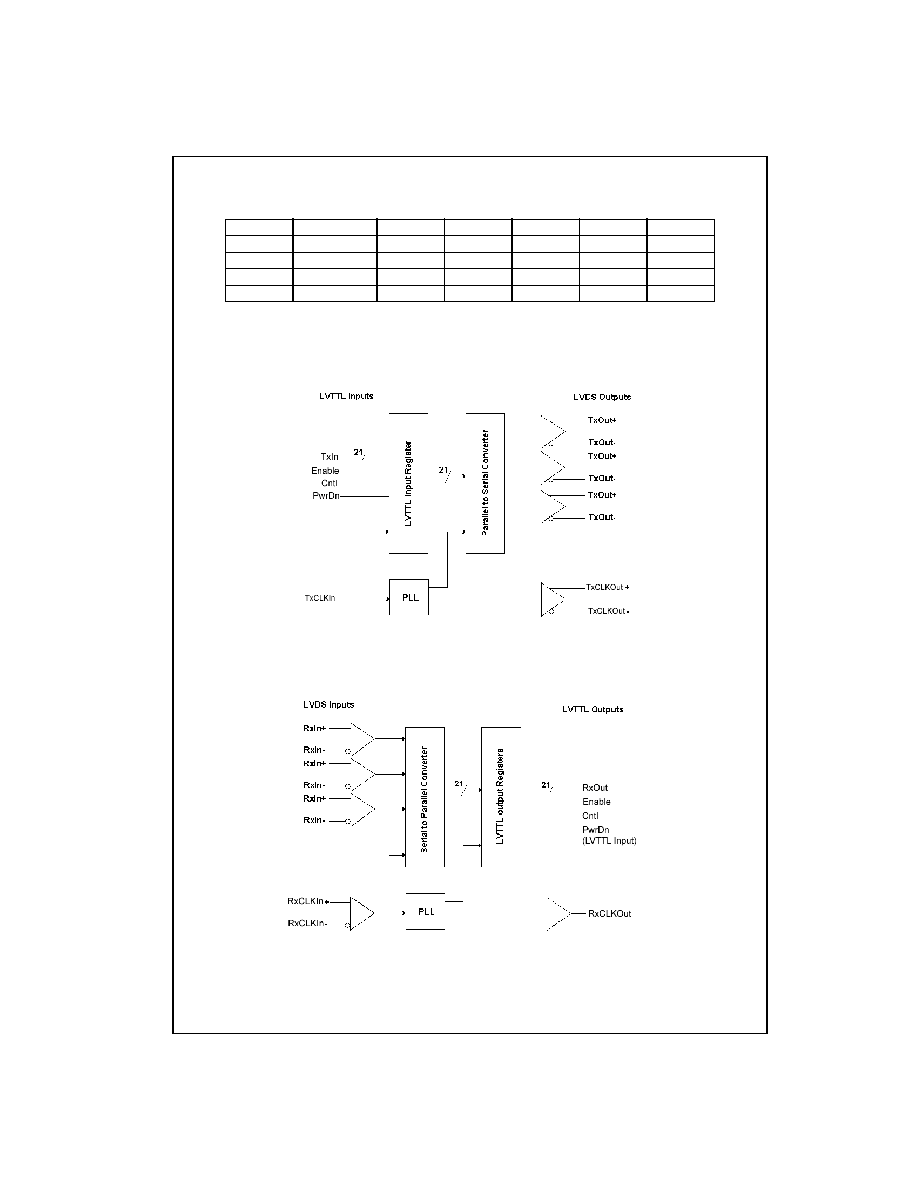

Block Diagrams

Transmitter Functional Diagram for FIN1217 and FIN1215

Receiver Functional Diagram for FIN1218 and FIN1216

Part

CLK Frequency

LVTTL IN

LVDS OUT

LVDS IN

LVTTL OUT

Package

FIN1217

85

21

3

48 TSSOP

FIN1218

85

3

21

48 TSSOP

FIN1215

66

21

3

48 TSSOP

FIN1216

66

3

21

48 TSSOP

3

www.fairchildsemi.com

FI

N1217

∑

FI

N1218

∑

FI

N1215

∑

FI

N1216

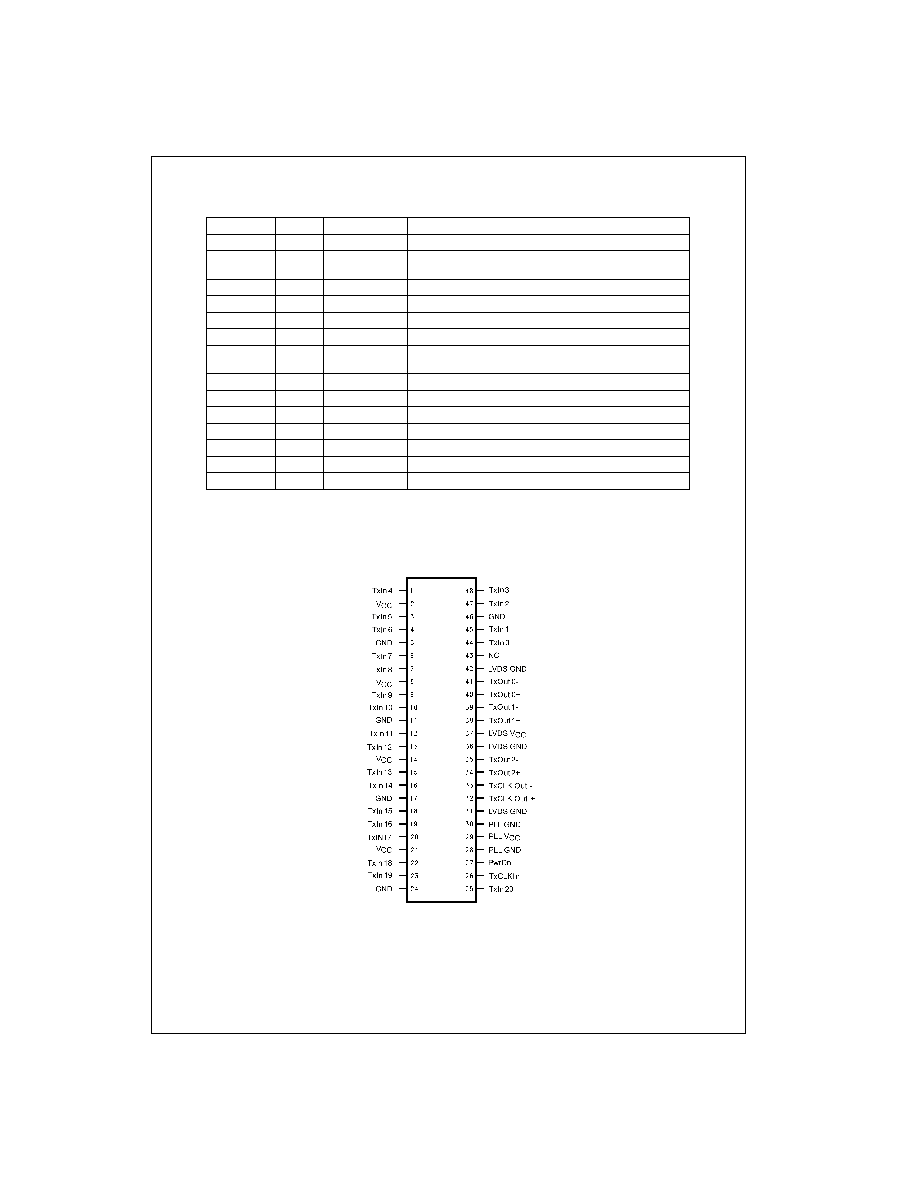

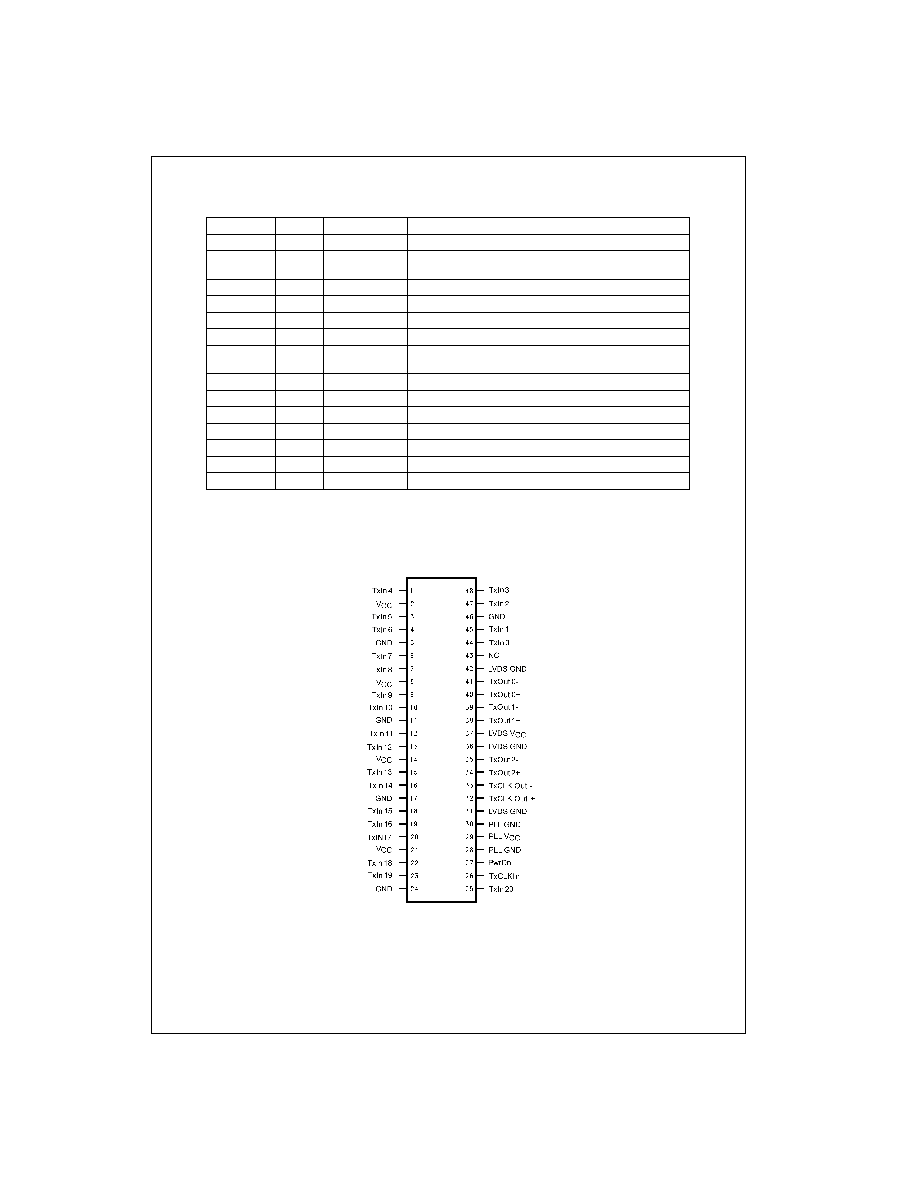

Transmitters

Pin Descriptions

Connection Diagram

FIN1217 and FIN1215 (21:3 Transmitter)

Pin Assignment for TSSOP

Pin Names

I/O Type Number of Pins

Description of Signals

TxIn

I

21

LVTTL Level Inputs

TxCLKIn

I

1

LVTTL Level Clock Input

The rising edge is for data strobe.

TxOut

+

O

3

Positive LVDS Differential Data Output

TxOut

-

O

3

Negative LVDS Differential Data Output

TxCLKOut

+

O

1

Positive LVDS Differential Clock Output

TxCLKOut

-

O

1

Negative LVDS Differential Clock Output

PwrDn

I

1

LVTTL Level Power-Down Input

Assertion (LOW) puts the outputs in high-impedance state.

PLL V

CC

I

1

Power Supply Pin for PLL

PLL GND

I

2

Ground Pins for PLL

LVDS V

CC

I

1

Power Supply Pin for LVDS Outputs

LVDS GND

I

3

Ground Pins for LVDS Outputs

V

CC

I

4

Power Supply Pins for LVTTL Inputs

GND

I

5

Ground pins for LVTTL Inputs

NC

No Connect

www.fairchildsemi.com

4

FIN12

17

∑

FIN12

18

∑

FIN121

5

∑

FIN1216

Receivers

Pin Descriptions

Connection Diagram

FIN1218 and FIN1216 (3:21 Receiver)

Pin Assignment for TSSOP

Pin Names

I/O Type

Number

of

Pins

Description of Signals

RxIn

I

3

Negative LVDS Differential Data Inputs

RxIn

+

I

3

Positive LVDS Differential Data Inputs

RxCLKIn

-

I

1

Negative LVDS Differential Clock Input

RxCLKIn

+

I

1

Positive LVDS Differential Clock Input

RxOut

O

21

LVTTL Level Data Outputs

Goes HIGH for PwrDn LOW

RxCLKOut

O

1

LVTTL Clock Output

PwrDn

I

1

LVTTL Level Input

Refer to Transmitter and Receiver Power-Up and Power-Down Operation Truth Table

PLL V

CC

I

1

Power Supply Pin for PLL

PLL GND

I

2

Ground Pins for PLL

LVDS V

CC

I

1

Power Supply Pin for LVDS Inputs

LVDS GND

I

3

Ground Pins for LVDS Inputs

V

CC

I

4

Power Supply for LVTTL Outputs

GND

I

5

Ground Pins for LVTTL Outputs

NC

No Connect

5

www.fairchildsemi.com

FI

N1217

∑

FI

N1218

∑

FI

N1215

∑

FI

N1216

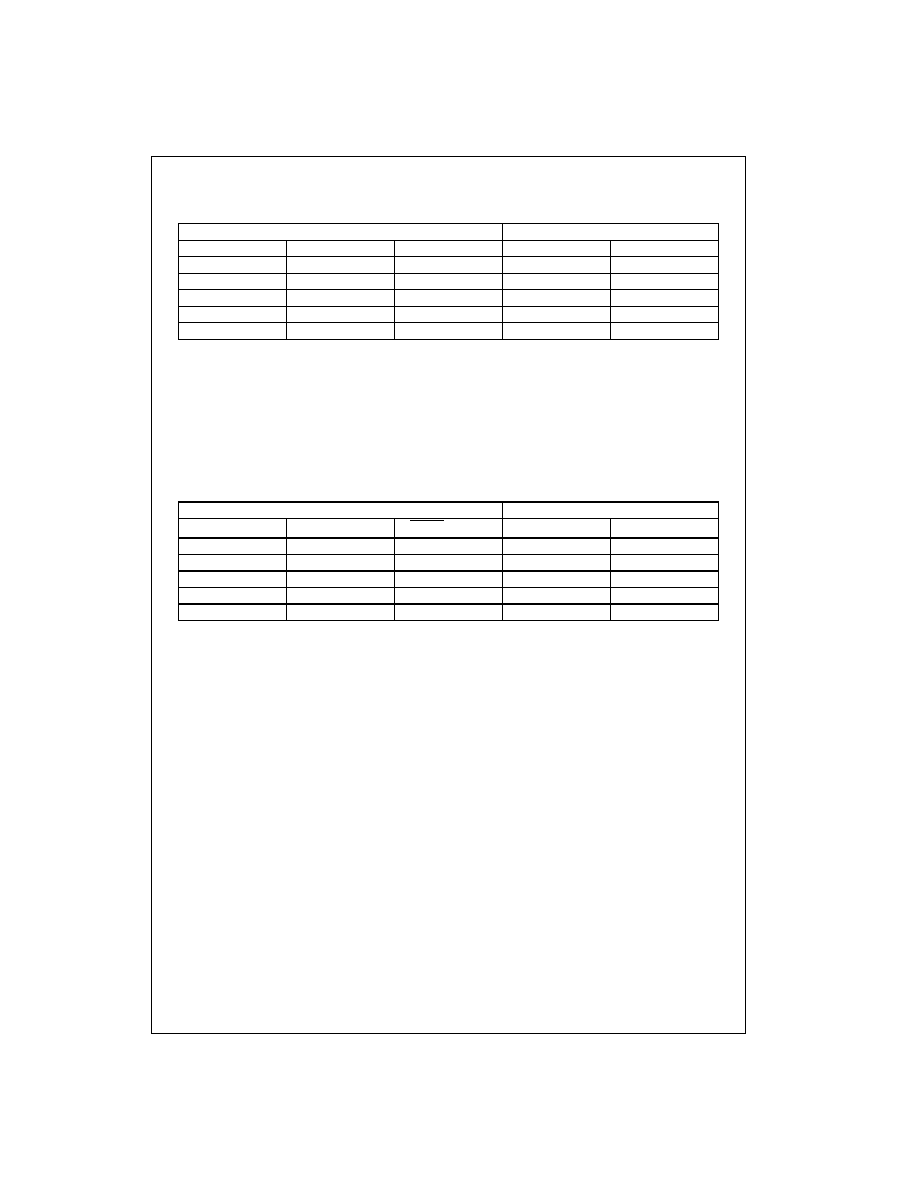

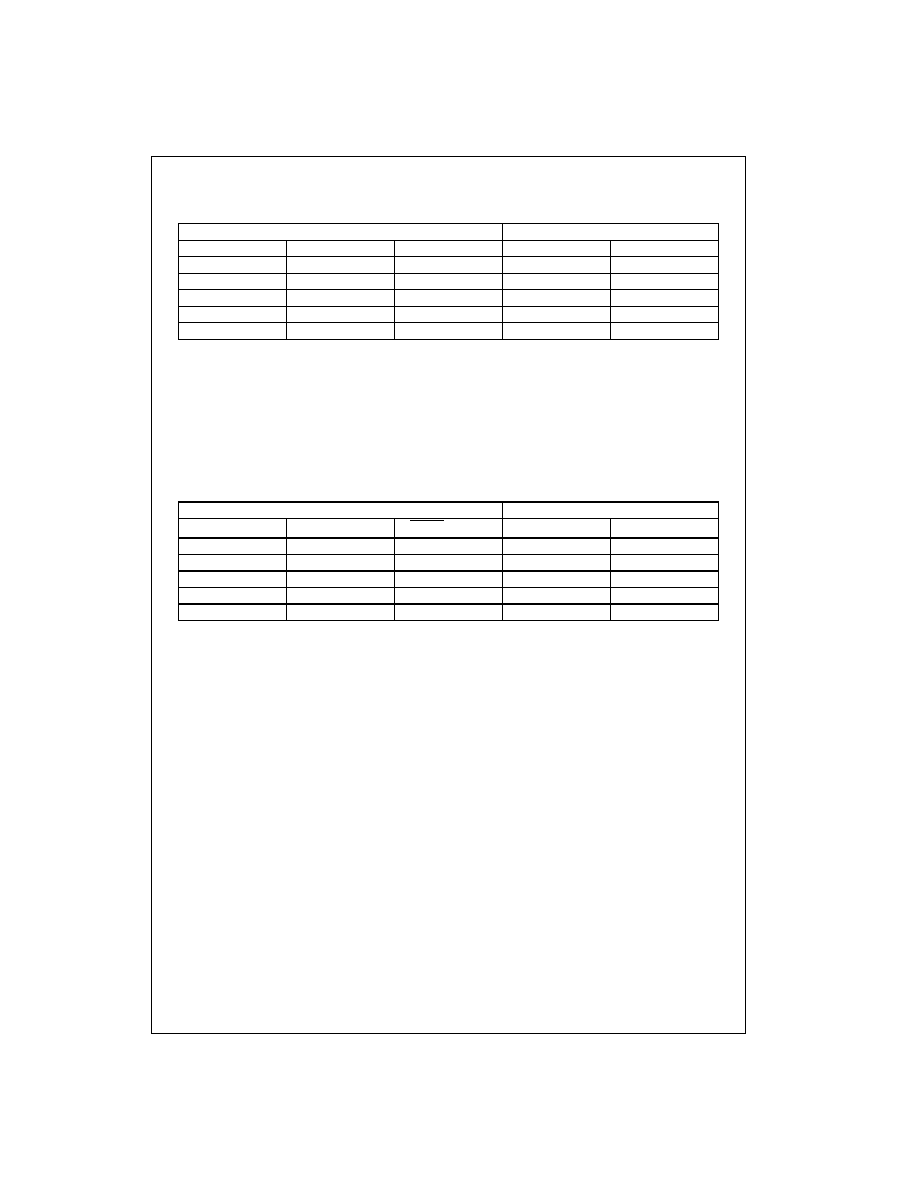

Truth Tables

Transmitter Truth Table

H

=

HIGH Logic Level

L

=

LOW Logic Level

X

=

Don't Care

Z

=

High Impedance

F

=

Floating

Note 1: The outputs of the transmitter or receiver will remain in a High Impedance state until V

CC

reaches 2V.

Note 2: TxCLKOut

±

will settle at a free running frequency when the part is powered up, PwrDn is HIGH and the TxCLKIn is a steady logic level (L/H/Z).

Receiver Truth Table

H

=

HIGH Logic Level

L

=

LOW Logic Level

P

=

Last Valid State

X

=

Don't Care

Z

=

High Impedance

F

=

Failsafe Condition

Note 3: The outputs of the transmitter or receiver will remain in a High Impedance state until V

CC

reaches 2V.

Note 4: Failsafe condition is defined as the input being terminated and un-driven (Z) or shorted or open.

Note 5: If RxCLKIn

±

is removed prior to the RxIn

±

data being removed, RxOut will be the last valid state. If RxIn

±

data is removed prior to RxCLKIn

±

being

removed, RxOut will be HIGH.

Inputs

Outputs

TxIn

TxCLKIn

PwrDn (Note 1)

TxOut

±

TxCLKOut

±

Active

Active

H

L/H

L/H

Active

L/H/Z

H

L/H

X (Note 2)

F

Active

H

L

L/H

F

F

H

L

X (Note 2)

X

X

L

Z

Z

Inputs

Outputs

RxIn

±

RxCLKIn

±

PwrDn (Note 3)

RxOut

RxCLKOut

Active

Active

H

L/H

L/H

Active

F (Note 4)

H

P

H

F (Note 4)

Active

H

H

L/H

F (Note 4)

F (Note 4)

H

P (Note 5)

H

X

X

L

L

H