1

www.fairchildsemi.com

FM25C640U Rev. B

FM25C640U 64K-Bit SPI Interface Serial CMOS EEPROM

FM25C640U

64K-Bit SPITM Interface

Serial CMOS EEPROM

Block Diagram

February 2002

© 2002 Fairchild Semiconductor Corporation

Instruction

Decoder

Control Logic

and Clock

Generators

High Voltage

Generator

and

Program

Timer

Instruction

Register

Program

Enable

Data In/Out Register

8 Bits

Data Out

Buffer

Non-Volatile

Status Register

Decoder

Address

Counter/

Register

EEPROM Array

Read/Write Amps

/CS

/HOLD

SCK

V

CC

V

SS

V

PP

/WP

SI

SO

General Description

The FM25C640U is a 64K bit serial interface CMOS EEPROM

(Electrically Erasable Programmable Read-Only Memory). This

device fully conforms to the SPI 4-wire protocol which uses Chip

Select (/CS), Clock (SCK), Data-in (SI) and Data-out (SO) pins to

synchronously control data transfer between the SPI microcontroller

and the EEPROM. In addition, the serial interface allows a minimal

pin count, packaging designed to simplify PC board layout re-

quirements and offers the designer a variety of low voltage and low

power options.

This SPI EEPROM family is designed to work with the 68HC11 or

any other SPI-compatible, high-speed microcontroller and offers

both hardware (/WP pin) and software ("block write") data protec-

tion. For example, entering a 2-bit code into the STATUS REGIS-

TER prevents programming in a selected block of memory and all

programming can be inhibited by connecting the /WP pin to V

SS

;

allowing the user to protect the entire array or a selected section.

In addition, SPI devices feature a /HOLD pin, which allows a

temporary interruption of the datastream into the EEPROM.

Fairchild EEPROMs are designed and tested for applications

requiring high endurance, high reliability, and low power con-

sumption for a continuously reliable non-volatile solution for all

markets.

Functions

I SPI MODE 0 interface

I 64K bits organized as 8K x 8

I Extended 2.7V to 5.5V operating voltage

I 2.1 MHz operation @ 4.5V - 5.5V

I Self-timed programming cycle

I "Programming complete" indicated by STATUS REGISTER

polling

I /WP pin and BLOCK WRITE protection

Features

I Sequential read of entire array

I 32 byte "Page write" mode to minimize total write time per

byte

I /WP pin and BLOCK WRITE protection to prevent inadvert-

ent programming as well as programming ENABLE and

DISABLE opcodes.

I /HOLD pin to suspend data transfer

I Typical 1µA standby current (I

SB

) for "L" devices and 0.1

µA

standby current for "LZ" devices.

I Endurance: Up to 1,000,000 data changes

I Data retention greater than 40 years

SPITM is a trademark of Motorola Corporation

2

www.fairchildsemi.com

FM25C640U Rev. B

FM25C640U 64K-Bit SPI Interface Serial CMOS EEPROM

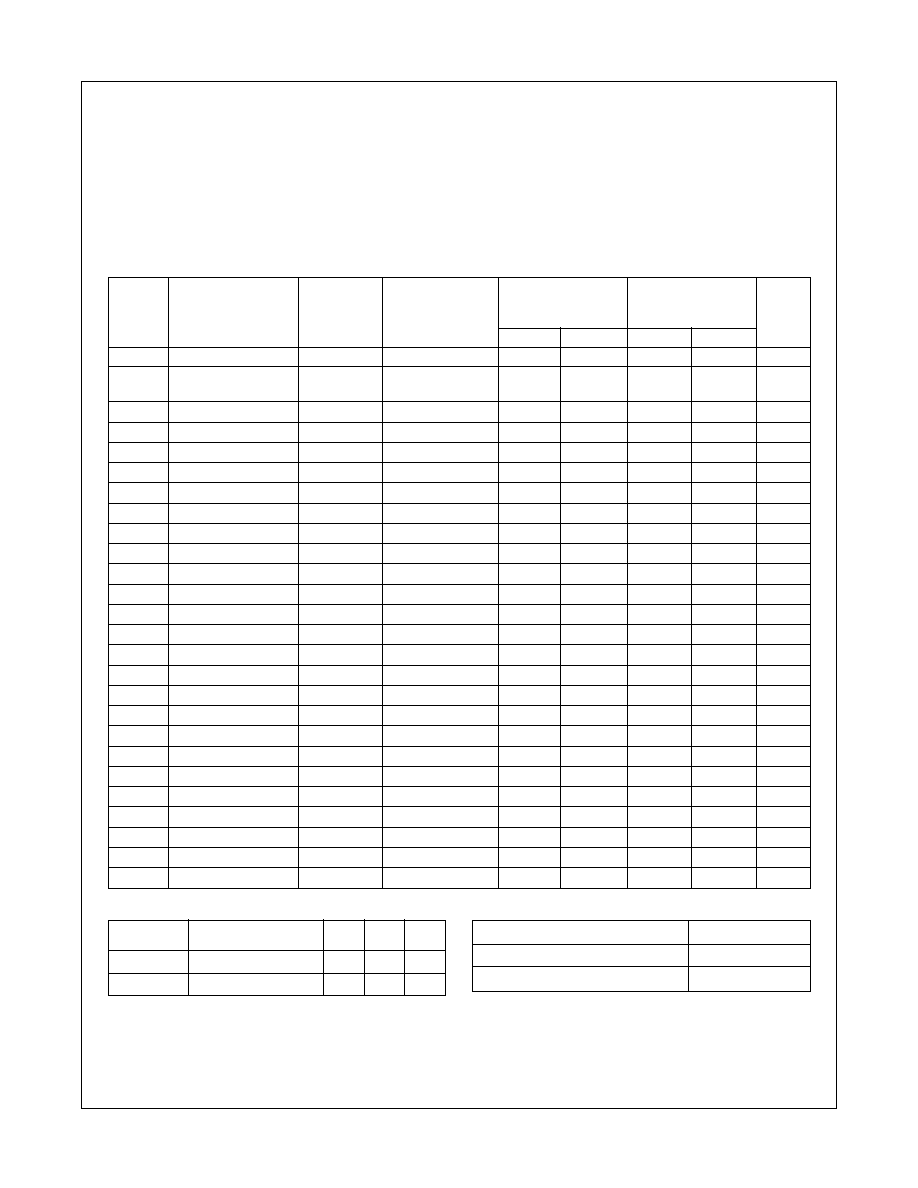

Connection Diagram

Dual-In-Line Package (N) and SO Package (M8)

Top View

See Package Number N08E (N) and M08A (M8)

Pin Names

/CS

Chip Select Input

SO

Serial Data Output

/WP

Write Protect

V

SS

Ground

SI

Serial Data Input

SCK

Serial Clock Input

/HOLD

Suspends Serial Data

V

CC

Power Supply

Ordering Information

FM

25

C

XX

U

LZ

E

XX

Letter Description

Package

N

8-pin DIP

M8

8-pin SO

Temp. Range

None

0 to 70

∞C

V

-40 to +125

∞C

E

-40 to +85

∞C

Voltage Operating Range

Blank

4.5V to 5.5V

L

2.7V to 5.5V

LZ

2.7V to 5.5V and

<1

µA Standby Current

Ultralite

CS100UL Process

Density/Mode

640

64K, mode 0

C

CMOS technology

Interface

25

SPI

FM

Fairchild Nonvolatile

Memory Prefix

/CS

SO

/WP

V

SS

V

CC

/HOLD

SCK

SI

8

7

6

5

1

2

3

4

FM25C640U

3

www.fairchildsemi.com

FM25C640U Rev. B

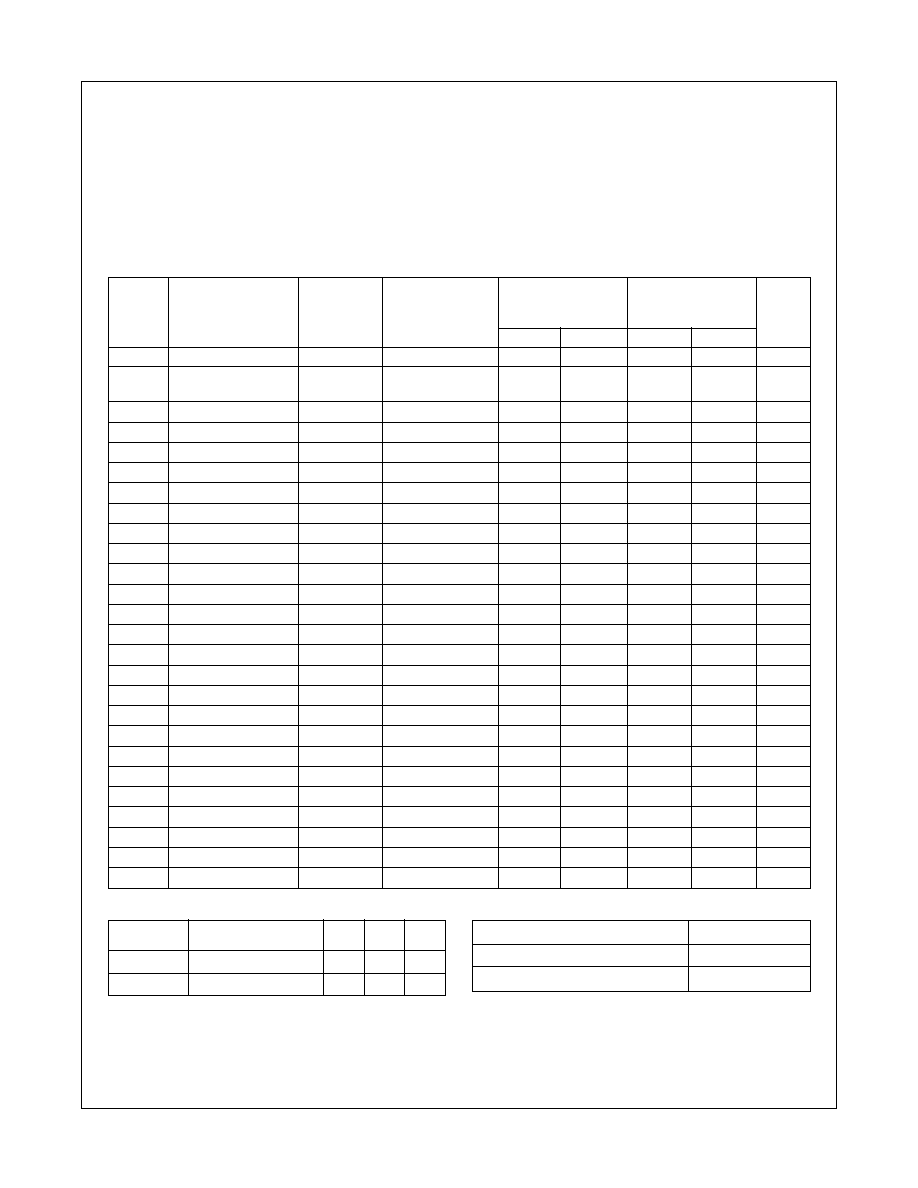

FM25C640U 64K-Bit SPI Interface Serial CMOS EEPROM

Standard Voltage 4.5

V

CC

5.5V Specifications

Absolute Maximum Ratings

(Note 1)

Ambient Storage Temperature

-65

∞C to +150∞C

All Input or Output Voltage with

Respect to Ground

+6.5V to -0.3V

Lead Temp. (Soldering, 10 sec.)

+300

∞C

ESD Rating

2000V

Operating Conditions

Ambient Operating Temperature

FM25C640U

0

∞C to +70∞C

FM25C640UE

-40

∞C to +85∞C

FM25C640UV

-40

∞C to +125∞C

Power Supply (V

CC

)

4.5V to 5.5V

DC and AC Electrical Characteristics

4.5V

V

CC

5.5V (unless otherwise specified)

Symbol

Parameter

Conditions

Min

Max

Units

I

CC

Operating Current

/CS = V

IL

3

mA

I

CCSB

Standby Current

/CS = V

CC

50

µA

I

IL

Input Leakage

V

IN

= 0 to V

CC

-1

+1

µA

I

OL

Output Leakage

V

OUT

= GND to V

CC

-1

+1

µA

V

IL

CMOS Input Low Voltage

-0.3

V

CC

* 0.3

V

V

IH

CMOS Input High Voltage

0.7 * V

CC

V

CC

+ 0.3

V

V

OL

Output Low Voltage

I

OL

= 1.6 mA

0.4

V

V

OH

Output High Voltage

I

OH

= -0.8 mA

V

CC

- 0.8

V

f

OP

SCK Frequency

2.1

MHz

t

RI

Input Rise Time

2.0

µs

t

FI

Input Fall Time

2.0

µs

t

CLH

Clock High Time

(Note 2)

190

ns

t

CLL

Clock Low Time

(Note 2)

190

ns

t

CSH

Min /CS High Time

(Note 3)

240

ns

t

CSS

/CS Setup Time

240

ns

t

DIS

Data Setup Time

100

ns

t

HDS

/HOLD Setup Time

90

ns

t

CSN

/CS Hold Time

240

ns

t

DIN

Data Hold Time

100

ns

t

HDN

/HOLD Hold Time

90

ns

t

PD

Output Delay

C

L

= 200 pF

240

ns

t

DH

Output Hold Time

0

ns

t

LZ

/HOLD to Output Low Z

100

ns

t

DF

Output Disable Time

C

L

= 200 pF

240

ns

t

HZ

/HOLD to Output High Z

100

ns

t

WP

Write Cycle Time

1≠16 Bytes

10

ms

Capacitance

T

A

= 25

∞C, f = 2.1/1 MHz (Note 4)

Symbol

Test

Typ Max Units

C

OUT

Output Capacitance

3

8

pF

C

IN

Input Capacitance

2

6

pF

AC Test Conditions

Output Load

C

L

= 200 pF

Input Pulse Levels

0.1 * V

CC

≠ 0.9 * V

CC

Timing Measurement Reference Level

0.3 * V

CC

- 0.7 * V

CC

Note 1: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the

device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Note 2: The f

OP

frequency specification specifies a minimum clock period of 1/f

OP

. Therefore, for every f

OP

clock cycle, t

CLH

+ t

CLL

must be equal to or greater than 1/f

OP

. For

example, for a f

OP

of 2.1MHz, the period equals 476ns. In this case if t C

LH

= is set to 190ns, then t

CLL

must be set to a minimum of 286ns.

Note 3: /CS must be brought high for a minimum of t

CSH

between consecutive instruction cycles.

Note 4: This parameter is periodically sampled and not 100% tested.

4

www.fairchildsemi.com

FM25C640U Rev. B

FM25C640U 64K-Bit SPI Interface Serial CMOS EEPROM

Low Voltage 2.7V

V

CC

4.5V Specifications

Absolute Maximum Ratings

(Note 5)

Ambient Storage Temperature

-65

∞C to +150∞C

All Input or Output Voltage with

Respect to Ground

+6.5V to -0.3V

Lead Temp. (Soldering, 10 sec.)

+300

∞C

ESD Rating

2000V

Operating Conditions

Ambient Operating Temperature

FM25C640UL/LZ

0

∞C to +70∞C

FM25C640ULE/LZE

-40

∞C to +85∞C

FM25C640ULV

-40

∞C to +125∞C

Power Supply (V

CC

)

2.7V≠4.5V

DC and AC Electrical Characteristics

2.7V

V

CC

4.5V (unless otherwise specified)

25C640UL/LE

25C640ULV

25C640ULZ/ZE

Symbol

Parameter

Part

Conditions

Min.

Max.

Min

Max

Units

I

CC

Operating Current

/CS = V

IL

3

3

mA

I

CCSB

Standby Current

L

/CS = V

CC

10

10

µA

LZ

1

N/A

µA

I

IL

Input Leakage

V

IN

= 0 to V

CC

-1

1

-1

1

µA

I

OL

Output Leakage

V

OUT

= GND to V

CC

-1

1

-1

1

µA

V

IL

Input Low Voltage

-0.3

V

CC

* 0.3

-0.3

V

CC

* 0.3

V

V

IH

Input High Voltage

V

CC

* 0.7

V

CC

+ 0.3

V

CC

* 0.7

V

CC

+ 0.3

V

V

OL

Output Low Voltage

I

OL

= 0.8 mA

0.4

0.4

V

V

OH

Output High Voltage

I

OH

= ≠0.8 mA

V

CC

- 0.8

V

CC

- 0.8

V

f

OP

SCK Frequency

1.0

1.0

MHz

t

RI

Input Rise Time

2.0

2.0

µs

t

FI

Input Fall Time

2.0

2.0

µs

t

CLH

Clock High Time

(Note 6)

410

410

ns

t

CLL

Clock Low Time

(Note 6)

410

410

ns

t

CSH

Min. /CS High Time

(Note 7)

500

500

ns

t

CSS

/CS Setup Time

500

500

ns

t

DIS

Data Setup Time

100

100

ns

t

HDS

/HOLD Setup Time

240

240

ns

t

CSN

/CS Hold Time

500

500

ns

t

DIN

Data Hold Time

100

100

ns

t

HDN

/HOLD Hold Time

240

240

ns

t

PD

Output Delay

C

L

= 200 pF

500

500

ns

t

DH

Output Hold Time

0

0

ns

t

LZ

/HOLD Output Low Z

240

240

ns

t

DF

Output Disable Time

C

L

= 200 pF

500

500

ns

t

HZ

/HOLD to Output Hi Z

240

240

ns

t

WP

Write Cycle Time

1-16 Bytes

15

15

ms

Capacitance

T

A

= 25

∞C, f = 2.1/1 MHz (Note 8)

Symbol

Test

Typ Max Units

C

OUT

Output Capacitance

3

8

pF

C

IN

Input Capacitance

2

6

pF

AC Test Conditions

Output Load

C

L

= 200pF

Input Pulse Levels

0.1 * V

CC

- 0.9 * V

CC

Timing Measurement Reference Level

0.3 * V

CC

- 0.7 * V

CC

Note 5: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device

at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended

periods may affect device reliability.

Note 6: The f

OP

frequency specification specifies a minimum clock period of 1/f

OP

. Therefore, for every f

OP

clock cycle, t

CLH

+ t

CLL

must be equal to or greater than 1/f

OP

. For

example, for a f

OP

of 1MHz, the period equals 1000ns. In this case if t

CLH

= is set to 410ns, then t

CLL

must be set to a minimum of 590ns.

Note 7: /CS must be brought high for a minimum of t

CSH

between consecutive instruction cycles.

Note 8: This parameter is periodically sampled and not 100% tested.

5

www.fairchildsemi.com

FM25C640U Rev. B

FM25C640U 64K-Bit SPI Interface Serial CMOS EEPROM

FIGURE 1. Synchronous Data Timing Diagram

tCSS

tCLH

tCLL

tCSH

tDF

tPD

tDIS

tDIH

tDH

tCSI

SCK

SI

SO

/CS

Valid Input

Valid Output

High Z

Mode 3

Mode 3

Mode 0

Mode 0

SCK

CS

SO

/HOLD

Output (n+1)

Output (n)

Output (n)

Output (n+2)

tHDS

tHZ

tLZ

tHDH

tHDS tHDH

tDIS

High Z

SI

Input (n+1)

Input (n)

Input (n)

Input (n+2)

Don't Care

Low state ( /CS = 0)

Don't Care

FIGURE 3. HOLD Timing

FIGURE 2. SPI Protocol

SCK

SI

SO

/CS

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Don't Care

High Z

Mode 3

Mode 3