©2002 Fairchild Semiconductor Corporation

FQA18N50

V2

QFET

TM

Rev. B, August 2002

FQA18N50V2

500V N-Channel MOSFET

General Description

These N-Channel enhancement mode power field effect

transistors are produced using Fairchild's proprietary,

planar stripe, DMOS technology.

This advanced technology has been especially tailored to

minimize on-state resistance, provide superior switching

performance, and withstand high energy pulse in the

avalanche and commutation mode. These devices are well

suited for high efficient switched mode power supplies,

active power factor correction, electronic lamp ballast

based on half bridge topology.

Features

∑ 20A, 500V, R

DS(on)

= 0.265

@V

GS

= 10 V

∑ Low gate charge ( typical 42 nC)

∑ Low Crss ( typical 11 pF)

∑ Fast switching

∑ 100% avalanche tested

∑ Improved dv/dt capability

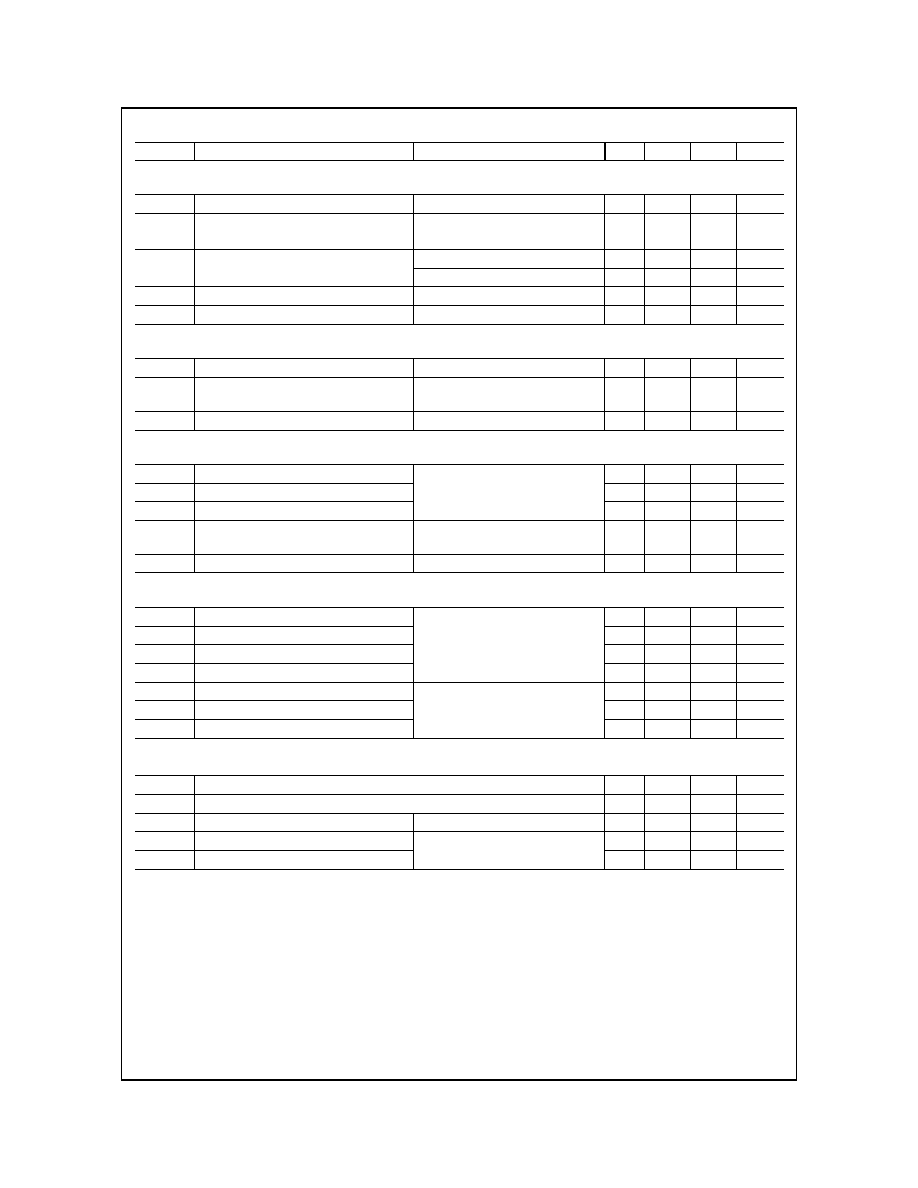

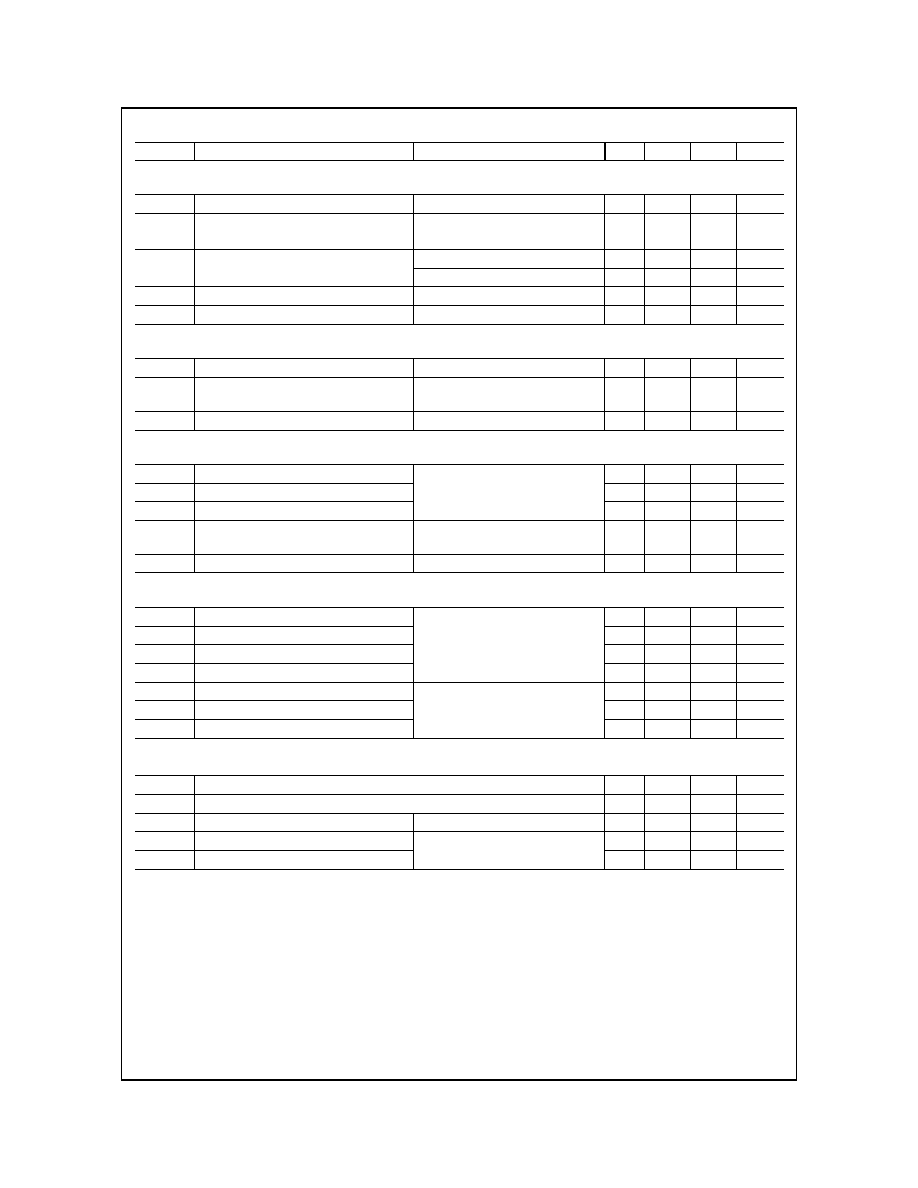

Absolute Maximum Ratings

T

C

= 25∞C unless otherwise noted

Thermal Characteristics

Symbol

Parameter

FQA18N50V2

Units

V

DSS

Drain-Source Voltage

500

V

I

D

Drain Current

- Continuous (T

C

= 25∞C)

20

A

- Continuous (T

C

= 100∞C)

12.7

A

I

DM

Drain Current

- Pulsed

(Note 1)

80

A

V

GSS

Gate-Source Voltage

±

30

V

E

AS

Single Pulsed Avalanche Energy

(Note 2)

330

mJ

I

AR

Avalanche Current

(Note 1)

20

A

E

AR

Repetitive Avalanche Energy

(Note 1)

27.7

mJ

dv/dt

Peak Diode Recovery dv/dt

(Note 3)

4.5

V/ns

P

D

Power Dissipation (T

C

= 25∞C)

277

W

- Derate above 25∞C

2.22

W/∞C

T

J

, T

STG

Operating and Storage Temperature Range

-55 to +150

∞C

T

L

Maximum lead temperature for soldering purposes,

1/8

"

from case for 5 seconds

300

∞C

Symbol

Parameter

Typ

Max

Units

R

JC

Thermal Resistance, Junction-to-Case

--

0.45

∞C

/

W

R

CS

Thermal Resistance, Case-to-Sink

0.24

--

∞C

/

W

R

JA

Thermal Resistance, Junction-to-Ambient

--

40

∞C

/

W

! "

!

!

!

"

"

"

! "

!

!

!

"

"

"

S

D

G

TO-3P

FQA Series

G

S

D

Rev. B, August 2002

FQA18N50

V2

©2002 Fairchild Semiconductor Corporation

Electrical Characteristics

T

C

= 25∞C unless otherwise noted

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature

2. L = 1.83mH, I

AS

= 18A, V

DD

= 50V, R

G

= 25

,

Starting T

J

= 25∞C

3. I

SD

18A, di/dt

200A/

µ

s, V

DD

BV

DSS,

Starting T

J

= 25∞C

4. Pulse Test : Pulse width

300

µ

s, Duty cycle

2%

5. Essentially independent of operating temperature

Symbol

Parameter

Test Conditions

Min

Typ

Max

Units

Off Characteristics

BV

DSS

Drain-Source Breakdown Voltage

V

GS

= 0 V, I

D

= 250

µ

A

500

--

--

V

BV

DSS

/

T

J

Breakdown Voltage Temperature

Coefficient

I

D

= 250

µ

A, Referenced to 25∞C

--

0.5

--

V/∞C

I

DSS

Zero Gate Voltage Drain Current

V

DS

= 500 V, V

GS

= 0 V

--

--

1

µ

A

V

DS

= 400 V, T

C

= 125∞C

--

--

10

µ

A

I

GSSF

Gate-Body Leakage Current, Forward

V

GS

= 30 V, V

DS

= 0 V

--

--

100

nA

I

GSSR

Gate-Body Leakage Current, Reverse

V

GS

= -30 V, V

DS

= 0 V

--

--

-100

nA

On Characteristics

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250

µ

A

3.0

--

5.0

V

R

DS(on)

Static Drain-Source

On-Resistance

V

GS

= 10 V, I

D

= 10 A

--

0.225

0.265

g

FS

Forward Transconductance

V

DS

= 40 V, I

D

= 10 A

(Note 4)

--

16

--

S

Dynamic Characteristics

C

iss

Input Capacitance

V

DS

= 25 V, V

GS

= 0 V,

f = 1.0 MHz

--

2530

3290

pF

C

oss

Output Capacitance

--

300

390

pF

C

rss

Reverse Transfer Capacitance

--

11

14.3

pF

C

oss

Output Capacitance

V

DS

= 400 V, V

GS

= 0 V,

f = 1.0 MHz

--

76

--

pF

C

oss

eff.

Effective Output Capacitance

V

DS

= 0V to 400 V, V

GS

= 0 V

--

150

--

pF

Switching Characteristics

t

d(on)

Turn-On Delay Time

V

DD

= 250 V, I

D

= 18 A,

R

G

= 25

--

40

90

ns

t

r

Turn-On Rise Time

--

150

310

ns

t

d(off)

Turn-Off Delay Time

--

95

200

ns

t

f

Turn-Off Fall Time

--

110

230

ns

Q

g

Total Gate Charge

V

DS

= 400 V, I

D

= 18 A,

V

GS

= 10 V

--

42

55

nC

Q

gs

Gate-Source Charge

--

12

--

nC

Q

gd

Gate-Drain Charge

--

14

--

nC

Drain-Source Diode Characteristics and Maximum Ratings

I

S

Maximum Continuous Drain-Source Diode Forward Current

--

--

20

A

I

SM

Maximum Pulsed Drain-Source Diode Forward Current

--

--

80

A

V

SD

Drain-Source Diode Forward Voltage

V

GS

= 0 V, I

S

= 20 A

--

--

1.4

V

t

rr

Reverse Recovery Time

V

GS

= 0 V, I

S

= 18 A,

dI

F

/ dt = 100 A/

µ

s

--

420

--

ns

Q

rr

Reverse Recovery Charge

--

5.4

--

µ

C

(Note 4, 5)

(Note 4)

(Note 4, 5)

©2002 Fairchild Semiconductor Corporation

FQA18N50

V2

Rev. B, August 2002

Typical Characteristics

10

-1

10

0

10

1

10

-1

10

0

10

1

V

GS

Top : 15.0 V

10.0 V

8.0 V

7.0 V

6.5 V

6.0 V

Bottom : 5.5 V

Notes :

1. 250

s Pulse Test

2. T

C

= 25

I

D

, D

r

ai

n

C

u

rrent

[A

]

V

DS

, Drain-Source Voltage [V]

0

5

10

15

20

25

30

35

40

45

0

2

4

6

8

10

12

V

DS

= 250V

V

DS

= 100V

V

DS

= 400V

Note : I

D

= 18A

V

GS

,

G

a

t

e

-

S

our

ce V

o

l

t

age [

V

]

Q

G

, Total Gate Charge [nC]

10

-1

10

0

10

1

0

1000

2000

3000

4000

5000

6000

7000

C

iss

= C

gs

+ C

gd

(C

ds

= shorted)

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

Notes :

1. V

GS

= 0 V

2. f = 1 MHz

C

rss

C

oss

C

iss

C

a

p

a

c

i

ta

nc

e [p

F

]

V

DS

, Drain-Source Voltage [V]

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

10

-1

10

0

10

1

25

150

Notes :

1. V

GS

= 0V

2. 250

s Pulse Test

I

DR

,

R

e

ve

r

s

e D

r

ai

n

C

u

r

r

e

nt

[

A

]

V

SD

, Source-Drain Voltage [V]

0

10

20

30

40

50

60

70

0.0

0.2

0.4

0.6

0.8

1.0

V

GS

= 20V

V

GS

= 10V

Note : T

J

= 25

R

DS

(

O

N)

[

],

D

r

ai

n-

S

o

ur

c

e

On-

R

es

i

s

t

a

nc

e

I

D

, Drain Current [A]

Figure 5. Capacitance Characteristics

Figure 6. Gate Charge Characteristics

Figure 3. On-Resistance Variation vs.

Drain Current and Gate Voltage

Figure 4. Body Diode Forward Voltage

Variation vs. Source Current

and Temperature

Figure 2. Transfer Characteristics

Figure 1. On-Region Characteristics

2

4

6

8

10

10

-1

10

0

10

1

Notes :

1. V

DS

= 40V

2. 250

s Pulse Test

-55

150

25

I

D

, D

r

a

i

n

C

u

r

r

e

n

t

[A

]

V

GS

, Gate-Source Voltage [V]

©2002 Fairchild Semiconductor Corporation

FQA18N50

V2

Rev. B, August 2002

25

50

75

100

125

150

0

5

10

15

20

I

D

,

D

r

ain

C

u

r

r

en

t

[

A

]

T

C

, Case Temperature [

]

1 0

-5

1 0

-4

1 0

-3

1 0

-2

1 0

-1

1 0

0

1 0

1

1 0

-2

1 0

-1

1 0

0

N o t e s :

1 . Z

J C

( t ) = 0 .4 5

/W M a x .

2 . D u t y F a c to r , D = t

1

/t

2

3 . T

J M

- T

C

= P

D M

* Z

J C

( t )

s in g le p u ls e

D = 0 .5

0 .0 2

0 .2

0 .0 5

0 .1

0 .0 1

Z

JC

(t

),

T

h

e

r

m

a

l

R

e

s

p

o

n

s

e

t

1

, S q u a r e W a v e P u ls e D u r a tio n [s e c ]

Typical Characteristics

(Continued)

10

0

10

1

10

2

10

3

10

-1

10

0

10

1

10

2

DC

10 ms

1 ms

100 us

Operation in This Area

is Limited by R

DS(on)

Notes :

1. T

C

= 25

o

C

2. T

J

= 150

o

C

3. Single Pulse

I

D

,

D

r

ai

n C

u

r

r

ent

[

A

]

V

DS

, Drain-Source Voltage [V]

Figure 11. Transient Thermal Response Curve

t

1

P

DM

t

2

-100

-50

0

50

100

150

200

0.0

0.5

1.0

1.5

2.0

2.5

3.0

Notes :

1. V

GS

= 10 V

2. I

D

= 10 A

R

DS

(

O

N)

, (

N

or

m

a

l

i

zed)

D

r

ai

n-

S

our

ce O

n

-

R

es

istance

T

J

, Junction Temperature [

o

C]

-100

-50

0

50

100

150

200

0.8

0.9

1.0

1.1

1.2

Notes :

1. V

GS

= 0 V

2. I

D

= 250

A

BV

DS

S

,

(Norm

a

l

i

zed)

D

r

ai

n-

Source Breakdown V

o

l

t

age

T

J

, Junction Temperature [

o

C]

Figure 9

.

.

.

.

Maximum Safe Operating Area

Figure 7. Breakdown Voltage Variation

vs. Temperature

Figure 8. On-Resistance Variation

vs. Temperature

Figure 10. Maximum Drain Current

vs. Case Temperature

©2002 Fairchild Semiconductor Corporation

FQA18N50

V2

Rev. B, August 2002

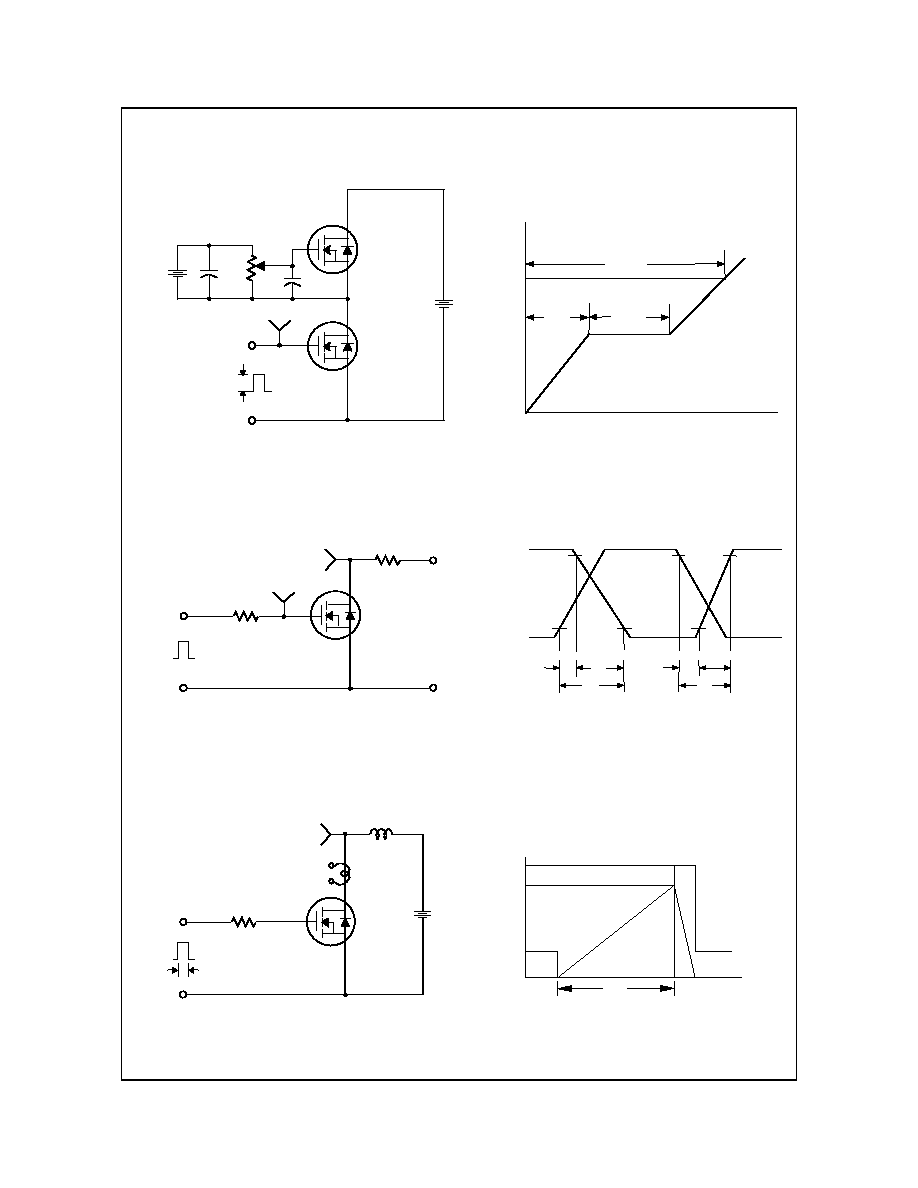

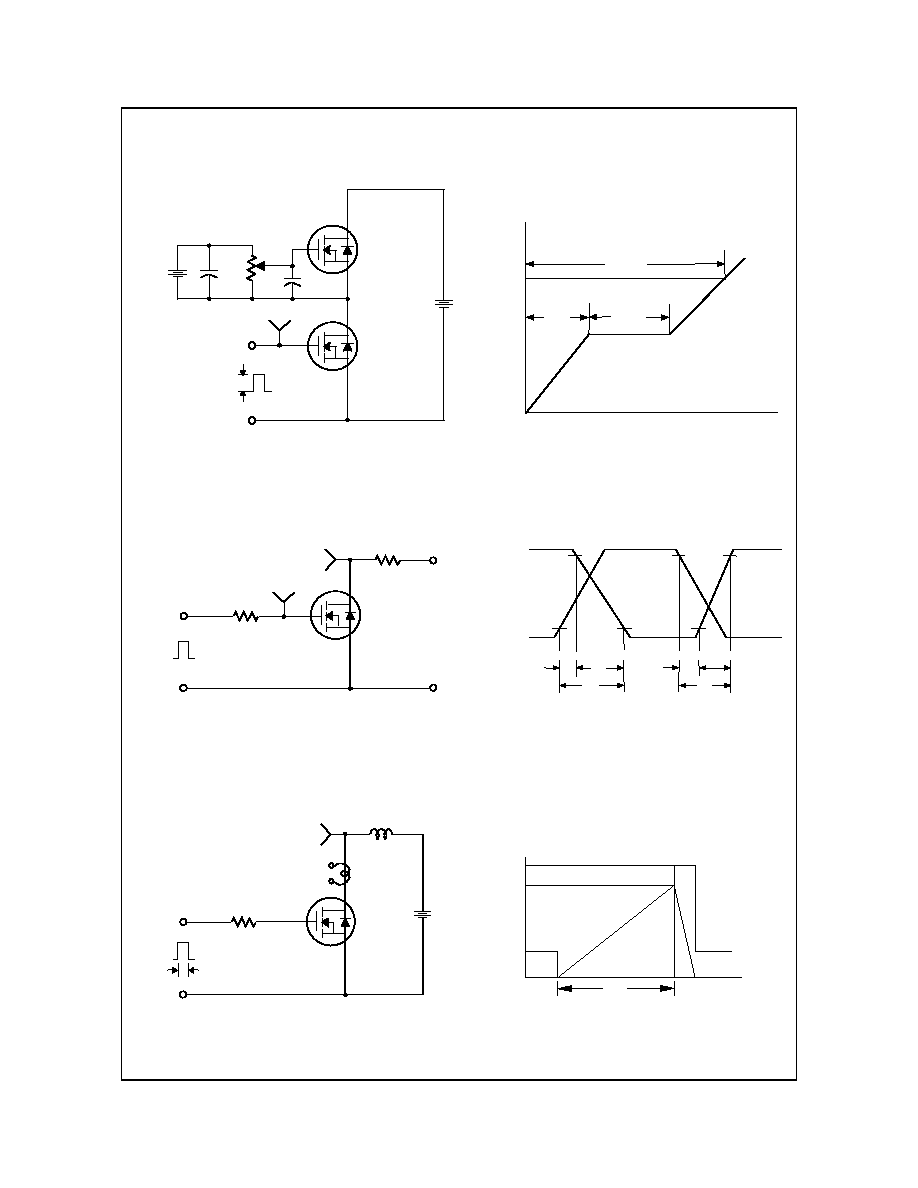

Gate Charge Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms

Charge

V

GS

10V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K

200nF

12V

Same Type

as DUT

Charge

V

GS

10V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K

200nF

12V

Same Type

as DUT

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

10V

V

DS

R

L

DUT

R

G

V

GS

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

10V

V

DS

R

L

DUT

R

G

V

GS

E

AS

=

L I

AS

2

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V

DUT

R

G

L

I

D

t

p

E

AS

=

L I

AS

2

----

2

1

E

AS

=

L I

AS

2

----

2

1

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V

DUT

R

G

L

L

I

D

I

D

t

p