| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: FQP17N08L | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©2000 Fairchild Semiconductor International

December 2000

Rev. A2, December 2000

FQP

17N08L

QFET

QFET

QFET

QFET

TM

FQP17N08L

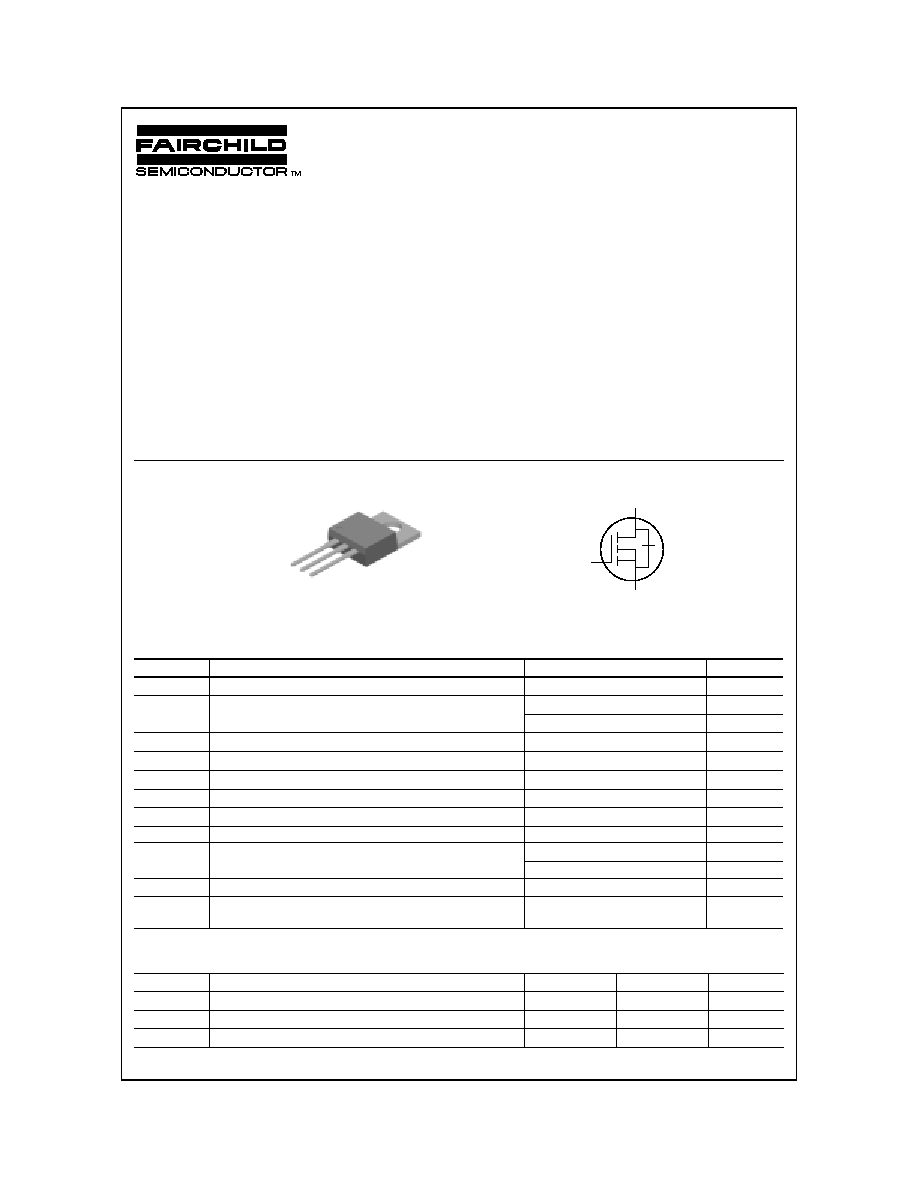

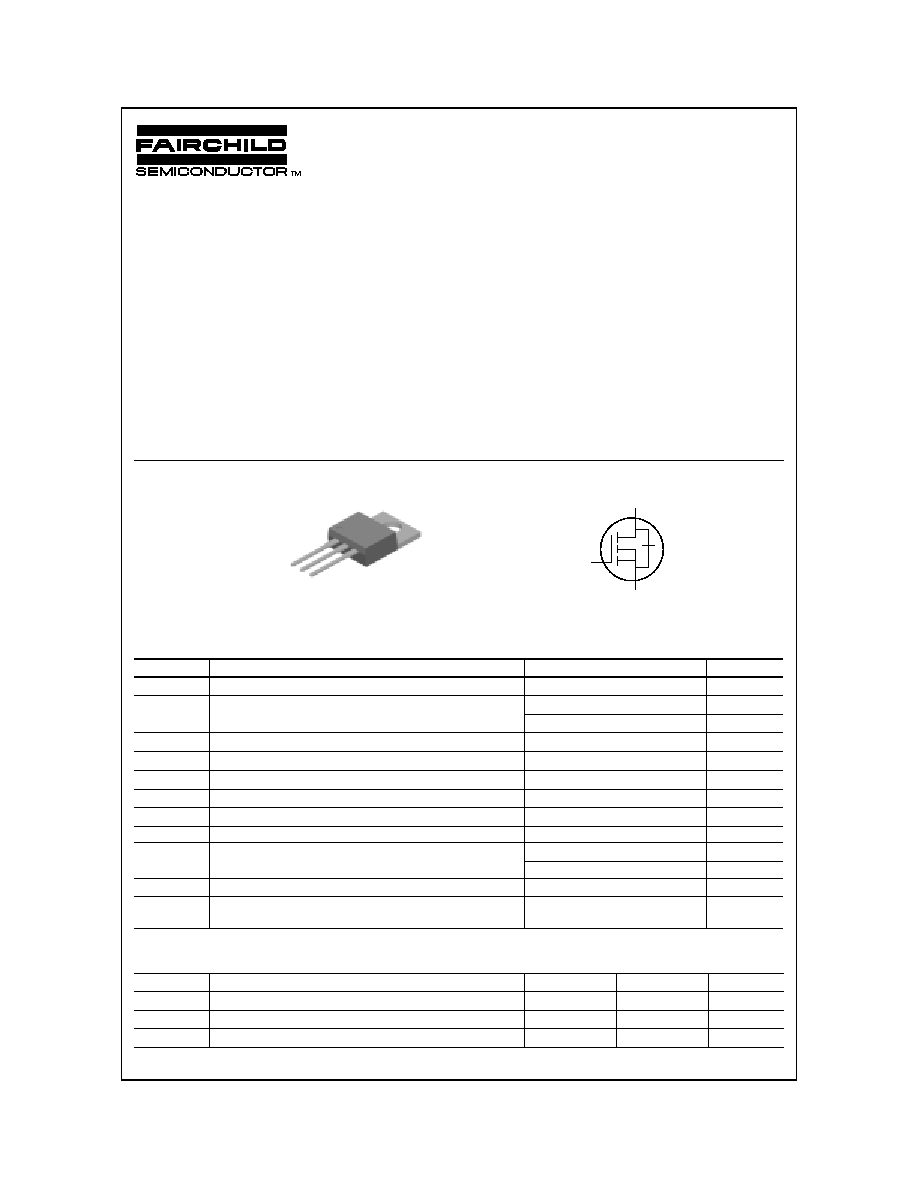

80V LOGIC N-Channel MOSFET

General Description

These N-Channel enhancement mode power field effect

transistors are produced using Fairchild's proprietary,

planar stripe, DMOS technology.

This advanced technology is especially tailored to minimize

on-state resistance, provide superior switching

performance, and withstand a high energy pulse in the

avalanche and commutation modes. These devices are

well suited for low voltage applications such as automotive,

high efficiency switching for DC/DC converters, and DC

motor control.

Features

∑ 16.5A, 80V, R

DS(on)

= 0.1

@V

GS

= 10 V

∑ Low gate charge ( typical 8.8 nC)

∑ Low Crss ( typical 29 pF)

∑ Fast switching

∑ 100% avalanche tested

∑ Improved dv/dt capability

∑ 175

∞

C maximum junction temperature rating

∑ Low level gate drive requirements allowing

direct operation from logic drives

Absolute Maximum Ratings

T

C

= 25∞C unless otherwise noted

Thermal Characteristics

Symbol

Parameter

FQP17N08L

Units

V

DSS

Drain-Source Voltage

80

V

I

D

Drain Current

- Continuous (T

C

= 25∞C)

16.5

A

- Continuous (T

C

= 100∞C)

11.6

A

I

DM

Drain Current

- Pulsed

(Note 1)

66

A

V

GSS

Gate-Source Voltage

±

20

V

E

AS

Single Pulsed Avalanche Energy

(Note 2)

100

mJ

I

AR

Avalanche Current

(Note 1)

16.5

A

E

AR

Repetitive Avalanche Energy

(Note 1)

6.5

mJ

dv/dt

Peak Diode Recovery dv/dt

(Note 3)

6.5

V/ns

P

D

Power Dissipation (T

C

= 25∞C)

65

W

- Derate above 25∞C

0.43

W/∞C

T

J

, T

STG

Operating and Storage Temperature Range

-55 to +175

∞C

T

L

Maximum lead temperature for soldering purposes,

1/8

"

from case for 5 seconds

300

∞C

Symbol

Parameter

Typ

Max

Units

R

JC

Thermal Resistance, Junction-to-Case

--

2.31

∞C

/

W

R

CS

Thermal Resistance, Case-to-Sink

0.5

--

∞C

/

W

R

JA

Thermal Resistance, Junction-to-Ambient

--

62.5

∞C

/

W

! "

!

!

!

"

"

"

! "

!

!

!

"

"

"

S

D

G

TO-220

FQP Series

G

S

D

Rev. A2, December 2000

FQP

17N08L

(Note 4)

(Note 4, 5)

(Note 4, 5)

(Note 4)

©2000 Fairchild Semiconductor International

Electrical Characteristics

T

C

= 25∞C unless otherwise noted

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature

2. L = 0.5mH, I

AS

= 16.5A, V

DD

= 25V, R

G

= 25

,

Starting T

J

= 25∞C

3. I

SD

16.5A, di/dt

300A/

µ

s, V

DD

BV

DSS,

Starting T

J

= 25∞C

4. Pulse Test : Pulse width

300

µ

s, Duty cycle

2%

5. Essentially independent of operating temperature

Symbol

Parameter

Test Conditions

Min

Typ

Max

Units

Off Characteristics

BV

DSS

Drain-Source Breakdown Voltage

V

GS

= 0 V, I

D

= 250

µ

A

80

--

--

V

BV

DSS

/

T

J

Breakdown Voltage Temperature

Coefficient

I

D

= 250

µ

A, Referenced to 25∞C

--

0.08

--

V/∞C

I

DSS

Zero Gate Voltage Drain Current

V

DS

= 80 V, V

GS

= 0 V

--

--

1

µ

A

V

DS

= 64 V, T

C

= 150∞C

--

--

10

µ

A

I

GSSF

Gate-Body Leakage Current, Forward

V

GS

= 20 V, V

DS

= 0 V

--

--

100

nA

I

GSSR

Gate-Body Leakage Current, Reverse

V

GS

= -20 V, V

DS

= 0 V

--

--

-100

nA

On Characteristics

V

GS(th)

Gate Threshold Voltage

V

DS

= V

GS

, I

D

= 250

µ

A

1.0

--

2.0

V

R

DS(on)

Static Drain-Source

On-Resistance

V

GS

= 10 V, I

D

= 8.25 A

V

GS

= 5 V, I

D

= 8.25 A

--

0.076

0.090

0.100

0.115

g

FS

Forward Transconductance

V

DS

= 25 V, I

D

= 8.25 A

--

12.4

--

S

Dynamic Characteristics

C

iss

Input Capacitance

V

DS

= 25 V, V

GS

= 0 V,

f = 1.0 MHz

--

400

520

pF

C

oss

Output Capacitance

--

120

155

pF

C

rss

Reverse Transfer Capacitance

--

29

37

pF

Switching Characteristics

t

d(on)

Turn-On Delay Time

V

DD

= 40 V, I

D

= 16.5 A,

R

G

= 25

--

7

25

ns

t

r

Turn-On Rise Time

--

290

590

ns

t

d(off)

Turn-Off Delay Time

--

20

50

ns

t

f

Turn-Off Fall Time

--

75

160

ns

Q

g

Total Gate Charge

V

DS

= 64 V, I

D

= 16.5 A,

V

GS

= 5 V

--

8.8

11.5

nC

Q

gs

Gate-Source Charge

--

2.0

--

nC

Q

gd

Gate-Drain Charge

--

5.4

--

nC

Drain-Source Diode Characteristics and Maximum Ratings

I

S

Maximum Continuous Drain-Source Diode Forward Current

--

--

16.5

A

I

SM

Maximum Pulsed Drain-Source Diode Forward Current

--

--

66

A

V

SD

Drain-Source Diode Forward Voltage

V

GS

= 0 V, I

S

= 16.5 A

--

--

1.5

V

t

rr

Reverse Recovery Time

V

GS

= 0 V, I

S

= 16.5 A,

dI

F

/ dt = 100 A/

µ

s

--

55

--

ns

Q

rr

Reverse Recovery Charge

--

85

--

nC

FQP

17N08L

Rev. A2, December 2000

©2000 Fairchild Semiconductor International

0

2

4

6

8

10

12

14

16

0

2

4

6

8

10

12

V

DS

= 40V

V

DS

= 64V

Note : I

D

= 16.5A

V

GS

,

G

a

t

e

-

S

our

c

e

V

o

l

t

ag

e [

V

]

Q

G

, Total Gate Charge [nC]

10

-1

10

0

10

1

0

100

200

300

400

500

600

700

800

900

1000

1100

C

iss

= C

gs

+ C

gd

(C

ds

= shorted)

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

Notes :

1. V

GS

= 0 V

2. f = 1 MHz

C

rss

C

oss

C

iss

C

apa

ci

t

anc

e [

p

F]

V

DS

, Drain-Source Voltage [V]

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

10

-1

10

0

10

1

25

175

Notes :

1. V

GS

= 0V

2. 250

s Pulse Test

I

DR

, R

e

v

e

r

s

e

D

r

a

i

n

C

u

rr

e

n

t [A

]

V

SD

, Source-Drain Voltage [V]

0

10

20

30

40

50

0.0

0.1

0.2

0.3

0.4

Note : T

J

= 25

V

GS

= 10V

V

GS

= 5V

R

D

S

(

on)

[

],

D

r

ai

n

-

S

o

u

r

ce

O

n

-

R

esi

s

t

a

nce

I

D

, Drain Current [A]

0

2

4

6

8

10

10

-1

10

0

10

1

Notes :

1. V

DS

= 25V

2. 250

s Pulse Test

-55

175

25

I

D

, D

r

a

i

n

C

u

r

r

e

n

t [A

]

V

GS

, Gate-Source Voltage [V]

10

-1

10

0

10

1

10

0

10

1

V

GS

Top : 10.0 V

8.0 V

6.0 V

5.0 V

4.5 V

4.0 V

3.5 V

Bottom : 3.0 V

Notes :

1. 250

s Pulse Test

2. T

C

= 25

I

D

,

D

r

ai

n

C

u

r

r

e

nt

[

A

]

V

DS

, Drain-Source Voltage [V]

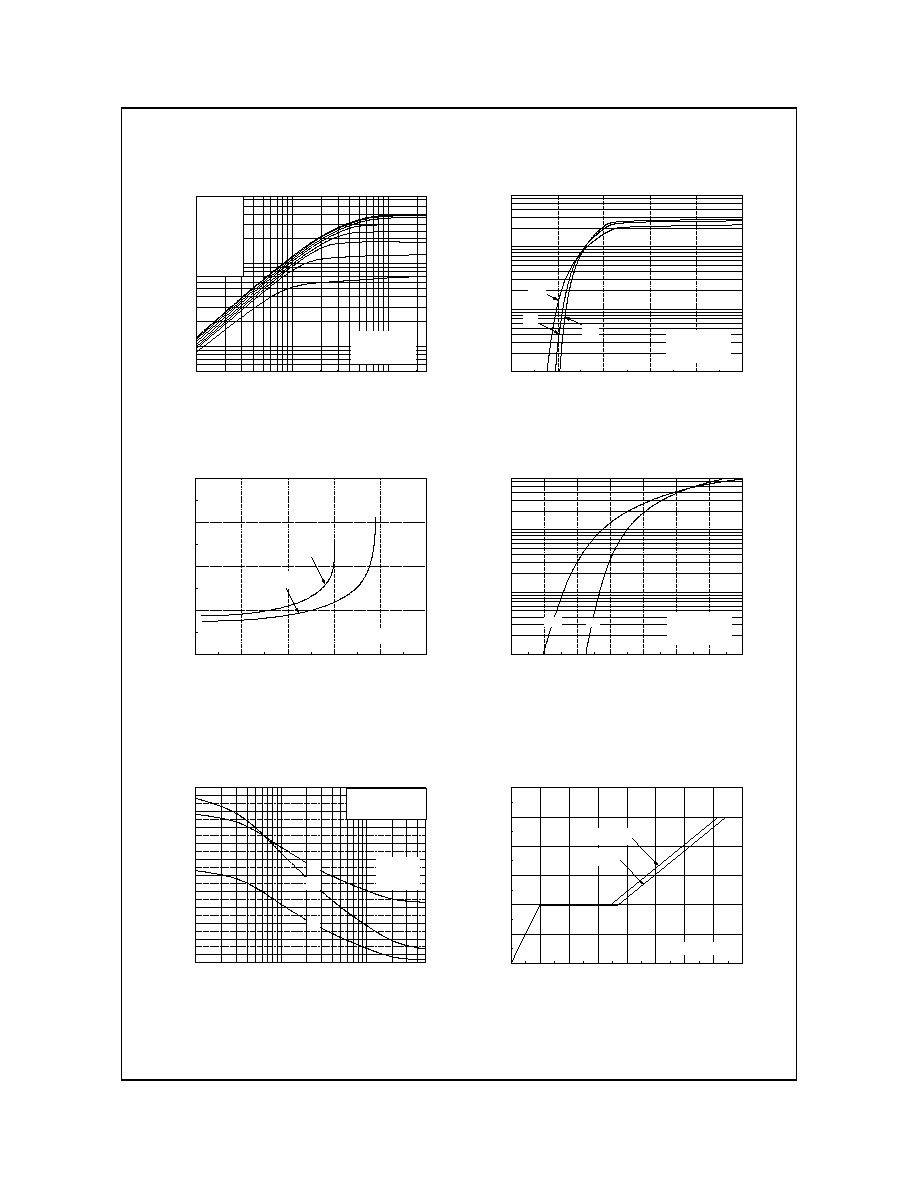

Typical Characteristics

Figure 5. Capacitance Characteristics

Figure 6. Gate Charge Characteristics

Figure 3. On-Resistance Variation vs.

Drain Current and Gate Voltage

Figure 4. Body Diode Forward Voltage

Variation vs. Source Current

and Temperature

Figure 2. Transfer Characteristics

Figure 1. On-Region Characteristics

©2000 Fairchild Semiconductor International

FQP

17N08L

Rev. A2, December 2000

1 0

-5

1 0

-4

1 0

-3

1 0

-2

1 0

-1

1 0

0

1 0

1

1 0

-2

1 0

-1

1 0

0

N o te s :

1 . Z

J C

( t) = 2 .3 1

/W M a x .

2 . D u ty F a c to r , D = t

1

/t

2

3 . T

J M

- T

C

= P

D M

* Z

J C

( t)

s in g le p u ls e

D = 0 .5

0 .0 2

0 .2

0 .0 5

0 .1

0 .0 1

Z

JC

(

t

)

,

T

h

er

m

a

l

R

e

s

p

onse

t

1

, S q u a r e W a v e P u ls e D u r a t io n [ s e c ]

25

50

75

100

125

150

175

0

3

6

9

12

15

18

I

D

,

D

r

ai

n

C

u

r

r

e

nt

[

A

]

T

C

, Case Temperature [

]

10

0

10

1

10

2

10

-1

10

0

10

1

10

2

DC

10 ms

1 ms

100

µ

s

Operation in This Area

is Limited by R

DS(on)

Notes :

1. T

C

= 25

o

C

2. T

J

= 175

o

C

3. Single Pulse

I

D

,

D

r

ai

n C

u

r

r

en

t

[

A

]

V

DS

, Drain-Source Voltage [V]

-100

-50

0

50

100

150

200

0.0

0.5

1.0

1.5

2.0

2.5

3.0

Notes :

1. V

GS

= 10 V

2. I

D

= 8.25 A

R

DS

(

O

N)

,

(

N

or

m

a

l

i

z

e

d)

D

r

ai

n-

S

o

ur

c

e

O

n

-

R

es

i

s

t

a

nc

e

T

J

, Junction Temperature [

o

C]

-100

-50

0

50

100

150

200

0.8

0.9

1.0

1.1

1.2

Notes :

1. V

GS

= 0 V

2. I

D

= 250

A

BV

DSS

, (

N

o

r

m

a

liz

e

d

)

D

r

ai

n-

S

o

u

r

ce B

r

eak

d

o

w

n

V

o

l

t

age

T

J

, Junction Temperature [

o

C]

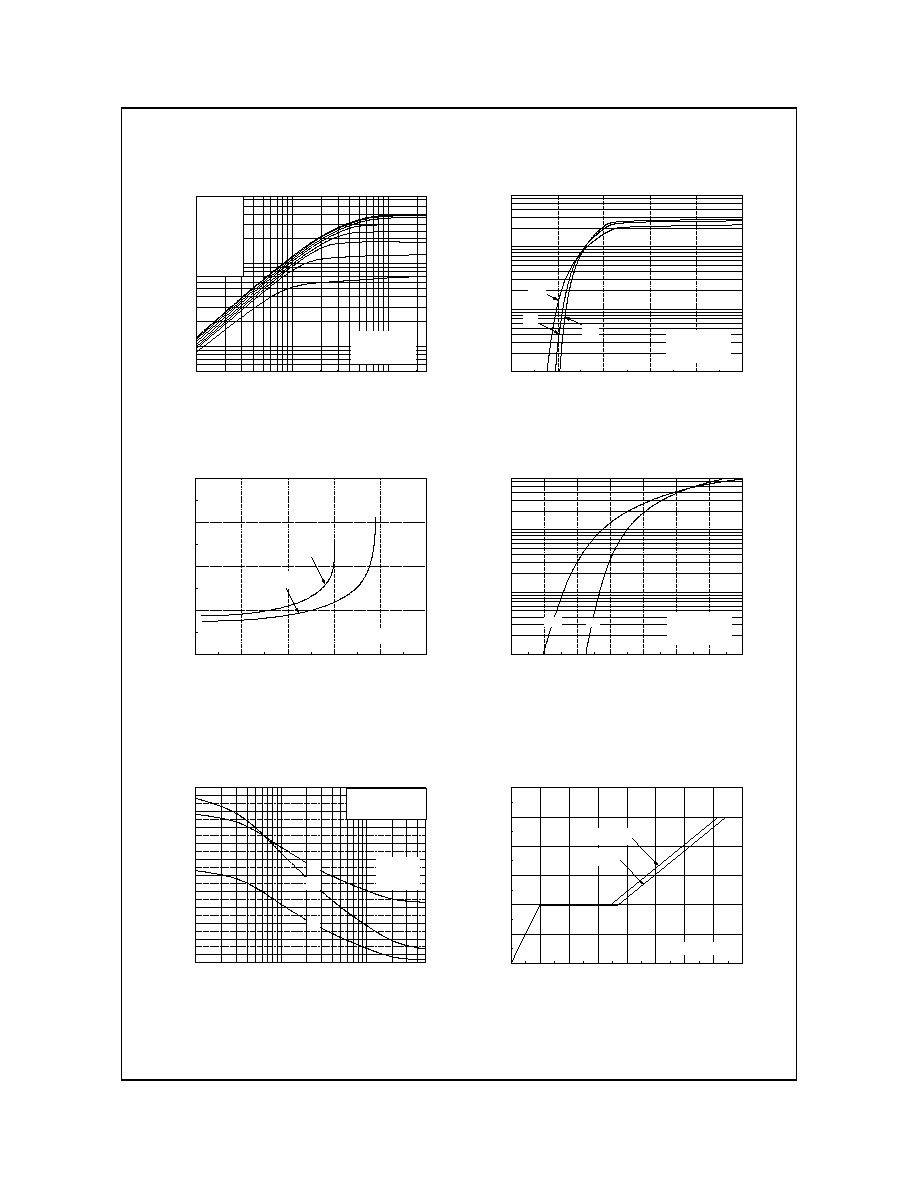

Typical Characteristics

(Continued)

Figure 9. Maximum Safe Operating Area

Figure 10. Maximum Drain Current

vs. Case Temperature

Figure 7. Breakdown Voltage Variation

vs. Temperature

Figure 8. On-Resistance Variation

vs. Temperature

Figure 11. Transient Thermal Response Curve

t

1

P

DM

t

2

FQP

17N08L

Rev. A2, December 2000

©2000 Fairchild Semiconductor International

Charge

V

GS

5V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K

200nF

12V

Same Type

as DUT

Charge

V

GS

5V

Q

g

Q

gs

Q

gd

3mA

V

GS

DUT

V

DS

300nF

50K

200nF

12V

Same Type

as DUT

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

5V

V

DS

R

L

DUT

R

G

V

GS

V

GS

V

DS

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

V

DD

5V

V

DS

R

L

DUT

R

G

V

GS

E

AS

=

L I

AS

2

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V

DUT

R

G

L

I

D

t

p

E

AS

=

L I

AS

2

----

2

1

E

AS

=

L I

AS

2

----

2

1

----

2

1

--------------------

BV

DSS

- V

DD

BV

DSS

V

DD

V

DS

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

10V

DUT

R

G

L

L

I

D

I

D

t

p

Gate Charge Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms