| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: FSDH321L | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©2005 Fairchild Semiconductor Corporation

www.fairchildsemi.com

Rev.1.0.5

FPS

TM

is a trademark of Fairchild Semiconductor Corporation.

Features

∑ Internal Avalanche Rugged Sense FET

∑ Consumes only 0.65W at 240VAC & 0.3W load with

Advanced Burst-Mode Operation

∑ Frequency Modulation for EMI Reduction

∑ Precision Fixed Operating Frequency

∑ Internal Start-up Circuit

∑ Pulse-by-Pulse Current Limiting

∑ Abnormal Over Current Protection (AOCP)

∑ Over Voltage Protection (OVP)

∑ Over Load Protection (OLP)

∑ Internal Thermal Shutdown Function (TSD)

∑ Auto-Restart Mode

∑ Under Voltage Lockout (UVLO)

∑ Low Operating Current (max 3mA)

∑ Adjustable Peak Current Limit

∑ Built-in Soft Start

Applications

∑ SMPS for STB, Low cost DVD Player

∑ Auxiliary Power for PC

∑ Adapter & Charger

Related Application Notes

∑ AN-4137, 4141, 4147(Flyback) / AN-4134(Forward)

Description

Each product in the FSDx321 (x for H, L) family consists of

an integrated Pulse Width Modulator (PWM) and Sense

FET, and is specifically designed for high performance off-

line Switch Mode Power Supplies (SMPS) with minimal

external components. Both devices are integrated high volt-

age power switching regulators which combine an avalanche

rugged Sense FET with a current mode PWM control block.

The integrated PWM controller features include: a fixed

oscillator with frequency modulation for reduced EMI,

Under Voltage Lock Out (UVLO) protection, Leading Edge

Blanking (LEB), an optimized gate turn-on/turn-off driver,

Thermal Shut Down (TSD) protection, Abnormal Over Cur-

rent Protection (AOCP) and temperature compensated preci-

sion current sources for loop compensation and fault

protection circuitry. When compared to a discrete MOSFET

and controller or RCC switching converter solution, the

FSDx321 devices reduce total component count, design size,

weight while increasing efficiency, productivity and system

reliability. Both devices provide a basic platform that is well

suited for the design of cost-effective flyback converters.

Notes:

1. Typical continuous power in a non-ventilated enclosed

adapter with sufficient drain pattern as a heat sinker, at

50

∞C ambient.

2. Maximum practical continuous power in an open frame

design with sufficient drain pattern as a heat sinker, at 50

∞C

ambient.

3. 230 VAC or 100/115 VAC with doubler.

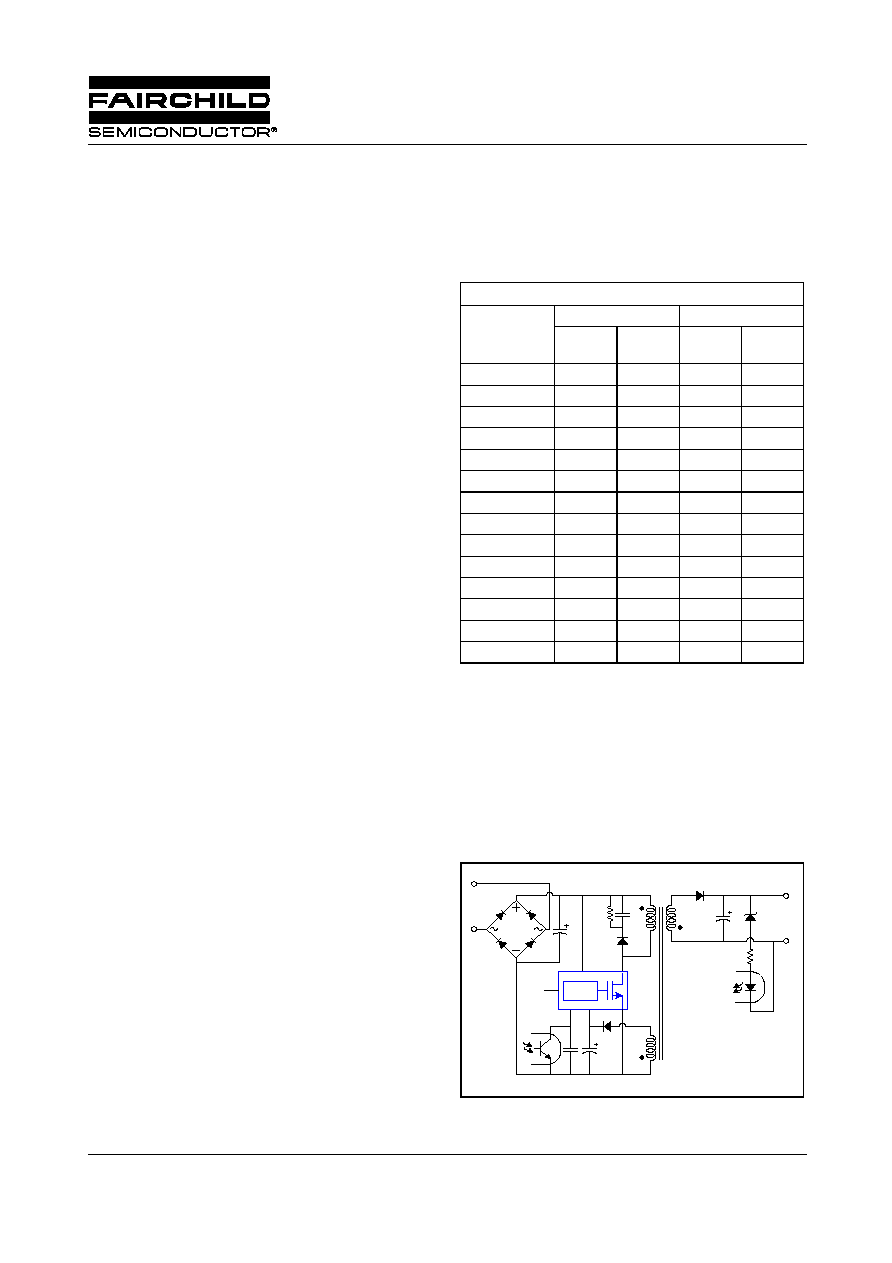

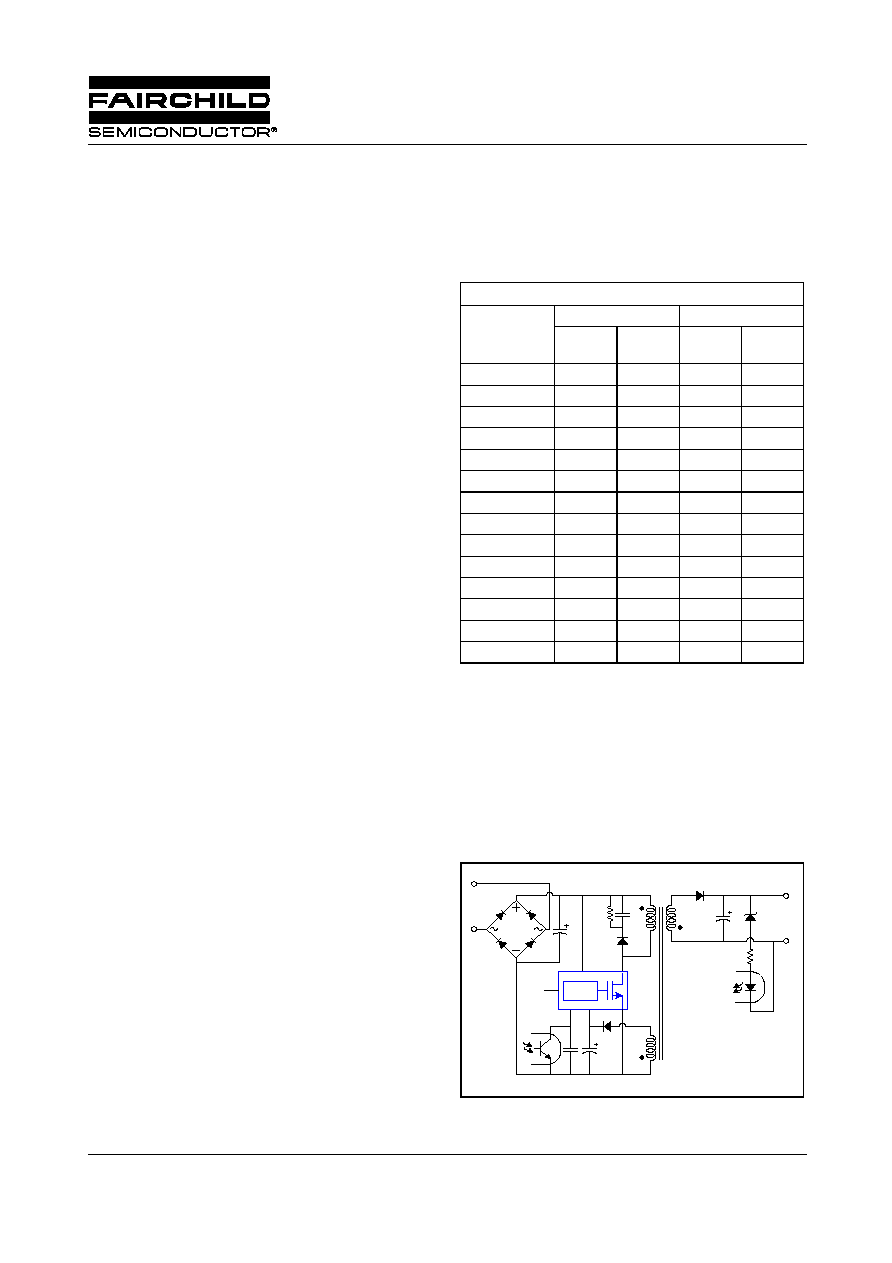

Typical Circuit

Figure 1. Typical Flyback Application

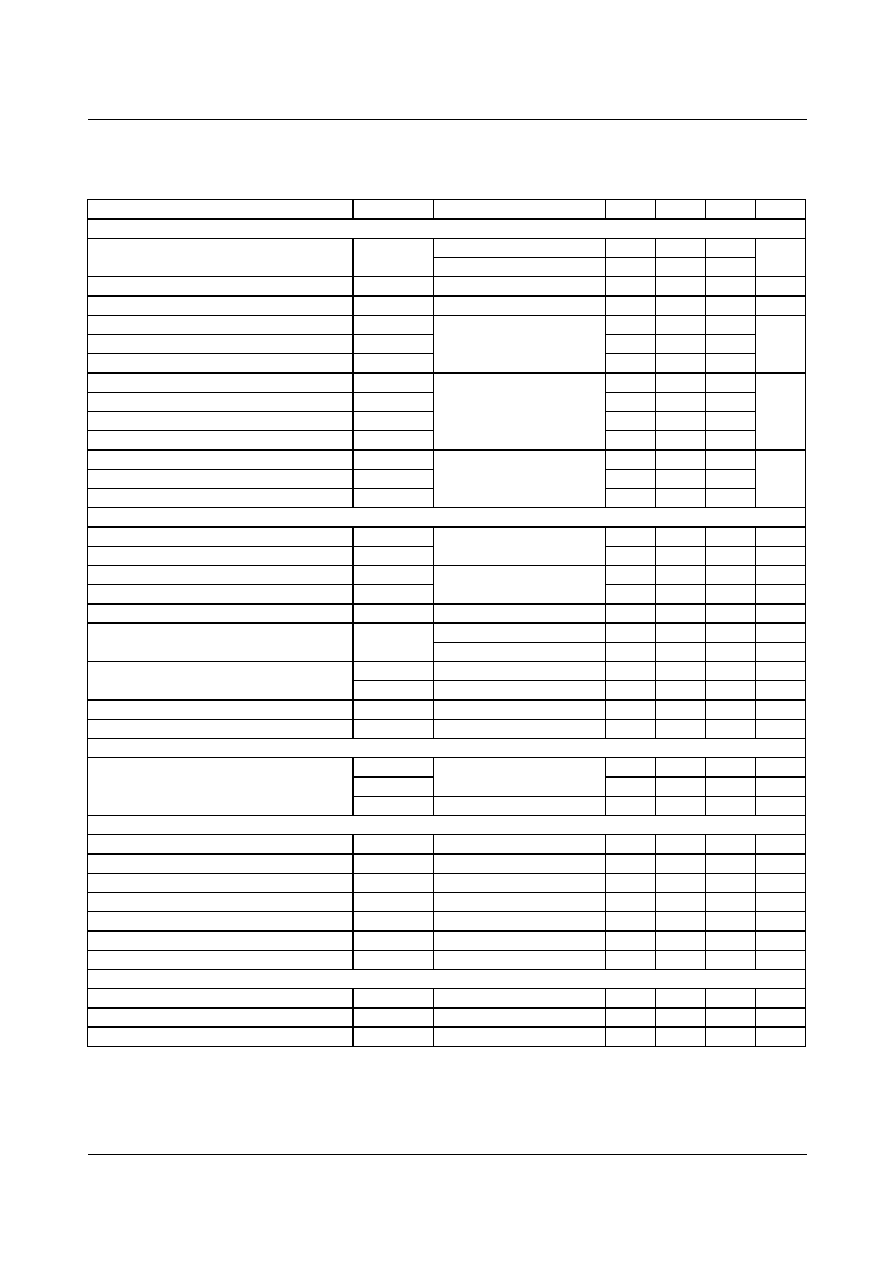

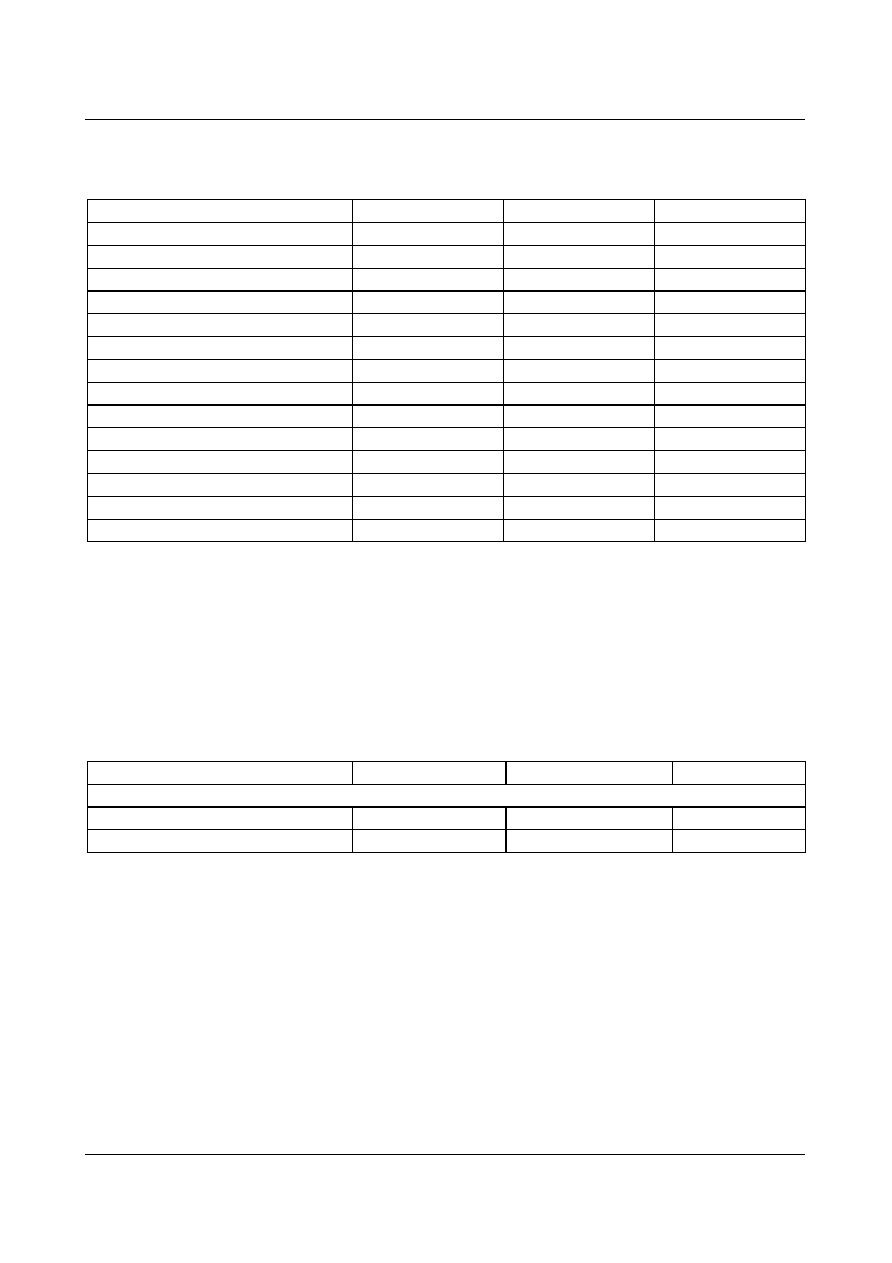

OUTPUT POWER TABLE

PRODUCT

230VAC

±15%

(3)

85-265VAC

Adapt-

er

(1)

Open

Frame

(2)

Adapt-

er

(1)

Open

Frame

(2)

FSDL321

11W

17W

8W

12W

FSDH321

11W

17W

8W

12W

FSDL0165RN

13W

23W

11W

17W

FSDM0265RN

16W

27W

13W

20W

FSDH0265RN

16W

27W

13W

20W

FSDL0365RN

19W

30W

16W

24W

FSDM0365RN

19W

30W

16W

24W

FSDL321L

11W

17W

8W

12W

FSDH321L

11W

17W

8W

12W

FSDL0165RL

13W

23W

11W

17W

FSDM0265RL

16W

27W

13W

20W

FSDH0265RL

16W

27W

13W

20W

FSDL0365RL

19W

30W

16W

24W

FSDM0365RL

19W

30W

16W

24W

Drain

Source

Vstr

Vfb

Vcc

PWM

AC

IN

DC

OUT

Ipk

FSDH321, FSDL321

Green Mode Fairchild Power Switch (FPS

TM

)

FSDH321, FSDL321

2

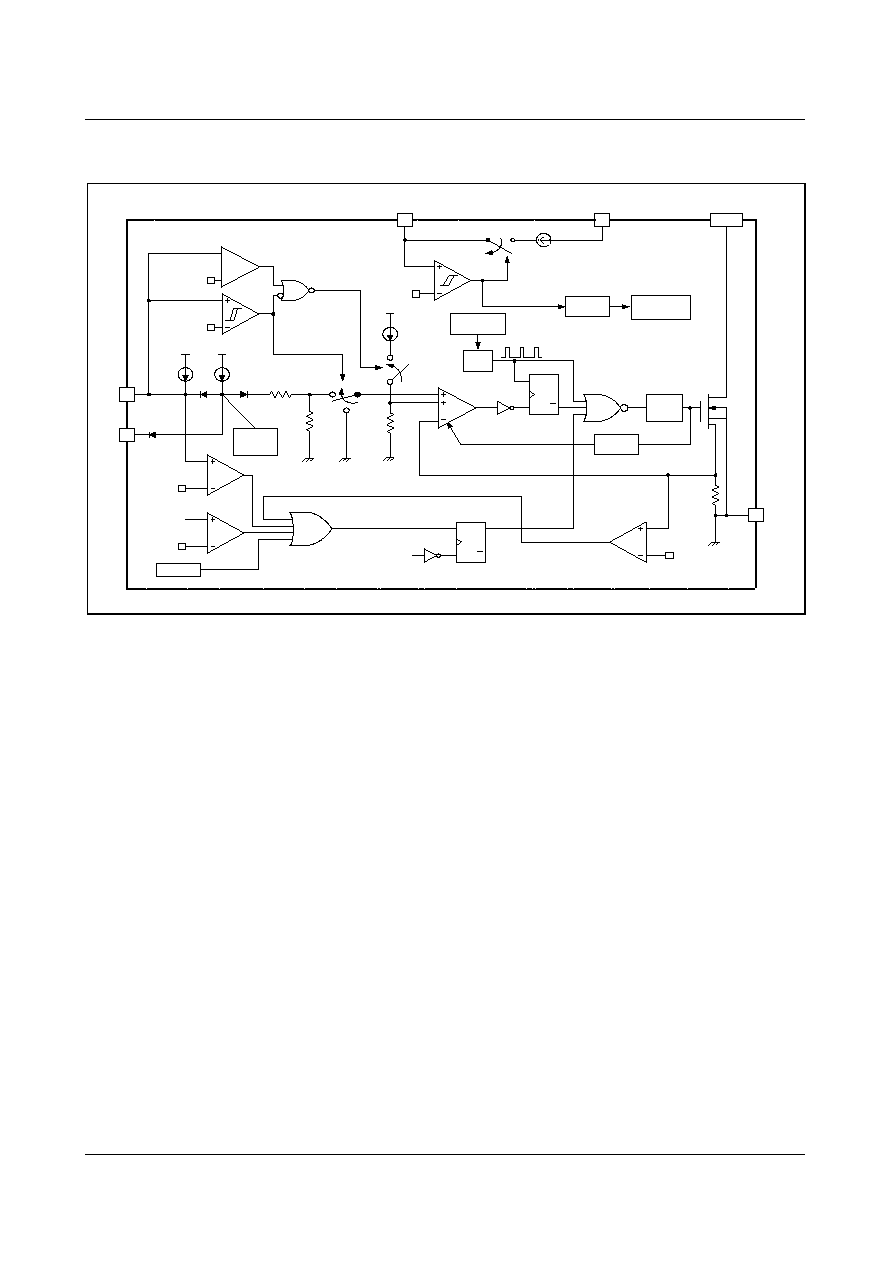

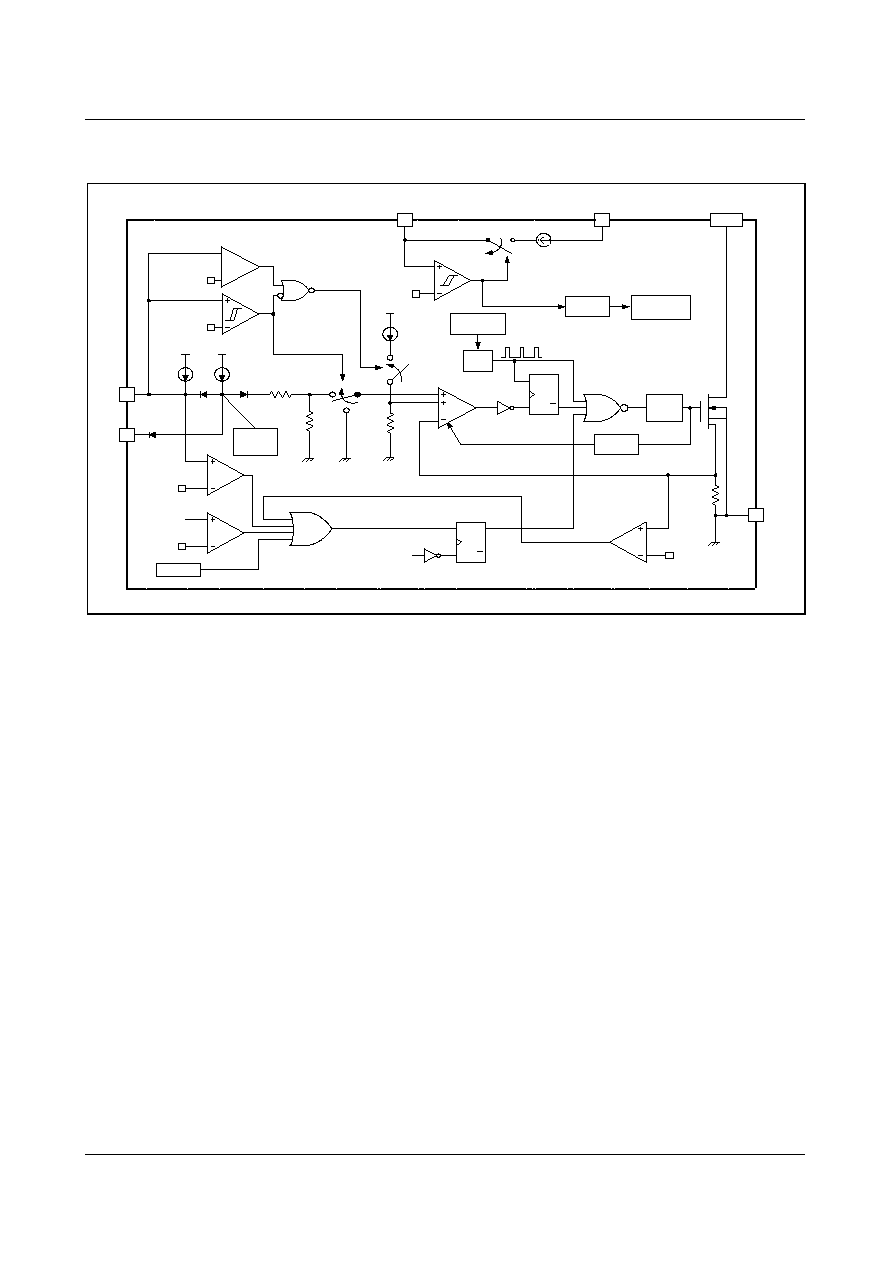

Internal Block Diagram

Figure 2. Functional Block Diagram of FSDx321

8V/12V

2

6,7,8

1

3

Vref

Internal

Bias

S

Q

Q

R

OSC

Vcc

Vcc

I

DELAY

I

FB

V

SD

TSD

Vovp

Vcc

Vocp

S

Q

Q

R

R

2.5R

Vcc good

Vcc

Drain

Vfb

GND

AOCP

Gate

driver

5

Vstr

I

CH

Vcc good

V

BURL

/V

BURH

LEB

PWM

+

-

4

Ipk

Freq.

Modulation

V

BURH

Vcc

I

BUR(pk)

Burst

Normal

Soft

Start

FSDH321, FSDL321

3

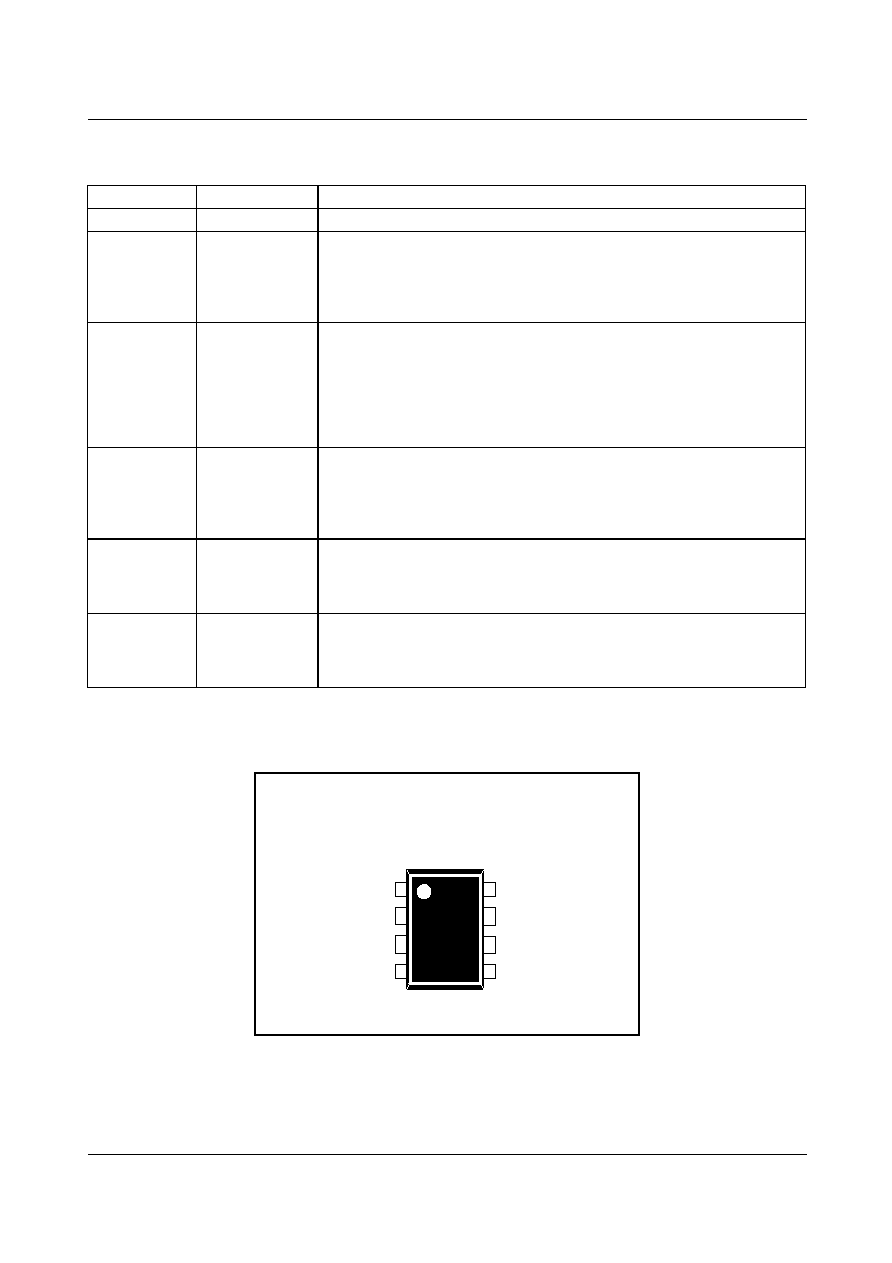

Pin Definitions

Pin Configuration

Figure 3. Pin Configuration (Top View)

Pin Number

Pin Name

Pin Function Description

1

GND

Sense FET source terminal on primary side and internal control ground.

2

Vcc

Positive supply voltage input. Although connected to an auxiliary transform-

er winding, current is supplied from pin 5 (Vstr) via an internal switch during

startup (see Internal Block Diagram section). It is not until Vcc reaches the

UVLO upper threshold (12V) that the internal start-up switch opens and de-

vice power is supplied via the auxiliary transformer winding.

3

Vfb

The feedback voltage pin is the non-inverting input to the PWM comparator.

It has a 0.9mA current source connected internally while a capacitor and op-

tocoupler are typically connected externally. A feedback voltage of 6V trig-

gers over load protection (OLP). There is a time delay while charging

external capacitor Cfb from 3V to 6V using an internal 5uA current source.

This time delay prevents false triggering under transient conditions, but still

allows the protection mechanism to operate under true overload conditions.

4

Ipk

This pin adjusts the peak current limit of the Sense FET. The feedback

0.9mA current source is diverted to the parallel combination of an internal

2.8k

resistor and any external resistor to GND on this pin to determine the

peak current limit. If this pin is tied to Vcc or left floating, the typical peak cur-

rent limit will be 0.7A.

5

Vstr

This pin connects directly to the rectified AC line voltage source. At start up

the internal switch supplies internal bias and charges an external storage

capacitor placed between the Vcc pin and ground. Once the Vcc reaches

12V, the internal switch is opened.

6, 7, 8

Drain

The drain pins are designed to connect directly to the primary lead of the

transformer and are capable of switching a maximum of 650V. Minimizing

the length of the trace connecting these pins to the transformer will decrease

leakage inductance.

1

2

3

4

5

6

7

8

GND

Vcc

Vfb

Ipk

Vstr

Drain

Drain

Drain

8DIP

8LSOP

FSDH321, FSDL321

4

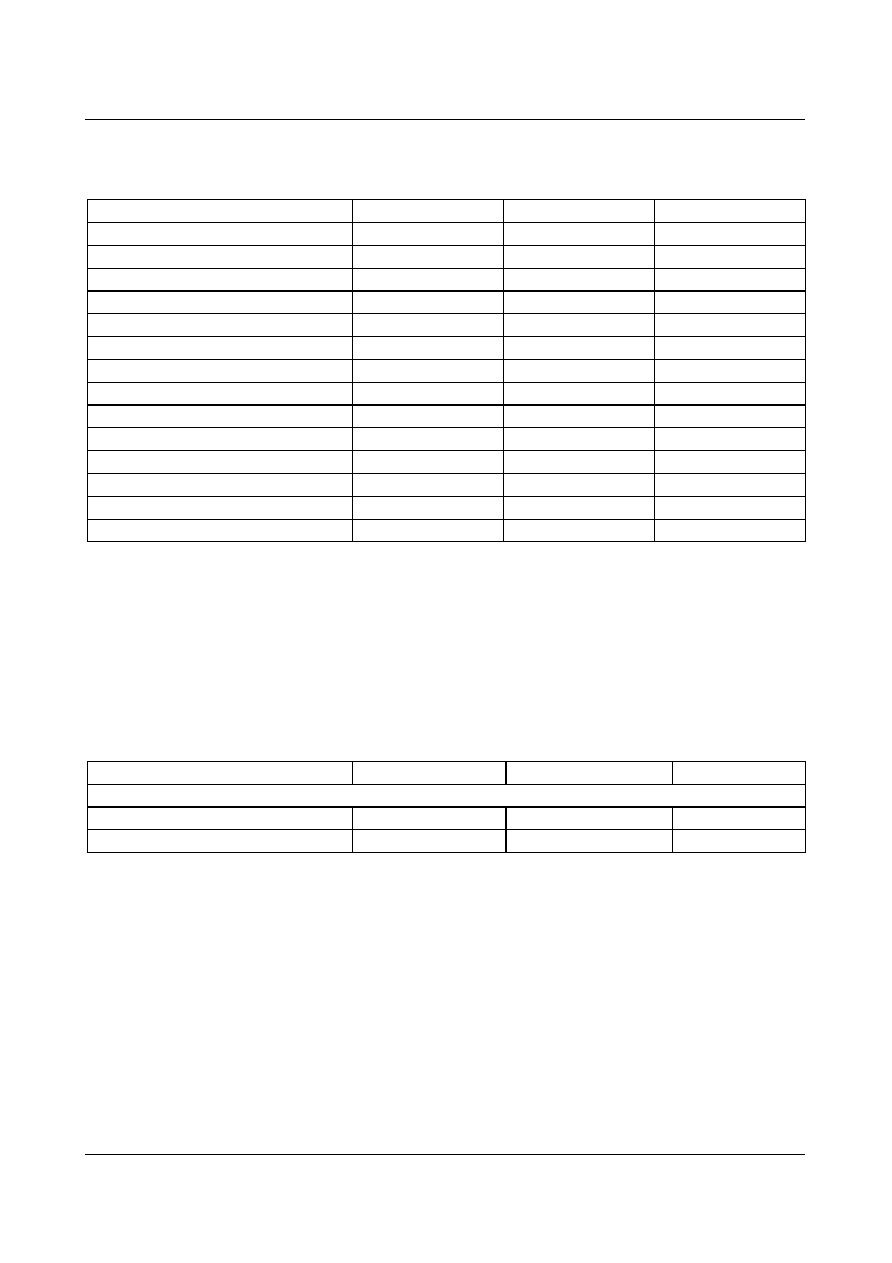

Absolute Maximum Ratings

(Ta=25

∞C, unless otherwise specified)

Note:

1. Repetitive rating: Pulse width is limited by maximum junction temperature

2. L = 24mH, starting Tj = 25

∞C

Thermal Impedance

(Ta=25

∞C, unless otherwise specified)

Note:

1. Free standing with no heatsink; Without copper clad.

/ Measurement Condition : Just before junction temperature T

J

enters into OTP.

2. Measured on the DRAIN pin close to plastic interface.

- all items are tested with the standards JESD 51-2 and 51-10 (DIP).

Characteristic

Symbol

Value

Unit

Drain Pin Voltage

V

DRAIN

650

V

Vstr Pin Voltage

V

STR

650

V

Drain-Gate Voltage

V

DG

650

V

Gate-Source Voltage

V

GS

± 20

V

Drain Current Pulsed

(1)

I

DM

1.5

A

Continuous Drain Current

(Tc=25)

I

D

0.7

A

Continuous Drain Current

(Tc=100)

I

D

0.32

A

Single Pulsed Avalanche Energy

(2)

E

AS

10

mJ

Supply Voltage

V

CC

20

V

Feedback Voltage Range

V

FB

-0.3 to V

CC

V

Total Power Dissipation

P

D

1.40

W

Operating Junction Temperature

T

J

Internally limited

∞C

Operating Ambient Temperature

T

A

-25 to +85

∞C

Storage Temperature

T

STG

-55 to +150

∞C

Parameter

Symbol

Value

Unit

8DIP

Junction-to-Ambient Thermal

(1)

JA

88.84

∞C/W

Junction-to-Case Thermal

(2)

JC

13.94

∞C/W

FSDH321, FSDL321

5

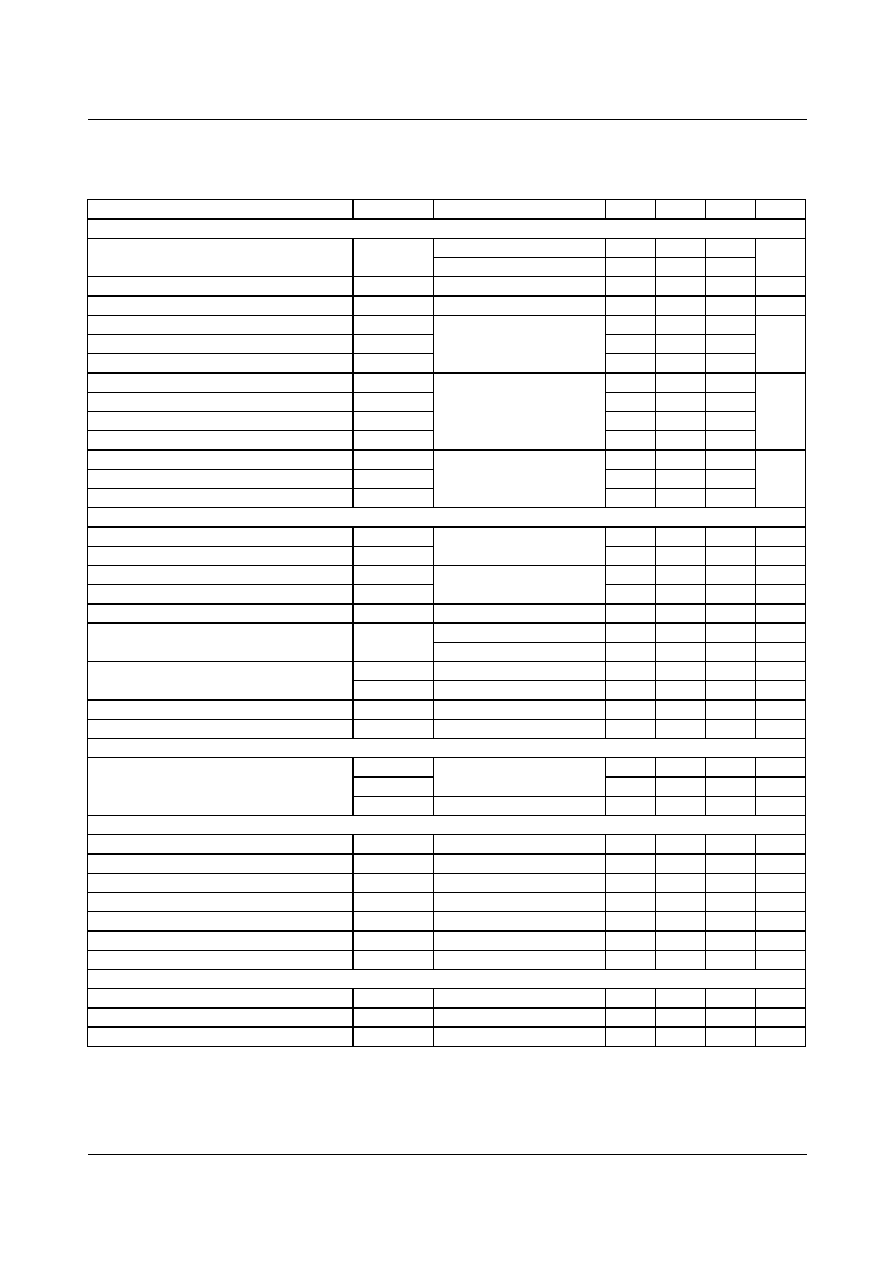

Electrical Characteristics

(Ta = 25

∞C unless otherwise specified)

Note:

1. Pulse test: Pulse width 300us, duty 2%

2. These parameters, although guaranteed, are tested in EDS (wafer test) process

3. These parameters, although guaranteed, are not 100% tested in production

Parameter Symbol

Condition

Min.

Typ.

Max.

Unit

SENSE FET SECTION

Zero-Gate-Voltage Drain Current

I

DSS

V

DS

=650V, V

GS

=0V -

-

25

µA

V

DS

=520V, V

GS

=0V, T

C

=125

∞C

-

-

200

Drain-Source On-State Resistance

R

DS(ON)

V

GS

=10V, I

D

=0.5A -

14

19

Forward Trans-Conductance

(1)

g

fs

V

DS

=50V, I

D

=0.5A 1.0

1.3

-

S

Input Capacitance

C

ISS

V

GS

=0V, V

DS

=25V,

f=1MHz

-

162

-

pF

Output Capacitance

C

OSS

-

18

-

Reverse Transfer Capacitance

C

RSS

-

3.8

-

Turn-On Delay Time

t

d(on)

V

DS

=325V, I

D

=1.0A

-

9.5

-

ns

Rise Time

t

r

-

19

-

Turn-Off Delay Time

t

d(off)

-

33

-

Fall Time

t

f

-

42

-

Total Gate Charge

Q

g

V

GS

=10V, I

D

=1.0A,

V

DS

=325V

-

7.0

-

nC

Gate-Source Charge

Q

gs

-

3.1

-

Gate-Drain (Miller) Charge

Q

gd

-

0.4

-

CONTROL SECTION

Switching Frequency

f

OSC

FSDH321

90 100 110 KHz

Switching Frequency Modulation

f

MOD

±2.5 ±3.0 ±3.5 KHz

Switching Frequency

f

OSC

FSDL321

45 50 55 KHz

Switching Frequency Modulation

f

MOD

±1.0 ±1.5 ±2.0 KHz

Switching Frequency Variation

(2)

f

OSC

-25

∞C Ta 85∞C

-

±5 ±10 %

Maximum Duty Cycle

D

MAX

FSDH321

62 67 72 %

FSDL321

71

77

83

%

UVLO Threshold Voltage

V

START

V

FB

=GND 11

12

13

V

V

STOP

V

FB

=GND 7

8

9

V

Feedback Source Current

I

FB

V

FB

=GND 0.7

0.9

1.1

mA

Internal Soft Start Time

t

S/S

V

FB

=4V 10

15

20

ms

BURST MODE SECTION

Burst Mode Voltage

V

BURH

Tj=25

∞C

0.4 0.5 0.6 V

V

BURL

0.25 0.35 0.45 V

V

BUR(HYS)

Hysteresis

-

150 -

mV

PROTECTION SECTION

Peak Current Limit

I

LIM

Tj=25

∞C, i/t=250mA/us 0.60 0.70

0.80 A

Current Limit Delay Time

(3)

t

CLD

Tj=25

∞C

-

600 -

ns

Thermal Shutdown Temperature

(3)

T

SD

125

145

-

∞C

Shutdown Feedback Voltage

V

SD

5.5

6.0

6.5

V

Over Voltage Protection

V

OVP

18

19

20

V

Shutdown Delay Current

I

DELAY

V

FB

=4V 3.5

5.0

6.5

µA

Leading Edge Blanking Time

t

LEB

200 -

-

ns

TOTAL DEVICE SECTION

Operating Supply Current

(control part only)

I

OP

V

CC

=14V, V

FB

=0V

1 3 5 mA

Start-Up Charging Current

I

CH

V

CC

=0V 0.7

0.85

1.0

mA

Vstr Supply Voltage

V

STR

V

CC

=0V 35

-

-

V