| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: IRLWI520A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

IRLW/I520A

BV

DSS

= 100 V

R

DS(on)

= 0.22

I

D

= 9.2 A

100

9.2

6.5

32

±

20

112

9.2

4.9

6.5

3.8

49

0.33

- 55 to +175

300

3.04

40

62.5

--

--

--

1

s

Avalanche Rugged Technology

s

Rugged Gate Oxide Technology

s

Lower Input Capacitance

s

Improved Gate Charge

s

Extended Safe Operating Area

s

175

Operating Temperature

s

Lower Leakage Current : 10

A (Max.) @ V

DS

= 100V

s

Lower R

DS(ON)

: 0.176

(Typ.)

Advanced Power MOSFET

Thermal Resistance

Junction-to-Case

Junction-to-Ambient

Junction-to-Ambient

R

JC

R

JA

R

JA

/W

Characteristic

Max.

Units

Symbol

Typ.

FEATURES

D

2

-PAK

1. Gate 2. Drain 3. Source

1

3

2

1

2

3

I

2

-PAK

*

*

When mounted on the minimum pad size recommended (PCB Mount).

Absolute Maximum Ratings

Drain-to-Source Voltage

Continuous Drain Current (T

C

=25

)

Continuous Drain Current (T

C

=100

)

Drain Current-Pulsed

Gate-to-Source Voltage

Single Pulsed Avalanche Energy

Avalanche Current

Repetitive Avalanche Energy

Peak Diode Recovery dv/dt

Total Power Dissipation (T

A

=25

)

Total Power Dissipation (T

C

=25

)

Linear Derating Factor

Operating Junction and

Storage Temperature Range

Maximum Lead Temp. for Soldering

Purposes, 1/8" from case for 5-seconds

Characteristic

Value

Units

Symbol

I

DM

V

GS

E

AS

I

AR

E

AR

dv/dt

P

D

I

D

T

J

, T

STG

T

L

A

V

mJ

A

mJ

V/ns

W

W

W/

A

V

DSS

V

*

IRLW/I520A

100

--

1.0

--

--

--

--

--

0.1

--

--

--

--

--

90

39

5

10

19

9

10.2

1.7

6.0

--

--

2.0

100

-100

10

100

0.22

--

440

115

50

20

30

50

30

15

--

--

7.7

340

--

--

--

98

0.34

9.2

32

1.5

--

--

Notes ;

Repetitive Rating : Pulse Width Limited by Maximum Junction Temperature

L=2mH, I

AS

=9.2A, V

DD

=25V, R

G

=27

, Starting T

J

=25

I

SD

9.2A, di/dt

300A/

s, V

DD

BV

DSS

, Starting T

J

=25

Pulse Test : Pulse Width = 250

s, Duty Cycle

2%

Essentially Independent of Operating Temperature

2

N-CHANNEL

POWER MOSFET

Electrical Characteristics

(T

C

=25

unless otherwise specified)

Drain-Source Breakdown Voltage

Breakdown Voltage Temp. Coeff.

Gate Threshold Voltage

Gate-Source Leakage , Forward

Gate-Source Leakage , Reverse

Characteristic

Symbol

Max. Units

Typ.

Min.

Test Condition

Static Drain-Source

On-State Resistance

Forward Transconductance

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

Turn-On Delay Time

Rise Time

Turn-Off Delay Time

Fall Time

Total Gate Charge

Gate-Source Charge

Gate-Drain(

Miller

) Charge

g

fs

C

iss

C

oss

C

rss

t

d(on)

t

r

t

d(off)

t

f

Q

g

Q

gs

Q

gd

BV

DSS

BV/

T

J

V

GS(th)

R

DS(on)

I

GSS

I

DSS

V

V/

V

nA

A

pF

ns

nC

--

--

--

--

--

--

--

--

--

--

--

--

--

V

GS

=0V,I

D

=250

A

I

D

=250

A See Fig 7

V

DS

=5V,I

D

=250

A

V

GS

=20V

V

GS

=-20V

V

DS

=100V

V

DS

=80V,T

C

=150

V

GS

=5V,I

D

=4.6A

V

DS

=40V,I

D

=4.6A

V

DD

=50V,I

D

=9.2A,

R

G

=9

See Fig 13

V

DS

=80V,V

GS

=5V,

I

D

=9.2A

See Fig 6 & Fig 12

Drain-to-Source Leakage Current

V

GS

=0V,V

DS

=25V,f =1MHz

See Fig 5

Source-Drain Diode Ratings and Characteristics

Continuous Source Current

Pulsed-Source Current

Diode Forward Voltage

Reverse Recovery Time

Reverse Recovery Charge

I

S

I

SM

V

SD

t

rr

Q

rr

Characteristic

Symbol

Max. Units

Typ.

Min.

Test Condition

--

--

--

--

--

A

V

ns

C

Integral reverse pn-diode

in the MOSFET

T

J

=25

,I

S

=9.2A,V

GS

=0V

T

J

=25

,I

F

=9.2A

di

F

/dt=100A/

s

IRLW/I520A

10

-1

10

0

10

1

10

-1

10

0

10

1

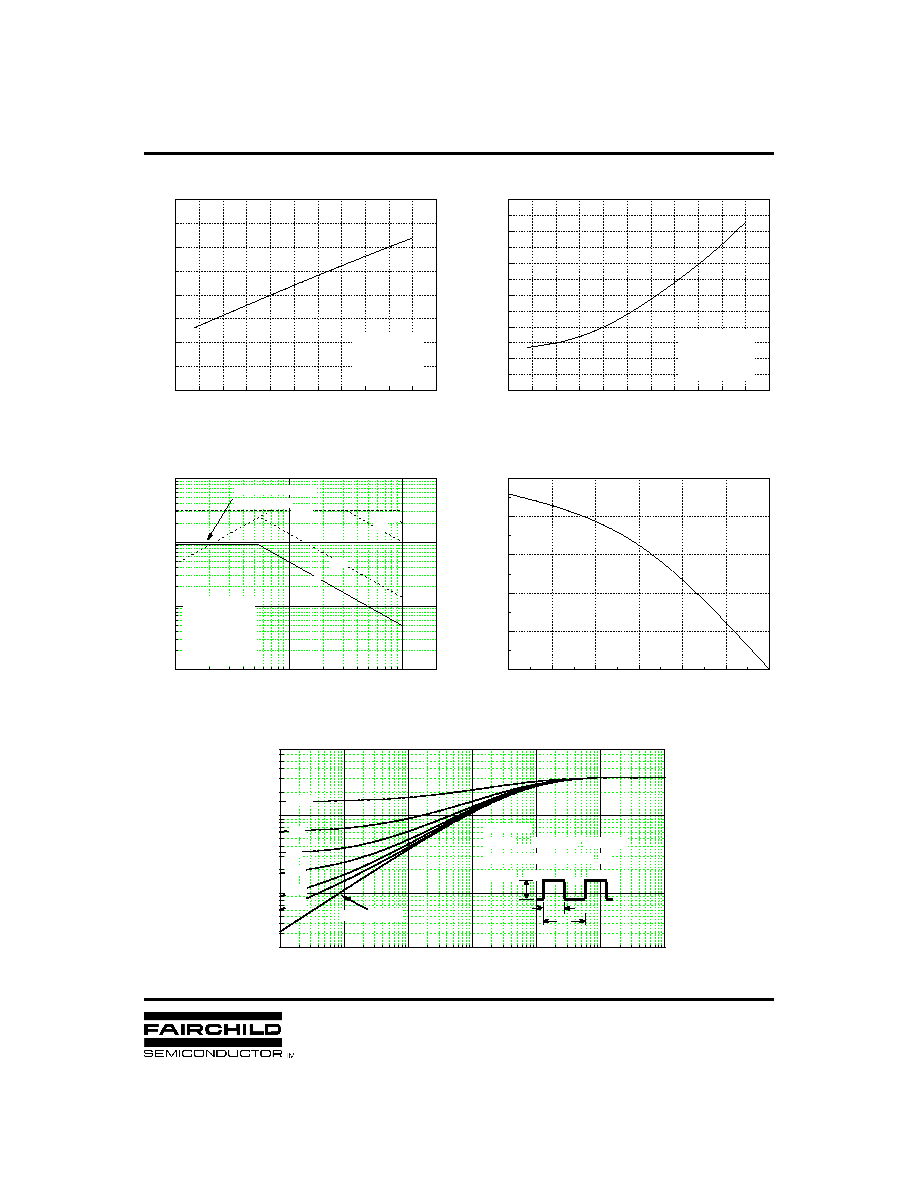

@ Notes :

1. 250

µ

s Pulse Test

2. T

C

= 25

o

C

V

GS

Top : 7.0 V

6.0 V

5.5 V

5.0 V

4.5 V

4.0 V

3.5 V

Bottom : 3.0 V

I

D

, Dr

ai

n Cu

rr

en

t [A

]

V

DS

, Drain-Source Voltage [V]

0

2

4

6

8

10

10

-1

10

0

10

1

25

o

C

175

o

C

- 55

o

C

@ Notes :

1. V

GS

= 0 V

2. V

DS

= 40 V

3. 250

µ

s Pulse Test

I

D

, Dr

ai

n Cu

rr

en

t [A

]

V

GS

, Gate-Source Voltage [V]

0

10

20

30

40

0.0

0.1

0.2

0.3

0.4

@ Note : T

J

= 25

o

C

V

GS

= 10 V

V

GS

= 5 V

R

DS

(o

n)

, [

]

Dr

ai

n-

So

ur

ce

O

n

-

Res

is

ta

nc

e

I

D

, Drain Current [A]

0

2

4

6

8

10

12

0

2

4

6

V

DS

= 80 V

V

DS

= 50 V

V

DS

= 20 V

@ Notes : I

D

= 9.2 A

V

GS

, Ga

te

-S

ou

rc

e Vo

l

t

a

g

e

[V

]

Q

G

, Total Gate Charge [nC]

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

2.0

2.2

10

-1

10

0

10

1

175

o

C

25

o

C

@ Notes :

1. V

GS

= 0 V

2. 250

µ

s Pulse Test

I

DR

, Re

ve

rs

e Dr

ai

n C

u

r

r

e

n

t

[A

]

V

SD

, Source-Drain Voltage [V]

10

0

10

1

0

120

240

360

480

600

C

iss

= C

gs

+ C

gd

(

C

ds

= shorted

)

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

@ Notes :

1. V

GS

= 0 V

2. f = 1 MHz

C

rss

C

oss

C

iss

Ca

pa

ci

ta

nc

e

[

p

F

]

V

DS

, Drain-Source Voltage [V]

3

N-CHANNEL

POWER MOSFET

Fig 1. Output Characteristics

Fig 2. Transfer Characteristics

Fig 6. Gate Charge vs. Gate-Source Voltage

Fig 5. Capacitance vs. Drain-Source Voltage

Fig 4. Source-Drain Diode Forward Voltage

Fig 3. On-Resistance vs. Drain Current

IRLW/I520A

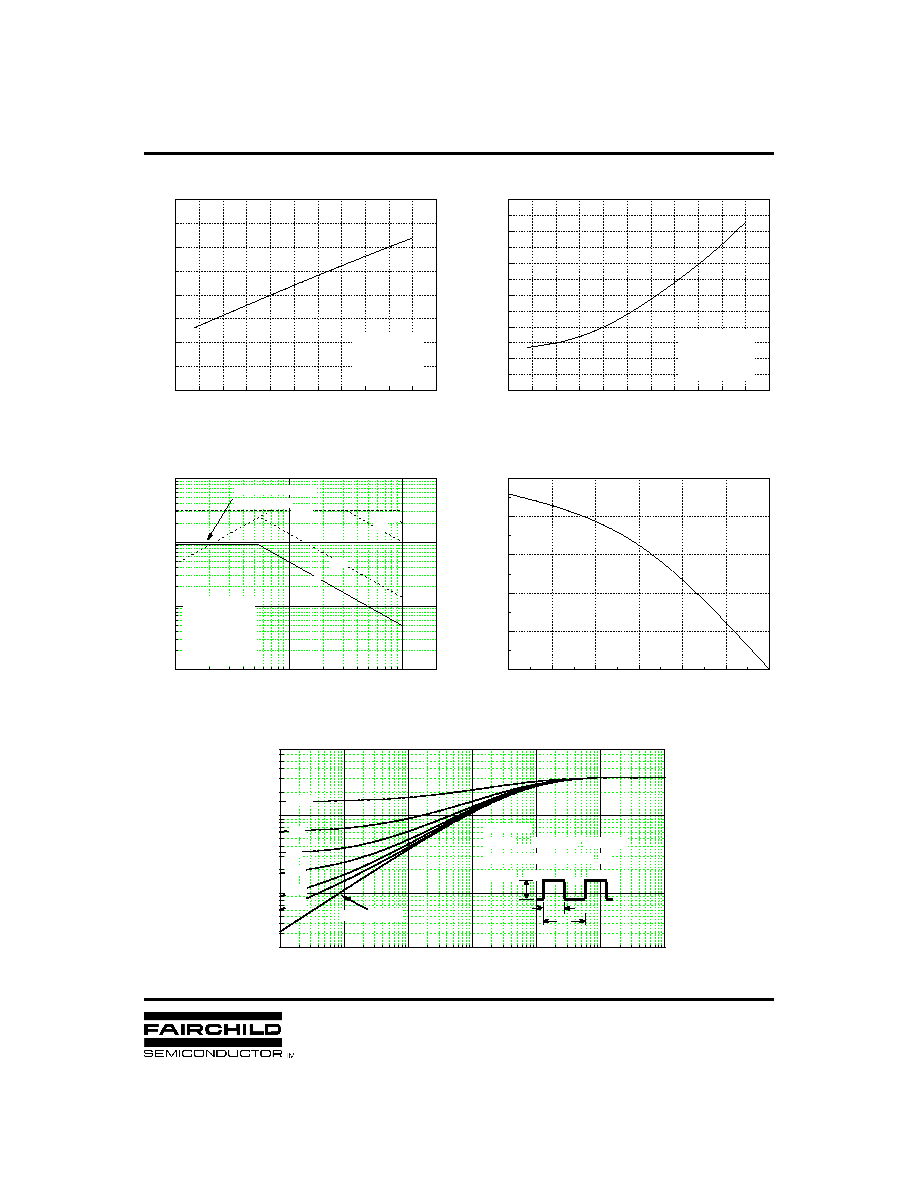

-75

-50

-25

0

25

50

75

100

125

150

175

200

0.8

0.9

1.0

1.1

1.2

@ Notes :

1. V

GS

= 0 V

2. I

D

= 250

µ

A

BV

DS

S

, (N

or

ma

li

ze

d)

Dr

ai

n-

So

ur

ce

B

r

e

akd

ow

n

Vo

lt

ag

e

T

J

, Junction Temperature [

o

C]

10

0

10

1

10

2

10

-1

10

0

10

1

10

2

DC

100

µ

s

1 ms

10 ms

@ Notes :

1. T

C

= 25

o

C

2. T

J

= 175

o

C

3. Single Pulse

Operation in This Area

is Limited by R

DS(on)

I

D

, Dr

ai

n Cu

rr

en

t [A

]

V

DS

, Drain-Source Voltage [V]

25

50

75

100

125

150

175

0

2

4

6

8

10

I

D

, Dr

ai

n Cu

rr

en

t [A

]

T

c

, Case Temperature [

o

C]

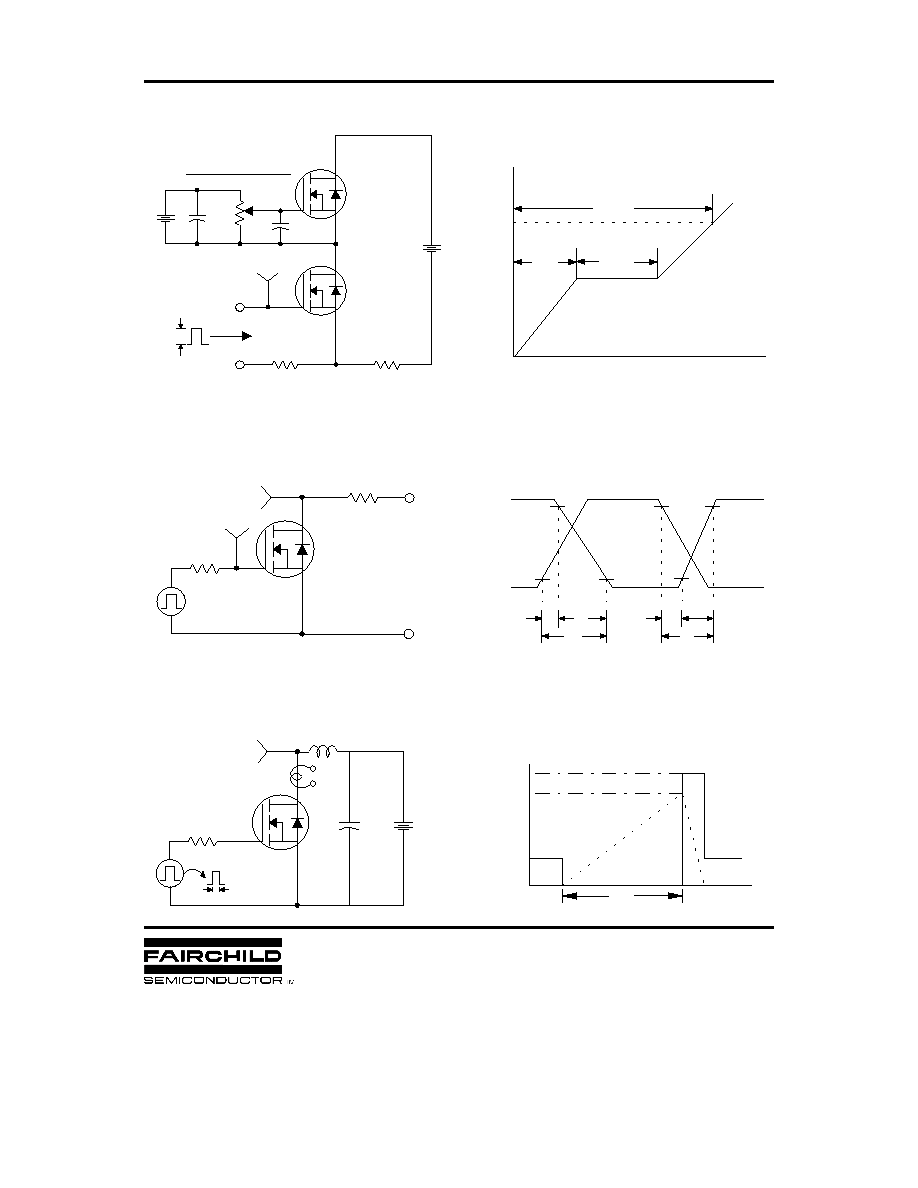

10

- 5

10

- 4

10

- 3

10

- 2

10

- 1

10

0

10

1

10

- 1

10

0

single pulse

0.2

0.1

0.01

0.02

0.05

D=0.5

@ Notes :

1. Z

J C

(t)=3.04

o

C/W Max.

2. Duty Factor, D=t

1

/t

2

3. T

J M

-T

C

=P

D M

*Z

J C

(t)

Z

JC

(

t

)

,

Th

er

ma

l

Re

sp

on

se

t

1

, Square Wave Pulse Duration [sec]

-75

-50

-25

0

25

50

75

100

125

150

175

200

0.0

0.5

1.0

1.5

2.0

2.5

3.0

@ Notes :

1. V

GS

= 5 V

2. I

D

= 4.6 A

R

DS

(o

n)

, (N

or

ma

li

ze

d)

Dr

ai

n-

So

ur

ce

O

n

-

Res

is

ta

nc

e

T

J

, Junction Temperature [

o

C]

4

N-CHANNEL

POWER MOSFET

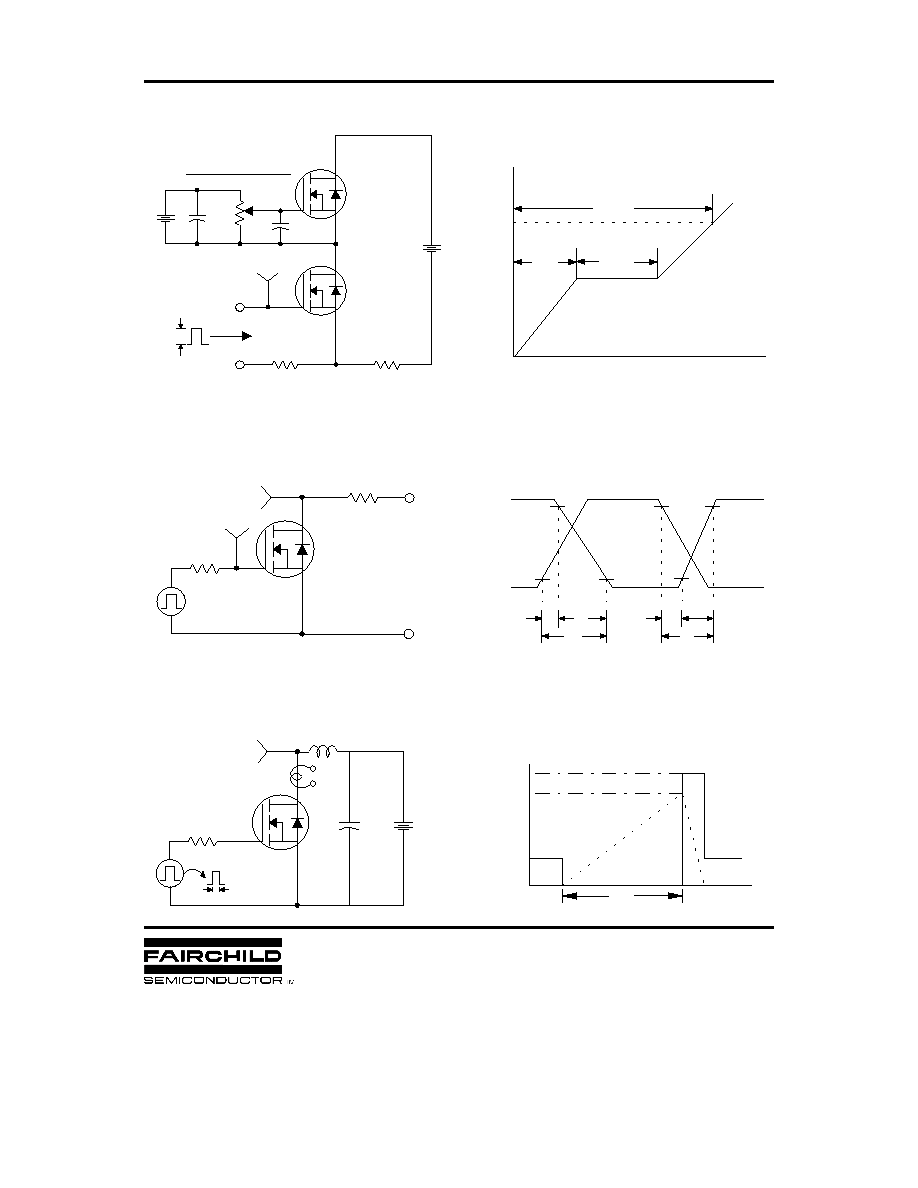

Fig 7. Breakdown Voltage vs. Temperature

Fig 8. On-Resistance vs. Temperature

Fig 11. Thermal Response

Fig 10. Max. Drain Current vs. Case Temperature

Fig 9. Max. Safe Operating Area

P

DM

t

1

t

2

IRLW/I520A

5

N-CHANNEL

POWER MOSFET

Fig 12. Gate Charge Test Circuit & Waveform

Fig 13. Resistive Switching Test Circuit & Waveforms

Fig 14. Unclamped Inductive Switching Test Circuit & Waveforms

E

AS

=

L

L

I

AS

2

----

2

1

--------------------

BV

DSS

-- V

DD

BV

DSS

V

in

V

out

10%

90%

t

d(on)

t

r

t

on

t

off

t

d(off)

t

f

Charge

V

GS

10V

Q

g

Q

gs

Q

gd

Vary t

p

to obtain

required peak I

D

5V

V

DD

C

L

L

V

DS

I

D

R

G

t

p

DUT

BV

DSS

t

p

V

DD

I

AS

V

DS

(t)

I

D

(t)

Time

V

DD

( 0.5 rated V

DS

)

10V

V

out

V

in

R

L

DUT

R

G

3mA

V

GS

Current Sampling (I

G

)

Resistor

Current Sampling (I

D

)

Resistor

DUT

V

DS

300nF

50K

200nF

12V

Same Type

as DUT

* Current Regulator "

R

1

R

2