| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 56F8023 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

MC56F8023E

Rev. 0, 09/2006

56F8023

Freescale Semiconductor

©Freescale Semiconductor, Inc. 2006. All rights reserved.

Preliminary Chip Errata

56F8023 Digital Signal Controller

This document reports errata information on chip revision A. Errata numbers are in the form n.m, where n is the

number of the errata item and m identifies the document revision number. This document is a pre-publication draft.

Chip Revision A

Errata Information:

The following errata items apply only to Revision A

56F8023 devices.

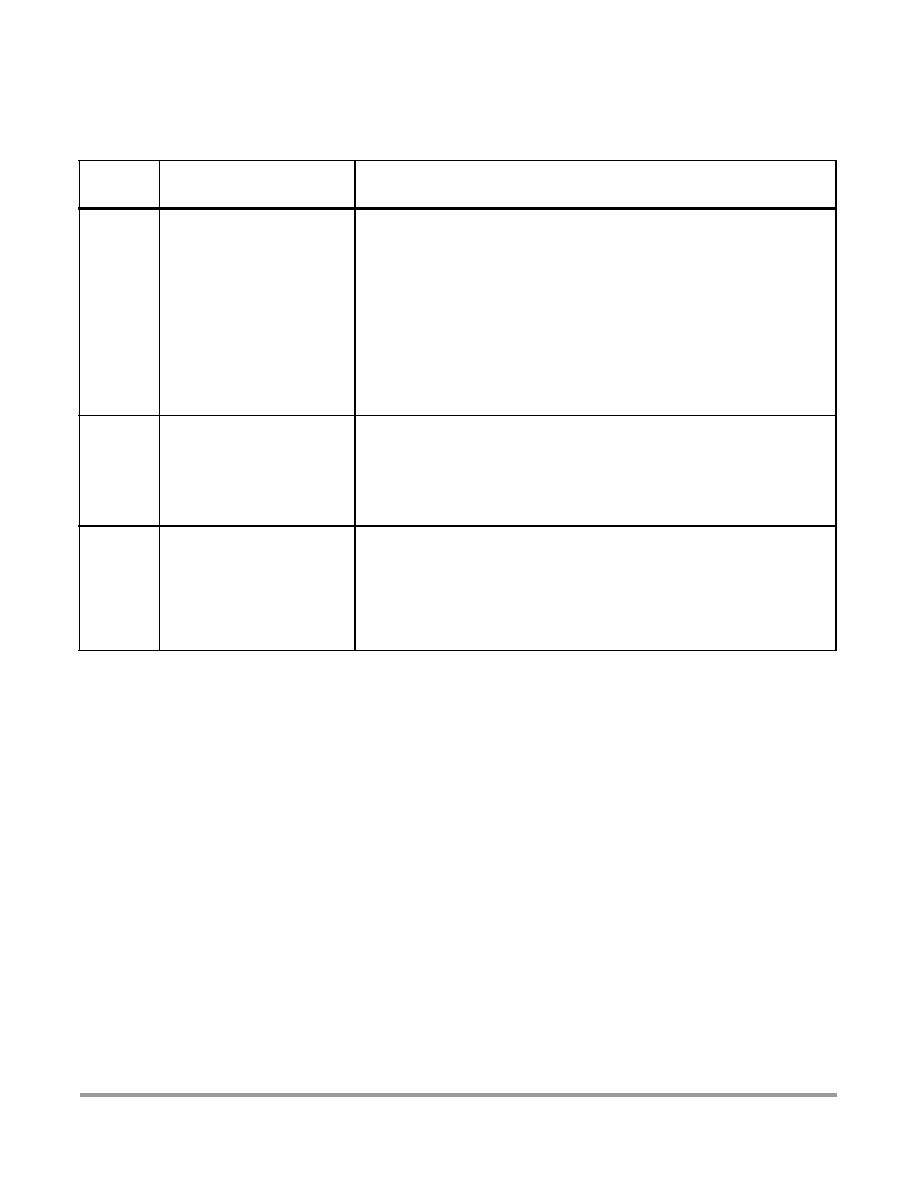

Errata

Number

Description

Impact and Work Around

1.0

In the DAC, the up/down

counter which implements

waveform generation in

automatic mode in the DAC

gasket does not handle negative

numbers.

Impact:

Down counting to a negative number will wrap the counter and continue down

counting.

Work Around:

Adjust MAXVAL, MINVAL, and/or STEP size so the terminal value while down

counting is positive or zero.

2.0

I

2

C fails to detect arbitration loss

when the loss occurs while the

ACK bit of data bytes is received

in master RX mode.

Impact:

No impact on bus behavior.

Arbitration loss software counters will not be accurate in this situation.

Work Around:

None available.

3.0

Some I

2

C slave TX FIFO

flushes don't interrupt the CPU.

Impact:

If the number of bytes written to the TX FIFO exceeds the number of data bytes

retrieved by the remote master, there is no CPU indication that the excess data bytes

were flushed from the TX FIFO.

Software must accommodate this behavior

Work Around:

None available

4.0

I

2

C ACKs its own address and

data during general calls when

both master and slave are

enabled and the module initiates

the general call. This means the

transmission will always be

completed and it's impossible to

determine if another device is

ACKing the call.

Impact:

Since the module always ACKs the general call address and data in the scenario, the

module will never know if any of the other nodes NACKed the general call.

Use work around until fixed.

Work Around:

Disable slave mode prior to initiating a general call.

2

56F8023 Preliminary Technical Data

5.0

Although required by the Philips

spec, the I

2

C does not reset its

bus logic, and thereby prepare to

receive address following an

unexpected START or repeated

START. An unexpected START

or repeated START is one that is

not positioned according to the

proper format.

Impact:

Avoid all unexpected START conditions. Typically, this is not an issue in a single

master system. In a multi-master system, avoid an unexpected START by powering

up all master I

2

Cs while the bus remains idle or by initiating master activity in a newly

powered up master only when the bus is idle.

Work Around:

Use work around until fixed.

6.0

The I

2

C bus locks up when

disabled in slave TX mode.

Impact:

Same as description.

Work Around:

The user's software must ensure that slv_activity and mst_activity are deasserted when

disabling the module. To prevent this problem, follow the full module disabling

procedure outlined in documentation.

7.0

If you power up the I

2

C in

master mode and write to the TX

FIFO for the first time while the

bus is not idle, the I

2

C may

transmit onto the non-idle bus.

Impact:

Same as description.

Work Around:

If it's possible to power up the module while the bus is busy, the user should monitor

for I

2

C bus STOP detection or idle conditions before writing to the TX FIFO for the

first time.

8.0

I

2

C may deassert interrupts

during module disabling.

Impact:

Same as description; reported to inform user of related module functionality.

Work Around:

Once enabled, if I

2

C is disabled, the user's software must be able to manage the

possible deassertion of asserted interrupt outputs.

9.0

I

2

C prematurely releases SCL in

slave TX abort, causing all-ones

data to be clocked out.

Impact:

Same as description.

Work Around:

While operating in slave transmitter mode, do not write a read command to the TX

FIFO .

10.0

I

2

C provides only one IPBus

clock period of noise

suppression.

Impact:

Same as description.

Work Around:

Ensure that noise spikes do not exceed one IPBus clock period.

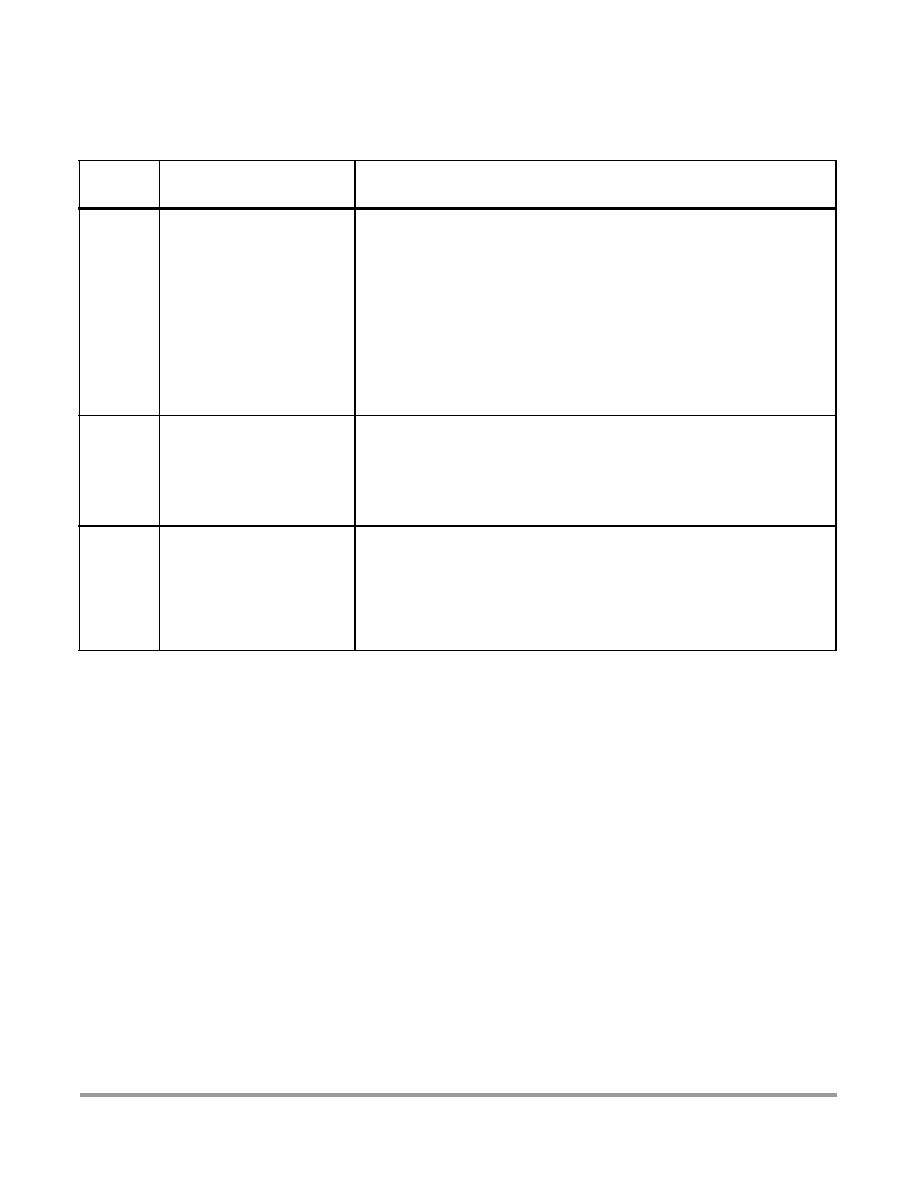

Chip Revision A

Errata Information:

The following errata items apply only to Revision A

56F8023 devices.

Errata

Number

Description

Impact and Work Around

56F8023 Preliminary Technical Data

3

11.0

If the I

2

C is generating a STOP

condition on the bus, the CPU

cannot write to the TX FIFO

following a transmit abort.

Impact:

Same as description.

Work Around:

If a transmit abort interrupt service routing needs to write data to the TX FIFO, poll

the STAT register's ACT bit (bit 0) until the bit is zero, before writing to the TX

FIFO.

This work around is needed only if the TX abort source generates a STOP condition

on the bus. The following TX abort sources generate STOP conditions: RNORST,

SACKDET, GCREAD, GCNACK, TDNACK, AD2NACK, AD1NACK, and

AD7NACK.

12.0

In the ADC, V

REFL

and V

REFH

functions are attached to the

wrong ADC channels and thus

are pinned out on the wrong

external GPIO pads.

This errata will be corrected in Revision B of the device (production version).

13.0

ROSC exceeds its -3%

frequency variation spec when

operating below -20∞C.

Impact:

The SCI interface can malfinction if the part is operating on the ROSC and the

frequency variation spec is violated.

Work Around:

Avoid using the SCI or other frequency critical functionality when operating below

-20∞C.

Chip Revision A

Errata Information:

The following errata items apply only to Revision A

56F8023 devices.

Errata

Number

Description

Impact and Work Around

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064, Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

FreescaleTM and the Freescale logo are trademarks of Freescale Semiconductor,

Inc. All other product or service names are the property of their respective owners.

This product incorporates SuperFlashÆ technology licensed from SST.

© Freescale Semiconductor, Inc. 2005. All rights reserved.

MC56F8023E

Rev. 0

09/2006

Information in this document is provided solely to enable system and

software implementers to use Freescale Semiconductor products. There are

no express or implied copyright licenses granted hereunder to design or

fabricate any integrated circuits or integrated circuits based on the

information in this document.

Freescale Semiconductor reserves the right to make changes without further

notice to any products herein. Freescale Semiconductor makes no warranty,

representation or guarantee regarding the suitability of its products for any

particular purpose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or

incidental damages. "Typical" parameters that may be provided in Freescale

Semiconductor data sheets and/or specifications can and do vary in different

applications and actual performance may vary over time. All operating

parameters, including "Typicals", must be validated for each customer

application by customer's technical experts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

Freescale Semiconductor products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other

application in which the failure of the Freescale Semiconductor product could

create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended

or unauthorized application, Buyer shall indemnify and hold Freescale

Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the

functionality and electrical characteristics of their non-RoHS-compliant and/

or non-Pb-free counterparts. For further information, see

http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to

http://www.freescale.com/epp.