DS07-13704-5E

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F

2

MC-16LX MB90590/590G Series

MB90591/591G/F591A/F591G/594/594G/F594A/F594G

MB90V590A/V590G

s

DESCRIPTION

The MB90590/590G series with two FULL-CAN*

1

interfaces and FLASH ROM is especially designed for automo-

tive and industrial applications. Its main features are two on board CAN Interfaces, which conform to V2.0 Part A

and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal

full CAN approach.

The instruction set of F

2

MC-16LX CPU core inherits an AT architecture of the F

2

MC*

2

family with additional

instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division instructions,

and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long

word data.

The MB90590/590G series has peripheral resources of 8/10-bit A/D converters, UART (SCI), extended I/O serial

interface, 8/16-bit PPG timer, I/O timer (input capture (ICU), output compare (OCU)), stepping motor controller,

and sound generator.

*1 : Controller Area Network (CAN) - License of Robert Bosch GmbH

*2 : F

2

MC stands for FUJITSU Flexible Microcontroller.

s

PACKAGE

100-pin Plastic QFP

(FPT-100P-M06)

MB90590/590G Series

2

s

FEATURES

∑ Clock

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from divided-by-2 of oscillation or one to four times the oscillation

(at oscillation of 4 MHz, 4 MHz to 16 MHz).

Minimum instruction execution time : 62.5 ns (operation at oscillation of 4 MHz, four times the oscillation clock,

V

CC

of 5.0 V)

∑ Instruction set to optimize controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

Enhanced signed multiplication/division instruction and RETI instruction functions

Enhanced precision calculation realized by the 32-bit accumulator

∑ Instruction set designed for high level language (C language) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

∑ Program patch function (for two address pointers)

∑ Enhanced execution speed : 4-byte instruction queue

∑ Enhanced interrupt function : 8 levels, 34 factors

∑ Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI

2

OS) : Up to 10 channels

∑ Embedded ROM size and types

Mask ROM : 256 Kbytes/384 Kbytes

Flash ROM : 256 Kbytes/384 Kbytes

Embedded RAM size : 6 Kbytes/8 Kbytes

∑ Flash ROM

Supports automatic programming, Embedded Algorithm

TM

*

Write/Erase/Erase-Suspend/Resume commands

A flag indicating completion of the algorithm

Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory

Erase can be performed on each block

Block protection with external programming voltage

∑ Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Clock mode

Hardware stand-by mode

∑ Process

0.5

µ

m CMOS technology

∑ I/O port

General-purpose I/O ports : 78 ports

∑ Timer

Watchdog timer : 1 channel

8/16-bit PPG timer : 8/16-bit

◊

6 channels

16-bit re-load timer : 2 channels

MB90590/590G Series

3

∑ 16-bit I/O timer

16-bit free-run timer : 1 channel

Input capture : 6 channels

Output compare : 6 channels

∑ Extended I/O serial interface : 1 channel

∑ UART (3 channels)

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized (with start/stop bit) transmission can be selectively used.

∑ Stepping motor controller (4 channels)

∑ External interrupt circuit (8 channels)

A module for starting an extended intelligent I/O service (EI

2

OS) and generating an external interrupt which

is triggered by an external input.

∑ Delayed interrupt generation module

Generates an interrupt request for switching tasks.

∑ 8/10-bit A/D converter (8 channels)

8/10-bit resolution can be selectively used.

Starting by an external trigger input.

∑ FULL-CAN interfaces : 2

Conforming to Version 2.0 Part A and Part B

Flexible message buffering (mailbox and FIFO buffering can be mixed)

∑ Sound generator

∑ 18-bit Time-base counter

∑ Clock timer : 1 channel

∑ External bus interface : Maximum address space 16 Mbytes

* : Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.

MB90590/590G Series

4

s

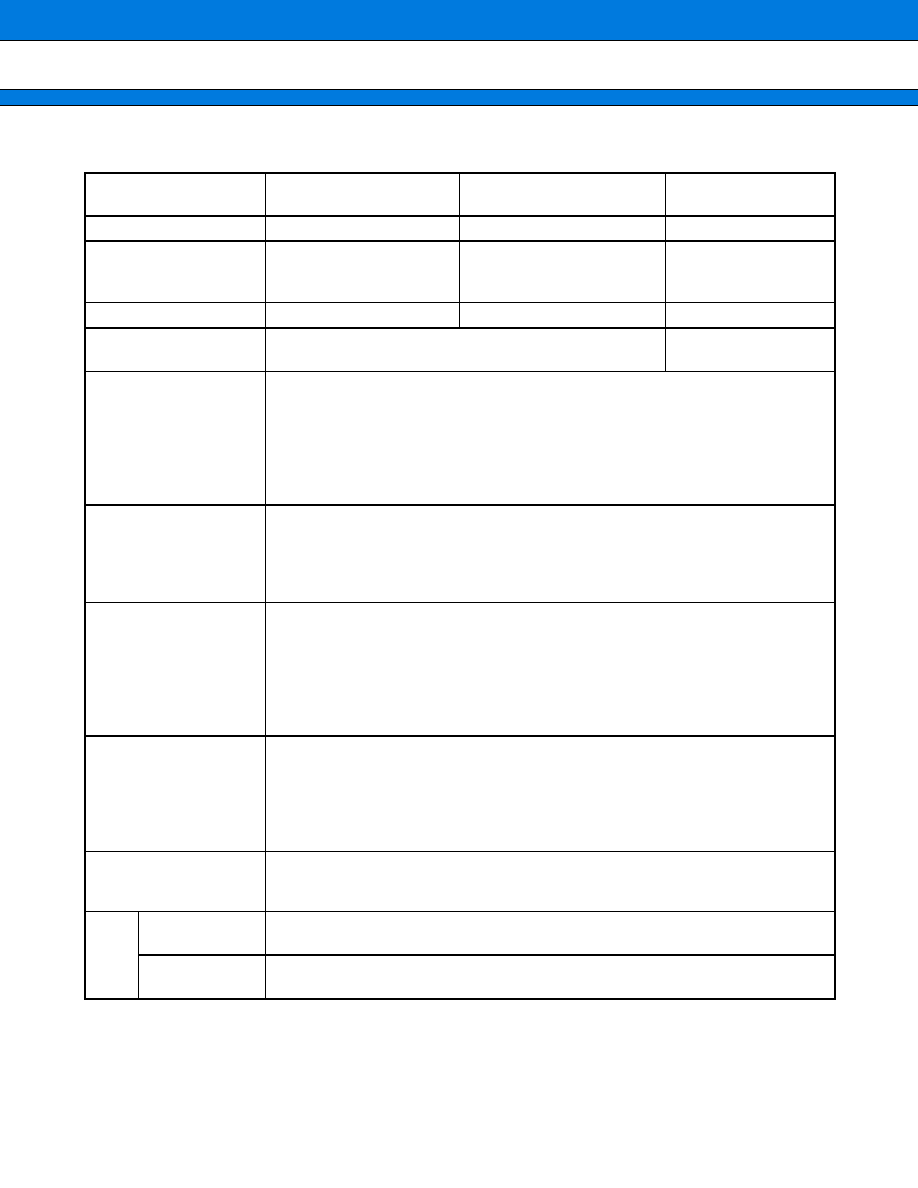

PRODUCT LINEUP

(Continued)

Features

MB90591/591G/594/594G

MB90F591A/F591G/

F594A/F594G

MB90V590A/V590G

Classification

Mask ROM product

Flash ROM product

Evaluation product

ROM size

384/256 Kbytes

384/256 Kbytes

Boot block

Hard-wired reset vector

None

RAM size

8/6 Kbytes

8/6 Kbytes

8 Kbytes

Emulator-specific power

supply *

1

None

CPU functions

The number of instructions : 340

Instruction bit length : 8 bits, 16 bits

Instruction length : 1 byte to 7 bytes

Data bit length : 1 bit, 8 bits, 16 bits

Minimum execution time : 62.5 ns (at machine clock frequency of 16 MHz)

Interrupt processing time : 1.5

µ

s

(at machine clock frequency of 16 MHz, minimum value)

UART (3 channels)

Clock synchronized transmission (500 Kbps / 1 Mbps / 2 Mbps)

Clock asynchronized transmission (4808/5208/9615/10417/19230/38460/62500

/500000 bps at machine clock frequency of 16 MHz)

Transmission can be performed by bi-directional serial transmission or by master/

slave connection.

8/10-bit A/D converter

Conversion precision : 8/10-bit can be selectively used.

Number of inputs : 8

One-shot conversion mode (converts selected channel once only)

Scan conversion mode (converts two or more successive channels and can program

up to 8 channels)

Continuous conversion mode (converts selected channel continuously)

Stop conversion mode (converts selected channel and stop operation repeatedly)

8/16-bit PPG timers

(6 channels)

Number of channels : 6 (8/16-bit

◊

6 channels)

PPG operation of 8-bit or 16-bit

A pulse wave of given intervals and given duty ratios can be output.

Pulse interval : fsys, fsys/2

1

, fsys/2

2

, fsys/2

3

, fsys/2

4

, 128

µ

s

(at oscillation of 4 MHz, fsys

=

system clock frequency of 16 MHz, fosc = oscillation

clock frequency)

16-bit Reload timer

Number of channels : 2

Operation clock frequency : fsys/2

1

, fsys/2

3

, fsys/2

5

(fsys = System clock frequency)

Supports External Event Count function

16-bit

I/O

timer

16-bit

Output compares

Number of channels : 6 (8/16-bit

◊

6 channels)

Pin input factor : A match signal of compare register

Input captures

Number of channels : 6

Rewriting a register value upon a pin input (rising, falling, or both edges)

MB90590/590G Series

5

(Continued)

*1 : It is setting of DIP switch S2 when Emulation pod (MB2145-507) is used.

Please refer to the MB2145-507 hardware manual (2.7 Emulator-specific Power Pin) about details.

*2 : Varies with conditions such as the operating frequency. (See section "

s

Electrical Characteristics.")

Features

MB90591/591G/594/594G

MB90F591A/F591G/

F594A/F594G

MB90V590A/V590G

CAN Interface

Number of channels : 2

Conforms to CAN Specification Version 2.0 Part A and B

Automatic re-transmission in case of error

Automatic transmission responding to Remote Frame

Prioritized 16 message buffers for data and ID's

Supports multiple messages

Flexible configuration of acceptance filtering :

Full bit compare / Full bit mask / Two partial bit masks

Supports up to 1Mbps

CAN bit timing setting :

MB90xxx : TSEG2

RSJW

+

2TQ

MB90xxxG : TSEG2

RSJW

Stepping motor controller

(4 channels)

Four high current outputs for each channel

Synchronized two 8-bit PWM's for each channel

External interrupt circuit

Number of inputs : 8

Started by a rising edge, a falling edge, an "H" level input, or an "L" level input.

Sound generator

8-bit PWM signal is mixed with tone frequency from 8-bit reload counter

PWM frequency : 62.5K, 31.2K, 15.6K, 7.8KHz (at System clock = 16MHz)

Tone frequency

:

PWM frequency / 2 / (reload value + 1)

Extended I/O serial

interface

Clock synchronized transmission (31.25K/62.5K/125K/500K/1Mbps at machine clock

frequency of 16 MHz)

LSB first/MSB first

Clock timer

Directly operates with the system clock

Read/Write accessible Second/Minute/Hour registers

Watchdog timer

Reset generation interval : 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms

(at oscillation of 4 MHz, minimum value)

Flash Memory

Supports automatic programming, Embedded Algorithm

TM

and

Write/Erase/Erase-Suspend/Resume commands

A flag indicating completion of the algorithm

Hard-wired reset vector available in order to point to a fixed boot sector in Flash

Memory

Boot block configuration

Erase can be performed on each block

Block protection with external programming voltage

Flash Writer from Minato Electronics Inc.

Low-power consumption

(stand-by) mode

Sleep/stop/CPU intermittent operation/clock timer/hardware stand-by

Process

CMOS

Power supply voltage for

operation*

2

5 V

±

10 % (MB90V590A, MB90F594A, MB90594, MB90V590G,

MB90F594G, MB90594G)

5 V

±

5 % (MB90F591G, MB90591G, MB90F591A, MB90591)

Package

QFP-100

PGA-256