| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MB1504 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DS04≠21301≠5E

DATA SHEET

1

Copyright

©

1994 by FUJITSU LIMIED

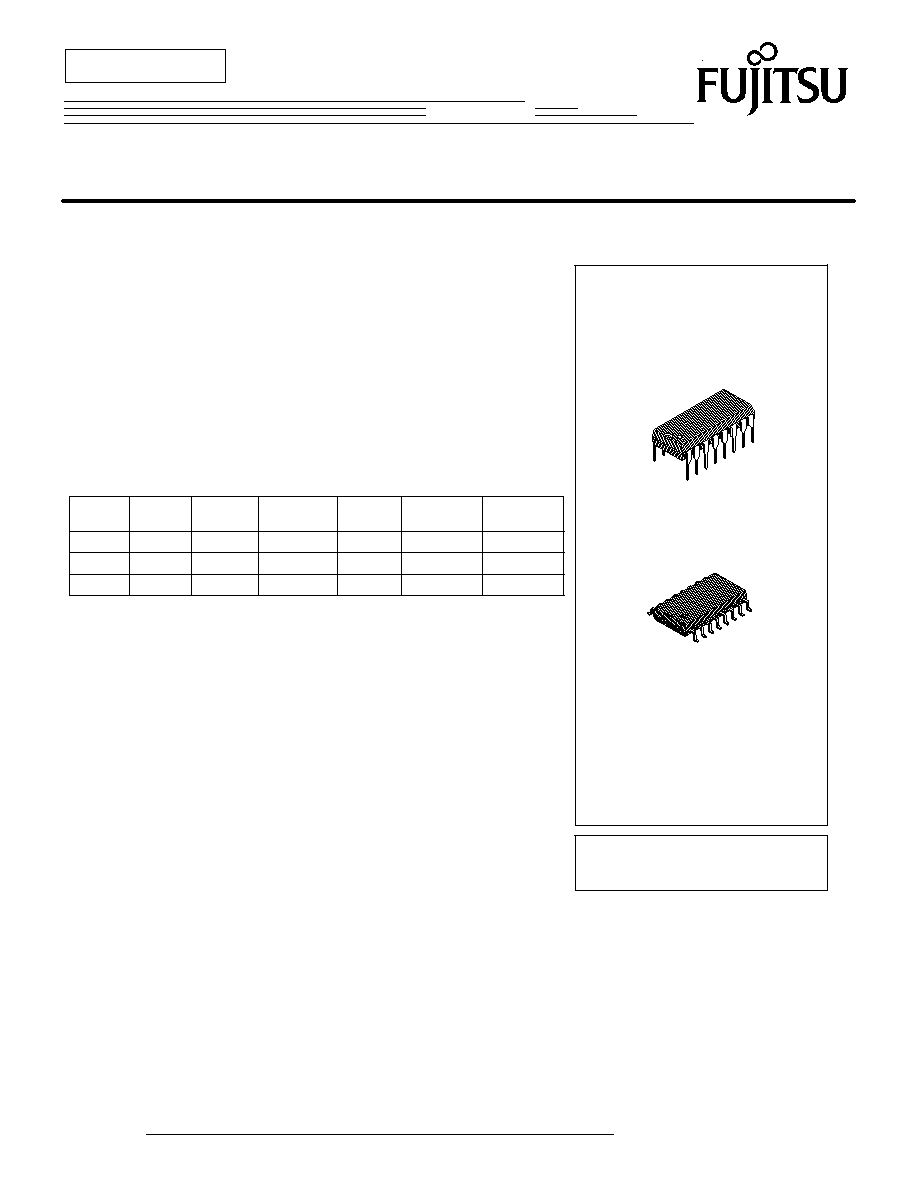

ASSP SERIAL INPUT PLL FREQUENCY SYNTHESIZER

MB1504/MB1504H/MB1504L

This device contains circuitry to protect the inputs against

damage due to high static voltages or electric fields. How-

ever, it is advised that normal precautions be taken to avoid

application of any voltage higher than maximum rated volt-

ages to this high impedance circuit.

PLASTIC PACKAGE

FPT-16P-M06

SERIAL INPUT PLL FREQUENCY SYNTHESIZER

WITH 520MHz PRESCALER

The Fujitsu MB1504/MB1504H/MB1504L, utilizing BI-CMOS technology, is a single chip

serial input PLL frequency synthesizer with pulse-swallow function.

The MB1504 series contains a 520MHz two modulus prescaler that can select either 32/33

or 64/65 divide ratio; control signal generator; 16-bit shift register; 15-bit latch;

programmable reference divider (binary 14-bit programmable reference counter); 1-bit

switch counter; phase comparator with phase inverse function; charge pump; crystal

oscillator; 19-bit shift register; 18-bit latch; and a programmable divider (binary 7-bit

swallow counter and binary 11-bit programmable counter).

The MB1504 operates from a low supply voltage (3V typ) and consumes low power (30mW

at 520MHz).

FEATURES

∑

High operating frequency: f

IN MAX

=520MHz (V

IN MIN

=0.20V

P-P

)

∑

On-chip prescaler

∑

Low power supply voltage: 2.7V to 5.5V (3.0V typ)

∑

Low power supply consumption: 30mW (3.0V, 520MHz operation)

∑

Serial input 18-bit programmable divider consisting of:

≠Binary 7-bit swallow counter (Divide ratio: 0 to 127)

≠Binary 11-bit programmable counter (Divide ratio: 16 to 2047)

∑

Serial input 15-bit programmable reference divider consisting of:

≠Binary 14-bit programmable reference counter (Divide ratio: 8 to 16383)

≠1-bit switch counter (SW) Sets divide ratio of prescaler

∑

2 types of phase detector output

≠On-chip charge pump (Bipolar type)

≠Output for external charge pump

∑

Wide operating temperature: T

A

=≠40

_

C to +85

_

C

PLASTIC PACKAGE

DIP-16P-M04

MB1504

MB1504L

MB1504H

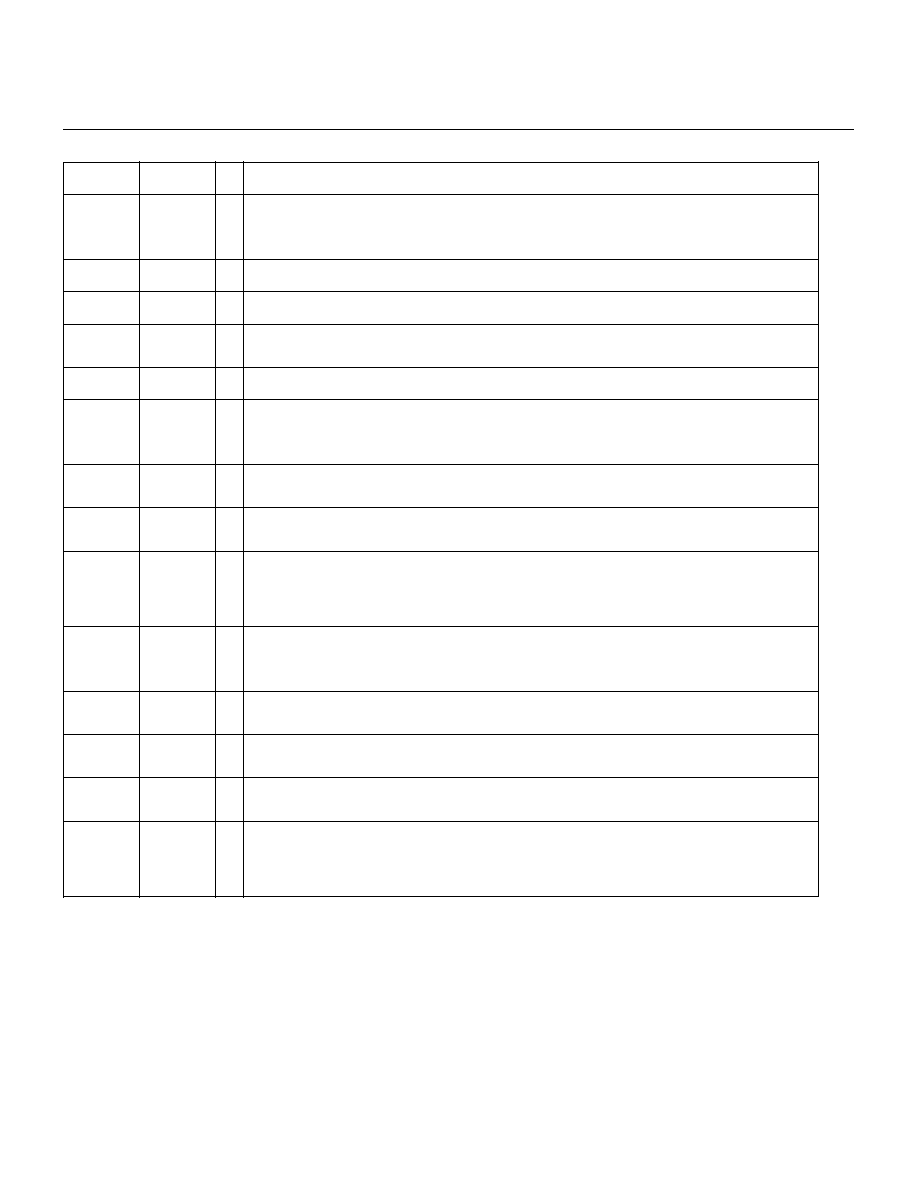

V

P

Voltage

V

OOP

Voltage

Lock up Time

D

O

Output

Width

High-level

Output Current

Low-level

Output Current

8V max

10V max

8V max

8.5V max

10.0V max

8.5V max

Middle speed

High speed

Low speed

Middle

Low

High

Middle

High

Low

Middle

Low

High

MB1504 Product Line

MB1504

MB1504H

MB1504L

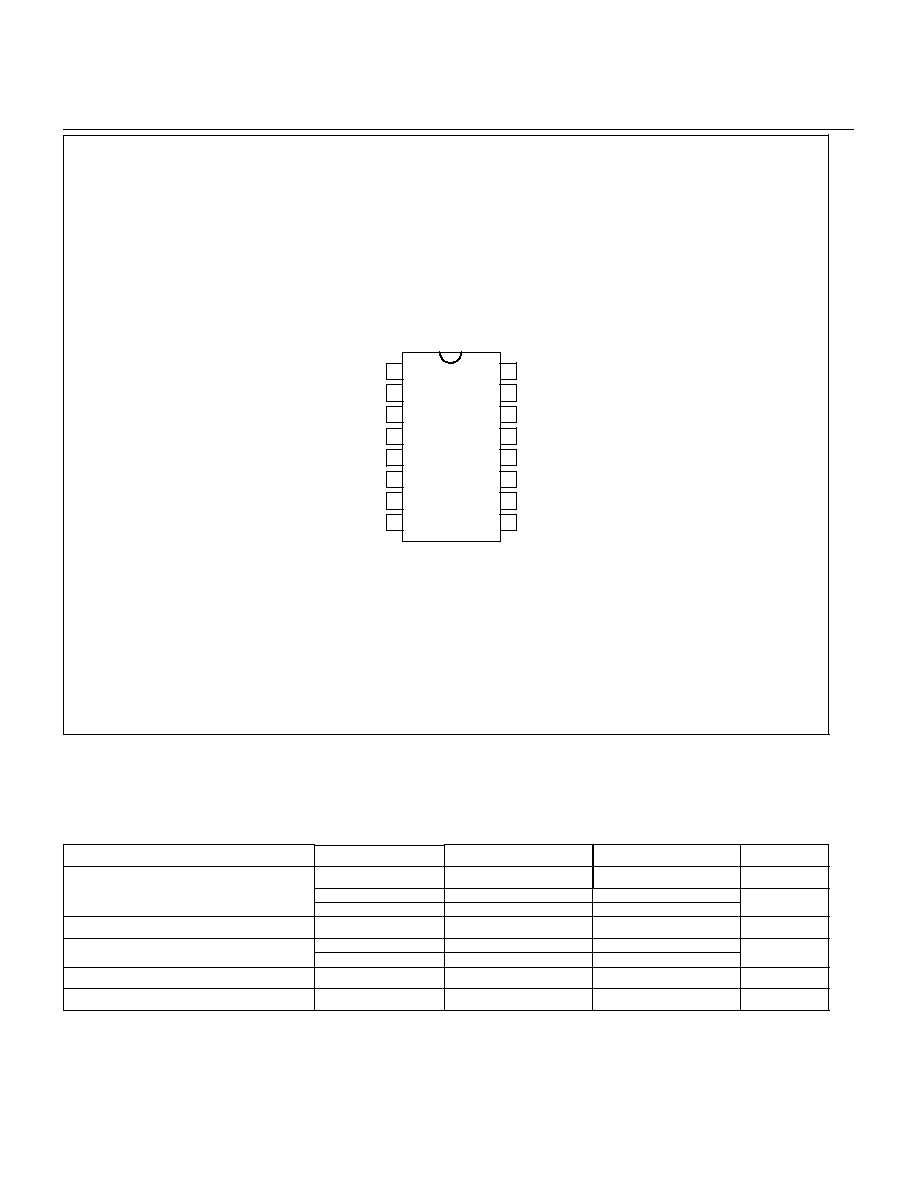

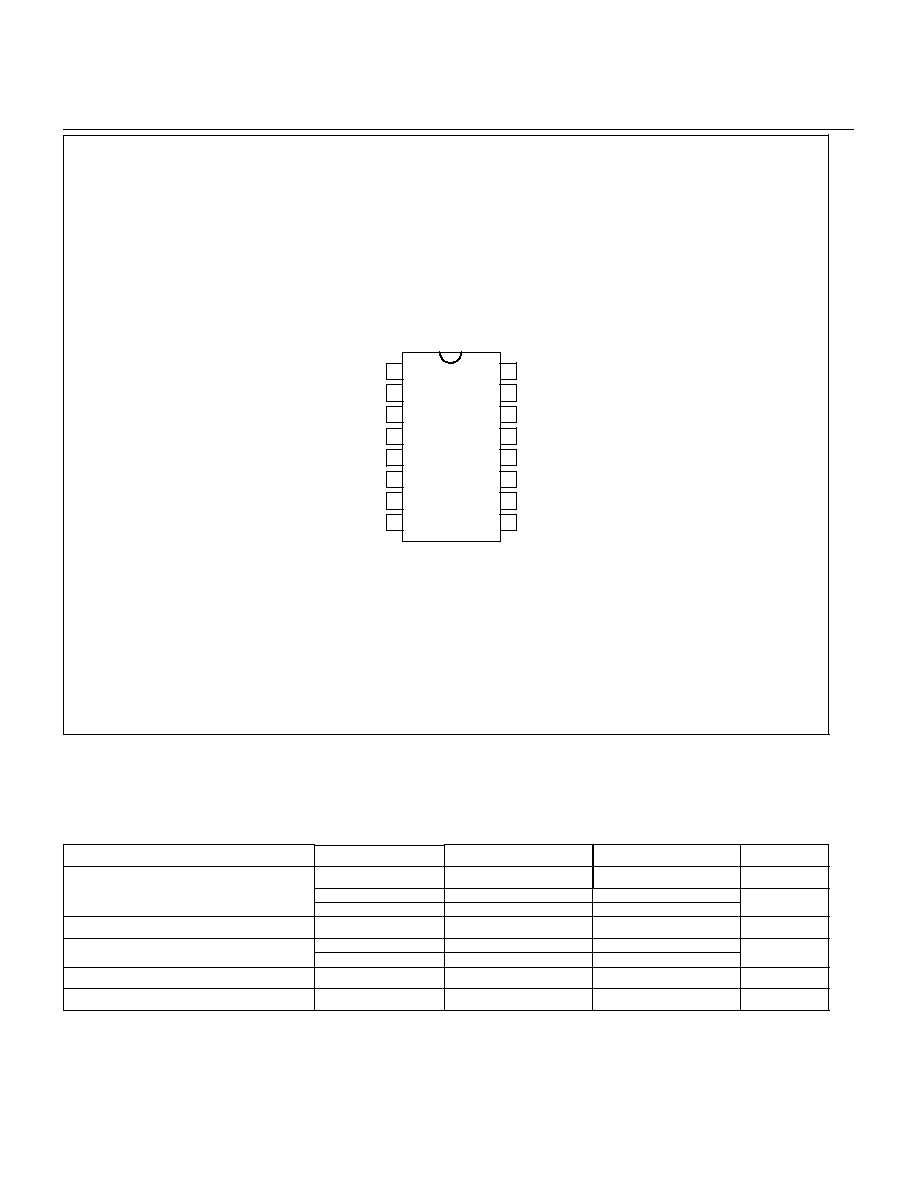

2

MB1504H

MB1504/1504L

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

OSC

IN

OSC

OUT

V

P

V

CC

D

O

GND

LD

f

in

ÿR

ÿP

f

P

f

r

FC

LE

Data

Clock

( TOP VIEW )

PIN ASSIGNMENT

ABSOLUTE MAXIMUM RATINGS (see NOTE)

Rating

Power Supply Voltage

Symbol

Value

Unit

NOTE:

Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted

to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended

periods may affect device reliability.

Output Voltage

Output Current

V

CC

I

OUT

mA

V

PH

+

10

V

V

T

STG

∞

C

Storage Temperature

≠55 to +125

Open-drain Output

V

V

OUT

V

≠0.5 to +7.0

V

CC

to 12.0

≠0.5 to V

CC

+0.5

Condition

V

P

,V

PL

V

CC

to 10.0

V

OOPH

≠0.5 to 11.0

V

OOP

,V

OOPL

MB1504H

MB1504/1504L

≠0.5 to 9.0

--

--

--

--

MB1504

MB1504H

MB1504L

3

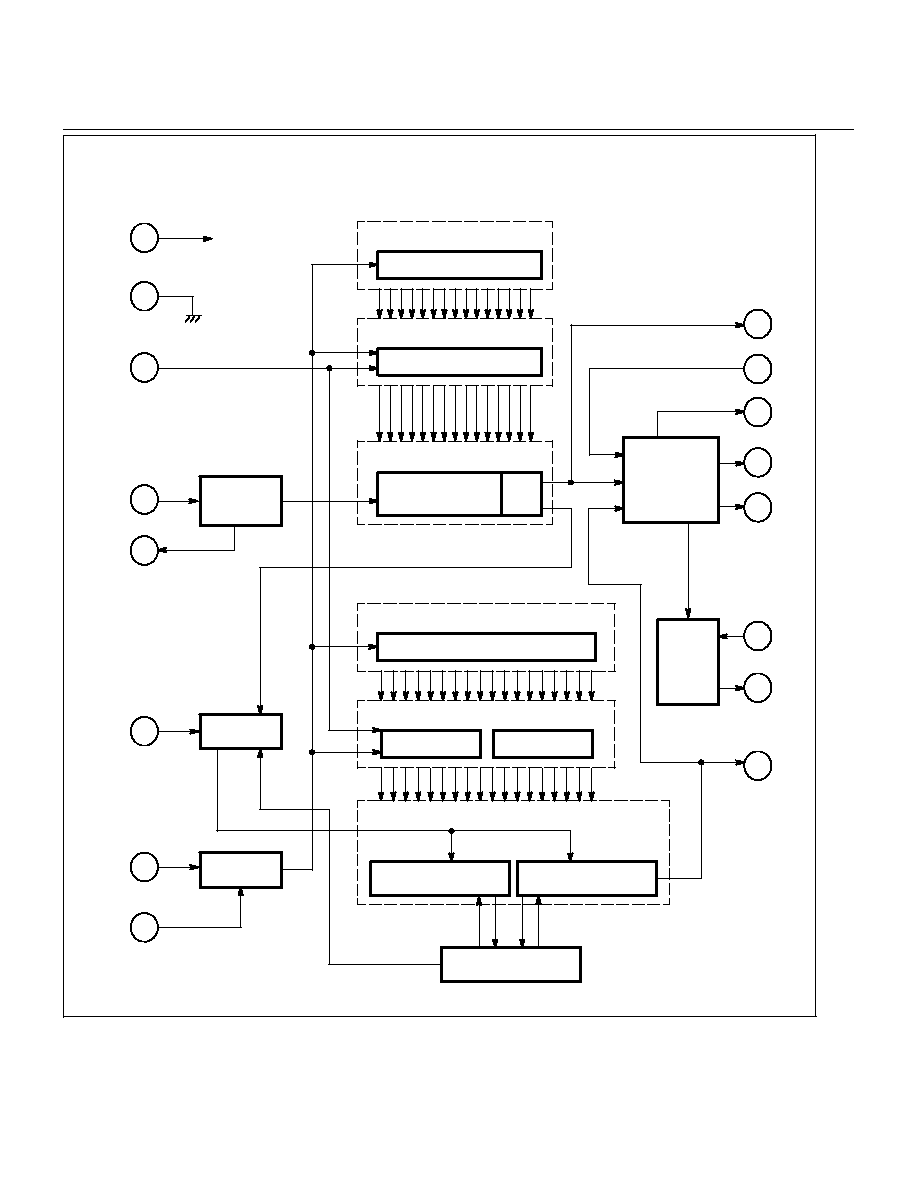

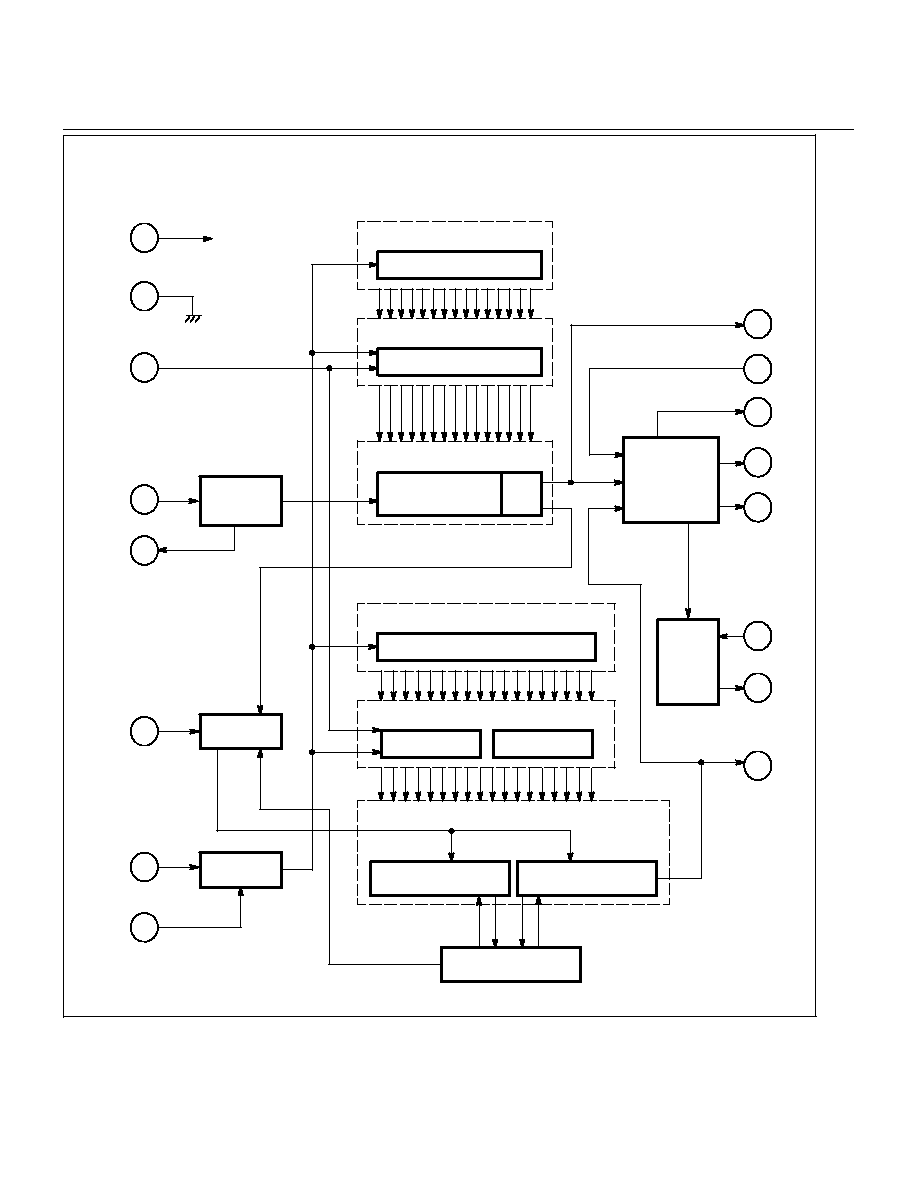

MB1504/MB1504H/MB1504L BLOCK DIAGRAM

4

6

V

CC

GND

16-Bit Shift Register

16-Bit Shift Register

15-Bit Latch

15-Bit Latch

11

LE

Programmable

Reference Divider

Binary 14-Bit

Reference Counter

1-bit

SW

Crystal

Oscillator

Circuit

OSC

IN

1

OSC

OUT

2

19-Bit Shift Register

19-Bit Shift Register

18-Bit Latch

7-Bit Latch

11-Bit Latch

Programmable Divider

Control Circuit

Binary 7-Bit

Swallow Counter

Binary 11-Bit

Programmable Counter

10

Data

Control

1-Bit Latch

Prescaler

Circuit

9

Clock

8

f

IN

Phase

Comparator

Charge

Pump

f

r

FC

LD

ÿR

ÿP

15

16

7

12

13

D

O

5

14

V

P

3

f

P

MB1504

MB1504H

MB1504L

4

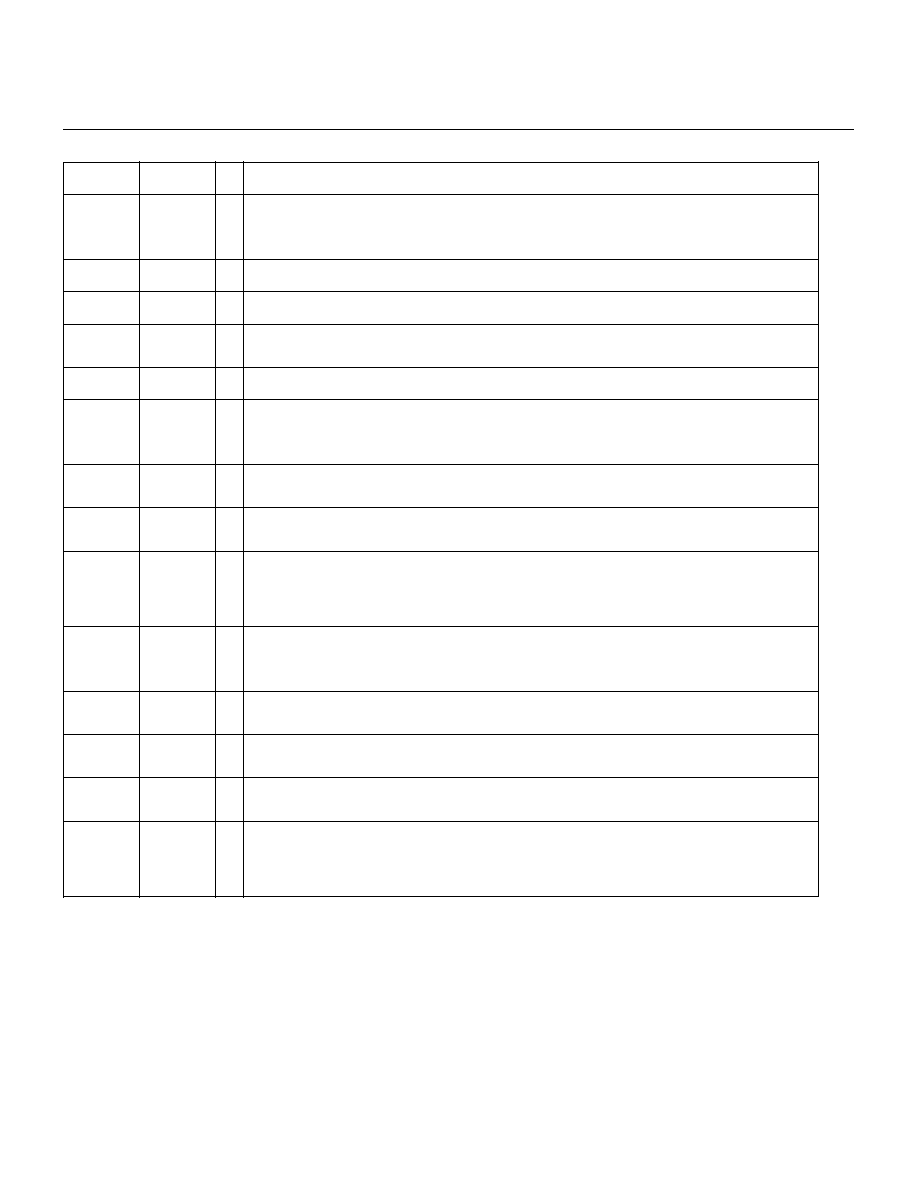

PIN DESCRIPTIONS

Pin No.

Pin Name

Descriptions

1

2

3

OSC

IN

V

P

Oscillator input

Oscillator output

A crystal is placed between OSC

IN

and OSC

OUT

.

Power supply input for charge pump

4

V

CC

Power supply voltage input

OSC

OUT

D

O

5

Charge pump output

The phase characteristics can be inversed depending upon the FC input.

6

GND

Ground

LD

Phase comparator output

This pin outputs high when the phase is locked. While the phase difference of f

r

and f

p

exists, the output

level goes low.

f

IN

Prescaler input

The connection with an external VCO should be an AC connection.

7

8

Clock

9

Clock input for 19-bit shift register and 16-bit shift register

Each rising edge of the clock shifts one bit of data into the shift registers.

Serial data of binary code input

The last bit of the data is a control bit. The last data bit specifies which latch is activated.

When the last bit is high level and LE is high-level, data is transferred to the 15-bit latch.

When the last bit is low level and LE is high level, data is transferred to the 18-bit latch.

10

Data

11

LE

Load enable input (with internal pull up resistor)

When LE is high level (or open), data stored in the shift register is transferred to the latch depending on the

control data.

FC

Phase selecting input of phase comparator (with internal pull up resistor)

When FC is low level, the charge pump and phase detector characteristics can be inversed.

13

Monitor pin of phase comparator input

It is the same as the programmable reference divider output.

14

f

r

f

P

Monitor pin of phase comparator input

It is the same as the programmable divider output.

12

Outputs for external charge pump

The phase characteristics can be inversed depending on the FC input.

The ÿP pin is an N-channel open-drain output.

15

16

ÿP

ÿR

I/O

I

O

--

--

O

--

O

I

I

I

I

O

O

O

O

O

MB1504

MB1504H

MB1504L

5

FUNCTIONAL DESCRIPTIONS

SERIAL DATA INPUT

Serial data input is input using the Data pin, Clock pin and LE pin. The 15-bit programmable reference divider and 18-bit programmable divider are

controlled, respectively.

On rising edge of the clock, one bit of the data shifts into the internal shift registers.

When load enable (LE) is high level (or open), data stored in the shift registers is transferred to the 15-bit latch or 18-bit latch depending upon the control bit

level.

Control data "H" : Data is transferred into the 15-bit latch.

Control data "L" : Data is transferred into the 18-bit latch.

PROGRAMMABLE REFERENCE DIVIDER

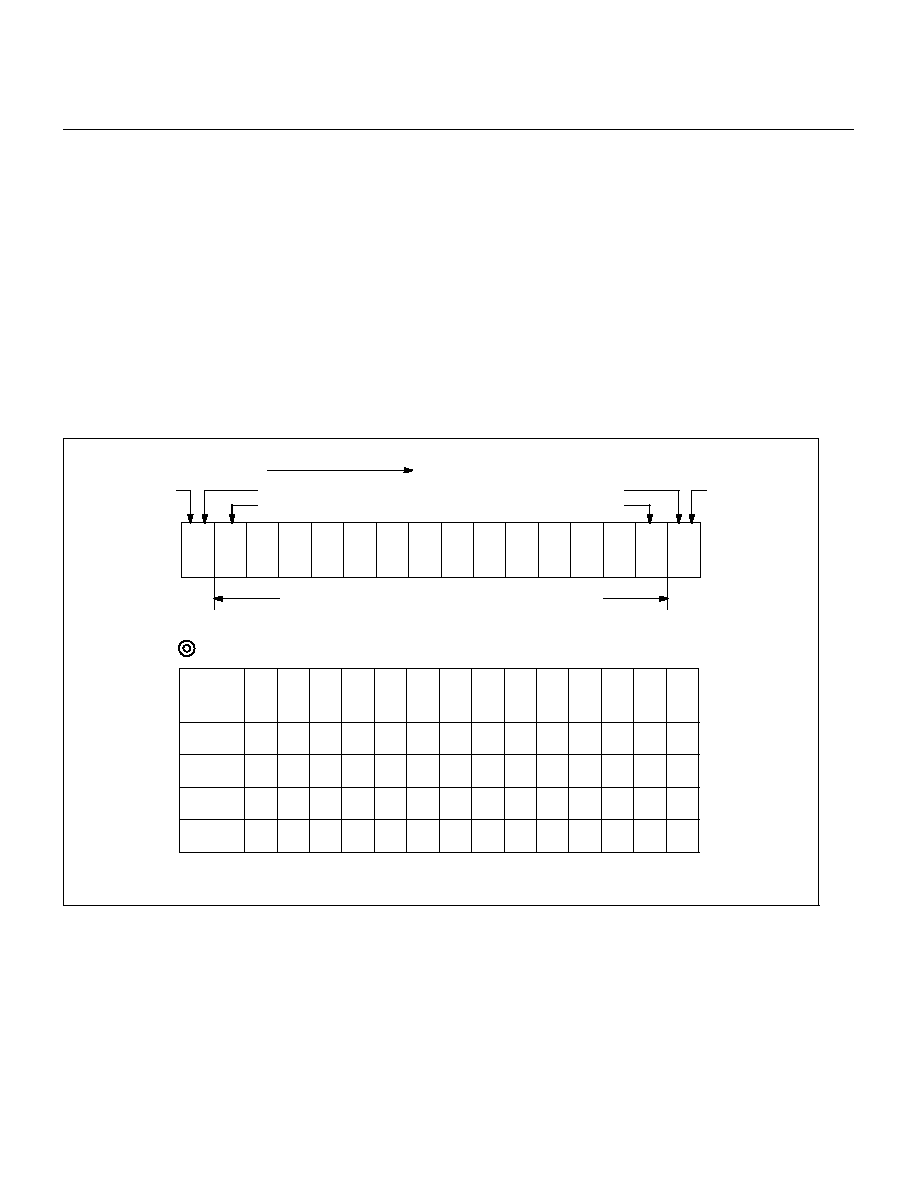

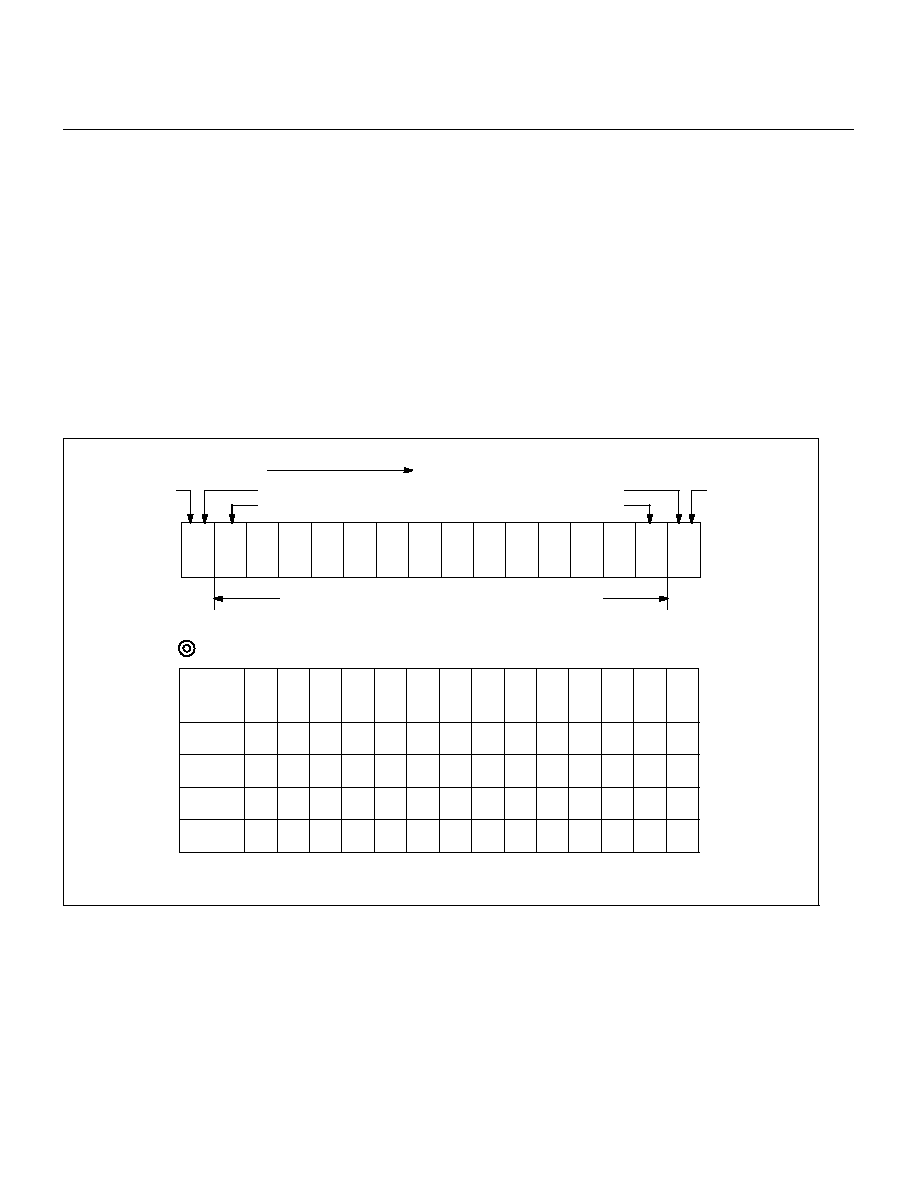

The programmable reference divider consists of a 16-bit shift register, 15-bit latch and 14-bit reference counter. Serial 16-bit data format is shown below.

1

2

3

4

S

5

S

6

S

7

S

8

S

9

S

10

S

11

12

S

S

13

S

14

SW

C

S

S

S

Control bit

LSB

Divide ratio of programmable reference counter setting bits

Divide ratio of prescaler setting bit

MSB

S

14

13

12

11

S

10

S

9

S

8

S

7

S

6

S

5

S

4

3

S

S

2

S

1

S

S

S

S

Divide

ratio

R

8

9

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

0

0

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

SW: Divide ratio of prescaler setting bit

SW="H": 32

SW="L" : 64

S

1

to S

14

: Divide ratio of programmable reference counter setting bits (8 to 16383)

C: Control bit (control bit is set to high)

14-BIT PROGRAMMABLE REFERENCE COUNTER DIVIDE RATIO

First data input

Last data input

Data input

Divide ratio less than 8 is prohibited

Divide ratio R: 8 to 16383

16383

1

1

1

1

1

1

1

1

1

1

1

1

1

1