DS05-50211-1E

FUJITSU SEMICONDUCTOR

DATA SHEET

Stacked MCP (Multi-Chip Package) FLASH MEMORY & SRAM

CMOS

64M (

◊

8/

◊

16) FLASH MEMORY &

8M (

◊

8/

◊

16) STATIC RAM

MB84VD23280EA

-90

/MB84VD23280EE

-90

s

FEATURES

∑ Power supply voltage of 2.7 V to 3.3 V

∑ High performance

90 ns maximum access time (Flash)

70 ns maximum access time (SRAM)

∑ Operating Temperature

≠25

∞

C to +85

∞

C

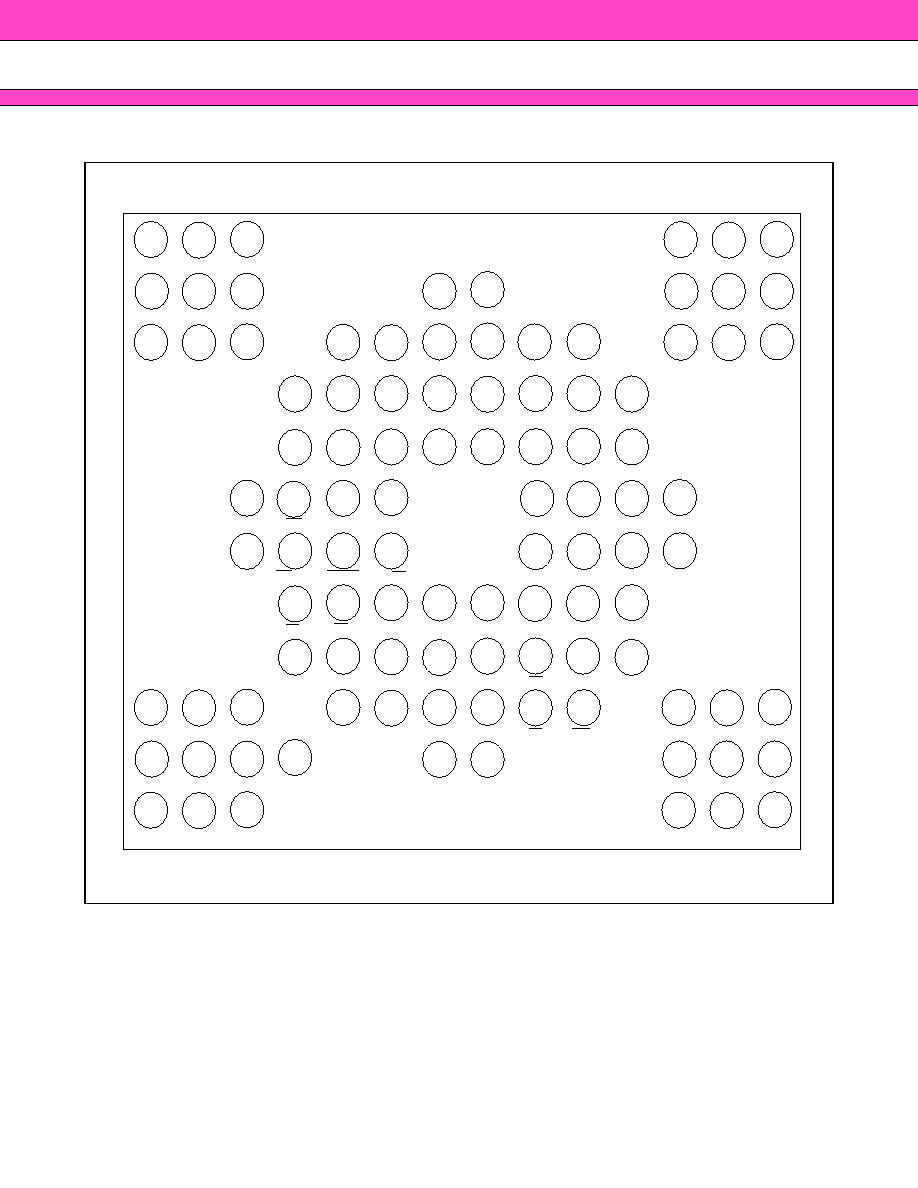

∑ Package 101-ball BGA

(Continued)

s

PRODUCT LINEUP

s

PACKAGE

Flash Memory

SRAM

Ordering Part No.

V

CC

f, V

CC

s = 3.0 V

MB84VD23280EA-90/MB84VD23280EE-90

Max. Address Access Time (ns)

90

70

Max. CE Access Time (ns)

90

70

Max. OE Access Time (ns)

35

35

101-pin plastic FBGA

BGA-101P-M01

+0.3V

≠0.3 V

MB84VD23280EA-90/MB84VD23280EE-90

2

(Continued)

-- FLASH MEMORY

∑ Simultaneous Read/Write operations (flex bank)

Two virtual Banks are chosen from the combination of four physical banks

Host system can program or erase in one bank, then read immediately and simultaneously read from the other

bank between read and write operations

Read-while-erase

Read-while-program

∑ Minimum 100,000 write/erase cycles

∑ Sector erase architecture

Sixteen 4 K words and one hundred twenty-six 32 K word.

Any combination of sectors can be concurrently erased. Also supports full chip erase.

∑ Embedded Erase

TM

* Algorithms

Automatically pre-programs and erases the chip or any sector

∑ Embedded Program

TM

* Algorithms

Automatically writes and verifies data at specified address

∑ Data Polling and Toggle Bit feature for detection of program or erase cycle completion

∑ Ready-Busy output (RY/BY)

Hardware method for detection of program or erase cycle completion

∑ Automatic sleep mode

When addresses remain stable, automatically switch themselves to low power mode.

∑ Low V

CC

write inhibit

2.5 V

∑ Hidden ROM (Hi-ROM) region

256 byte of Hi-ROM, accessible through a new "Hi-ROM Enable" command sequence

Factory serialized and protected to provide a secure electronic serial number (ESN)

∑ WP/ACC input pin

At V

IL

, allows protection of 2 of 8 Kbytes on both ends of each boot sector, regardless of sector protection/

unprotection status.

At V

IH

, allows removal of boot sector protection

At V

ACC

, increases program performance

∑ Program Suspend/Resume

Suspends the program operation to allow a read in another address

∑ Erase Suspend/Resume

Suspends the erase operation to allow a read in another sector within the same device

∑ Please refer to "MBM29DL640E" data sheet in detailed function

-- SRAM

∑ Power dissipation

Operating : 50 mA Max.

Standby : 25

µ

A Max.

∑ Power down features using CE1s and CE2s

∑ Data retention supply voltage: 1.5 V to 3.3 V

∑ CE1s and CE2s Chip Select

∑ Byte data control: LBs (DQ

7

-DQ

0

), UBs (DQ

15

-DQ

8

)

*: Embedded Erase

TM

and Embedded Program

TM

are trademarks of Advanced Micro Devices, Inc.

MB84VD23280EA-90/MB84VD23280EE-90

4

s

s

s

s

PIN DESCRIPTION

Pin name

Input/

Output

Description

A

18

to A

0

I

Address Inputs (Common)

A

21

to A

19

, A

≠1

I

Address Inputs (Flash)

SA

I

Address Input (SRAM)

DQ

15

to DQ

0

I/O

Data Inputs/Outputs (Common)

CEf

I

Chip Enable (Flash)

CE1s

I

Chip Enable (SRAM)

CE2s

I

Chip Enable (SRAM)

OE

I

Output Enable (Common)

WE

I

Write Enable (Common)

RY/BY

O

Ready/Busy Output (Flash) Open Drain Output

UBs

I

Upper Byte Control (SRAM)

LBs

I

Lower Byte Control (SRAM)

CIOf

I

I/O Configuration (Flash)

CIOf = V

IH

is Word mode (◊16), CIOf = V

IL

is Byte mode (◊8)

CIOs

I

I/O Configuration (SRAM)

CIOs = V

IH

is Word mode (◊16), CIOs = V

IL

is Byte mode (◊8)

RESET

I

Hardware Reset Pin/Sector Protection Unlock (Flash)

WP/ACC

I

Write Protect / Acceleration (Flash)

N.C.

--

No Internal Connection

V

SS

Power

Device Ground (Common)

V

CC

f

Power

Device Power Supply (Flash)

V

CC

s

Power

Device Power Supply (SRAM)