| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MB86698A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Product Flyer

March 1999

MB86698

Version 1.1

FireStreamTM155G

ATM 155Mbps SAR Device

FML/NPD/FS155G/FL/2131

Copyright © 1999 Fujitsu Microelectronics Limited

Page 1 of 7

The FireStream155G is a high performance ATM protocol

controller which autonomously terminates ATM Adaptation

Layer standard Type 5 (AAL5). ATM cells are passed via a

UTOPIA v2.01 compliant interface. Access to system

memory is through a 50MHz generic bus interface to achieve

simultaneous segmentation and reassembly at an average

rate in excess of 155Mbps.

All ATM Forum traffic classes (ABR, VBR, CBR, UBR) are

supported with traffic management to ATM Forum TM4.0

specification on up to 65536 virtual circuits (VCs).

The device is ideally suited to many ATM applications

including ATM switches, access units, adaptor cards, multi-

protocol hubs, bridges and routers.

Features

∑

Broadband ISDN Adaptation Layer standard Type 5 (AAL5)

∑

Simultaneous segmentation and reassembly on up to 64K VCs

∑

ABR, VBR, UBR and CBR traffic classes with traffic management compliant to TM4.0

∑

Autonomous Resource Management (RM) cell handling

∑

50MHz 32-bit Generic Bus interface compatible with Intel i960 and Motorola 860 buses

∑

Write-only interface for PDU handling with copy of SAR registers maintained in host memory

∑

Configuration through Generic Bus slave port

∑

Transparent ATM cell and cell payload modes (AAL0) with support for Operations and Maintenance

(OAM) cells

∑

8/16-bit, up to 52MHz UTOPIA v2.01 level 1 and level 2 compliant cell stream interface with master/

slave modes and optional HEC checking on receive

∑

Flexible routing tag append / remove mode for direct ATM Switch connection

∑

32-bit Local memory port connects directly to low cost SRAM

∑

JTAG compliant to IEEE1149.1

∑

Fabricated in CMOS technology with CMOS/TTL compatible 5V tolerant I/O and a 3.3V power supply

∑

-40

∞

C to +85

∞

C Industrial temperature range

PLASTIC PACKAGE

HQFP240

March 1999 Version 1.1

FML/NPD/FS155G/FL/2131

MB86698 FireStreamTM155G

Copyright © 1999 Fujitsu Microelectronics Limited

Page 2 of 7

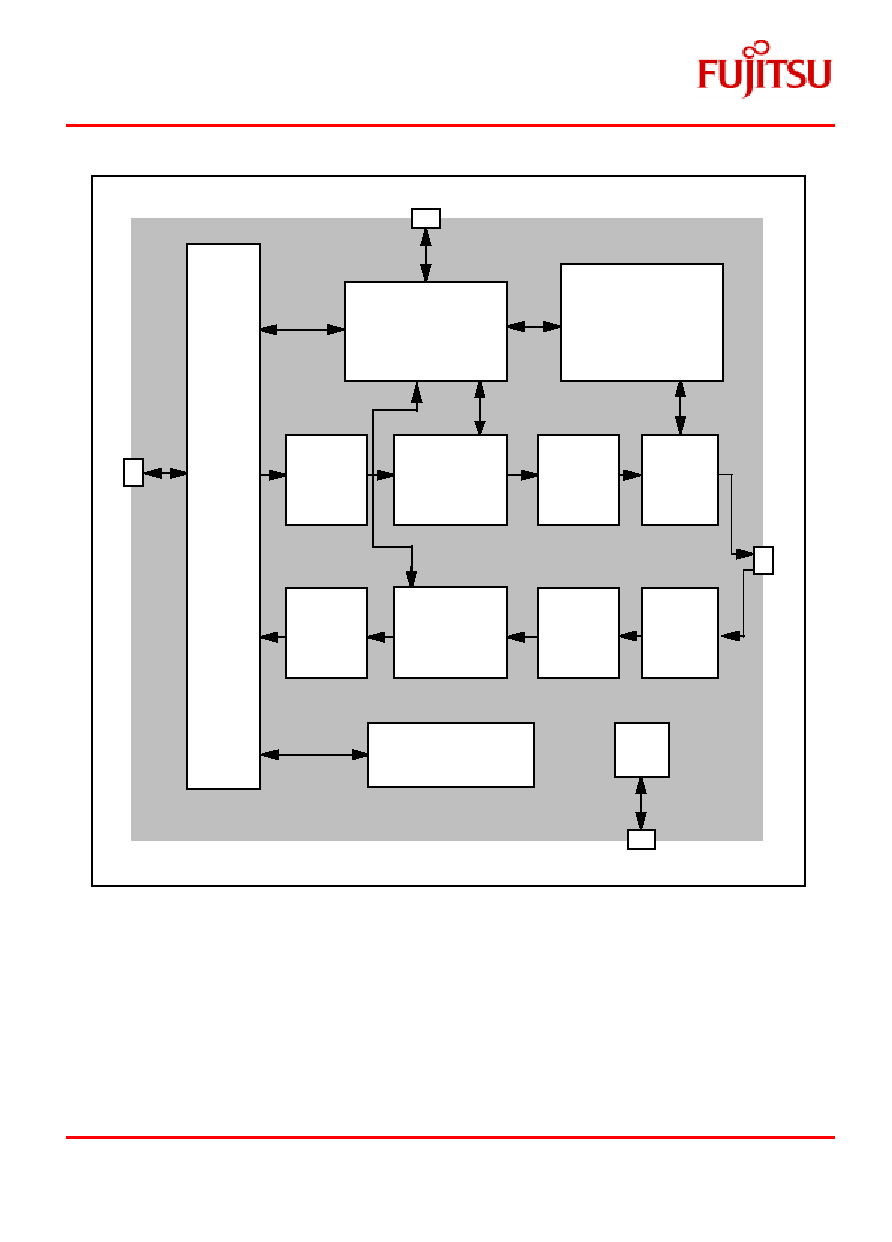

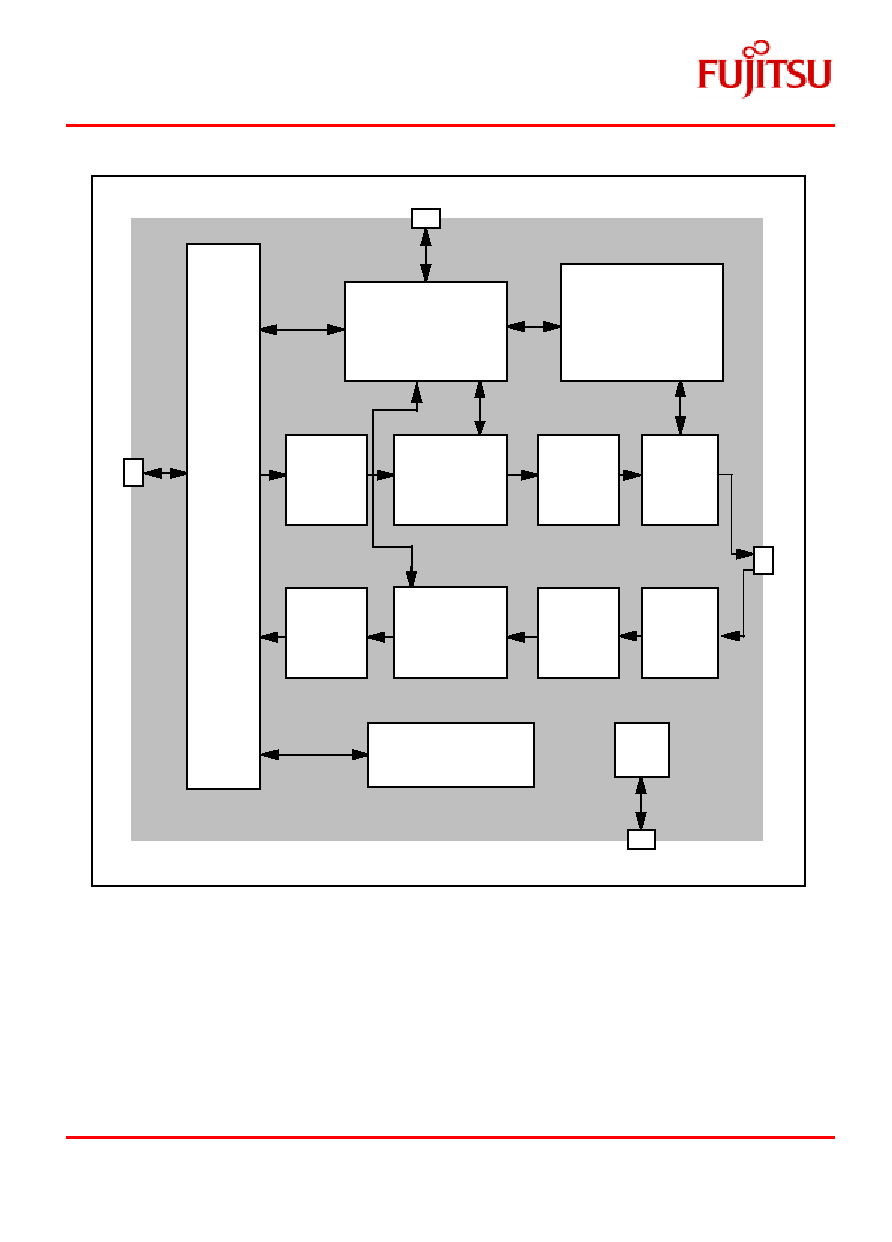

Figure 1: FireStream155G block diagram

General

The FireStream155G simultaneously supports autonomous segmentation and

reassembly of user data packets on up to 64K virtual circuits (VCs). User data

packets are transferred to and from shared data structure memory using a high

speed 32-bit Generic (Intel/Motorola) multiplexed bus and transferred to and

from the network using an 8/16-bit UTOPIA interface.

High

Speed

DMA

Controller

ATM

Cell

Input

ATM

Cell

Output

Cell Input

Buffer

(3Cells)

Receive

Buffer

(96 Cells)

Reassembly and

Convergence

Sub-layer

Controller

Cell Output

Buffer

(3 Cells)

Transmit

Buffer

(12 Cells)

Segmentation

and

Convergence

Sub-layer

Controller

Local

Memory

Controller

JTAG

Traffic

Management

Controller

Internal

Registers

JTAG Interface

Local Memory Interface

Host

Interf

ace

(Gener

ic)

UT

OPIA Interf

ace

March 1999 Version 1.1

FML/NPD/FS155G/FL/2131

MB86698 FireStreamTM155G

Copyright © 1999 Fujitsu Microelectronics Limited

Page 3 of 7

Adaptation

Layer Support

The FireStream155G autonomously terminates the protocols involved in seg-

menting and reassembling data streams conforming to ATM Adaptation Layer

(AAL) Type 5 to I.363. Streaming and Message Modes as defined for AAL5 are

supported. In Message Mode, the Convergence Sublayer payload (Service

Data Unit) is considered to be the user data transmitted from or received into a

single entity - a single entity being regarded as one user data buffer or linked

chain of user data buffers. In Streaming Mode, the Convergence Sublayer pay-

load is considered to be the user data transmitted from or received into multiple

entities separated in time. This allows a partial segmentation or reassembly.

The device recognises OAM and RM cells and separates them from the data

stream.

The FireStream155G device supports two transparent modes (AAL0) with

optional CRC-10 generation and checking. In transparent payload mode the 48

byte ATM cell payload is received or transmitted transparently into or from SAR

Memory. In transparent cell mode the complete ATM cell, excluding the HEC, is

received or transmitted transparently into or from SAR Memory.

Traffic Shaping

The FireStream155G supports autonomous traffic shaping functions for ABR,

VBR, UBR and CBR traffic. Traffic parameters are stored on a per-circuit basis

in local memory. A calendar algorithm is used for traffic scheduling and has four

priority levels which are independent of traffic type. ABR support includes

autonomous handling of RM cells. Transmitted FRM cells are dropped into the

data stream at the correct rate. Received BRM cells modify the associated VC's

traffic parameters. Received FRM cells are stored locally and automatically

rescheduled for transmission.

Local Memory

Control structures are initialised by the host and then copied by the

FireStream155G into local memory. These include circuit information such as

VP/VC values and descriptor information such as data pointers and buffer

lengths. The FireStream155G then works on the local copy of these structures

and hence does not consume any further system bandwidth. The local memory

also contains static and dynamic traffic parameters and pointers for the traffic

scheduling algorithm.

Cell Stream

Interface

The FireStream155G interfaces via a standard UTOPIA level 1 or level 2 inter-

face. This 16-bit interface which operates at up to 52MHz can be configured as

an ATM or a PHY (master or slave) device depending on the application. In rout-

ing tag modes the FireStream155G adds a programmable length routing tag to

the start of each ATM cell to allow connection to a switch matrix. The HEC is

inserted on transmit and checked on receive. A 52-byte cell option is provided

where the HEC is omitted.

March 1999 Version 1.1

FML/NPD/FS155G/FL/2131

MB86698 FireStreamTM155G

Copyright © 1999 Fujitsu Microelectronics Limited

Page 4 of 7

Generic Master

Interface

The FireStream155G has a high performance 32-bit Generic Bus master inter-

face, compatible with Intel i960 and Motorola 860 standards. The programming

interface has a "write-only" mode which minimizes bus occupancy by removing

the need for the Host to make slave read accesses.

Generic Slave

Interface

A simple slave control/status port is used to configure the device. Its function

includes the initialization of the queue structures and the monitoring of cell and

packet loss. An interrupt mechanism is implemented to indicate queue updates

and exception conditions.

Circuit

Initialization

Circuits are initialized for both transmit and receive by placing an entry on a high

or low priority Transmit Pending Queue or onto an on-chip queue. This entry

points to configuration information. A Status Queue is used to inform the user

that the operation has been completed.

Transmit

Operation

Transmit operation is initiated using a simple queue structure. A buffer contain-

ing part or all of a packet's data is scheduled by placing a Transmit Descriptor

pointer

on

the

high

or

low

priority

Transmit

Pending

Queue.

The

FireStream155G links queued descriptors for the same VC into a list. Data is

then segmented under the control of the traffic scheduler into cells. The data

pointer is contained in the Transmit Descriptor. When a buffer is exhausted it is

returned to the host by putting the Transmit Descriptor pointer on a Release

Queue.

Receive

Operation

On receiving ATM cells the FireStream155G takes a buffer from one of eight

simple Buffer Free Pools. Each pool forms a linked list and buffers are allocated

to the device by linking Receive Descriptors onto the list. Each pool may use a

different buffer size. Receive Circuits can be allocated to one of these pools.

Alternatively the device may be configured so that Receive Circuits use an initial

buffer from one pool followed by subsequent buffers from another pool to reas-

semble a packet. This maximizes memory efficiency. Receive Circuits can have

a low-priority discard mode where free buffers will not be allocated while the

number of free entries is below a programmable threshold. This improves

robustness of the system under heavy receive traffic loading by preventing the

free pools under running. When buffers are completed they are returned to the

host by putting the Receive Descriptor identifier on one of four Buffer Ready

Queues.

JTAG

A JTAG port Boundary Scan port provides support for PCB production test.

March 1999 Version 1.1

FML/NPD/FS155G/FL/2131

MB86698 FireStreamTM155G

Copyright © 1999 Fujitsu Microelectronics Limited

Page 5 of 7

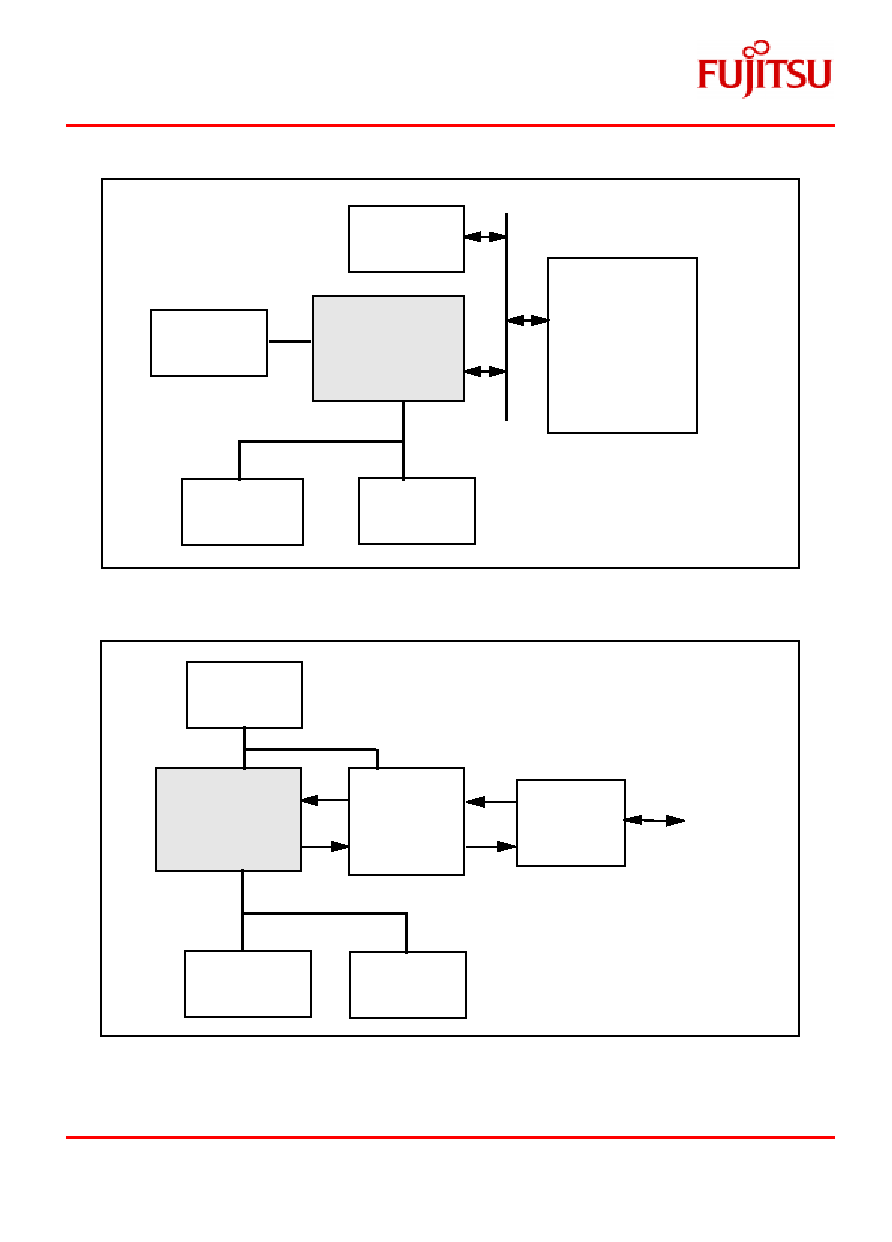

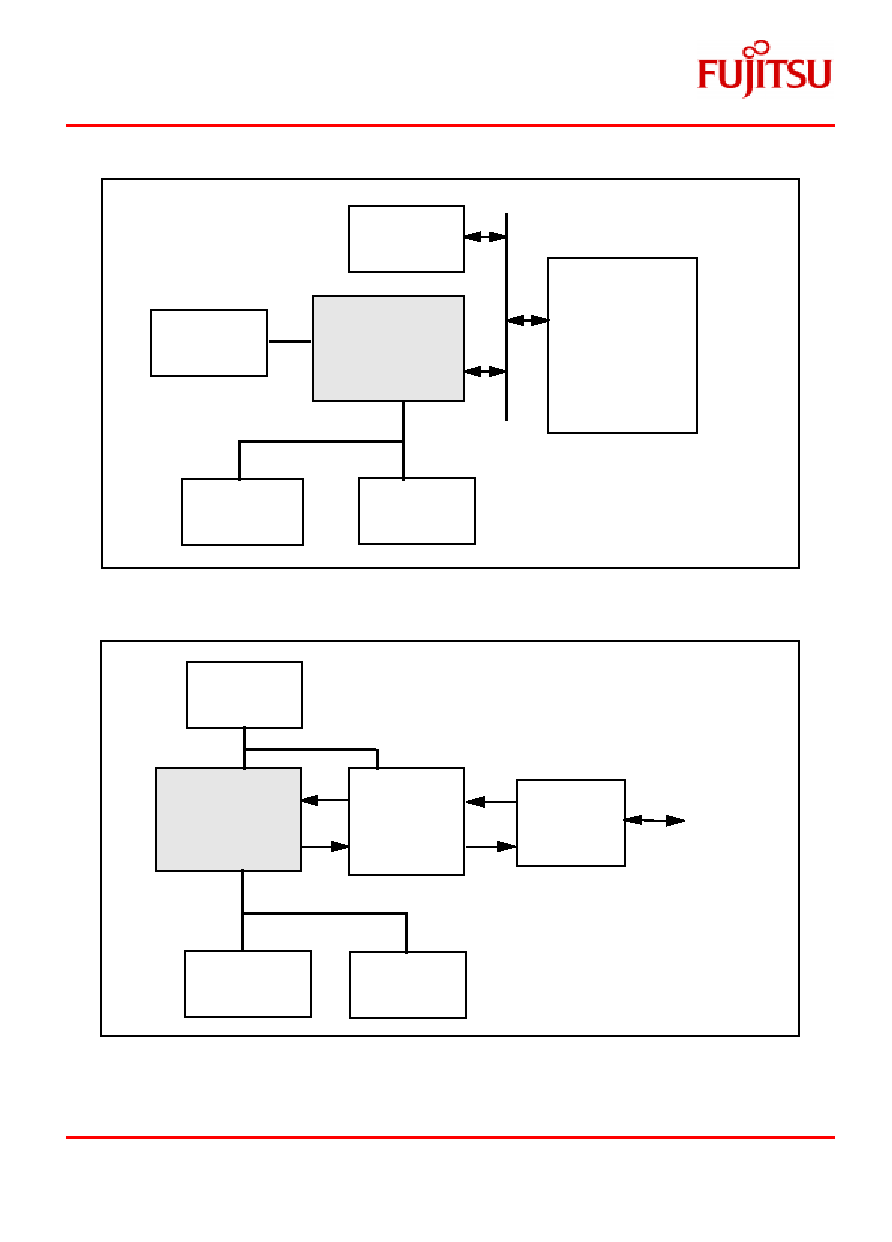

Figure 2: ATM Switch Port designed around the FireStream155G

Figure 3: ATM Terminal Equipment based around the FireStream155G

Switch Matrix

Host CPU

System Memory

Local Memory

FireStream155G

MB86698

FireStream155G

UTOPIA interface in Slave

Mode shares switch port

with PHY devices

PHY device

FireBurst155

Intel/Motorola

Local Memory

FireStream155G

MB86698

PHY Device

Line Driver

&

Receive

Equalisation

User Network

Interface

(UNI)

System Memory

Host CPU

Intel/Motorola