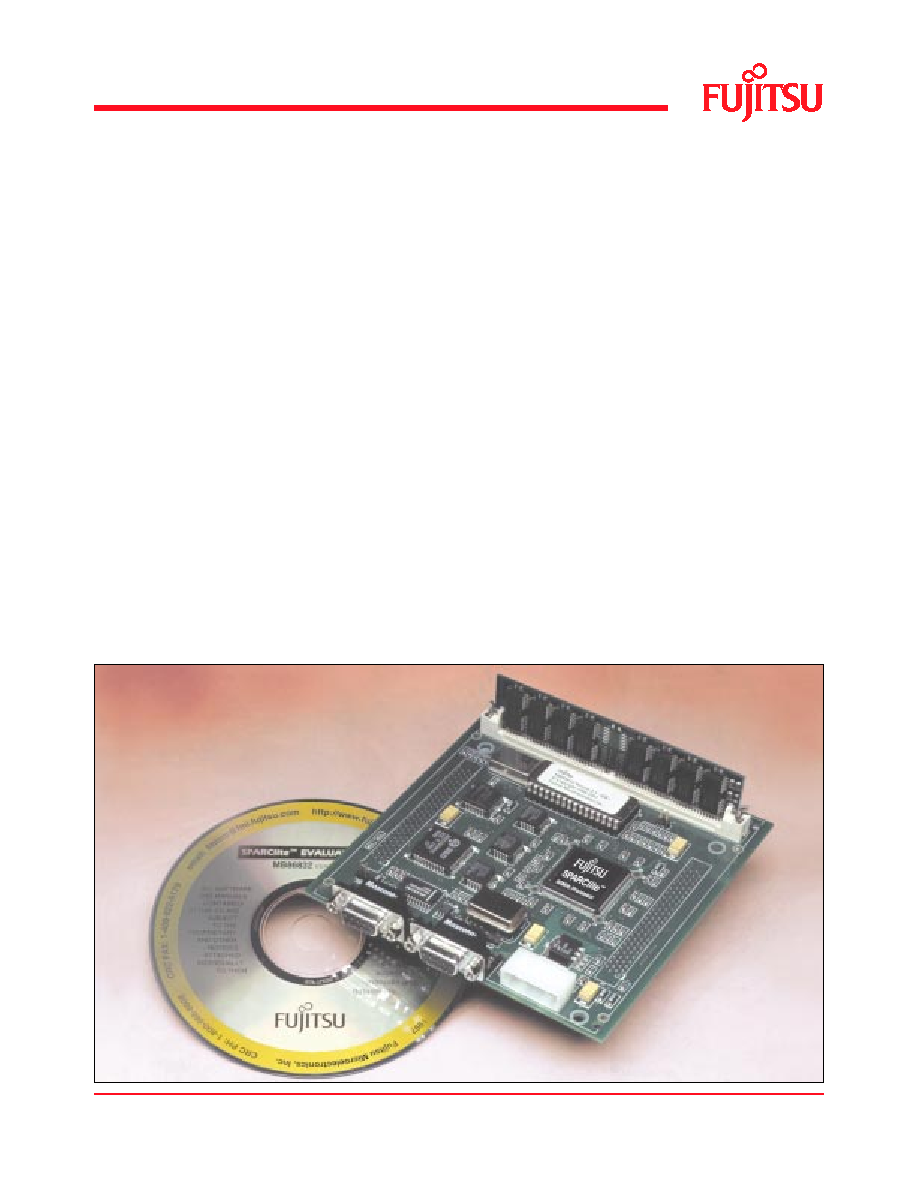

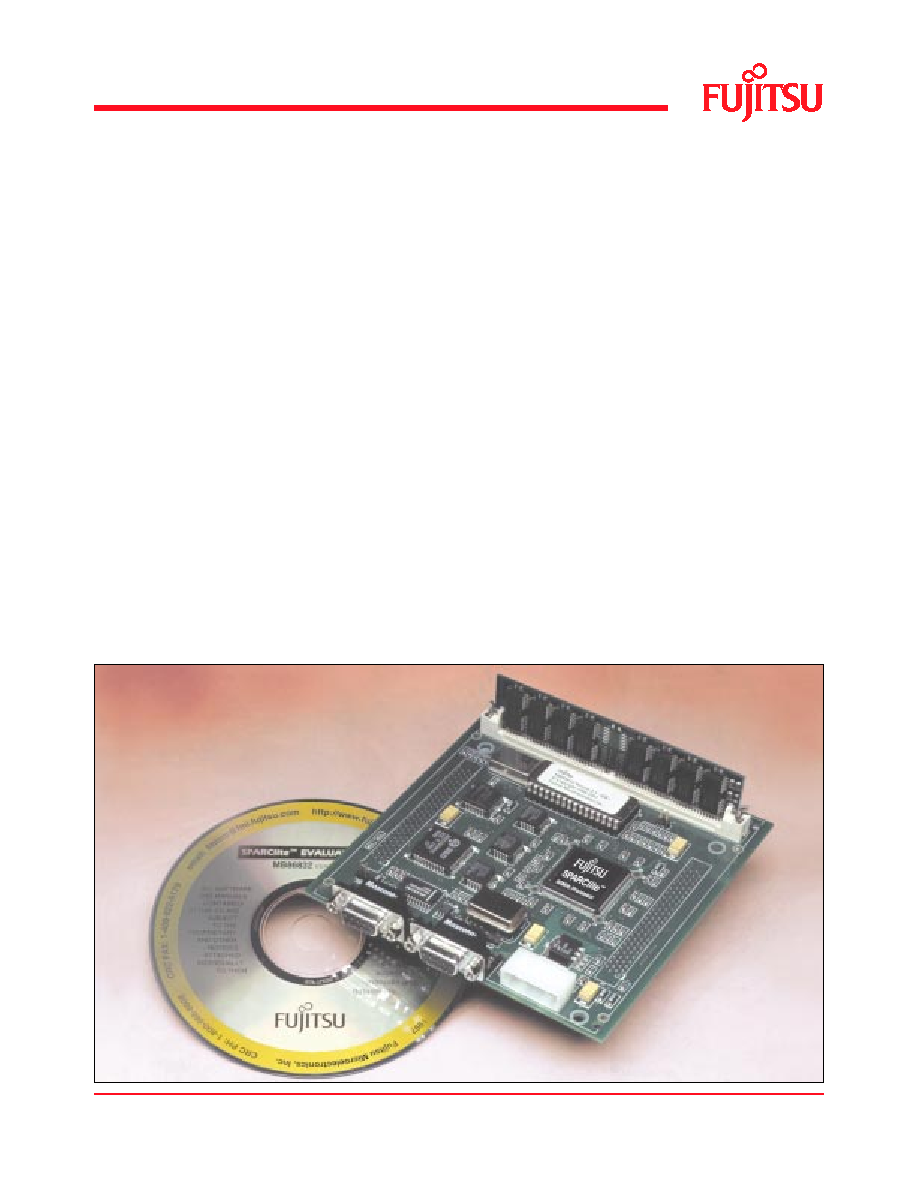

MB86832 EVALUATION KIT

DESCRIPTION

Fujitsu introduces a full-featured, low-cost evaluation kit

for the SPARCliteTM RISC processor. The kit includes a

board module and software to allow users to evaluate

SPARClite's performance.

The GNU-C cross compiler included in the kit is DOS

hosted. It is optimized for SPARClite and can produce

executable code for the entire SPARClite family of prod-

ucts. It will also be possible for users to debug the test

code with the GNU GDB software. This tool is resident in

the PC Windows environment and provides a user friend-

ly Windows interface. This tool offers feature rich debug-

ging commands such as single stepping and software and

hardware breakpointing. It also displays the registers,

flags, assembly, and C with assembly interlaced. Rather

than using software simulation, code can actually be

debugged on the evaluation board itself.

A variety of tools and libraries are available to the users.

In addition to serving as an evaluation tool, this kit will

also be a stepping stone to software development and

hardware expansion.

SYSTEM REQUIREMENTS

n

PC/AT Compatible System (486 or better)

- Minimum 8MB RAM

- Minimum 30MB Hard Disk Space

- Minimum WindowsÆ 3.1

- CD-ROM Drive

n

PC/AT Power Supply

n

Cables

n

Secondary ASCII Terminal

EVALUATION KIT CONTENTS

n

MB86832 SPARClite Evaluation Board

- MB86832 SPARClite 80 MHz Processor

- 4MByte DRAM Memory

- 2 Serial Ports

n

MB86832 Evaluation Kit CD

- GNU C Development Tools

- MB86832 Data Sheet and User Manual

- SPARClite Evaluation Board Software

- SPARClite Evaluation Kit Manuals

- UNIXÆ (SUNOS 4.X and Solaris 2.X) version of

the GNU C Development Tools and the SPARClite

Software

September 1997

MB86832 EVALUATION KIT

n

80 MHz version with clock doubling

n

SPARC

Æ

high performance RISC architecture

8 window, 136 word register file

n

16 address spaces, 256 MByte each

n

Harvard-style separate instruction and data buses

on-chip

n

8 Kbytes 2-way set associative instruction cache

n

8 Kbytes 2-way set associative data cache

n

Flexible locking mechanism for data and instruction

cache entries

n

Option to force non-cached operation based on chip

selects on Non-Cache Pin

n

Four deep buffered writes and one deep instruction

pre-fetching

n

Core can run up to 4 times the frequency of the

Bus Interface Unit

n

Bus interface support for 8, 16 or 32-bit memories

read/write

n

Support for burst mode cache fills

n

Built-in DRAM & EDO DRAM controller

n

Interrupt Controller with fast interrupt response time,

with programmable priority

n

Sleep mode support

n

Parity generation and checking

n

Programmable address decoder and wait-state generator

n

On-chip clock generator circuit

n

Single vector trapping

n

Power down modes, with global or selective

power down

n

Debug Support Unit (DSU)

n

0.35 micron gate, 2 level metal CMOS technology,

3.3V internal and 3.3/5.0V I/O

EC-FS-20593-9/97

MB86832 SPARClite 32-BIT RISC EMBEDDED PROCESSOR

FEATURES

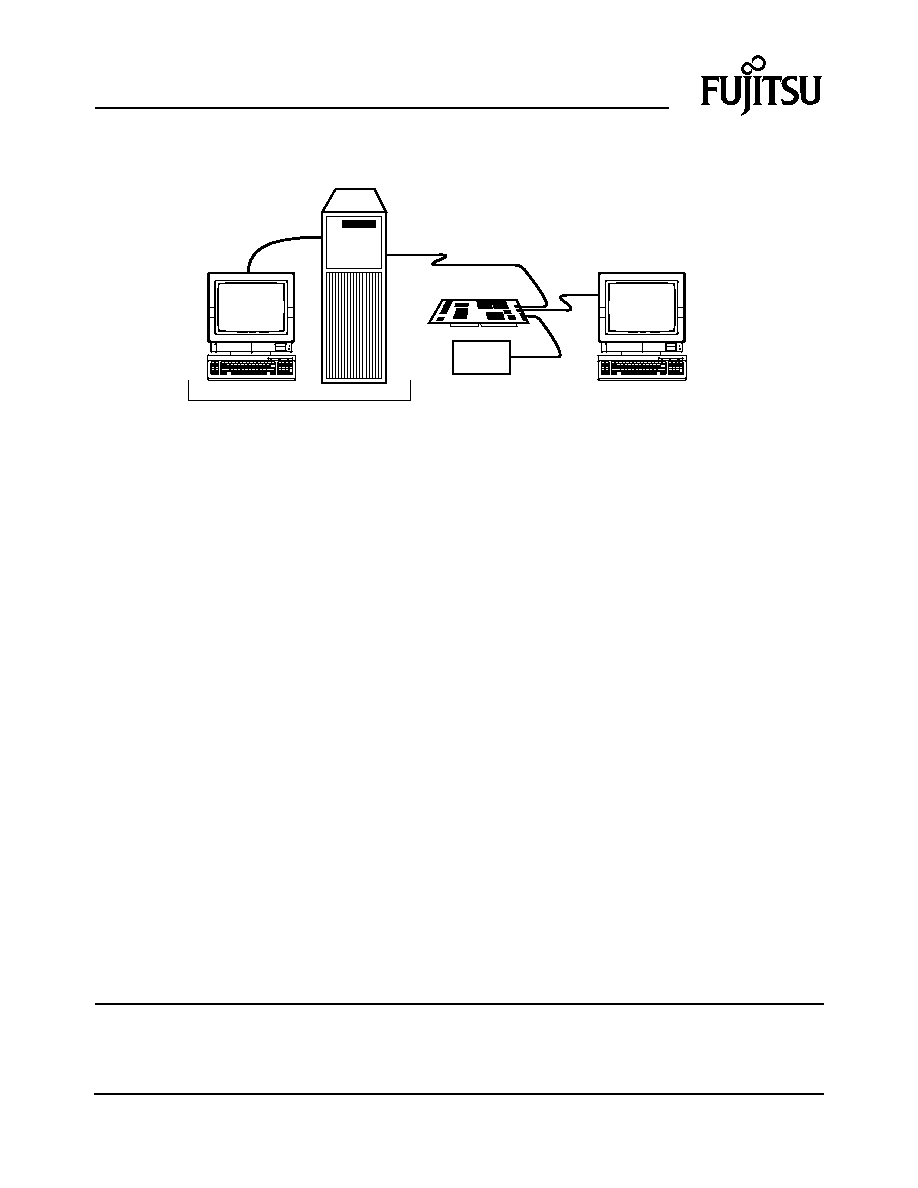

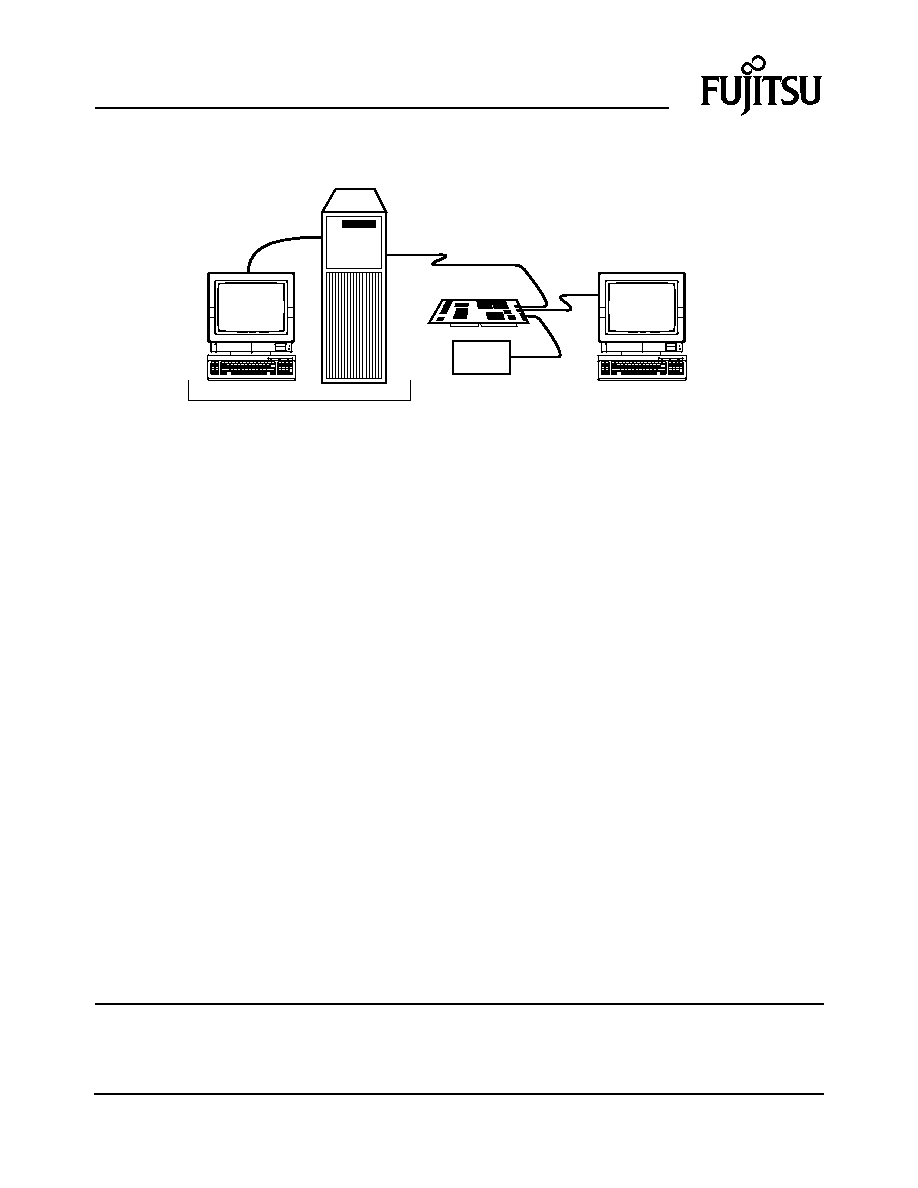

DEVELOPMENT SYSTEM ENVIRONMENT

PC HOST SYSTEM

EVALUATION BOARD

POWER SUPPLY

SECONDARY TERMINAL

SPARClite is a trademark of SPARC International, Inc., licensed exclusively to Fujitsu Microelectronics Inc.

All trademarks or registered trademarks are the property of their respective owners.

SPARC is a registered trademark of SPARC International, Inc., based on technology developed by Sun Microsystems, Inc.

Printed in the U.S.A.

FUJITSU MICROELECTRONICS, INC.

3545 North First Street, San Jose, California 95134-1804

Customer Response Center (CRC)

CRC Tel: 1-800-866-8608, CRC Fax: 408-922-9179

http://www.fujitsumicro.com