DS07-13504-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F

2

MC-16F MB90230 Series

MB90233/234/P234/W234

s

DESCRIPTION

The MB90230 series is a member of general-purpose, 16-bit microcontrollers designed for those applications which

require high-speed realtimeprocessing, proving to be suitable for various industrial machines, camera and video

devices, OA equipment, and for process control. The CPU used in this series is the F

2

MC*-16F. The instruction

set for the F

2

MC-16F CPU core is designed to be optimized for controller applications while inheriting the AT

architecture of the F

2

MC-16/16H series, allowing a wide range of control tasks to be processed efficiently at high

speed.

The peripheral resources integrated in the MB90230 series include: the UART (clock asynchronous/synchronous

transfer)

�

1 channel, the extended serial I/O interface

�

1 channel, the A/D converter (8/10-bit precision)

�

8

channels, the D/A converter (8-bit precision)

�

2 channels, the level comparator

�

1 channel, the external interrupt

input

�

4 lines, the 8-bit PPG timer (PWM/single-shot function)

�

1 channel, the 8-bit PWM controller

�

6 channels,

the 16-bit free run timer

�

1 channel, the input capture unit

�

4 channels, the output compare unit

�

6 channels,

and the serial E

2

PROM interface.

*: F

2

MC stands for FUJITSU Flexible Microcontroller.

s

FEATURES

F

2

MC-16F CPU block

� Minimum execution time: 62.5 ns (at machine clock frequency of 16 MHz)

� Instruction set optimized for controllers

Various data types supported (bit, byte, word, and long-word)

Extended addressing modes: 23 types

High coding efficiency

Higher-precision operation enhanced by a 32-bit accumulator

Signed multiplication and division instructions

(Continued)

s

PACKAGE

100-pin Plastic LQFP

(FPT-100P-M05)

100-pin Ceramic LQFP

(FPT-100C-C01)

MB90230 Series

2

(Continued)

� Enhanced instructions applicable to high-level language (C) and multitasking

System stack pointer

Enhanced pointer-indirect instructions

Barrel shift instructions

� Increased execution speed: 8-byte instruction queue

� 8-level, 32-factor powerful interrupt service functions

� Automatic transfer function independent of the CPU (EI

2

OS)

� General-purpose ports: Up to 84 lines

Ports with input pull-up resistor available: 24 lines

Ports with output open-drain available: 9 lines

Peripheral blocks

� ROM:48 Kbytes (MB90233)

96 Kbytes (MB90234)

EPROM: 96 Kbytes (MB90W234)

One-time PROM: 96 Kbytes (MB90P234)

� RAM: 2 Kbytes (MB90233)

3 Kbytes (MB90234/W234/P234)

� PWM control circuit: (simple 8 bits): 6 channels

� Serial interface

UART: 1 channel

Extended serial I/O interface

Switchable I/O port: 1 channel

Communication prescaler (Source clock generator for the UART, serial I/O interface, CKOT, and level

comparator): 1 channel

� Serial E

2

PROM interface: 1 channel

� A/D converter with 8/10-bit resolution: input 8 channels

� Level comparator: 1 channel

4-bit D/A converter integrated

� D/A converter with 8-bit resolution: 2 channels

8-bit PPG timer: 1 channel

� Input/output timer

16-bit free run timer: 1 channel

16-bit output compare unit: 6 channels

16-bit input capture unit: 4 channels

� 18-bit timebase timer

� Watchdog timer function

� Standby modes

Sleep mode

Stop mode

3

MB90230 Series

s

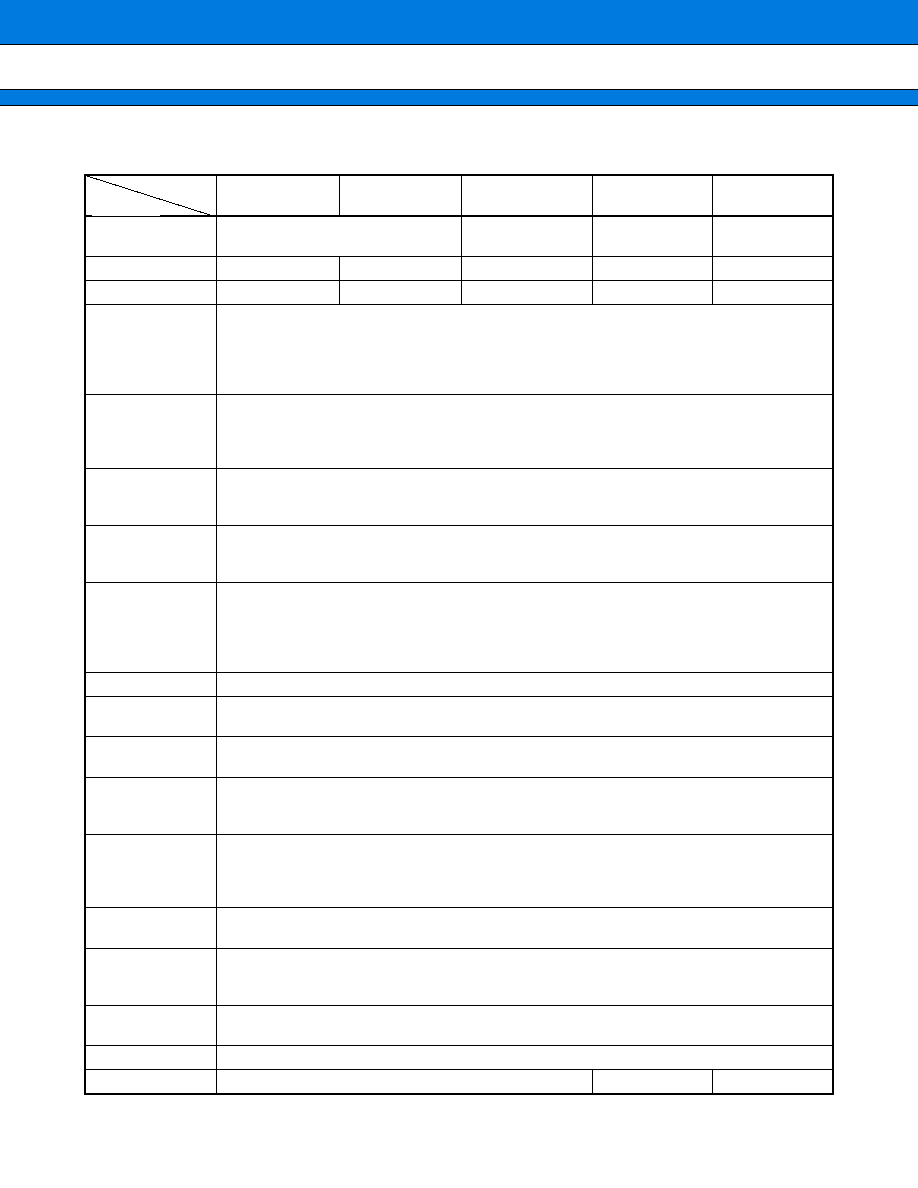

PRODUCT LINEUP

NB90234

MB90P234

MB90W234

MB90V230

Classification

Mask ROM products

One-time PROM

model

EPROM model

Evaluation

model

ROM size

48 Kbytes

96 Kbytes

96 Kbytes

96 Kbytes

--

RAM size

2 Kbytes

3 Kbytes

3 Kbytes

3 Kbytes

4 Kbytes

CPU functions

Number of instructions: 420

Instruction bit length: 8 or 16 bits

Instruction length: 1 to 7 bytes

Data bit length: 1, 4, 8, 16, or 32 bits

Minimum execution time: 62.5 ns at 16 MHz (internal)

Ports

Up to 84 lines

I/O ports (CMOS): 51

I/O ports (CMOS) with pull-up resistor available: 24

I/O ports (open-drain): 9

UART

Number of channels: 1 (switchable I/O)

Clock synchronous communication (2404 to 38460 bps, full-duplex double buffering)

Clock asynchronous communication (500K to 5M bps, full-duplex double buffering)

Serial interface

Number of channels: 1

Internal or external clock mode

Clock synchronous transfer (62.5 kHz to 1 MHz, "LSB first" or "MSB first" transfer)

A/D converter

Resolution: 10 or 8 bits, Number of input lines: 4

Single conversion mode (conversion for a specified input channel)

Scan conversion mode (continuous conversion for specified consecutive channels)

Continuous conversion mode (repeated conversion for a specified channel)

Stop conversion mode (periodical conversion)

D/A converter

Resolution: 8 bits, Number of output pins: 2

Level

comparator

Comparison to internal D/A converter (4-bit resolution)

PWM

Number of channels: 6

8-bit PWM control circuit (operation of 1

�

, 2

�

, 16

�

, 32

�

)

PPG timer

Number of channels: 1 channel with 8-bit resolution

PWM function: Continuous output of pulse synchronous to trigger

Single-shot function: Output of single pulse by trigger

Serial E

2

PROM

interface

Number of channels: 1

Instruction code (NS type)

Variable address length: 8 to 11 bits (with address increment function)

Variable data length: 8 or 16 bits

Timer

Number of channels: 6

16-bit reload timer operation (operation clock cycle of 0.25

�

s to 1.05 s)

Free run timer

Number of channels: 1

16-bit input capture unit: 4 channels

16-bit output compare unit: 6 channels

External interrupt

input

Number of input pins: 4

Standby mode

Stop mode and sleep mode

Package

FPT-100P-M05

FPT-100C-C01

PGA256-A02

MB90233

Parameter

Part number

MB90230 Series

4

s

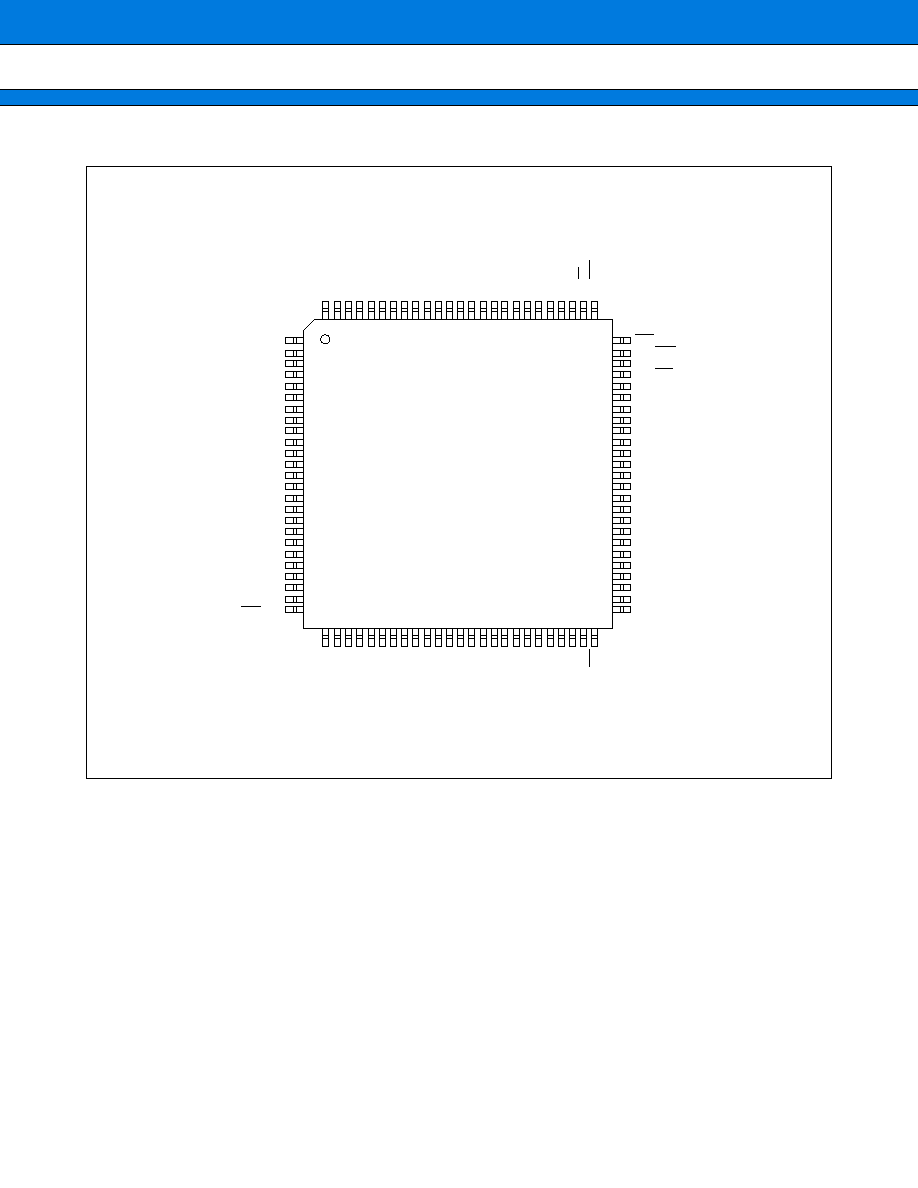

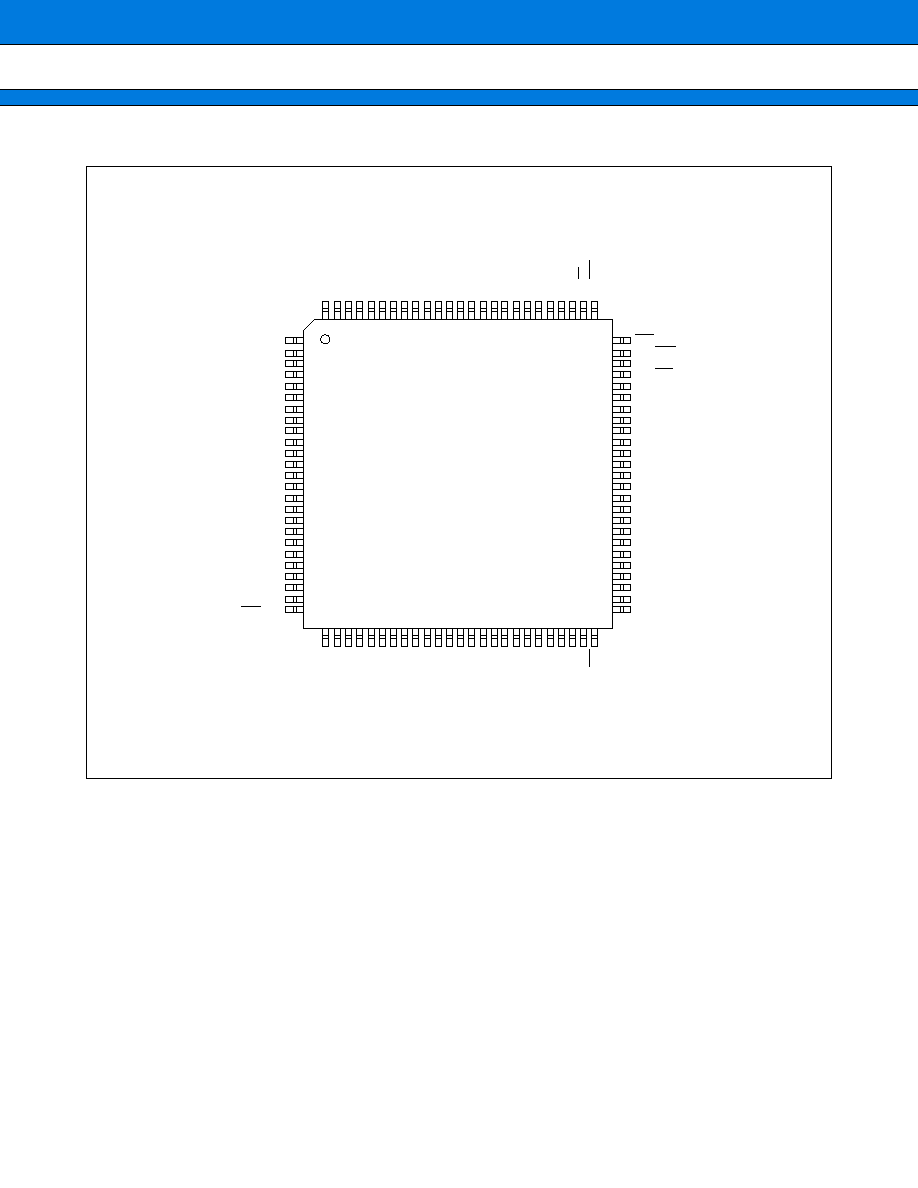

PIN ASSIGNMENT

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

RST

P54/WRH

P53/HRQ

P52/HAK

P51/RDY

P50/CLK

PA5/SCK2

PA4/SOT2

PA3/SIN2

PA2/SCK1

PA1/SOT1

PA0/SIN1

P96/SCK0

P95/SOT0

P94/SIN0

P93/IN3/CKOT

P92/IN2

P91/IN1

P90/IN0

P87/OUT5

P86/OUT4

P85/OUT3

P84/OUT2

P83/OUT1/INT3

P82/OUT0/INT2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

P22/A02

P23/A03

P24/A04

P25/A05

P26/A06

P27/A07

P30/A08

P31/A09

V

SS

P32/A10

P33/A11

P34/A12

P35/A13

P36/A14

P37/A15

PWM0/P40/A16

PWM1/P41/A17

PWM2/P42/A18

PWM3/P43/A19

PWM4/P44/A20

V

CC

PWM5/P45/A21

TRG/P46/A22

PPG/P47/A23

ATG/P70

P71/EDI

P72/EDO

P73/ESK

P74/ECS

P75/DA0

P76/DA1

AV

CC

AVRH

AVRL

AV

SS

P60/AN0

P61/AN1

P62/AN2

P63/AN3

V

SS

P64/AN4

P65/AN5

P66/AN6

P67/AN7/CMP

P80/INT0

P81/INT1

MD0

MD1

MD2

HST

P21/A01

P20/A00

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D09

P10/D08

P07/D07

P06/D06

P05/D05

P04/D04

P03/D03

P02/D02

P01/D01

P00/D00

V

CC

X1

X0

V

SS

P57

P56/RD

P55/WRL

(TOP VIEW)

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

(FPT-100P-M05)

(FPT-100C-C01)

5

MB90230 Series

s

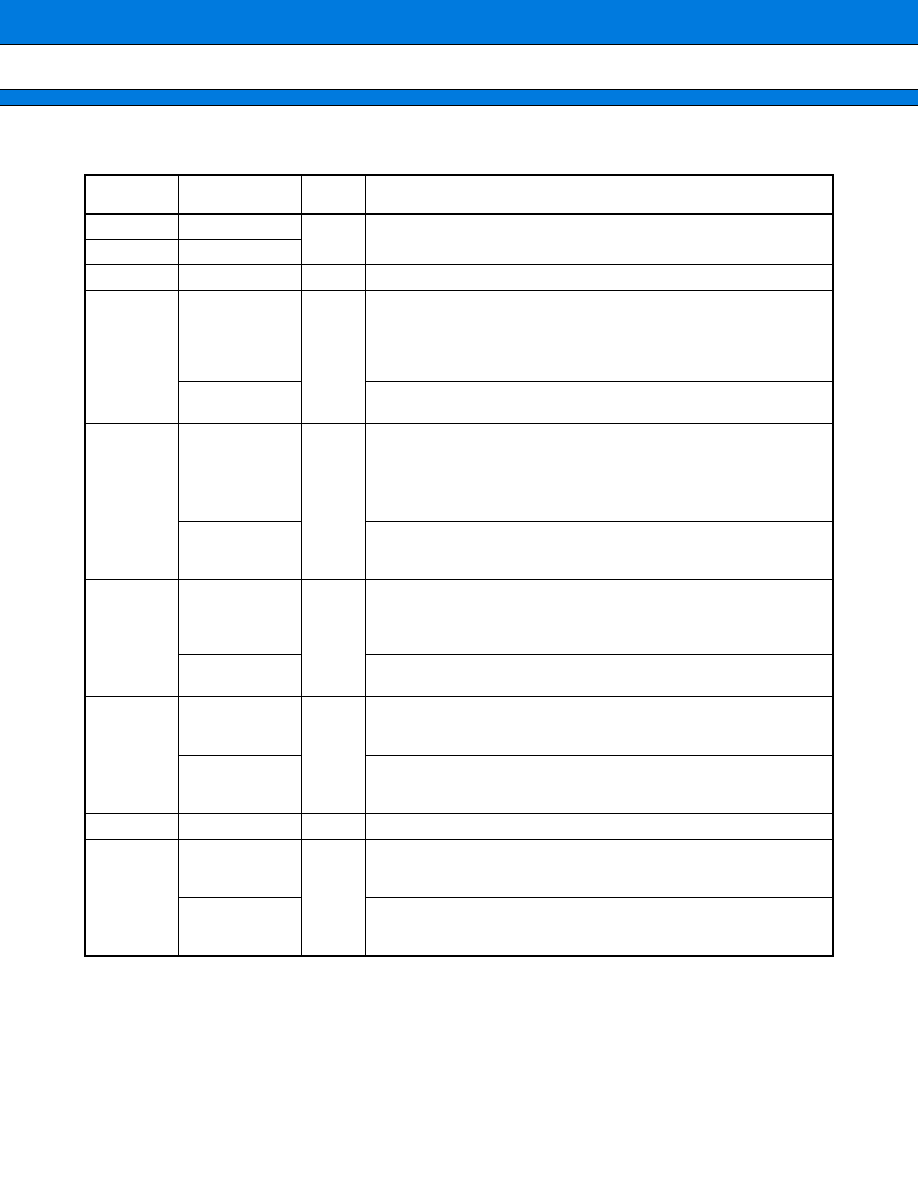

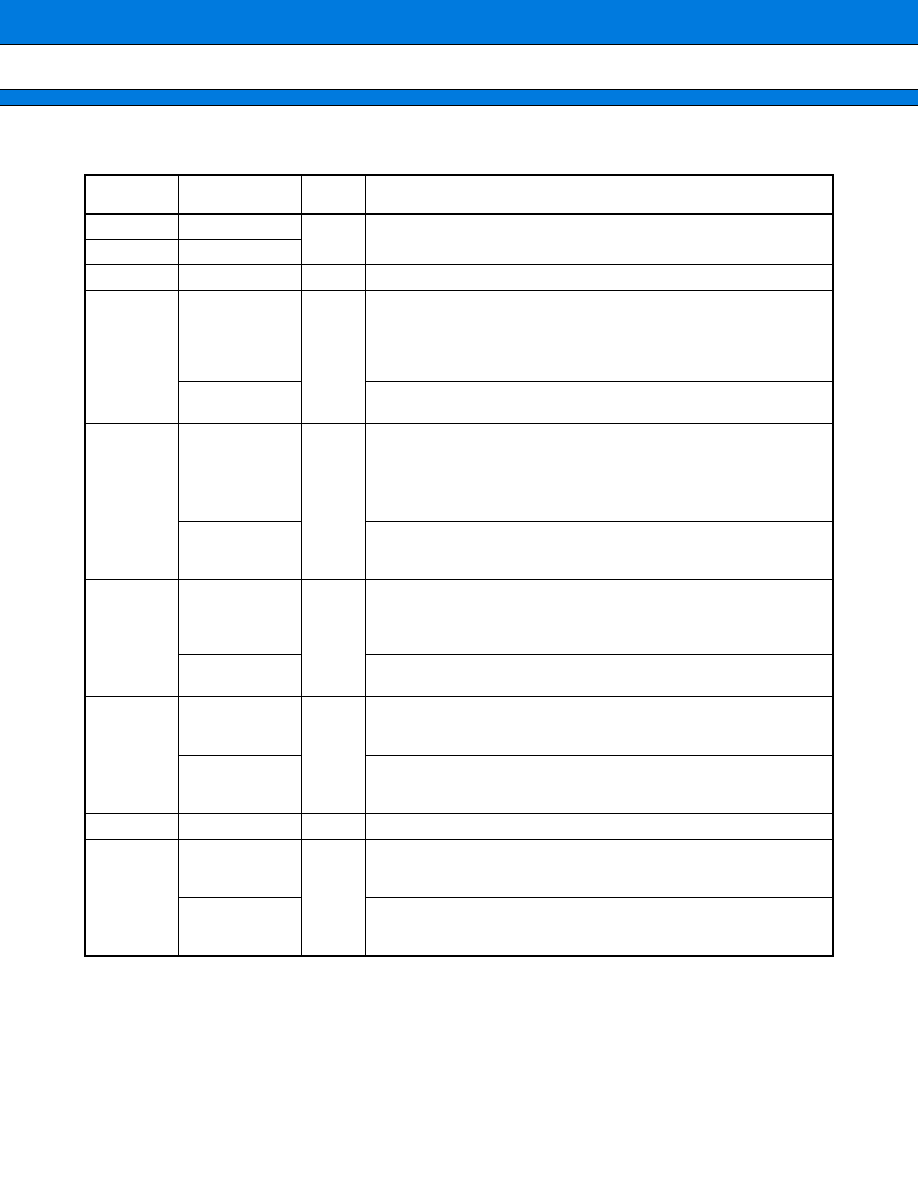

PIN DESCRIPTION

(Continued)

Pin no.

Pin name

Circuit

type

Function

80

X0

A

Oscillator pins

81

X1

82

V

CC

--

Power supply pin

83 to 90

P00 to P07

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the

pull-up resistor setting register.

These pins serve as D00 to D07 pins in bus modes other than the

single-chip mode.

D00 to D07

I/O pins for the lower eight bits of the external data bus.

These pins are enabled in an external-bus enabled mode.

91 to 98

P10 to P17

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the pull-up

resistor setting register.

These pins are enabled in the single-chip mode with the external-bus

enabled and the 8-bit data bus specified.

D08 to D15

I/O pins for the upper eight bits of the external data bus

These pins are enabled in an external-bus enabled mode with the 16-

bit data bus specified.

99, 100

1 to 6

P20 to P27

G

General-purpose I/O port

An input pull-up resistor can be added to the port by setting the

pull-up resistor setting register.

These pins are enabled in the single-chip mode.

A00 to A07

I/O pins for the lower eight bits of the external data bus

These pins are enabled in an external-bus enabled mode.

7, 8

P30, P31

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the middle

address control register setting is "port."

A08, A09

I/O pins for the middle eight bits of the external data bus

These pins are enabled in an external-bus enabled mode when the

middle address control register setting is "address."

9

V

SS

--

Power supply pin

10 to 15

P32 to P37

E

General-purpose I/O port

This port is enabled in the single-chip mode or when the middle

address control register setting is "port."

A10 to A15

I/O pins for the middle eight bits of the external data bus

These pins are enabled in an external-bus enabled mode when the

middle address control register setting is "address."