DS07-16308-1E

FUJITSU SEMICONDUCTOR

DATA SHEET

32-Bit RISC Microcontroller

CMOS

FR30 Series

MB91133/MB91F133

s

DESCRIPTION

The MB91133/MB91F133, a standard single-chip microcontroller featuring various I/O resources and bus control

mechanisms to incorporate the control required for high-performance high-speed CPU processes, is the core unit

in the 32-bit RISC CPU (FR family) .

This unit has the optimal specifications for incorporating applications that require high-performance CPU pro-

cessing power by featuring peripheral I/O resources suitable for single-lens reflex cameras, digital video cameras,

etc.

s

FEATURES

1.

CPU

∑ 32-bit RISC (FR30) , load/store architecture, 5-level pipeline

∑ Multi-purpose register : 32 bits

◊

16

∑ 16-bit fixed length instructions (basic instructions) , 1 instruction per cycle

∑ Instructions for barrel shift, bit processing and inter-memory transfers : Instructions suited to loading purposes

∑ Function entry / exit instruction, multi load / store instruction of register details : High-level language handling

instruction

∑ Register interlock function : Simplification of assembler description

∑ Branch instruction with delay slot : Reduction in overheads in case of branching

∑ Multiplier is built-in / supported at instruction level.

∑ Signed 32-bit multiplication : 5 cycles

∑ Signed 16-bit multiplication : 3 cycles

∑ Interruption (saving PC and PS) : 6 cycles, 16 priority levels

(Continued)

s

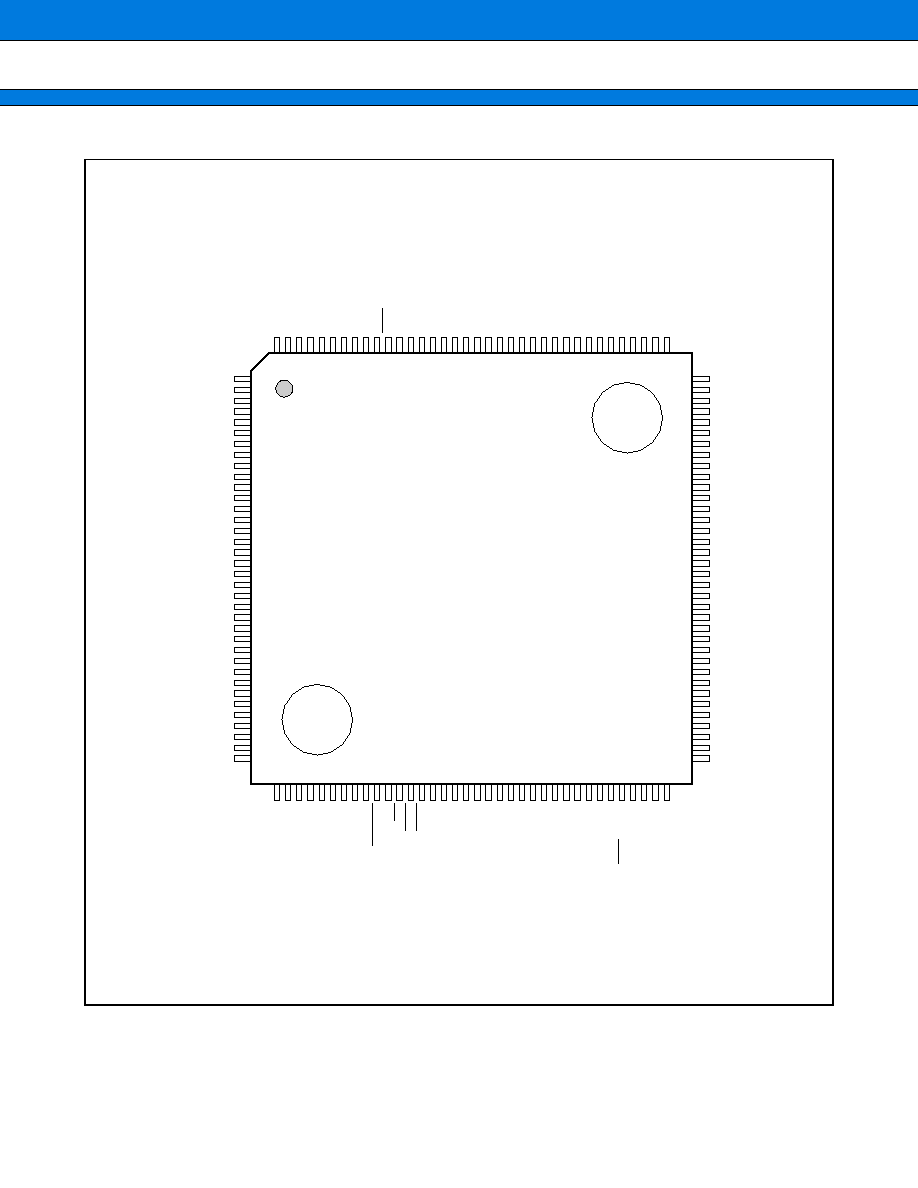

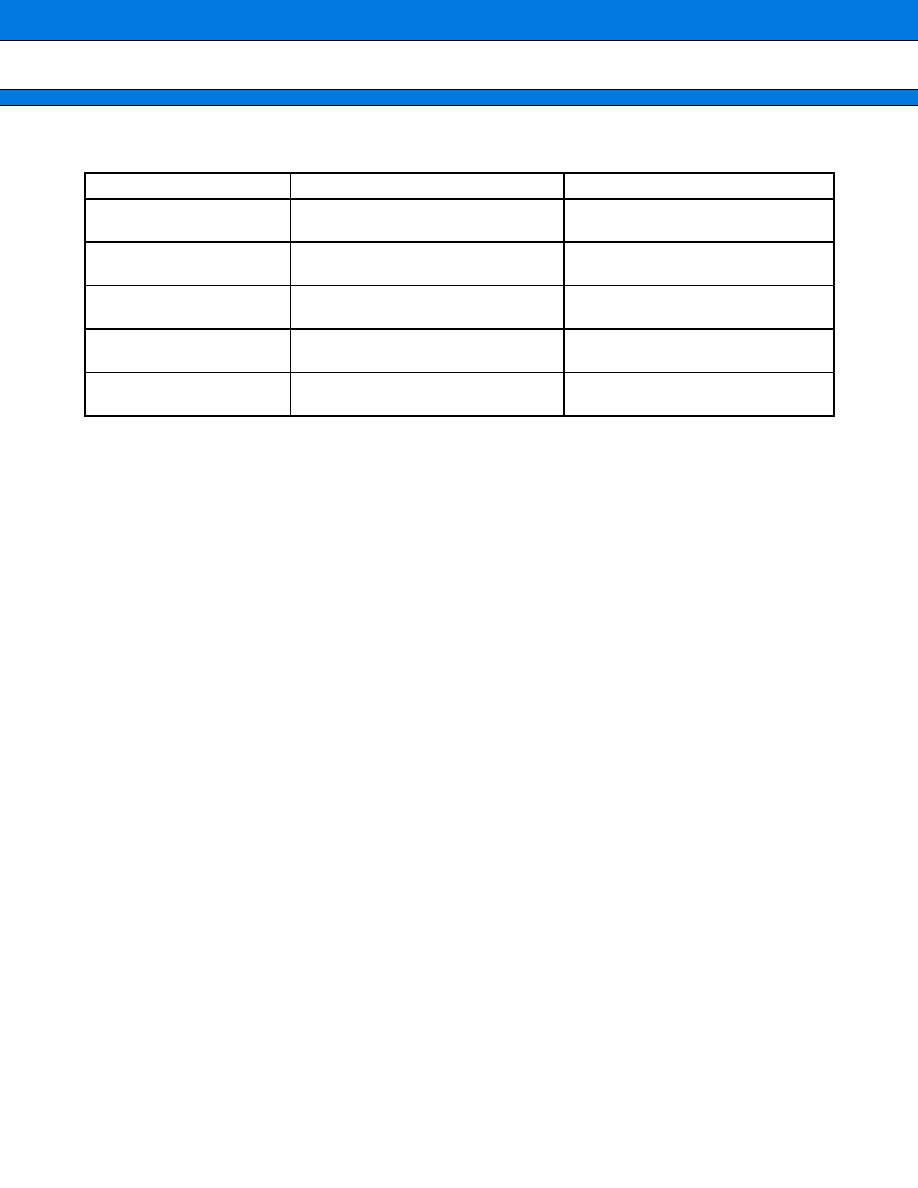

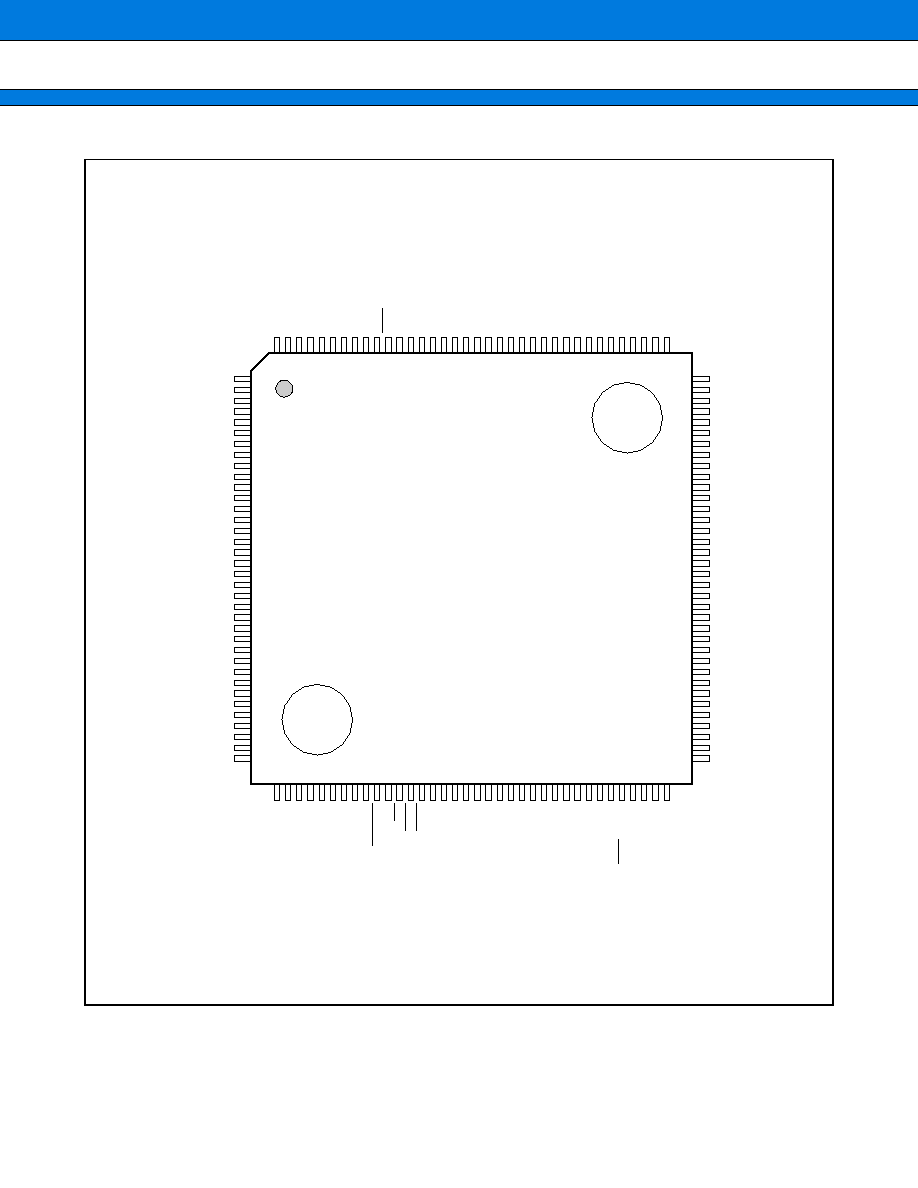

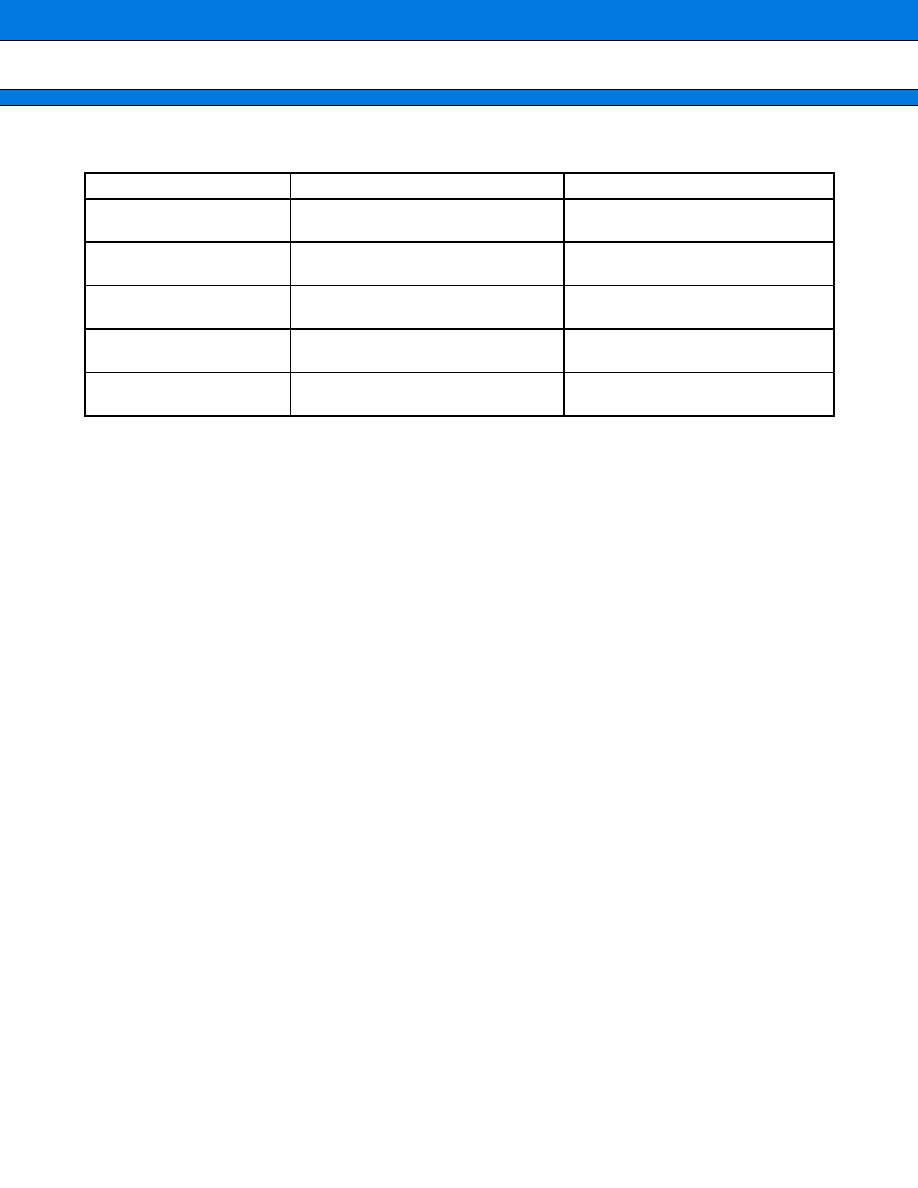

PACKAGES

144-pin plastic FBGA

144-pin plastic LQFP

(BGA-144P-M01)

(FPT-144P-M08)

MB91133/MB91F133

2

(Continued)

2.

Bus Interface

∑ 24-bit address output, 8/16-bit data input/output

∑ Basic bus cycle : 2 clock cycles

∑ Interface support for various memories

∑ Unused data and address pins can be used as input/output ports.

∑ Supports "little endian" mode

3.

Built-in ROM

Mask device : 254 KB; FLASH device : 254 KB; EVA-FLASH device : 254 KB

4.

Built-in RAM

Mask device : 8 KB; FLASH device : 8 KB; EVA-FLASH device : 8 KB

5.

DMA Controller

This is a descriptor-type MA controller whose transfer parameters are arranged in the main memory.

A maximum of 8 factors in total (internal and external) can be transferred.

External factors are 3 channels.

6.

Bit Search Module

Searches the first "1" / "0" change bit positions within 1 cycle from MSB in 1 word

7.

Timer

∑ 16-bit reload timer

◊

5 channels

∑ 16-bit OCU

◊

8 channels, ICU

◊

4 channels, free-run timer

◊

1 channel

Output waveform adjusting function for AC motor waveforms is included in the above timer.

∑ 8/16-bit up/down timer/counter (8-bit

◊

2 channels or 16-bit

◊

1 channel)

External interruption and pin are shared for AIN and BIN.

∑ 16-bit down count timer

◊

5 channels; can also be used as the UART baud rate timer

∑ 16-bit PPG timer

◊

6 channels; out-pulse cycle / duty can be changed at random

8.

D/A Converter

∑ 8-bit

◊

3 channels

9.

A/D Converter (Sequential comparison type)

∑ 10-bit

◊

8 channels

∑ Sequential conversion method (conversion time 5.0

µ

s at 33 MHz)

∑ Setting for single conversion, scan conversion and repeat conversion is possible.

∑ Conversion starting function using hardware or software

10. Serial I/O

∑ UART

◊

5 channels; clock synchronous serial transfer with LSB / MSB switching function is possible for both.

∑ Serial data output or serial lock output can be selected using push-pull / open-drain software.

11. Level Comparator Input

∑ 1 channel; shared input and pins of A/D converter.

12. Clock Switching Function

∑ Base clock : Software can be used to select from two types of clock sources, namely 32 kHz and high-speed.

∑ Gear function : Four types of settings (1 : 1, 1 : 2, 1 : 4, 1 : 8) can be set individually as the operating clock

ratio to the basic clock per CPU and peripheral equipment.

MB91133/MB91F133

3

13. Interruption Controller

∑ External interruption input (total 24 channels)

∑ With pull up pin control / standby return function : 4 channels

(rising / falling / H level / L level settings are possible)

∑ With pull up pin control / standby return function; AIN / BIN pins of the up/down counter are shared : 4 channels

(rising / falling / H level / L level settings are possible)

∑ With pull up pin controln : 16 channels

(rising / falling / H level / L level settings are possible)

∑ Internal interruption factor

∑ Interruption / delay interruption by resource

14. Others

∑ Reset factors

Power on reset, watchdog timer, software reset, external reset

∑ Low power consumption mode

Sleep/stop mode

∑ Packages

FBGA-144, LQFP-144

∑ CMOS technology (0.35

µ

m)

∑ Power

Two power sources (5 V / 3 V)

1) 5 V system : 5 V

±

10

%

(A/D, D/A and level comparator included)

2) 3 V system : A) 3.0 V to 3.6 V : All functions guaranteed

B) 2.7 V to 3.0 V : All functions guaranteed for single-chip mode of mask devices only

s

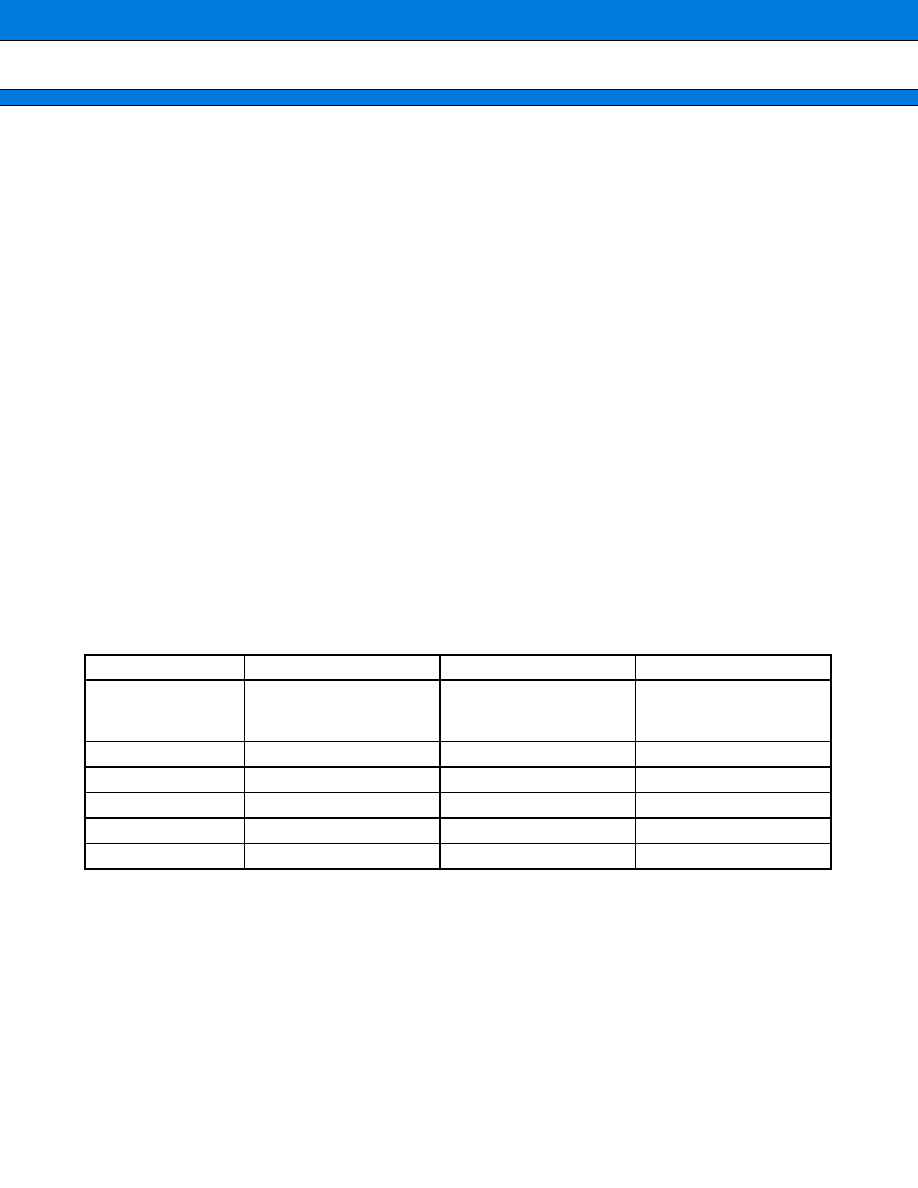

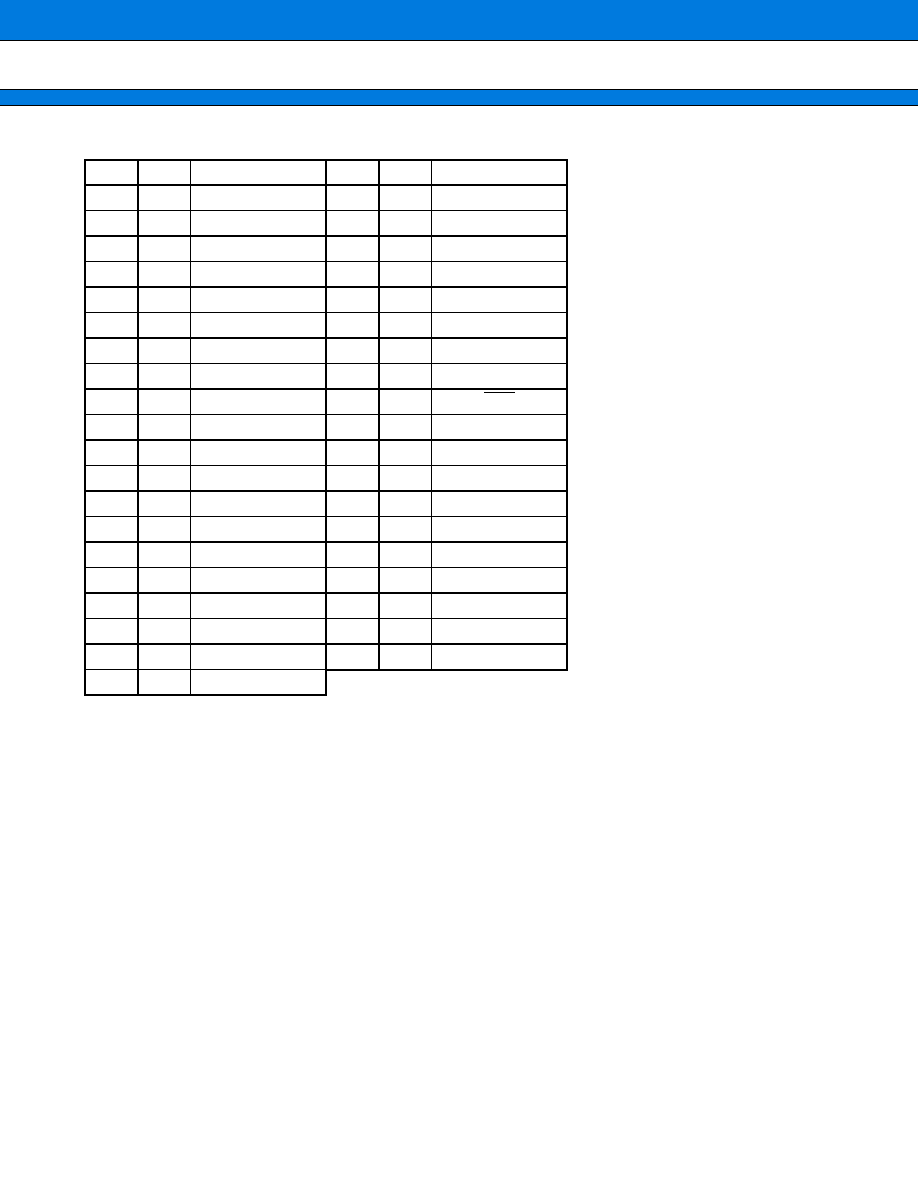

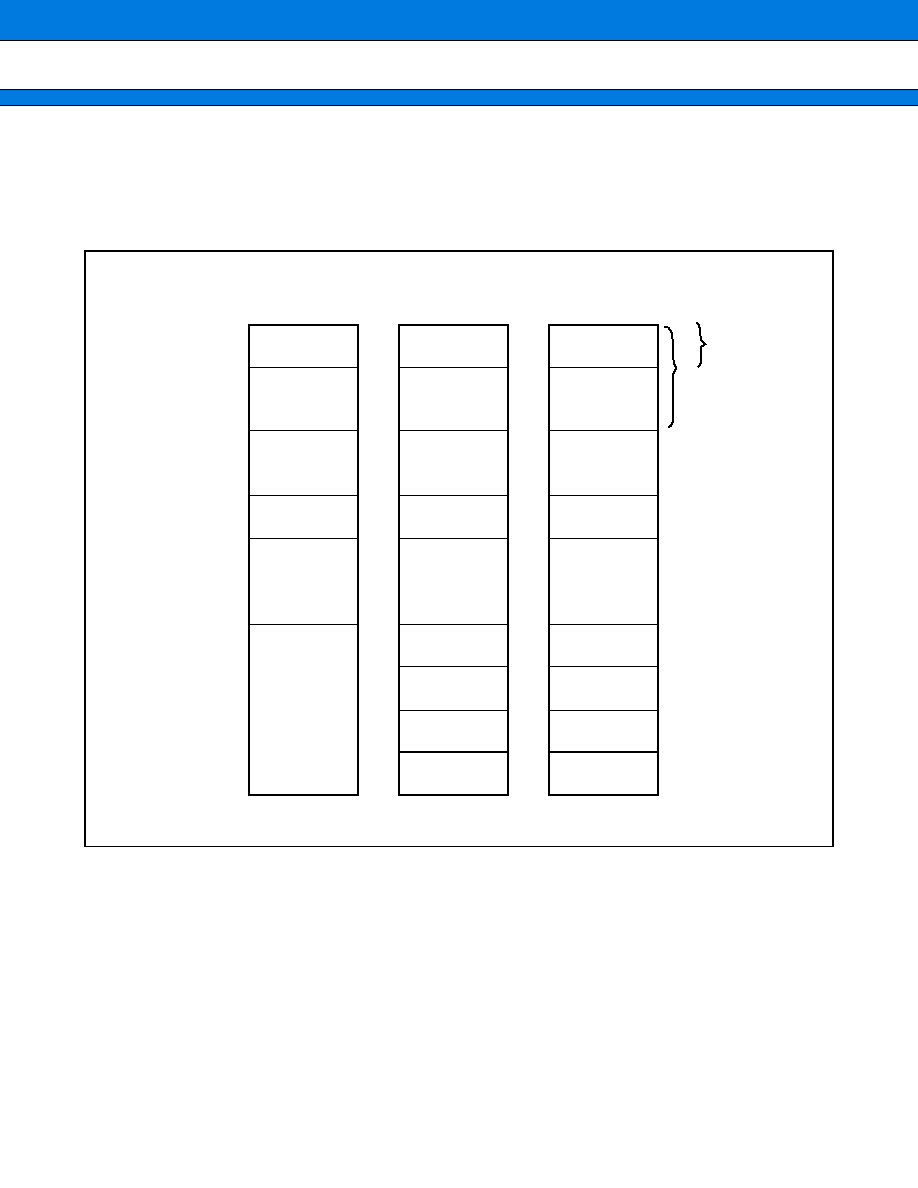

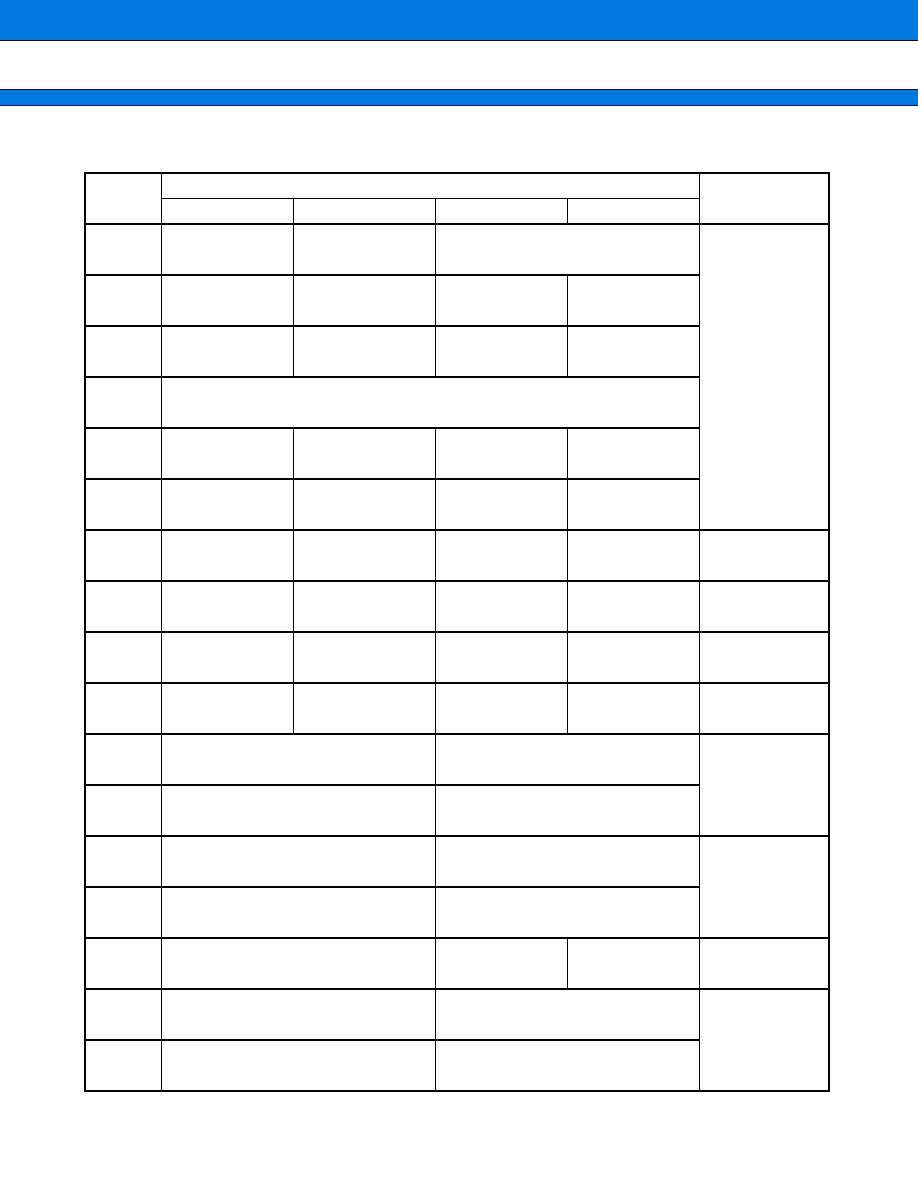

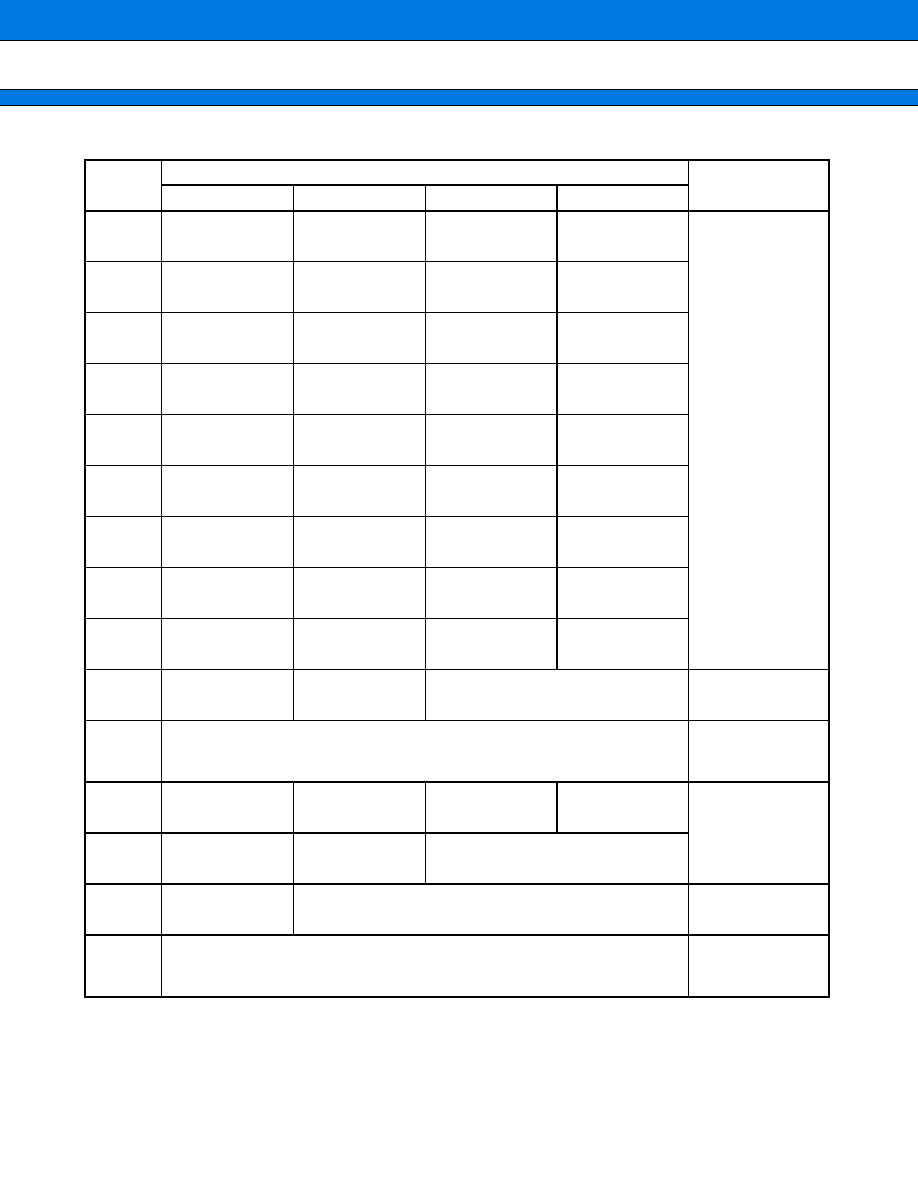

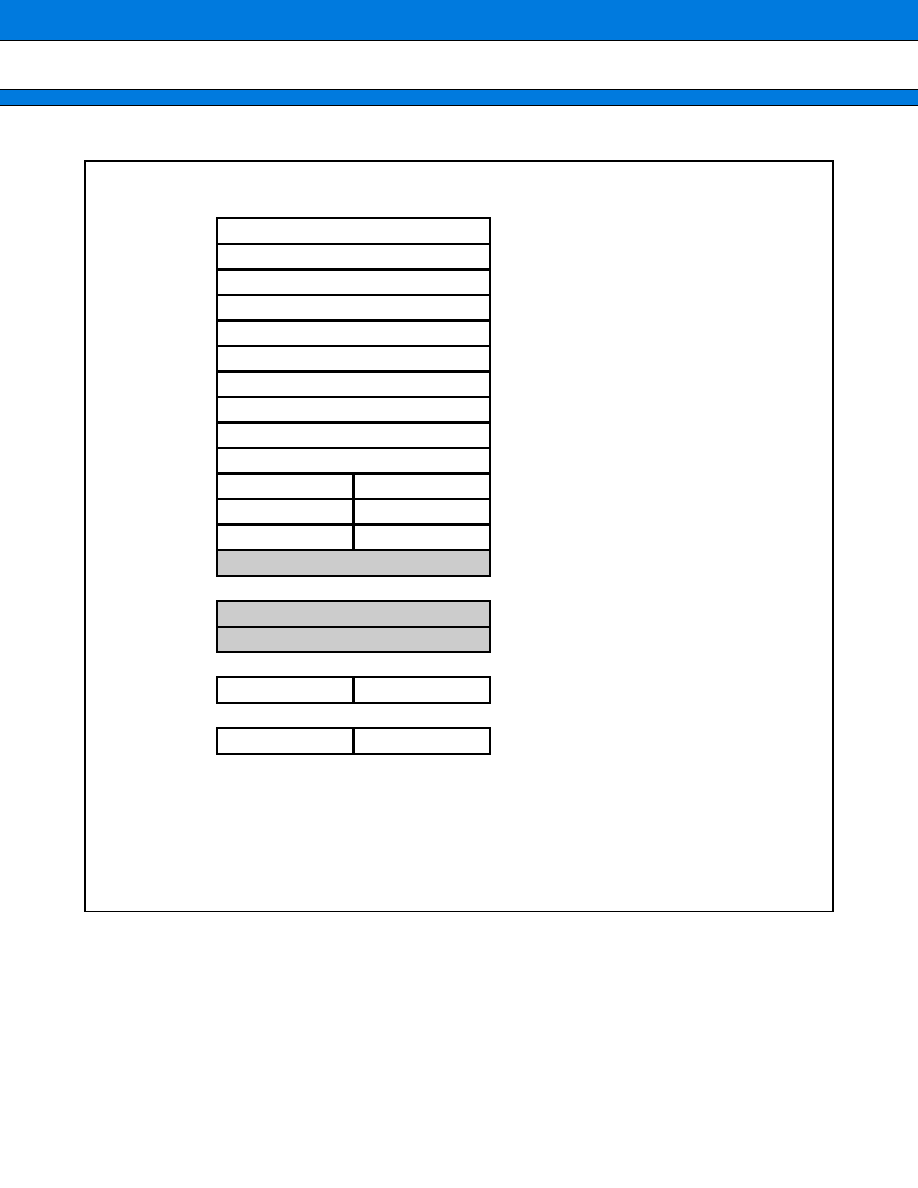

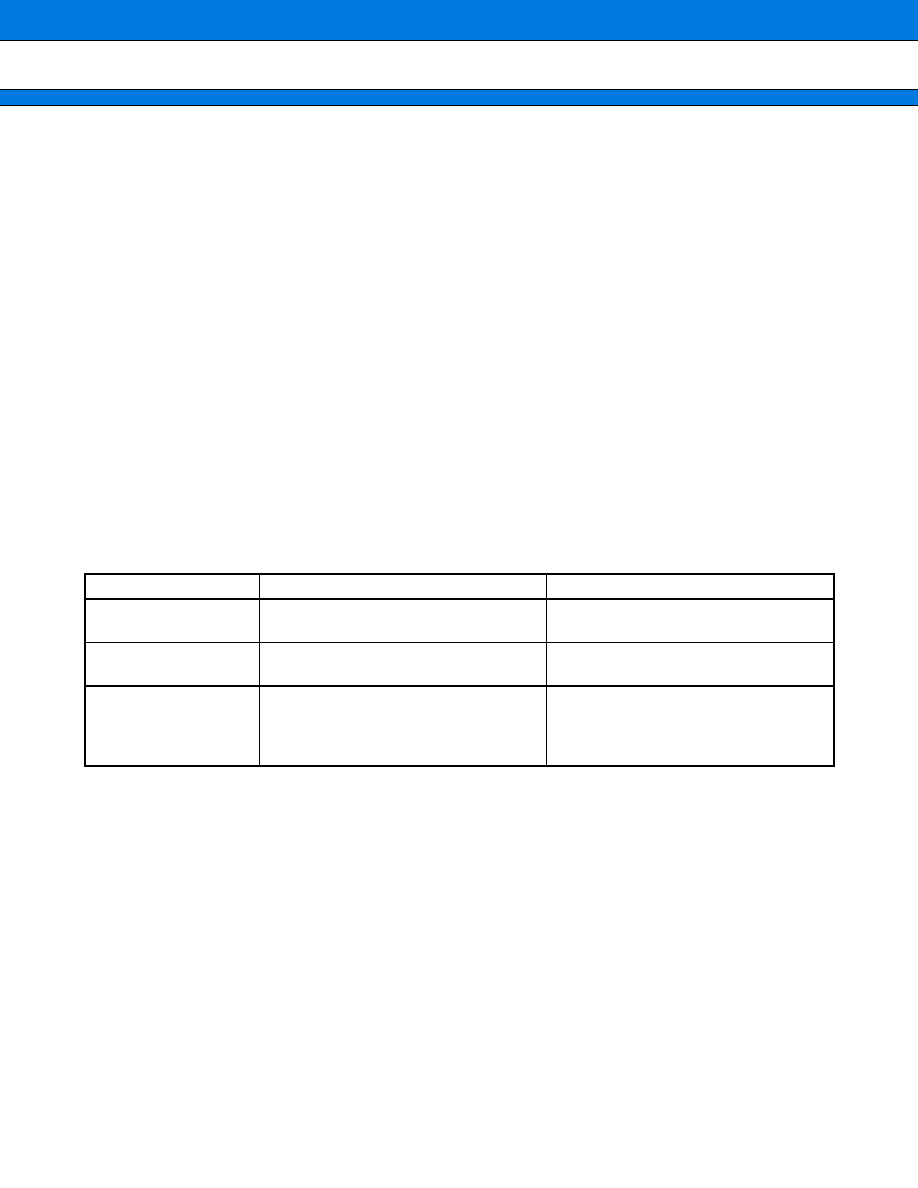

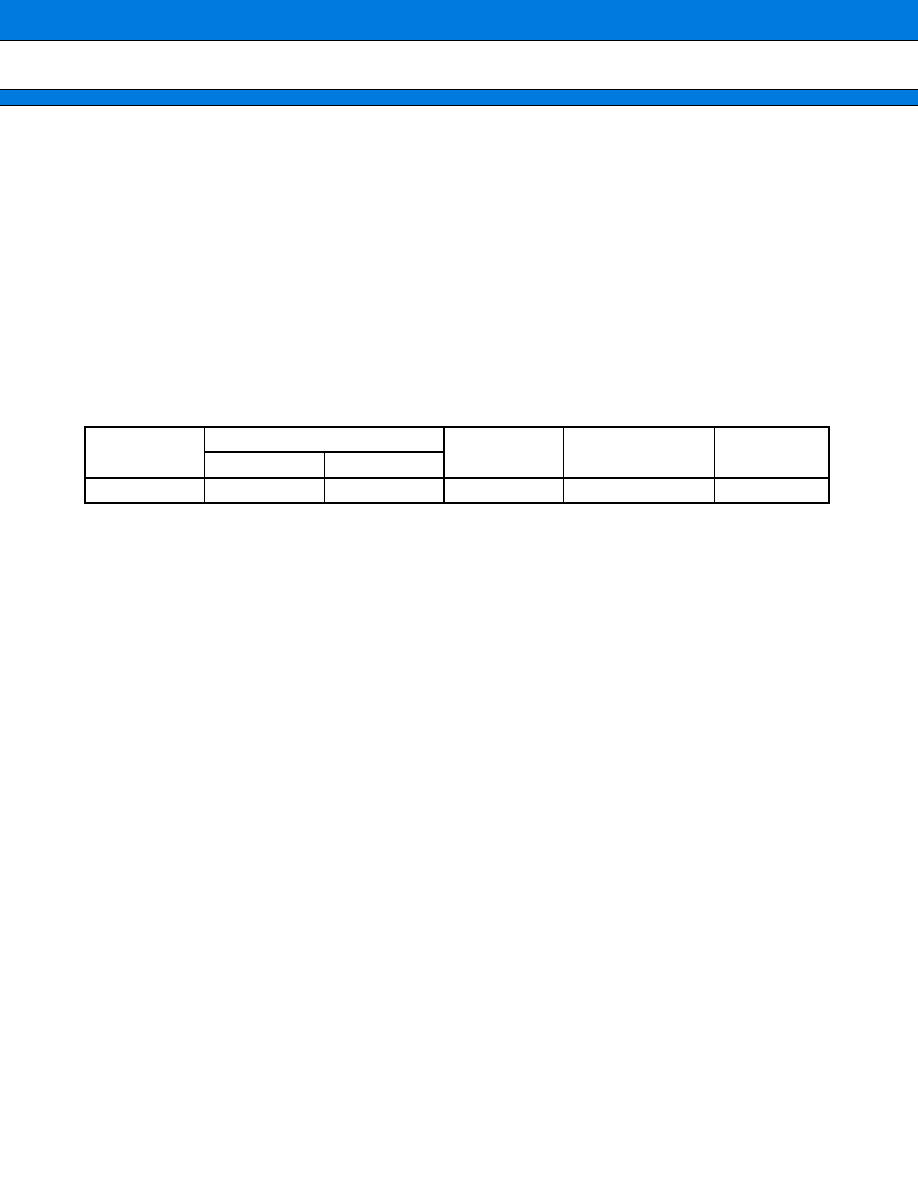

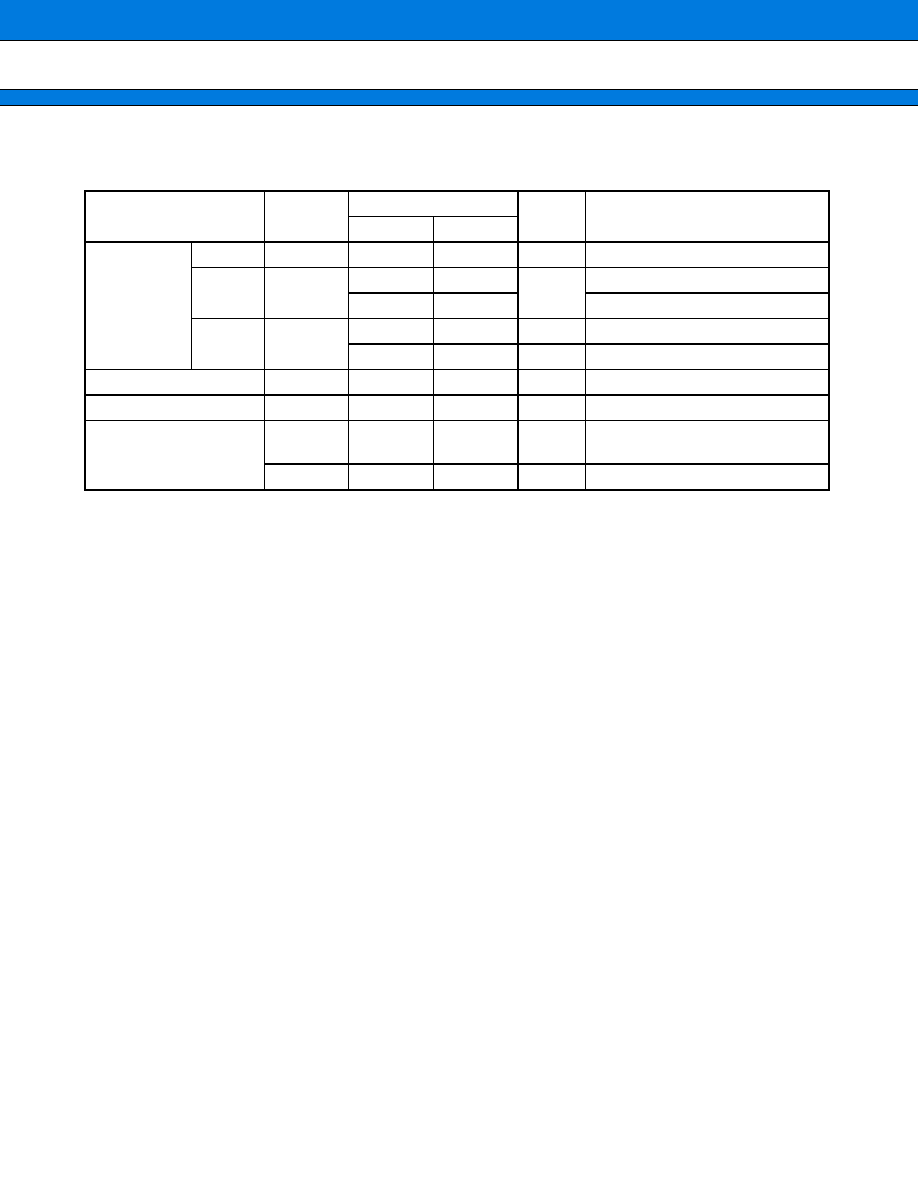

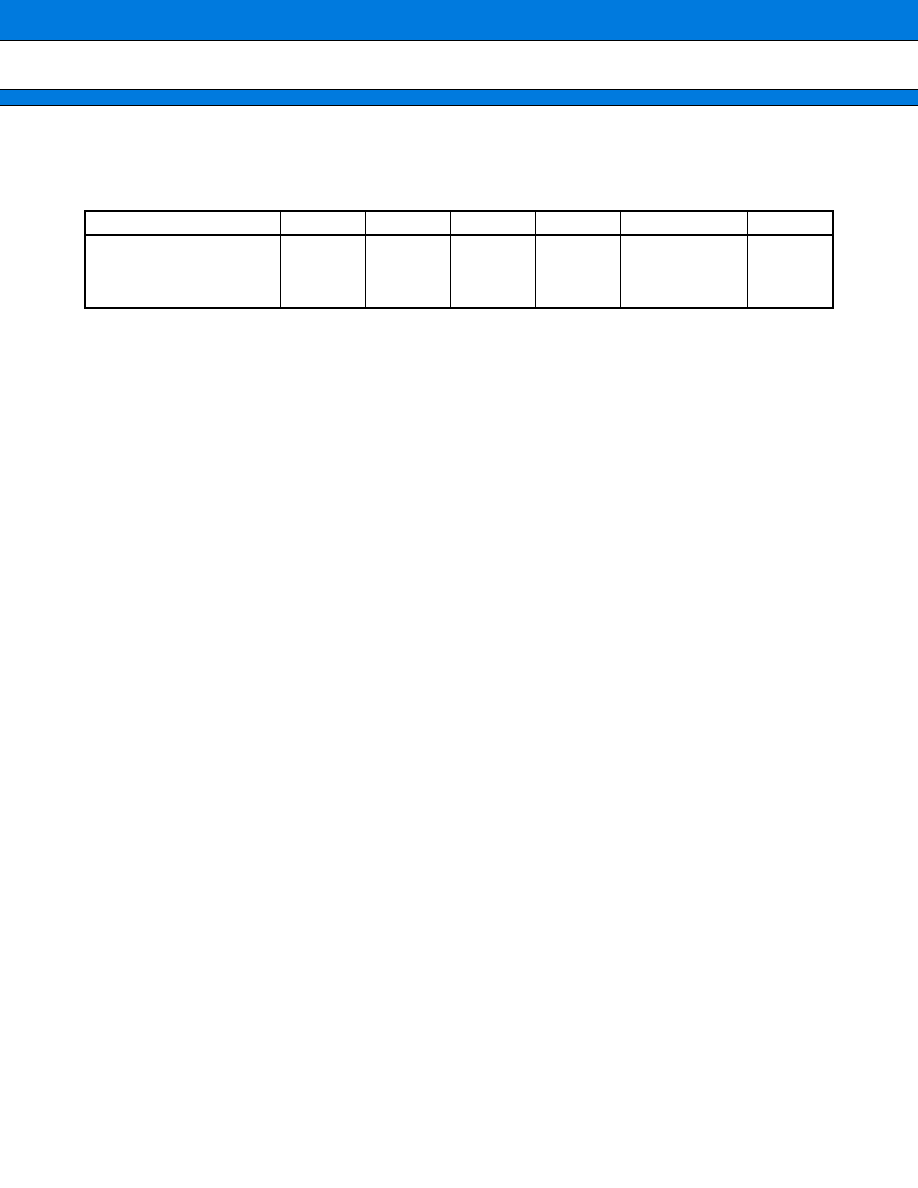

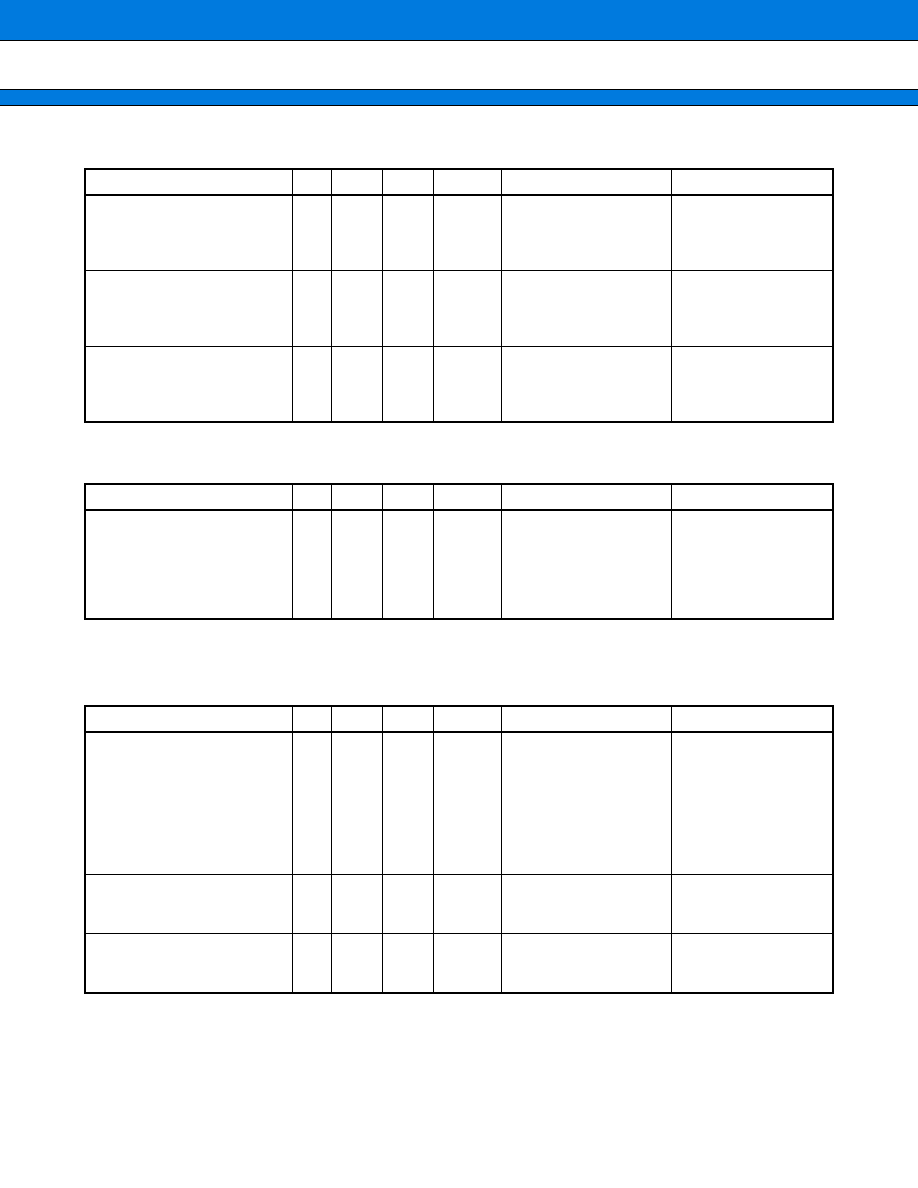

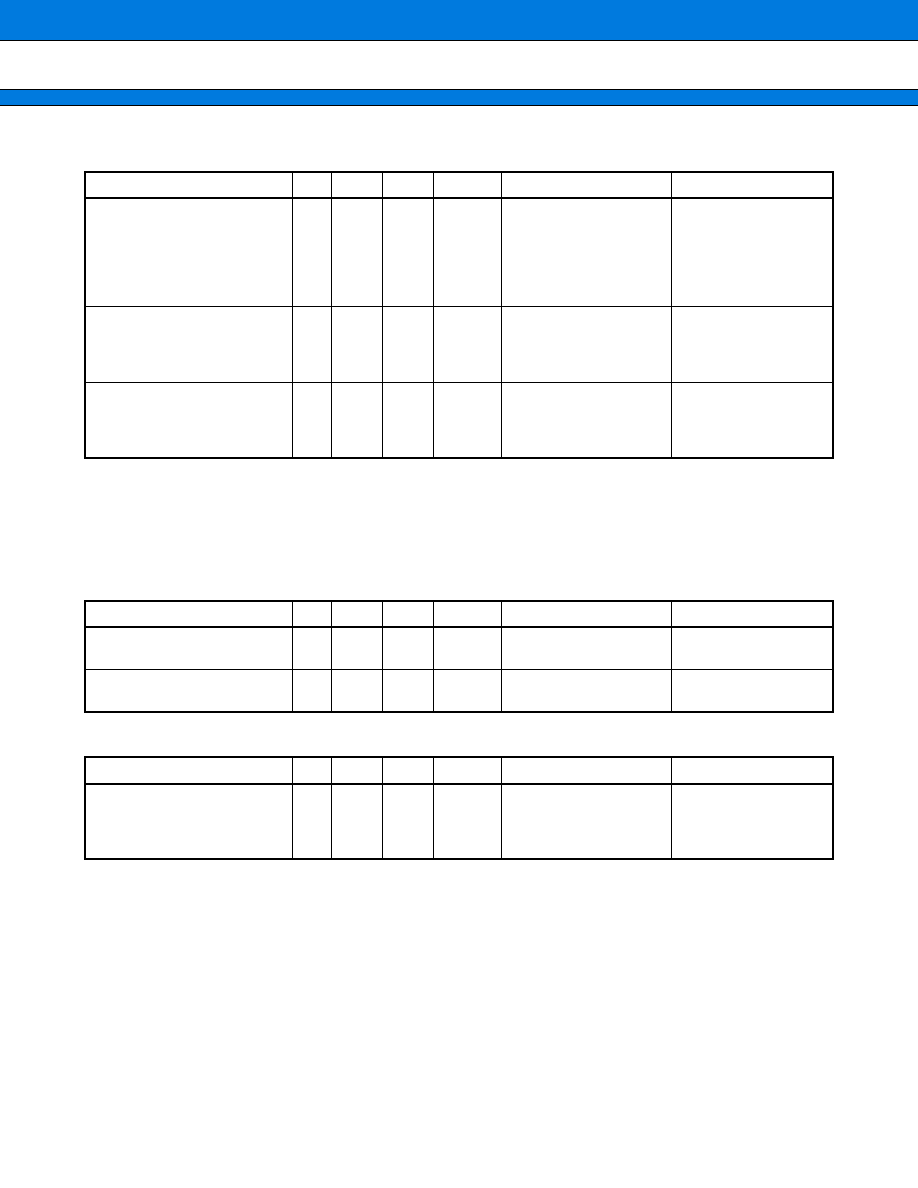

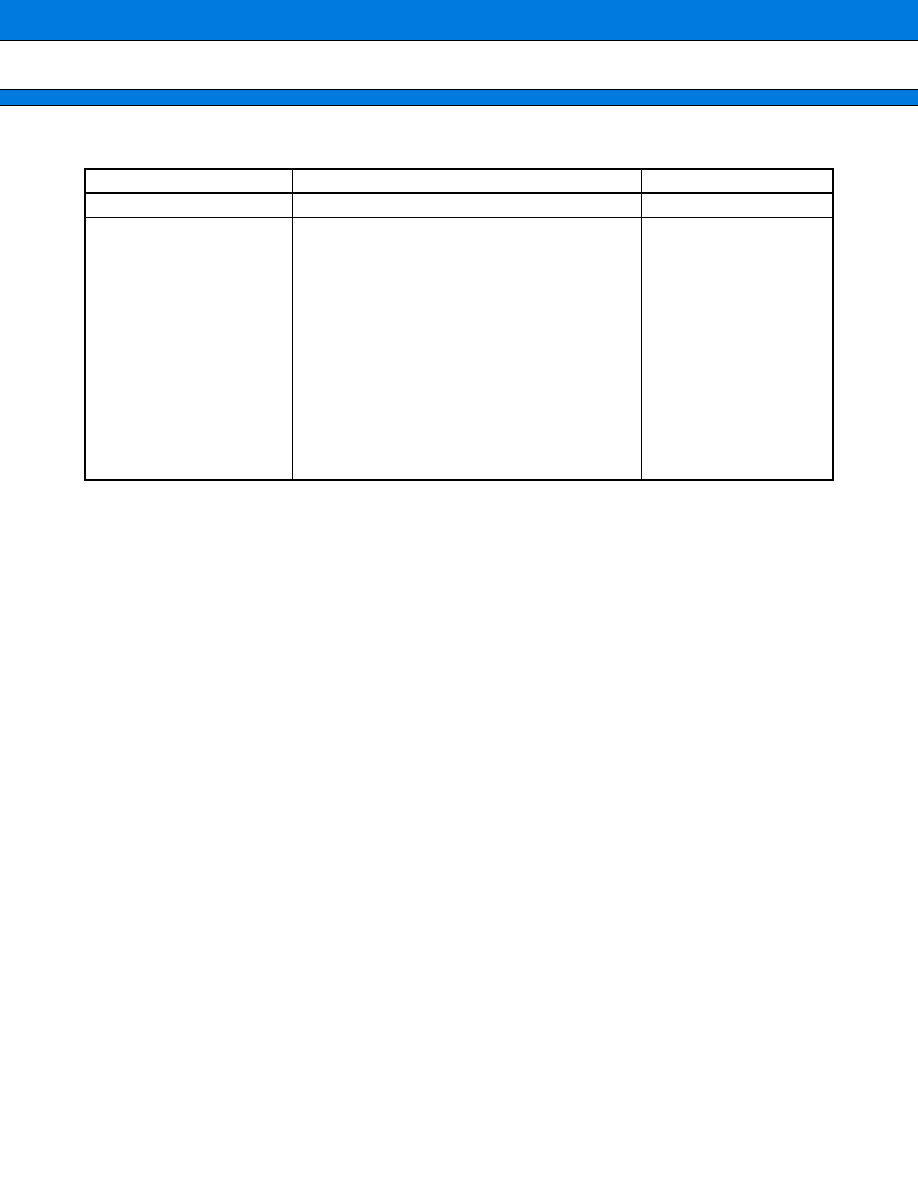

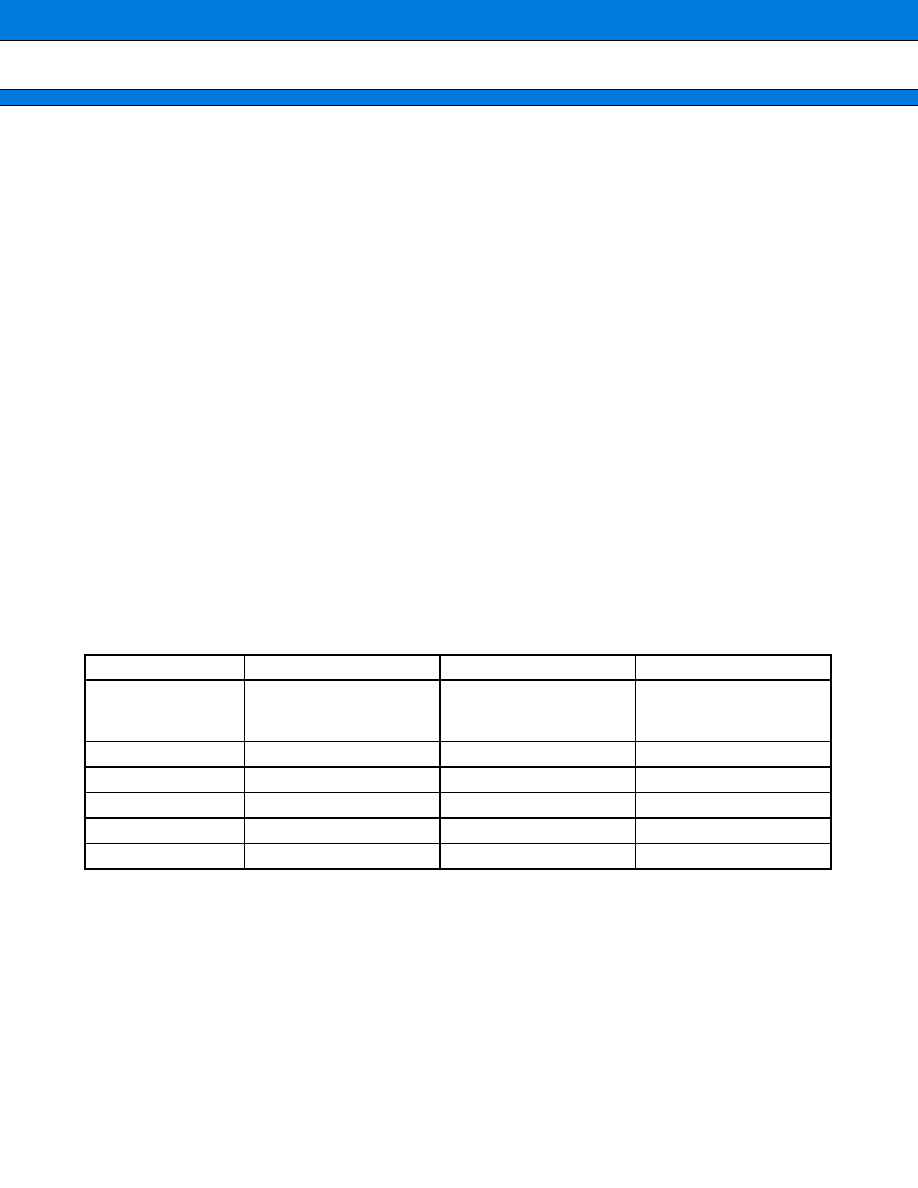

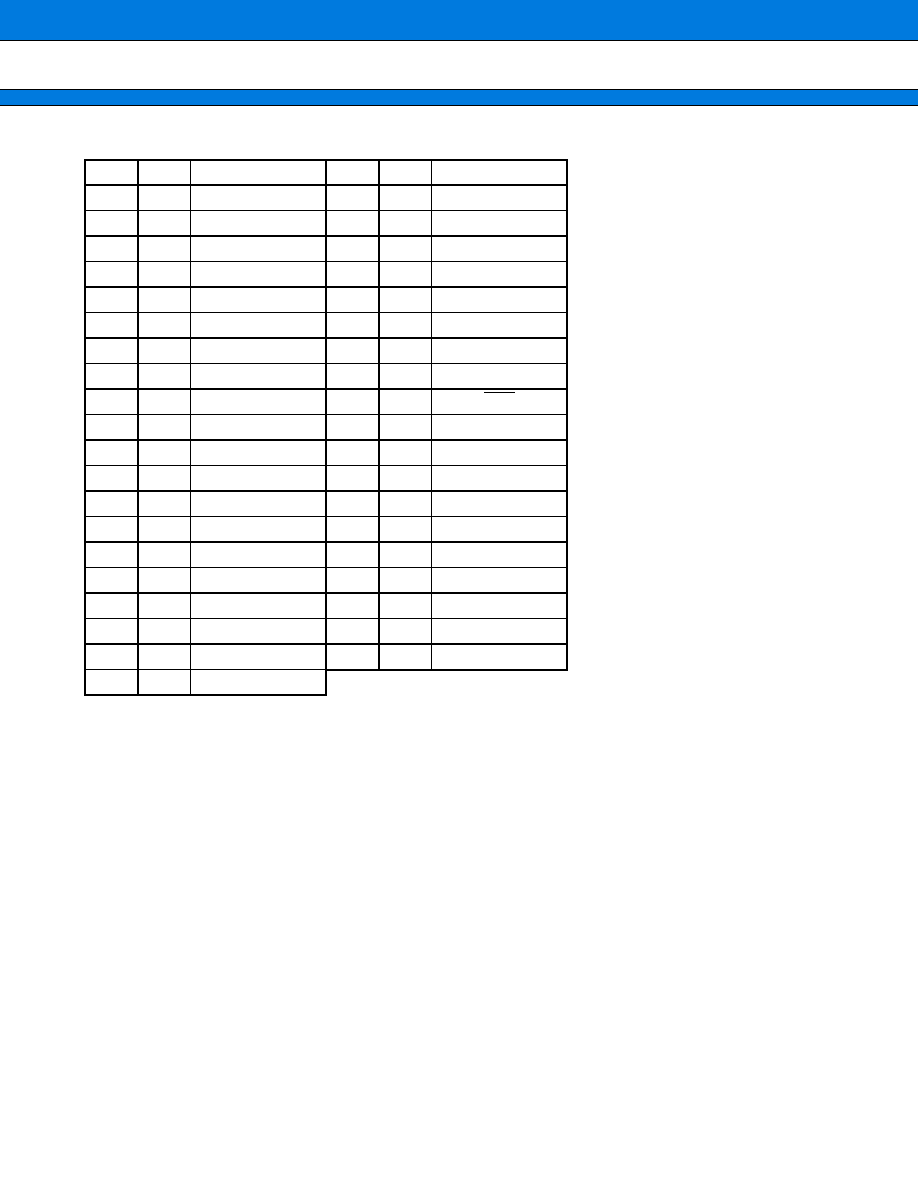

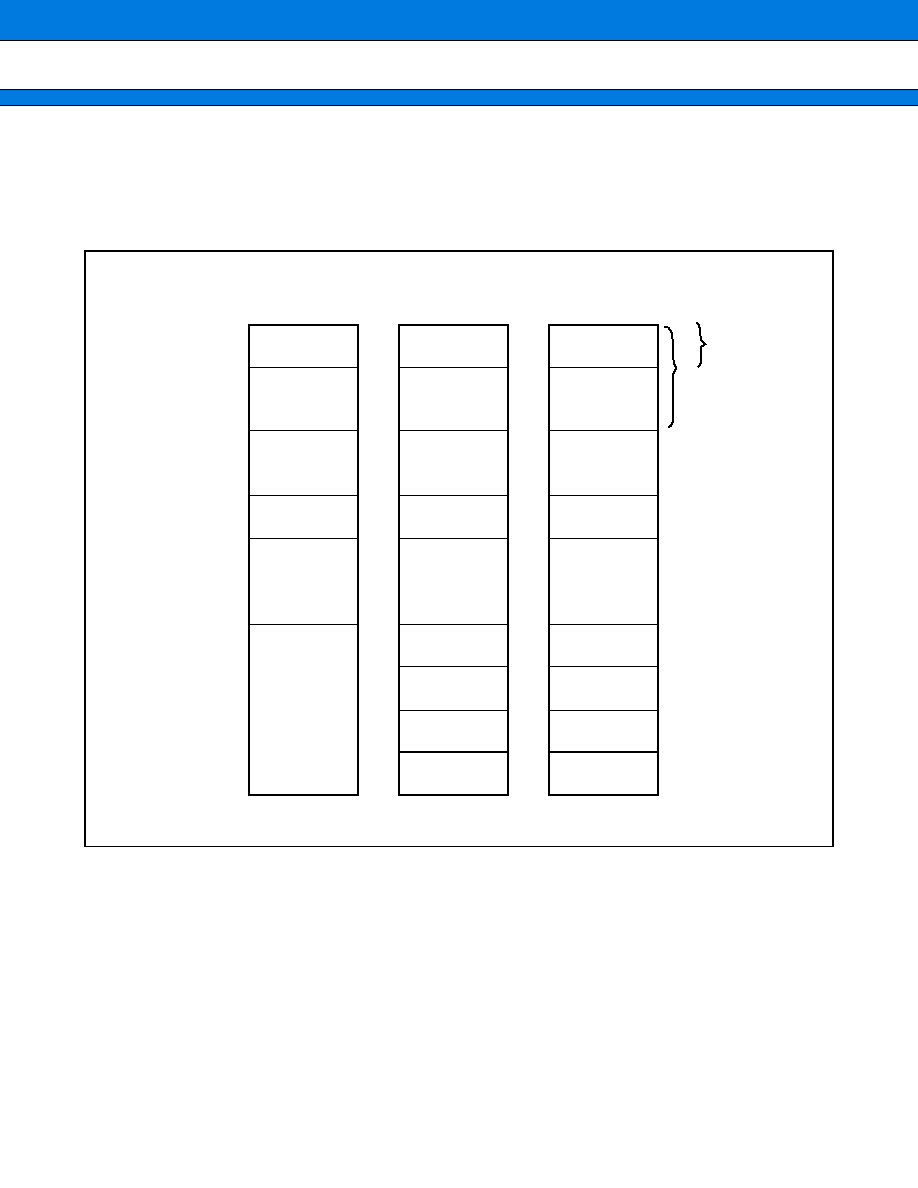

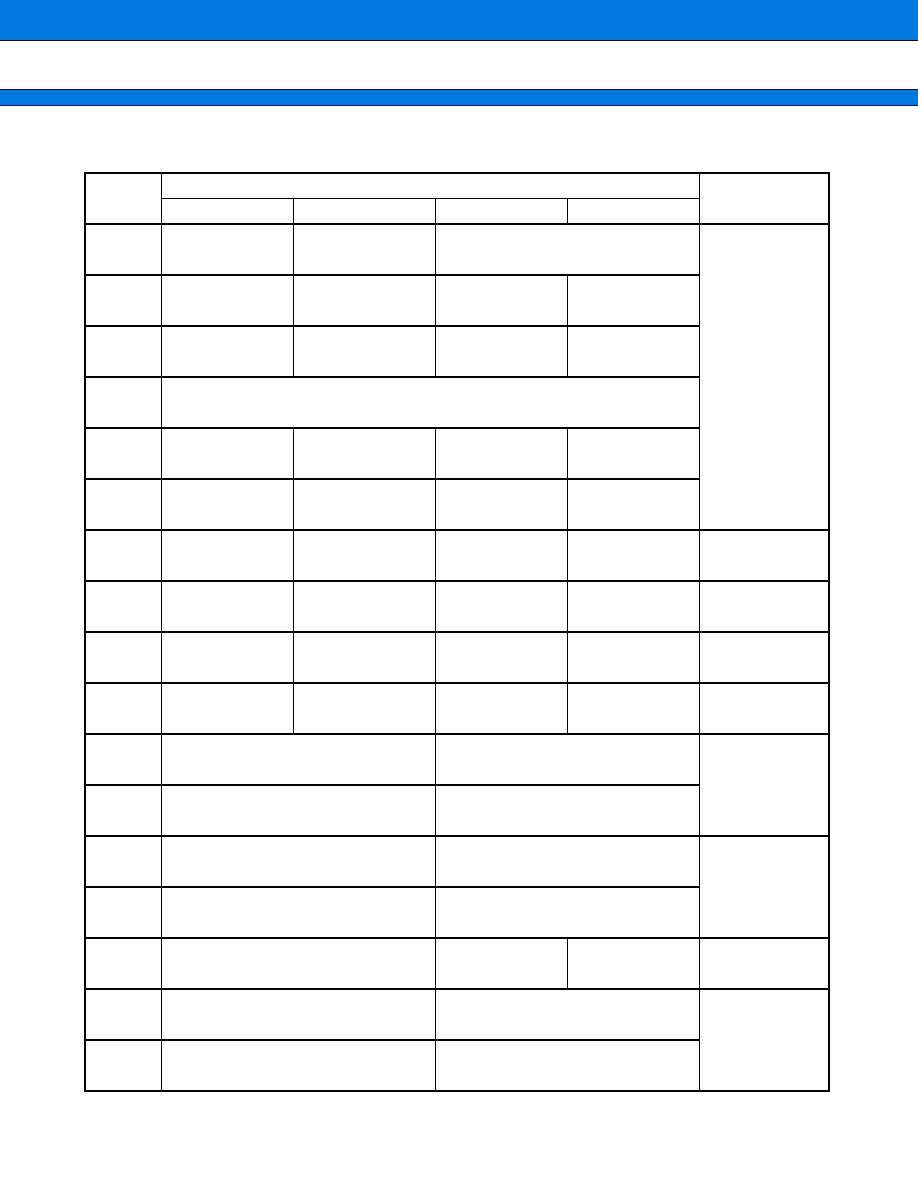

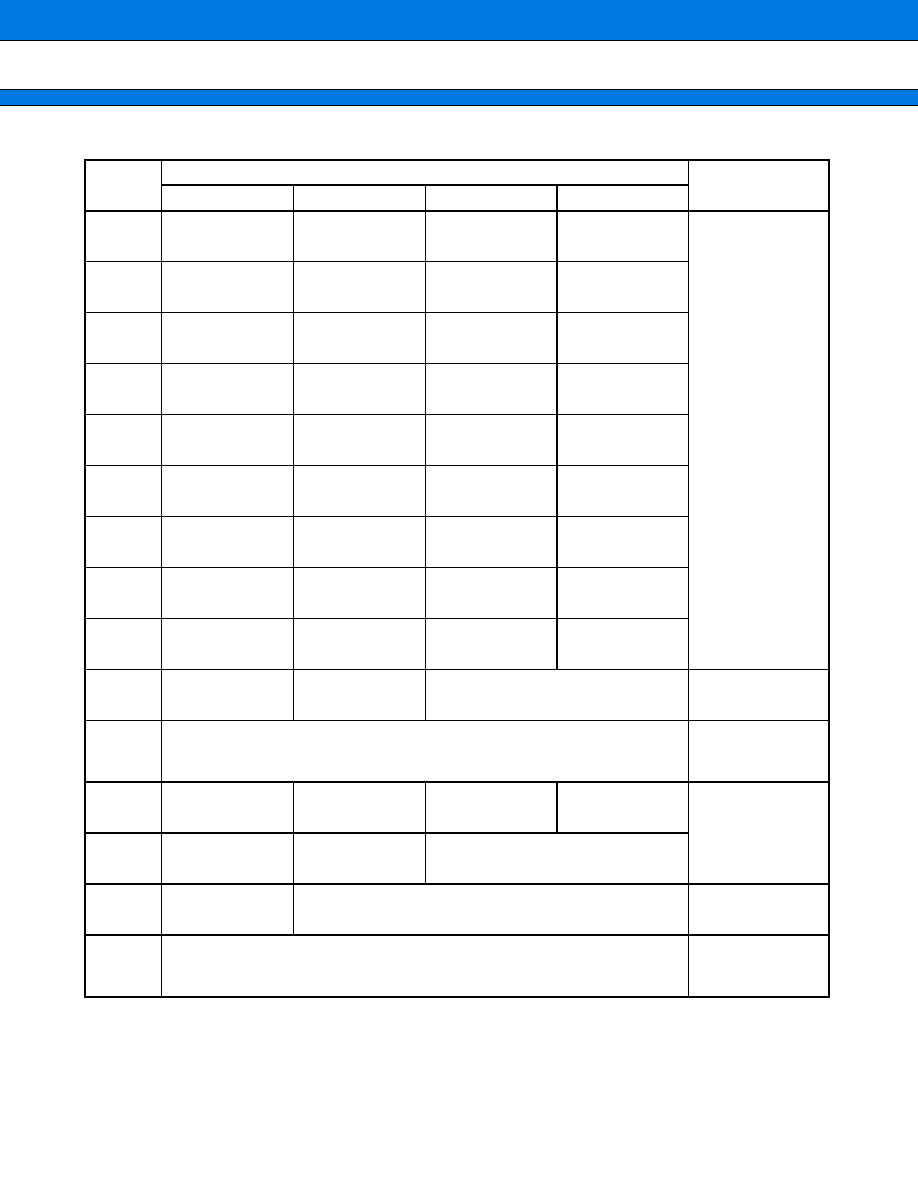

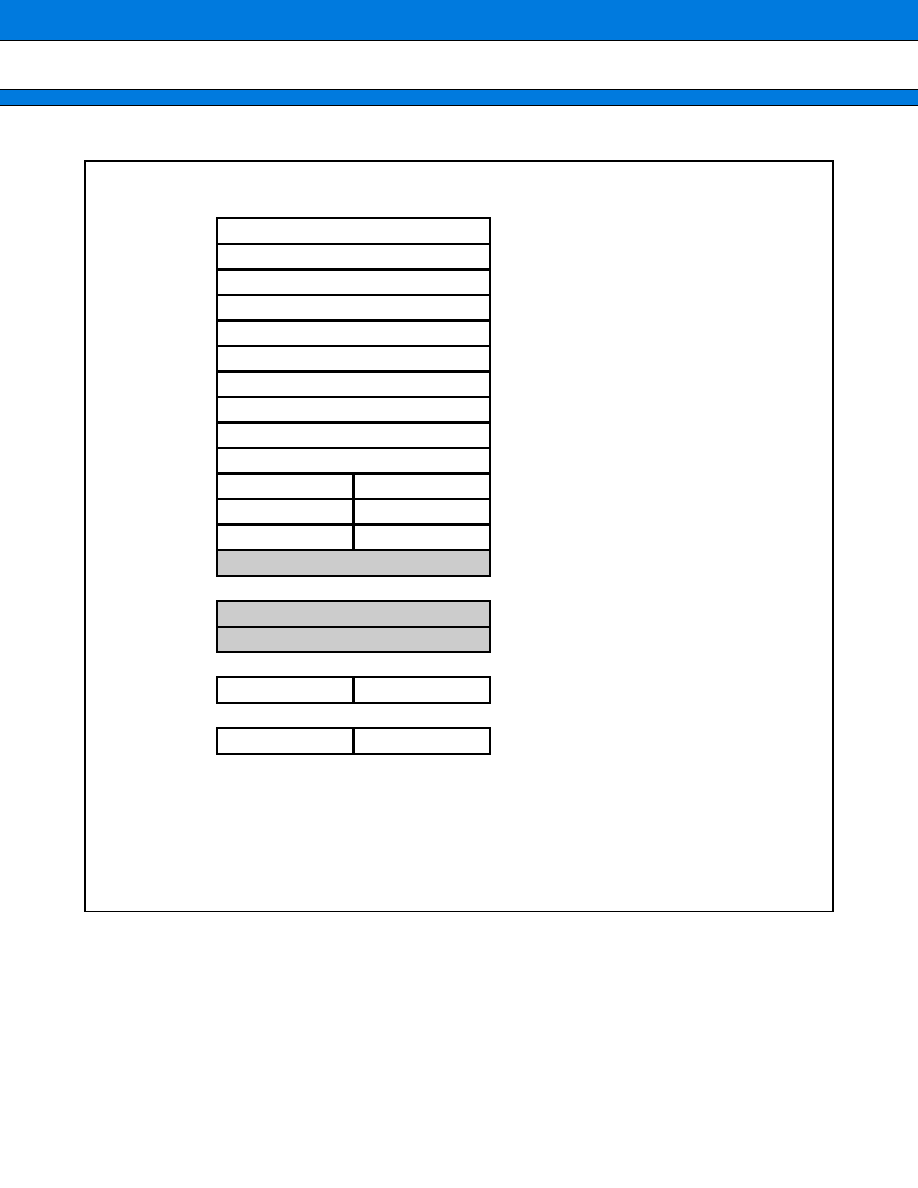

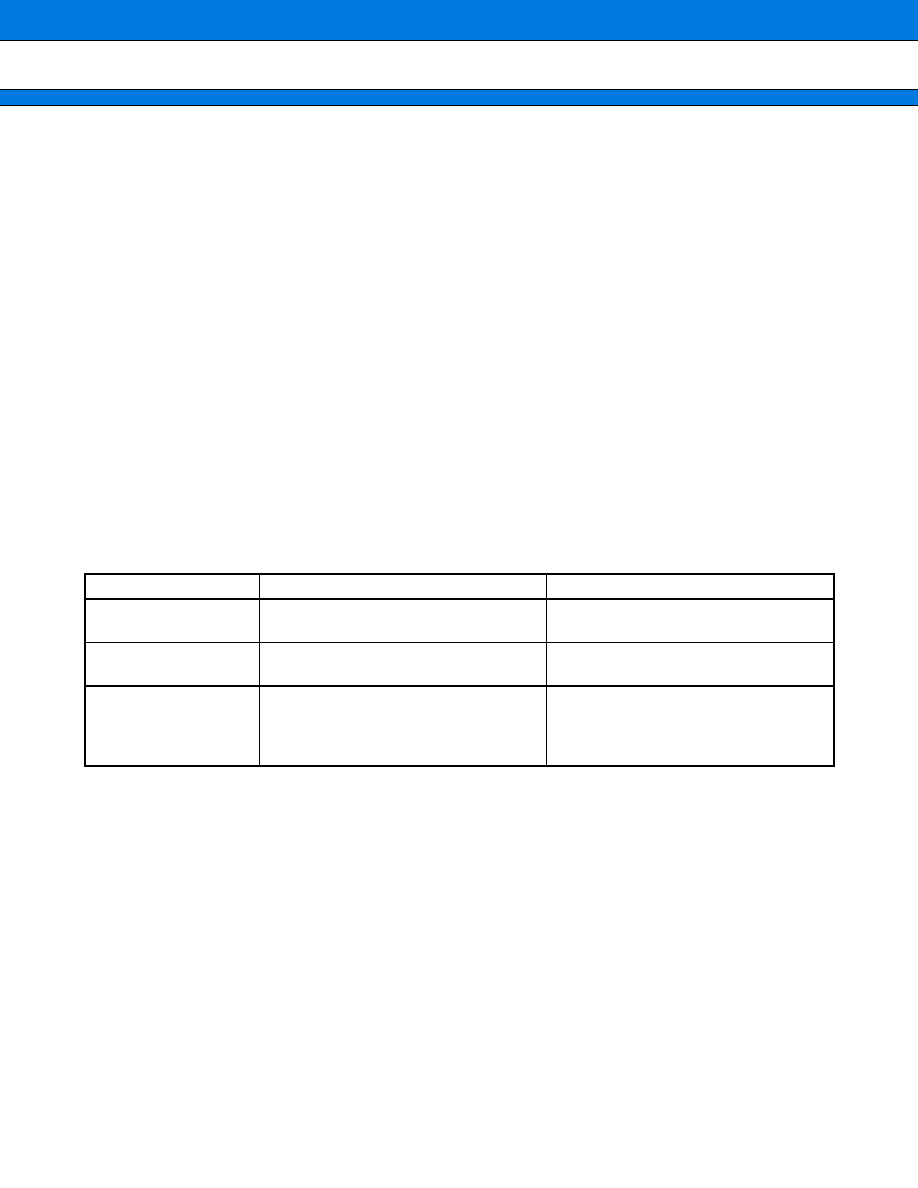

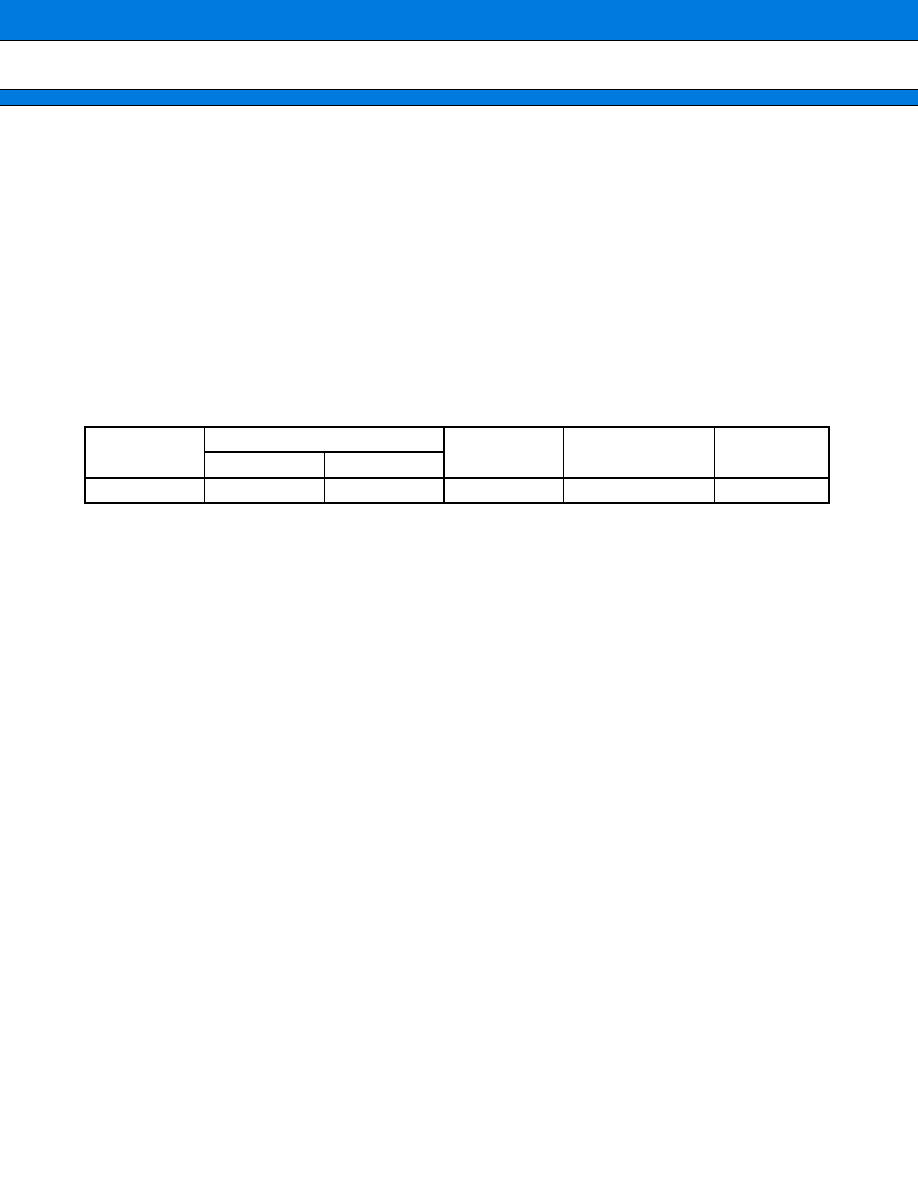

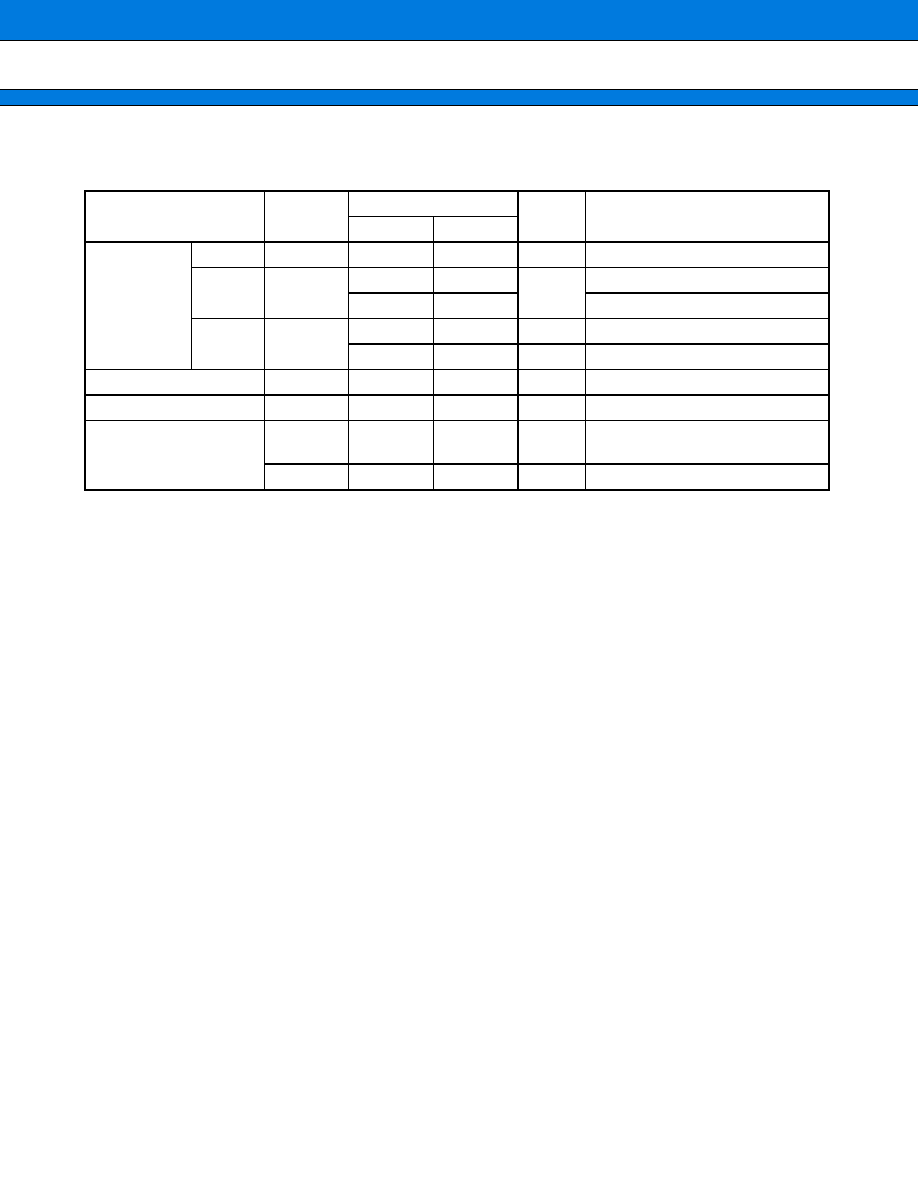

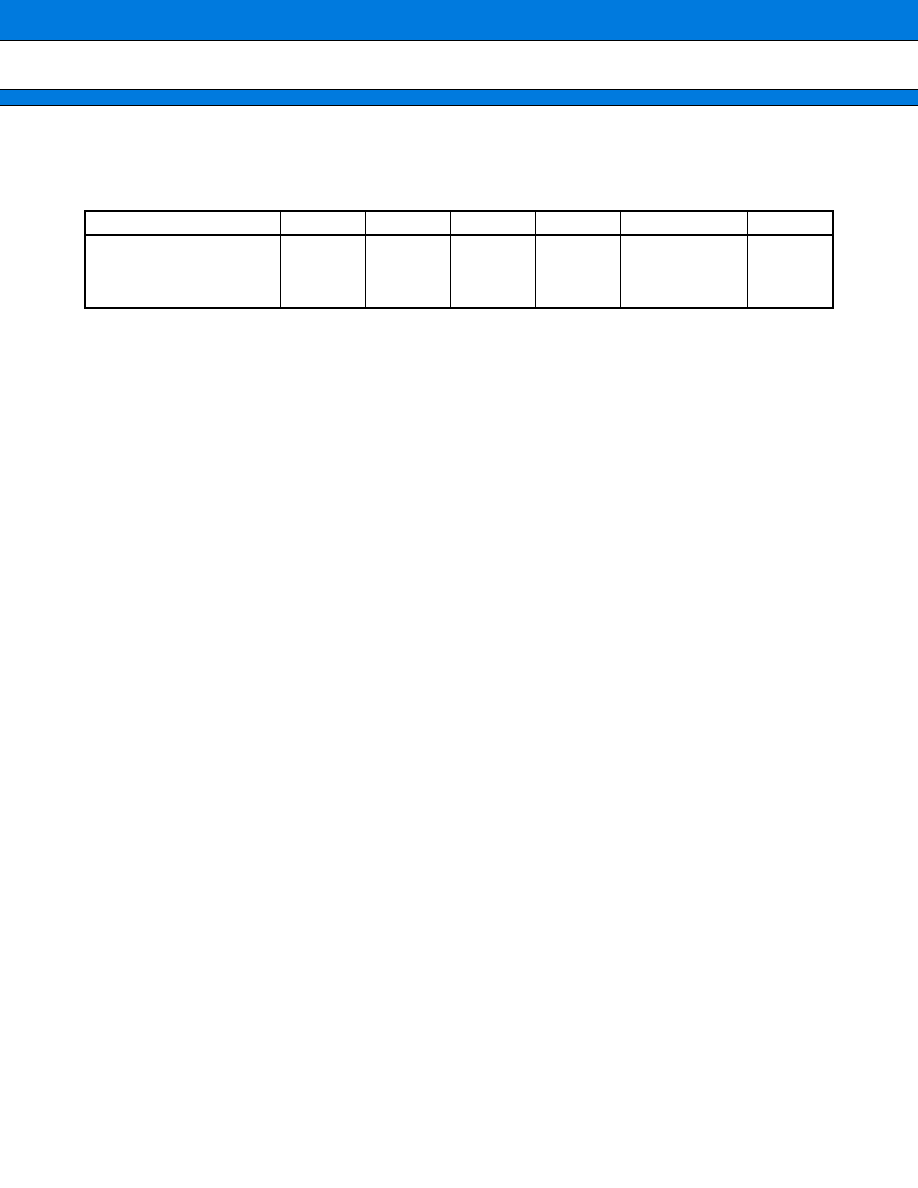

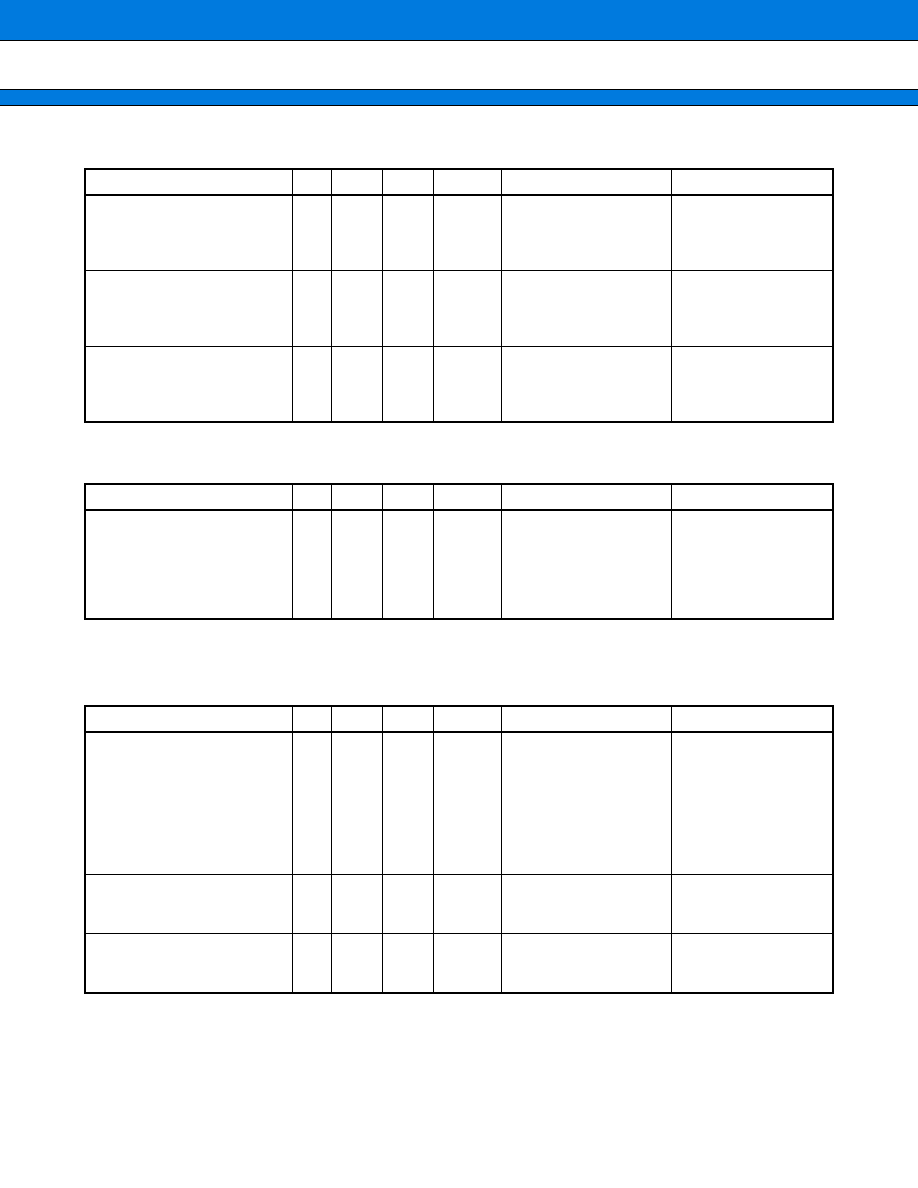

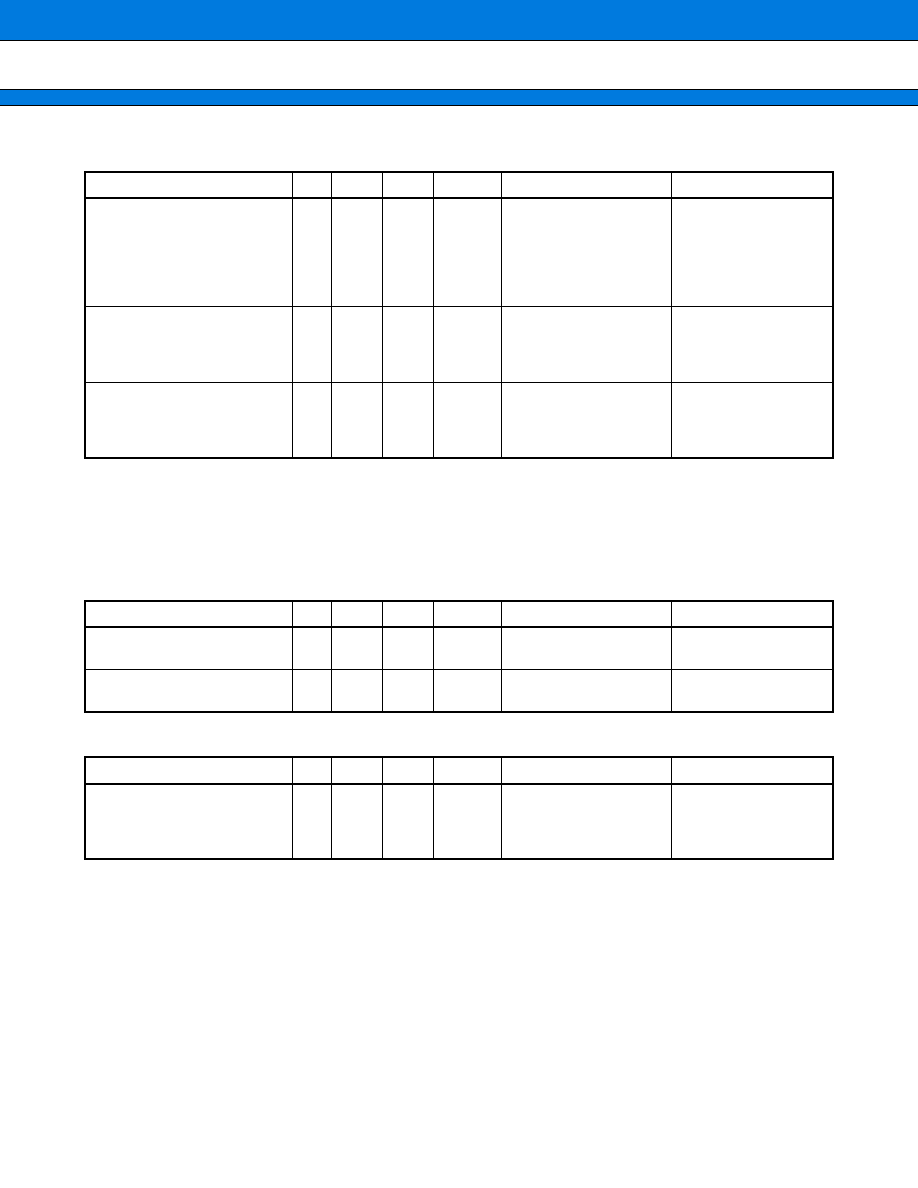

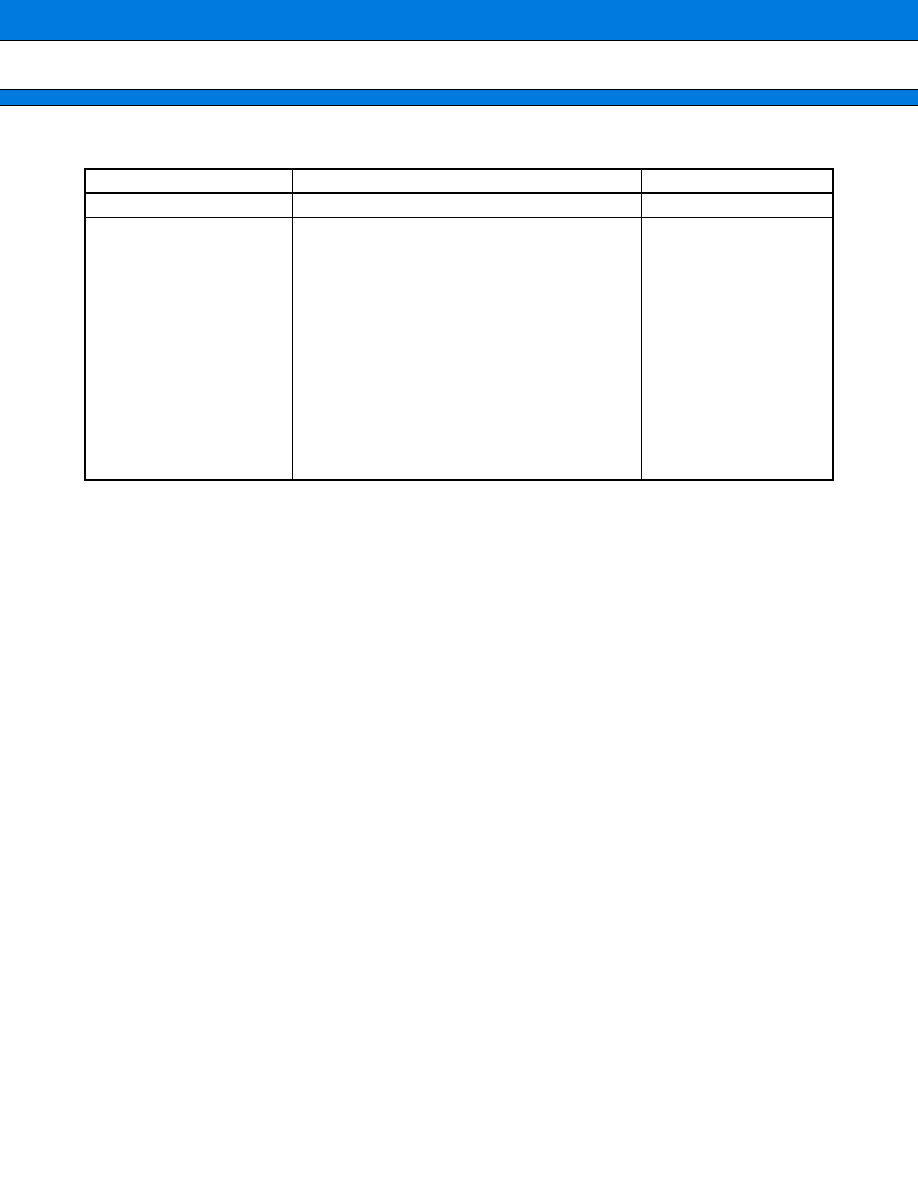

PRODUCT LINEUP

MB91133

MB91F133

MB91FV130

CLASSIFICATION

MASK ROM device

(mass production item)

FLASH ROM device

(for evaluation)

Piggy/EVA device

(for evaluation /

development)

RAM capacity

6 KB

6 KB

6 KB

CROM capacity

254 KB

FLASH capacity

254 KB

254 KB

CRAM capacity

2 KB

2 KB

2 KB

Others

Mass production

Trial production

Provided

MB91133/MB91F133

4

s

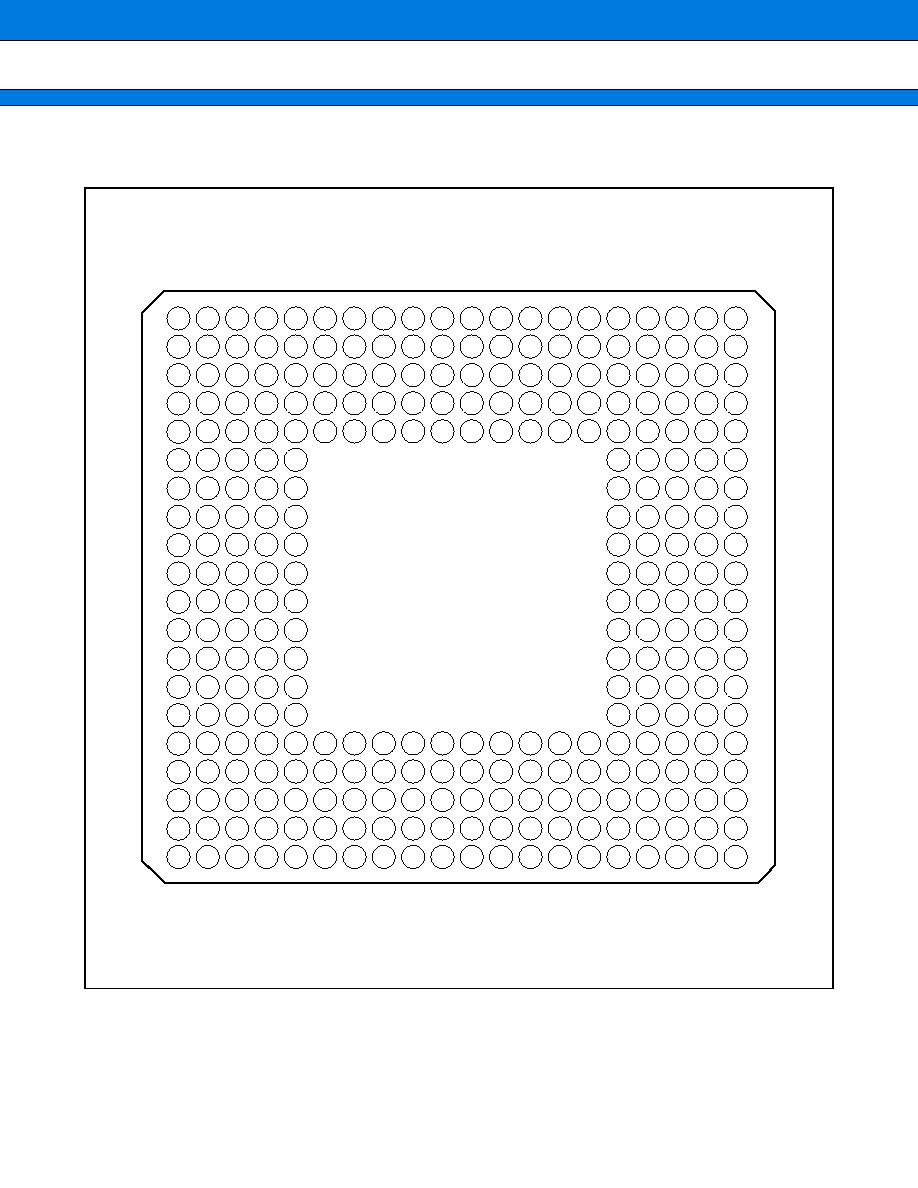

PIN ASSIGNMENTS

∑ MB91FV130

(BOTTOM VIEW)

(PGA-299C-A01)

3

2

5

8

25

27

32

34

22

29

37

50

53

45

49

52

57

68

71

74

299 296 293 277 274 270 268 278 275 262 254 247 257 252 250 245 233 230 224

298 292 289 286 283 280 276 269 264 263 258 251 248 243 240 237 234 225 221

10

4

297 291 287 284 279 271 265 261 256 249 242 239 235 229 228 219 218

13

6

300 295 290 285 281 272 267 259 255 246 241 236 231 226 223 215 207

16

11

7

1

294 288 282 273 266 260 253 244 238 232 227 222 217 212 202

19

15

12

9

220 216 213 209 199

23

18

17

14

214 211 210 205 195

26

24

21

20

208 206 204 201 203

33

31

30

28

198 197 196 194 200

39

38

35

36

192 193 191 190 187

40

41

43

42

186 185 188 189 179

44

46

47

48

178 180 181 183 172

51

54

56

58

170 171 174 176 184

55

60

61

64

164 167 168 173 182

59

63

66

70

159 162 165 169 177

62

67

72

77

82

88

94

103 110 116 123 133 139 145 153 157 161 166 175

65

73

76

81

86

91

96

105 109 117 122 131 136 141 147 151 156 163 158

69

78

79

85

89

92

99

106 111 115 121 129 135 138 142 148 154 160 155

75

84

87

90

93

98

101 108 113 114 119 126 130 134 137 140 144 150 152

80

83

95

100 102 107

97

104 112 125 128 118 120 124 127 132 143 146 149

MB91133/MB91F133

5

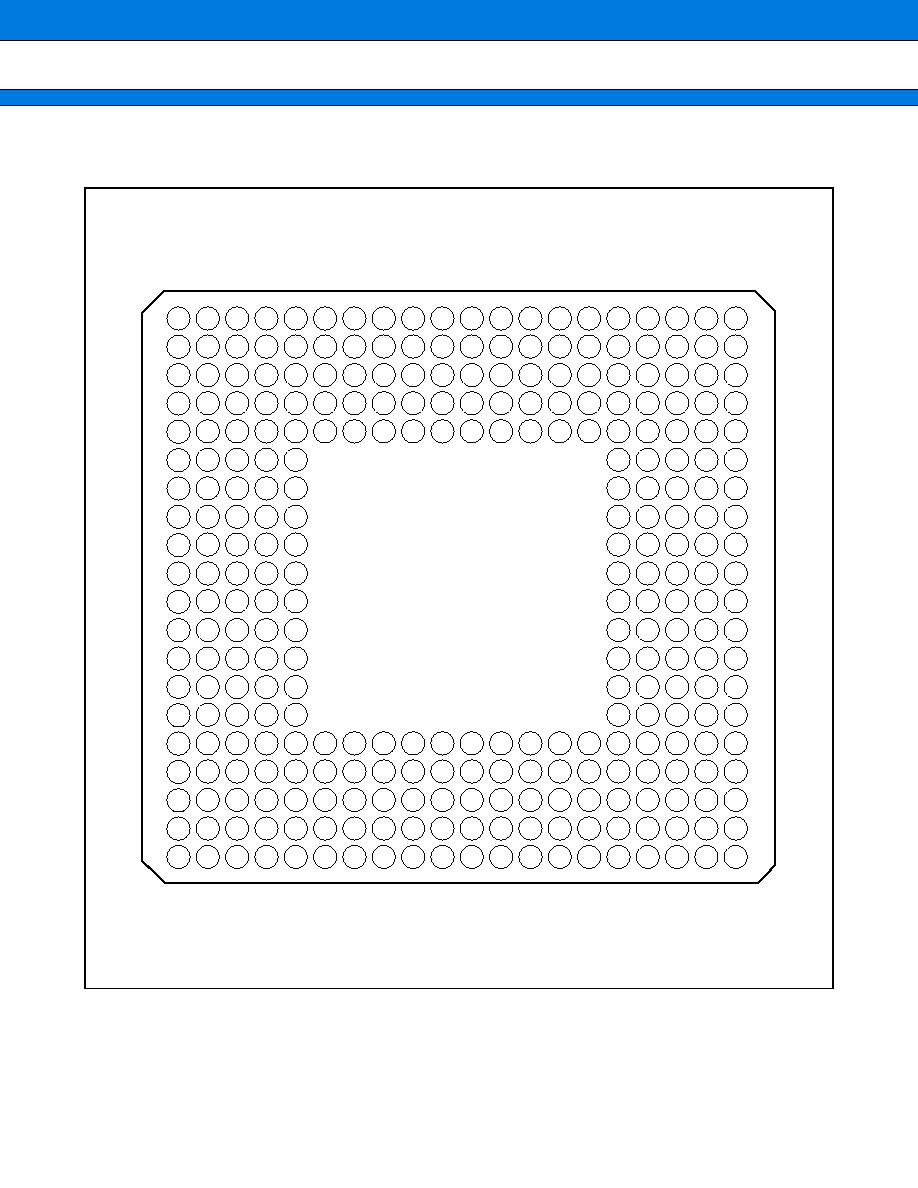

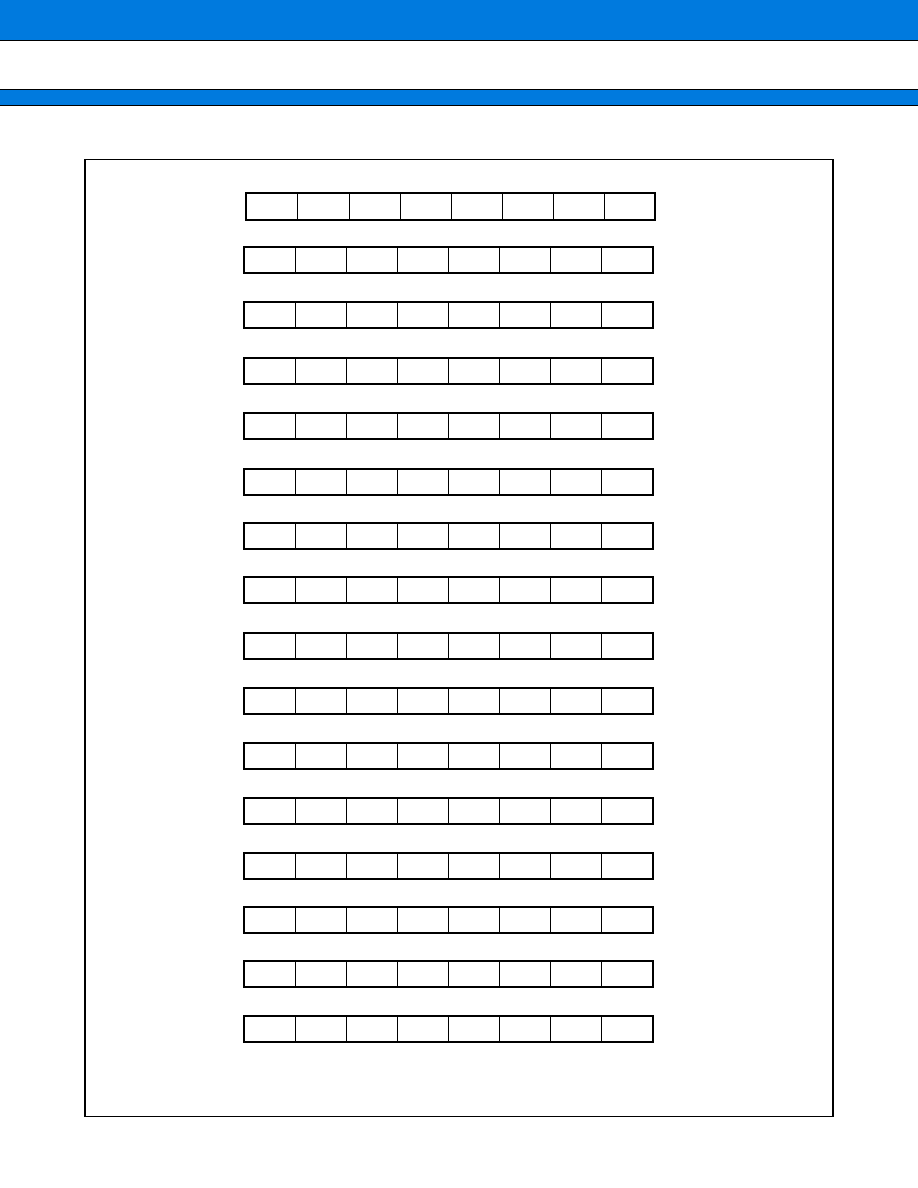

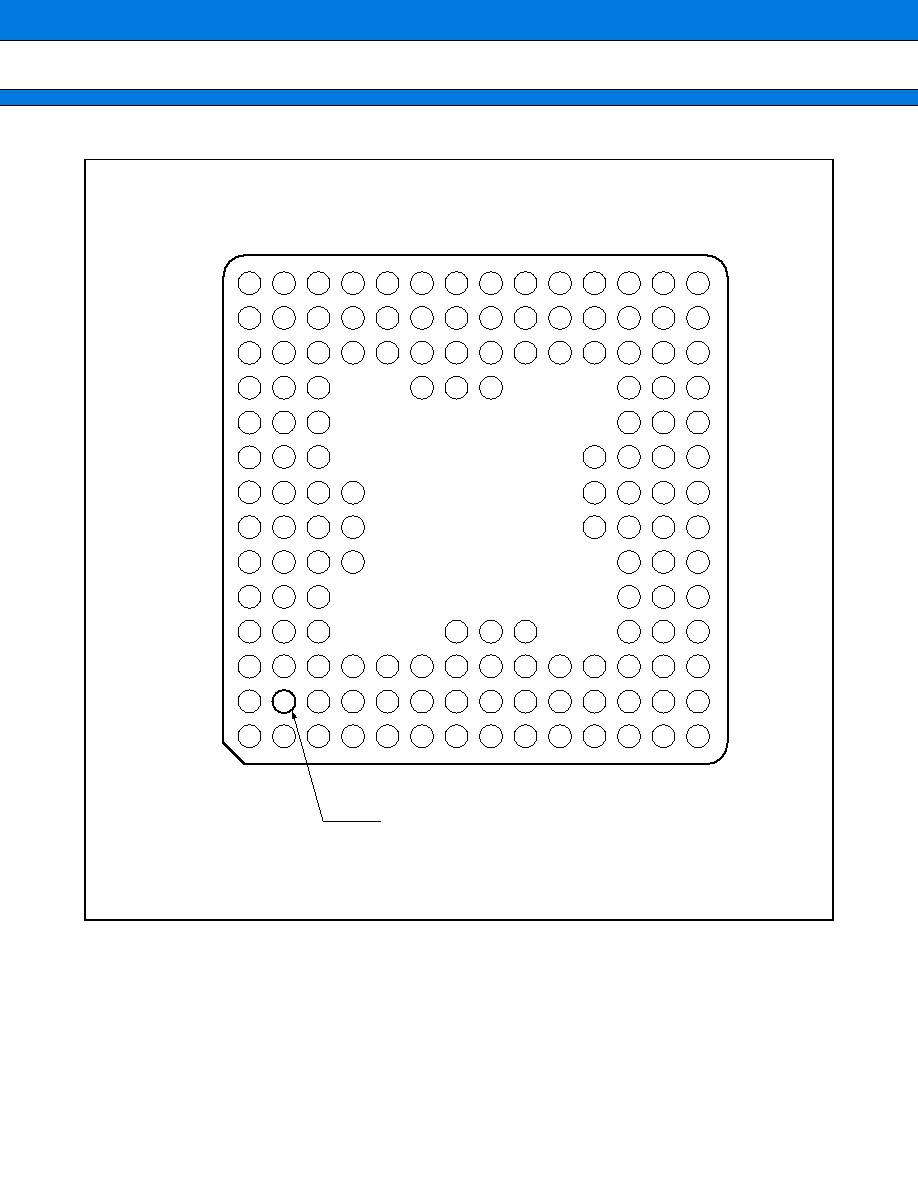

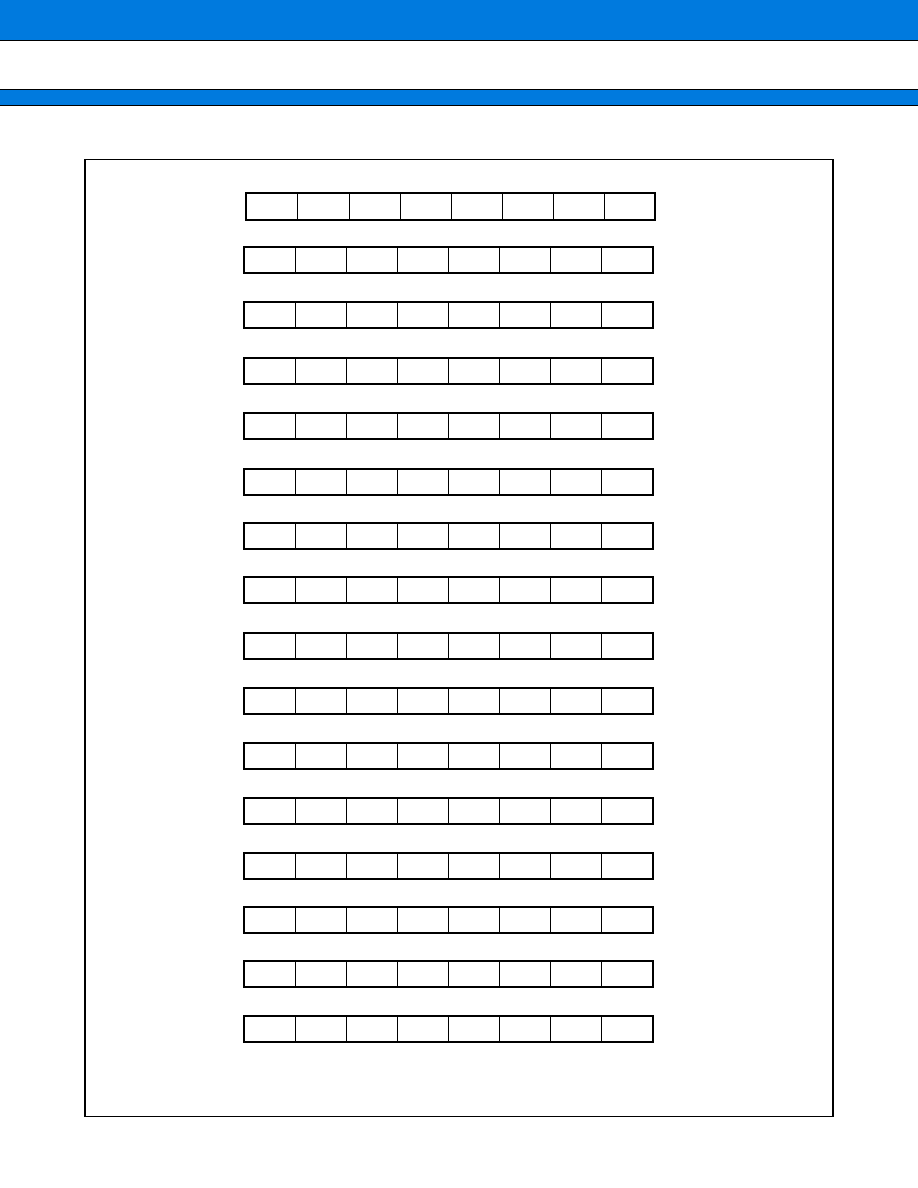

∑ MB91F133/MB91133

(TOP VIEW)

(BGA-144P-M01)

14

13

12

11

10

9

8

7

6

5

4

3

2

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

INDEX

108

107

106

110

109

105

111

112

113

102

103

104

99

100

101

96

97

98

95

92

93

91

94

89

88

90

85

84

86

82

81

83

79

78

80

75

76

77

74

73

69

72

71

70

87

115

114

116

118

117

119

121

120

122

125

124

126

123

128

129

127

130

132

133

134

131

135

136

137

138

139

140

142

141

5

8

143

1

4

6

144

2

3

7

11

9

10

14

12

13

18

15

16

17

19

22

21

20

26

23

25

24

29

28

27

32

31

30

41

44

47

50

54

51

55

58

62

65

68

59

33

34

40

42

45

48

52

57

61

64

67

37

35

39

43

46

49

53

56

60

63

66

38

36

MB91133/MB91F133

6

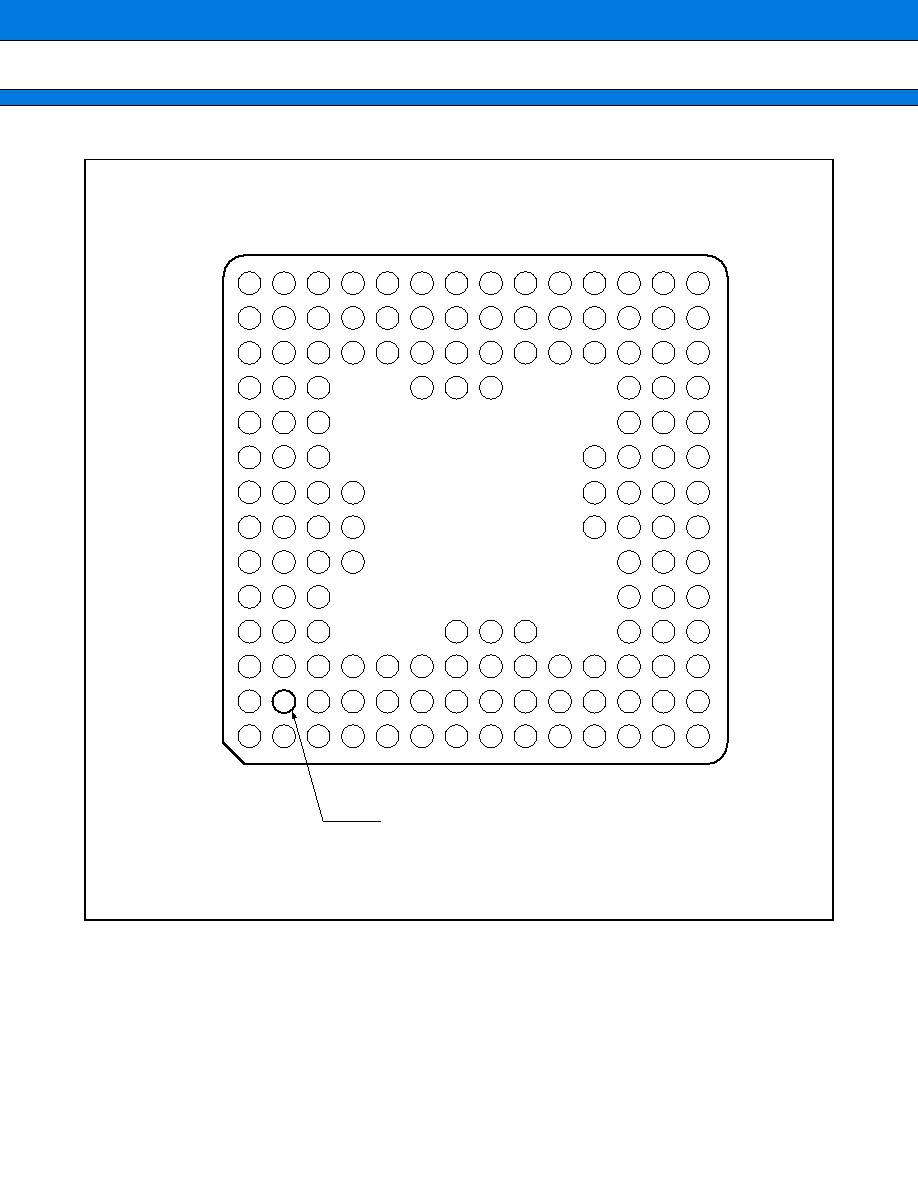

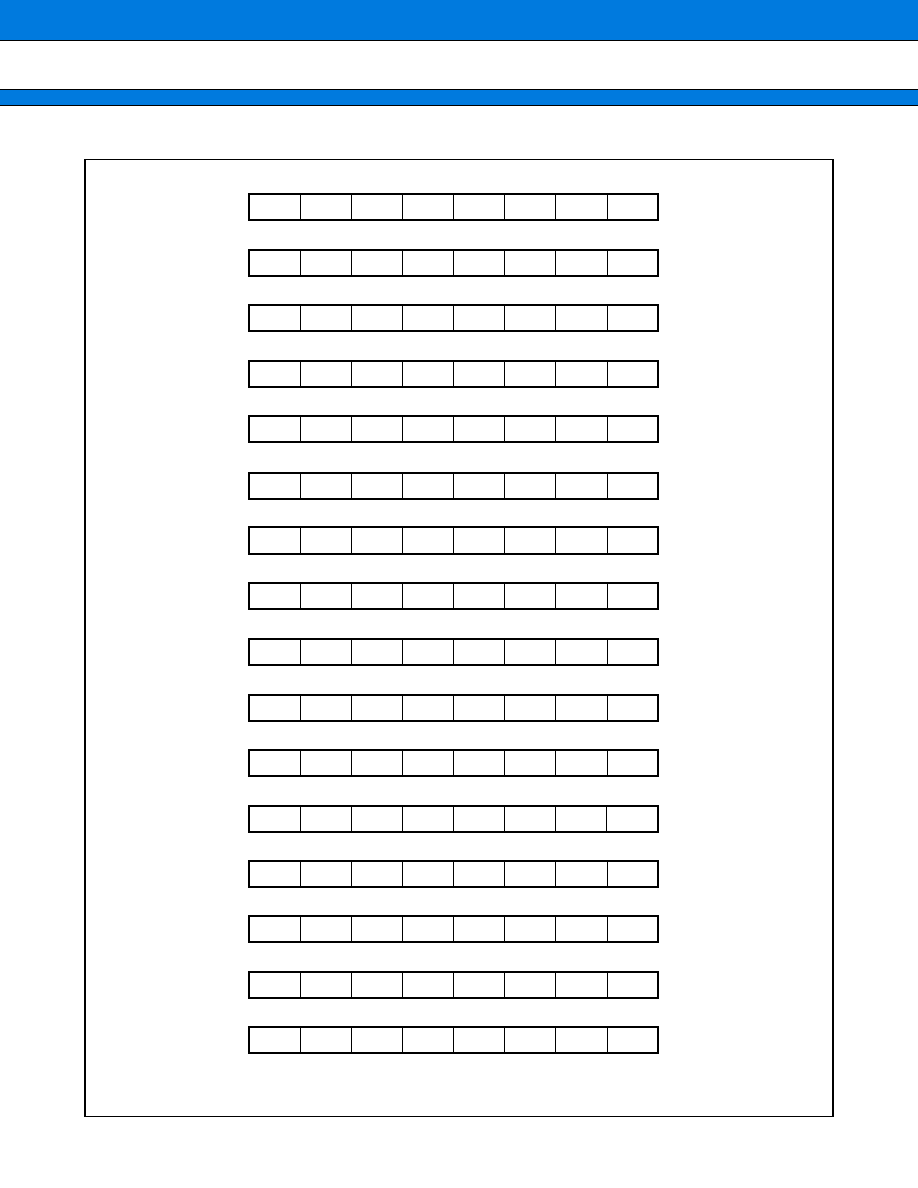

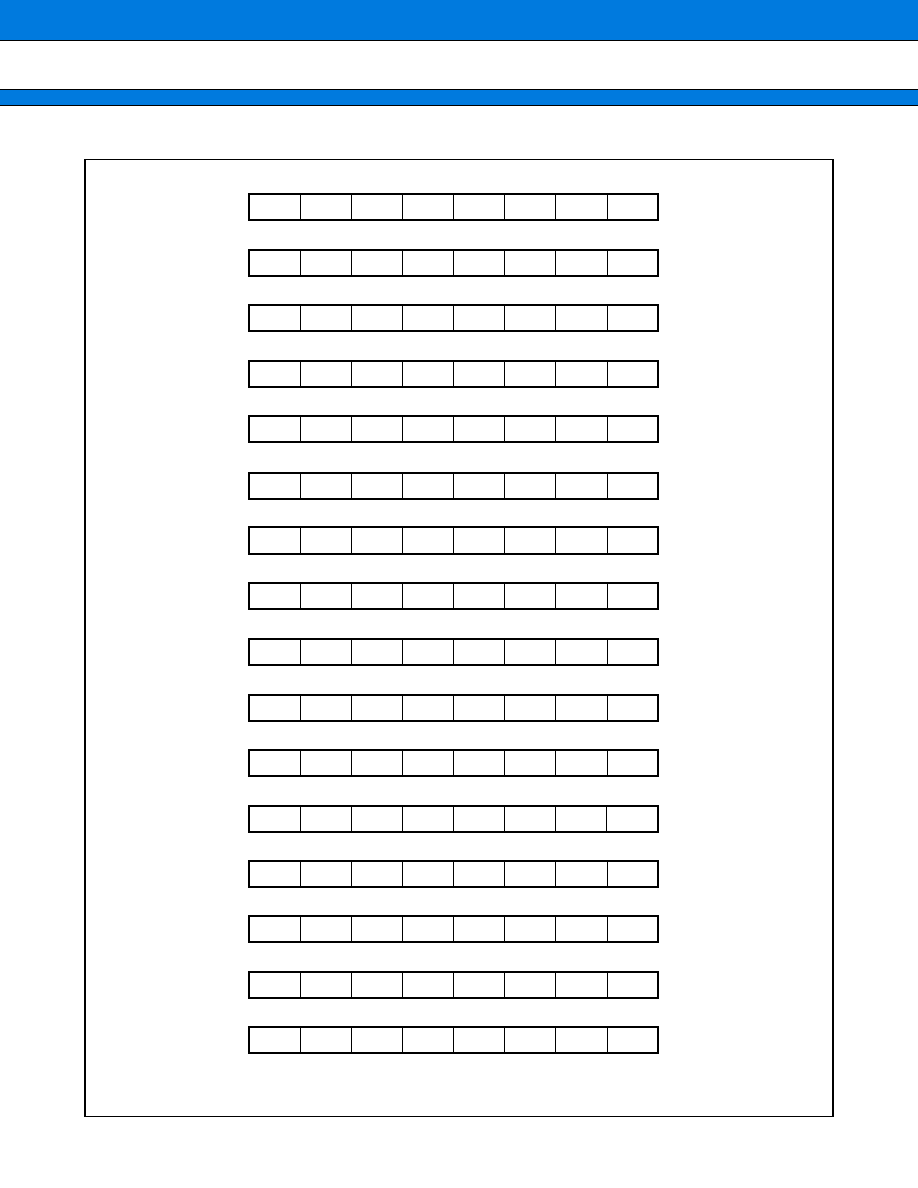

∑ MB91F133/MB91133

(TOP VIEW)

(FPT-144P-M08)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

V

SS

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

P37/D31

P40/A00

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

V

SS

V

CC

5

P50/A08

P51/A09

P52/A10

P53/A11

P54/A12

P55/A13

P56/A14

P57/A15

P60/A16/INT16

MD2

MD1

MD0

V

SS

X1

X0

V

CC

3

X1A

X0A

V

SS

RST

PL7/DACK2

PL6/DREQ2

PL5/DEOP1

PL4/DACK1

PL3/DREQ1

PL2/DEOP0

PL1/DACK0

PL0/DREQ0

PK7/AN7/CMP

PK6/AN6

PK5/AN5

PK4/AN4

PK3/AN3

PK2/AN2

PK1/AN1

PK0/AN0

AV

SS

AVRL

AVRH

AV

CC

DAVC

DAVS

DA0

DA1

DA2

V

CC

5

PH0/SIN0

PH1/SOT0

PH2/SCK0

PI0/SIN1

PI1/SOT1

PI2/SCK1

PI3/SIN2

PI4/SOT2

PI5/SCK2

PJ0/SIN3

PJ1/SOT3

PJ2/SCK3

PJ3/SIN4

PJ4/SOT4

PJ5/SCK4

V

CC

3

V

SS

PG5/PPG5

PG4/PPG4

PG3/PPG3

PG2/PPG2

PG1/PPG1

PG0/PPG0

PF7/RTO7

PF6/RTO6

PF5/RTO5

PF4/RTO4

PF3/RTO3

PF2/RTO2

PF1/RTO1

PF0/RTO0

PE7/DTTI

PE6/FRCK

PE5/IN3

PE4/IN2

P61/A17/INT17

P62/A18/INT18

P63/A19/INT19

P64/A20/INT20

P65/A21/INT21

P66/A22/INT22

P67/A23/INT23

V

CC

3

P80/RDY

P81/BGRNT

P82/BRQ

P83/RD

P84/WR0

P85/WR1

P86/CLK

V

SS

PC0/INT0

PC1/INT1

PC2/INT2

PC3/INT3

PC4/AIN0/INT4

PC5/BIN0/INT5

PC6/AIN1/INT6

PC7/BIN1/INT7

PD0/INT8/TRG0

PD1/INT9/TRG1

PD2/INT10/TRG2

PD3/INT11/TRG3

PD4/INT12/TRG4

PD5/INT13/TRG5

PD6/DEOP2/INT14

PD7/ATG/INT15

PE0/ZIN0

PE1/ZIN1

PE2/IN0

PE3/IN1

MB91133/MB91F133

7

s

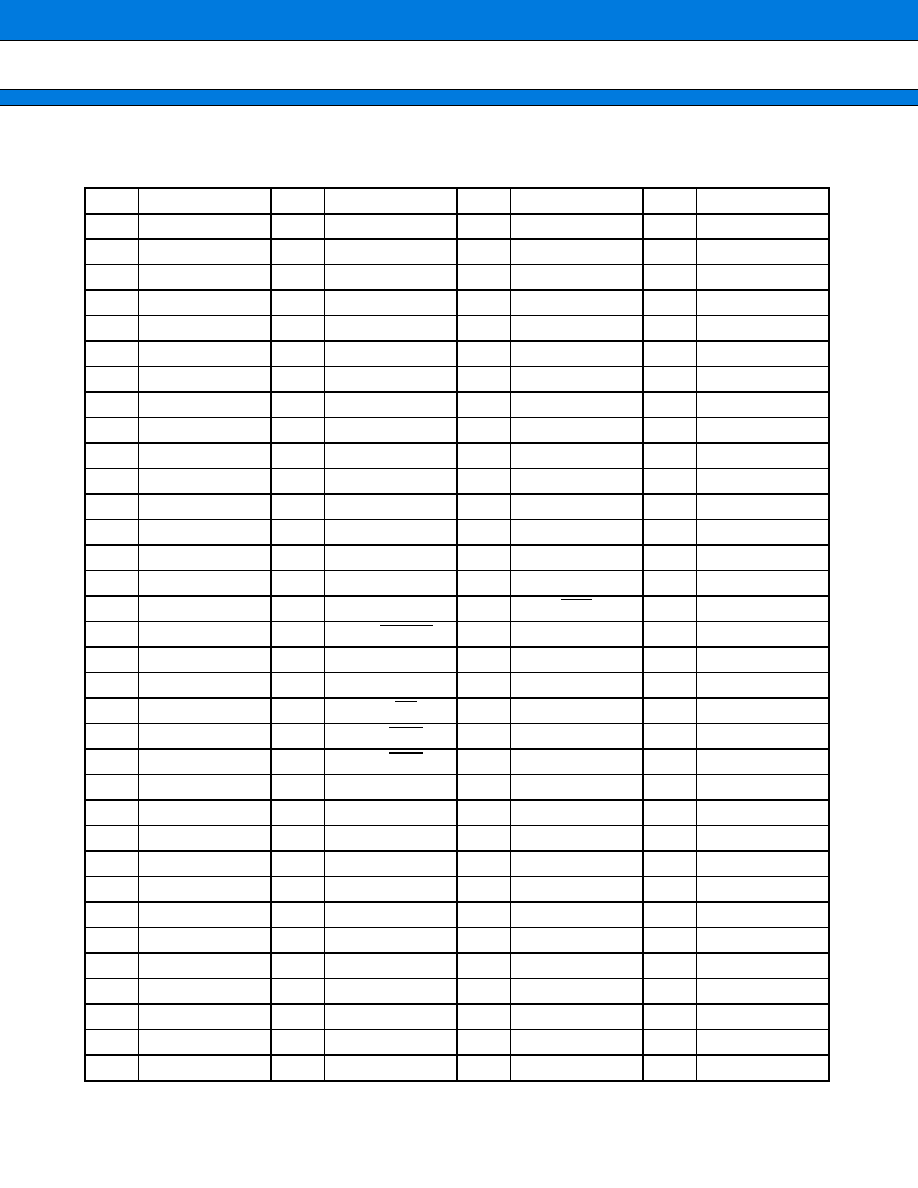

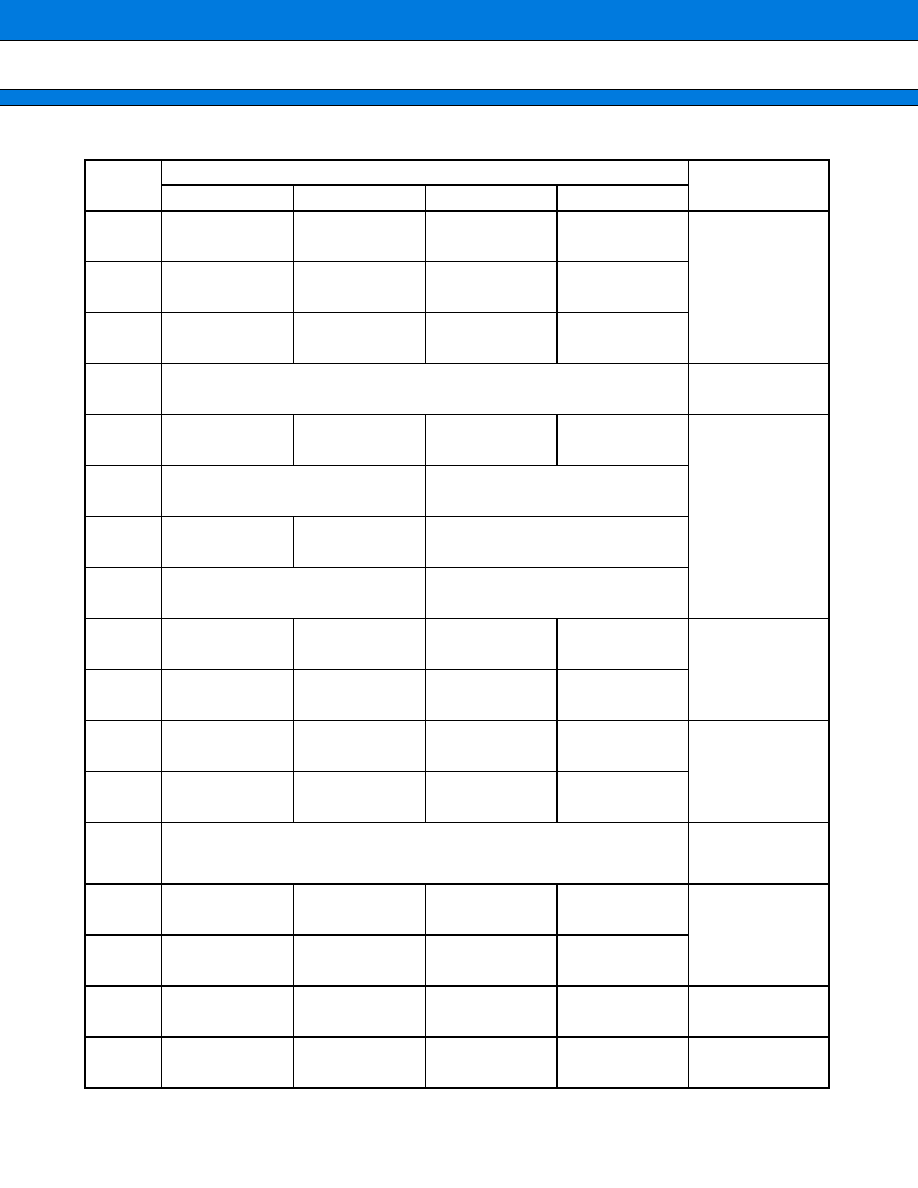

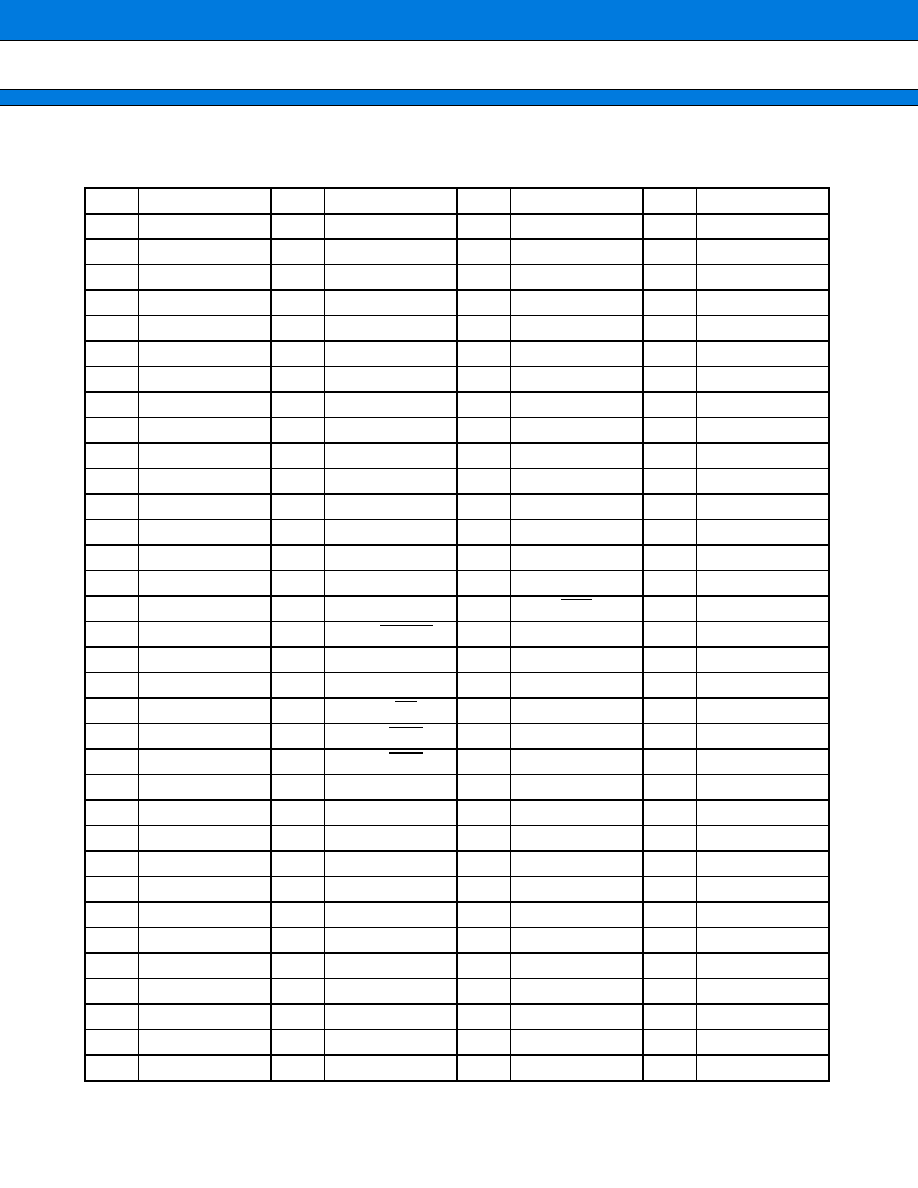

PIN NUMBERS LIST

∑ Device : MB91FV130

Package : PGA-299C-A01

(Continued)

No.

Pin Name

No.

Pin Name

No.

Pin Name

No.

Pin Name

1

P20/D16

35

P54/A12

69

N.C.

103

PK3/AN3

2

V

SS

36

P55/A13

70

N.C.

104

V

CC

5

3

OPEN

37

V

CC

5

71

V

SS

105

PK4/AN4

4

P21/D17

38

P56/A14

72

N.C.

106

PK5/AN5

5

V

CC

5

39

P57/A15

73

N.C.

107

PK6/AN6

6

P22/D18

40

P60/A16/INT16

74

V

CC

5

108

PK7/AN7/CMP

7

P23/D19

41

P61/A17/INT17

75

N.C.

109

DAVC

8

V

SS

42

P62/A18/INT18

76

MD0

110

DAVS

9

P24/D20

43

P63/A19/INT19

77

MD1

111

DA0

10

P25/D21

44

P64/A20/INT20

78

MD2

112

V

SS

11

P26/D22

45

P65/A21/INT21

79

V

CC

3

113

DA1

12

P27/D23

46

P66/A22/INT22

80

V

SS

114

DA2

13

P30/D24

47

P67/A23/INT23

81

X0

115

PH0/SIN0

14

P31/D25

48

P80/RDY

82

X1

116

PH1/SOT0

15

P32/D26

49

V

CC

3

83

V

CC

5

117

PH2/SCK0

16

P33/D27

50

V

SS

84

RST

118

PI0/SIN1

17

P34/D28

51

P81/BGRNT

85

N.C.

119

PI1/SOT1

18

P35/D29

52

P82/BRQ

86

ICLK

120

PI2/SCK1

19

P36/D30

53

V

CC

5

87

ICS0

121

PI3/SIN2

20

P37/D31

54

P83/RD

88

ICS1

122

PI4/SOT2

21

P40/A00

55

P84/WR0

89

ICS2

123

PI5/SCK2

22

V

CC

5

56

P85/WR1

90

ICD0

124

PJ0/SIN3

23

P41/A01

57

P86/CLK

91

ICD1

125

V

CC

5

24

P42/A02

58

PL0/DREQ0

92

ICD2

126

PJ1/SOT3

25

P43/A03

59

PL1/DACK0

93

ICD3

127

PJ2/SCK3

26

P44/A04

60

PL2/DEOP0

94

BREAK

128

V

SS

27

P45/A05

61

PL3/DREQ1

95

AV

CC

129

V

CC

3

28

P46/A06

62

PL4/DACK1

96

AVRH

130

X0A

29

V

SS

63

PL5/DEOP1

97

V

SS

131

X1A

30

P47/A07

64

PL6/DREQ2

98

AVRL

132

V

SS

31

P50/A08

65

PL7/DACK2

99

AV

SS

133

PJ3/SIN4

32

P51/A09

66

N.C.

100

PK0/AN0

134

PJ4/SOT4

33

P52/A10

67

N.C.

101

PK1/AN1

135

PJ5/SCK4

34

P53/A11

68

V

CC

5

102

PK2/AN2

136

PC0/INT0

MB91133/MB91F133

8

(Continued)

No.

Pin Name

No.

Pin Name

No.

Pin Name

No.

Pin Name

No.

Pin Name

137

PC1/INT1

173

PF5/RTO5

209

TAD14

245

TDT23

281

TDT53

138

PC2/INT2

174

PF6/RTO6

210

TAD15

246

TDT24

282

TDT54

139

PC3/INT3

175

PF7/RTO7

211

V

CC

3

247

V

SS

283

TDT55

140

PC4/INT4/AIN0

176

PG0/PPG0

212

TOE

248

TDT25

284

TDT56

141

PC5/INT5/BIN0

177

PG1/PPG1

213

TCE1

249

TDT26

285

TDT57

142

PC6/INT6/AIN1

178

PG2/PPG2

214

TADSC

250

TDT27

286

V

CC

3

143

V

CC

5

179

V

SS

215

TWR

251

TDT28

287

TDT58

144

PC7/INT7/BIN1

180

PG3/PPG3

216

TDT00

252

TDT29

288

TDT59

145

PD0/INT8/TRG0

181

PG4/PPG4

217

TDT01

253

TDT30

289

TDT60

146

V

SS

182

PG5/PPG5

218

V

SS

254

V

CC

5

290

TDT61

147

PD1/INT9/TRG1

183

N.C.

219

TDT02

255

TDT31

291

TDT62

148

PD2/INT10/TRG2

184

N.C.

220

TDT03

256

TDT32

292

TDT63

149

V

CC

5

185

N.C.

221

V

CC

5

257

TDT33

293

V

CC

5

150

PD3/INT11/TRG3

186

N.C.

222

TDT04

258

TDT34

294

TDT64

151

PD4/INT12/TRG4

187

V

CC

5

223

TDT05

259

TDT35

295

TDT65

152

V

SS

188

EXRAM

224

V

SS

260

TDT36

296

V

SS

153

PD5/INT13/TRG5

189

TAD00

225

TDT06

261

TDT37

297

TDT66

154

PD6/INT14/DEOP2

190

TAD01

226

TDT07

262

V

SS

298

TDT67

155

V

CC

5

191

TAD02

227

TDT08

263

TDT38

299

V

CC

5

156

PD7/INT15/ATG

192

TAD03

228

TDT09

264

TDT39

300

TDT68

157

PE0/ZIN0

193

V

CC

3

229

TDT10

265

TDT40

158

V

SS

194

TAD04

230

V

CC

5

266

TDT41

159

PE1/ZIN1

195

TAD05

231

TDT11

267

TDT42

160

PE2/IN0

196

TAD06

232

TDT12

268

TDT43

161

PE3/IN1

197

TAD07

233

V

SS

269

V

CC

3

162

PE4/IN2

198

TAD08

234

TDT13

270

TDT44

163

PE5/IN3

199

TAD09

235

TDT14

271

TDT45

164

PE6/FRCK

200

V

SS

236

TDT15

272

TDT46

165

PE7/DTTI

201

TAD10

237

TDT16

273

TDT47

166

V

CC

3

202

TAD11

238

TDT17

274

TDT48

167

PF0/RTO0

203

V

CC

5

239

TDT18

275

V

CC

5

168

PF1/RTO1

204

TAD12

240

V

CC

3

276

TDT49

169

PF2/RTO2

205

TAD13

241

TDT19

277

TDT50

170

PF3/RTO3

206

TAD14

242

TDT20

278

V

SS

171

PF4/RTO4

207

TAD15

243

TDT21

279

TDT51

172

V

CC

5

208

TCLK

244

TDT22

280

TDT52

MB91133/MB91F133

9

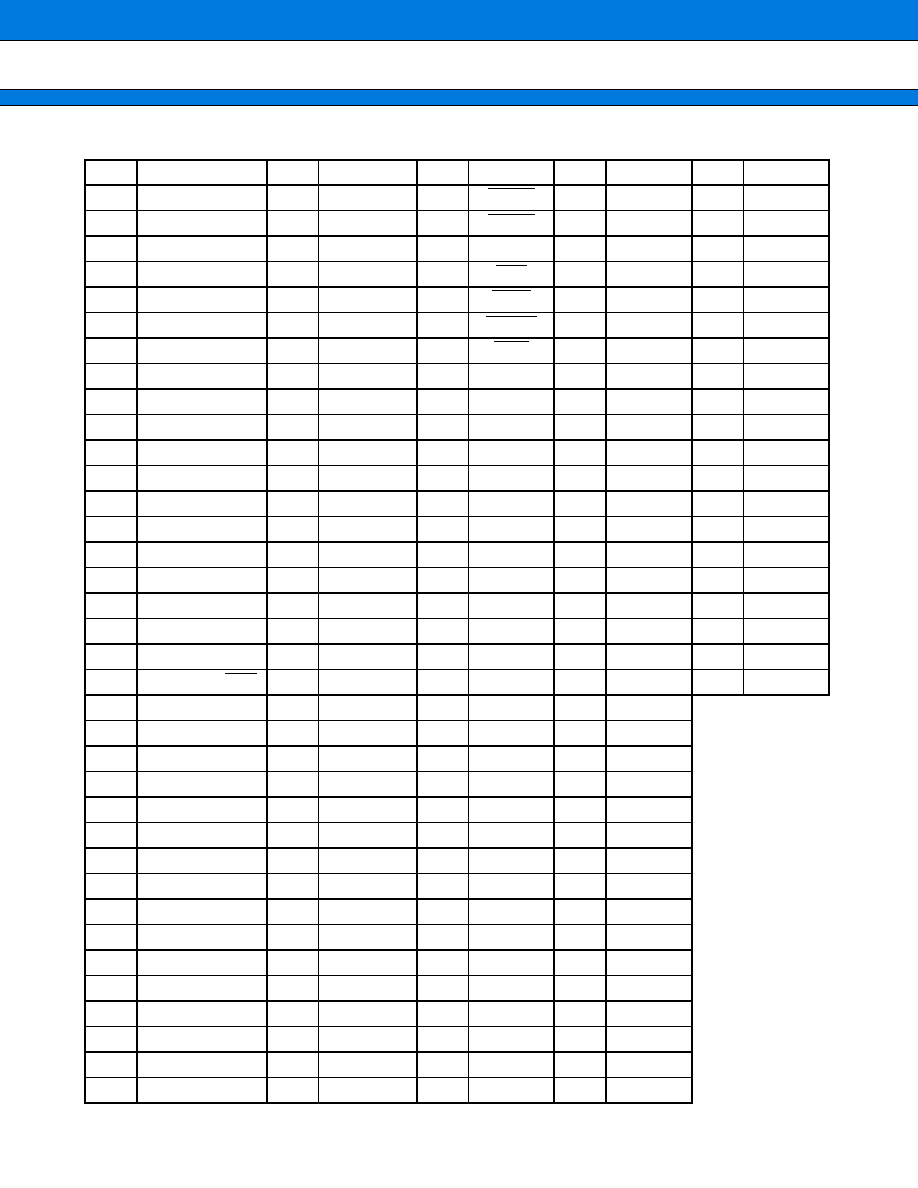

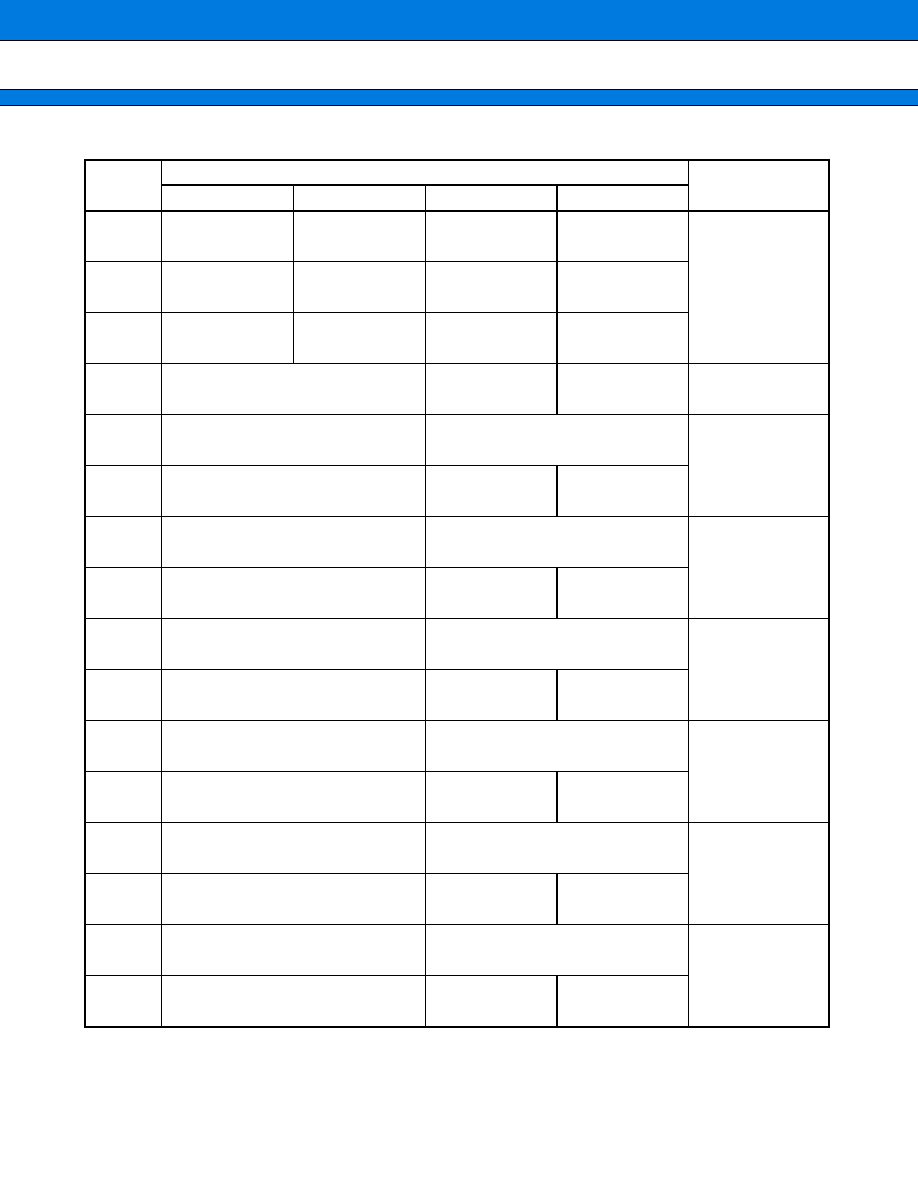

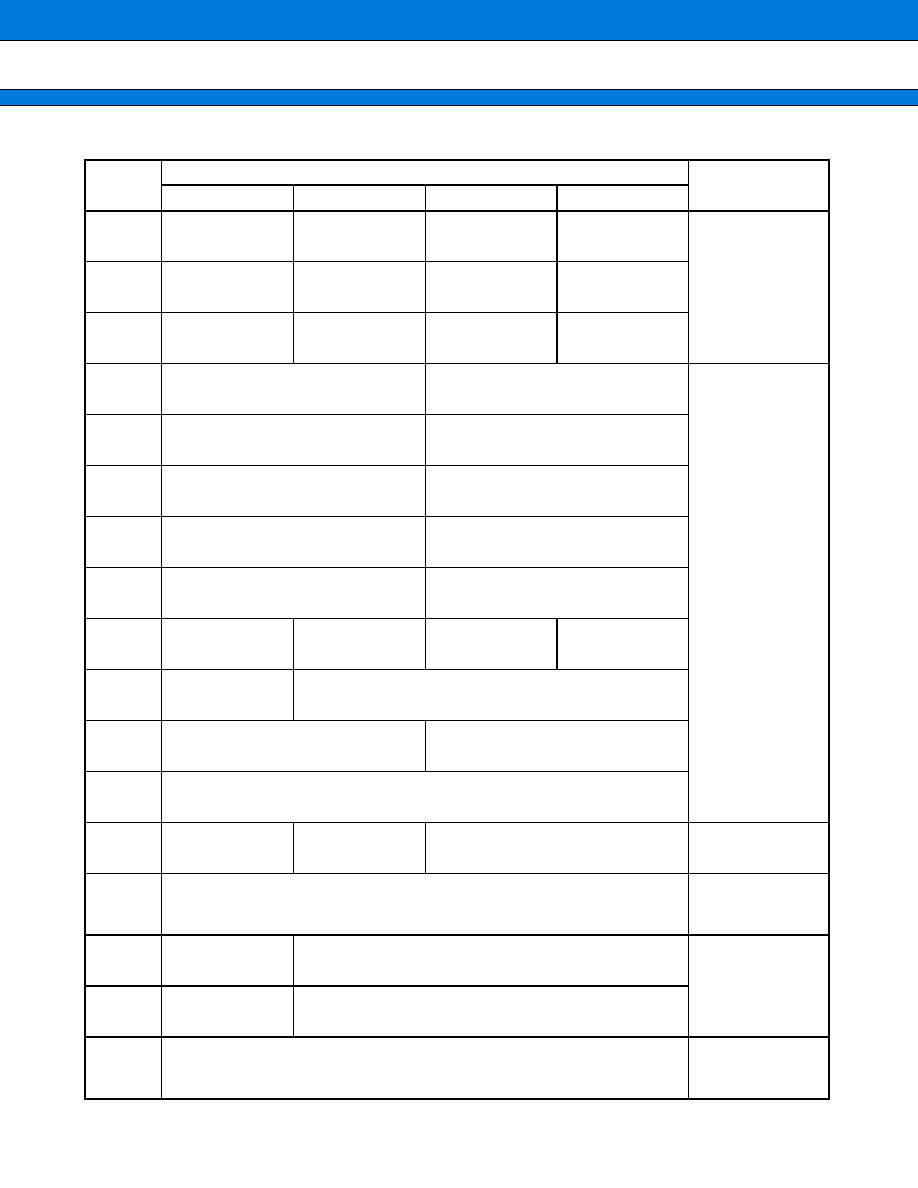

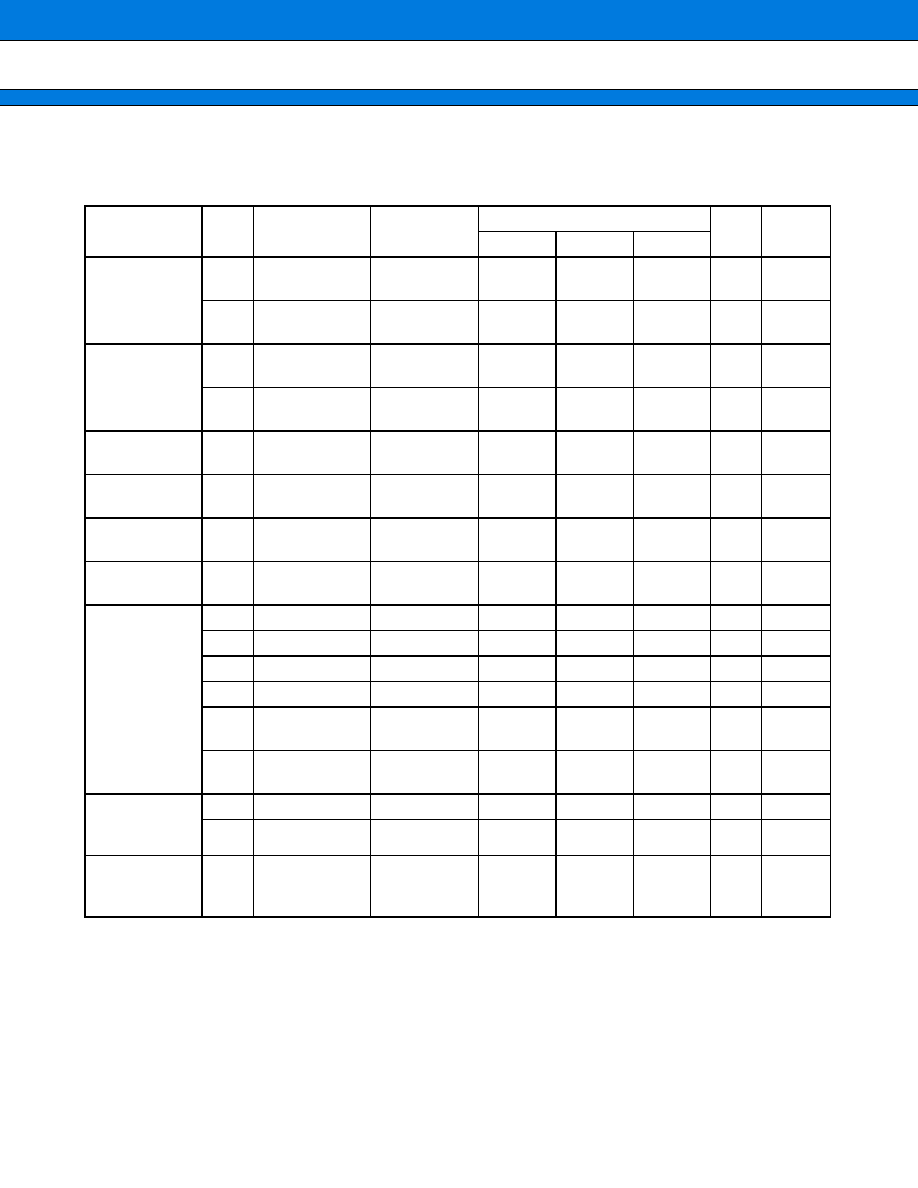

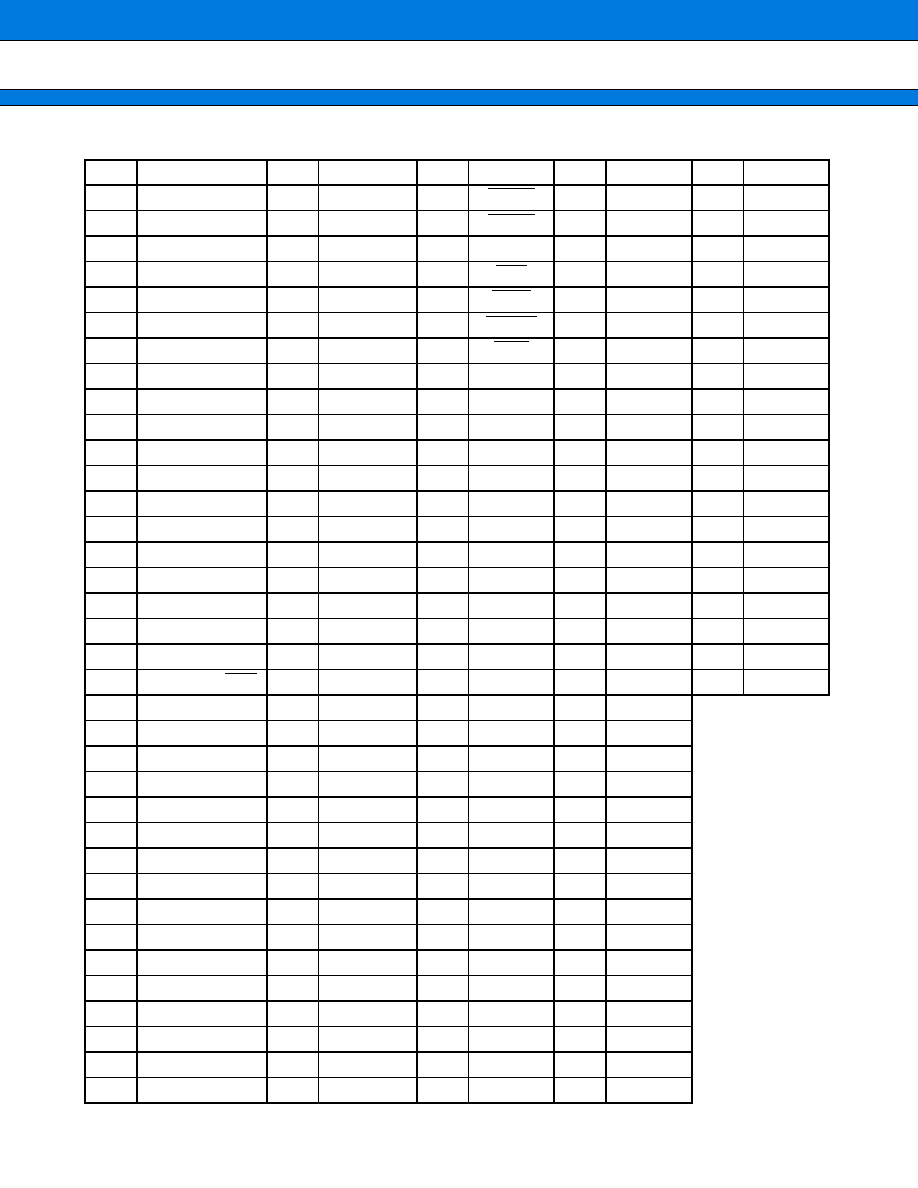

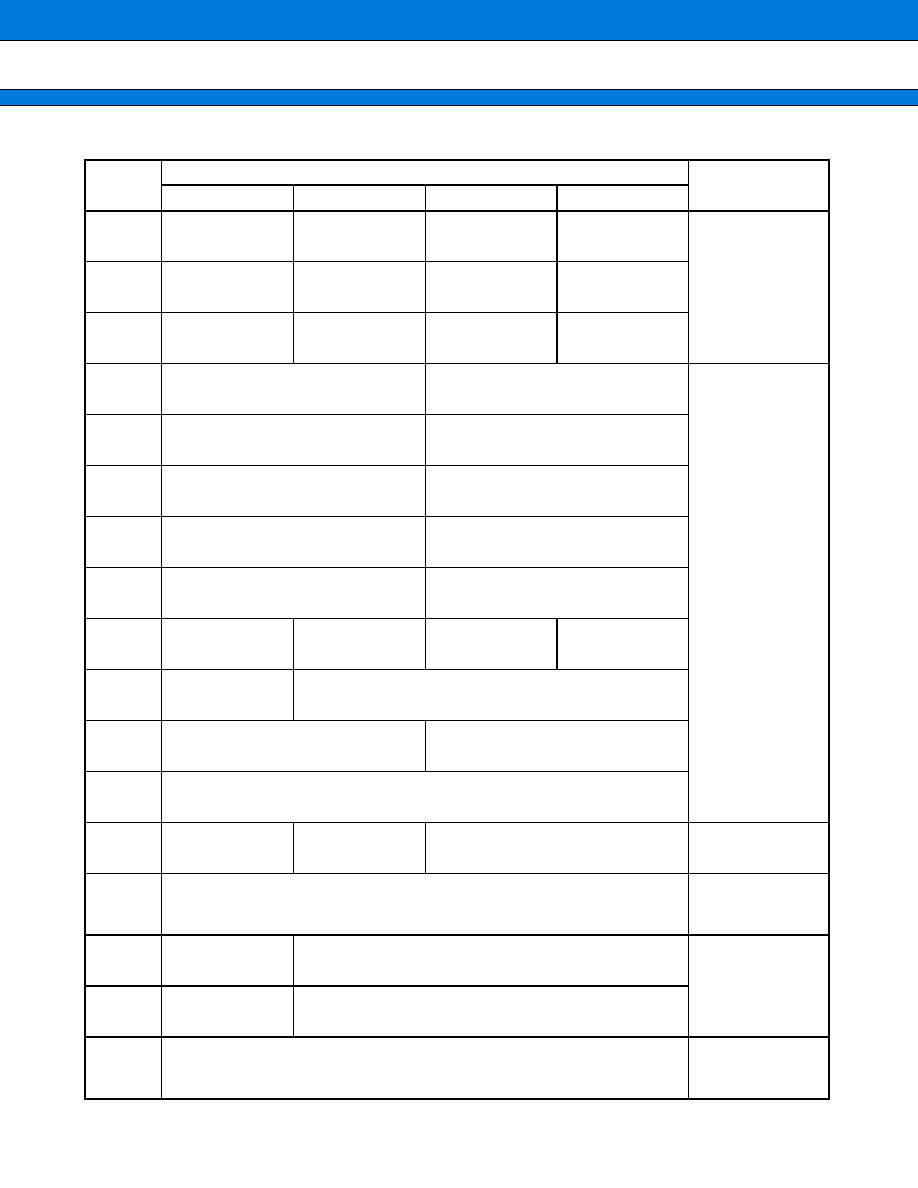

∑ Device : MB91F133/MB91133

Package : BGA-144P-M01/FPT-144P-M08

(Continued)

LQFP FBGA

Pin Name

LQFP FBGA

Pin Name

LQFP FBGA

Pin Name

1

B2

P20/D16

36

P1

P60/A16/INT16

71

P13

PE2/IN0

2

B1

P21/D17

37

N2

P61/A17/INT17

72

P14

PE3/IN1

3

C1

P22/D18

38

P2

P62/A18/INT18

73

N13

PE4/IN2

4

C2

P23/D19

39

P3

P63/A19/INT19

74

N14

PE5/IN3

5

C3

P24/D20

40

N3

P64/A20/INT20

75

M14

PE6/FRCK

6

D2

P25/D21

41

M3

P65/A21/INT21

76

M13

PE7/DTTI

7

D1

P26/D22

42

N4

P66/A22/INT22

77

M12

PF0/RTO0

8

D3

P27/D23

43

P4

P67/A23/INT23

78

L13

PF1/RTO1

9

E2

V

SS

44

M4

V

CC

3

79

L14

PF2/RTO2

10

E1

P30/D24

45

N5

P80/RDY

80

L12

PF3/RTO3

11

E3

P31/D25

46

P5

P81/BGRNT

81

K13

PF4/RTO4

12

F2

P32/D26

47

M5

P82/BRQ

82

K14

PF5/RTO5

13

F1

P33/D27

48

N6

P83/RD

83

K12

PF6/RTO6

14

F3

P34/D28

49

P6

P84/WR0

84

J13

PF7/RTO7

15

G4

P35/D29

50

M6

P85/WR1

85

J14

PG0/PPG0

16

G2

P36/D30

51

L7

P86/CLK

86

J12

PG1/PPG1

17

G1

P37/D31

52

N7

V

SS

87

H11

PG2/PPG2

18

G3

P40/A00

53

P7

PC0/INT0

88

H13

PG3/PPG3

19

H3

P41/A01

54

M7

PC1/INT1

89

H14

PG4/PPG4

20

H1

P42/A02

55

M8

PC2/INT2

90

H12

PG5/PPG5

21

H2

P43/A03

56

P8

PC3/INT3

91

G12

V

SS

22

H4

P44/A04

57

N8

PC4/AIN0/INT4

92

G14

V

CC

3

23

J4

P45/A05

58

L8

PC5/BIN0/INT5

93

G13

PJ5/SCK4

24

J1

P46/A06

59

L9

PC6/AIN1/INT6

94

G11

PJ4/SOT4

25

J2

P47/A07

60

P9

PC7/BIN1/INT7

95

F11

PJ3/SIN4

26

J3

V

SS

61

N9

PD0/INT8/TRG0

96

F14

PJ2/SCK3

27

K1

V

CC

5

62

M9

PD1/INT9/TRG1

97

F13

PJ1/SOT3

28

K2

P50/A08

63

P10

PD2/INT10/TRG2

98

F12

PJ0/SIN3

29

K3

P51/A09

64

N10

PD3/INT11/TRG3

99

E14

PI5/SCK2

30

L1

P52/A10

65

M10

PD4/INT12/TRG4

100

E13

PI4/SOT2

31

L2

P53/A11

66

P11

PD5/INT13/TRG5

101

E12

PI3/SIN2

32

L3

P54/A12

67

N11

PD6/DEOP2/INT14

102

D14

PI2/SCK1

33

M2

P55/A13

68

M11

PD7/ATG/INT15

103

D13

PI1/SOT1

34

M1

P56/A14

69

N12

PE0/ZIN0

104

D12

PI0/SIN1

35

N1

P57/A15

70

P12

PE1/ZIN1

105

C13

PH2/SCK0

MB91133/MB91F133

10

(Continued)

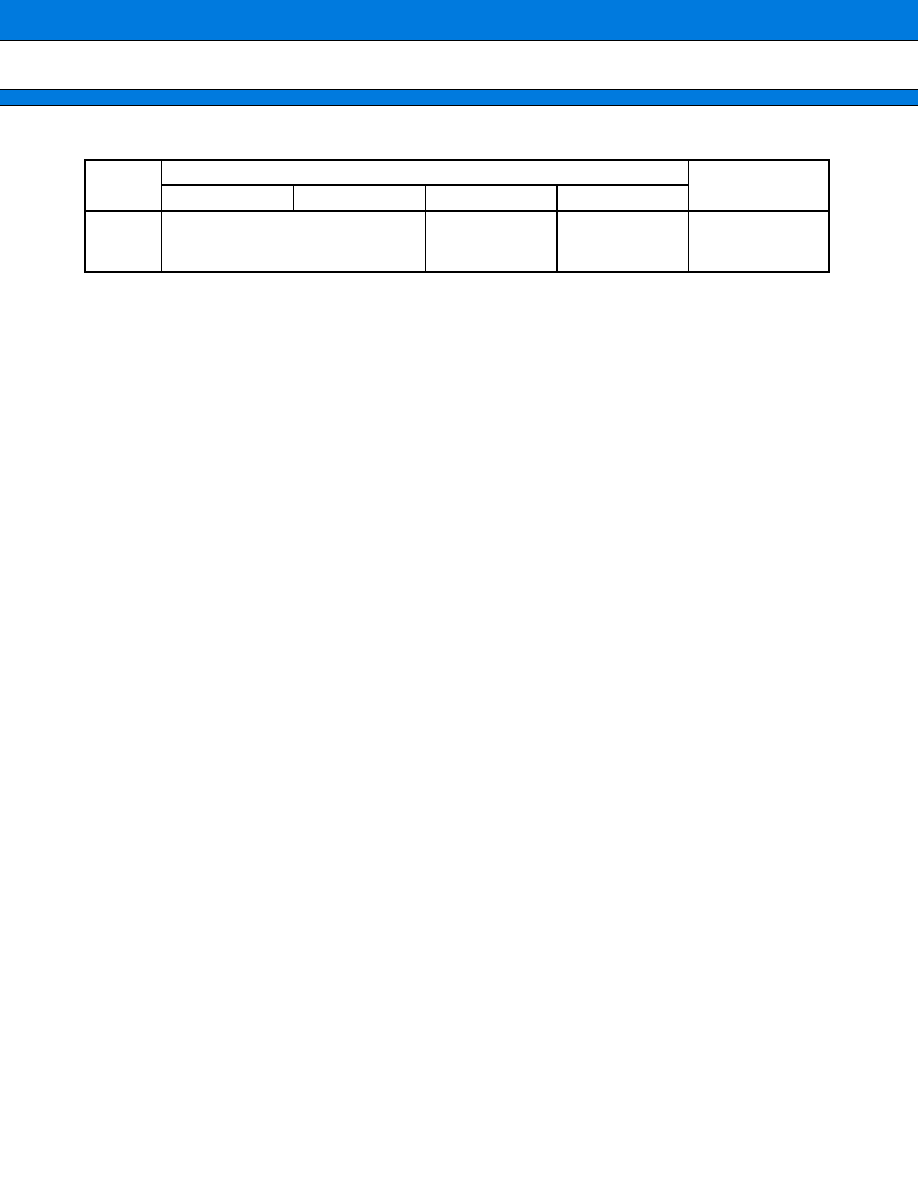

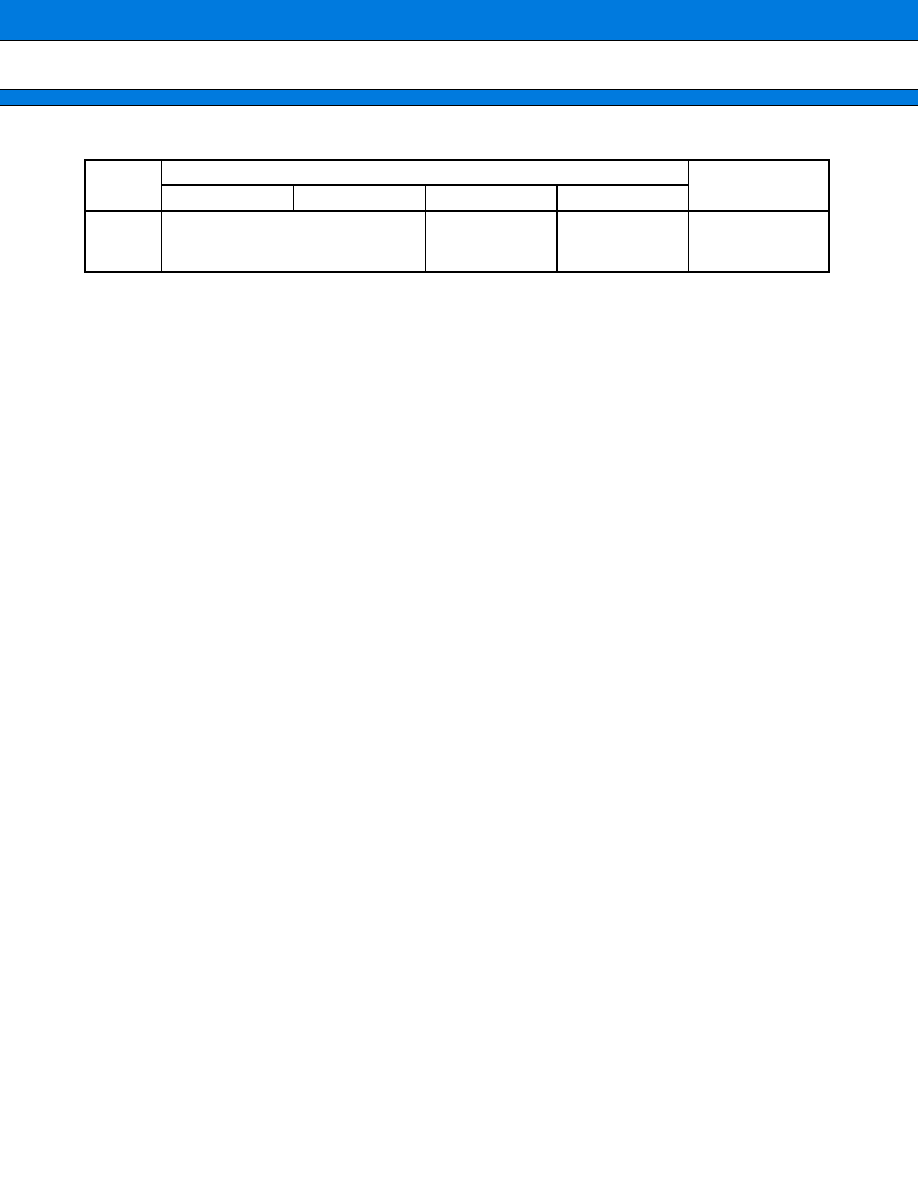

LQFP FBGA

Pin Name

LQFP FBGA

Pin Name

106

C14

PH1/SOT0

126

C8

PL0/DREQ0

107

B14

PH0/SIN0

127

C7

PL1/DACK0

108

A14

V

CC

5

128

A7

PL2/DEOP0

109

B13

DA2

129

B7

PL3/DREQ1

110

A13

DA1

130

D7

PL4/DACK1

111

B12

DA0

131

D6

PL5/DEOP1

112

A12

DAVS

132

A6

PL6/DREQ2

113

C12

DAVC

133

B6

PL7/DACK2

114

B11

AV

CC

134

C6

RST

115

A11

AVRH

135

A5

V

SS

116

C11

AVRL

136

B5

X0A

117

B10

AV

SS

137

C5

X1A

118

A10

PK0/AN0

138

A4

V

CC

3

119

C10

PK1/AN1

139

B4

X0

120

B9

PK2/AN2

140

C4

X1

121

A9

PK3/AN3

141

B3

V

SS

122

C9

PK4/AN4

142

A3

MD0

123

D8

PK5/AN5

143

A2

MD1

124

B8

PK6/AN6

144

A1

MD2

125

A8

PK7/AN7/CMP

MB91133/MB91F133

11

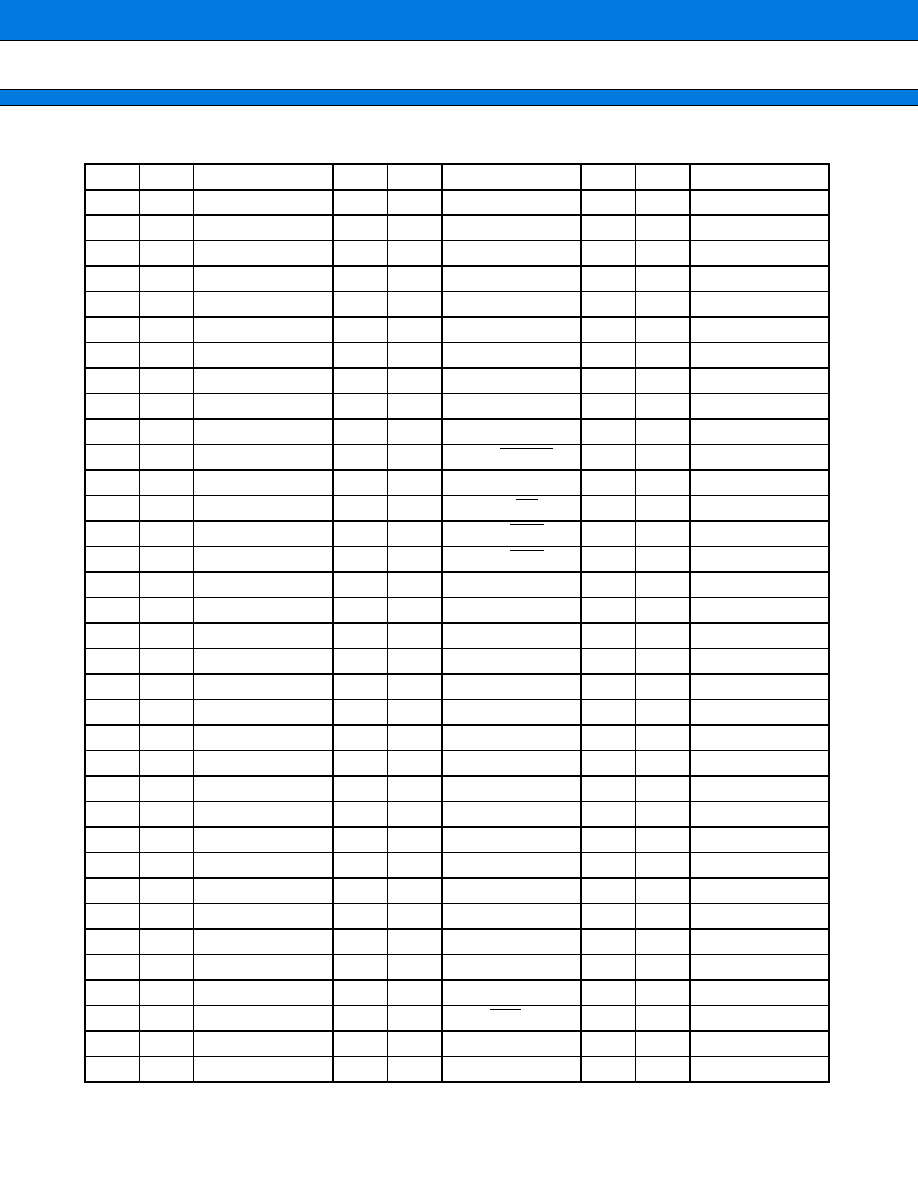

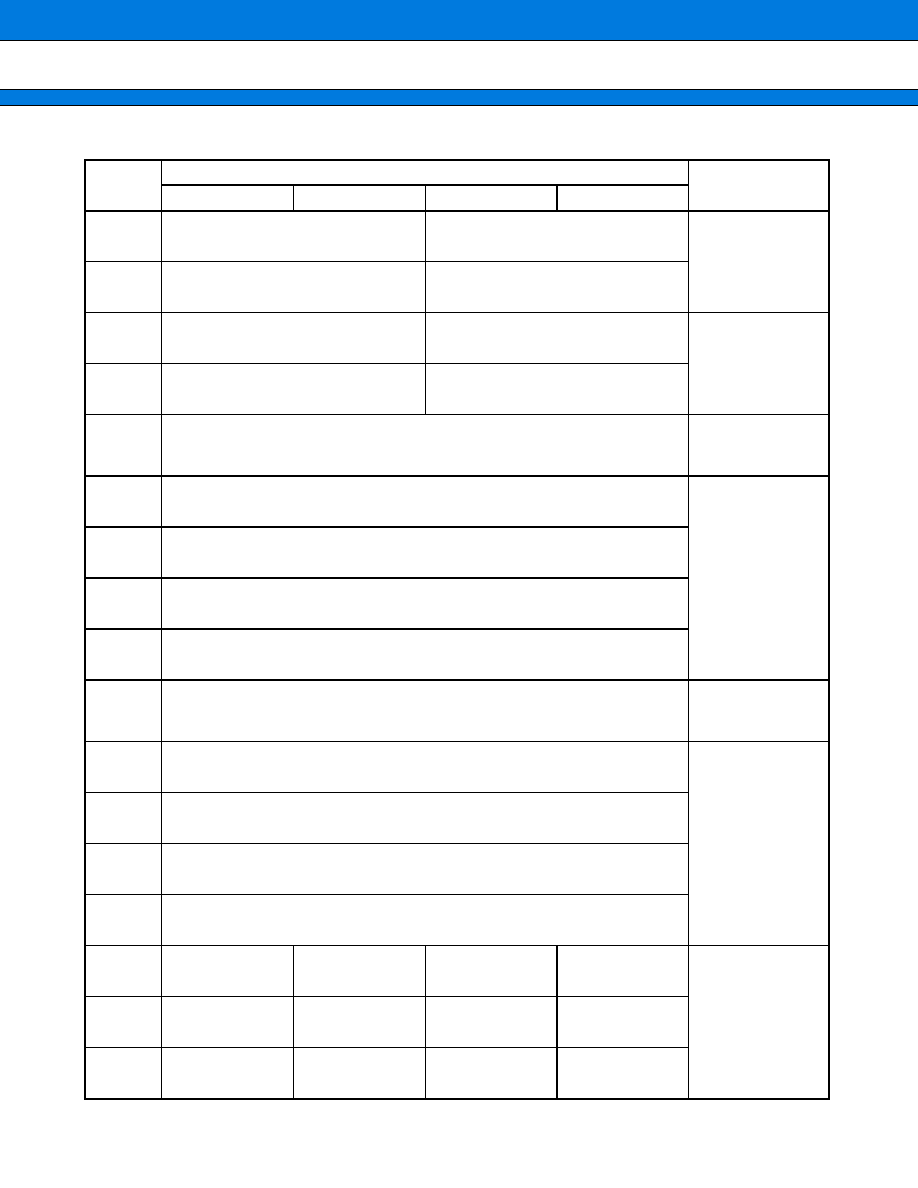

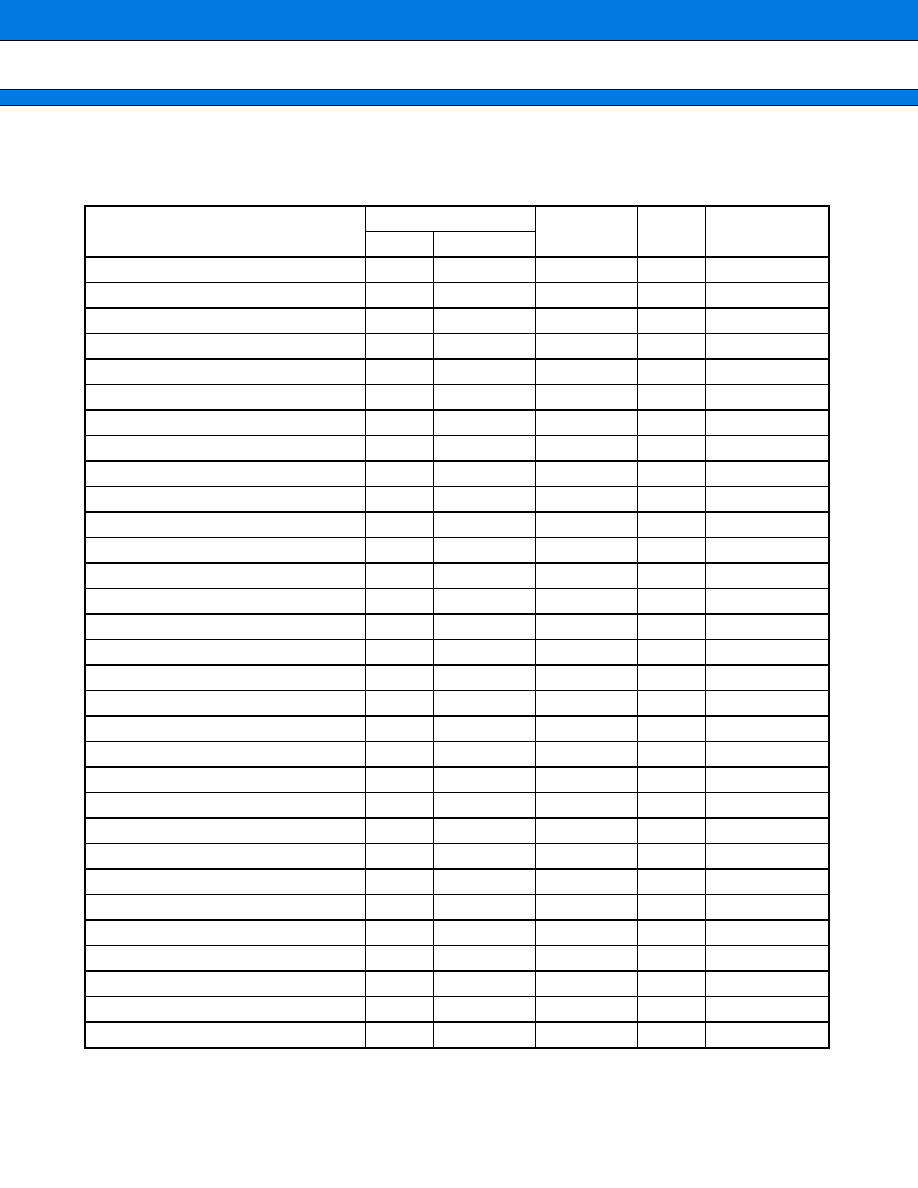

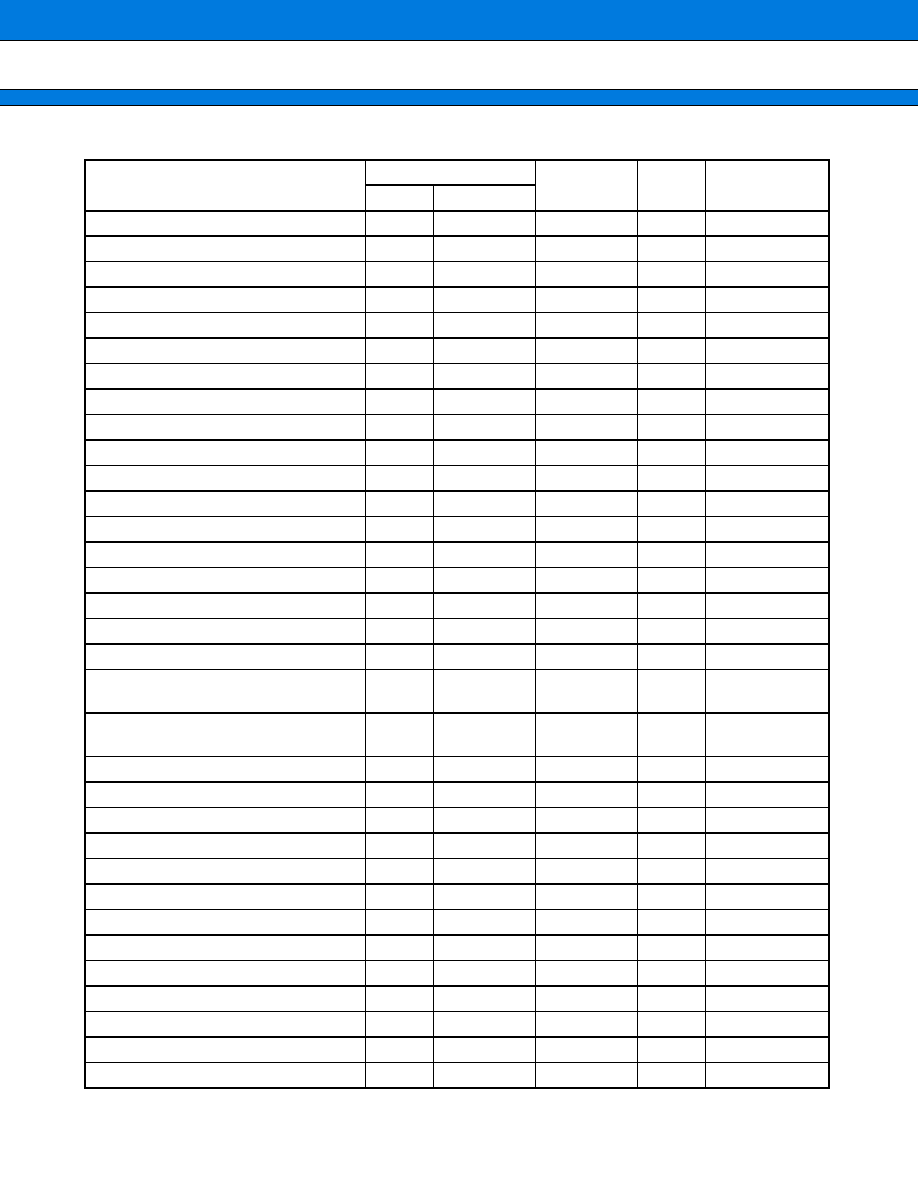

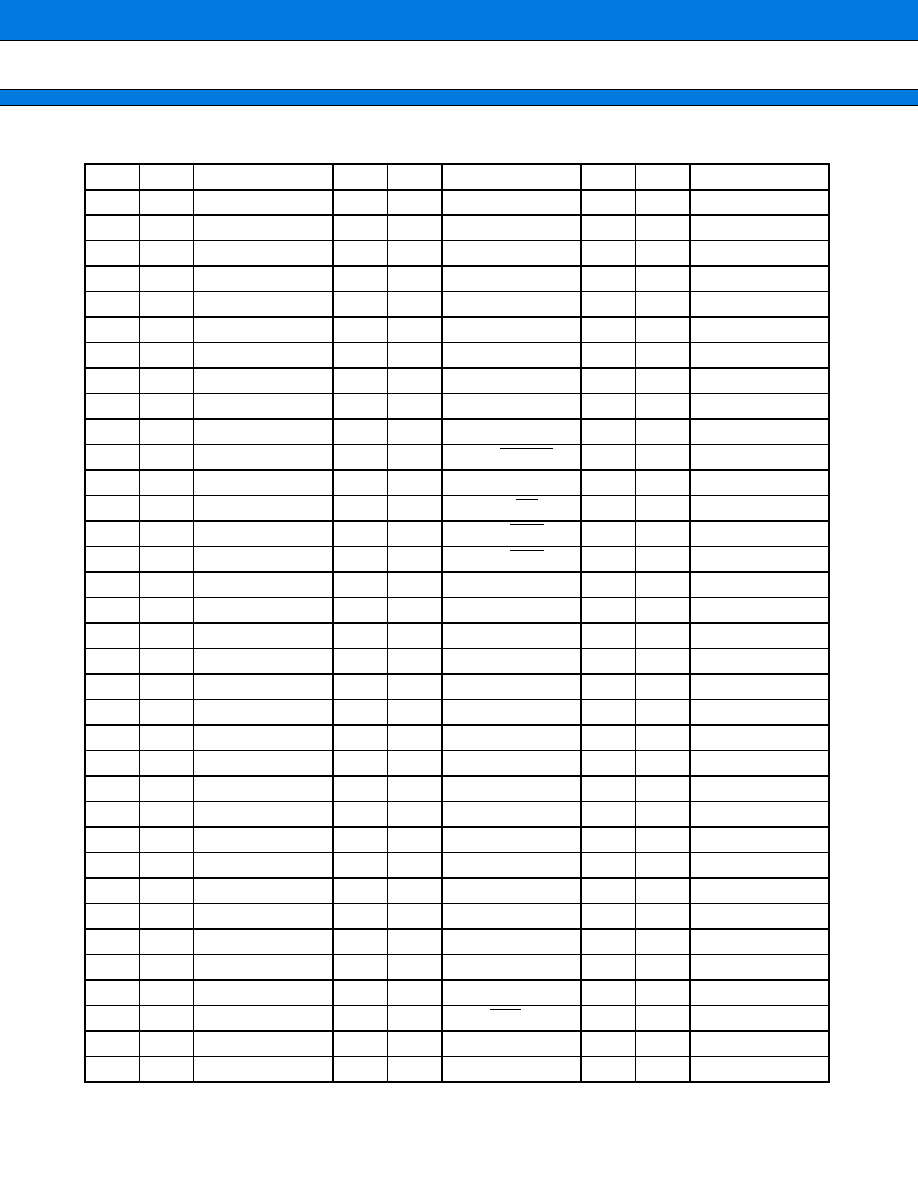

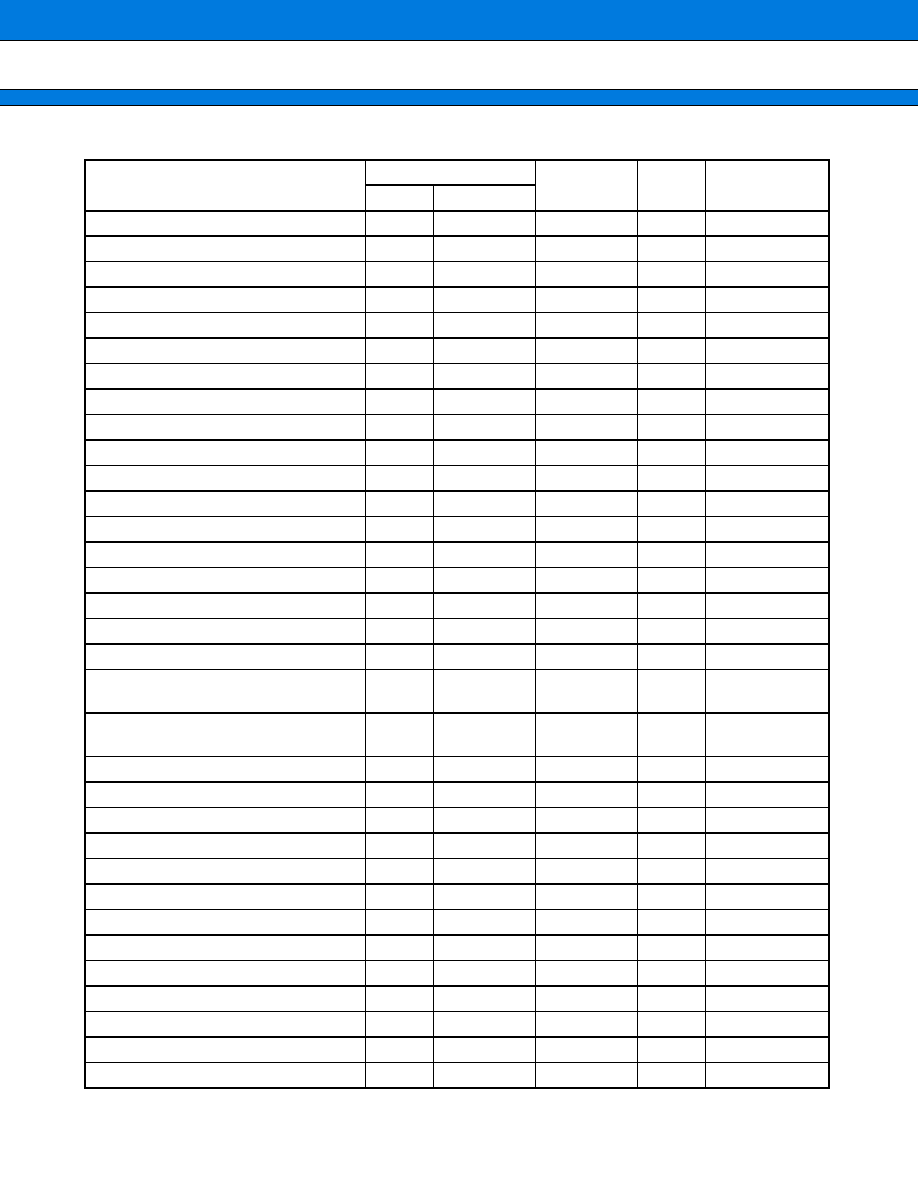

s

PIN DESCRIPTIONS

(Continued)

Pin No.

Pin name

Circuit

type

Function

1

2

3

4

5

6

7

8

D16/P20

D17/P21

D18/P22

D19/P23

D20/P24

D21/P25

D22/P26

D23/P27

C

External data bus bits 16 to 23

Only valid for external bus 16-bit mode. Can be used as ports in

single-chip and external bus 8-bit modes.

10

11

12

13

14

15

16

17

D24/P30

D25/P31

D26/P32

D27/P33

D28P34

D29/P35

D30/P36

D31/P37

C

External data bus bits 24 to 31

Can be used as ports in single-chip mode.

18

19

20

21

22

23

24

25

28

29

30

31

32

33

34

35

A00/P40

A01/P41

A02/P42

A03/P43

A04/P44

A05/P45

A06/P46

A07/P47

A08/P50

A09/P51

A10/P52

A11/P53

A12/P54

A13/P55

A14/P56

A15/P57

F

External address bus bits 0 to 15

Valid for external bus mode. Can be used as ports in single-chip

mode.

36

37

38

39

40

41

42

43

A16/INT16/P60

A17/INT17/P61

A18/INT18/P62

A19/INT19/P63

A20/INT20/P64

A21/INT21/P65

A22/INT22/P66

A23/INT23/P67

O

External address bus bits 16 to 23

[ INT16 to 23 ] are external interruption request inputs 16 to 23.

These inputs are always used when dealing with external interrup-

tions is permitted, so output by ports should be stopped except

when carried out intentionally.

Can be used as ports when address bus and external interruption

request input are not used.

45

RDY/P80

C

External RDY input

This function is valid when external RDY input is permitted. "0" is

input if the bus cycle being executed is not completed.

Can be used as a port when the external RDY input is not used.

MB91133/MB91F133

12

(Continued)

Pin No.

Pin name

Circuit

type

Function

46

BGRNT/P81

F

External bus open reception output

This function is valid when external bus open reception output is

permitted. "L" is output if the external bus is opened. Can be used

as a port when the external bus open reception output is prohibit-

ed.

47

BRQ/P82

C

External bus open request input

This function is valid when external bus open request input is per-

mitted. "1" is input if the external bus requests to be opened.

Can be used as a port when the external bus open request input is

not used.

48

RD/P83

F

External bus read strobe output

This function is valid when external bus read strobe output is per-

mitted. Can be used as a port when the external bus read strobe

output is prohibited.

49

WR0/P84

F

External bus write strobe output

This function is valid in external bus mode. Can be used as a port

in single-chip mode.

50

WR1/P85

F

External bus write strobe output

This function is valid in external bus mode and with 16-bit buses.

Can be used as a port in single-chip mode or with external 8-bit

bus.

51

CLK/P86

F

System clock output

Outputs the same clock frequency as the external bus operation.

Can be used as a port when it is not otherwise used.

53

54

55

56

INT0/PC0

INT1/PC1

INT2/PC2

INT3/PC3

H

External interruption request inputs 0 to 3

These inputs are always used when dealing with external interrup-

tions is permitted, so output by ports should be stopped except

when carried out intentionally.

Can be used to reset standby as input is permitted in this port un-

der standby status.Can be used as ports when external interrup-

tion request input is not used.

57

58

59

60

AIN0/INT4/PC4

BIN0/INT5/PC5

AIN1/INT6/PC6

BIN1/INT7/PC7

H

External interruption request inputs 4 to 7

These inputs are always used when dealing with external interrup-

tions is permitted, so output by ports should be stopped except

when carried out intentionally. Can be used to reset standby as in-

put is permitted in these ports under standby status.

[ AIN, BIN ] Up/down timer input

This input is always used when input is permitted, so output by

ports should be stopped except when carried out intentionally.

Can be used as a port when external interruption request input and

up/down timer input are not used.

MB91133/MB91F133

13

(Continued)

Pin No.

Pin name

Circuit

type

Function

61

62

63

64

65

66

67

68

TRG0/INT8/PD0

TRG1/INT9/PD1

TRG2/INT10/PD2

TRG3/INT11/PD3

TRG4/INT12/PD4

TRG5/INT13/PD5

DEOP2/INT14/PD6

ATG/INT15/PD7

O

External interruption request inputs 8 to 15

These inputs are always used when dealing with external interrup-

tions is permitted, so output by ports should be stopped except

when carried out intentionally.

[ TRG0 to 5 ] These are external trigger inputs for PPG timers.

[ DEOP2 ] DMA external transfer termination output

This function is valid when external transfer termination output

specification of the DMA controller is permitted.

[ ATG ] A/D converter external trigger input

These inputs are always used when they are selected as A/D initi-

ation factors, so output by ports should be stopped except when

carried out intentionally. Can be used as ports when not otherwise

used.

69

70

ZIN0/PE0

ZIN1/PE1

O

Up/down timer input

These inputs are always used when input is permitted, so output

by ports should be stopped except when carried out intentionally.

Can be used as ports when up/down timer input is not used.

71

72

73

74

IN0/PE2

IN1/PE3

IN2/PE4

IN3/PE5

F

Input capture input

This function is valid when input capture activates input. Can be

used as ports when input capture input is not used.

75

FRCK/PE6

F

External clock input pin of free-run timer

Can be used as a port when external clock input of free-run timer

is not used.

76

DTTI/PE7

F

RTOn pin level fixed input

Invalid when input is permitted in the waveform generation area.

Can be used as a port when RTOn pin level fixed input is not used.

77

78

79

80

81

82

83

84

RTO0/PF0

RTO1/PF1

RTO2/PF2

RTO3/PF3

RTO4/PF4

RTO5/PF5

RTO6/PF6

RTO7/PF7

F

Output compare event pins/waveform output pins in the

waveform generation area

Can be used as ports when specification of the output compare

event pin/waveform output pin of the waveform generation area is

prohibited.

85

86

87

88

89

90

PPG0/PG0

PPG1/PG1

PPG2/PG2

PPG3/PG3

PPG4/PG4

PPG5/PG5

F

PPG timer output

This function is valid when output specification of the PPG timer is

permitted. Can be used as ports when output specification of the

PPG timer is prohibited.

111

110

109

DA0

DA1

DA2

D/A converter output

This function is valid when output specification of the D/A converter

is permitted.

MB91133/MB91F133

14

(Continued)

Pin No.

Pin name

Circuit

type

Function

107

SIN0/PH0

P

UART0 data input

This input is always used when UART0 activates input, so output

by ports should be stopped except when carried out intentionally.

Can be used as a port when UART0 data input is not used.

106

SOT0/PH1

P

UART0 data output

This function is valid when UART0 data output specification is per-

mitted. Can be used as a port when UART0 data output specifica-

tion is prohibited.

105

SCK0/PH2

P

UART0 clock input/output

This function is valid when UART0 clock output specification is per-

mitted. Can be used as a port when UART0 clock output specifi-

cation is prohibited.

104

SIN1/PI0

P

UART1 data input

This input is always used when UART1 activates input, so output

by ports should be stopped except when carried out intentionally.

Can be used as a port when UART1 data input is not used.

103

SOT1/PI1

P

UART1 data output

This function is valid when UART1 data output specification is per-

mitted. Can be used as a port when UART1 data output specifica-

tion is prohibited.

102

SCK1/PI2

P

UART1 clock input/output

This function is valid when UART1 clock output specification is per-

mitted. Can be used as a port when UART1 clock output specifi-

cation is prohibited.

101

SIN2/PI3

P

UART2 data input

This input is always used when UART2 activates input, so output

by ports should be stopped except when carried out intentionally.

Can be used as a port when UART2 data input is not used.

100

SOT2/PI4

P

UART2 data output

This function is valid when UART2 data output specification is per-

mitted. Can be used as a port when UART2 data output specifica-

tion is prohibited.

99

SCK2/PI5

P

UART2 clock input/output

This function is valid when UART2 clock output specification is per-

mitted. Can be used as a port when UART2 clock output specifi-

cation is prohibited.

98

SIN3/PJ0

P

UART3 data input

This input is always used when UART3 activates input, so output

by ports should be stopped except when carried out intentionally.

Can be used as a port when UART3 data input is not used.

97

SOT3/PJ1

P

UART3 data output

This function is valid when UART3 data output specification is per-

mitted. Can be used as a port when UART3 data output specifica-

tion is prohibited.

MB91133/MB91F133

15

(Continued)

Pin No.

Pin name

Circuit

type

Function

96

SCK3/PJ2

P

UART3 clock input/output

This function is valid when UART3 clock output specification is per-

mitted. Can be used as a port when UART3 clock output specifi-

cation is prohibited.

95

SIN4/PJ3

P

UART4 data input

This input is always used when UART4 activates input, so output

by ports should be stopped except when carried out intentionally.

Can be used as a port when UART4 data input is not used.

94

SOT4/PJ4

P

UART4 data output

This function is valid when UART4 data output specification is per-

mitted. Can be used as a port when UART4 data output specifica-

tion is prohibited.

93

SCK4/PJ5

P

UART4 clock input/output

This function is valid when UART4 clock output specification is per-

mitted. Can be used as a port when UART4 clock output specifi-

cation is prohibited.

118

119

120

121

122

123

124

125

AN0/PK0

AN1/PK1

AN2/PK2

AN3/PK3

AN4/PK4

AN5/PK5

AN6/PK6

CMP/AN7/PK7

N

A/D converter analog input

This is valid when the AICK register specification is analog input.

[ CMP ] level comparator input

Can be used as ports when A/D converter analog input is not used.

126

DREQ0/PL0

F

DMA external transfer request input

This input is always used if selected as the transfer factor for the

DMA controller, so output by ports should be stopped except when

carried out intentionally. Can be used as a port when DMA exter-

nal transfer request input is not used.

127

DACK0/PL1

F

DMA external transfer request reception output

This function is valid when external transfer request reception out-

put specification of the DMA controller is permitted. Can be used

as a port when transfer request reception output specification of

the DMA controller is prohibited.

128

DEOP0/PL2

F

DMA external transfer termination output

This function is valid when external transfer termination output

specification of the DMA controller is permitted.

129

DREQ1/PL3

F

DMA external transfer request input

This input is always used if selected as the transfer factor for the

DMA controller, so output by ports should be stopped except when

carried out intentionally. Can be used as a port when DMA exter-

nal transfer request input is not used.

MB91133/MB91F133

16

(Continued)

Note : In most of the above pins, the input/output of the I/O ports and resources are multiplexed, such as xxxx/Pxx.

If the output from ports and resources of those pins compete with each other, the resource is given priority.

Pin No.

Pin name

Circuit

type

Function

130

DACK1/PL4

F

DMA external transfer request reception output

This function is valid when external transfer request reception out-

put specification of the DMA controller is permitted. Can be used

as a port when transfer request reception output specification of

the DMA controller is prohibited.

131

DEOP1/PL5

F

DMA external transfer termination output

This function is valid when external transfer termination output

specification of the DMA controller is permitted.

132

DREQ2/PL6

F

DMA external transfer request input

This input is always used if selected as the transfer factor for the

DMA controller, so output by ports should be stopped except when

carried out intentionally. Can be used as a port when DMA exter-

nal transfer request input is not used.

133

DACK2/PL7

F

DMA external transfer request reception output

This function is valid when external transfer request reception out-

put specification of the DMA controller is permitted. Can be used

as a port when transfer request reception output specification of

the DMA controller is prohibited.

134

RST

B

External reset input

136

137

X0A

X1A

K

Oscillation pin for low-speed clock (32 kHz)

139

140

X0

X1

A

Oscillation pin for high-speed clock (16.5 MHz)

142

143

144

MD0

MD1

MD2

G

Mode pins

Basic MCU operation mode is set by these pins. They should be

directly connected to V

CC

or V

SS

for use.

112

DAVS

Ground pin of D/A converter (connected to analog ground)

113

DAVC

Power pin of D/A converter

114

AV

CC

Power pin for A/D converter

115

AVRH

Reference voltage pin for A/D converter (high electric poten-

tial side)

When this pin is turned on/off, AVRH or more electric potential

must be supplied to V

CC

.

116

AVRL

Reference voltage pin for A/D converter (low electric potential

side)

117

AV

SS

Ground pin for A/D converter (connected to analog ground)

27, 108

V

CC

5

5 V power of digital circuit

Power must be connected to all V

CC

5 pins for use.

44, 92

138

V

CC

3

3 V power of digital circuit

Power must be connected to all V

CC

3 pins for use.

9, 26, 52,

91, 135,

141

V

SS

Ground level of digital circuit

MB91133/MB91F133

17

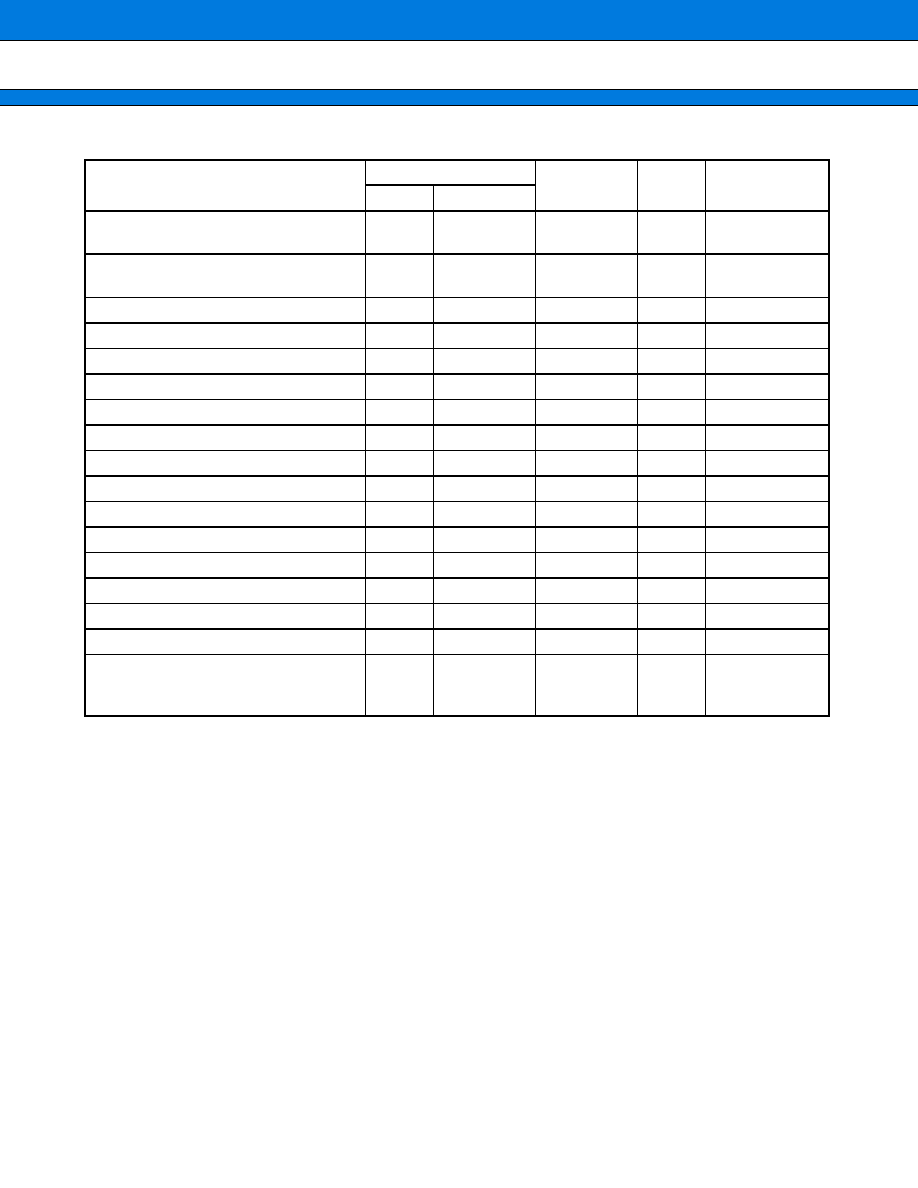

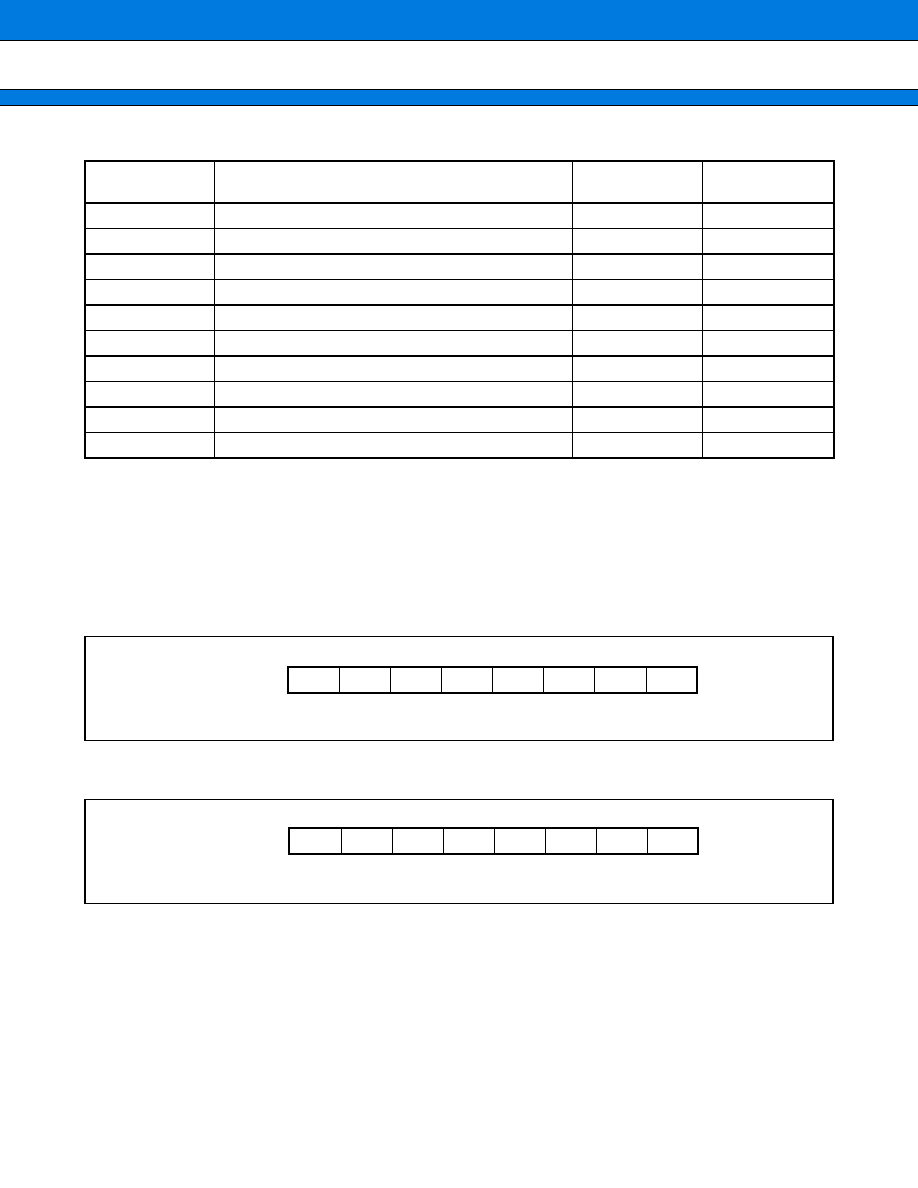

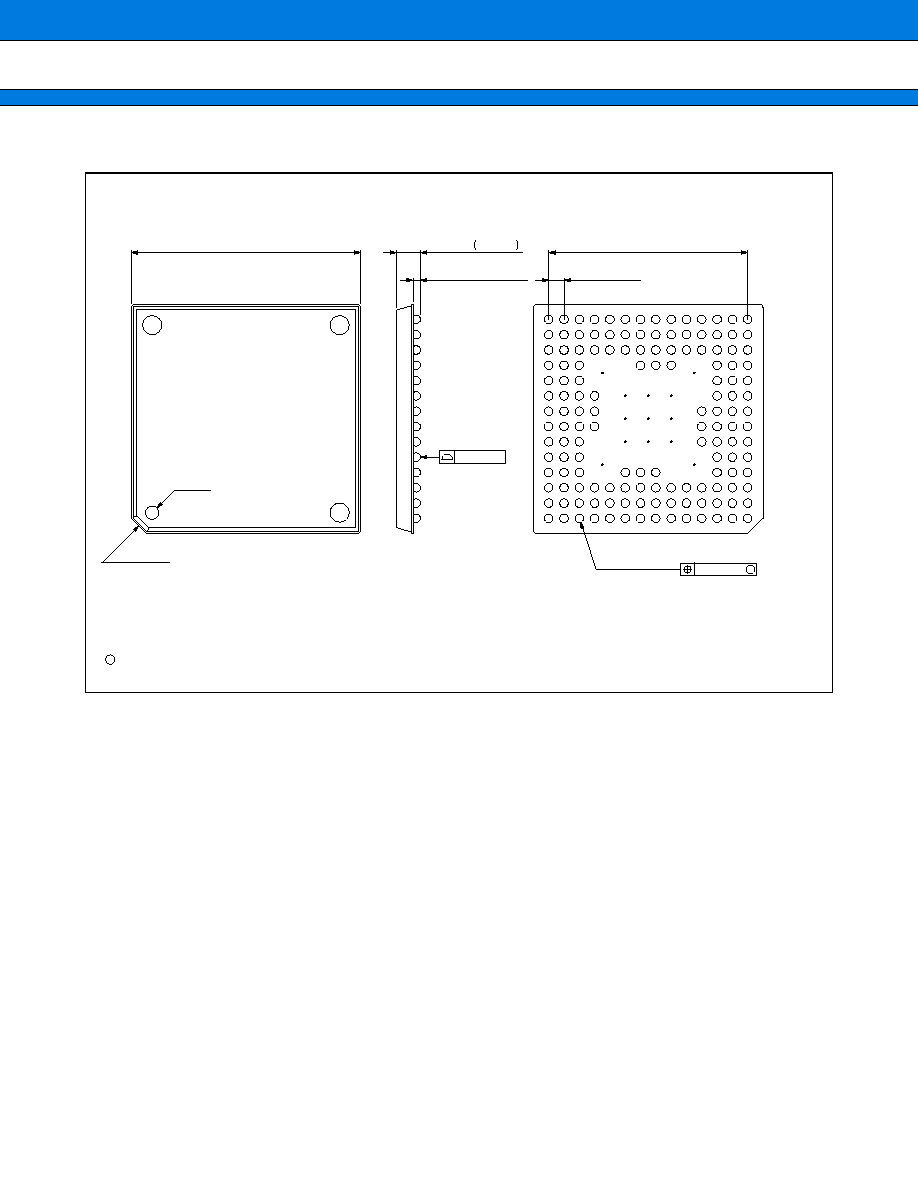

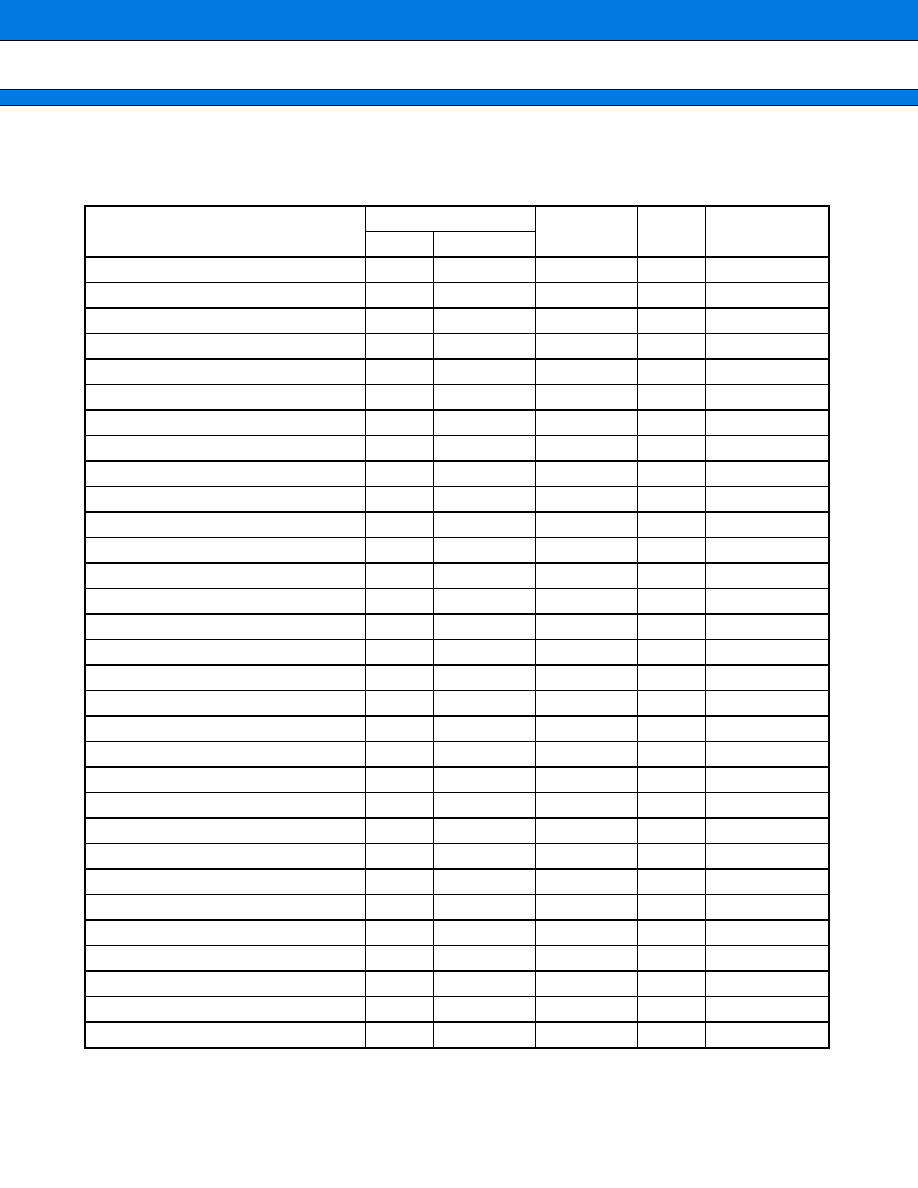

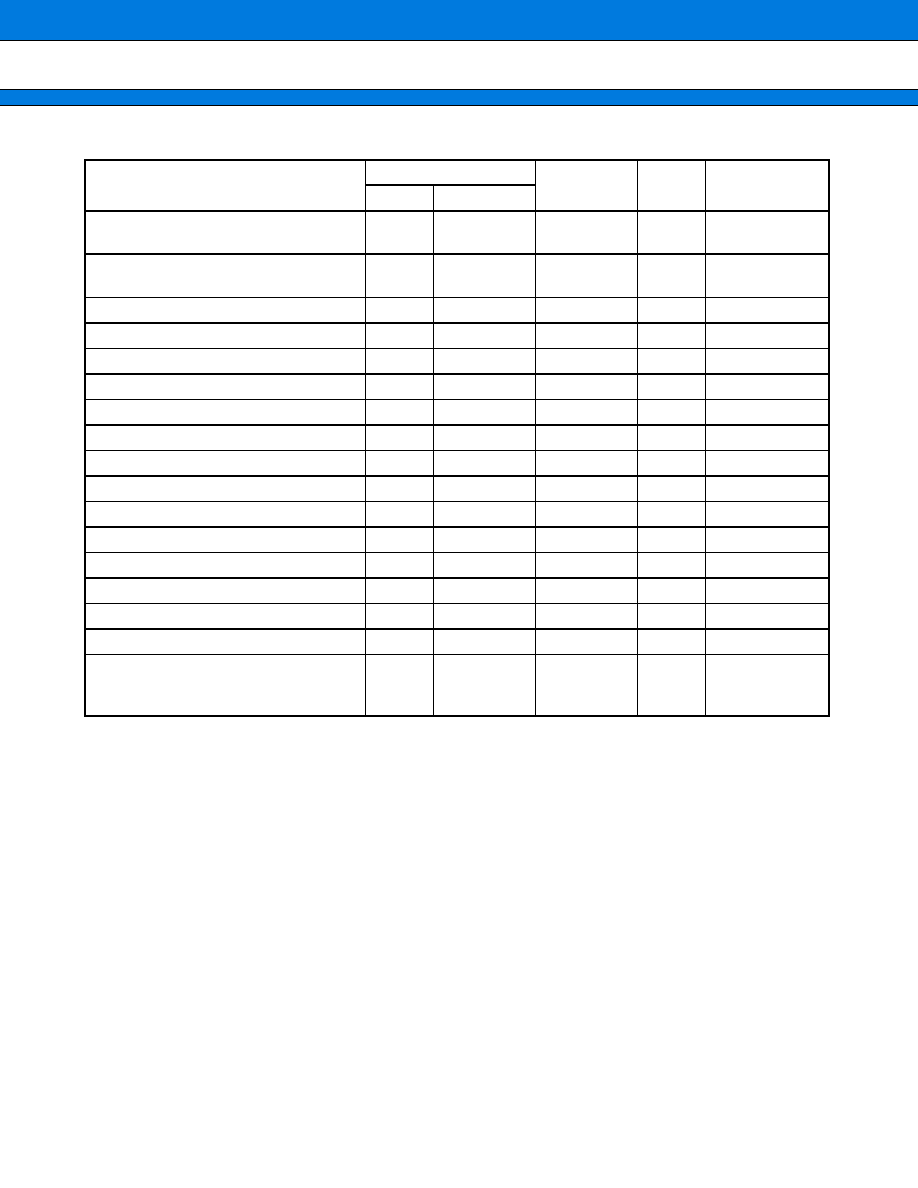

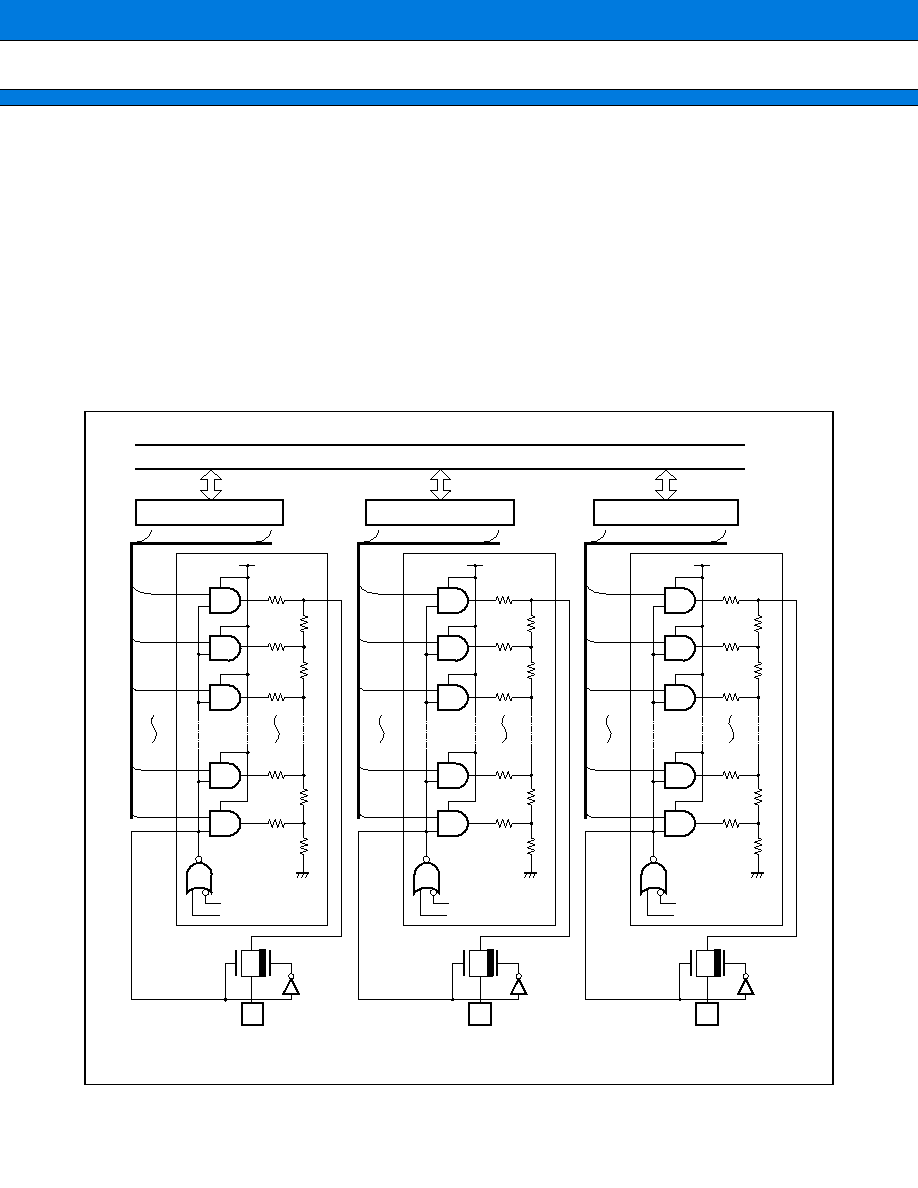

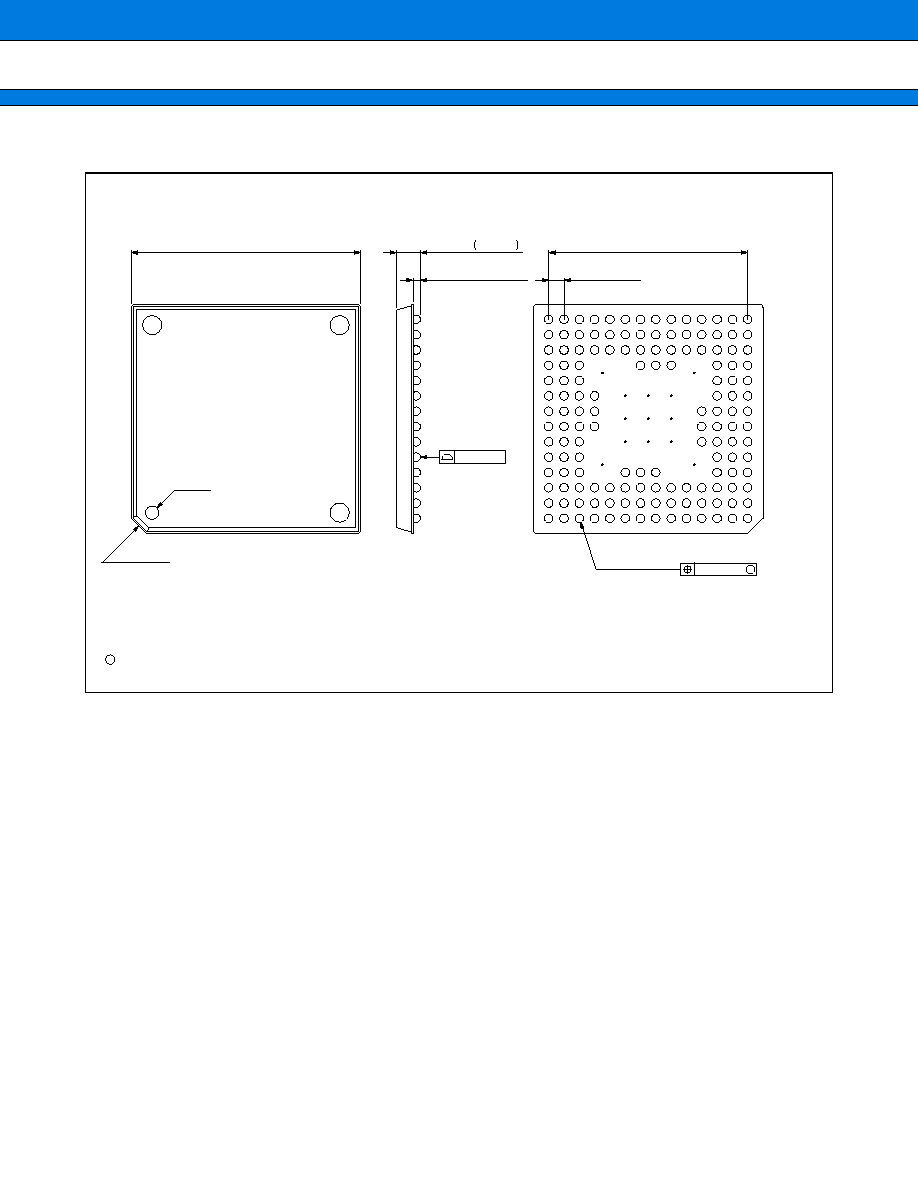

s

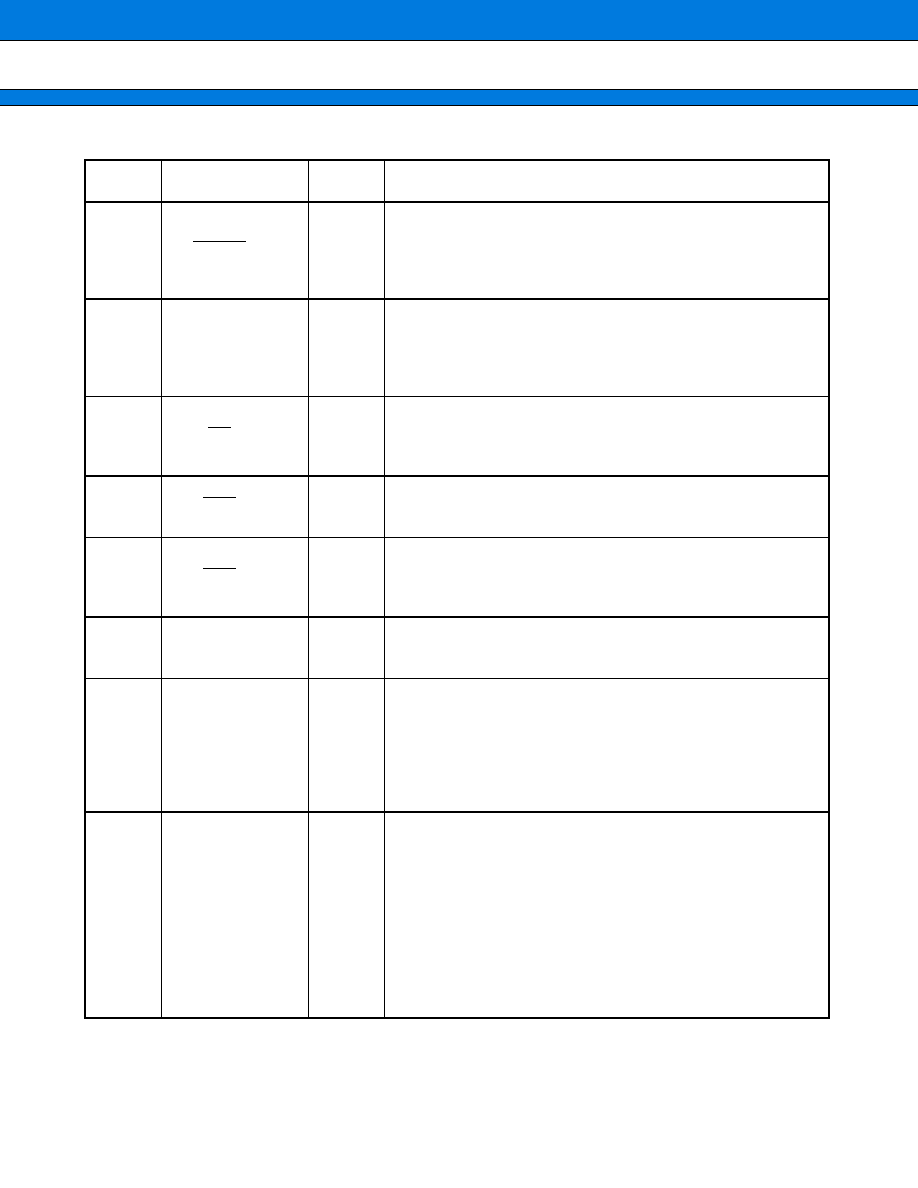

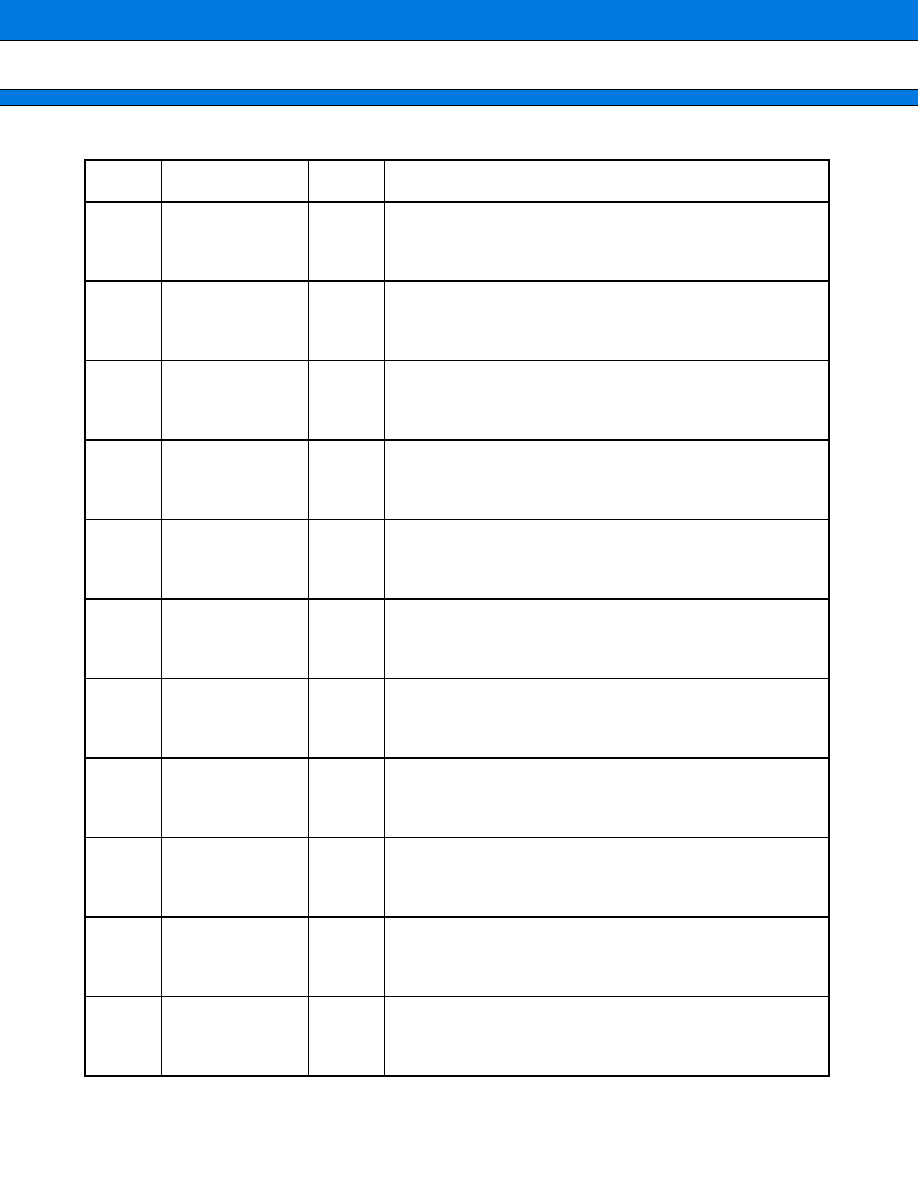

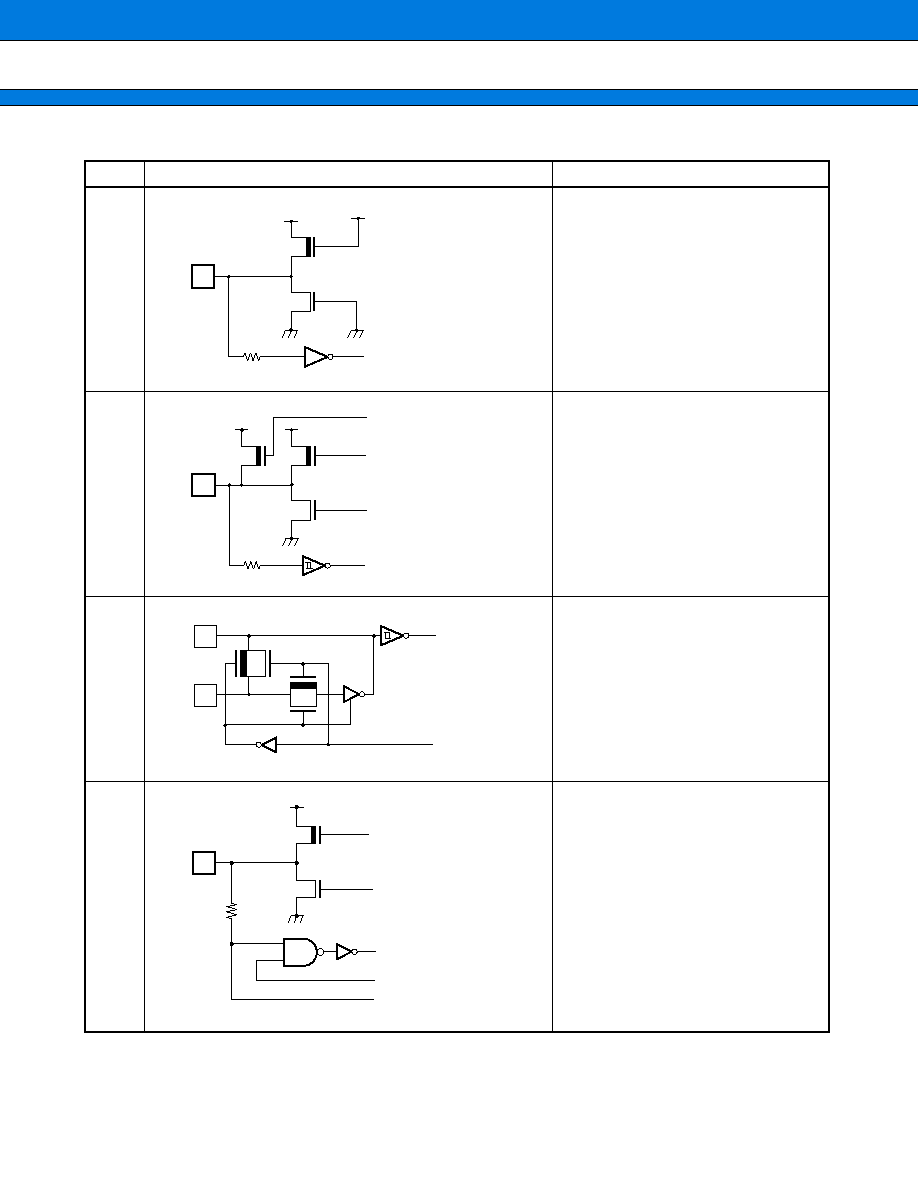

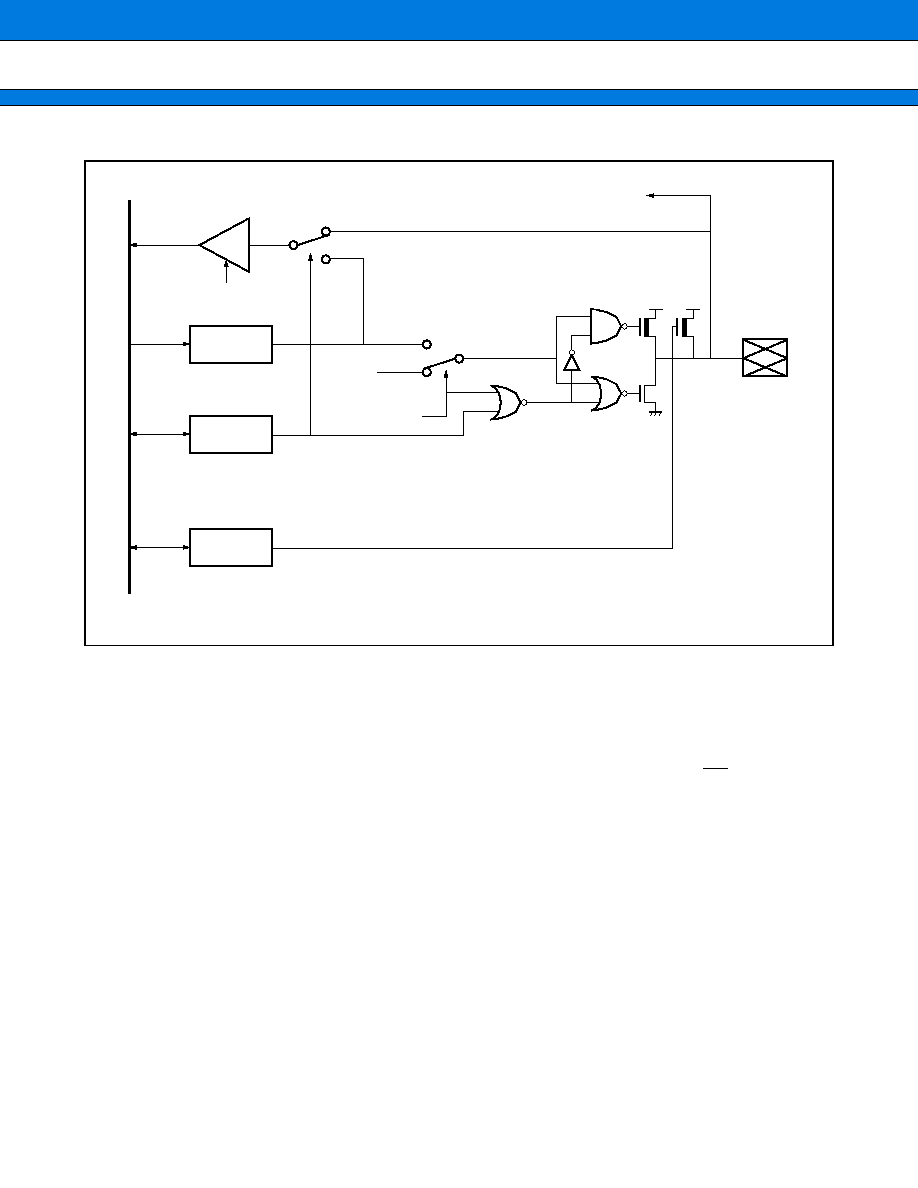

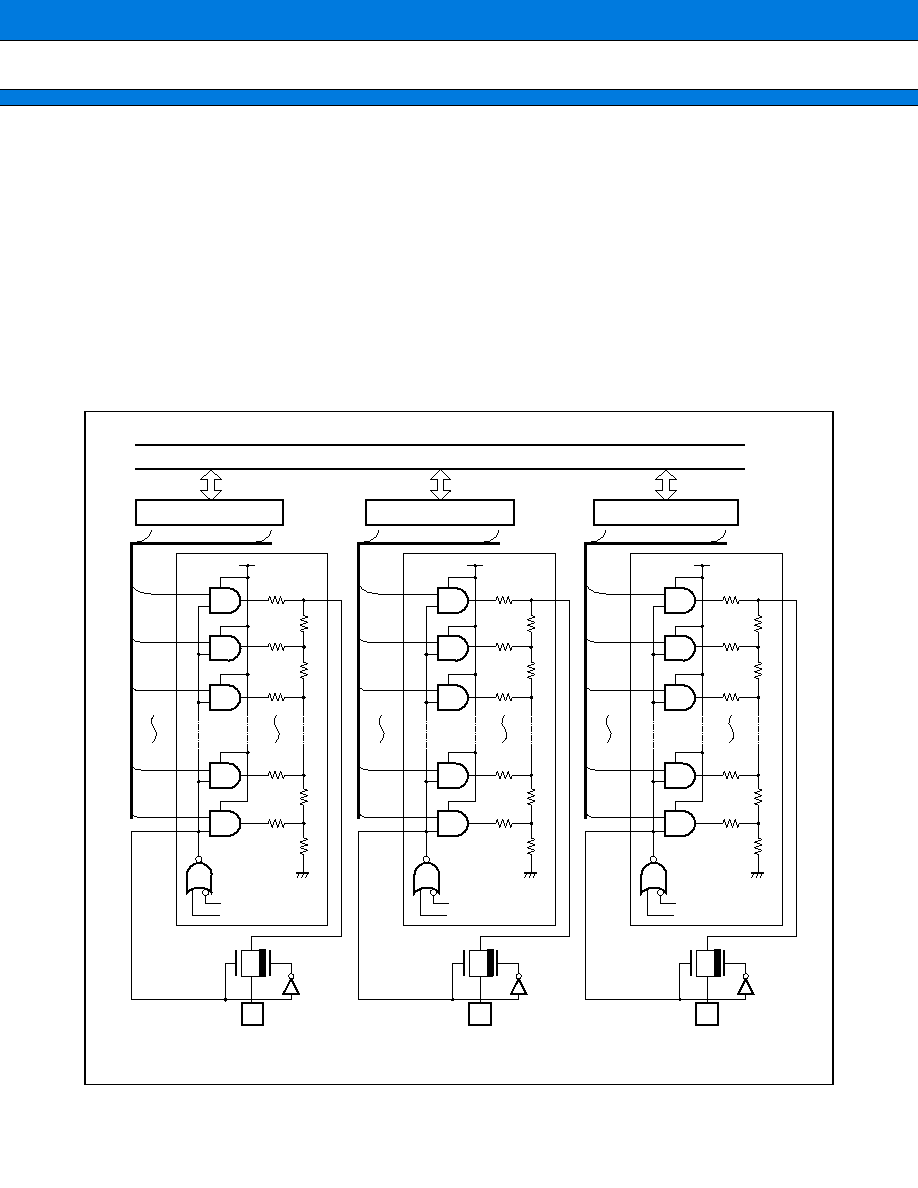

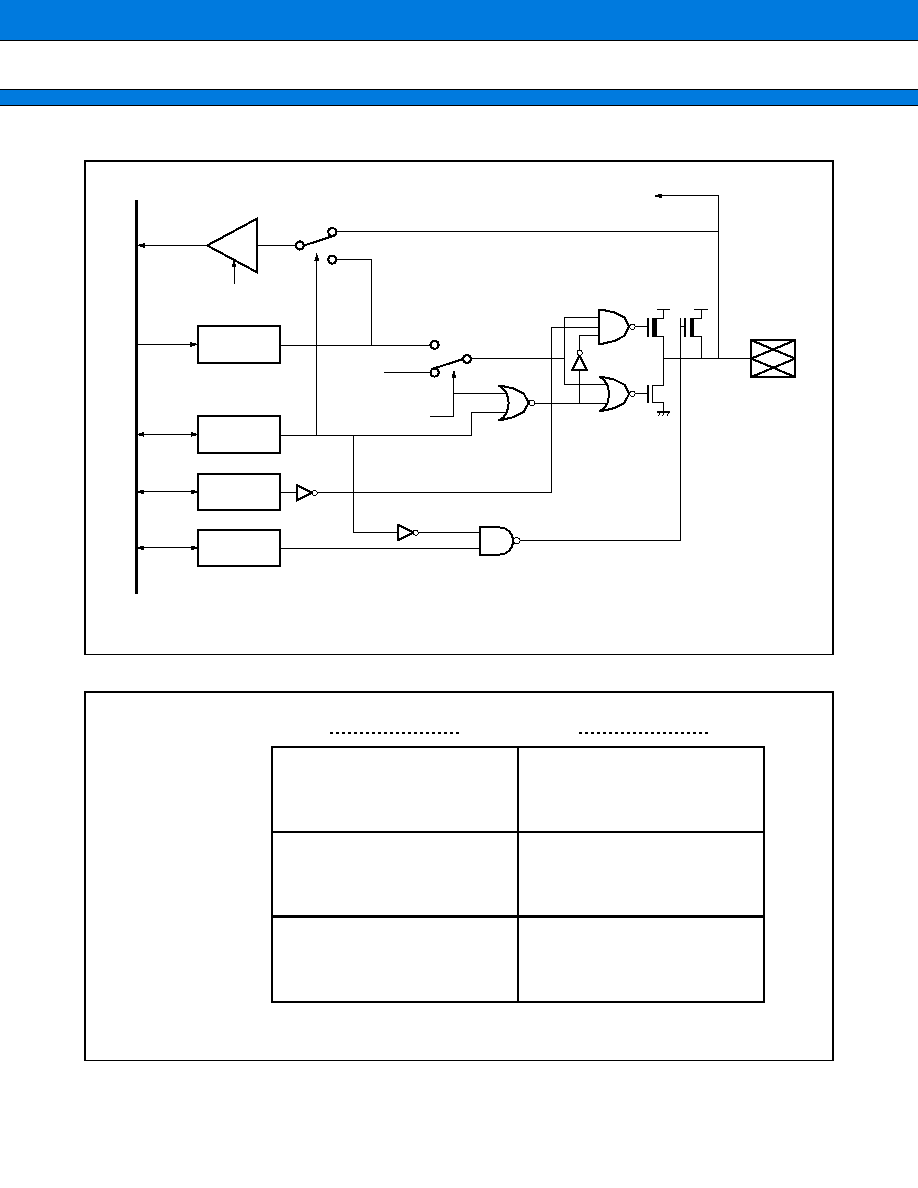

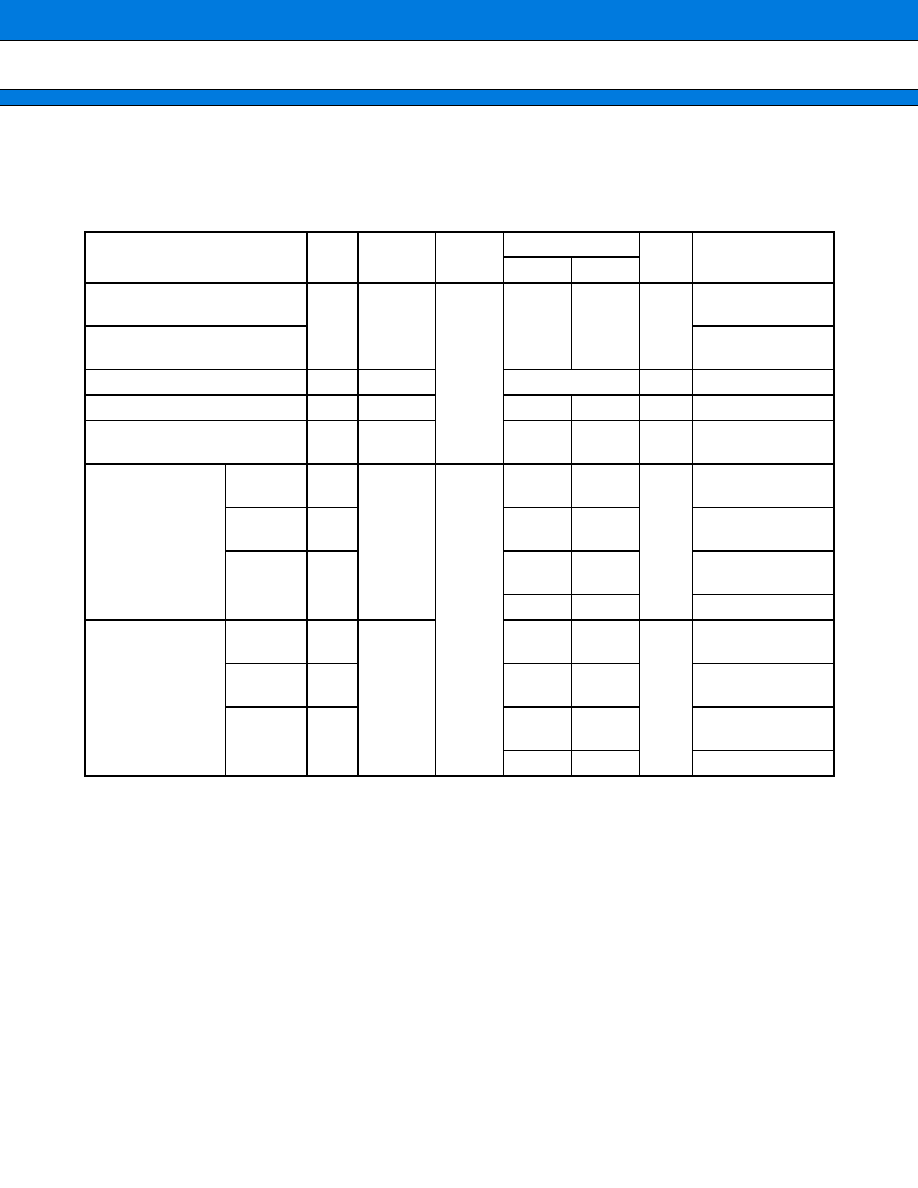

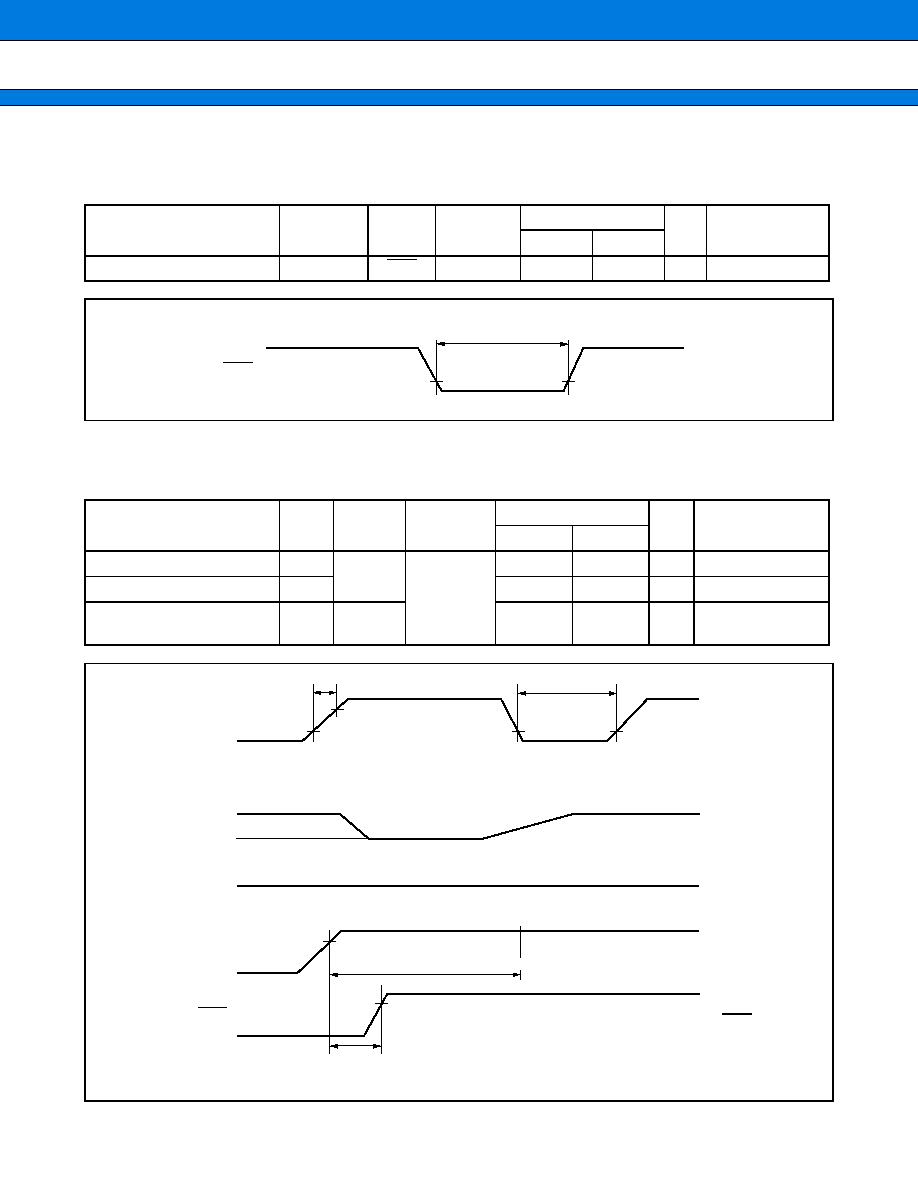

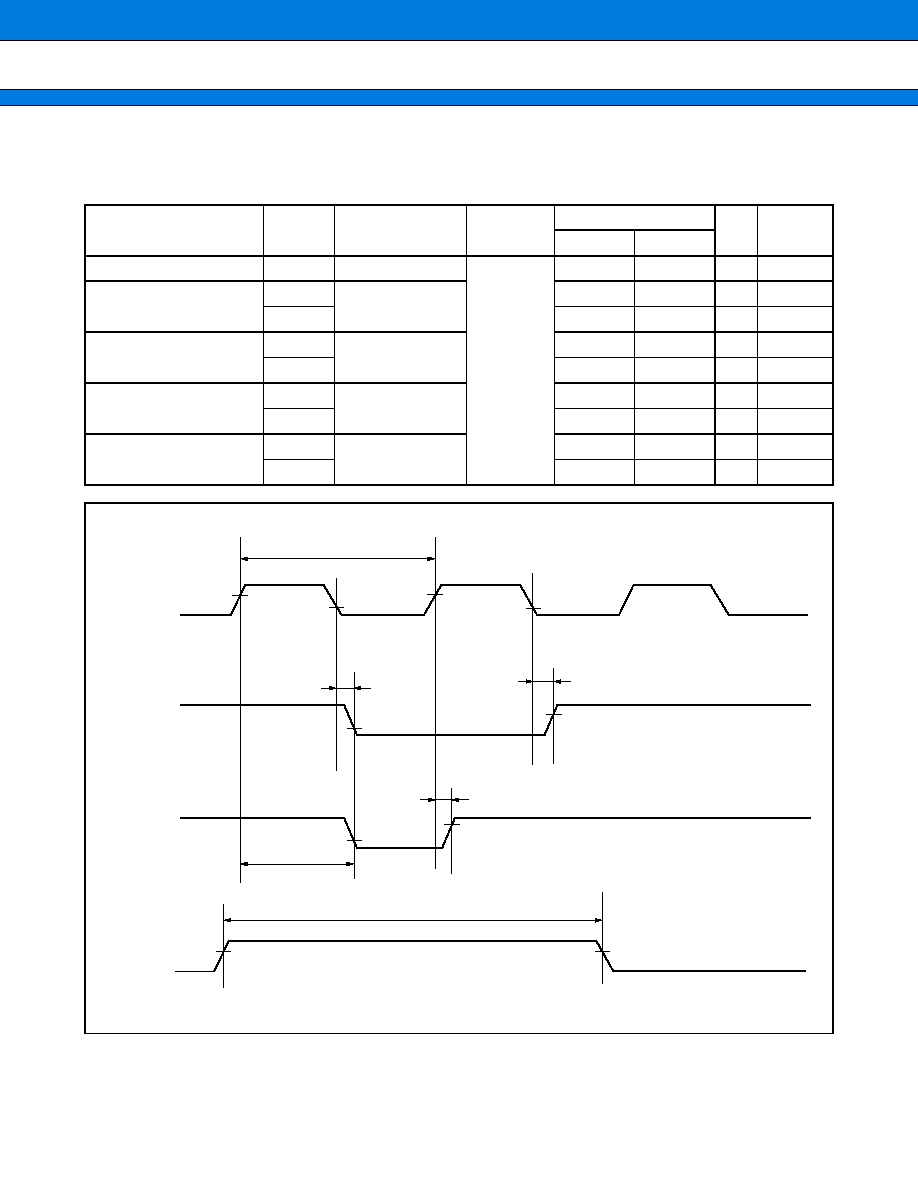

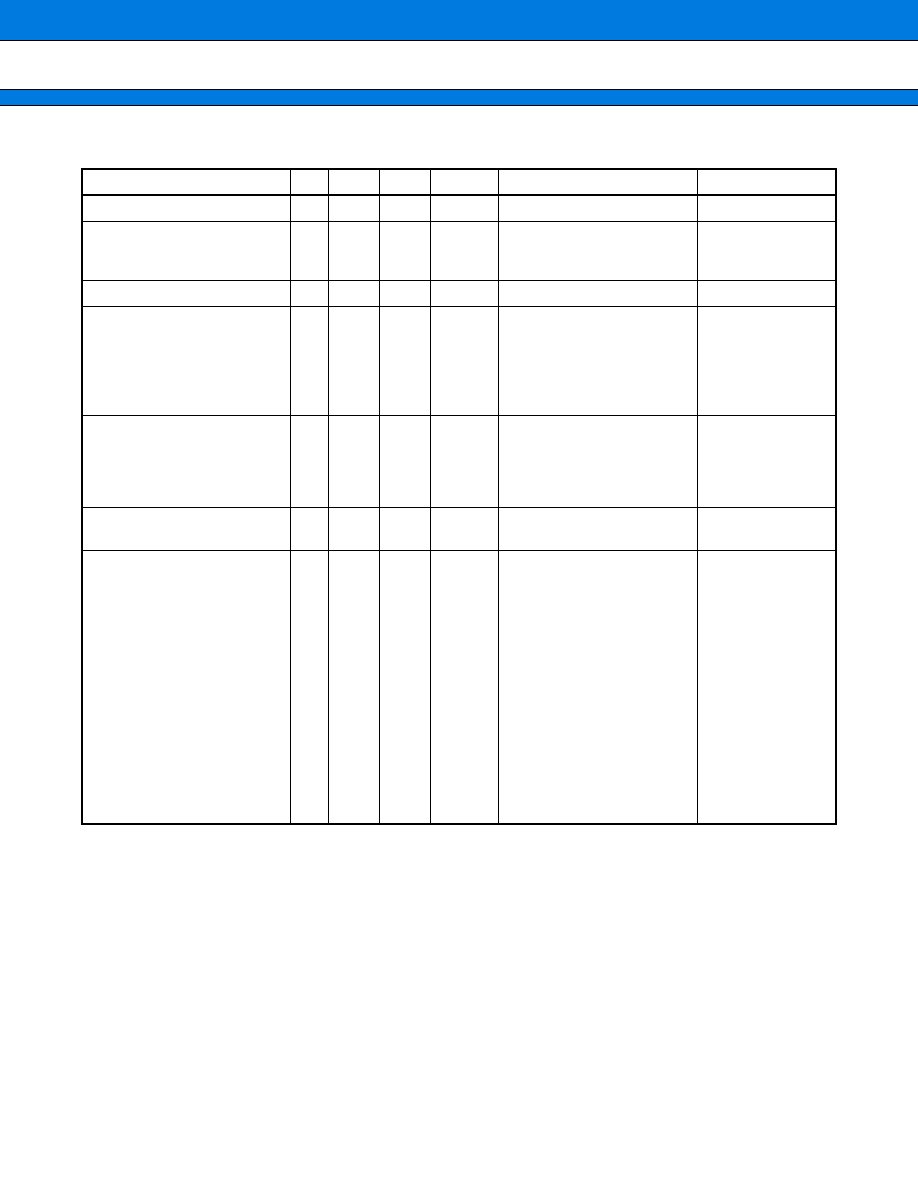

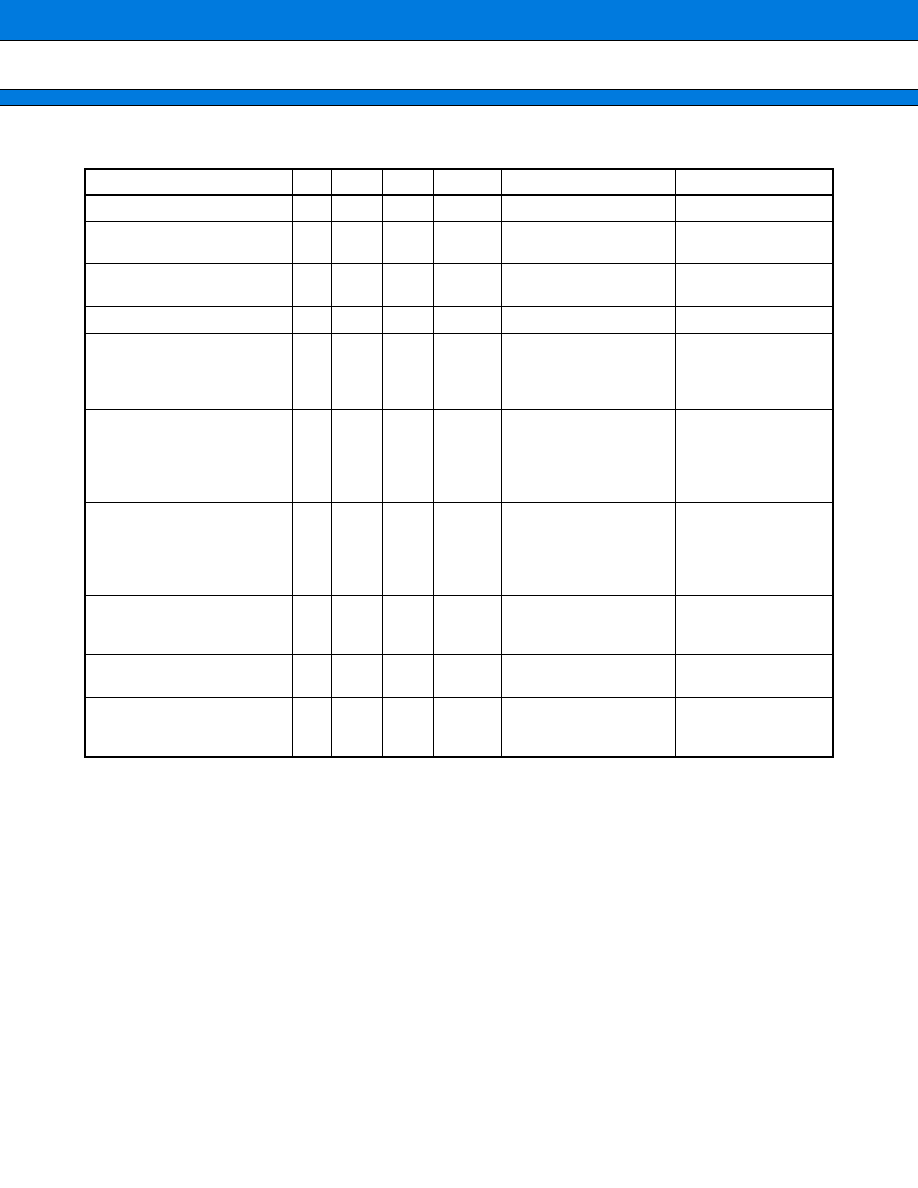

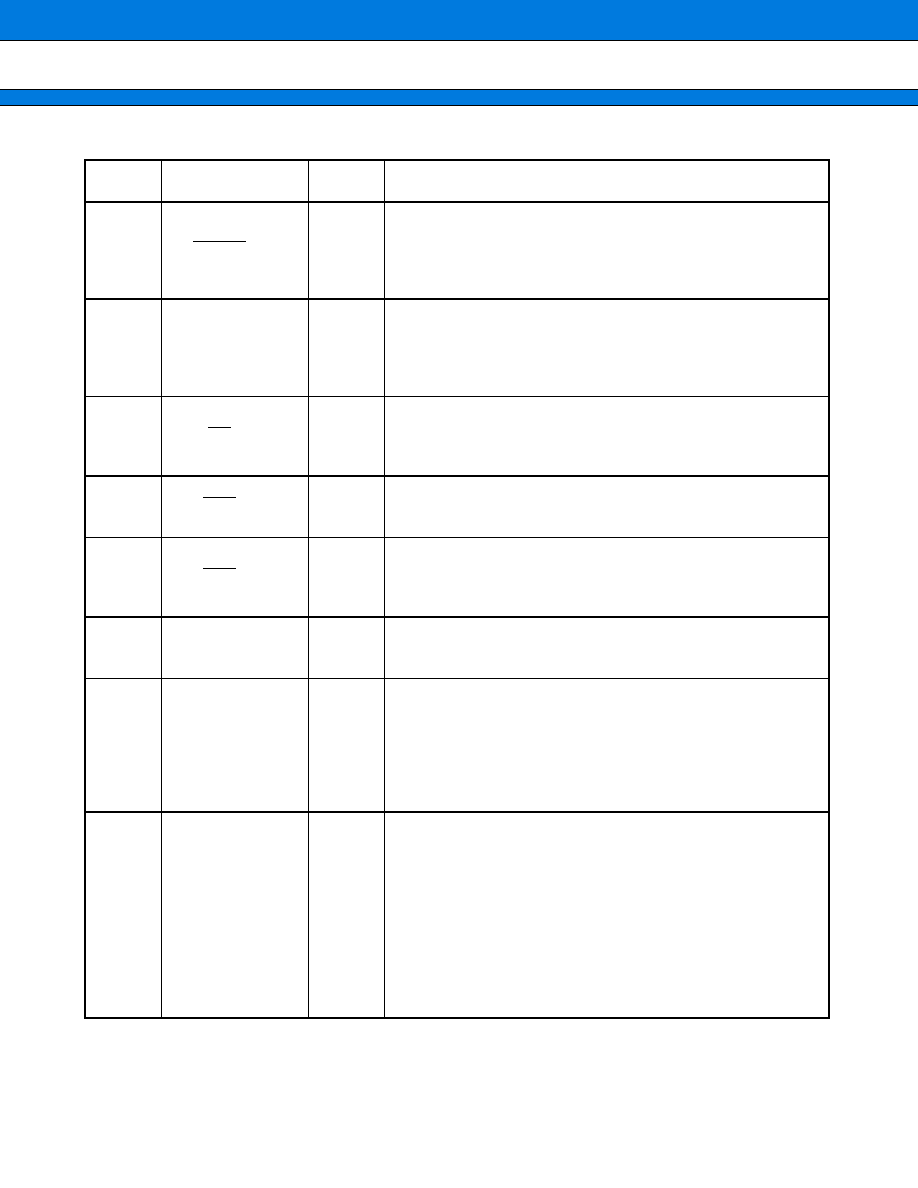

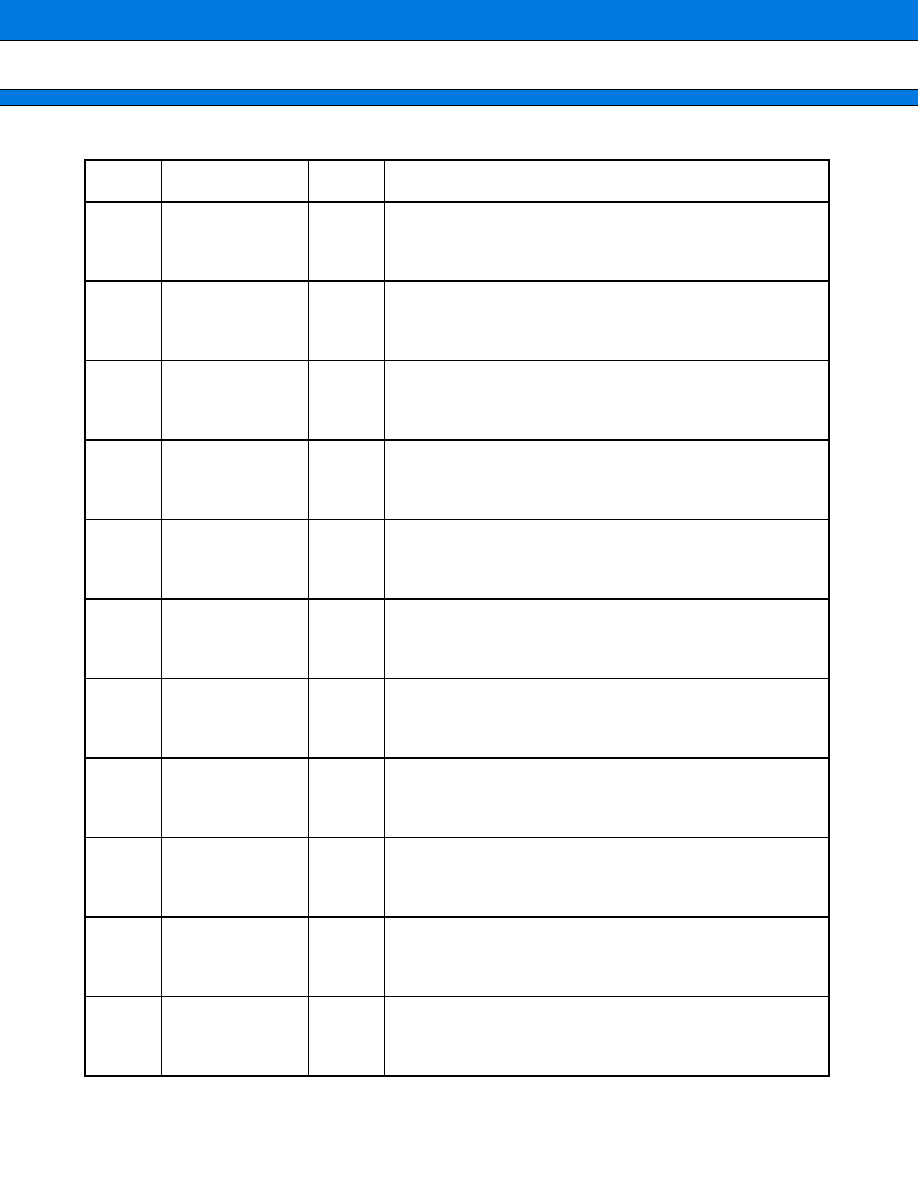

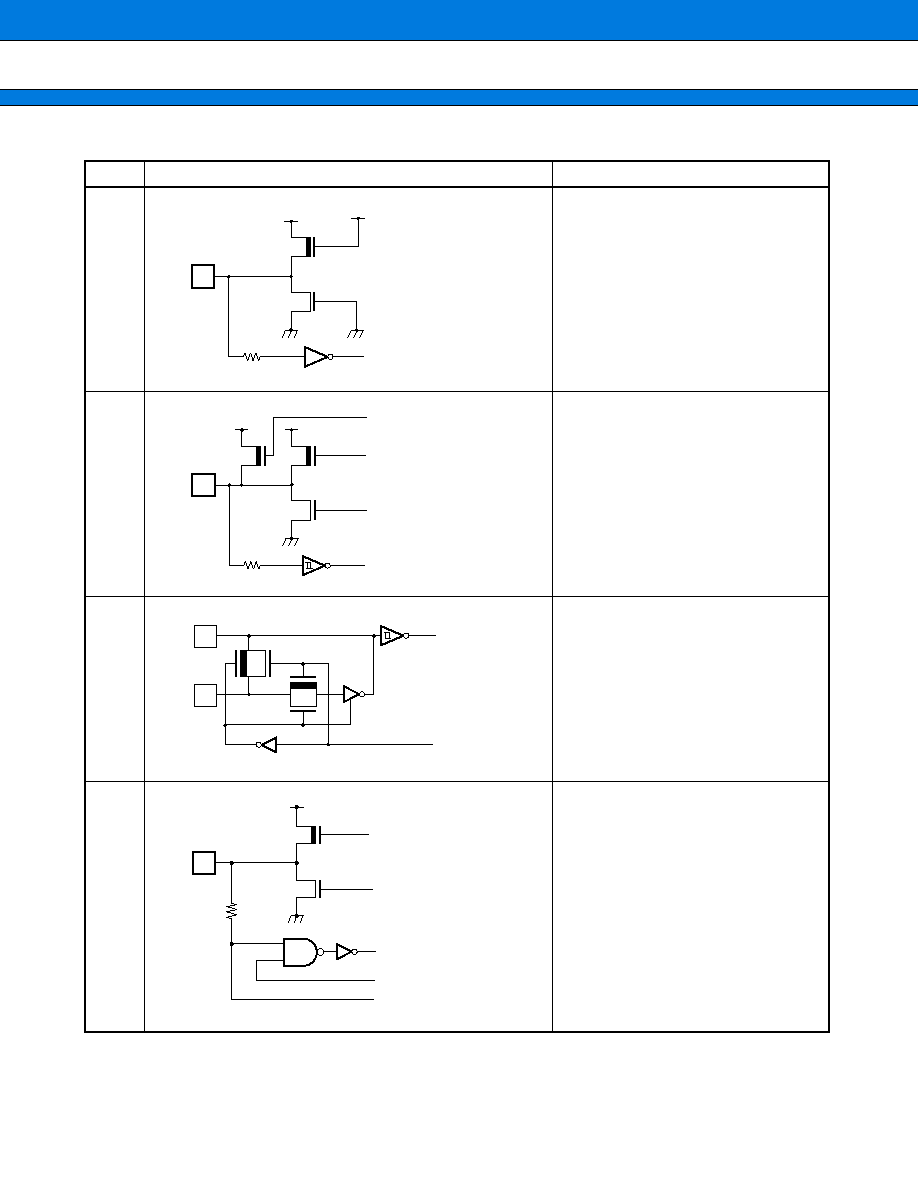

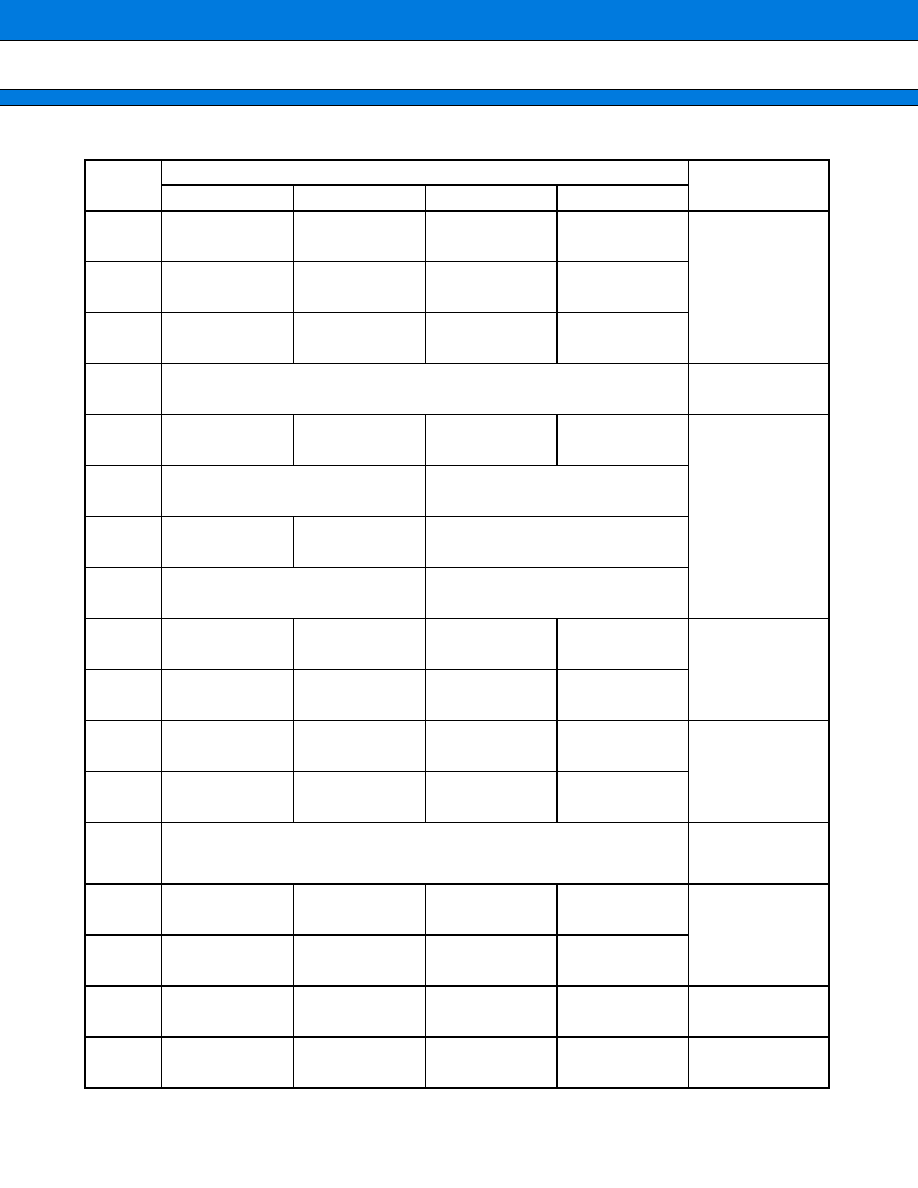

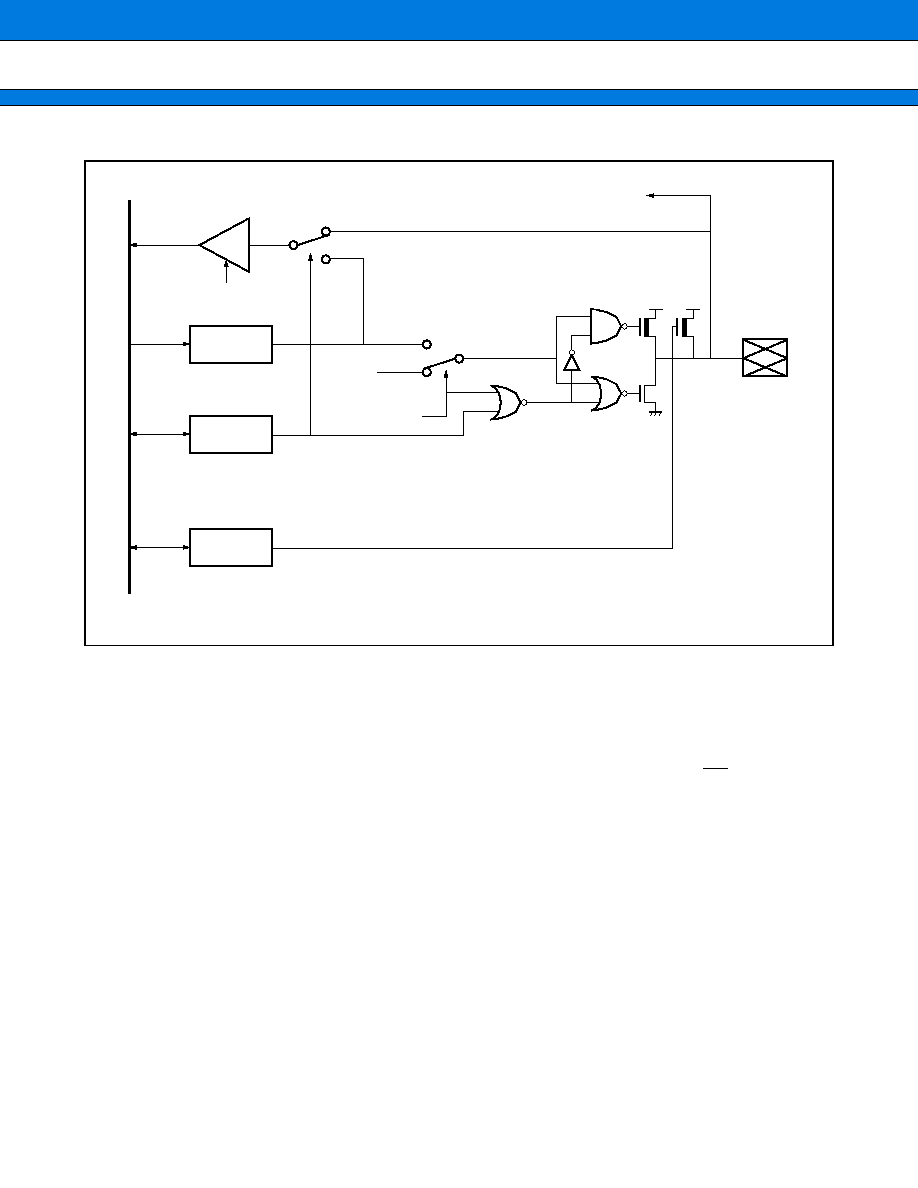

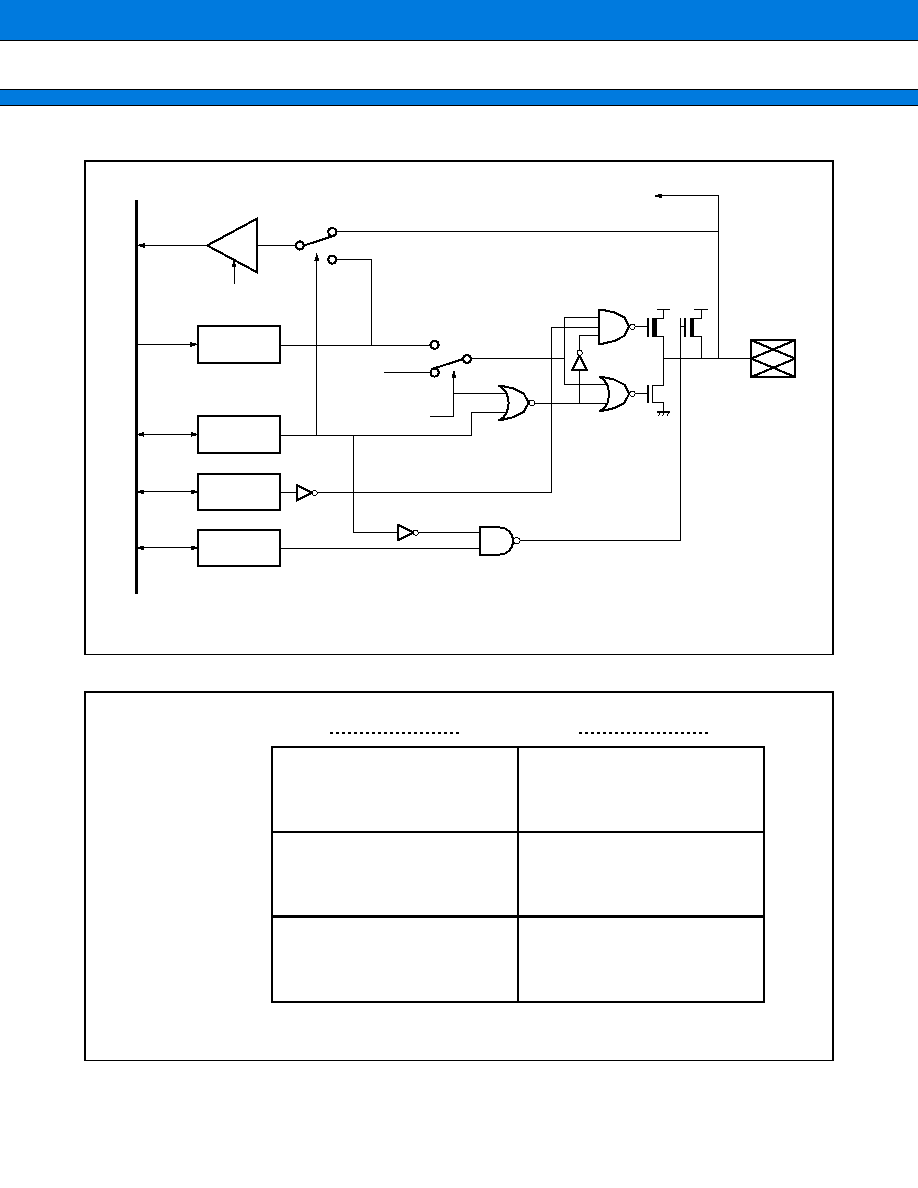

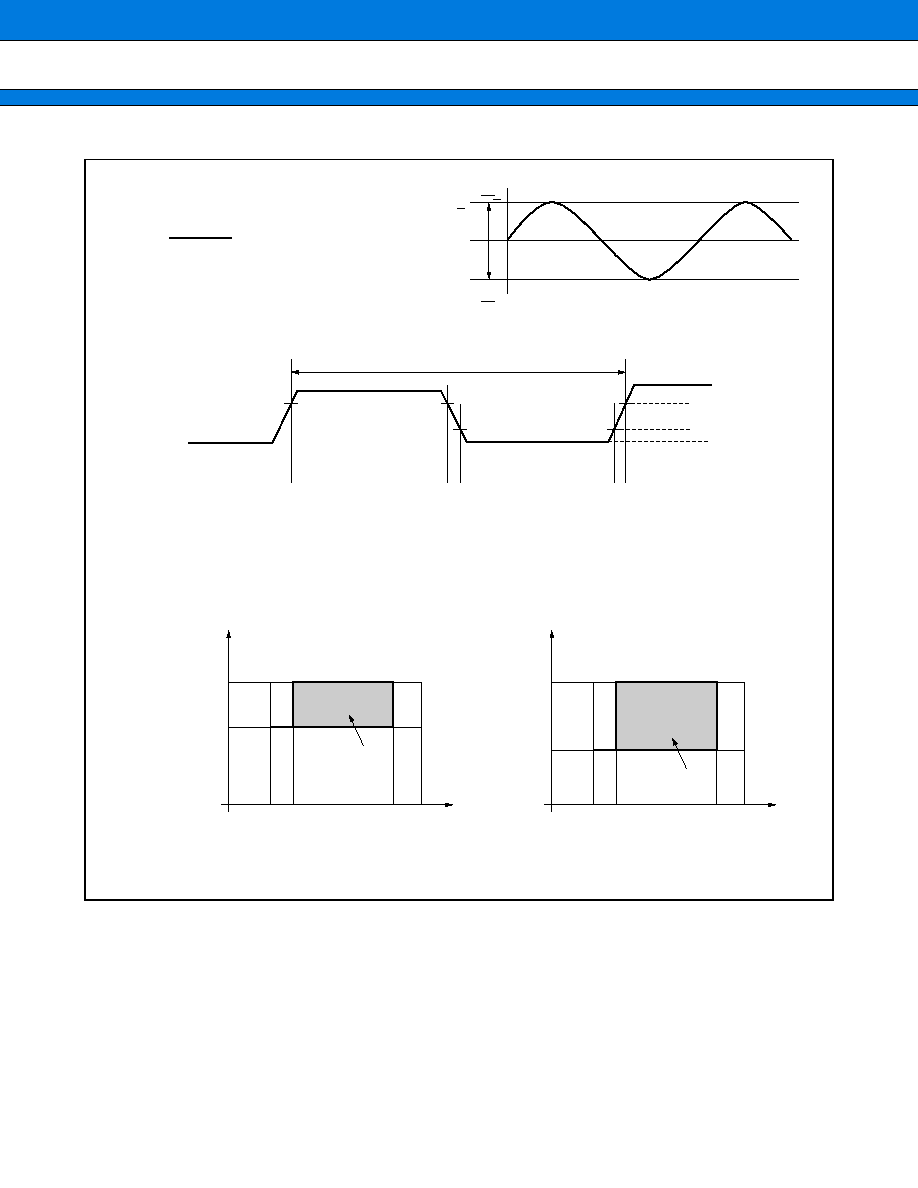

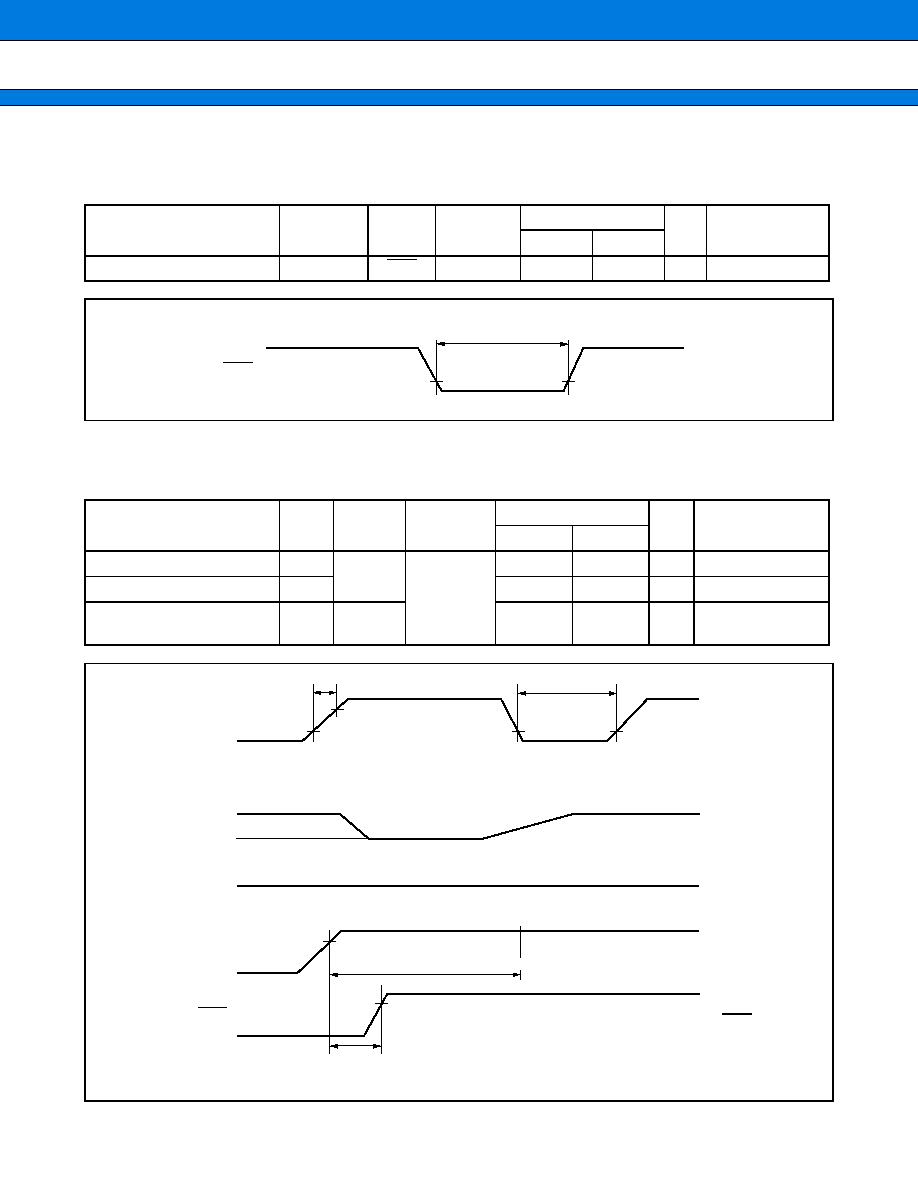

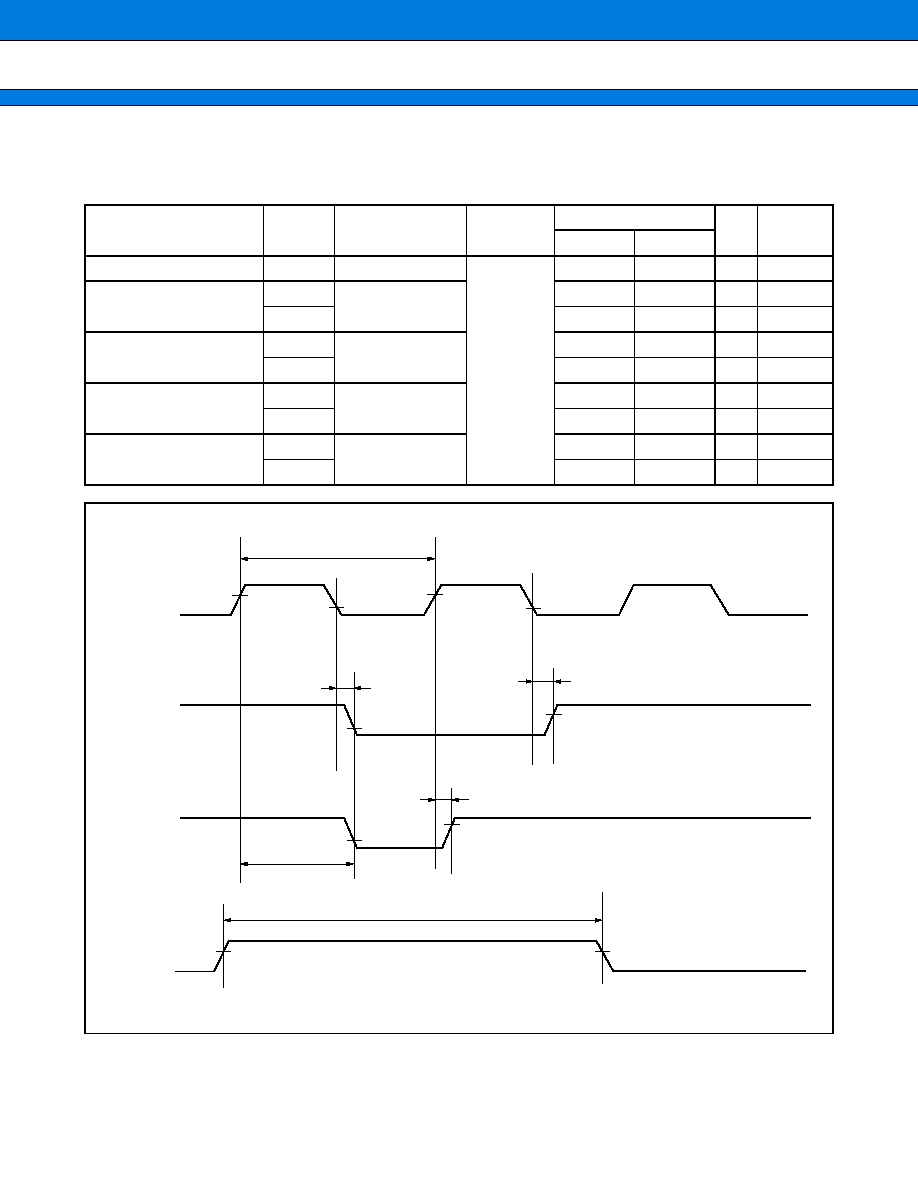

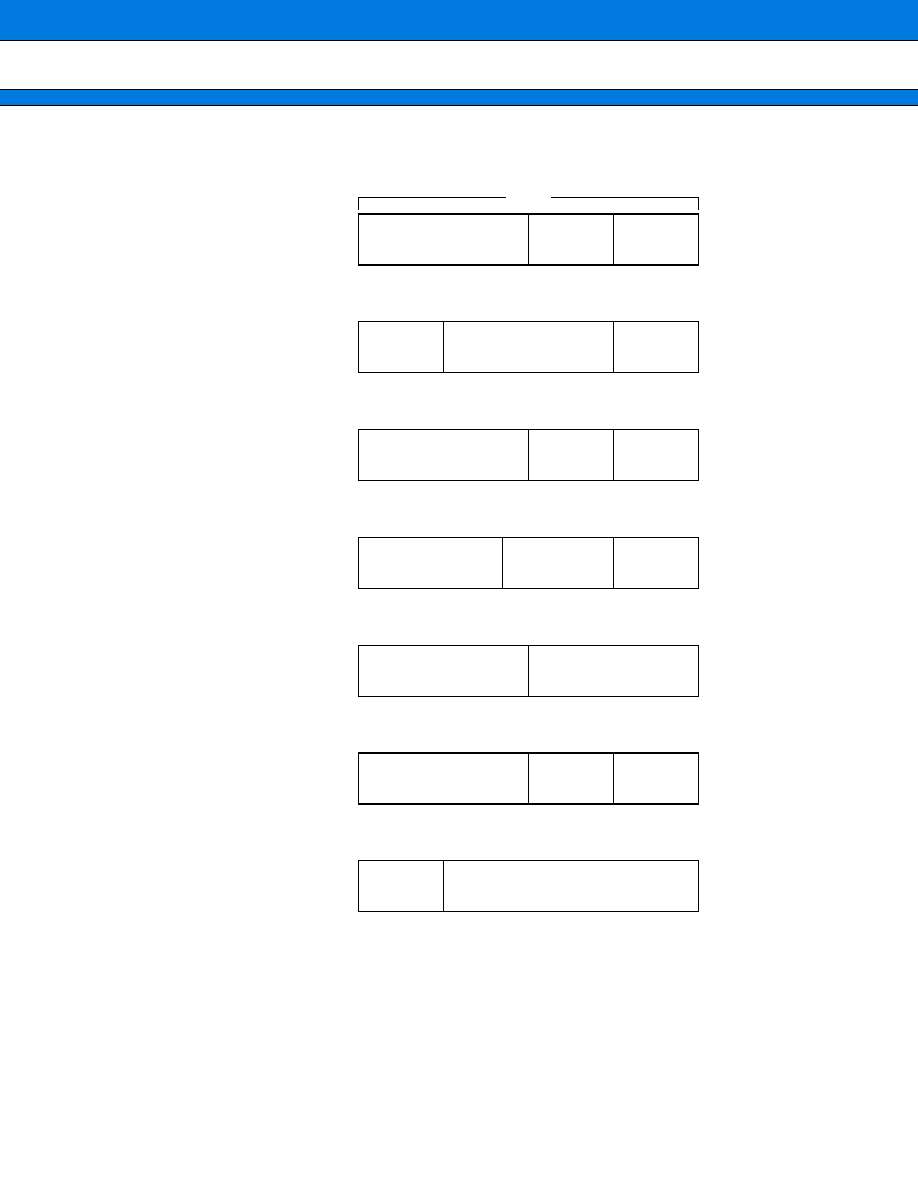

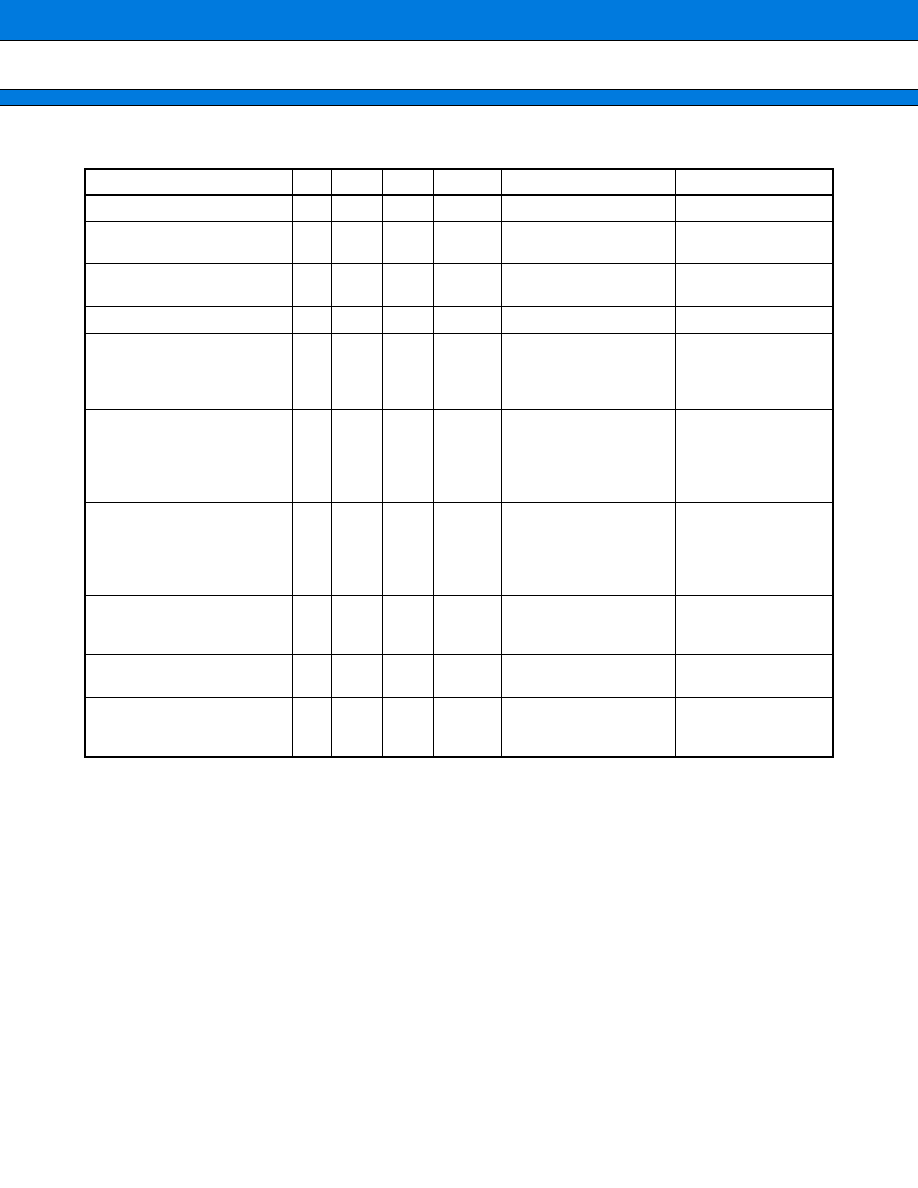

INPUT/OUTPUT CIRCUIT TYPES

(Continued)

Type

Circuit

Remarks

A

∑ High-speed oscillation circuit

(16.5 MHz)

Oscillation feedback resistance

=

approximately 1 M

3 V CMOS level input

B

∑ With pull up resistance

CMOS level input

Pull-up resistance value

=

approximately 25 k

(Typ.)

C

∑ CMOS level input/output pin

CMOS level output

CMOS level input

(with standby control)

I

OL

=

4 mA

F

∑ CMOS hysteresis input/output pin

CMOS level output

CMOS hysteresis input

(with standby control)

I

OL

=

4 mA

X1

X0

Xout

Standby control signal

Digital input

Pout

Nout

CMOS input

Standby control

R

Pout

Nout

Hysteresis input

Standby control

R

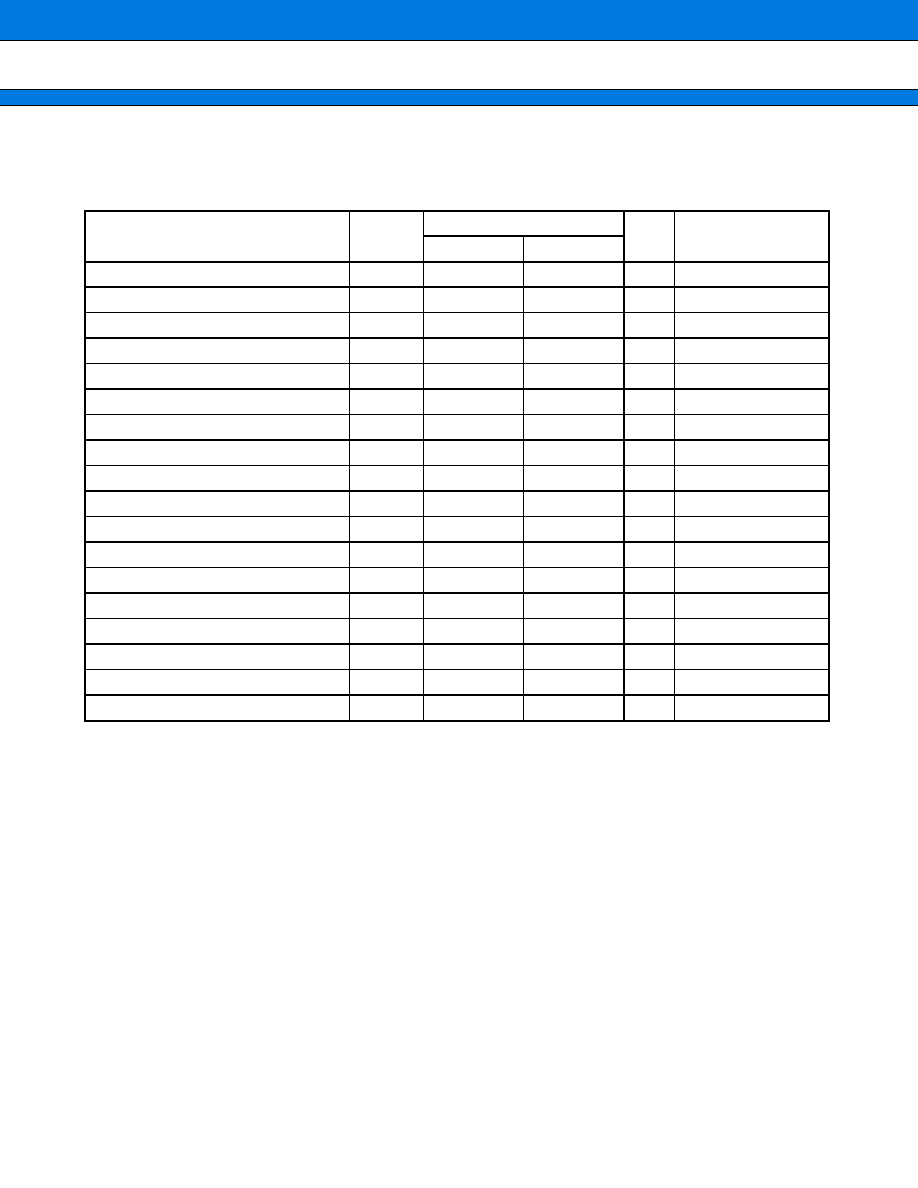

MB91133/MB91F133

18

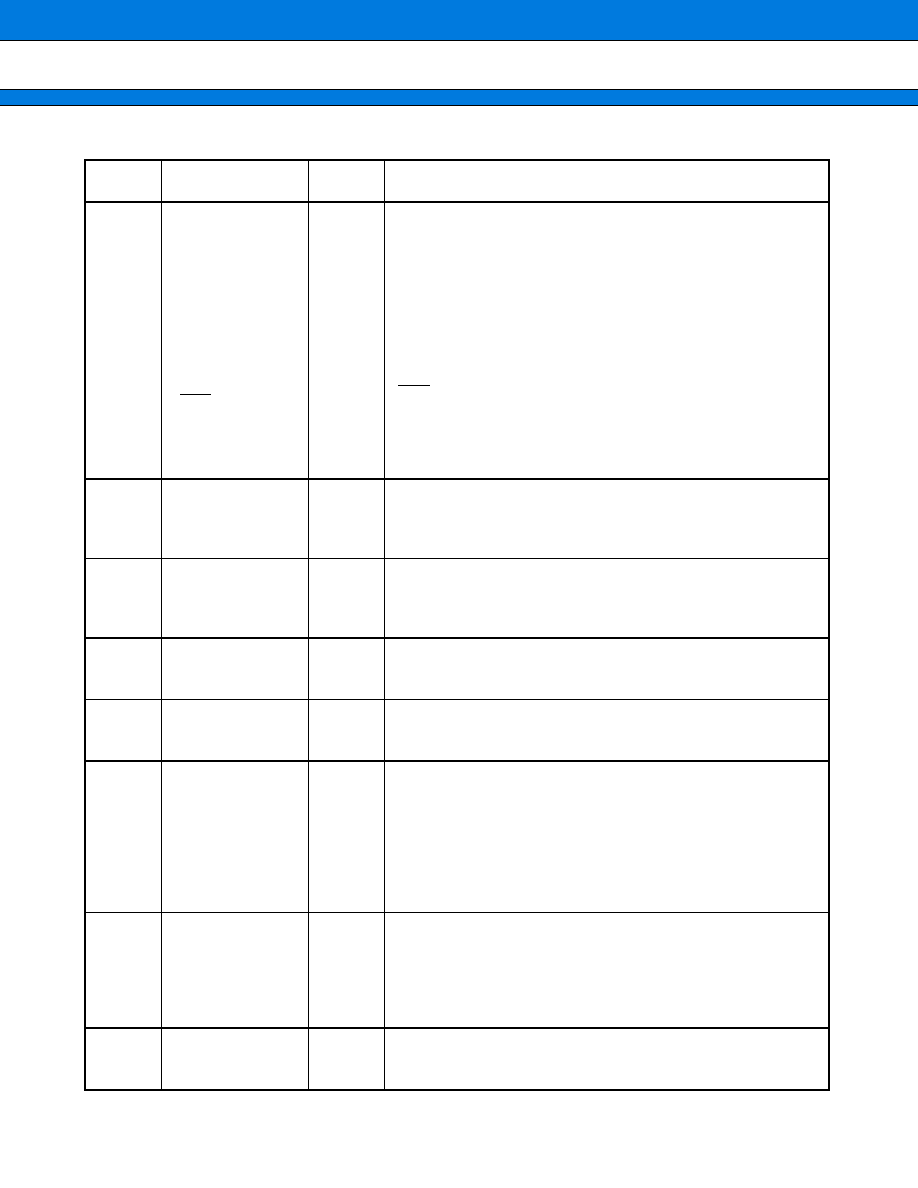

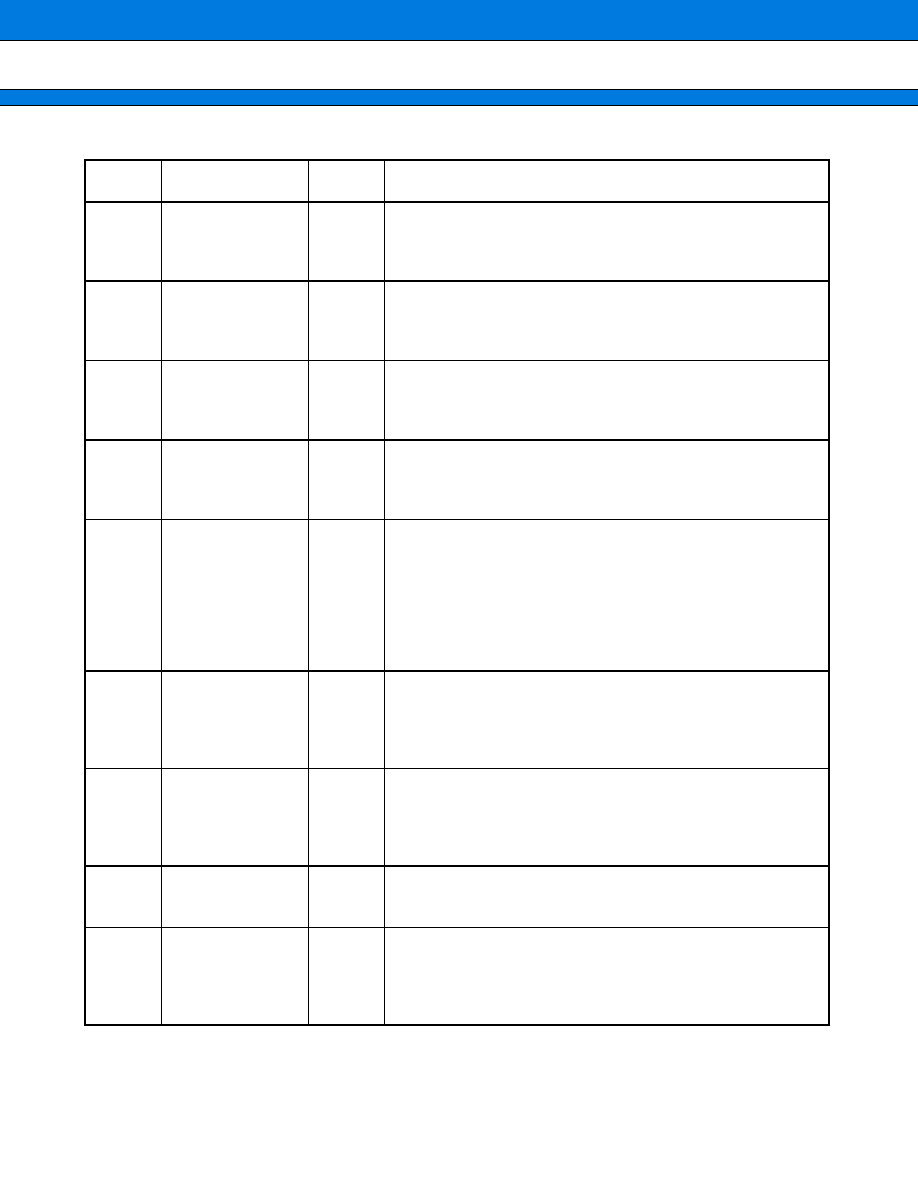

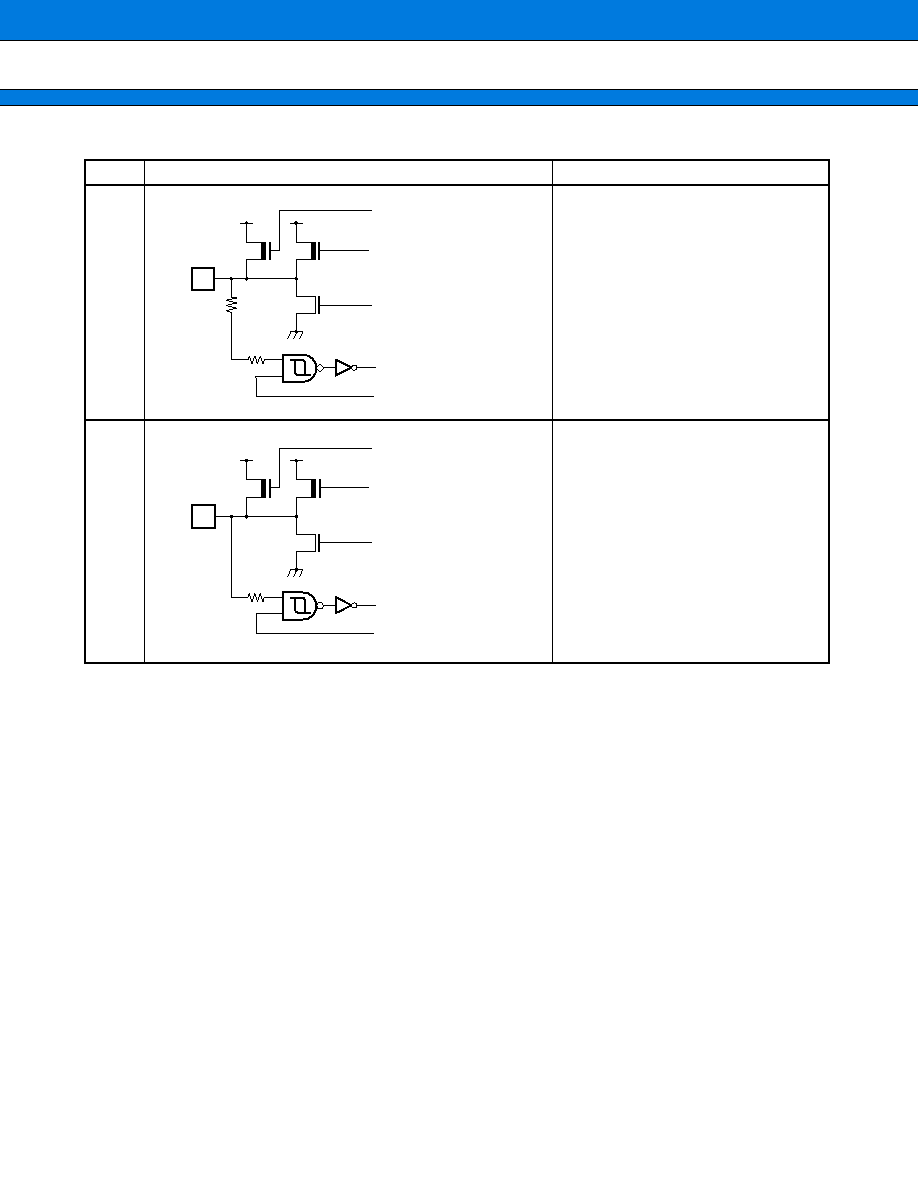

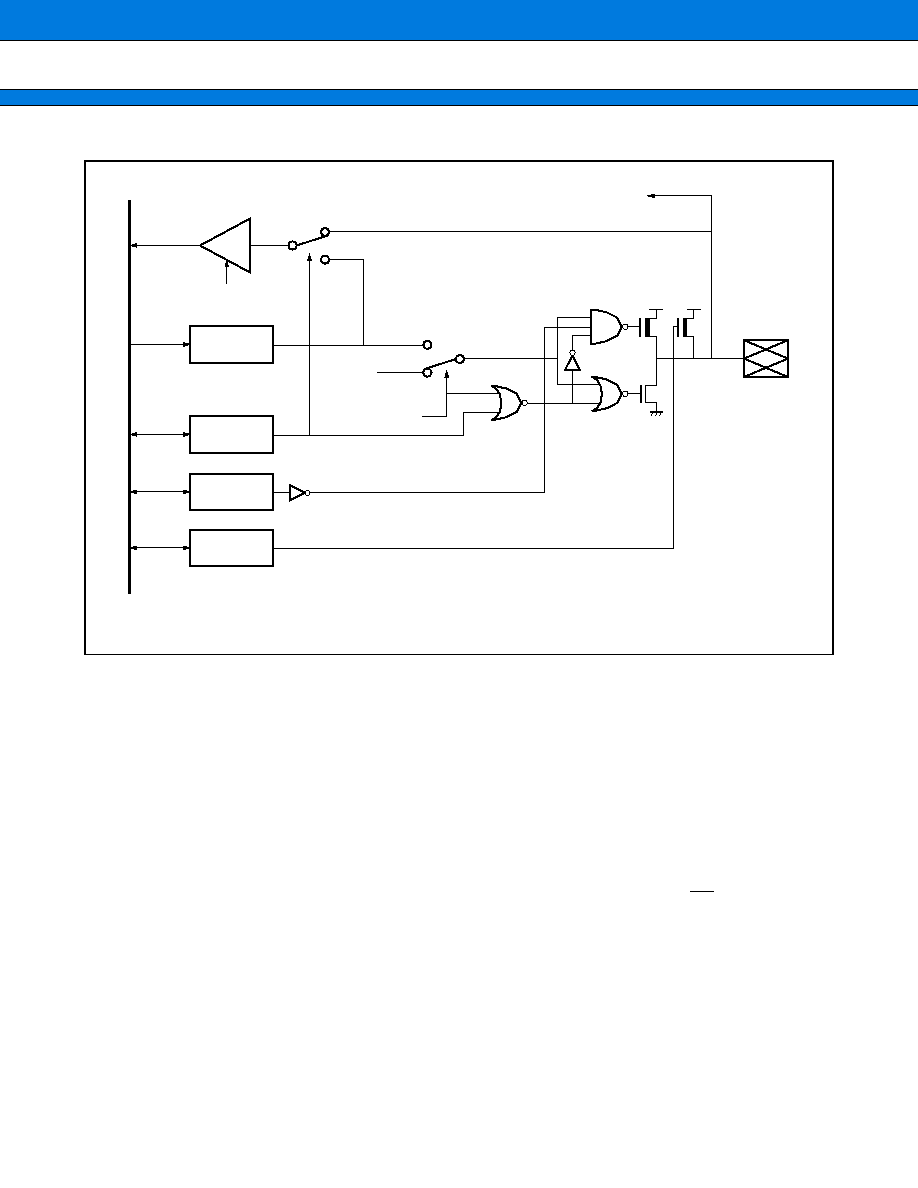

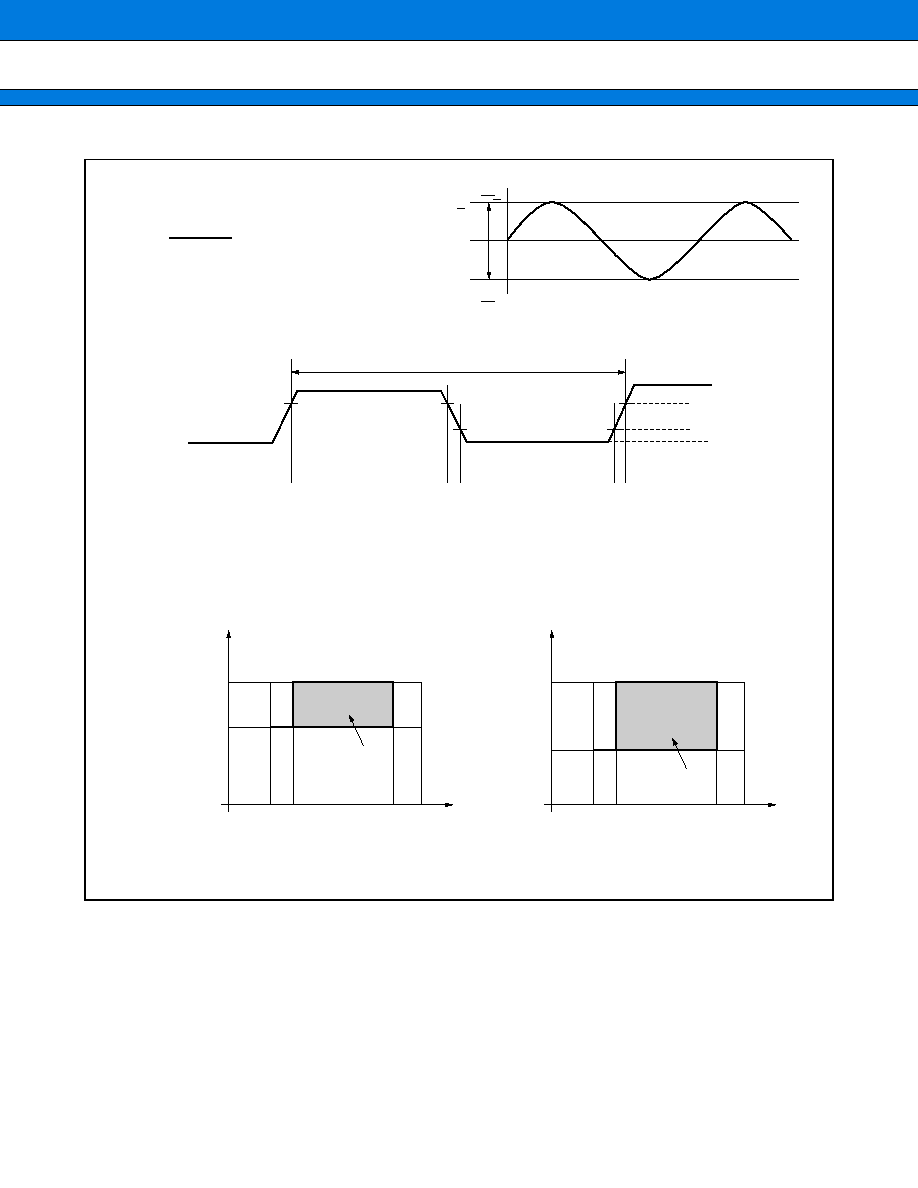

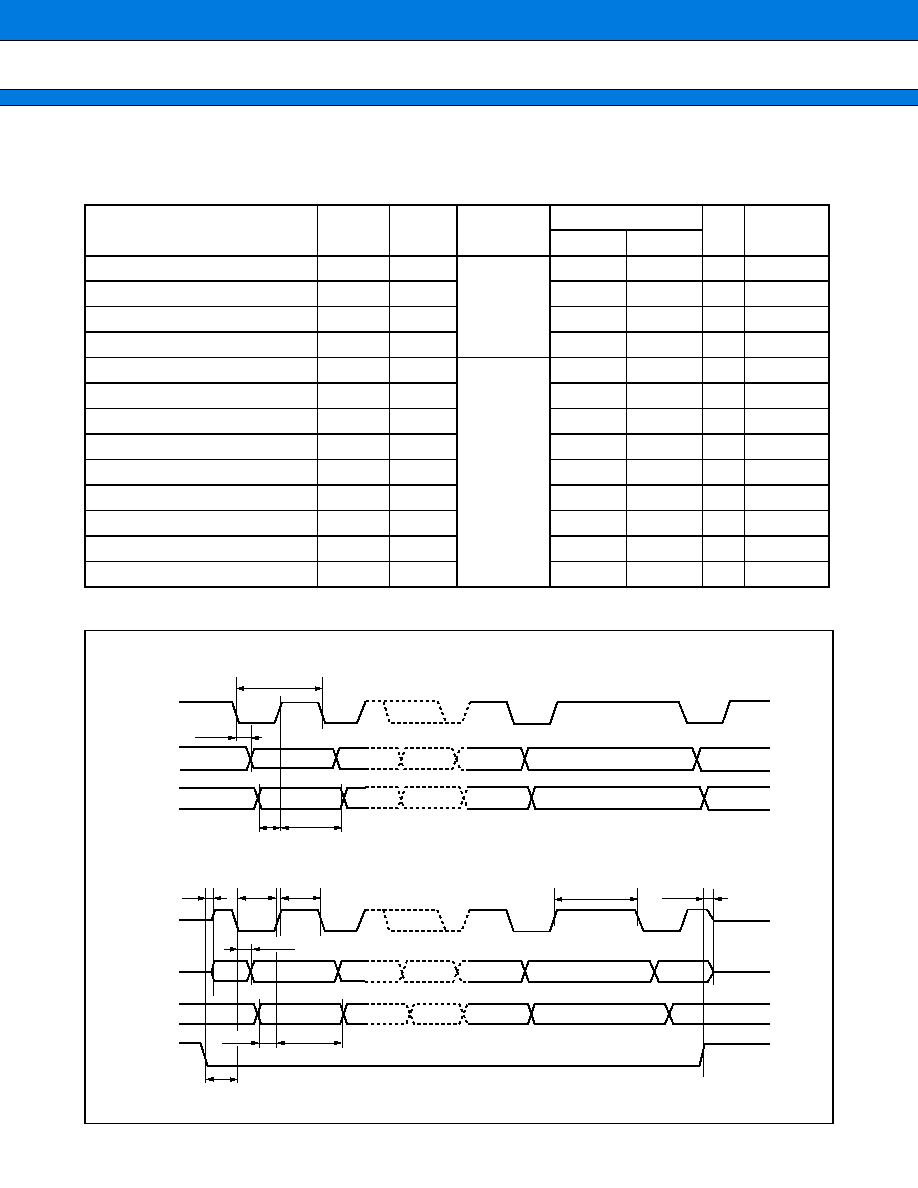

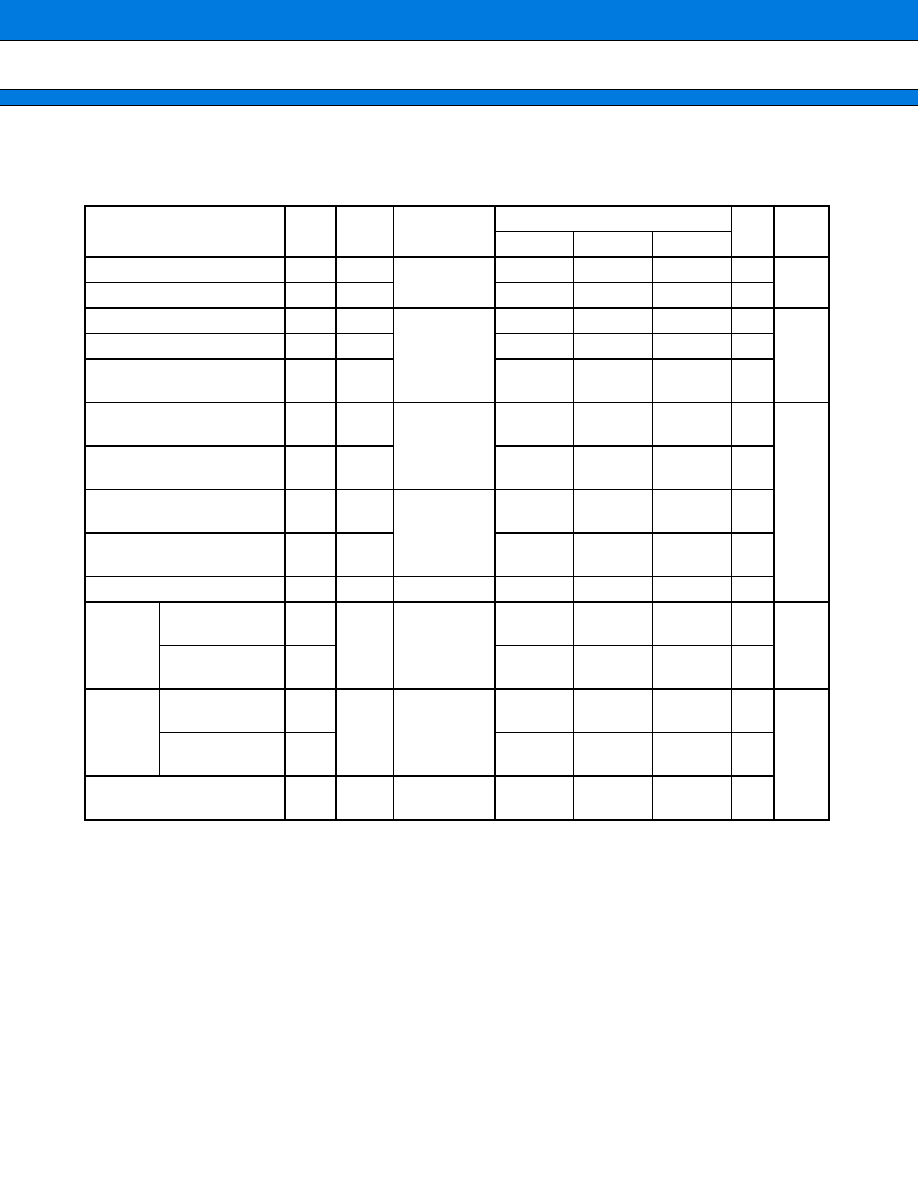

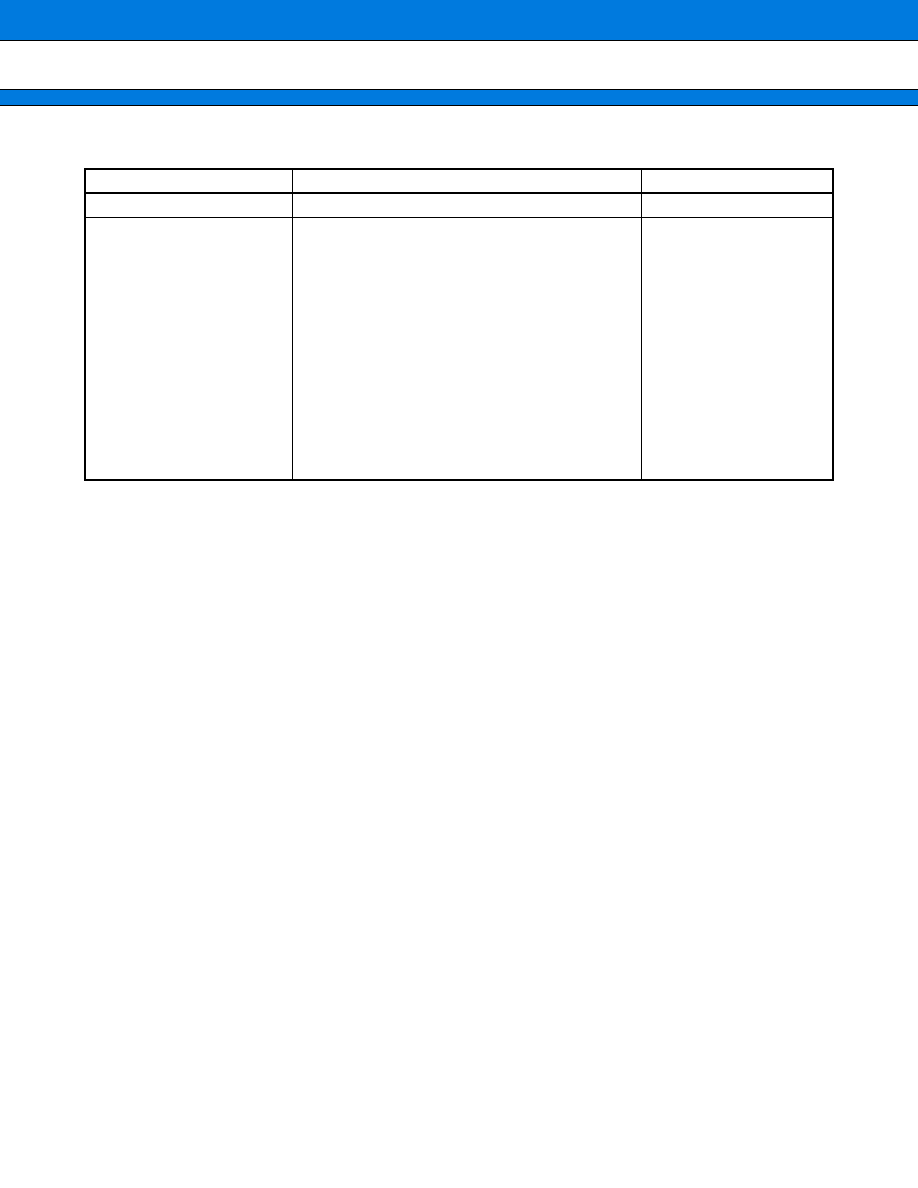

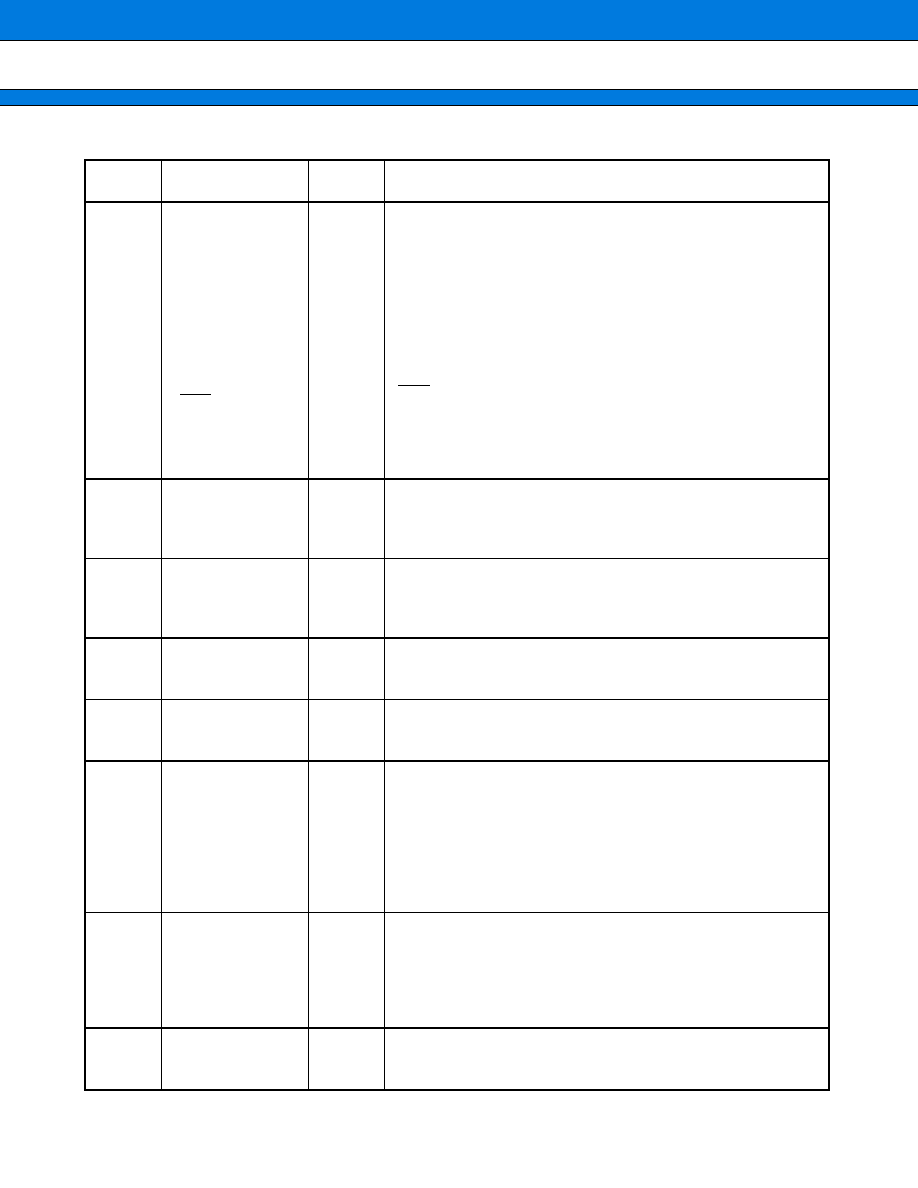

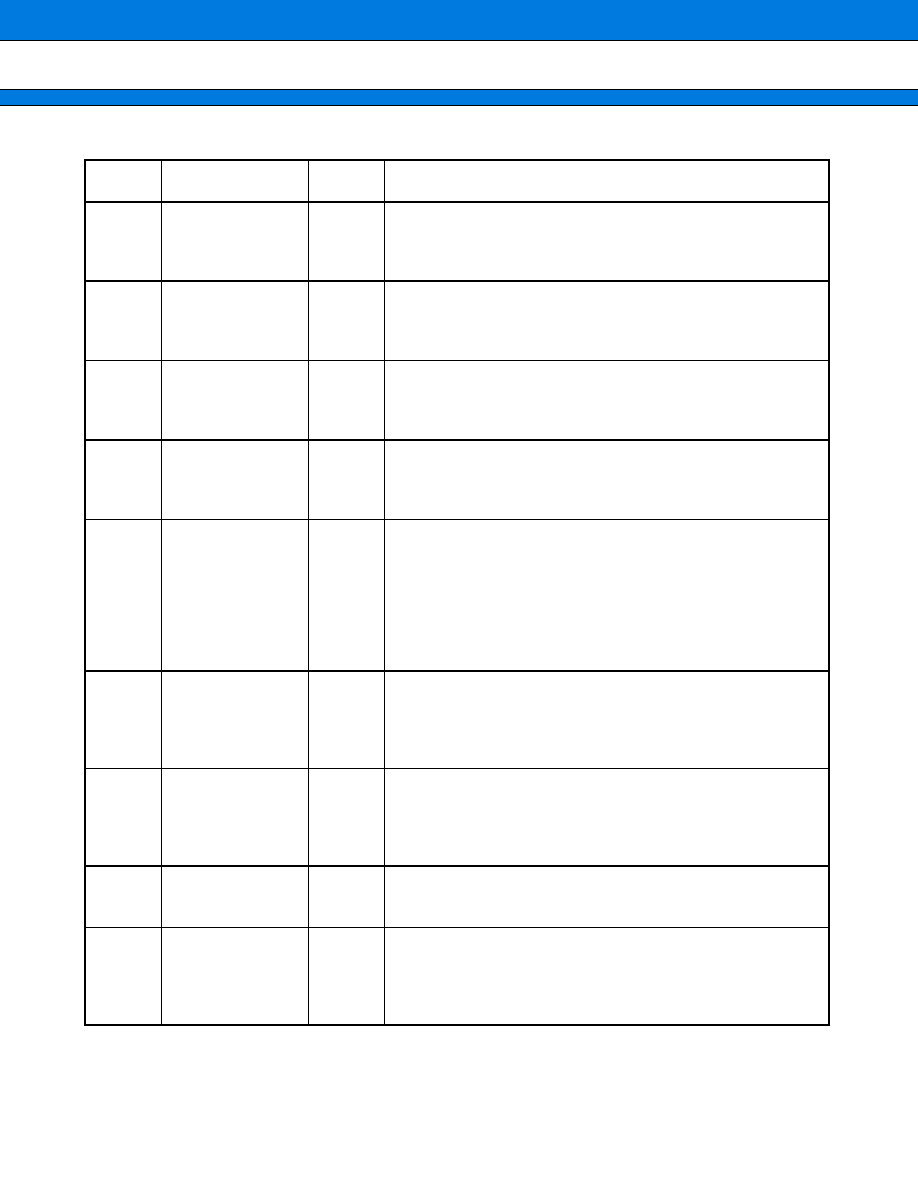

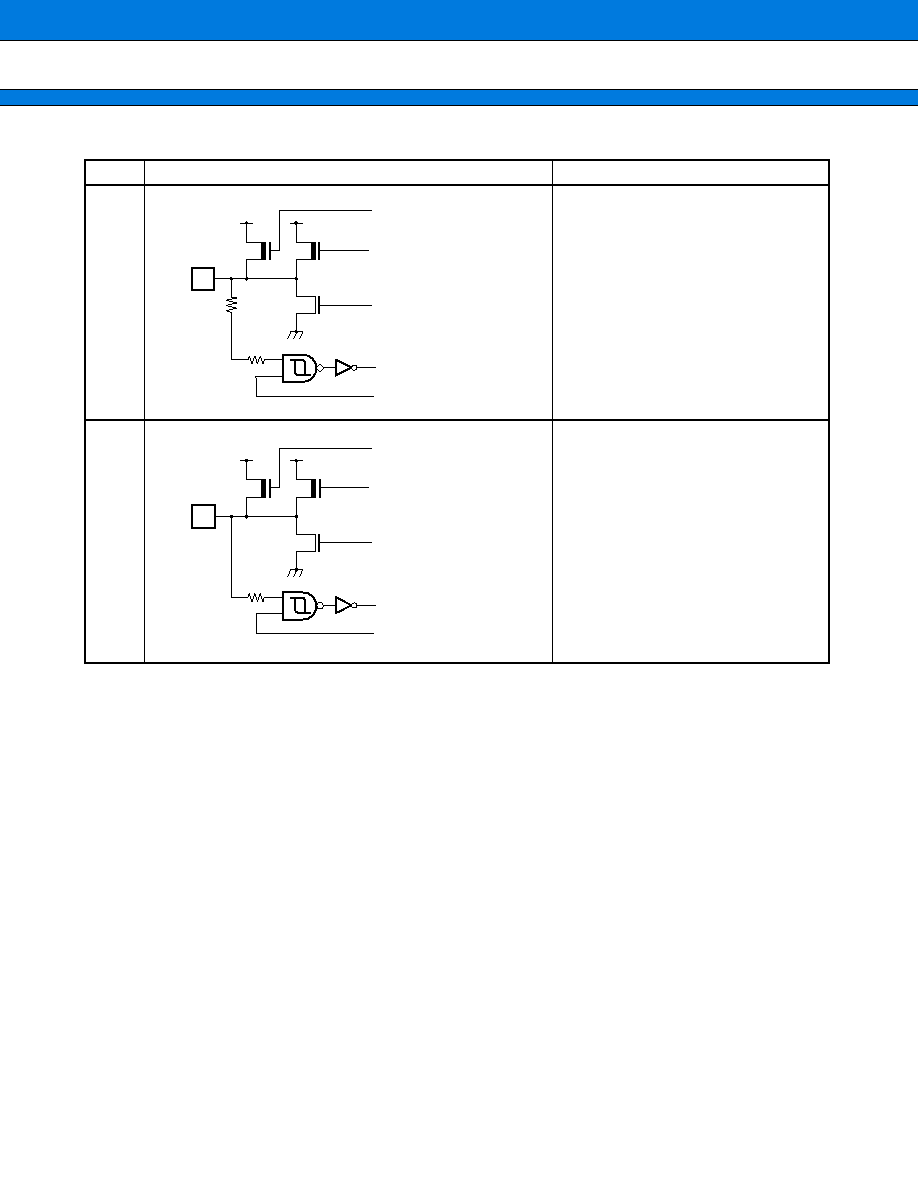

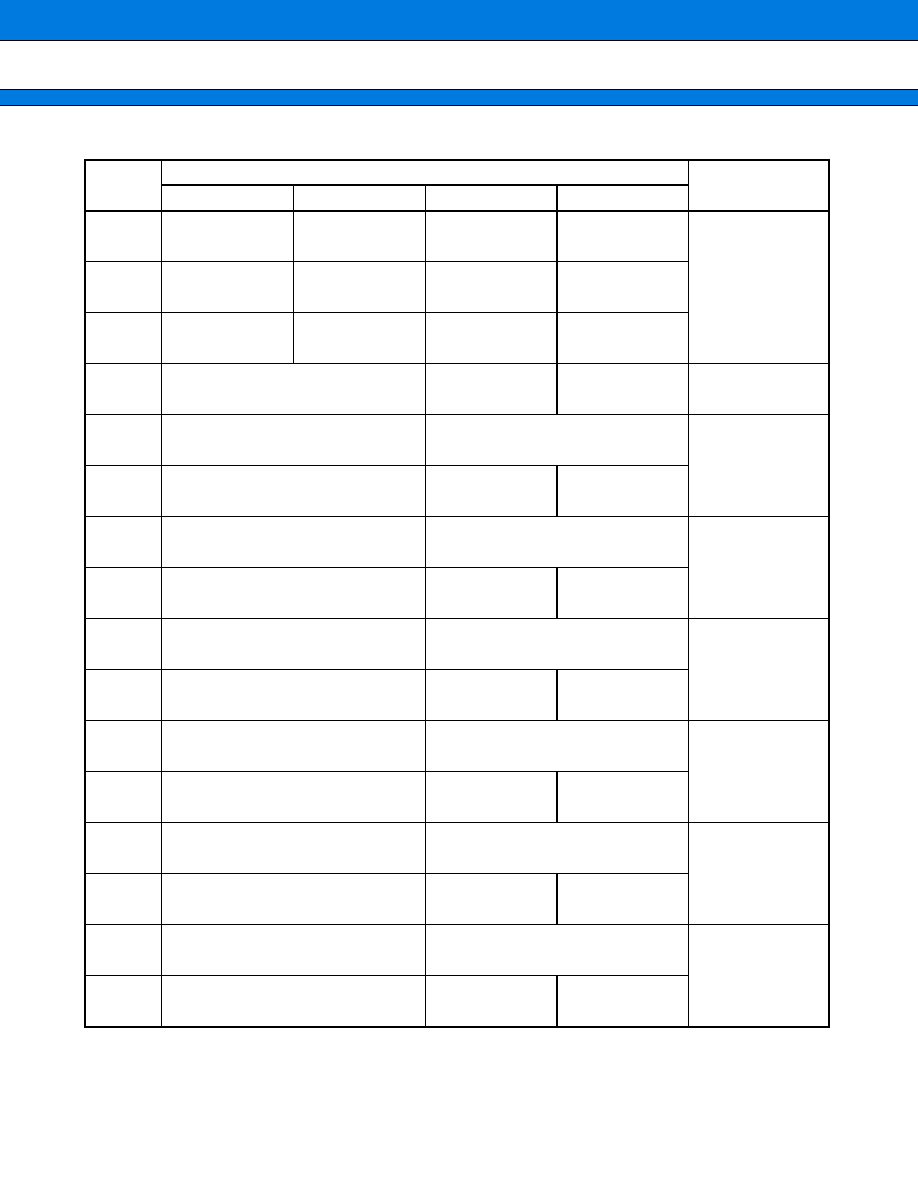

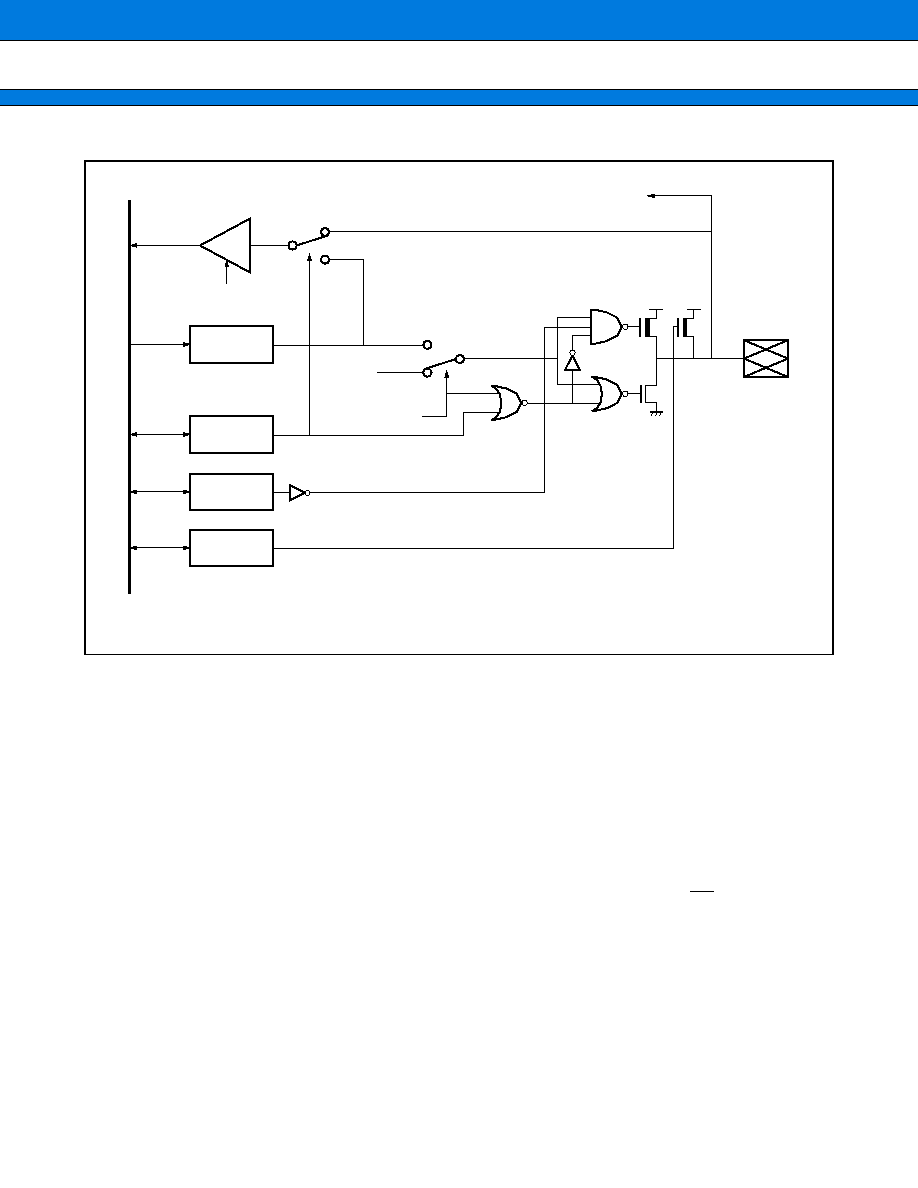

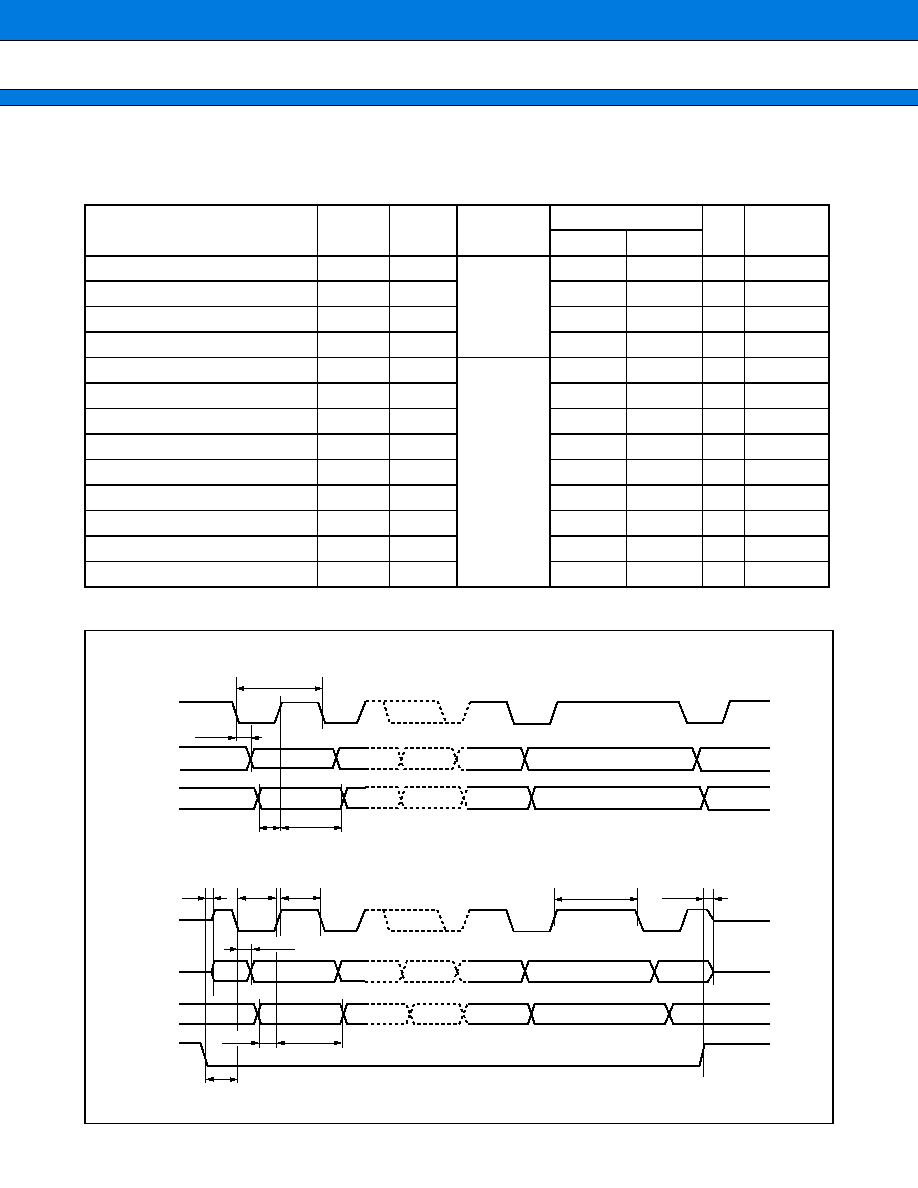

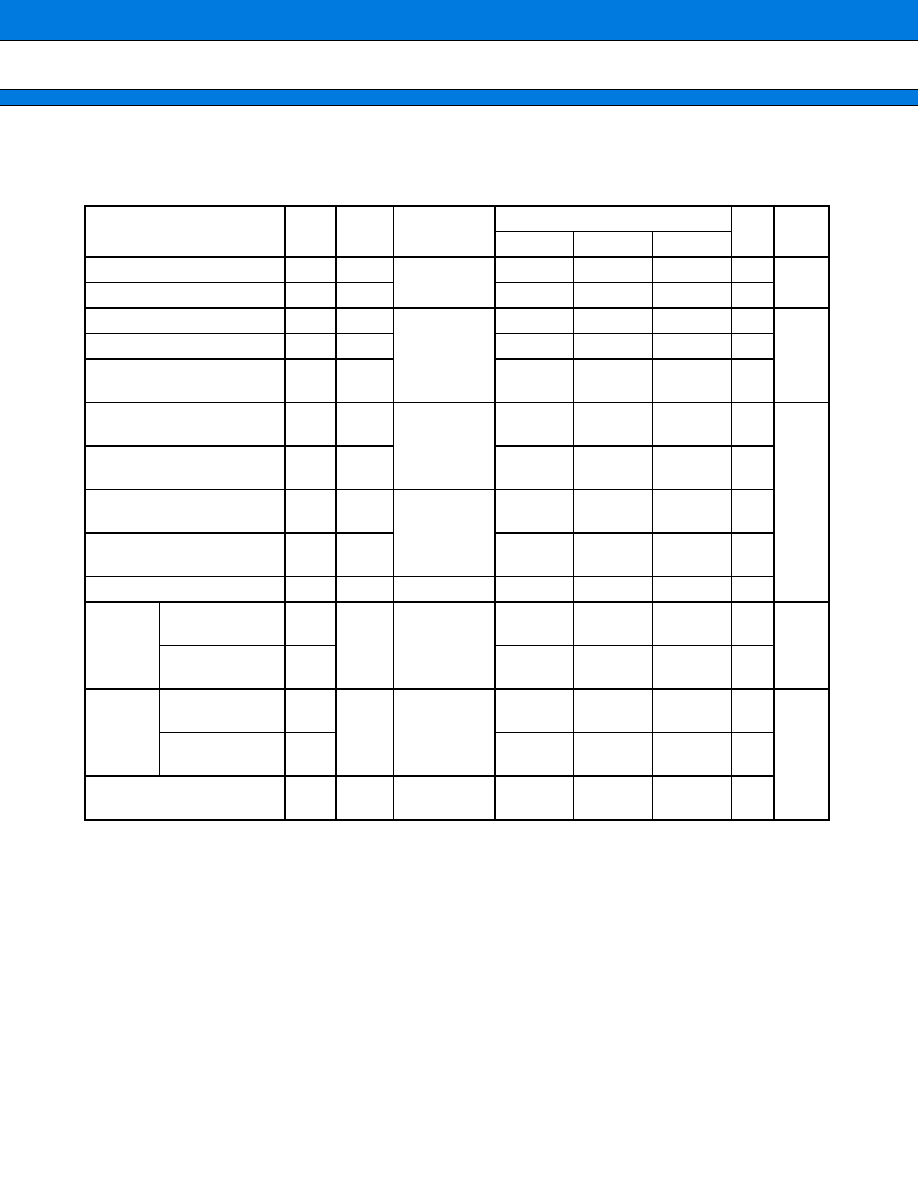

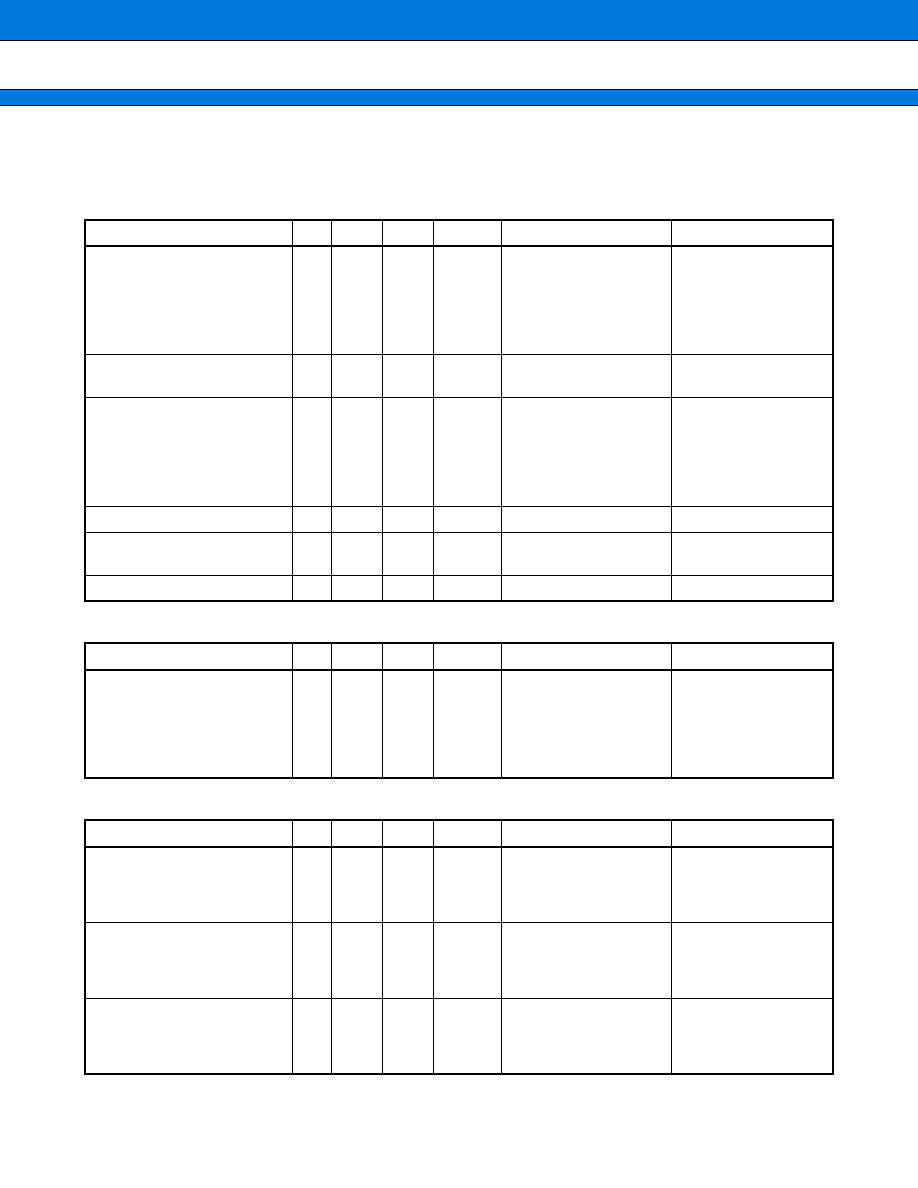

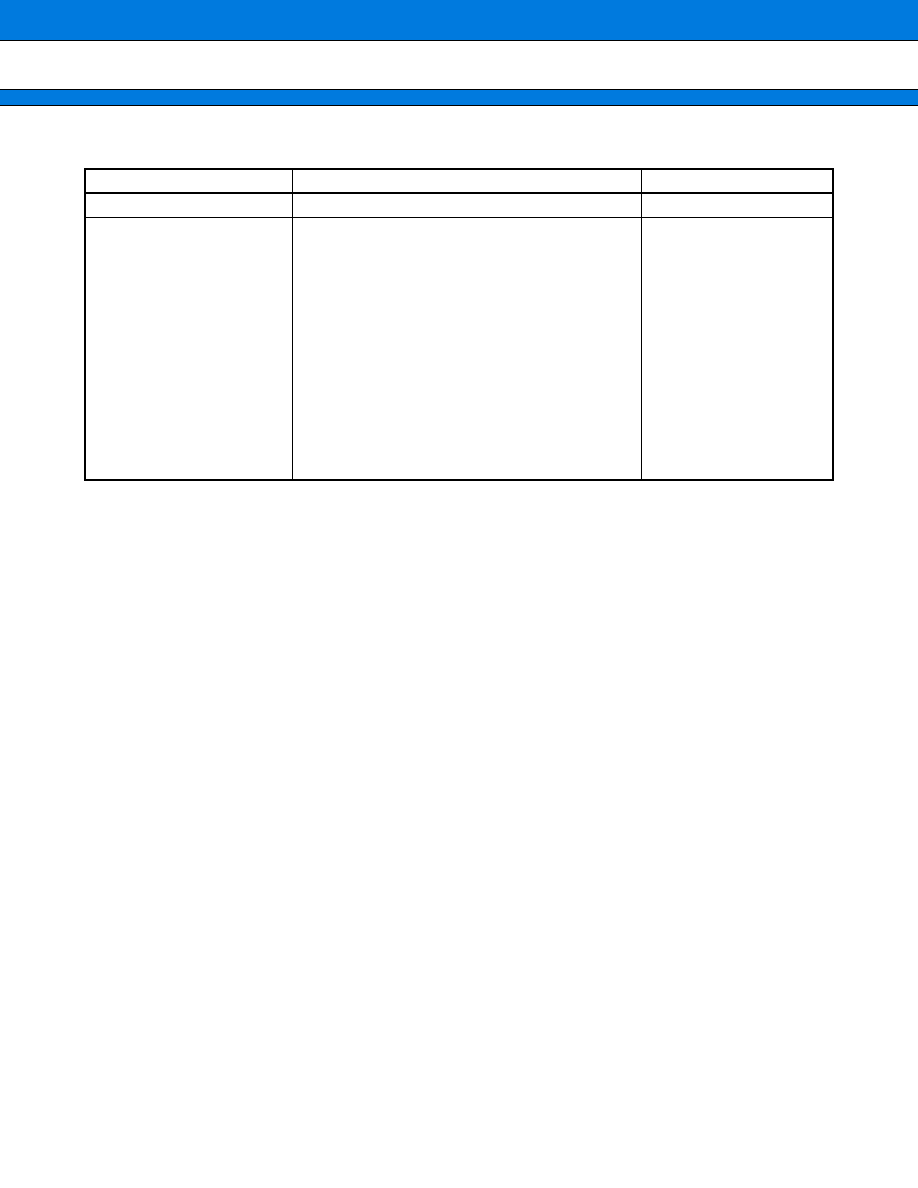

(Continued)

Type

Circuit

Remarks

G

∑ CMOS level input pin

CMOS level input

(without standby control)

I

OL

=

4 mA

H

∑ CMOS hysteresis input/output pin

with pull- up control

CMOS level output

CMOS hysteresis input

(without standby control)

Pull-up resistance value

=

approximately 50 k

(Typ.)

I

OL

=

4 mA

K

∑ Clock oscillation circuit (32 kHz)

Oscillation feedback resistance

=

approximately 4.5 M

/3 V

3 V CMOS level input

N

∑ Analog/CMOS level input/output pin

CMOS level output

CMOS level input

(with standby control)

Analog input

(Analog input is valid when bit dealt

by AIC is "1".)

I

OL

=

4 mA

R

Digital input

R

R

Pout

Pull-up control

Hysteresis input

Nout

X1A

X0A

Xout

Standby control signal

Pout

CMOS input

Standby control

Analog input

Nout

R

MB91133/MB91F133

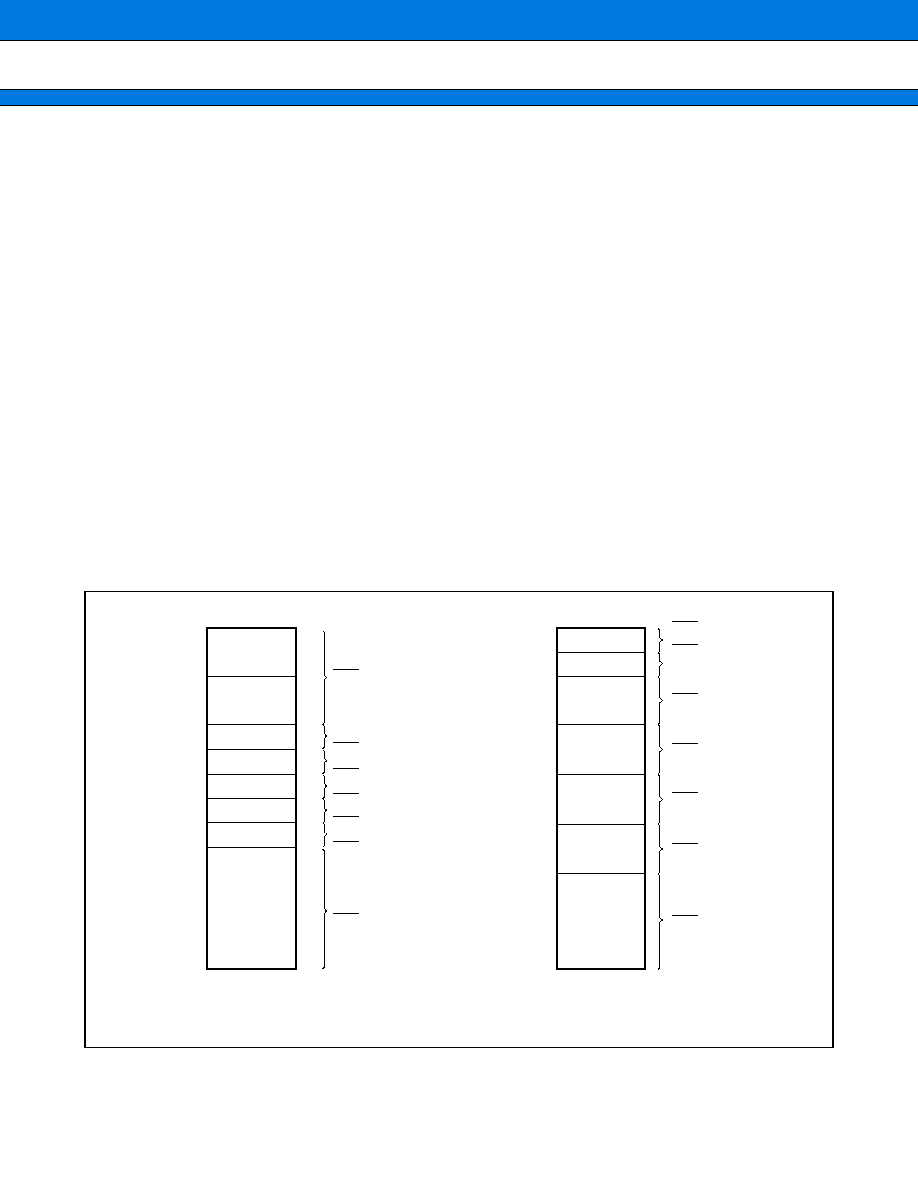

19

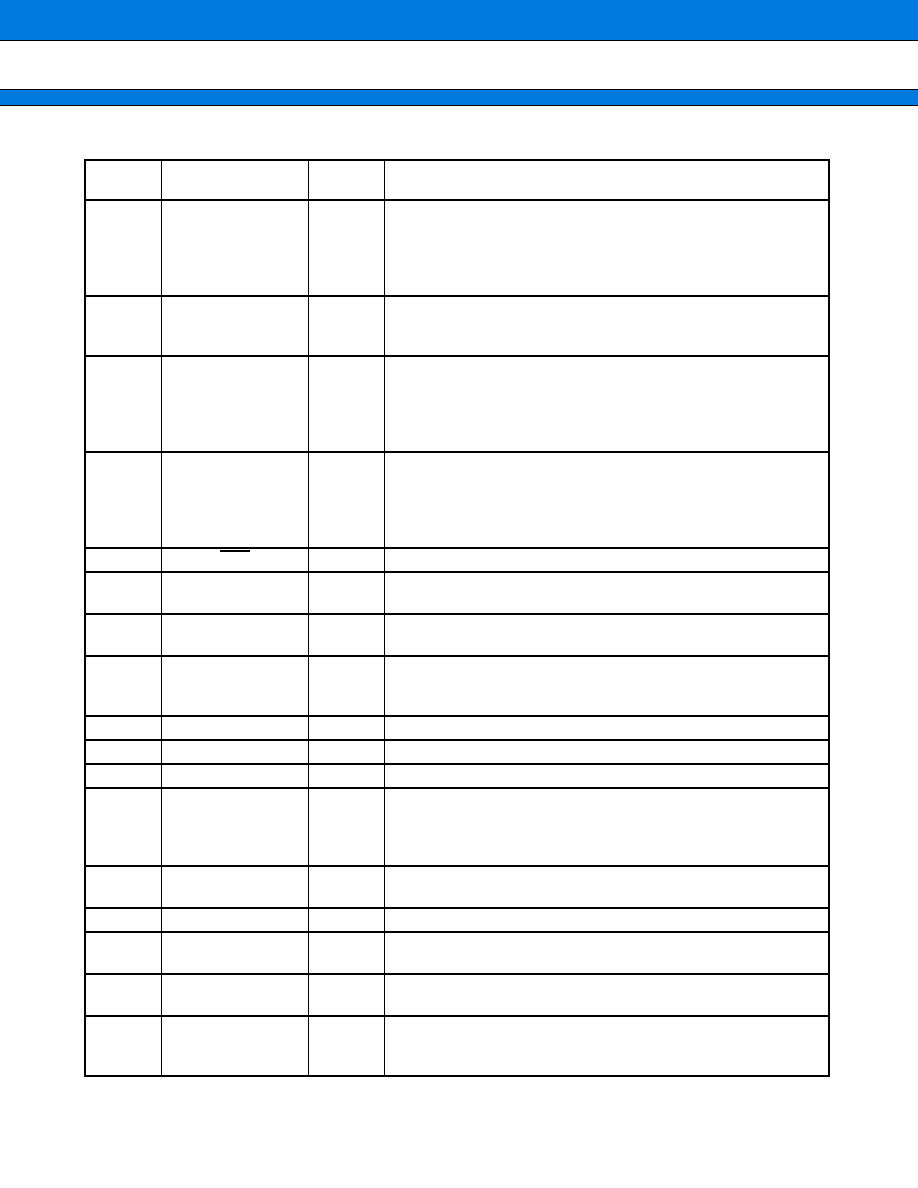

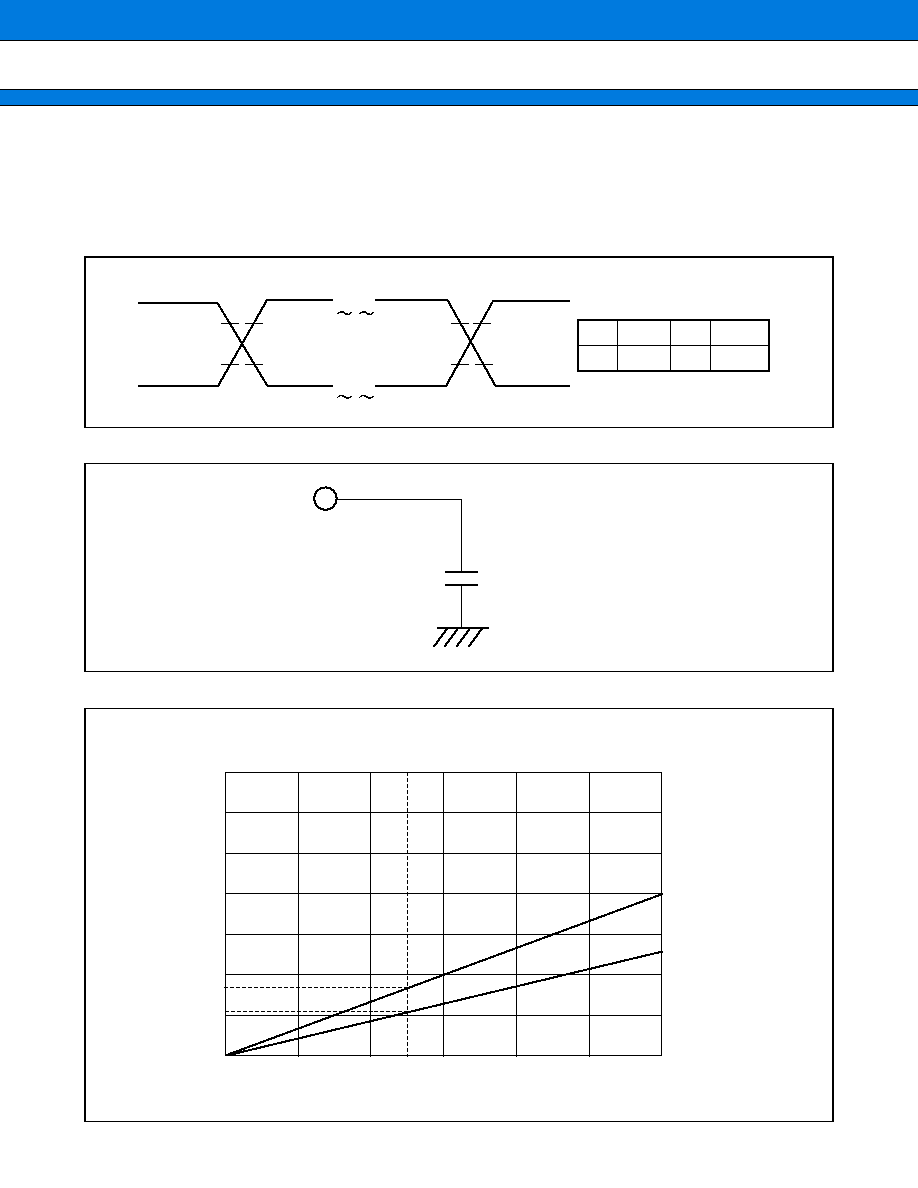

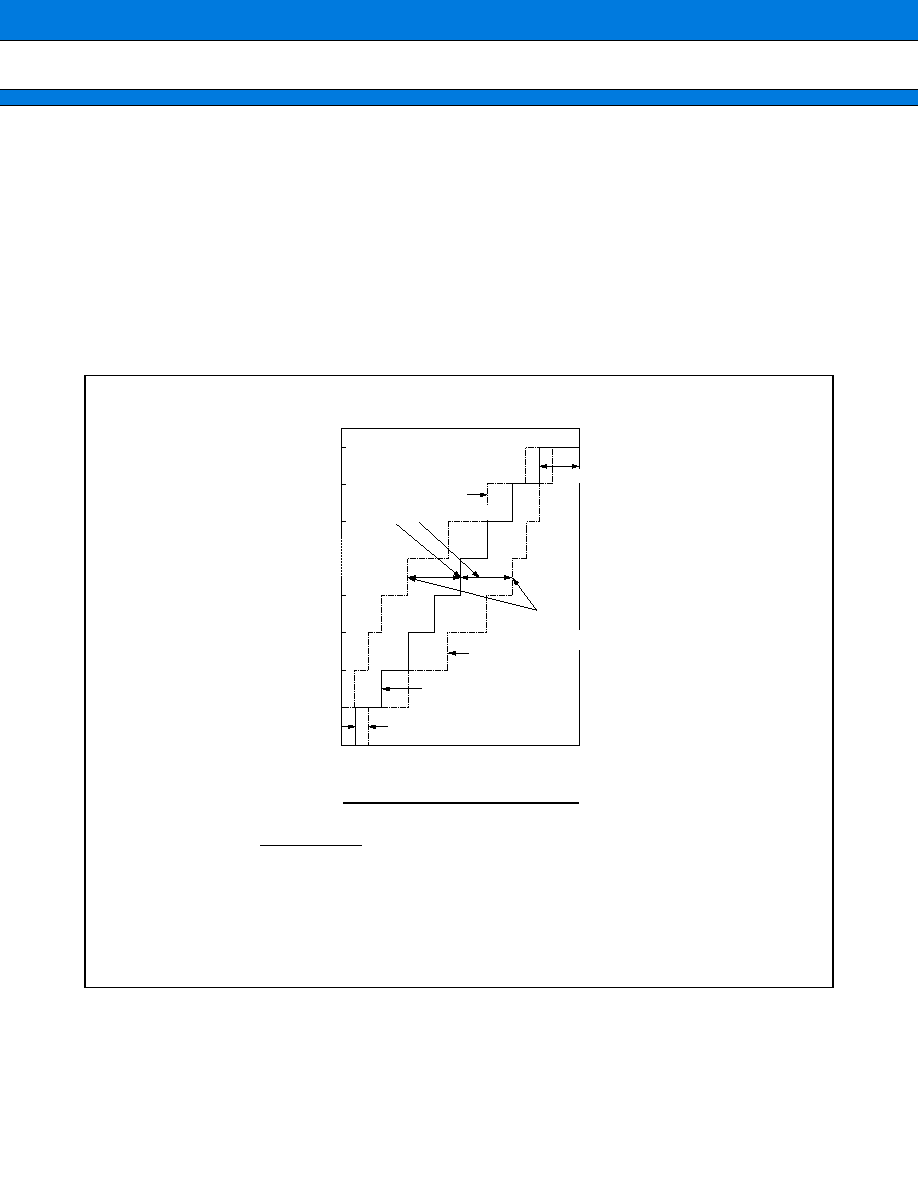

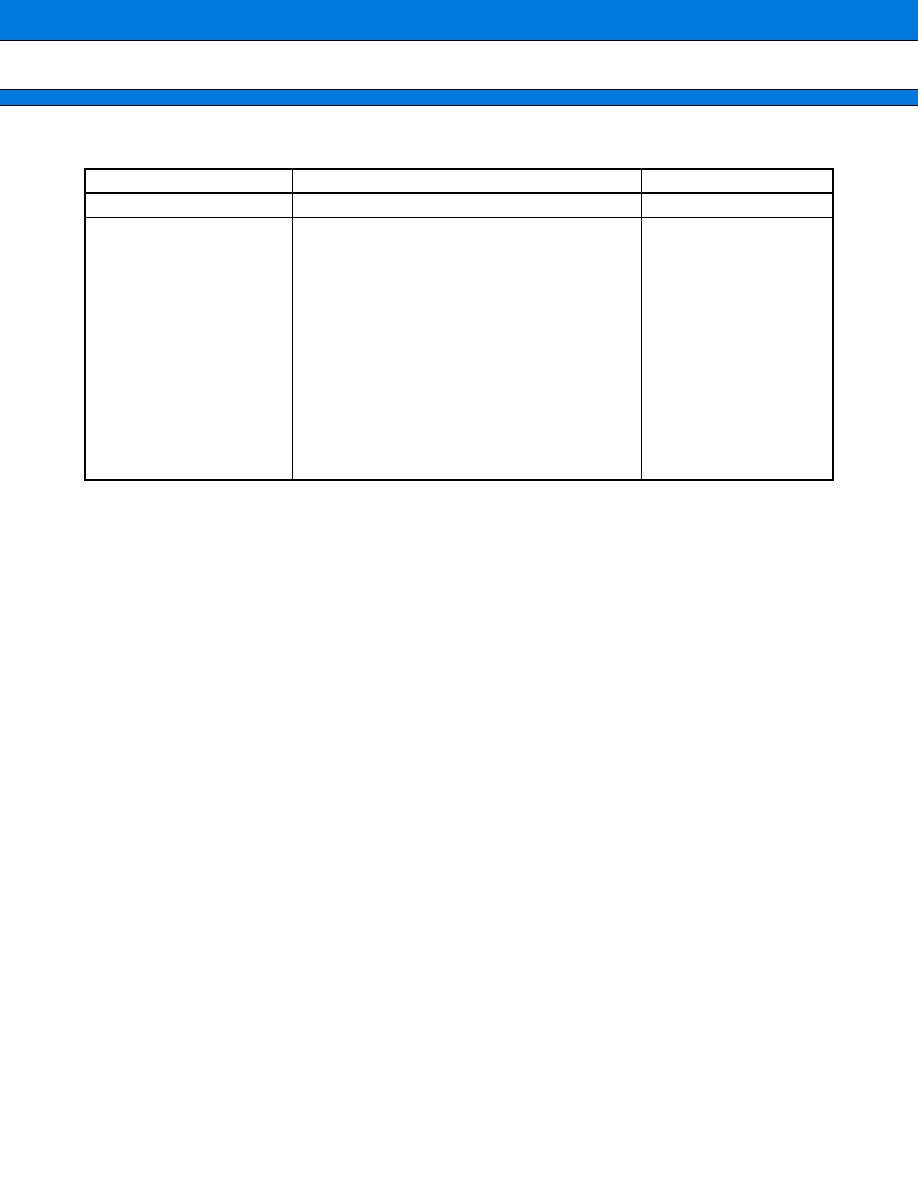

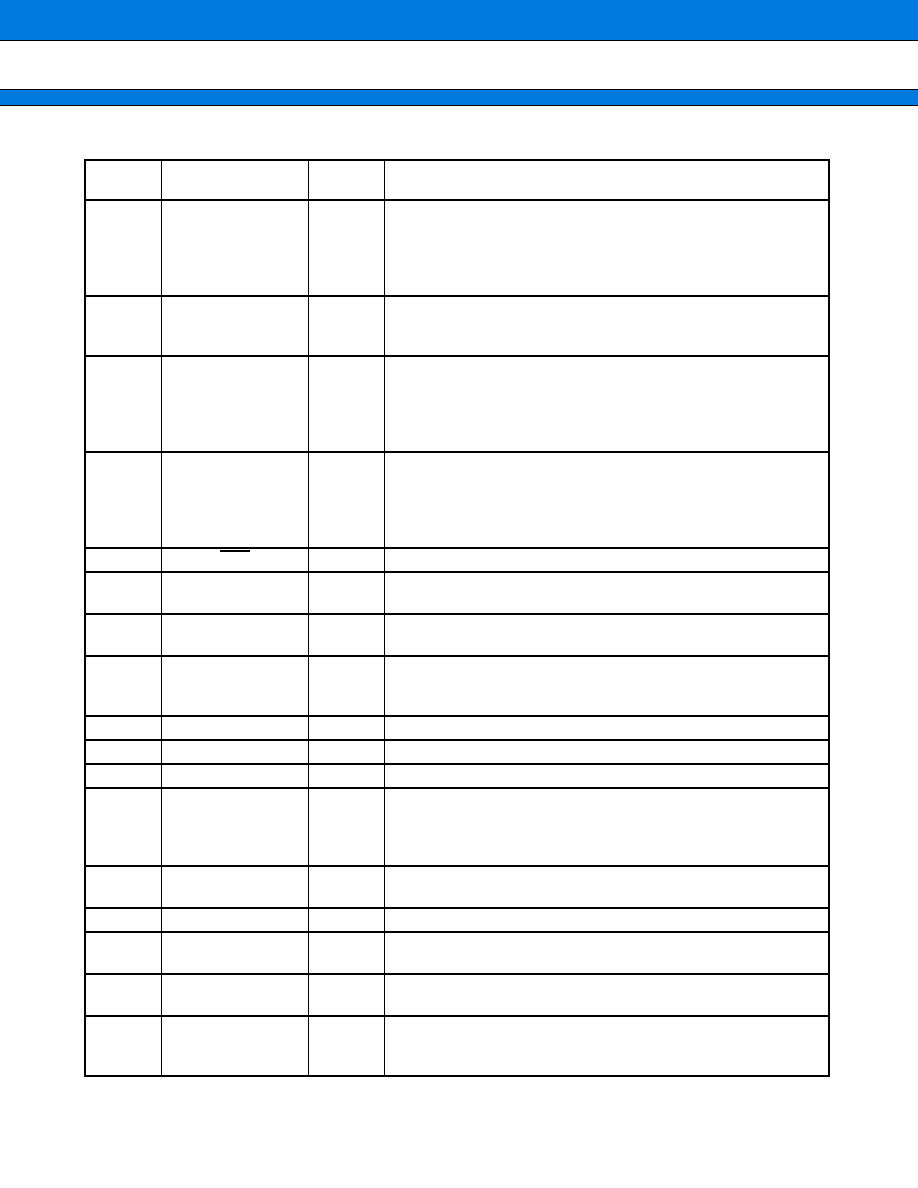

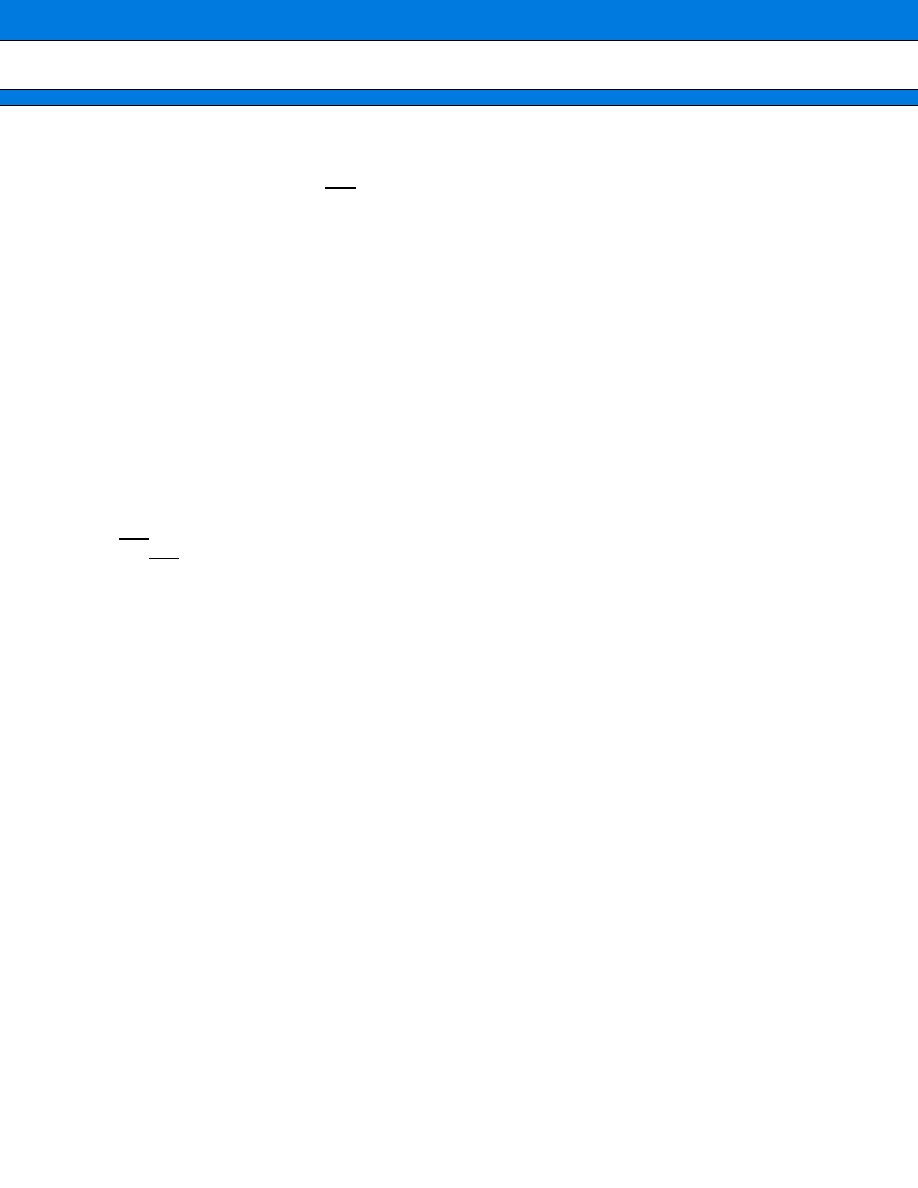

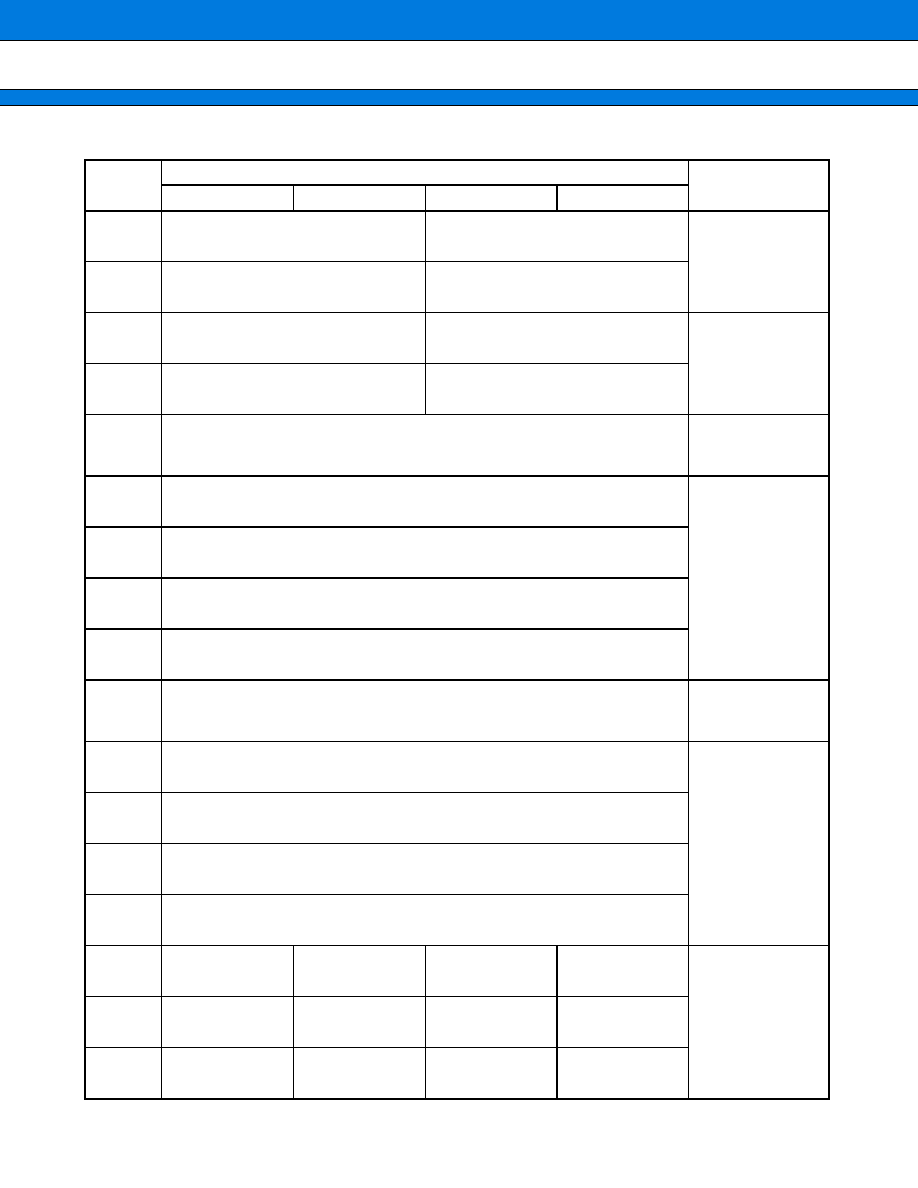

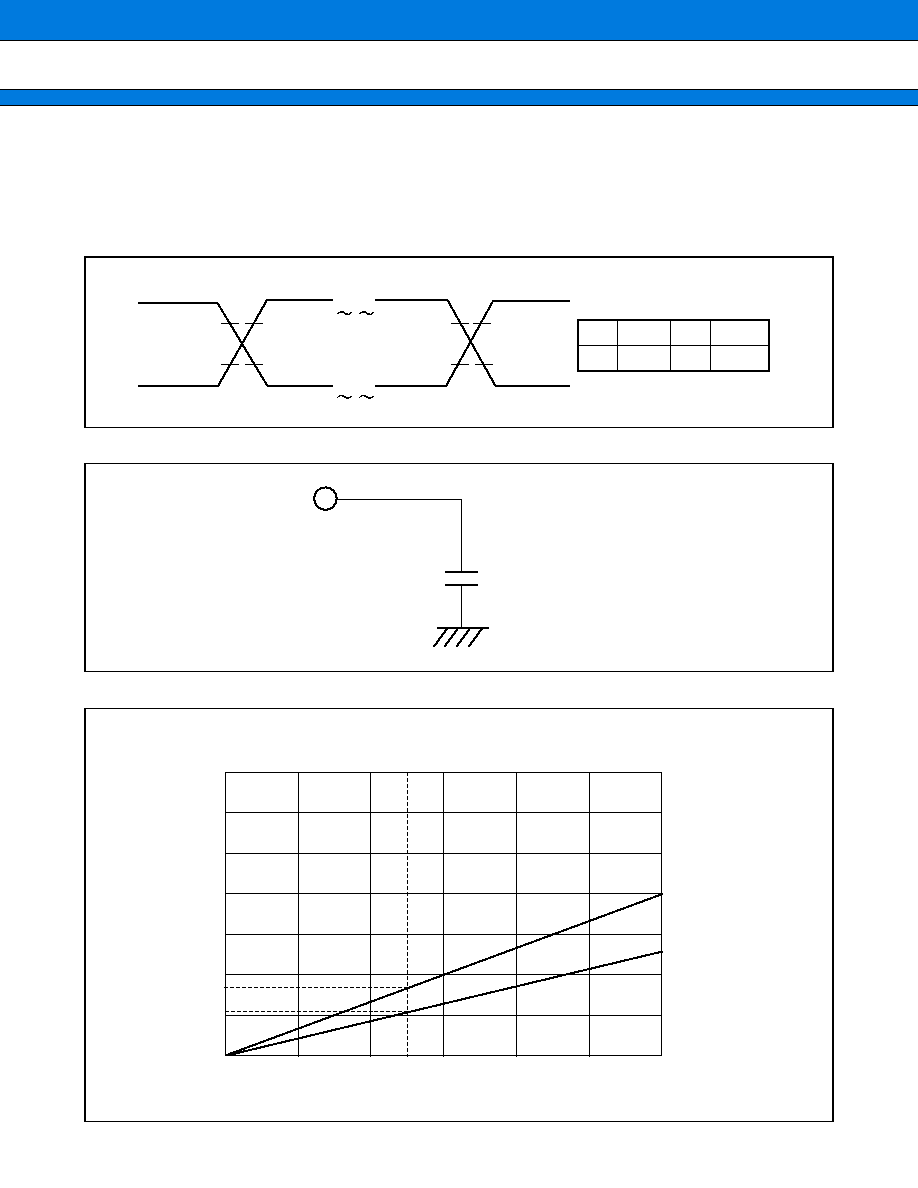

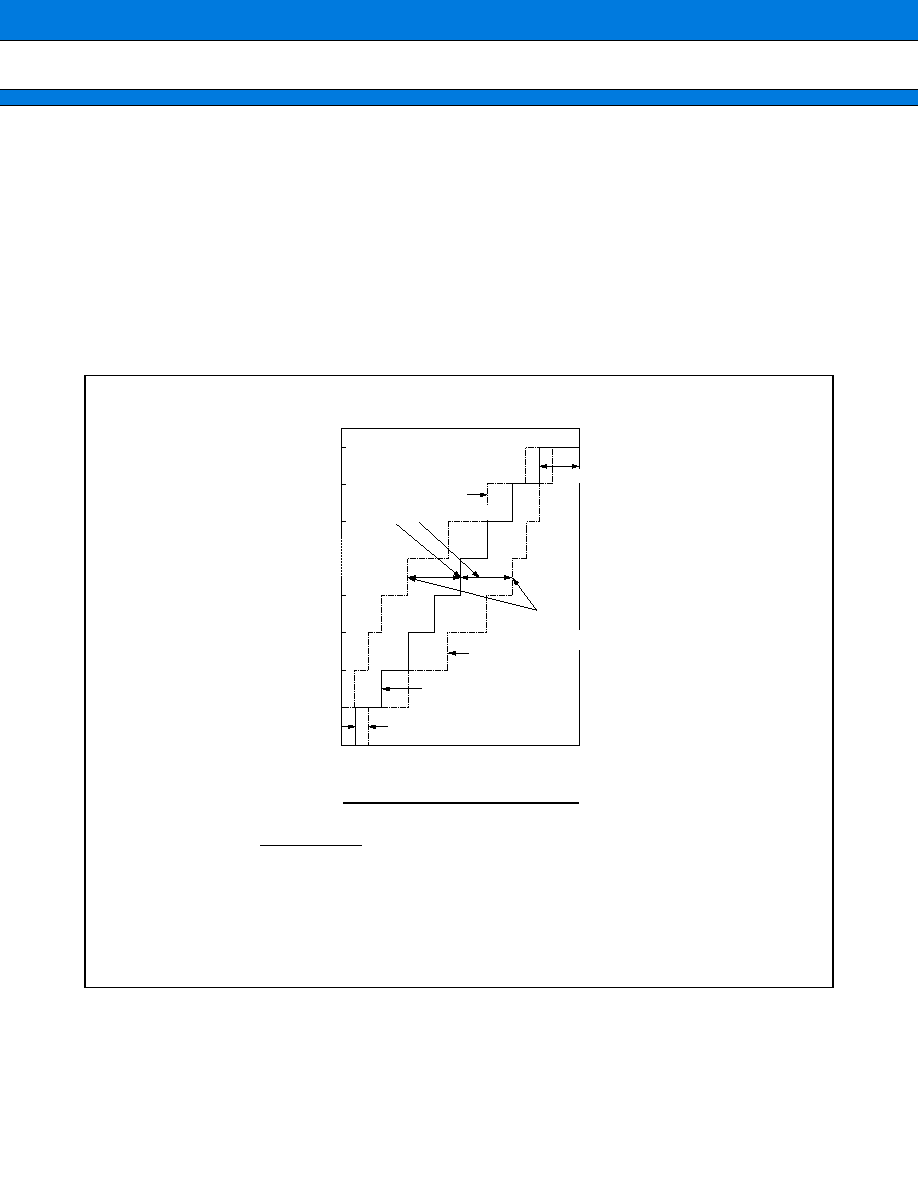

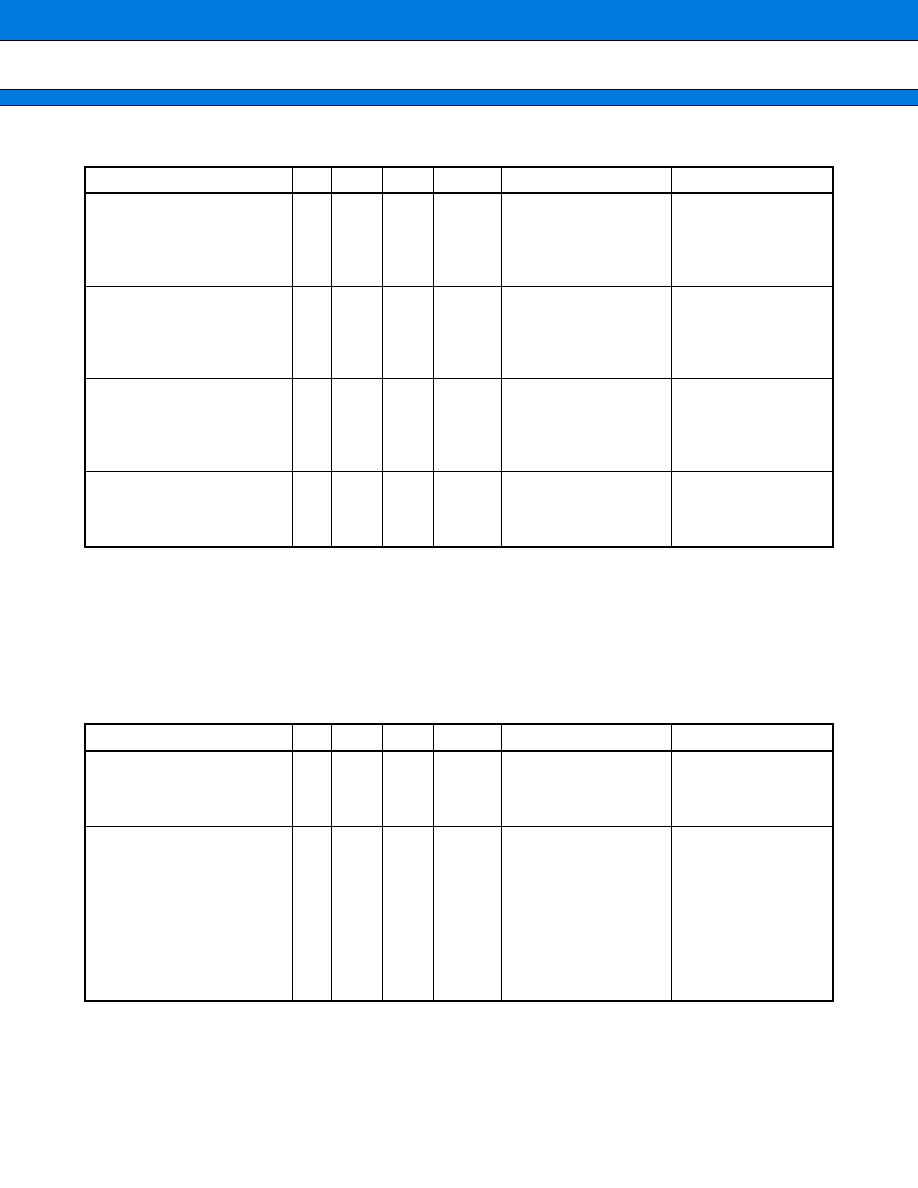

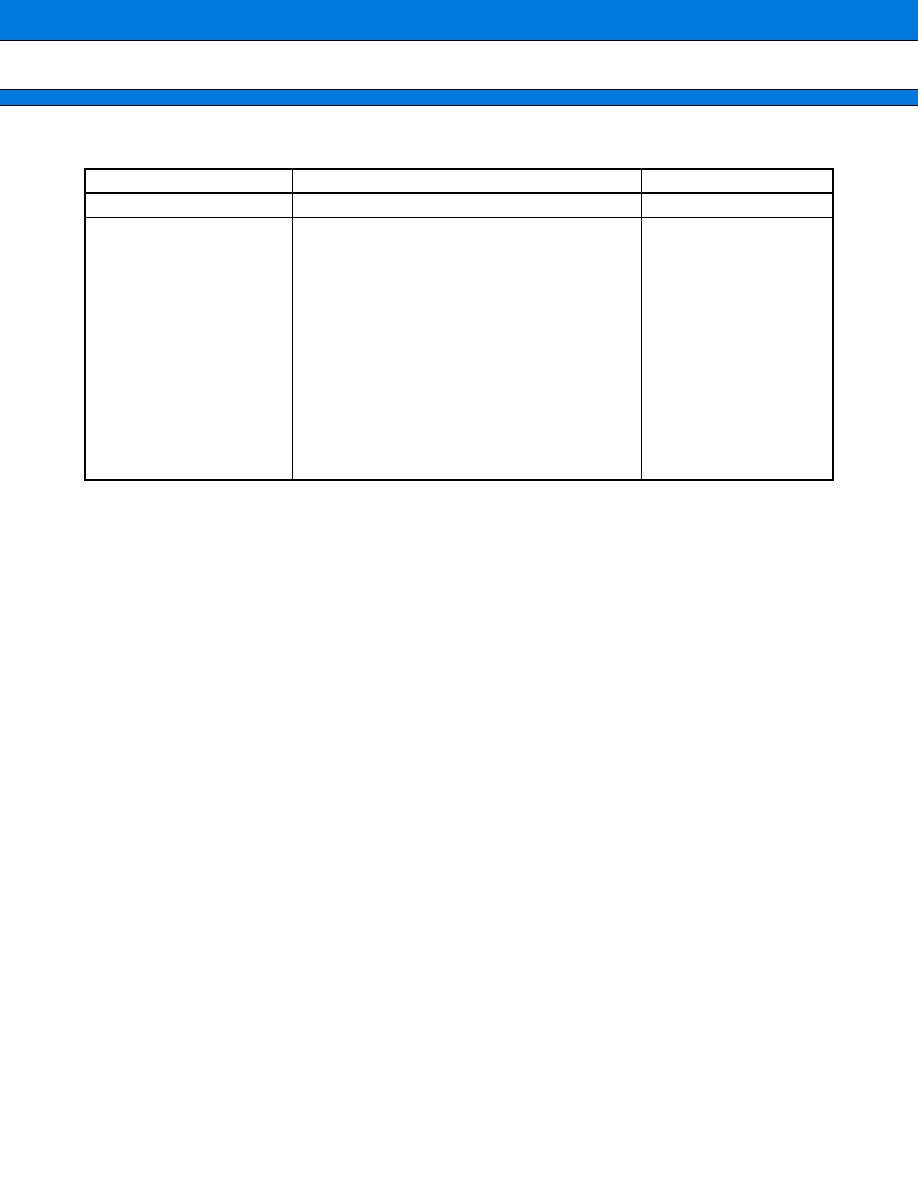

(Continued)

Type

Circuit

Remarks

O

∑ CMOS hysteresis input/output pin

with pull-up control

CMOS level output

CMOS hysteresis input

(with standby control)

Pull-up resistance value

=

approximately 50 k

(Typ.)

I

OL

=

4 mA

P

∑ CMOS hysteresis input/output pin

with pull-up control

CMOS level output

(with open-drain control)

CMOS hysteresis input

(with standby control)

Pull-up resistance value

=

approximately 50 k

(Typ)

I

OL

=

4 mA

Pout

Pull-up control

Hysteresis input

Standby control

Nout

R

R

Nout

Pull-up control

Open-drain control

Hysteresis input

Standby control

R

R

MB91133/MB91F133

20

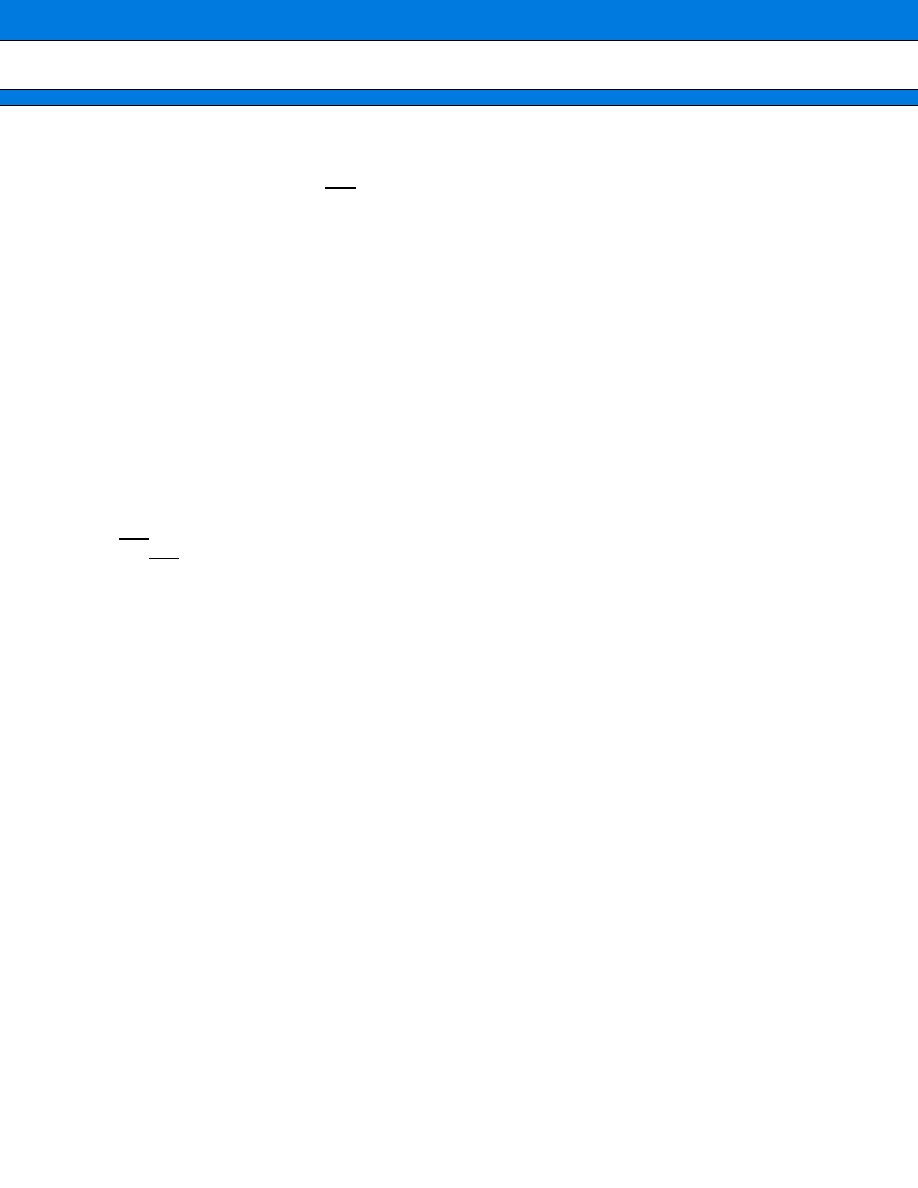

s

HANDLING DEVICES

1.

Points to Note on Handling Devices

(1) Latch-up prevention

Latch-up may occur by CMOS IC if a voltage in excess of V

CC

5 or lower than V

SS

is applied to the input/output

pins, or if the voltage exceeds the rating between V

CC

5 and V

SS

. If latch-up occurs, the electrical current increases

significantly and may destroy certain components due to excessive heat, so great care must be taken to ensure

that the maximum rating is not exceeded during use.

(2) Handling Pins

∑ Handling unused pins

Input pins that are not used should be pulled up or down as they may cause erroneous operations if left open.

∑ Handling N.C. pins

N.C. pins must be opened for use.

∑ Handling output pins

Excessive electric current may flow if the output pin is shorted by the power source or other output pins, or

connected to large loads. If such status is prolonged, the device is liable to be damaged, so great care must

be taken to ensure that the usage volume does not exceed the maximum rating.

∑ Mode pins (MD0 to MD2)

Those pins must be directly connected to V

CC

5 or V

SS

for use.

Pattern lengths between V

CC

5 or V

SS

and each mode pin on the printed-circuit board should be arranged to

be as short as possible to prevent the test mode from being erroneously turned on due to noise, and they

should be connected with low impedance.

∑ Power pins

When there are a number of V

CC

5/V

CC

3/V

SS

, those whose electrical potential must be the same within the

device are connected to prevent erroneous operation such as latch-up for device design purposes, but those

must be externally connected to a power source and earthed to follow the general output current standard and

prevent erroneous operation of strobe signals due to increased ground level and reduction in unnecessary

radiation.

Care must also be taken to ensure that they are connected to the V

CC

5/V

SS

or V

CC

3/V

SS

of this device at the

lowest possible impedance from the source of the electrical current supply.

Furthermore, it is recommended that a ceramic capacitor of around 0.1

µ

F be used to connect the V

CC

5 and

V

SS

, or V

CC

3 and V

SS

near the device as a bypass capacitor.

∑ Crystal oscillation circuits

Noise near the X0, X1, X0A or X1A pins can cause erroneous operation. The printed-circuit board must be

designed so that the X0, X1, X0A and X1A pins, crystal oscillator (or ceramic oscillator) and bypass capacitor

to the ground can be arranged as close as possible.

Also, a printed-circuit board with grounded artwork enclosing the X0, X1, X0A and X1A pins is strongly

recommended to ensure stable operation.

MB91133/MB91F133

21

(3) Points to note on usage

∑ External reset input

"L" level should be input to the RST pin, which is required for at least five machine cycles to ensure that the

internal status is reset.

∑ Oscillation pin

Oscillation pin is 3 V CMOS input level.

∑ External clock

Use with an external clock is prohibited. A crystal (or ceramic) oscillator should be used.

∑ Analog Power

The AV

CC

should always be used at the same electric potential as V

CC

5. If the V

CC

5 is larger than the AV

CC

,

electricity may flow through pins AN 0 to AN 7.

∑ Points to note for using level comparator

When the level comparator is used, a reference current (IR) flows even though it is stopped. The stop mode

must be turned on after prohibiting action of the level comparator.

2.

Points to Note on Turning On Power

∑ RST pin handling

The RST pin must be started from "L" level when the power is turned on, and when the power is adjusted to

the V

DD

level, it should be changed to the "H" level after being left on for at least 5 cycles of the internal operation

clock.

∑ Original oscillation input

The clock must be input until the waiting status for oscillation stability is reset in the event that power is turned on.

∑ Power on reset

"Power on reset" must be executed if power is turned on, but the power voltage falls below the guaranteed

operating temperature and power is turned on again.

∑ Order for turning on power

Power should be turned on in the following order.

V

CC

3

V

CC

5

AV

CC

AVRH

The opposite order should be used when turning off.

MB91133/MB91F133

22

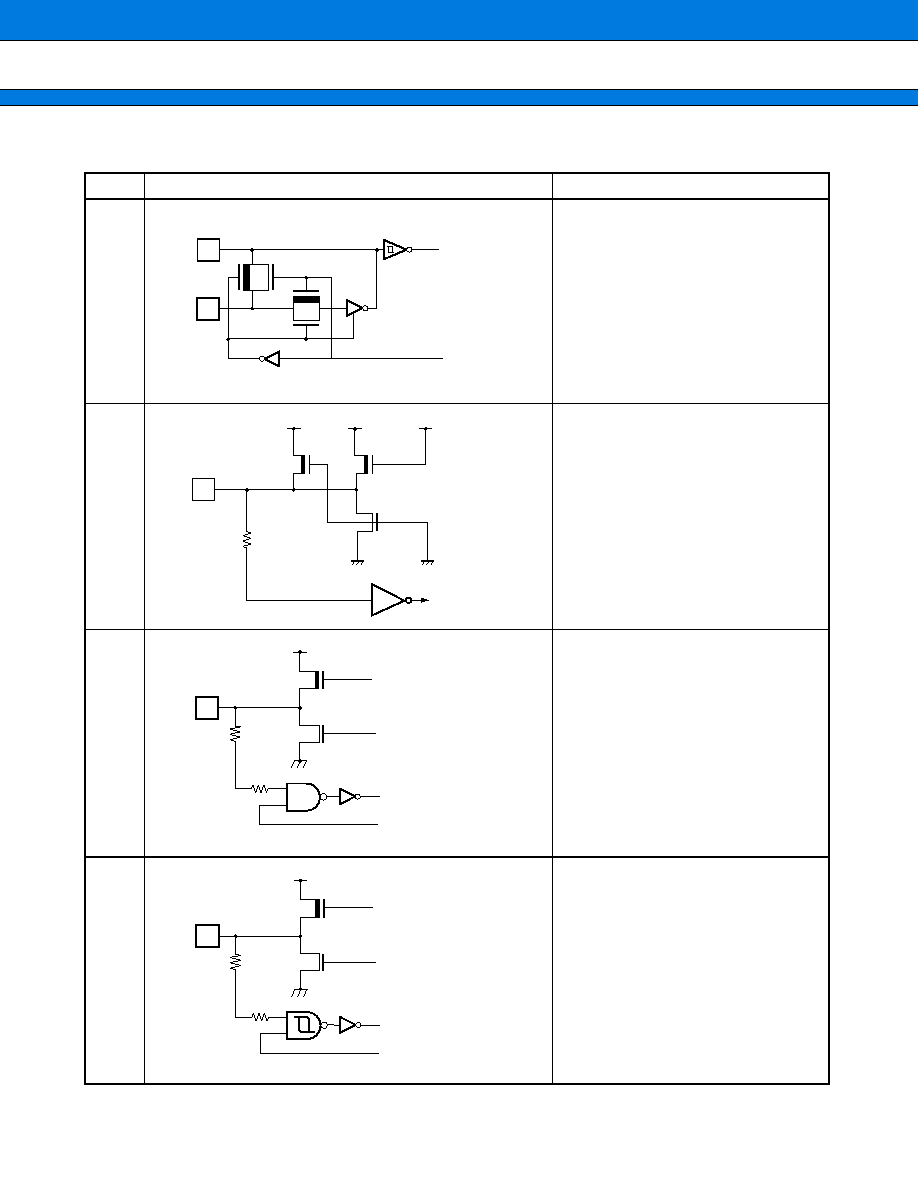

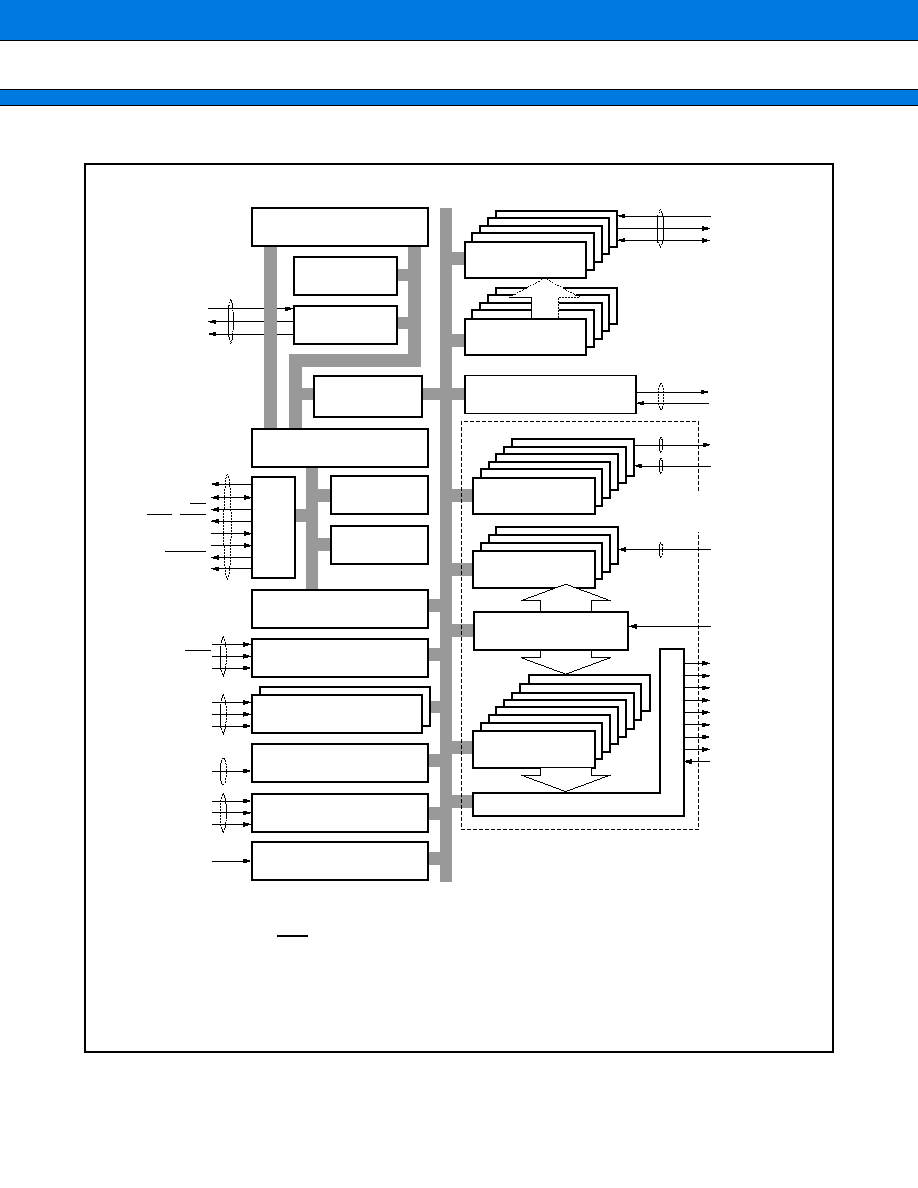

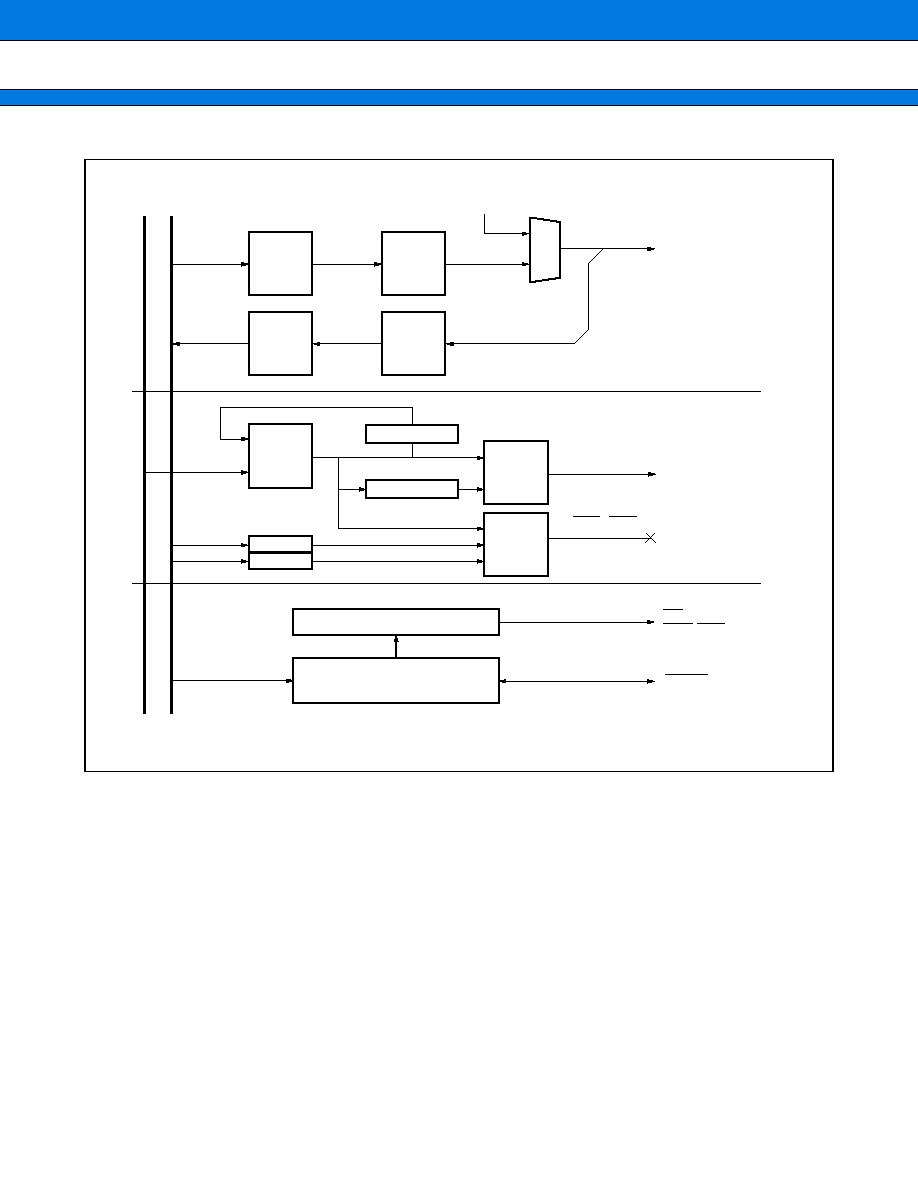

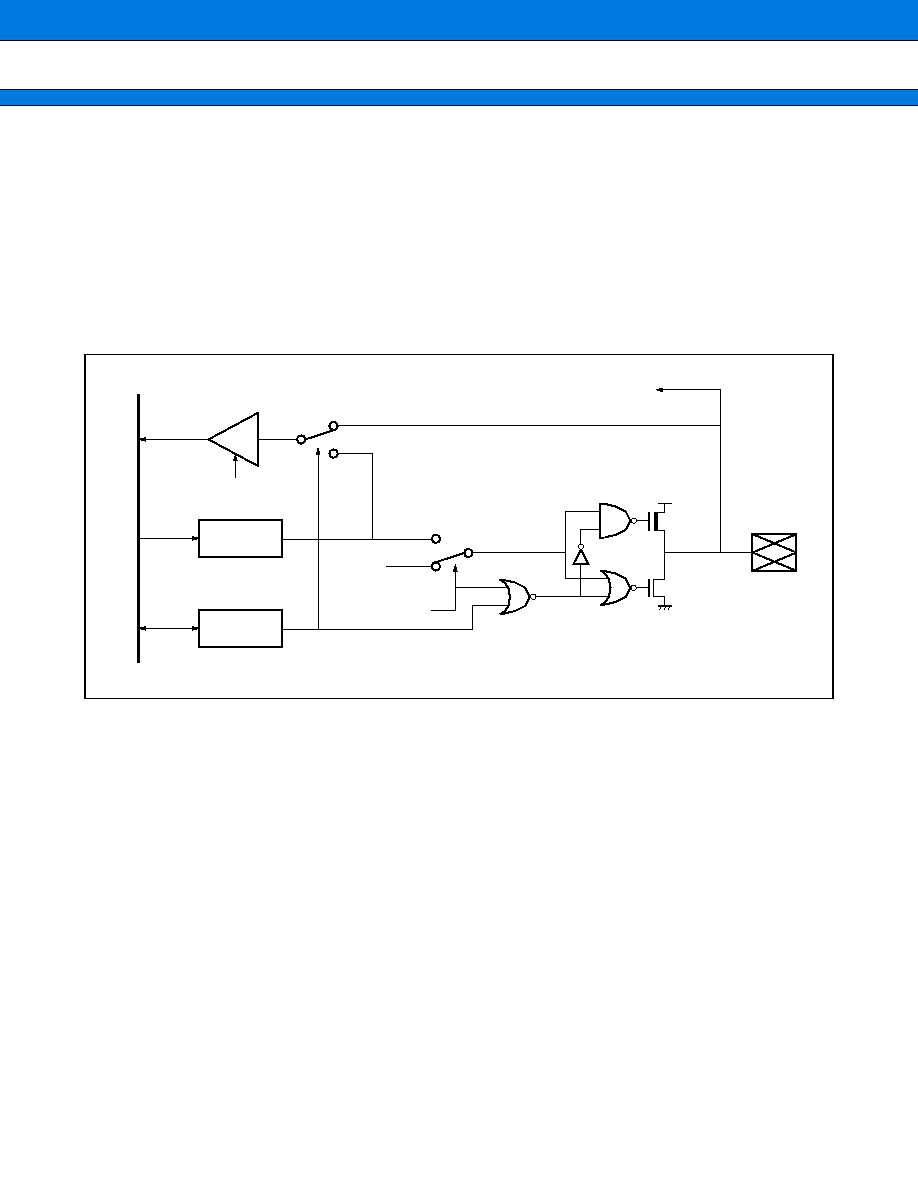

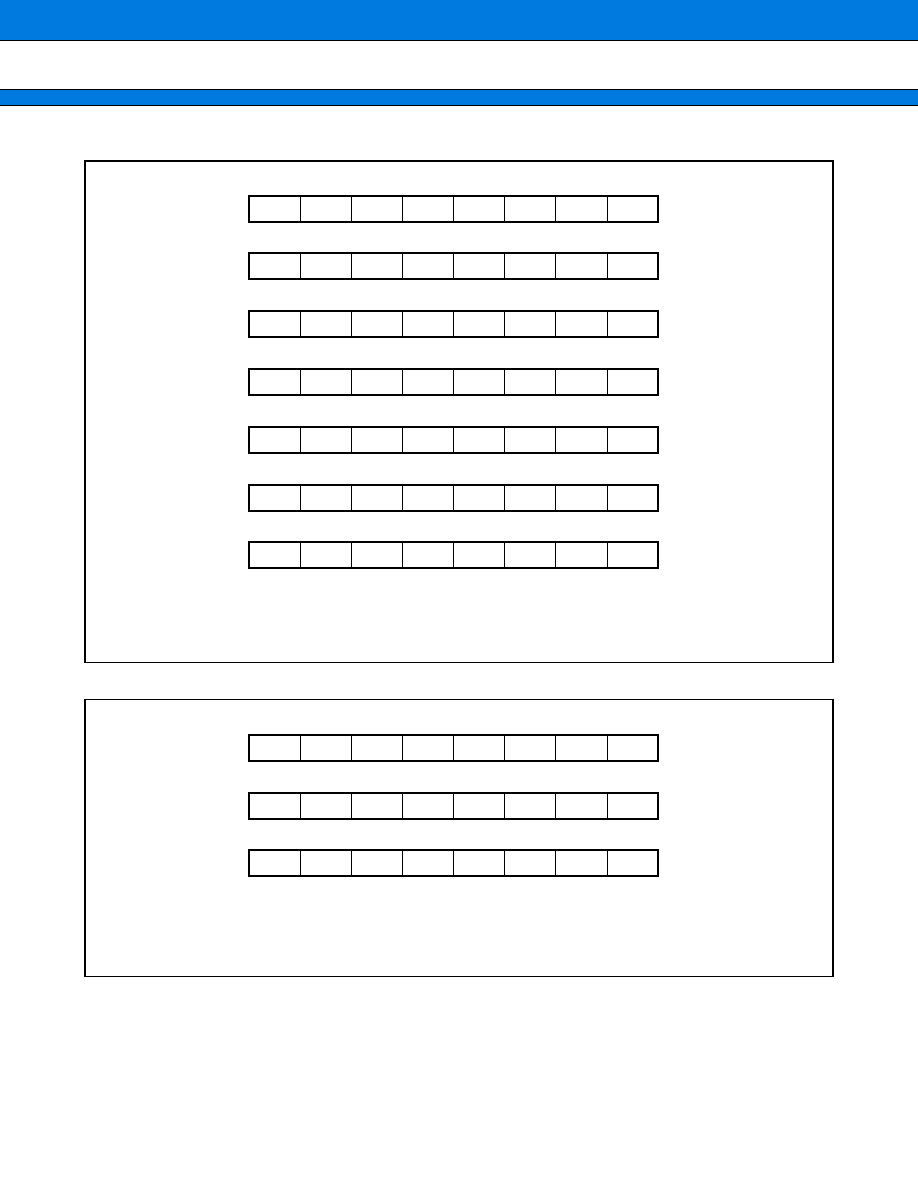

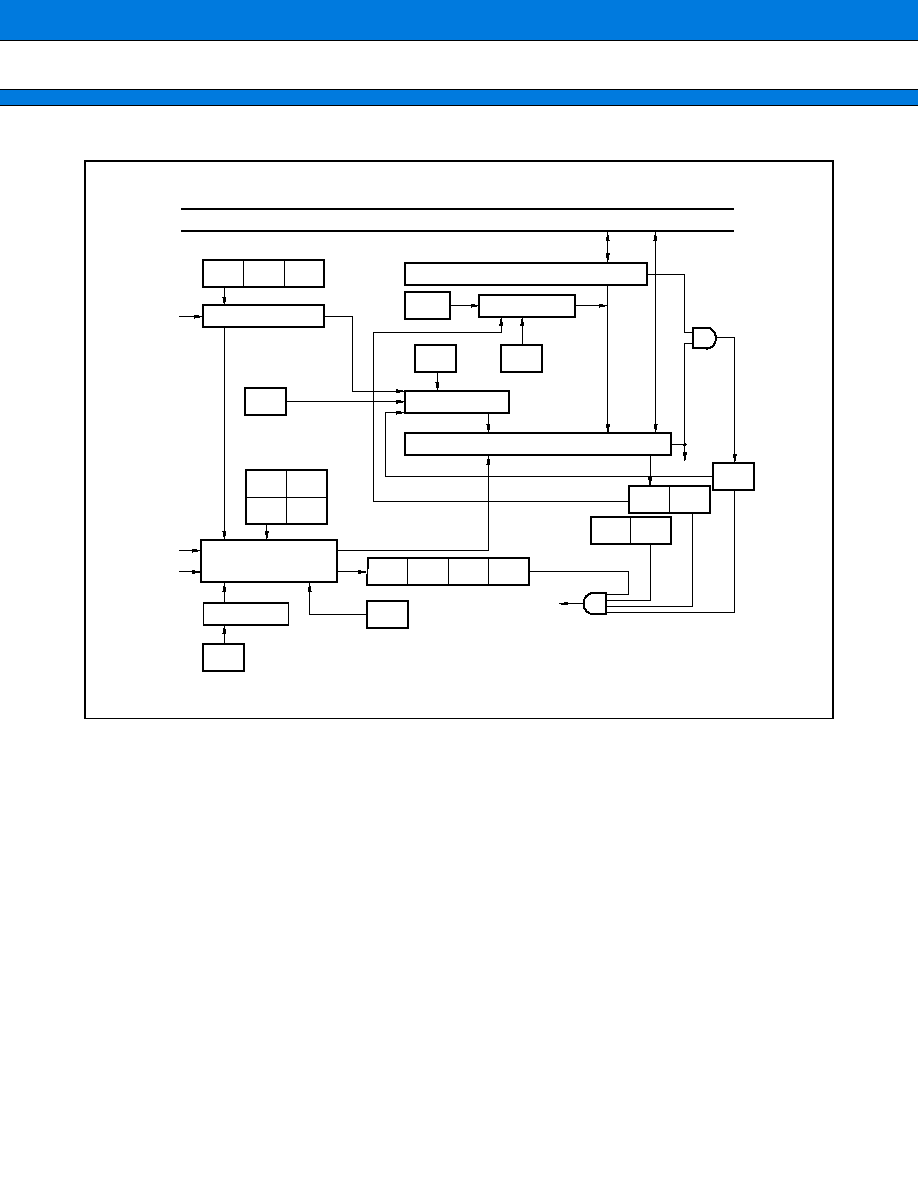

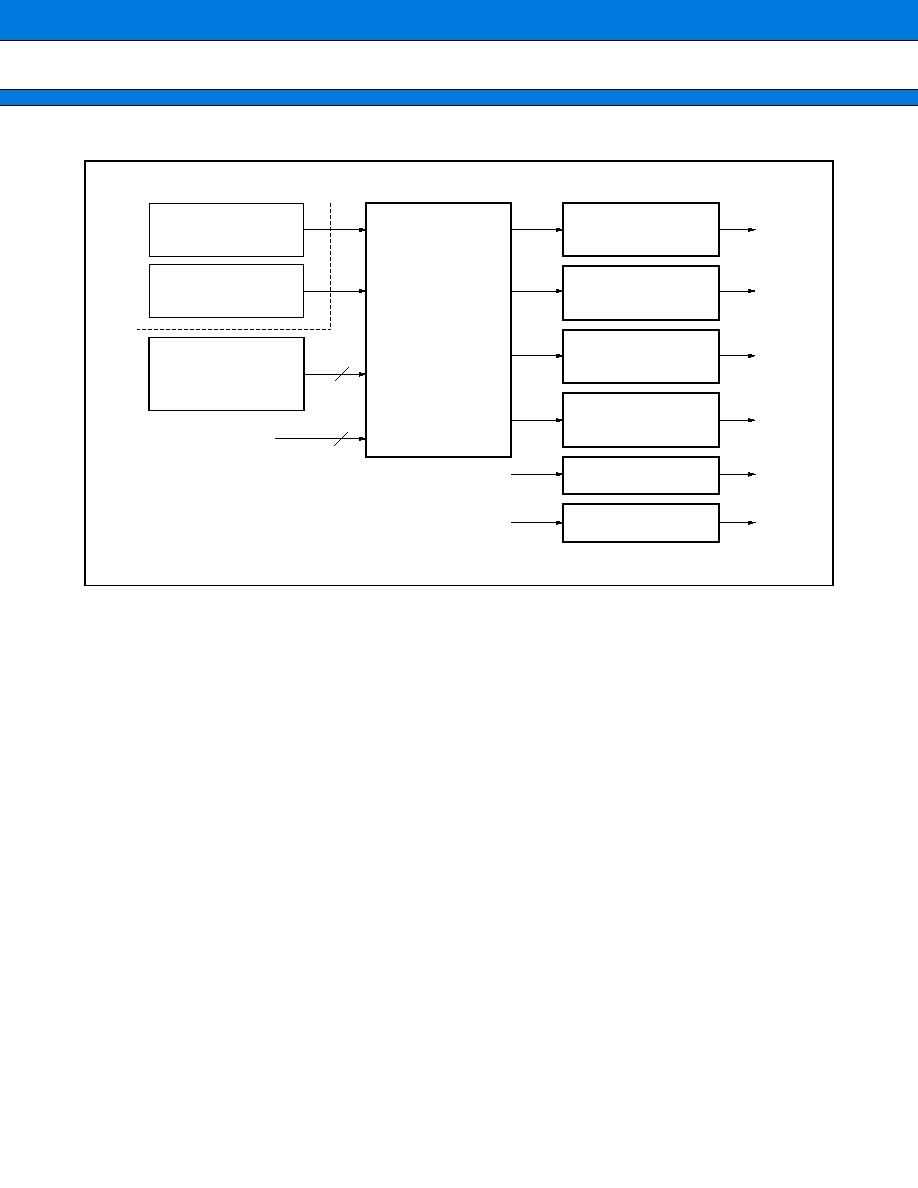

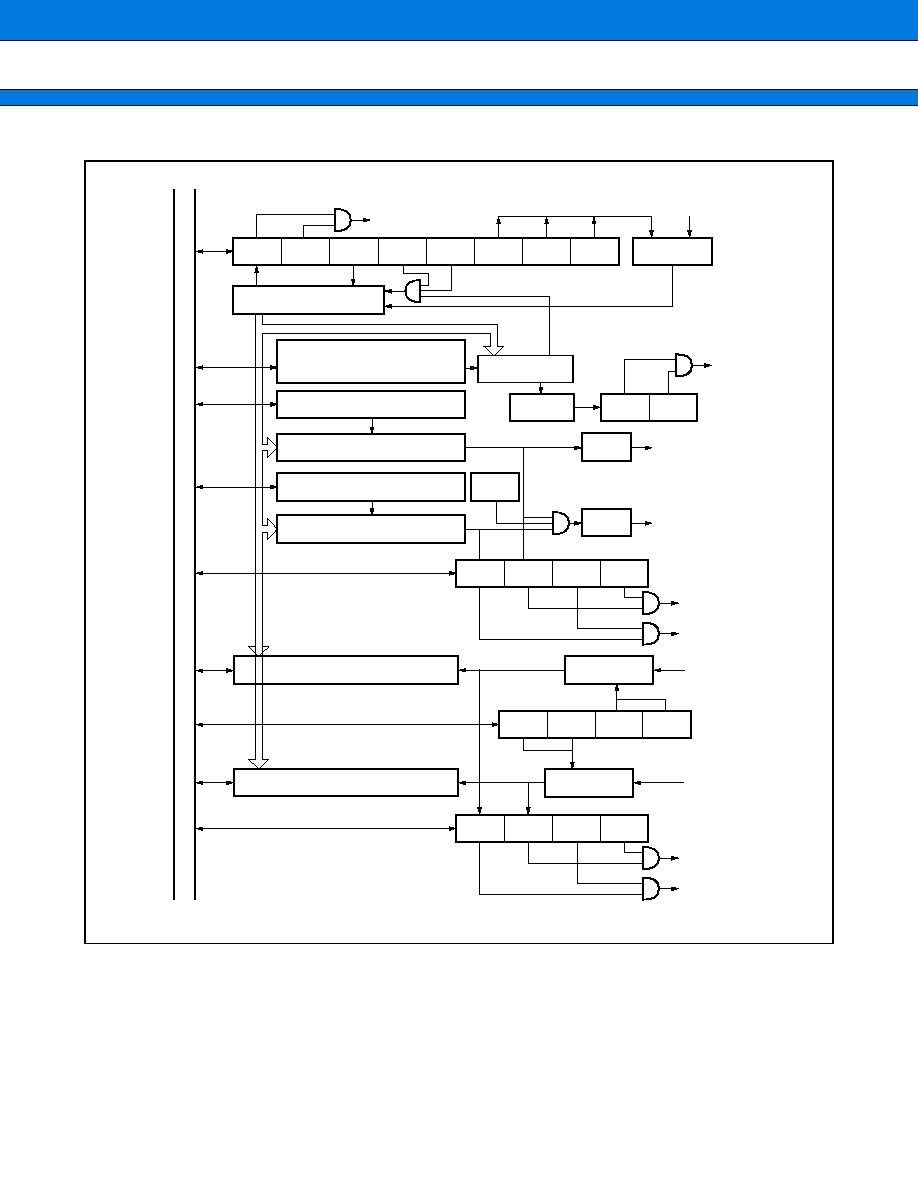

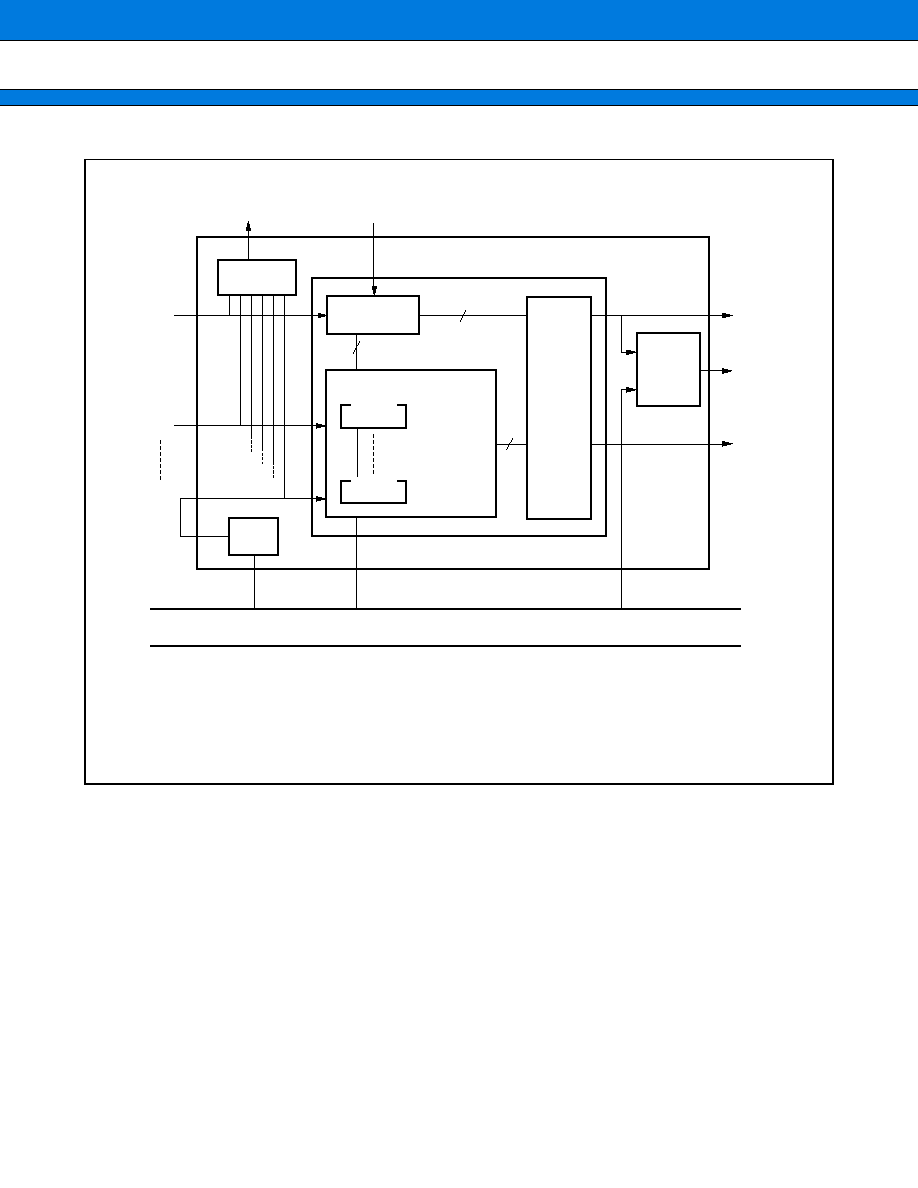

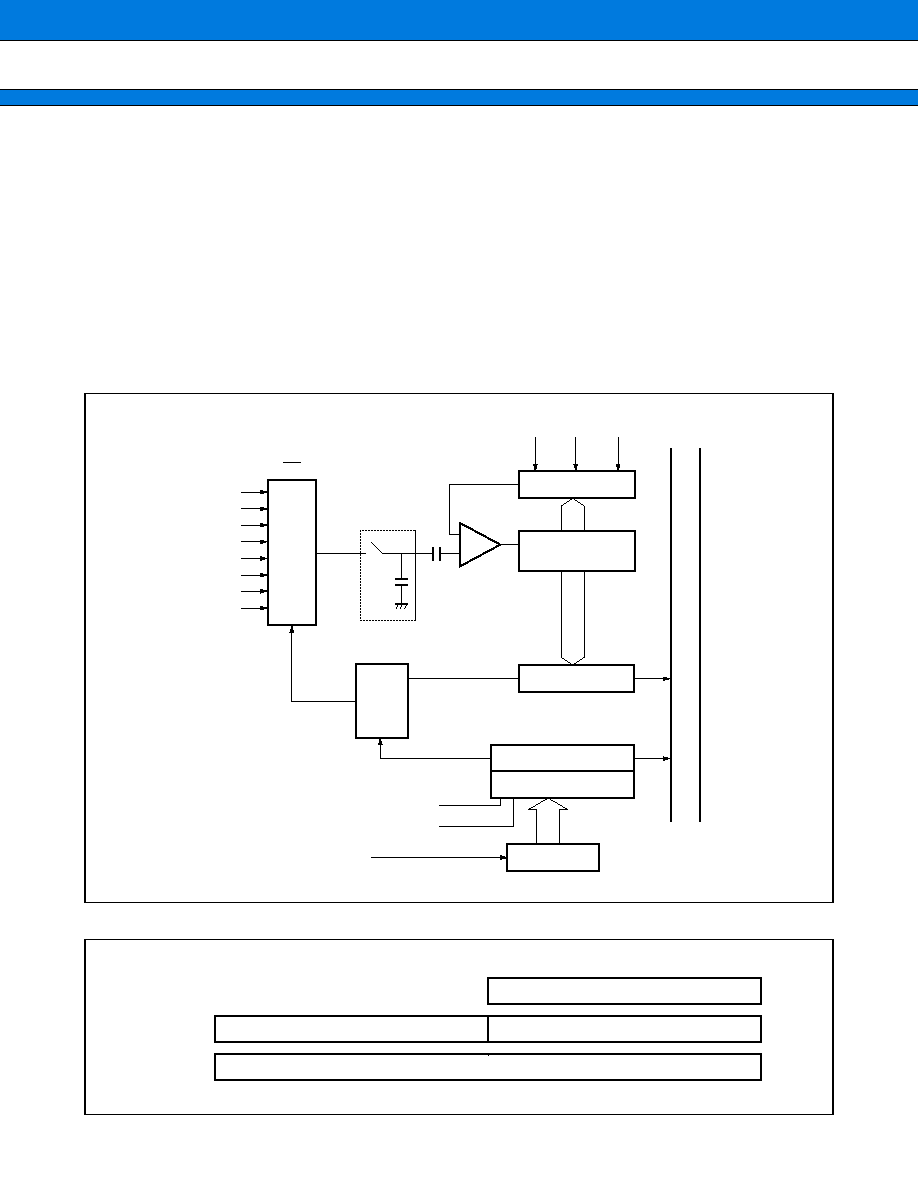

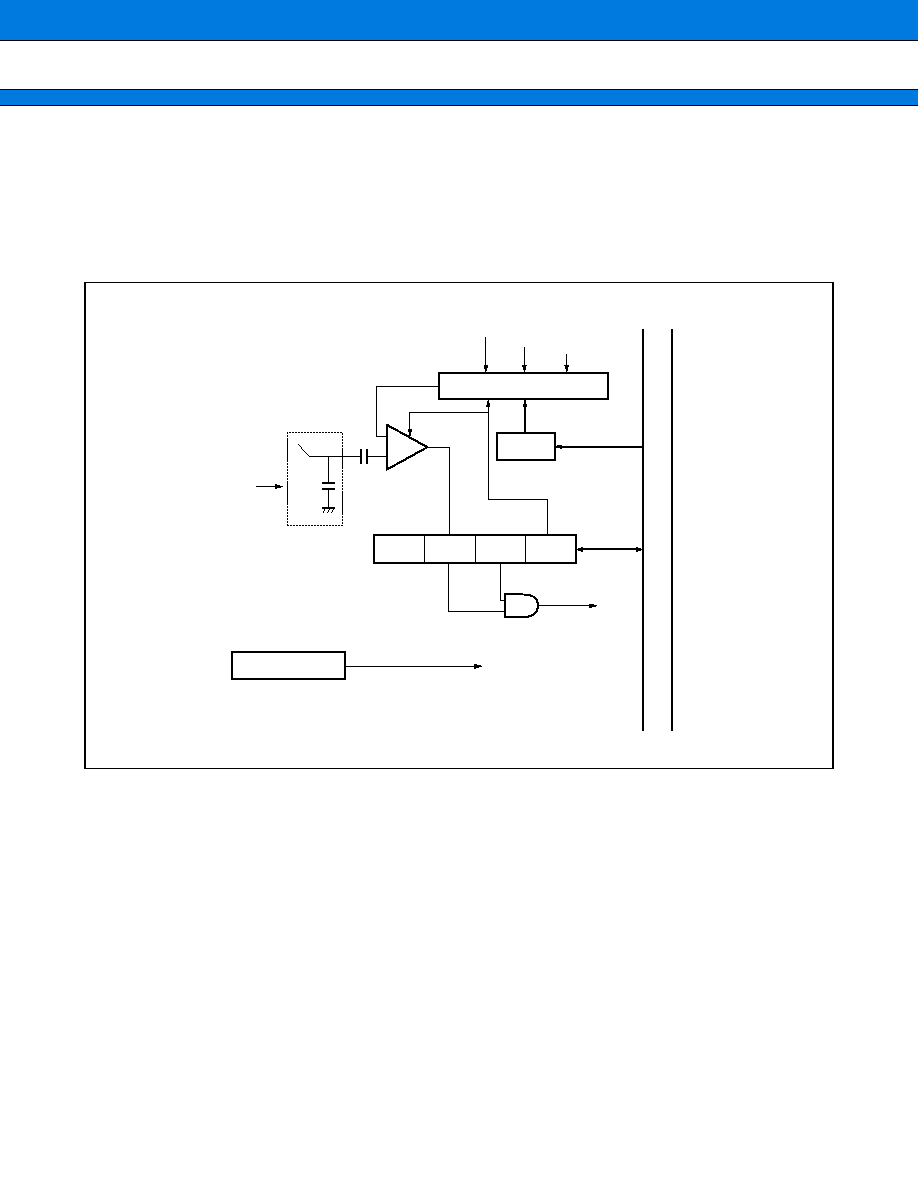

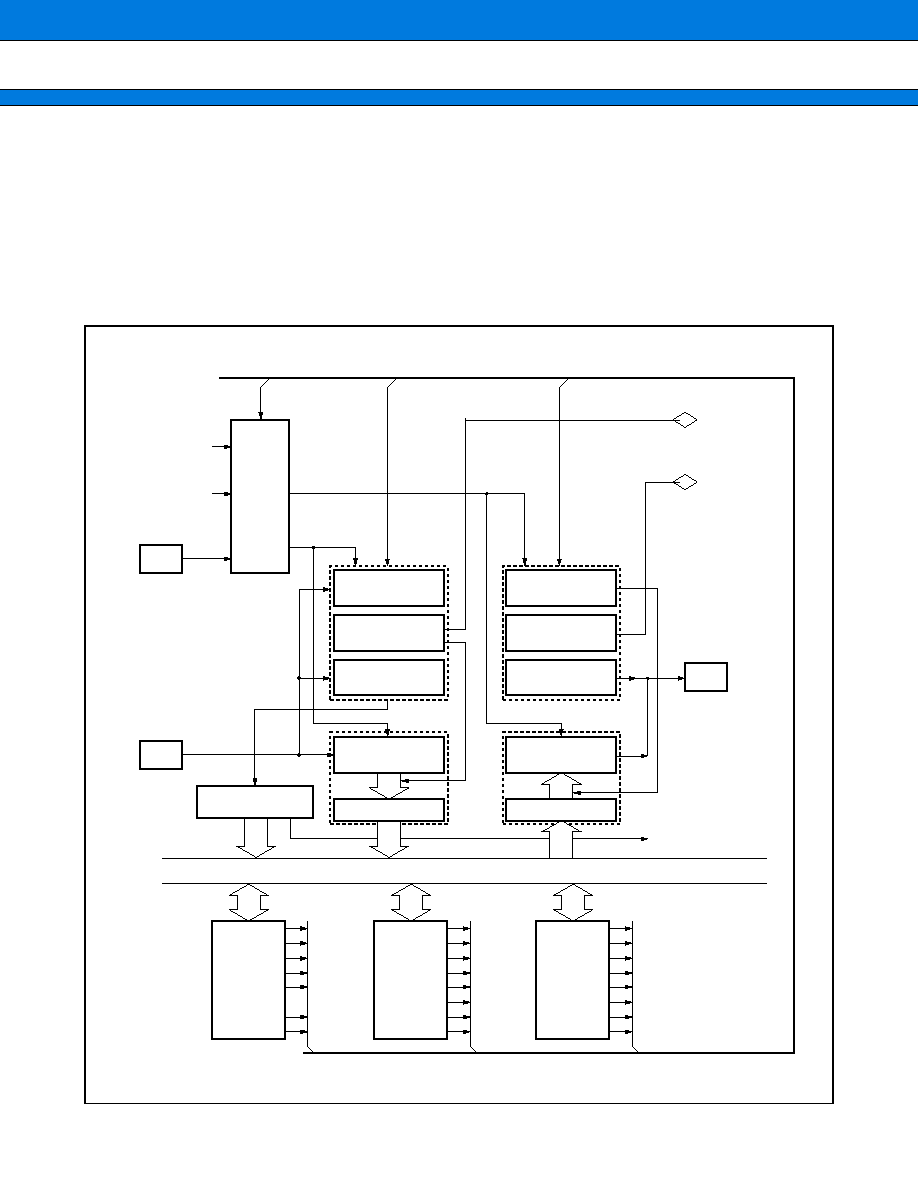

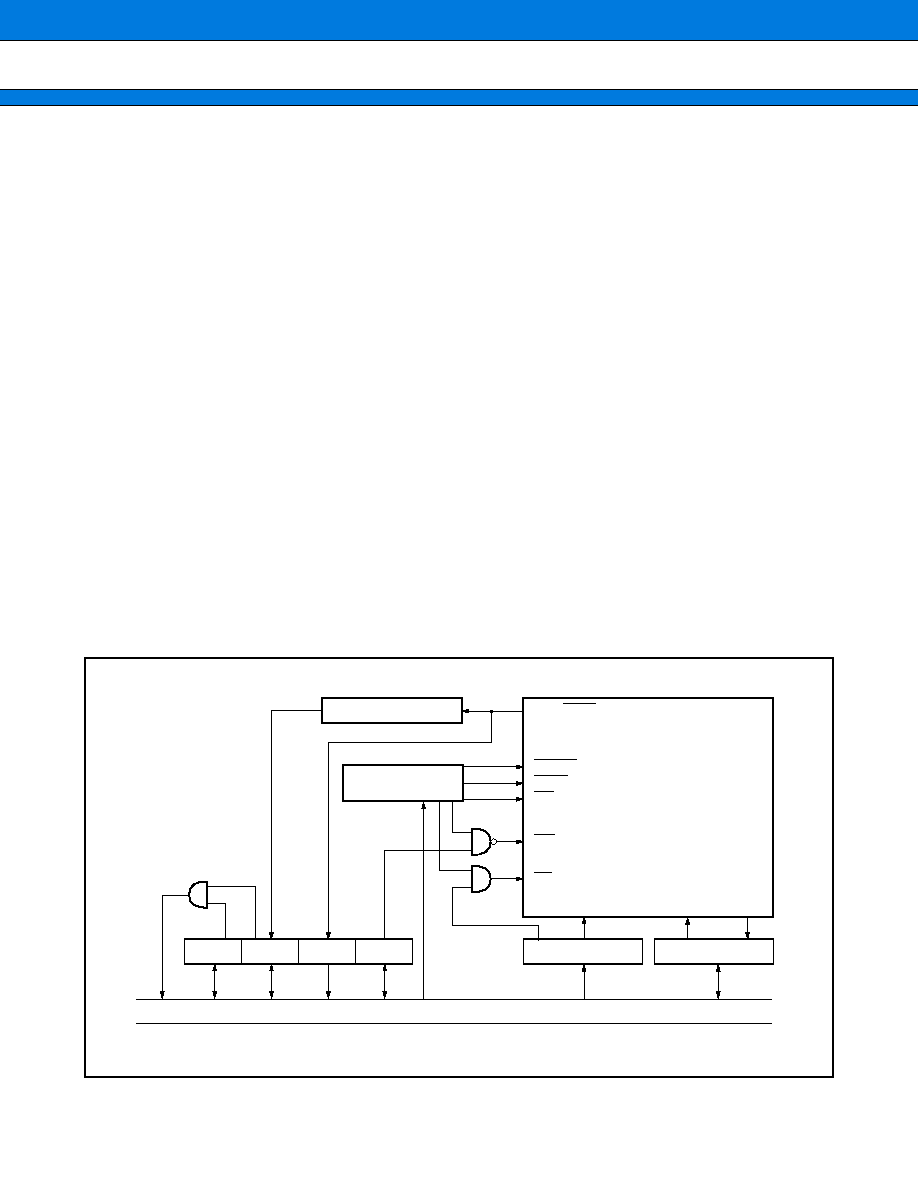

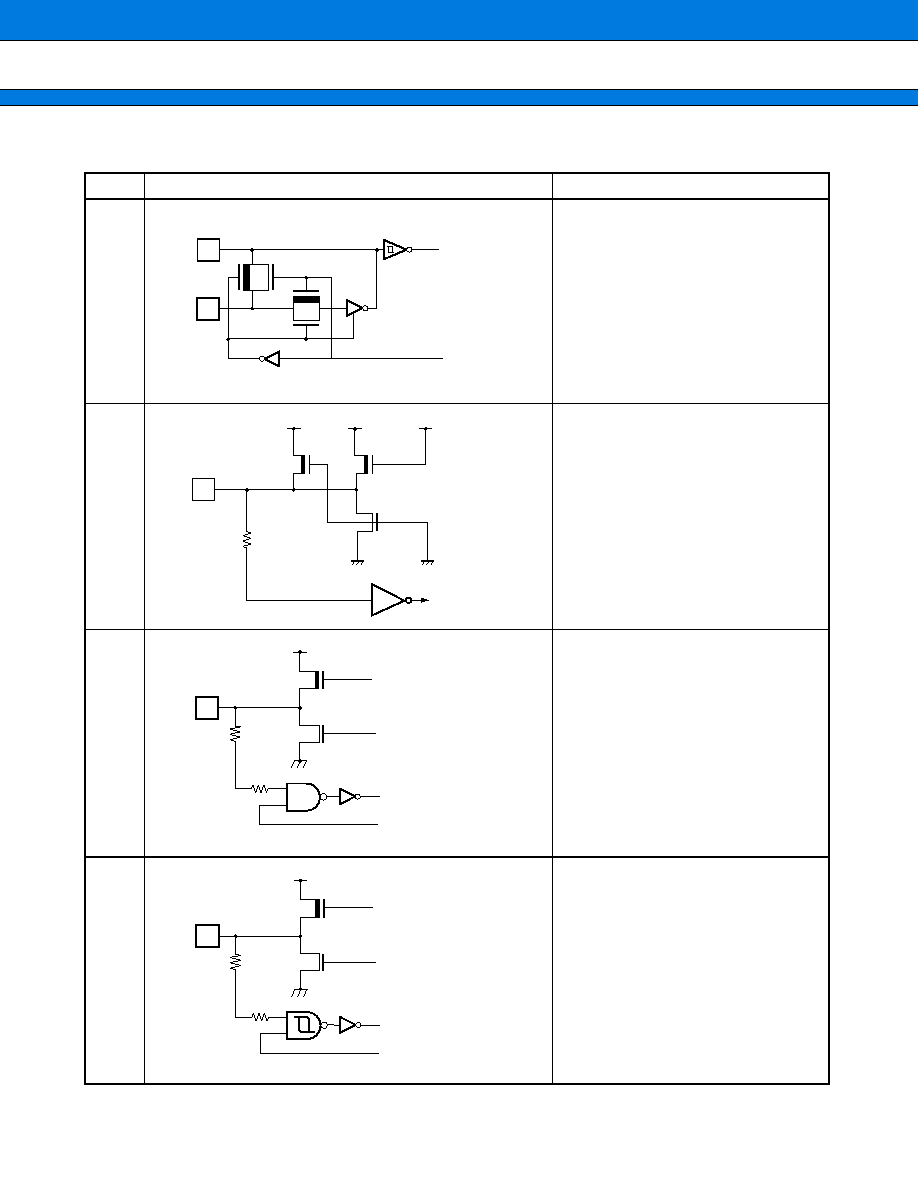

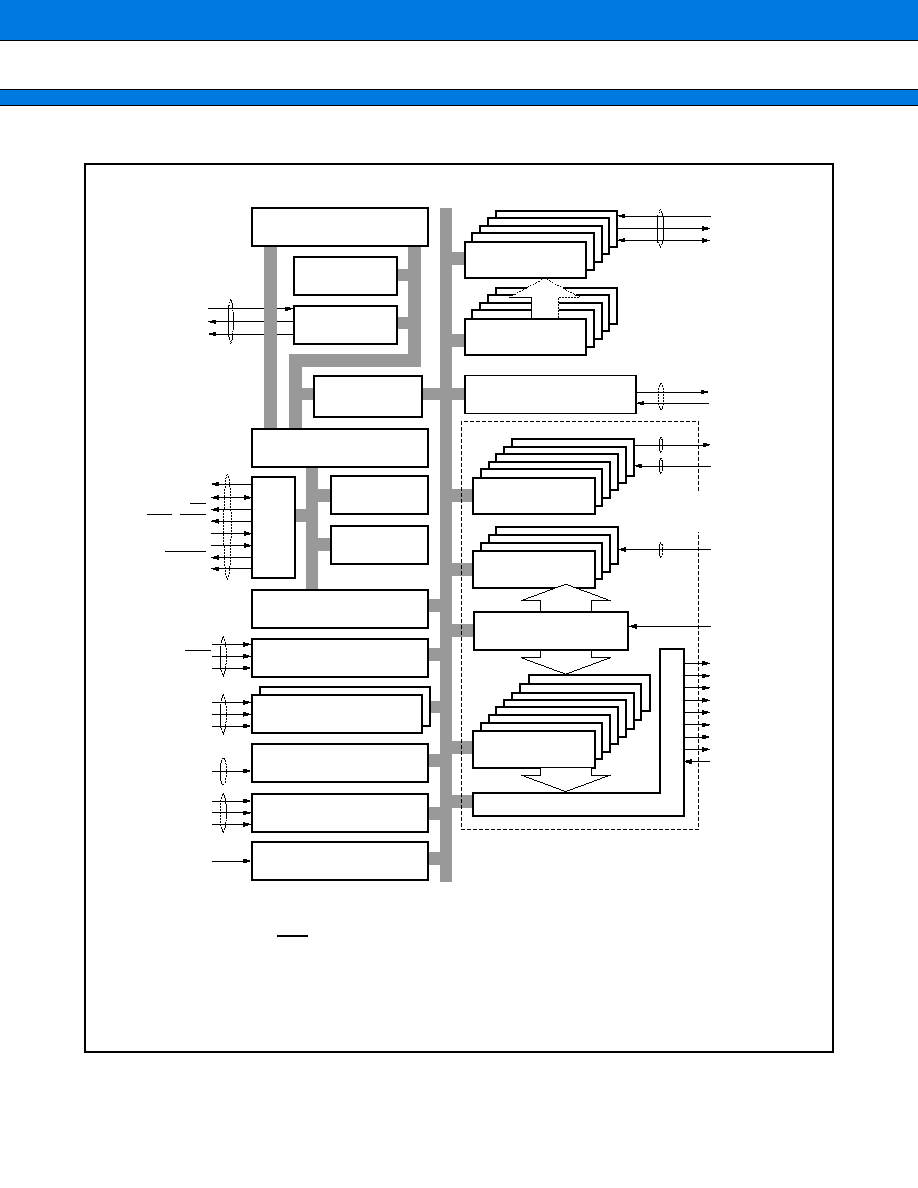

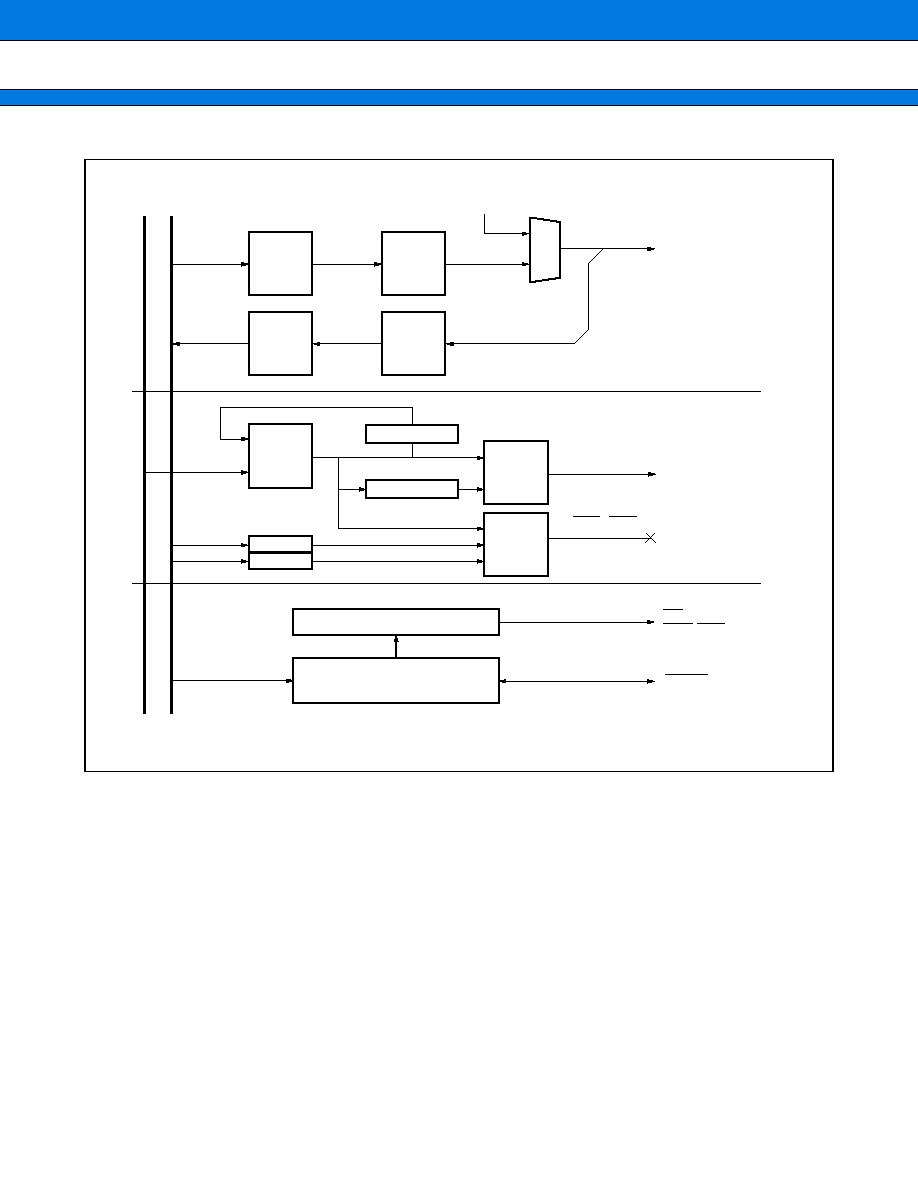

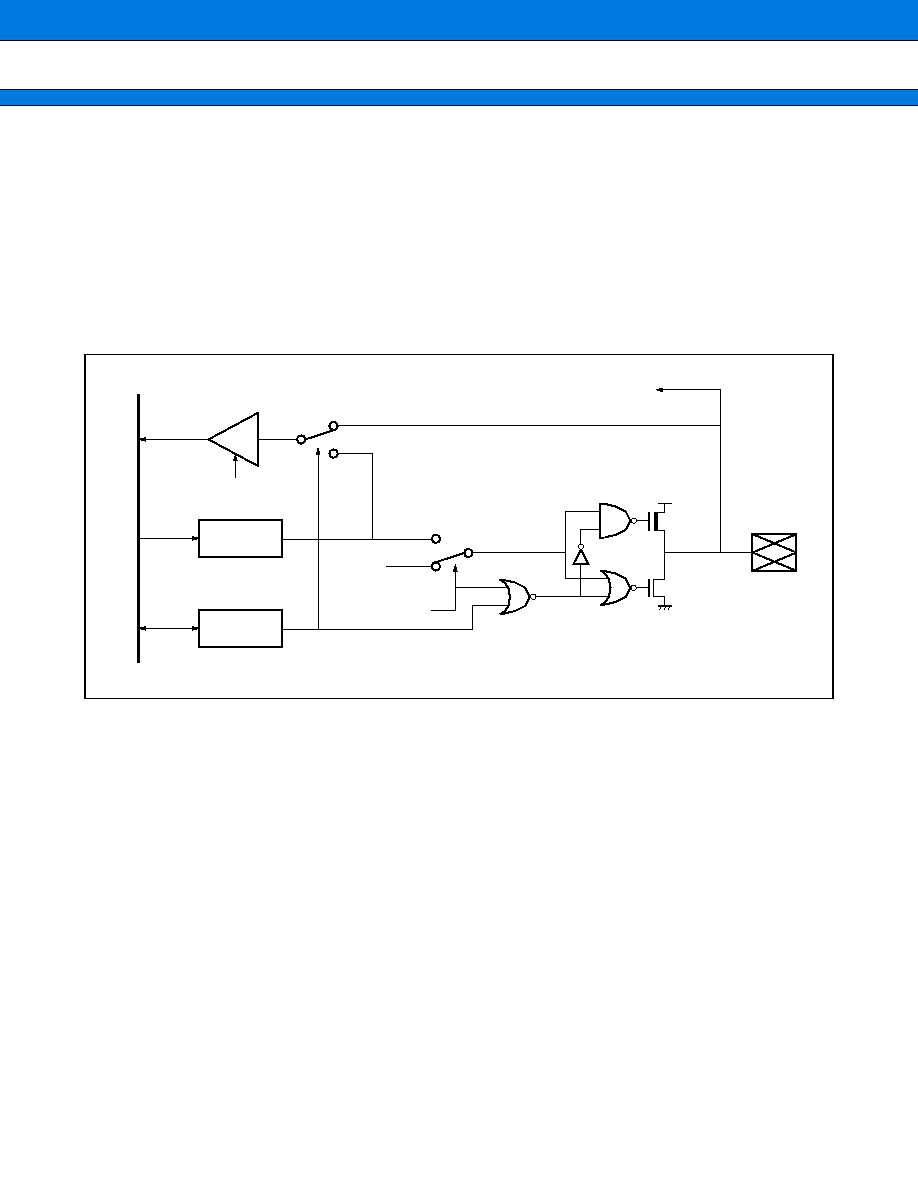

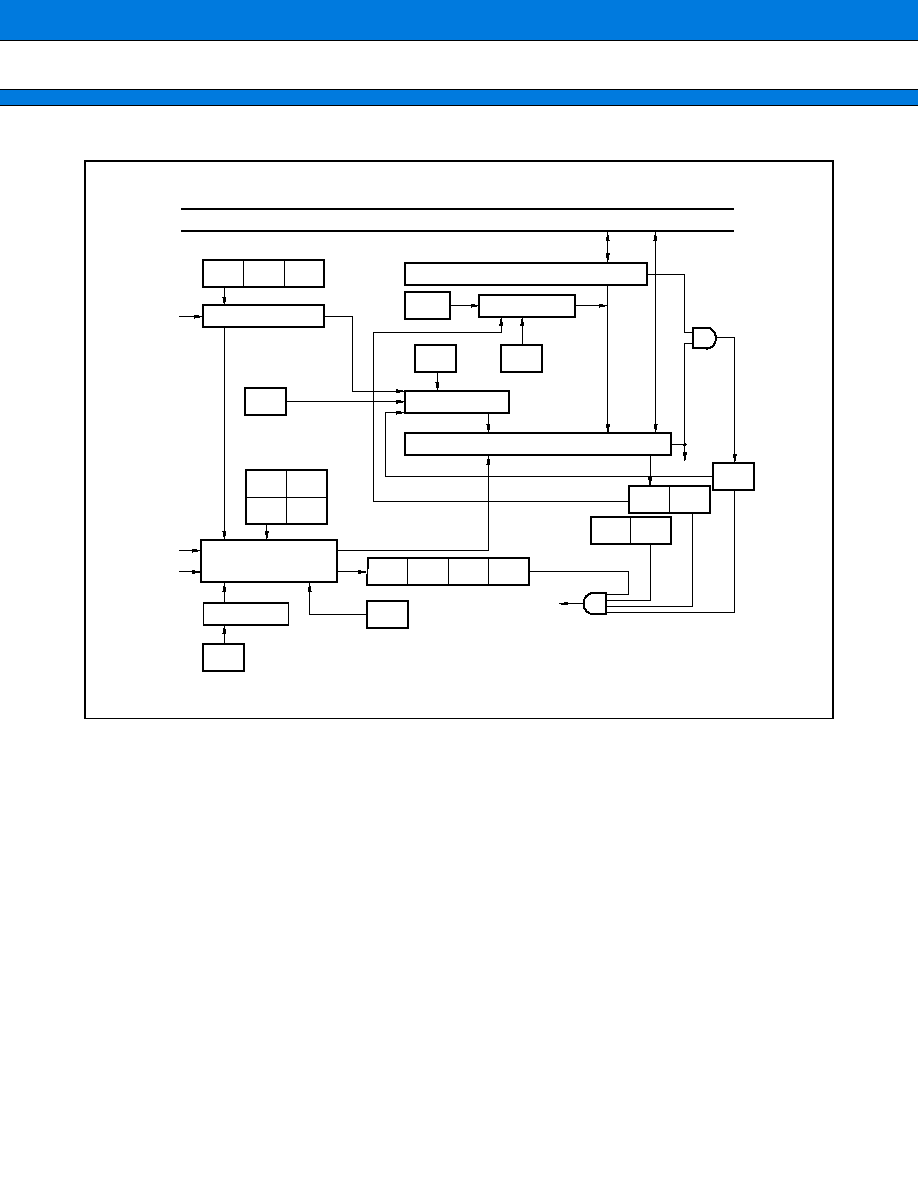

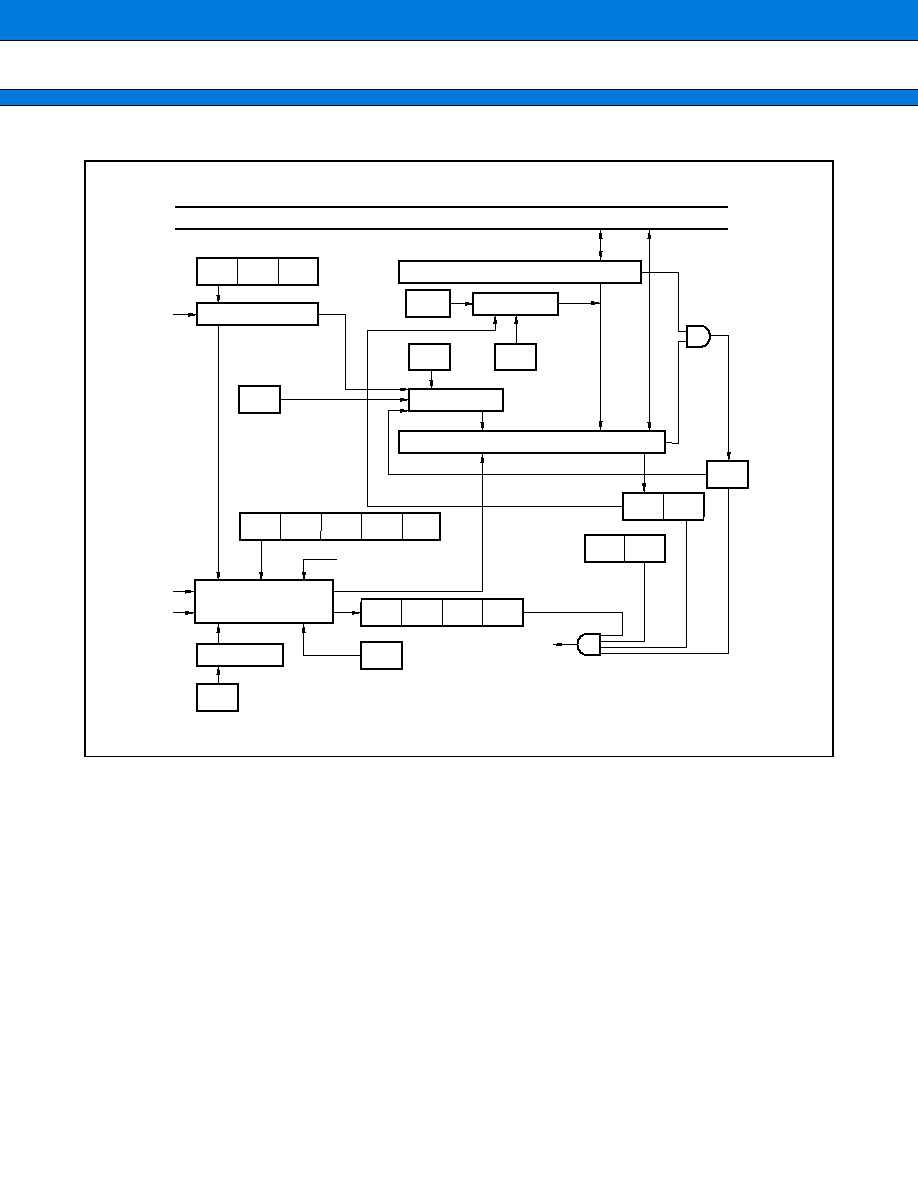

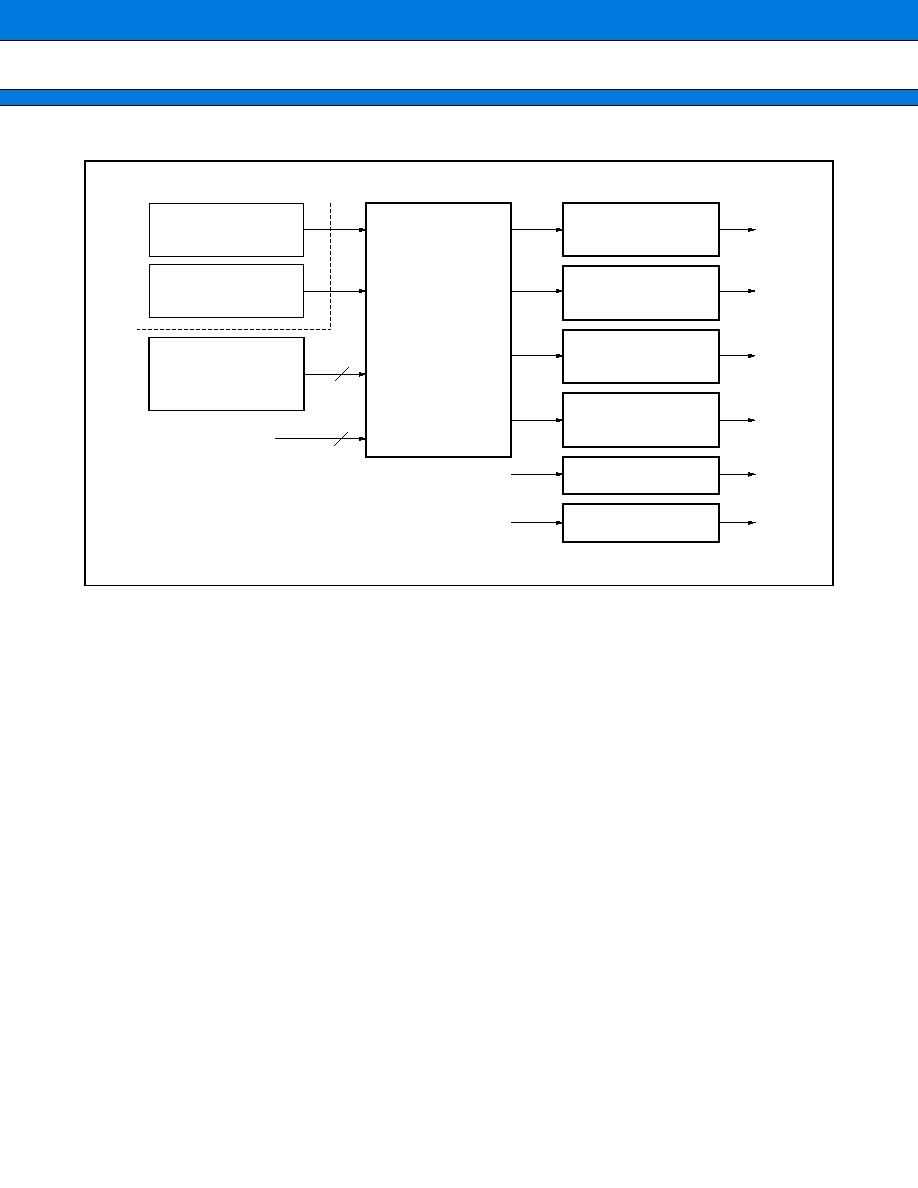

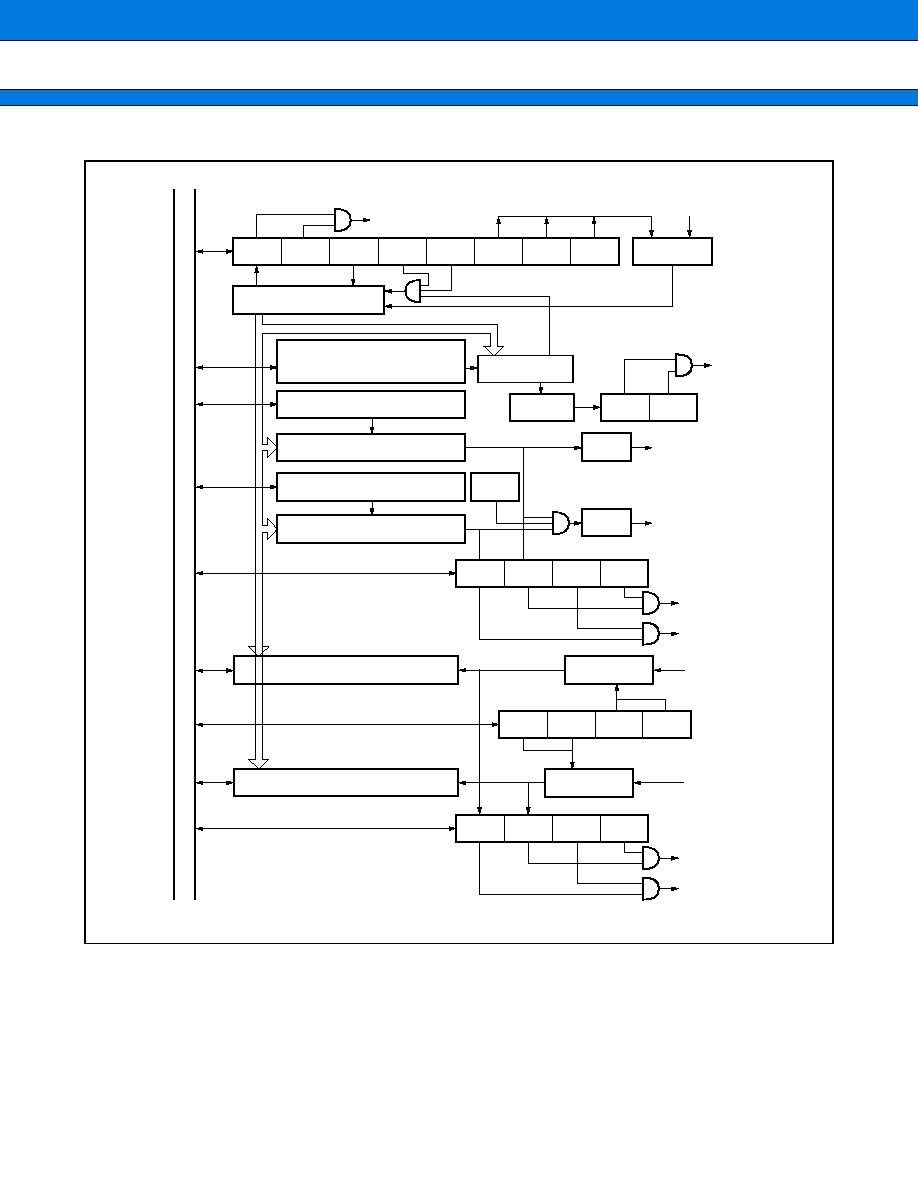

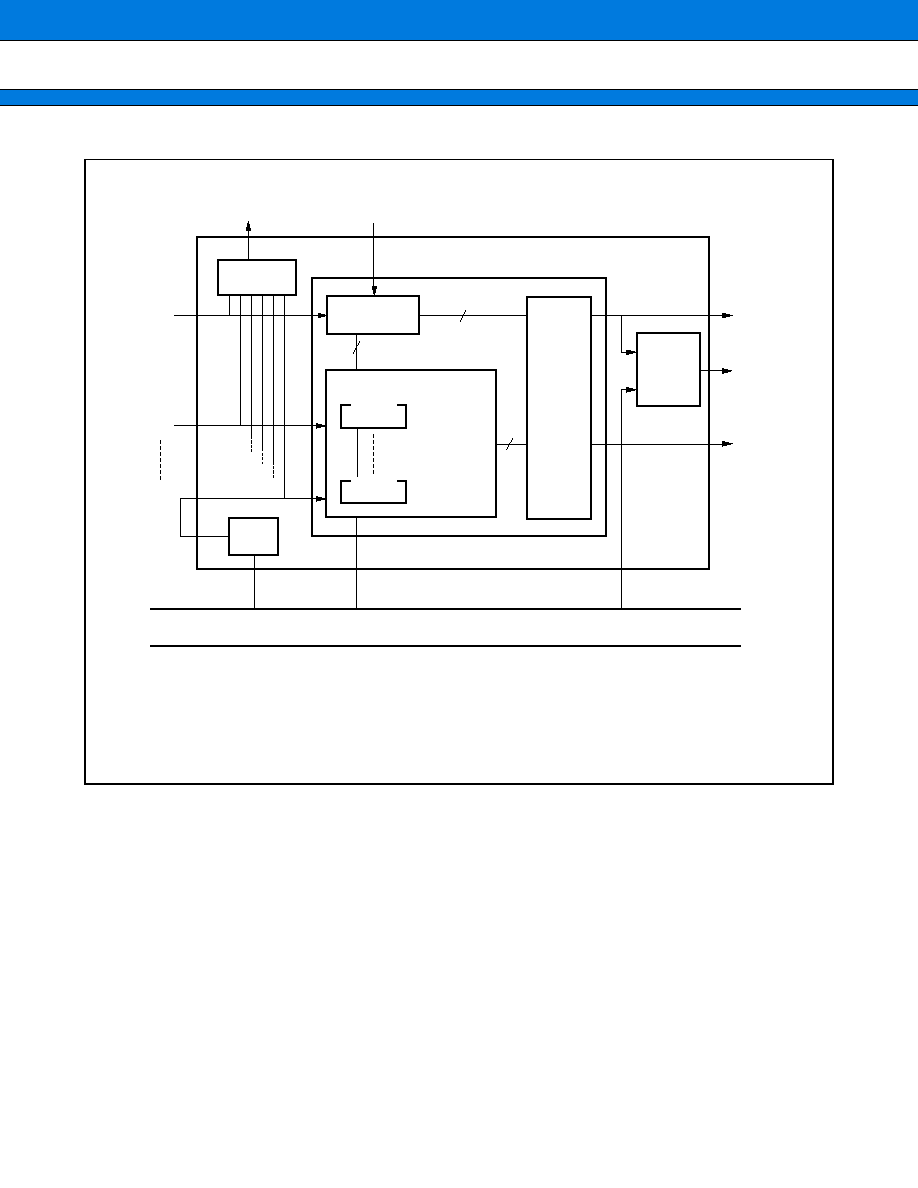

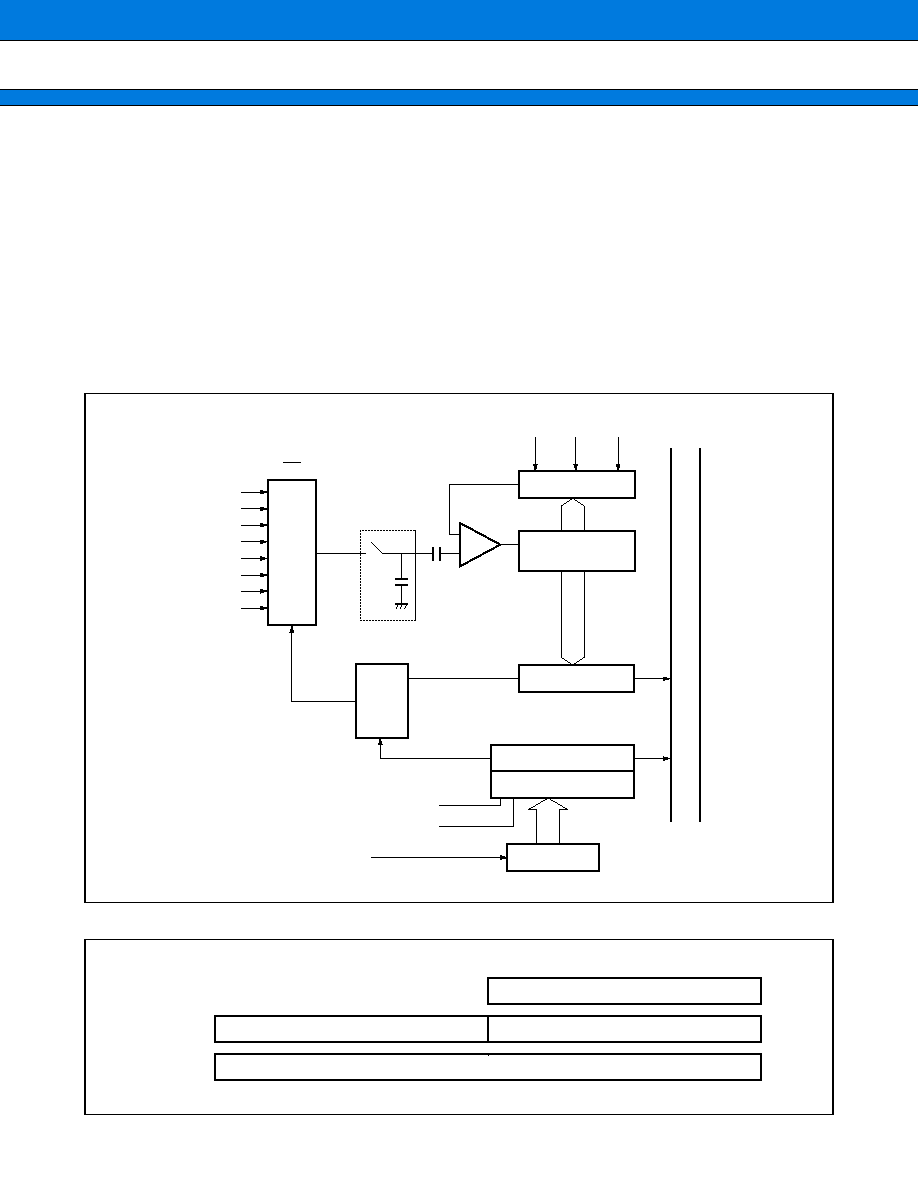

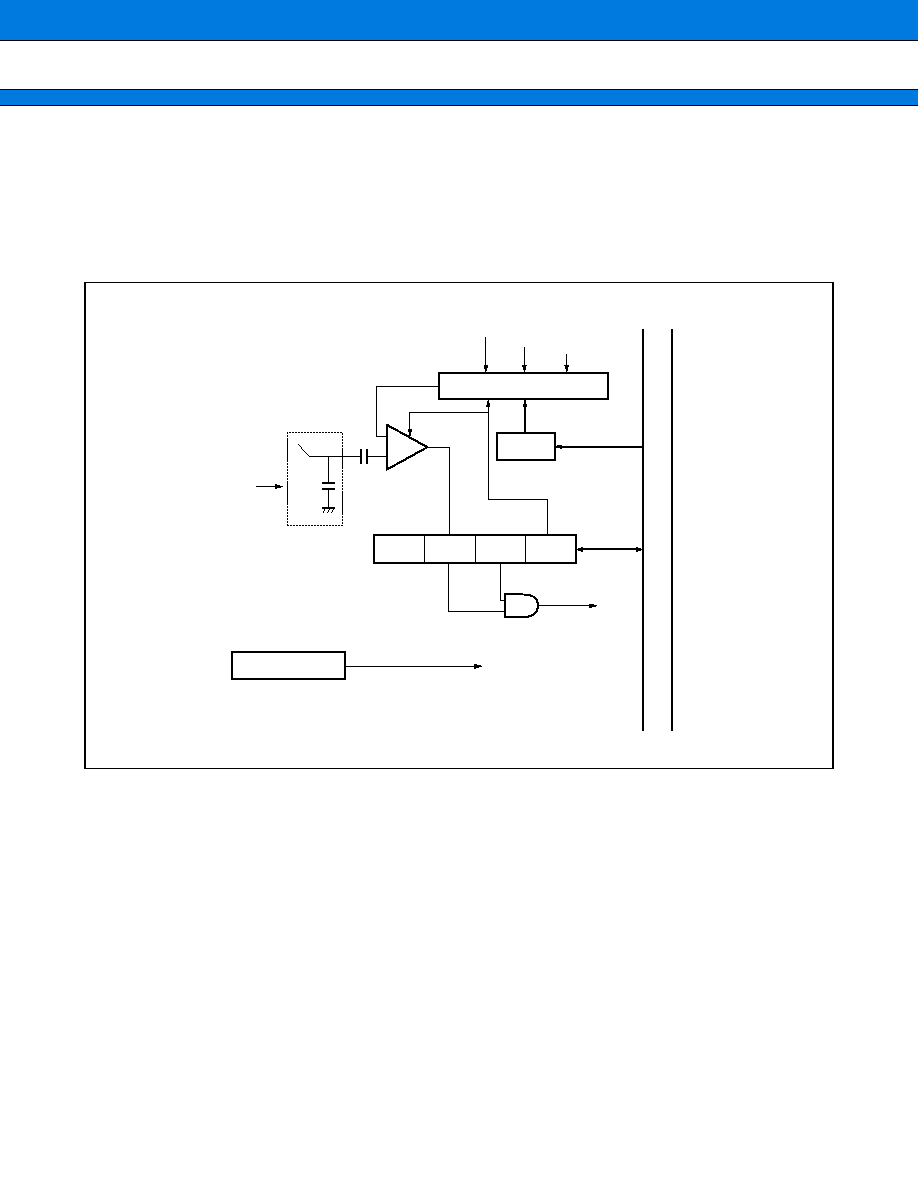

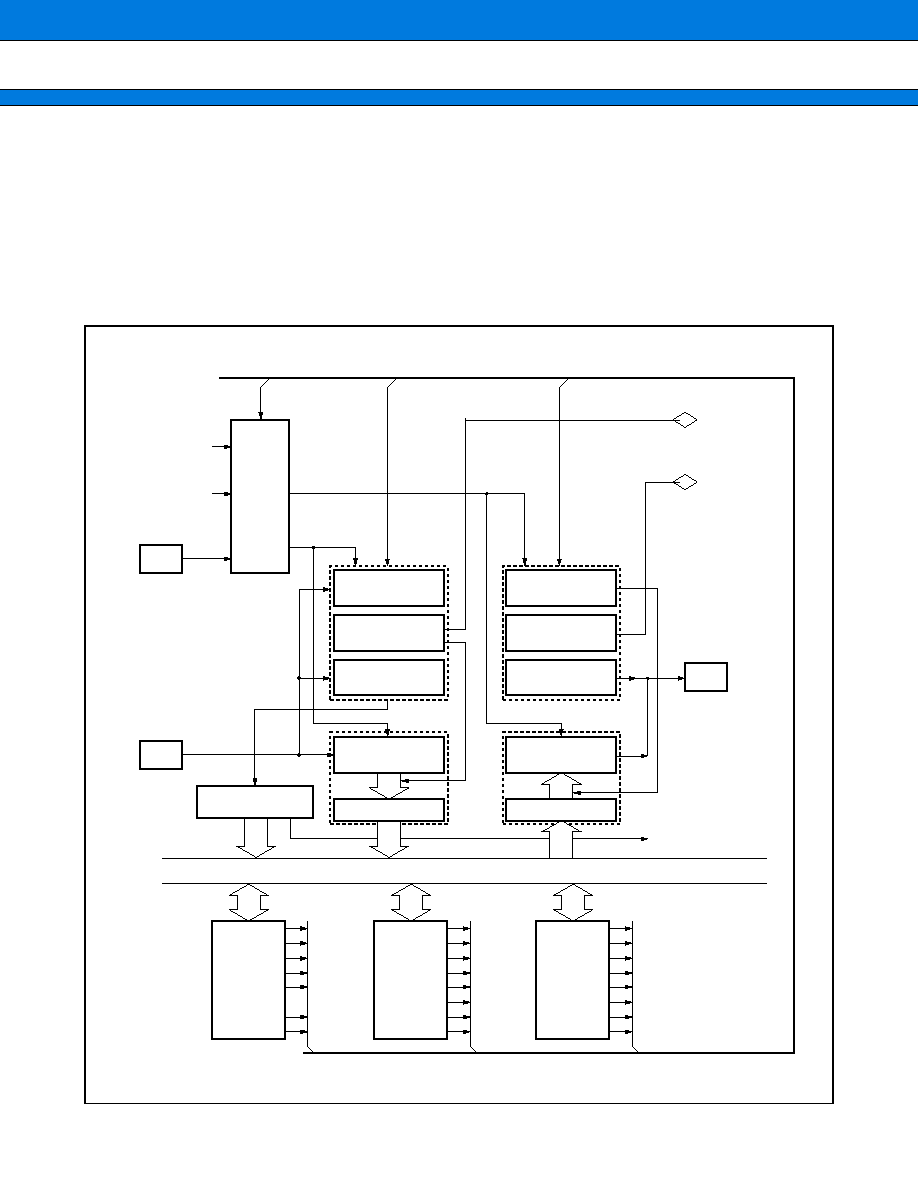

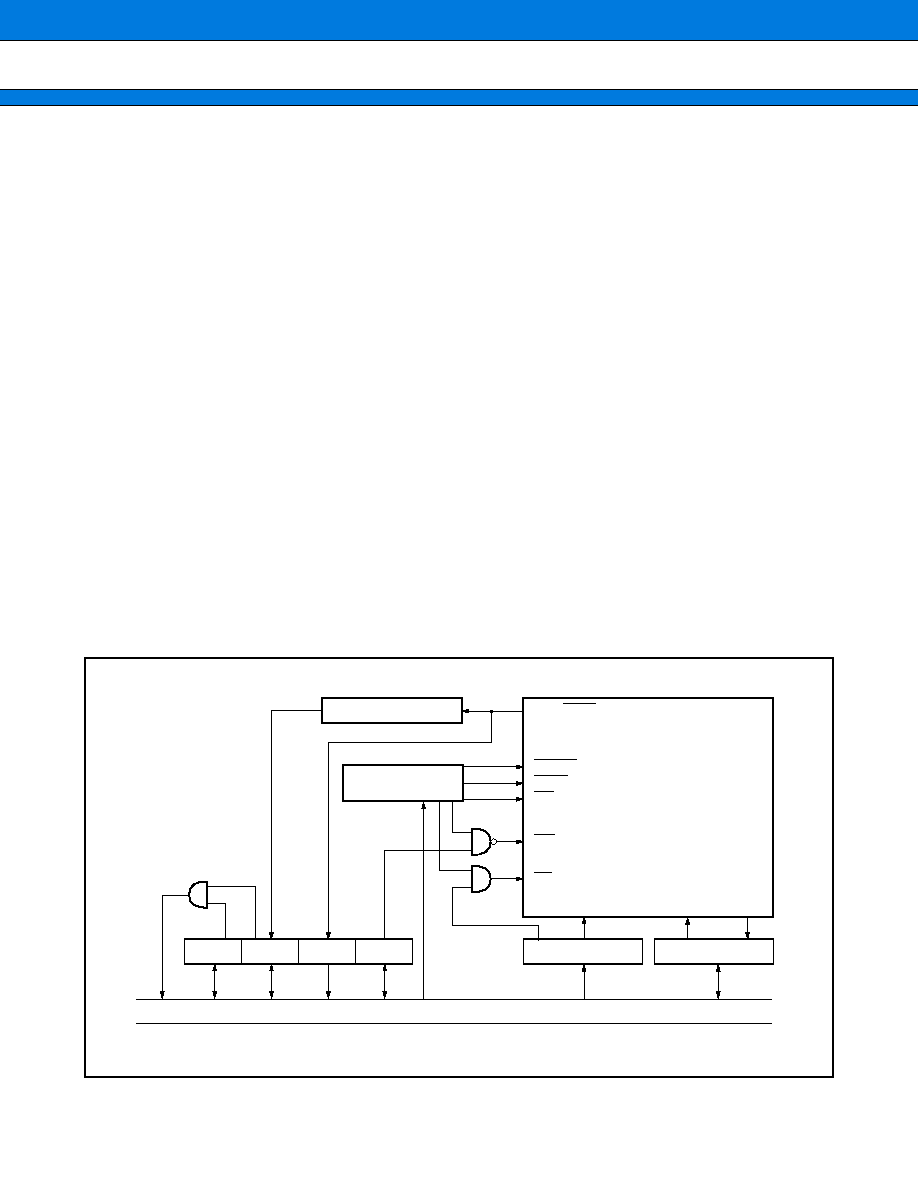

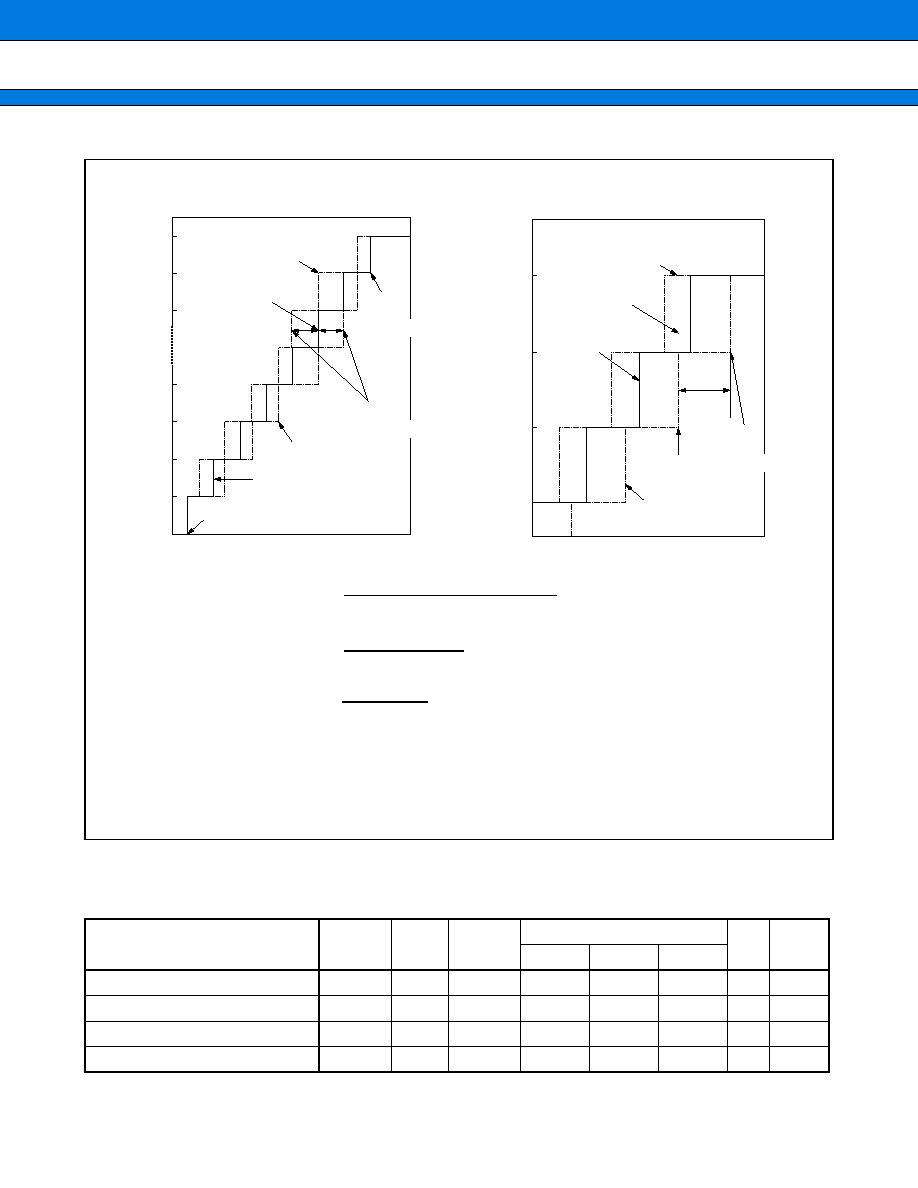

s

BLOCK DIAGRAM

* : INT23 to INT16 share pins with A23 to A16

* : INT15 shares pins with ATG

* : INT14 shares pins with DEOP2

* : INT13 to INT8 share pins with TRG5 to TRG0

* : INT7 to INT4 share pins with AIN0, BIN0, AIN1 and BIN1

The total number of above pins is 133. The remainder (144

-

133

=

11 pins) are V

CC

5 , V

CC

3 and V

SS

.

FR30 CPU

RAM 6 Kbyte

DMAC 8 ch

DREQ0 toDREQ

2

DACK0 toDACK

2

DEOP0 to

DEOP2

Resource Bus

Controller

Bus Converter

RAM 2 Kbyte

ROM 254 Kbyte

External Bus

Controller

A23 to A00

D31 to D16

RD

RDY

BRQ

BGRNT

CLK

WR1, WR0

Interrupt Controller

Clock Generator

Up/Down counter

◊

2 ch

24 ch external interrupt

10 bit 8 input A/D converter

level comparator

X0, X1, X0A, X1A

RST

MD0 to MD2

47

9

8

AIN0, 1

BIN0, 1

ZIN0, 1

INT0 to INT23 (

)

6

24

AN0 to AN7

AVRH, AVRL

AV

CC

, AV

SS

CMP (AN7)

12

15

5

6

6

SIN0 to SIN4

SOT0 to SOT4

SCK0 to SCK4

UART

◊

5 ch

Reload timer

◊

5 ch

8 bit 3 output D/A converter

DA0 toDA2

PPG0 to PPG5

TRG0 to TRG5

IN0 to IN3

FRCK

DAVC, DAVS

4

Multi-Function

Timer

16 bit PPG

◊

6 ch

16 bit ICU

◊

4 ch

16 bit FRT

16 bit OCU

◊

8 ch

Waveform Generator

RTO0 (U)

RTO1 (X)

RTO2 (V)

RTO3 (Y)

RTO4 (W)

RTO5 (Z)

RTO6

RTO7

DTTI

MB91133/MB91F133

23

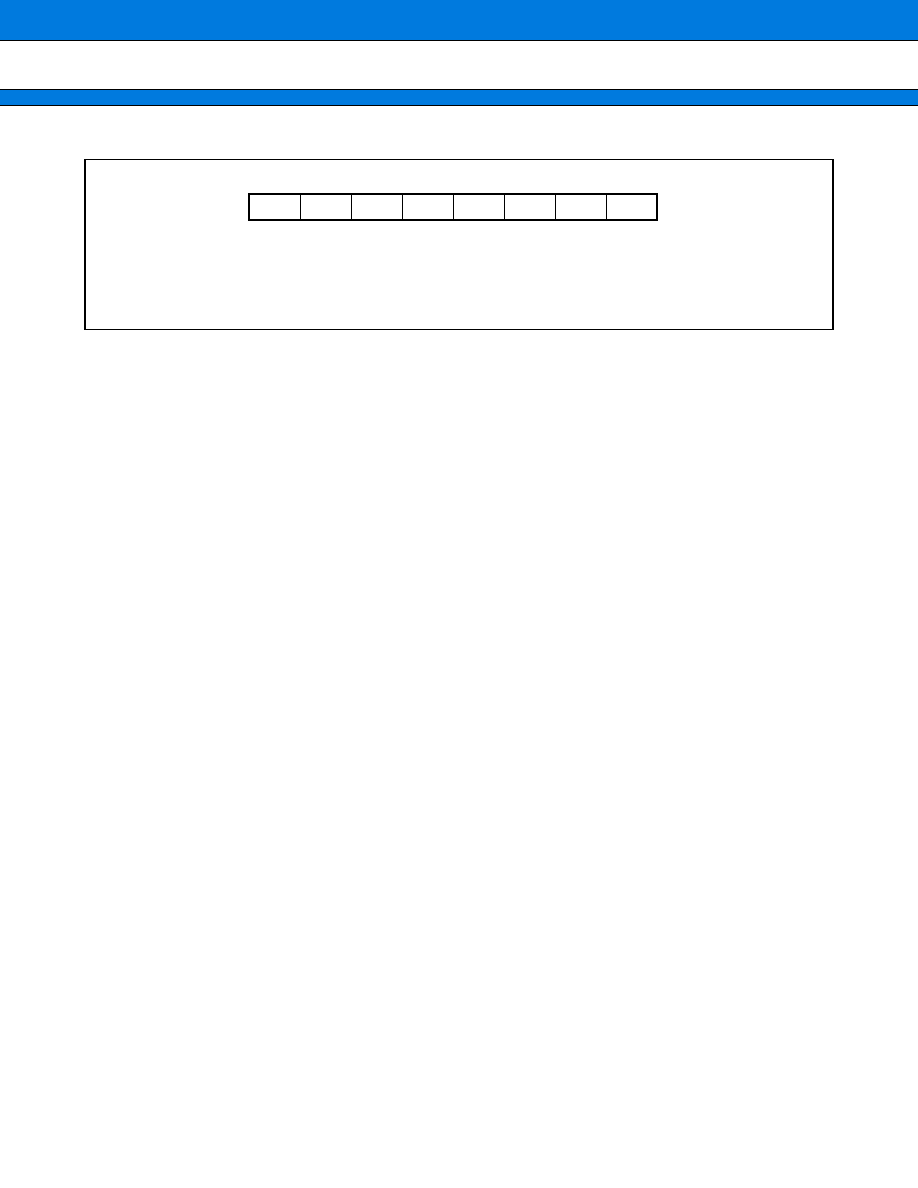

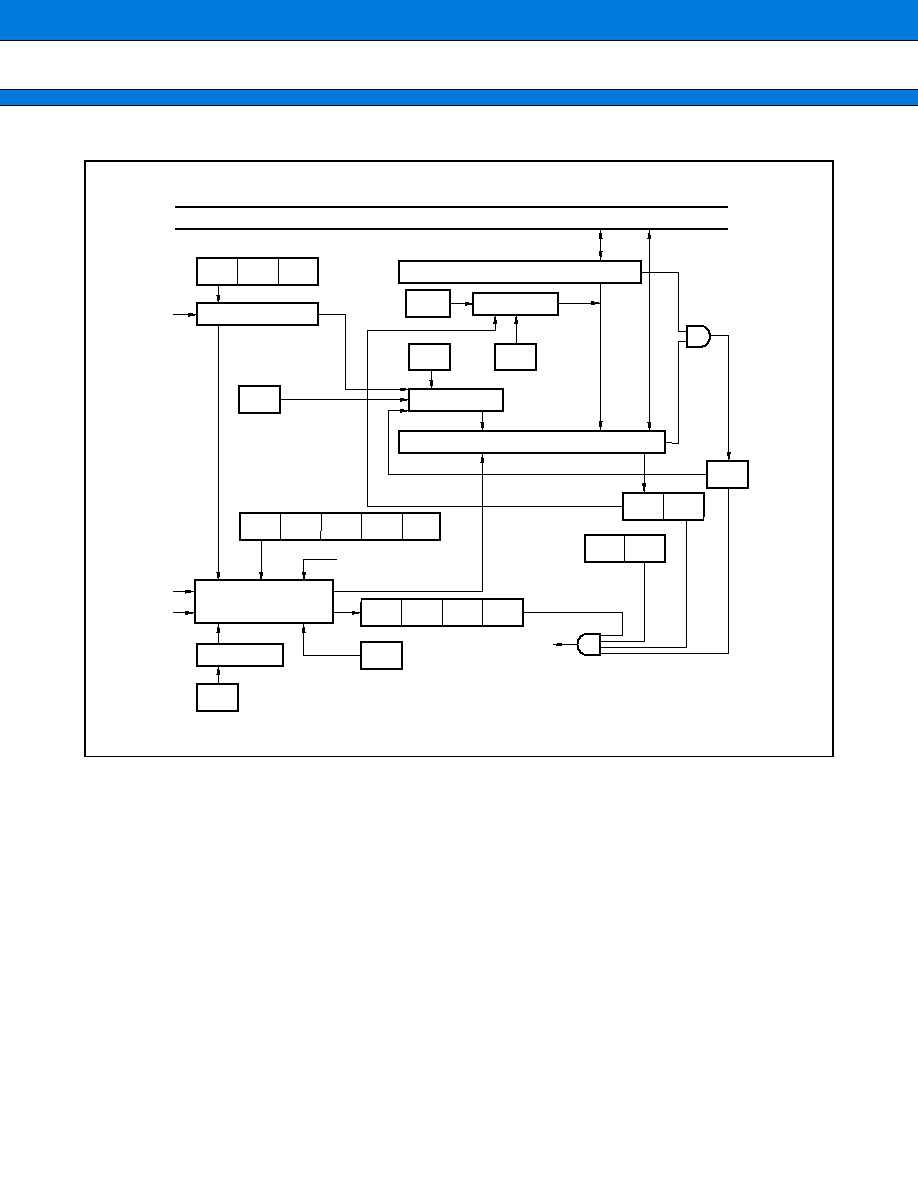

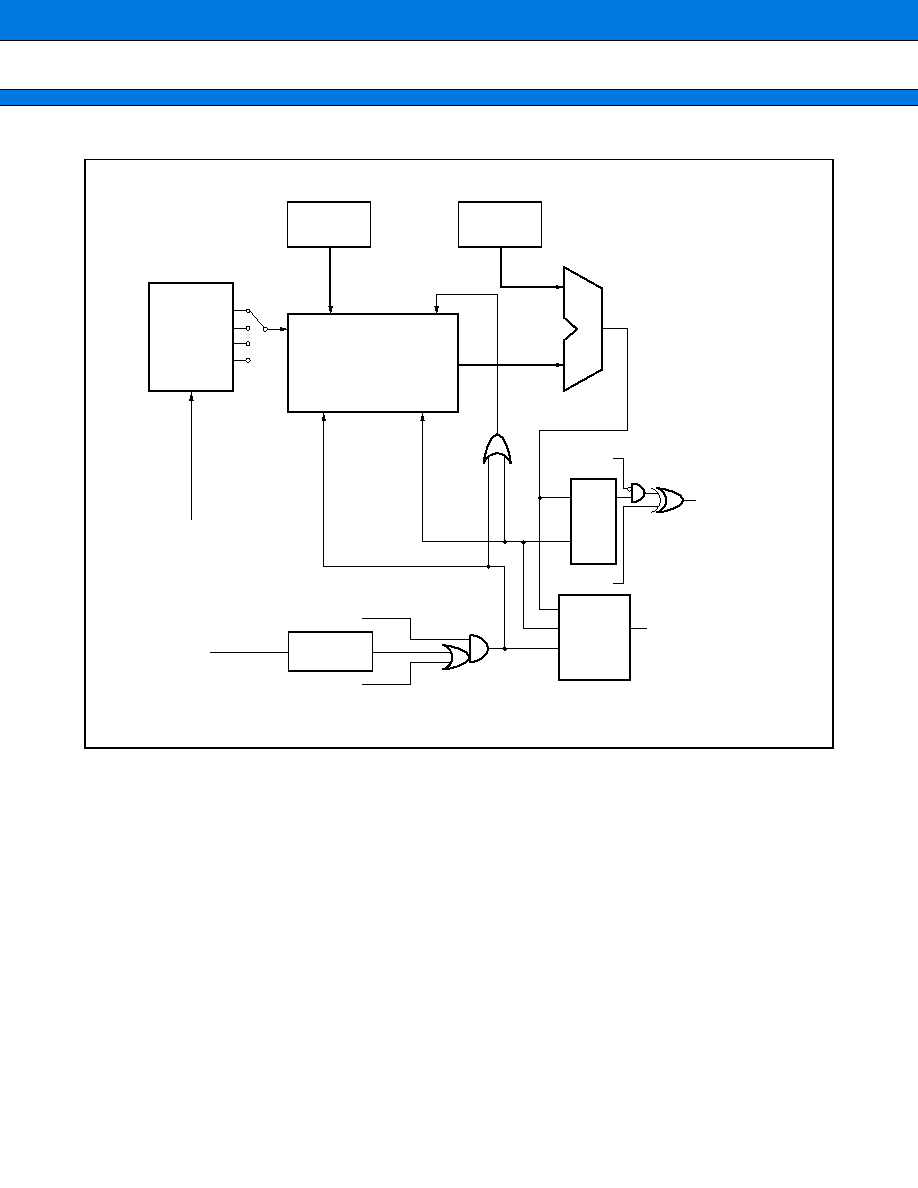

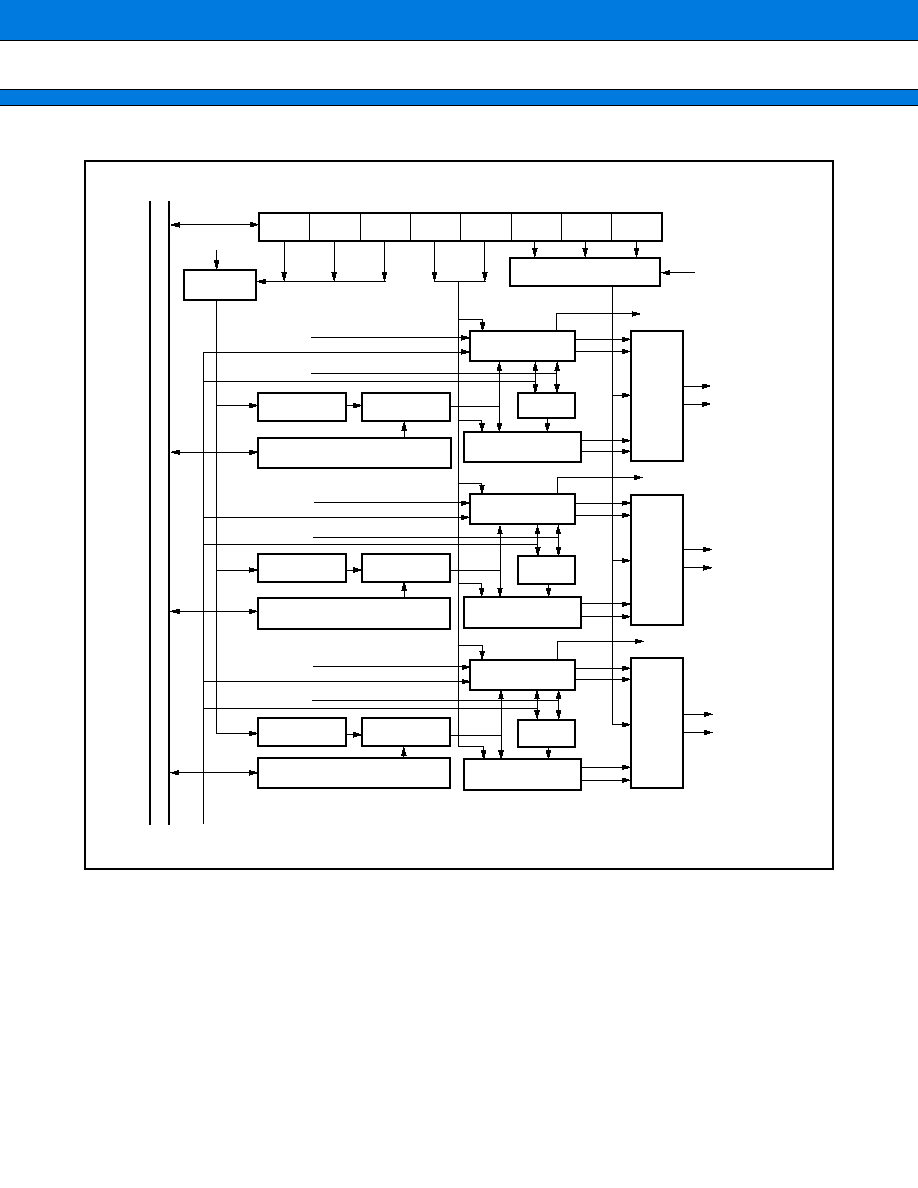

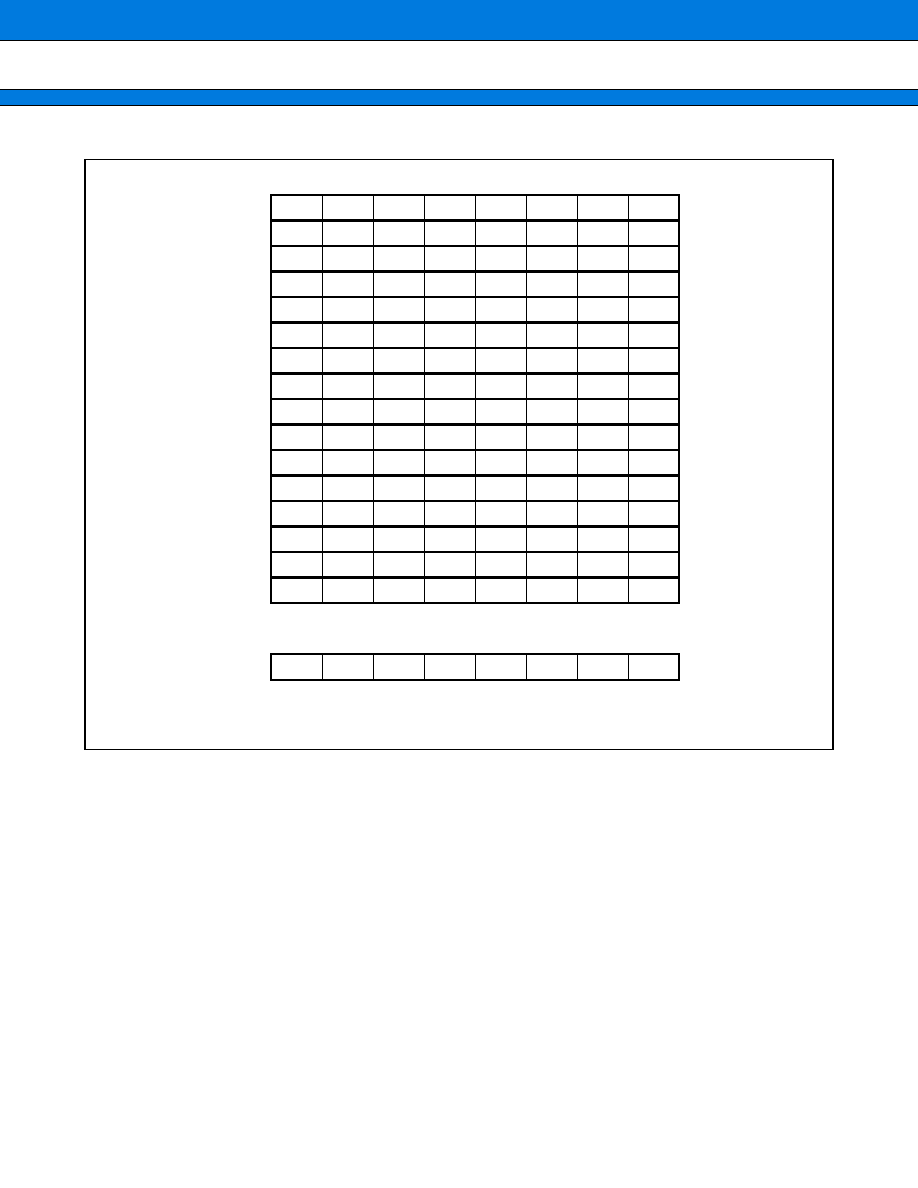

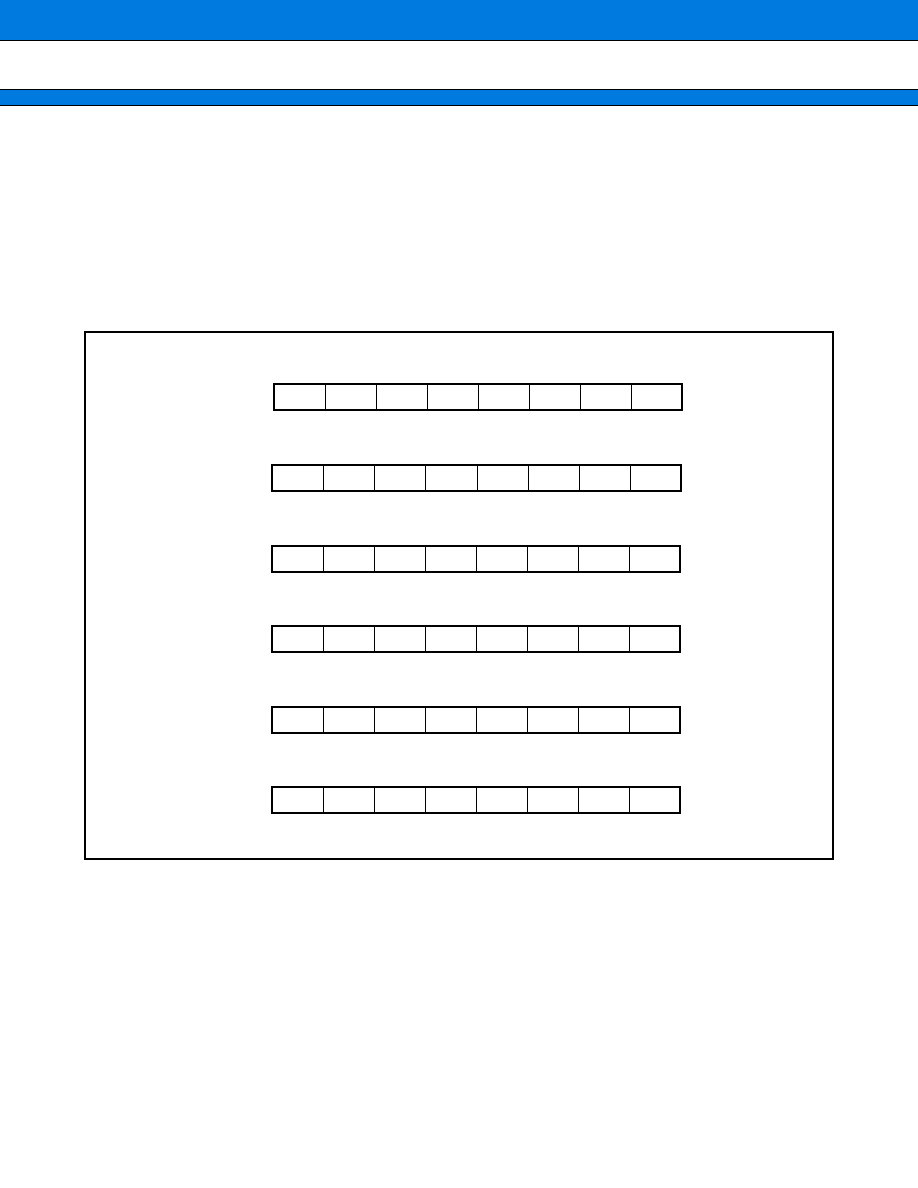

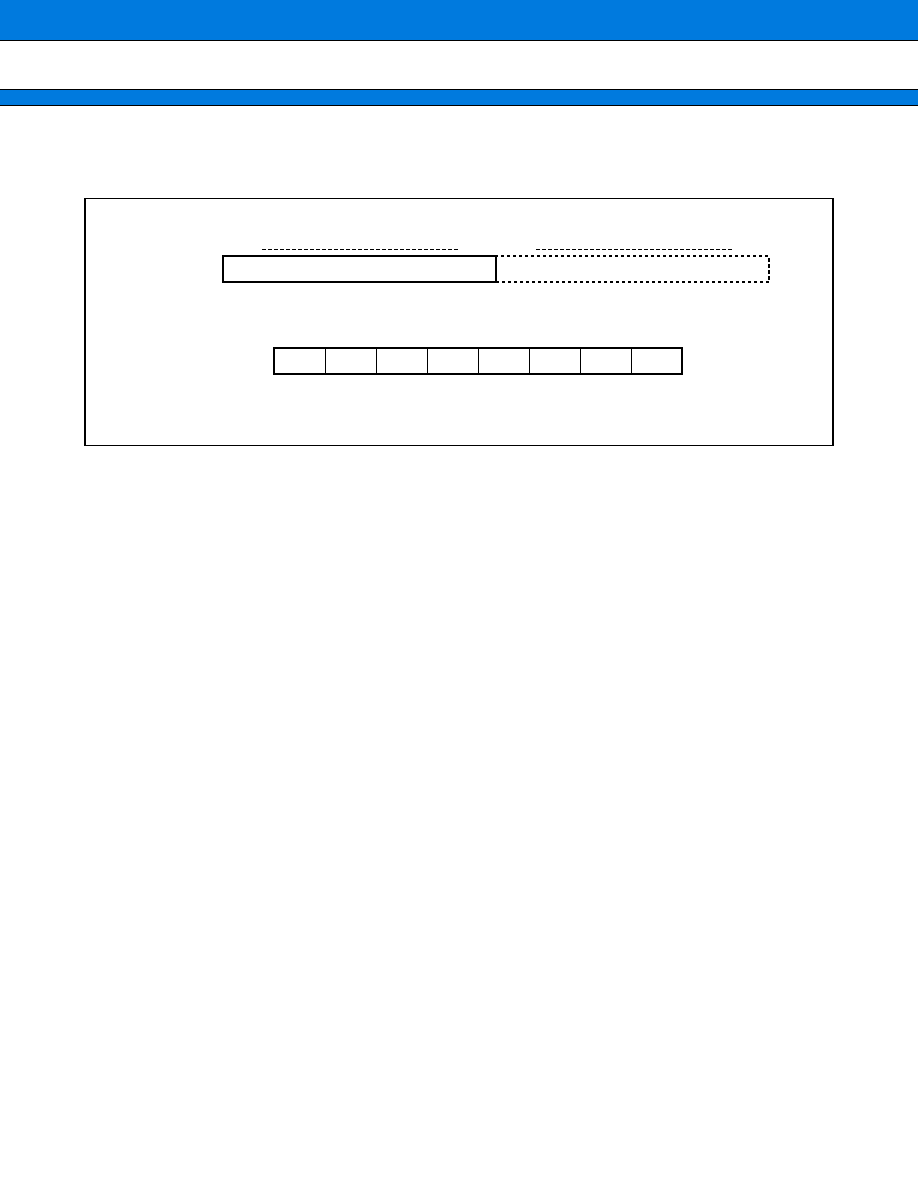

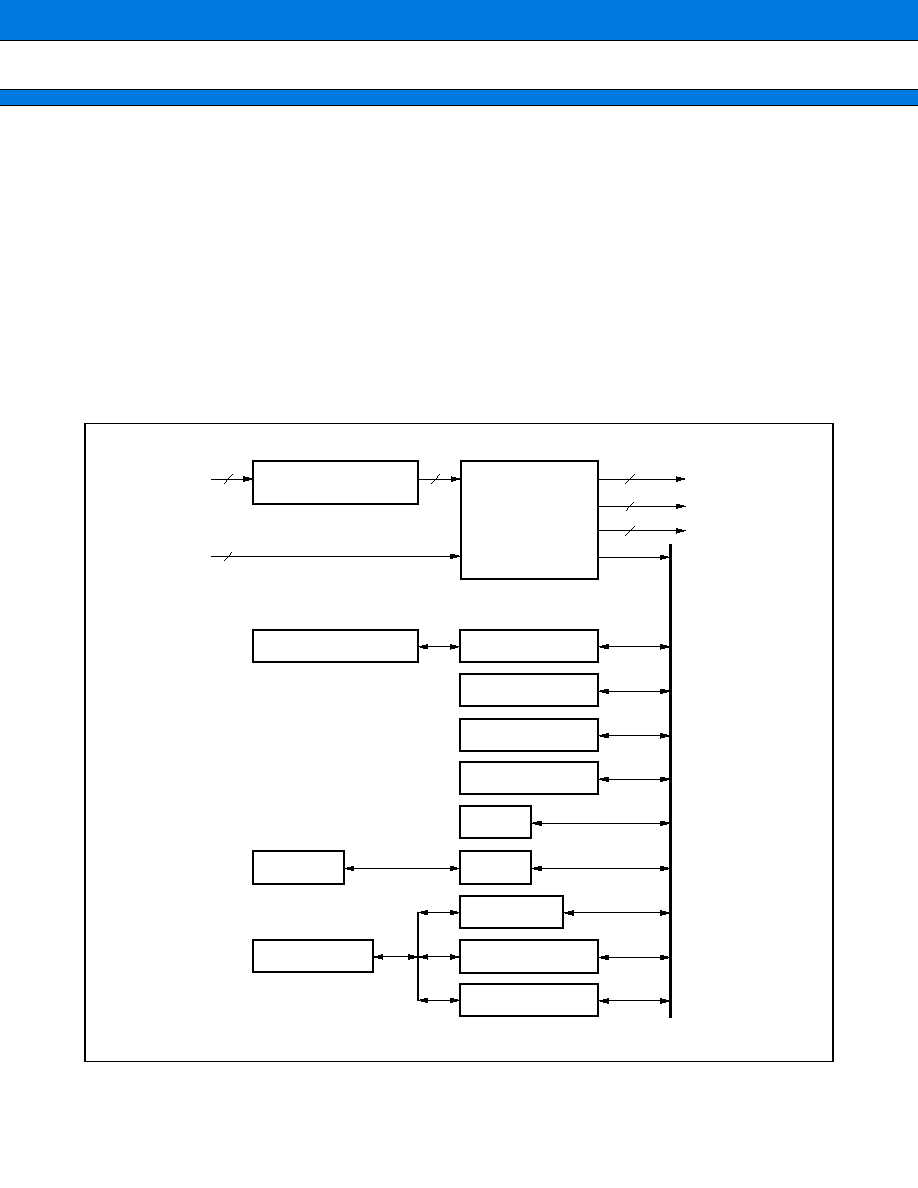

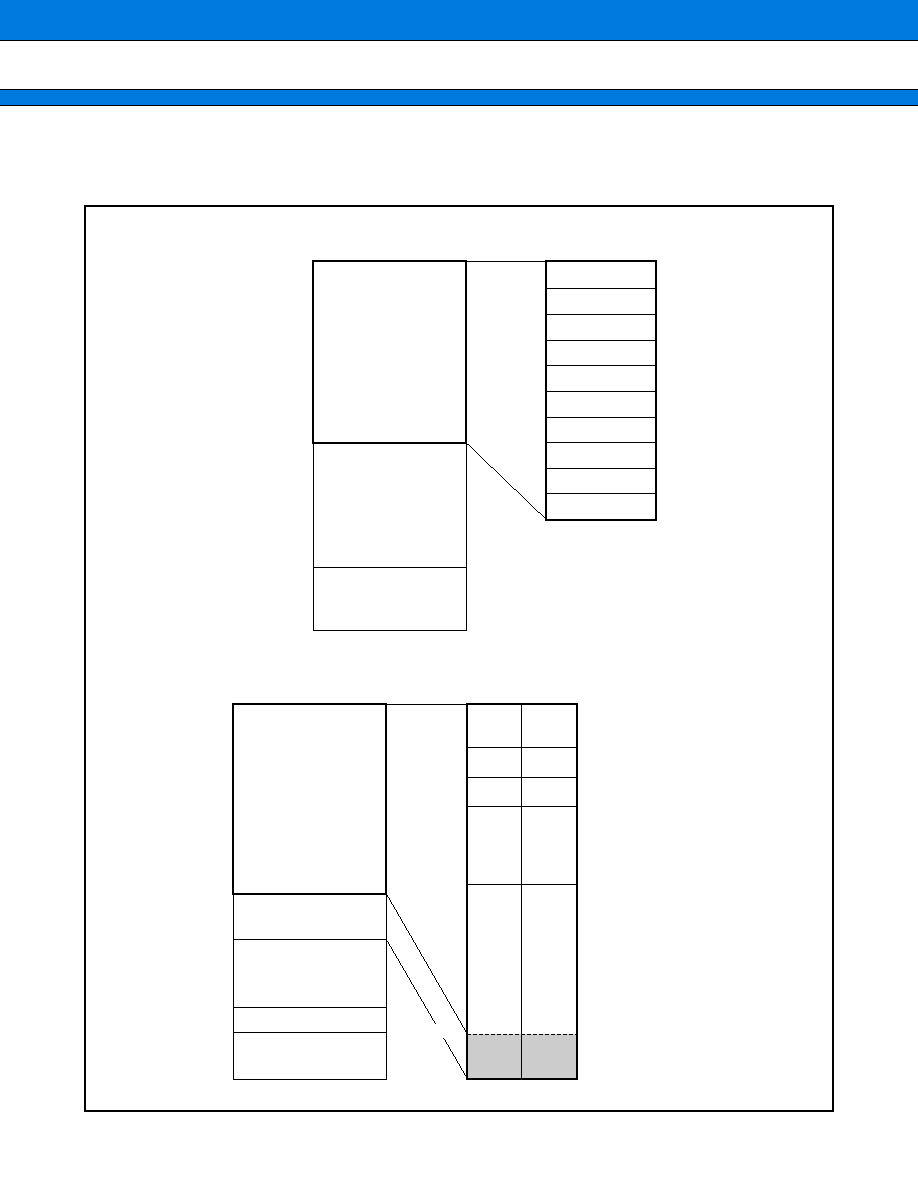

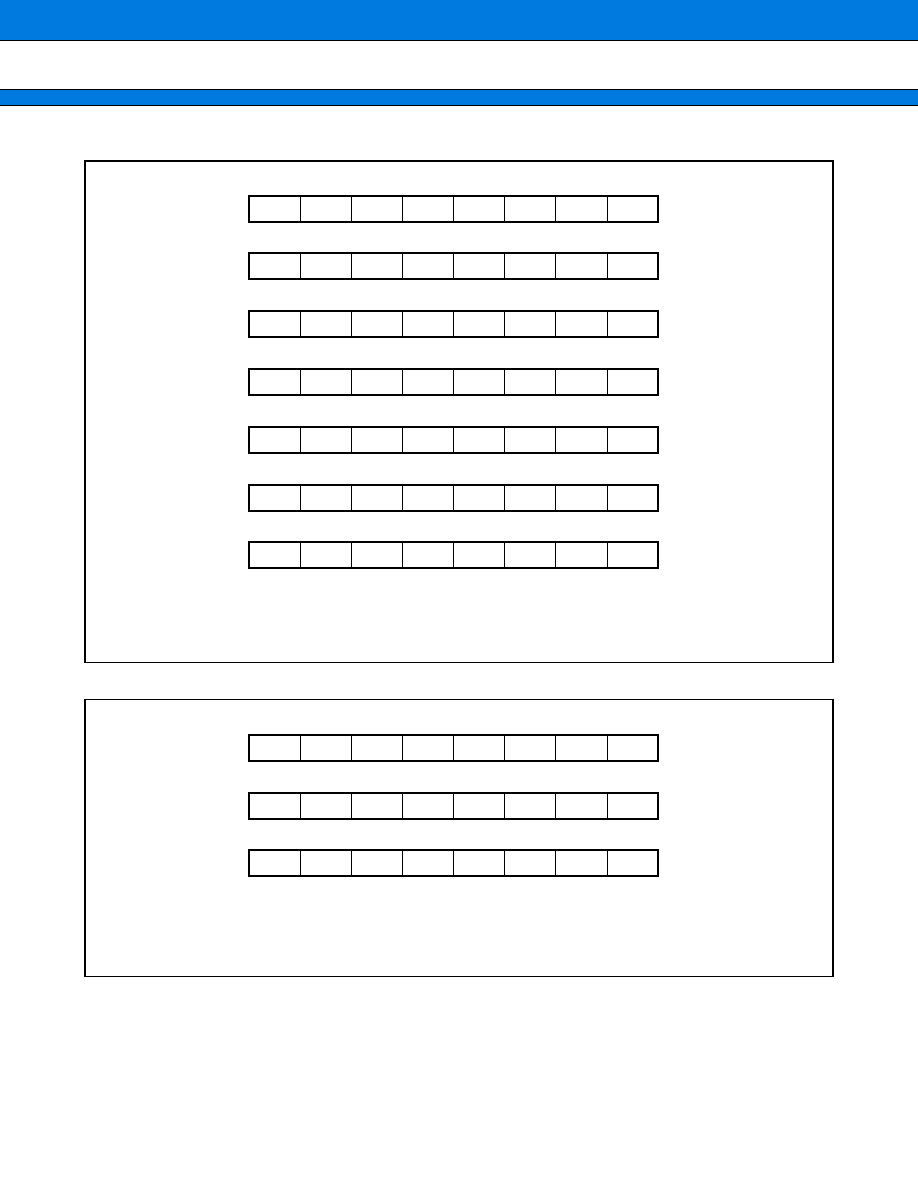

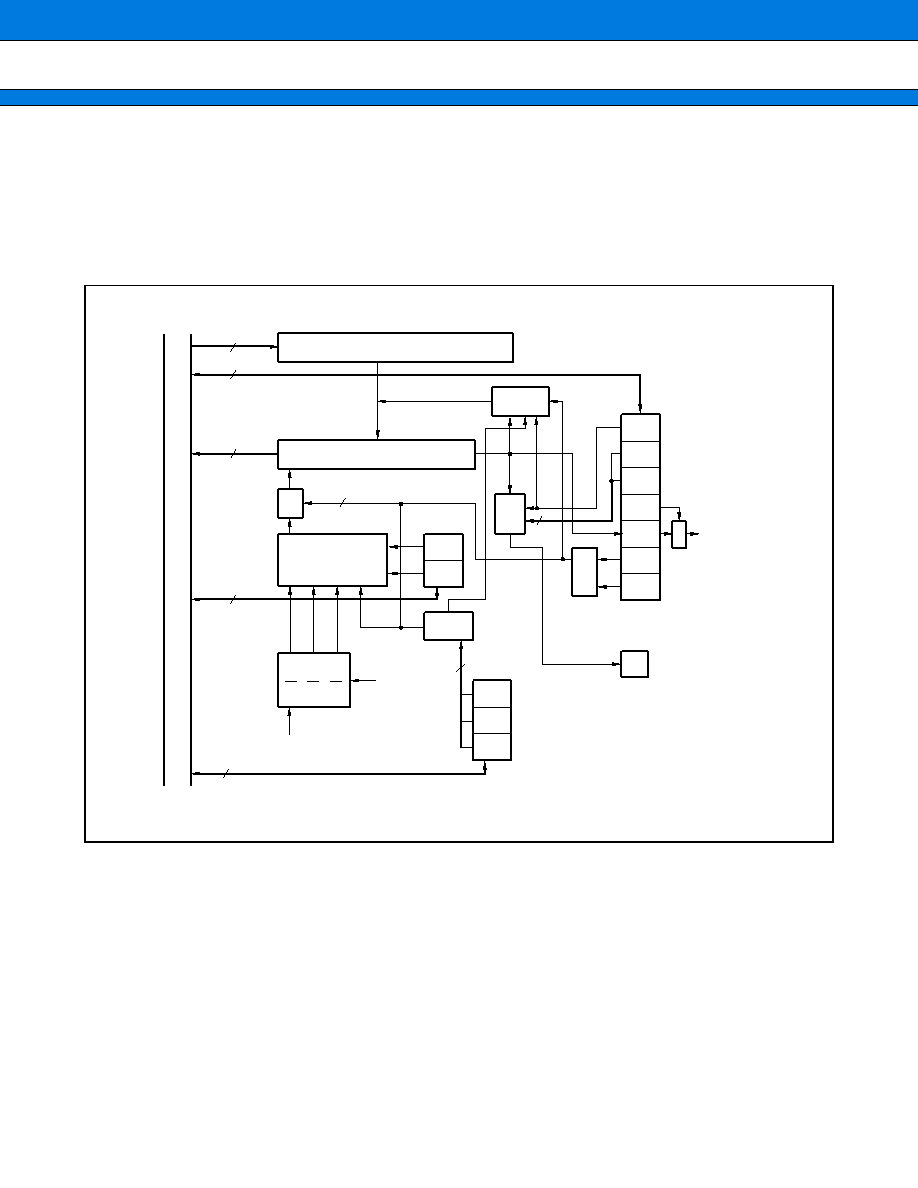

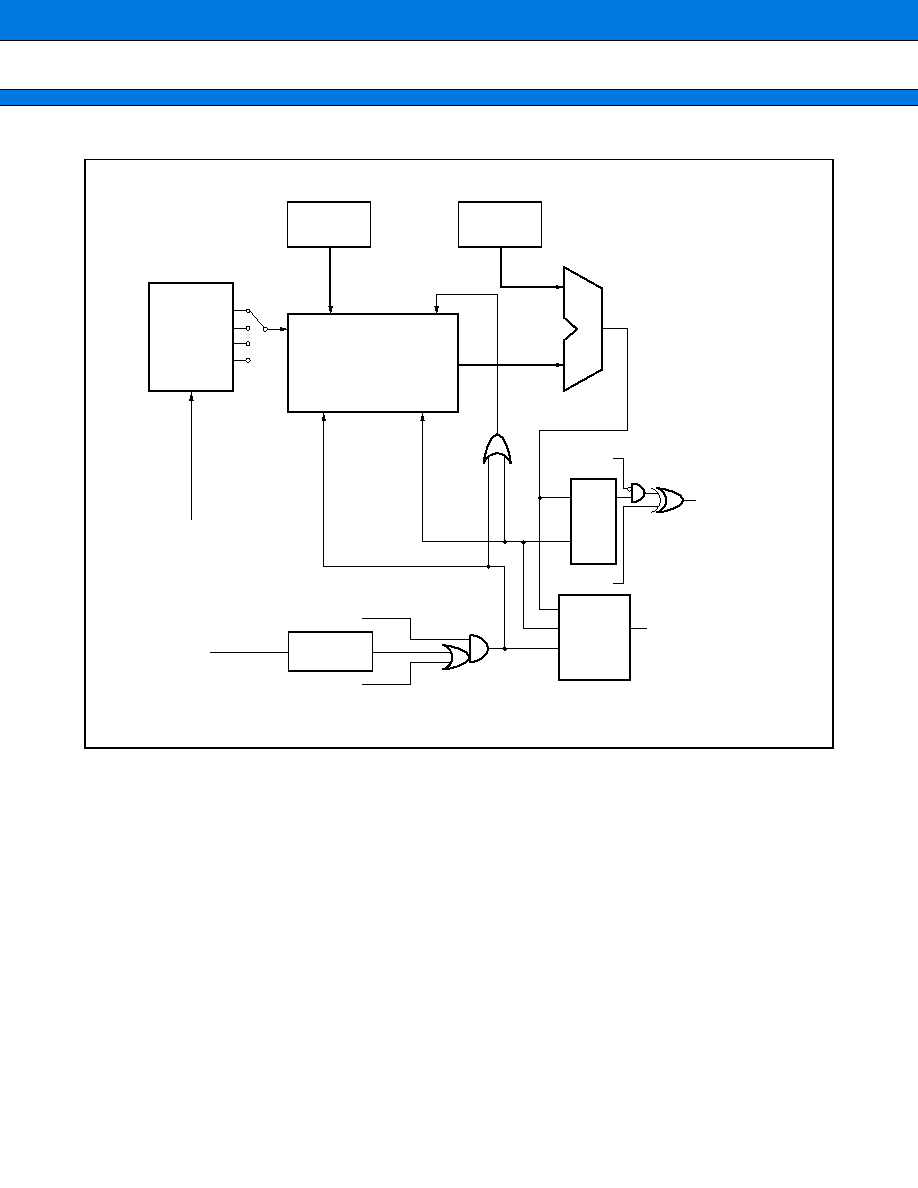

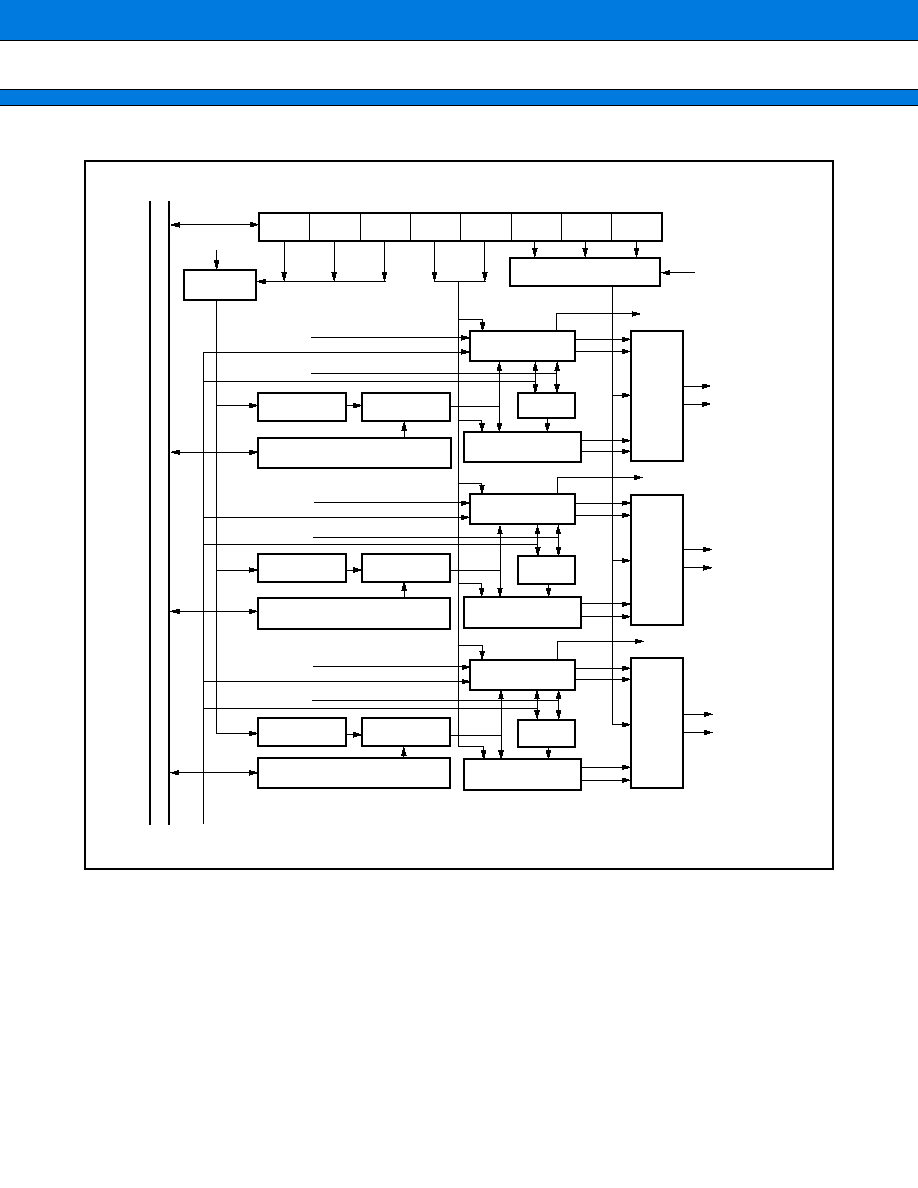

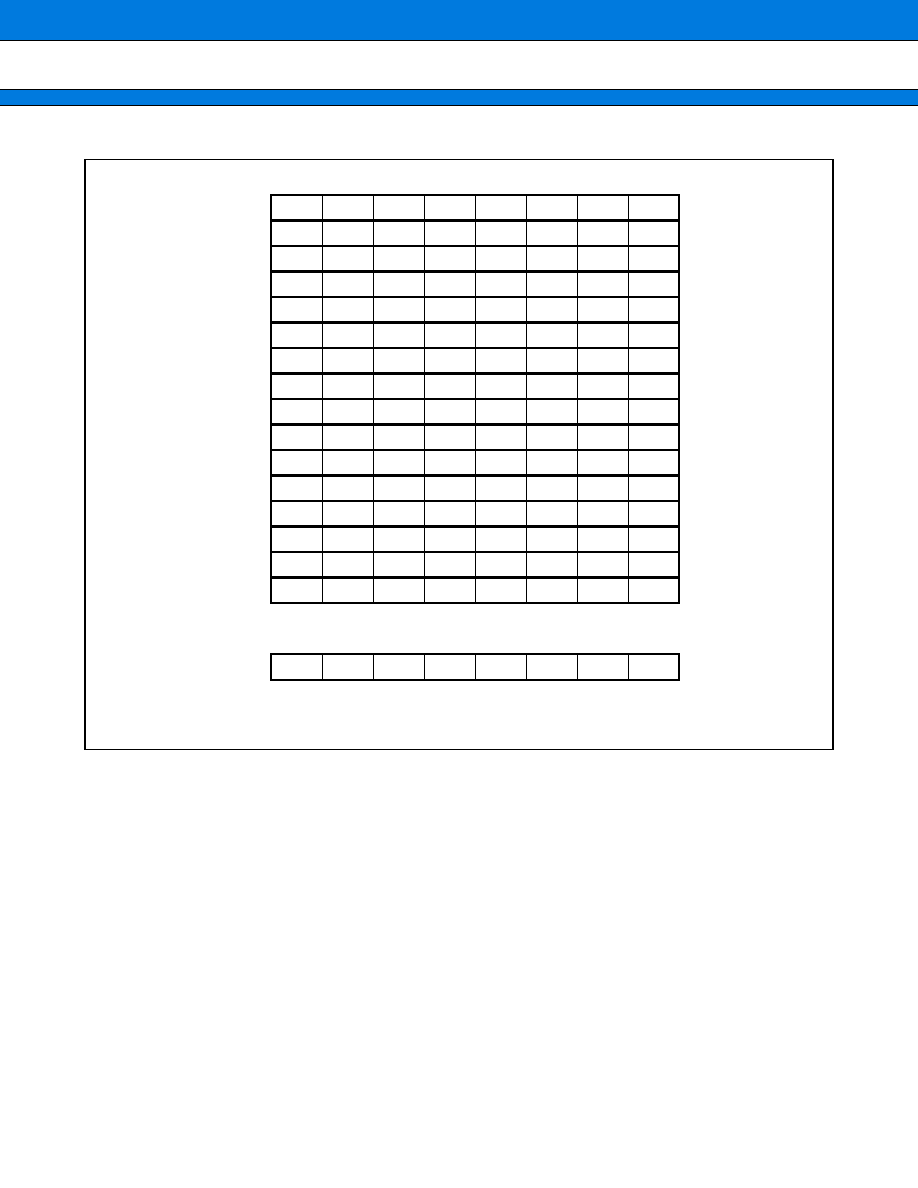

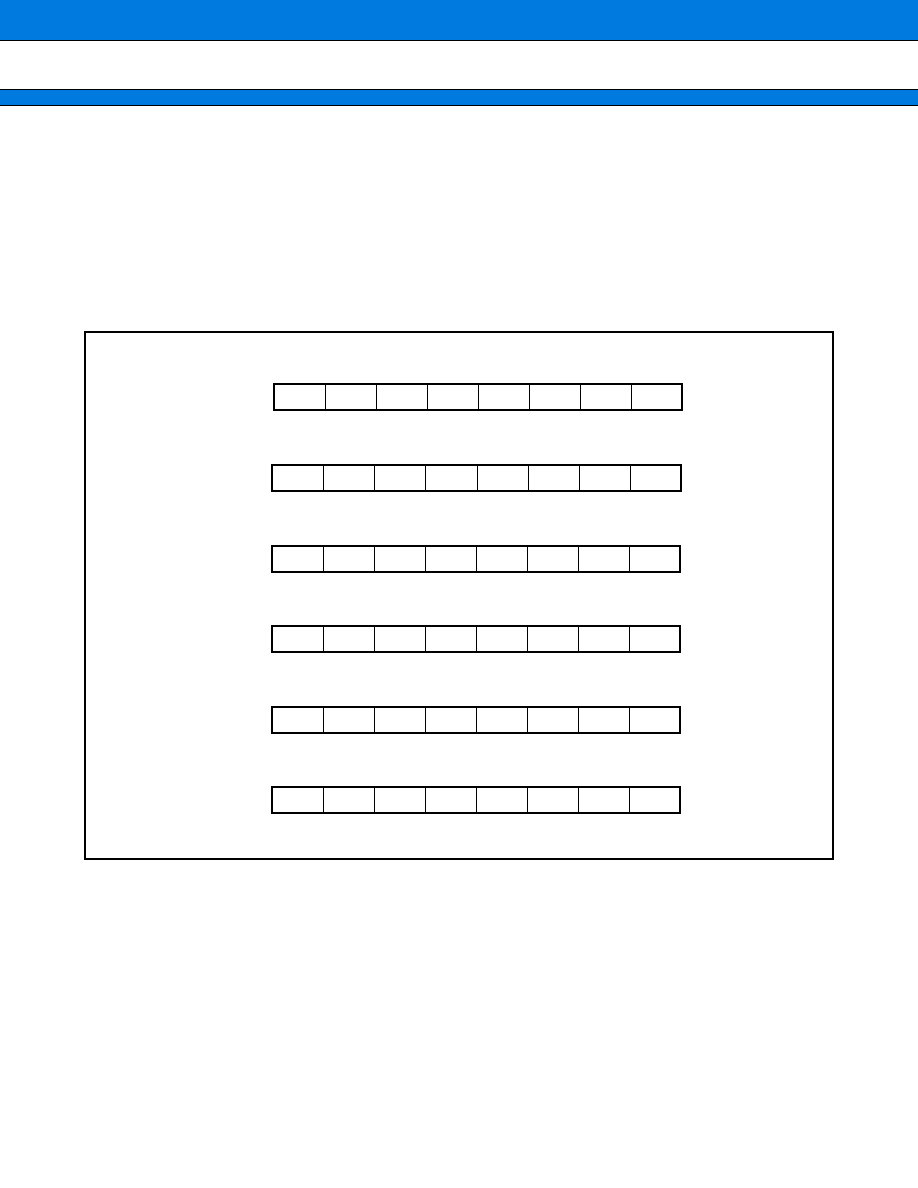

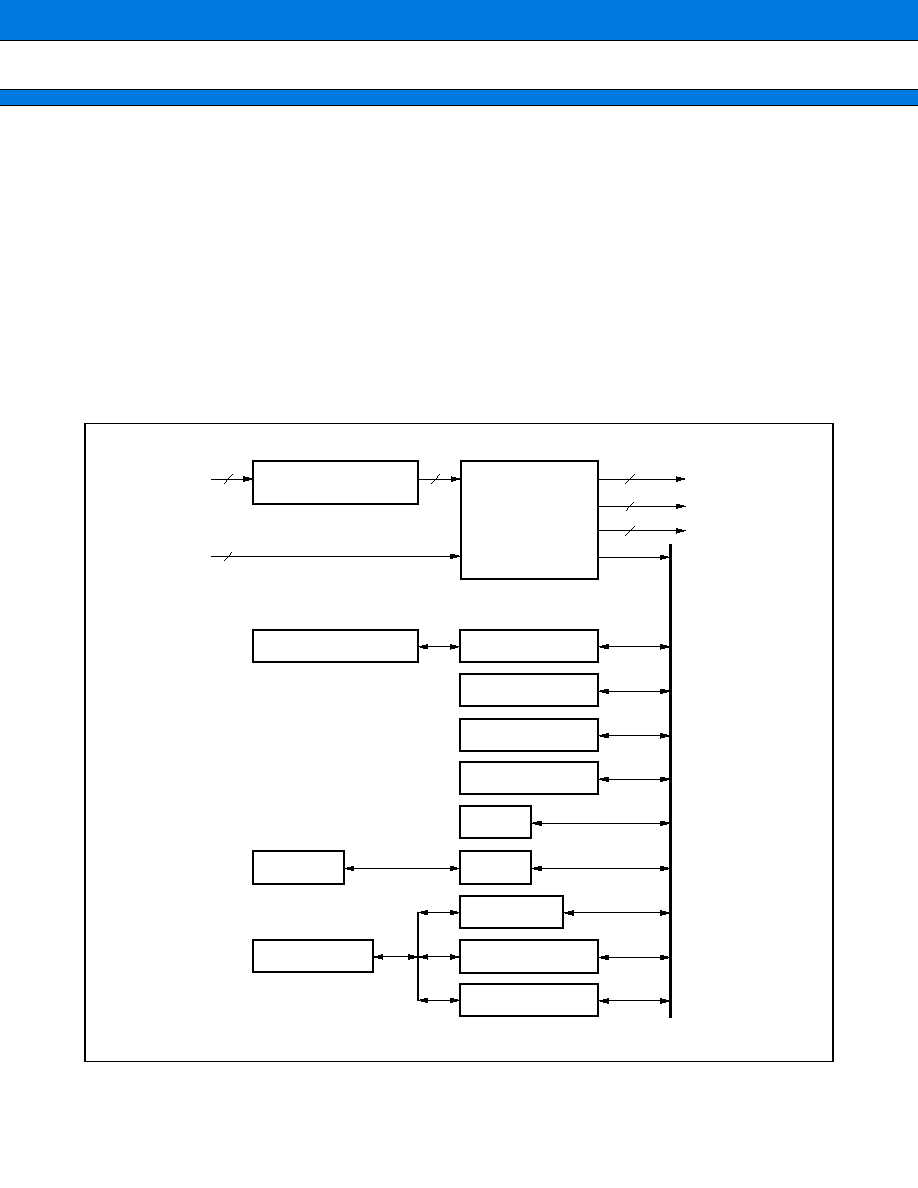

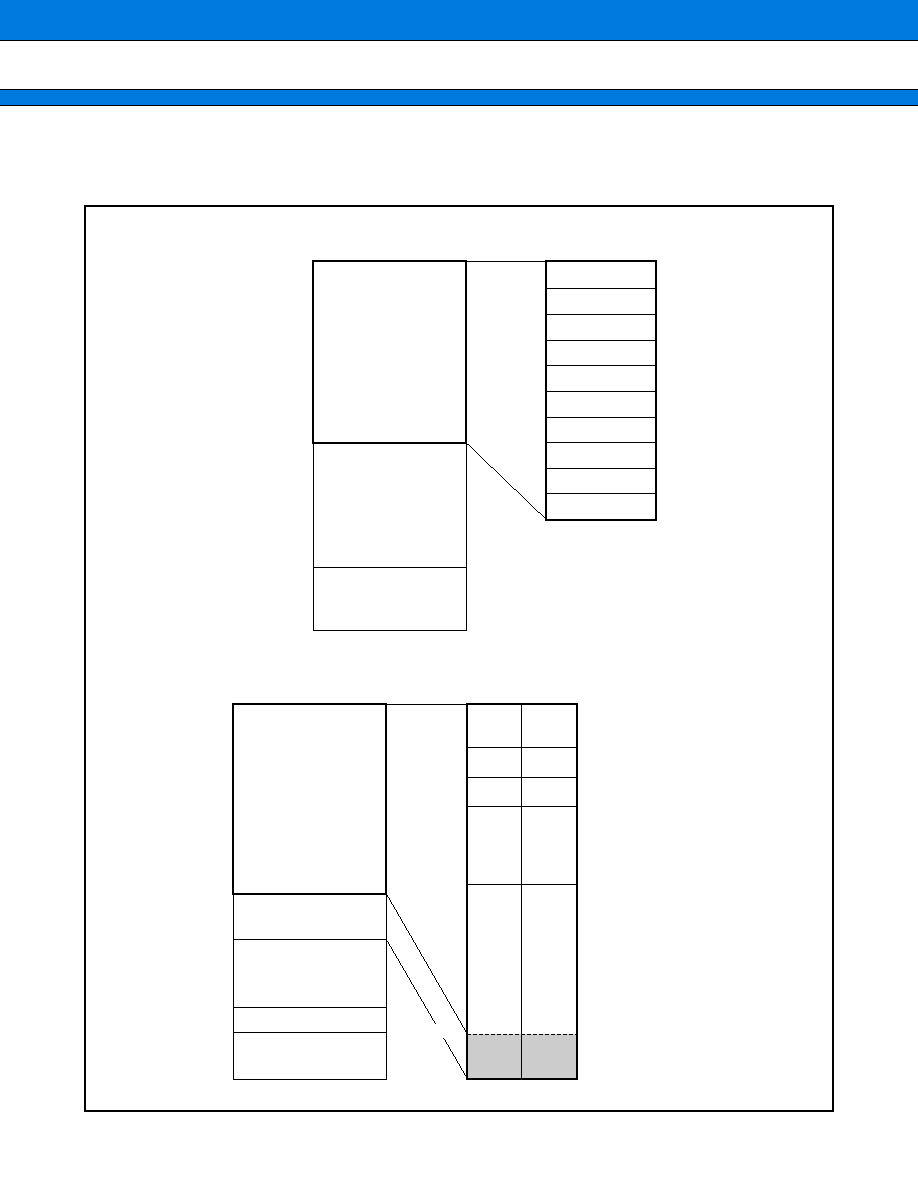

s

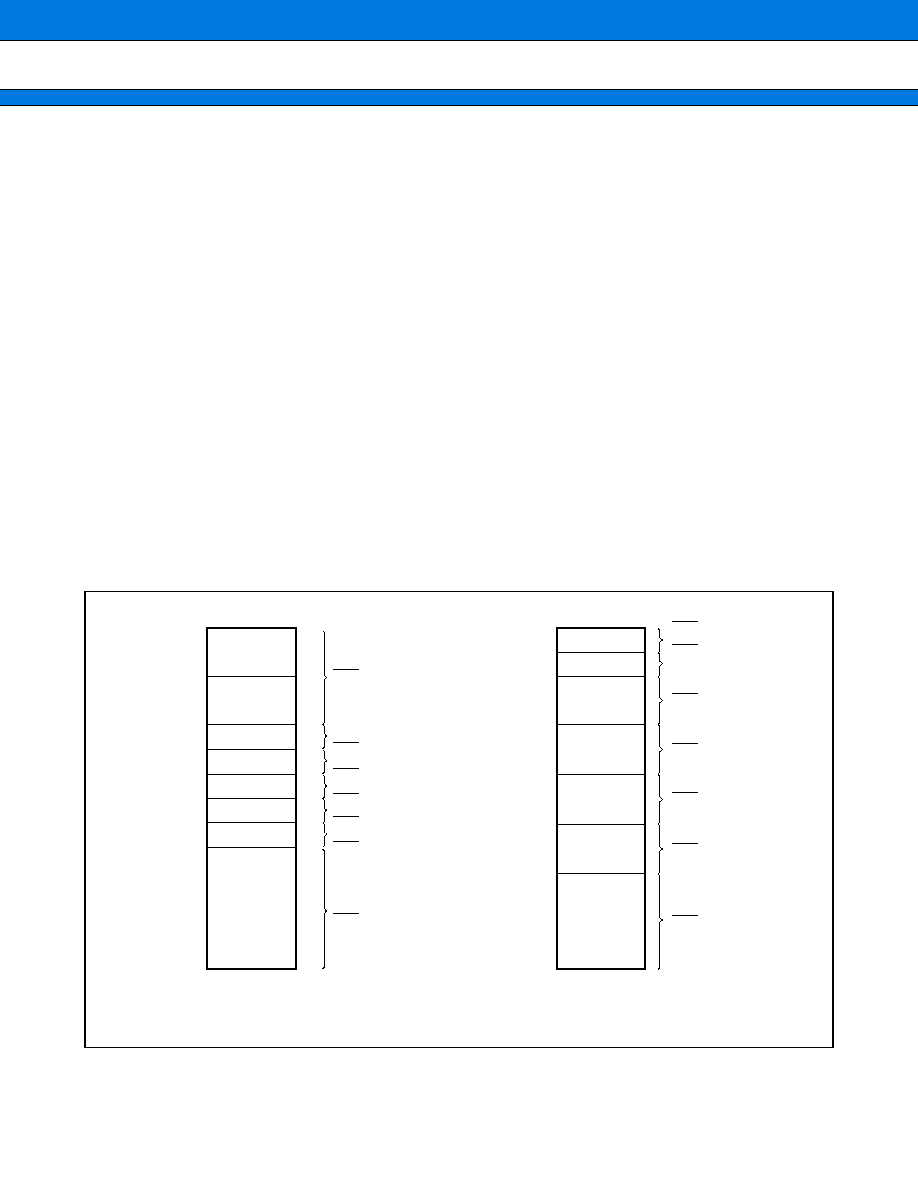

CPU

1.

Memory Space

The FR series has 4 Gbytes (2

32

addresses) of logic address space which the CPU accesses linearly.

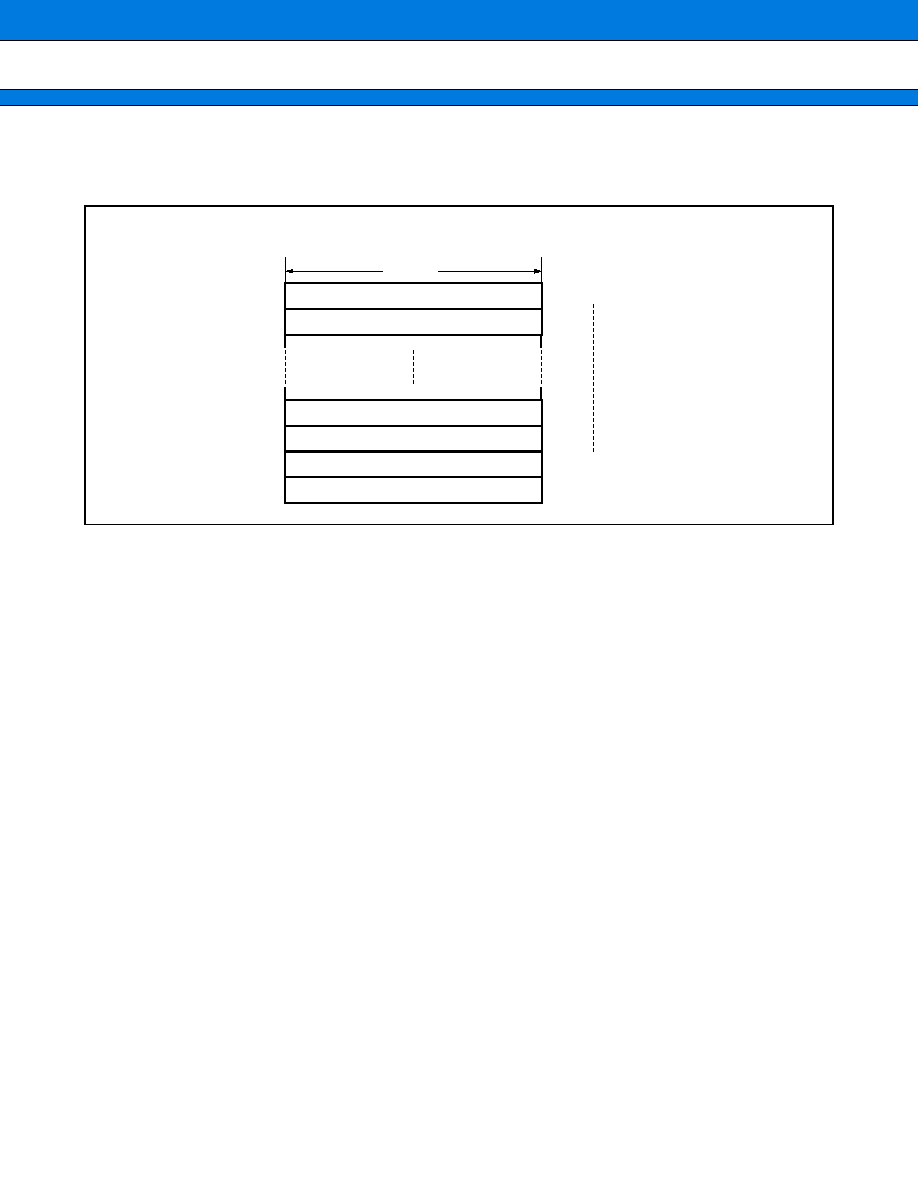

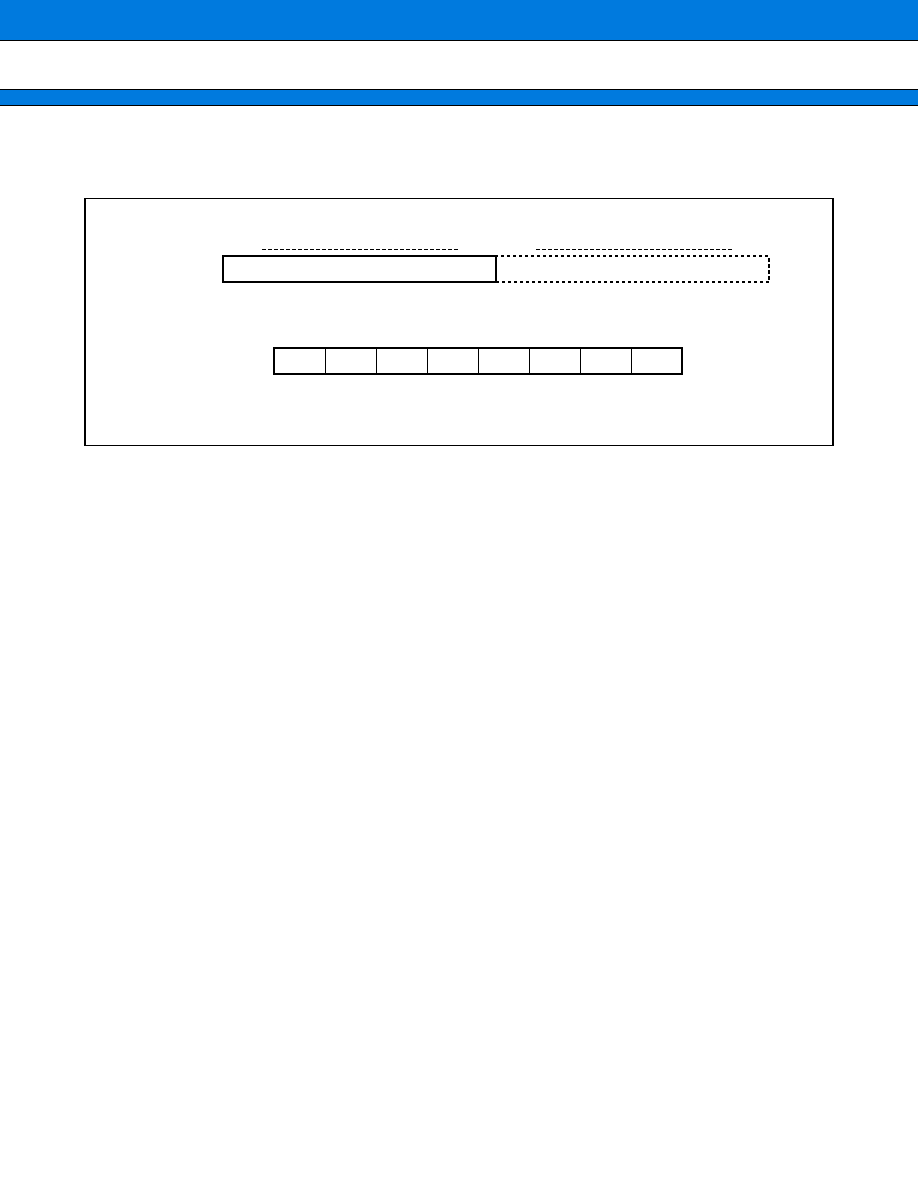

∑ Memory Map

* : It is impossible to access the external area on single-chip mode. When accessing the external area, select the

internal ROM external bus mode.

I/O

I/O

I/O

I/O

I/O

External ROM

external bus mode

Internal ROM

external bus mode

Single-chip mode

I/O

Access is

prohibited

Access is

prohibited

Access is

prohibited

Built-in RAM 6 KB

Built-in RAM 6 KB

Built-in RAM 6 KB

Access is

prohibited

Access is

prohibited

Access is

prohibited

External area

External area

External area

Built-in RAM 2KB

Built-in RAM 2KB

Built-in ROM

254KB

Built-in ROM

254KB

Access is

prohibited

Access is

prohibited

0000 0000

H

0000 0400

H

0000 0800

H

0000 1000

H

0000 2800

H

0001 0000

H

FFFF FFFF

H

010 0000

H

000C 0000

H

000C 0800

H

0001 0000

H

Refer to "I/O MAP"

Direct

Madressing

area

FFFF FFFF

H

MB91133/MB91F133

24

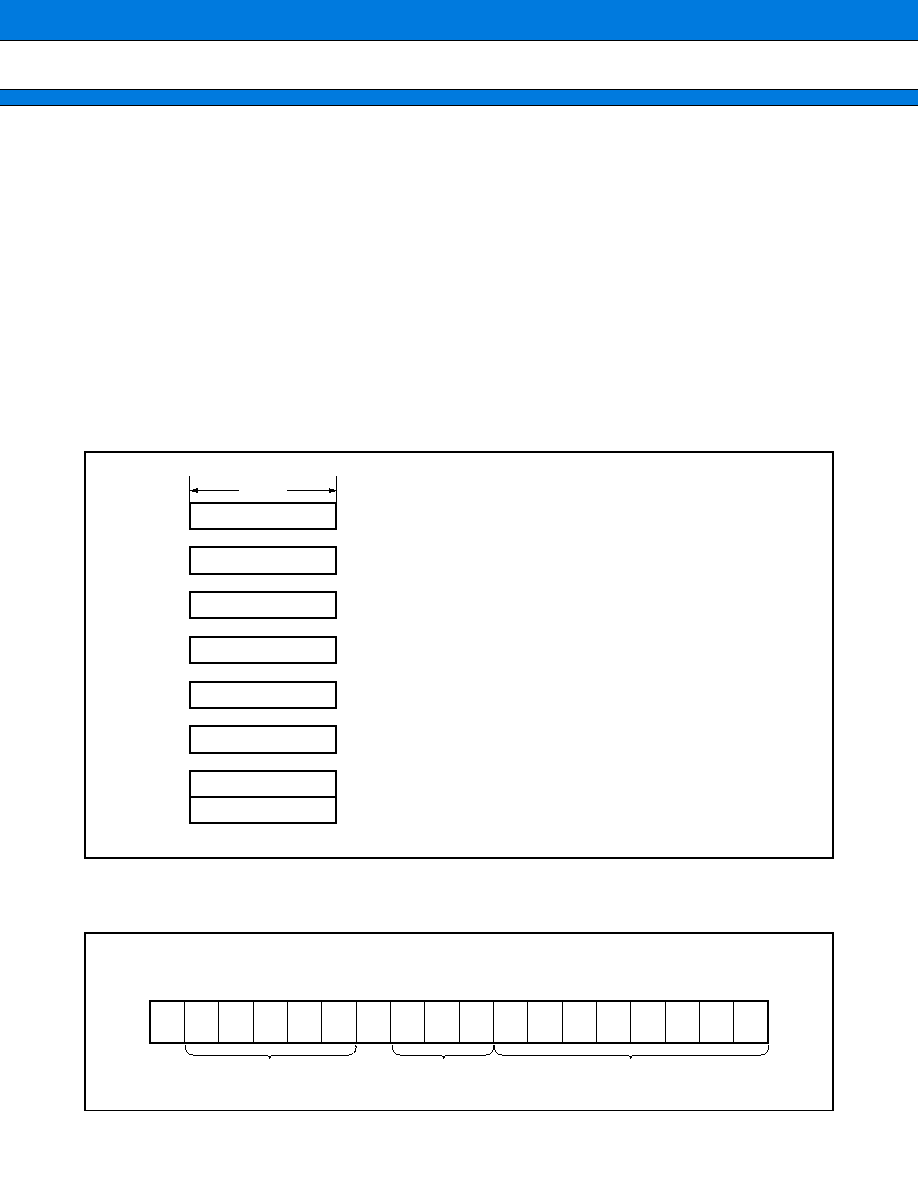

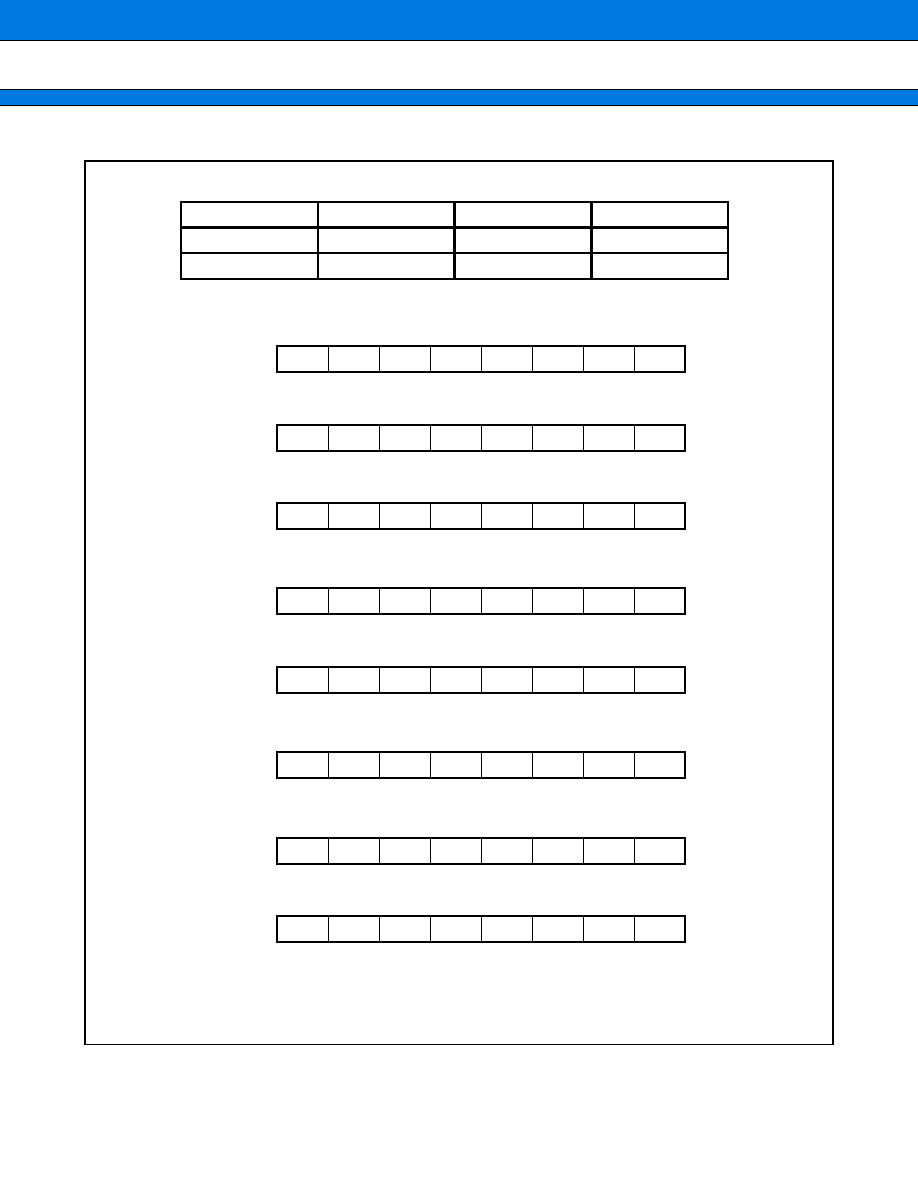

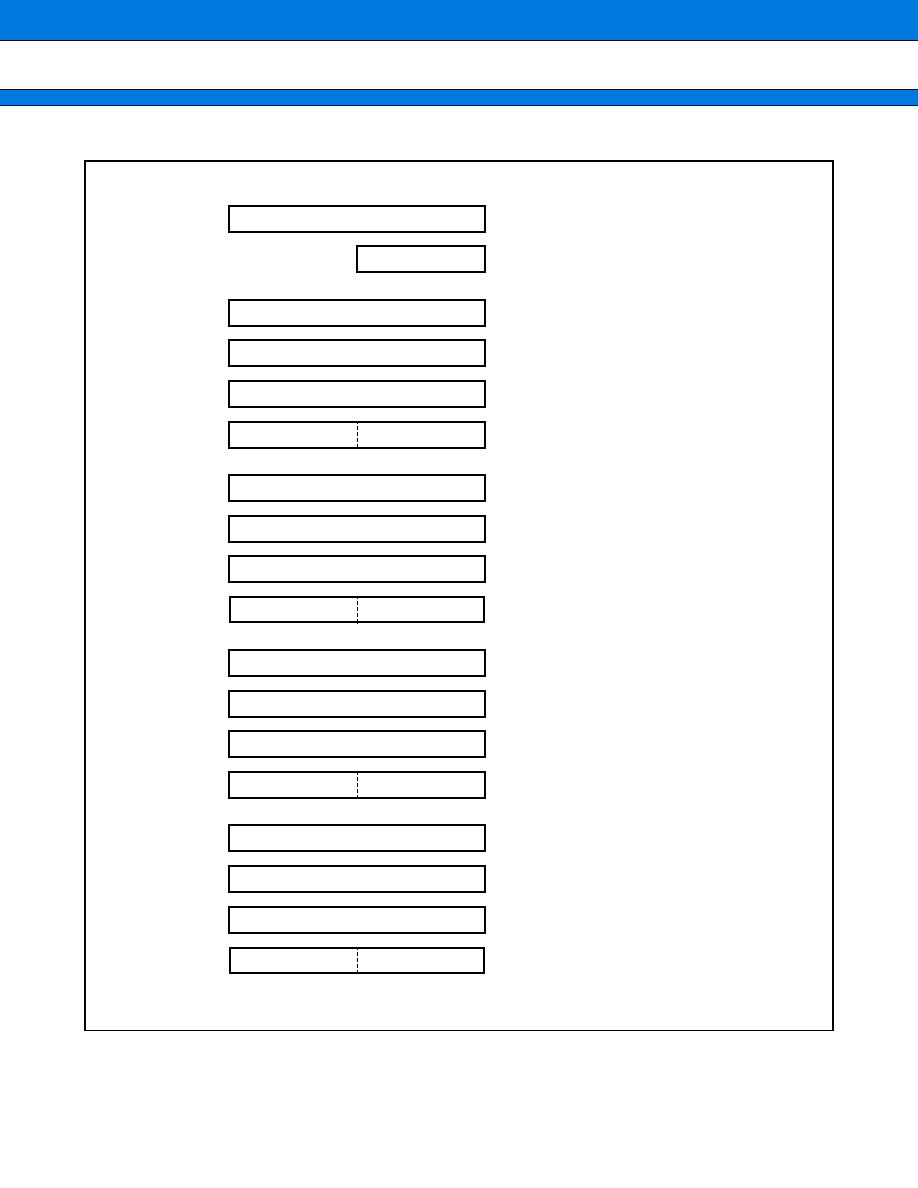

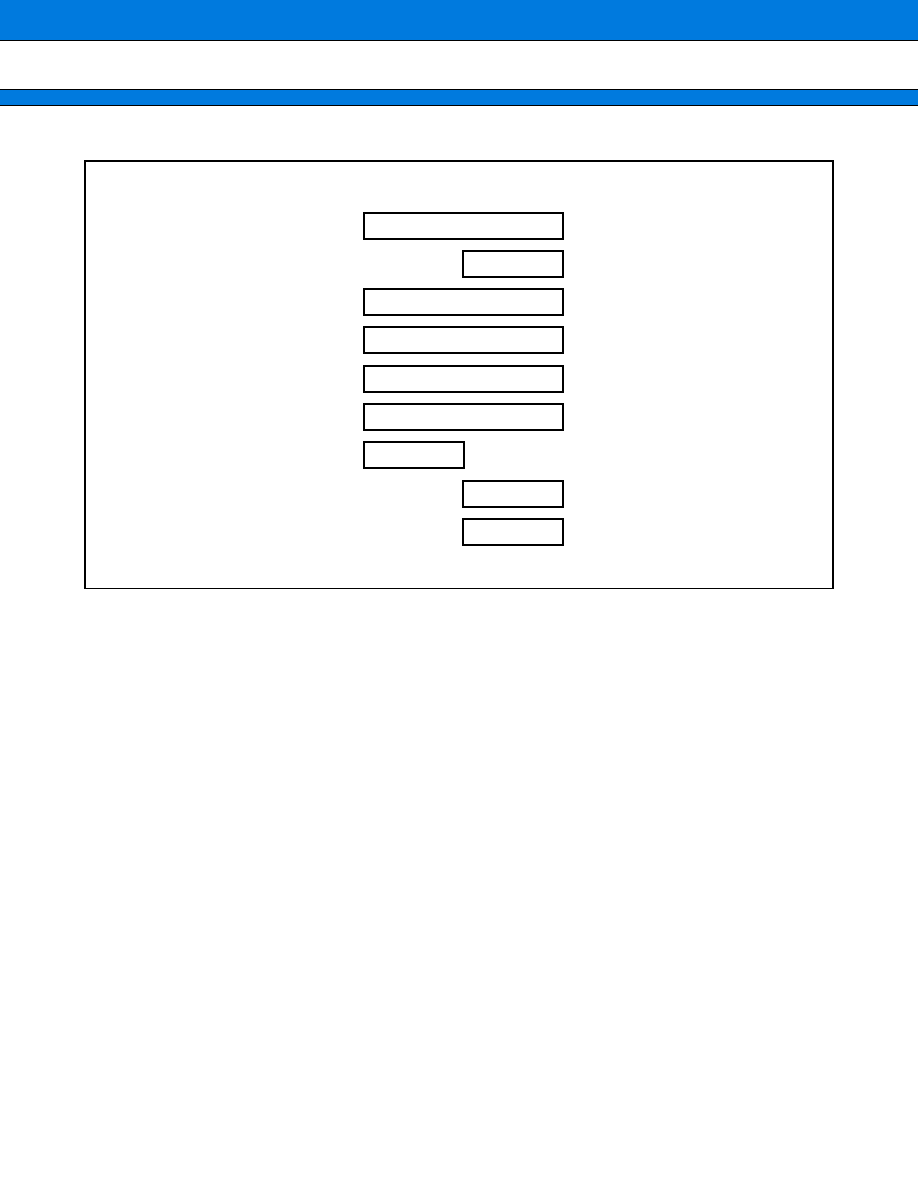

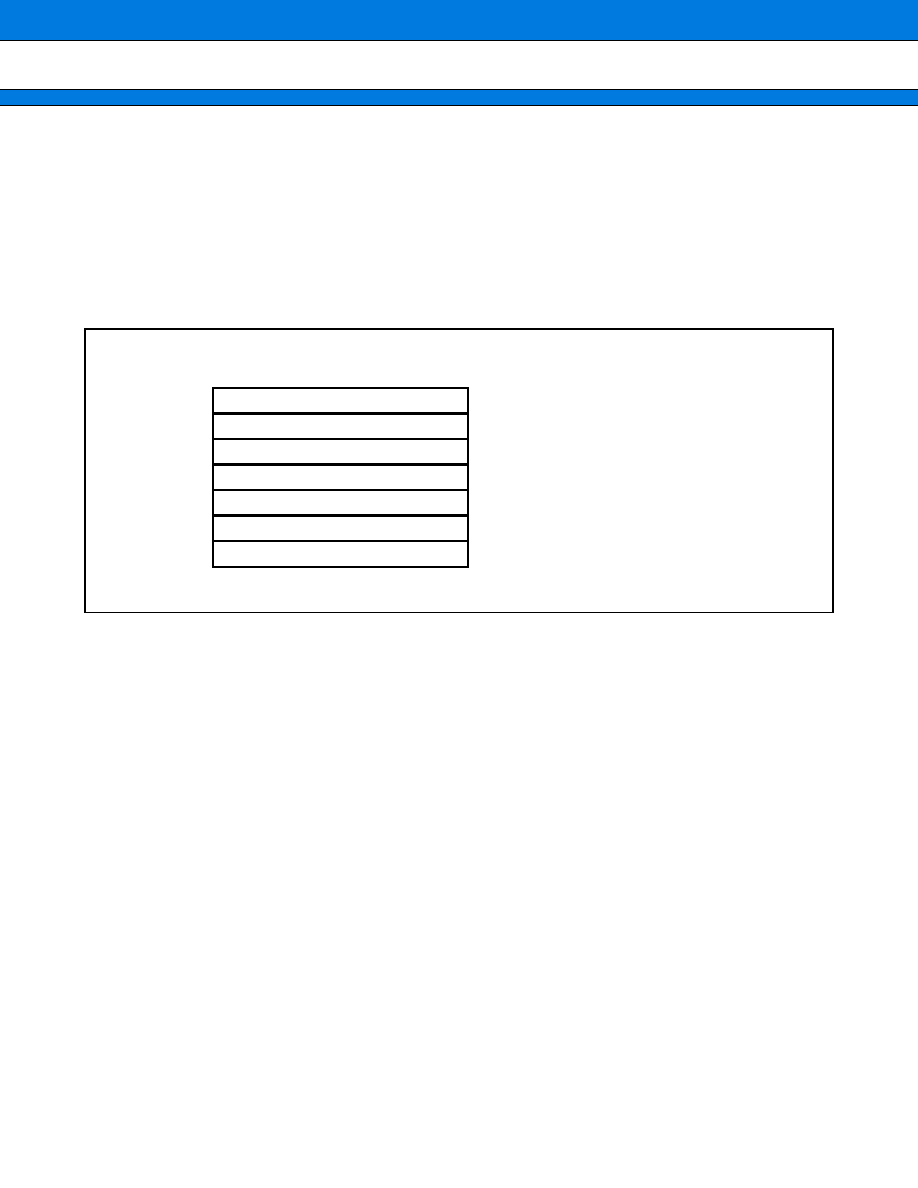

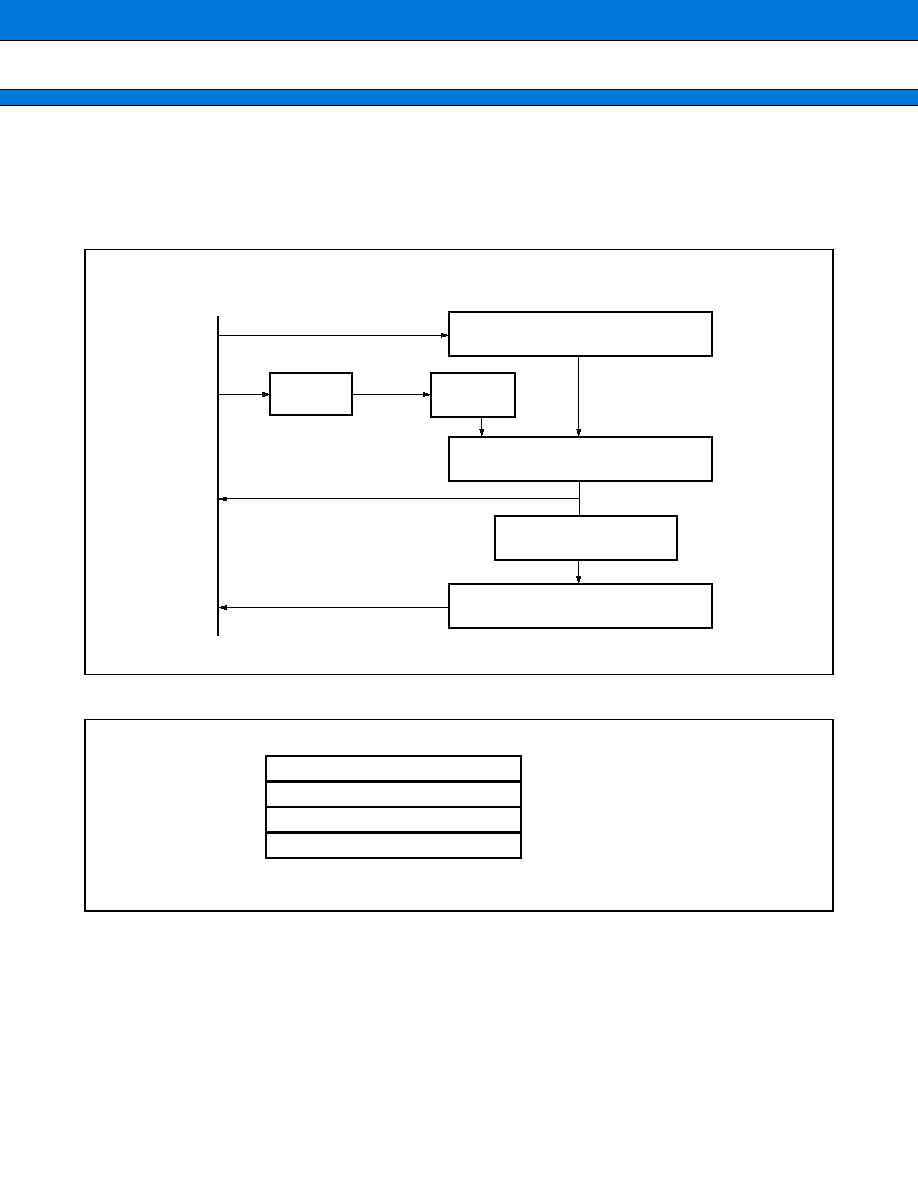

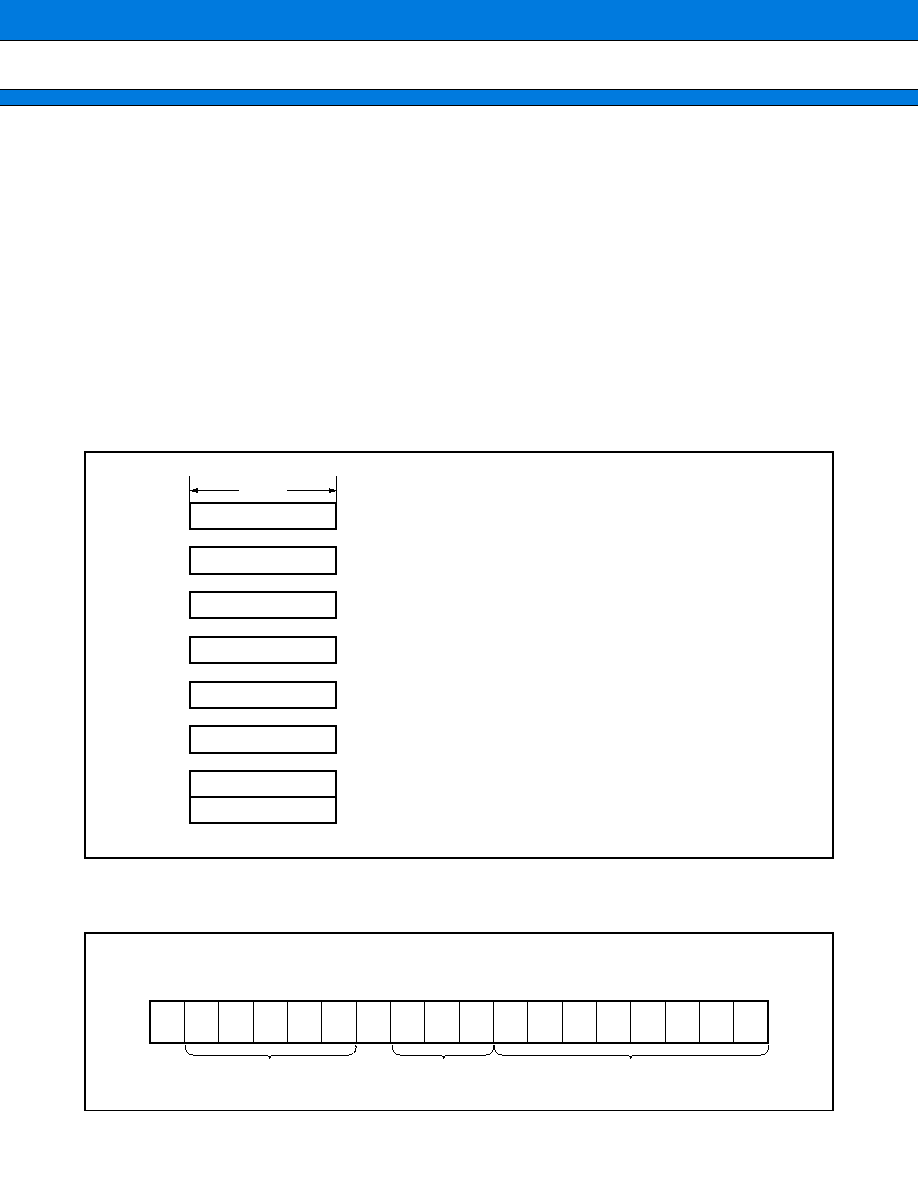

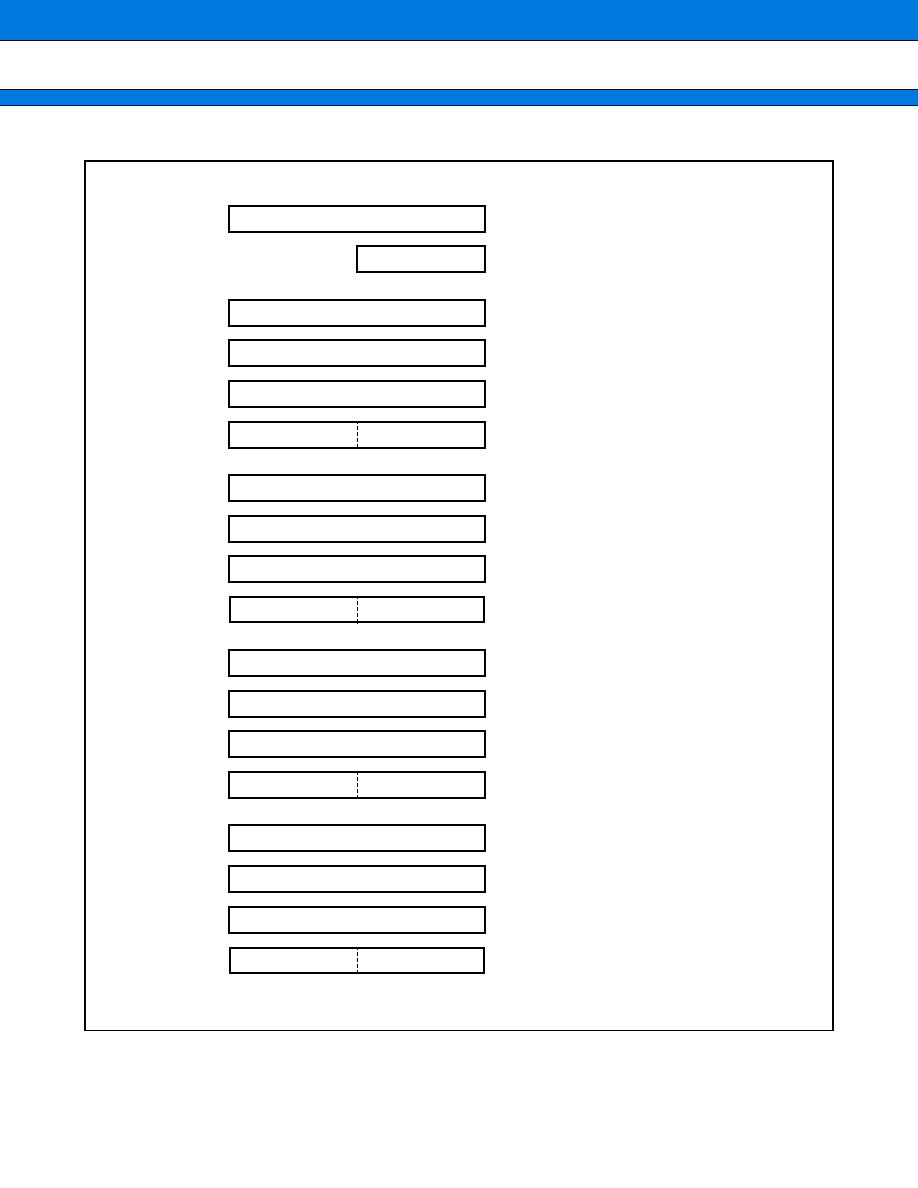

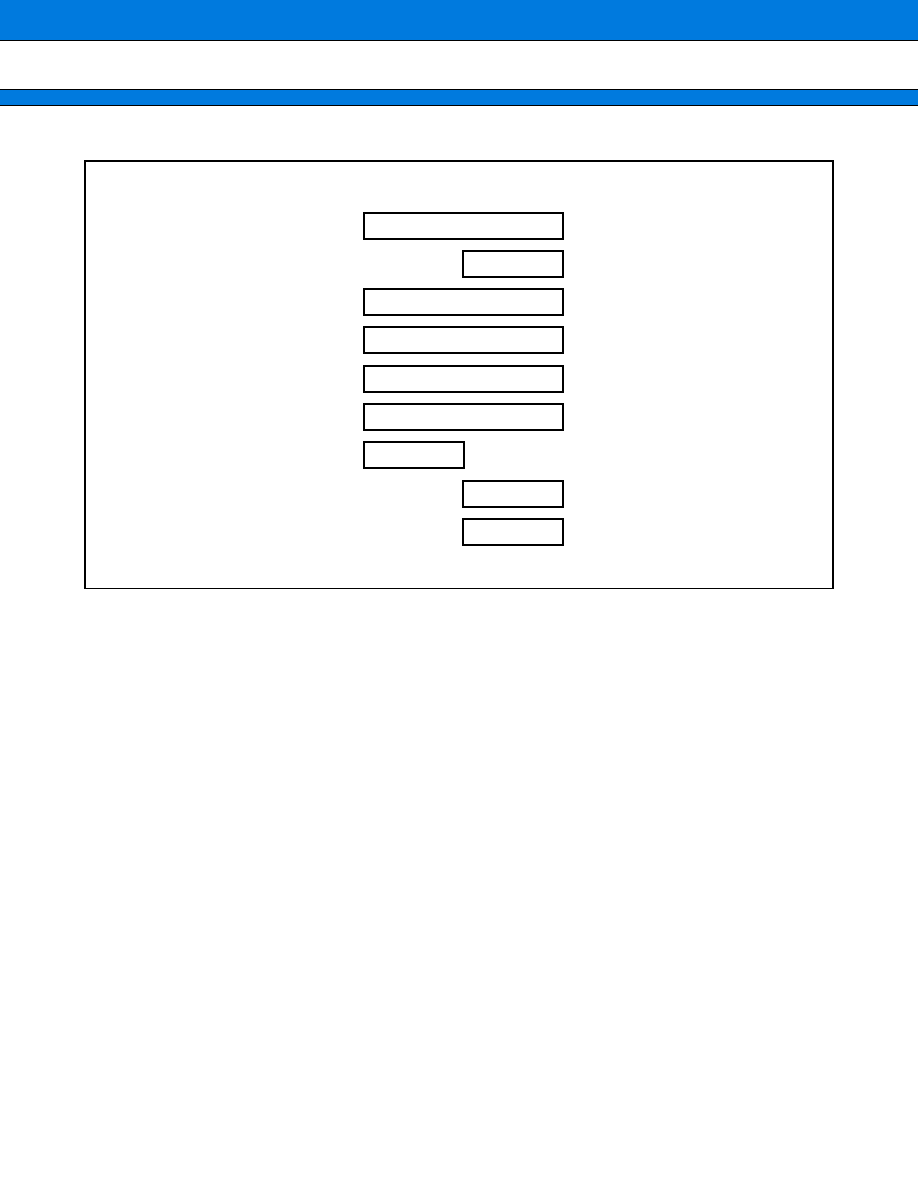

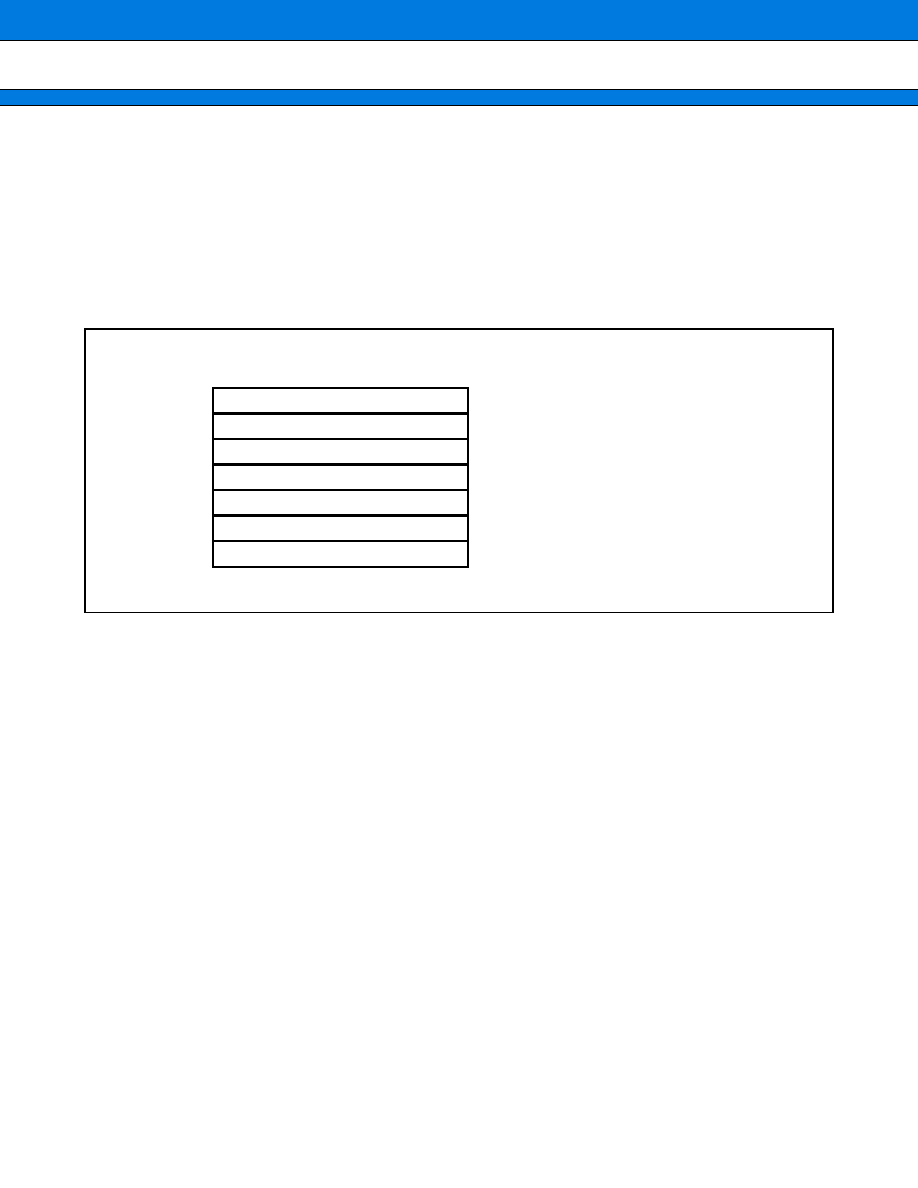

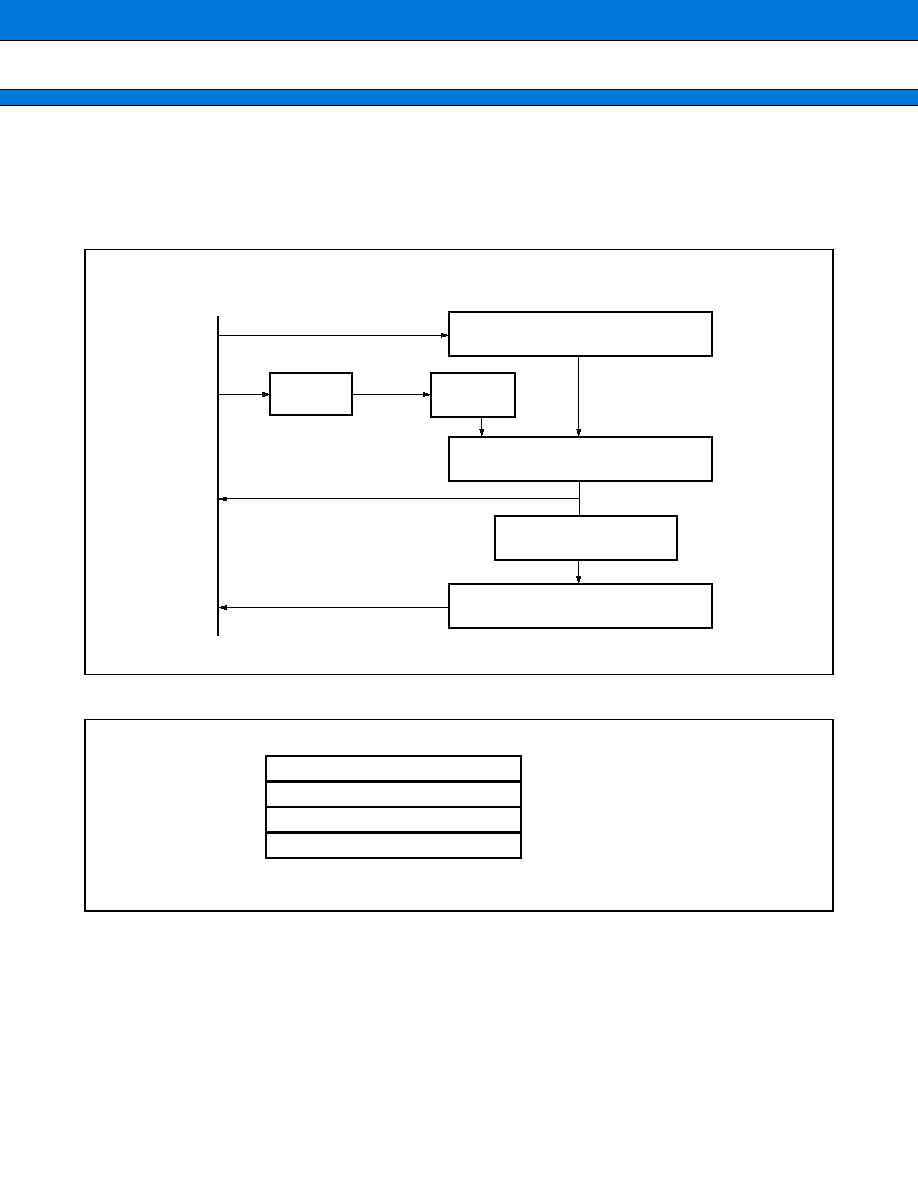

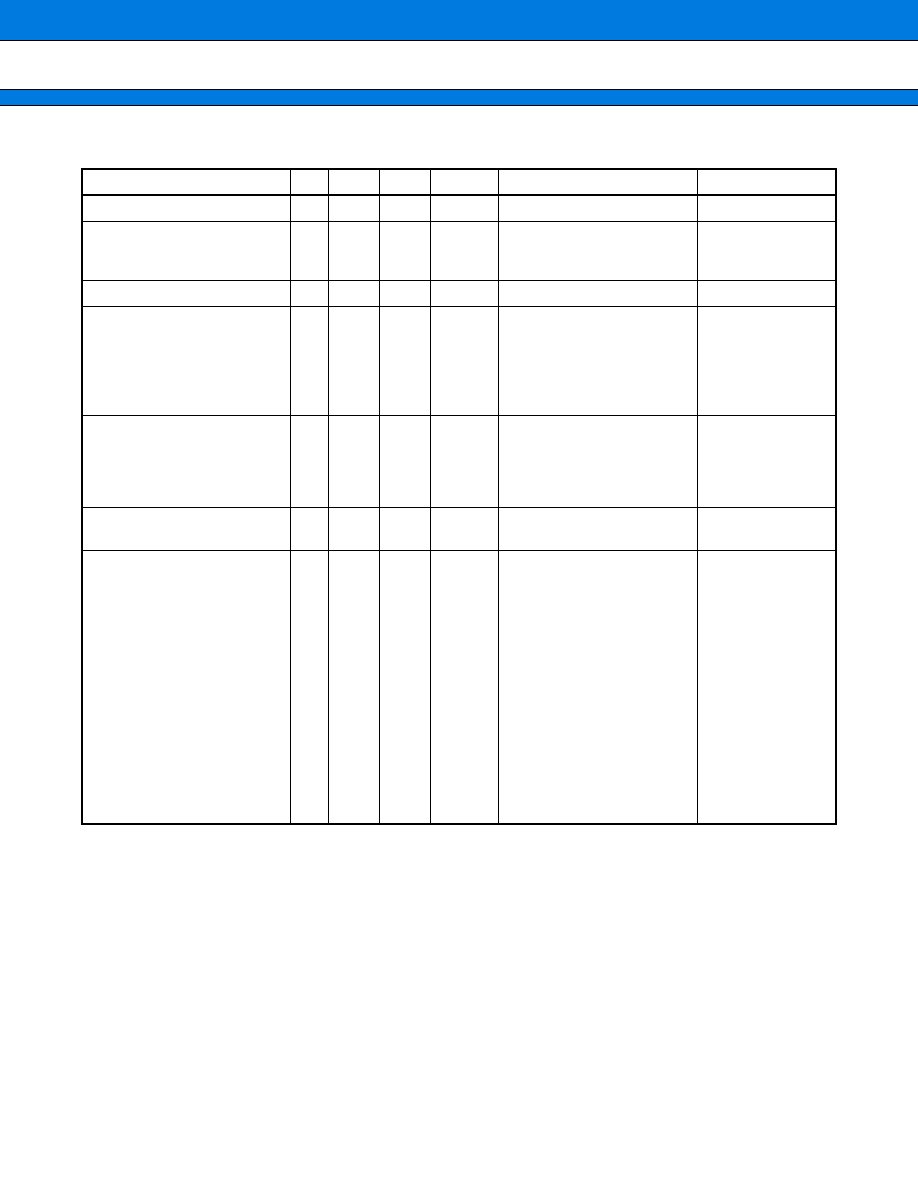

2.

Registers

There are two types of multi-purpose registers in the FR family. One is a dedicated purpose register that exists

within the CPU and the other is a multi-purpose register that exists in the memory.

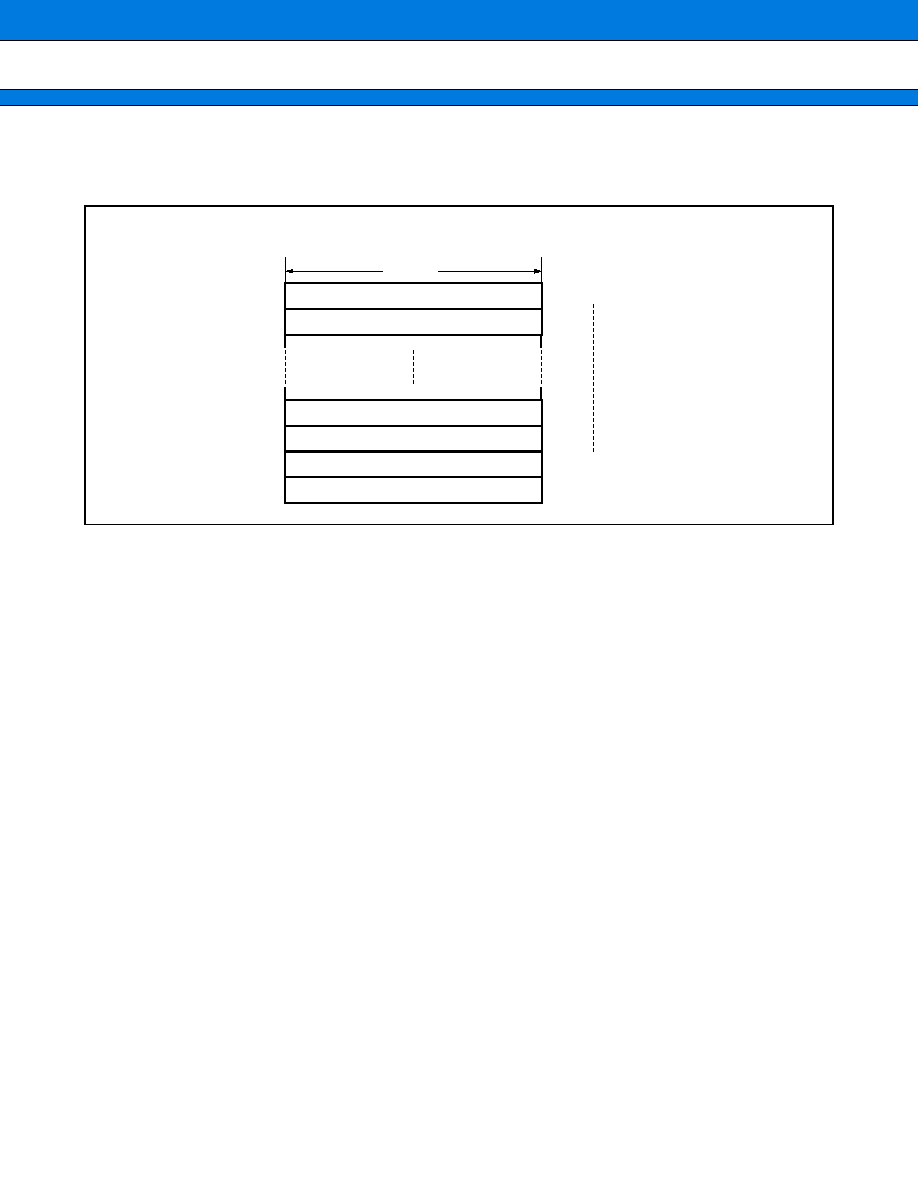

∑ Dedicated Registers

∑ Program Status (PS)

PS is the register that holds the program status and is classified into three categories, namely, Condition Code

Register (CCR) , System Condition Code Register (SCR) and Interruption Level Master Register (ILM) .

Program Counter (PC)

: 32-bit length; indicates instruction storage position.

Program Status (PS)

: 32-bit length; stores register pointers and condition codes.

Table Base Register (TBR)

: Holds the starting address of the vector table to be used for Exception,

Interruption and Trapping (EIT) .

Return Pointer (RP)

: Holds the address to return to from the sub-routine.

System Stuck Pointer (SSP) : Indicates the system stuck position.

User Stuck Pointer (USP)

: Indicates the user's stuck position.

Multiplication and Division

Results Resister (MDH/MDL) : 32-bit length; act as registers for multiplication and division.

PC

PS

TBR

RP

SSP

USP

MDH

MDL

XXXX XXXX

H

Initial values

XXXX XXXX

H

XXXX XXXX

H

XXXX XXXX

H

XXXX XXXX

H

(Undecided)

(Undecided)

(Undecided)

(Undecided)

(Undecided)

0000 0000

H

000F FC00

H

Program Counter

Return Pointer

User Stuck Pointer

Program Status

Multiplication and

Division Results Resister

System Stuck Pointer

Table Base Register

32 bit

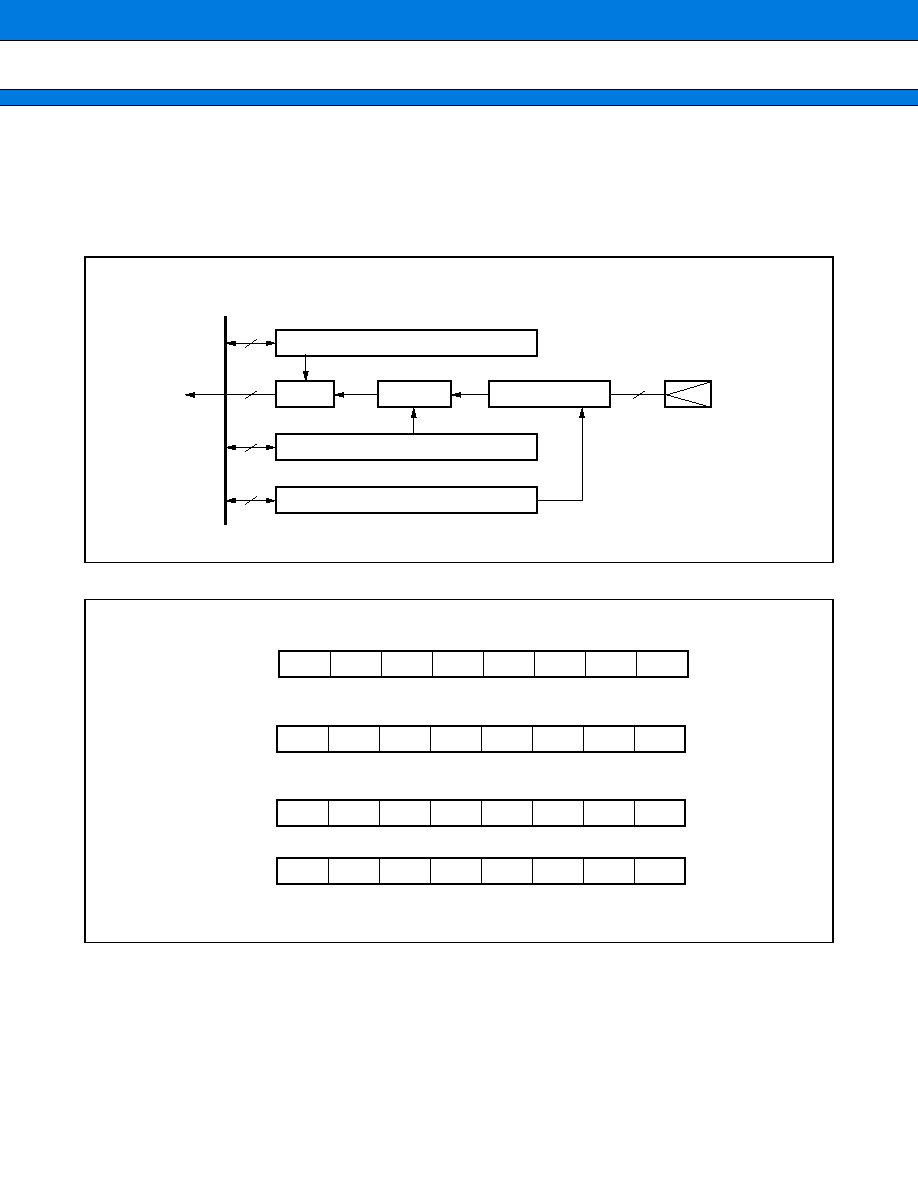

PS

ILM4 ILM3 ILM2

ILM

SCR

CCR

ILM1 ILM0

D1

D0

T

S

I

N

Z

V

C

0

1

2

3

4

5

6

7

8

9

10

16

17

18

19

20

31

MB91133/MB91F133

25

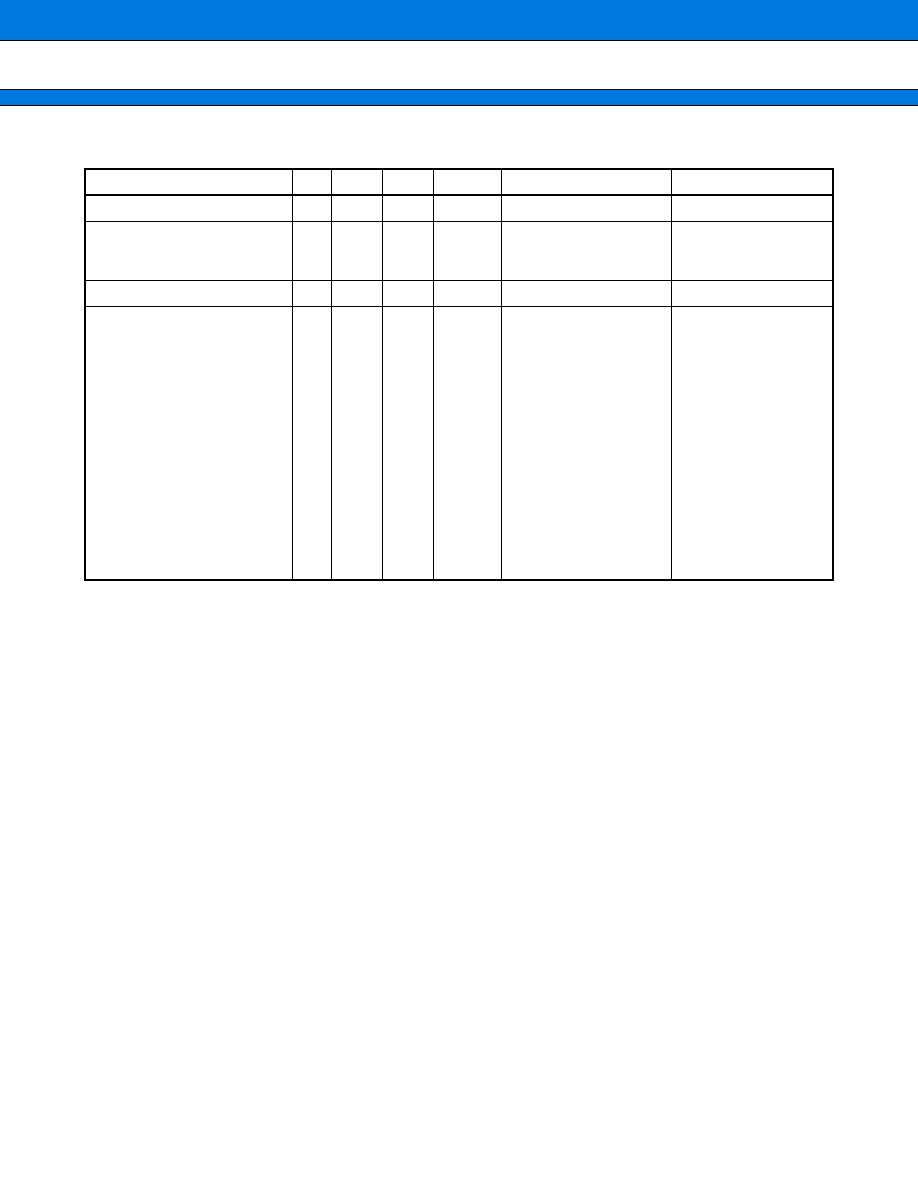

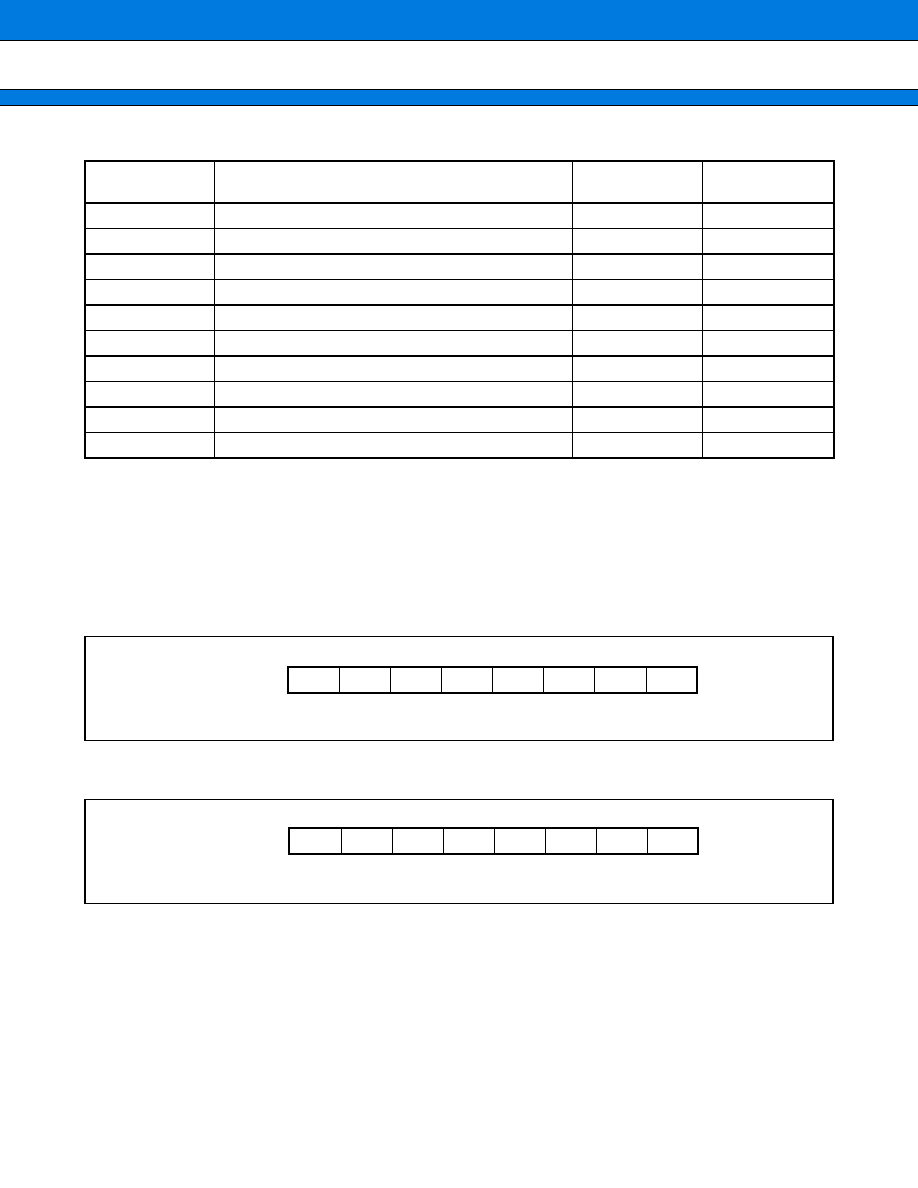

∑ Condition Code Register (CCR)

∑ System Condition Code Register (SCR)

∑ Interruption Level Mask Register (ILM)

S flag : Specifies the stuck pointer to be used as R15.

I flag

: Controls permission and prohibition of user interruption requests.

N flag : Indicates codes when computation results are defined as integers that are expressed in comple-

ments of 2.

Z flag : Indicates whether or not a result of the computation is "0" .

V flag : Operands used for computation are defined as integers expressed in complements of 2, and indi-

cate whether or not an overflow is generated as a result of the computation.

C flag : Indicates whether carrying or borrowing is generated from the highest bit as a result of the compu-

tation.

T flag : Specifies whether or not the step trace trap will be valid.

ILM4 to ILM0 : Holds the interruption level mask values, and those values that are held by the ILM are used

for the level mask. Interruption requests can be accepted only when the interruption levels

handled within the interruption requests to be input into the CPU are stronger than the levels

shown by the ILM.

ILM4

ILM3

ILM2

ILM1

ILM0

Interruption level

Strength

0

0

0

0

0

0

Strong

0

1

0

0

0

15

1

1

1

1

1

31

Weak

MB91133/MB91F133

26

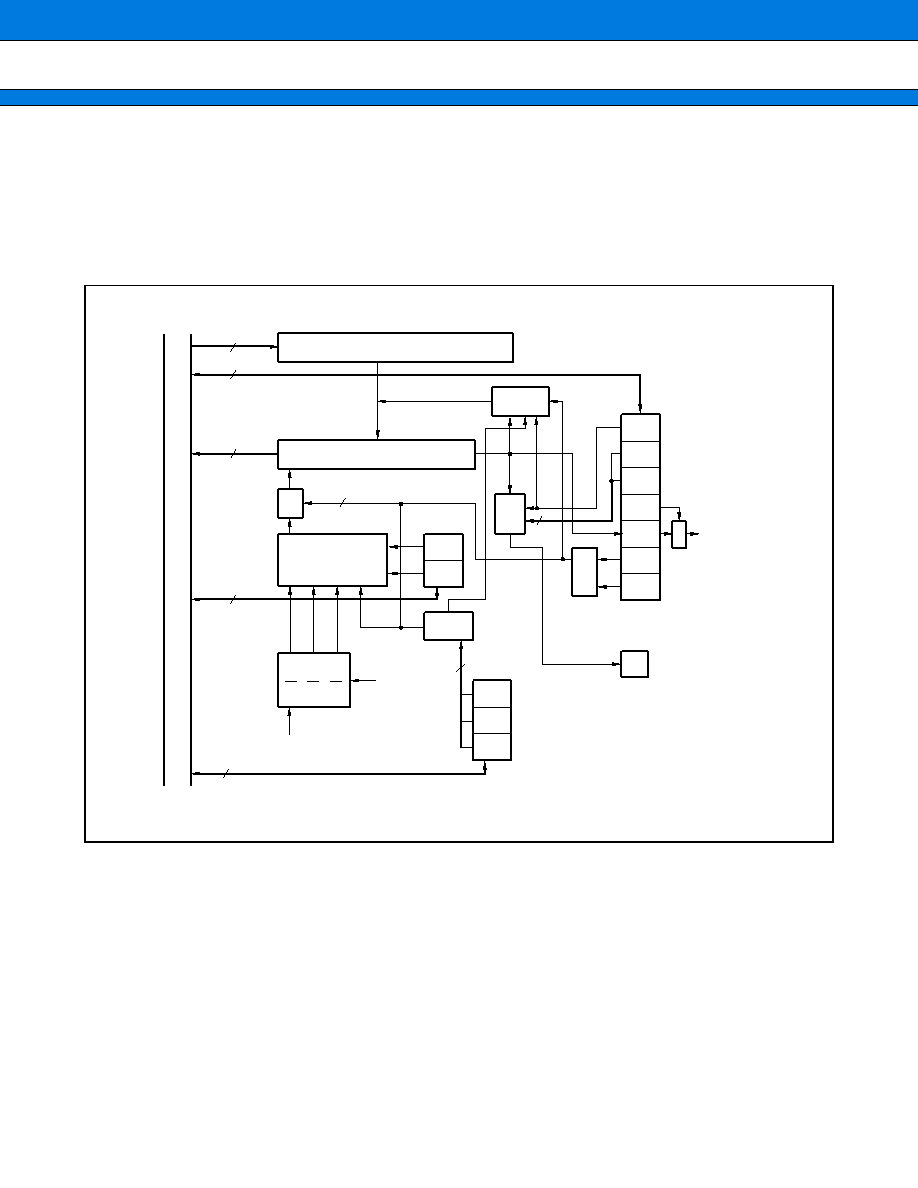

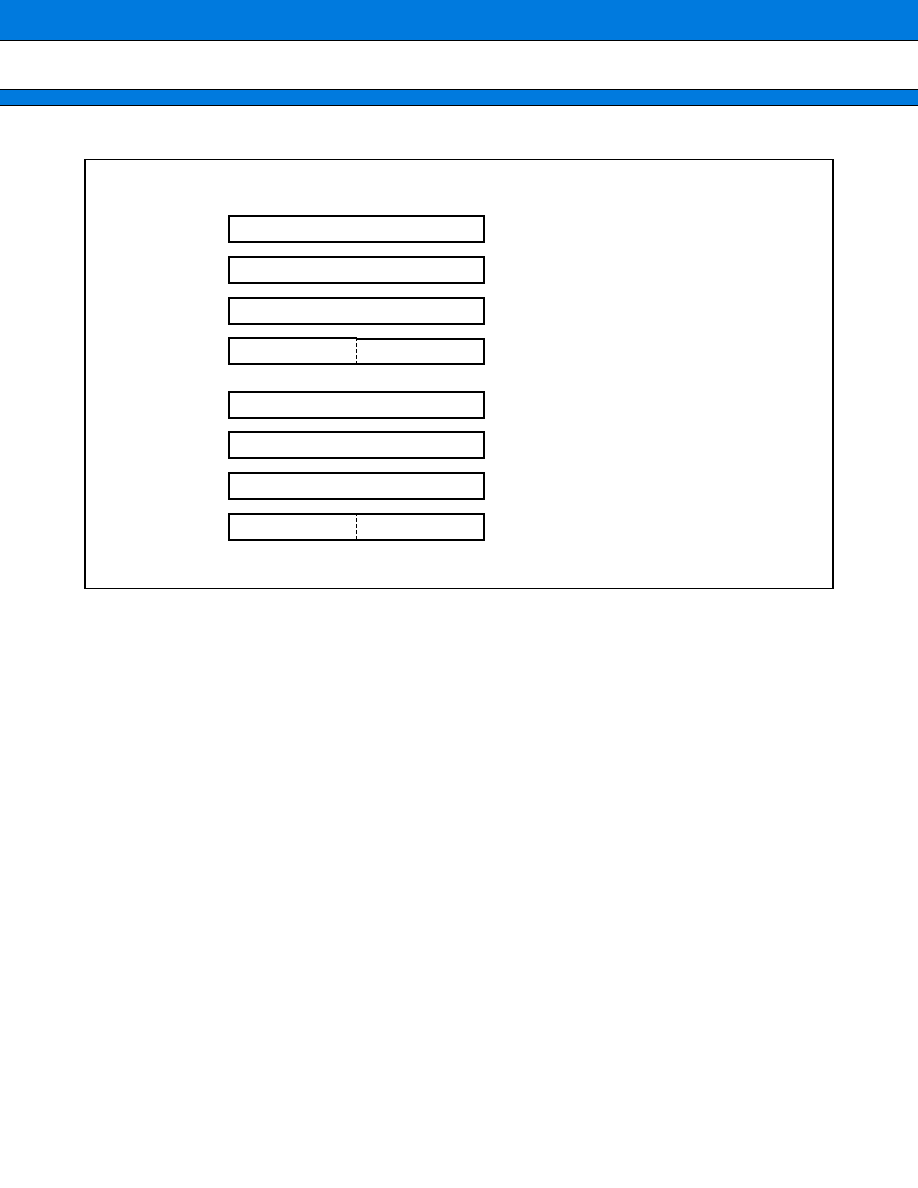

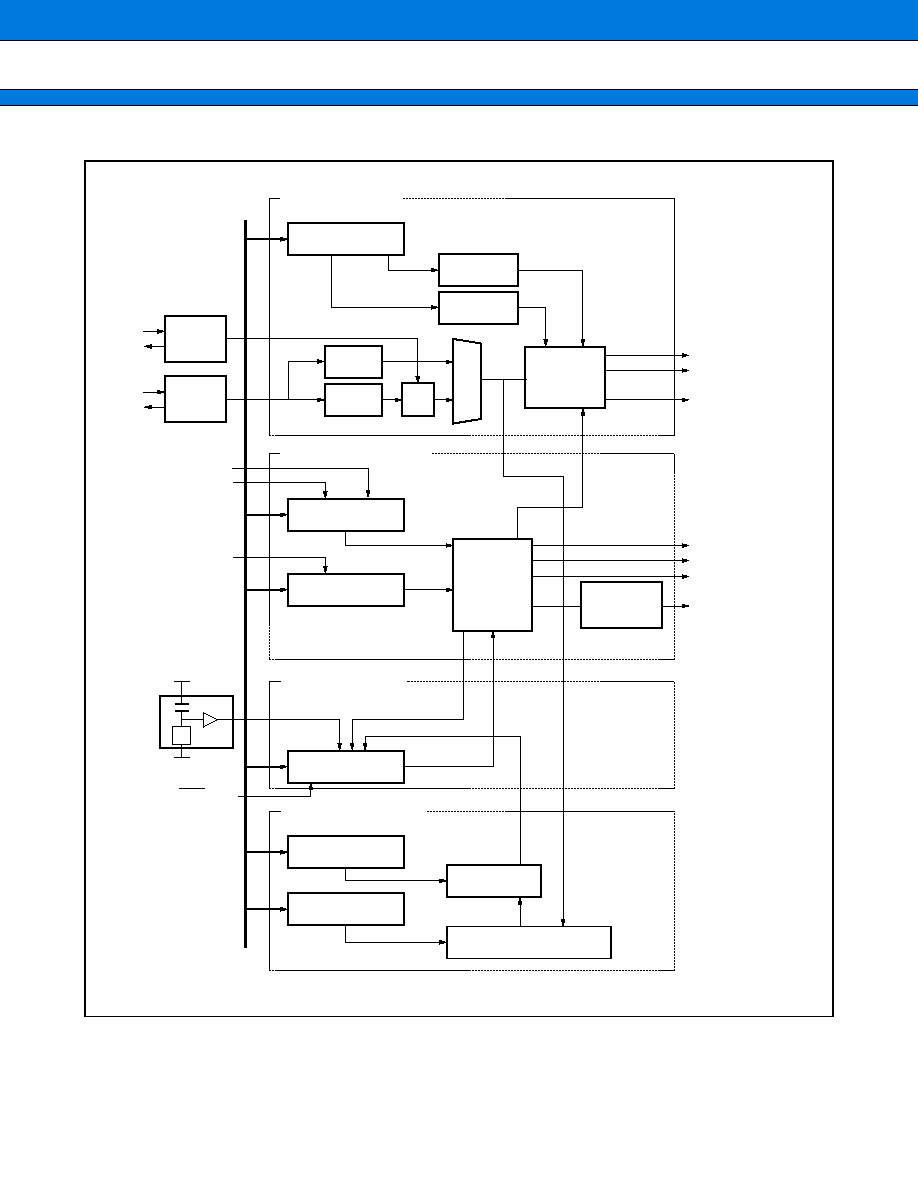

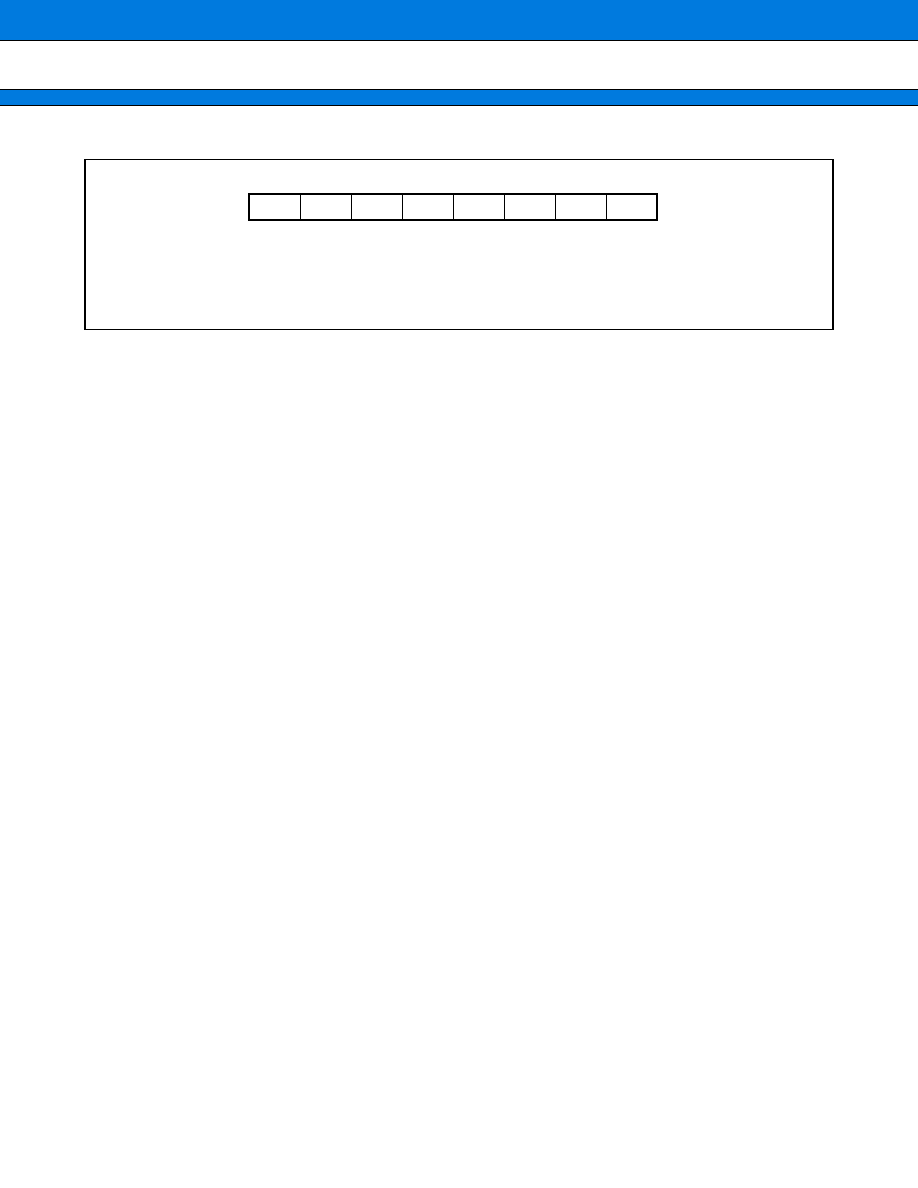

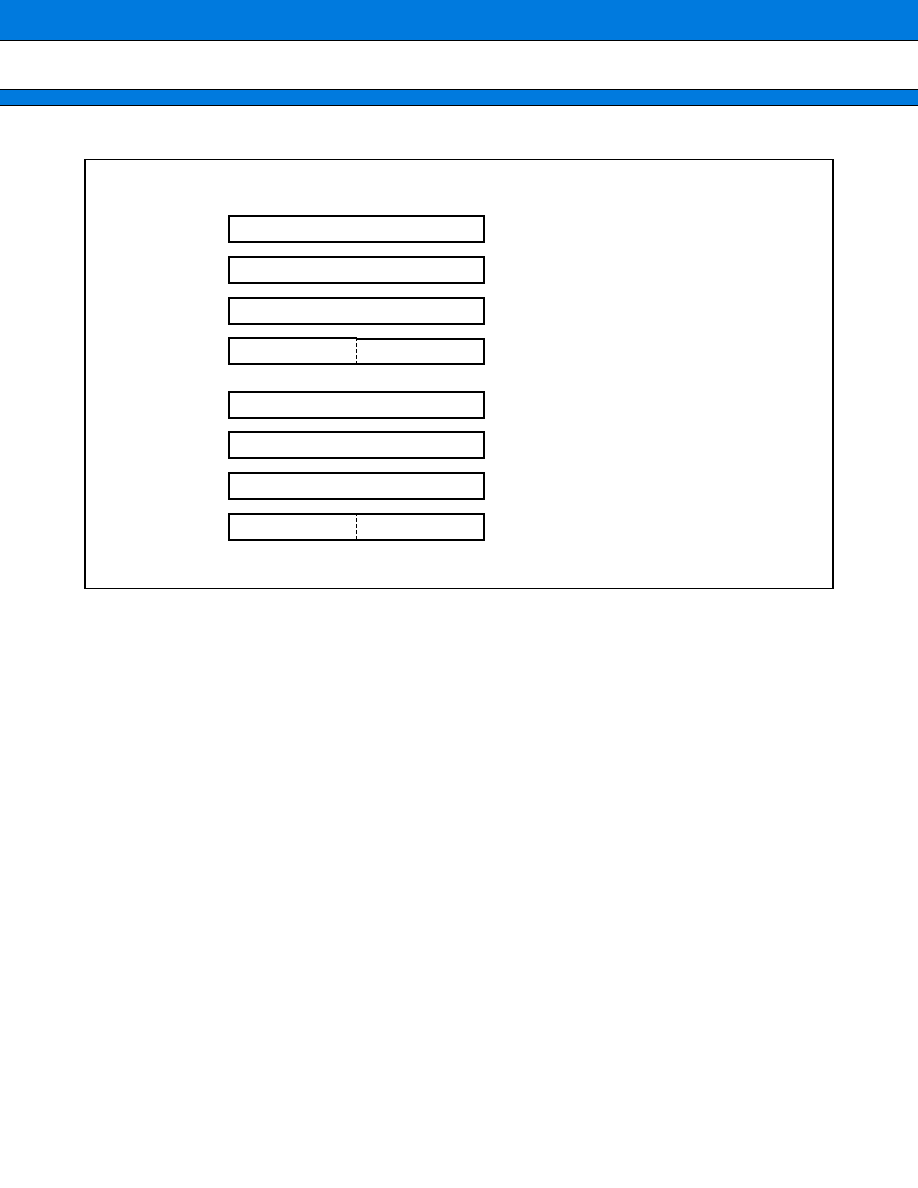

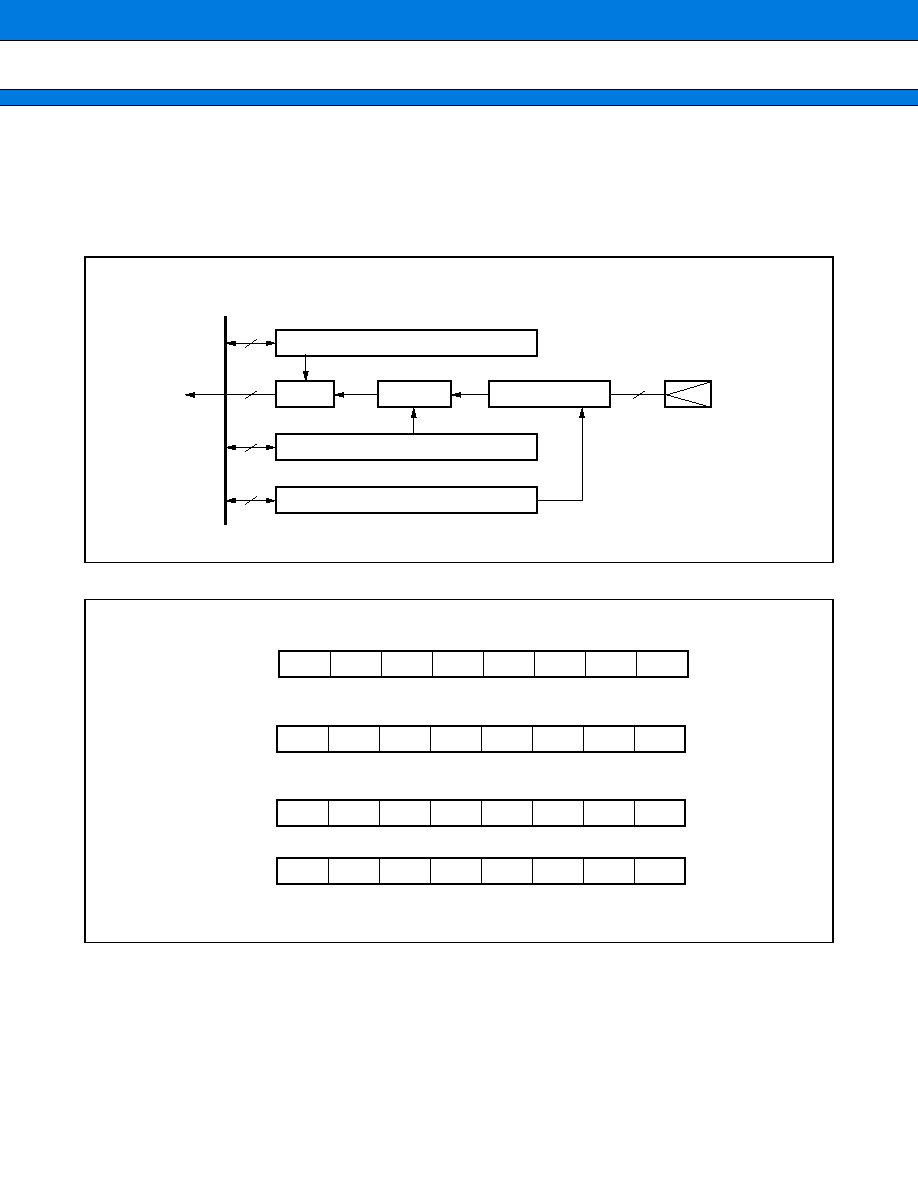

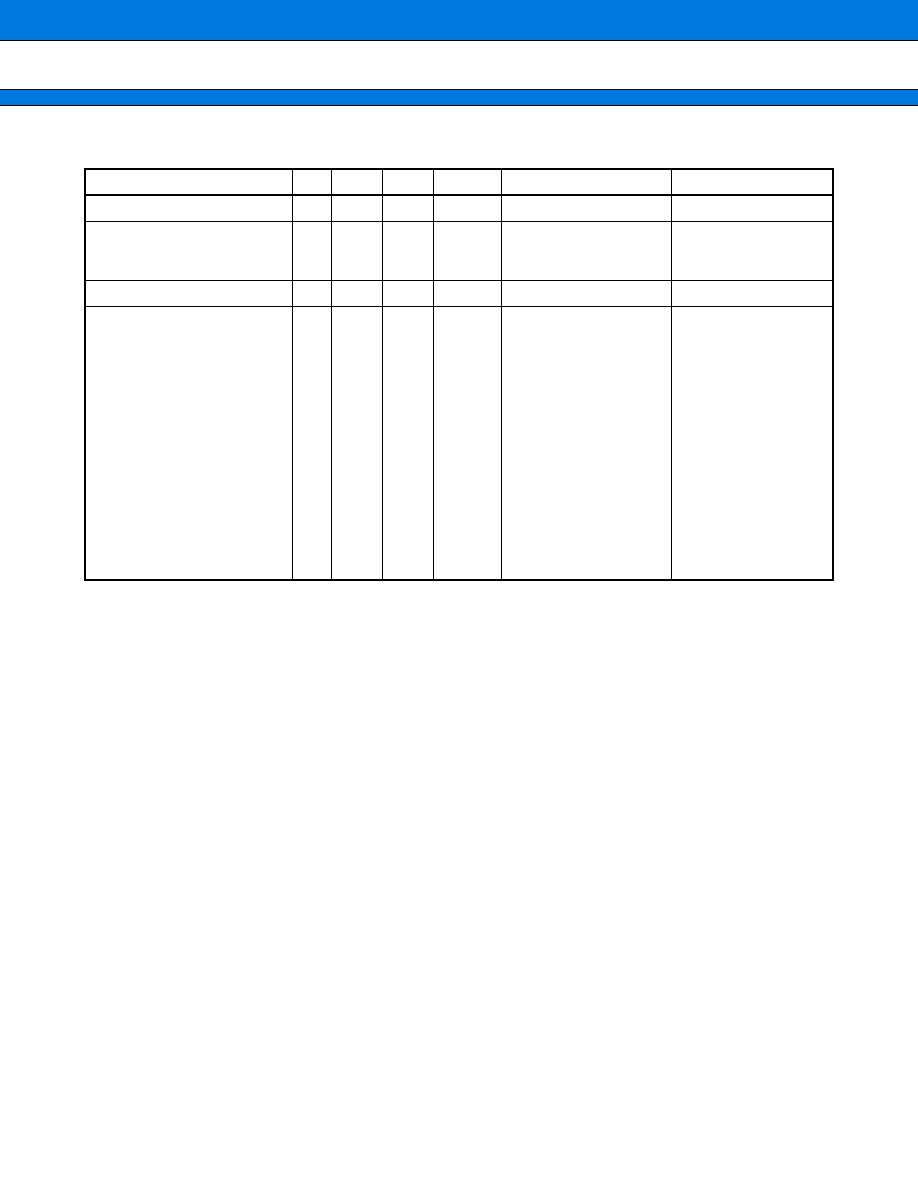

s

MULTI-PURPOSE REGISTERS

The multi-purpose registers are CPU registers R0 to R15 which are used as accumulators for various compu-

tations and memory access pointers (fields that indicate the address) .

Special purposes are assumed for the following 3 of the 16 registers. Thus, some instructions are emphasized.

R13 : Virtual accumulator (AC)

R14 : Frame Pointer (FP)

R15 : Stack Pointer (SP)

Initial values for R0 to R14 on resetting are unspecified. The initial value of R15 will be 0000 0000

H

(SSP value) .

∑ Register bank configuration

R0

R1

R12

R13

R14

R15

AC (Accumulator)

32-bit

FP (Frame Pointer)

SP (Stack Pointer)

XXXX XXXX

H

Initial value

XXXX XXXX

H

0000 0000

H

MB91133/MB91F133

27

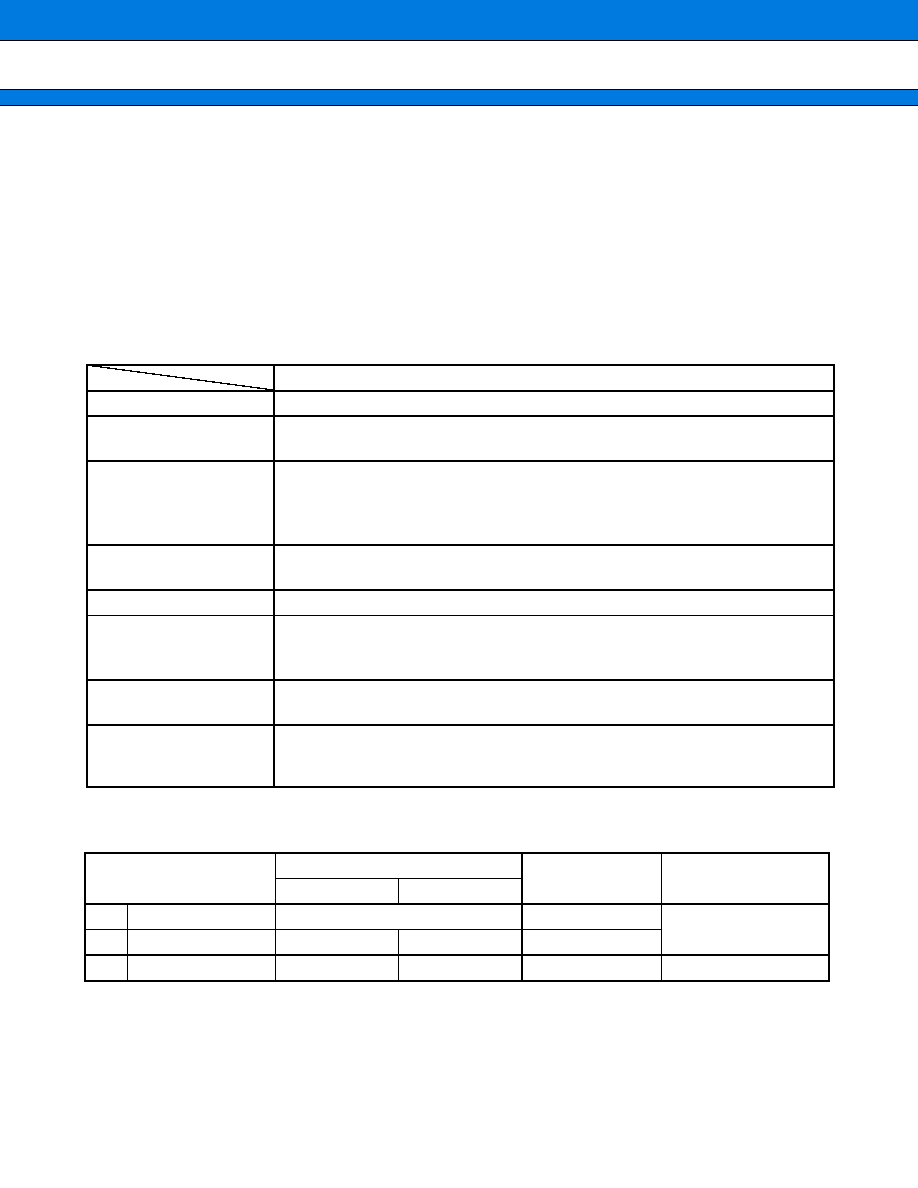

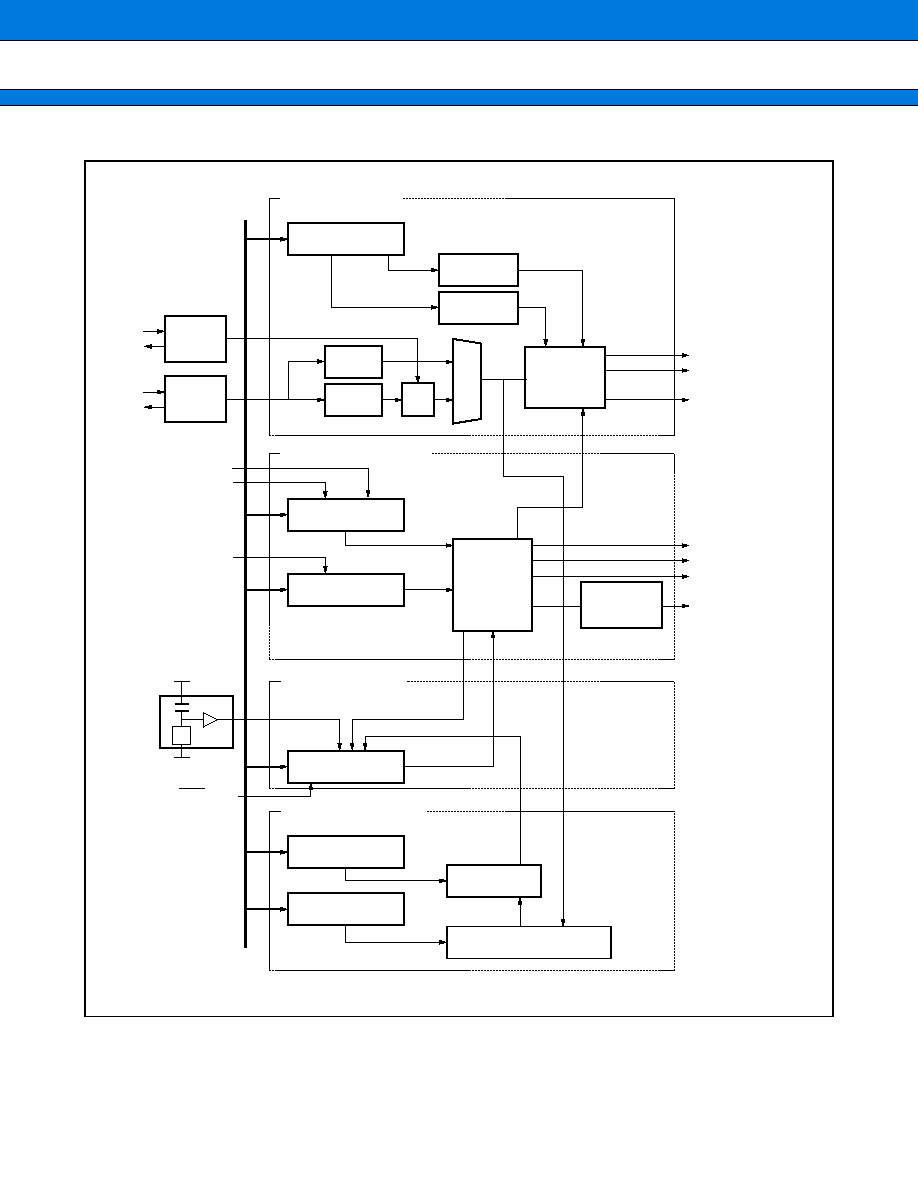

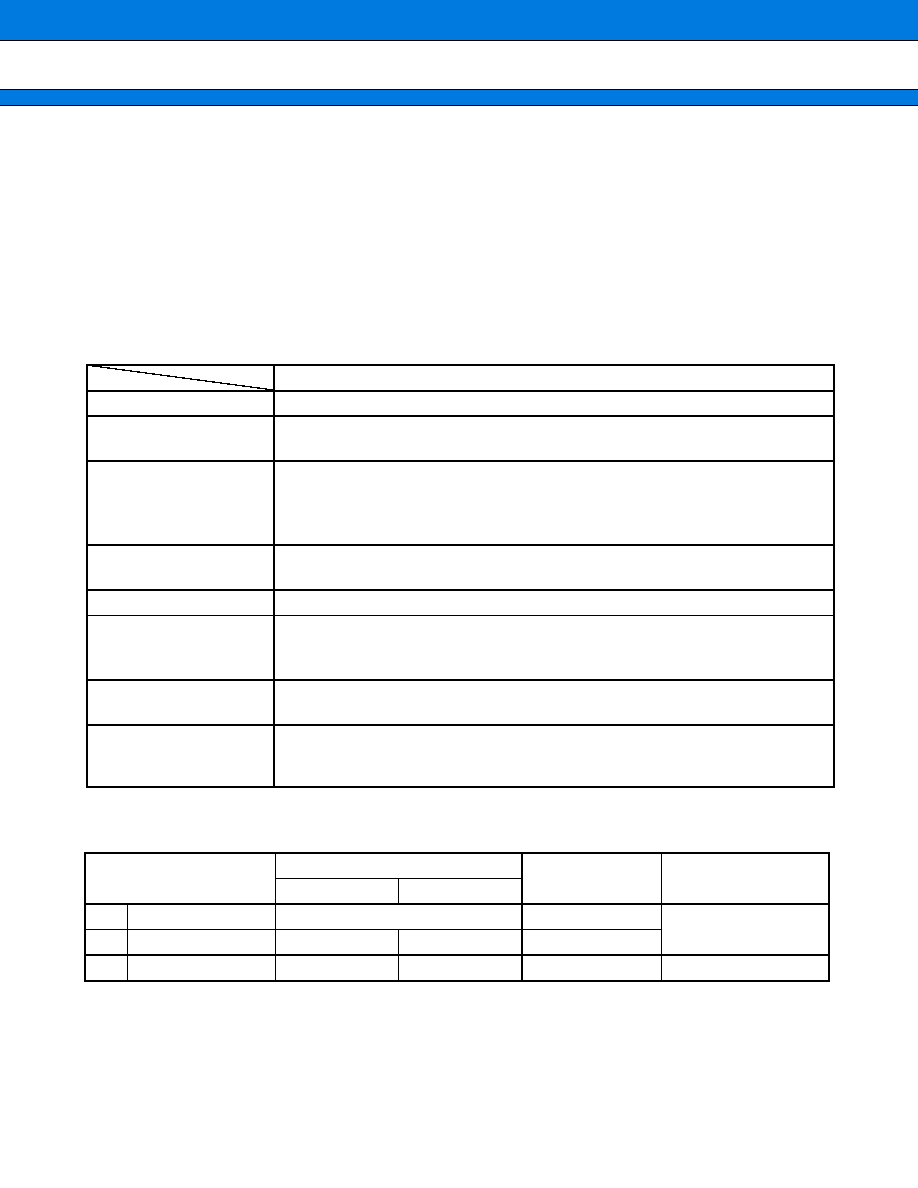

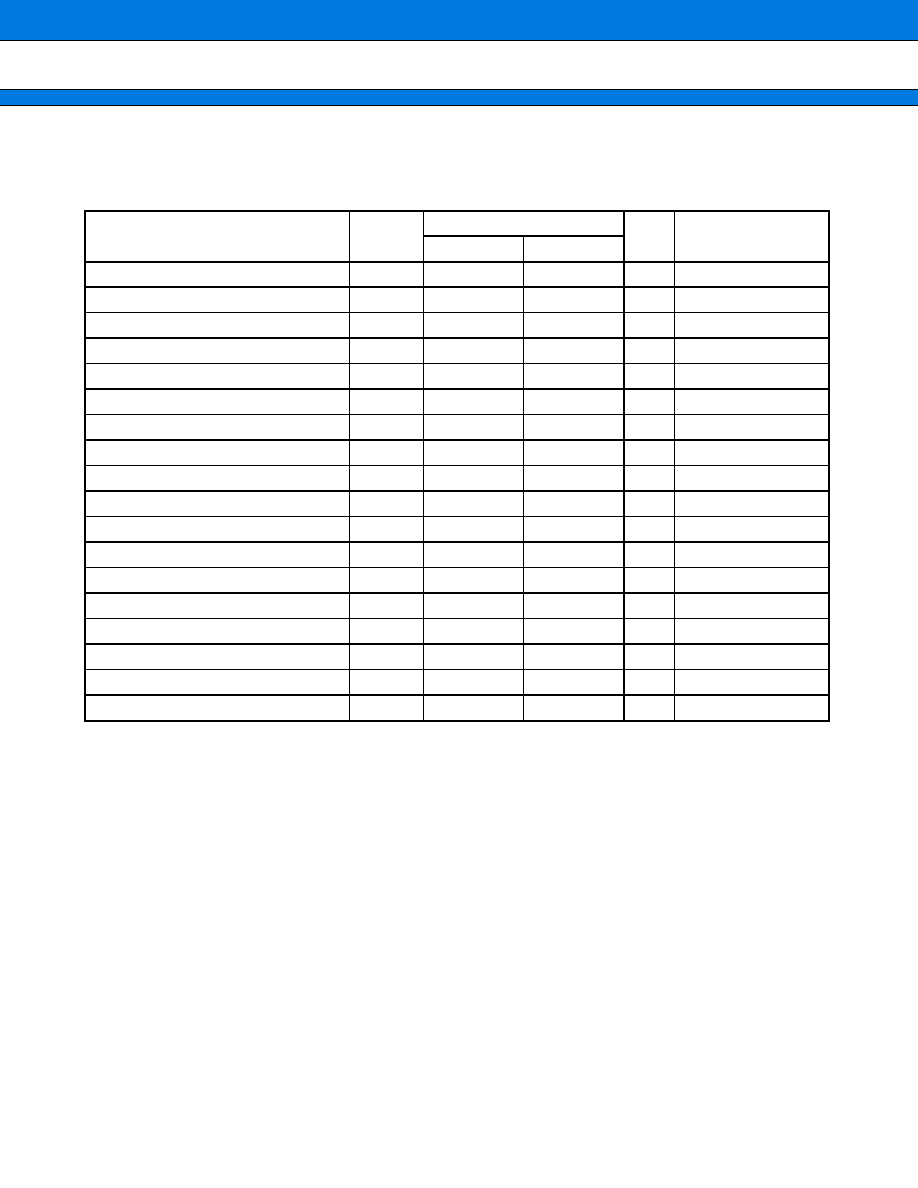

s

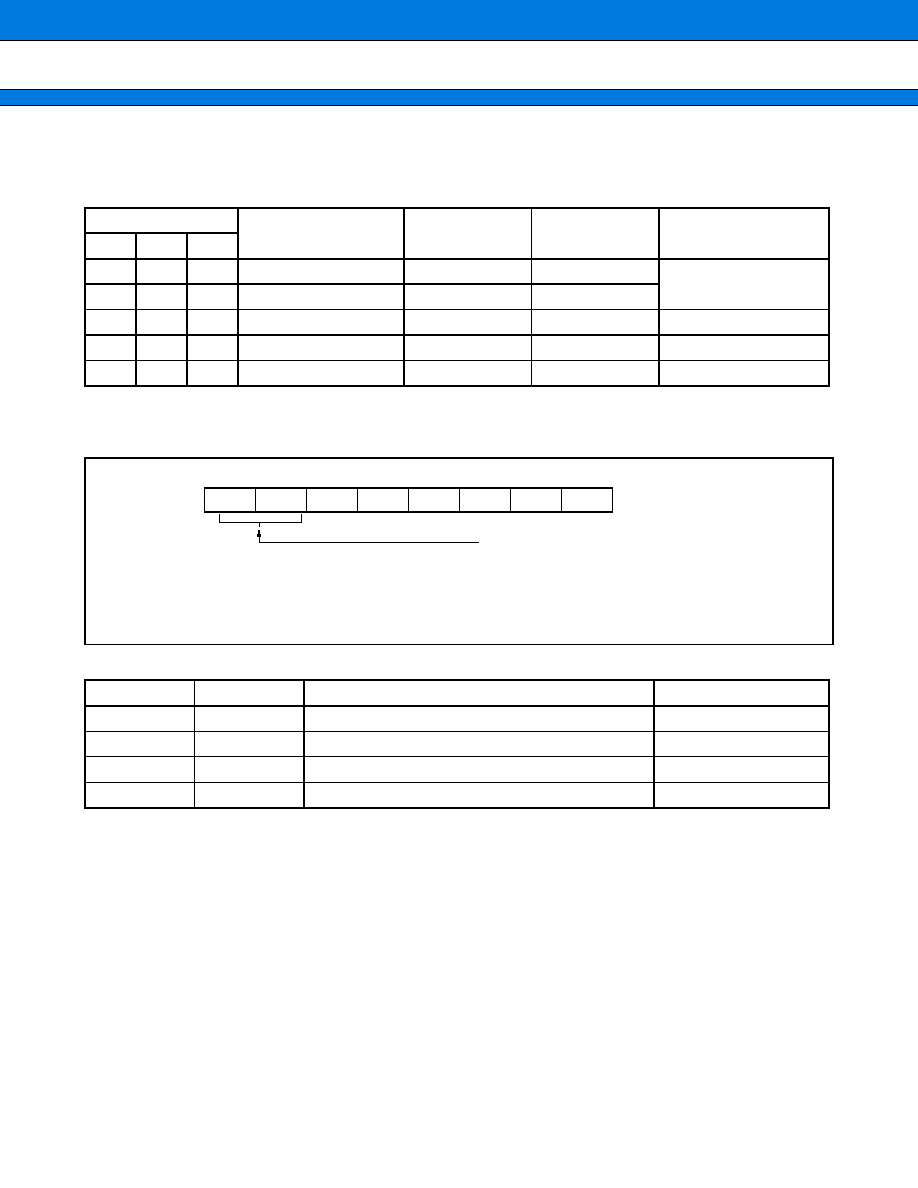

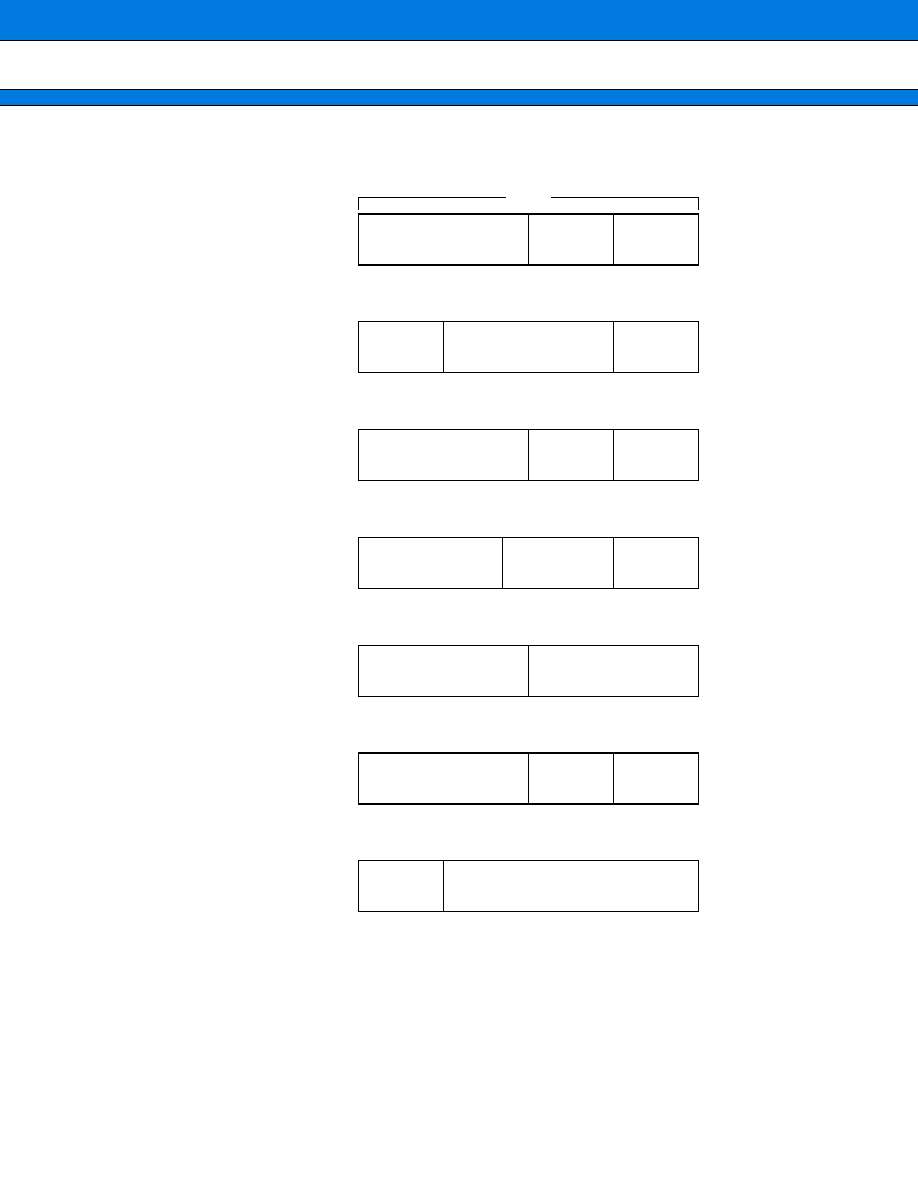

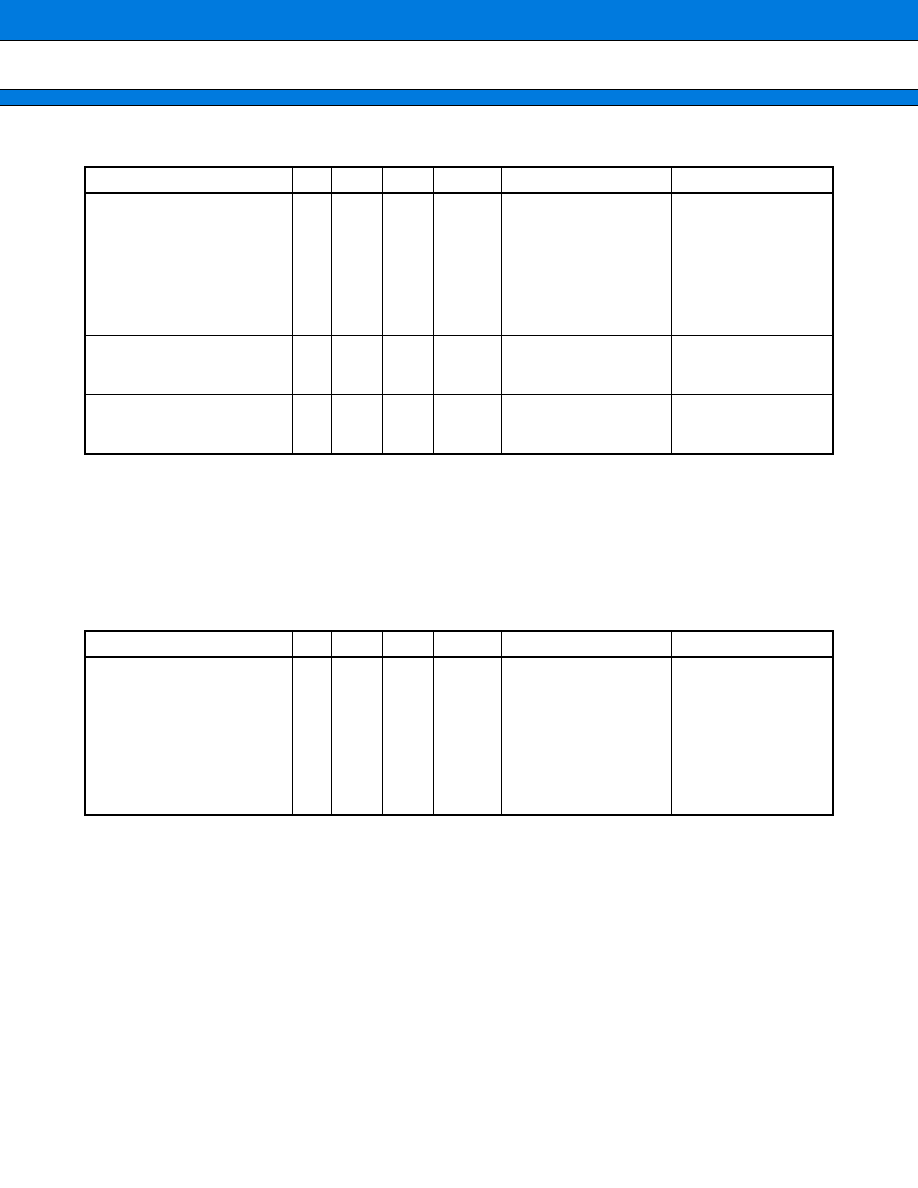

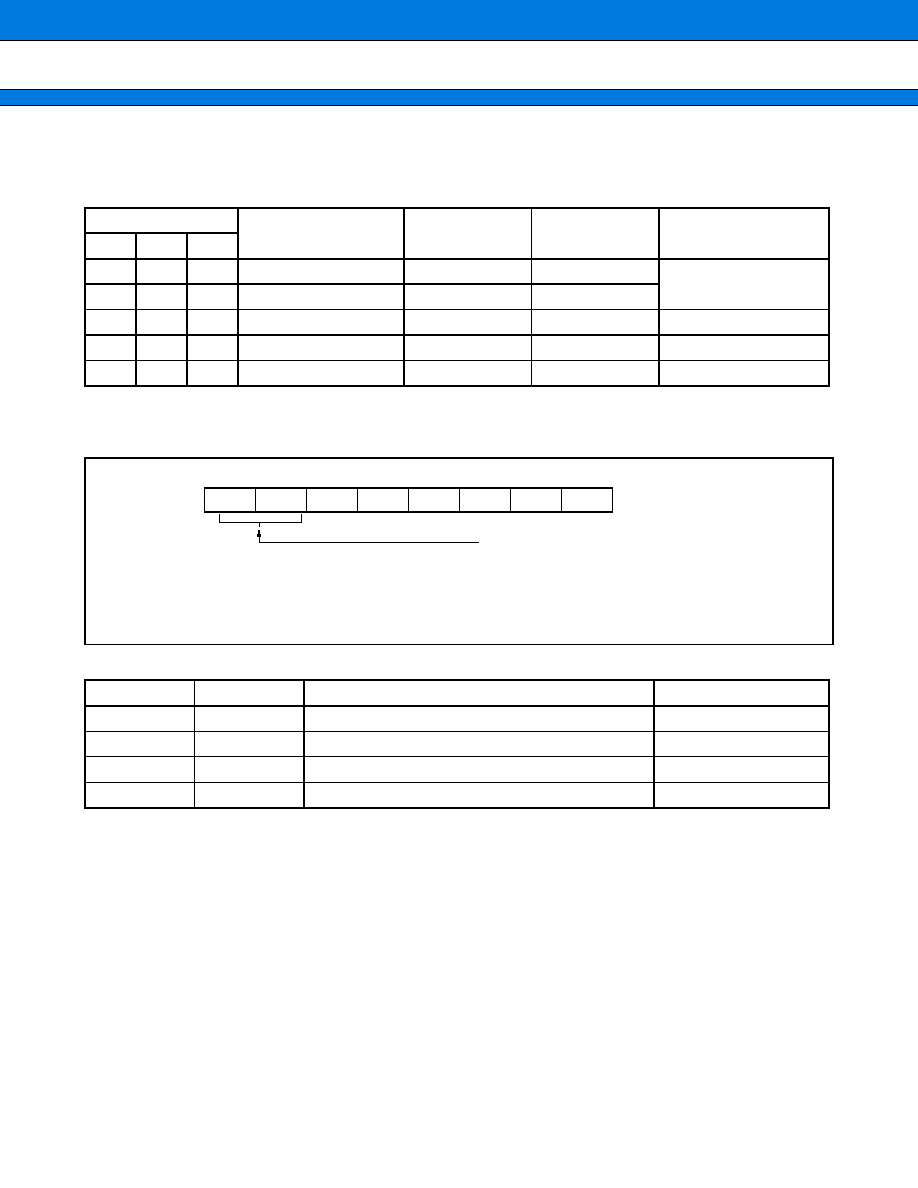

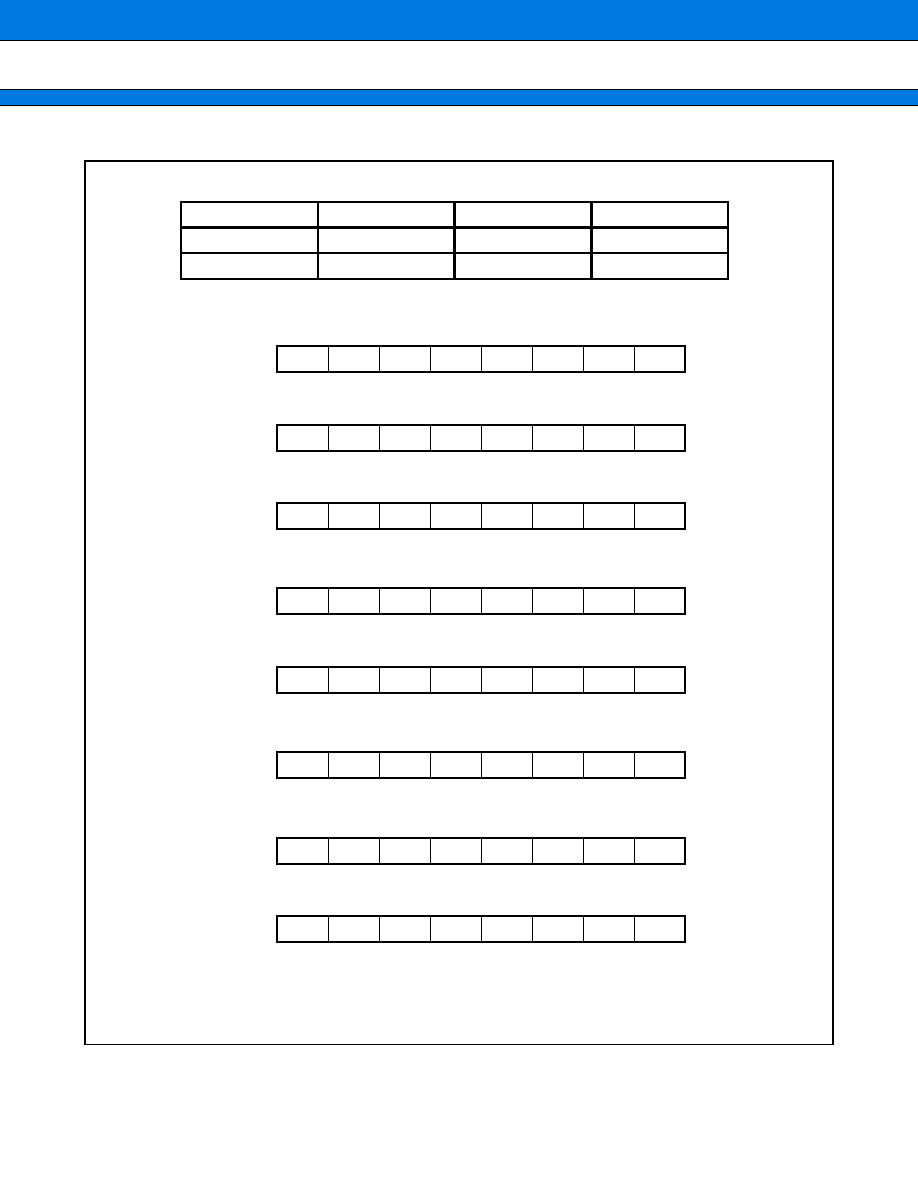

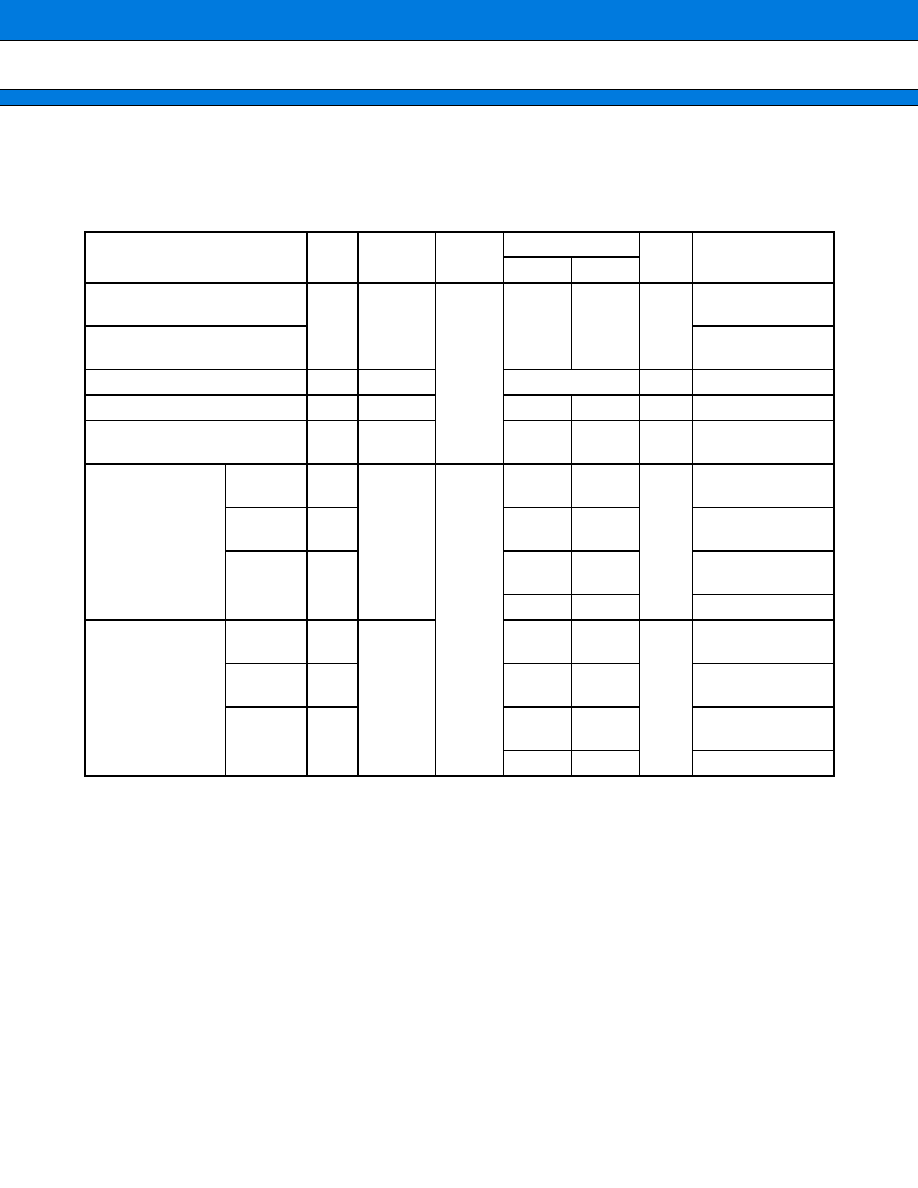

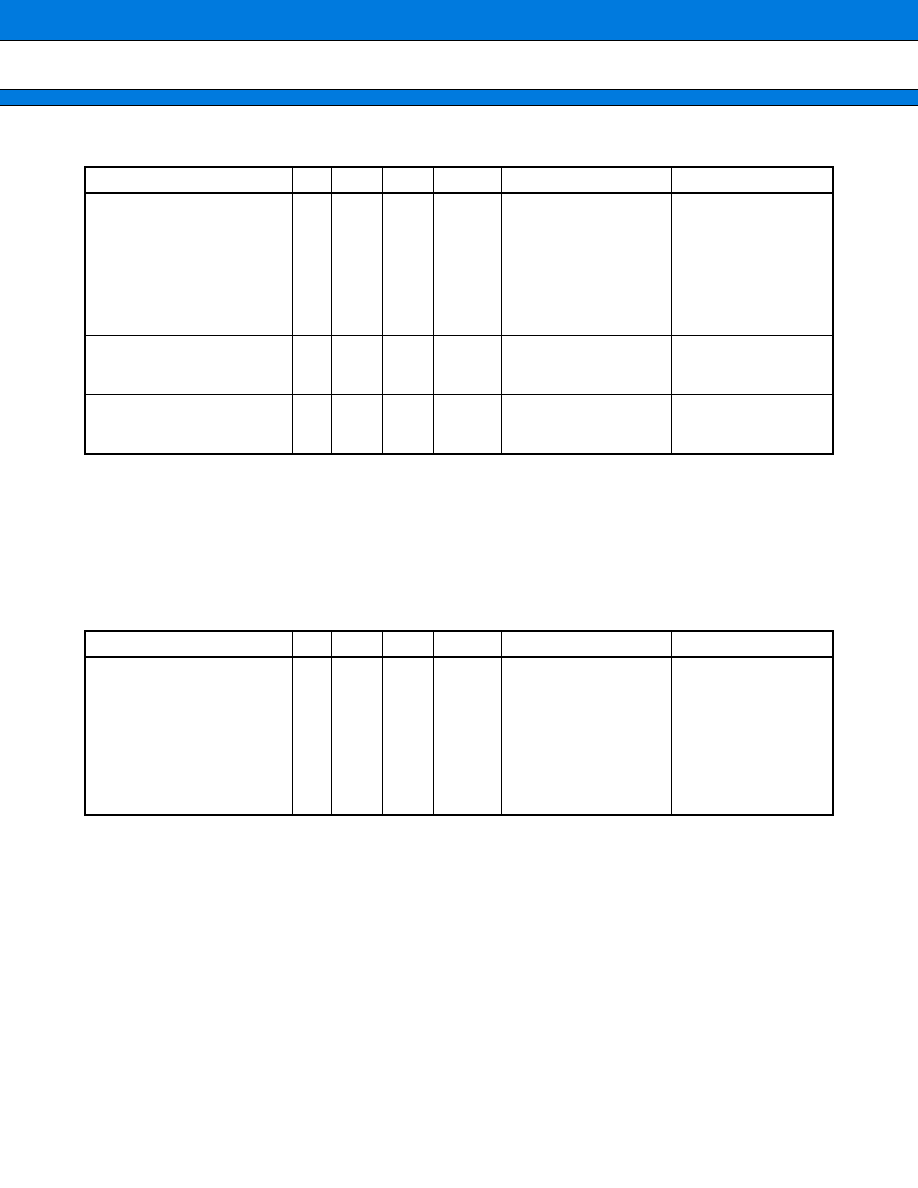

MODE SETTING

1.

Pins

∑ Mode pins and set mode

2.

Register

Mode register (MODR) and set mode

∑ Bus mode set bit and its functions

Mode pins

Mode name

Reset vector

access areas

External data

bus width

Bus modes

MD2

MD1

MD0

0

0

0

External vector mode 0

External

8-bit

External ROM external

bus mode

0

0

1

External vector mode 1

External

16-bit

0

1

0

Setting is prohibited

0

1

1

Internal vector mode

Internal

(Mode register) Single chip mode

1

Usage is prohibited

M1

M0

Functions

Remarks

0

0

Single chip mode

0

1

Internal ROM external bus mode

1

0

External ROM external bus mode

1

1

Setting is prohibited

Address

Initial value

Access

0000 07FF

H

XXXX XXXX

B

W

M1

M0

Bus mode set bit

*

*

*

*

*

*

W : Write only

X : Undecided

* : "0" should always be written for bits other than M1 and M0.

MB91133/MB91F133

28

s

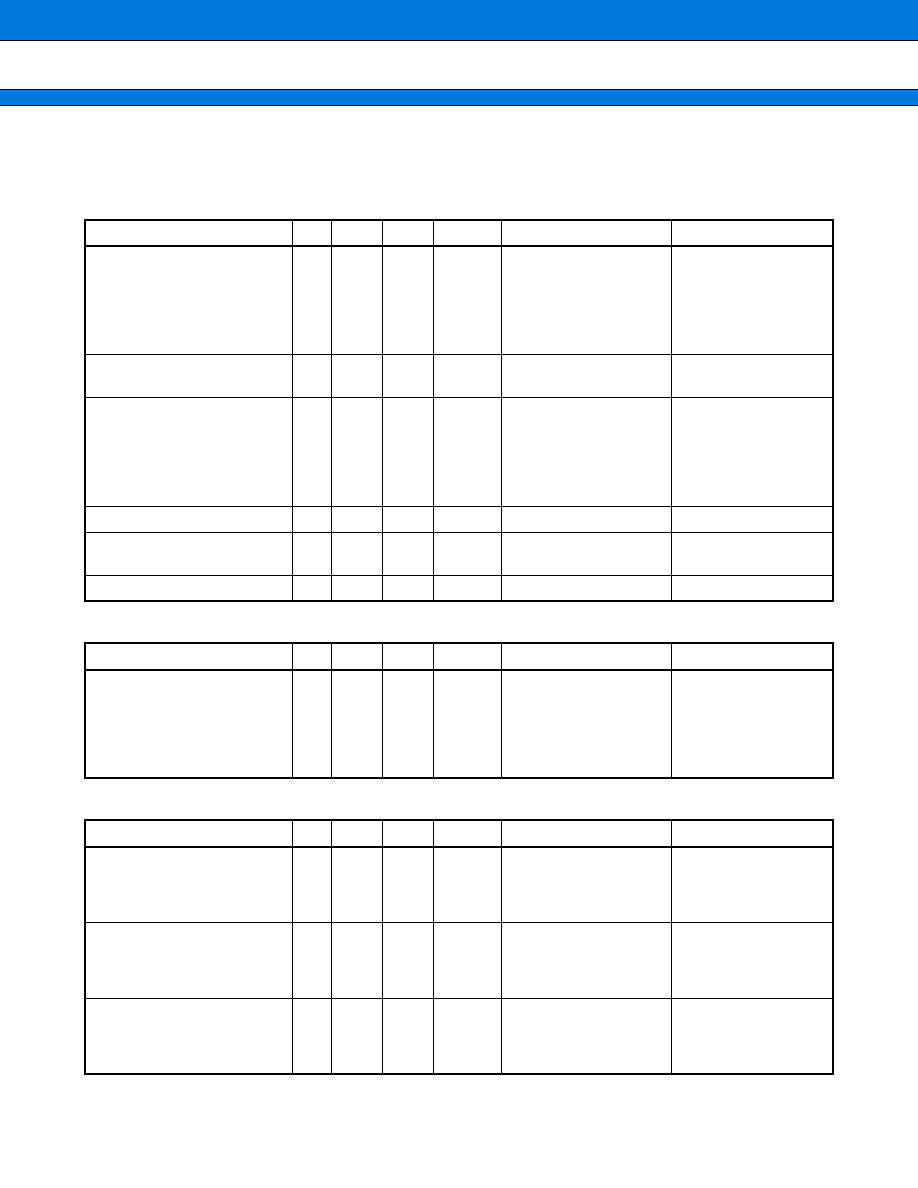

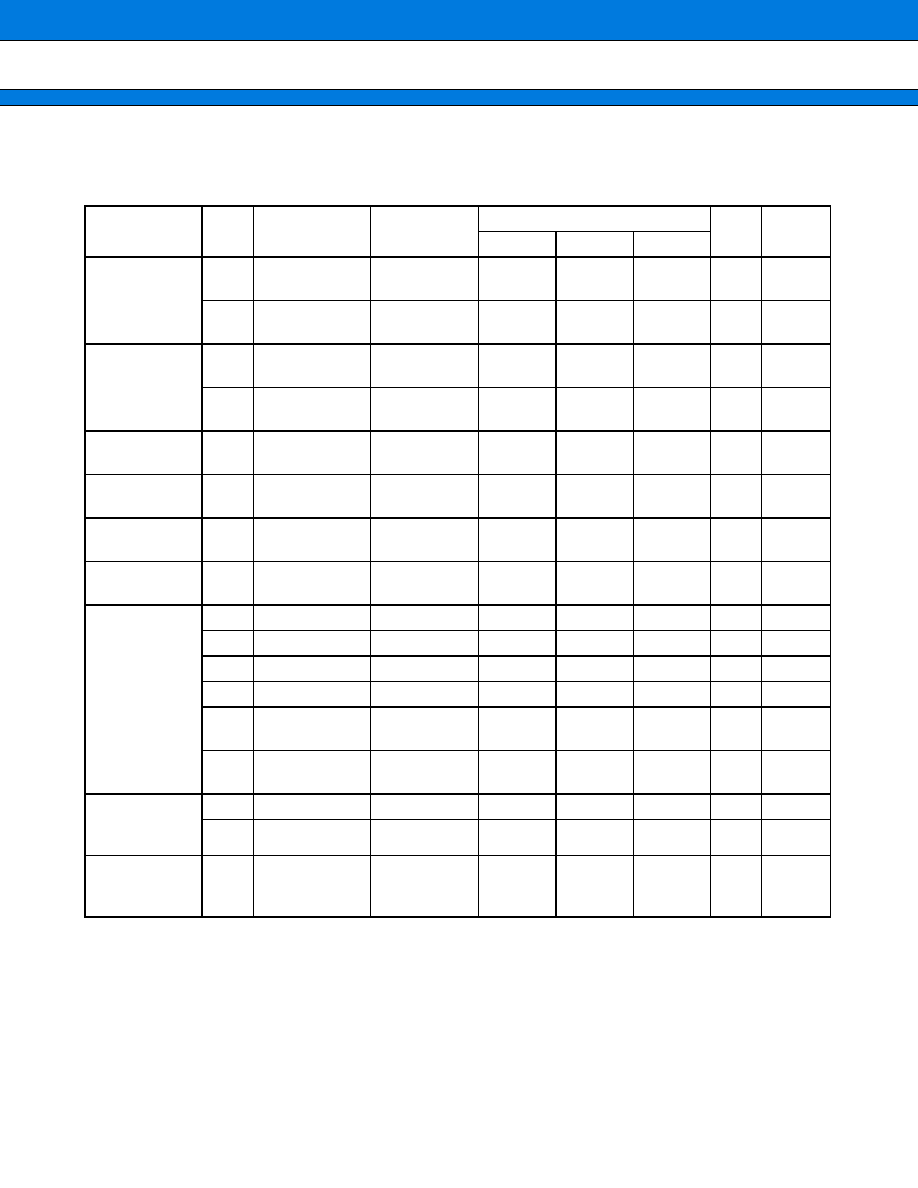

I/O MAP

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000000

H

PDR3

(R/W)

PDR2

(R/W)

Port Data

Register

XXXXXXXX

XXXXXXXX

000004

H

PDR6

(R/W)

PDR5

(R/W)

PDR4

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

000008

H

PDR8

(R/W)

-

XXXXXXX

00000C

H

000010

H

PDRF

(R/W)

PDRE

(R/W)

PDRD

(R/W)

PDRC

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000014

H

PDRJ

(R/W)

PDRI

(R/W)

PDRH

(R/W)

PDRG

(R/W)

-

-

XXXXXX

-

-

XXXXXX

-

-

-

-

-

XXX

-

-

XXXXXX

000018

H

LVLC

(R/W)

PDRL

(R/W)

PDRK

(R/W)

Level Comparator

XXXX

0

0

0

0

XXXXXXXX

XXXXXXXX

00001C

H

SSR0

(R/W)

SIDR0/SODR0 (R/W)

SCR0

(R/W)

SMR0

(R/W)

UART0

0 0 0 0 1 -

0

0

XXXXXXXX

0 0 0 0 0 1 0 0

0 0 0 0 0

-

0 0

000020

H

SSR1

(R/W)

SIDR1/SODR1 (R/W)

SCR1

(R/W)

SMR1

(R/W)

UART1

0 0 0 0 1 -

0

0

XXXXXXXX

0 0 0 0 0 1 0 0

0 0 0 0 0

-

0 0

000024

H

SSR2

(R/W)

SIDR2/SODR2 (R/W)

SCR2

(R/W)

SMR2

(R/W)

UART2

0 0 0 0 1 -

0

0

XXXXXXXX

0 0 0 0 0 1 0 0

0 0 0 0 0

-

0 0

000028

H

TMRLR

(W)

TMR

(R)

Reload Timer 0

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00002C

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0 0 0 0 0 0 0 0

000030

H

TMRLR

(W)

TMR

(R)

Reload Timer 1

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000034

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0 0 0 0 0 0 0 0

000038

H

ADCR

(R/W)

ADCS1

(R/W)

ADCS0

(R/W)

A/D Converter

(Sequential type)

0 0 1 0 1

-

XX XXXXXXXX

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

00003C

H

TMRLR

(W)

TMR

(R)

Reload Timer 2

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000040

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0 0 0 0 0 0 0 0

MB91133/MB91F133

29

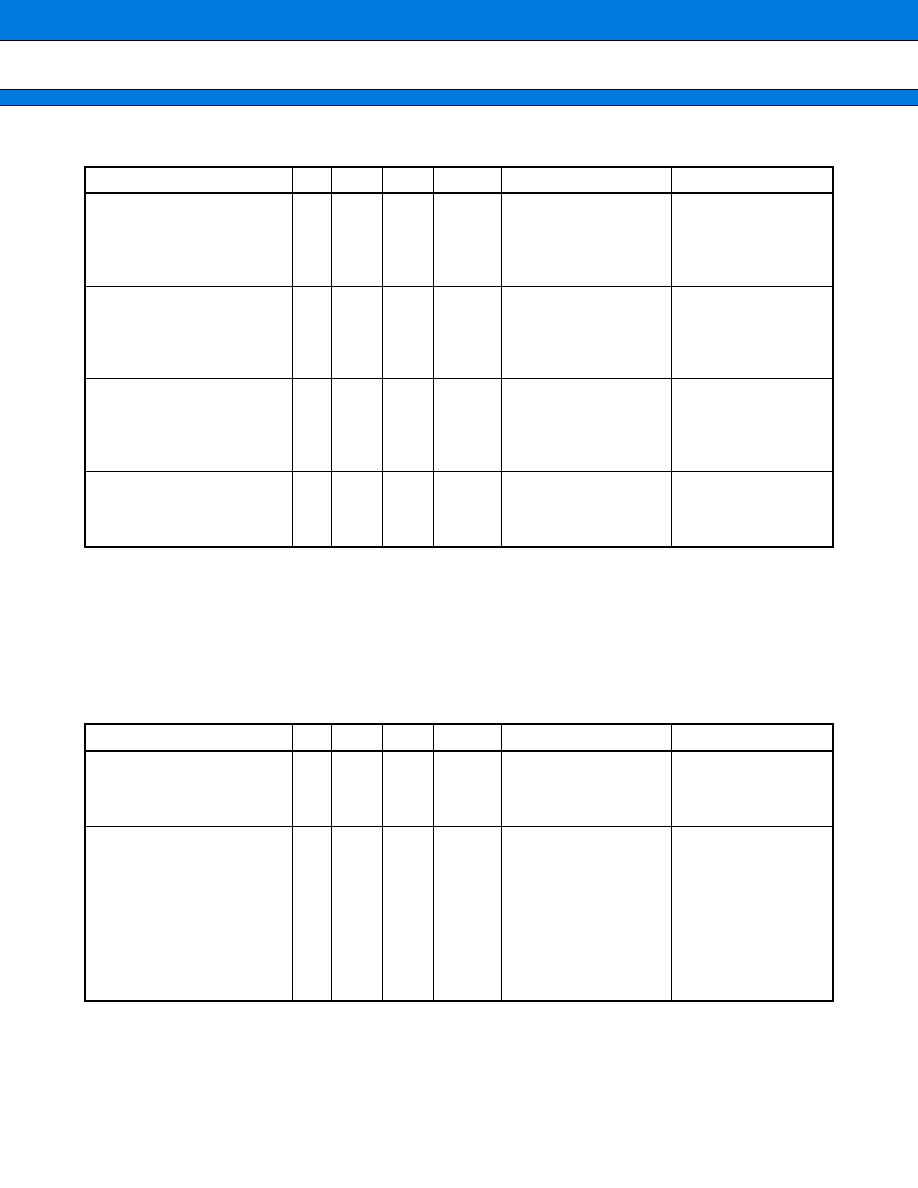

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000044

H

IPCP1

(R)

IPCP0

(R)

16-bit ICU

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000048

H

IPCP3

(R)

IPCP2

(R)

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00004C

H

ICS23

(R/W)

ICS01

(R/W)

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

000050

H

Reserved

000054

H

OCCP1

(R/W)

OCCP0

(R/W)

16-bit OCU

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000058

H

OCCP3

(R/W)

OCCP2

(R/W)

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00005C

H

OCCP5

(R/W)

OCCP4

(R/W)

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000060

H

OCCP7

(R/W)

OCCP6

(R/W)

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000064

H

OCS32

(R/W)

OCS10

(R/W)

XXX 0 0 0 0 0 0 0 0 0 XX 0 0

XXX 0 0 0 0 0 0 0 0 0 XX 0 0

000068

H

OCS76

(R/W)

OCS54

(R/W)

XXX 0 0 0 0 0 0 0 0 0 XX 0 0

XXX 0 0 0 0 0 0 0 0 0 XX 0 0

00006C

H

TCDT

(R/W)

TCCS

(R/W)

16-bit

Free-run Timer

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

-

-

-

-

-

-

- 0 0 0 0 0 0 0 0

000070

H

SSR3

(R/W)

SIDR3/SODR3 (R/W)

SCR3

(R/W)

SMR3

(R/W)

UART3

0 0 0 0 1 0 0

0

XXXXXXXX

0 0 0 0 0 1 0 0

0 0 0 0 0

-

0 0

000074

H

SSR4

(R/W)

SIDR4/SODR4 (R/W)

SCR4

(R/W)

SMR4

(R/W)

UART4

0 0 0 0 1 0 0

0

XXXXXXXX

0 0 0 0 0 1 0 0

0 0 0 0 0

-

0 0

000078

H

CDCR1

(R/W)

CDCR0

(R/W)

Communication

Pre-scalar

0 -

-

-

0 0 0 0

0 -

-

-

0 0 0 0

00007C

H

CDCR3

(R/W)

CDCR2

(R/W)

0 -

-

-

0 0 0 0

0 -

-

-

0 0 0 0

000080

H

CDCR4

(R/W)

0 -

-

-

0 0 0 0

MB91133/MB91F133

30

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000084

H

RCR1

(W)

RCR0

(W)

UDCR1

(R)

UDCR0

(R)

8-/16-bit

U/D Counter

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

000088

H

CCRH0

(R/W)

CCRL0

(R/W)

CSR0

(R/W)

0 0 0 0 0 0 0 0

-

0 0 0 1 0 0 0

0 0 0 0 0 0 0 0

00008C

H

CCRH1

(R/W)

CCRL1

(R/W)

CSR1

(R/W)

-

0 0 0 0 0 0 0

-

0 0 0 1 0 0 0

0 0 0 0 0 0 0 0

000090

H

Reserved

000094

H

EIRR0

(R/W)

ENIR0

(R/W)

EIRR1

(R/W)

ENIR1

(R/W)

Ext Int

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

000098

H

ELVR0

(R/W)

ELVR1

(R/W)

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

00009C

H

EIRR2

(R/W)

ENIR2

(R/W)

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0000A0

H

ELVR2

(R/W)

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0000A4

H

DACR2

(R/W)

DACR1

(R/W)

DACR0

(R/W)

D/A Converter

-

-

-

-

-

-

-

0

-

-

-

-

-

-

-

0

-

-

-

-

-

-

-

0

0000A8

H

DADR2

(R/W)

DADR1

(R/W)

DADR0

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

0000AC

H

DTCR1

(R/W)

TMRR1

(R/W)

DTCR0

(R/W)

TMRR0

(R/W)

Waveform

Generator

0 0 0 0 0 0 0 0

XXXXXXXX

0 0 0 0 0 0 0 0

XXXXXXXX

0000B0

H

SIGCR

(R/W)

DTCR2

(R/W)

TMRR2

(R/W)

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

XXXXXXXX

0000B4

H

to

0000BC

H

Reserved

0000C0

H

PCRE

(R/W)

PCRD

(R/W)

PCRC

(R/W)

Pull-up Control

-

-

-

-

-

-

0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0000C4

H

PCRJ

(R/W)

PCRI

(R/W)

PCRH

(R/W)

-

-

0 0 0 0 0 0

-

-

0 0 0 0 0 0

-

-

-

-

-

0 0 0

0000C8

H

OCRJ

(R/W)

OCRI

(R/W)

OCRH

(R/W)

Open-drain Control

-

-

0 0 0 0 0 0

-

-

0 0 0 0 0 0

-

-

-

-

-

0 0 0

0000CC

H

AICK

(R/W)

Analog

Input Control

0 0 0 0 0 0 0 0

MB91133/MB91F133

31

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

0000D0

H

DDRF

(R/W)

DDRE

(R/W)

DDRD

(R/W)

DDRC

(R/W)

Data Direction

Register

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0000D4

H

DDRJ

(R/W)

DDRI

(R/W)

DDRH

(R/W)

DDRG

(R/W)

-

-

0 0 0 0 0 0

-

-

0 0 0 0 0 0

-

-

-

-

-

0 0 0

-

-

0 0 0 0 0 0

0000D8

H

DDRL

(R/W)

DDRK

(R/W)

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0000DC

H

GCN1

(R/W)

GCN2

(R/W)

PPG ctl

0 0 1 1 0 0 1 0 0 0 0 1 0 0 0 0

0 0 0 0 0 0 0 0

0000E0

H

PTMR0

(R)

PCSR0

(W)

PPG0

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

0000E4

H

PDUT0

(W)

PCNH0

(R/W)

PCNL0

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

0000E8

H

PTMR1

(R)

PCSR1

(W)

PPG1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

0000EC

H

PDUT1

(W)

PCNH1

(R/W)

PCNL1

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

0000F0

H

PTMR2

(R)

PCSR2

(W)

PPG2

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

0000F4

H

PDUT2

(W)

PCNH2

(R/W)

PCNL2

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

0000F8

H

PTMR3

(R)

PCSR3

(W)

PPG3

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

0000FC

H

PDUT3

(W)

PCNH3

(R/W)

PCNL3

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

000100

H

PTMR4

(R)

PCSR4

(W)

PPG4

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

000104

H

PDUT4

(W)

PCNH4

(R/W)

PCNL4

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

000108

H

PTMR5

(R)

PCSR5

(W)

PPG5

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

XXXXXXXX XXXXXXXX

00010C

H

PDUT5

(W)

PCNH5

(R/W)

PCNL5

(R/W)

XXXXXXXX XXXXXXXX

0 0 0 0 0 0 0 -

0 0 0 0 0 0 0 0

MB91133/MB91F133

32

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

000110

H

TMRLR

(W)

TMR

(R)

Reload Timer 3

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

000114

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0 0 0 0 0 0 0 0

000118

H

TMRLR

(W)

TMR

(R)

Reload Timer 4

XXXXXXXX XXXXXXXX

XXXXXXXX XXXXXXXX

00011C

H

TMCSR

(R/W)

-

-

-

-

0

0

0

0 0 0 0 0 0 0 0 0

000120

H

to

0001FC

H

Reserved

000200

H

DPDP

(R/W)

DMAC

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

0 0 0 0 0 0 0

000204

H

DACSR

(R/W)

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

000208

H

DATCR

(R/W)

XXXXXXXX

XXXX0 0 0 0

XXXX0 0 0 0

XXXX0 0 0 0

00020C

H

000210

H

to

0003EC

H

Reserved

0003F0

H

BSD0

(W)

Bit Search Module

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003E4

H

BSD1

(R/W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003F8

H

BSDC

(W)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

0003FC

H

BSRR

(R)

XXXXXXXX

XXXXXXXX

XXXXXXXX

XXXXXXXX

000400

H

ICR00

(R/W)

ICR01

(R/W)

ICR02

(R/W)

ICR03

(R/W)

Interrupt Control

Unit

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000404

H

ICR04

(R/W)

ICR05

(R/W)

ICR06

(R/W)

ICR07

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000408

H

ICR08

(R/W)

ICR09

(R/W)

ICR10

(R/W)

ICR11

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

MB91133/MB91F133

33

(Continued)

Address

Register

Block

+

0

+

1

+

2

+

3

00040C

H

ICR12

(R/W)

ICR13

(R/W)

ICR14

(R/W)

ICR15

(R/W)

Interrupt Control

Unit

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000410

H

ICR16

(R/W)

ICR17

(R/W)

ICR18

(R/W)

ICR19

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000414

H

ICR20

(R/W)

ICR21

(R/W)

ICR22

(R/W)

ICR23

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000418

H

ICR24

(R/W)

ICR25

(R/W)

ICR26

(R/W)

ICR27

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

00041C

H

ICR28

(R/W)

ICR29

(R/W)

ICR30

(R/W)

ICR31

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000420

H

ICR32

(R/W)

ICR33

(R/W)

ICR34

(R/W)

ICR35

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000424

H

ICR36

(R/W)

ICR37

(R/W)

ICR38

(R/W)

ICR39

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

000428

H

ICR40

(R/W)

ICR41

(R/W)

ICR42

(R/W)

ICR43

(R/W)

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

-

-

-

-

1 1 1 1

00042C

H

ICR44

(R/W)

ICR45

(R/W)

ICR46

(R/W)

ICR47

(R/W)

-

-

-

-