DS07-08103-1E

FUJITSU SEMICONDUCTOR

DATA SHEET

Family

FR400 Series

VLIW Embedded Microprocessor

MB93423

DESCRIPTION

This specifications describe the implementation of the MB93423, incorporating a processor core (FR403-SoC)

designed for embedded applications, which is based on a VLIW (Very Long Instruction Word) architecture (the

FR-V architecture) .

This processor can issue the integer operation instruction, media instruction, and branch instruction, up to two

instructions, in units called the "VLIW instruction" on a cycle-by-cycle basis.

Also, the processor incorporates the following resources : SDRAM controller (SDRAMC) , interrupt controller

(IRC) , DMA controller (DMAC) , asynchronous transfer module (UART) , timer/counter (TIMER/COUNTER) ,

general-purpose I/O (GPIO) , video display controller (VDC) , video capture controller (VCC) , scaler, audio

interface, serial interface (I

2

C*) , USB interface, and memory stick interface. The VLIW instruction and these

resources achieve an excellent cost performance in a complex of high-performance general-purpose processing

and media processing, such as multifunction printers, digital cameras, and portable information terminals.

* : Purchase of Fujitsu I

2

C components conveys a license under the Philips I

2

C Patent Rights to use, these

components in an I

2

C system provided that the system conforms to the I

2

C Standard Specification as defined

by Philips.

PACKAGE

337-ball plastic PFBGA

(BGA-337P-M03)

MB93423

2

FEATURES

CPU Core

� 2-way 240 MHz or 266 MHz VLIW Processor Core

� Peak Performance

480 MIPS (Integer operation performance) at 240 MHz

1920 MOPS

+

240 MIPS (media operation performance) at 240 MHz

532 MIPS (Integer operation performance) at 266 MHz

2128 MOPS

+

266 MIPS (media operation performance) at 266 MHz

� 64 32-bit registers (32GR

+

32FR)

Cache

� Instruction cache : 8 Kbyte (2way) , line size 32 byte

� Data cache : 8 Kbyte (2way) , line size 32 byte

� Cache line replace algorithm : LRU

� lnstruction cache preload instruction (ICPL) , Data cache preload instruction (DCPL) support

� Cache lock support of both instruction and data for each line

� Non-blocking cache (data cache)

� Store buffer : 64-byte (data cache)

SDRAM Interface

� SDRAM in accordance with the PC100 or PC133 standard can be connected.

� Changeable 32/16-bit data bus

� Four CS (2 support only registered-DIMM)

DMAC

� Four channels (dual address mode)

� Data transfer size is selected from 1, 2, 4 and 32 bytes

� Maximum 4G-byte data transfer

� Priority is fixed or round robin.

� Four external request demand signals (DREQ#[3 : 0])

� 32-byte FIFO is built in each DMA channel

� Address update

Select from increment, holding and decrement

� Circular addressing

When the transfer byte count reaches the specified value, the transfer address is reset to the initial value and

transfer continues.

When internal request is specified while circular addressing is specified, the internal request will be ignored.

� 2D addressing

When the transfer byte count reaches the specified value, "initial value

+

AP value" is set to transfer address

and transfer continues.

Local Bus Interface

� 24-bit address / 16-bit or 8-bit data

� Can directly connect SRAM, ROM, etc.

� The programmable address decoder is built into, and maximum 4 chip select pins are equipped with.

� Can specify the bus width by each chip select. (Select from 16 bits or 8 bits)

� The programmable wait state generator is built into.

Interrupt Controller

� Maximum 4 external interrupt factors are input (IRQ3-0) / 11 internal interrupt factors are input : (DMA

=

4,

Timer

=

3, UART

=

2 and Error response

=

2)

� Interrupt factors are mapped in 15 levels of interrupt requests.

(Continued)

MB93423

3

UART

� 16550 subsets

� 2 channels of UART are equipped.

� Prescaler to generate baud rate is built into.

� Modem control signal external pins (RTS#/CTS#) are equipped (to only channel 0) .

Timer

� 8254 subsets

� 3 channels of 16-bit timer are equipped.

� Supports mode 0 (terminal count interrupt) , mode 2 (rate generator) , mode 4 (software trigger strobe) , and

mode 5 (hardware trigger strobe) . No other mode is supported.

� Supports the binary counter. (BCD counter is not supported.)

� One channel of prescaler is mounted on the former steps in the timer block.

GPIO

� 16-bit general-purpose I/O port is equipped with. (Other peripheral functions and I/O pins are shared.)

JTAG

� Supports the IEEE1149.1 JTAG Boundary Scan function.

Video Output

� Progressive or interlaced scan method

� 320 to 1920 pixels horizontal resolution, 240 to 1200 pixels vertical resolution

� Supports 4 : 2 : 2 YCbCr 8 bits (Time-shared; CbYCrY; conforms to BT.656) , 4 : 2 : 2 YCbCr 16 bits (Cb

and Cr output time-shared; Cb precedes Cr) , 4 : 2 : 2 YCbCr 24 bits (Cb and Cr output concurrently; 2 clocks

output) , 4 : 4 : 4 RGB 24 bits for output format

� Supports 4 : 2 : 2 YCbCr 16 bits (Cb and Cr time-shared; Cb precedes Cr) , 4 : 4 : 4 RGB 24 bits (No filler

byte) for input data

� Hardware cursor : 1 piece (32

�

32; 2 colors

+

transparent color)

Video Input

� Progressive or interlaced scan method

� 320 to 1920 pixels horizontal resolution, 240 to 1200 pixels vertical resolution

� Supports 4 : 2 : 2 YCbCr 8 bits (Time-shared; CbYCrY; conforms to BT.656) , 4 : 2 : 2 YCbCr 16 bits (Cb

and Cr output time-shared; Cb precedes Cr) , 4 : 2 : 2 YCbCr 24 bits (Cb and Cr output concurrently; 2 clocks

output) , 4 : 4 : 4 RGB 24 bits for input format

� Supports 4 : 2 : 2 YCbCr 16 bits (Cb and Cr time-shared; Cb precedes Cr) , 4 : 4 : 4 RGB 24 bits (No filler

byte) for output data

� Hardware cursor : 1 piece (32

�

32; 2 colors

+

transparent color)

Scaler

� Maximum pixel count in horizontal direction for input image size : 1920 (brightness component)

� Maximum pixel count in vertical direction for input image size

: 768

� Maximum pixel count in horizontal direction for output image size : 360 (brightness component)

� Maximum pixel count in vertical direction for output image size

: 288

Audio Output

� This is an interface supporting the 3-wire serial (supporting I

2

S which is MSB-justified) and the PCM highway.

� Maximum : 32 bits/sample (I

2

S which is MSB-justified)

� Fixed at 8 bits/sample (PCM highway)

� Depends on frequency of supplied clock (Either of the following is supplied from outside : 256/384/512/768 fs.)

(Continued)

MB93423

4

(Continued)

Audio Input

� This is an interface supporting the 3-wire serial (supporting I

2

S which is MSB-justified) and the PCM highway.

Input data is arranged in the front-justified format (starting with MSB) .

� Maximum : 32 bits/sample (I

2

S which is MSB-justified)

� Fixed at 8 bits/sample (PCM highway)

� Depends on frequency of supplied clock (Either of the following is supplied from outside : 256/384/512/768 fs.)

USB

� Compliant with USB 2.0 FS function.

� V bus and isochronous transfer are not supported.

I

2

C

� Standard mode (100 Kbps) and the Fast mode (400 Kbps) are supported.

Memory Stick

� Compliant with Memory Stick Standard Format Specification ver1.4.

� Memory Stick Pro and Memory Stick Duo are supported. (However, excluded Magic Gate function.)

AV GPIO

� 32 bits (correspond to the pins shared with other functions.)

Clock Control

� Clock supply can be turned on/off for each unit.

Recommended Operation Condition

� Power supply voltage : Externally 3.3 V

�

0.15 V, Internally 1.8 V

�

0.1 V

� Operating temperature range from 0

�

C to

+

70

�

C

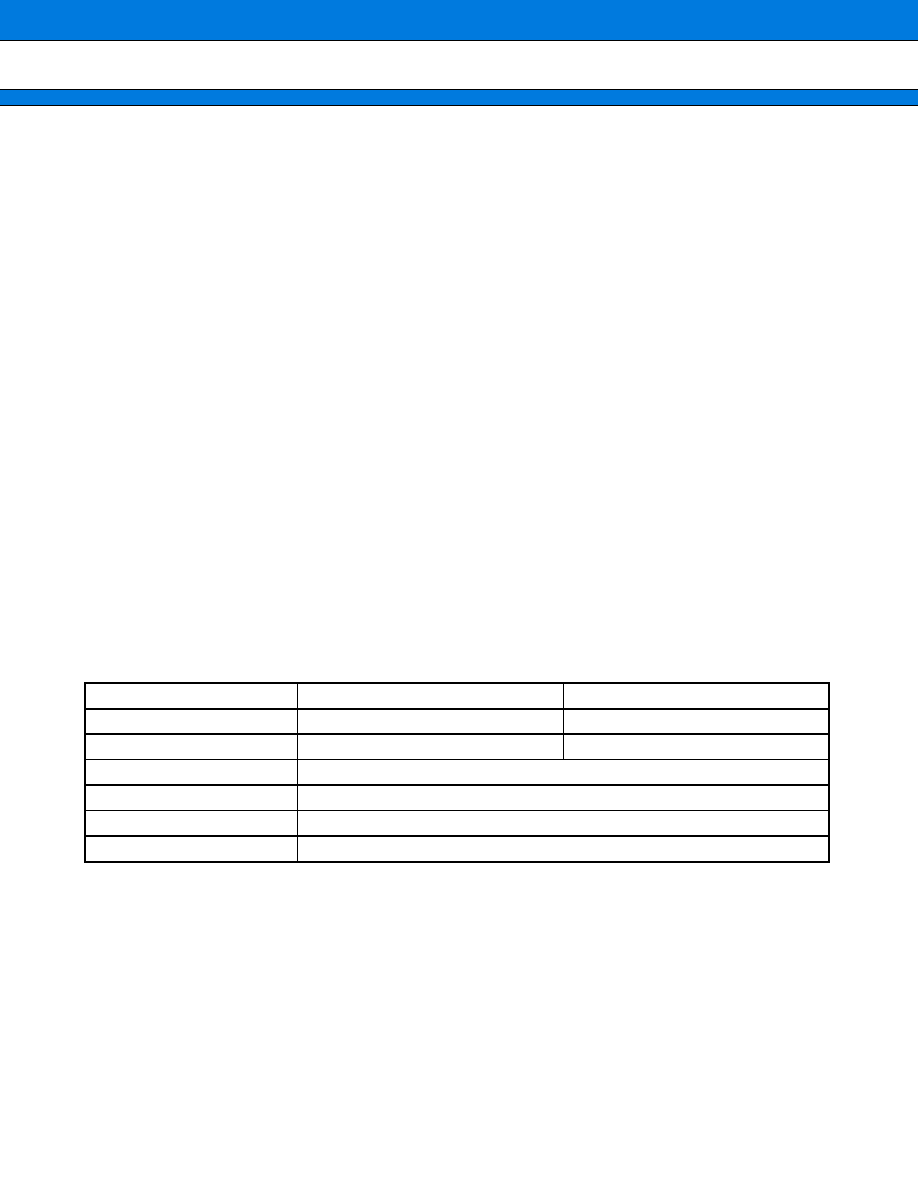

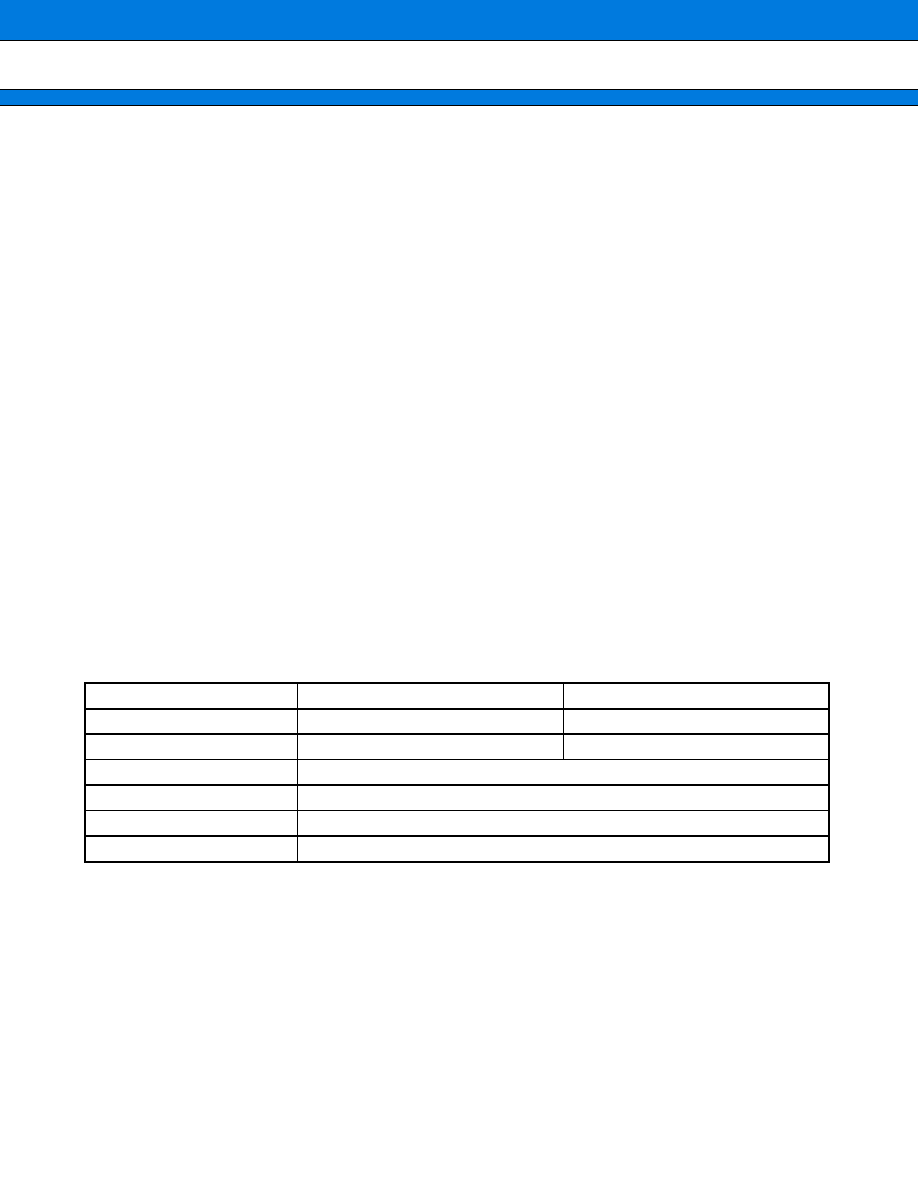

PRODUCT LINEUP

These specifications have indicated two kinds of following products.

Part number

MB93423BGL-GE1

MB93423-26BGL-GE1

Core frequency

240 MHz

266 MHz

Voltage external / internal

3.3 V

�

0.15 V / 1.8 V

�

0.1 V

3.3 V

�

0.15 V / 1.8 V

�

0.1V

Ta

0

�

C to

+

70

�

C

Package (Code)

PFBGA337 (BGA-337P-M03)

Thermal resistance Rth (ja)

45

�

C/W (0 m/s)

Remarks

Lead-free Solder ball

MB93423

5

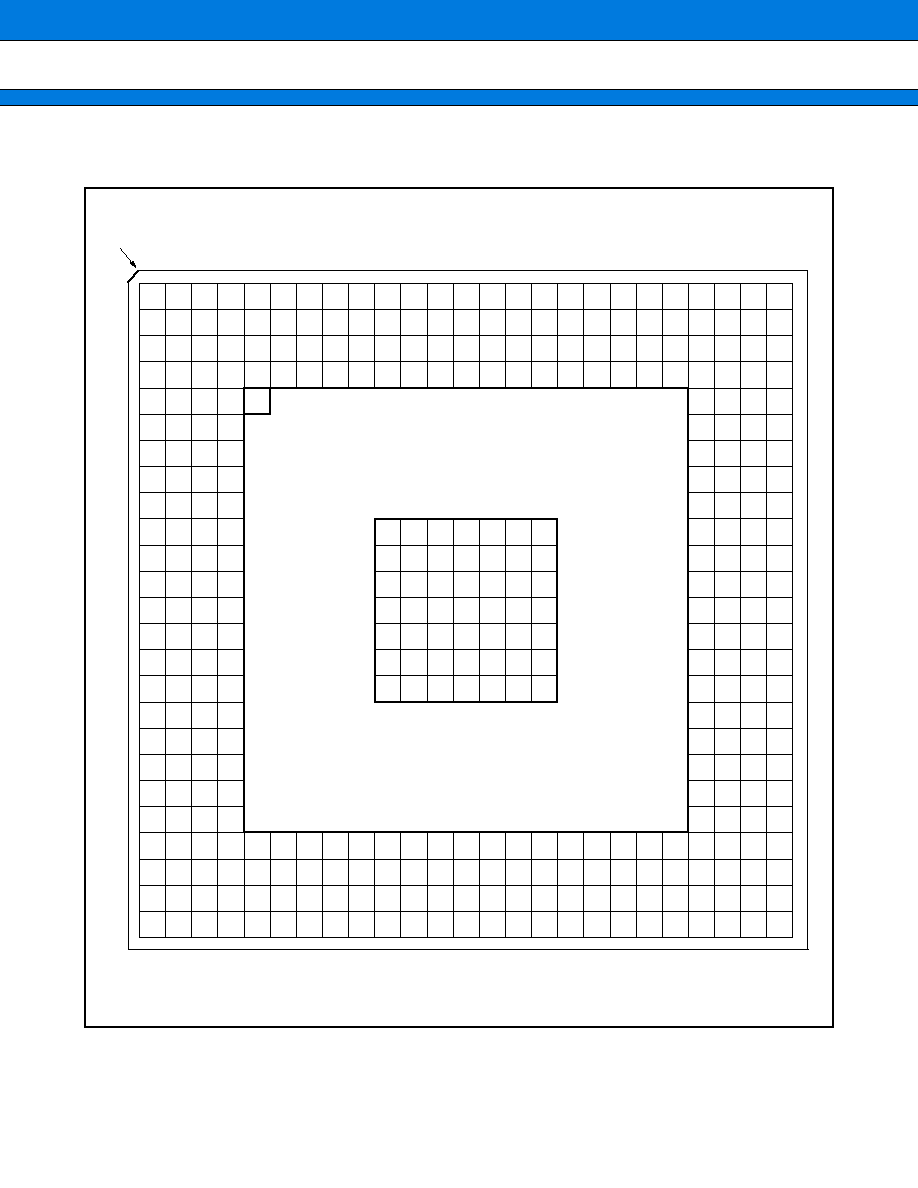

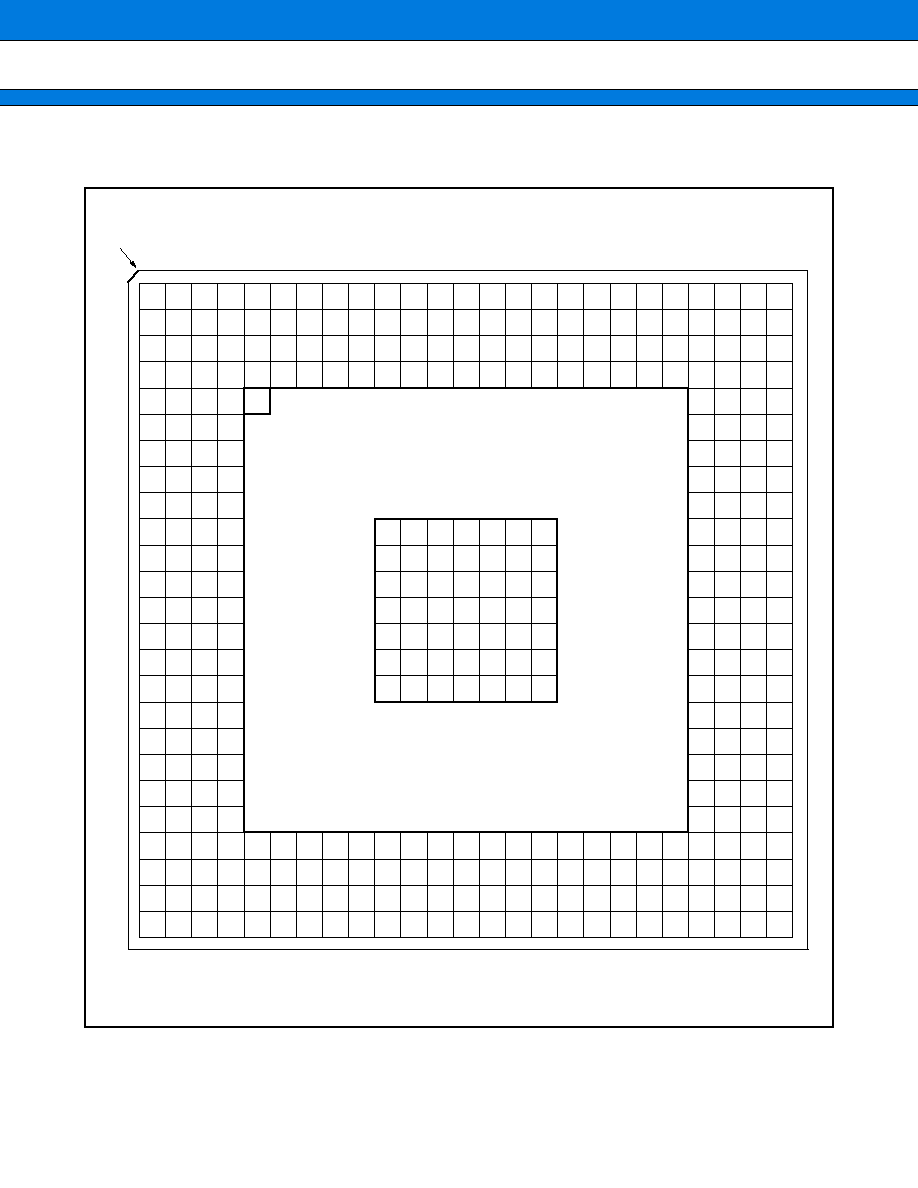

PIN ASSIGNMENT

49 pins from K10 to T16 are for thermal. Connect them to VSS.

INDEX

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

74

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

48

75

164

245

244

243

242

241

240

239

238

237

236

235

234

233

232

231

230

229

228

227

226

225

140

47

300

223

138

45

77

166

247

320

78

167

248

321

299

222

137

44

79

168

249

322

298

221

136

43

297

220

135

42

80

169

250

323

81

170

251

324

296

219

134

41

82

171

252

325

295

218

133

40

83

172

253

326

294

217

132

39

84

173

254

327

293

216

131

38

85

174

255

328

292

215

130

37

86

175

256

329

291

214

129

36

87

176

257

330

290

213

128

35

88

177

258

331

289

212

127

34

89

178

259

332

288

211

126

33

90

179

260

333

287

210

125

32

91

180

261

334

286

209

124

31

92

181

262

335

285

208

123

30

93

182

263

336

337

284

207

122

29

94

183

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

206

121

28

95

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

120

27

76

165

246

319

318

317

316

315

314

313

312

311

310

309

308

307

306

305

304

303

302

301

224

139

46

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

26

25

24

23

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

22

1

2

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

(BGA-337P-M03)

(TOP-VIEW)