Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

1

G751

Global Mixed-mode Technology Inc.

Digital Temperature Sensor and Thermal Watchdog

with Two-Wire Interface

Features

SMBus interface

Programmable Trip Point (T

OS

) and Hysteresis

(T

HYST

)

Separate open-drain output pin operates as

interrupt or comparator at output

Register readback capability

Power up defaults permit stand-alone opera-

tion as thermostat

Shutdown mode to minimize power consump-

tion

Up to 8 G751s can be connected to a single

bus

Key Specifications

Supply Voltage 3.0V to 5.5V

Supply Current operating 280�A (typ)

1mA (max)

shutdown 2�A(typ)

Temperature Accuracy

-25�C to 100�C �2�C (max)

-55�C to 125�C �3�C (max)

Applications

System Thermal Management

Personal Computers

Office Electronics

Electronic Test Equipment

Pin Configuration

General Description

The G751 is a temperature sensor, Delta-Sigma

analog-to-digital converter, and digital over- tem-

perature detector with SMBus

interface. The host

can query the G751 at any time to read temperature.

The open-drain Over temperature Shutdown (O.S.)

output becomes active when the temperature ex-

ceeds a programmable limit. This pin can operate in

either "Comparator" or "Interrupt" mode.

The host can program both the temperature alarm

threshold (T

OS

) and the temperature at which the

alarm condition goes away (T

HYST

). In addition, the

host can read back the contents of the G751's T

OS

and T

HYST

registers. The sensor powers up in Com-

parator mode with default thresholds of 50�C T

OS

45�C T

HYST.

for G751-1 and 80�C T

OS

, 75�C T

HYST

for G751-2.

Ordering Information

PART T

OS

T

HYST

TRANSPORT

MEDIA

PACKAGE

G751-1P1 50�C/45�C

2500 Units on Tape

and Reel

8 SOP

G751-2P1 80�C

/75�C

2500 Units on Tape

and Reel

8 SOP

G751-2P8 80�C

/75�C

2500 Units on Tape

and Reel

8 MSOP

P1: 8 SOP; P8: 8 MSOP

Typical Application

SMBDATA

8Pin SOP/MSOP

1

2

3

4

5

6

7

8

G751

+Vs

A0

A1

A2

SMBCLK

O.S.

GND

G751

+V

S

3V to 5.5V

Typical Bypass 0.1 �F

(Unless mounted close

to Processor)

To Processor

Interrupt Line

O.S. Set for active low for

wire OR'd multiple

interrupt line

Address(Set as

desired)

Interface

8

3

O.S. Out

4

7

6

5

1

2

A0

A1

A2

SMBDATA

SMBCLK

SMBDATA

8Pin SOP/MSOP

1

2

3

4

5

6

7

8

G751

+Vs

A0

A1

A2

SMBCLK

O.S.

GND

G751

+V

S

3V to 5.5V

Typical Bypass 0.1 �F

(Unless mounted close

to Processor)

To Processor

Interrupt Line

O.S. Set for active low for

wire OR'd multiple

interrupt line

Address(Set as

desired)

Interface

8

3

O.S. Out

4

7

6

5

1

2

A0

A1

A2

SMBDATA

SMBCLK

G751

+V

S

3V to 5.5V

Typical Bypass 0.1 �F

(Unless mounted close

to Processor)

To Processor

Interrupt Line

O.S. Set for active low for

wire OR'd multiple

interrupt line

Address(Set as

desired)

Interface

8

3

O.S. Out

4

7

6

5

1

2

A0

A1

A2

SMBDATA

SMBCLK

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

2

G751

Global Mixed-mode Technology Inc.

Absolute Maximum Ratings.

Supply Voltage..................................-0.3V to 6.5V

Voltage at any Pin......................-0.3V to +Vs +0.3V

Input Current at any Pin..................................5mA

Package Input Current..................................20mA

O.S. Output Sink Current...............................10mA

O.S. Output Voltage.......................................6.5V

Storage Temperature.....................-65�C to +150�C

Soldering Information, Lead Temperature

SOP Package

Vapor Phase (60 seconds)............................215�C

Infrared (15 seconds)...................................220�C

ESD Susceptibility

Human Body Model.....................................2000V

Machine Model.............................................200V

Operating Ratings

Specified Temperature Range................T

MIN

to T

MAX

-55�C

to

+125�C

Supply Voltage Range (+Vs)..............+3.0V to +5.5V

Temperature-to-Digital Converter Characteristics

Unless otherwise noted, these specifications apply for +Vs=+3.3v Vdc. Boldface limits apply for T

A

=T

J

=T

MIN

to

T

MAX

; all other limits T

A

=T

J

= +25�C, unless otherwise noted.

PARAMETER CONDITIONS

TYPICAL

LIMITS

UNITS

Accuracy

TA=-25�C to +100�C

TA=-55�C to +125�C

�

2.0

�

3.0

�C (max)

Resolution

9

Bits

Temperature Conversion Time

100

Ms

Quiescent Current

SMBus Inactive

SMBus Active

Shutdown Mode

0.

25

1

1.0

Ma

mA (max)

�A

O.S. Output Saturation Voltage

I

OUT

= 4.0mA

0.8

V (max)

O.S. Delay

1

6

Conversions (min)

Conversions (max)

T

OS

Default Temperature G751-1/G751-2

50/80

�C

T

HYST

Default Temperature G751-1/G751-2

45/75

�C

Block Diagram

Silicon

Bandgap

Temperature

Sensor

Configuration

Register

Pointer

Register

T

HYST

Set Point

Register

Temperature

Threshold

Set Point

Comparator

Reset

T

OS

Set Point

Register

Two-Wire Interface

9-Bit Delta-Sigma

Analog-to-Digital

Converter

4

1

2

3

O.S.

7

6

5

A0

A1

A2

8

+V

S

3.0V - 5.5V

SMBDATA

SMBCLK

Silicon

Bandgap

Temperature

Sensor

Configuration

Register

Pointer

Register

T

HYST

Set Point

Register

Temperature

Threshold

Set Point

Comparator

Reset

T

OS

Set Point

Register

Two-Wire Interface

9-Bit Delta-Sigma

Analog-to-Digital

Converter

4

1

2

3

O.S.

7

6

5

A0

A1

A2

8

+V

S

3.0V - 5.5V

SMBDATA

SMBCLK

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

3

G751

Global Mixed-mode Technology Inc.

Logic Electrical Characteristics

Digital DC Characteristics

Unless otherwise noted, these specifications apply for +Vs=+3.3 Vdc. Boldface limits apply for T

A

=T

J

=T

MIN

to

T

MAX

; all other limits T

A

=T

J

=+25�C, unless otherwise noted.

SYMBOL PARAMETER

CONDITIONS TYPICAL

LIMITS

UNITS

V

IN (1)

Logical "1" Input Voltage

+Vs���� 0.7

+Vs + 0.5

V (min)

V (max)

V

IN (0)

Logical "0" Input Voltage

-0.3

+Vs����0.3

V (min)

V (max)

I

IN (1)

Logical "1"Intput Current

V

IN

=5V 0.005

1.0

�A

I

IN (0)

Logical "0"Intput Current

V

IN

=0V -0.005

-1.0

�A

C

IN

All Digital Inputs

20

PF

I

OH

High Level Output Current

V

OH

=5V

100

�A (max)

V

OL

Low Level Output Voltage

I

OL

=3ma

0.4

V (max)

t

OF

Output Fall Time

C

L

=400pF,I

O

=3ma 250

ns (max)

SMBus Digital Switching Characteristics

Unless otherwise noted, these specifications apply for +Vs = +3.3 Vdc and C

L

(load capacitance) on output lines =

80pF unless otherwise specified. Boldface limits apply for T

A

= T

J

= T

MIN

to T

MAX

; all other limits T

A

= T

J

= +25�C,

unless otherwise noted.

The switching characteristics of the G751 fully meet or exceed the published specifications of the SMBus. The

following parameters are the timing relationships between SMBCLK and SMBDATA signals related to the G751.

They are not the SMBus specifications.

SYMBOL PARAMETER CONDITIONS

TYPICAL

LIMITS

UNITS

t

1

SMBCLK (Clock) Period

2.5

�s (min)

t

2

Data in Set-Up Time to SMBCLK High

100

ns (min)

t

3

Data Out Stable after SMBCLK Low

0

ns (min)

t

4

SMBDATA Low Set-Up Time to SMBCLK Low (Start Condition)

100

ns (min)

t

5

SMBDATA High Hold Time after SMBCLK High (Stop Condition)

100

ns (min)

Pin Description

PIN LABEL

FUNCTION

TYPICAL

CONNECTION

1

SMBDATA SMBus Serial Bi-Directional Data Line

From Controller

2

SMBCLK SMBus Clock Input

From Controller

3

O.S.

Overtemperature Shutdown Open Drain Output

Pull Up Resistor, Controller Interrupt Line

4

GND

Power Supply Ground

Ground

5,6,7

A0-A2 User-Set SMBus Address Inputs

Ground (Low, "0") or +Vs (High, "1")

8

+Vs

Positive Supply Voltage Input

DC Voltage from 3V to 5.5V

Logic Electrical Characteristics

SMBCLK

SMBDATA

Data in

SMBDATA

Data out

t

1

t

4

t

2

t

5

t

3

SMBCLK

SMBDATA

Data in

SMBDATA

Data out

t

1

t

4

t

2

t

5

t

3

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

4

G751

Global Mixed-mode Technology Inc.

0,1111,1010

+125�C

-55�C

-25�C

-0.5�C

0�C

+0.5�C

+25�C

Temperature

O

u

t

p

u

t

Code

0,0011,0010

0,0000,0001

0,0000,0000

1,1111,1111

1,1100,1110

1,1001,0010

Temperature-to-Digital Transfer Function (Non-linear scale for clarity)

Functional Description

The G751 temperature sensor incorporates a

band-gap type temperature sensor and 9-bit ADC

(Delta-Sigma Analog- to-Digital Converter). The

temperature data output of the G751 is available at

all times via the SMBus. If a conversion is in pro-

gress, it will be stopped and restarted after the read.

A digital comparator is also incorporated that com-

pares a series of readings, the number of which is

user-selectable, to user-programmable setpoint and

hysteresis values. The comparator trips the O.S.

output line, which is programmable for mode and

polarity.

O.S. Output, T

OS

and T

HYST

Limits

In Comparator mode the O.S. Output behaves like a

thermostat. The output becomes active when tem-

perature exceeds the T

OS

limit, and leaves the active

state when the temperature drops below the T

HYST

limit. In this mode the O.S. output can be used to

turn a cooling fan on, initiate an emergency system

shutdown, or reduce system clock speed. Shutdown

mode does not reset O.S. state in a comparator

mode.

In interrupt mode exceeding T

OS

also makes O.S.

active but O.S. will remain active indefinitely until

reset by reading any register via the SMBus inter-

face. Once O.S. has been activated by crossing T

OS

,

then reset, it can activated again only by Tempera-

ture going below T

HYST

. Again, it will remain active

indefinitely until being reset by a read. Placing the

G751 in shutdown mode also resets the O.S. output.

Default Modes

G751 always powers up in a known state. G751

power up default conditions are:

1. Comparator mode

2. T

OS

set to 50�C for G751-1, to 80�C for G751-2

3. T

HYST

set to 45�C for G751-1, to 75�C for G751-2

4. O.S. active low

5. Pointer set to "00"; Temperature Register

With these operating conditions G751 can act as a

stand-alone thermostat with the above temperature

settings. Connection to an SMBus is not required.

SMBus Interface

The G751 operates as a slave on the SMBus, so the

SMBCLK line is an input (no clock is generated by

the G751) and the SMBDATA line is a bi-directional

serial data path. According to SMBus specifications,

the G751 has a 7-bit slave address. The four most

significant bits of the slave address are hard wired

inside the G751 and are "1001". The three least sig-

nificant bits of the address are assigned to pins

A2-A0, and are set by connecting these pins to

ground for a low, (0); or to +Vs for a high, (1).

Therefore, the complete slave address is:

1 0 0 1 A2

A1

A0

MSB LSB

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

5

G751

Global Mixed-mode Technology Inc.

Figure1 O.S. Output Temperature Response Diagram

Temperature Data Format

Temperature data can be read from the Temperature,

T

OS

Set Point, and T

HYST

Set Point registers; and

written to the T

OS

Set Point, and T

HYST

Set Point reg-

isters. Temperature data is represented

by a 9-bit, two's complement word with an LSB

(Least Significant Bit) equal to 0.5�C:

DIGITAL OUTPUT

TEMPERATURE

BINARY HEX

+125�C 0

1111

1010

0FAh

+25�C 0

0011

0010

032h

+0.5�C 0

0000

0001

001h

0�C 0

0000

0000

000h

-0.5�C 1

1111

1111

1FFh

-25�C 1

1100

1110

1CEh

-55�C 1

1001

0010

192h

Shutdown Mode

Shutdown mode is enabled by setting the shutdown

bit in the Configuration register via the SMBus. Shut-

down mode reduces power supply current to 1 �A

typical. In interrupt mode O.S. is reset if previously

set and is undefined in Compatator mode during

shutdown. The SMBus interface remains active. Ac-

tivity on the clock and data lines of the SMBus may

slightly increase shutdown mode quiescent current.

T

OS

, T

HYST

, and Configuration registers can be read

from and written to in shutdown mode.

Fault Queue

A fault queue of up to 6 faults is provided to prevent

false tripping of O.S. when the G751 is used in noisy

environments. The number of faults set in the queue

must occur consecutively to set the O.S. output.

Comparator/Interrupt Mode

As indicated in the O.S. Output Temperature Re-

sponse Diagram, Figure 1, the events that trigger

O.S. are identical for either Comparator or Interrupt

mode. The most important difference is that in Inter-

rupt mode the O.S. will remain set indefinitely once it

has been set. To reset O.S. while in Interrupt mode,

perform a read from any register in the G751.

O.S. Output

The O.S. output is an open-drain output and does

not have an internal pull-up. A "high" level will not be

observed on this pin until pull-up current is provided

from some external source, typically a pull-up resis-

tor. Choice of resistor value depends on many sys-

tem factors but, in general, the pull-up resistor

should be as large as possible. This will minimize

any errors due to internal heating of the G751. The

maximum resistance of the pull up, based on G751

specification for High Level Output Current, to pro-

vide a 2V high level, is 30k

.

O.S. Polarity

The O.S. output can be programmed via the con-

figuration register to be either active low (default

mode), or active high. In active low mode the O.S.

output goes low when triggered exactly as shown on

the O.S. Output Temperature Response Diagram,

Figure 1. Active high simply inverts the polarity of the

O.S. output.

T

OS

T

HY

S

T

O.

S.

(Com

pa

r

a

tor M

o

de

)

O.

S.

(In

t

errup

t

M

o

de

)

Ti

m

e

T

e

m

per

at

u

r

e res

pon

s

e

S

h

o

w

n

fo

r

O

.

S

.

s

e

t fo

r

a

c

ti

v

e

l

o

w

.

*

r

e

a

d a

n

y

r

e

g

i

s

t

e

r

or pl

a

c

e

d

in

s

hut

d

o

w

n

*

*

*

T

OS

T

HY

S

T

O.

S.

(Com

pa

r

a

tor M

o

de

)

O.

S.

(In

t

errup

t

M

o

de

)

Ti

m

e

T

e

m

per

at

u

r

e res

pon

s

e

S

h

o

w

n

fo

r

O

.

S

.

s

e

t fo

r

a

c

ti

v

e

l

o

w

.

*

r

e

a

d a

n

y

r

e

g

i

s

t

e

r

or pl

a

c

e

d

in

s

hut

d

o

w

n

*

*

*

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

6

G751

Global Mixed-mode Technology Inc.

Internal Register Structure

There are four data registers in the G751, selected

by the Pointer register. At power-up the Pointer is set

to "00"; the location for the Temperature Register.

The Pointer register latches whatever the last loca-

tion it was set to. In Interrupt Mode, a read from the

G751, or placing the device in shutdown mode, re-

sets the O.S. output. All registers are read and write,

except the Temperature register which is read only.

A write to the G751 will always include the address

byte and the Pointer byte. A write to the Configura-

tion register requires one data byte, and the T

OS

and

T

HYST

registers require two data bytes.

Reading the G751 can take place either of two ways:

If the location latched in the Pointer is correct (most

of the time it is expected that the Pointer will point to

Temperature register because it will be the data

most frequently read from the G751), then the read

can simply consist of an address byte, followed by

retrieving the corresponding number of data bytes. If

the Pointer needs to be set, than an address byte,

pointer byte, repeat start, and another address byte

will accomplish a read.

The first data byte is the most significant byte with

most signification bit first, permitting only as much

data as necessary to be read to determine tempera-

ture condition. For instance, if the first four bits of the

temperature data indicates an overtemperature con-

dition, the host processor could immediately take

action to remedy the excessive temperatures. At the

end of a read, the G751 can accept either Acknowl-

edge or No Acknowledge from the Master (No Ac-

knowledge is typically used as a signal for the salve

that the Master has read its last byte).

An inadvertent 8-bit read from a 16-bit register, with

the D7 bit low, can cause the G751 to stop in a state

where the SDA line is held low as shown in Figure 2.

This can prevent any further bus communication until

at least 9 additional clock cycles have occurred. Al-

ternatively, the master can issue clock cycles until

SDA goes high, at which time issuing a "Stop" condi-

tion will reset the G751.

Figure 2. Inadvertent 8-Bit Read from 16-Bit Register where D7 is Zero

Interface

Pointer Register

(Selects register for

communication

Temperature

(Read-only)

Pointer = 00000000

TOS Set Point

(Read-write)

Pointer = 00000011

Configuration

(Read-write, sets operating

Mode)

Pointer = 00000001

THYST Set Point

(Read-write)

Pointer = 00000010

Register Select

Address

Data

SMBDATA

SMBCLK

Interface

Pointer Register

(Selects register for

communication

Temperature

(Read-only)

Pointer = 00000000

TOS Set Point

(Read-write)

Pointer = 00000011

Configuration

(Read-write, sets operating

Mode)

Pointer = 00000001

THYST Set Point

(Read-write)

Pointer = 00000010

Register Select

Address

Data

SMBDATA

SMBCLK

A2

A1

A0

D15

D14

D13

D12

D11

D10

D9

D8

D6

D5

D4

D3

D2

D1

D0

SMBCLK

SMBDATA

Start

by

Master

Address Byte

R/W

Bit

Ack

by

G751

Most Significant

Data Byter

Ack

by

Master

D7

Intended Stop by

Master but G751 locks SMBDATA low

Master detects the error

of its ways

Ack

by

Master

Stop

Cond

by

Master

A2

A1

A0

D15

D14

D13

D12

D11

D10

D9

D8

D6

D5

D4

D3

D2

D1

D0

SMBCLK

SMBDATA

Start

by

Master

Address Byte

R/W

Bit

Ack

by

G751

Most Significant

Data Byter

Ack

by

Master

D7

Intended Stop by

Master but G751 locks SMBDATA low

Master detects the error

of its ways

Ack

by

Master

Stop

Cond

by

Master

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

7

G751

Global Mixed-mode Technology Inc.

Pointer Register

(Selects which registers will be read from or written to):

P7 P6 P5 P4 P3 P2 P1 P0

0 0 0 0 0 0 Register

Select

P0-P1 :Register Select:

P1 P0

REGISTER

0

0

Temperature (Read only) (Power-up default)

0 1

Configuration

(Read/Write)

1 0

T

HYST

(Read/Write)

1 1

T

OS

(Read/Write)

P2-P7 :Must be kept zero.

Temperature Register

(Read Only):

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

MSB

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

LSB

X

X

X

X

X

X

X

D0-D6 :Undefined

D7-D15 :Temperature Data. One LSB = 0.5�C. Two's complement format.

Configuration Register

(Read/Write):

D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 Fault

Queue

O.S.

Polarity

Cmp/Int

Shutdown

Power up default is with all bits "0" (zero).

D0 :Shutdown : When set to 1 the G751 goes to low power shutdown mode.

D1 :Comparator / Interrupt mode : 0 is Comparator mode, 1 is Interrupt mode.

D2 :O.S. Polarity : 0 is active low, 1 is active high. O.S. is an open-drain output under all conditions.

D3-D4 :Fault Queue : Number of faults necessary to detect before setting O.S. output to avoid false tripping due

to noise :

D4 D3

NUMBER

OF

FAULTS

0

0

1 (Power-up default)

0 1 2

1 0 4

1 1 6

D5-D7 :These bits are used for production testing and must be kept zero for normal operation.

T

HYST

and T

OS

Register

(Read/Write):

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

MSB

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

LSB

X

X

X

X

X

X

X

D0-D6 :Undefined

D7-D15 :T

HYST

Or T

OS

Trip Temperature Data. Power up default is T

OS

= 50�C /80�C for G751-1/G751-2, T

HYST

=

45�C /75�C for G751-1/G751-2.

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

8

G751

Global Mixed-mode Technology Inc.

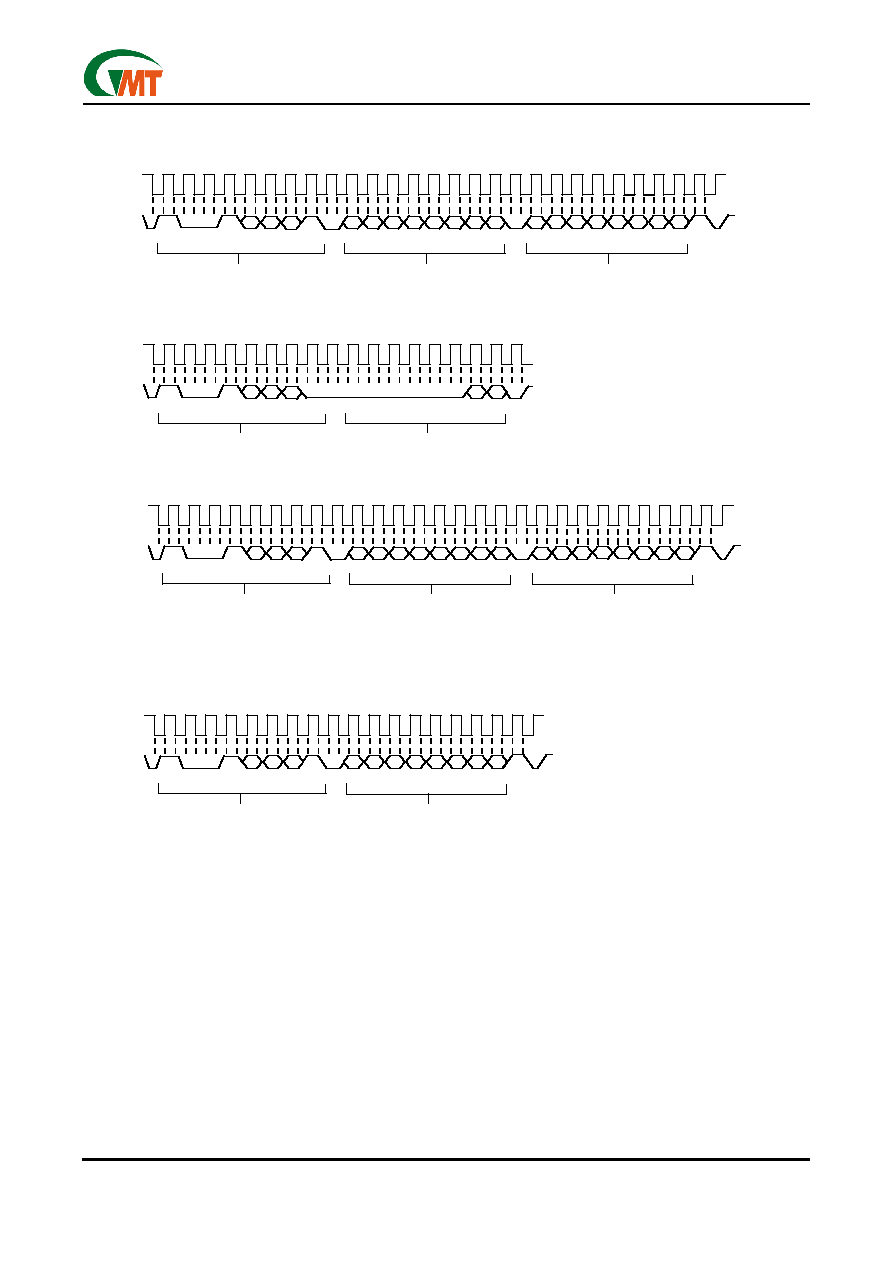

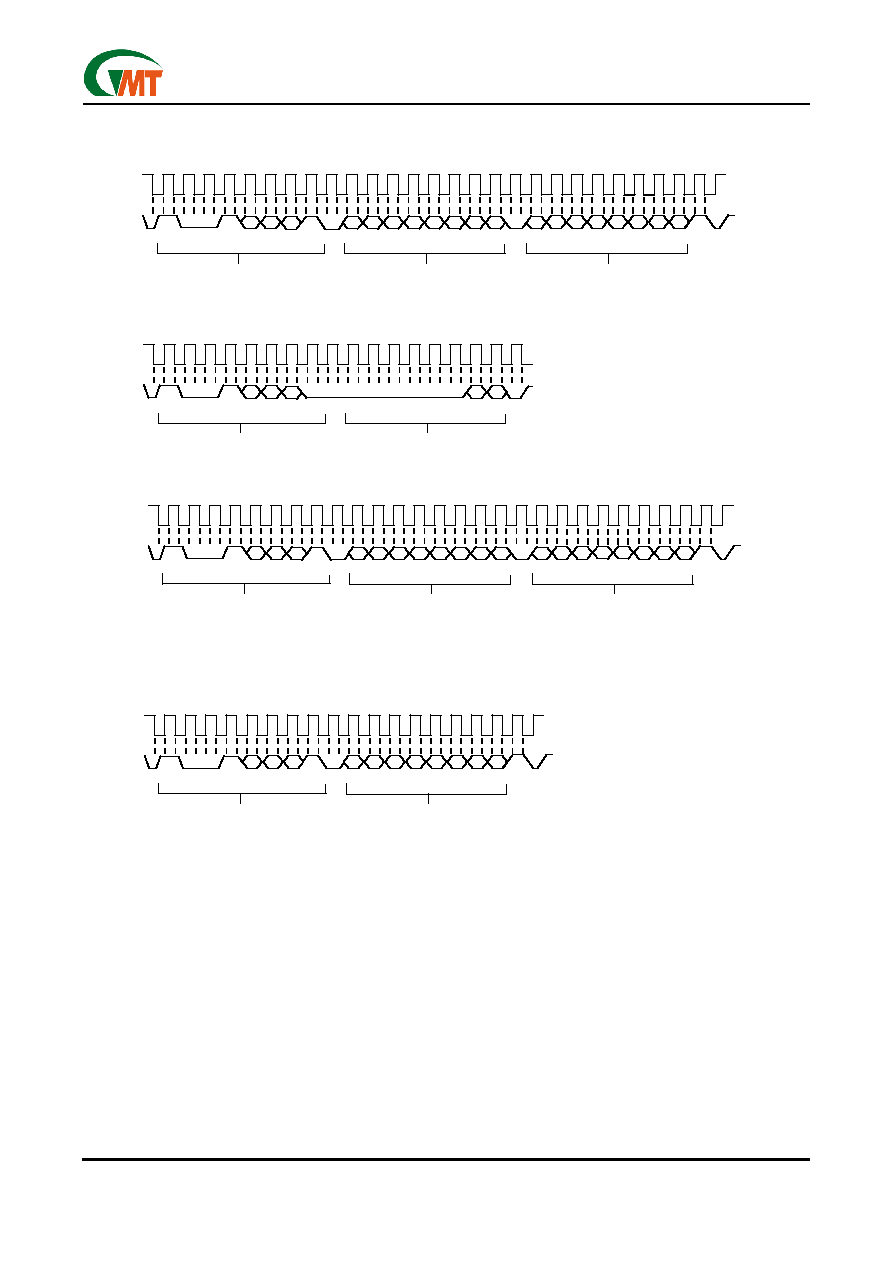

SMBus Timing Diagrams

Start

by

Master

Address Byte

R/W

Ack

by

G751

Pointer Byte

Ack

by

G751

1

0

0

1

9

1

9

1

0

0

0

0

0

0

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

Start

by

Master

Address Byte

R/W

Ack

by

G751

Most Significant Data Byte

Ack

by

Master

D7

No Ack

by

Master

Stop

Cond

by

Master

D7

D6

D4

D5

D3

1

0

0

1

Least Significant Data Byte

9

1

9

1

9

1

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

Repeat

Start

by

Master

Address Byte

R/W

Ack

by

G751

Most Significant Data Byte

Ack

by

Master

D7

No Ack

by

Master

Stop

Cond

by

Master

D7

D6

D4

D5

D3

1

0

0

1

Least Significant Data Byte

9

1

9

1

9

1

A2

A1

A0

D1

D0

Start

by

Master

Address Byte

R/W

Ack

by

G751

Pointer Byte

Ack

by

G751

1

0

0

1

9

1

9

1

D7

D6

D5

D4

D3

D2

Stop

Cond

by

Master

D1

D0

A2

A1

A0

Start

by

Master

Address Byte

R/W

Ack

by

G751

Pointer Byte

Ack

by

G751

1

0

0

1

9

1

9

1

0

0

0

0

0

0

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

Start

by

Master

Address Byte

R/W

Ack

by

G751

Most Significant Data Byte

Ack

by

Master

D7

No Ack

by

Master

Stop

Cond

by

Master

D7

D6

D4

D5

D3

1

0

0

1

Least Significant Data Byte

Least Significant Data Byte

9

1

9

1

9

1

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

D2

D1

D0

Repeat

Start

by

Master

Address Byte

R/W

Ack

by

G751

Most Significant Data Byte

Ack

by

Master

D7

No Ack

by

Master

Stop

Cond

by

Master

D7

D6

D4

D5

D3

1

0

0

1

Least Significant Data Byte

Least Significant Data Byte

9

1

9

1

9

1

A2

A1

A0

D1

D0

Start

by

Master

Address Byte

R/W

Ack

by

G751

Pointer Byte

Ack

by

G751

1

0

0

1

9

1

9

1

D7

D6

D5

D4

D3

D2

Stop

Cond

by

Master

D1

D0

A2

A1

A0

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

9

G751

Global Mixed-mode Technology Inc.

Timing Diagrams (Continued)

St

o

p

Co

n

d

by

Ma

s

t

e

r

A2

A1

A0

D0

R/

W

D5

D4

D3

D2

D1

A2

A1

A0

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

No

Ac

k

by

Ma

s

t

e

r

1

0

0

1

A

ddr

ess

By

t

e

9

1

9

1

9

1

9

D0

D7

D6

1

0

0

1

D1

0

0

0

0

0

0

Re

pe

a

t

St

a

r

t

by

Ma

s

t

e

r

D

a

ta

B

y

te

Ack

by

G7

5

1

A2

A1

A0

D3

D2

D1

D0

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

Ack

by

G7

5

1

St

o

p

Co

n

d

by

Ma

s

t

e

r

D4

1

0

0

1

Conf

i

gur

at

i

on B

y

t

e

9

1

9

1

9

1

0

0

0

D0

D1

0

0

0

0

0

0

A2

A1

A0

D0

D5

D4

D3

D2

D1

D3

D2

D1

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

Ack

by

G7

5

1

St

o

p

Co

n

d

by

Ma

s

t

e

r

1

0

0

1

M

o

s

t

S

i

g

n

i

f

ica

n

t

D

a

ta

B

y

te

9

1

9

1

9

1

9

D0

D7

D6

0

0

0

0

0

0

Le

ast

S

i

gn

i

f

i

c

ant

Dat

a

By

t

e

Ack

by

G7

5

1

D1

D0

D4

D7

D6

D5

1

(

a

)

Ty

pi

cal

Poi

n

ter

Set f

o

l

l

o

w

ed by

Im

m

e

di

ate R

e

a

d

f

r

o

m

C

o

nfi

gur

at

i

o

n

Regi

ster

(

b

)

C

o

n

f

i

g

ur

ati

on Regi

st

e

r

W

r

i

t

e

(c) T

OS

and T

HY

S

T

Wr

i

t

e

St

o

p

Co

n

d

by

Ma

s

t

e

r

A2

A1

A0

D0

R/

W

D5

D4

D3

D2

D1

A2

A1

A0

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

No

Ac

k

by

Ma

s

t

e

r

1

0

0

1

A

ddr

ess

By

t

e

A

ddr

ess

By

t

e

9

1

9

1

9

1

9

D0

D7

D6

1

0

0

1

D1

0

0

0

0

0

0

Re

pe

a

t

St

a

r

t

by

Ma

s

t

e

r

D

a

ta

B

y

te

D

a

ta

B

y

te

Ack

by

G7

5

1

A2

A1

A0

D3

D2

D1

D0

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

Ack

by

G7

5

1

St

o

p

Co

n

d

by

Ma

s

t

e

r

D4

1

0

0

1

Conf

i

gur

at

i

on B

y

t

e

9

1

9

1

9

1

0

0

0

D0

D1

0

0

0

0

0

0

A2

A1

A0

D0

D5

D4

D3

D2

D1

D3

D2

D1

St

a

r

t

by

Ma

s

t

e

r

A

ddr

ess

By

t

e

R/

W

Ack

by

G7

5

1

Po

i

n

t

e

r

B

y

t

e

Ack

by

Ma

s

t

e

r

Ack

by

G7

5

1

St

o

p

Co

n

d

by

Ma

s

t

e

r

1

0

0

1

M

o

s

t

S

i

g

n

i

f

ica

n

t

D

a

ta

B

y

te

9

1

9

1

9

1

9

D0

D7

D6

0

0

0

0

0

0

Le

ast

S

i

gn

i

f

i

c

ant

Dat

a

By

t

e

Le

ast

S

i

gn

i

f

i

c

ant

Dat

a

By

t

e

Ack

by

G7

5

1

D1

D0

D4

D7

D6

D5

1

(

a

)

Ty

pi

cal

Poi

n

ter

Set f

o

l

l

o

w

ed by

Im

m

e

di

ate R

e

a

d

f

r

o

m

C

o

nfi

gur

at

i

o

n

Regi

ster

(

b

)

C

o

n

f

i

g

ur

ati

on Regi

st

e

r

W

r

i

t

e

(c) T

OS

and T

HY

S

T

Wr

i

t

e

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

10

G751

Global Mixed-mode Technology Inc.

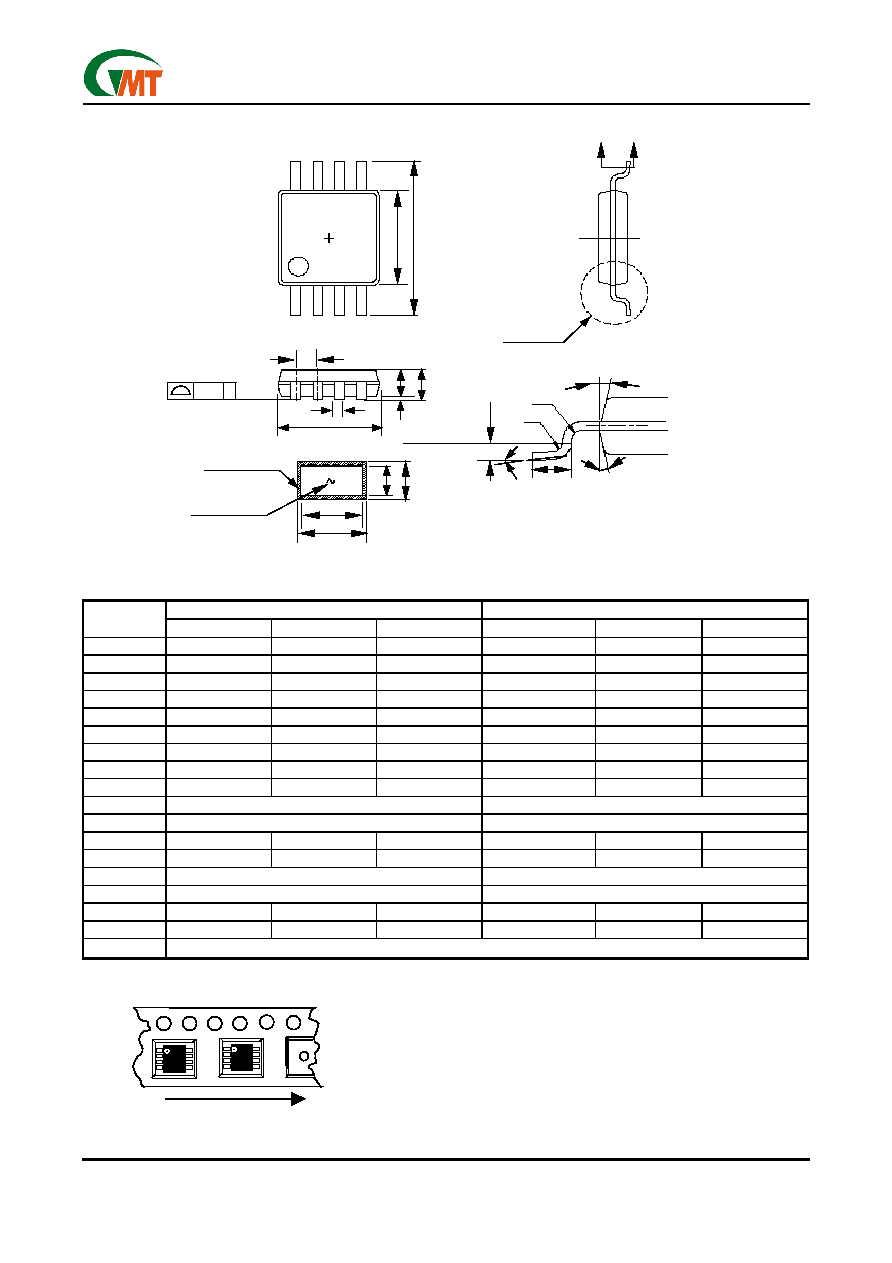

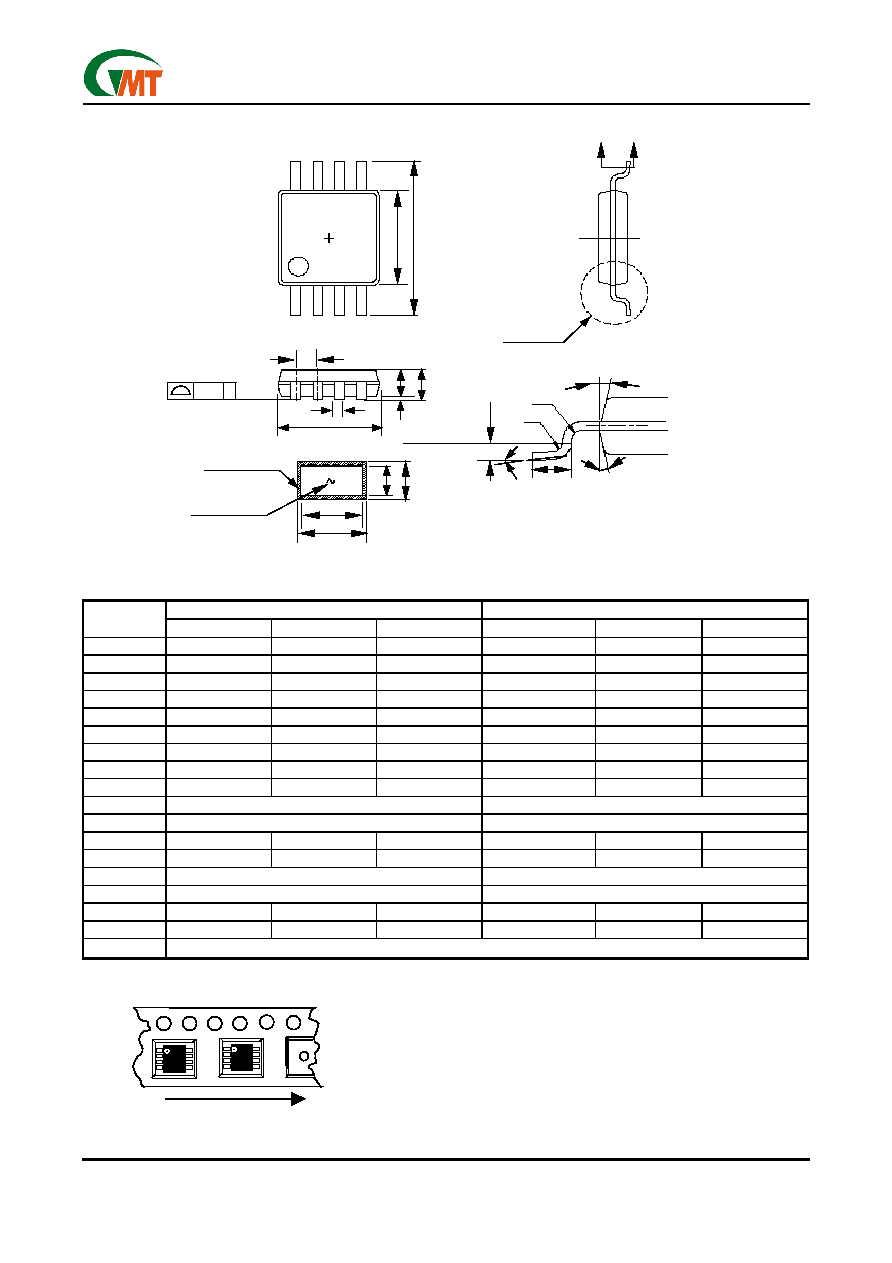

Package Information

8 Pin SOP Package

Note:

1. Package body sizes exclude mold flash and gate burrs

2. Dimension L is measured in gage plane

3. Tolerance 0.10mm unless otherwise specified

4. Controlling dimension is millimeter converted inch dimensions are not necessarily exact.

DIMENSION IN MM

DIMENSION IN INCH

SYMBOL

MIN. NOM. MAX. MIN. NOM. MAX.

A 1.35 1.60 1.75 0.053 0.063 0.069

A1 0.10 ----- 0.25 0.004

----- 0.010

A2 ----- 1.45 ----- ----- 0.057

-----

B 0.33 ----- 0.51 0.013

----- 0.020

C 0.19 ----- 0.25 0.007

----- 0.010

D 4.80 ----- 5.00 0.189

----- 0.197

E 3.80 ----- 4.00 0.150

----- 0.157

e ----- 1.27 ----- ----- 0.050

-----

H 5.80 ----- 6.20 0.228

----- 0.244

L 0.40 ----- 1.27 0.016

----- 0.050

y ----- ----- 0.10 ----- ----- 0.004

0� ----- 8� 0� ----- 8�

D

E

H

7

�

(4X)

A1

A2

A

e

B

y

C

L

Ver: 2.4

Nov 26, 2002

TEL: 886-3-5788833

http://www.gmt.com.tw

11

G751

Global Mixed-mode Technology Inc.

8 Pin MSOP Package

DIMENSION IN MM

DIMENSION IN INCH

SYMBOL

MIN. NOM. MAX. MIN. NOM. MAX.

A ----- ----- 1.10 ----- ----- 0.043

A1 0.05 ----- 0.15 0.002

----- 0.006

A2 0.81 0.86 0.91 0.032 0.034 0.036

b 0.25 ----- 0.40 0.008

----- 0.012

b1 0.25 0.30 0.35 0.010 0.012 0.014

c 0.13 ----- 0.23 0.005 0.009

c1 0.13 0.15 0.18 0.005 0.006 0.007

D 2.90 3.00 3.10 0.114 0.118 0.122

E1 2.90 3.00 3.10 0.114 0.118 0.122

e

0.65 BSC

0.026 BSC

E

4.90 BSC

0.193 BSC

L 0.445 0.55 0.648 0.0175 0.0217

0.0255

1

0

� ----- 6�

0

� ----- 6�

2

12 REF

12 REF

3

12 REF

12 REF

R 0.09 ----- ----- 0.004

----- -----

R1 0.09 ----- ----- 0.004

----- -----

JEDEC MO-187AA

Taping Specification

GMT Inc. does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and GMT Inc. reserves the right at any time without notice to change said circuitry and specifications.

Feed Direction

Typical SOP/MSOP Package Orientation

Feed Direction

Typical SOP/MSOP Package Orientation

E1

8

E

1

DETAIL "A"

A

A

CL

e

b

D

A2

A

A1

C

0.076

SEATING PLANE

b

b1

WITH PLATING

BASE METAL

c1

c

1

GAUGE PLANE

0.

2

5

R

R1

L

3

2

E1

8

E

1

DETAIL "A"

A

A

CL

e

b

D

A2

A

A1

C

0.076

SEATING PLANE

b

b1

WITH PLATING

BASE METAL

c1

c

1

GAUGE PLANE

0.

2

5

R

R1

L

3

2