Rev: 1.02 9/2001

1/11

© 1999, Giga Semiconductor, Inc.

For latest documentation see http://www.gsitechnology.com.

GS78116B

512K x 16

8Mb Asynchronous SRAM

10, 12, 15 ns

3.3 V V

DD

BGA

Commercial Temp

Industrial Temp

Features

∑ Fast access time: 10, 12, 15 ns

∑ CMOS low power operation: 300/250/220/180 mA at

minimum cycle time

∑ Single 3.3 V ± 0.3 V power supply

∑ All inputs and outputs are TTL-compatible

∑ Fully static operation

∑ Industrial Temperature Option: ≠40∞ to 85∞C

∑ 14 mm x 22 mm, 119-Bump, 1.27 mm Pitch Ball Grid Array

package

Description

The GS78116 is a high speed CMOS static RAM organized as

524,288-words by 16-bits. Static design eliminates the need for

external clocks or timing strobes. The GS78116 operates on a

single 3.3 V power supply and all inputs and outputs are TTL-

compatible. The GS78116 is available in 14 mm x 22 mm

BGA package.

Pin Descriptions

Symbol

Description

A

0

to A

18

Address input

DQ

1

to DQ

16

Data input/output

CE

Chip enable input

WE

Write enable input

OE

Output enable input

V

DD

+3.3 V power supply

V

SS

Ground

NC

No connect

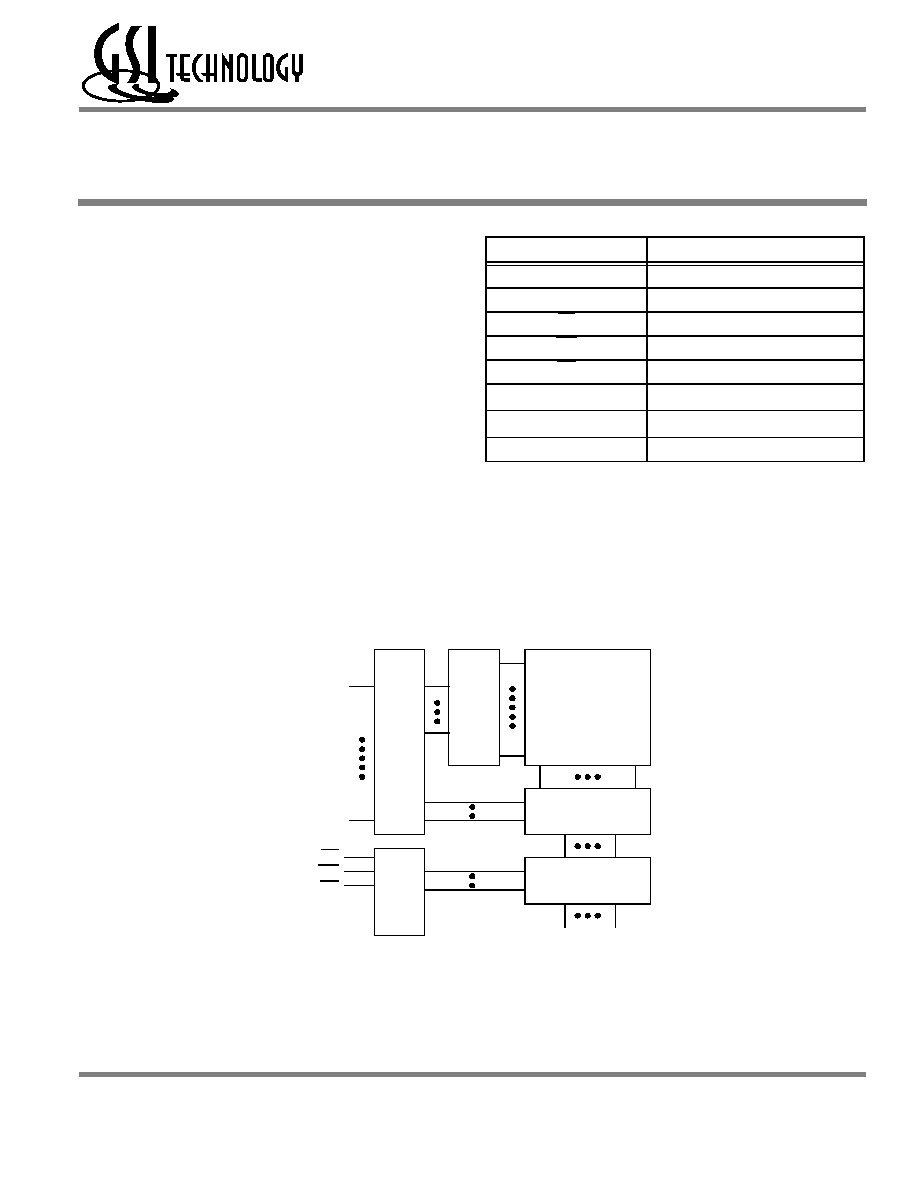

Memory Array

Row

Decoder

Column

Decoder

Address

Input

Buffer

Control

I/O Buffer

A

0

CE

WE

OE

DQ

1

A

18

Block Diagram

DQ

16

Rev: 1.02 9/2001

2/11

© 1999, Giga Semiconductor, Inc.

For latest documentation see http://www.gsitechnology.com.

GS78116B

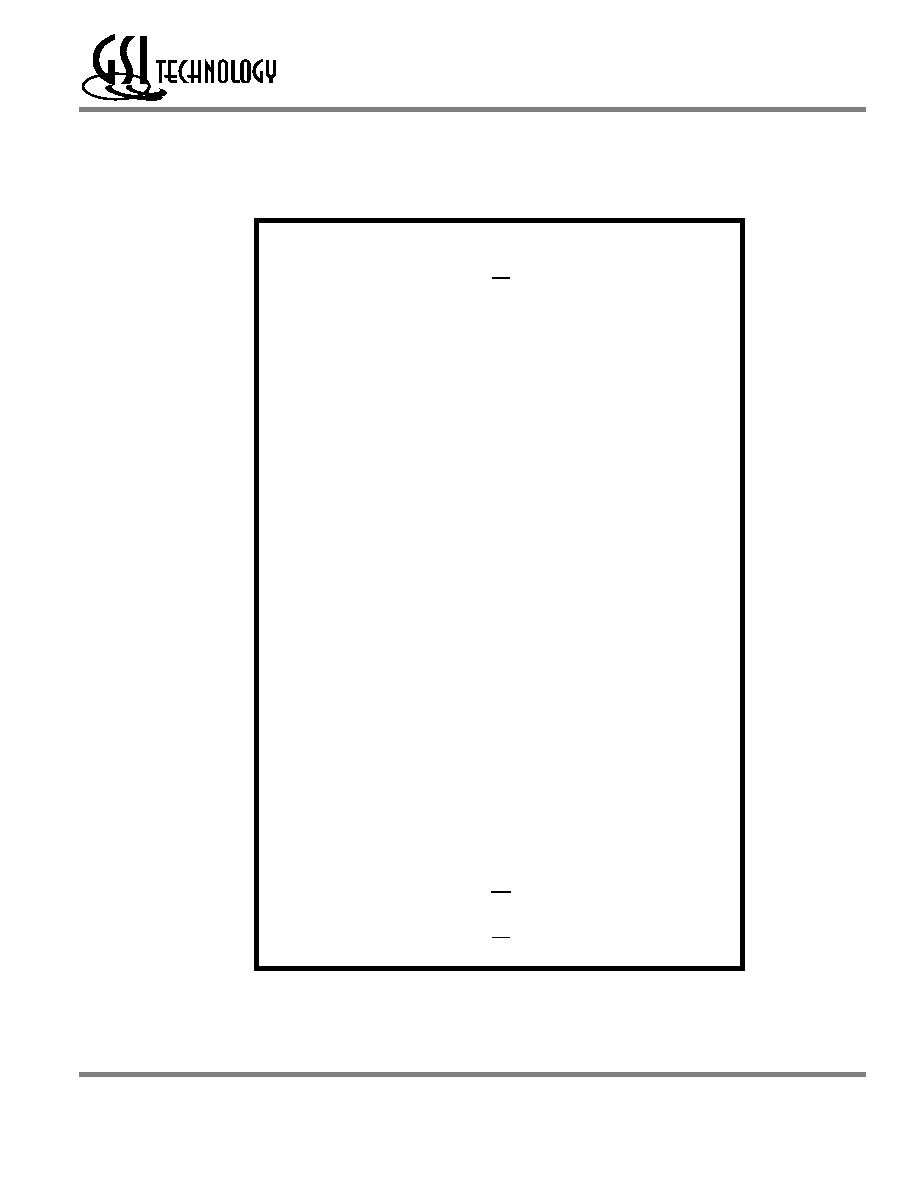

512K x 16 Async SRAM in 119-Bump, 14 mm x 22 mm

Note: Bumps 1B, 7T, 3C, and 5C are actually NC's but should be wired 3C = V

DD

and 1B, 7T and 5C = V

SS

to assure compatibility

with future versions.

Top View

1

2

3

4

5

6

7

A

NC

A

15

A

14

A

16

A

13

A

12

NC

B

NC,

V

SS

A

11

A

10

CE

A

9

A

8

NC

C

NC

NC

V

DD

,

NC

A

17

V

SS

,

NC

NC

NC

D

NC

V

DD

V

SS

V

SS

V

SS

V

DD

NC

E

DQ

1

NC

V

DD

V

SS

V

DD

NC

DQ

16

F

DQ

2

V

DD

V

SS

V

SS

V

SS

V

DD

DQ

15

G

DQ

3

NC

V

DD

V

SS

V

DD

NC

DQ

14

H

DQ

4

V

DD

V

SS

V

SS

V

SS

V

DD

DQ

13

J

V

DD

V

SS

V

DD

V

SS

V

DD

V

SS

V

DD

K

DQ

5

V

DD

V

SS

V

SS

V

SS

V

DD

DQ

12

L

DQ

6

NC

V

DD

V

SS

V

DD

NC

DQ

11

M

DQ

7

V

DD

V

SS

V

SS

V

SS

V

DD

DQ

10

N

DQ

8

NC

V

DD

V

SS

V

DD

NC

DQ

9

P

NC

V

DD

V

SS

V

SS

V

SS

V

DD

NC

R

NC

NC

NC

A

18

NC

NC

NC

T

NC

A

7

A

6

WE

A

5

A

4

NC,

V

SS

U

NC

A

3

A

2

OE

A

1

A

0

NC

Rev: 1.02 9/2001

3/11

© 1999, Giga Semiconductor, Inc.

For latest documentation see http://www.gsitechnology.com.

GS78116B

Note: X: "H" or "L"

Note:

Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation shall be restricted to Recommended

Operating Conditions. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

Notes:

1. Input overshoot voltage should be less than V

DD

+2 V and not exceed 20 ns.

2. Input undershoot voltage should be greater than ≠2 V and not exceed 20 ns.

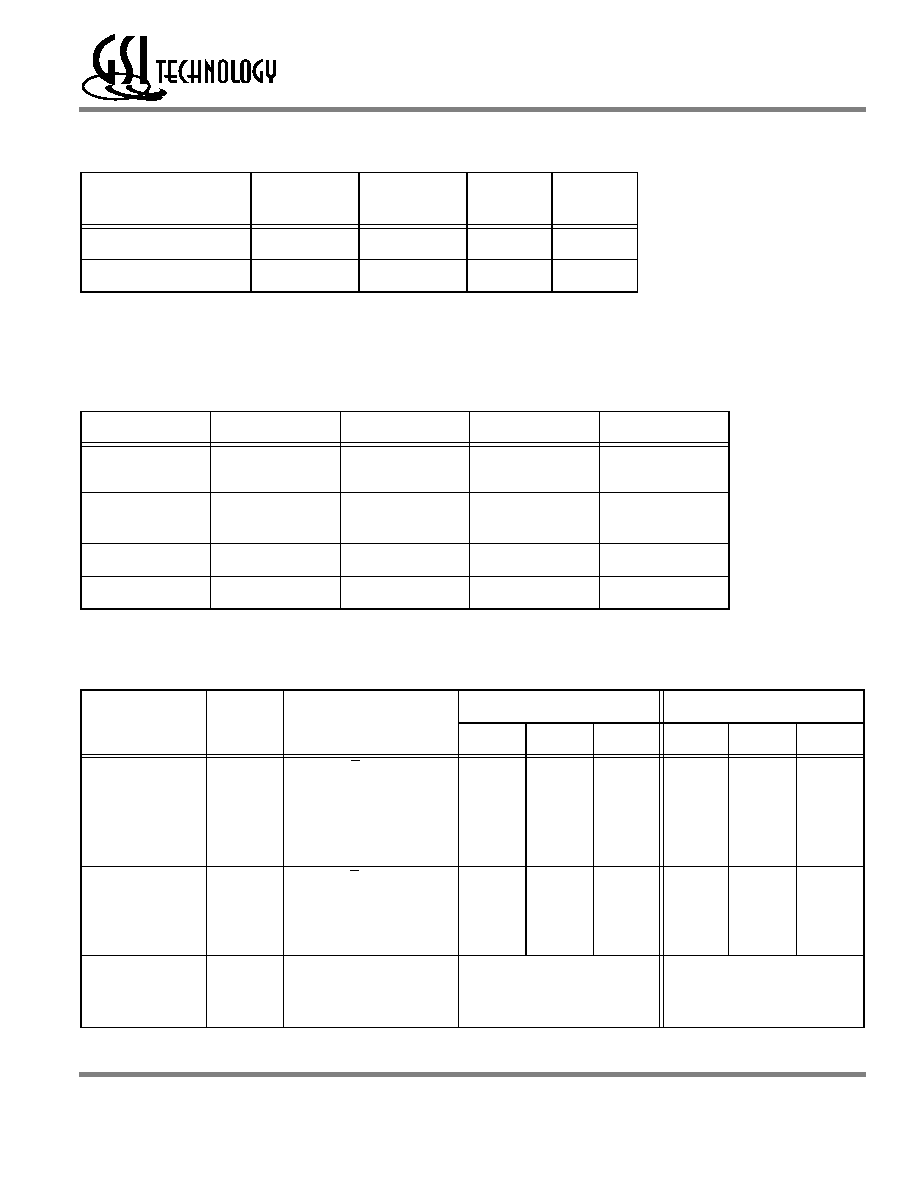

Truth Table

CE

OE

WE

DQ

1

to DQ

8

V

DD

Current

H

X

X

Not Selected

ISB1, ISB2

L

L

H

Read

L

X

L

Write

I

DD

L

H

H

High Z

Absolute Maximum Ratings

Parameter

Symbol

Rating

Unit

Supply Voltage

V

DD

≠0.5 to +4.6

V

Input Voltage

V

IN

≠0.5 to V

DD

+0.5

(

4.6 V max.)

V

Output Voltage

V

OUT

≠0.5 to V

DD

+0.5

(

4.6 V max.)

V

Allowable power dissipation

PD

1.5

W

Storage temperature

T

STG

≠55 to 150

o

C

Recommended Operating Conditions

Parameter

Symbol

Min

Typ

Max

Unit

Supply Voltage for -10/12/15

V

DD

3.0

3.3

3.6

V

Input High Voltage

V

IH

2.0

--

V

DD

+0.3

V

Input Low Voltage

V

IL

≠0.3

--

0.8

V

Ambient Temperature,

Commercial Range

T

Ac

0

--

70

o

C

Ambient Temperature,

Industrial Range

T

Ai

≠40

--

85

o

C

Rev: 1.02 9/2001

4/11

© 1999, Giga Semiconductor, Inc.

For latest documentation see http://www.gsitechnology.com.

GS78116B

Notes:

1. Tested at T

A

= 25∞C, f = 1 MHz

2. These parameters are sampled and are not 100% tested.

Capacitance

Parameter

Symbol

Test

Condition

Max

Unit

Input Capacitance

C

IN

V

IN

= 0 V

10

pF

Output Capacitance

C

OUT

V

OUT

= 0 V

7

pF

DC I/O Pin Characteristics

Parameter

Symbol

Test Conditions

Min

Max

Input Leakage

Current

I

IL

V

IN

= 0 to V

DD

≠2 uA

2 uA

Output Leakage

Current

I

OL

Output High Z,

V

OUT

= 0 to V

DD

≠1 uA

1 uA

Output High Voltage

V

OH

I

OH

= ≠4 mA

2.4

Output Low Voltage

V

OL

I

OL

= +4 mA

0.4 V

Power Supply Currents

Parameter

Symbol

Test Conditions

0 to 70∞C

≠40 to 85∞C

10 ns

12 ns

15 ns

10 ns

12 ns

15 ns

Operating

Supply

Current

I

DD

E

V

IL

All other inputs

V

IH

or

V

IL

Min. cycle time

I

OUT

= 0 mA

225 mA

220 mA

180 mA

270 mA

240 mA

200 mA

Standby

Current

I

SB1

E

V

IH

All other inputs

V

IH

or

V

IL

Min. cycle time

130 mA

120 mA

110 mA

150 mA

140 mA

130 mA

Standby

Current

I

SB2

E

V

DD

≠ 0.2V

All other inputs

V

DD

≠ 0.2 V or

0.2 V

60 mA

80 mA

Rev: 1.02 9/2001

5/11

© 1999, Giga Semiconductor, Inc.

For latest documentation see http://www.gsitechnology.com.

GS78116B

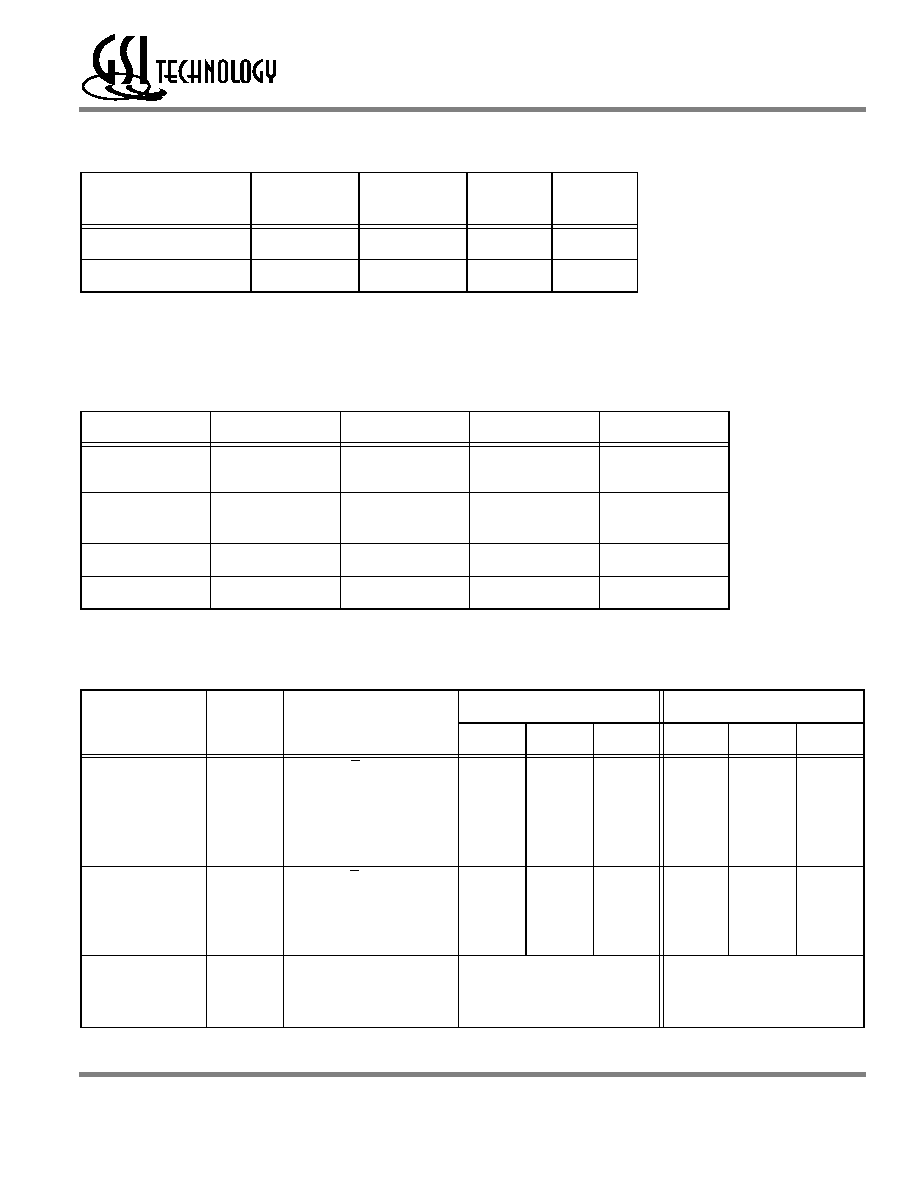

AC Test Conditions

AC Characteristics

Read Cycle

Parameter

Symbol

-10

-12

-15

Unit

Min Max Min Max Min Max

Read cycle time

t

RC

10

--

12

--

15

--

ns

Address access time

t

AA

--

10

--

12

--

15

ns

Chip enable access time (CE)

t

AC

--

10

--

12

--

15

ns

Output enable to output valid (OE)

t

OE

--

4

--

5

--

6

ns

Output hold from address change

t

OH

3

--

3

--

3

--

ns

Chip enable to output in low Z (CE)

t

LZ

*

3

--

3

--

3

--

ns

Output enable to output in low Z (OE)

t

OLZ

*

0

--

0

--

0

--

ns

Chip disable to output in High Z (CE)

t

HZ

*

--

5

--

6

--

7

ns

Output disable to output in High Z (OE)

t

OHZ

*

--

4

--

5

--

6

ns

DQ

VT = 1.4 V

50

30pF

1

DQ

3.3 V

Output Load 1

Output Load 2

589

434

5pF

1

Notes:

1. Include scope and jig capacitance.

2. Test conditions as specified with output loading as shown in Fig. 1

unless otherwise noted

3. Output load 2 for t

LZ

, t

HZ

, t

OLZ

and t

OHZ

.

Parameter

Conditions

Input high level

V

IH

= 2.4 V

Input low level

V

IL

= 0.4 V

Input rise time

tr = 1 V/ns

Input fall time

tf = 1 V/ns

Input reference level

1.4 V

Output reference level

1.4 V

Output load

Fig. 1& 2