Rev: 1.01 6/2003

1/30

© 2003, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

ByteSafe is a Trademark of Giga Semiconductor, Inc. (GSI Technology).

GS8321EV18/32/36E-250/225/200/166/150/133

2M x 18, 1M x 32, 1M x 36

36Mb Sync Burst SRAMs

250 MHz≠133 MHz

1.8 V V

DD

1.8 V I/O

165-Bump FP-BGA

Commercial Temp

Industrial Temp

Features

∑ FT pin for user-configurable flow through or pipeline opera-

tion

∑ Dual Cycle Deselect (DCD) operation

∑ IEEE 1149.1 JTAG-compatible Boundary Scan

∑ 1.8 V +10%/≠10% core power supply

∑ 1.8 V I/O supply

∑ LBO pin for Linear or Interleaved Burst mode

∑ Internal input resistors on mode pins allow floating mode pins

∑ Default to Interleaved Pipeline mode

∑ Byte Write (BW) and/or Global Write (GW) operation

∑ Internal self-timed write cycle

∑ Automatic power-down for portable applications

∑ JEDEC-standard 165-bump FP-BGA package

Functional Description

Applications

The GS8321EV18/32/36E is a 37,748,736-bit high

performance synchronous SRAM with a 2-bit burst address

counter. Although of a type originally developed for Level 2

Cache applications supporting high performance CPUs, the

device now finds application in synchronous SRAM

applications, ranging from DSP main store to networking chip

set support.

Controls

Addresses, data I/Os, chip enable (E1), address burst control

inputs (ADSP, ADSC, ADV) and write control inputs (Bx, BW,

GW) are synchronous and are controlled by a positive-edge-

triggered clock input (CK). Output enable (G) and power down

control (ZZ) are asynchronous inputs. Burst cycles can be

initiated with either ADSP or ADSC inputs. In Burst mode,

subsequent burst addresses are generated internally and are

controlled by ADV. The burst address counter may be

configured to count in either linear or interleave order with the

Linear Burst Order (LBO) input. The Burst function need not

be used. New addresses can be loaded on every cycle with no

degradation of chip performance.

Flow Through/Pipeline Reads

The function of the Data Output register can be controlled by

the user via the FT mode pin (Pin 14). Holding the FT mode pin

low places the RAM in Flow Through mode, causing output

data to bypass the Data Output Register. Holding FT high

places the RAM in Pipeline mode, activating the rising-edge-

triggered Data Output Register.

DCD Pipelined Reads

The GS8321EV18/32/36E is a DCD (Dual Cycle Deselect)

pipelined synchronous SRAM. SCD (Single Cycle Deselect)

versions are also available. DCD SRAMs pipeline disable

commands to the same degree as read commands. DCD RAMs

hold the deselect command for one full cycle and then begin

turning off their outputs just after the second rising edge of

clock.

Byte Write and Global Write

Byte write operation is performed by using Byte Write enable

(BW) input combined with one or more individual byte write

signals (Bx). In addition, Global Write (GW) is available for

writing all bytes at one time, regardless of the Byte Write

control inputs.

Sleep Mode

Low power (Sleep mode) is attained through the assertion

(High) of the ZZ signal, or by stopping the clock (CK).

Memory data is retained during Sleep mode.

Core and Interface Voltages

The GS8321EV18/32/36E operates on a 1.8 V power supply.

All input are 1.8 V compatible. Separate output power (V

DDQ

)

pins are used to decouple output noise from the internal circuits

and are 1.8 V compatible.

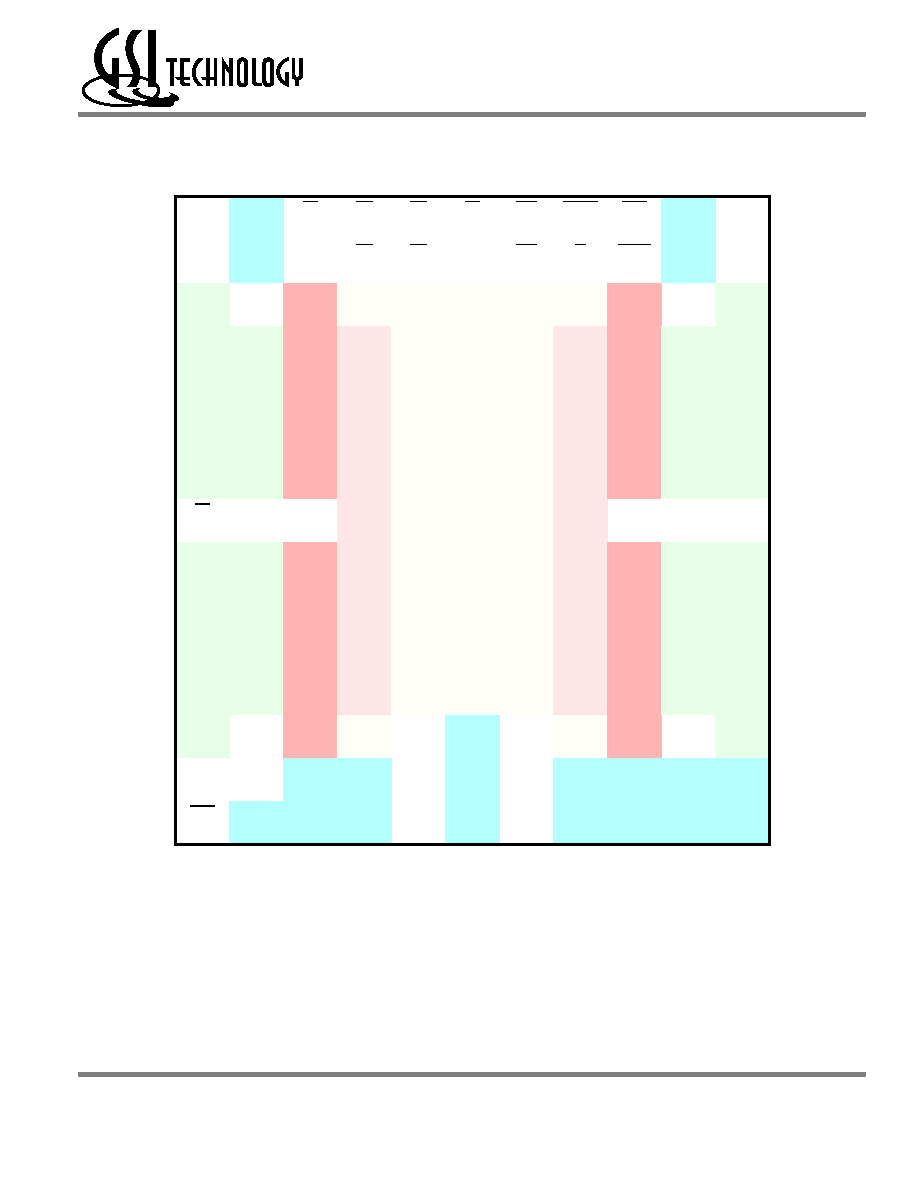

-250 -225 -200 -166 -150 -133 Unit

Pipeline

3-1-1-1

t

KQ

tCycle

2.3

4.0

2.5

4.4

2.7

5.0

2.9

6.0

3.3

6.7

3.5

7.5

ns

ns

Curr

(x18)

Curr

(x36)

285

350

265

320

245

295

220

260

210

240

185

215

mA

mA

Flow

Through

2-1-1-1

t

KQ

tCycle

6.5

6.5

7.0

7.0

7.5

7.5

8.0

8.0

8.5

8.5

8.5

8.5

ns

ns

Curr

(x18)

Curr

(x36)

205

235

195

225

185

210

175

200

165

190

155

175

mA

mA

Rev: 1.01 6/2003

2/30

© 2003, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8321EV18/32/36E-250/225/200/166/150/133

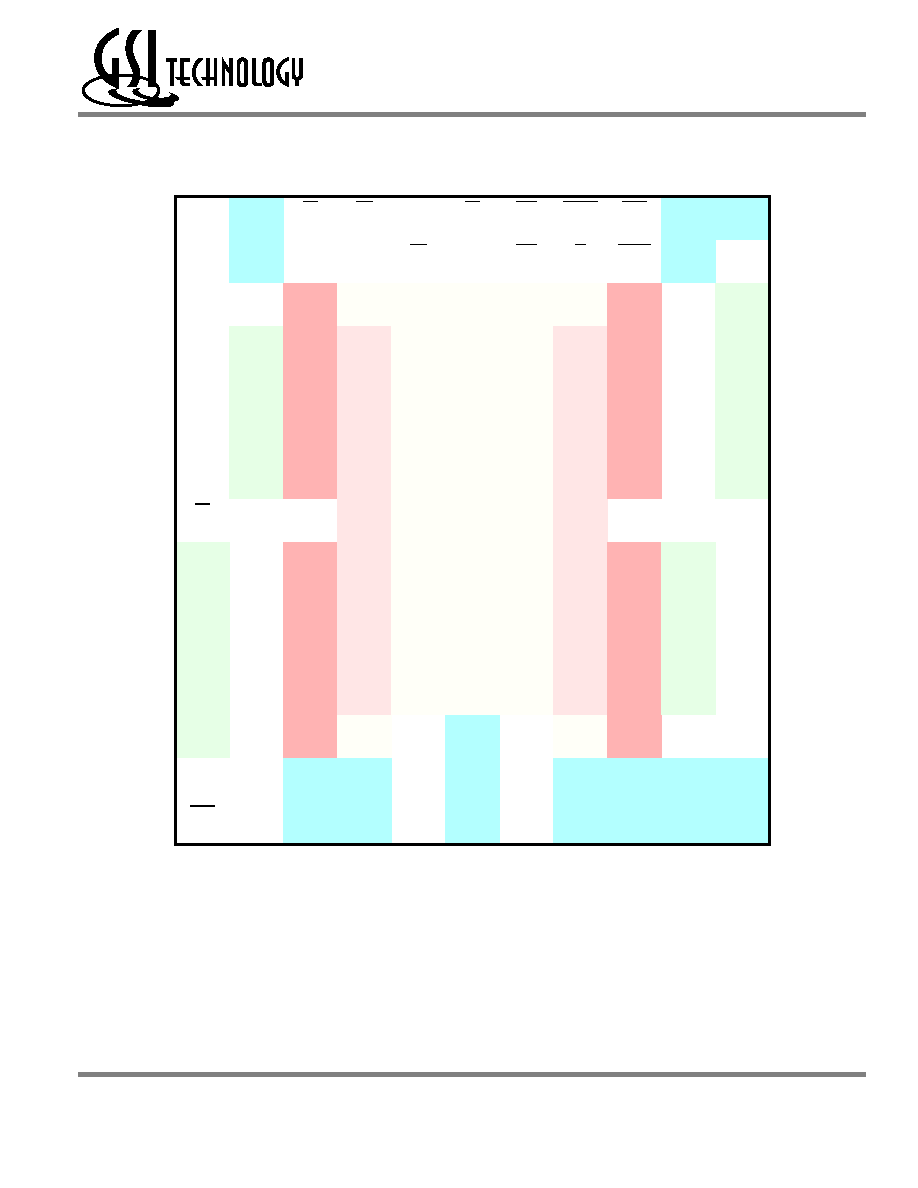

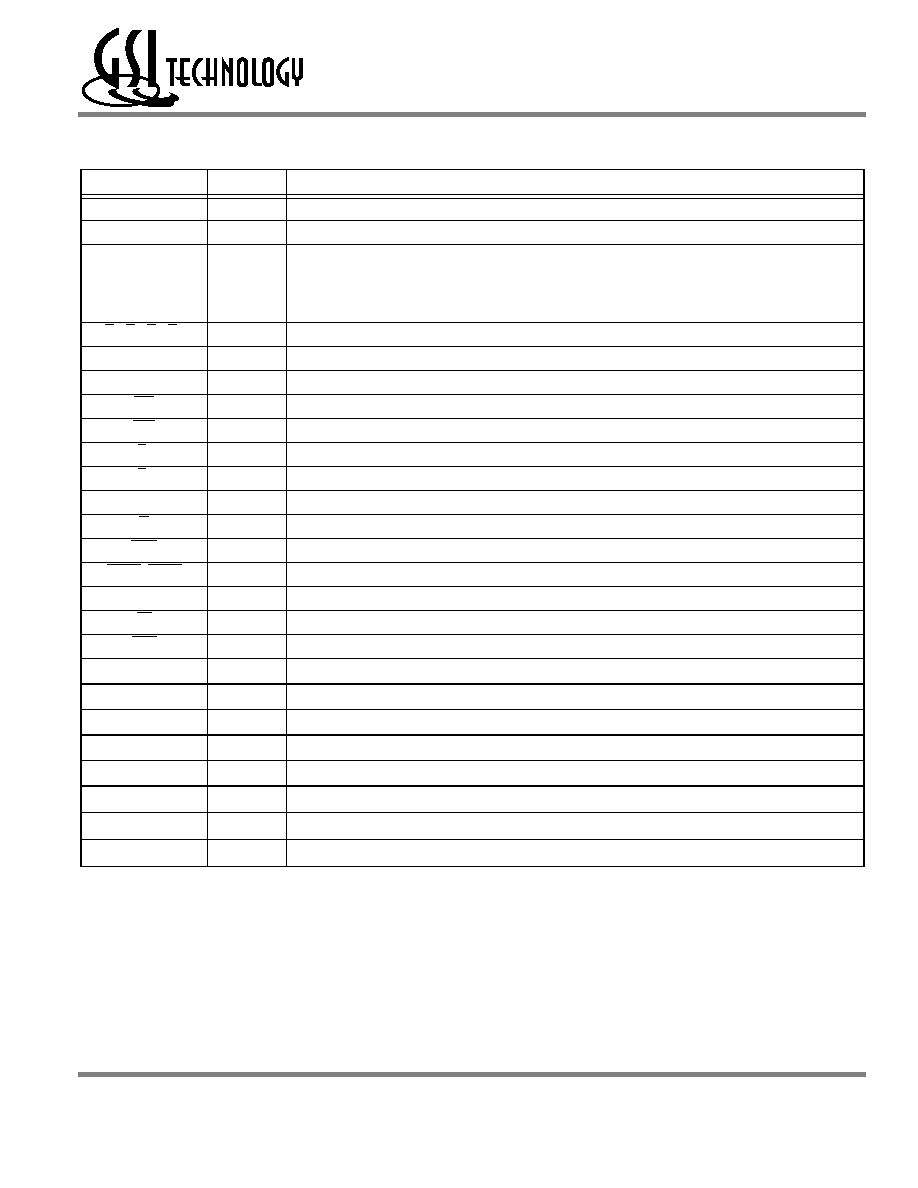

165 Bump BGA--x18 Commom I/O--Top View (Package E)

1

2

3

4

5

6

7

8

9

10

11

A

NC

A

E1

BB

NC

E3

BW

ADSC

ADV

A

A

A

B

NC

A

E2

NC

BA

CK

GW

G

ADSP

A

NC

B

C

NC

NC

V

DDQ

V

SS

V

SS

V

SS

V

SS

V

SS

V

DDQ

NC

DQPA

C

D

NC

DQB

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

NC

DQA

D

E

NC

DQB

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

NC

DQA

E

F

NC

DQB

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

NC

DQA

F

G

NC

DQB

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

NC

DQA

G

H

FT

MCL

NC

V

DD

V

SS

V

SS

V

SS

V

DD

NC

NC

ZZ

H

J

DQB

NC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

NC

J

K

DQB

NC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

NC

K

L

DQB

NC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

NC

L

M

DQB

NC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

NC

M

N

DQPB

NC

V

DDQ

V

SS

NC

A

NC

V

SS

V

DDQ

NC

NC

N

P

NC

NC

A

A

TDI

A1

TDO

A

A

A

A

P

R

LBO

A

A

A

TMS

A0

TCK

A

A

A

A

R

11 x 15 Bump BGA--15 mm x 17 mm Body--1.0 mm Bump Pitch

Rev: 1.01 6/2003

3/30

© 2003, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8321EV18/32/36E-250/225/200/166/150/133

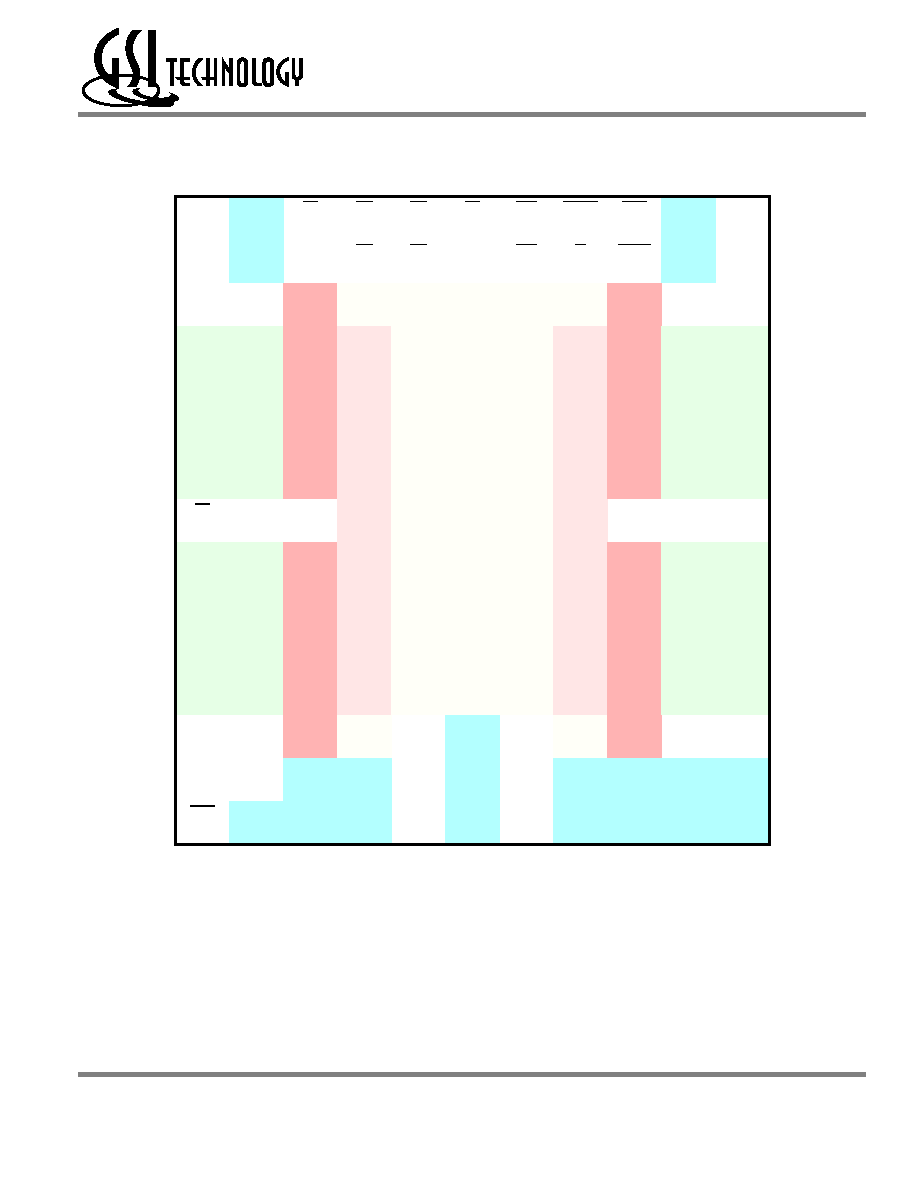

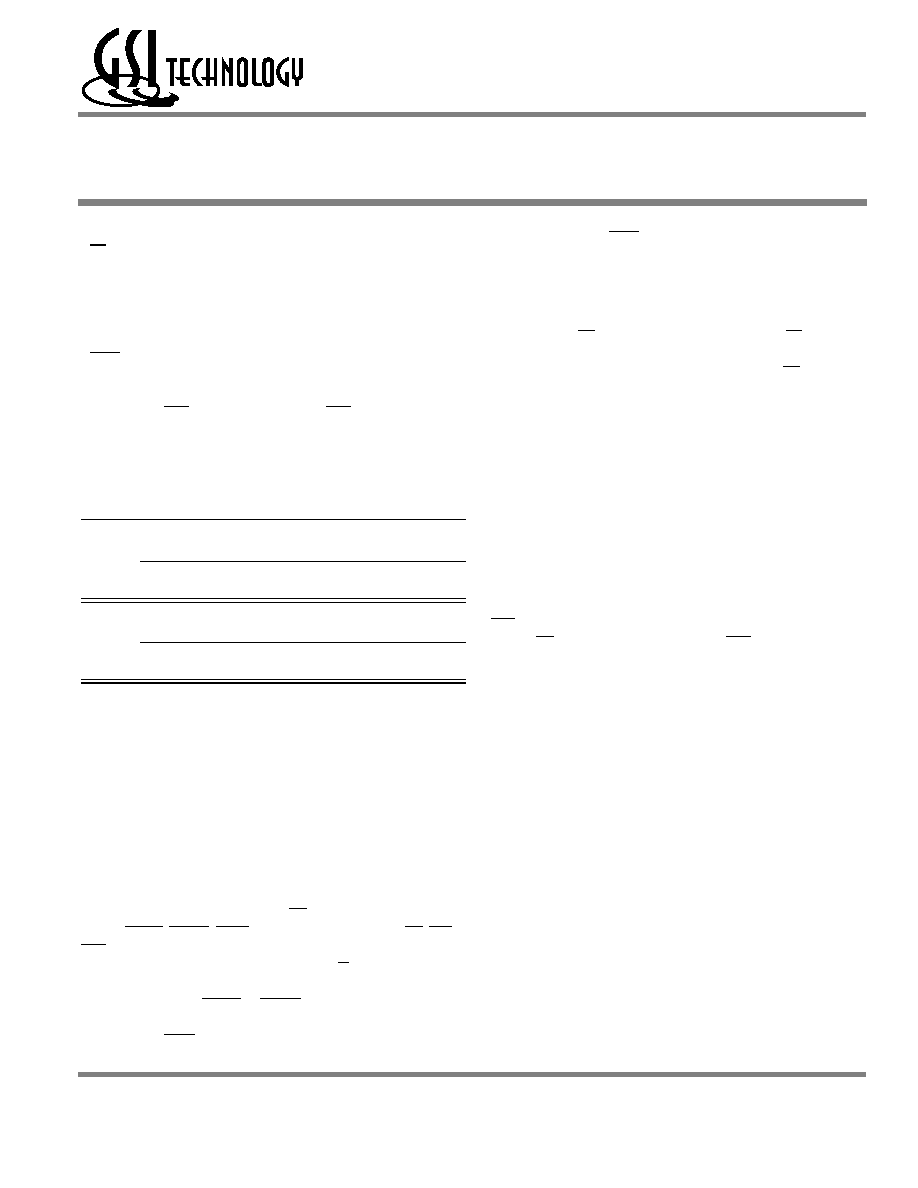

165 Bump BGA--x32 Common I/O--Top View (Package E)

1

2

3

4

5

6

7

8

9

10

11

A

NC

A

E1

BC

BB

E3

BW

ADSC

ADV

A

NC

A

B

NC

A

E2

BD

BA

CK

GW

G

ADSP

A

NC

B

C

NC

NC

V

DDQ

V

SS

V

SS

V

SS

V

SS

V

SS

V

DDQ

NC

NC

C

D

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

D

E

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

E

F

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

F

G

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

G

H

FT

MCL

NC

V

DD

V

SS

V

SS

V

SS

V

DD

NC

NC

ZZ

H

J

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

J

K

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

K

L

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

L

M

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

M

N

NC

NC

V

DDQ

V

SS

NC

A

NC

V

SS

V

DDQ

NC

NC

N

P

NC

NC

A

A

TDI

A1

TDO

A

A

A

A

P

R

LBO

A

A

A

TMS

A0

TCK

A

A

A

A

R

11 x 15 Bump BGA--15 mm x 17 mm Body--1.0 mm Bump Pitch

Rev: 1.01 6/2003

4/30

© 2003, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

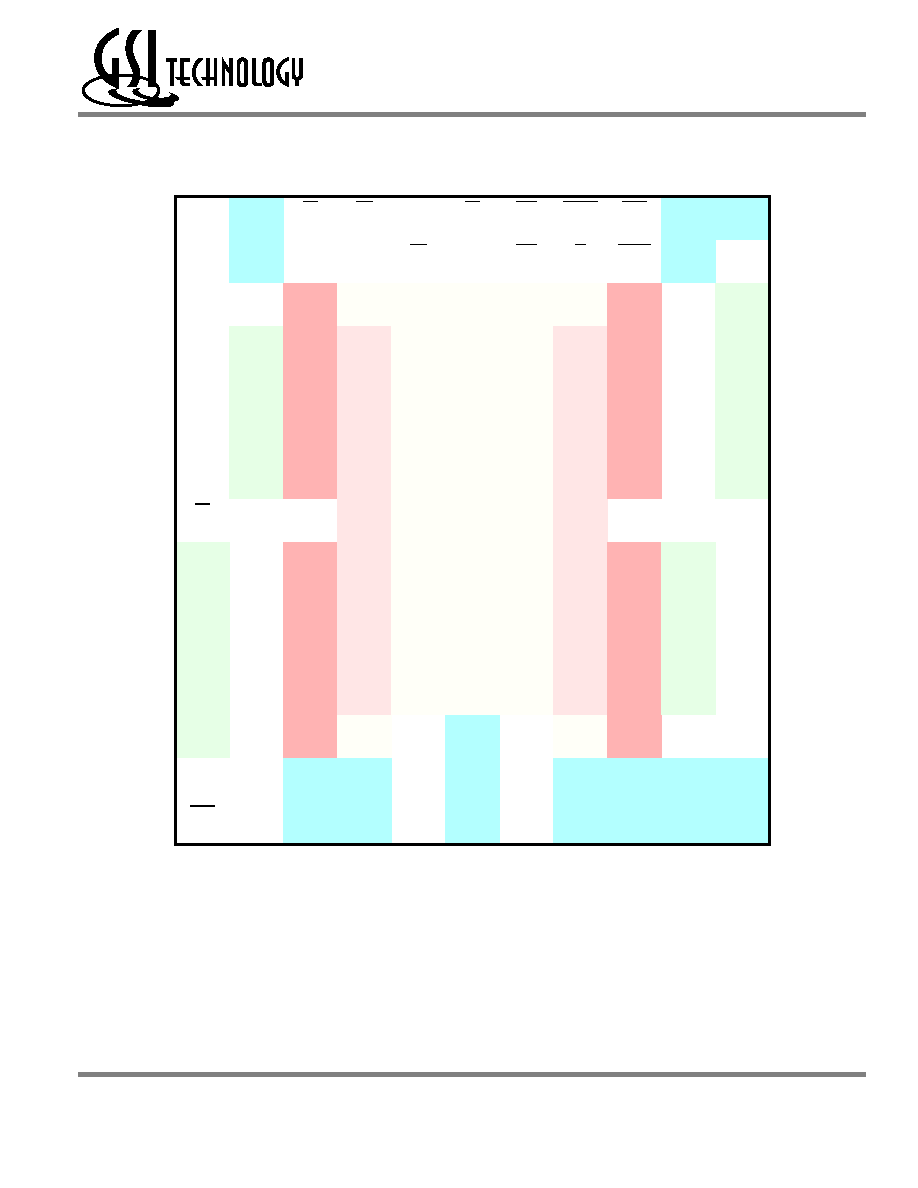

GS8321EV18/32/36E-250/225/200/166/150/133

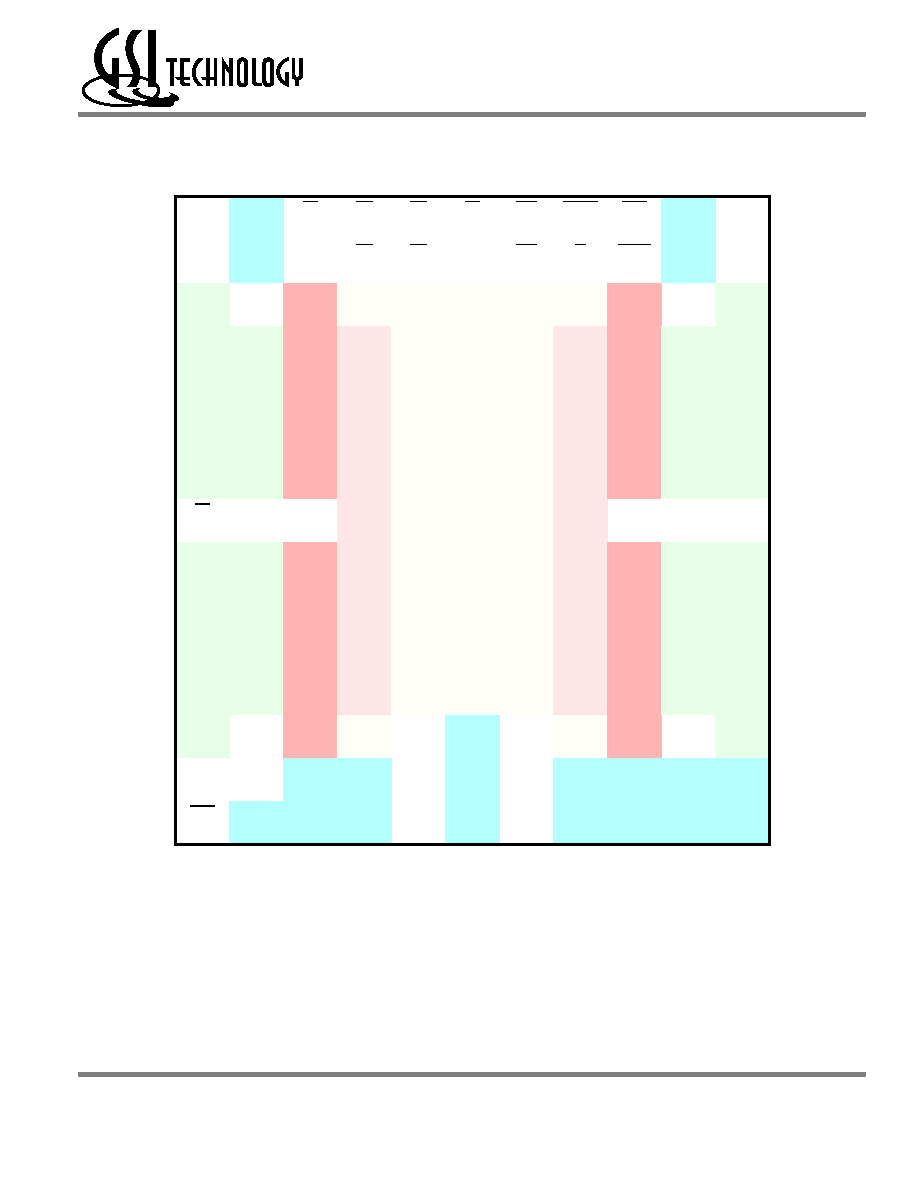

165 Bump BGA--x36 Common I/O--Top View (Package E)

1

2

3

4

5

6

7

8

9

10

11

A

NC

A

E1

BC

BB

E3

BW

ADSC

ADV

A

NC

A

B

NC

A

E2

BD

BA

CK

GW

G

ADSP

A

NC

B

C

DQPC

NC

V

DDQ

V

SS

V

SS

V

SS

V

SS

V

SS

V

DDQ

NC

DQPB

C

D

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

D

E

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

E

F

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

F

G

DQC

DQC

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQB

DQB

G

H

FT

MCL

NC

V

DD

V

SS

V

SS

V

SS

V

DD

NC

NC

ZZ

H

J

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

J

K

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

K

L

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

L

M

DQD

DQD

V

DDQ

V

DD

V

SS

V

SS

V

SS

V

DD

V

DDQ

DQA

DQA

M

N

DQPD

NC

V

DDQ

V

SS

NC

A

NC

V

SS

V

DDQ

NC

DQPA

N

P

NC

NC

A

A

TDI

A1

TDO

A

A

A

A

P

R

LBO

A

A

A

TMS

A0

TCK

A

A

A

A

R

11 x 15 Bump BGA--15 mm x 17 mm Body--1.0 mm Bump Pitch

Rev: 1.01 6/2003

5/30

© 2003, Giga Semiconductor, Inc.

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

GS8321EV18/32/36E-250/225/200/166/150/133

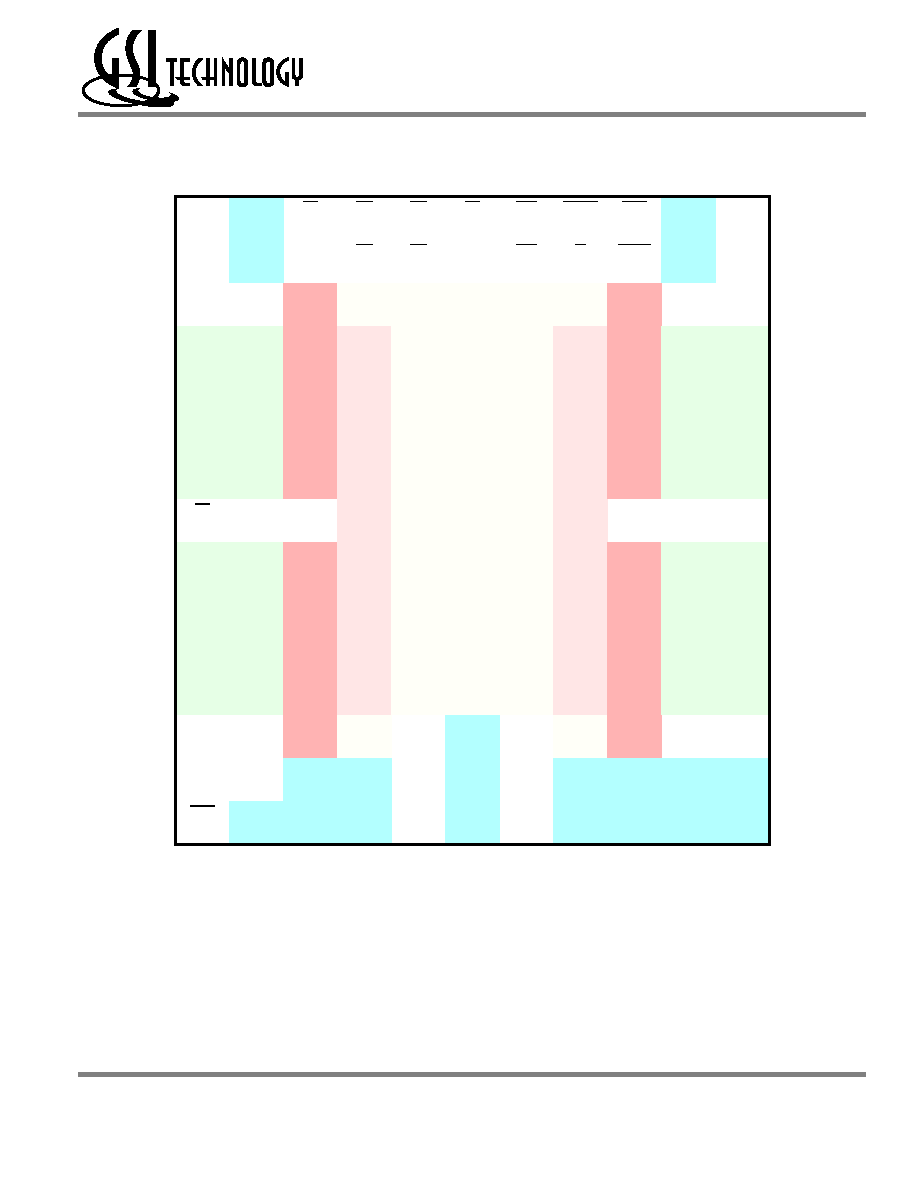

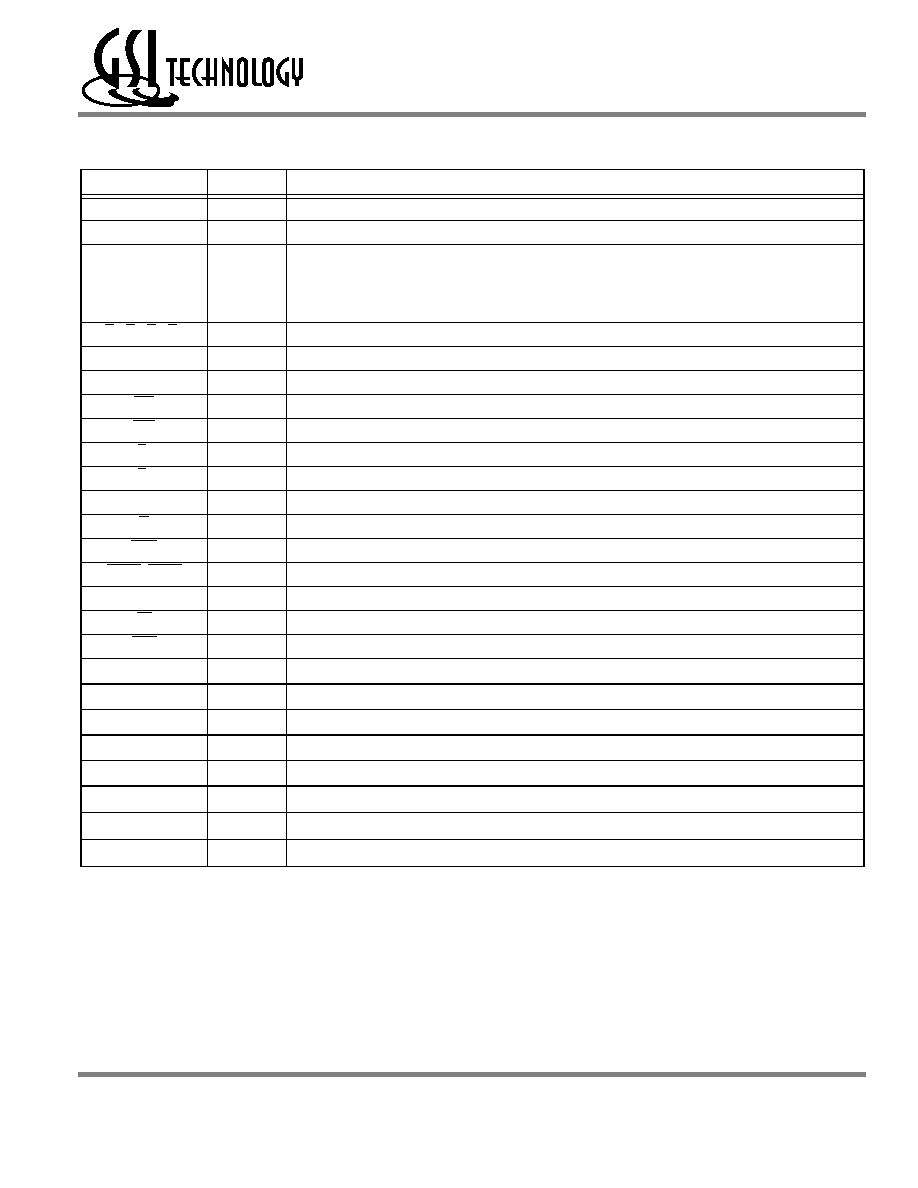

GS8321EV18/32/36E 165-Bump BGA Pin Description

Symbol

Type

Description

A

0

, A

1

I

Address field LSBs and Address Counter Preset Inputs

A

I

Address Inputs

DQ

A

DQ

B

DQ

C

DQ

D

I/O

Data Input and Output pins

B

A

, B

B

, B

C

, B

D

I

Byte Write Enable for DQ

A

, DQ

B

, DQ

C

, DQ

D

I/Os; active low

NC

--

No Connect

CK

I

Clock Input Signal; active high

BW

I

Byte Write--Writes all enabled bytes; active low

GW

I

Global Write Enable--Writes all bytes; active low

E

1

I

Chip Enable; active low

E

3

I

Chip Enable; active low

E

2

I

Chip Enable; active high

G

I

Output Enable; active low

ADV

I

Burst address counter advance enable; active l0w

ADSC, ADSP

I

Address Strobe (Processor, Cache Controller); active low

ZZ

I

Sleep mode control; active high

FT

I

Flow Through or Pipeline mode; active low

LBO

I

Linear Burst Order mode; active low

TMS

I

Scan Test Mode Select

TDI

I

Scan Test Data In

TDO

O

Scan Test Data Out

TCK

I

Scan Test Clock

MCL

--

Must Connect Low

V

DD

I

Core power supply

V

SS

I

I/O and Core Ground

V

DDQ

I

Output driver power supply