Rev: 1.00 6/2003

1/26

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.

Preliminary

GS890QV18D-200/167/133/100

9Mb

2x2B2

SigmaQuad SRAM

100 MHz≠200 MHz

2.5 V V

DD

1.8 V and 1.5 V I/O

165-Bump BGA

Commercial Temp

Industrial Temp

Features

∑ Simultaneous Read and Write SigmaQuadTM Interface

∑ JEDEC-standard pinout and package

∑ Dual DoubleData Rate interface

∑ Byte Write controls sampled at data-in time

∑ Burst of 2 Read and Write

∑ 2.5 V +100/≠100 mV core power supply

∑ 1.5 V or 1.8 V HSTL Interface

∑ Pipelined read operation

∑ Fully coherent read and write pipelines

∑ ZQ mode pin for programmable output drive strength

∑ IEEE 1149.1 JTAG-compliant Boundary Scan

∑ 165-bump, 13 mm x 15 mm, 1 mm bump pitch BGA package

∑ Pin-compatible with future 18Mb, 36Mb, 72Mb, and 144Mb devices

SigmaRAMTM Family Overview

GS890QV18 are built in compliance with the SigmaQuad SRAM

pinout standard for Separate I/O synchronous SRAMs. They are

9,437,184-bit (9Mb) SRAMs. These are the first in a family of wide,

very low voltage HSTL I/O SRAMs designed to operate at the speeds

needed to implement economical high performance networking

systems.

Clocking and Addressing Schemes

A

2x2B2 SigmaQuad SRAM is a synchronous device. It employs

two input register clock inputs, K and K. K and K are independent

single-ended clock inputs, not differential inputs to a single differential

clock input buffer. The device also allows the user to manipulate the

output register clock inputs quasi independently with the C and C

clock inputs. C and C are also independent single-ended clock inputs,

not differential inputs. If the C clocks are tied high, the K clocks are

routed internally to fire the output registers instead.

Because Separate I/O

2x2B2

RAMs always transfer data in two

packets, A0 is internally set to 0 for the first read or write transfer, and

automatically incremented by 1 for the next transfer. Because the LSB

is tied off internally, the address field of a

2x2B2

RAM is always one

address pin less than the advertised index depth (e.g., the 512K x 18

has a 256K addressable index).

Alternating Read-Write Operations

SigmaQuad SRAMs follow a few simple rules of operation.

- Read or Write commands issued on one port are never allowed to

interrupt an operation in progress on the other port.

- Read or Write data transfers in progress may not be interrupted and

re-started.

- R and W high always deselects the RAM.

- All address, data, and control inputs are sampled on clock edges.

In order to enforce these rules, each RAM combines present state

information with command inputs. See the Truth Table on page 10

for details.

-200

-167

-133

-100

tKHKH

5.0 ns

6.0 ns

7.5 ns

10.0 ns

tKHQV

2.3 ns

2.4 ns

3.0 ns

3.0 ns

165-Bump, 13 mm x 15 mm BGA

1 mm Bump Pitch, 11 x 15 Bump Array

Bottom View

JEDEC Std. MO-216, Variation CAB-1

Rev: 1.00 6/2003

2/26

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.

Preliminary

GS890QV18D-200/167/133/100

1M x 18 SigmaQuad SRAM -- Top View

1

2

3

4

5

6

7

8

9

10

11

A NC

V

SS

/SA

(144Mb)

NC/SA

(36Mb)

W

BW1

K

NC

R

NC/SA

(18Mb)

V

SS

/SA

(72Mb)

NC

B NC

Q9

D9

SA

NC

K

BW0

SA

NC

NC

Q8

C NC

NC

D10

V

SS

SA

SA

SA

V

SS

NC

Q7

D8

D NC

D11

Q10

V

SS

V

SS

V

SS

V

SS

V

SS

NC

NC

D7

E NC

NC

Q11

V

DDQ

V

SS

V

SS

V

SS

V

DDQ

NC

D6

Q6

F

NC

Q12

D12

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

NC

NC

Q5

G NC

D13

Q13

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

NC

NC

D5

H NC

V

REF

V

DDQ

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

V

DDQ

V

REF

ZQ

J NC

NC

D14

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

NC

Q4

D4

K NC

NC

Q14

V

DDQ

V

DD

V

SS

V

DD

V

DDQ

NC

D3

Q3

L NC

Q15

D15

V

DDQ

V

SS

V

SS

V

SS

V

DDQ

NC

NC

Q2

M NC

NC

D16

V

SS

V

SS

V

SS

V

SS

V

SS

NC

Q1

D2

N NC

D17

Q16

V

SS

SA

SA

SA

V

SS

NC

NC

D1

P NC

NC

Q17

SA

SA

C

SA

SA

NC

D0

Q0

R TDO

TCK

SA

SA

SA

C

SA

SA

SA

TMS

TDI

11 x 15 Bump BGA--13 x 15 mm2 Body--1 mm Bump Pitch

Notes:

1. Expansion addresses: A3 for 36Mb, A10 for 72Mb, A2 for 144Mb

2. BW0 controls writes to D0:D8. BW1 controls writes to D9:D17.

3. MCL = Must Connect Low

4. It is recommended that H1 be tied low for compatibility with future devices.

Rev: 1.00 6/2003

3/26

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.

Preliminary

GS890QV18D-200/167/133/100

Note: NC = Not Connected to die or any other pin

Background

Separate I/O SRAMs, from a system architecture point of view, are attractive in applications where alternating reads and writes are needed.

Therefore, the SigmaQuad SRAM interface and truth table are optimized for alternating reads and writes. Separate I/O SRAMs are unpopular in

applications where multiple reads or multiple writes are needed because burst read or write transfers from Separate I/O SRAMs can cut the

RAM's bandwidth in half.

A SigmaQuad SRAM can begin an alternating sequence of reads and writes with either a read or a write. In order for any separate I/O SRAM that

shares a common address between its two ports to keep both ports running all the time, the RAM must implement some sort of burst transfer

protocol. The burst must be at least long enough to cover the time the opposite port is receiving instructions on what to do next. The rate at which

a RAM can accept a new random address is the most fundamental performance metric for the RAM. Each of the three SigmaQuad SRAMs

support similar address rates because random address rate is determined by the internal performance of the RAM and they are all based on the

same internal circuits. Differences between the truth tables of the different SigmaQuad SRAMs, or any other Separate I/O SRAMs, follow from

differences in how the RAM's interface is contrived to interact with the rest of the system. Each mode of operation has its own advantages and

disadvantages. The user should consider the nature of the work to be done by the RAM to evaluate which version is best suited to the application

at hand.

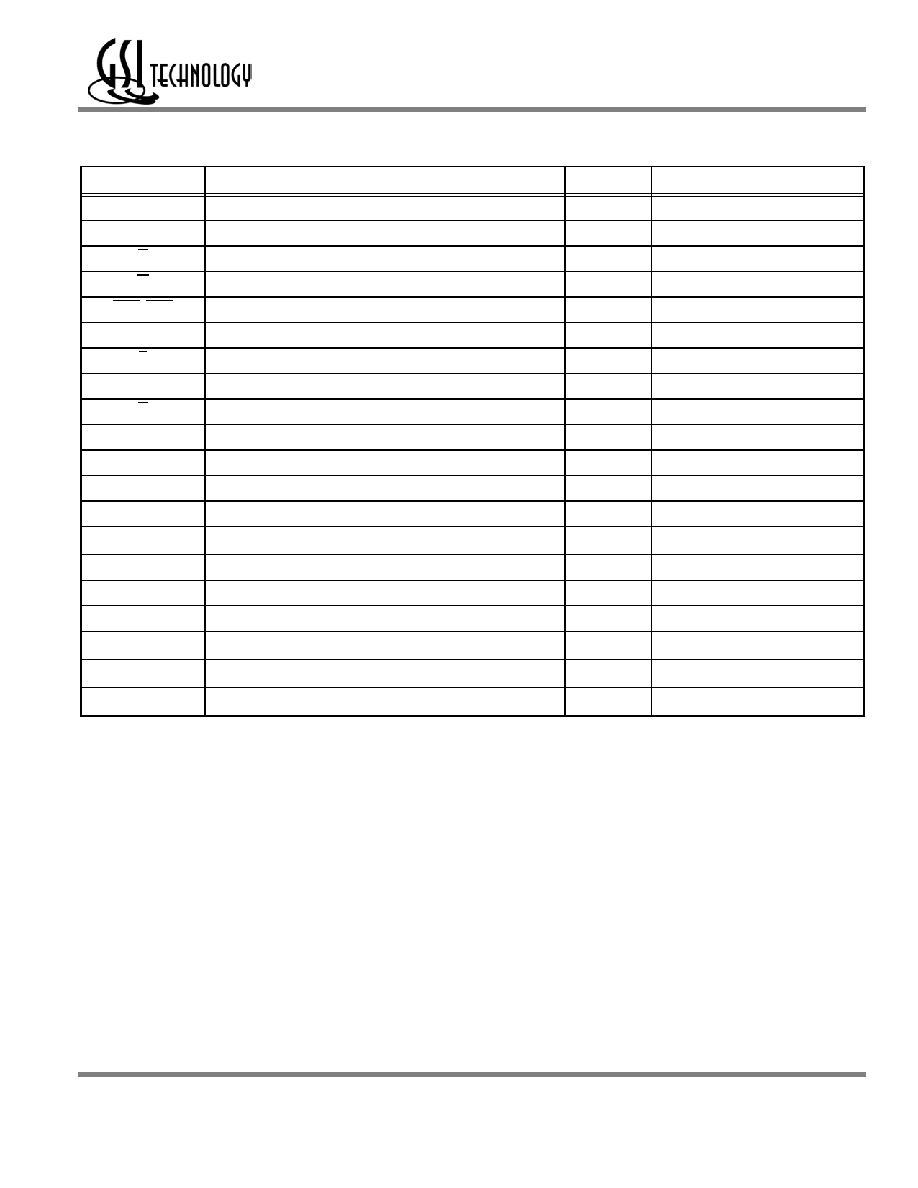

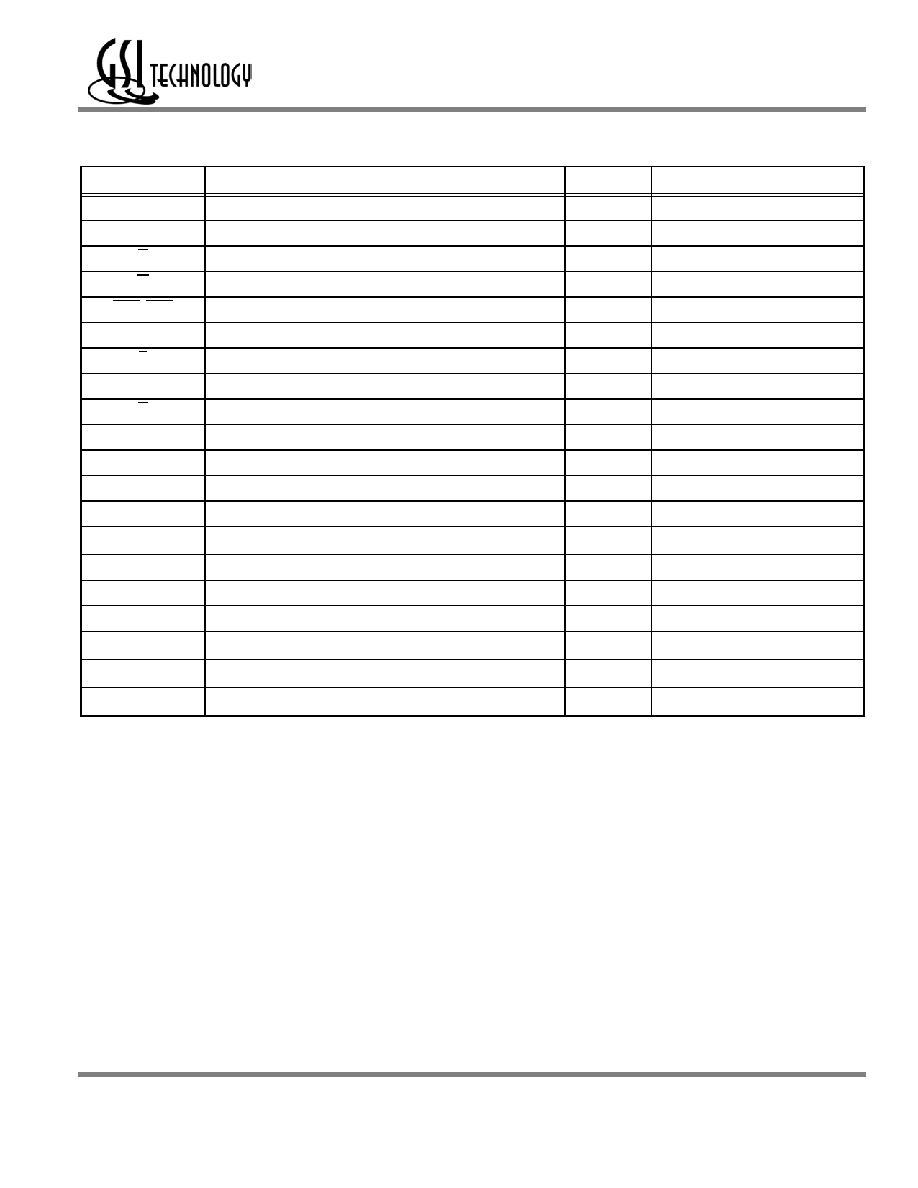

Pin Description Table

Symbol

Description

Type

Comments

SA

Synchronous Address Inputs

Input

--

NC

No Connect

--

--

R

Synchronous Read

Input

Active Low

W

Synchronous Write

Input

Active Low

BW0≠BW1

Synchronous Byte Writes

Input

Active Low

K

Input Clock

Input

Active High

K

Input Clock

Input

Active Low

C

Output Clock

Input

Active High

C

Output Clock

Input

Active Low

TMS

Test Mode Select

Input

--

TDI

Test Data Input

Input

--

TCK

Test Clock Input

Input

--

TDO

Test Data Output

Output

--

V

REF

HSTL Input Reference Voltage

Input

--

ZQ

Output Impedance Matching Input

Input

--

D0≠D17

Synchronous Data Inputs

Input

--

Q0≠Q17

Synchronous Data Outputs

Output

--

V

DD

Power Supply

Supply

2.5 V Nominal

V

DDQ

Isolated Output Buffer Supply

Supply

1.5 V Nominal

V

SS

Power Supply: Ground

Supply

--

Rev: 1.00 6/2003

4/26

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.

Preliminary

GS890QV18D-200/167/133/100

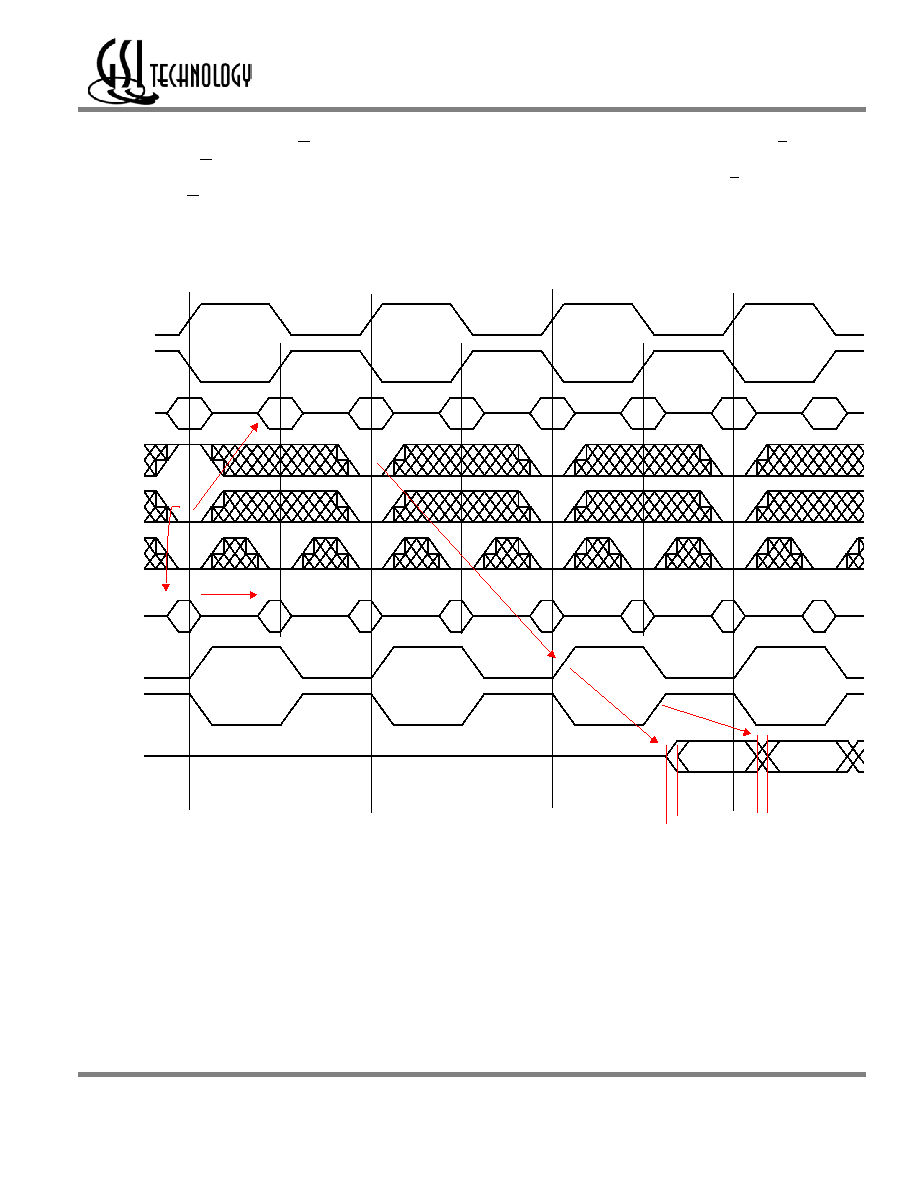

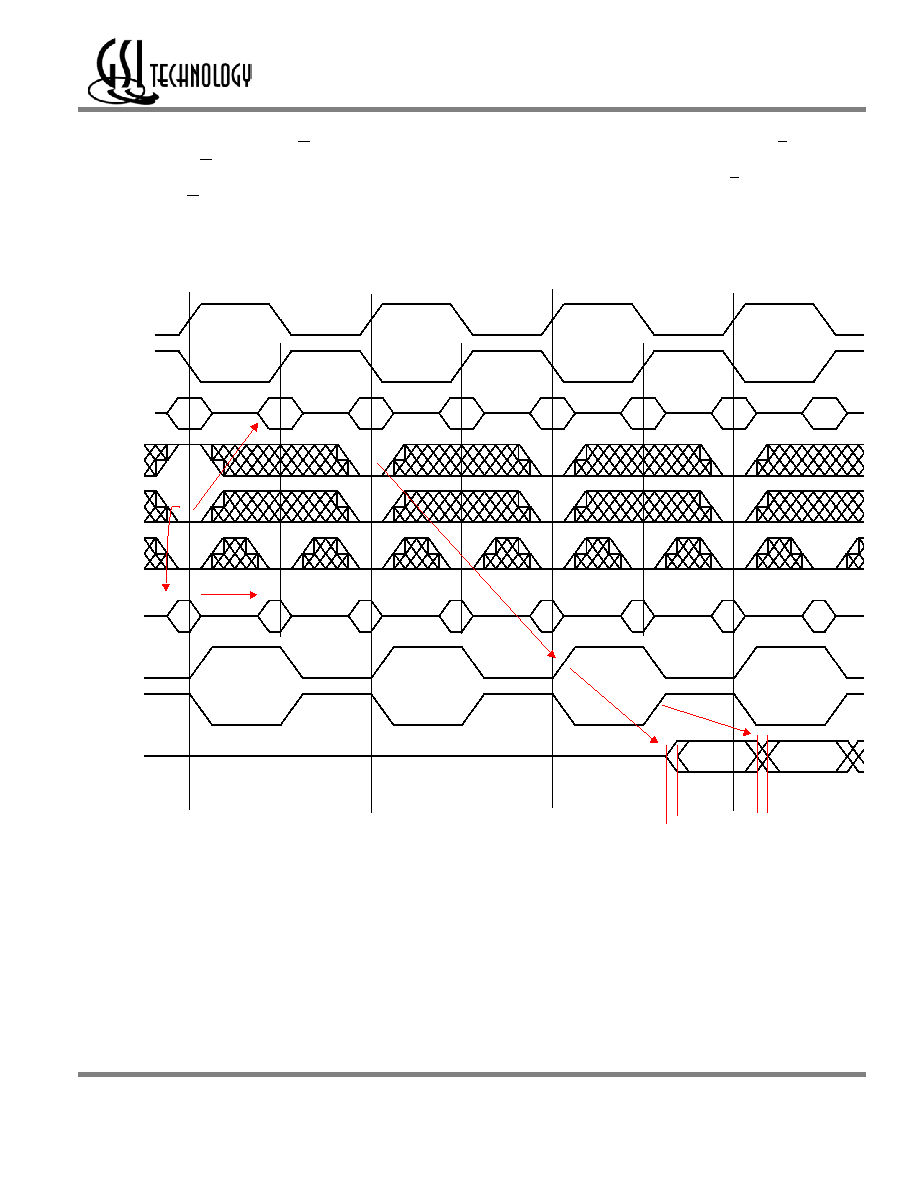

2x2B2 SigmaQuad SRAM DDR Read

The read port samples the status of the Address Input and R pins at each rising edge of K. A low on the Read Enable-bar pin, R, begins a read

cycle. Data can be clocked out one cycle later and again one half cycle after that. A high on the Read Enable-bar pin, R, begins a read port

deselect cycle.

2x2B2 Double Data Rate SigmaQuad SRAM Read First

Dwg Rev. G

DC0

DC1

DE0

DE1

DG0

DG1

QB0

QB1

E

No Op

Read

Write

Read

Write

XX

K

/K

Address

XX

B

C

D

No Op

C

/C

D

Q

/R

/W

/BWx

Write

Read

G

F

Rev: 1.00 6/2003

5/26

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.

Preliminary

GS890QV18D-200/167/133/100

2x2B2 SigmaQuad SRAM DDR Write

The write port samples the status of the W pin at each rising edge of K and the Address Input pins on the following rising edge of K. A low on the

Write Enable-bar pin, W, begins a write cycle. The first of the data-in pairs associated with the write command is clocked in with the same rising

edge of K used to capture the write command. The second of the two data in transfers is captured on the rising edge of K along with the write

address. A high on W causes a write port deselect cycle.

2x2B2 Double Data Rate SigmaQuad SRAM Write First

Dwg Rev. G

DB0

DB1

DD0

DD1

DF0

DF1

DH0

DH1

/C

K

/K

D

Q

Read

Write

Address

XX

B

C

D

E

F

No Op

Write

Read

Write

C

/R

/W

/BWx

Write

Read

H

QC0

QC1

G