HD66740

1

HD66740

(112 x 80-dot Graphics LCD Controller/Driver)

Rev 1.0

August, 2001

Description

The HD66740, 112-by-80 dot-matrix graphics LCD controller and driver LSI, displays graphics such as

text, kanji and pictograms. It can be configured to drive a dot-matrix liquid crystal under the control of the

microprocessor connected via the clock-synchronized serial or 4/8-bit bus. The HD66740 has a smooth

vertical scroll display and a double-height display for the remaining bit map areas. It fixed-displays a part

of the graphics icons so that the user can easily see a variety of information.

The HD66740 has various functions to reduce the power consumption of an LCD system such as low-

voltage operation of 1.8 V min., a booster to generate maximum five-times LCD drive voltage from the

supplied voltage, and voltage-followers to decrease the direct current flow in the LCD drive bleeder-

resistors. Combining these hardware functions with software functions such as standby and sleep modes

allows fine power control. The HD66740 is suitable for any portable battery-driven product requiring

long-term driving capabilities such as cellular phones, pagers, or electronic wallets.

Features

∑

Control and drive of a graphics LCD

∑

112 x 80-dot display

∑

Fixed display of graphics icons (pictograms)

∑

Low-power operation support:

Vcc = 1.8 to 3.6 V (low voltage)

V

LCD

= 4.5 to 15.0 V (liquid crystal drive voltage)

Triple, quadruple, or five-times booster for liquid crystal drive voltage

64-step contrast adjuster and voltage followers to decrease direct current flow in the LCD drive

bleeder-resistors

Power-save functions such as the standby mode and sleep mode supported

Programmable drive duty ratios and bias values displayed on LCD

∑

High-speed clock-synchronized serial interface (serial transfer rate: 5 MHz max.)

∑

I2C bus interface

∑

High-speed 4-/8-bit bus interface capability

∑

112-segment

◊

80-common liquid crystal display driver

∑

1,120-byte (112

◊

80 dots) character generator RAM

HD66740

2

∑

Vertical smooth scroll

∑

Partial smooth scroll control (fixed display of graphics icons)

∑

Vertical double-height display by each display line

∑

Black-and-white reversed display

∑

Wide range of instruction functions:

Display on/off control, black-and-white reversed

∑

No wait time for instruction execution and RAM access

∑

Internal oscillation and hardware reset

∑

n-raster-row AC liquid-crystal drive (C-pattern waveform drive)

∑

Shift change of segment and common driver

∑

Tape carrier package (TCP)

Table 1

Progammable Display Sizes and Duty Ratios

Graphics Display

Duty

Ratio

Optimum

Drive Bias

Bit Map

12 x 13-dot

Font Width

14 x 15-dot

Font Width

16 x 16-dot

Font Width

1/32

1/7

112 x 32 dots 2 lines x 9

characters

2 lines x 8

characters

2 lines x 7

characters

1/40

1/7

112 x 40 dots 3 lines x 9

characters

2.5 lines x 8

characters

2.5 lines x 7

characters

1/48

1/8

112 x 48 dots 3 lines x 9

characters

3 lines x 8

characters

3 line x 7

characters

1/56

1/8

112 x 56 dots 4 lines x 9

characters

3.5 lines x 8

characters

3.5 lines x 7

characters

1/64

1/9

112 x 64 dots 5 lines x 9

characters

4 lines x 8

characters

4 lines x 7

characters

1/72

1/9.5

112 x 72 dots 6 lines x 9

characters

4.5 lines x 8

characters

4.5 lines x 7

characters

1/80

1/10

112 x 80 dots 6 lines x 9

characters

5 lines x 8

characters

5 lines x 7

characters

HD66740

3

<Target values>

Total Current Consumption Characteristics (Vcc = 3 V, TYP Conditions, LCD

Drive Power Current Included)

Total Power Consumption

Normal Display Operation

Character

Display Dot

Size

Duty

Ratio

R-C

Oscillation

Frequency

Frame

Frequency

Internal

Logic

LCD

Power

Total*

Sleep

Mode

Standby

Mode

112 x 32 dots 1/32

75 kHz

73 Hz

(27 µA)

(16 µA)

Triple

(75 µA)

(15 µA) 0.1 µA

112 x 40 dots 1/40

75 kHz

73 Hz

(27 µA)

(16 µA)

Triple

(75 µA)

(15 µA)

112 x 48 dots 1/48

75 kHz

74 Hz

(27 µA)

(16 µA)

Triple

(75 µA)

(15 µA)

112 x 56 dots 1/56

75 kHz

74 Hz

(27 µA)

(16 µA)

Triple

(75 µA)

(15 µA)

112 x 64 dots 1/64

75 kHz

73 Hz

(27 µA)

(18 µA)

Quadruple

(99 µA)

(15 µA)

112 x 72 dots 1/72

80 kHz

70 Hz

(32 µA)

(18 µA)

Quadruple

(104 µA)

(15 µA)

112 x 80 dots 1/80

90 kHz

70 Hz

(35 µA)

(20 µA)

Five-times

(135 µA)

(15 µA)

Note : When a triple, quadruple, or five-times booster is used:

the total power consumption = Internal logic current + LCD power current x 3 (triple booster),

the total power consumption = Internal logic current + LCD power current x 4 (quadruple booster),

and

the total power consumption = Internal logic current + LCD power current x 5 (five-times booster)

Type Name

Types

External

Dimensions

Bus Interface

Operation Voltages

HD66740TB0

Bending TCP

4/8-bits parallel and clock synchronized serial

HD66740WTB0

Bending TCP

4/8-bits parallel and I2C bus interface

HCD66740BP

Au-bumped chip

4/8-bits parallel and clock synchronized serial

HCD66740WBP

Au-bumped chip

4/8-bits parallel and I2C bus interface

1.8 V to 3.6 V

HD66740

4

LCD Specification Comparison

(Under development)

Items

HD66725

HD66728

HD66740

Character display sizes

16 characters x 3 lines

16 characters x 10 lines

--

Graphic display sizes

96 x 26 dots

112 x 80 dots

112 x 80 dots

Multiplexing icons

192

--

--

Annunciator

1/2 duty: 192

--

--

Key scan control

8 x 4

8 x 4

--

LED control ports

--

--

--

General output ports

3

3

--

Operating power voltages

1.8 V to 5.5 V

1.8 V to 5.5 V

1.8 V to 3.6 V

Liquid crystal drive voltages

3 V to 6 V

4.5 V to 15 V

4.5 V to 15 V

I2C bus

--

--

I2C bus interface

(HD66740W)

Serial bus

Clock-synchronized serial

Clock-synchronized serial

Clock-synchronized serial

Parallel bus

4 bits, 8 bits

4 bits, 8 bits

4 bits, 8 bits

Expansion driver control

Impossible

Impossible

Impossible

Liquid crystal drive duty ratios

1/2, 10, 18, 26

1/8, 16, 24, 32, 40, 48, 56, 64

72, 80

1/8, 16, 24, 32, 40, 48, 56, 64

72, 80

Liquid crystal drive biases

1/4 to 1/6.5

1/4 to 1/10

1/4 to 1/10

Liquid crystal drive waveforms

B

B, C

B, C

Liquid crystal voltage booster

Single, double, or triple

Triple, quadruple, or five-

times

Triple, quadruple, or five-

times

Bleeder-resistor for liquid crystal drive

Incorporated (external)

Incorporated (external)

Incorporated (external)

Liquid crystal drive operational amplifier

Incorporated

Incorporated

Incorporated

Liquid crystal contrast adjuster

Incorporated

Incorporated

Incorporated

Horizontal smooth scroll

3-dot unit

--

--

Vertical smooth scroll

Line unit

Line unit

Line unit

Double-height display

Yes

Yes

Yes

DDRAM

80 x 8

160 x 8

--

CGROM

20,736

20,736

--

CGRAM

384 x 8

1,120 x 8

1,120 x 8

SEGRAM

96 x 8

--

--

No. of CGROM fonts

240 + 192

240 + 192

--

No. of CGRAM fonts

64

64

--

Font sizes

6 x 8

6 x 8

--

Bit map areas

96 x 26

112 x 80

112 x 80

R-C oscillation resistor/

oscillation frequency

External resistor,

incorporated (32 kHz)

External resistor

(70≠90 kHz)

External resistor

(70≠90 kHz)

Reset function

External

External

External

Low power control

Partial display off

Oscillation off

Liquid crystal power off

Key wake-up interrupt

Partial display off

Oscillation off

Liquid crystal power off

Key wake-up interrupt

Partial display off

Oscillation off

Liquid crystal power off

SEG/COM direction switching

SEG, COM

SEG, COM

SEG, COM

QFP package

--

--

--

TQFP package

--

--

--

TCP package

TCP-170

TCP-243

TCP-233

Bare chip

--

--

--

Bumped chip

Yes

Yes

Yes

No. of pins

170

243

243

Chip sizes

10.97 x 2.51

13.67 x 2.78

9.40 x 2.18

Pad intervals

80 µm

70 µm

50 µm

HD66740

5

HD66740 Block Diagram

System

interface

- Clock

synchro-

nized

serial

- I2C bus

- 4-bit bus

- 8-bit bus

Data

register

(DR)

Instruction register

(IR)

Address

counter

(AC)

Timing generator

Character

generator RAM

(CGRAM)

1,120 bytes

Parallel/serial converter

112-bit

latch

circuit

112-bit

segment

shift

register

80-bit bidirectional

common shift register

Common

driver

Segment

driver

LCD drive

voltage

selector

CPG

Instruction

decoder

RS

RW/RD*/SDA

E/WR*/SCL

Vcc

V

LCD

COM1/80--

COM80/1

SEG1/112--

SEG112/1

OSC1

OSC2

8

8

8

10

8

Vci

Triple to

five-times

booster

C1+

IM2-1

RESET*

C1-

+ -

+ -

+ -

+ -

VLOUT

+ -

GND

VR

R

R

R

0

R

TEST

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

OPOFF

IM0/ID

C2+

C2-

CS*

C3+

C3-

Contrast adjuster

Drive bias controller

C4+

C4-

VTEST1--

VTEST3

DB0-DB7

HD66740

6

HD66740 Pad Arrangement

Rev 0.5

- Chip size : 9.40mm x 2.18mm

- Chip thickness : 550um (typ.)

- PAD coordinates : PAD center

- Coodinate origin : Chip center

- Au bump size (pin number is shown in the

blacket)

(1)80um x 80um

Dummy1(1) to Dummy2(78),

Dummy3(104), Dummy20(263)

(2)45um x 80um

COM34(105) to COM80(119)

Dummy4(120)

Dummy5(121) to Dummy10(126)

Dummy13(241) to Dummy18(246)

Dummy19(247)

COM72(248) to COM58(262)

(3)80um x 45um

COM57(264) to COM1(288)

COM9(79) to COM33(103)

(4)35um x 80um

Dummy11(127)

SEG1(128) to SEG112(239)

Dummy12(240)

- Au bump pitch:

Refer PAD coodinate

- Au bump height : 15um(typ.)

- No cross recognition mark

(Top view)

HD66740

OSC2

OSC1

Vci

Y

X

C2-

C2+

C2+

Vci

Vci

Vcc

E/WR*/SCL

VTEST3

VTEST2

VTEST1

GNDDUM2

C1-

C1-

VLOUT

VLOUT

V

LCD

V

LCD

C1+

Vcc

Vcc

RW/RD*/SDA

GND

GND

GND

RS

CS*

RESET*

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

GNDDUM

IM2

IM1

IM0/ID

VccDUM

OPOFF

TEST

C3-

C3-

C3+

C3+

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

COM1/80

COM2/79

COM3/78

COM4/77

COM6/75

COM7/74

COM8/73

COM41/40

COM42/39

COM43/38

COM44/37

COM5/76

COM45/36

COM46/35

COM47/34

COM48/33

COM49/32

COM50/31

COM51/30

COM52/29

COM53/28

COM54/27

COM55/26

COM56/25

COM14/67

COM15/66

COM16/65

COM17/64

COM18/63

COM19/62

COM21/60

COM22/59

COM23/58

COM24/57

COM25/56

COM26/55

COM27/54

COM28/53

COM20/61

COM29/52

COM30/51

COM13/68

COM12/69

COM11/70

COM10/71

COM31/50

COM32/49

SEG9/104

SEG8/105

SEG7/106

SEG6/107

SEG5/108

SEG4/109

SEG101/12

SEG102/11

SEG103/10

SEG104/9

SEG105/8

SEG106/7

SEG107/6

SEG108/5

SEG109/4

SEG112/1

SEG111/2

SEG1/112

SEG2/111

SEG3/110

SEG110/3

COM57/24

COM33/48

SEG10/103

SEG11/102

SEG100/13

SEG99/14

SEG12/101

SEG13/100

SEG14/99

C4-

C4-

C4+

C4+

COM72/9

COM71/10

COM70/11

COM69/12

COM68/13

COM67/14

COM66/15

COM58/23

COM59/22

COM60/21

COM61/20

COM62/19

COM63/18

COM64/17

COM65/16

COM80/1

COM79/2

COM78/3

COM77/4

COM76/5

COM75/6

COM74/7

COM34/47

COM35/46

COM36/45

COM37/44

COM38/43

COM39/42

COM40/41

COM73/8

Dummy1

SEG25/88

SEG26/87

SEG27/86

SEG28/85

SEG29/84

SEG30/83

SEG31/82

SEG32/81

SEG33/80

SEG34/79

SEG35/78

SEG36/77

SEG37/76

SEG38/75

SEG39/74

SEG40/73

SEG41/72

SEG42/71

SEG43/70

SEG44/69

SEG45/68

SEG46/67

SEG47/66

SEG48/65

SEG49/64

SEG50/63

SEG51/62

SEG52/61

SEG53/60

SEG54/59

SEG55/58

SEG56/57

SEG57/56

SEG58/55

SEG59/54

SEG60/53

SEG61/52

SEG62/51

SEG63/50

SEG64/49

SEG65/48

SEG66/47

SEG67/46

SEG68/45

SEG69/44

SEG70/43

SEG71/42

SEG72/41

SEG73/40

SEG74/39

SEG75/38

SEG76/37

SEG77/36

SEG78/35

SEG79/34

SEG80/33

SEG81/32

SEG82/31

SEG83/30

SEG84/29

SEG85/28

SEG86/27

SEG87/26

SEG88/25

SEG89/24

SEG90/23

SEG91/22

SEG92/21

SEG93/20

SEG94/19

SEG95/18

SEG96/17

SEG97/16

SEG98/15

SEG24/89

SEG23/90

SEG22/91

SEG21/92

SEG20/93

SEG19/94

SEG18/95

SEG17/96

SEG16/97

SEG15/98

COM9/72

C1+

C2-

VLOUT

V

LCD

Dummy2

Dummy3

Dummy4

Dummy5

Dummy6

Dummy7

Dummy11

Dummy20

Vcc

GND

C3+

C4-

C4+

C2-

C2+

C1-

VLOUT

V

LCD

C1+

C3-

Dummy8

Dummy9

Dummy12

Dummy13

Dummy14

Dummy15

Dummy19

Dummy16

Dummy17

Vci

Dummy10

Dummy18

GND

HD66740

TYPE CODE

NO.1

NO.2

NO.288

NO.78

NO.77

NO.79

NO.103

NO.104

NO.105

NO.262

NO.263

NO.264

HD66740

7

HD66740 Pad Coordinate

2000.06.13 (Unit : um)

No.

PAD NAME

X

Y

No.

PAD NAME

X

Y

No.

PAD NAME

X

Y

No.

PAD NAME

X

Y

1

DUMMY1

-4538

-930

73

V5OUT

3834

-930

145

SEG18/95

1930

928

217

SEG90/23

-1679

928

2

GNDDUM

-4336

-930

74

VTEST1

3936

-930

146

SEG19/94

1880

928

218

SEG91/22

-1729

928

3

IM2

-4190

-930

75

VTEST2

4038

-930

147

SEG20/93

1829

928

219

SEG92/21

-1779

928

4

IM1

-4045

-930

76

VTEST3

4140

-930

148

SEG21/92

1779

928

220

SEG93/20

-1829

928

5

IM0/ID

-3915

-930

77

GNDDUM2

4336

-930

149

SEG22/91

1729

928

221

SEG94/19

-1880

928

6

VCCDUM

-3813

-930

78

DUMMY2

4538

-930

150

SEG23/90

1679

928

222

SEG95/18

-1930

928

7

OPOFF

-3711

-930

79

COM9/72

4538

-721

151

SEG24/89

1629

928

223

SEG96/17

-1980

928

8

TEST

-3609

-930

80

COM10/71

4538

-661

152

SEG25/88

1579

928

224

SEG97/16

-2030

928

9

DB7

-3466

-930

81

COM11/70

4538

-601

153

SEG26/87

1529

928

225

SEG98/15

-2080

928

10

DB6

-3321

-930

82

COM12/69

4538

-541

154

SEG27/86

1479

928

226

SEG99/14

-2130

928

11

DB5

-3177

-930

83

COM13/68

4538

-481

155

SEG28/85

1428

928

227

SEG100/13

-2180

928

12

DB4

-3032

-930

84

COM14/67

4538

-421

156

SEG29/84

1378

928

228

SEG101/12

-2230

928

13

DB3

-2887

-930

85

COM15/66

4538

-361

157

SEG30/83

1328

928

229

SEG102/11

-2281

928

14

DB2

-2742

-930

86

COM16/65

4538

-301

158

SEG31/82

1278

928

230

SEG103/10

-2331

928

15

DB1

-2597

-930

87

COM17/64

4538

-240

159

SEG32/81

1228

928

231

SEG104/9

-2381

928

16

DB0

-2453

-930

88

COM18/63

4538

-180

160

SEG33/80

1178

928

232

SEG105/8

-2431

928

17

RESET*

-2308

-930

89

COM19/62

4538

-120

161

SEG34/79

1128

928

233

SEG106/7

-2481

928

18

CS*

-2163

-930

90

COM20/61

4538

-60

162

SEG35/78

1078

928

234

SEG107/6

-2531

928

19

RS

-2018

-930

91

COM21/60

4538

0

163

SEG36/77

1028

928

235

SEG108/5

-2581

928

20

E/WR*/SCL

-1873

-930

92

COM22/59

4538

60

164

SEG37/76

977

928

236

SEG109/4

-2631

928

21

RW/RD*/SDA

-1729

-930

93

COM23/58

4538

120

165

SEG38/75

927

928

237

SEG110/3

-2682

928

22

GND

-1627

-930

94

COM24/57

4538

180

166

SEG39/74

877

928

238

SEG111/2

-2732

928

23

GND

-1525

-930

95

COM25/56

4538

240

167

SEG40/73

827

928

239

SEG112/1

-2782

928

24

GND

-1423

-930

96

COM26/55

4538

301

168

SEG41/72

777

928

240

DUMMY12

-2836

928

25

GND

-1321

-930

97

COM27/54

4538

361

169

SEG42/71

727

928

241

DUMMY13

-2981

928

26

GND

-1219

-930

98

COM28/53

4538

421

170

SEG43/70

677

928

242

DUMMY14

-3041

928

27

OSC2

-1117

-930

99

COM29/52

4538

481

171

SEG44/69

627

928

243

DUMMY15

-3101

928

28

OSC1

-972

-930

100

COM30/51

4538

541

172

SEG45/68

576

928

244

DUMMY16

-3161

928

29

VCC

-791

-930

101

COM31/50

4538

601

173

SEG46/67

526

928

245

DUMMY17

-3221

928

30

VCC

-689

-930

102

COM32/49

4538

661

174

SEG47/66

476

928

246

DUMMY18

-3281

928

31

VCC

-587

-930

103

COM33/48

4538

721

175

SEG48/65

426

928

247

DUMMY19

-3431

928

32

VCC

-485

-930

104

DUMMY3

4538

928

176

SEG49/64

376

928

248

COM72/9

-3495

928

33

VCI

-332

-930

105

COM34/47

4336

928

177

SEG50/63

326

928

249

COM71/10

-3555

928

34

VCI

-230

-930

106

COM35/46

4276

928

178

SEG51/62

276

928

250

COM70/11

-3615

928

35

VCI

-128

-930

107

COM36/45

4216

928

179

SEG52/61

226

928

251

COM69/12

-3675

928

36

VCI

-26

-930

108

COM37/44

4156

928

180

SEG53/60

175

928

252

COM68/13

-3735

928

37

C4+

76

-930

109

COM38/43

4096

928

181

SEG54/59

125

928

253

COM67/14

-3795

928

38

C4+

178

-930

110

COM39/42

4036

928

182

SEG55/58

75

928

254

COM66/15

-3856

928

39

C4+

280

-930

111

COM40/41

3976

928

183

SEG56/57

25

928

255

COM65/16

-3916

928

40

C4-

381

-930

112

COM73/8

3916

928

184

SEG57/56

-25

928

256

COM64/17

-3976

928

41

C4-

483

-930

113

COM74/7

3856

928

185

SEG58/55

-75

928

257

COM63/18

-4036

928

42

C4-

585

-930

114

COM75/6

3795

928

186

SEG59/54

-125

928

258

COM62/19

-4096

928

43

C3+

687

-930

115

COM76/5

3735

928

187

SEG60/53

-175

928

259

COM61/20

-4156

928

44

C3+

789

-930

116

COM77/4

3675

928

188

SEG61/52

-226

928

260

COM60/21

-4216

928

45

C3+

891

-930

117

COM78/3

3615

928

189

SEG62/51

-276

928

261

COM59/22

-4276

928

46

C3-

993

-930

118

COM79/2

3555

928

190

SEG63/50

-326

928

262

COM58/23

-4336

928

47

C3-

1095

-930

119

COM80/1

3495

928

191

SEG64/49

-376

928

263

DUMMY20

-4538

928

48

C3-

1197

-930

120

DUMMY4

3431

928

192

SEG65/48

-426

928

264

COM57/24

-4538

721

49

C2+

1299

-930

121

DUMMY5

3281

928

193

SEG66/47

-476

928

265

COM56/25

-4538

661

50

C2+

1401

-930

122

DUMMY6

3221

928

194

SEG67/46

-526

928

266

COM55/26

-4538

601

51

C2+

1503

-930

123

DUMMY7

3161

928

195

SEG68/45

-576

928

267

COM54/27

-4538

541

52

C2-

1605

-930

124

DUMMY8

3101

928

196

SEG69/44

-627

928

268

COM53/28

-4538

481

53

C2-

1707

-930

125

DUMMY9

3041

928

197

SEG70/43

-677

928

269

COM52/29

-4538

421

54

C2-

1809

-930

126

DUMMY10

2981

928

198

SEG71/42

-727

928

270

COM51/30

-4538

361

55

C1+

1911

-930

127

DUMMY11

2836

928

199

SEG72/41

-777

928

271

COM50/31

-4538

301

56

C1+

2013

-930

128

SEG1/112

2782

928

200

SEG73/40

-827

928

272

COM49/32

-4538

240

57

C1+

2115

-930

129

SEG2/111

2732

928

201

SEG74/39

-877

928

273

COM48/33

-4538

180

58

C1-

2217

-930

130

SEG3/110

2682

928

202

SEG75/38

-927

928

274

COM47/34

-4538

120

59

C1-

2319

-930

131

SEG4/109

2631

928

203

SEG76/37

-977

928

275

COM46/35

-4538

60

60

C1-

2421

-930

132

SEG5/108

2581

928

204

SEG77/36

-1028

928

276

COM45/36

-4538

0

61

VLOUT

2523

-930

133

SEG6/107

2531

928

205

SEG78/35

-1078

928

277

COM44/37

-4538

-60

62

VLOUT

2625

-930

134

SEG7/106

2481

928

206

SEG79/34

-1128

928

278

COM43/38

-4538

-120

63

VLOUT

2727

-930

135

SEG8/105

2431

928

207

SEG80/33

-1178

928

279

COM42/39

-4538

-180

64

VLOUT

2829

-930

136

SEG9/104

2381

928

208

SEG81/32

-1228

928

280

COM41/40

-4538

-240

65

VLCD

2930

-930

137

SEG10/103

2331

928

209

SEG82/31

-1278

928

281

COM8/73

-4538

-301

66

VLCD

3032

-930

138

SEG11/102

2281

928

210

SEG83/30

-1328

928

282

COM7/74

-4538

-361

67

VLCD

3134

-930

139

SEG12/101

2230

928

211

SEG84/29

-1378

928

283

COM6/75

-4538

-421

68

VLCD

3236

-930

140

SEG13/100

2180

928

212

SEG85/28

-1428

928

284

COM5/76

-4538

-481

69

V1OUT

3426

-930

141

SEG14/99

2130

928

213

SEG86/27

-1479

928

285

COM4/77

-4538

-541

70

V2OUT

3528

-930

142

SEG15/98

2080

928

214

SEG87/26

-1529

928

286

COM3/78

-4538

-601

71

V3OUT

3630

-930

143

SEG16/97

2030

928

215

SEG88/25

-1579

928

287

COM2/79

-4538

-661

72

V4OUT

3732

-930

144

SEG17/96

1980

928

216

SEG89/24

-1629

928

288

COM1/80

-4538

-721

HD66740

8

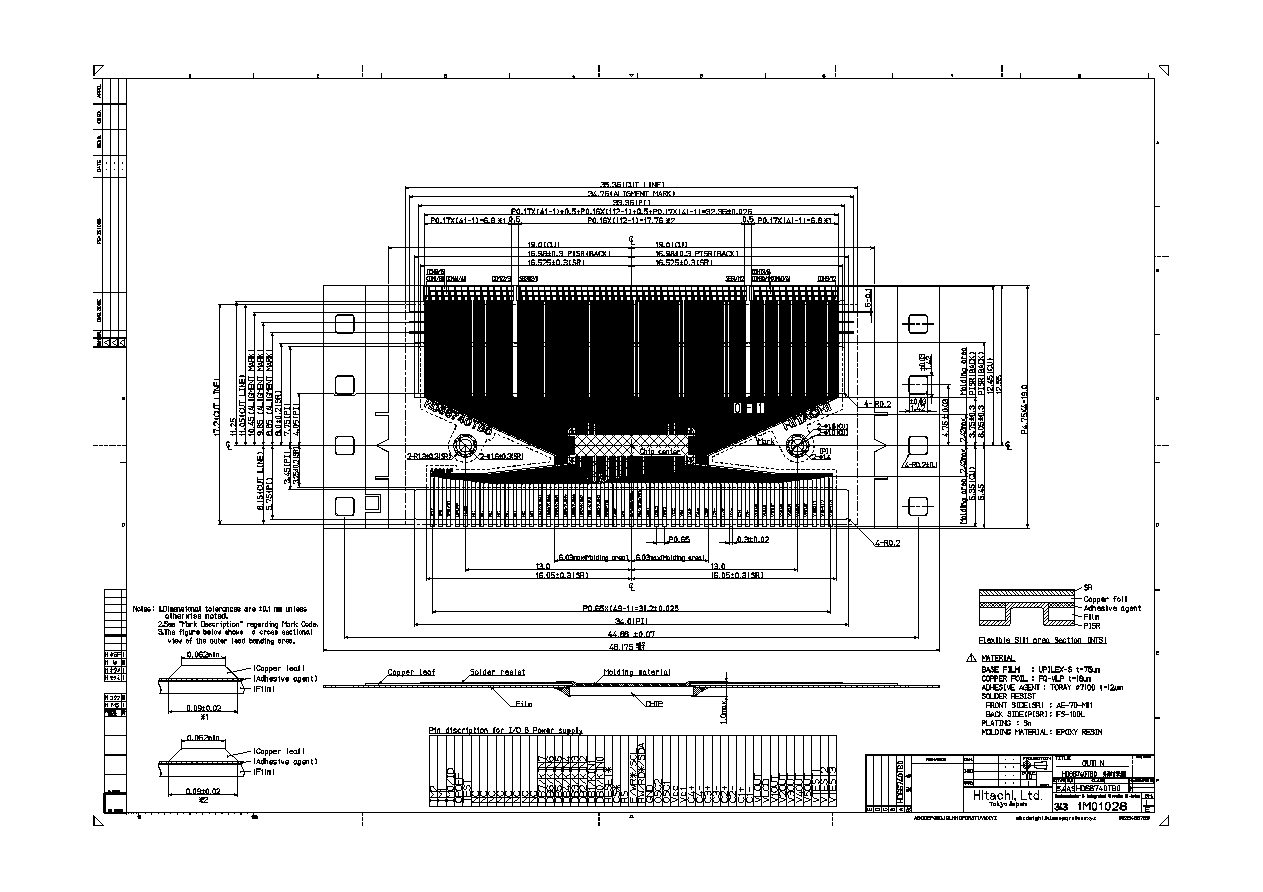

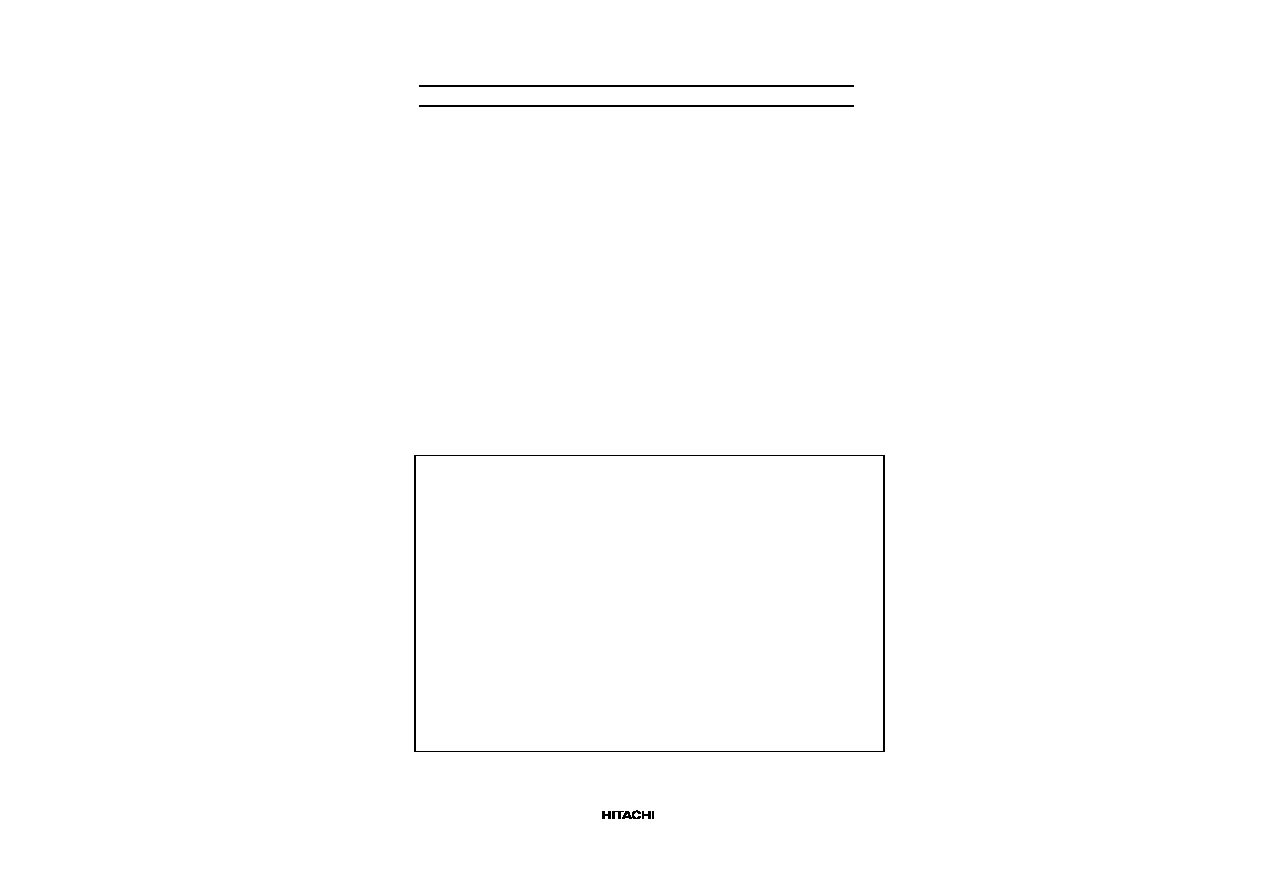

TCP Dimensions (HD66740TB0)

COM1/80

COM8/73

SEG112/1

SEG1/112

COM9/72

0.16-mm

pitch

HITACHI

HITACHI

HD66740

HD66740

COM41/40

COM72/9

IM2

IM1

IM0/ID

OPOFF

TEST

NC

NC

NC

NC

NC

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

RESET*

CS*

RS

E/WR*/SCL

RW/RD*/SDA

GND

OSC2

OSC1

Vcc

Vci

C2+

C2-

C1+

C1-

VLOUT

VLCD

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

NC

NC

NC

VTEST1

VTSET2

VTEST3

0.65-mm

pitch

Dummy

Dummy

C3+

C3-

COM80/1

COM73/8

COM40/41

Bending slit

4.0 mm

0.17P x (41 ≠ 1)

= 6.80 mm

0.17P x (41 ≠ 1)

= 6.80 mm

0.50 mm

0.50 mm

32.36 mm

SEG111/2

SEG110/3

SEG109/4

SEG2/111

SEG3/110

SEG4/109

C4+

C4-

I/O, Power supply

0.65P x (49 ≠ 1)

= 31.20 mm

LCD drive

0.16P x (112 ≠ 1)

= 17.76 mm

HD66740

9

Pin Functions

Table 2

Pin Functional Description

Signals

Number of

Pins

I/O

Connected to

Functions

IM2, IM1

2

I

GND or V

CC

Selects the MPU interface mode:

IM2

"GND"

"GND"

"Vcc"

"Vcc"

IM1

"GND"

"Vcc"

"GND"

"Vcc"

MPU interface mode

Clock synchronized serial interface

68-system parallel interface

I2C bus interface

80-system parallel interface

IM0/ID

1

I

GND or V

CC

Selects the transfer bus length for a parallel bus

interface.

GND: 8-bit bus, Vcc: 4-bit bus

Inputs the ID of the device ID code for a serial bus and

I2C bus interface.

CS*

1

I

MPU

Selects the HD66740:

Low: HD66740 is selected and can be accessed

High: HD66740 is not selected and cannot be

accessed

Must be fixed at GND level when not in use.

RS

1

I

MPU

Selects the register for a parallel bus interface.

Low: Instruction

High: RAM access

Must be fixed at GND level when not in use.

E/WR*/SCL

1

I

MPU

For an 80-system parallel bus interface, serves as a

write strobe signal and writes data at the low level.

For a 68-system parallel bus interface, serves as an

enable signal to activate data read/write operation.

Inputs the serial transfer clock for a serial interface.

Fetches data at the rising edge of a clock.

RW/RD*/

SDA

1

I or

I/O

MPU

For an 80-system parallel bus interface, serves as a

write strobe signal and reads data at the low level.

For a 68-system parallel bus interface, serves as a

signal to select data read/write operation.

Low: Write High: Read

Serves as the bidirectional serial transfer data for a

serial interface. Sends/Receives data.

HD66740

10

Table 2

Pin Functional Description (cont)

Signals

Number of

Pins

I/O

Connected to

Functions

DB0≠DB7

8

I/O or

I

MPU

Serves as a bidirectional data bus for a parallel bus

interface.

For a 4-bit bus, data transfer uses DB7-DB4

Must be fixed at GND level when serial interface mode

is used.

COM1/80≠

COM80/1

80

O

LCD

Common output signals for graphics display: COM1 to

COM8 for the first line, COM9 to COM16 for the

second line, COM17 to COM24 for the third line,

COM25 to COM32 for the fourth line, and COM73 to

COM80 for the 10th line. All the unused pins output

unselected waveforms. In the sleep mode (SLP = 1) or

standby mode (STB = 1), all pins output GND level.

The CMS bit can change the shift direction of the

common signal. For example, if CMS = 0, COM1/80 is

COM1. If CMS = 1, COM1/80 is COM80.

Note that the start position of the common output (the

first line) is shifted by CN1≠CN0 bits.

SEG1/112≠

SEG112/1

112

O

LCD

Segment output signals for graphics display. In the

sleep mode (SLP = 1) or standby mode (STB = 1), all

pins output GND level.

The SGS bit can change the shift direction of the

segment signal. For example, if SGS = 0, SEG1/112 is

SEG1. If SGS = 1, SEG1/112 is SEG112.

V1OUT≠V5

OUT

5

I or O

Open or

external

bleeder-resistor

Used for output from the internal operational amplifiers

when they are used (OPOFF = GND); attach a

capacitor to stabilize the output. When the amplifiers

are not used (OPOFF = V

CC

), V1 to V5 voltages can be

supplied to these pins externally.

V

LCD

3

--

Power supply

Power supply for LCD drive. V

LCD

≠ GND = 15 V max.

V

CC

, GND

12

--

Power supply

V

CC

: +1.8 V to +3.6 V; GND (logic): 0 V

OSC1,

OSC2

2

I or O

Oscillation-

resistor or clock

For R-C oscillation using an external resistor, connect

an external resistor. For external clock supply, input

clock pulses to OSC1.

Vci

5

I

Power supply

Inputs a reference voltage and supplies power to the

booster; generates the liquid crystal display drive

voltage from the operating voltage. The boosting

output voltage must not be larger than the absolute

maximum ratings.

Must be left disconnected when the booster is not

used.

VLOUT

3

O

V

LCD

pin/booster

capacitance

Potential difference between Vci and GND is triple- to

five-times-boosted and then output. Magnitude of

boost is selected by instruction.

HD66740

11

Table 2

Pin Functional Description (cont)

Signals

Number of

Pins

I/O

Connected to

Functions

C1+, C1≠

8

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C2+, C2≠

6

--

Booster

capacitance

External capacitance should be connected here when

using the triple or more booster.

C3+, C3≠

6

--

Booster

capacitance

External capacitance should be connected here when

using the quadruple and five-times booster.

C4+, C4≠

6

--

Booster

capacitance

External capacitance should be connected here when

using the five-times booster.

RESET*

1

I

MPU or external

R-C circuit

Reset pin. Initializes the LSI when low.

OPOFF

1

I

V

CC

or GND

Turns the internal operational amplifier off when

OPOFF = V

CC

, and turns it on when OPOFF = GND. If

the amplifier is turned off (OPOFF = V

CC

), V1 to V5

must be supplied to the V1OUT to V5OUT pins.

VccDUM

1

O

Input pins

Outputs the internal V

CC

level; shorting this pin sets the

adjacent input pin to the V

CC

level.

GNDDUM

1

O

Input pins

Outputs the internal GND level; shorting this pin sets

the adjacent input pin to the GND level.

Dummy

5

--

--

Dummy pad. Must be left disconnected.

TEST

1

I

GND

Test pin. Must be fixed at GND level.

VTEST1

1

I

GND or V

CC

Adjusts the driving capability of the internal operationa

amplifier for the LCD. This signal enters the normal

drive mode in the GND side, and it enters the high-

power drive mode in the V

CC

side. When the display

quality is not sufficient, use the high-power drive mode

even though the power-consumption current is large.

VTEST2

1

--

--

Test pin. Must be left disconnected.

VTEST3

1

I

V

CC

or GND

Adjusts the driving capability of the internal operationa

amplifier for the LCD. This signal enters the normal

drive mode or high-power mode in the GND side

according to the VTEST1 pin setting, and it enters the

low-power drive mode in the V

CC

side. Use this signa

in the low-power mode so that the display quality is no

lowered.

HD66740

12

Block Function Description

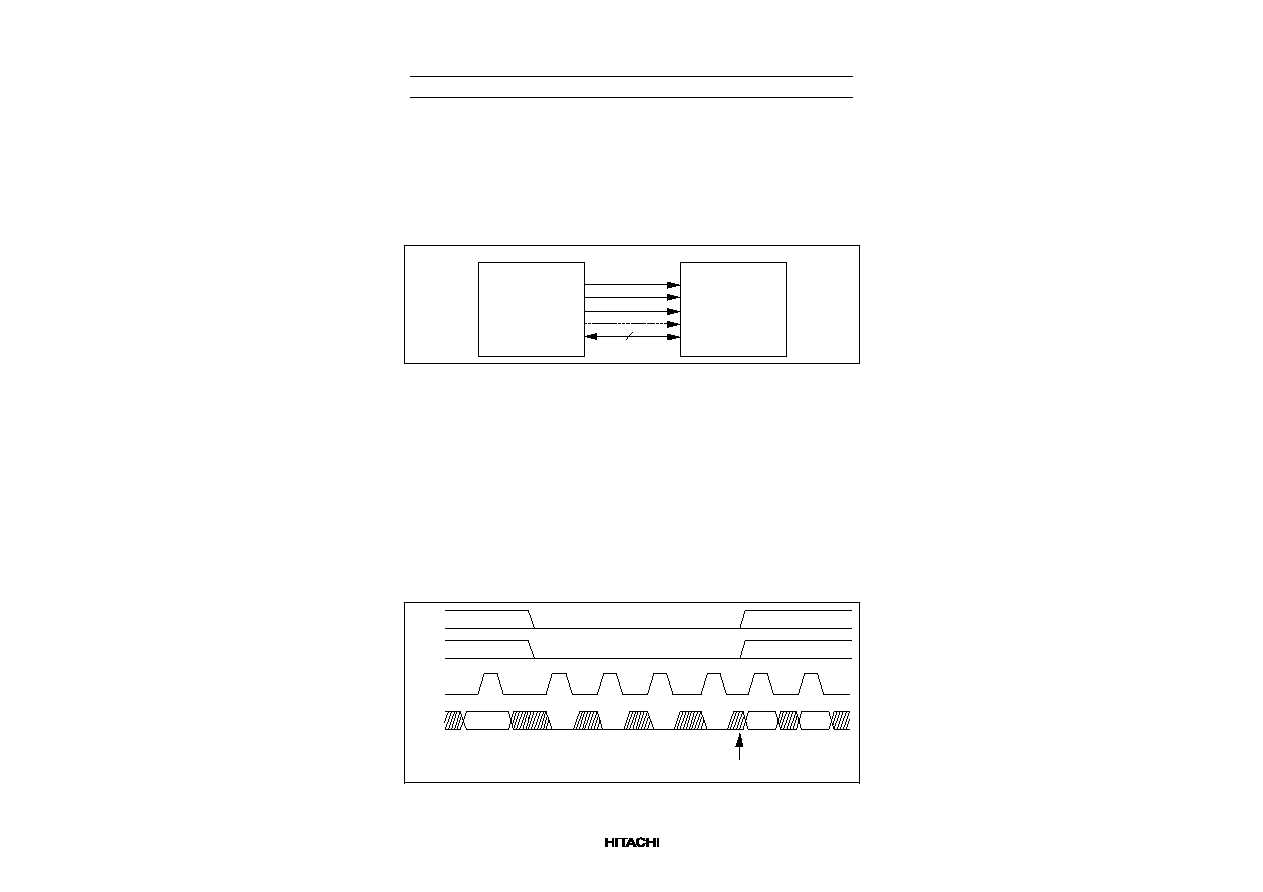

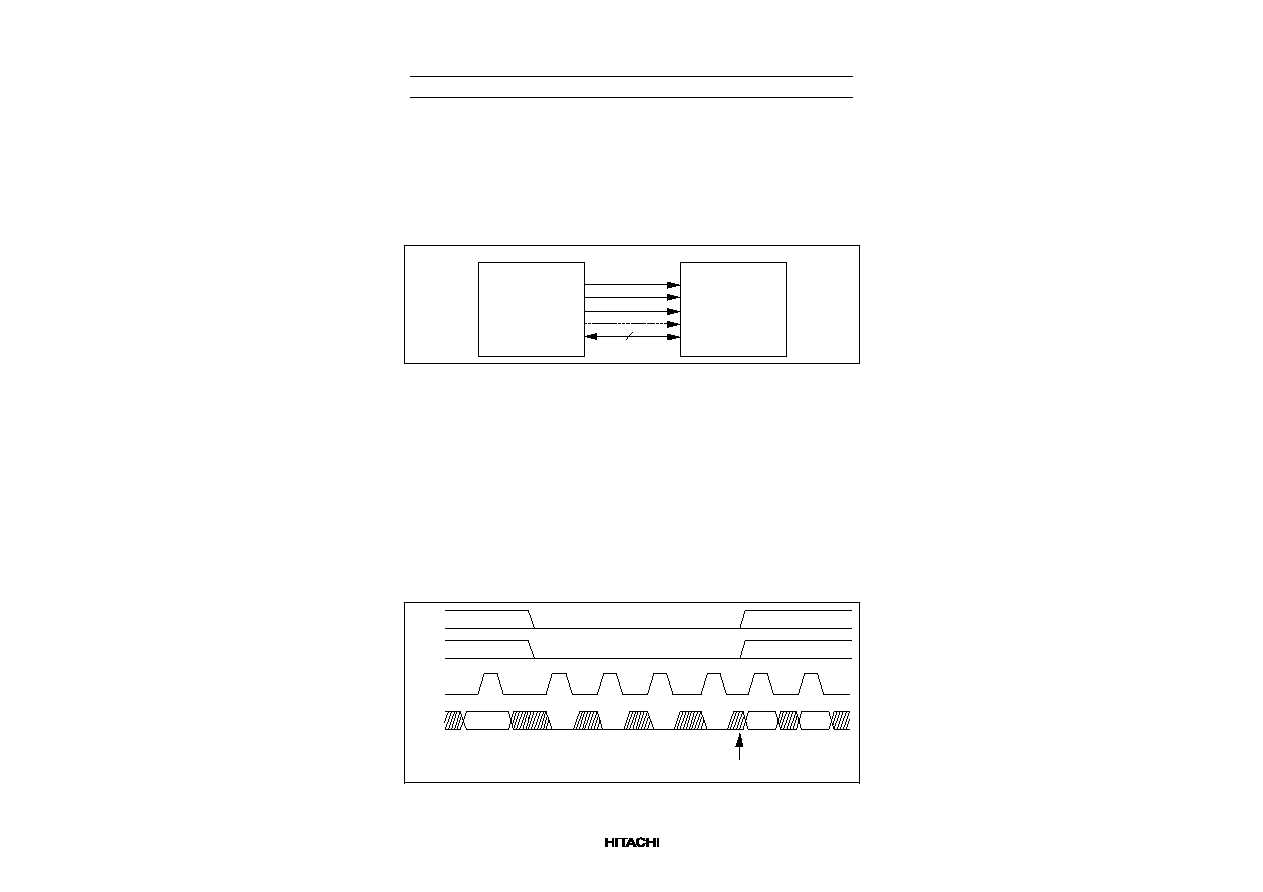

System Interface

The HD66740 has six types of system interfaces, and a clock-synchronized serial, an I2C bus interface, a

68-system 4-bit/8-bit bus, and a 80-system 4-bit/8-bit bus. The interface mode is selected by the IM2-0

pins.

The HD66740 has two 8-bit registers: an instruction register (IR) and a data register (DR).

The IR stores instruction codes, such as clear display, display control, and address information for the

display character generator RAM (CGRAM).

The DR temporarily stores data to be written into the CGRAM. Data written into the DR from the MPU is

automatically written into the CGRAM by internal operation. When address information is written into the

IR, data is read and then stored in the DR from the CGRAM by internal operation. Data is read through the

DR when reading from the RAM, and the first read data is invalid and the second and the following data are

normal. After reading, data in the CGRAM at the next address is sent to the DR for the next reading from

the MPU.

Execution time for instruction excluding clear display is 0 clock cycle and instructions can be written in

succession.

Table 3

Register Selection by RS and R/W Bits

R/W Bit

RS Bit

Operations

0

0

Write instructions to IR

1

0

-

0

1

DR write as an internal operation (DR to CGRAM)

1

1

DR read as an internal operation (CGRAM to DR)

Address Counter (AC)

The address counter (AC) assigns addresses to the CGRAM. When an address set instruction is written into

the IR, the address information is sent from the IR to the AC.

After writing into the CGRAM, the AC is automatically incremented by 1 (or decremented by 1). After

reading from the data, the RDM bit automatically updates or does not update the AC.

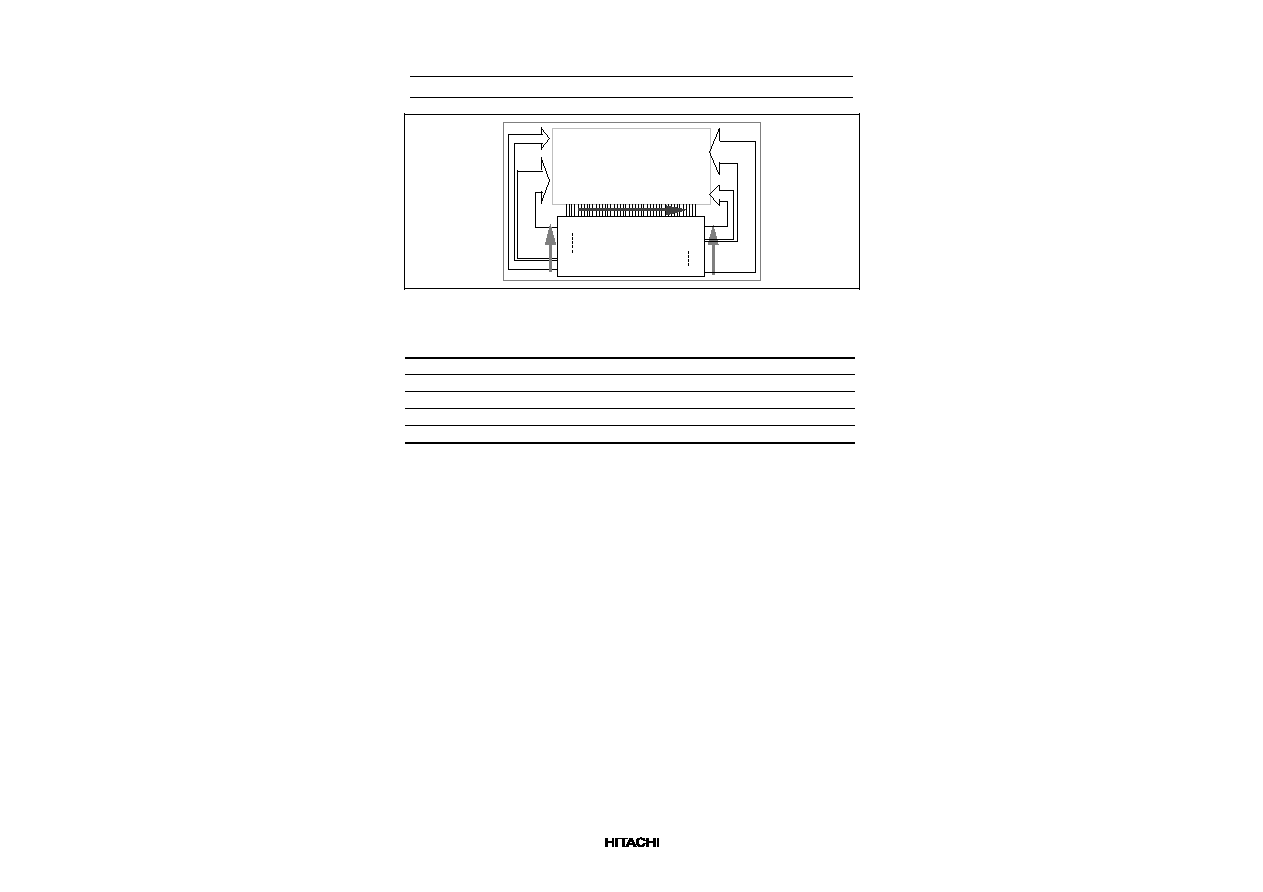

Character Generator RAM (CGRAM)

The CGRAM serves as a RAM to store 112 x 80-dot bit pattern data in the graphics display mode. Here,

display patterns are directly written into CGRAM. For details, see the Graphics Display section.

Timing Generator

The timing generator generates timing signals for the operation of internal circuits such as the CGRAM.

The RAM read timing for display and internal operation timing by MPU access are generated separately to

avoid interference with one another. This prevents flickering in areas other than the display area when

writing data to the CGRAM, for example.

HD66740

13

Oscillation Circuit (OSC)

The HD66740 can provide R-C oscillation simply through the addition of an external oscillation-resistor

between the OSC1 and OSC2 pins. The appropriate oscillation frequency for operating voltage, display size,

and frame frequency can be obtained by adjusting the external-resistor value. Clock pulses can also be

supplied externally. Since R-C oscillation stops during the standby mode, current consumption can be

reduced. For details, see the Oscillation circuit section.

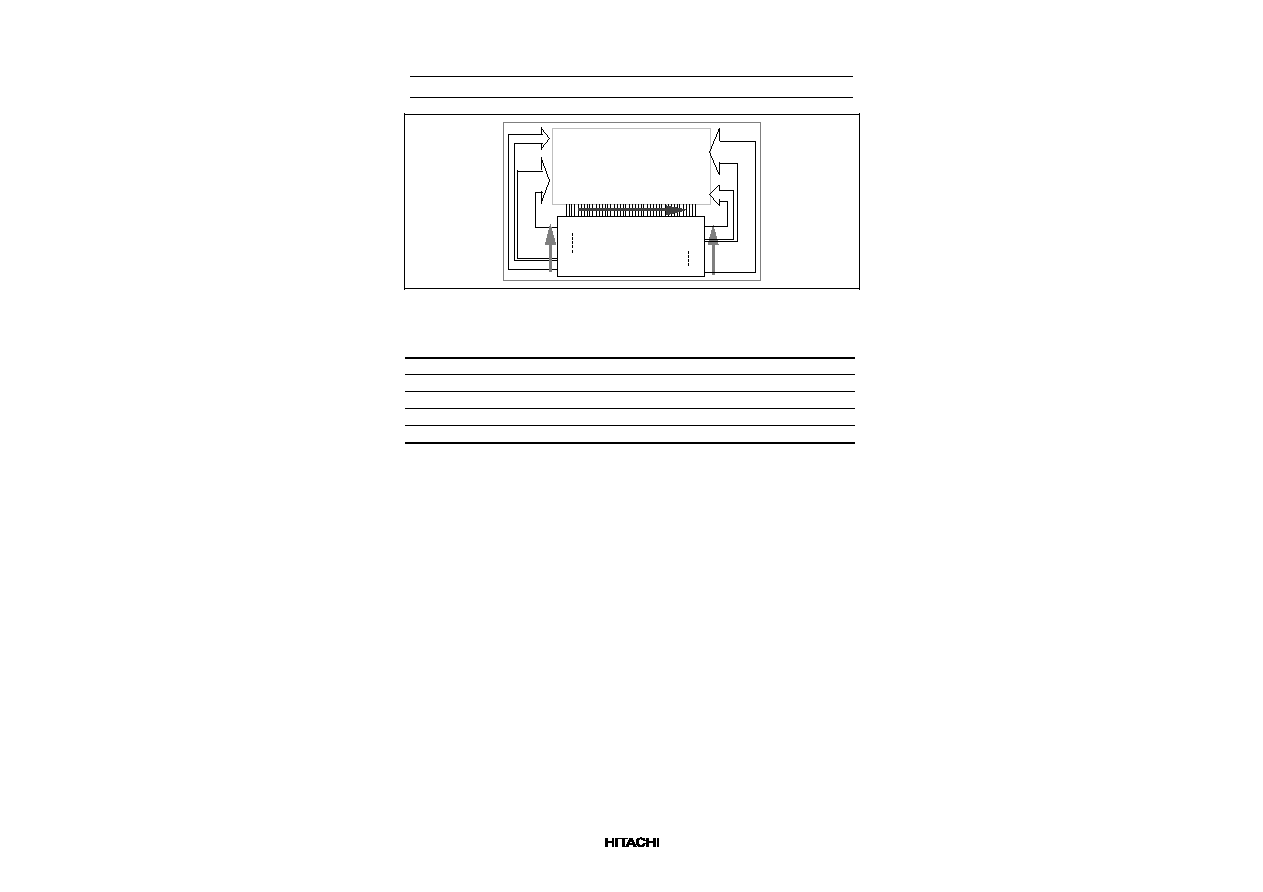

Liquid Crystal Display Driver Circuit

The liquid crystal display driver circuit consists of 80 common signal drivers (COM1 to COM80) and 112

segment signal drivers (SEG1 to SEG112). When the number of lines are selected by a program, the

required common signal drivers automatically output drive waveforms, while the other common signal

drivers continue to output unselected waveforms.

Graphics data is sent serially through a 112-bit shift register and latched when all needed data has arrived.

The latched data then enables the segment signal drivers to generate drive waveform outputs.

The shift direction of 112-bit data can be changed by the SGS bit. The shift direction for the common driver

can also be changed by the CMS bit by selecting an appropriate direction for the device mounting

configuration.

When display is off, or during the standby or sleep mode, all the above common and segment signal drivers

output the GND level, halting the display.

Booster (DC-DC Converter)

The booster generates triple, quadruple, or five-times voltage input to the Vci pin. With this, both the

internal logic units and LCD drivers can be controlled with a single power supply. Boost output level from

triple to five-times boost can be selected by software. For details, see the Power Supply for Liquid Crystal

Display Drive section.

V-Pin Voltage Follower

A voltage follower for each voltage level (V1 to V5) reduces current consumption by the LCD drive power

supply circuit. No external resistors are required because of the internal bleeder-resistor, which generates

different levels of LCD drive voltage. This internal bleeder-resistor can be software-specified from 1/4 bias

to 1/10 bias, according to the liquid crystal display drive duty value. The voltage followers can be turned off

while multiplexing drive is not being used. For details, see the Power Supply for Liquid Crystal Display

Drive section.

Contrast Adjuster

The contrast adjuster can be used to adjust LCD contrast in 64 steps by varying the LCD drive voltage by

software. This can be used to select an appropriate LCD brightness or to compensate for temperature.

HD66740

14

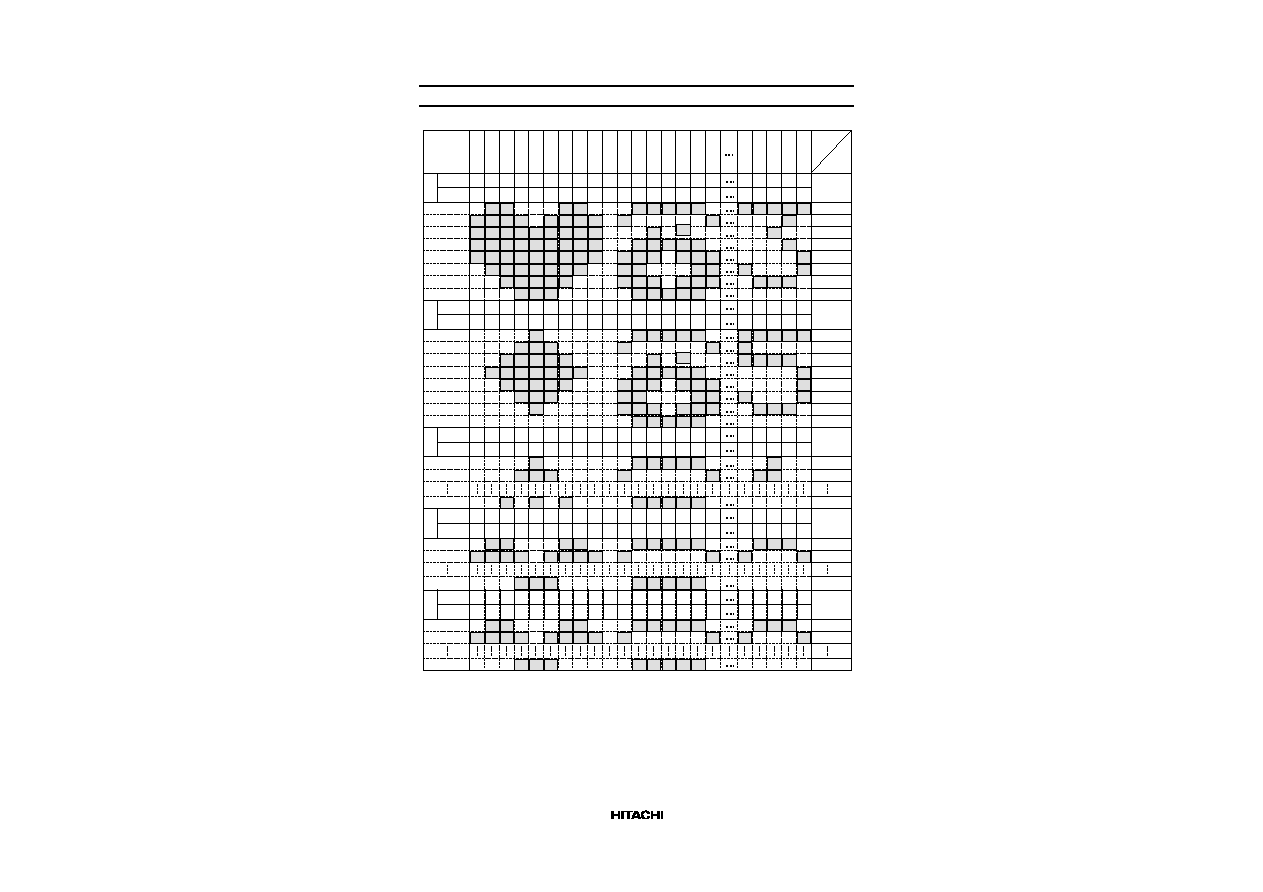

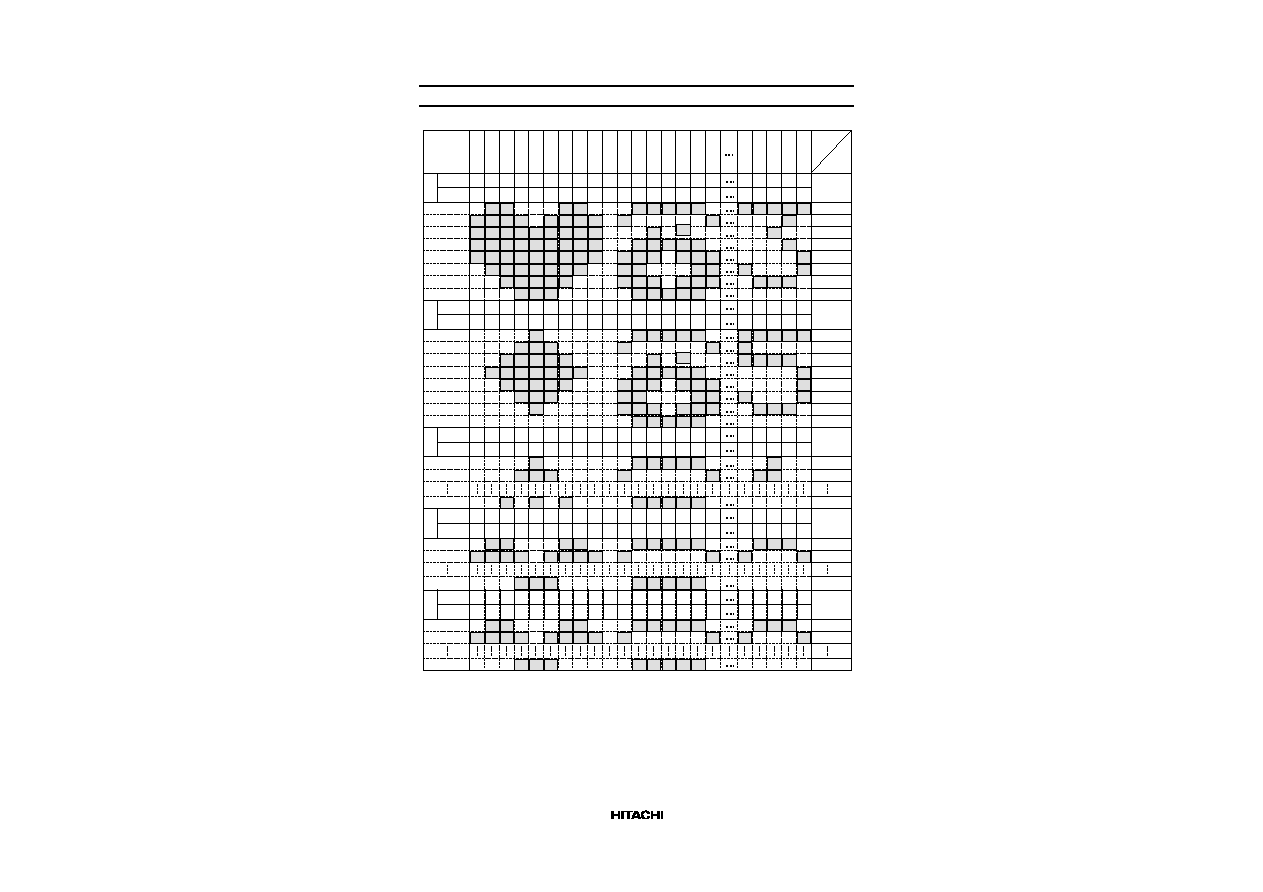

CGRAM Address Map

Table 4

Relationship between Display Position and CGRAM Address (1)

DB0

000

DB1

DB2

DB3

DB4

DB5

DB6

DB7

001 002 003 004 005 006 007 008 009 00A 00B 00C 00D 00E 00F 010

06E 06F

06D

06C

06B

COM1

COM2

COM3

COM4

COM5

COM6

COM7

COM8

DB0

080

DB1

DB2

DB3

DB4

DB5

DB6

DB7

081 082 083 084 085 086 087 088 089 08A 08B 08C 08D 08E 08F 090

0EE 0EF

0ED

0EC

0EB

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

DB0

100

DB1

DB7

101 102 103 104 105 106 107 108 109 10A 10B 10C 10D10E 10F 110

16E 16F

16D

16C

16B

COM17

COM18

COM24

SEG1/112

SEG2/111

SEG3/110

SEG4/109

SEG5/108

SEG6/107

SEG7/106

SEG8/105

SEG9/104

SEG10/103

SEG11/102

SEG12/101

SEG13/100

SEG14/99

SEG15/98

SEG16/97

SEG17/96

SEG108/5

SEG109/4

SEG110/3

SEG111/2

SEG112/1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

(HEX)

(HEX)

(HEX)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

DB0

180

DB1

DB7

181 182 183 184 185 186 187 188 189 18A 18B 18C 18D 18E 18F 180

1EE 1EF

1ED

1EC

1EB

COM25

COM26

COM32

0

0

0

1

0

1

1

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

(HEX)

0

0

0

0

0

0

0

0

0

1

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

1

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

06F 06E 06D 06C 06B 06A 069 068 067 066 065 064 063 062 061 060 05F

001 000

002

003

004

0EF 0EE 0ED0EC0EB 0EA 0E9 0E8 0E7 0E6 0E5 0E4 0E3 0E2 0E1 0E0 0DF

081 080

082

083

084

1EF 1EE 1ED1EC1EB 1EA 1E9 1E8 1E7 1E6 1E5 1E4 1E3 1E2 1E1 1E0 1DF

181 180

182

183

184

16F 16E 16D16C 16B 16A 169 168 167 166 165 164 163 162 161 160 15F

101 100

102

103

104

DB0

200

DB1

DB7

201 202 203 204 205 206 207 208 209 20A 20B 20C 20D 20E 20F 210

26E 26F

26D

26C

26B

COM33

COM34

COM40

0

0

0

1

0

1

1

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

(HEX)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

26F 26E 26D 26C 26B 26A 269 268 267 266 265 264 263 262 261 260 25F

201 200

202

203

204

SGS="0"

SGS="1"

Segment

Driver

Address

Common

Segment

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

Notes: 1. A set bit in CGRAM data 1 corresponds to display selection (lit) and 0 to non-selection (unlit).

HD66740

15

Table 5

Relationship between Display Position and CGRAM Address (2)

280 281 282 283 284 285 286 287 288 289 28A 28B 28C 28D 28E 28F 290

2EE 2EF

2ED

2EC

2EB

SEG1/112

SEG2/111

SEG3/110

SEG4/109

SEG5/108

SEG6/107

SEG7/106

SEG8/105

SEG9/104

SEG10/103

SEG11/102

SEG12/101

SEG13/100

SEG14/99

SEG15/98

SEG16/97

SEG17/96

SEG108/5

SEG109/4

SEG110/3

SEG111/2

SEG112/1

(HEX)

2EF 2EE 2ED2EC2EB 2EA 2E9 2E8 2E7 2E6 2E5 2E4 2E3 2E2 2E1 2E0 2DF

281 280

282

283

284

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

COM41

COM42

COM43

COM44

COM45

COM46

COM47

COM48

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

1

1

0

0

0

0

0

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

COM49

COM50

COM51

COM52

COM53

COM54

COM55

COM56

1

0

1

1

1

1

0

1

1

1

1

1

1

1

1

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

1

1

0

0

0

0

0

0

1

1

0

1

1

1

1

1

1

0

0

0

1

1

0

0

1

0

1

1

0

0

1

1

1

0

0

1

1

0

0

0

0

0

0

1

1

0

0

1

0

1

1

1

1

0

0

1

1

1

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

DB0

DB1

DB7

COM57

COM58

COM64

0

1

1

1

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

1

0

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

0

1

0

0

0

0

1

1

0

0

0

0

1

1

0

1

1

DB0

DB1

DB7

COM65

COM66

COM72

1

1

1

1

1

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

1

1

0

0

0

0

1

0

0

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

0

1

1

0

300 301 302 303 304 305 306 307 308 309 30A 30B 30C 30D 30E 30F 310

36E 36F

36D

36C

36B

(HEX)

36F 36E 36D 36C 36B 36A 369 368 367 366 365 364 363 362 361 360 35F

301 300

302

303

304

380 381 382 383 384 385 386 387 388 389 38A 38B 38C 38D 38E 38F 390

3EE 3EF

3ED

3EC

3EB

(HEX)

3EF 3EE 3ED3EC 3EB 3EA 3E9 3E8 3E7 3E6 3E5 3E4 3E3 3E2 3E1 3E0 3DF

381 380

382

383

384

400 401 402 403 404 405 406 407 408 409 40A 40B 40C 40D 40E 40F 410

46E 46F

46D

46C

46B

(HEX)

46F 46E 46D 46C 46B 46A 469 468 467 466 465 464 463 462 461 460 45F

401 400

402

403

404

DB0

DB1

DB7

COM73

COM74

COM80

1

1

1

1

1

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

1

1

0

0

0

0

1

0

0

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

0

1

1

480 481 482 483 484 485 486 487 488 489 48A 48B 48C 48D 48E 48F 490

4EE 4EF

4ED

4EC

4EB

(HEX)

4EF 4EE 4ED4EC4EB 4EA 4E9 4E8 4E7 4E6 4E5 4E4 4E3 4E2 4E1 4E0 4DF

481 480

482

483

484

SGS="0"

SGS="1"

Segment

Driver

Address

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

SGS="0"

SGS="1"

Address

Common

Segment

Notes: 1. A set bit in CGRAM data 1 corresponds to display selection (lit) and 0 to non-selection (unlit).

HD66740

16

Instructions

Outline

Only the instruction register (IR) and the data register (DR) of the HD66740 can be controlled by the

MPU. Before starting internal operation of the HD66740, control information is temporarily stored in

these registers to allow interfacing with various peripheral control devices or MPUs which operate at

different speeds. The internal operation of the HD66740 is determined by signals sent from the MPU.

These signals, which include the register selection signal (RS), the read/write signal (R/W), and the data

bus signal (DB0 to DB7), make up the HD66740 instructions. There are four categories of instructions

that:

∑

Control the display

∑

Control power management

∑

Set internal RAM addresses

∑

Transfer data with the internal RAM

Normally, instructions that perform data transfer with the internal RAM are used the most. However,

auto-incrementation by 1 (or auto-decrementation by 1) of internal HD66740 RAM addresses after each

data write can lighten the MPU program load.

Because instructions are executed in 0 cycle, instructions can be written in succession.

HD66740

17

Instruction Descriptions

Start Oscillation

The start oscillation instruction restarts the oscillator from the halt state in the standby mode. After

issuing this instruction, wait at least 10 ms for oscillation to stabilize before issuing the next instruction.

(See the Standby Mode section.)

R/W RS DB7

DB0

0

0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

0

0

0

1

1

Figure 1 Start Oscillation Instruction

Driver Output Control

CMS: Selects the output shift direction of a common driver. When CMS = "0", COM1/80 shifts to

COM1, and COM80/1 to COM80. When CMS = "1", COM1/80 shifts to COM80, and COM80/1 to

COM1. Output position of a common driver shifts depending on the CN1≠0 bit setting. For details,

see the Display On/Off Control section.

SGS: Selects the output shift direction of a segment driver. When SGS = "0", SEG1/112 shifts to

SEG1, and SEG112/1 to SEG112. When SGS = "1", SEG1/112 shifts SEG112, and SEG112/1 to

SEG1.

R/W RS DB7

DB0

0

0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

0

0

1

CMS SGS

Figure 2 Driver Output Control Instruction

HD66740

18

Power Control

AMP: When AMP = 1, each voltage follower for V1 to V5 pins and the booster are turned on. When

AMP = 0, current consumption can be reduced while the display is not being used.

SLP: When SLP = 1, the HD66740 enters the sleep mode, where the internal operations are halted except

for the R-C oscillator, thus reducing current consumption. For details, see the Sleep Mode section. Only

the power control (AMP, SLP, and STB bits) instruction can be executed during the sleep mode.

During the sleep mode, the other RAM data and instructions cannot be updated although they are

retained.

STB: When STB = 1, the HD66740 enters the standby mode, where display operation completely stops,

halting all the internal operations including the internal R-C oscillator. Further, no external clock pulses

are supplied. For details, see the Standby Mode section.

Only the following instructions can be executed during the standby mode.

a. Standby mode cancel (STB = 0)

b. Voltage follower circuit on/off (AMP = 1/0)

c. Start oscillation

During the standby mode, the other RAM data and instructions may be lost. To prevent this, they must be

set again after the standby mode is canceled.

R/W RS DB7

DB0

0

0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

0

1

AMP SLP STB

Figure 3 Power Control Instruction

HD66740

19

Contrast Control 1/2

SW: Switches the bit configuration for the contrast control instruction.

CT4≠CT0: When SW = 0, they control the LCD drive voltage (potential difference between V1 and

GND) to adjust contrast. A 64-step adjustment is also possible by using the CT5 bit which are set in the

entry mode register. For details, see the Contrast Adjuster section.

R/W RS DB7

DB0

0

0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

1

0

SW

CT4 CT3

BT1 BT0

(SW = 0)

(SW = 1)

0

0

0

0

0

1

1

CT1 CT0

BS1 BS0

(SW = 0)

(SW = 1)

CT2

BS2

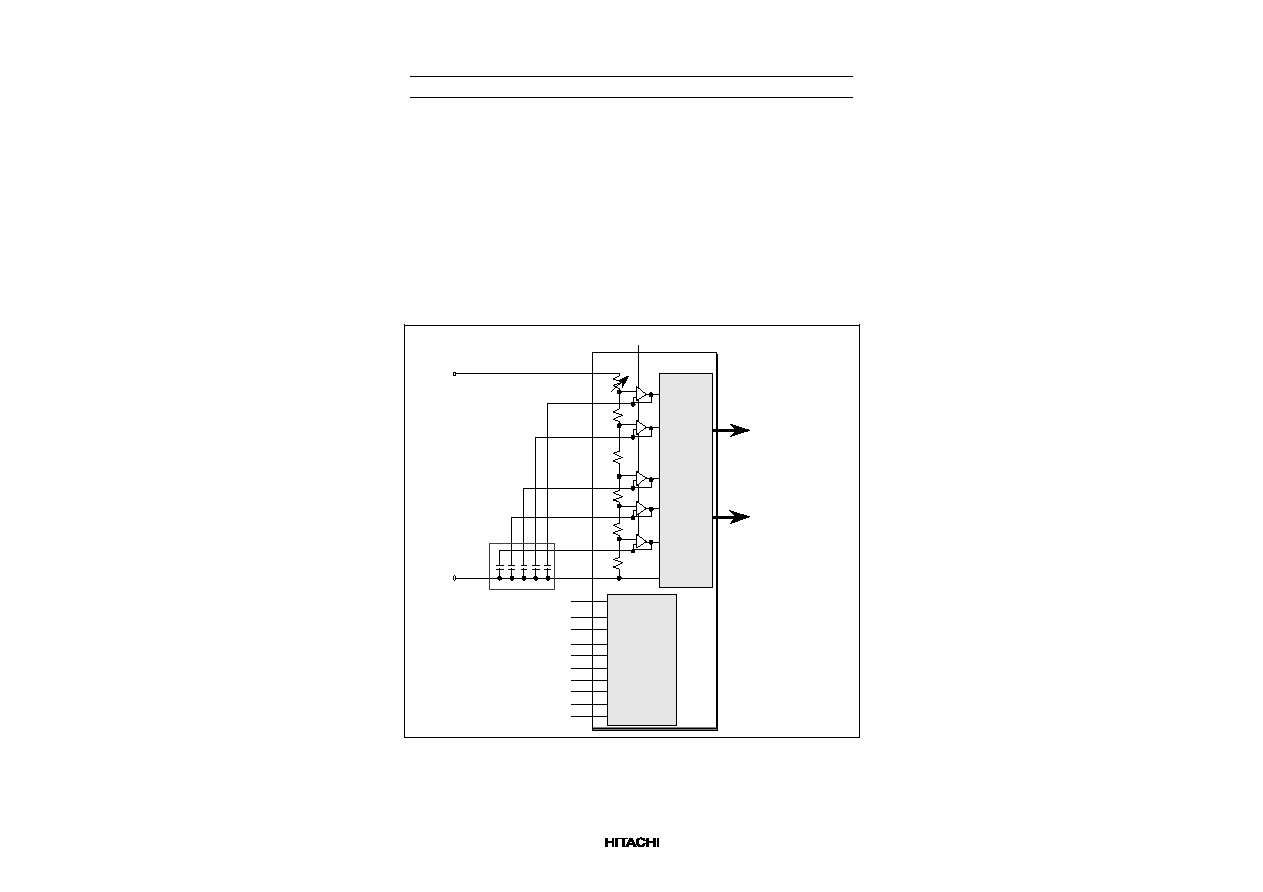

Figure 4 Contrast-Control 1/2 Instruction

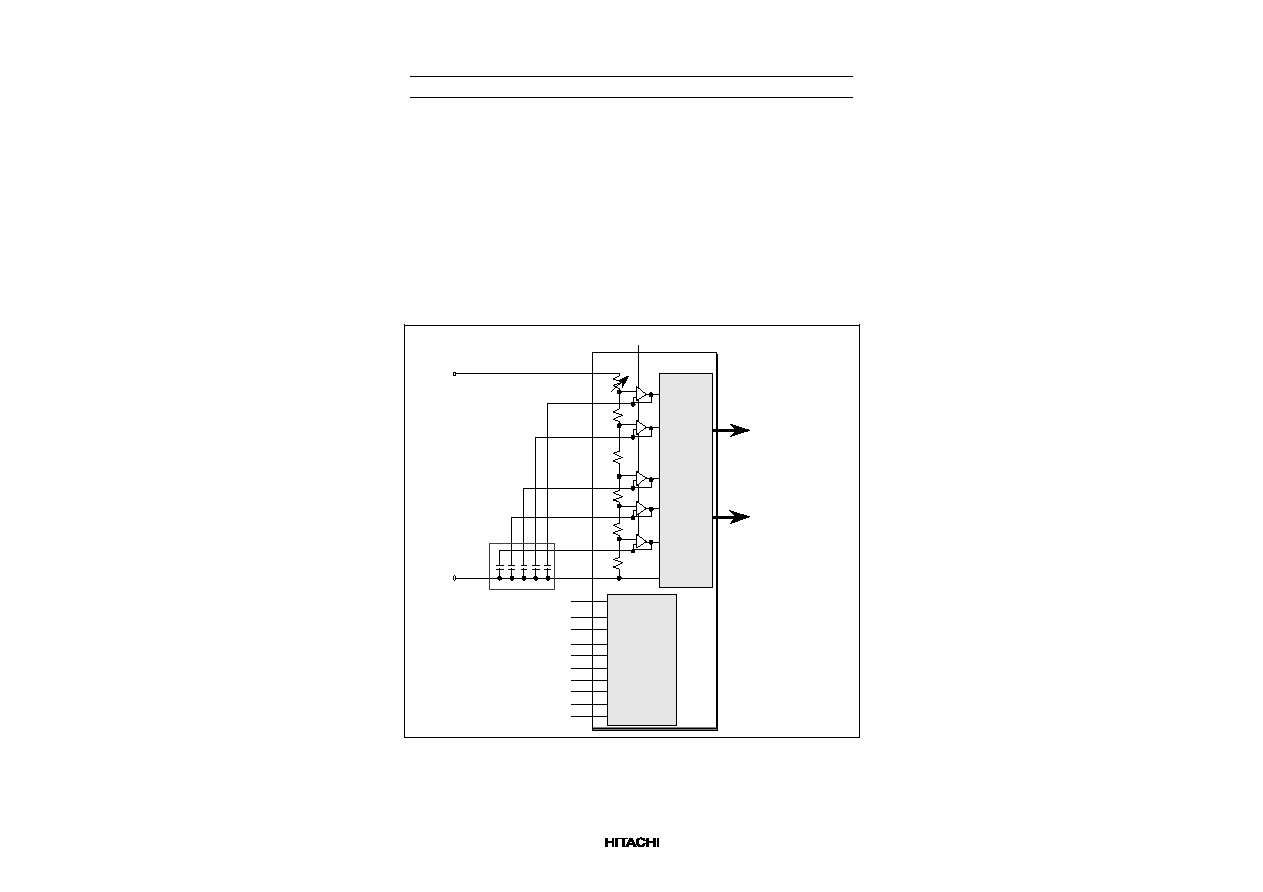

V

LCD

V1

V2

V3

V4

V5

VR

R

R

R

0

R

R

-

+

-

+

-

+

-

+

-

+

GND

HD66740

GND

Figure 5 Contrast Adjuster

HD66740

20

Table 6

CT Bits and Variable Resistor Value of Contrast Adjuster

CT Set Value

CT5

CT4

CT3

CT2

CT1

CT0

Variable Resistor (VR)

0

0

0

0

0

0

3.20 x R

0

0

0

0

0

1

3.15 x R

0

0

0

0

1

0

3.10 x R

0

0

0

0

1

1

3.05 x R

0

0

0

1

0

0

3.00 x R

∑

∑

∑

∑

0

1

1

1

1

1

1.65 x R

1

0

0

0

0

0

1.60 x R

1

0

0

0

0

1

1.55 x R

1

0

0

0

1

0

1.50 x R

∑

∑

∑

∑

1

1

1

1

0

1

0.15 x R

1

1

1

1

1

0

0.10 x R

1

1

1

1

1

1

0.05 x R

BT1-0: When SW = 1, they switch the output of V5OUT between triple, quadruple, and five-times boost.

The liquid crystal display drive voltage level can be selected according to its drive duty ratio and bias.

A lower amplification of the booster consumes less current.

BS2-0: When SW = 1, they set the crystal display drive bias value within the range of 1/4 to 1/10 bias.

The liquid crystal display drive bias value can be selected according to its drive duty ratio and voltage.

For details, see the Liquid Crystal Display Drive Bias Selector section.

Table 7

BT Bits and Output Level

BT1

BT0

V5OUT Output Level

0

0

Triple boost

0

1

Quadruple boost

1

0

Five-times boost

1

1

Setting inhibited

HD66740

21

Table 8

BS Bits and LCD Drive Bias Value

BS2

BS1

BS0

Liquid Crystal Display Drive Bias Value

0

0

0

1/10 bias drive

0

0

1

1/9.5 bias drive

0

1

0

1/9 bias drive

0

1

1

1/8 bias drive

1

0

0

1/7 bias drive

1

0

1

1/6 bias drive

1

1

0

1/5 bias drive

1

1

1

1/4 bias drive

HD66740

22

Entry Mode

REV: Displays all graphics display sections with black-and-white reversal when SW = 0 and REV = 1.

For details, see the Reversed Display Function section.

I/D: When SW = 0, increments (I/D = 1) or decrements (I/D = 0) the CGRAM address by 1 when a data

is written into or read from the CGRAM.

CT5: Sets the most significant bit (CT5) for contrast adjustment when SW = 1. A 64-step adjustment is

also possible by using the CT4≠CT0 bits which are set in the contrast-control 1/2 instruction.

RDM: When SW = 1 and RDM = 0, the RDM increments or decrements the address counter value

according to the I/D bit setting after reading the data from the CGRAM. When RDM = 1, the address

counter value is not updated after the data has been read from the CGRAM. The address counter value

is used when the RAM data is read, modified, and written. Since the first read data is invalid, the read

must be continuously done twice. After writing to the RAM, the address counter value must be

updated.

R/W RS DB7

DB0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

0

1

0

0

I/D

RDM

(SW = 0)

(SW = 1)

REV

CT5

0

1

Figure 6 Entry Mode Set Instruction

HD66740

23

Display On/Off Control

D: Display is on when SW = 0 and D = 1 and off when D = 0. When off, the display data remains in the

DDRAM or CGRAM, and can be displayed instantly by setting D = 1. When D is 0, the display is off

with the SEG1 to SEG112 outputs and COM1 to COM80 outputs set to the GND level. Because of this,

the HD66740 can control charging current for the LCD with AC driving.

DL10: When SW = 0, DL10 can be set. When DL10 = 1, the 10th line is displayed at double height.

DL9≠DL7: When SW = 1, DL9≠DL7 can be set. Double-height display is specified for any display

line. When DL7 = 1, the seventh line is displayed at double height. Double-height display is used for

the eighth line when DL8 = 1 and for the ninth line when DL9 = 1. For double-height display for the

first to the sixth lines, control them by using DL1≠DL6 bits in the display-line control instruction.

R/W RS DB7

DB0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

0

1

1

0

DL10

DL8 DL7

(SW = 0)

(SW = 1)

D

DL9

0

Figure 7 Display On/Off Control Instruction

HD66740

24

Display Line Control

NL3-0: Set NL2≠NL0 bits when SW = 0, and the NL3 bit when SW = 1 to specify the display lines.

Display lines change the liquid crystal display drive duty ratio. CGRAM address mapping does not

depend on the number of display lines.

R/W RS DB7

DB0

0

0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

1

1

1

NL1 NL0

NL2

CN0 NL3

CN1

(SW = 0)

(SW = 1)

Figure 8 Display-line Control Instruction

Table 9

NL Bits and Display Lines

NL3

NL2

NL1

NL0

Graphics

Display

LCD Drive

Duty

Common

Driver Used

0

0

0

0

112 x 8 dots

1/8 Duty

COM1≠COM8

0

0

0

1

112 x 16 dots

1/16 Duty

COM1≠COM16

0

0

1

0

112 x 24 dots

1/24 Duty

COM1≠COM24

0

0

1

1

112 x 32 dots

1/32 Duty

COM1≠COM32

0

1

0

0

112 x 40 dots

1/40 Duty

COM1≠COM40

0

1

0

1

112 x 48 dots

1/48 Duty

COM1≠COM48

0

1

1

0

112 x 56 dots

1/56 Duty

COM1≠COM56

0

1

1

1

112 x 64 dots

1/64 Duty

COM1≠COM64

1

0

0

0

112 x 72 dots

1/72 Duty

COM1≠COM72

1

0

0

1

112 x 80 dots

1/80 Duty

COM1≠COM80

CN1≠CN0: Set CN1≠CN0 bits when SW = 1. When CN1≠0 = 01, the display position is shifted by 16

dots below and display starts from COM17. When the liquid crystal is driven at low duty in the system

wait state, it can display partially at the center of the screen. For details, see the Partial-display-on

Function section.

When CN1≠CN0 = 10, the display position is shifted by 8 dots above and second-line display starts from

COM1. The 8 dots of the first line are moved to the lowest edge of the display screen. The output

position of the lowest edge depends on the drive duty setting. In vertical smooth scrolling, PS1≠PS0

bits can selectively fixed-display only the first to the third lines. Combining these functions enables the

fixed display of one line of the lowest edge. For details, see the Partial Smooth Scroll Display Function

section.

HD66740

25

Table 10

Common Driver Pin Function

Common Driver Pin Function

CN 1≠0 = 00

(Normal Output)

CN 1≠0 = 01

(Center Output)

CN1≠0 = 10

(Lowest-edge Output)

Common

Driver Pin

CMS = 0

CMS = 1

CMS = 0

CMS = 1

CMS = 0

CMS = 1

COM1/80

COM1

COM80

COM65

COM64

COM9

COM8

COM2/79

COM2

COM79

COM66

COM63

COM10

COM7

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM7/72

COM7

COM74

COM71

COM58

COM15

COM2

COM8/73

COM8

COM73

COM72

COM57

COM16

COM1

COM9/72

COM9

COM72

COM73

COM56

COM17

COM80

COM10/71

COM10

COM71

COM74

COM55

COM18

COM79

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM15/66

COM15

COM66

COM79

COM50

COM23

COM73

COM16/65

COM16

COM65

COM80

COM49

COM24

COM72

COM17/64

COM17

COM64

COM1

COM48

COM25

COM71

COM18/63

COM18

COM63

COM2

COM47

COM26

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM66

COM24/57

COM24

COM57

COM8

COM41

COM32

COM65

COM25/56

COM25

COM56

COM9

COM40

COM33

COM64

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM32/49

COM32

COM49

COM16

COM33

COM40

COM57

COM33/48

COM33

COM48

COM17

COM32

COM41

COM56

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM40/41

COM40

COM41

COM24

COM25

COM48

COM49

COM41/40

COM41

COM40

COM25

COM24

COM49

COM48

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM48/33

COM48

COM33

COM32

COM17

COM56

COM41

COM49/32

COM49

COM32

COM33

COM16

COM57

COM40

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM56/25

COM56

COM25

COM40

COM9

COM64

COM33

COM57/24

COM57

COM24

COM41

COM8

COM65

COM32

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM64/17

COM64

COM17

COM48

COM1

COM72

COM25

COM65/16

COM65

COM16

COM49

COM80

COM73

COM24

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM72/9

COM72

COM9

COM56

COM73

COM80

COM17

COM73/8

COM73

COM8

COM57

COM72

COM1

COM16

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

COM2

COM15

COM79/2

COM79

COM2

COM63

COM66

∑

∑

∑

∑

COM80/1

COM80

COM1

COM64

COM65

COM8

COM9

Double-height Display Control

DL3-1: Can be specified when SW = 0. Specify the double-height display for any line. When DL1 =

1, the first line is displayed at double height. When DL2 = 1, the second line is displayed at double

HD66740

26

height. When DL3 = 1, the third line is displayed at double height. Double-height display of multiple

lines is possible. For details, see the Double-height Display section.

DL6-4: Can be specified when SW = 1. Specify the double-height display for any line. When DL4 =

1, the fourth line is displayed at double height. When DL5 = 1, the fifth line is displayed at double

height. When DL6 = 1, the sixth line is displayed at double height. For the seventh to 10th lines,

control double-height display by using the DL7≠DL10 bits in the display-line control instruction. For

details, see the Double-height Display section.

R/W RS DB7

DB0

DB6 DB5 DB4 DB3 DB2 DB1

0

0

0

1

0

0

0

DL2 DL1

DL3

DL5 DL4

DL6

(SW = 0)

(SW = 1)

Figure 9 Double-height Display Control Instruction

HD66740

27

Vertical Scroll Control 1/2

SN3-0: Set SN2 to SN0 bits when SW = 0. Set the SN3 bit when SW = 1. Specify the display start

line output from COM1. Because the CGRAM is assigned a 10-line display area, the data is displayed

sequentially from the first line to the 10th line then repeated from the first line again. In partial smooth

scrolling, these bits specify the display start line for the next line of the fixed-display line. For details,

see the Partial Smooth Scroll Display Function section.

SL2≠0: Select the top raster-row to be displayed (display-start raster-row) in the display-start line

specified by SN2 to SN0. Any raster-row from the first to eighth can be selected (table 12). This function

is used to achieve vertical smooth scrolling together with SN2 to SN0. For details, see the Vertical

Smooth Scroll section.