Preliminary

1

HD66750/1

(128 x 128-dot Graphics LCD Controller/Driver with

Four-grayscale Functions)

Rev 0.7

July 26th, 1999

Description

The HD66750/1, dot-matrix graphics LCD controller and driver LSI, displays 128-by-128-dot graphics

for four monochrome grayscales. Since the HD66750/1 incorporates bit-operation functions and a 16-bit

high-speed bus interface, it enables efficient data transfer and high-speed rewriting of data in the graphics

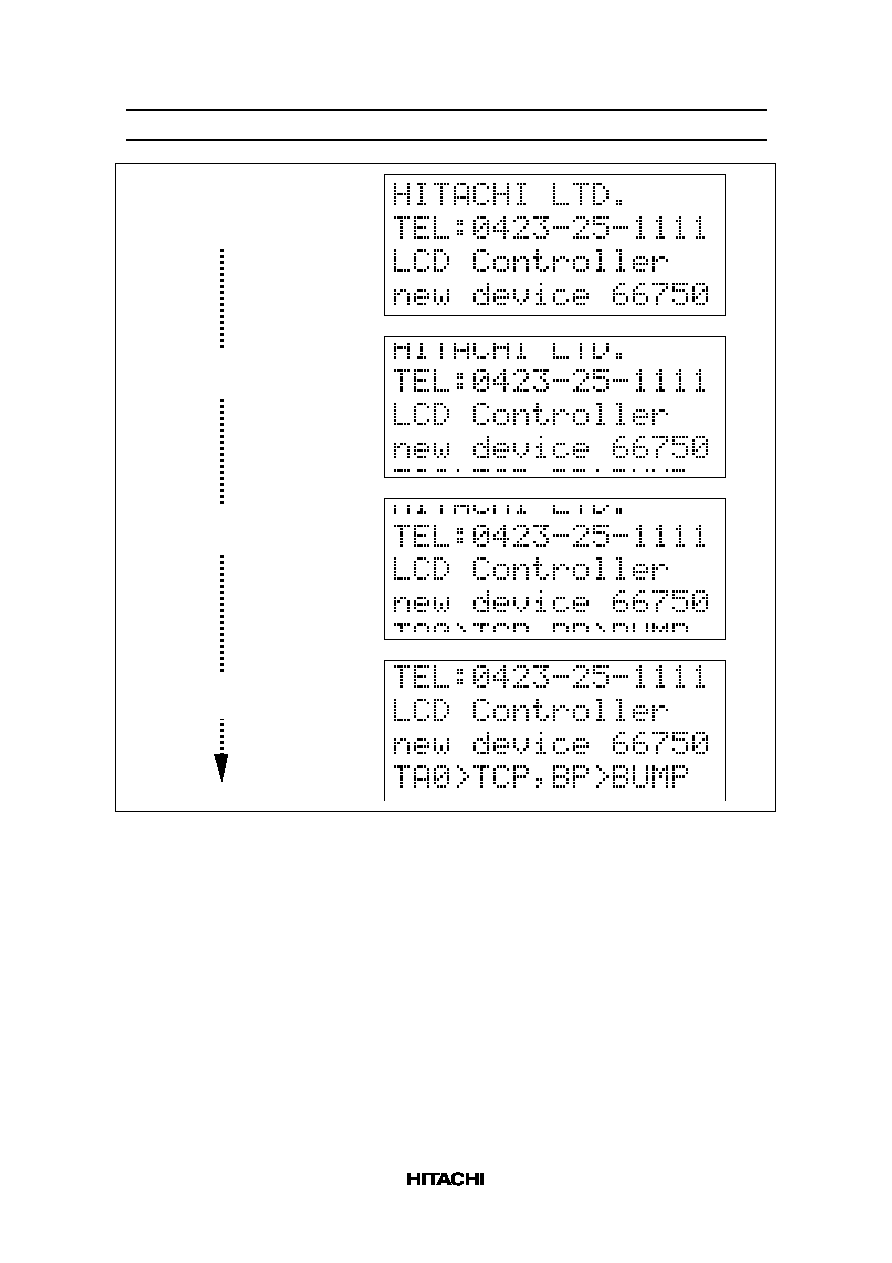

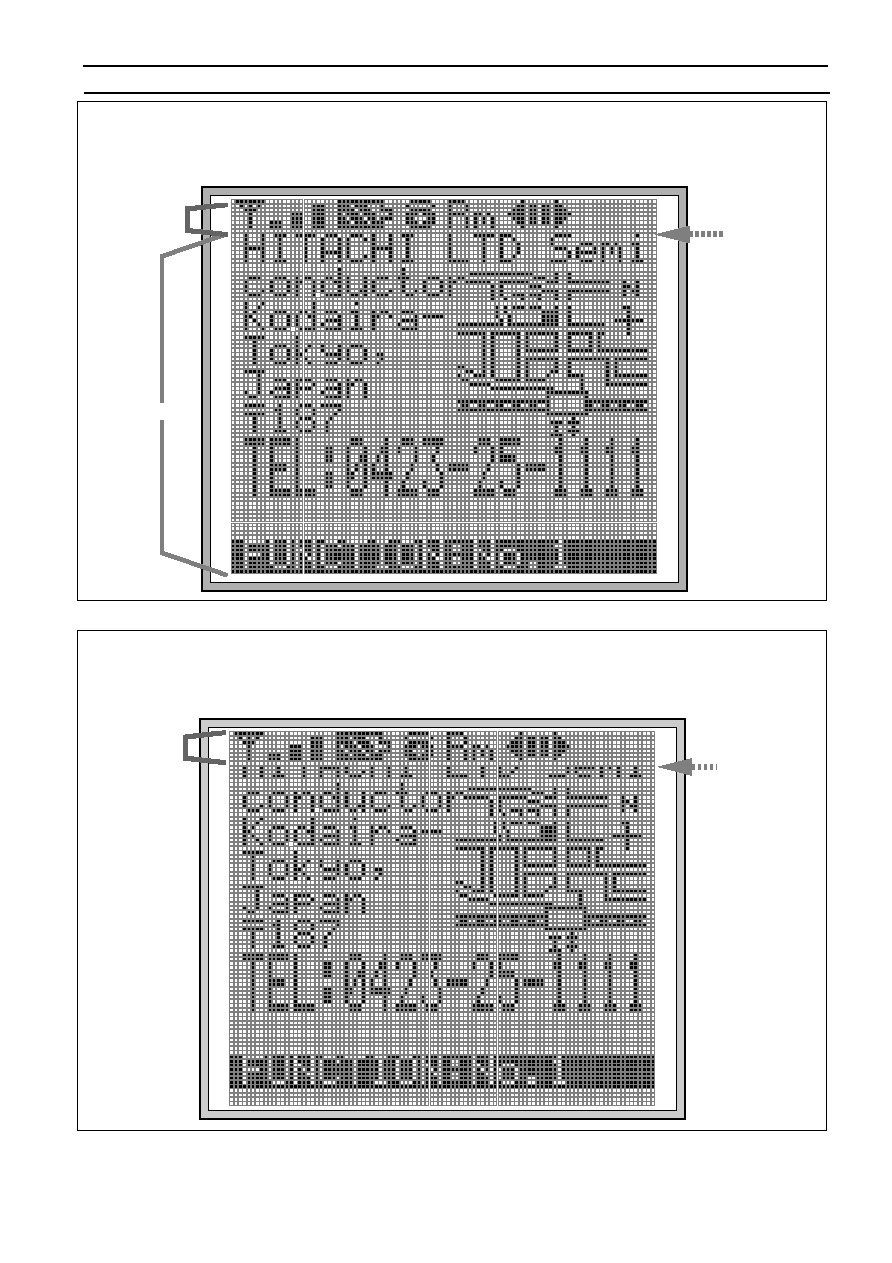

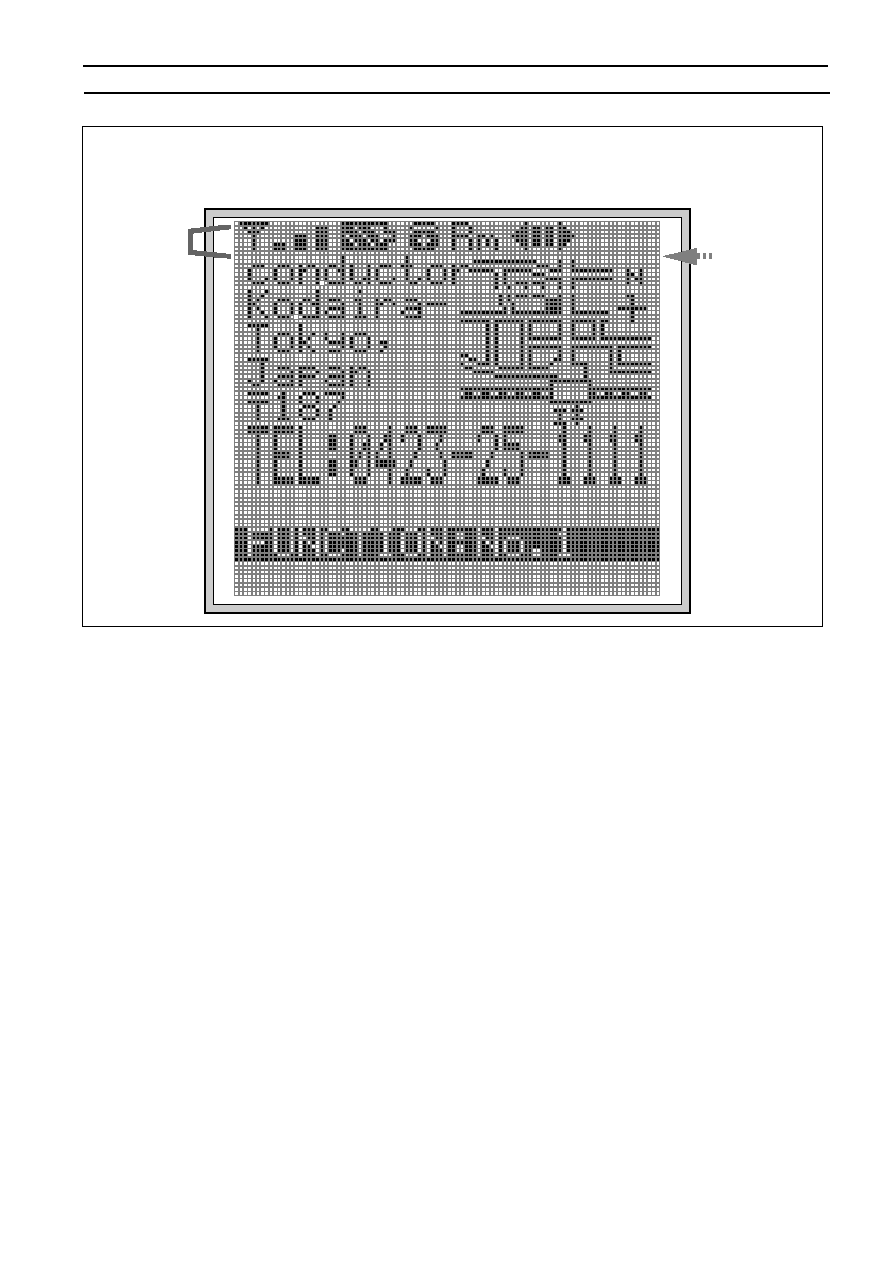

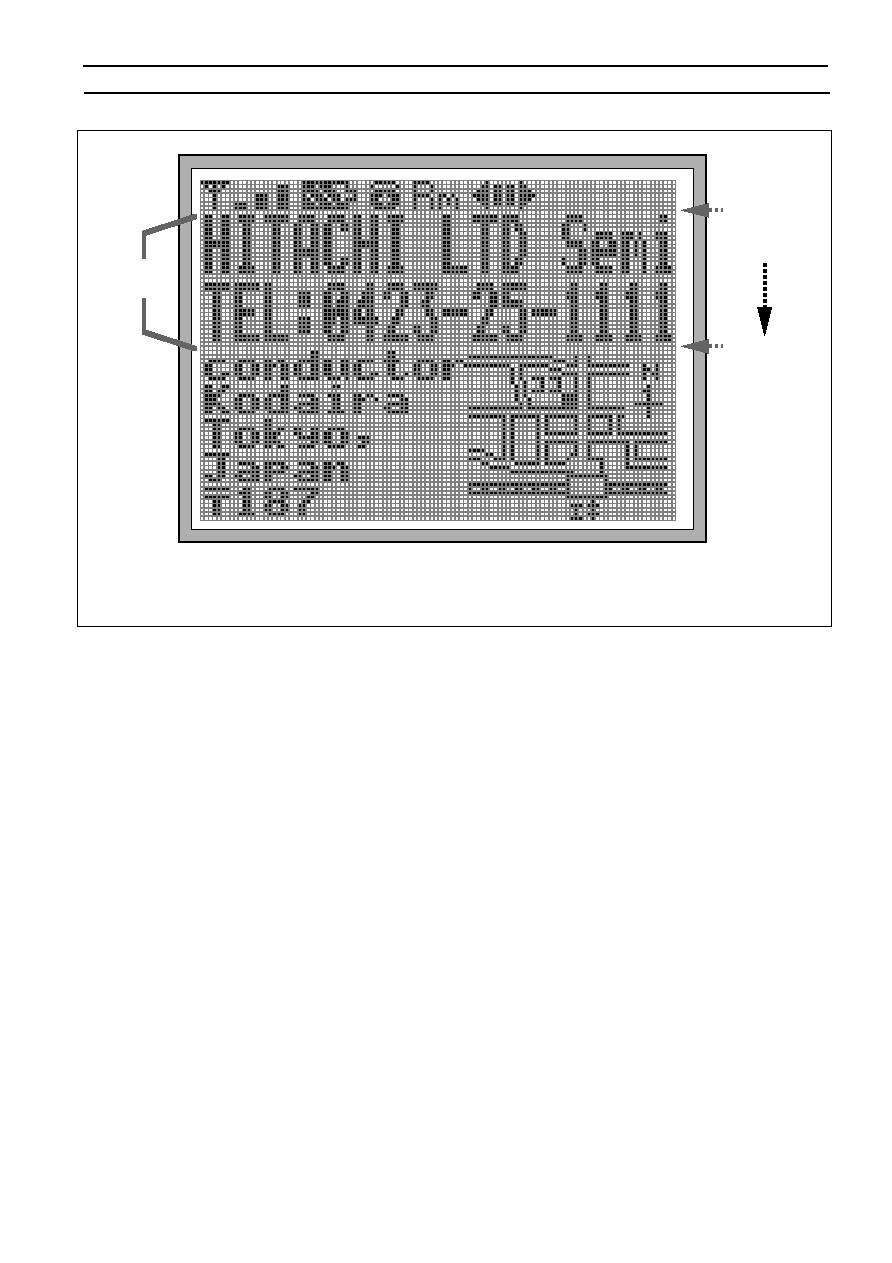

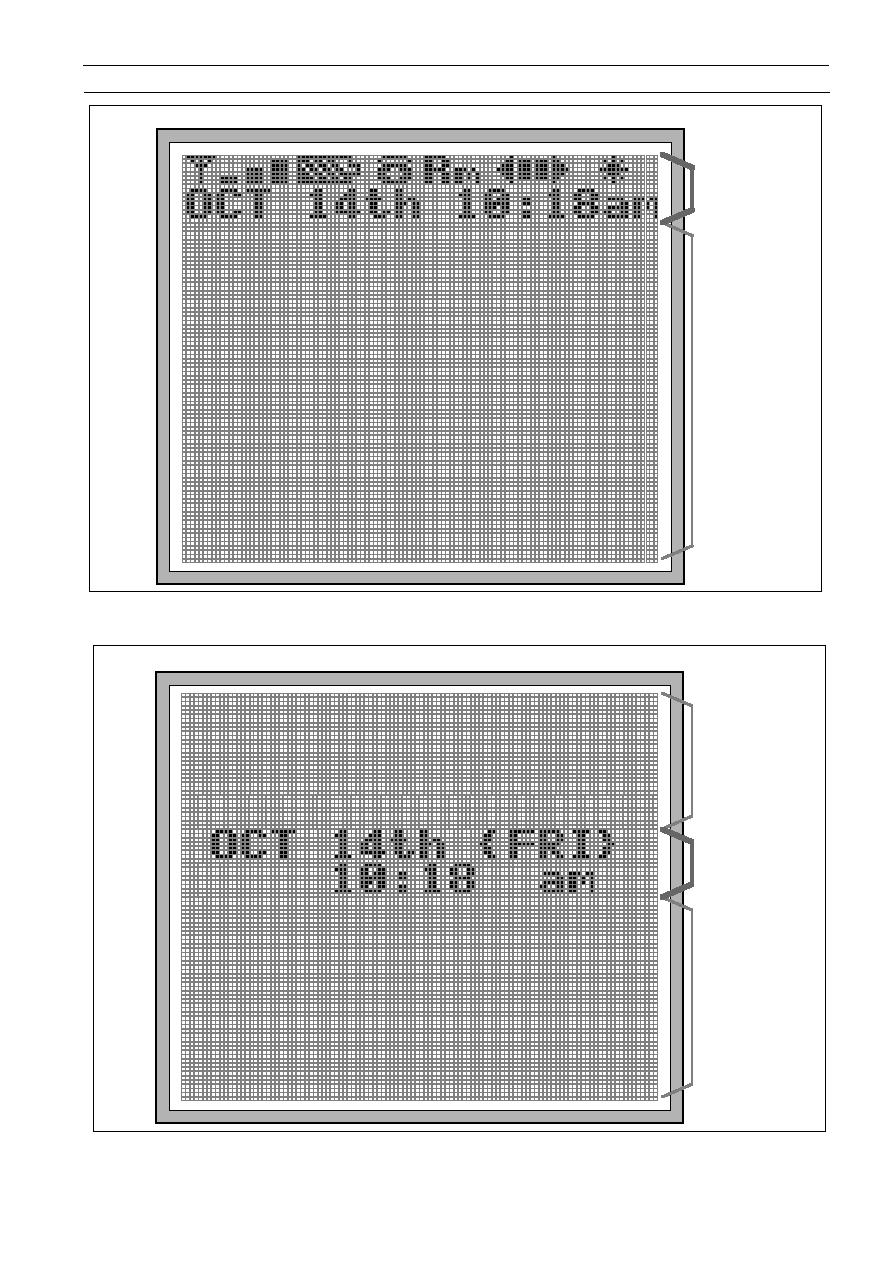

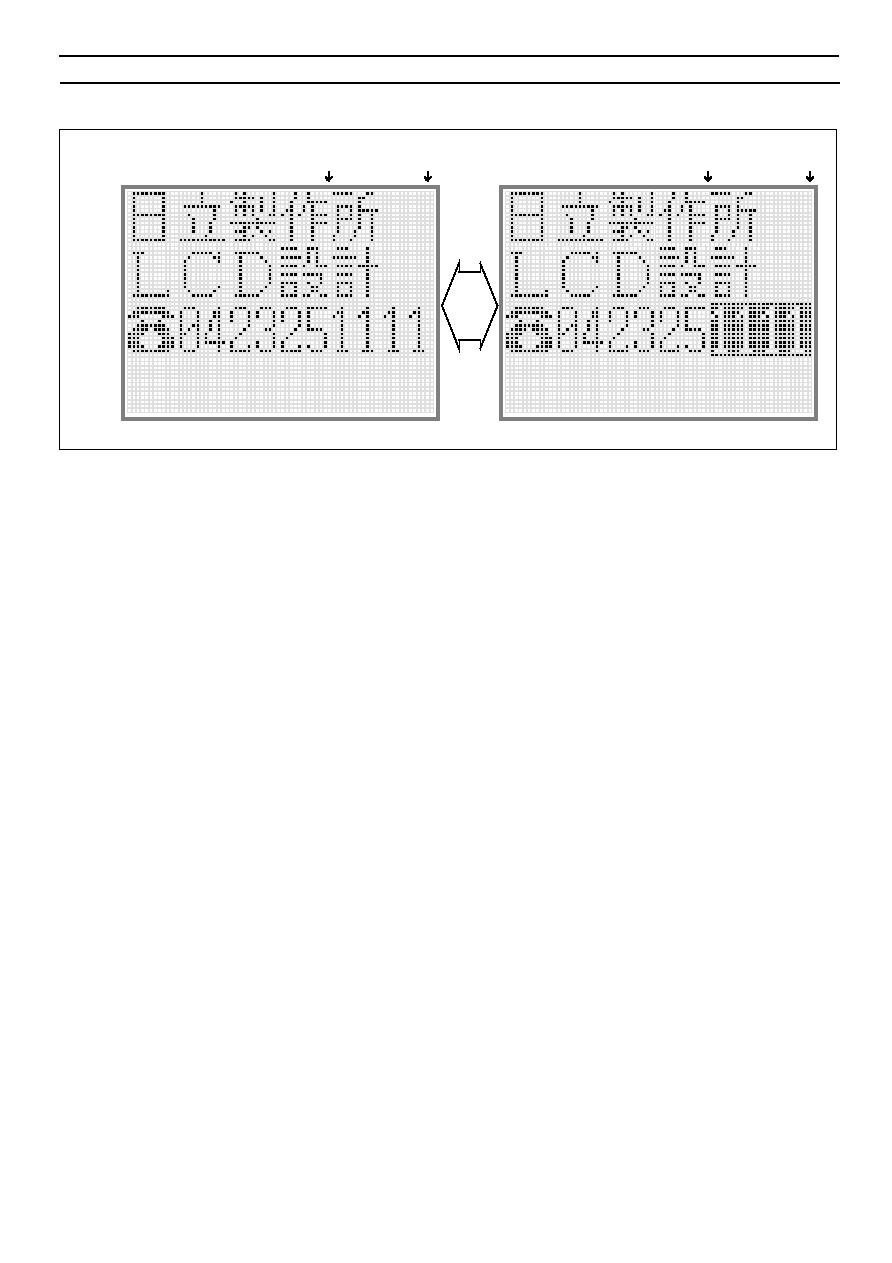

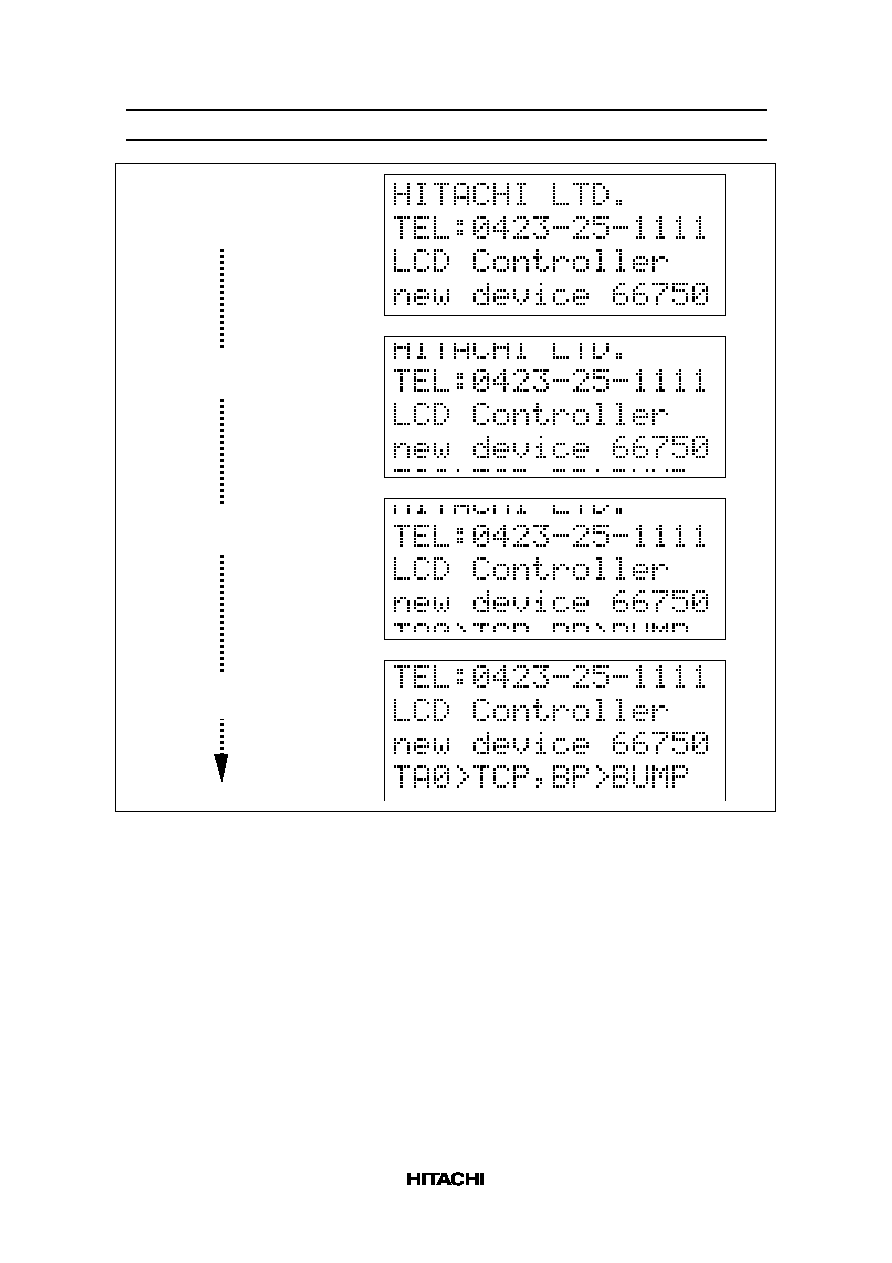

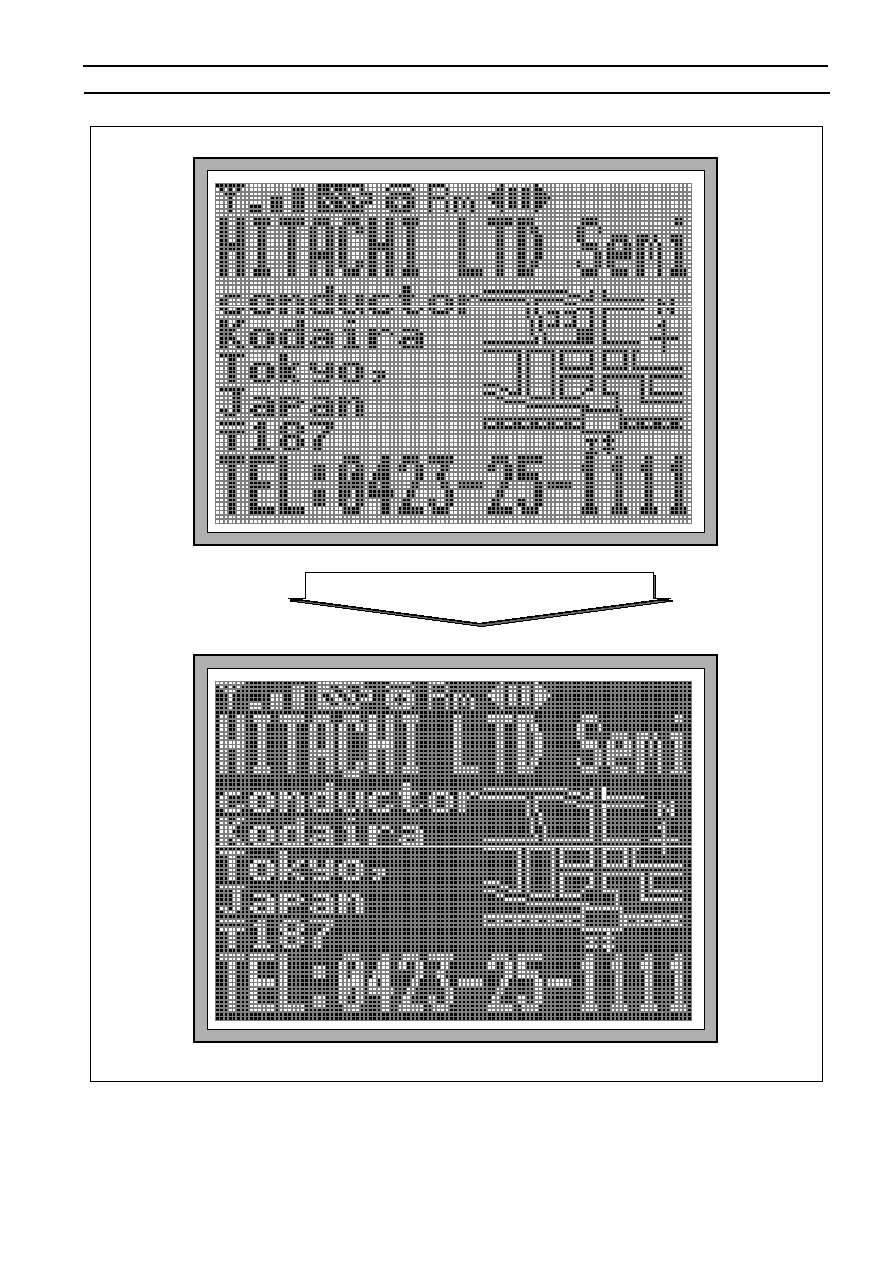

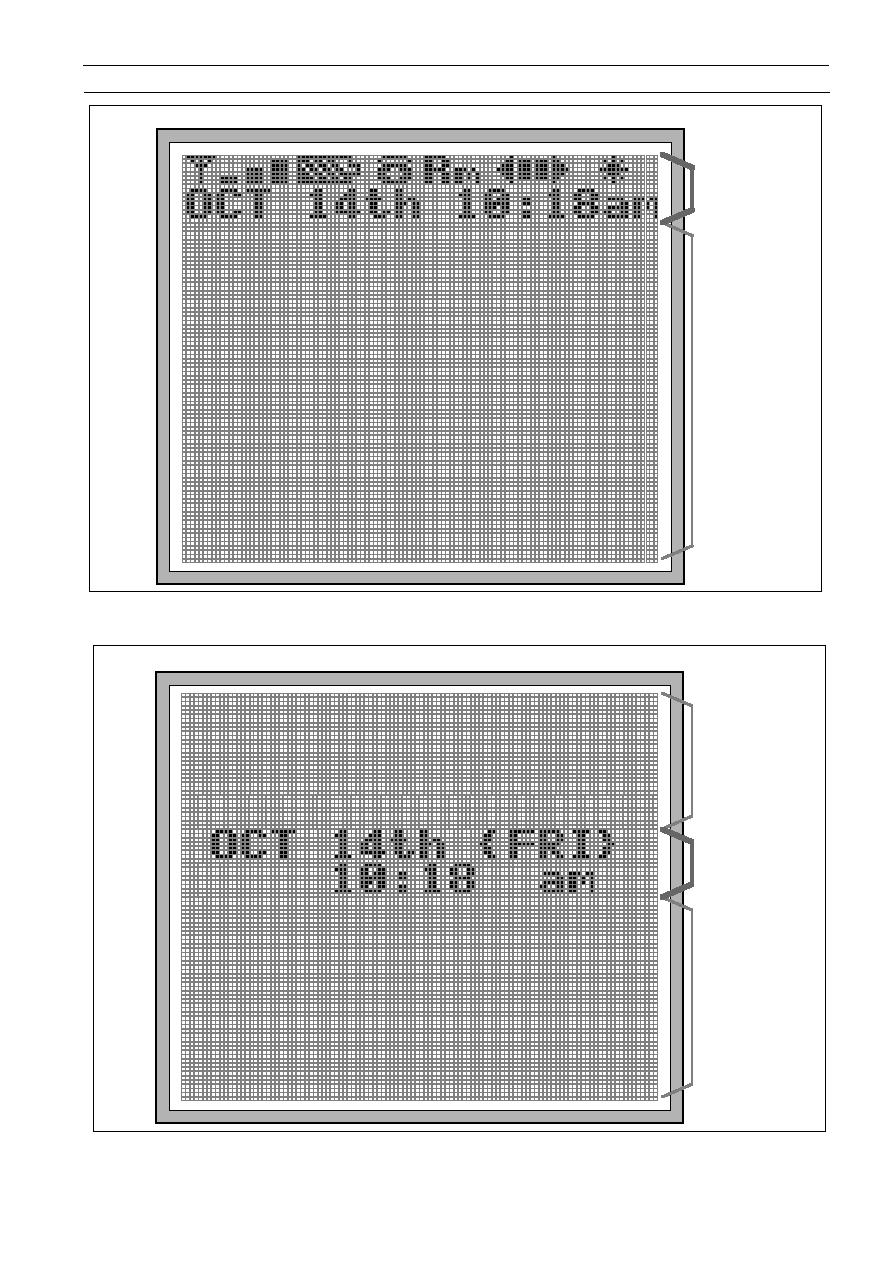

RAM. The following functions allow the user to easily see a variety of information: a smooth scroll

display function that fixed-displays a part of the graphics icons and perform vertical smooth scrolling of the

remaining bit-map areas, a double-height display function, and a hardware-supported window cursor

display function.

The HD66750/1 has various functions to reduce the power consumption of an LCD system such as low-

voltage operation of 1.8 V min., a booster to generate maximum seven-times LCD drive voltage from the

supplied voltage, and voltage-followers to decrease the direct current flow in the LCD drive bleeder-

resistors. Combining these hardware functions with software functions, such as a partial display with

low-duty drive and standby and sleep modes, allows precise power control. The HD66750/1 is suitable

for any mid-sized or small portable battery-driven product requiring long-term driving capabilities, such as

digital cellular phones supporting a WWW browser, bidirectional pagers, and small PDAs.

Features

•

128

¥ 128-dot graphics display LCD controller/driver for four monochrome grayscales

•

Fixed display of graphics icons (pictograms)

•

16-/8-bit high-speed bus interface capability

•

Bit-operation functions for graphics processing incorporated:

— Write-data mask function in bit units

— Bit rotation function

— Bit logic-operation function

•

Low-power operation support:

— Vcc = 1.8 to 3.6 V (low voltage)

— V

LCD

= 5 to 15.5 V (liquid crystal drive voltage)

— Two-, five-, six-, or seven-times booster for liquid crystal drive voltage

— 64-step contrast adjuster and voltage followers to decrease direct current flow in the LCD drive

bleeder-resistors

HD66750/1

2

— Power-save functions such as the standby mode and sleep mode supported

— Programmable drive duty ratios and bias values displayed on LCD

•

128-segment

¥ 128-common liquid crystal display driver

•

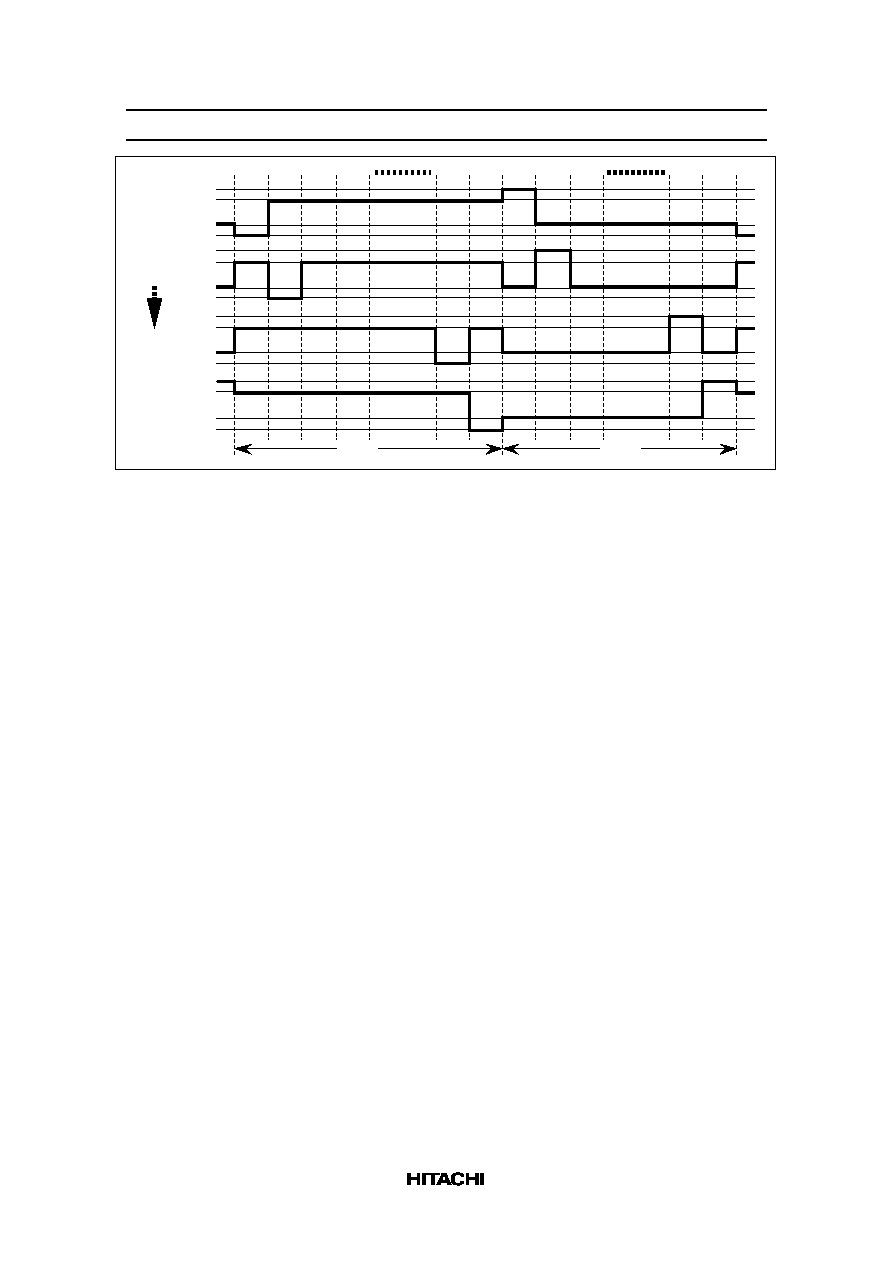

n-raster-row AC liquid-crystal drive (C-pattern waveform drive)

•

Duty ratio and drive bias (selectable by program)

•

Window cursor display supported by hardware

•

Vertical smooth scroll

•

Partial smooth scroll control (fixed display of graphics icons)

•

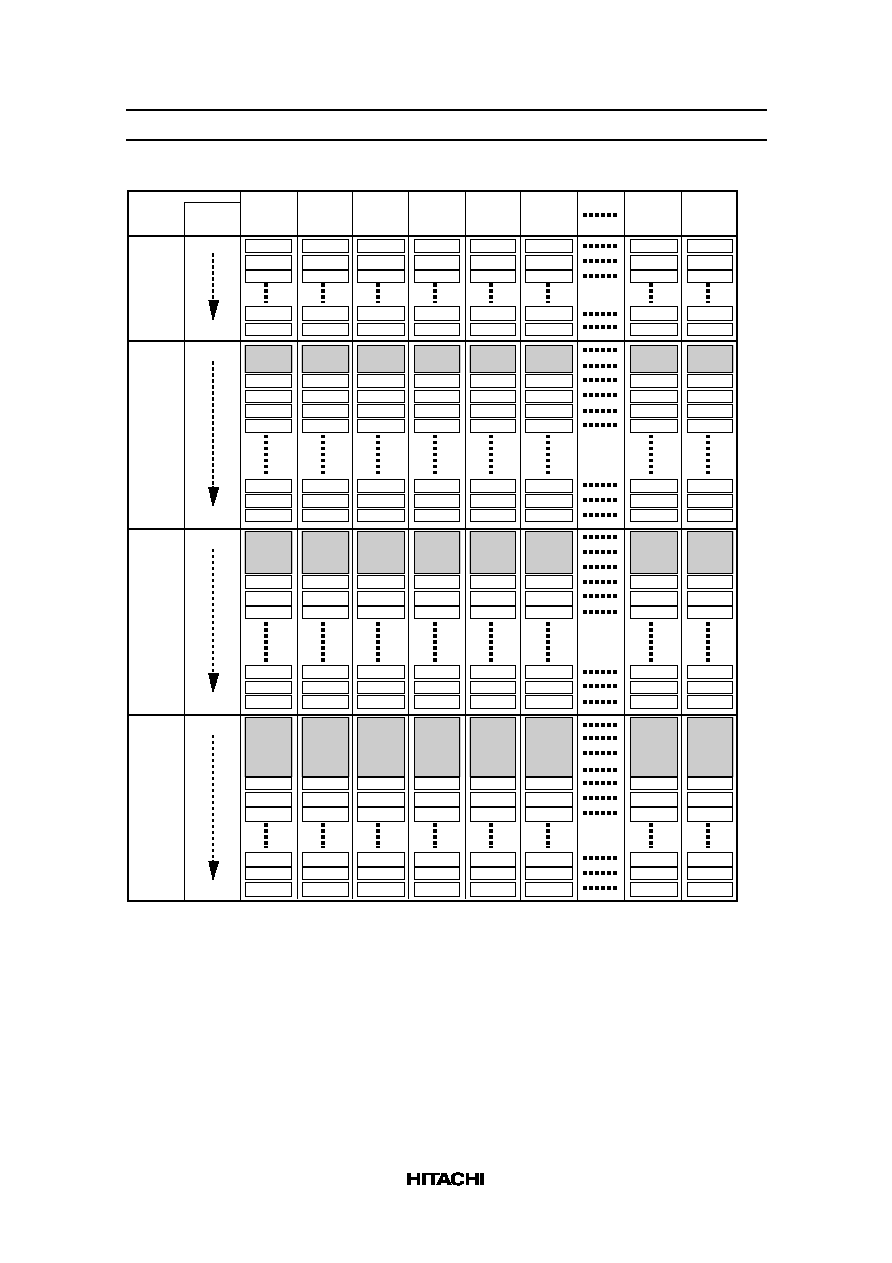

Vertical double-height display by each display raster-row

•

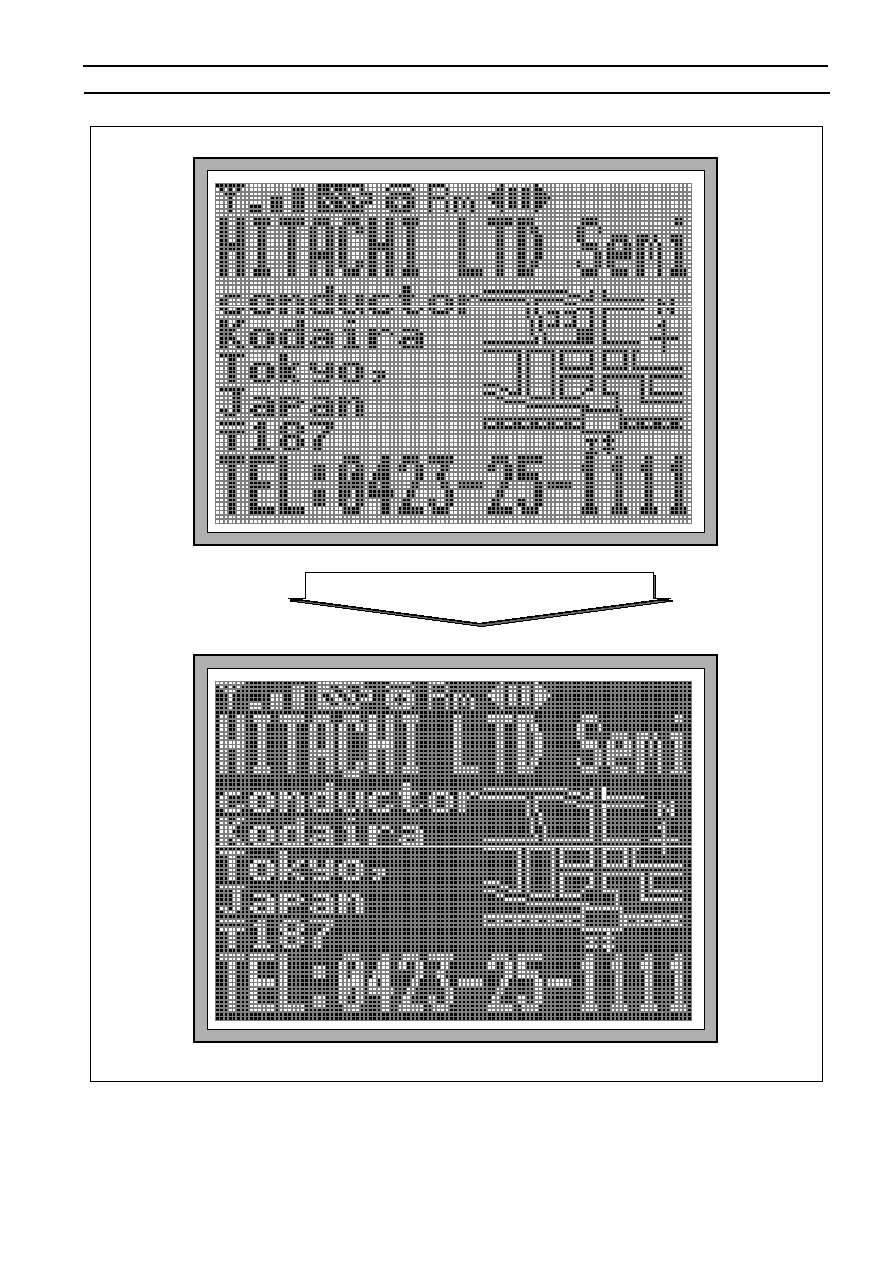

Black-and-white reversed display

•

No wait time for instruction execution and RAM access

•

Internal oscillation and hardware reset

•

Shift change of segment and common driver

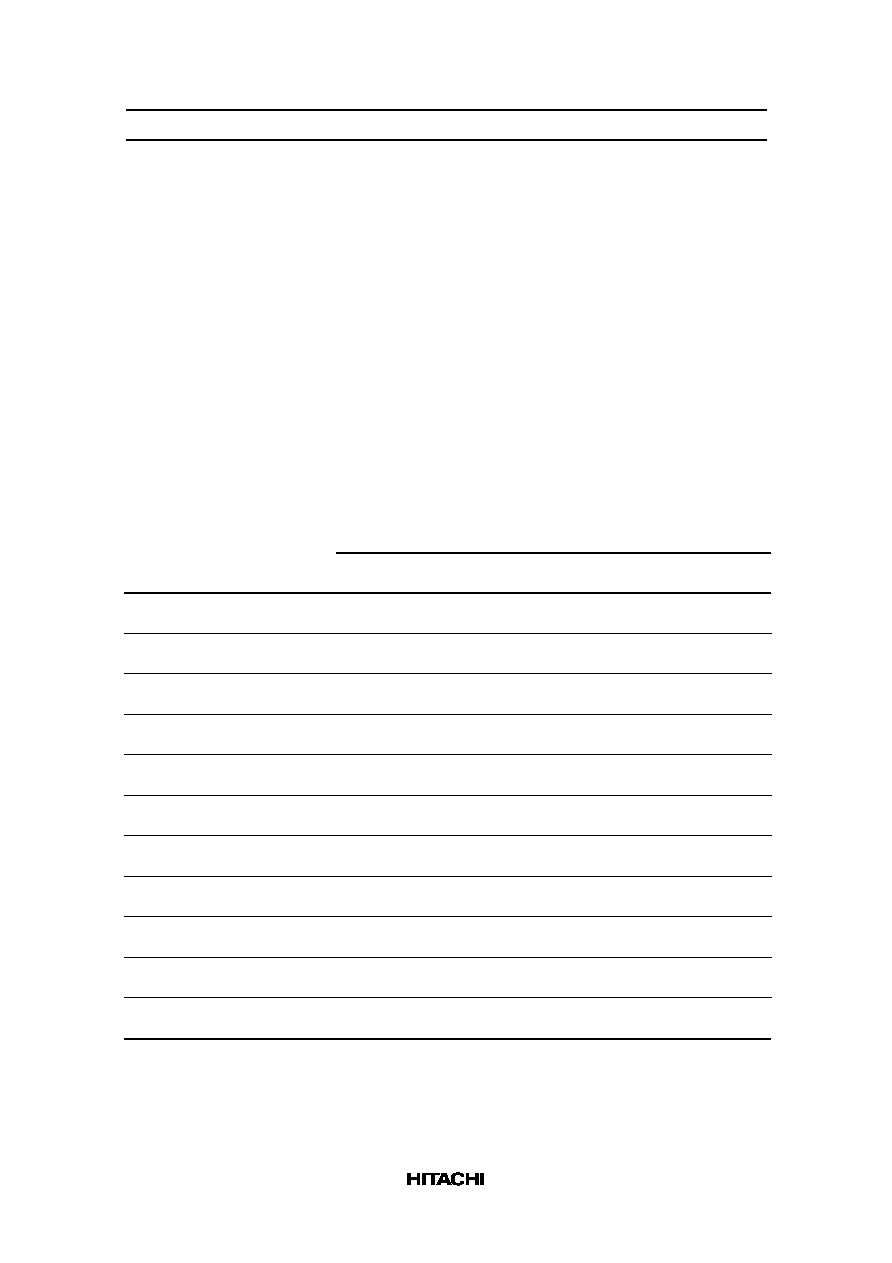

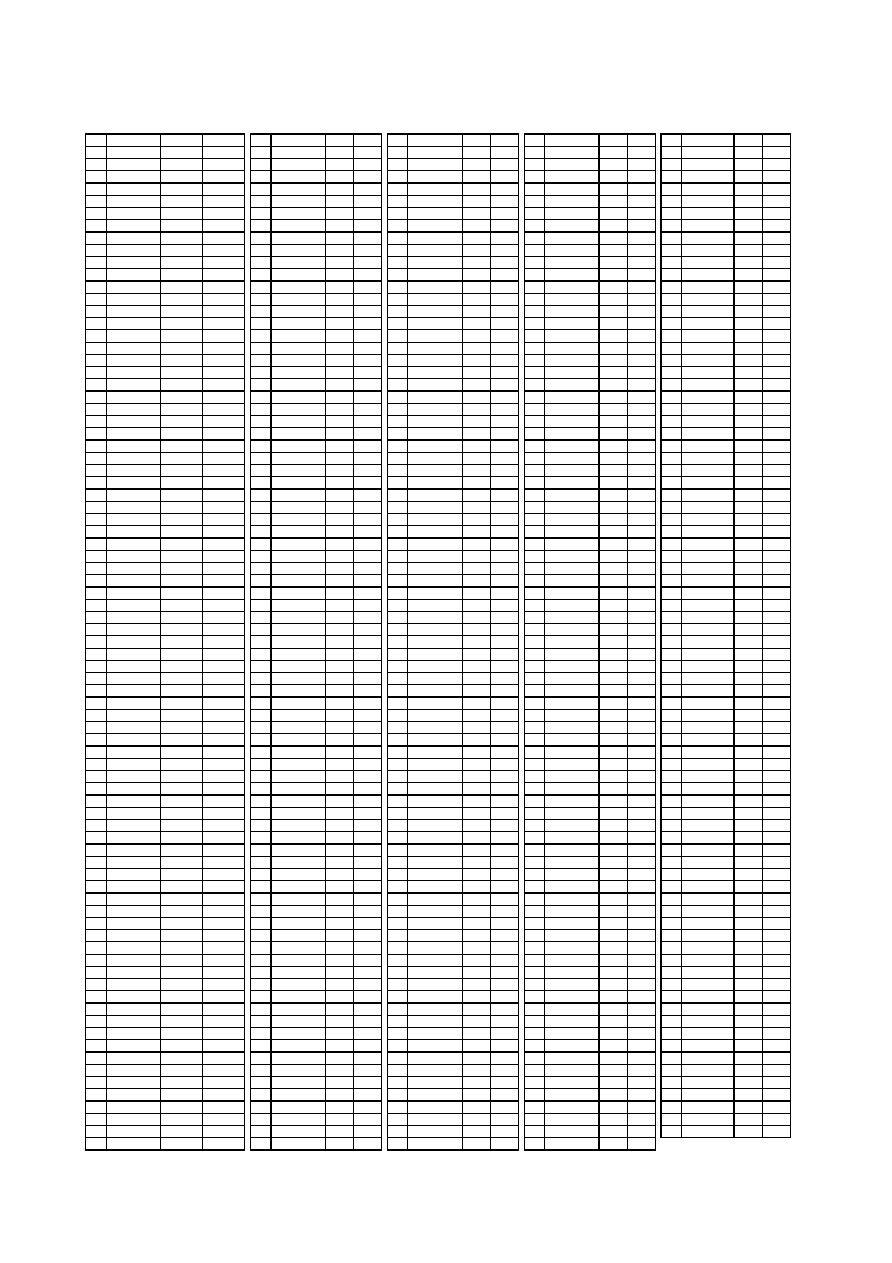

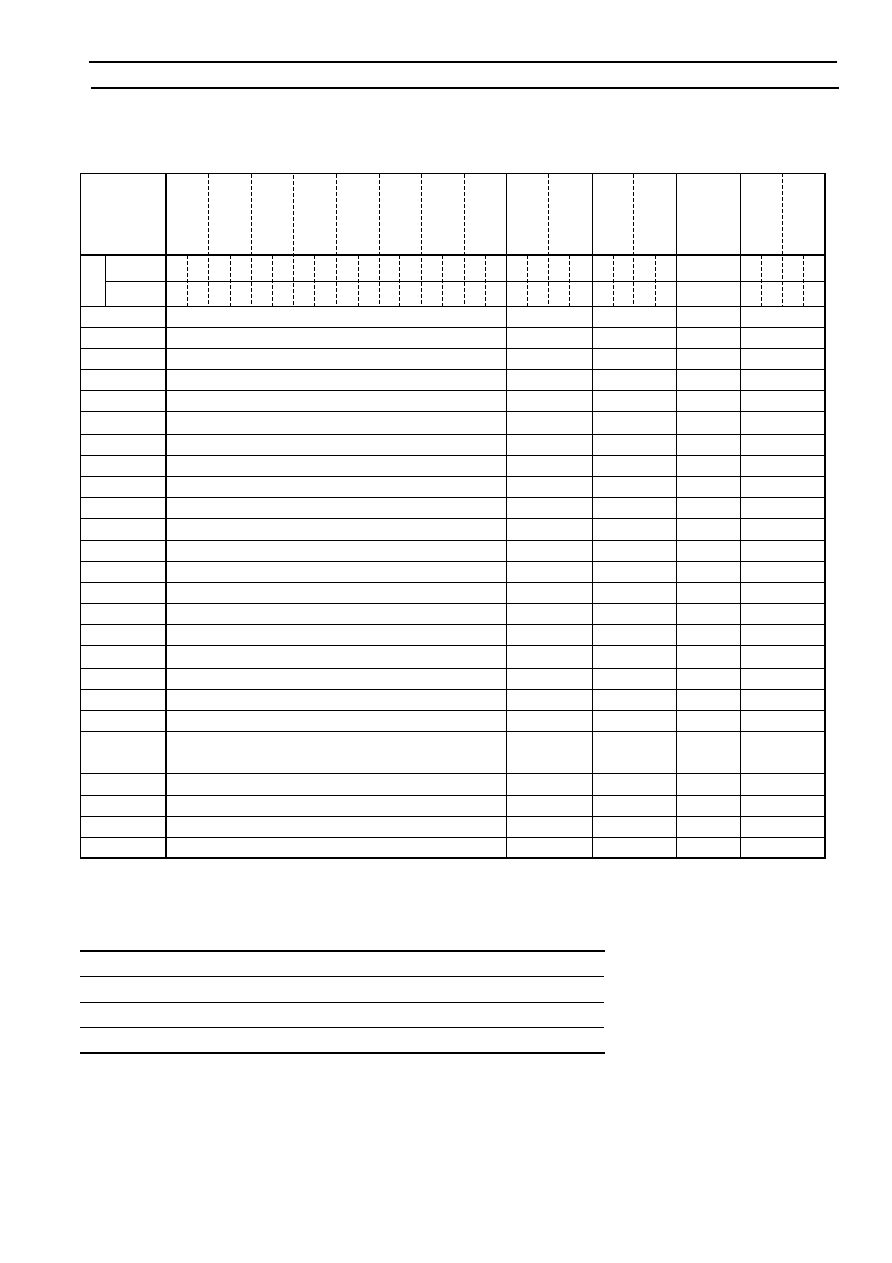

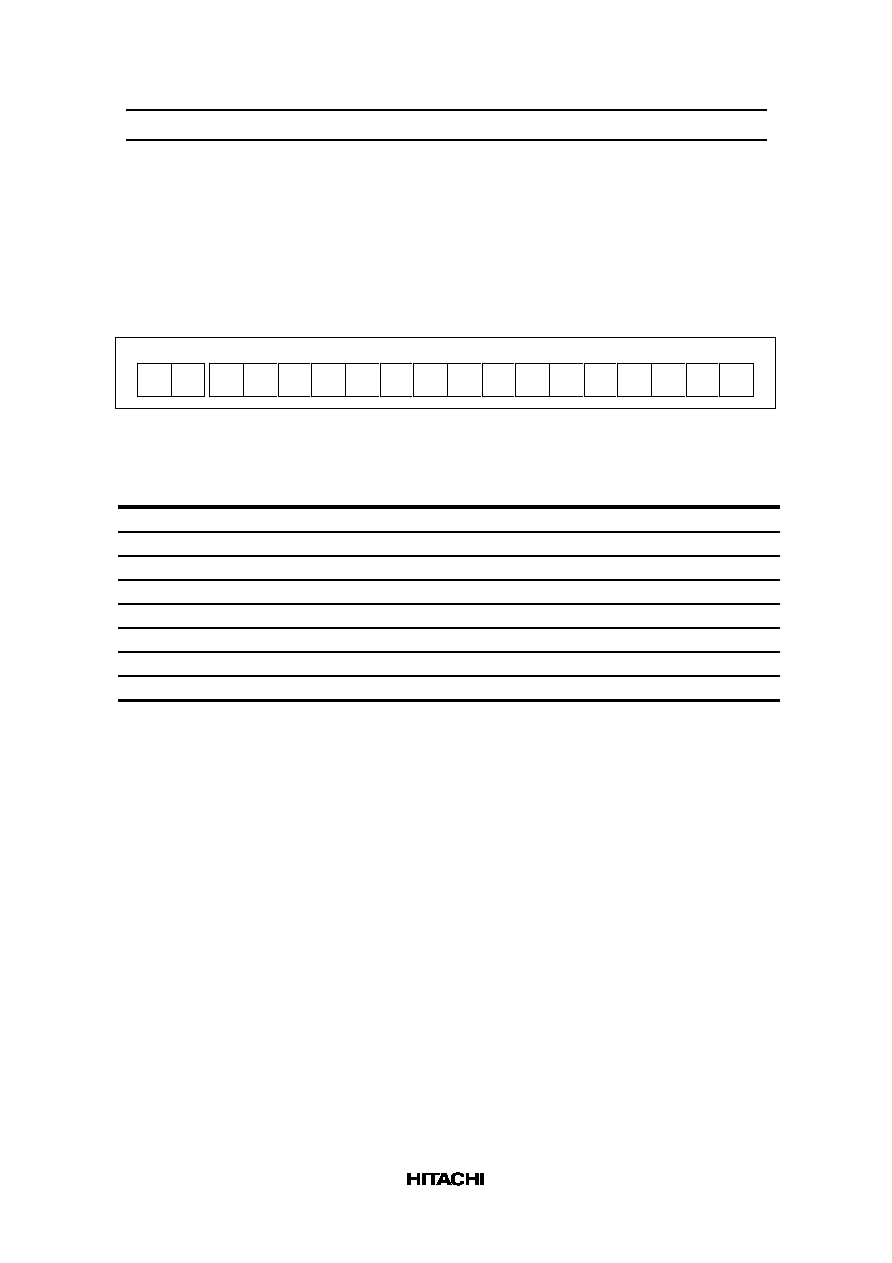

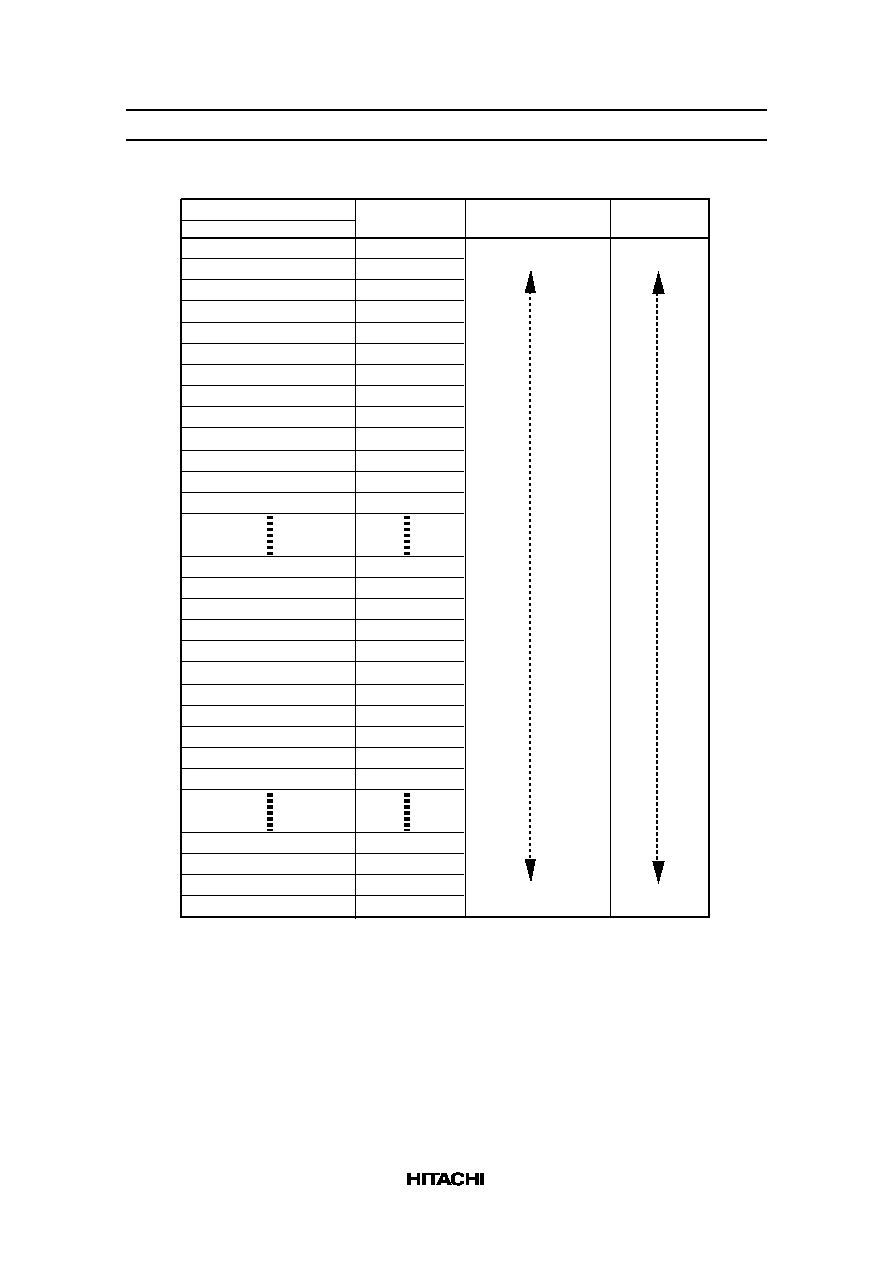

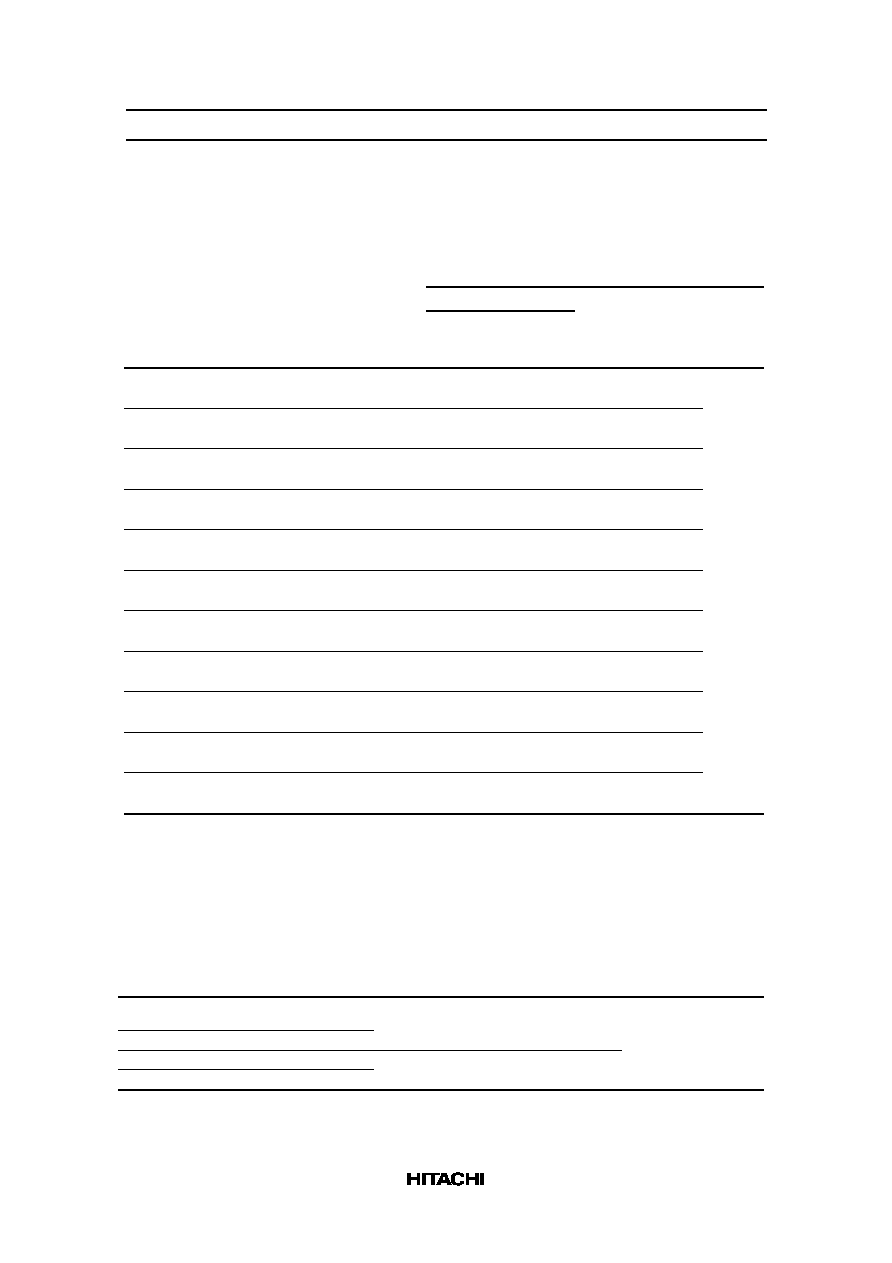

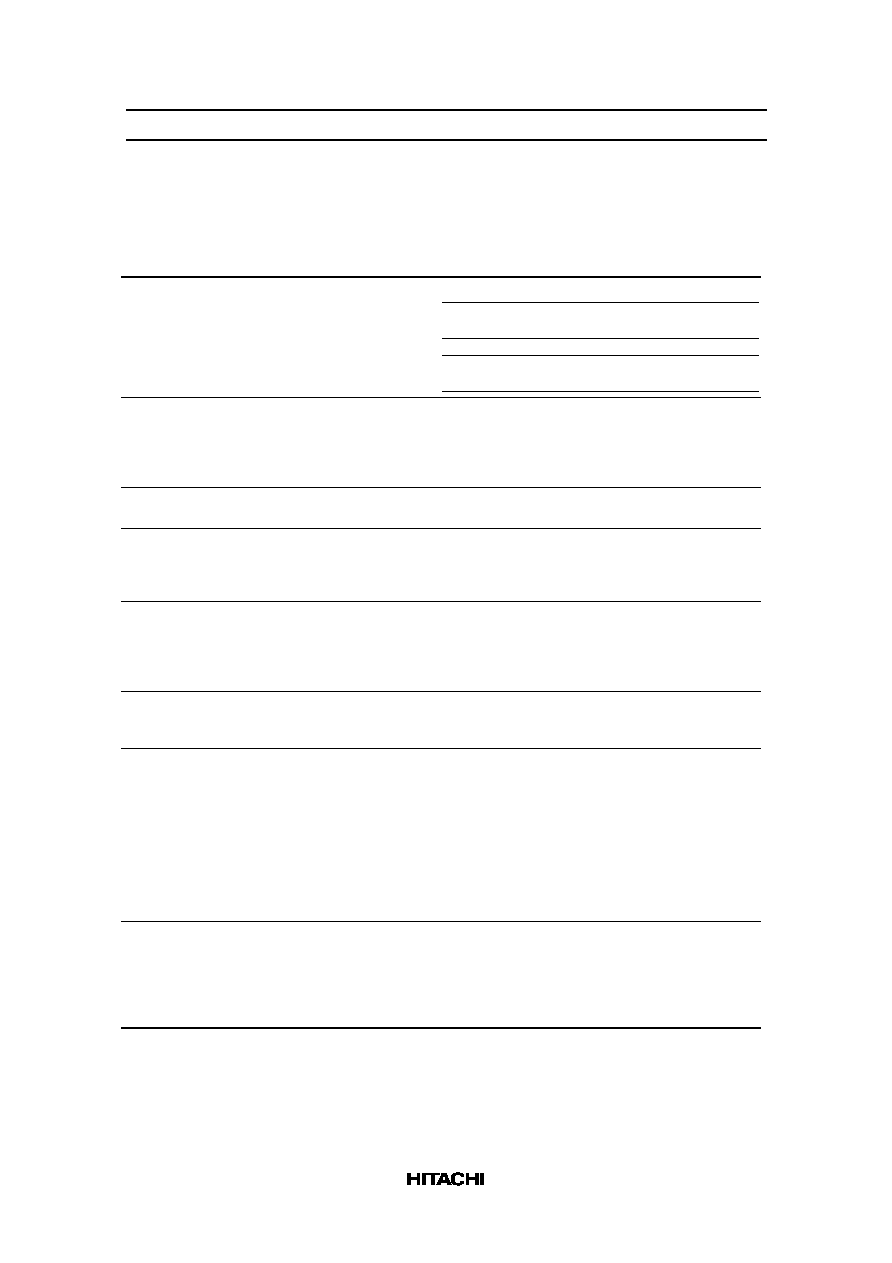

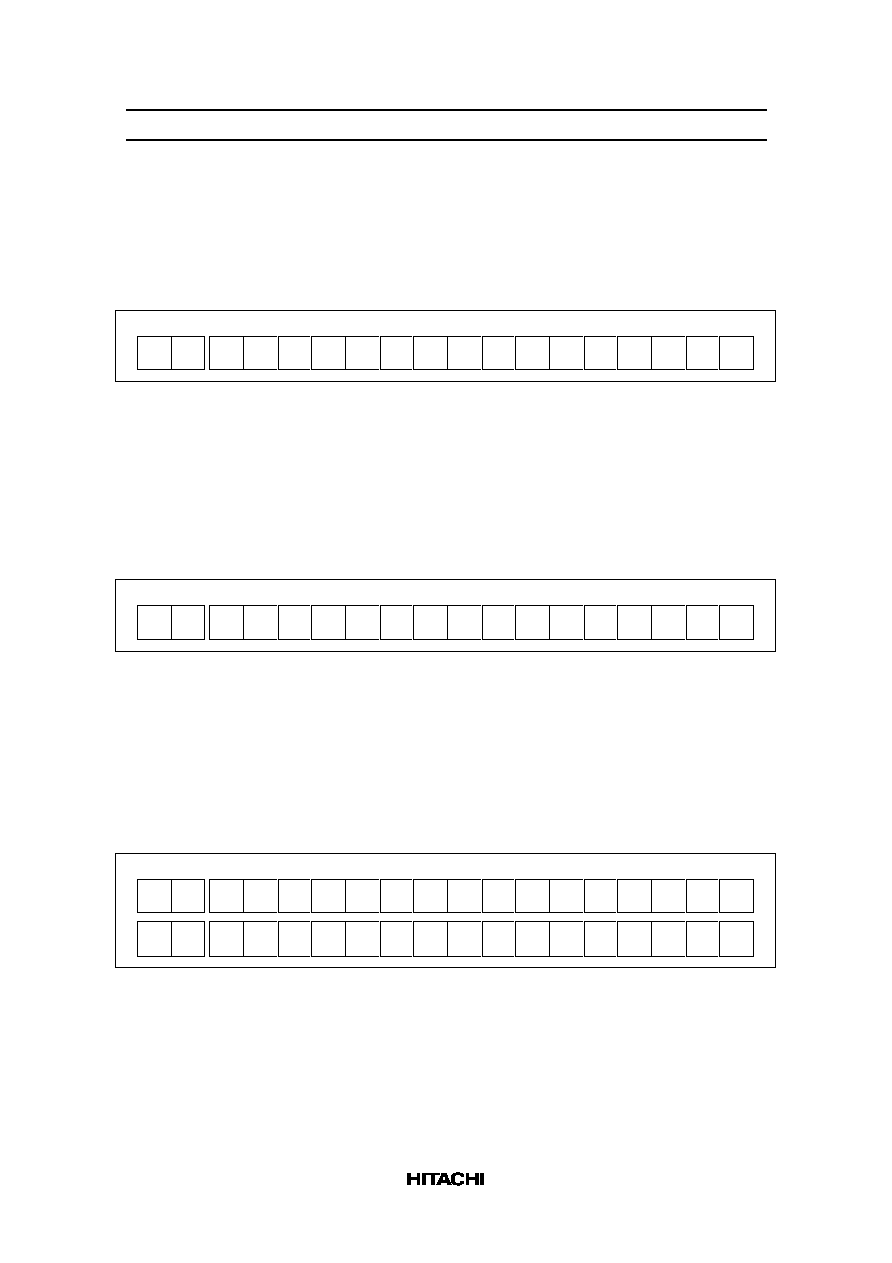

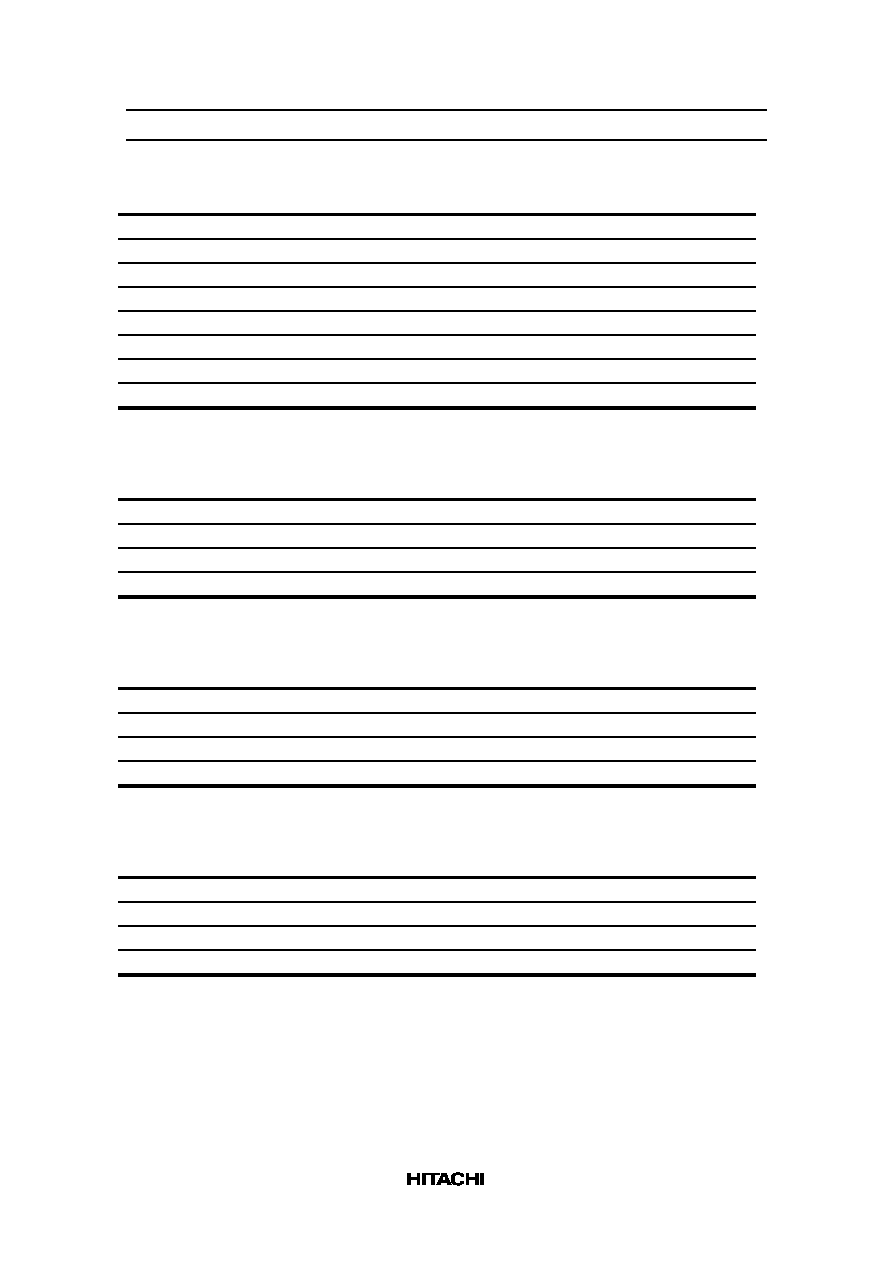

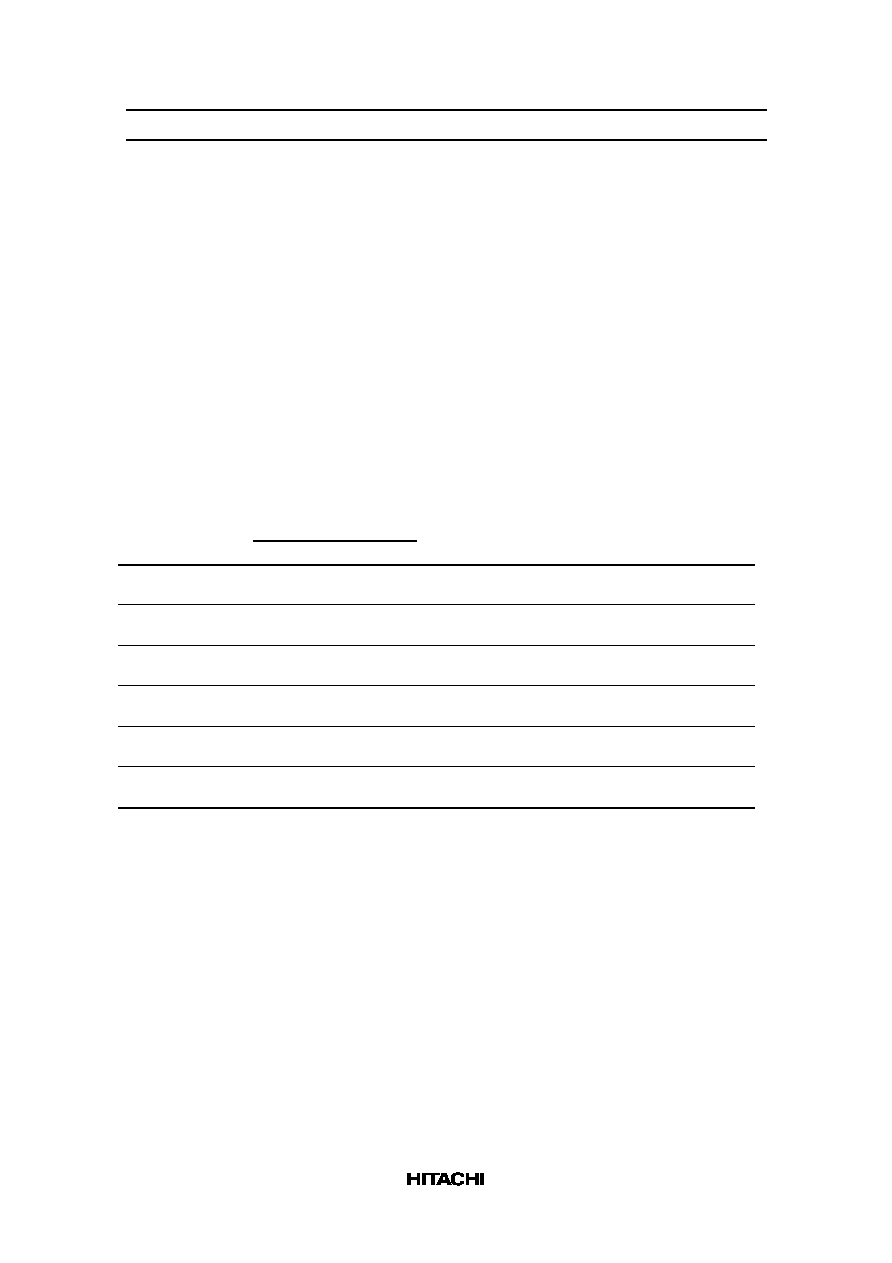

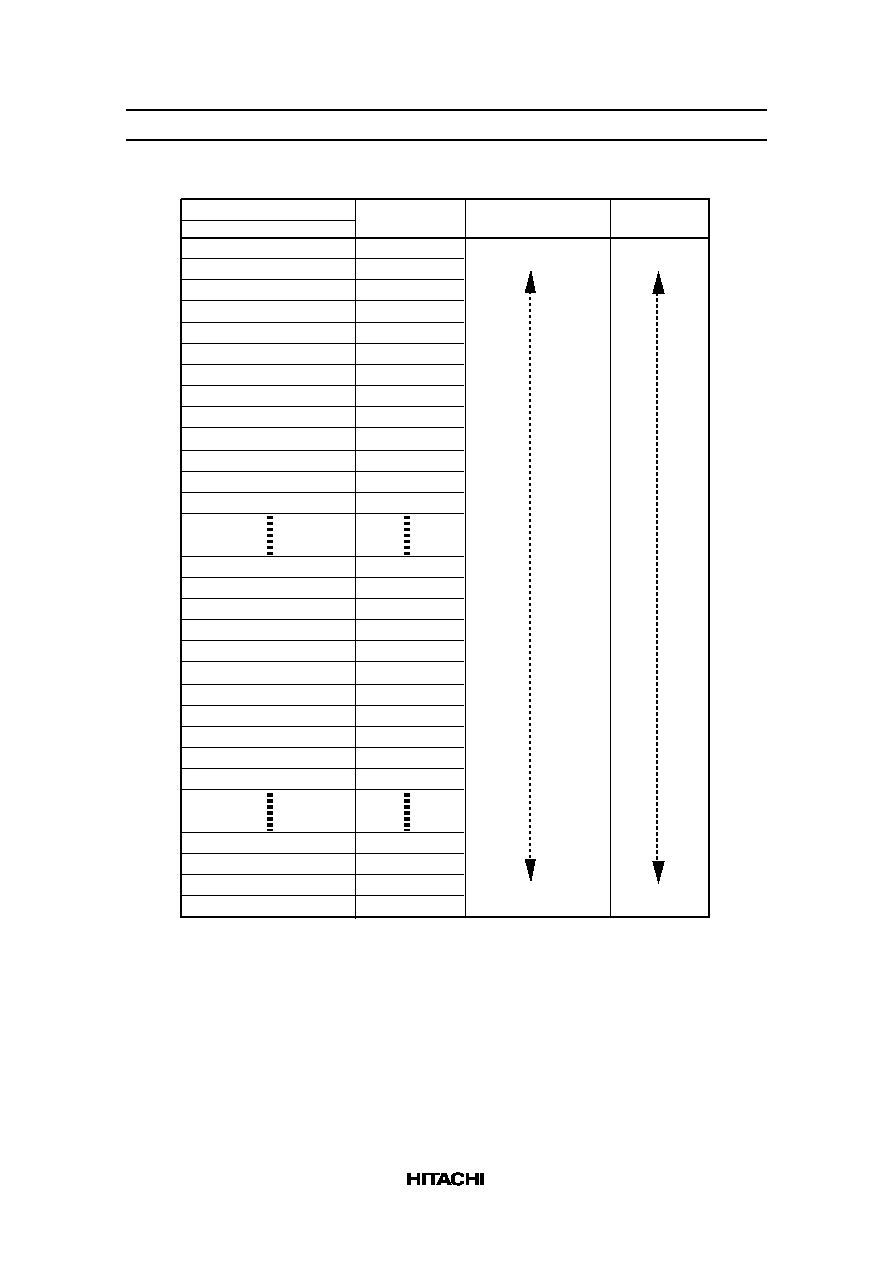

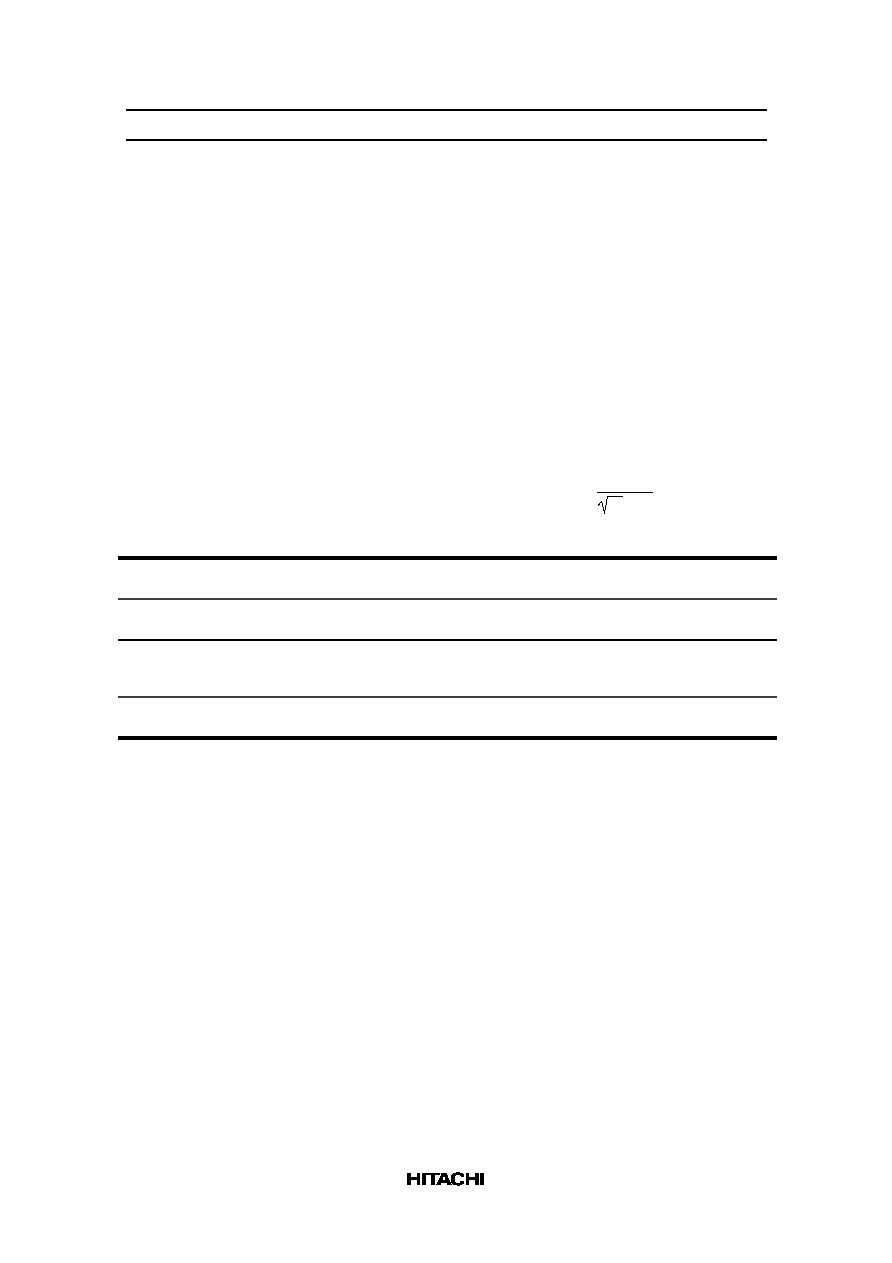

Table 1

Progammable Display Sizes and Duty Ratios

Graphics Display

Duty

Ratio

Optimum

Drive Bias

Bit-map

Display Area

12 x 12-dot

Font Width

12 x 13-dot

Font Width

14 x 15-dot

Font Width

16 x 16-dot

Font Width

8 x 10-dot

Font Width

1/16

1/5

128 x 16 dots 1 line x 10

characters

1 line x 10

characters

1 line x 9

characters

1 line x 8

characters

1 line x 16

characters

1/24

1/6

128 x 24 dots 2 lines x 10

characters

1 line x 10

characters

1 line x 9

characters

1 line x 8

characters

2 lines x 16

characters

1/32

1/6

128 x 32 dots 2 lines x 10

characters

2 lines x 10

characters

2 lines x 9

characters

2 lines x 8

characters

3 lines x 16

characters

1/72

1/9

128 x 72 dots 6 lines x 10

characters

5 lines x 10

characters

4 lines x 9

characters

4 lines x 8

characters

7 lines x 16

characters

1/80

1/10

128 x 80 dots 6 lines x 10

characters

6 lines x 10

characters

5 lines x 9

characters

5 lines x 8

characters

8 lines x 16

characters

1/88

1/10

128 x 88 dots 7 lines x 10

characters

6 lines x 10

characters

5 lines x 9

characters

5 lines x 8

characters

8 lines x 16

characters

1/96

1/10

128 x 96 dots 8 lines x 10

characters

7 lines x 10

characters

6 lines x 9

characters

6 lines x 8

characters

9 lines x 16

characters

1/104

1/11

128 x 104

dots

8 lines x 10

characters

8 lines x 10

characters

6 lines x 9

characters

6 lines x 8

characters

10 lines x 16

characters

1/112

1/11

128 x 112

dots

9 lines x 10

characters

8 lines x 10

characters

7 lines x 9

characters

7 lines x 8

characters

11 lines x 16

characters

1/120

1/11

128 x 120

dots

10 lines x 10

characters

9 lines x 10

characters

8 lines x 9

characters

7 lines x 8

characters

12 lines x 16

characters

1/128

1/11

128 x 128

dots

10 lines x 10

characters

9 lines x 10

characters

8 lines x 9

characters

8 lines x 8

characters

12 lines x 16

characters

HD66750/1

3

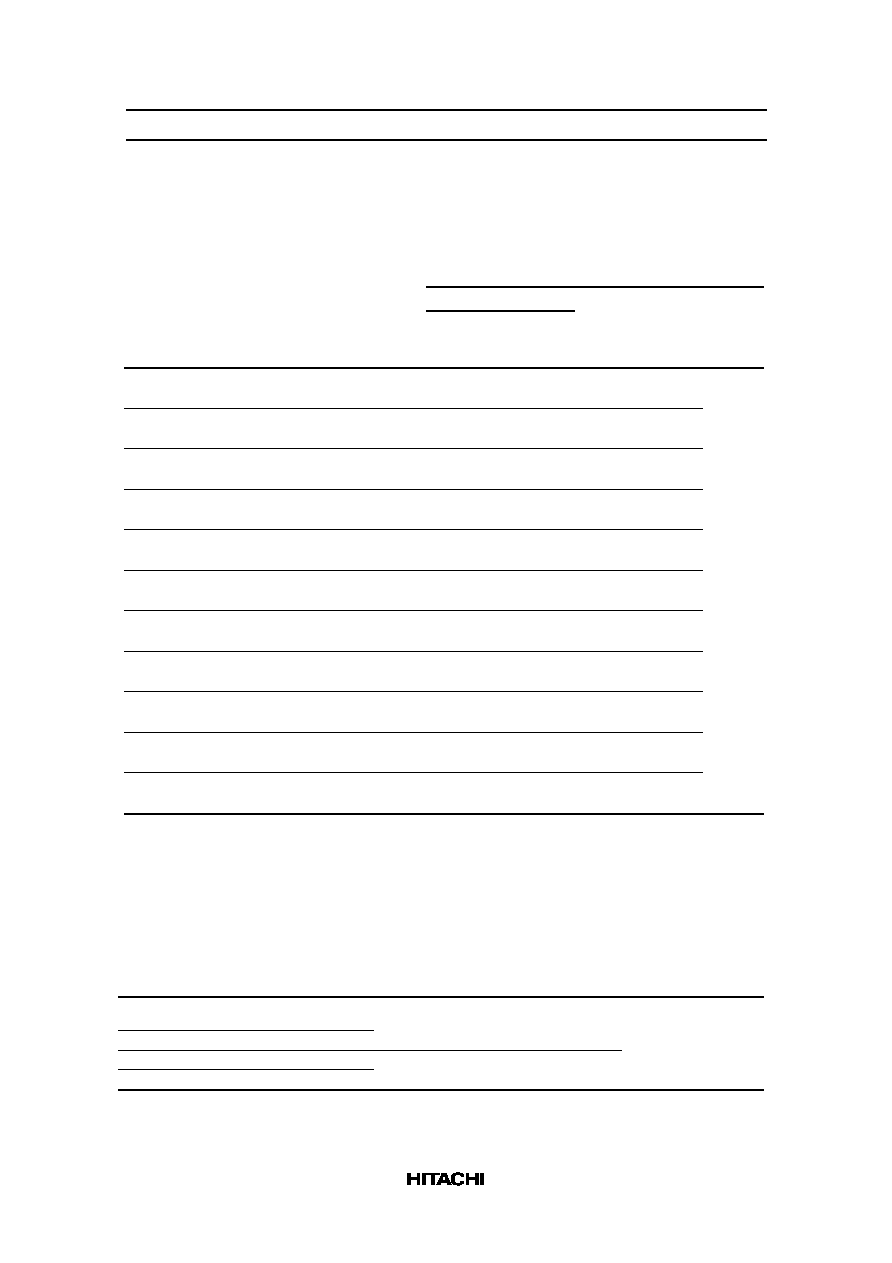

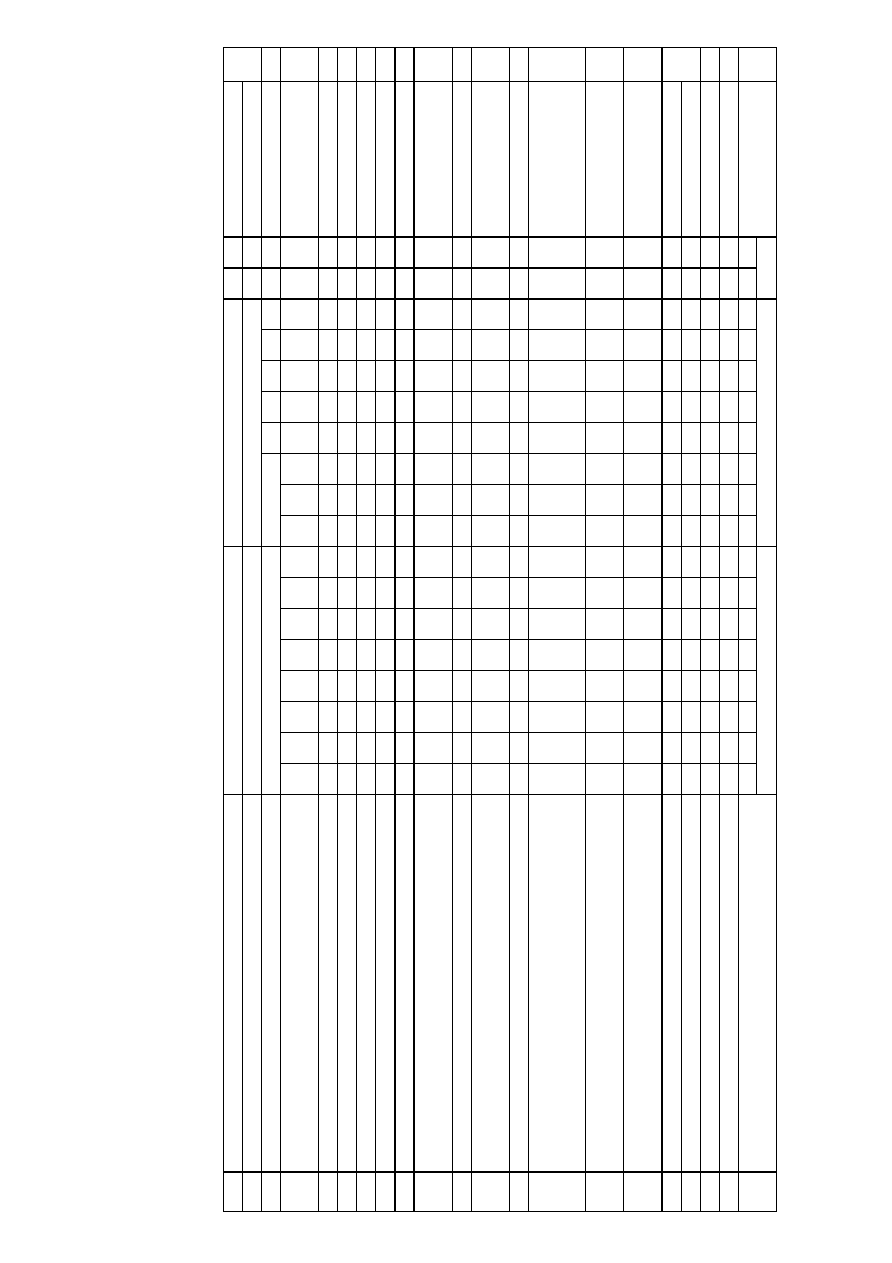

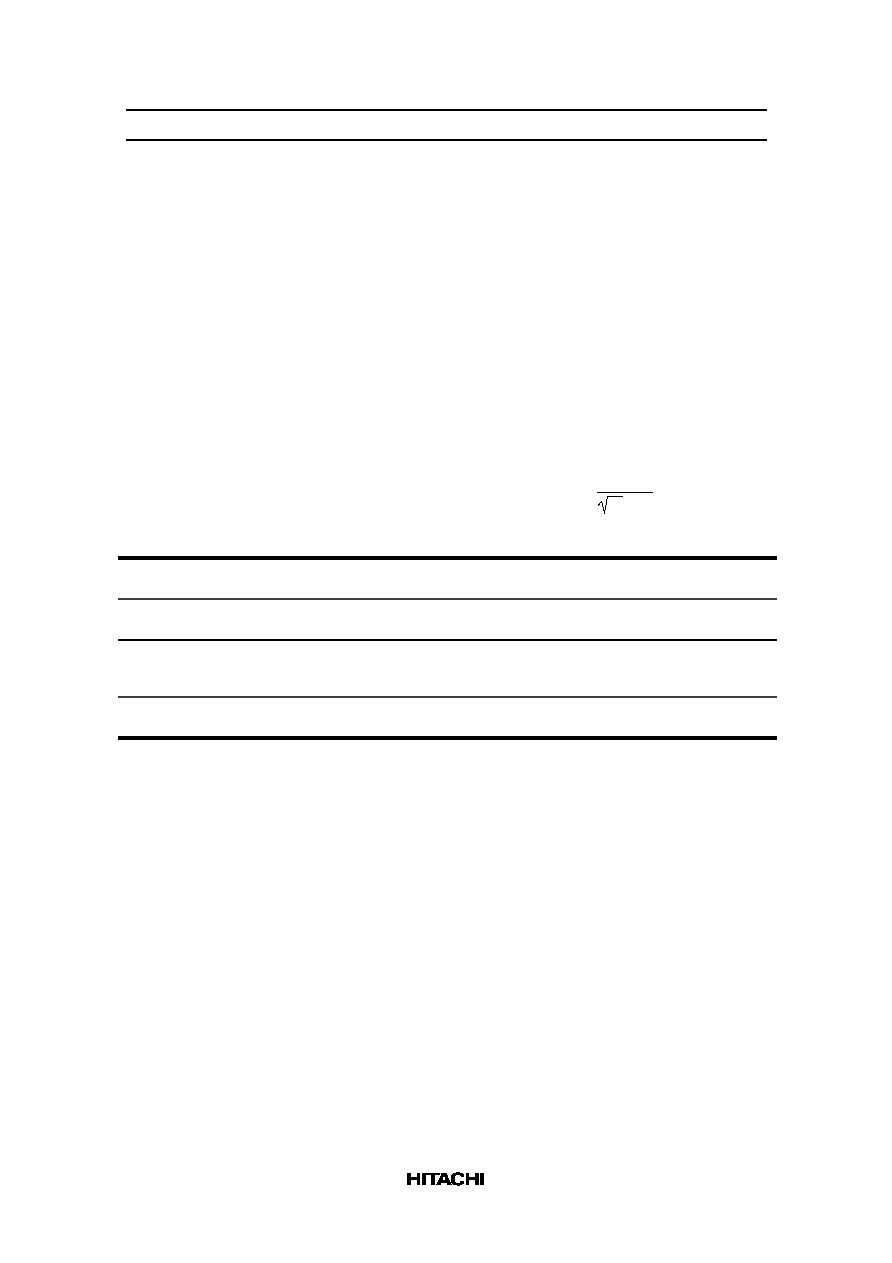

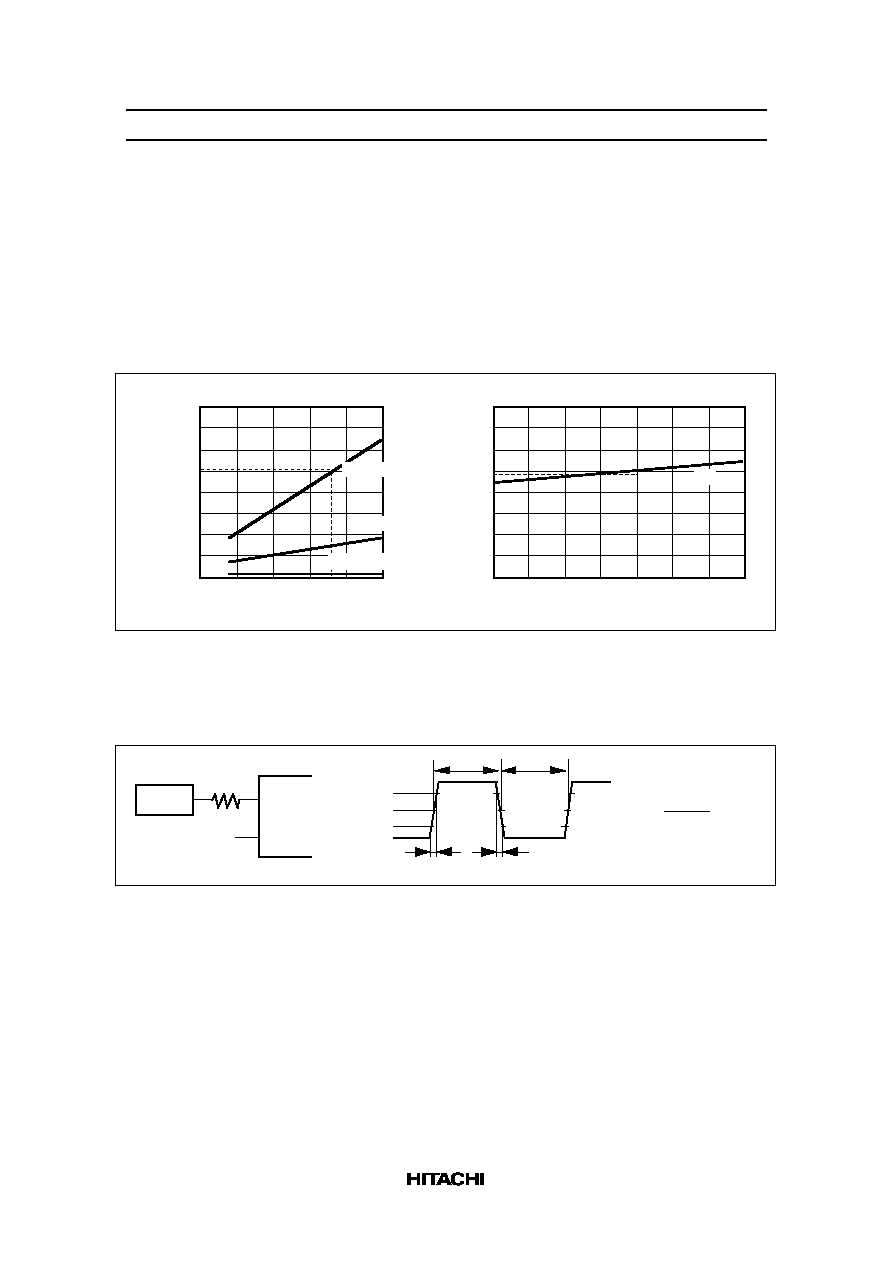

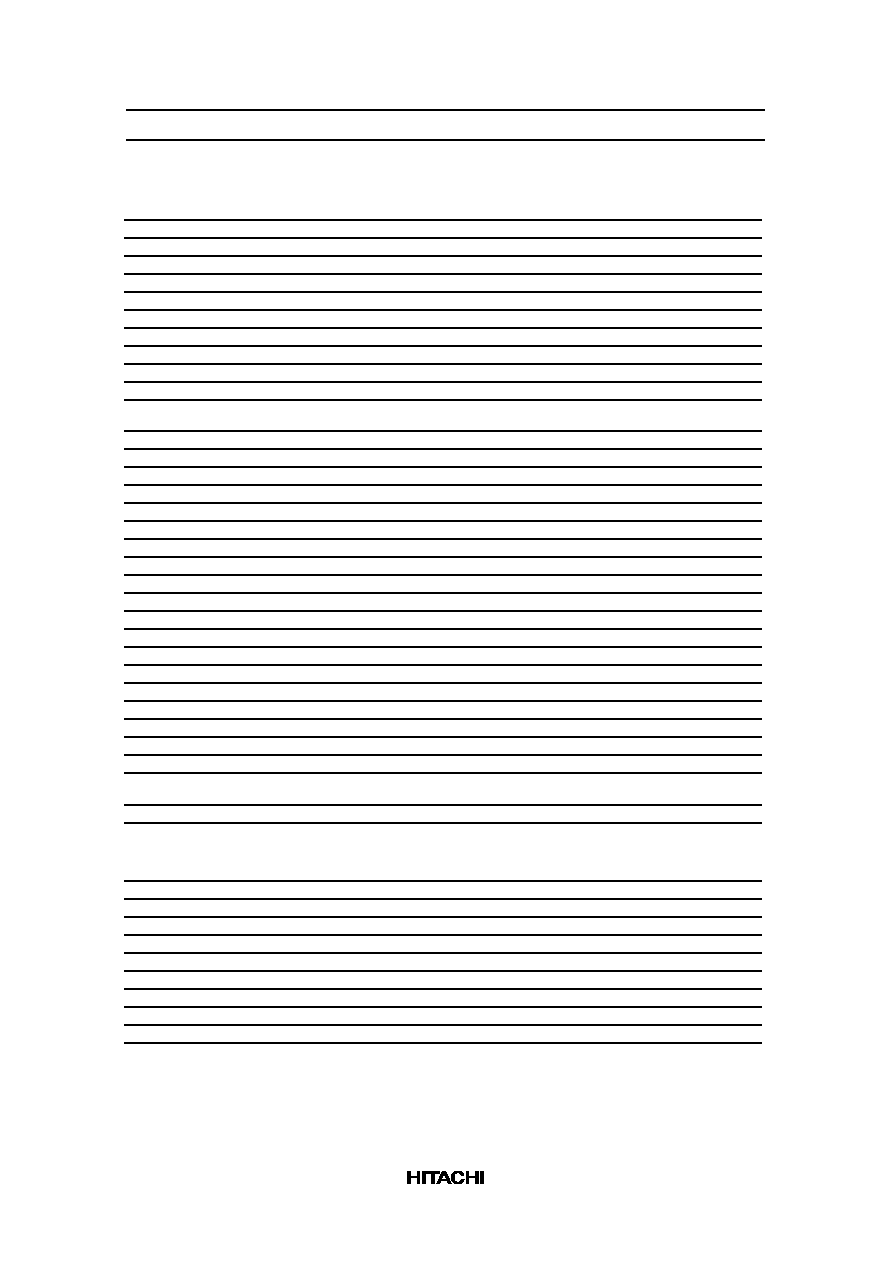

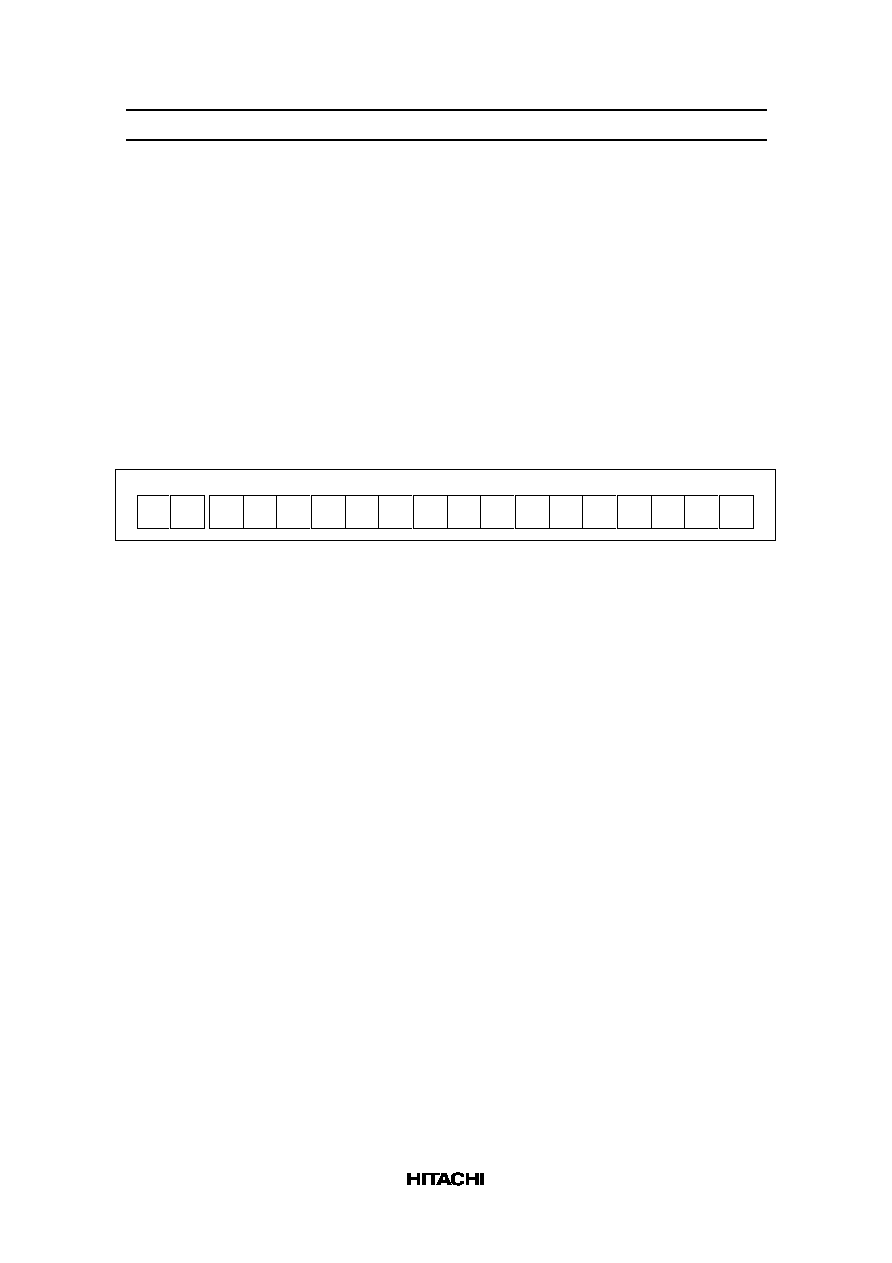

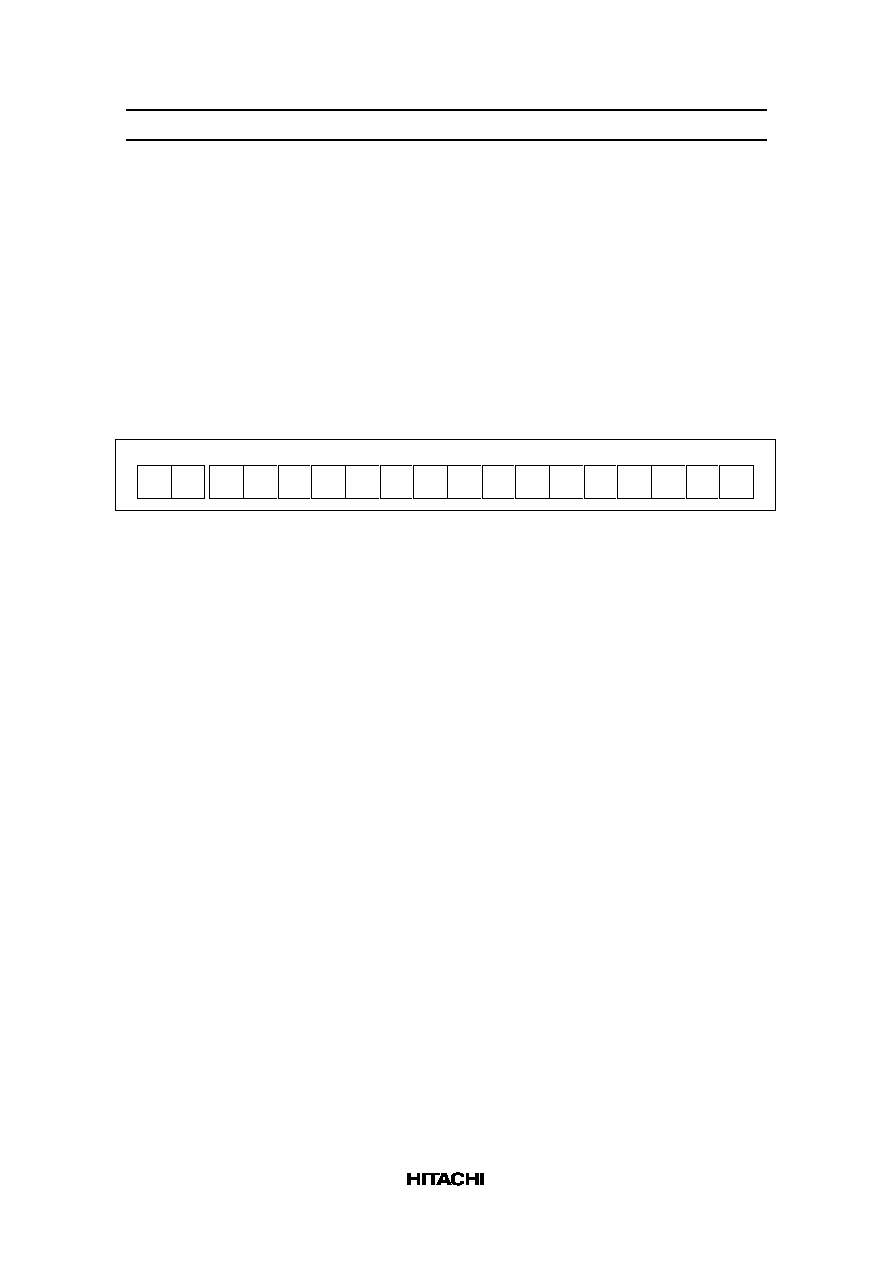

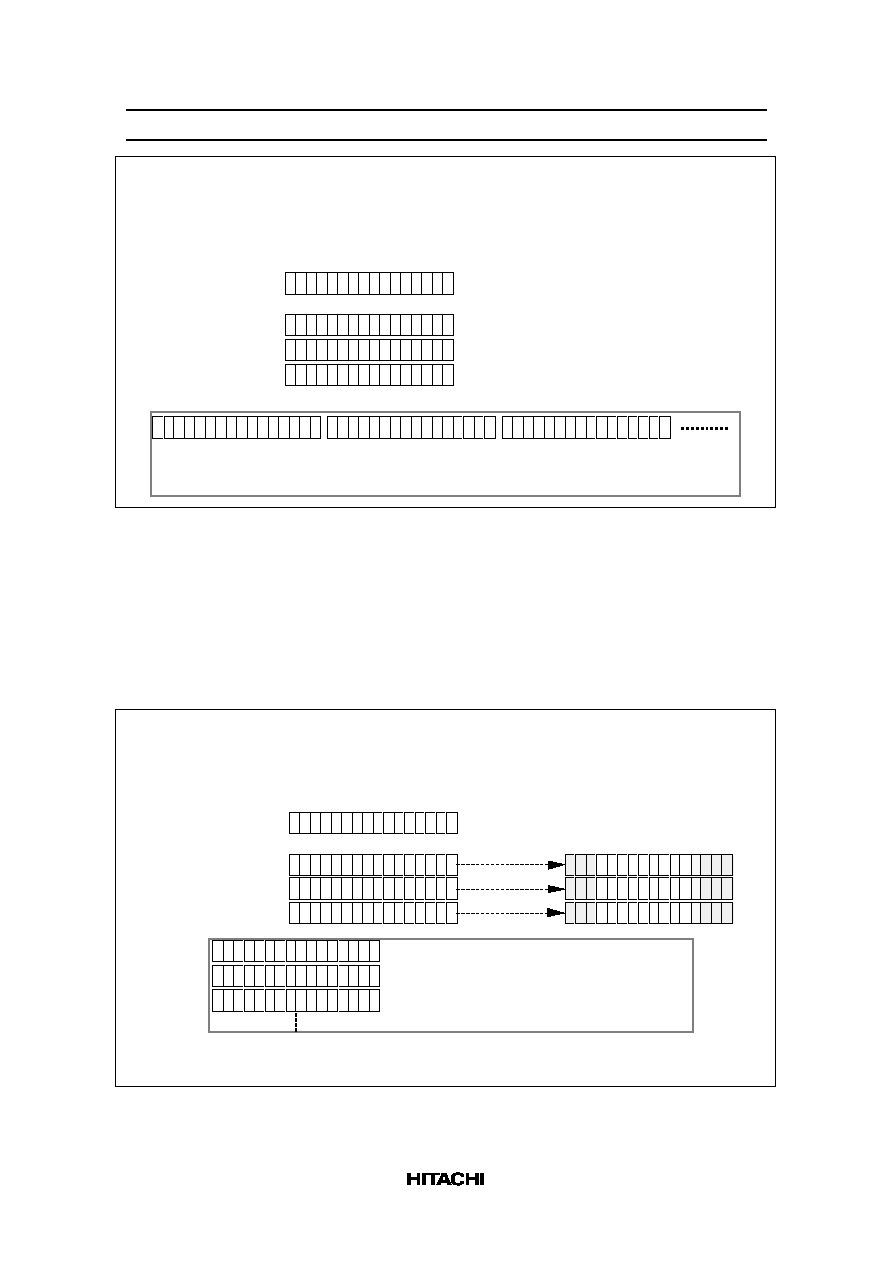

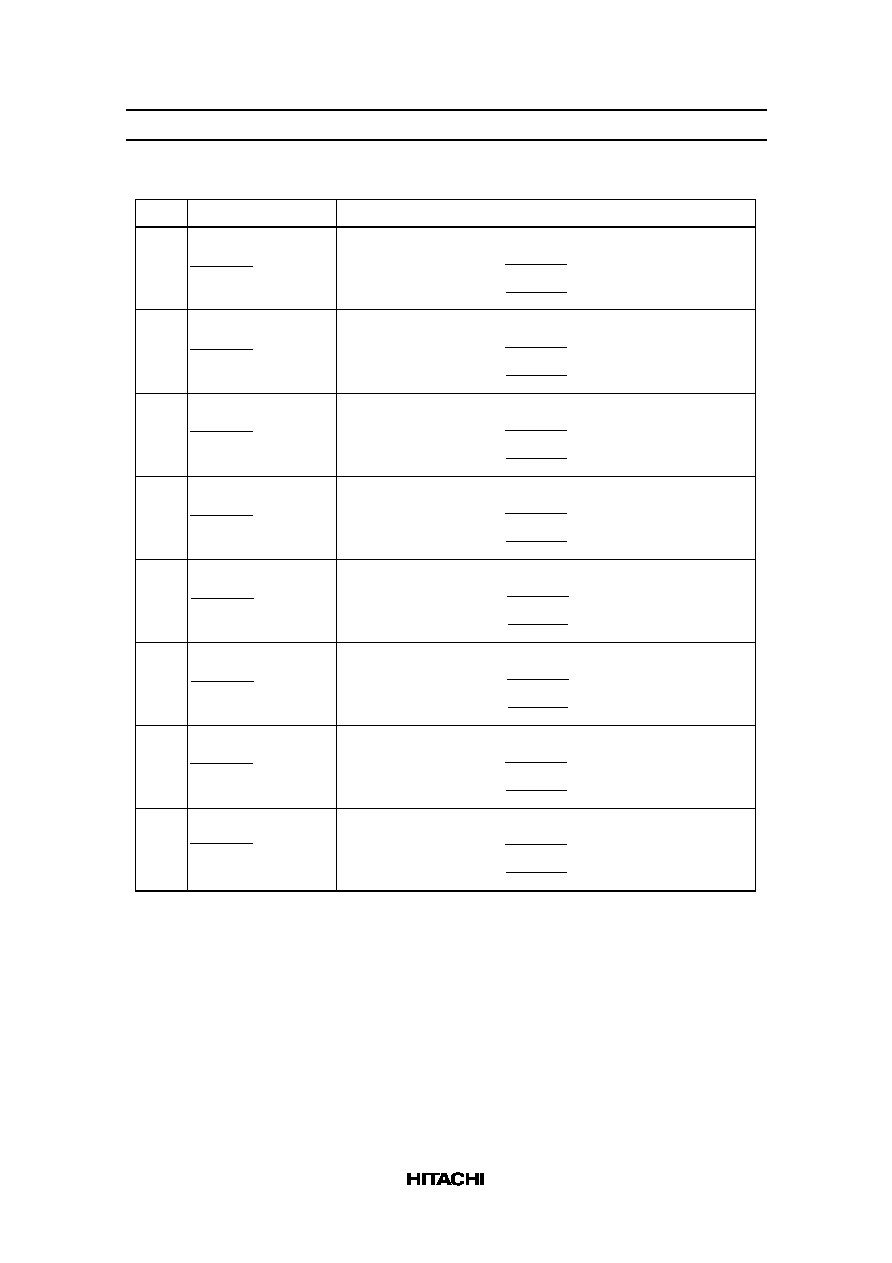

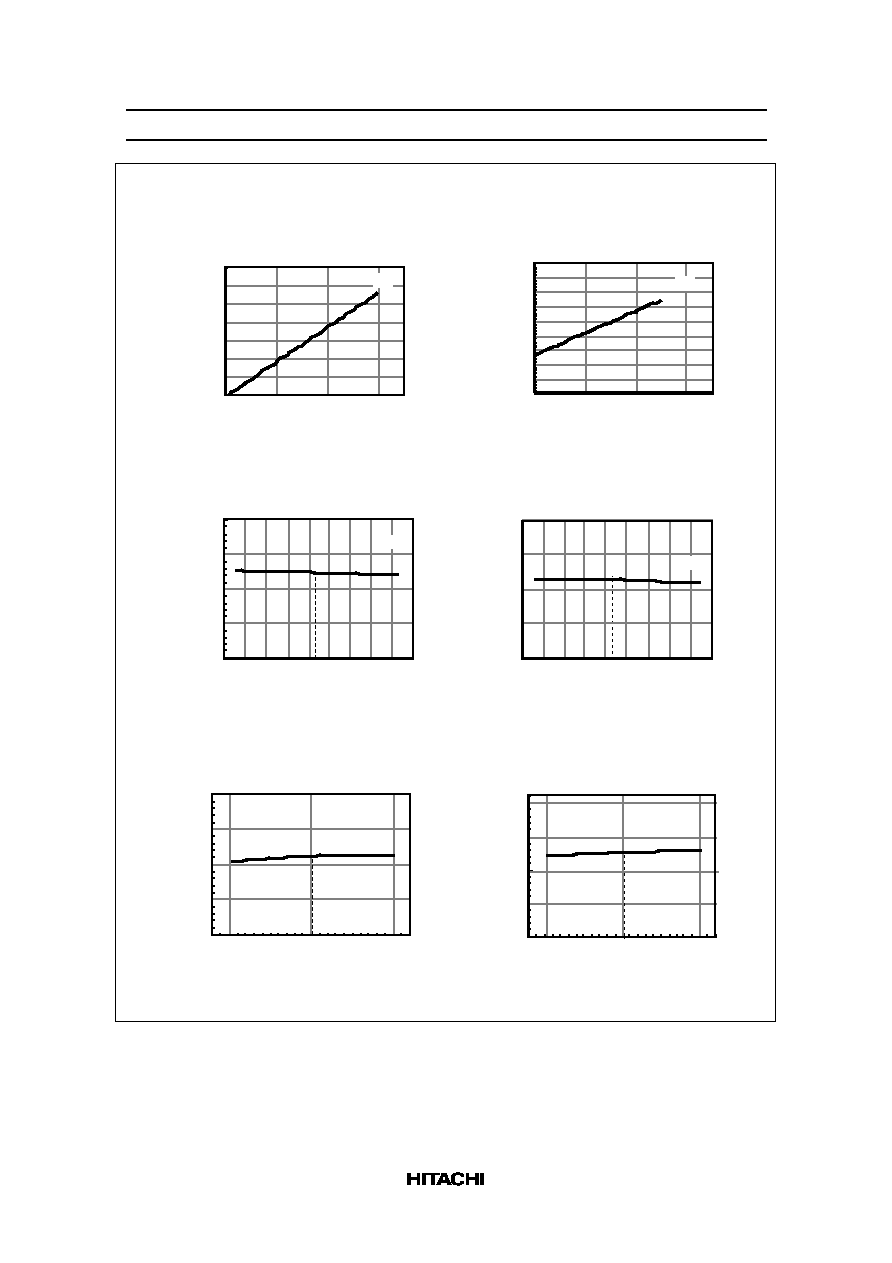

<Target values>

Total Current Consumption Characteristics (Vcc = 3 V, TYP Conditions, LCD

Drive Power Current Included)

Total Power Consumption

Normal Display Operation

Character

Display Dot

Size

Duty

Ratio

R-C

Oscillation

Frequency

Frame

Frequency

Internal

Logic

LCD

Power

Total*

Sleep

Mode

Standby

Mode

128 x 16 dots 1/16

70 kHz

72 Hz

(15

mA)

(15

mA)

Two-times

(45

mA)

(10

mA) 0.1 mA

128 x 24 dots 1/24

70 kHz

72 Hz

(15

mA)

(15

mA)

Two-times

(45

mA)

(10

mA)

128 x 32 dots 1/32

70 kHz

72 Hz

(15

mA)

(15

mA)

Two-times

(45

mA)

(10

mA)

128 x 72 dots 1/72

70 kHz

71 Hz

(40

mA)

(18

mA)

Five-times

(130

mA)

(10

mA)

128 x 80 dots 1/80

70 kHz

73 Hz

(40

mA)

(18

mA)

Five-times

(130

mA)

(10

mA)

128 x 88 dots 1/88

70 kHz

74 Hz

(45

mA)

(18

mA)

Five-times

(135

mA)

(10

mA)

128 x 96 dots 1/96

70 kHz

74 Hz

(45

mA)

(20

mA)

Five-times

(145

mA)

(10

mA)

128 x 104 dots 1/104

70 kHz

73 Hz

(45

mA)

(20

mA)

Five-times

(145

mA)

(10

mA)

128 x 112 dots 1/112

70 kHz

71 Hz

(50

mA)

(25

mA)

Six-times

(200

mA)

(10

mA)

128 x 120 dots 1/120

70 kHz

76 Hz

(50

mA)

(25

mA)

Six-times

(200

mA)

(10

mA)

128 x 128 dots 1/128

70 kHz

72 Hz

(50

mA)

(25

mA)

Six-times

(200

mA)

(10

mA)

Note:

When a two-, five-, six-, or seven-times booster is used:

the total power consumption = internal logic current + LCD power current x 2 (two-times booster),

the total power consumption = internal logic current + LCD power current x 5 (five-times booster),

the total power consumption = internal logic current + LCD power current x 6 (six-times booster), and

the total power consumption = internal logic current + LCD power current x 7 (seven-times booster)

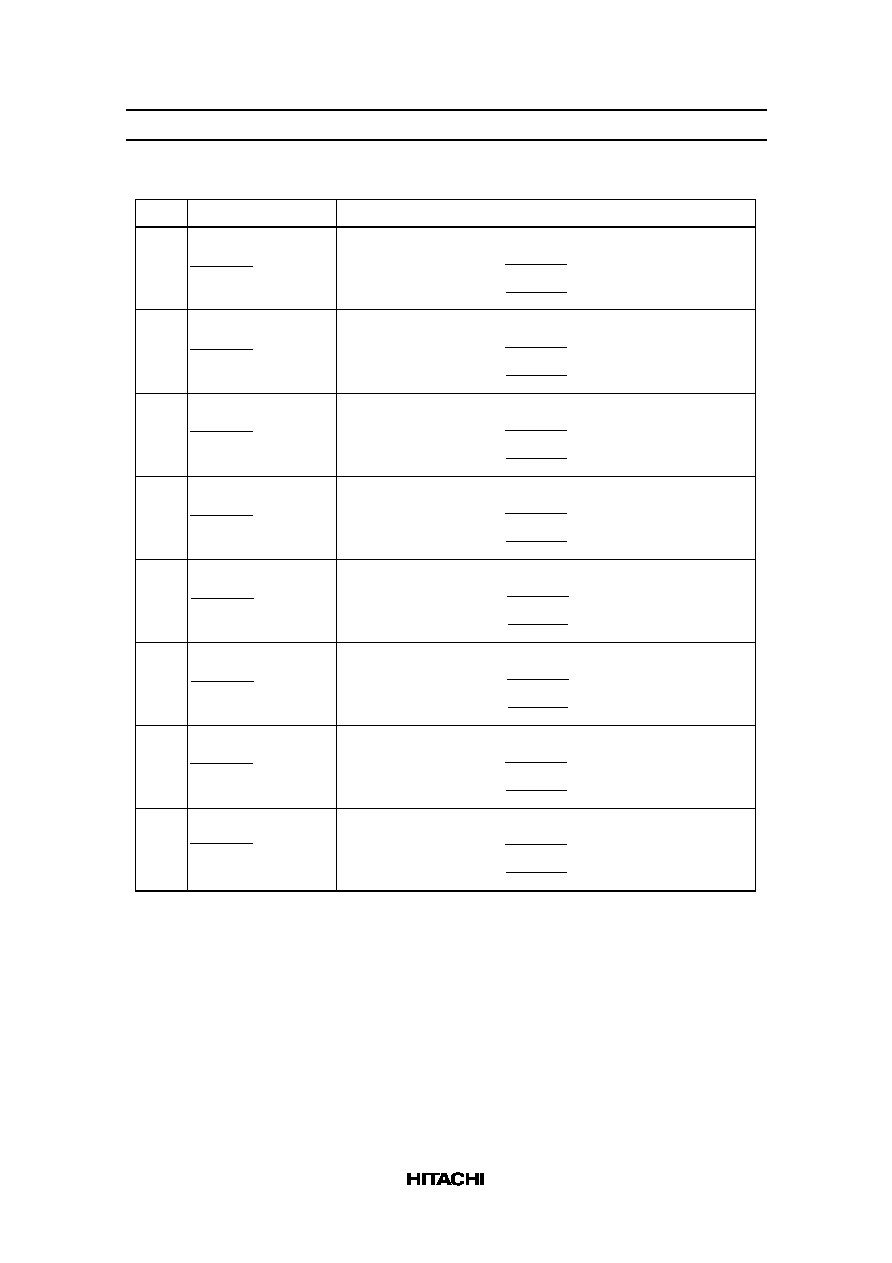

Type Name

Types

External Dimensions

COM Driver Arrangement

Display

HD66750TB0

Bending TCP

Both sides of COM

(Output from left and right sides of the chip)

Four monochrome

grayscales

HCD66750BP

Au-bump chip

HD66751TB0

Bending TCP

One side of COM

HCD66751BP

Au-bump chip

(Output from one side of the chip)

HD66750/1

4

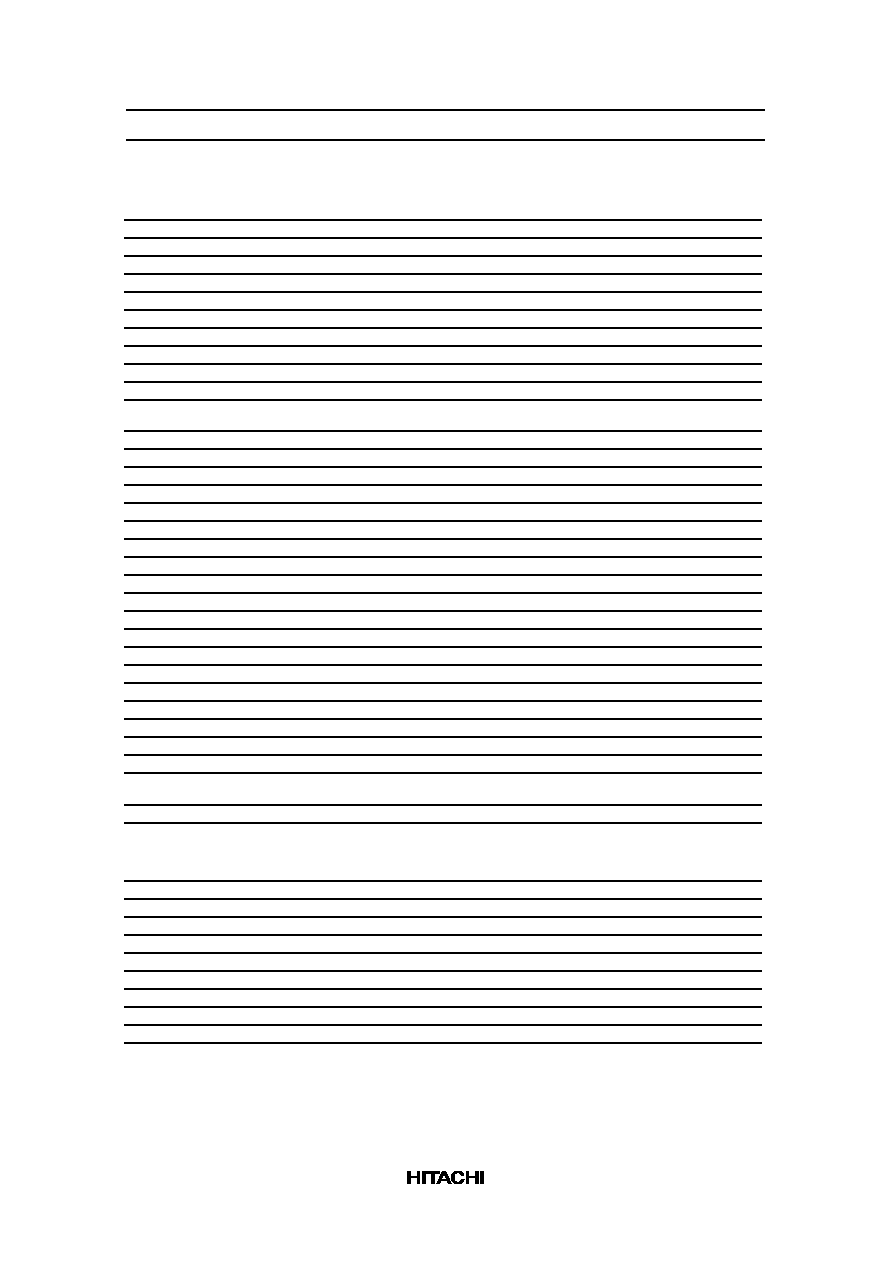

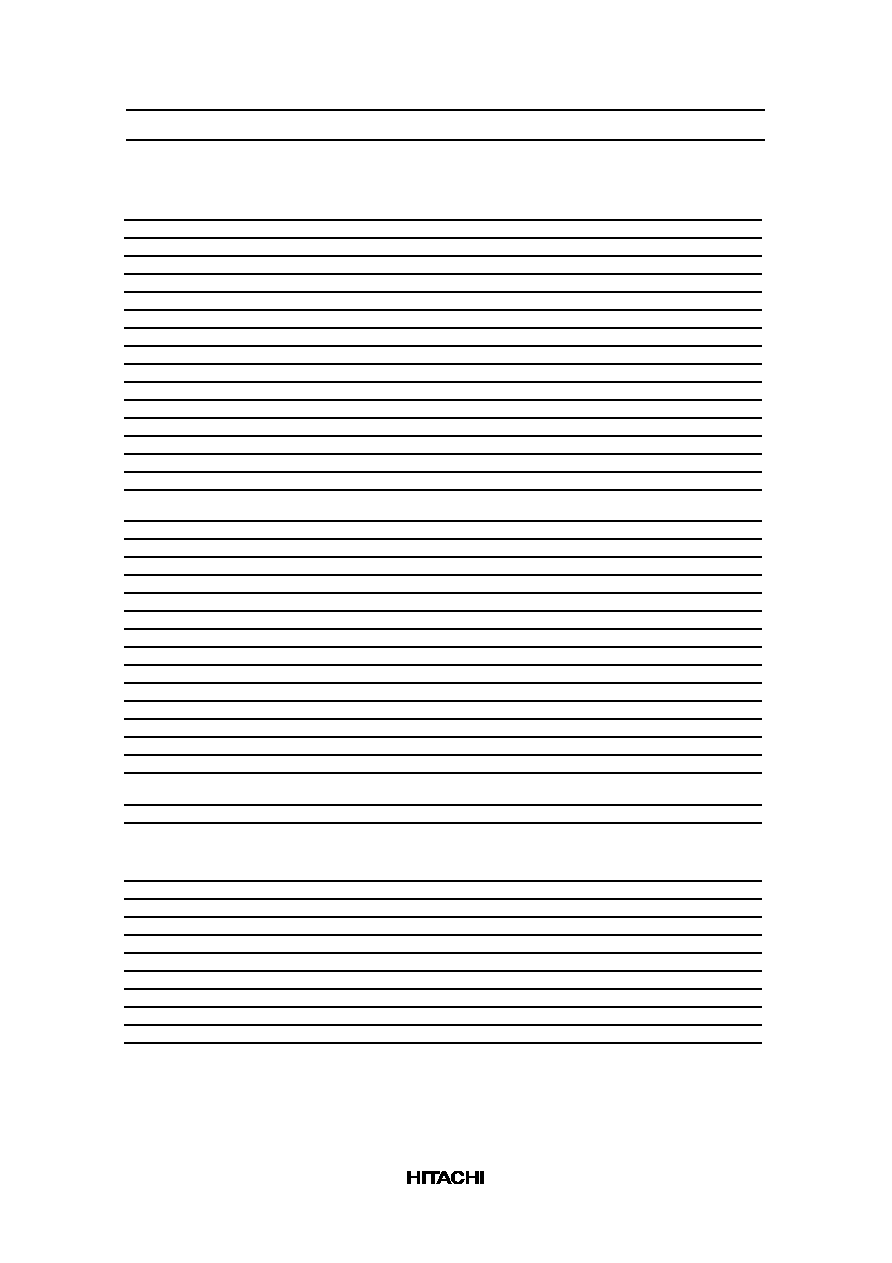

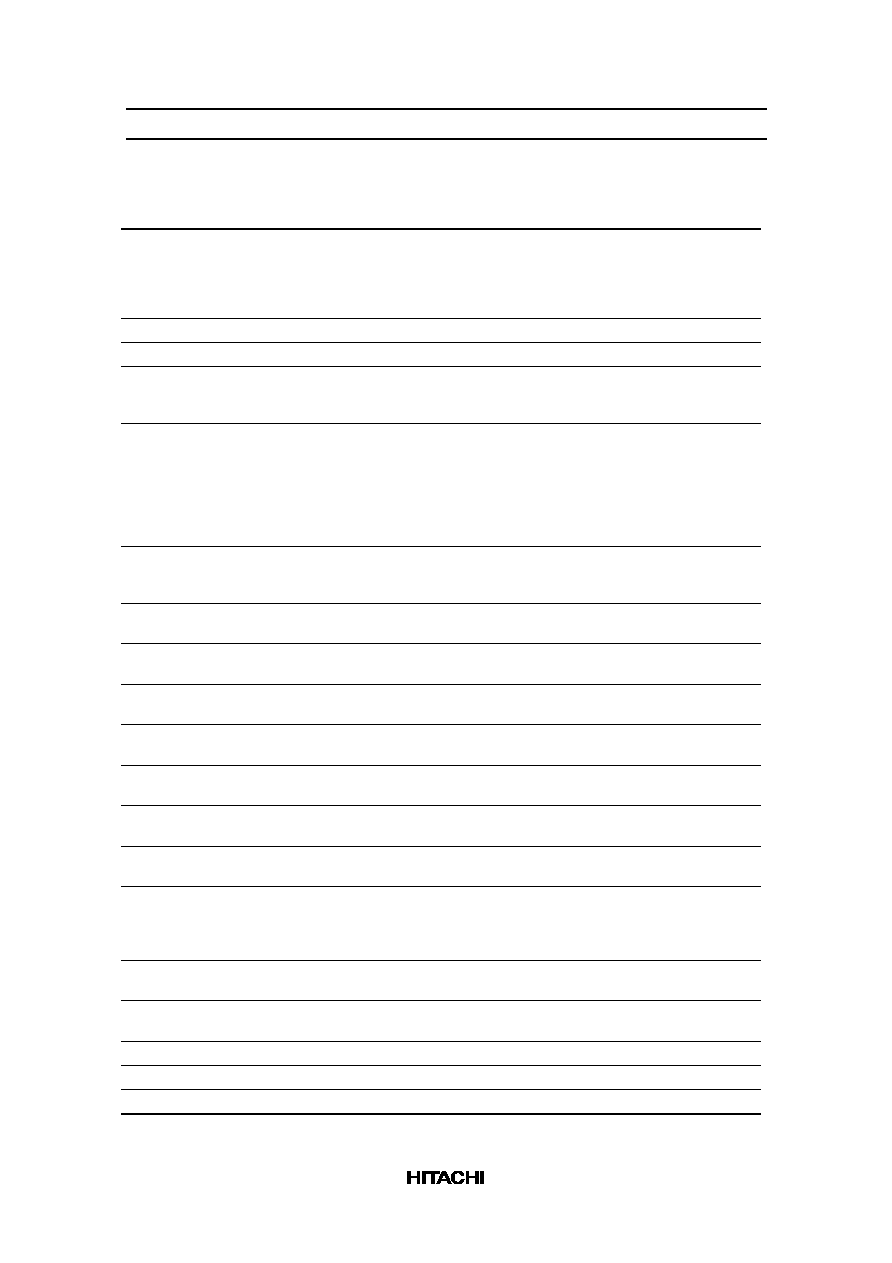

LCD Family Comparison

Items

HD66705U

HD66717

HD66727

Character display sizes

12 characters x 2 lines

12 characters x 4 lines

12 characters x 4 lines

Graphic display sizes

—

—

—

Grayscale display

—

—

—

Multiplexing icons

40

40

40

Annunciator

Static: 10

Static: 10

Static: 12

Key scan control

—

—

4 x 8

LED control ports

—

—

3

General output ports

—

—

3

Operating power voltages

2.4 V to 5.5 V

2.4 V to 5.5 V

2.4 V to 5.5 V

Liquid crystal drive voltages

3 V to 9 V

3 V to 13 V

3 V to 13 V

Serial bus

Clock-synchronized serial

I2C, Clock-synchronized

serial

I2C, Clock-synchronized

serial

Parallel bus

4 bits, 8 bits

4 bits, 8 bits

—

Liquid crystal drive duty ratios

1/10, 18

1/10, 18, 26, 34

1/10, 18, 26, 34

Liquid crystal drive biases

1/4

1/4, 1/6

1/4, 1/6

Liquid crystal drive waveforms

B

B

B

Liquid crystal voltage booster

Two- or three-times

Two- or three-times

Two- or three-times

Bleeder-resistor for liquid crystal drive

Incorporated (external)

Incorporated (external)

Incorporated (external)

Liquid crystal drive operational amplifier

Incorporated

Incorporated

Incorporated

Liquid crystal contrast adjuster

Incorporated

Incorporated

Incorporated

Horizontal smooth scroll

—

—

—

Vertical smooth scroll

Line unit

Line unit

Line unit

Double-height display

Yes

Yes

Yes

DDRAM

60 x 8

60 x 8

60 x 8

CGROM

9,600

9,600

11,520

CGRAM

32 x 5

32 x 5

32 x 6

SEGRAM

8 x 5

8 x 5

8 x 6

No. of CGROM fonts

240

240

240

No. of CGRAM fonts

4

4

4

Font sizes

5 x 8

5 x 8

5 x 8, 6 x 8

Bit map area

—

—

—

R-C oscillation resistor/

oscillation frequency

External resistor

(40, 80 kHz)

External resistor

(40-160 kHz)

External resistor

(40-160 kHz)

Reset function

External

External

External

Low power control

Partial display off,

Oscillation off,

Liquid crystal power off

Partial display off,

Oscillation off,

Liquid crystal power off

Partial display off,

Oscillation off,

Liquid crystal power off,

Key wake-up interrupt

SEG/COM direction switching

SEG only

SEG only

SEG, COM

QFP package

—

—

—

TQFP package

—

—

—

TCP package

TCP-153

TCP-153

TCP-158

Bare chip

Yes

Yes

Yes

Bumped chip

Yes

Yes

Yes

No. of pins

153

153

158

Chip sizes

9.69 x 2.73

10.88 x 2.89

11.39 x 2.89

Pad intervals

120

mm

120

mm

120

mm

HD66750/1

5

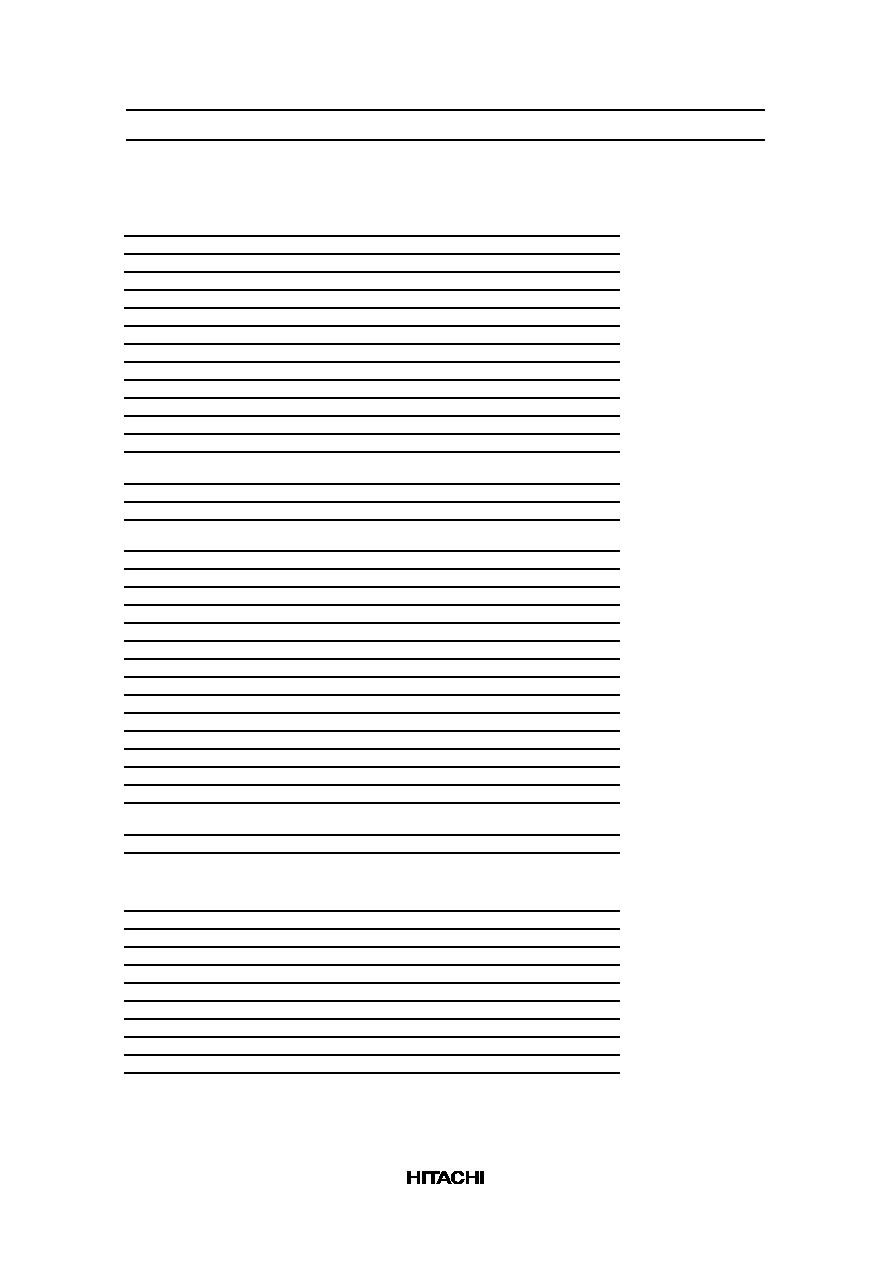

LCD Family Comparison (cont)

Items

HD66724

HD66725

HD66726

Character display sizes

12 characters x 3 lines

16 characters x 3 lines

16 characters x 5 lines

Graphic display sizes

72 x 26 dots

96 x 26 dots

96 x 42 dots

Grayscale display

—

—

—

Multiplexing icons

144

192

192

Annunciator

1/2 duty: 144

1/2 duty: 192

1/2 duty: 192

Key scan control

8 x 4

8 x 4

8 x 4

LED control ports

—

—

—

General output ports

3

3

3

Operating power voltages

1.8 V to 5.5 V

1.8 V to 5.5 V

1.8 V to 5.5 V

Liquid crystal drive voltages

3 V to 6.5 V

3 V to 6.5 V

4.5 V to 11 V

Serial bus

Clock-synchronized serial

Clock-synchronized serial

Clock-synchronized serial

Parallel bus

4 bits, 8 bits

4 bits, 8 bits

4 bits, 8 bits

Liquid crystal drive duty ratios

1/2, 10, 18, 26

1/2, 10, 18, 26

1/2, 10, 18, 26, 34, 42

Liquid crystal drive biases

1/4 to 1/6.5

1/4 to 1/6.5

1/2 to 1/8

Liquid crystal drive waveforms

B

B

B

Liquid crystal voltage booster

Single, two-, or three-times

Single, two-, or three-times

Single, two-, three-, or four-

times

Bleeder-resistor for liquid crystal drive

Incorporated (external)

Incorporated (external)

Incorporated (external)

Liquid crystal drive operational amplifier

Incorporated

Incorporated

Incorporated

Liquid crystal contrast adjuster

Incorporated

Incorporated

Incorporated

Horizontal smooth scroll

3-dot unit

3-dot unit

—

Vertical smooth scroll

Line unit

Line unit

Line unit

Double-height display

Yes

Yes

Yes

DDRAM

80 x 8

80 x 8

80 x 8

CGROM

20,736

20,736

20,736

CGRAM

384 x 8

384 x 8

480 x 8

SEGRAM

72 x 8

96 x 8

96 x 8

No. of CGROM fonts

240 + 192

240 + 192

240 + 192

No. of CGRAM fonts

64

64

64

Font sizes

6 x 8

6 x 8

6 x 8

Bit map areas

72 x 26

96 x 26

96 x 42

R-C oscillation resistor/

oscillation frequency

External resistor, incorporated

(32 kHz)

External resistor, incorporated

(32 kHz)

External resistor

(50 kHz)

Reset function

External

External

External

Low power control

Partial display off,

Oscillation off,

Liquid crystal power off,

Key wake-up interrupt

Partial display off,

Oscillation off,

Liquid crystal power off,

Key wake-up interrupt

Partial display off,

Oscillation off,

Liquid crystal power off,

Key wake-up interrupt

SEG/COM direction switching

SEG, COM

SEG, COM

SEG, COM

QFP package

—

—

—

TQFP package

—

—

—

TCP package

TCP-146

TCP-170

TCP-188

Bare chip

—

—

Yes

Bumped chip

Yes

Yes

Yes

No. of pins

146

170

188

Chip sizes

10.34 x 2.51

10.97 x 2.51

13.13 x 2.51

Pad intervals

80

mm

80

mm

100

mm

HD66750/1

6

LCD Family Comparison (cont)

(WS available)

Items

HD66728

HD66729

Character display sizes

16 characters x 10 lines

—

Graphic display sizes

112 x 80 dots

105 x 68 dots

Grayscale display

—

—

Multiplexing icons

—

—

Annunciator

—

—

Key scan control

8 x 4

—

LED control ports

—

—

General output ports

3

—

Operating power voltages

1.8 V to 5.5 V

1.8 V to 5.5 V

Liquid crystal drive voltages

4.5 V to 15 V

4.0 V to 13 V

Serial bus

Clock-synchronized serial

Clock-synchronized serial

Parallel bus

4 bits, 8 bits

4 bits, 8 bits

Liquid crystal drive duty ratios

1/8, 16, 24, 32, 40, 48, 56, 64,

72, 80

1/8, 16, 24, 32, 40, 48, 56, 64,

68

Liquid crystal drive biases

1/4 to 1/10

1/4 to 1/9

Liquid crystal drive waveforms

B, C

B, C

Liquid crystal voltage booster

Three-, four-, or five-times

Two-, three-, four-, or five-

times

Bleeder-resistor for liquid crystal drive

Incorporated (external)

Incorporated (external)

Liquid crystal drive operational amplifier

Incorporated

Incorporated

Liquid crystal contrast adjuster

Incorporated

Incorporated

Horizontal smooth scroll

—

—

Vertical smooth scroll

Line unit

Line unit

Double-height display

Yes

Yes

DDRAM

160 x 8

—

CGROM

20,736

—

CGRAM

1,120 x 8

1,050 x 8

SEGRAM

—

—

No. of CGROM fonts

240 + 192

—

No. of CGRAM fonts

64

—

Font sizes

6 x 8

—

Bit map areas

112 x 80

105 x 68

R-C oscillation resistor/

oscillation frequency

External resistor

(70–90 kHz)

External resistor

(75 kHz)

Reset function

External

External

Low power control

Partial display off,

Oscillation off,

Liquid crystal power off,

Key wake-up interrupt

Partial display off,

Oscillation off,

Liquid crystal power off

SEG/COM direction switching

SEG, COM

SEG, COM

QFP package

—

—

TQFP package

—

—

TCP package

TCP-243

TCP-213

Bare chip

—

—

Bumped chip

Yes

Yes

No. of pins

243

213

Chip sizes

13.67 x 2.78

12.23 x 2.52

Pad intervals

70

mm

70

mm

HD66750/1

7

LCD Family Comparison (cont)

(Under development)

Items

HD66741

HD66750/751

Character display sizes

—

—

Graphic display sizes

128 x 80 dots

128 x 128 dots

Grayscale display

—

Four monochrome grayscales

Multiplexing icons

—

—

Annunciator

—

—

Key scan control

—

—

LED control ports

—

—

General output ports

3

—

Operating power voltages

1.8 V to 5.5 V

1.8 V to 3.6 V

Liquid crystal drive voltages

4.5 V to 15 V

5 V to 15.5 V

Serial bus

Clock-synchronized serial

—

Parallel bus

4 bits, 8 bits

8 bits, 16 bits

Liquid crystal drive duty ratios

1/8, 16, 24, 32, 40, 48, 56, 64,

72, 80

1/16, 24, 72, 80, 88, 96, 104,

112, 120, 128

Liquid crystal drive biases

1/4 to 1/10

1/4 to 1/11

Liquid crystal drive waveforms

B, C

B, C

Liquid crystal voltage booster

Three-, four-, or five-times

Two-, five-, six-, or seven-times

Bleeder-resistor for liquid crystal drive

Incorporated (external)

Incorporated (external)

Liquid crystal drive operational amplifier

Incorporated

Incorporated

Liquid crystal contrast adjuster

Incorporated

Incorporated

Horizontal smooth scroll

—

—

Vertical smooth scroll

Line unit

Line unit

Double-height display

Yes

Yes

DDRAM

—

—

CGROM

—

—

CGRAM

1,280 x 8

4,096 x 8

SEGRAM

—

—

No. of CGROM fonts

—

—

No. of CGRAM fonts

—

—

Font sizes

—

—

Bit map areas

128 x 80

128 x 128

R-C oscillation resistor/

oscillation frequency

External resistor

(70–90 kHz)

External resistor

(70 kHz)

Reset function

External

External

Low power control

Partial display off,

Oscillation off,

Liquid crystal power off

Partial display off,

Oscillation off,

Liquid crystal power off

SEG/COM direction switching

SEG, COM

SEG, COM

QFP package

—

—

TQFP package

—

—

TCP package

TCP-254

TCP-308

Bare chip

—

—

Bumped chip

Yes

Yes

No. of pins

243

308

Chip sizes

14.30 x 2.78

10.97 x 4.13

Pad intervals

70

mm

60

mm

HD66750/1

8

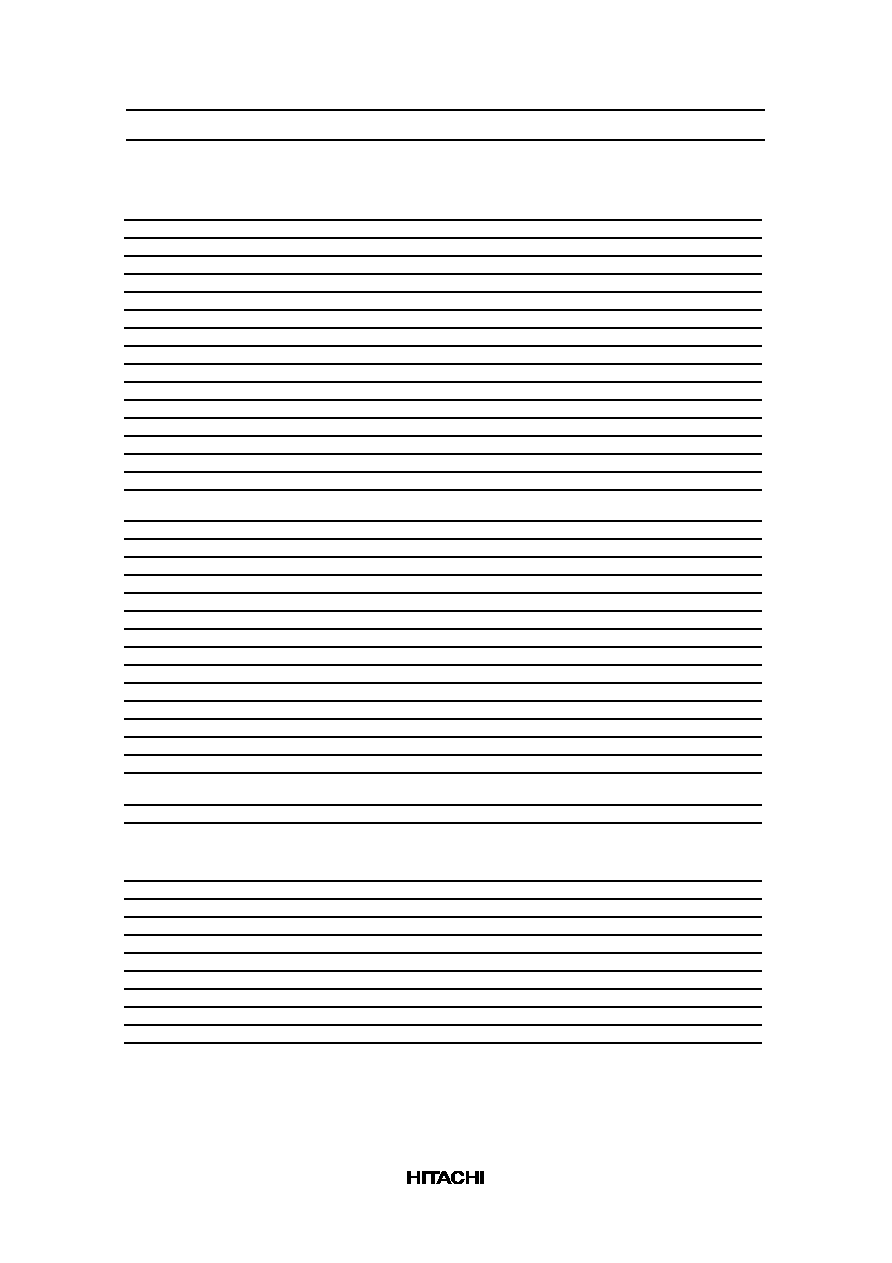

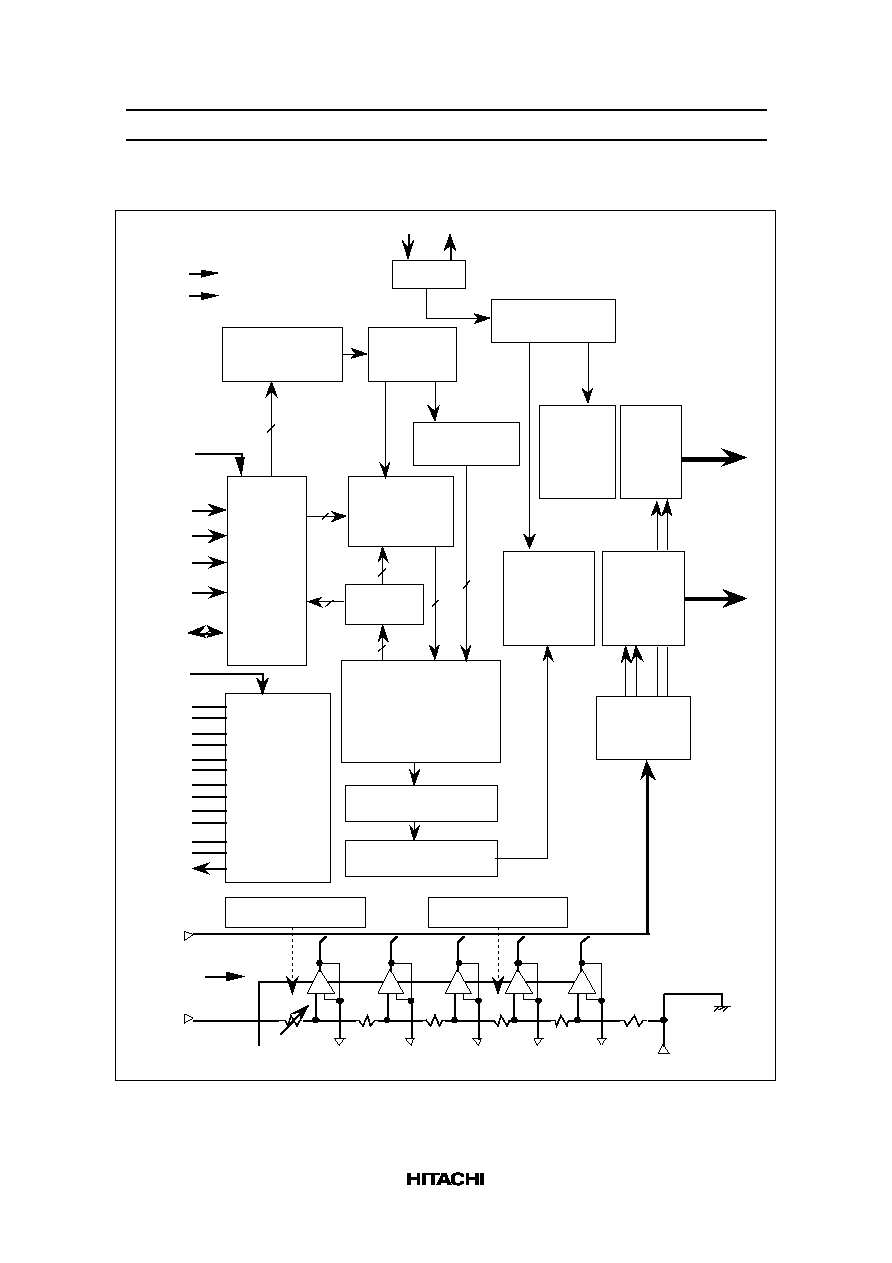

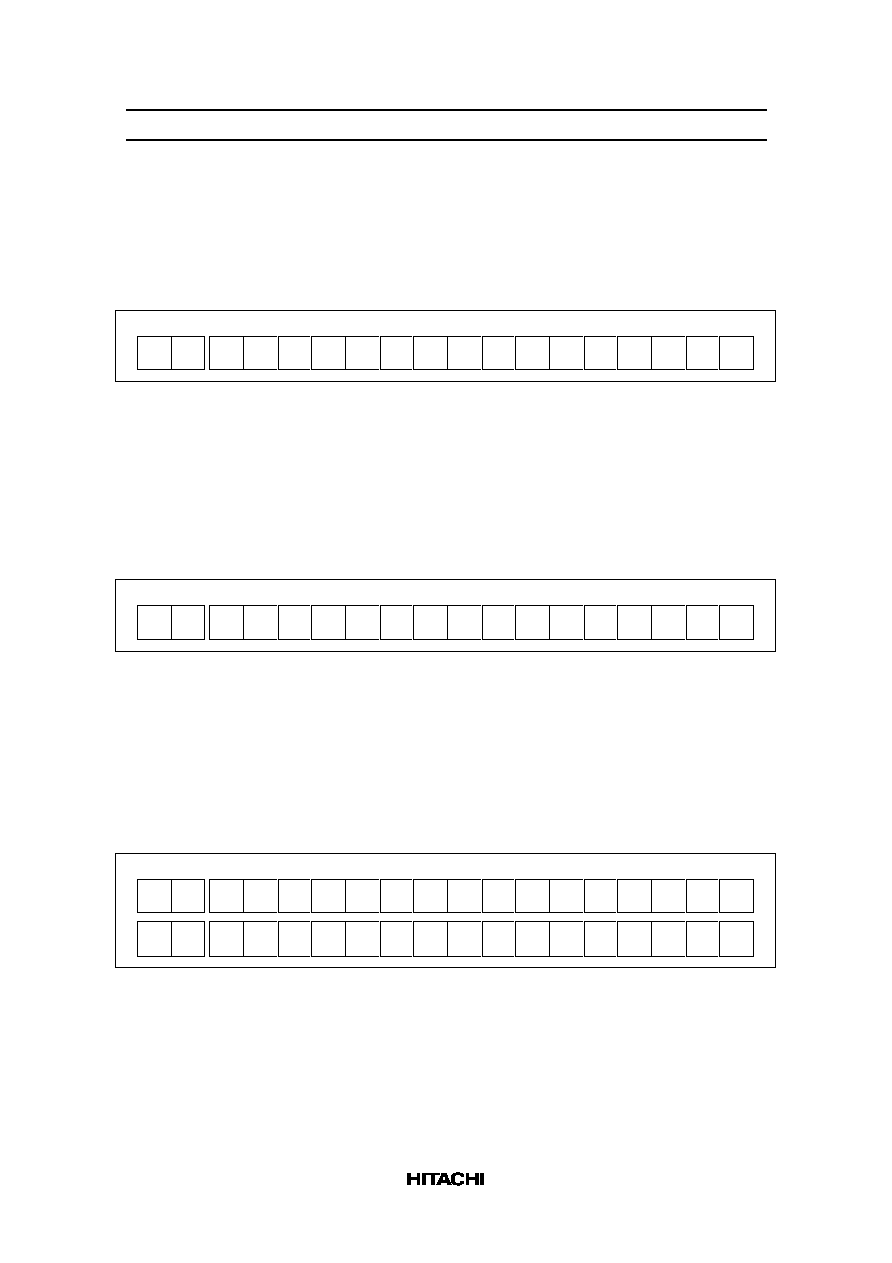

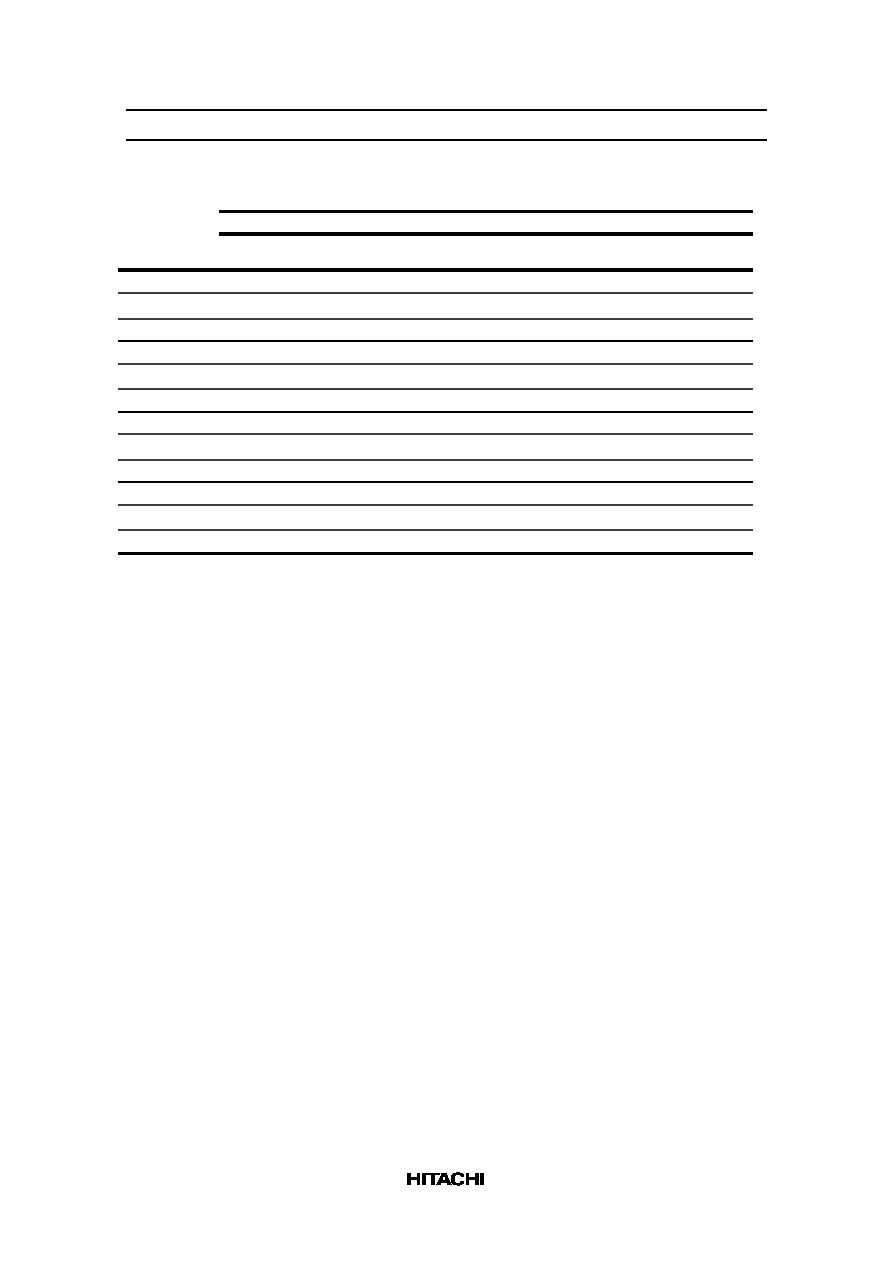

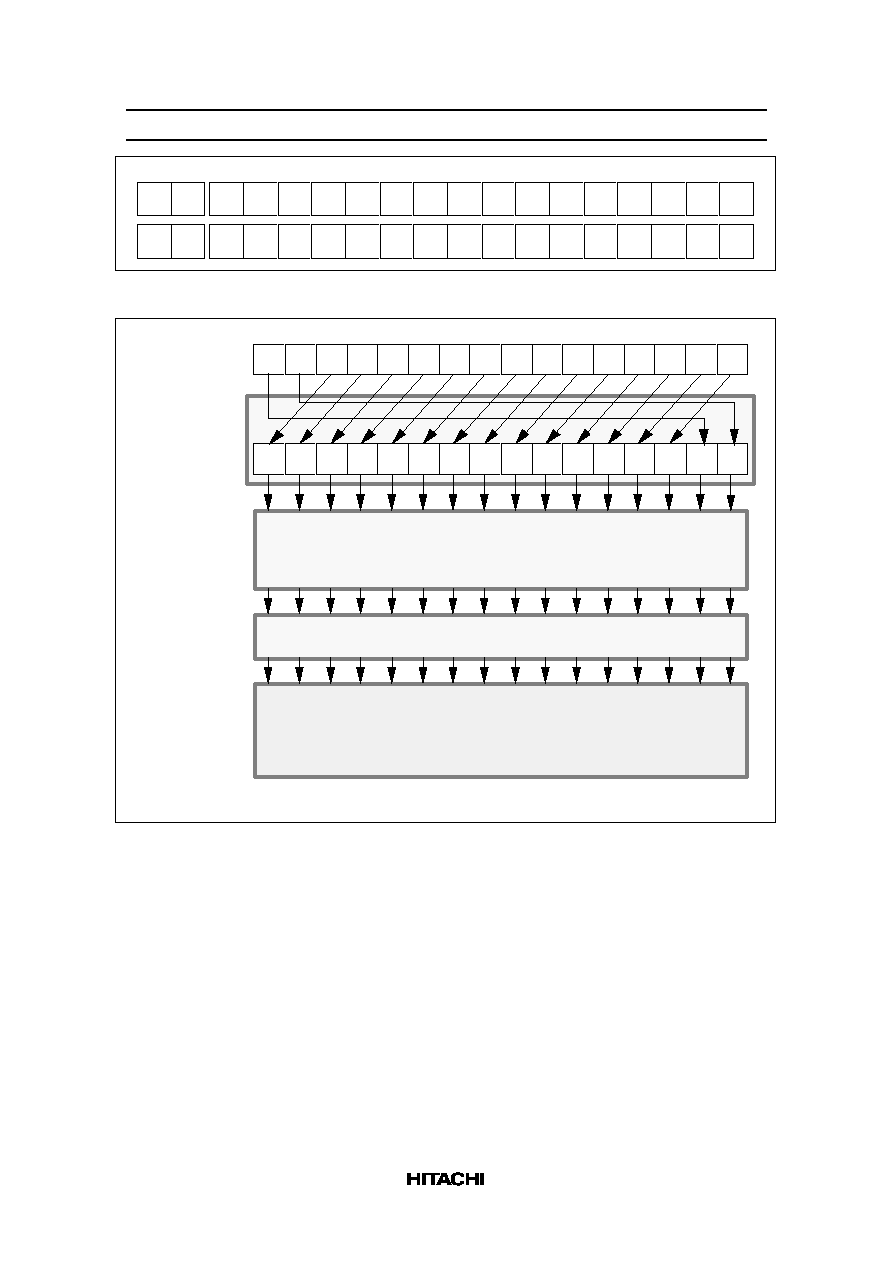

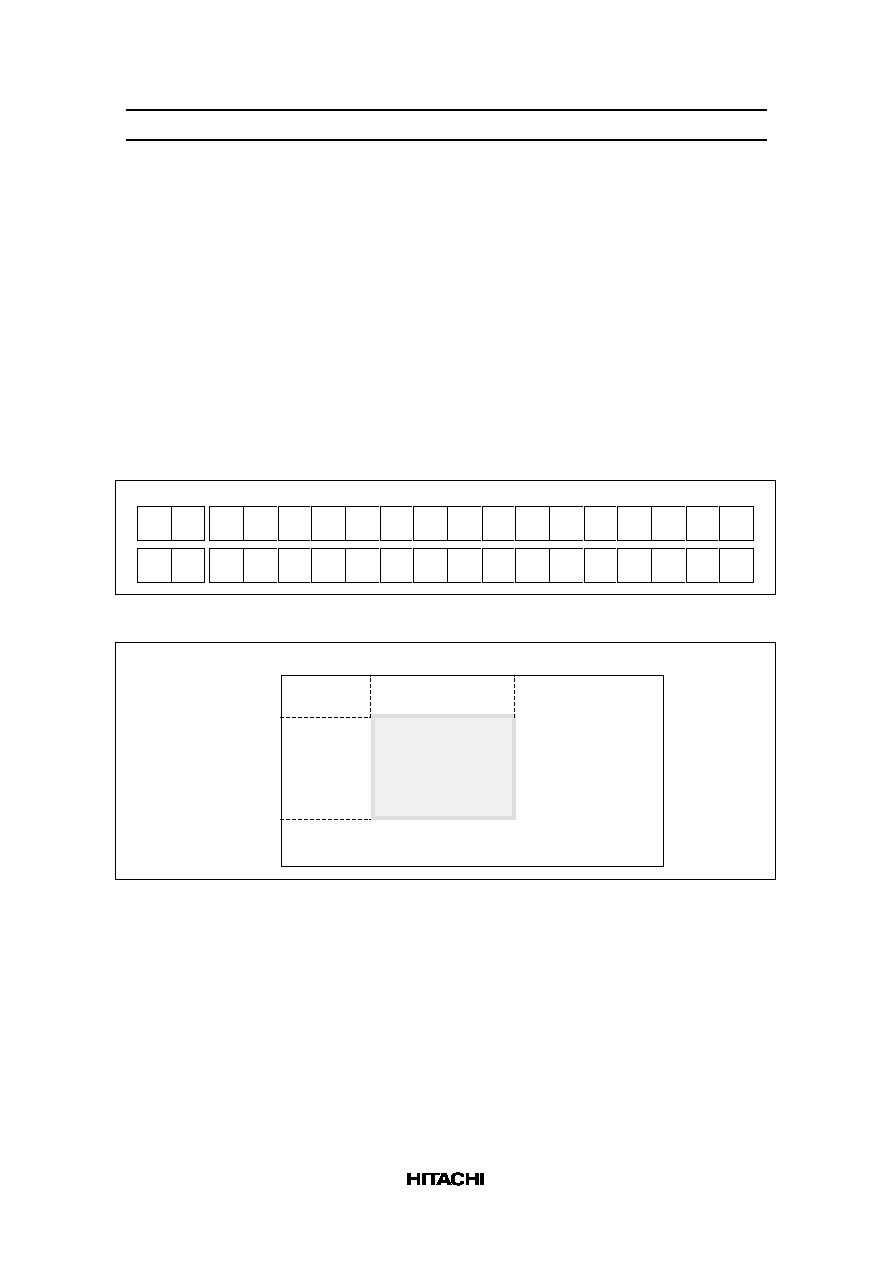

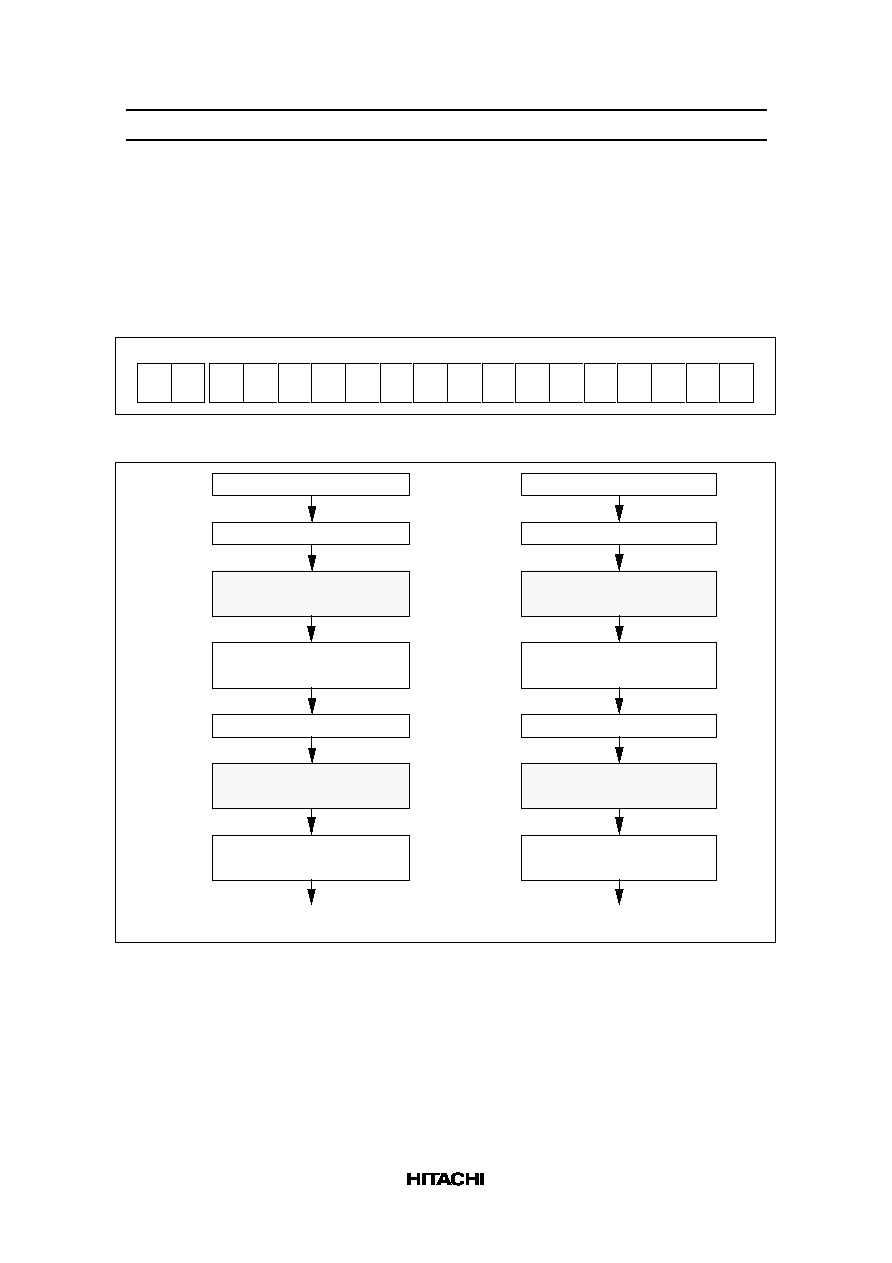

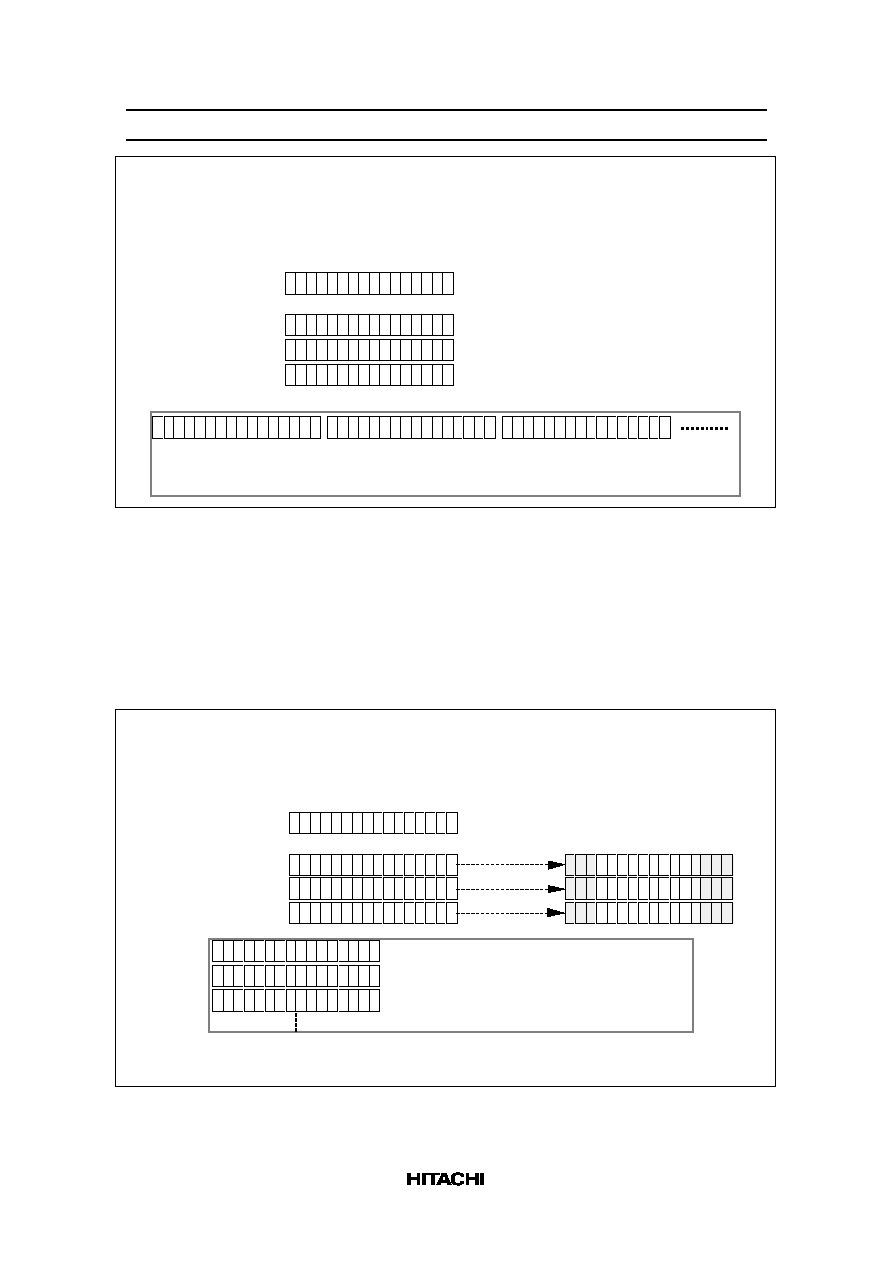

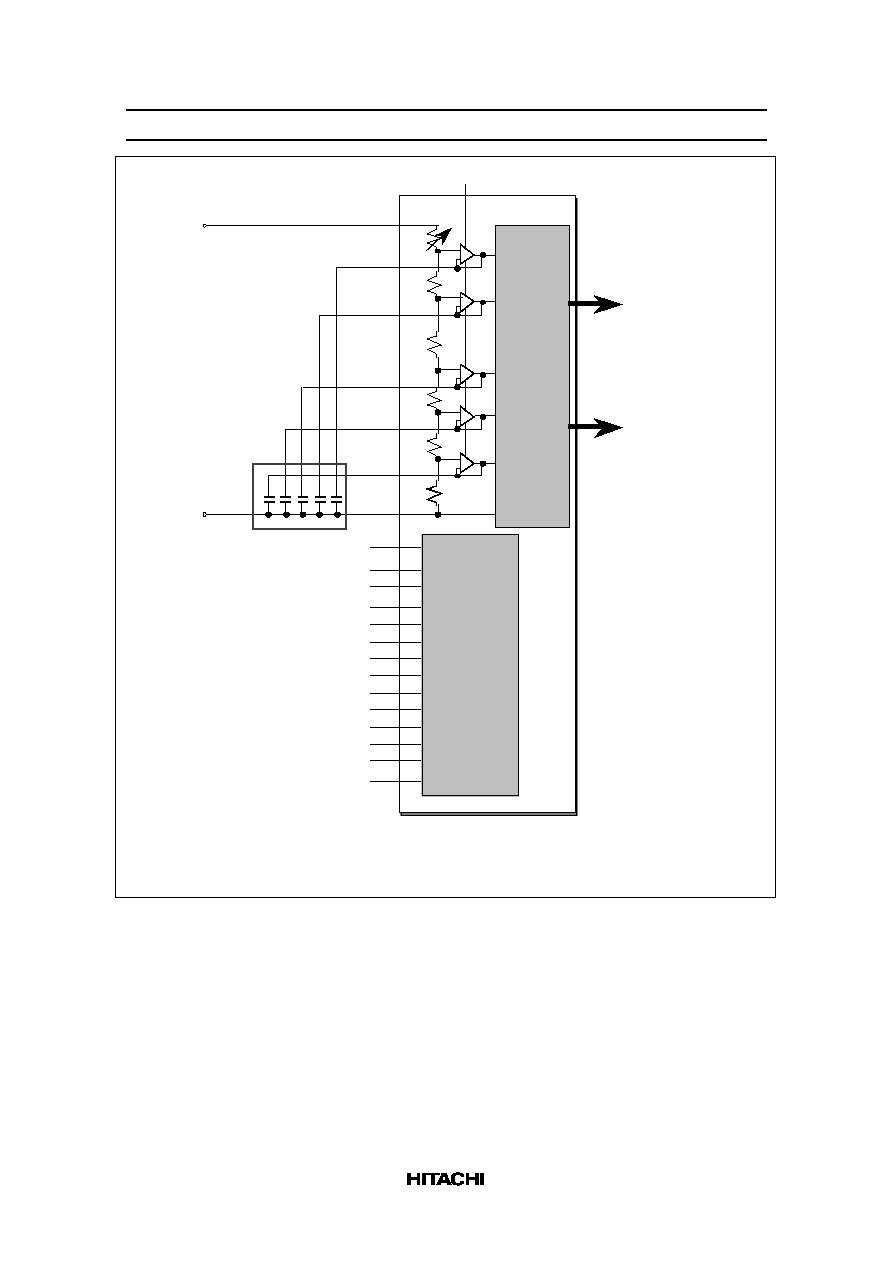

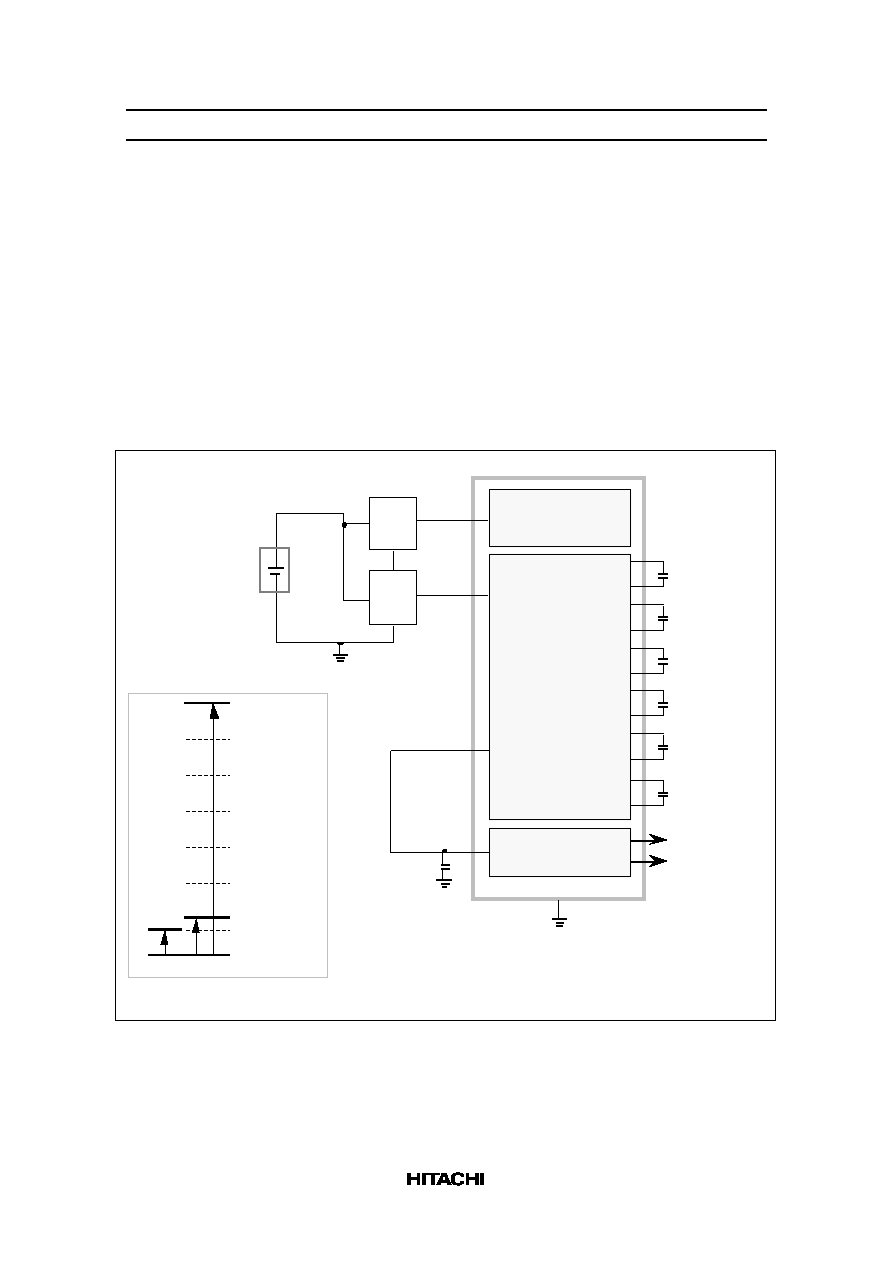

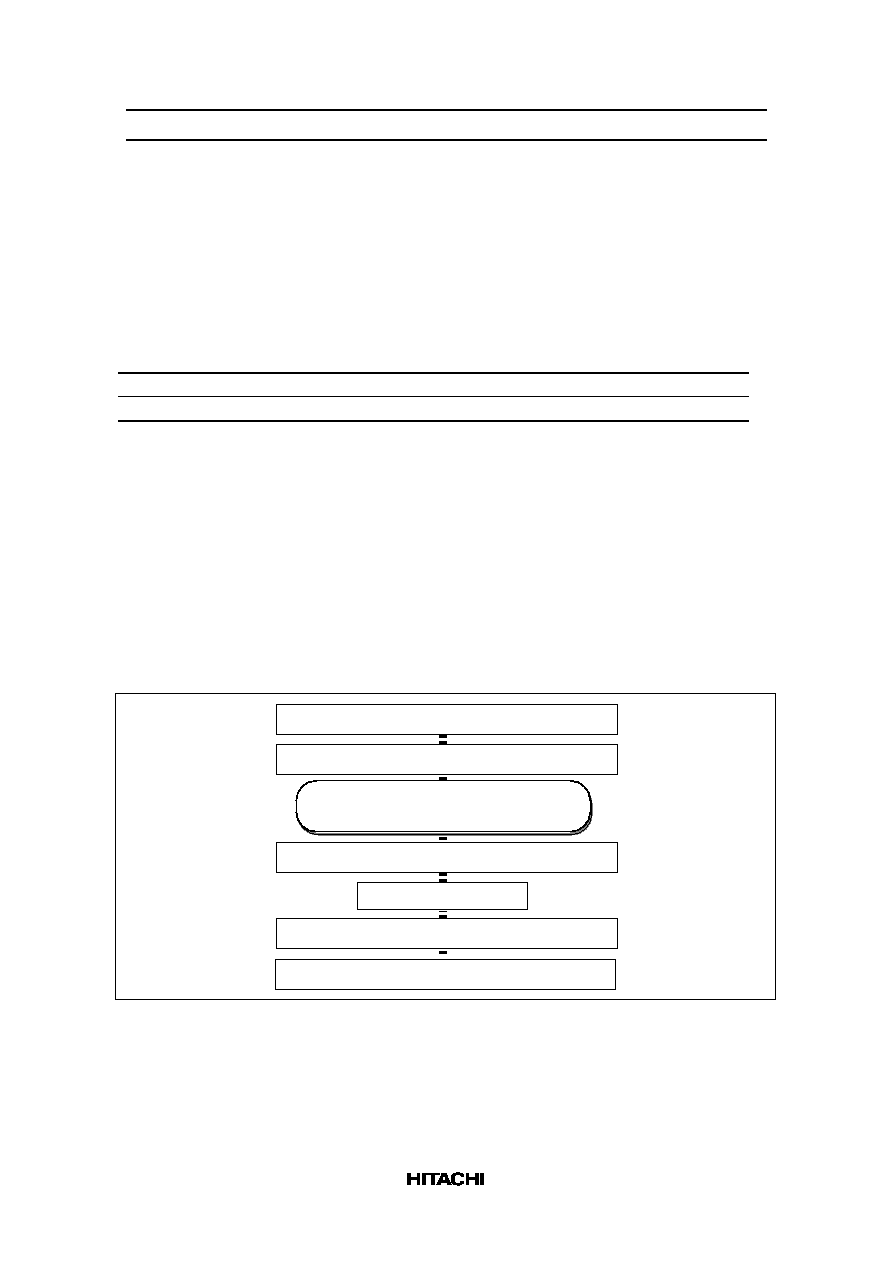

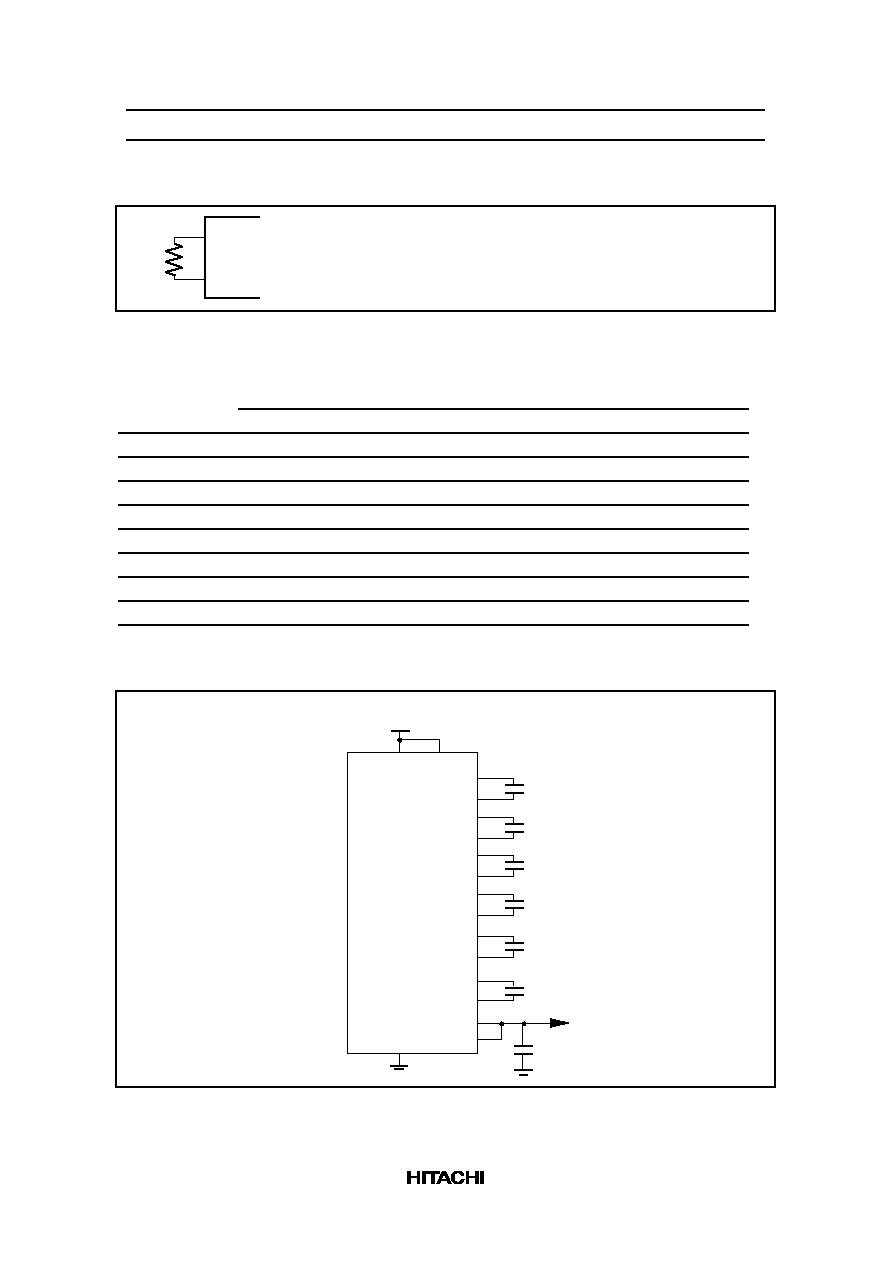

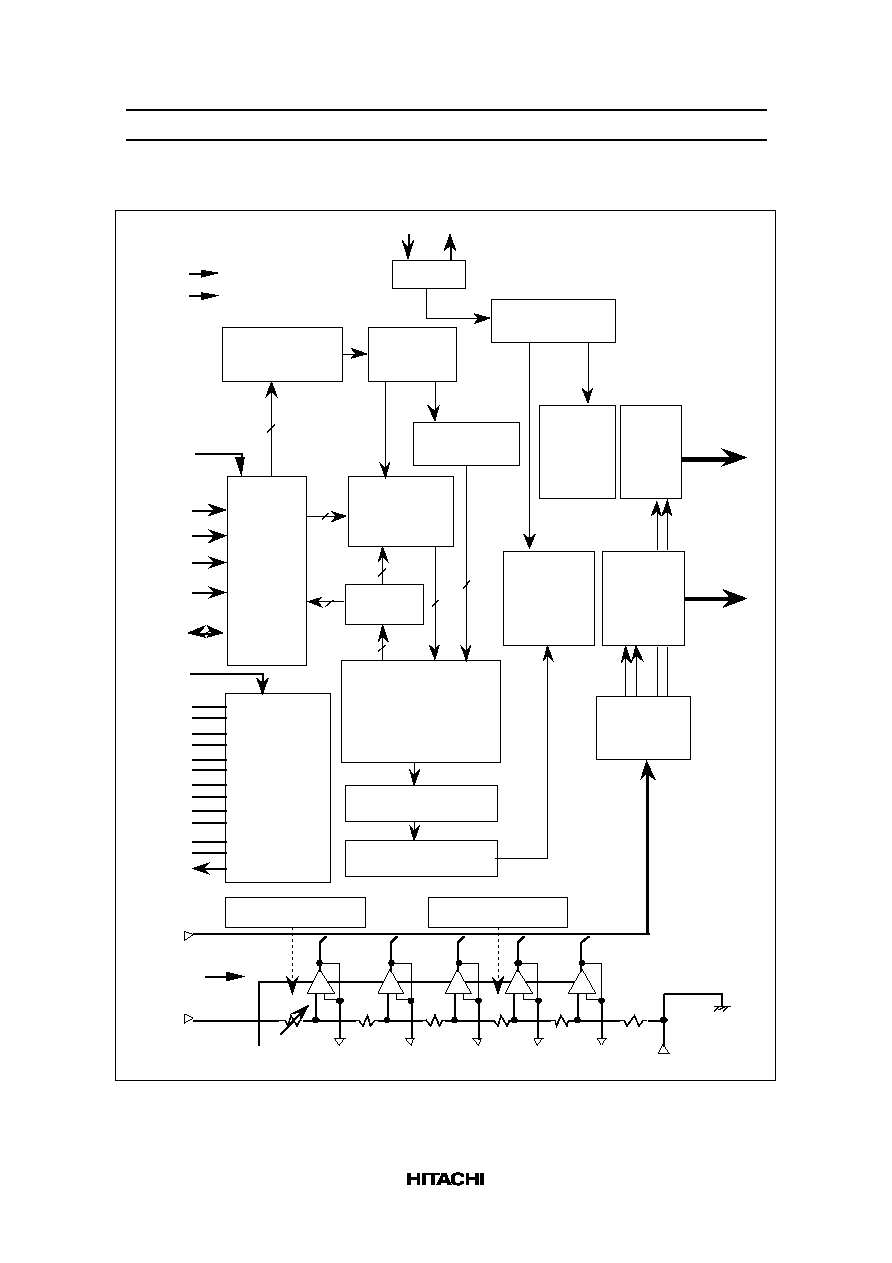

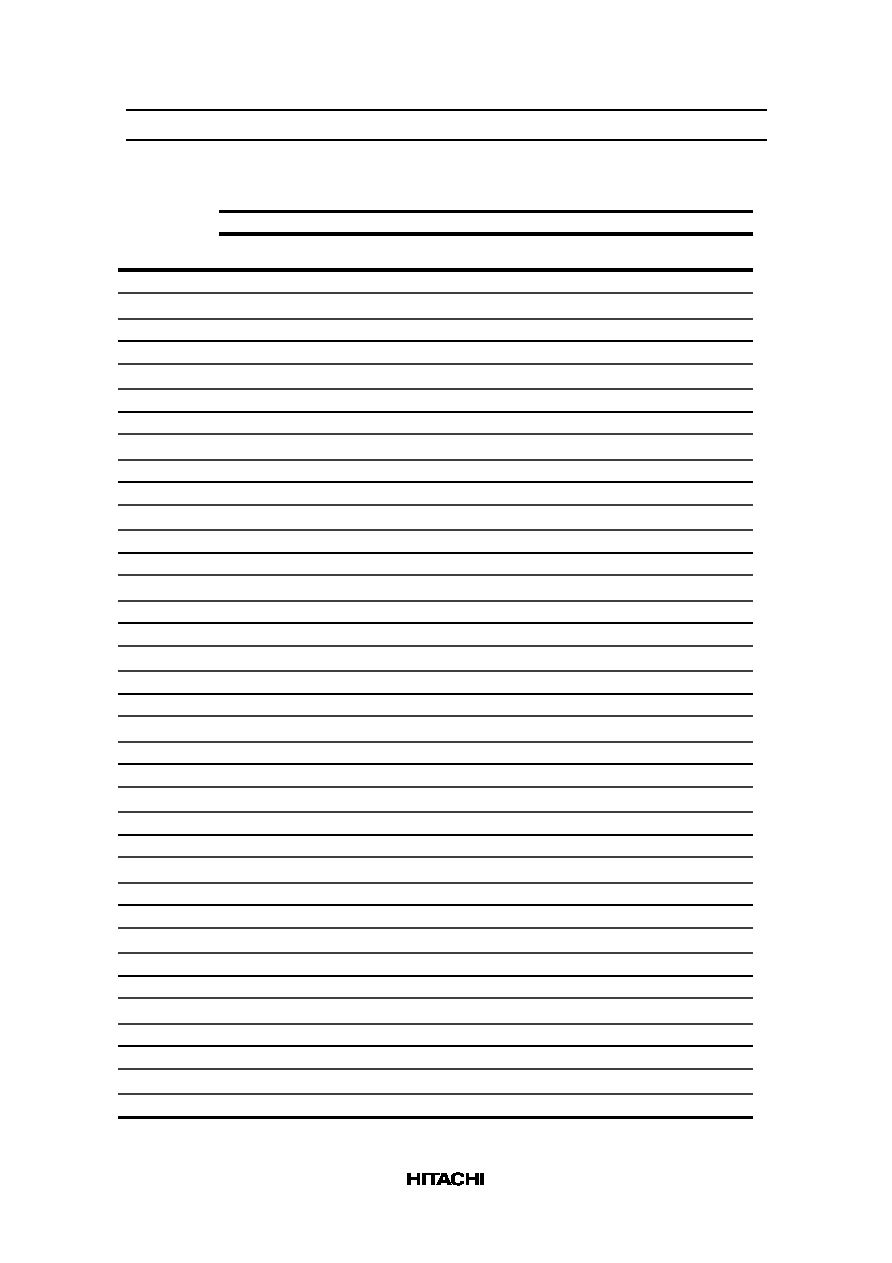

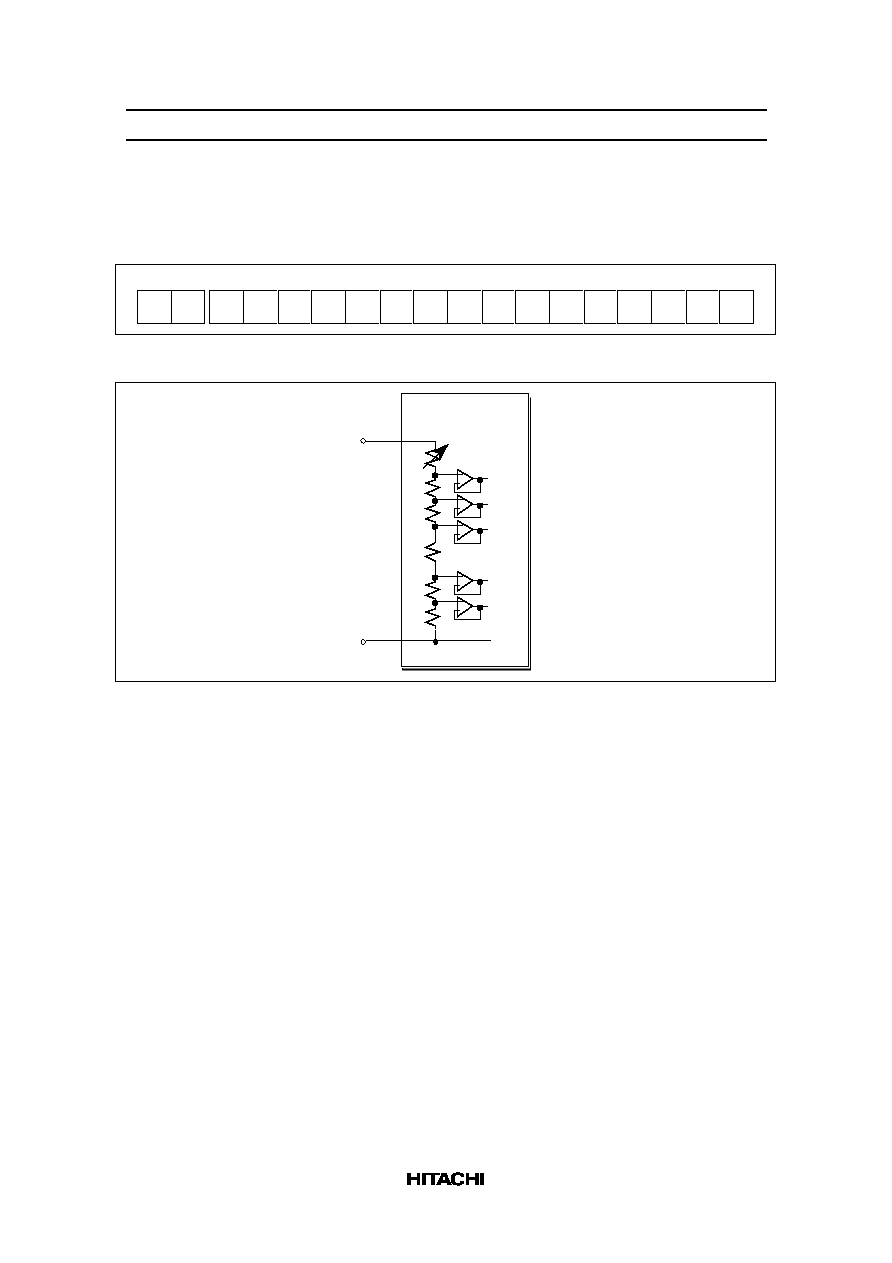

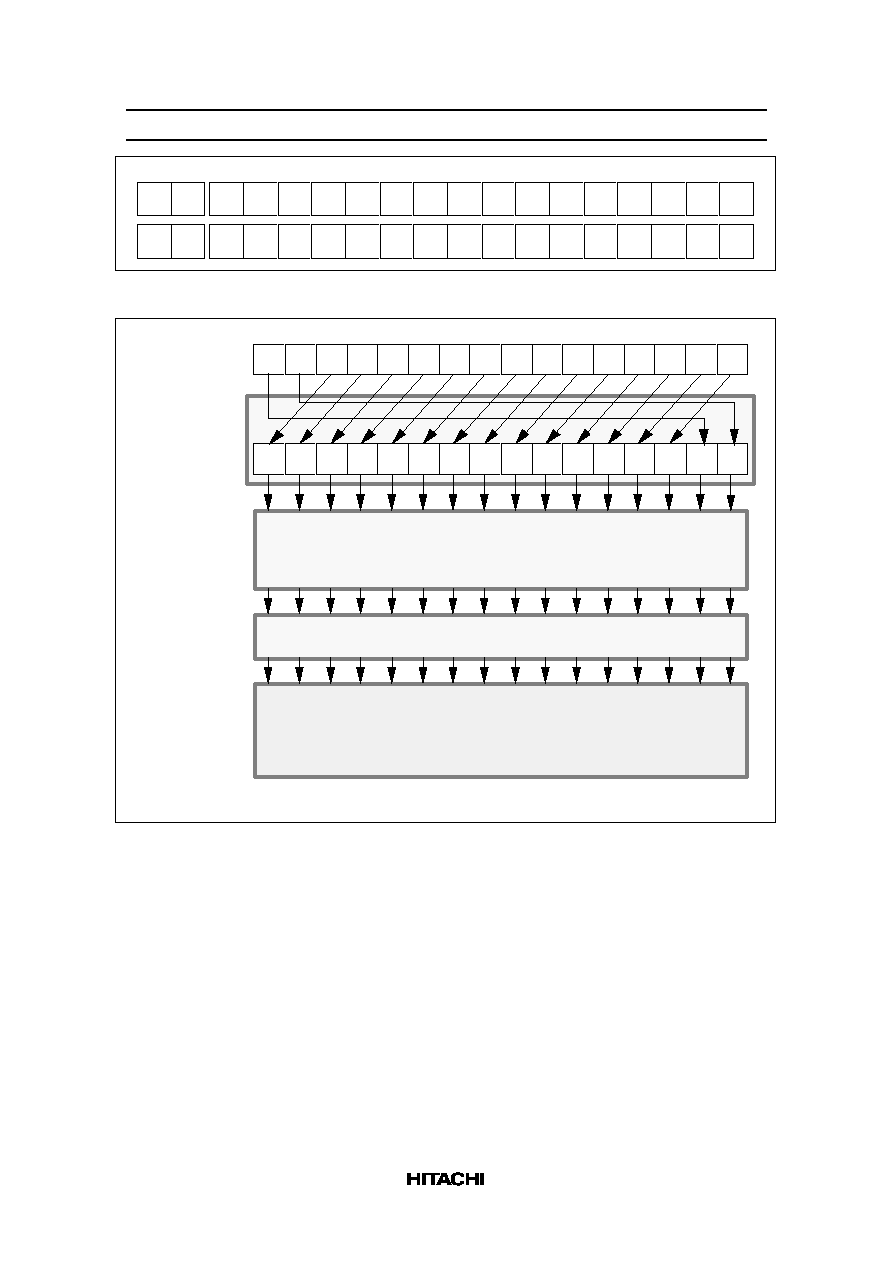

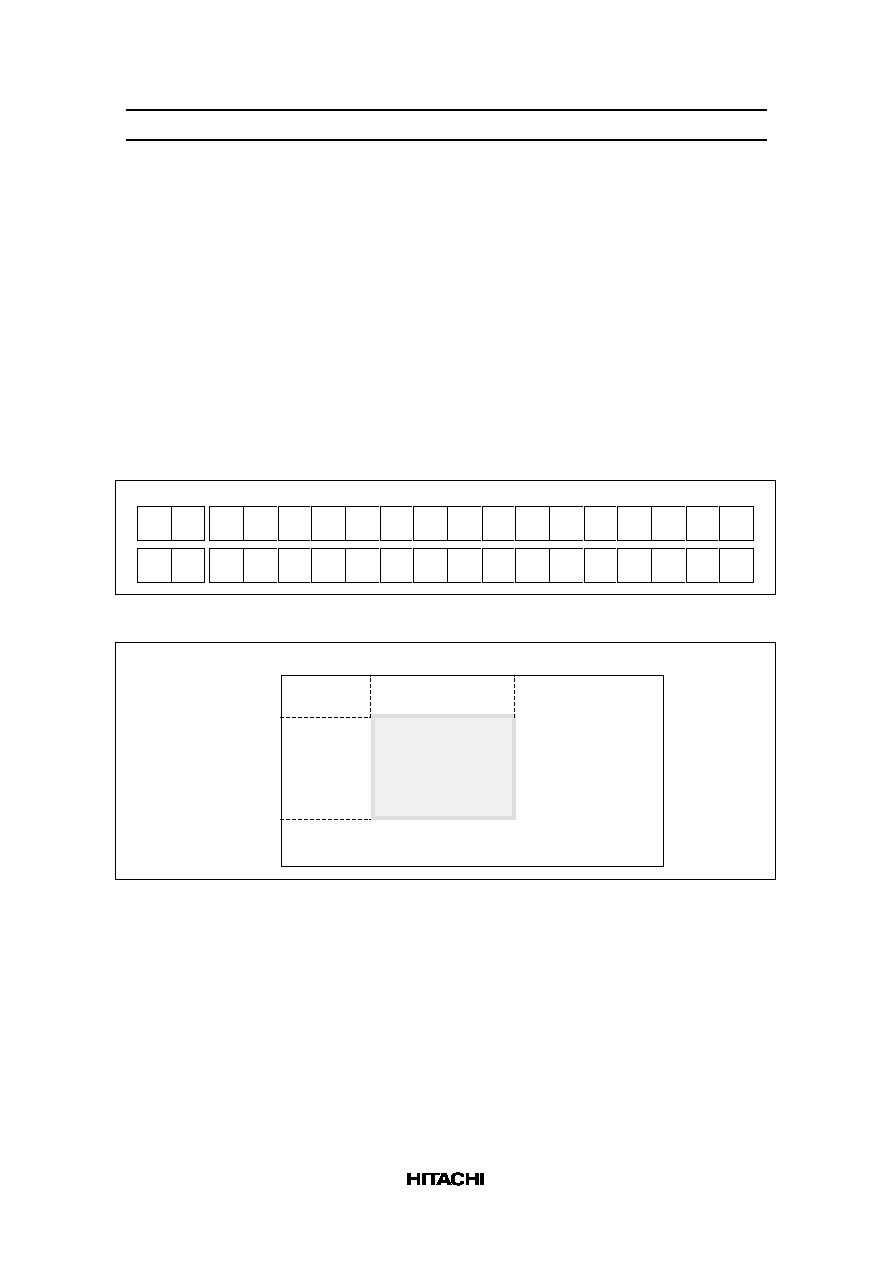

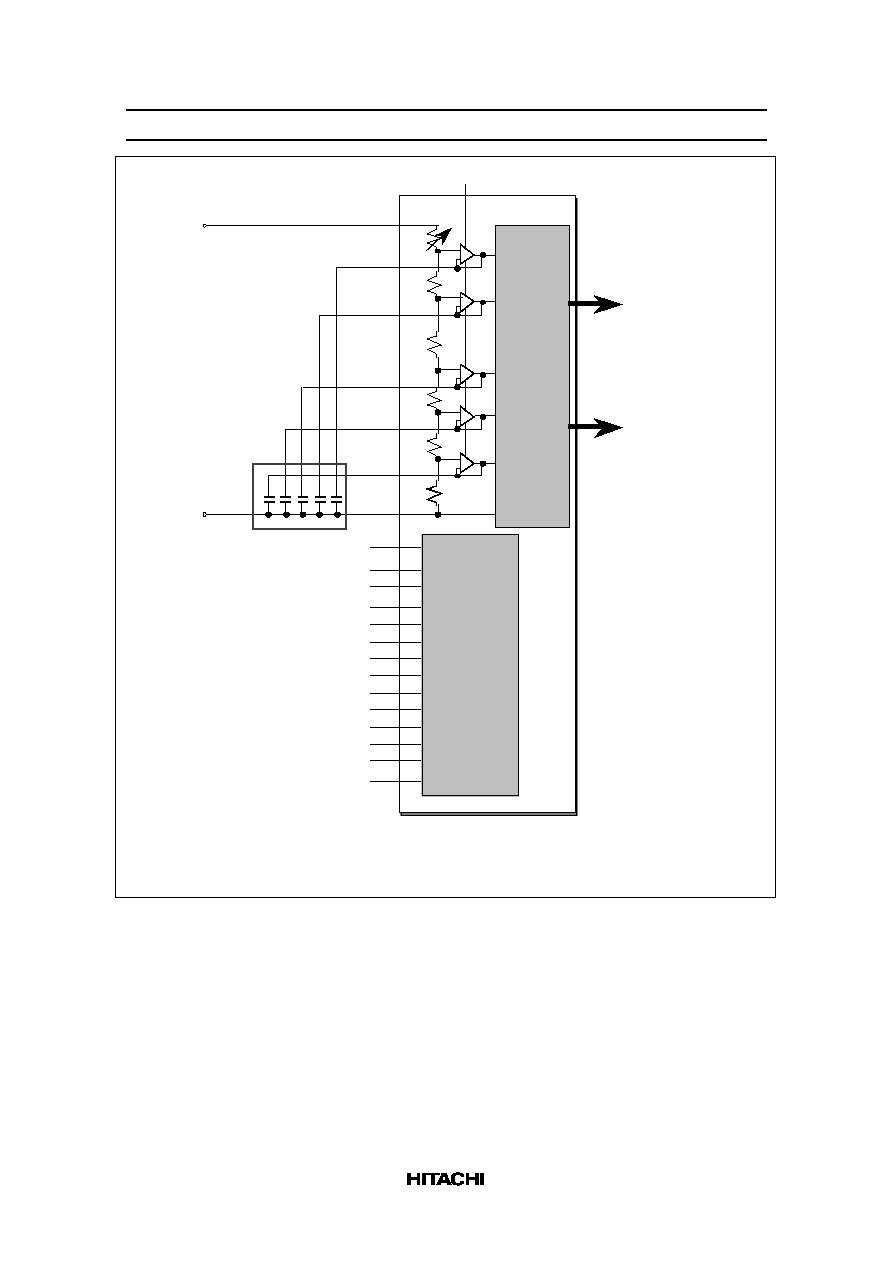

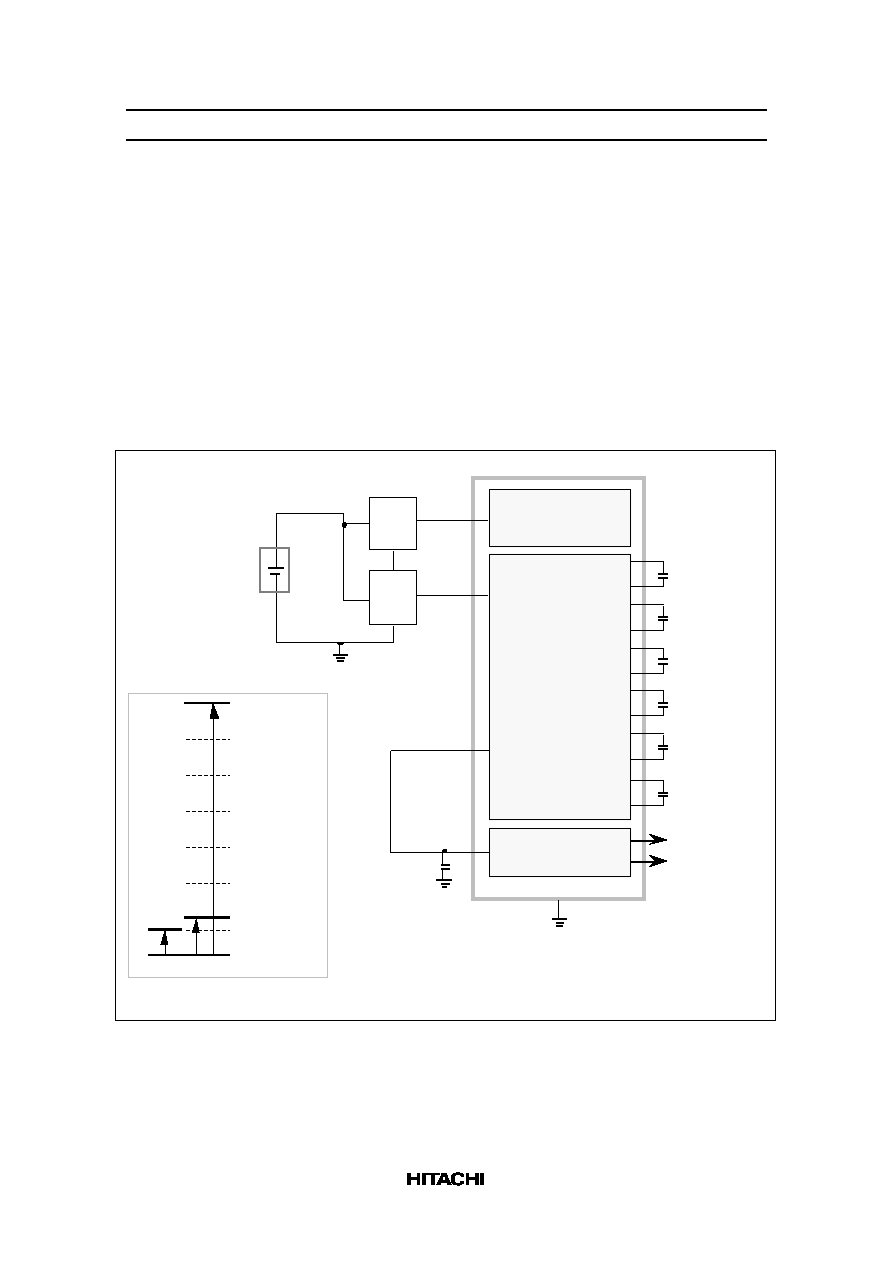

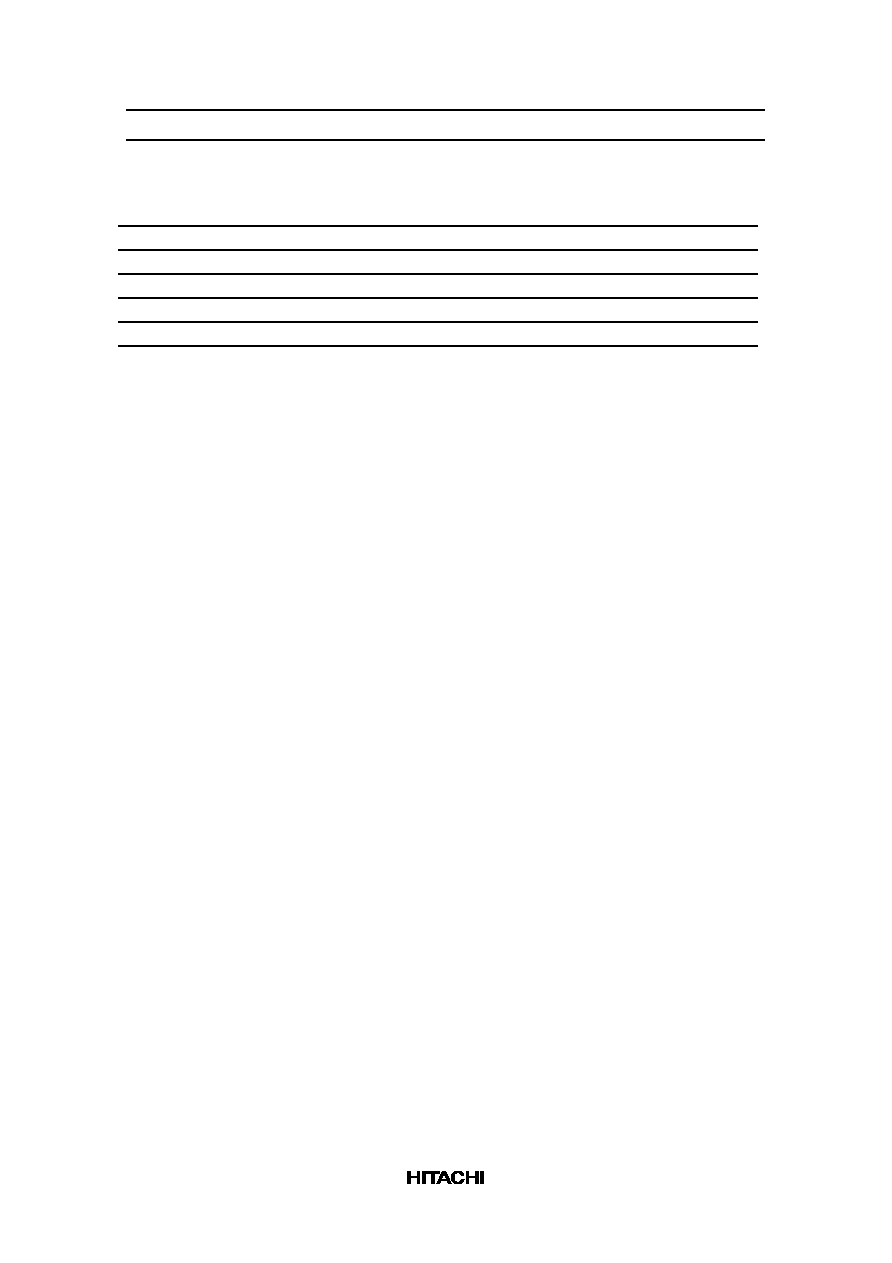

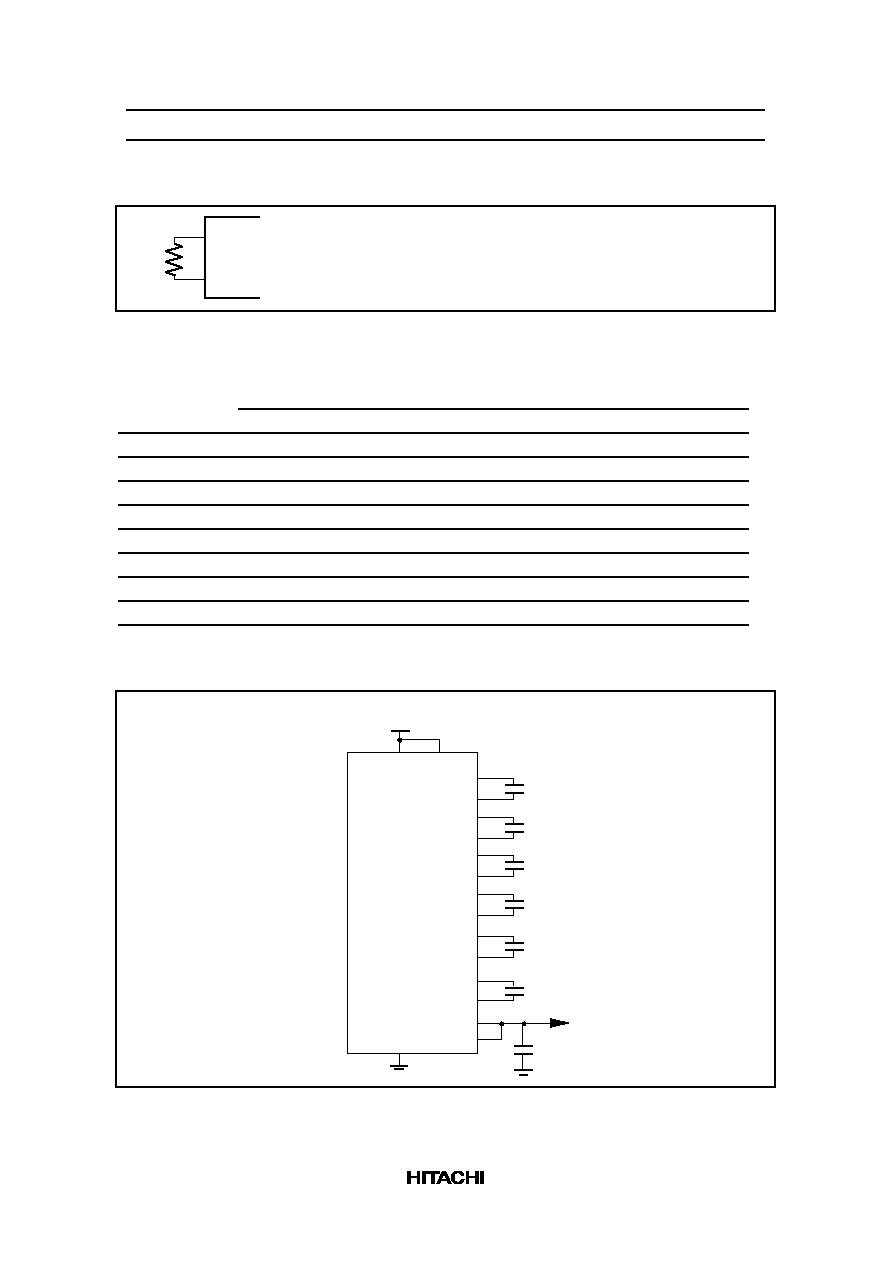

HD66750/1 Block Diagram

RS

RW/RD*

E/WR*

Vcc

V

LCD

16

12

16

Vci

C1+

IM1-0

C1-

+ -

+ -

+ -

+ -

VLOUT

+ -

GND

VR

R

R

R

0

R

R

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

OPOFF

DB0-DB15

VTEST

C2+

C2-

CS*

C3+

C3-

C4+

C4-

16

C5+

C5-

16

16

16

16

C6+

C6-

Instruction register

(IR)

Timing generator

CPG

Instruction

decoder

OSC1

OSC2

RESET*

TEST

System

interface

• 16-bit bus

• 8-bit bus

Address counter

(AC)

Graphic RAM

(CGRAM)

4,096 bytes

128-bit latch

circuit

128-bit

bidirectional

common shift

register

Common

driver

Segment

driver

LCD drive

voltage selector

COM1/128–

COM128/1

SEG1/128-

SEG128/1

Two-, five-,

six-, and

seven-times

booster

Contrast adjuster

Drive bias controller

Window cursor control

Four grayscale control

circuit

Read data

latch

Bit operation

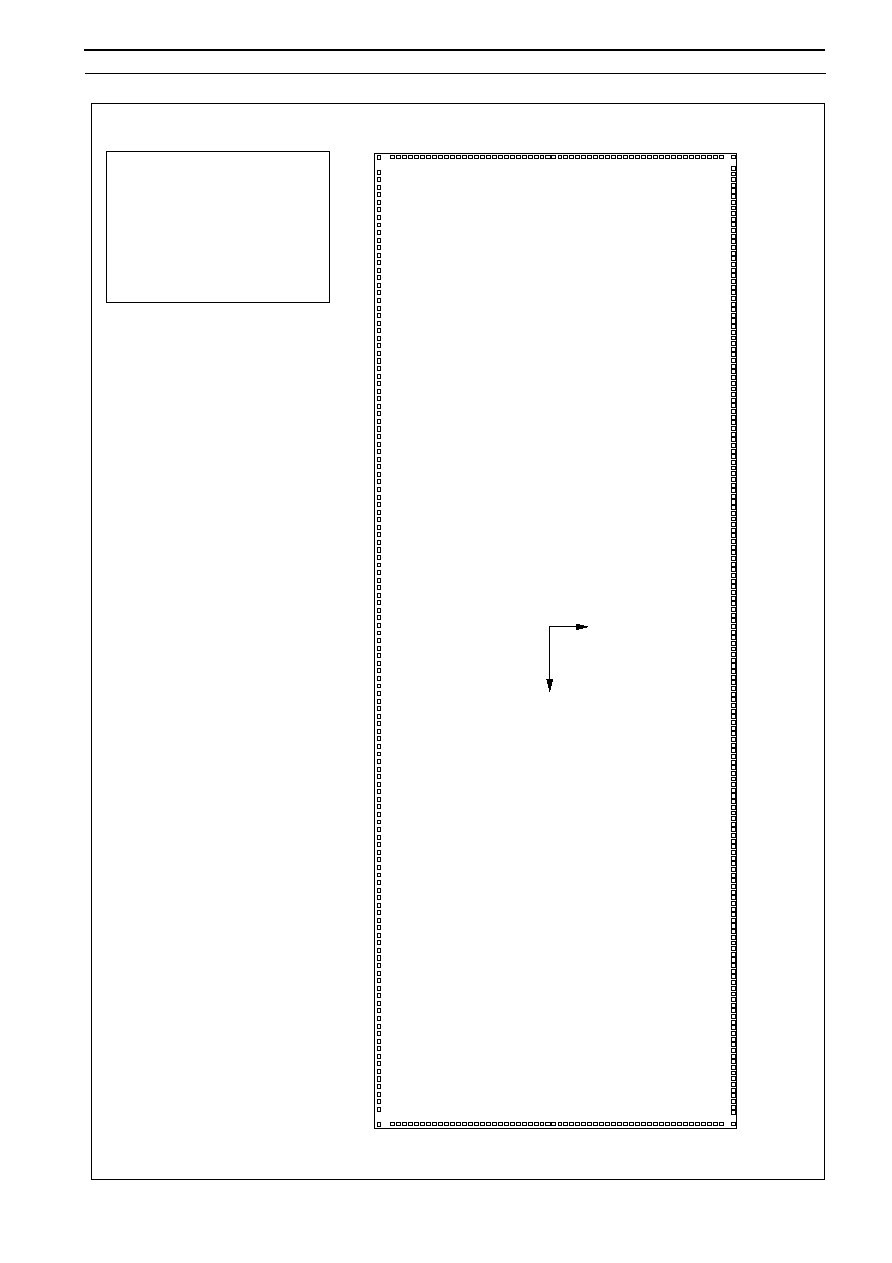

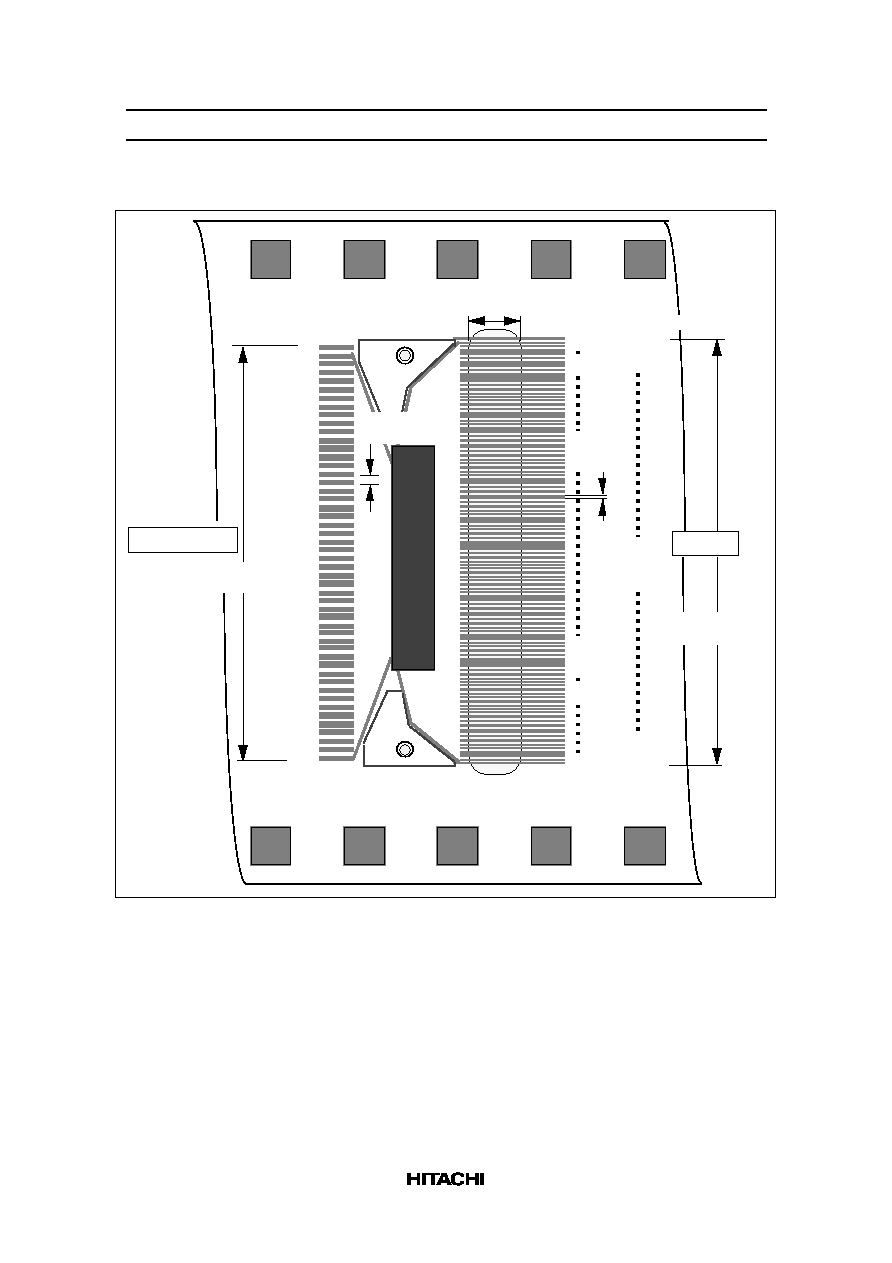

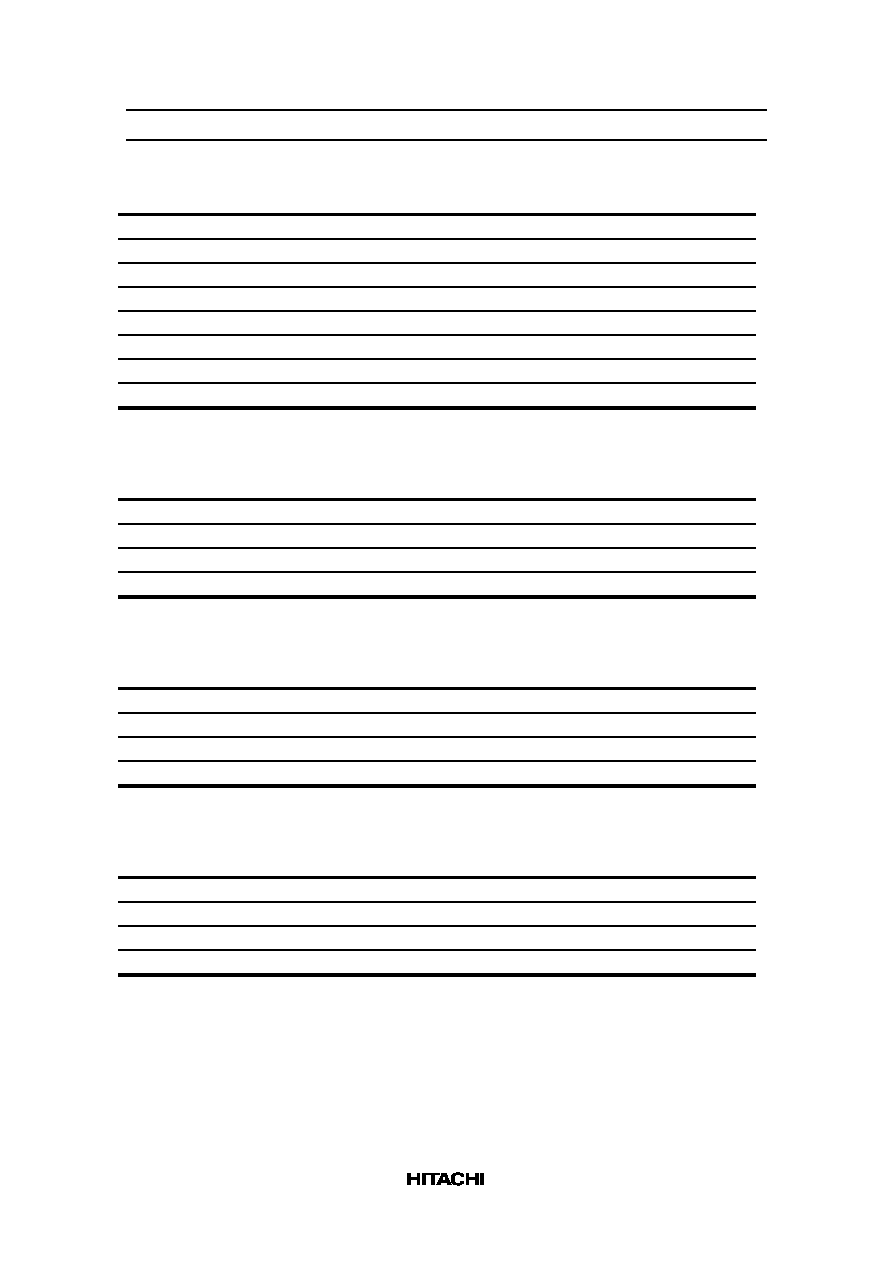

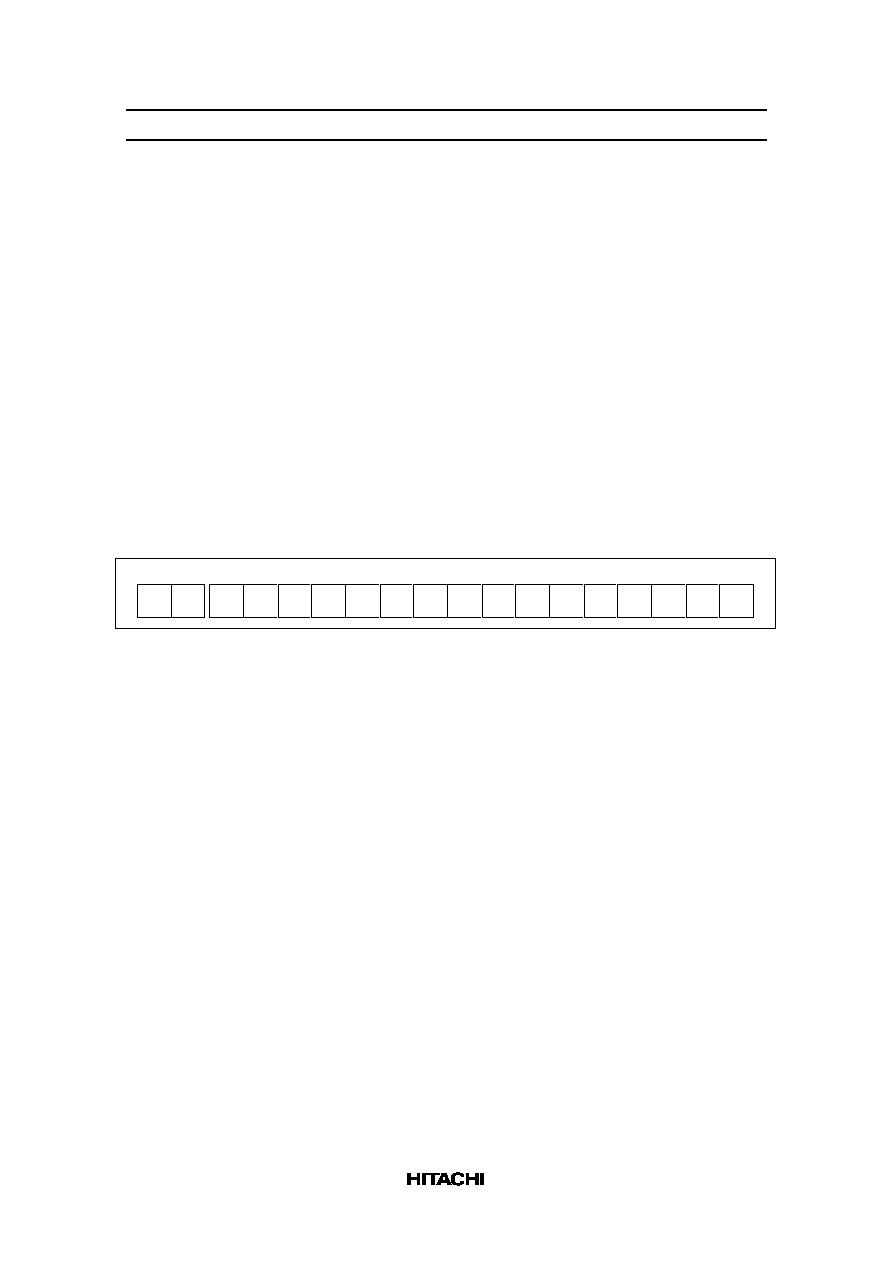

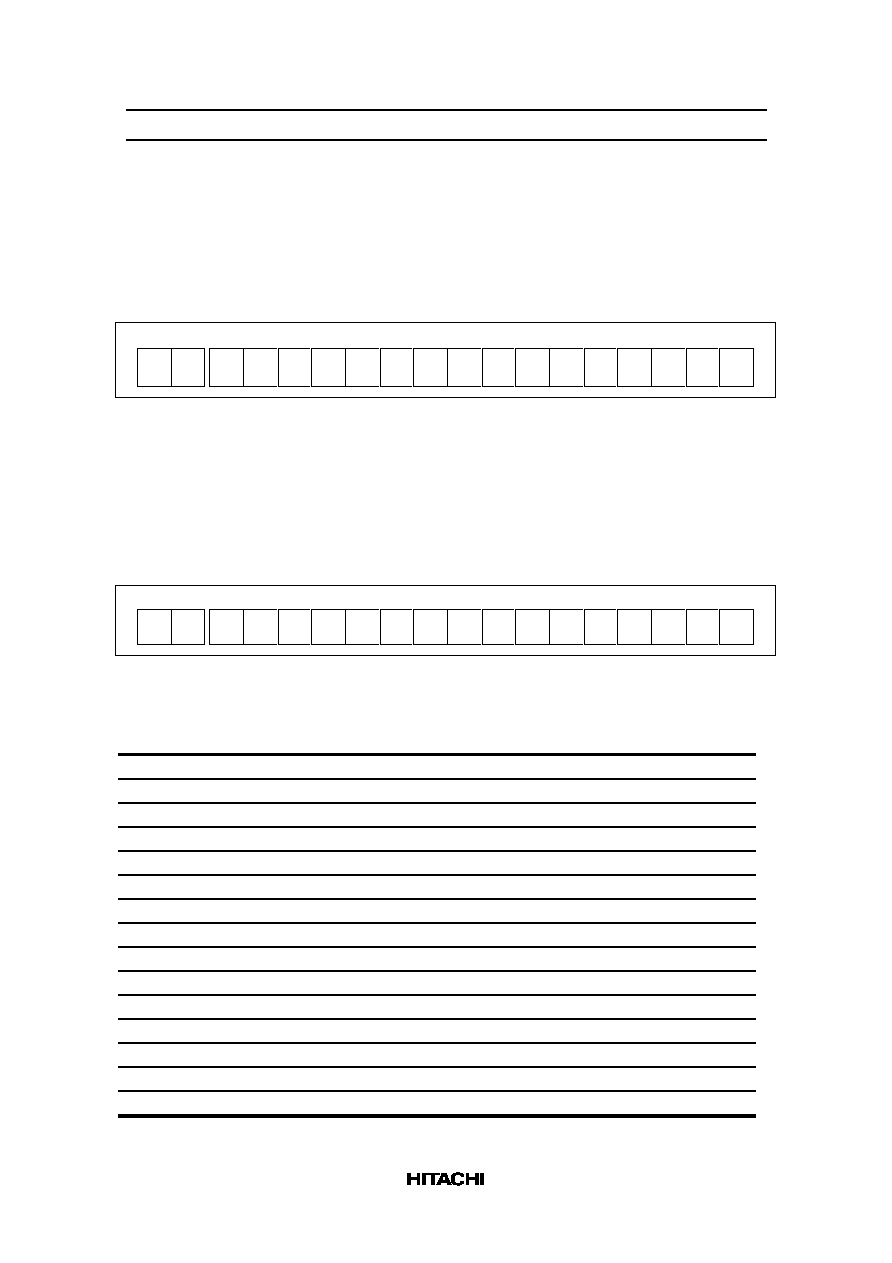

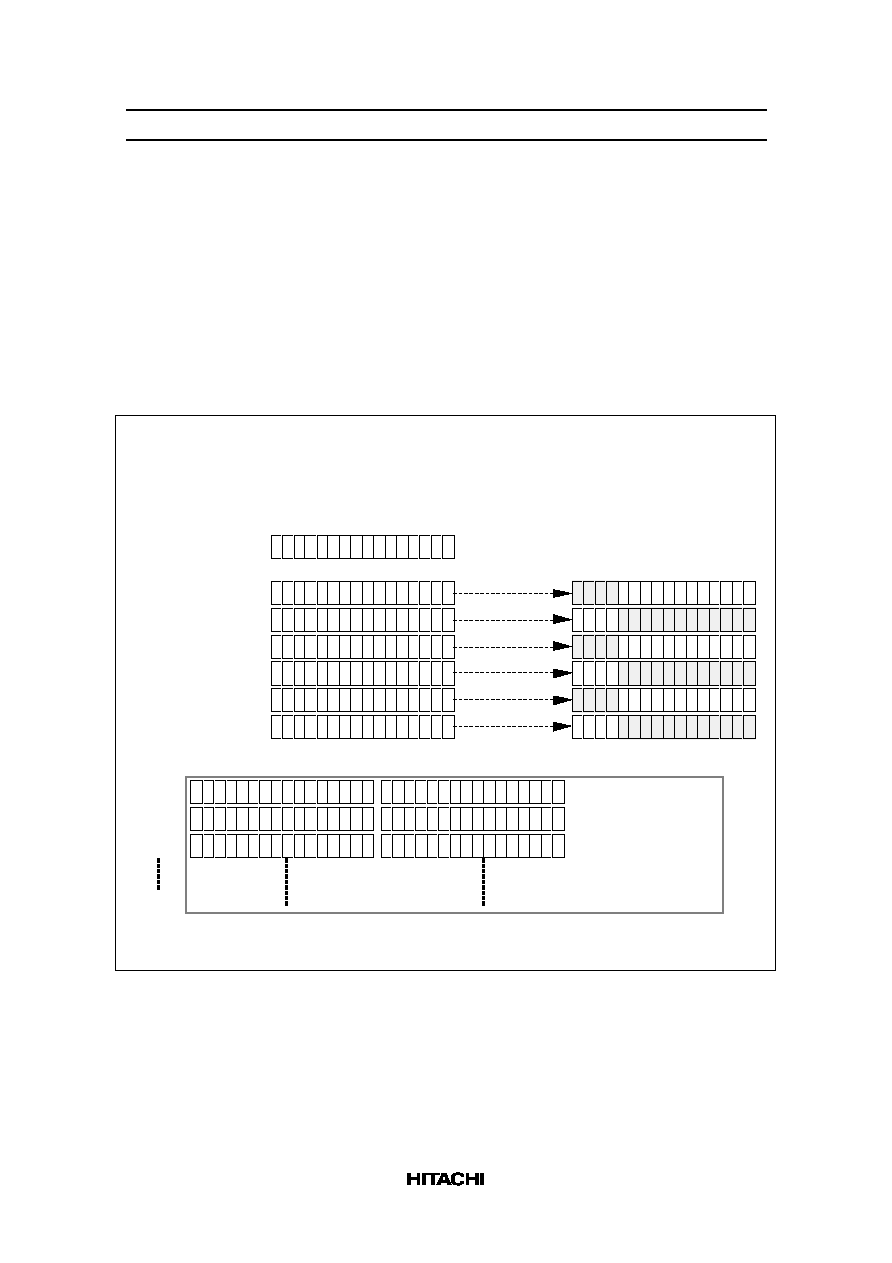

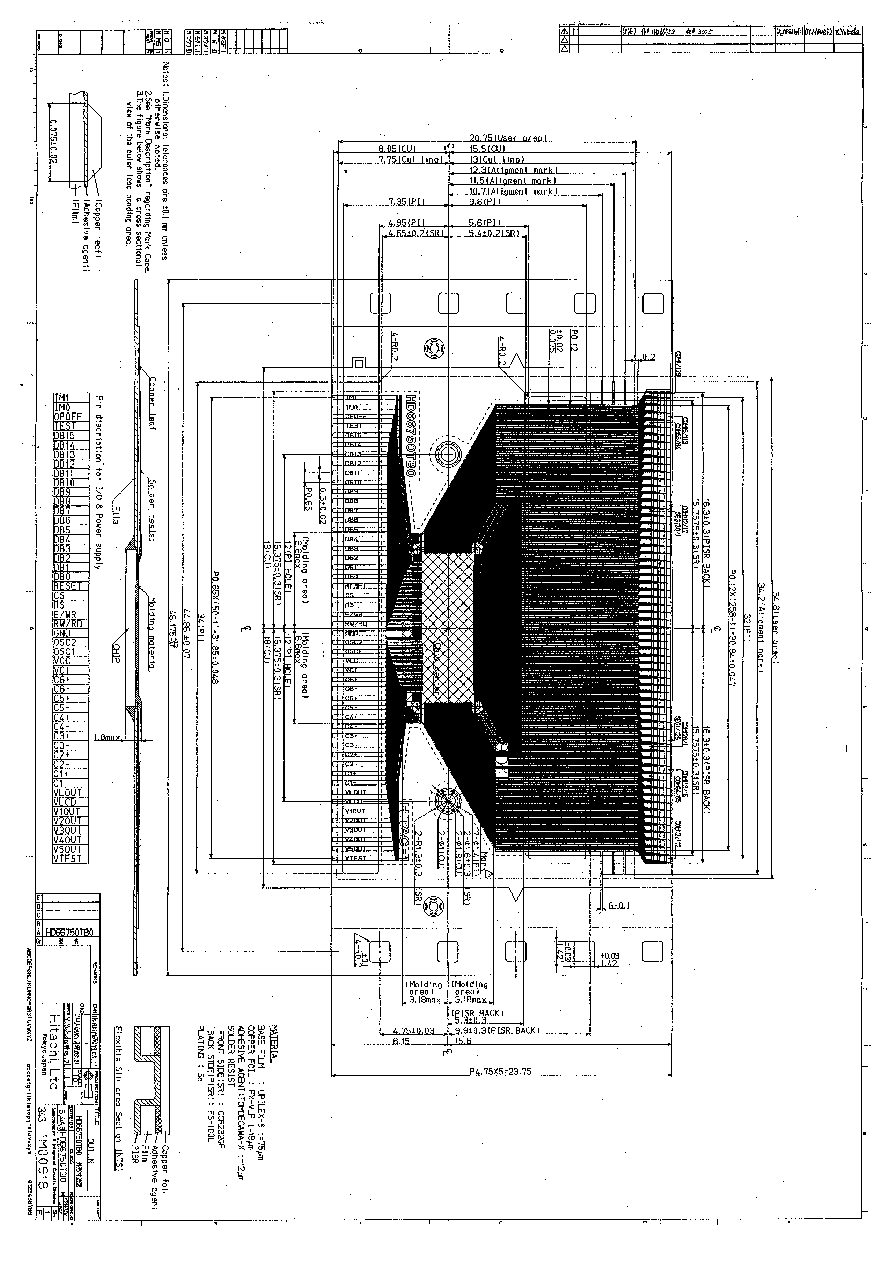

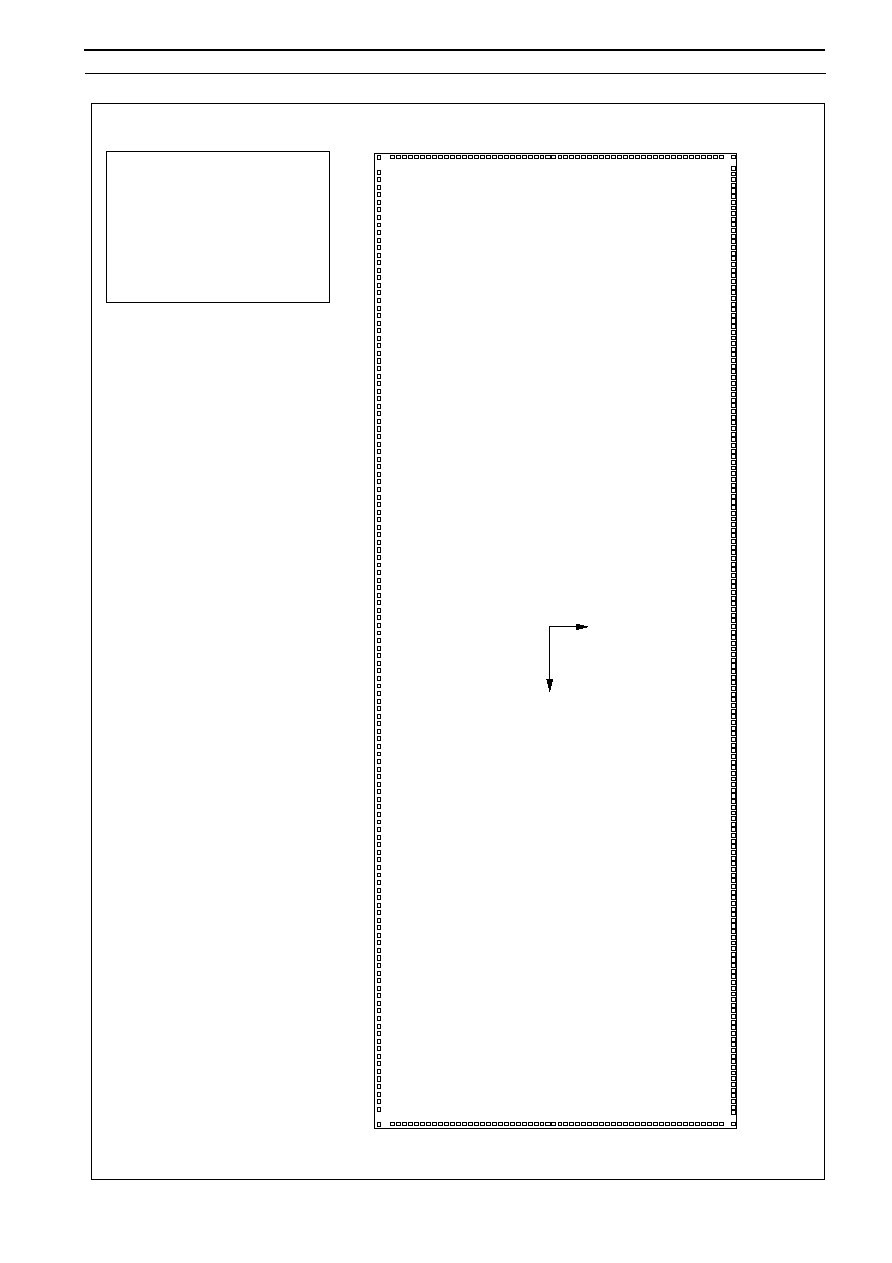

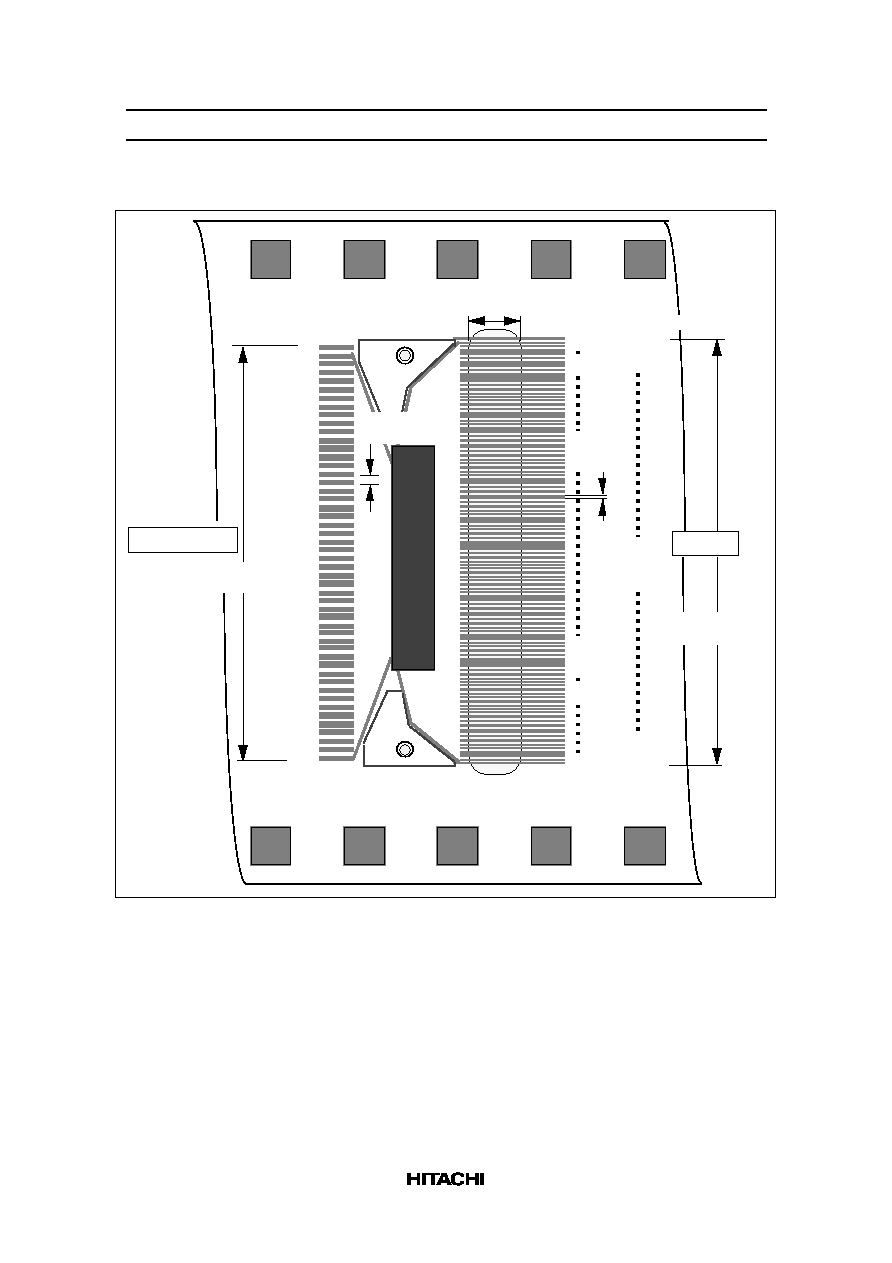

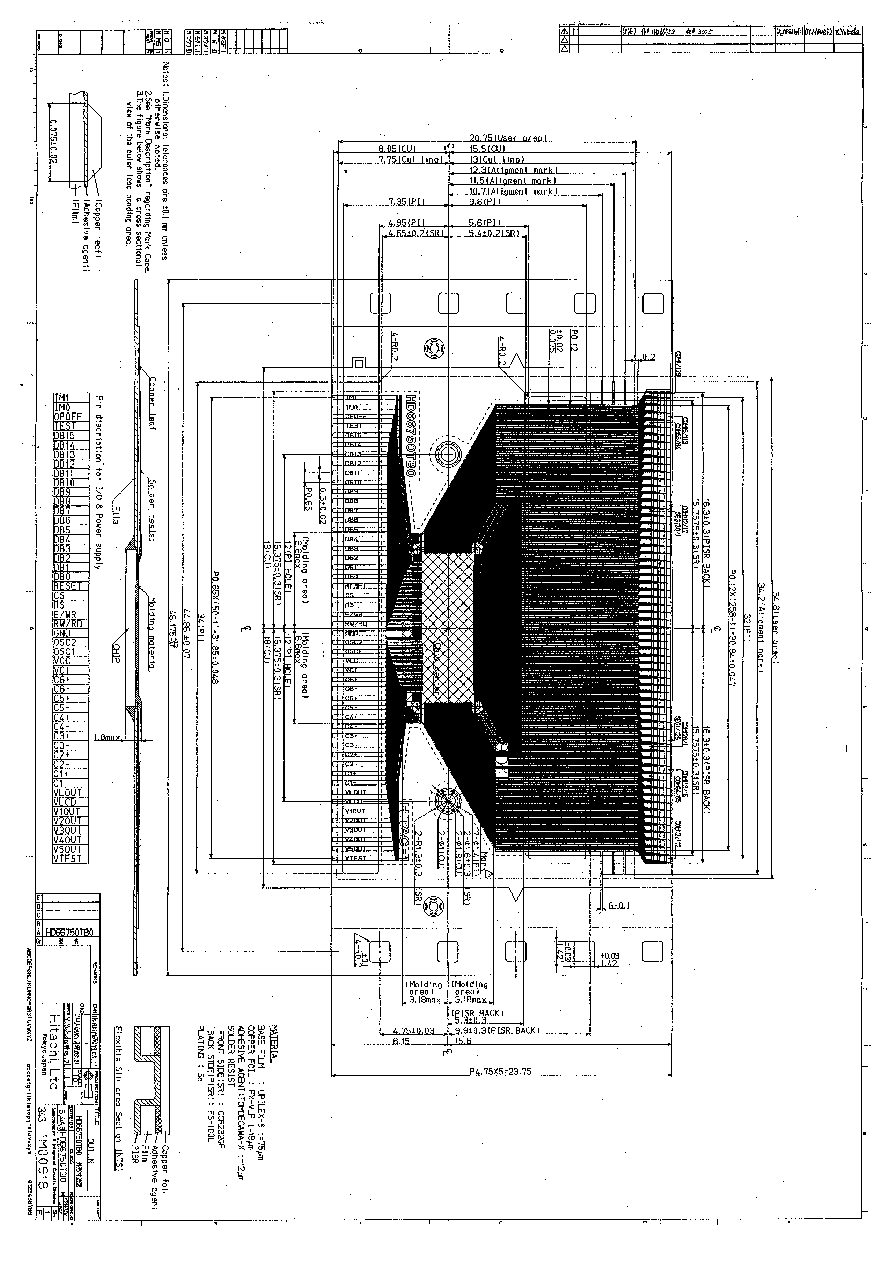

• Chip size: 10.97 mm X 4.13 mm

• Pad coordinates: Pad center

• Coordinate origin: Chip center

• Au bump size: 40

µ

m x 90

µ

m

Chip corner bump size : 90

µ

m x 90

µ

m

(Dummy1, Dummy22, Dummy23 and Dummy 48)

• Au bump pitch: 60

µ

m (min.)

• Au bump height: 20

µ

m (typ.)

(Top view)

HD66750

Y

X

HD66750/1

HITACHI

9

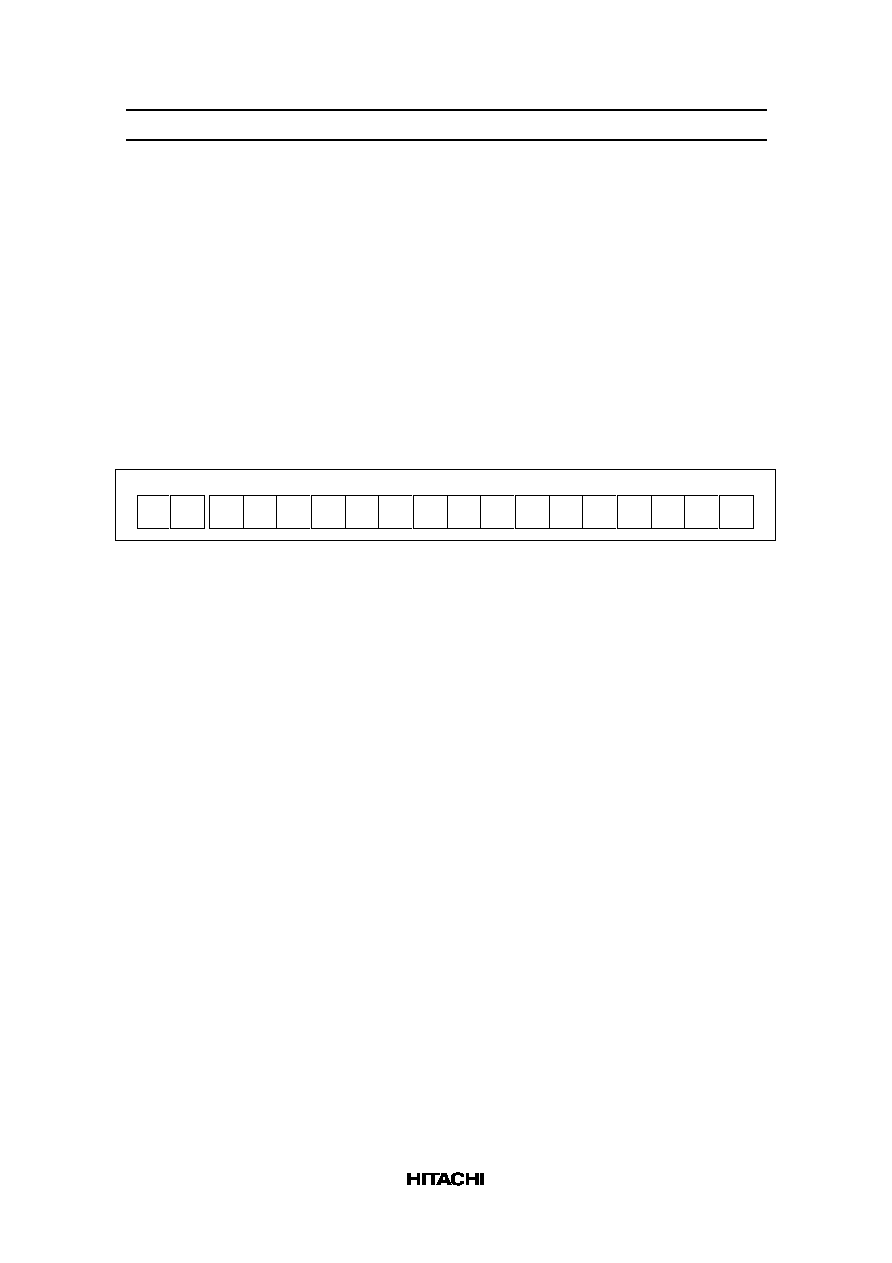

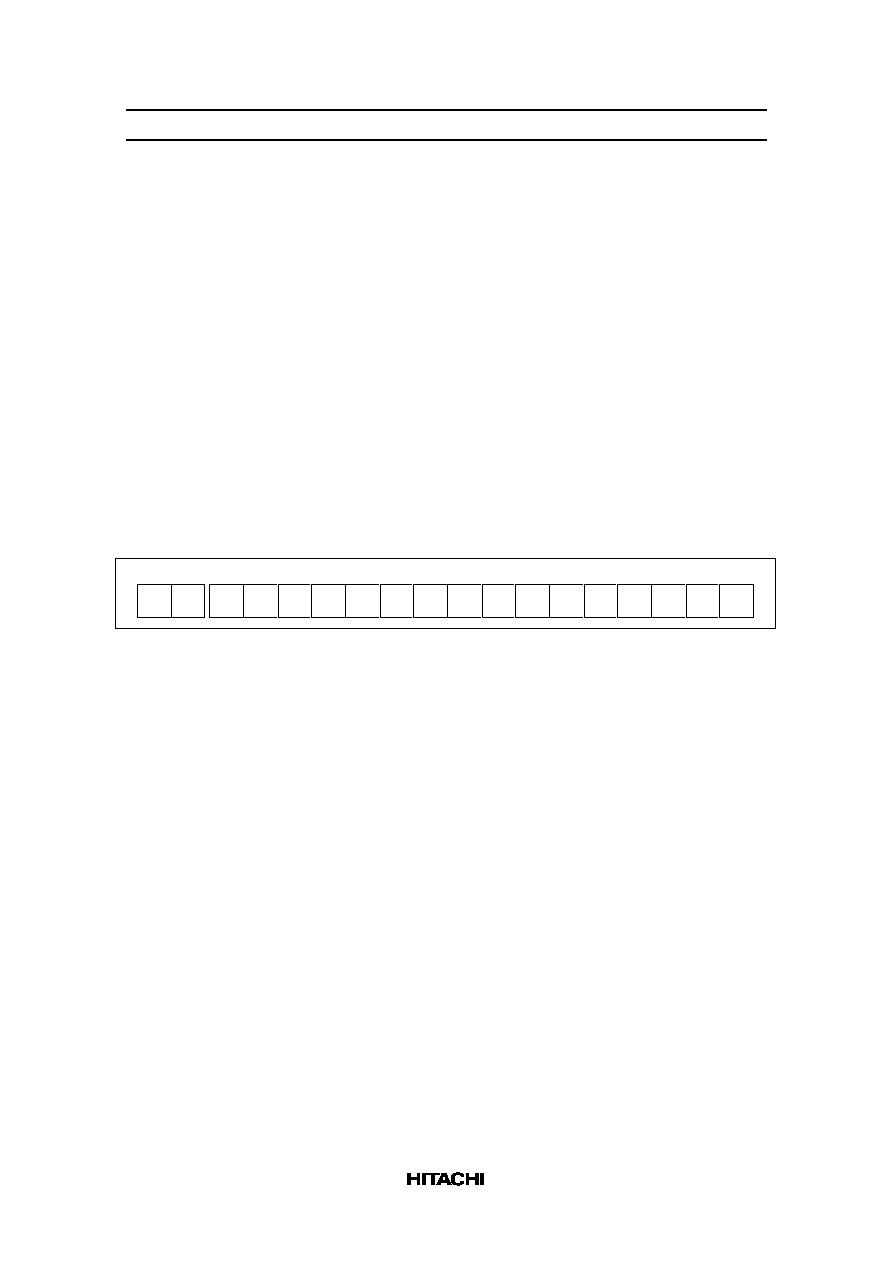

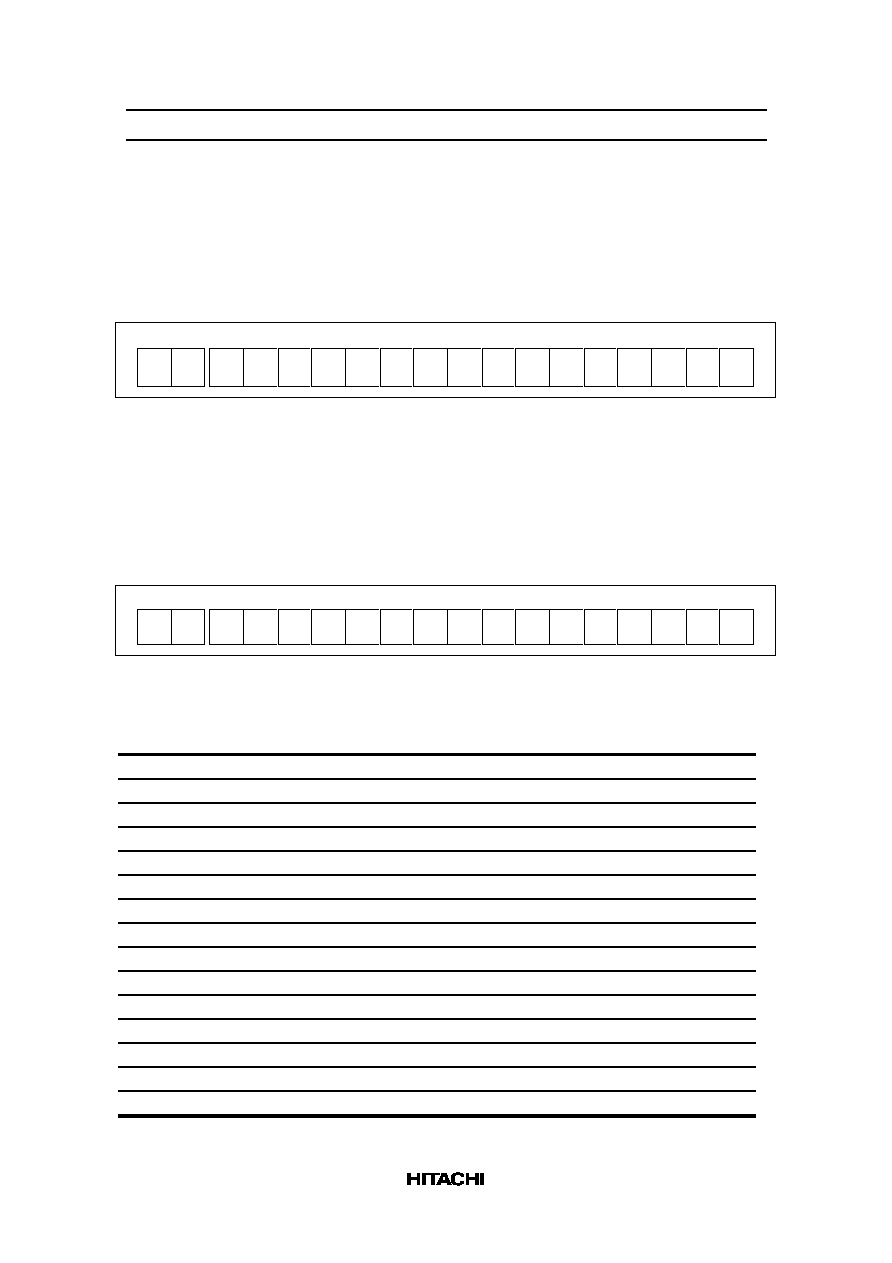

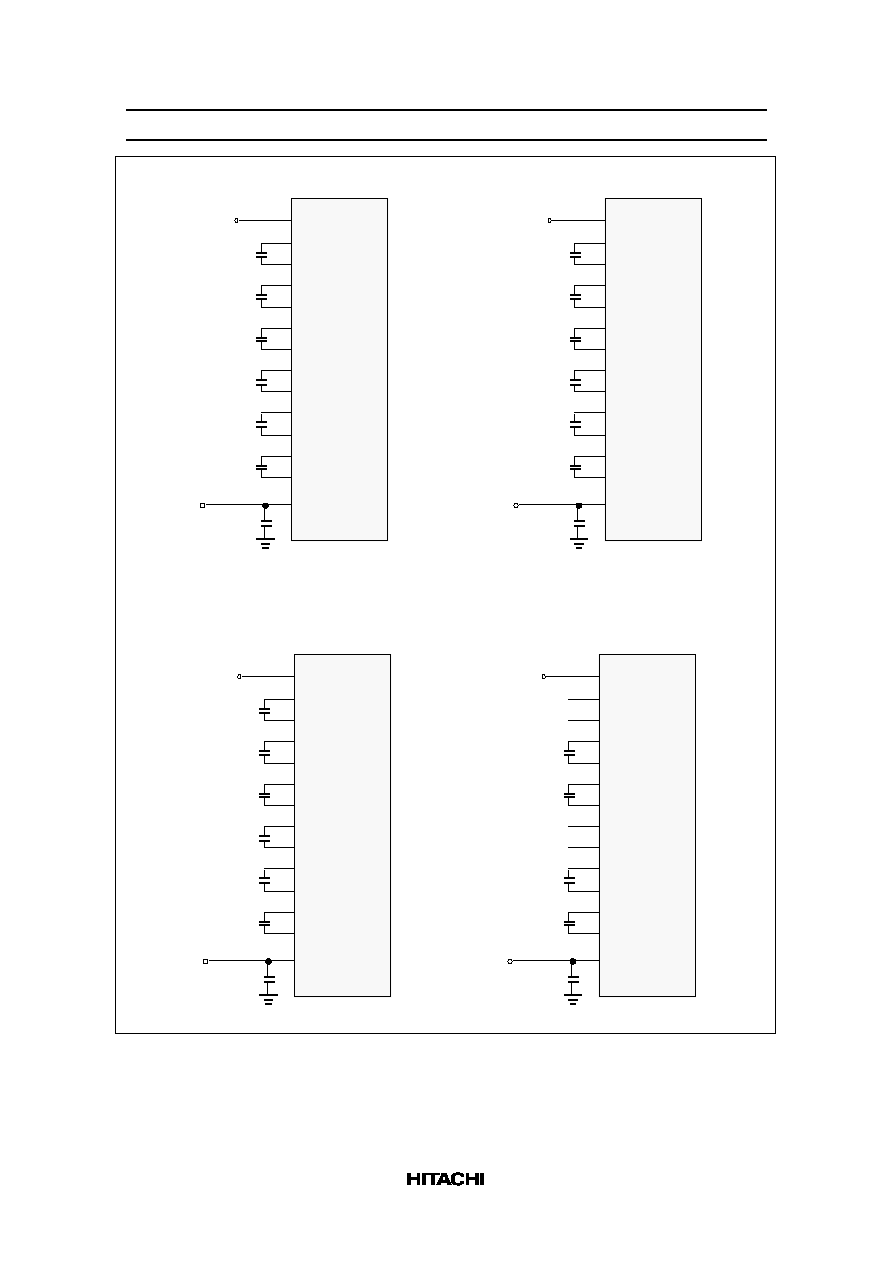

HD66750 Pad Arrangement

COM29/100

COM28/101

COM27/102

COM26/103

COM25/104

COM24/105

COM23/106

COM22/107

COM21/108

COM20/109

COM19/110

COM18/111

COM17/112

COM119/10

COM118/11

COM117/12

COM116/13

COM115/14

COM114/15

COM113/16

SEG72/57

SEG128/1

SEG127/2

SEG126/3

SEG87/42

SEG88/41

SEG89/40

SEG125/4

SEG124/5

SEG123/6

SEG122/7

SEG121/8

SEG120/9

SEG119/10

SEG118/11

SEG117/12

SEG116/13

SEG115/14

SEG114/15

SEG113/16

SEG112/17

SEG111/18

SEG110/19

SEG109/20

SEG108/21

SEG107/22

SEG106/23

SEG105/24

SEG104/25

SEG103/26

SEG102/27

SEG101/28

SEG100/29

SEG99/30

SEG98/31

SEG97/32

SEG96/33

SEG95/34

SEG94/35

SEG93/36

SEG92/37

SEG91/38

SEG90/39

SEG86/43

SEG85/44

SEG84/45

SEG83/46

SEG82/47

SEG81/48

SEG80/49

SEG79/50

SEG78/51

SEG77/52

SEG76/53

SEG75/54

SEG74/55

SEG73/56

SEG71/58

SEG70/59

SEG69/60

SEG68/61

SEG67/62

SEG66/63

SEG65/64

SEG64/65

SEG63/66

SEG62/67

SEG61/68

SEG60/69

SEG59/70

SEG58/71

SEG57/72

SEG56/73

SEG55/74

SEG54/75

SEG53/76

SEG52/77

SEG51/78

SEG50/79

SEG49/80

SEG48/81

SEG47/82

SEG46/83

SEG45/84

SEG44/85

SEG43/86

SEG42/87

SEG41/88

SEG40/89

SEG39/90

SEG38/91

SEG37/92

SEG36/93

SEG35/94

SEG34/95

SEG33/96

SEG32/97

SEG31/98

SEG30/99

SEG29/100

SEG28/101

SEG27/102

SEG26/103

SEG25/104

SEG24/105

SEG23/106

SEG22/107

SEG21/108

SEG20/109

SEG19/110

SEG18/111

SEG17/112

SEG16/113

SEG15/114

SEG14/115

SEG13/116

SEG12/117

SEG11/118

SEG10/119

SEG9/120

SEG8/121

SEG7/122

SEG6/123

SEG5/124

SEG4/125

SEG3/126

SEG2/127

SEG1/128

COM64/65

COM63/66

COM62/67

COM61/68

COM60/69

COM59/70

COM58/71

COM57/72

COM56/73

COM55/74

COM54/75

COM53/76

COM52/77

COM51/78

COM50/79

COM49/80

COM48/81

COM47/82

COM46/83

COM45/84

COM44/85

COM43/86

COM42/87

COM41/88

COM40/89

COM39/90

COM38/91

COM37/92

COM36/93

COM35/94

COM34/95

COM33/96

COM32/97

COM31/98

COM30/99

COM16/113

COM15/114

COM14/115

COM13/116

COM12/117

COM11/118

COM10/119

COM9/120

COM8/121

COM7/122

COM6/123

COM5/124

COM4/125

COM3/126

COM2/127

COM1/128

COM128/1

COM127/2

COM126/3

COM125/4

COM124/5

COM123/6

COM122/7

COM121/8

COM120/9

COM112/17

COM111/18

COM110/19

COM109/20

COM108/21

COM107/22

COM106/23

COM105/24

COM72/57

COM71/58

COM70/59

COM69/60

COM68/61

COM67/62

COM66/63

COM65/64

COM87/42

COM88/41

COM89/40

COM104/25

COM103/26

COM102/27

COM101/28

COM100/29

COM99/30

COM98/31

COM97/32

COM96/33

COM95/34

COM94/35

COM93/36

COM92/37

COM91/38

COM90/39

COM86/43

COM85/44

COM84/45

COM83/46

COM82/47

COM81/48

COM80/49

COM79/50

COM78/51

COM77/52

COM76/53

COM75/54

COM74/55

COM73/56

OSC2

OSC1

E/WR*

RW/RD*

GND

RS

CS*

RESET*

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

GNDDUM1

IM1

IM0

VccDUM1

OPOFF

TEST

GNDDUM2

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

GNDDUM3

Dummy1

C1+

C2-

C2+

Vci

VTEST

C1-

VLOUT

V

LCD

Vcc

C3-

C3+

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

C4-

C4+

C5-

C5+

C6-

C6+

Dummy22

V

LCD

VLOUT

C1-

C1+

C2-

C2+

C3-

C3+

C4-

C4+

C5-

C5+

C6-

C6+

Vci

Vcc

GND

GND

GND

GND

RW/RD*

E/WR*

RS

CS*

RESET*

DB0

DB1

DB2

DB4

DB3

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

TEST

OPOFF

IM0

IM1

Dummy21

Dummy20

Dummy19

Dummy18

Dummy17

Dummy15

Dummy16

Dummy14

Dummy13

Dummy12

Dummy11

OSC1

OSC2

GND

GND

GND

GND

Dummy2

Dummy3

Dummy4

Dummy5

Dummy6

Dummy7

Dummy8

Dummy9

Dummy10

Dummy29

Dummy28

Dummy27

Dummy25

Dummy26

Dummy23

Dummy24

Dummy31

Dummy32

Dummy33

Dummy34

Dummy35

Dummy30

Dummy48

Dummy47

Dummy43

Dummy42

Dummy41

Dummy40

Dummy39

Dummy38

Dummy46

Dummy45

Dummy44

Dummy37

Dummy36

(note)

This figure is shown pad arrangement from chip top view

which has Au-bumps and LSI pattern layer.

OSC2

OSC1

E/WR*

RW/RD*

GND

RS

CS*

RESET*

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

GNDDUM1

IM1

IM0

VccDUM1

OPOFF

TEST

SEG128/1

SEG72/57

Dummy48

GNDDUM2

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

GNDDUM3

SEG127/2

SEG126/3

SEG87/42

Dummy1

SEG88/41

SEG89/40

C1+

C2-

C2+

Vci

VTEST

C1-

VLOUT

V

LCD

Vcc

C3-

C3+

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

C4-

C4+

C5-

C5+

C6-

C6+

SEG125/4

SEG124/5 SEG123/6

SEG122/7 SEG121/8

SEG120/9 SEG119/10

SEG118/11 SEG117/12

SEG116/13 SEG115/14

SEG114/15 SEG113/16

SEG112/17 SEG111/18

SEG110/19 SEG109/20

SEG108/21 SEG107/22

SEG106/23 SEG105/24

SEG104/25 SEG103/26

SEG102/27 SEG101/28

SEG100/29 SEG99/30

SEG98/31 SEG97/32

SEG96/33 SEG95/34

SEG94/35 SEG93/36

SEG92/37 SEG91/38

SEG90/39

SEG86/43 SEG85/44

SEG84/45 SEG83/46

SEG82/47 SEG81/48

SEG80/49 SEG79/50

SEG78/51 SEG77/52

SEG76/53 SEG75/54

SEG74/55 SEG73/56

SEG71/58

SEG70/59

SEG69/60

SEG68/61

SEG67/62

SEG66/63

SEG65/64

SEG64/65

SEG63/66

SEG62/67

SEG61/68

SEG60/69

SEG59/70

SEG58/71

SEG57/72

SEG56/73

SEG55/74

SEG54/75

SEG53/76

SEG52/77

SEG51/78

SEG50/79

SEG49/80

SEG48/81

SEG47/82

SEG46/83

SEG45/84

SEG44/85

SEG43/86

SEG42/87

SEG41/88

SEG40/89

SEG39/90

SEG38/91

SEG37/92

SEG36/93

SEG35/94

SEG34/95

SEG33/96

SEG32/97

SEG31/98

SEG30/99

SEG29/100

SEG28/101

SEG27/102

SEG26/103

SEG25/104

SEG24/105

SEG23/106

SEG22/107

SEG21/108

SEG20/109

SEG19/110

SEG18/111

SEG17/112

SEG16/113

SEG15/114

SEG14/115

SEG13/116

SEG12/117

SEG11/118

SEG10/119

SEG9/120

SEG8/121

SEG7/122

SEG6/123

SEG5/124

SEG4/125

SEG3/126

SEG2/127

SEG1/128

Dummy29

Dummy22

COM72/57

COM71/58

COM70/59

COM69/60

COM68/61

COM67/62

COM66/63

COM65/64

COM64/65

COM63/66

COM62/67

COM61/68

COM60/69

COM59/70

COM58/71

COM57/72

COM56/73

COM55/74

COM54/75

COM53/76

COM52/77

COM51/78

COM50/79

COM49/80

COM48/81

COM47/82

COM46/83

COM45/84

COM44/85

COM43/86

COM42/87

COM41/88

COM40/89

COM39/90

COM38/91

COM37/92

COM36/93

COM35/94

COM34/95

COM33/96

COM32/97

COM31/98

COM30/99

COM29/100

COM28/101

COM27/102

COM26/103

COM25/104

COM24/105

COM23/106

COM22/107

COM21/108

COM20/109

COM19/110

COM18/111

COM17/112

COM16/113

COM15/114

COM14/115

COM13/116

COM12/117

COM11/118

COM10/119

COM9/120

COM8/121

COM7/122

COM6/123

COM5/124

COM4/125

COM3/126

COM2/127

COM1/128

COM128/1

COM127/2

COM126/3

COM87/42

COM88/41

COM89/40

COM125/4

COM124/5

COM123/6

COM122/7

COM121/8

COM120/9

COM119/10

COM118/11

COM117/12

COM116/13

COM115/14

COM114/15

COM113/16

COM112/17

COM111/18

COM110/19

COM109/20

COM108/21

COM107/22

COM106/23

COM105/24

COM104/25

COM103/26

COM102/27

COM101/28

COM100/29

COM99/30

COM98/31

COM97/32

COM96/33

COM95/34

COM94/35

COM93/36

COM92/37

COM91/38

COM90/39

COM86/43

COM85/44

COM84/45

COM83/46

COM82/47

COM81/48

COM80/49

COM79/50

COM78/51

COM77/52

COM76/53

COM75/54

COM74/55

COM73/56

Dummy28

Dummy27

Dummy25

VLOUT

C1-

C1+

C2-

C2+

C3-

C3+

C4-

C4+

C5-

C5+

C6-

C6+

Vci

Vcc

GND

GND

GND

GND

RW/RD*

E/WR*

RS

CS*

RESET*

DB0

DB1

DB2

DB4

DB3

DB5

DB6

DB7

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

TEST

OPOFF

IM0

IM1

V

LCD

Dummy47

Dummy36

Dummy43

Dummy42

Dummy41

Dummy26

Dummy23

Dummy21

Dummy20

Dummy19

Dummy18

Dummy17

Dummy15

Dummy16

Dummy14

Dummy13

Dummy12

Dummy11

OSC1

OSC2

GND

GND

GND

GND

Dummy2

Dummy3

Dummy4

Dummy5

Dummy6

Dummy7

Dummy8

Dummy9

Dummy10

Dummy24

Dummy31

Dummy32

Dummy33

Dummy34

Dummy35

Dummy40

Dummy39

Dummy38

Dummy37

Dummy46

Dummy45

Dummy44

Dummy30

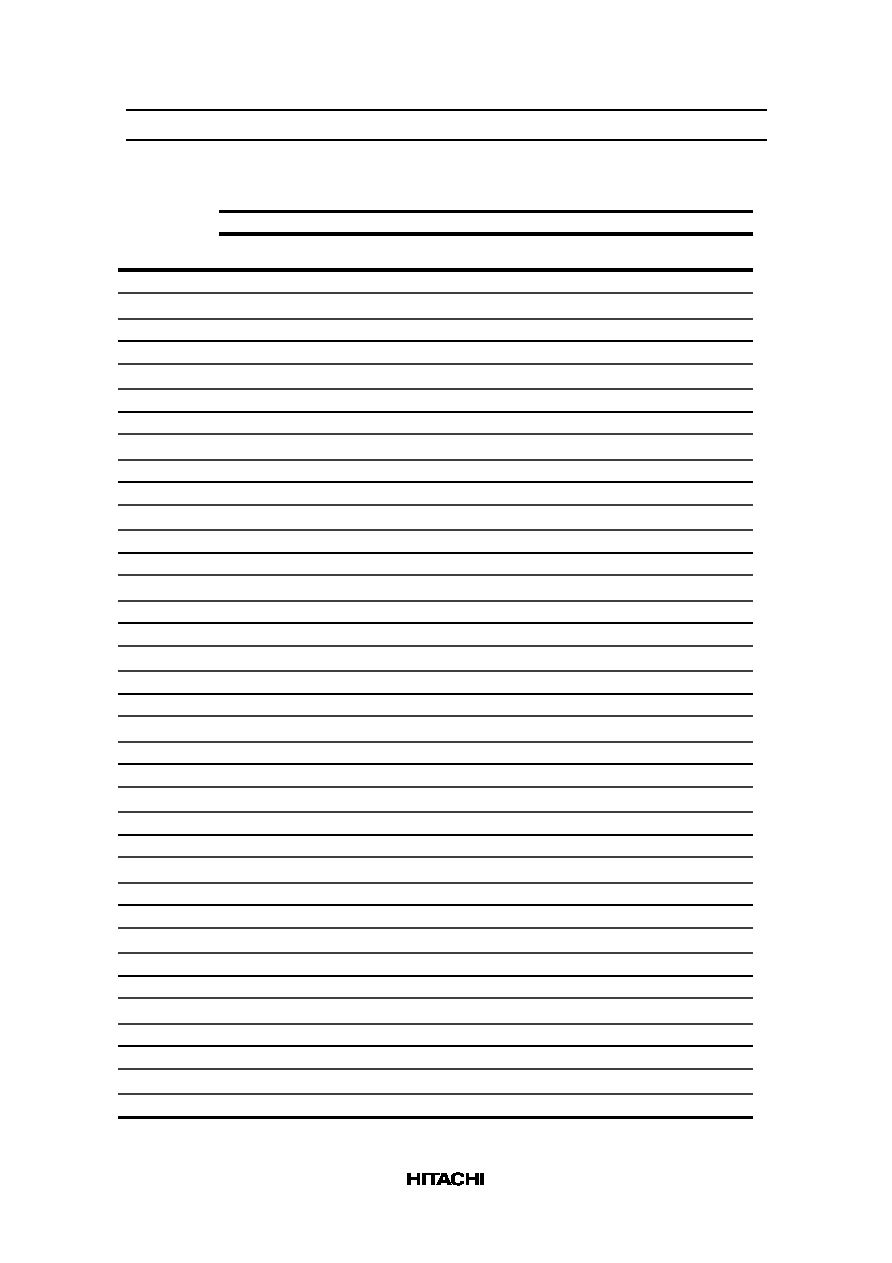

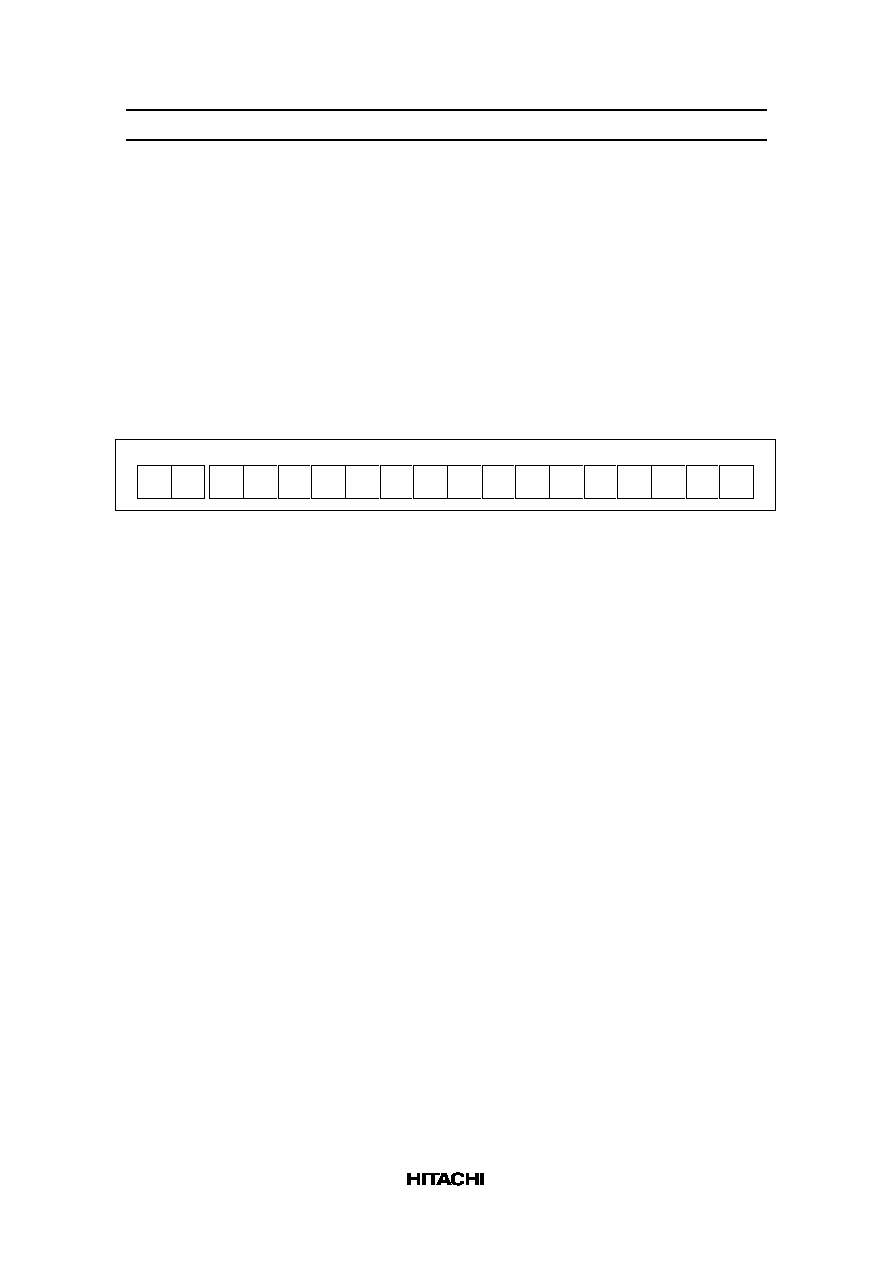

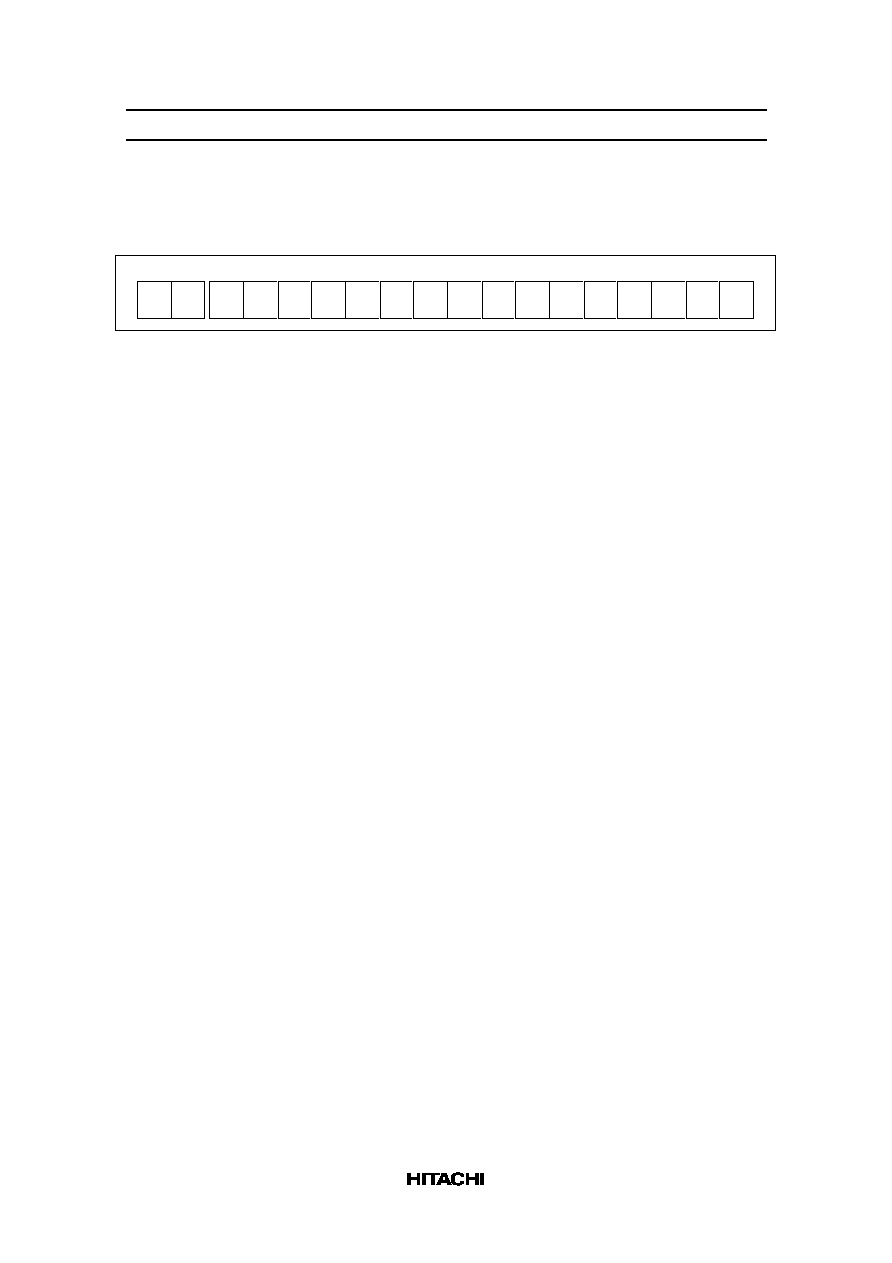

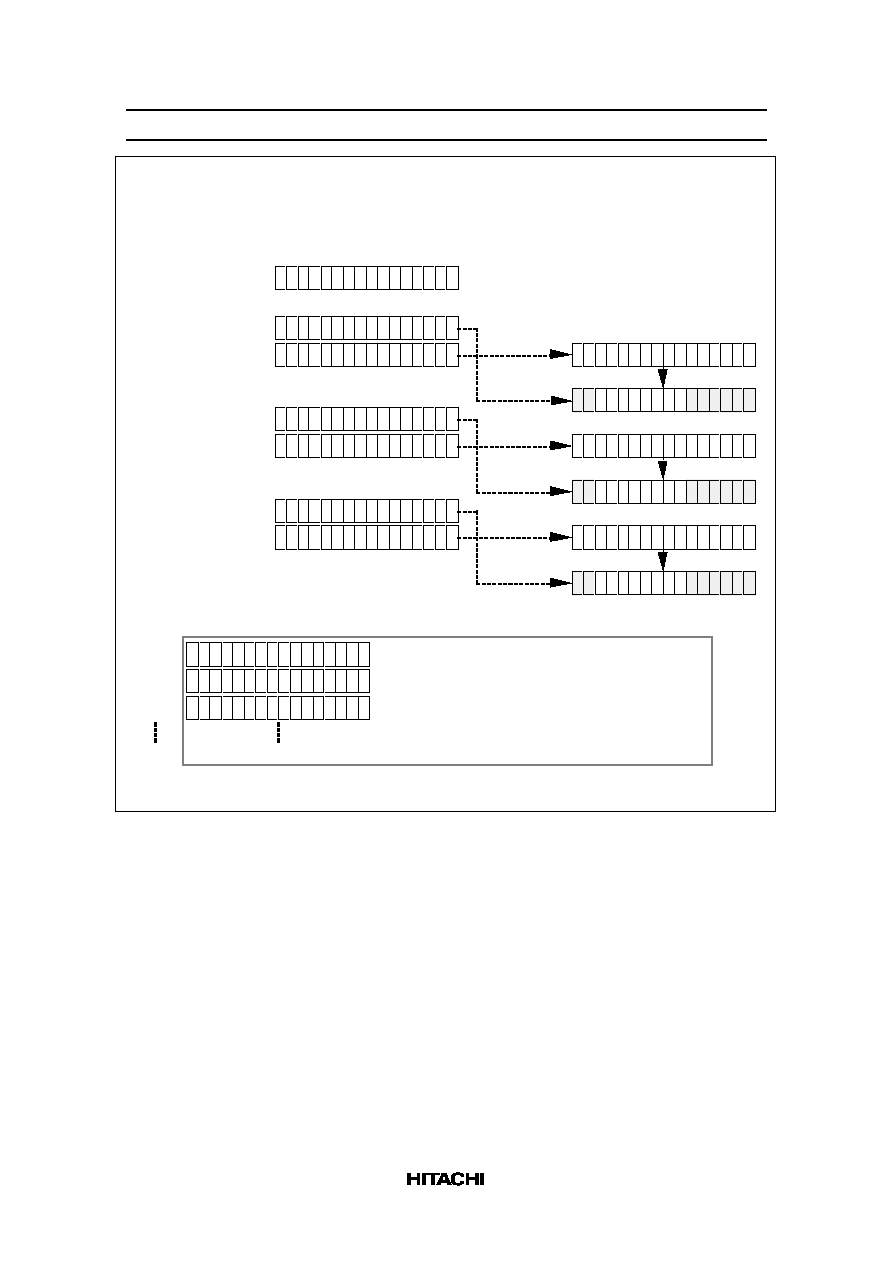

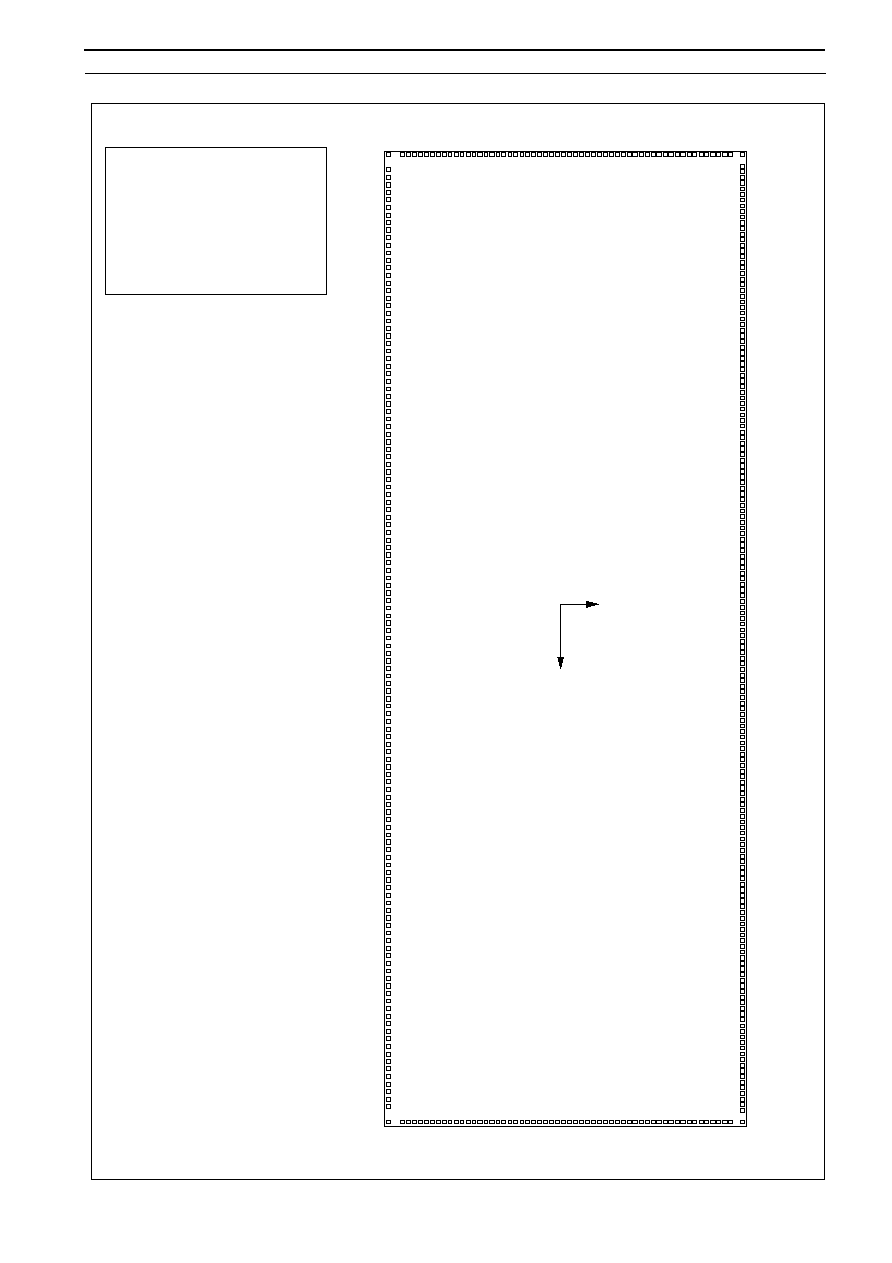

(Top view)

HD66751

Y

X

HD66750/1

HITACHI

10

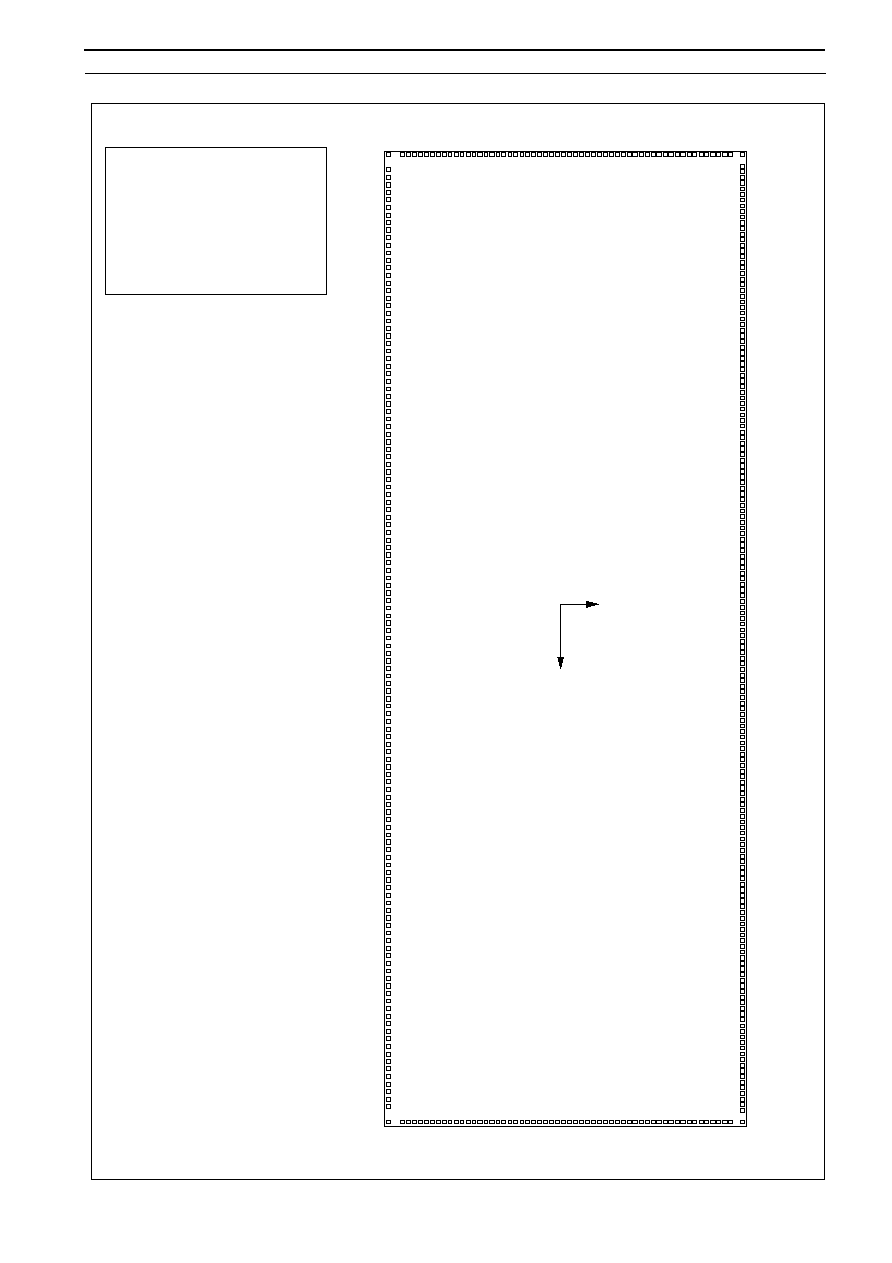

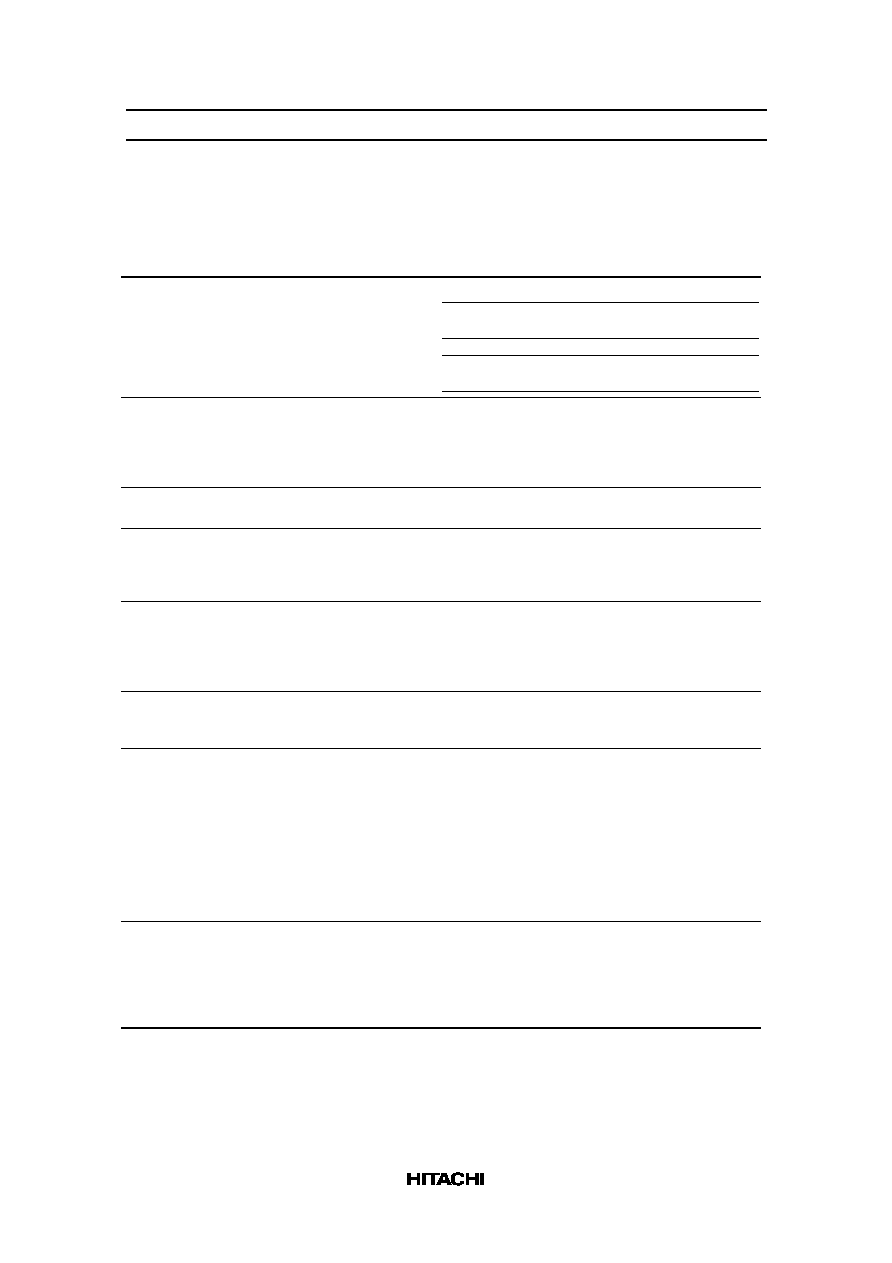

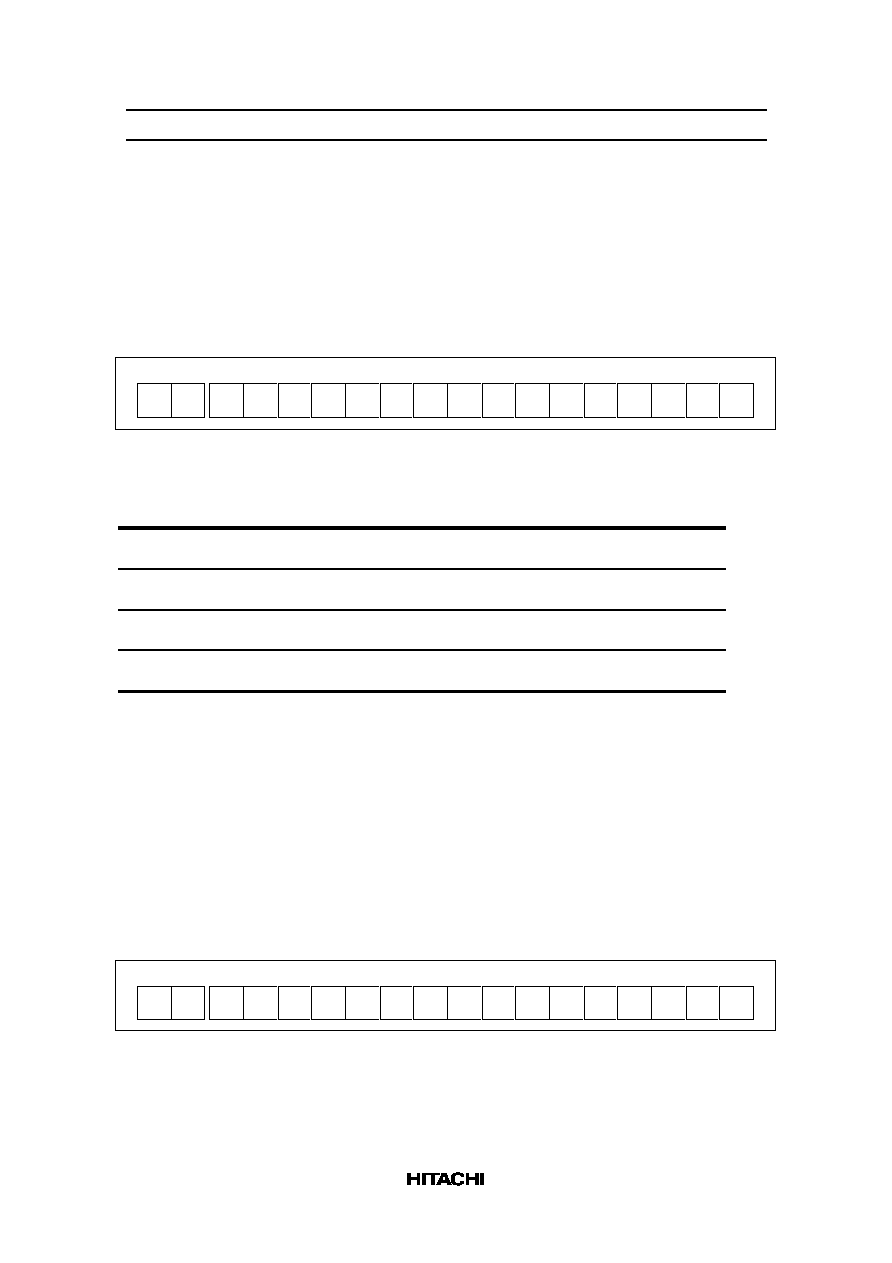

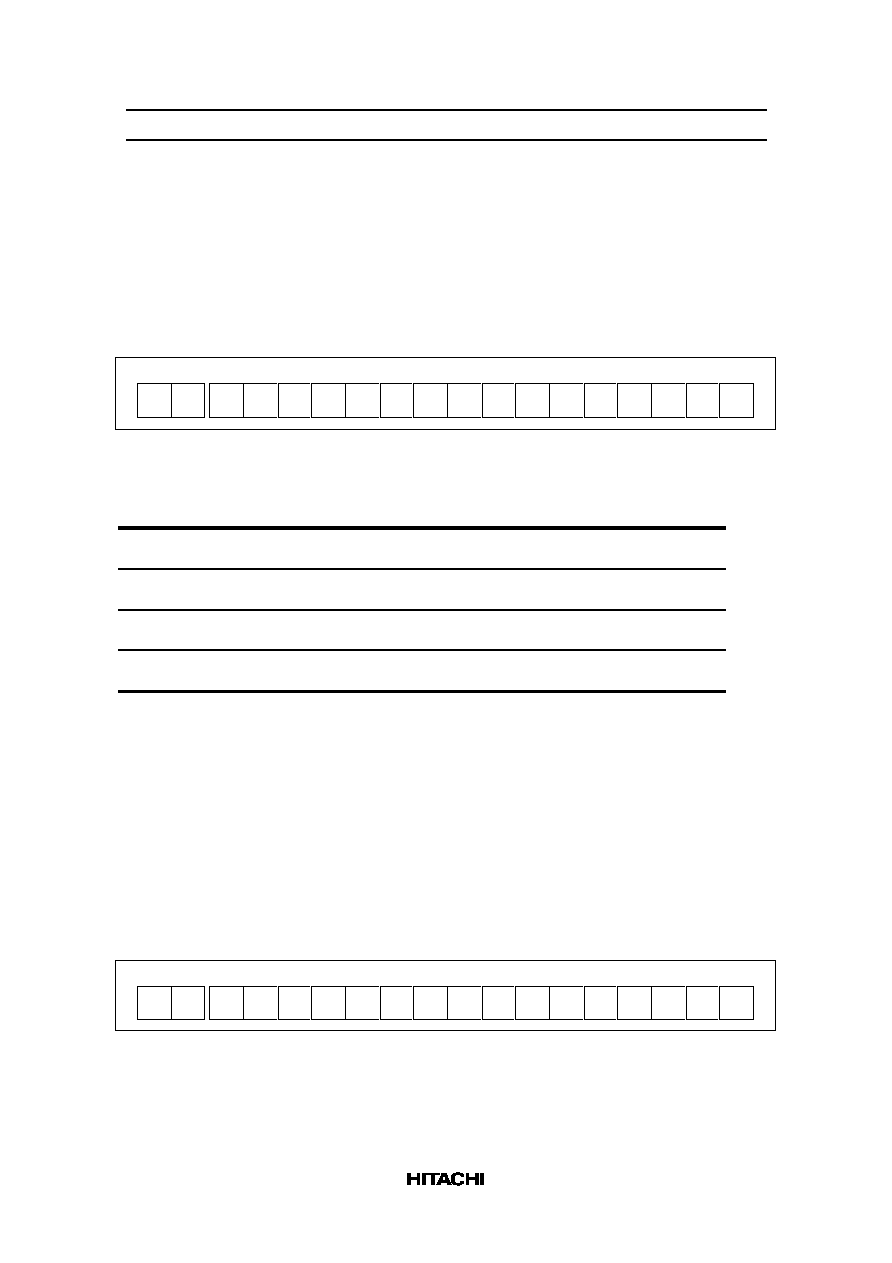

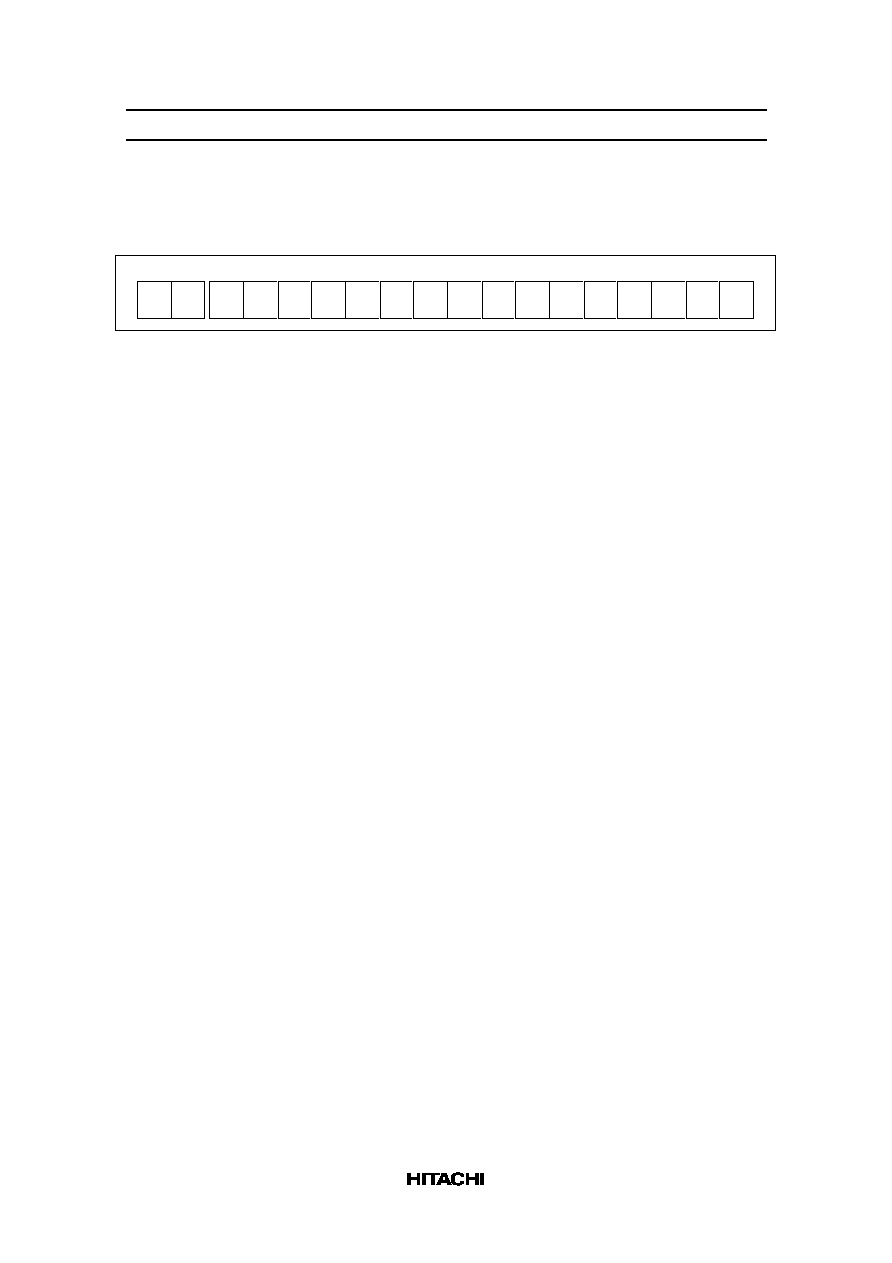

HD66751 Pad Arrangement

• Chip size: 10.97 mm X 4.13 mm

• Pad coordinates: Pad center

• Coordinate origin: Chip center

• Au bump size: 40

µ

m x 90

µ

m

Chip corner bump size : 90

µ

m x 90

µ

m

(Dummy1, Dummy22, Dummy23 and Dummy 48)

• Au bump pitch: 60

µ

m (min.)

• Au bump height: 20

µ

m (typ.)

(note)

This figure is shown pad arrangement from chip top view

which has Au-bumps and LSI pattern layer.

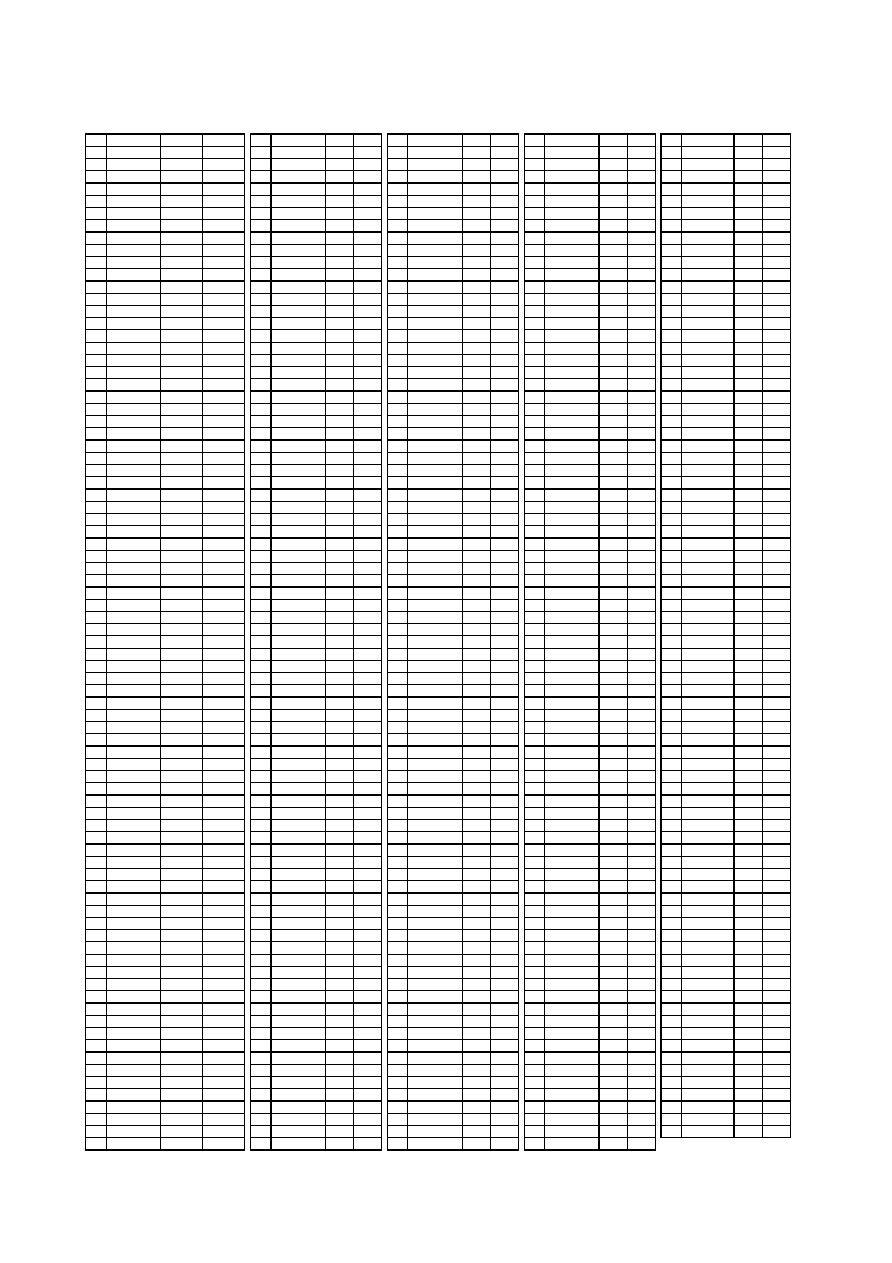

HD66750/1

HD66750 Pad Coordinate

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

1 Dummy1

-5269

-1895

83 C6+

1582 -1849

165 COM54/75

5269

571

247 SEG43/86

1310

1849

329 SEG125/4

-3655

1849

2 Dummy2

-5089

-1895

84 C6-

1703 -1849

166 COM55/74

5269

631

248 SEG44/85

1250

1849

330 SEG126/3

-3715

1849

3 Dummy3

-5029

-1895

85 C6-

1763 -1849

167 COM56/73

5269

691

249 SEG45/84

1190

1849

331 SEG127/2

-3775

1849

4 Dummy4

-4969

-1895

86 C5+

1883 -1849

168 COM57/72

5269

752

250 SEG46/83

1130

1849

332 SEG128/1

-3835

1849

5 Dummy5

-4909

-1895

87 C5+

1943 -1849

169 COM58/71

5269

812

251 SEG47/82

1070

1849

333 COM112/17 -3931

1849

6 Dummy6

-4848

-1895

88 C5-

2063 -1849

170 COM59/70

5269

872

252 SEG48/81

1010

1849

334 COM111/18 -3991

1849

7 Dummy7

-4788

-1895

89 C5-

2124 -1849

171 COM60/69

5269

932

253 SEG49/80

950

1849

335 COM110/19 -4051

1849

8 Dummy8

-4728

-1895

90 C4+

2244 -1849

172 COM61/68

5269

992

254 SEG50/79

889

1849

336 COM109/20 -4111

1849

9 Dummy9

-4668

-1895

91 C4+

2304 -1849

173 COM62/67

5269

1052

255 SEG51/78

829

1849

337 COM108/21 -4171

1849

10 Dummy10

-4608

-1895

92 C4-

2424 -1849

174 COM63/66

5269

1112

256 SEG52/77

769

1849

338 COM107/22 -4232

1849

11 GNDDUM1

-4454

-1895

93 C4-

2484 -1849

175 COM64/65

5269

1172

257 SEG53/76

709

1849

339 COM106/23 -4292

1849

12 IM1

-4394

-1895

94 C3+

2605 -1849

176 COM113/16

5269

1232

258 SEG54/75

649

1849

340 COM105/24 -4352

1849

13 IM1

-4334

-1895

95 C3+

2665 -1849

177 COM114/15

5269

1293

259 SEG55/74

589

1849

341 Dummy36

-4428

1895

14 IM0

-4210

-1895

96 C3-

2785 -1849

178 COM115/14

5269

1353

260 SEG56/73

529

1849

342 Dummy37

-4488

1895

15 IM0

-4150

-1895

97 C3-

2845 -1849

179 COM116/13

5269

1413

261 SEG57/72

469

1849

343 Dummy38

-4548

1895

16 VccDUM1

-4086

-1895

98 C2+

2965 -1849

180 COM117/12

5269

1473

262 SEG58/71

409

1849

344 Dummy39

-4608

1895

17 OPOFF

-4026

-1895

99 C2+

3025 -1849

181 COM118/11

5269

1533

263 SEG59/70

348

1849

345 Dummy40

-4668

1895

18 OPOFF

-3966

-1895

100 C2-

3146 -1849

182 COM119/10

5269

1593

264 SEG60/69

288

1849

346 Dummy41

-4728

1895

19 TEST

-3842

-1895

101 C2-

3206 -1849

183 COM120/9

5269

1653

265 SEG61/68

228

1849

347 Dummy42

-4788

1895

20 TEST

-3782

-1895

102 C1+

3326 -1849

184 Dummy23

5269

1895

266 SEG62/67

168

1849

348 Dummy43

-4848

1895

21 GNDDUM2

-3722

-1895

103 C1+

3386 -1849

185 Dummy24

5089

1895

267 SEG63/66

108

1849

349 Dummy44

-4909

1895

22 DB15

-3658

-1895

104 C1-

3506 -1849

186 Dummy25

5029

1895

268 SEG64/65

48

1849

350 Dummy45

-4969

1895

23 DB15

-3598

-1895

105 C1-

3566 -1849

187 Dummy26

4969

1895

269 SEG65/64

-48

1849

351 Dummy46

-5029

1895

24 DB14

-3474

-1895

106 VLOUT

3687 -1849

188 Dummy27

4909

1895

270 SEG66/63

-108

1849

352 Dummy47

-5089

1895

25 DB14

-3414

-1895

107 VLOUT

3747 -1849

189 Dummy28

4848

1895

271 SEG67/62

-168

1849

353 Dummy48

-5269

1895

26 DB13

-3290

-1895

108 VLCD

3867 -1849

190 Dummy29

4788

1895

272 SEG68/61

-228

1849

354 COM104/25 -5269

1653

27 DB13

-3230

-1895

109 VLCD

3927 -1849

191 Dummy30

4728

1895

273 SEG69/60

-288

1849

355 COM103/26 -5269

1593

28 DB12

-3106

-1895

110 V1OUT

4047 -1849

192 Dummy31

4668

1895

274 SEG70/59

-348

1849

356 COM102/27 -5269

1533

29 DB12

-3046

-1895

111 V2OUT

4108 -1849

193 Dummy32

4608

1895

275 SEG71/58

-409

1849

357 COM101/28 -5269

1473

30 DB11

-2922

-1895

112 V3OUT

4168 -1849

194 Dummy33

4548

1895

276 SEG72/57

-469

1849

358 COM100/29 -5269

1413

31 DB11

-2862

-1895

113 V4OUT

4228 -1849

195 Dummy34

4488

1895

277 SEG73/56

-529

1849

359 COM99/30

-5269

1353

32 DB10

-2738

-1895

114 V5OUT

4288 -1849

196 Dummy35

4428

1895

278 SEG74/55

-589

1849

360 COM98/31

-5269

1293

33 DB10

-2678

-1895

115 VTEST

4348 -1849

197 COM121/8

4352

1849

279 SEG75/54

-649

1849

361 COM97/32

-5269

1232

34 DB9

-2554

-1895

116 Dummy11

4488 -1895

198 COM122/7

4292

1849

280 SEG76/53

-709

1849

362 COM96/33

-5269

1172

35 DB9

-2494

-1895

117 Dummy12

4548 -1895

199 COM123/6

4232

1849

281 SEG77/52

-769

1849

363 COM95/34

-5269

1112

36 DB8

-2370

-1895

118 Dummy13

4608 -1895

200 COM124/5

4171

1849

282 SEG78/51

-829

1849

364 COM94/35

-5269

1052

37 DB8

-2310

-1895

119 Dummy14

4668 -1895

201 COM125/4

4111

1849

283 SEG79/50

-889

1849

365 COM93/36

-5269

992

38 DB7

-2186

-1895

120 Dummy15

4728 -1895

202 COM126/3

4051

1849

284 SEG80/49

-950

1849

366 COM92/37

-5269

932

39 DB7

-2126

-1895

121 Dummy16

4788 -1895

203 COM127/2

3991

1849

285 SEG81/48

-1010

1849

367 COM91/38

-5269

872

40 DB6

-2002

-1895

122 Dummy17

4848 -1895

204 COM128/1

3931

1849

286 SEG82/47

-1070

1849

368 COM90/39

-5269

812

41 DB6

-1942

-1895

123 Dummy18

4909 -1895

205 SEG1/128

3835

1849

287 SEG83/46

-1130

1849

369 COM89/40

-5269

752

42 DB5

-1818

-1895

124 Dummy19

4969 -1895

206 SEG2/127

3775

1849

288 SEG84/45

-1190

1849

370 COM88/41

-5269

691

43 DB5

-1758

-1895

125 Dummy20

5029 -1895

207 SEG3/126

3715

1849

289 SEG85/44

-1250

1849

371 COM87/42

-5269

631

44 DB4

-1634

-1895

126 Dummy21

5089 -1895

208 SEG4/125

3655

1849

290 SEG86/43

-1310

1849

372 COM86/43

-5269

571

45 DB4

-1574

-1895

127 Dummy22

5269 -1895

209 SEG5/124

3595

1849

291 SEG87/42

-1370

1849

373 COM85/44

-5269

511

46 DB3

-1450

-1895

128 COM17/112

5269 -1653

210 SEG6/123

3535

1849

292 SEG88/41

-1431

1849

374 COM84/45

-5269

451

47 DB3

-1390

-1895

129 COM18/111

5269 -1593

211 SEG7/122

3475

1849

293 SEG89/40

-1491

1849

375 COM83/46

-5269

391

48 DB2

-1266

-1895

130 COM19/110

5269 -1533

212 SEG8/121

3415

1849

294 SEG90/39

-1551

1849

376 COM82/47

-5269

331

49 DB2

-1206

-1895

131 COM20/109

5269 -1473

213 SEG9/120

3354

1849

295 SEG91/38

-1611

1849

377 COM81/48

-5269

271

50 DB1

-1083

-1895

132 COM21/108

5269 -1413

214 SEG10/119

3294

1849

296 SEG92/37

-1671

1849

378 COM80/49

-5269

210

51 DB1

-1022

-1895

133 COM22/107

5269 -1353

215 SEG11/118

3234

1849

297 SEG93/36

-1731

1849

379 COM79/50

-5269

150

52 DB0

-899

-1895

134 COM23/106

5269 -1293

216 SEG12/117

3174

1849

298 SEG94/35

-1791

1849

380 COM78/51

-5269

90

53 DB0

-838

-1895

135 COM24/105

5269 -1232

217 SEG13/116

3114

1849

299 SEG95/34

-1851

1849

381 COM77/52

-5269

30

54 GNDDUM3

-775

-1895

136 COM25/104

5269 -1172

218 SEG14/115

3054

1849

300 SEG96/33

-1912

1849

382 COM76/53

-5269

-30

55 RESET*

-715

-1895

137 COM26/103

5269 -1112

219 SEG15/114

2994

1849

301 SEG97/32

-1972

1849

383 COM75/54

-5269

-90

56 RESET*

-654

-1895

138 COM27/102

5269 -1052

220 SEG16/113

2934

1849

302 SEG98/31

-2032

1849

384 COM74/55

-5269

-150

57 CS*

-531

-1895

139 COM28/101

5269

-992

221 SEG17/112

2873

1849

303 SEG99/30

-2092

1849

385 COM73/56

-5269

-210

58 CS*

-471

-1895

140 COM29/100

5269

-932

222 SEG18/111

2813

1849

304 SEG100/29

-2152

1849

386 COM72/57

-5269

-271

59 RS

-347

-1895

141 COM30/99

5269

-872

223 SEG19/110

2753

1849

305 SEG101/28

-2212

1849

387 COM71/58

-5269

-331

60 RS

-287

-1895

142 COM31/98

5269

-812

224 SEG20/109

2693

1849

306 SEG102/27

-2272

1849

388 COM70/59

-5269

-391

61 E/WR*

-163

-1895

143 COM32/97

5269

-752

225 SEG21/108

2633

1849

307 SEG103/26

-2332

1849

389 COM69/60

-5269

-451

62 E/WR*

-103

-1895

144 COM33/96

5269

-691

226 SEG22/107

2573

1849

308 SEG104/25

-2392

1849

390 COM68/61

-5269

-511

63 RW/RD*

21

-1895

145 COM34/95

5269

-631

227 SEG23/106

2513

1849

309 SEG105/24

-2453

1849

391 COM67/62

-5269

-571

64 RW/RD*

81

-1895

146 COM35/94

5269

-571

228 SEG24/105

2453

1849

310 SEG106/23

-2513

1849

392 COM66/63

-5269

-631

65 GND

151

-1895

147 COM36/93

5269

-511

229 SEG25/104

2392

1849

311 SEG107/22

-2573

1849

393 COM65/64

-5269

-691

66 GND

211

-1895

148 COM37/92

5269

-451

230 SEG26/103

2332

1849

312 SEG108/21

-2633

1849

394 COM16/113 -5269

-752

67 GND

271

-1895

149 COM38/91

5269

-391

231 SEG27/102

2272

1849

313 SEG109/20

-2693

1849

395 COM15/114 -5269

-812

68 GND

332

-1895

150 COM39/90

5269

-331

232 SEG28/101

2212

1849

314 SEG110/19

-2753

1849

396 COM14/115 -5269

-872

69 GND

392

-1895

151 COM40/89

5269

-271

233 SEG29/100

2152

1849

315 SEG111/18

-2813

1849

397 COM13/116 -5269

-932

70 GND

452

-1895

152 COM41/88

5269

-210

234 SEG30/99

2092

1849

316 SEG112/17

-2873

1849

398 COM12/117 -5269

-992

71 GND

512

-1895

153 COM42/87

5269

-150

235 SEG31/98

2032

1849

317 SEG113/16

-2934

1849

399 COM11/118 -5269 -1052

72 GND

572

-1895

154 COM43/86

5269

-90

236 SEG32/97

1972

1849

318 SEG114/15

-2994

1849

400 COM10/119 -5269 -1112

73 GND

632

-1895

155 COM44/85

5269

-30

237 SEG33/96

1912

1849

319 SEG115/14

-3054

1849

401 COM9/120

-5269 -1172

74 OSC2

702

-1895

156 COM45/84

5269

30

238 SEG34/95

1851

1849

320 SEG116/13

-3114

1849

402 COM8/121

-5269 -1232

75 OSC2

762

-1895

157 COM46/83

5269

90

239 SEG35/94

1791

1849

321 SEG117/12

-3174

1849

403 COM7/122

-5269 -1293

76 OSC1

886

-1895

158 COM47/82

5269

150

240 SEG36/93

1731

1849

322 SEG118/11

-3234

1849

404 COM6/123

-5269 -1353

77 OSC1

946

-1895

159 COM48/81

5269

210

241 SEG37/92

1671

1849

323 SEG119/10

-3294

1849

405 COM5/124

-5269 -1413

78 Vcc

1119

-1849

160 COM49/80

5269

271

242 SEG38/91

1611

1849

324 SEG120/9

-3354

1849

406 COM4/125

-5269 -1473

79 Vcc

1179

-1849

161 COM50/79

5269

331

243 SEG39/90

1551

1849

325 SEG121/8

-3415

1849

407 COM3/126

-5269 -1533

80 Vci

1342

-1849

162 COM51/78

5269

391

244 SEG40/89

1491

1849

326 SEG122/7

-3475

1849

408 COM2/127

-5269 -1593

81 Vci

1402

-1849

163 COM52/77

5269

451

245 SEG41/88

1431

1849

327 SEG123/6

-3535

1849

409 COM1/128

-5269 -1653

82 C6+

1522

-1849

164 COM53/76

5269

511

246 SEG42/87

1370

1849

328 SEG124/5

-3595

1849

11

HD66750/1

HD66751 Pad Coordinate

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

PAD NAME

X

Y

1 Dummy1

-5269

-1895

83 C6+

1582 -1849

165 COM38/91

5269

571

247 COM107/22

1310

1849

329 SEG61/68

-3655

1849

2 Dummy2

-5089

-1895

84 C6-

1703 -1849

166 COM39/90

5269

631

248 COM108/21

1250

1849

330 SEG62/67

-3715

1849

3 Dummy3

-5029

-1895

85 C6-

1763 -1849

167 COM40/89

5269

691

249 COM109/20

1190

1849

331 SEG63/66

-3775

1849

4 Dummy4

-4969

-1895

86 C5+

1883 -1849

168 COM41/88

5269

752

250 COM110/19

1130

1849

332 SEG64/65

-3835

1849

5 Dummy5

-4909

-1895

87 C5+

1943 -1849

169 COM42/87

5269

812

251 COM111/18

1070

1849

333 SEG65/64

-3931

1849

6 Dummy6

-4848

-1895

88 C5-

2063 -1849

170 COM43/86

5269

872

252 COM112/17

1010

1849

334 SEG66/63

-3991

1849

7 Dummy7

-4788

-1895

89 C5-

2124 -1849

171 COM44/85

5269

932

253 COM113/16

950

1849

335 SEG67/62

-4051

1849

8 Dummy8

-4728

-1895

90 C4+

2244 -1849

172 COM45/84

5269

992

254 COM114/15

889

1849

336 SEG68/61

-4111

1849

9 Dummy9

-4668

-1895

91 C4+

2304 -1849

173 COM46/83

5269

1052

255 COM115/14

829

1849

337 SEG69/60

-4171

1849

10 Dummy10

-4608

-1895

92 C4-

2424 -1849

174 COM47/82

5269

1112

256 COM116/13

769

1849

338 SEG70/59

-4232

1849

11 GNDDUM1

-4454

-1895

93 C4-

2484 -1849

175 COM48/81

5269

1172

257 COM117/12

709

1849

339 SEG71/58

-4292

1849

12 IM1

-4394

-1895

94 C3+

2605 -1849

176 COM49/80

5269

1232

258 COM118/11

649

1849

340 SEG72/57

-4352

1849

13 IM1

-4334

-1895

95 C3+

2665 -1849

177 COM50/79

5269

1293

259 COM119/10

589

1849

341 Dummy36

-4428

1895

14 IM0

-4210

-1895

96 C3-

2785 -1849

178 COM51/78

5269

1353

260 COM120/9

529

1849

342 Dummy37

-4488

1895

15 IM0

-4150

-1895

97 C3-

2845 -1849

179 COM52/77

5269

1413

261 COM121/8

469

1849

343 Dummy38

-4548

1895

16 VccDUM1

-4086

-1895

98 C2+

2965 -1849

180 COM53/76

5269

1473

262 COM122/7

409

1849

344 Dummy39

-4608

1895

17 OPOFF

-4026

-1895

99 C2+

3025 -1849

181 COM54/75

5269

1533

263 COM123/6

348

1849

345 Dummy40

-4668

1895

18 OPOFF

-3966

-1895

100 C2-

3146 -1849

182 COM55/74

5269

1593

264 COM124/5

288

1849

346 Dummy41

-4728

1895

19 TEST

-3842

-1895

101 C2-

3206 -1849

183 COM56/73

5269

1653

265 COM125/4

228

1849

347 Dummy42

-4788

1895

20 TEST

-3782

-1895

102 C1+

3326 -1849

184 Dummy23

5269

1895

266 COM126/3

168

1849

348 Dummy43

-4848

1895

21 GNDDUM2

-3722

-1895

103 C1+

3386 -1849

185 Dummy24

5089

1895

267 COM127/2

108

1849

349 Dummy44

-4909

1895

22 DB15

-3658

-1895

104 C1-

3506 -1849

186 Dummy25

5029

1895

268 COM128/1

48

1849

350 Dummy45

-4969

1895

23 DB15

-3598

-1895

105 C1-

3566 -1849

187 Dummy26

4969

1895

269 SEG1/128

-48

1849

351 Dummy46

-5029

1895

24 DB14

-3474

-1895

106 VLOUT

3687 -1849

188 Dummy27

4909

1895

270 SEG2/127

-108

1849

352 Dummy47

-5089

1895

25 DB14

-3414

-1895

107 VLOUT

3747 -1849

189 Dummy28

4848

1895

271 SEG3/126

-168

1849

353 Dummy48

-5269

1895

26 DB13

-3290

-1895

108 VLCD

3867 -1849

190 Dummy29

4788

1895

272 SEG4/125

-228

1849

354 SEG73/56

-5269

1653

27 DB13

-3230

-1895

109 VLCD

3927 -1849

191 Dummy30

4728

1895

273 SEG5/124

-288

1849

355 SEG74/55

-5269

1593

28 DB12

-3106

-1895

110 V1OUT

4047 -1849

192 Dummy31

4668

1895

274 SEG6/123

-348

1849

356 SEG75/54

-5269

1533

29 DB12

-3046

-1895

111 V2OUT

4108 -1849

193 Dummy32

4608

1895

275 SEG7/122

-409

1849

357 SEG76/53

-5269

1473

30 DB11

-2922

-1895

112 V3OUT

4168 -1849

194 Dummy33

4548

1895

276 SEG8/121

-469

1849

358 SEG77/52

-5269

1413

31 DB11

-2862

-1895

113 V4OUT

4228 -1849

195 Dummy34

4488

1895

277 SEG9/120

-529

1849

359 SEG78/51

-5269

1353

32 DB10

-2738

-1895

114 V5OUT

4288 -1849

196 Dummy35

4428

1895

278 SEG10/119

-589

1849

360 SEG79/50

-5269

1293

33 DB10

-2678

-1895

115 VTEST

4348 -1849

197 COM57/72

4352

1849

279 SEG11/118

-649

1849

361 SEG80/49

-5269

1232

34 DB9

-2554

-1895

116 Dummy11

4488 -1895

198 COM58/71

4292

1849

280 SEG12/117

-709

1849

362 SEG81/48

-5269

1172

35 DB9

-2494

-1895

117 Dummy12

4548 -1895

199 COM59/70

4232

1849

281 SEG13/116

-769

1849

363 SEG82/47

-5269

1112

36 DB8

-2370

-1895

118 Dummy13

4608 -1895

200 COM60/69

4171

1849

282 SEG14/115

-829

1849

364 SEG83/46

-5269

1052

37 DB8

-2310

-1895

119 Dummy14

4668 -1895

201 COM61/68

4111

1849

283 SEG15/114

-889

1849

365 SEG84/45

-5269

992

38 DB7

-2186

-1895

120 Dummy15

4728 -1895

202 COM62/67

4051

1849

284 SEG16/113

-950

1849

366 SEG85/44

-5269

932

39 DB7

-2126

-1895

121 Dummy16

4788 -1895

203 COM63/66

3991

1849

285 SEG17/112

-1010

1849

367 SEG86/43

-5269

872

40 DB6

-2002

-1895

122 Dummy17

4848 -1895

204 COM64/65

3931

1849

286 SEG18/111

-1070

1849

368 SEG87/42

-5269

812

41 DB6

-1942

-1895

123 Dummy18

4909 -1895

205 COM65/64

3835

1849

287 SEG19/110

-1130

1849

369 SEG88/41

-5269

752

42 DB5

-1818

-1895

124 Dummy19

4969 -1895

206 COM66/63

3775

1849

288 SEG20/109

-1190

1849

370 SEG89/40

-5269

691

43 DB5

-1758

-1895

125 Dummy20

5029 -1895

207 COM67/62

3715

1849

289 SEG21/108

-1250

1849

371 SEG90/39

-5269

631

44 DB4

-1634

-1895

126 Dummy21

5089 -1895

208 COM68/61

3655

1849

290 SEG22/107

-1310

1849

372 SEG91/38

-5269

571

45 DB4

-1574

-1895

127 Dummy22

5269 -1895

209 COM69/60

3595

1849

291 SEG23/106

-1370

1849

373 SEG92/37

-5269

511

46 DB3

-1450

-1895

128 COM1/128

5269 -1653

210 COM70/59

3535

1849

292 SEG24/105

-1431

1849

374 SEG93/36

-5269

451

47 DB3

-1390

-1895

129 COM2/127

5269 -1593

211 COM71/58

3475

1849

293 SEG25/104

-1491

1849

375 SEG94/35

-5269

391

48 DB2

-1266

-1895

130 COM3/126

5269 -1533

212 COM72/57

3415

1849

294 SEG26/103

-1551

1849

376 SEG95/34

-5269

331

49 DB2

-1206

-1895

131 COM4/125

5269 -1473

213 COM73/56

3354

1849

295 SEG27/102

-1611

1849

377 SEG96/33

-5269

271

50 DB1

-1083

-1895

132 COM5/124

5269 -1413

214 COM74/55

3294

1849

296 SEG28/101

-1671

1849

378 SEG97/32

-5269

210

51 DB1

-1022

-1895

133 COM6/123

5269 -1353

215 COM75/54

3234

1849

297 SEG29/100

-1731

1849

379 SEG98/31

-5269

150

52 DB0

-899

-1895

134 COM7/122

5269 -1293

216 COM76/53

3174

1849

298 SEG30/99

-1791

1849

380 SEG99/30

-5269

90

53 DB0

-838

-1895

135 COM8/121

5269 -1232

217 COM77/52

3114

1849

299 SEG31/98

-1851

1849

381 SEG100/29

-5269

30

54 GNDDUM3

-775

-1895

136 COM9/120

5269 -1172

218 COM78/51

3054

1849

300 SEG32/97

-1912

1849

382 SEG101/28

-5269

-30

55 RESET*

-715

-1895

137 COM10/119

5269 -1112

219 COM79/50

2994

1849

301 SEG33/96

-1972

1849

383 SEG102/27

-5269

-90

56 RESET*

-654

-1895

138 COM11/118

5269 -1052

220 COM80/49

2934

1849

302 SEG34/95

-2032

1849

384 SEG103/26

-5269

-150

57 CS*

-531

-1895

139 COM12/117

5269

-992

221 COM81/48

2873

1849

303 SEG35/94

-2092

1849

385 SEG104/25

-5269

-210

58 CS*

-471

-1895

140 COM13/116

5269

-932

222 COM82/47

2813

1849

304 SEG36/93

-2152

1849

386 SEG105/24

-5269

-271

59 RS

-347

-1895

141 COM14/115

5269

-872

223 COM83/46

2753

1849

305 SEG37/92

-2212

1849

387 SEG106/23

-5269

-331

60 RS

-287

-1895

142 COM15/114

5269

-812

224 COM84/45

2693

1849

306 SEG38/91

-2272

1849

388 SEG107/22

-5269

-391

61 E/WR*

-163

-1895

143 COM16/113

5269

-752

225 COM85/44

2633

1849

307 SEG39/90

-2332

1849

389 SEG108/21

-5269

-451

62 E/WR*

-103

-1895

144 COM17/112

5269

-691

226 COM86/43

2573

1849

308 SEG40/89

-2392

1849

390 SEG109/20

-5269

-511

63 RW/RD*

21

-1895

145 COM18/111

5269

-631

227 COM87/42

2513

1849

309 SEG41/88

-2453

1849

391 SEG110/19

-5269

-571

64 RW/RD*

81

-1895

146 COM19/110

5269

-571

228 COM88/41

2453

1849

310 SEG42/87

-2513

1849

392 SEG111/18

-5269

-631

65 GND

151

-1895

147 COM20/109

5269

-511

229 COM89/40

2392

1849

311 SEG43/86

-2573

1849

393 SEG112/17

-5269

-691

66 GND

211

-1895

148 COM21/108

5269

-451

230 COM90/39

2332

1849

312 SEG44/85

-2633

1849

394 SEG113/16

-5269

-752

67 GND

271

-1895

149 COM22/107

5269

-391

231 COM91/38

2272

1849

313 SEG45/84

-2693

1849

395 SEG114/15

-5269

-812

68 GND

332

-1895

150 COM23/106

5269

-331

232 COM92/37

2212

1849

314 SEG46/83

-2753

1849

396 SEG115/14

-5269

-872

69 GND

392

-1895

151 COM24/105

5269

-271

233 COM93/36

2152

1849

315 SEG47/82

-2813

1849

397 SEG116/13

-5269

-932

70 GND

452

-1895

152 COM25/104

5269

-210

234 COM94/35

2092

1849

316 SEG48/81

-2873

1849

398 SEG117/12

-5269

-992

71 GND

512

-1895

153 COM26/103

5269

-150

235 COM95/34

2032

1849

317 SEG49/80

-2934

1849

399 SEG118/11

-5269 -1052

72 GND

572

-1895

154 COM27/102

5269

-90

236 COM96/33

1972

1849

318 SEG50/79

-2994

1849

400 SEG119/10

-5269 -1112

73 GND

632

-1895

155 COM28/101

5269

-30

237 COM97/32

1912

1849

319 SEG51/78

-3054

1849

401 SEG120/9

-5269 -1172

74 OSC2

702

-1895

156 COM29/100

5269

30

238 COM98/31

1851

1849

320 SEG52/77

-3114

1849

402 SEG121/8

-5269 -1232

75 OSC2

762

-1895

157 COM30/99

5269

90

239 COM99/30

1791

1849

321 SEG53/76

-3174

1849

403 SEG122/7

-5269 -1293

76 OSC1

886

-1895

158 COM31/98

5269

150

240 COM100/29

1731

1849

322 SEG54/75

-3234

1849

404 SEG123/6

-5269 -1353

77 OSC1

946

-1895

159 COM32/97

5269

210

241 COM101/28

1671

1849

323 SEG55/74

-3294

1849

405 SEG124/5

-5269 -1413

78 Vcc

1119

-1849

160 COM33/96

5269

271

242 COM102/27

1611

1849

324 SEG56/73

-3354

1849

406 SEG125/4

-5269 -1473

79 Vcc

1179

-1849

161 COM34/95

5269

331

243 COM103/26

1551

1849

325 SEG57/72

-3415

1849

407 SEG126/3

-5269 -1533

80 Vci

1342

-1849

162 COM35/94

5269

391

244 COM104/25

1491

1849

326 SEG58/71

-3475

1849

408 SEG127/2

-5269 -1593

81 Vci

1402

-1849

163 COM36/93

5269

451

245 COM105/24

1431

1849

327 SEG59/70

-3535

1849

409 SEG128/1

-5269 -1653

82 C6+

1522

-1849

164 COM37/92

5269

511

246 COM106/23

1370

1849

328 SEG60/69

-3595

1849

12

HD66750/1

13

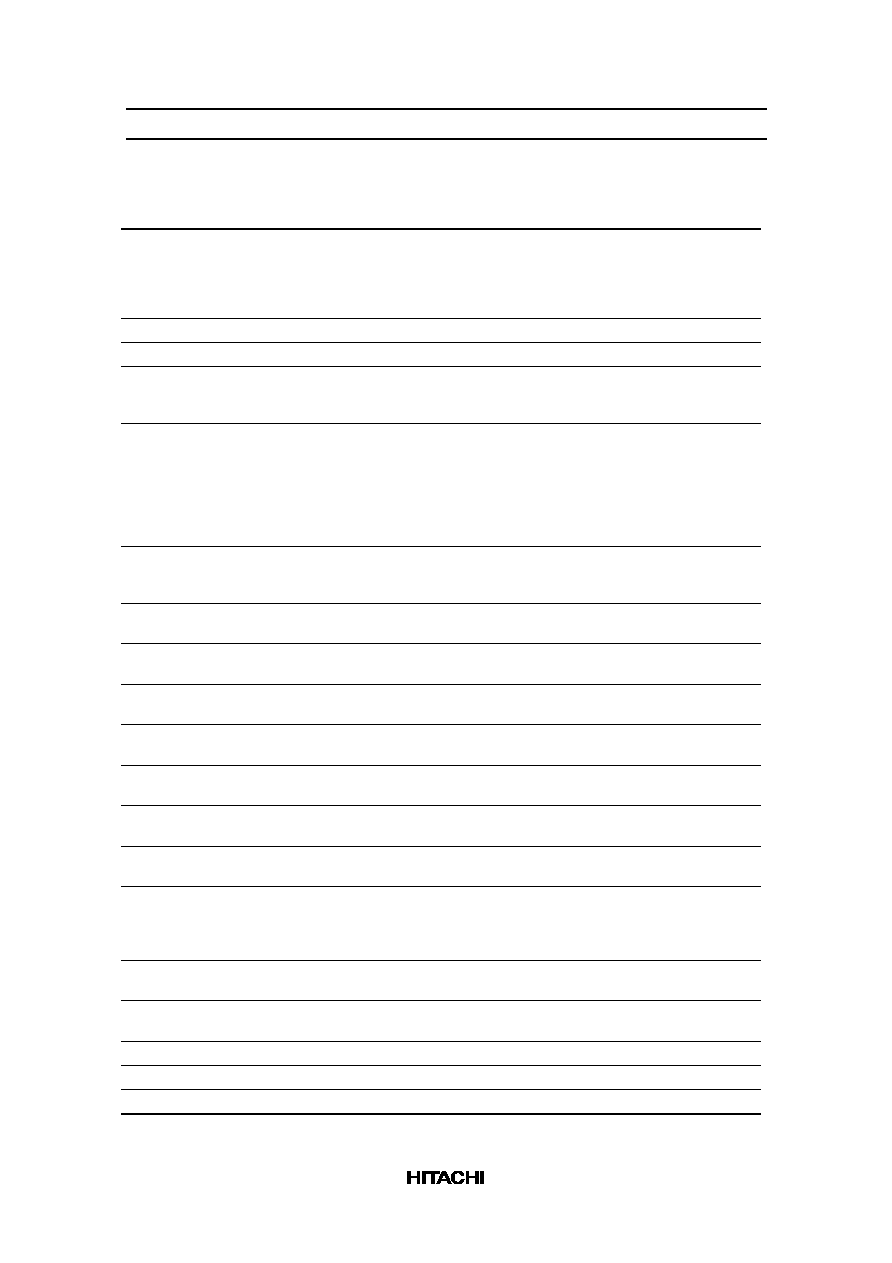

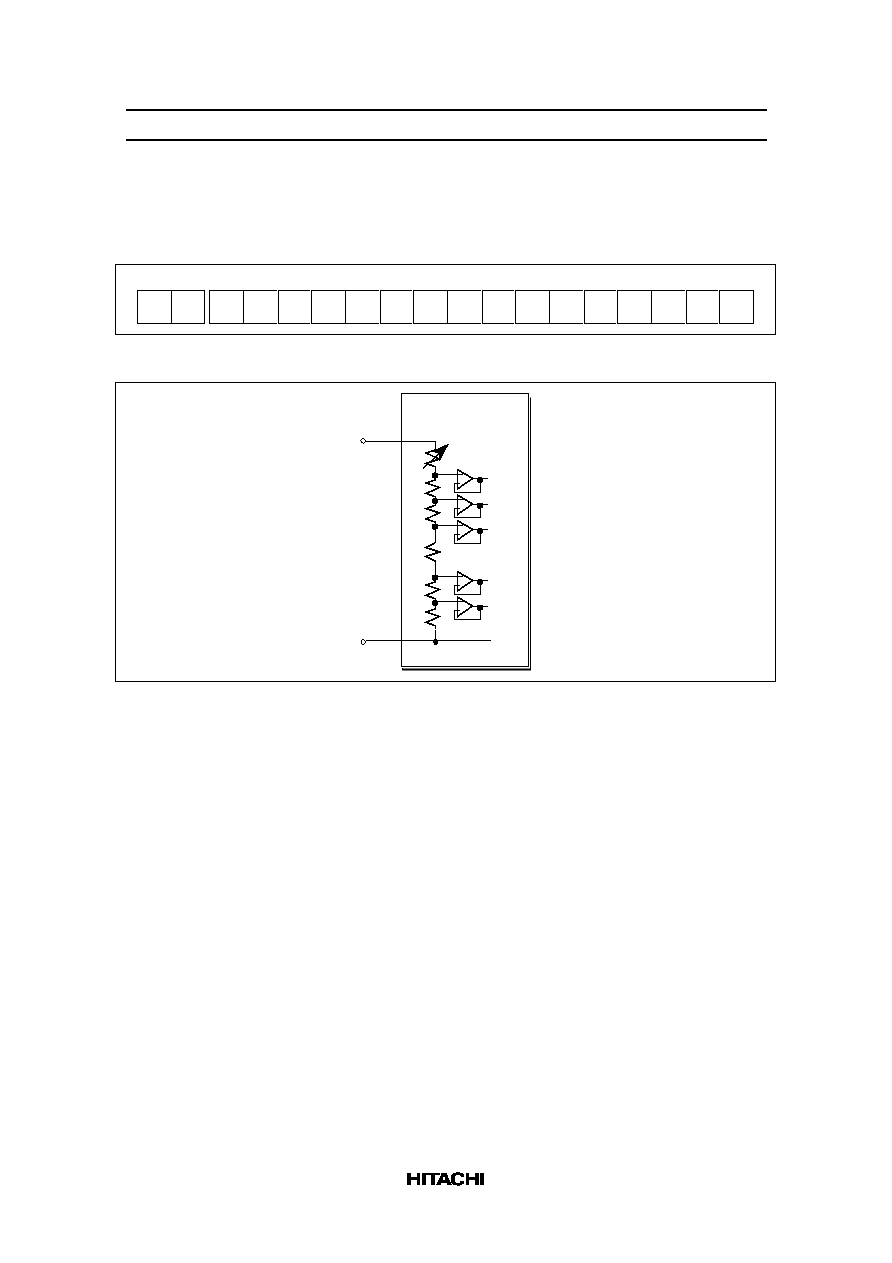

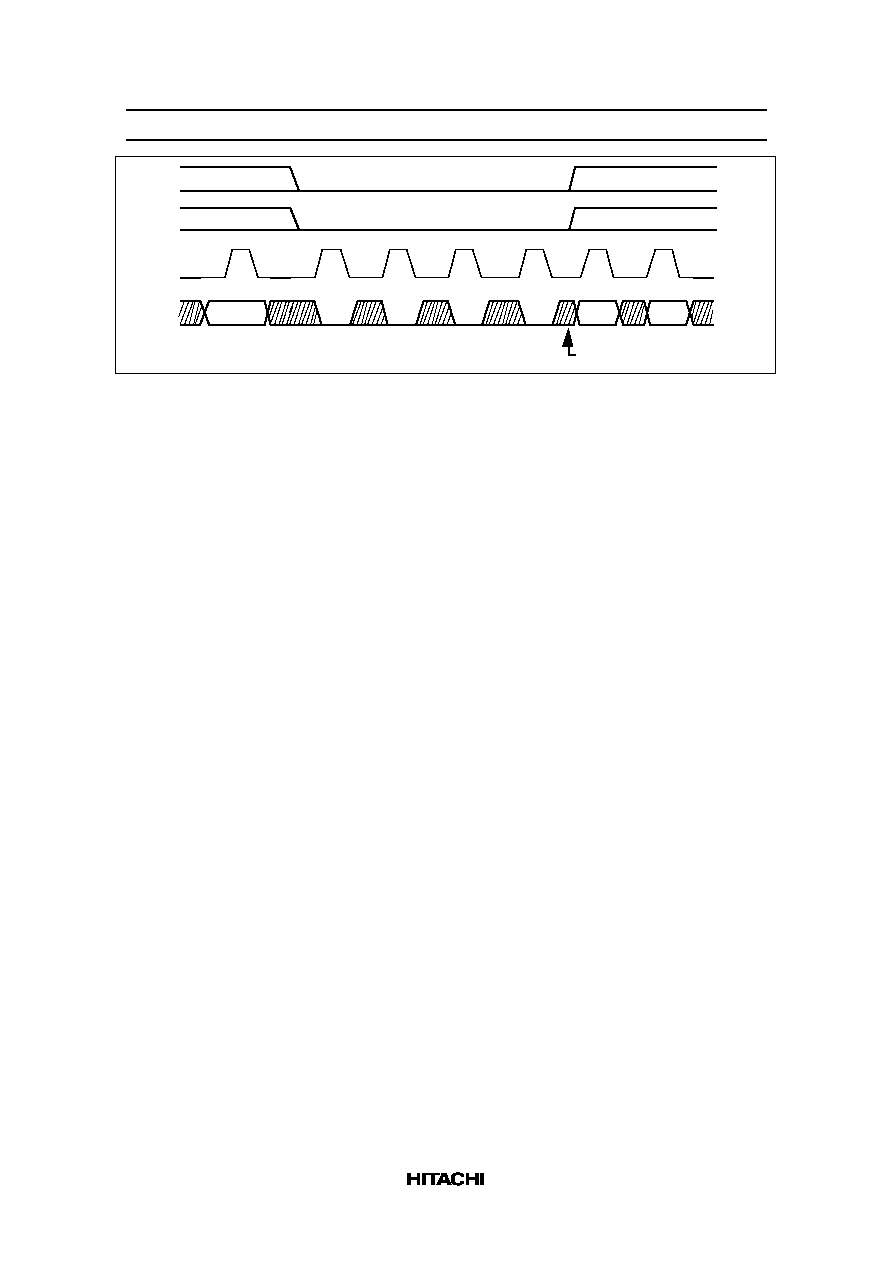

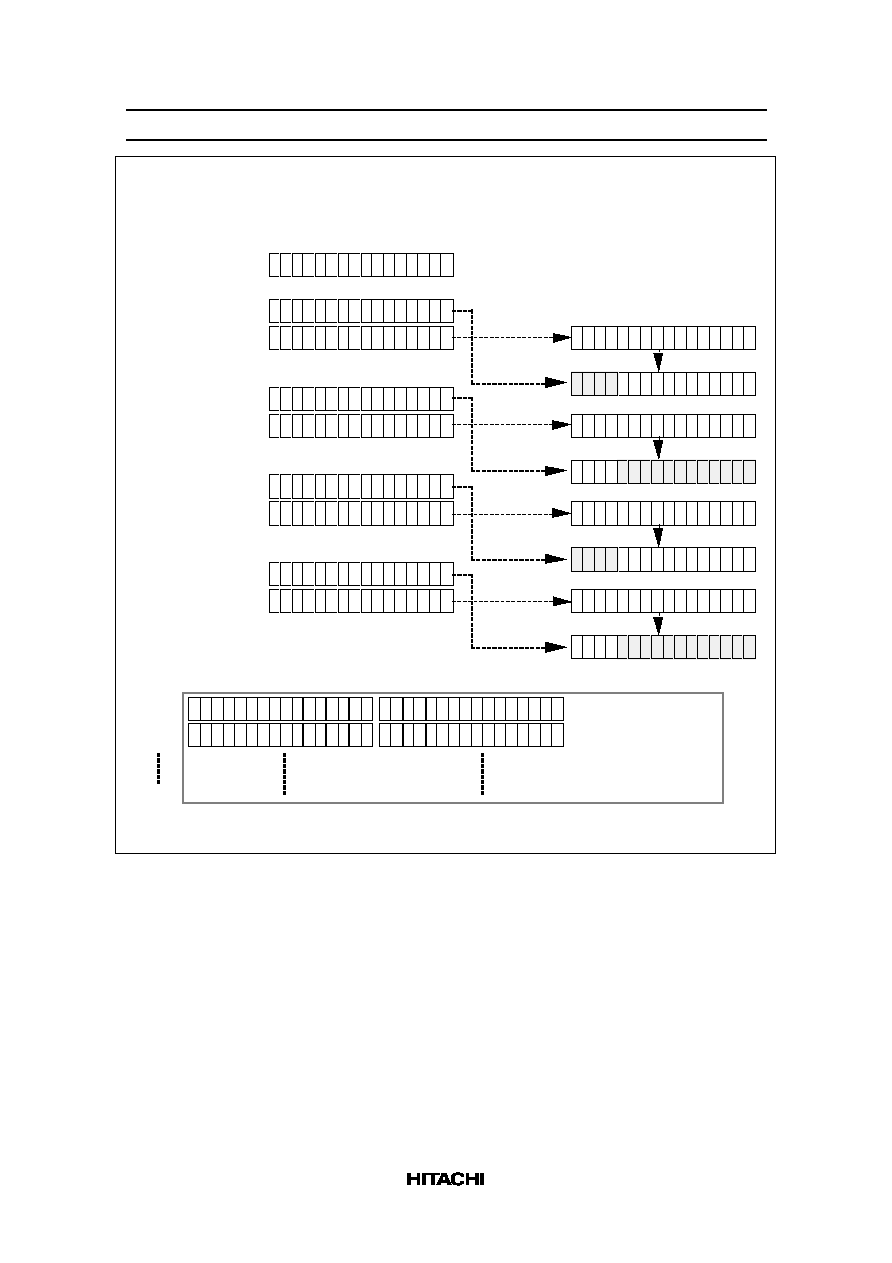

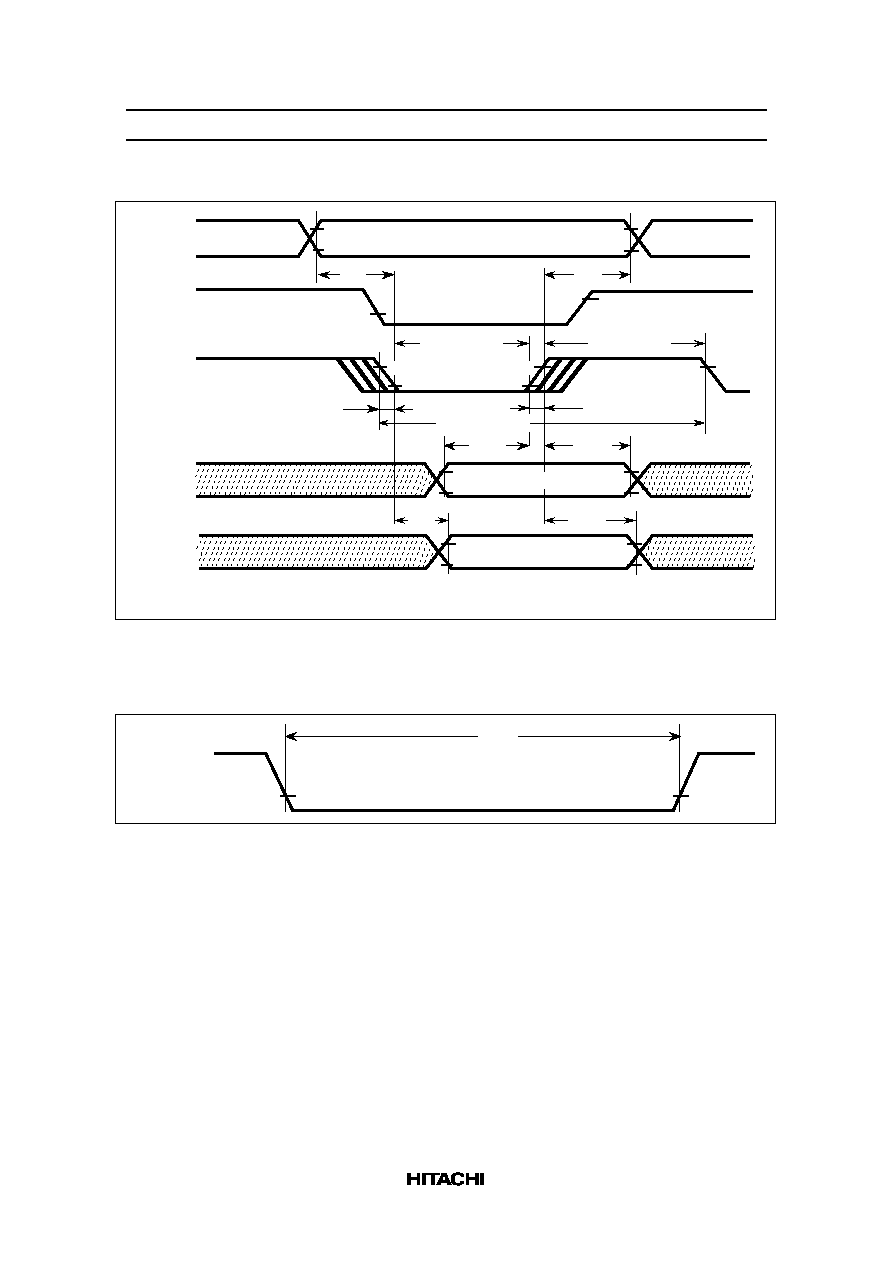

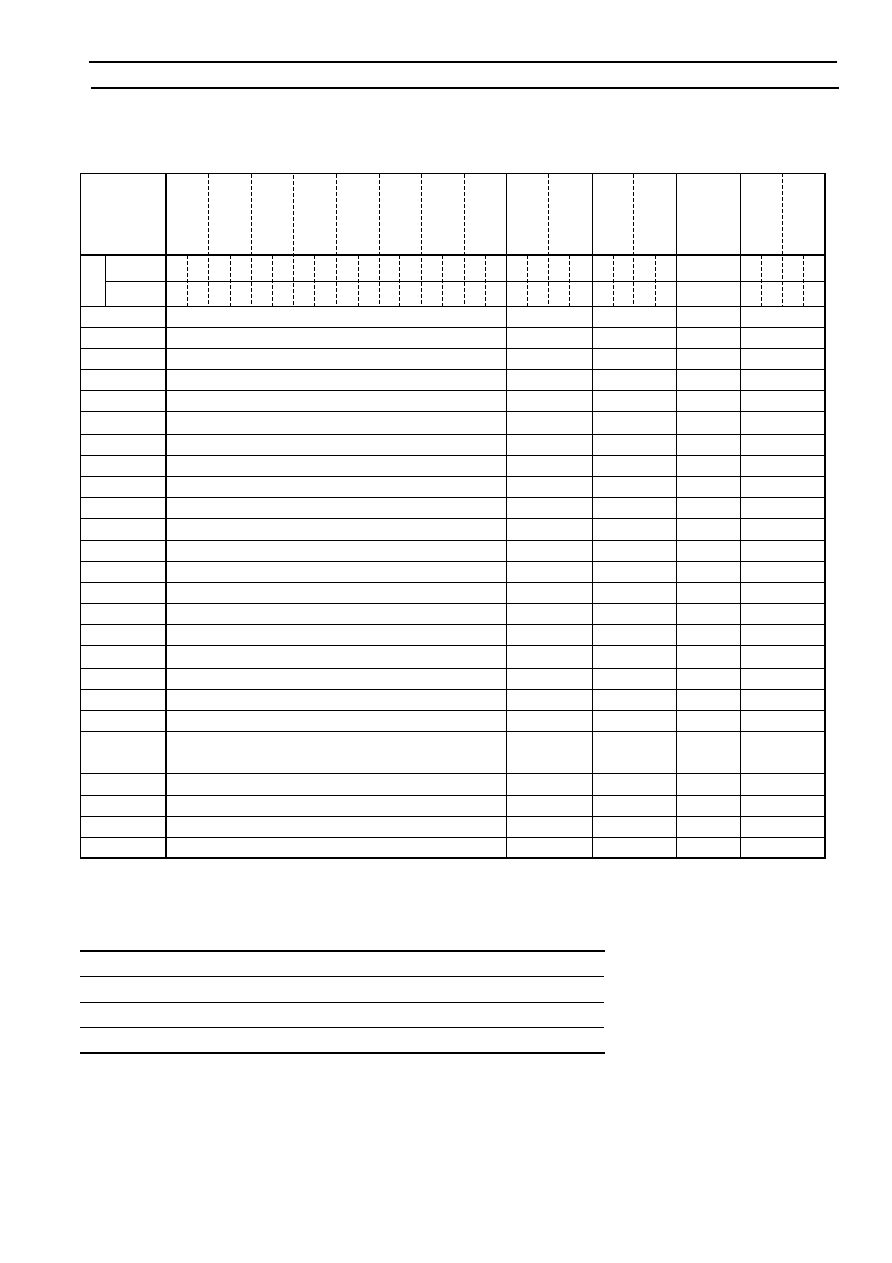

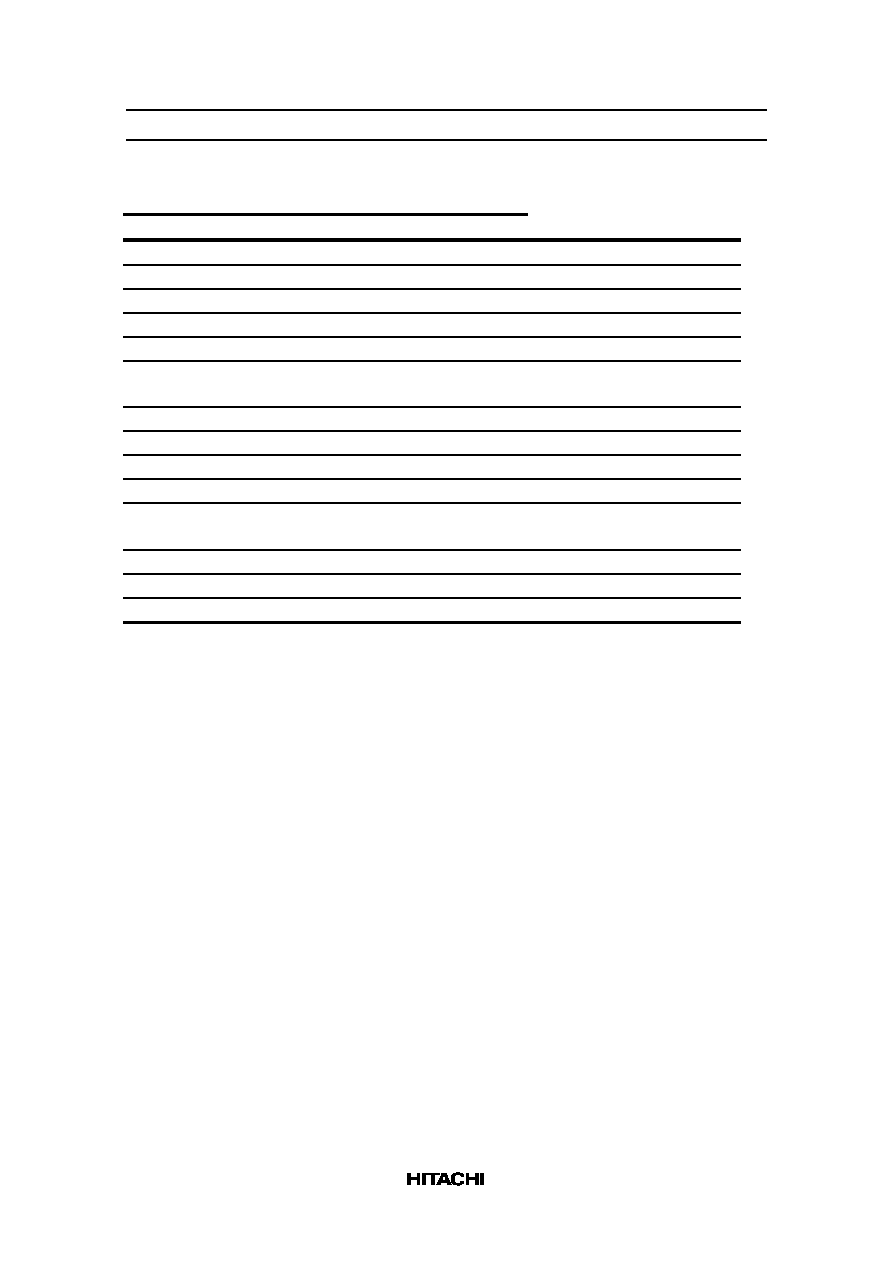

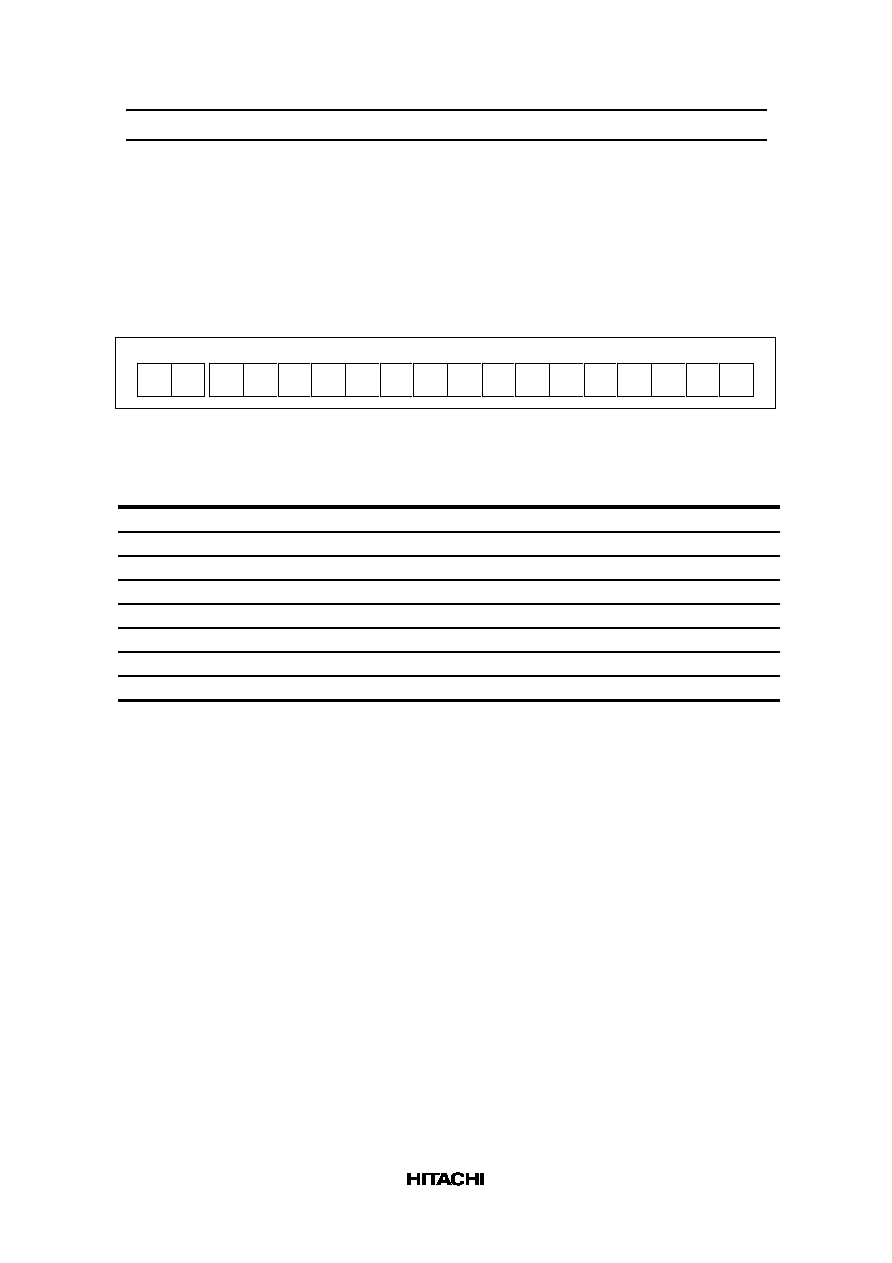

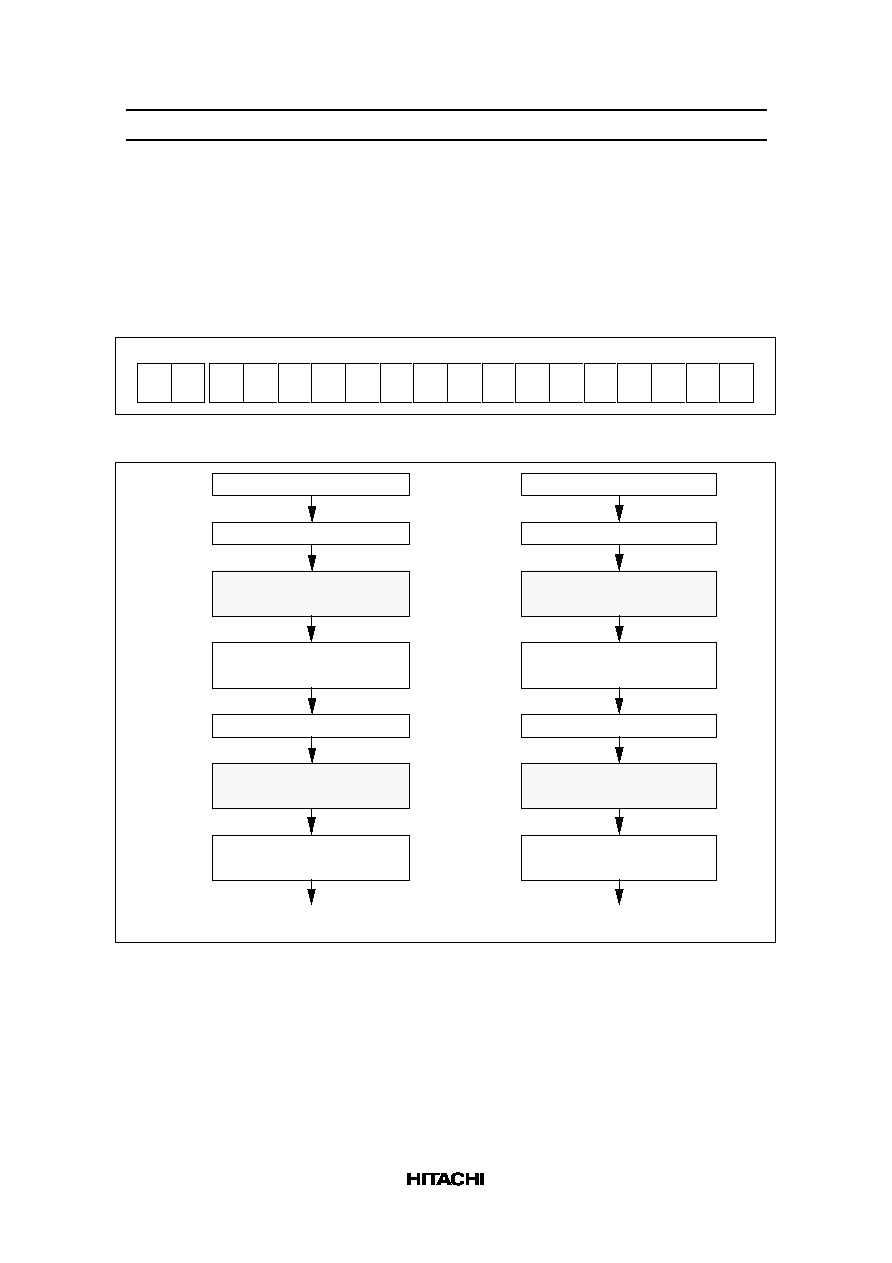

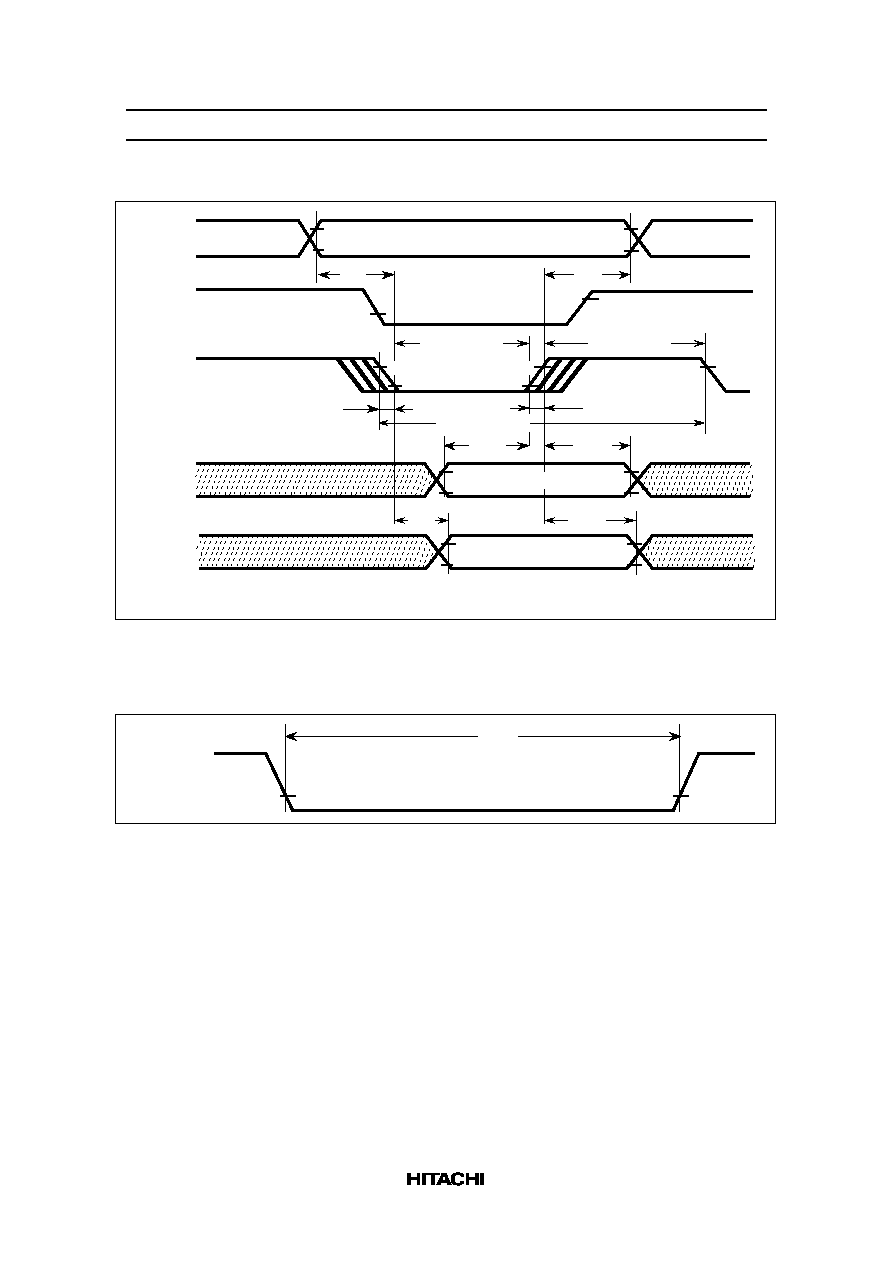

TCP Dimensions (HD66750TB0)

(SEG126/3)

(COM128/1)

SEG127/2

Bending slit

4.0 mm

COM1/128

COM16/113

SEG128/1

SEG1/128

COM17/112

0.14-mm

pitch

H

H

I

I

T

T

A

A

C

C

H

H

I

I

H

H

D

D

6

6

6

6

7

7

5

5

0

0

COM65/64

COM104/25

IM1

IM0

OPOFF

TEST

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

RESET*

CS*

RS

E/WR*

RW/RD*

GND

OSC2

OSC1

Vcc

Vci

C2+

C2-

C1+

C1-

VLOUT

VLCD

V1OUT

V2OUT

V3OUT

V4OUT

V5OUT

VTEST

0.65-mm

pitch

Dummy

Dummy

C3+

C3-

COM128/1

COM113/16

COM64/65

SEG126/3

SEG125/4

SEG2/127

SEG3/126

SEG4/125

C4+

C4-

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

C5+

C5-

C6+

C6-

(SEG128/1)

(SEG1/128)

(COM1/128)

(Dummy)

(Dummy)

(SEG127/2

(SEG125/4)

(SEG2/127)

(SEG3/126)

(SEG4/125)

(COM127/2)

(COM126/3)

(COM2/127)

(COM3/126)

HD66750

(HD66751)

I/O, Power supply

0.65P x (50 - 1)

= 31.85 mm

LCD drive

0.12P x (258 - 1)

= 30.784 mm

HD66750/1

14

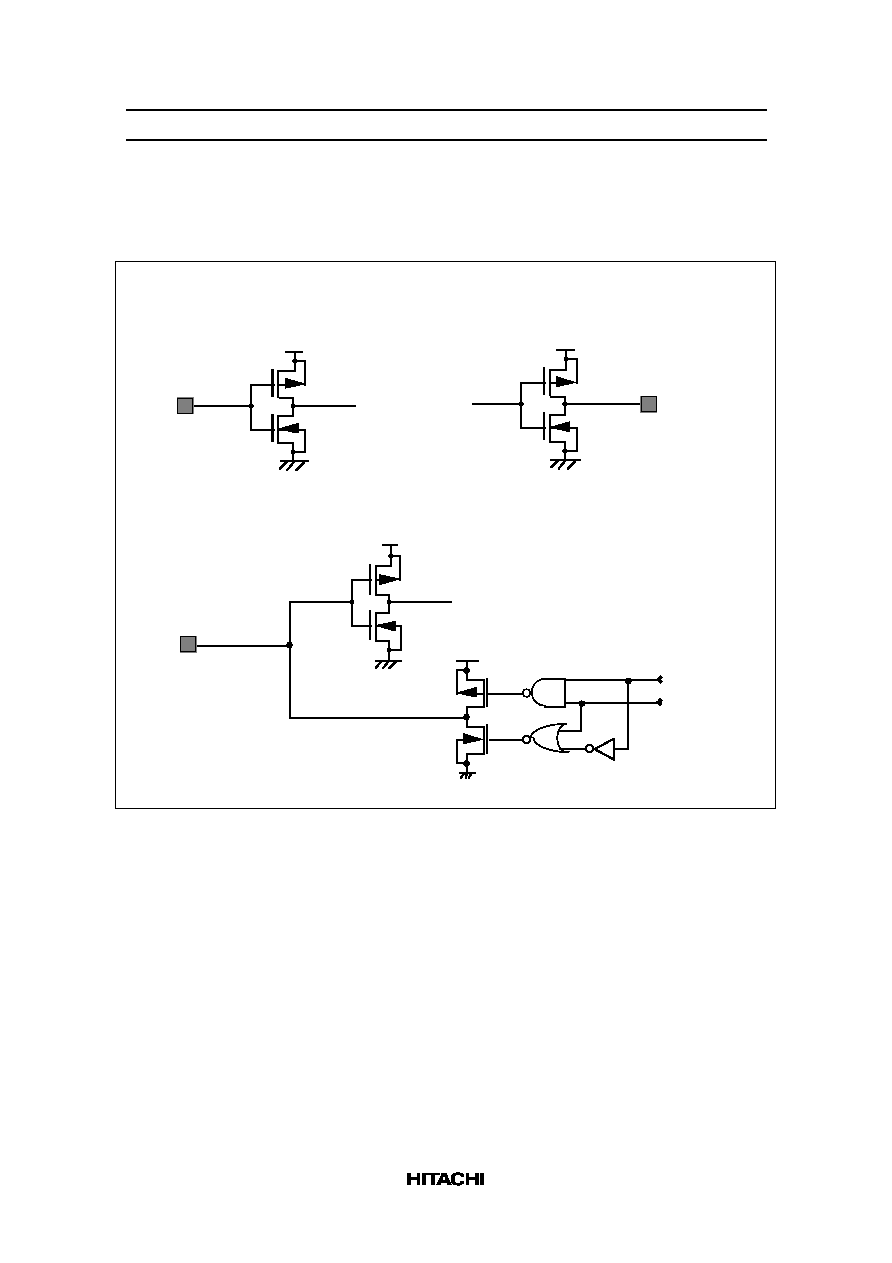

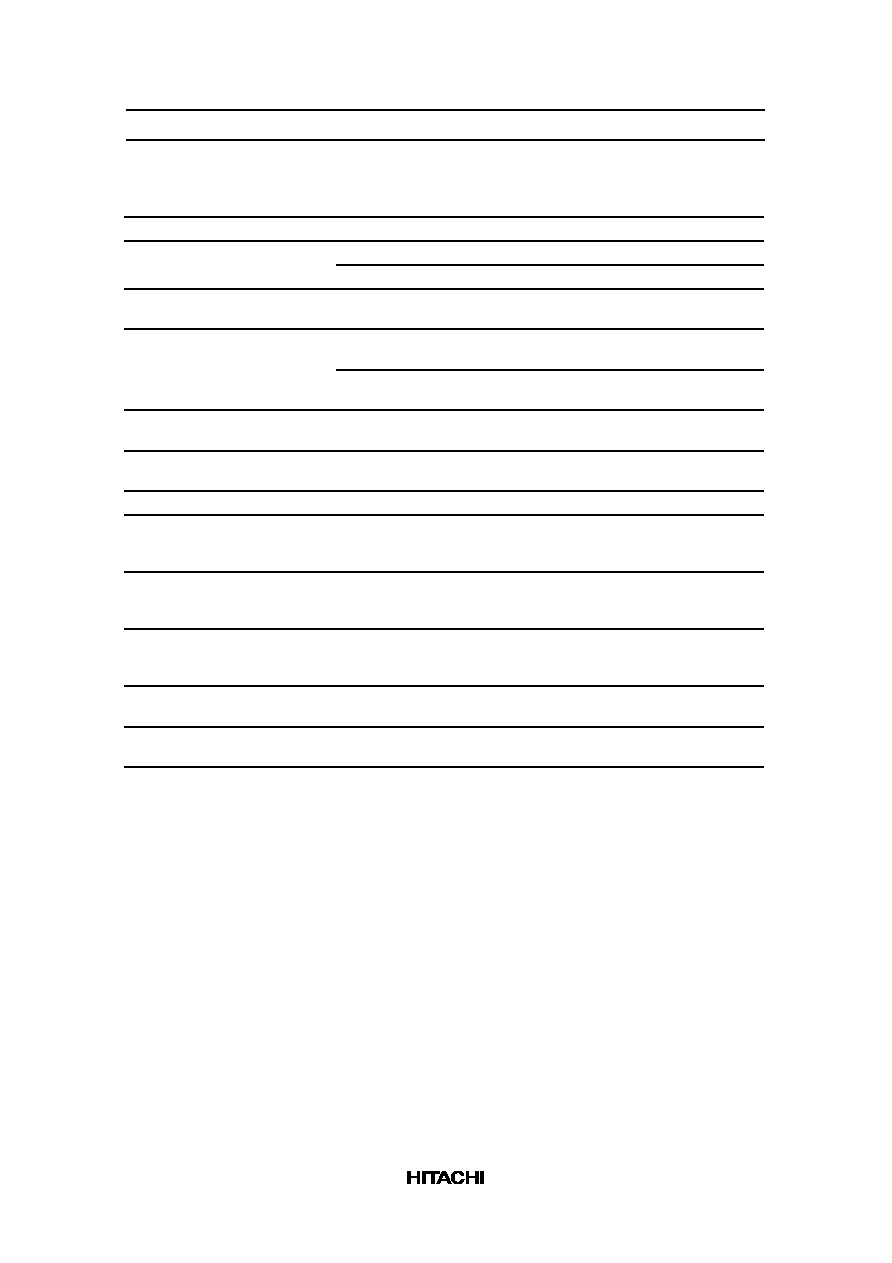

Pin Functions

Table 2

Pin Functional Description

Signals

Number of

Pins

I/O

Connected to

Functions

IM1, IM0

2

I

GND or V

CC

Selects the MPU interface mode:

IM1

GND

GND

Vcc

Vcc

IM0

GND

Vcc

GND

Vcc

MPU interface mode

68-system 16-bit bus interface

68-system 8-bit bus interface

80-system 16-bit bus interface

80-system 8-bit bus interface

CS*

1

I

MPU

Selects the HD66750/1:

Low: HD66750/1 is selected and can be accessed

High: HD66750/1 is not selected and cannot be

accessed

Must be fixed at GND level when not in use.

RS

1

I

MPU

Selects the register.

Low: Index/status High: Control

E/WR*

1

I

MPU

For a 68-system bus interface, serves as an enable

signal to activate data read/write operation.

For an 80-system bus interface, serves as a write

strobe signal and writes data at the low level.

RW/RD*

1

I

MPU

For a 68-system bus interface, serves as a signal to

select data read/write operation.

Low: Write High: Read

For an 80-system bus interface, serves as a read

strobe signal and reads data at the low level.

DB0–DB15

16

I/O

MPU

Serves as a 16-bit bidirectional data bus.

For an 8-bit bus interface, data transfer uses DB15-

DB8; fix unused DB7-DB0 to the Vcc or GND level.

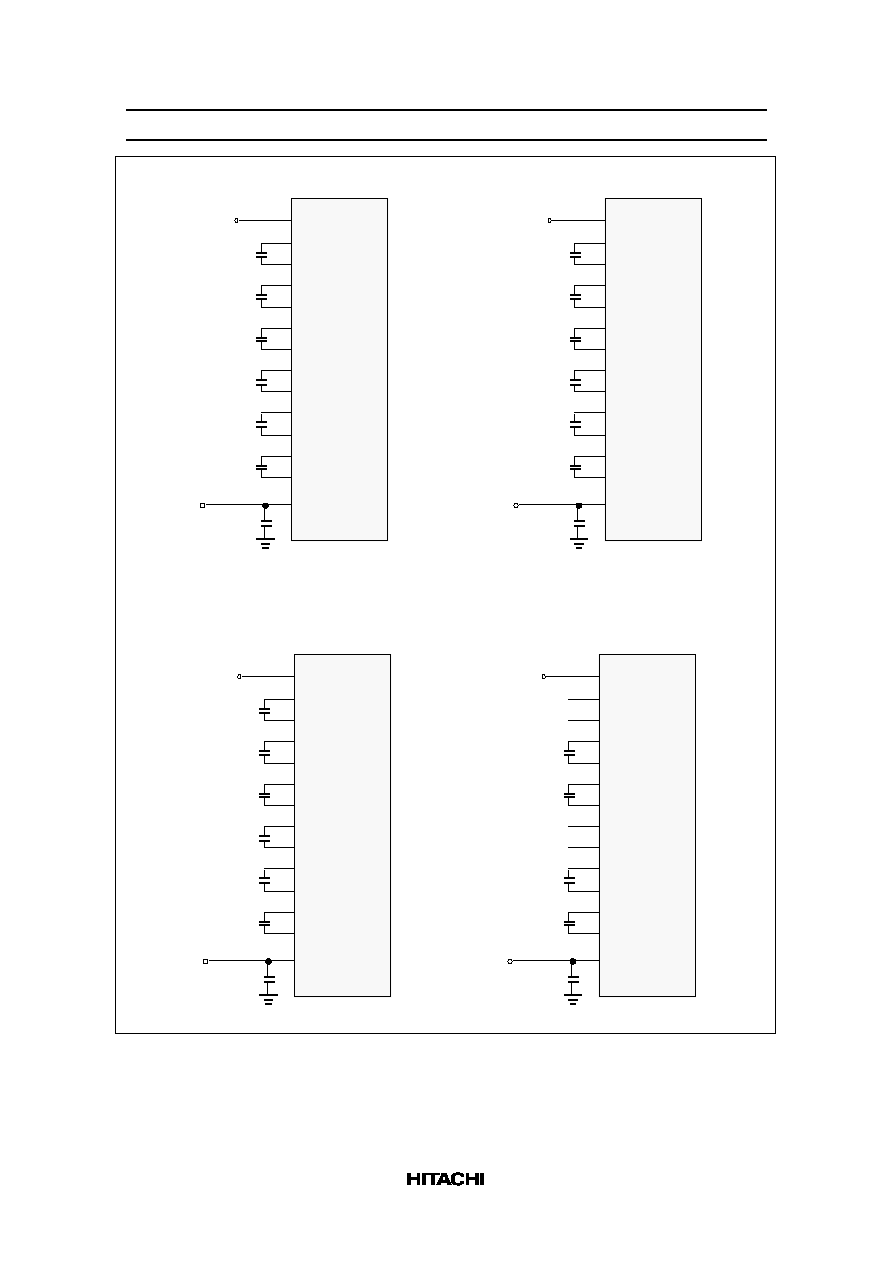

COM1/128–

COM128/1

128

O

LCD

Output signals for common drive: All the unused pins

output unselected waveforms. In the display-off

period (D = 0), sleep mode (SLP = 1), or standby

mode (STB = 1), all pins output GND level.

The CMS bit can change the shift direction of the

common signal. For example, if CMS = 0, COM1/128

is COM1, and COM128/1 is COM128. If CMS = 1,

COM1/128 is COM128, and COM128/1 is COM1.

Note that the start position of the common output is

shifted by CN1–CN0 bits.

SEG1/128–

SEG128/1

128

O

LCD

Output signals for segment drive. In the display-off

period (D = 0), sleep mode (SLP = 1), or standby

mode (STB = 1), all pins output GND level.

The SGS bit can change the shift direction of the

segment signal. For example, if SGS = 0, SEG1/128

is SEG1. If SGS = 1, SEG1/128 is SEG128.

HD66750/1

15

Table 2

Pin Functional Description (cont)

Signals

Number

of Pins

I/O

Connected

to

Functions

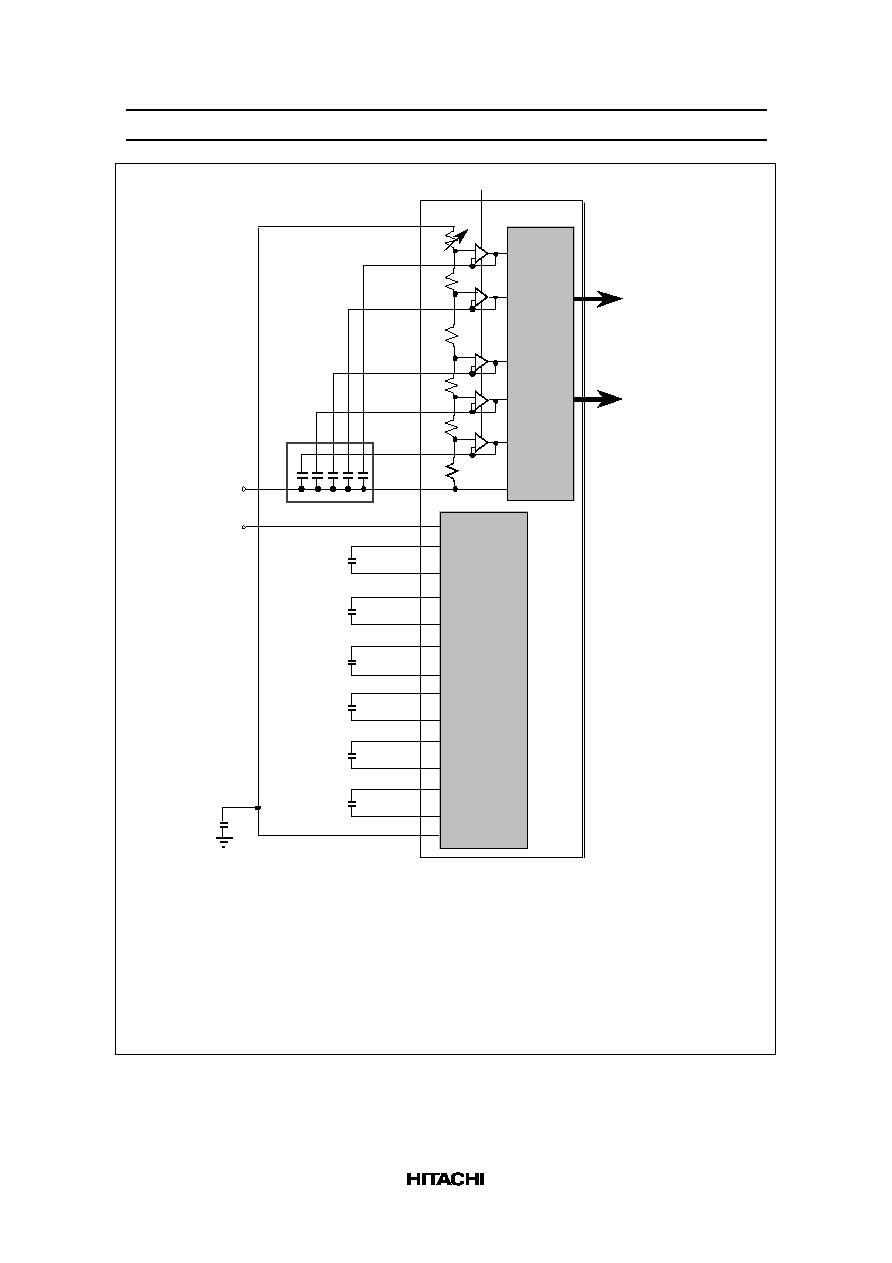

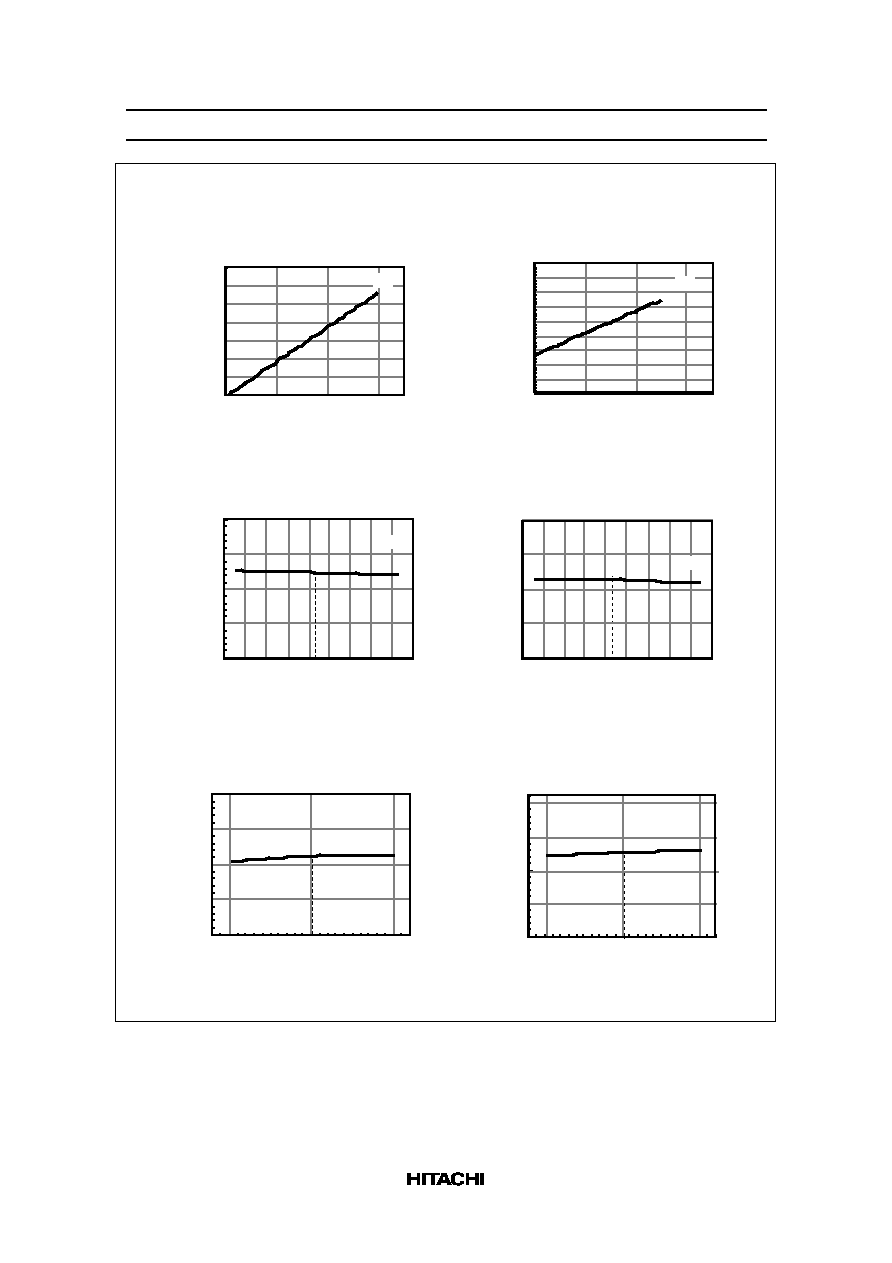

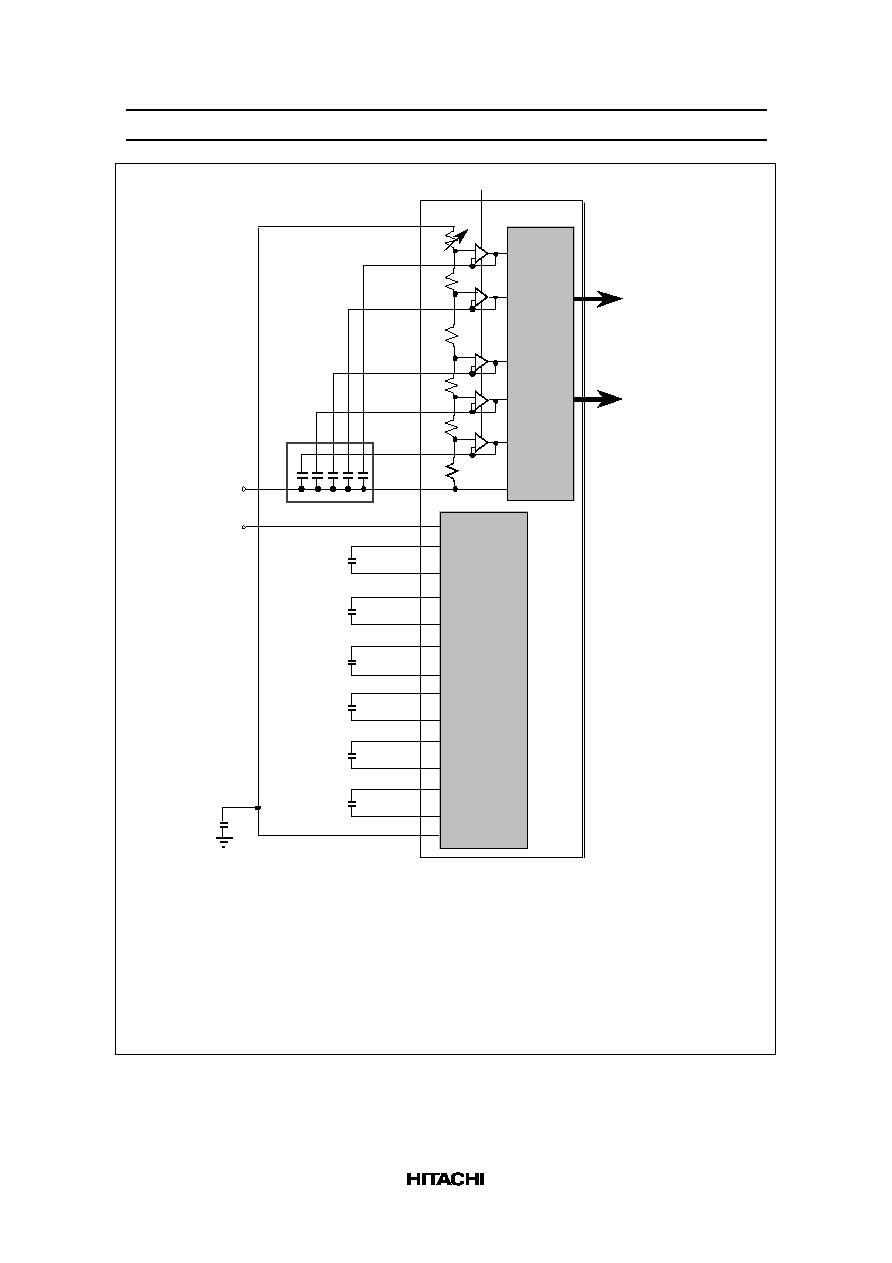

V1OUT≠

V5OUT

5

I or O

Open or

external

bleeder-resistor

Used for output from the internal operational

amplifiers when they are used (OPOFF = GND); attach

a capacitor to stabilize the output. When the

amplifiers are not used (OPOFF = V

CC

), V1 to V5

voltages can be supplied to these pins externally.

V

LCD

1

--

Power supply

Power supply for LCD drive. V

LCD

≠

GND = 17 V max.

V

CC

, GND

2

--

Power supply

V

CC

: +1.8 V to +5.5 V; GND (logic): 0 V

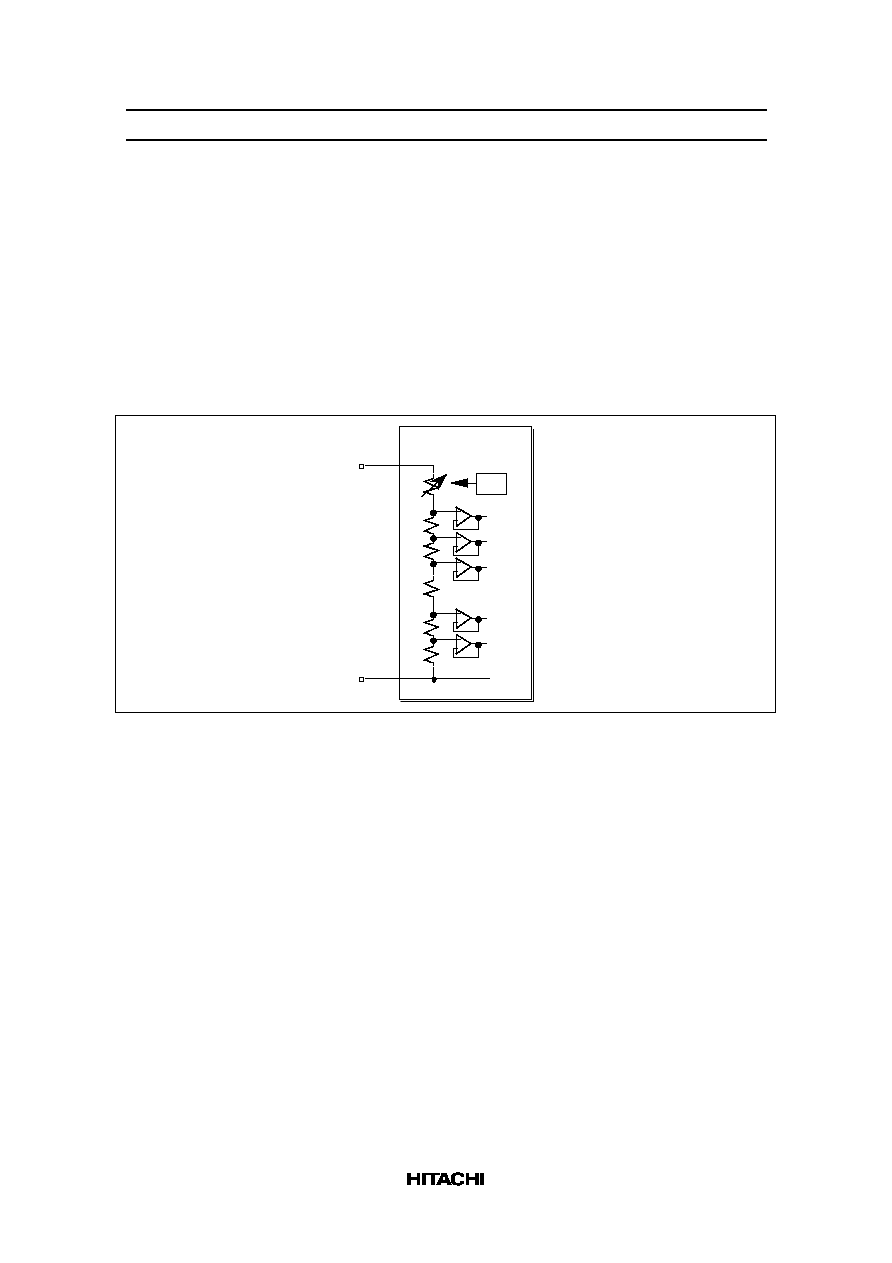

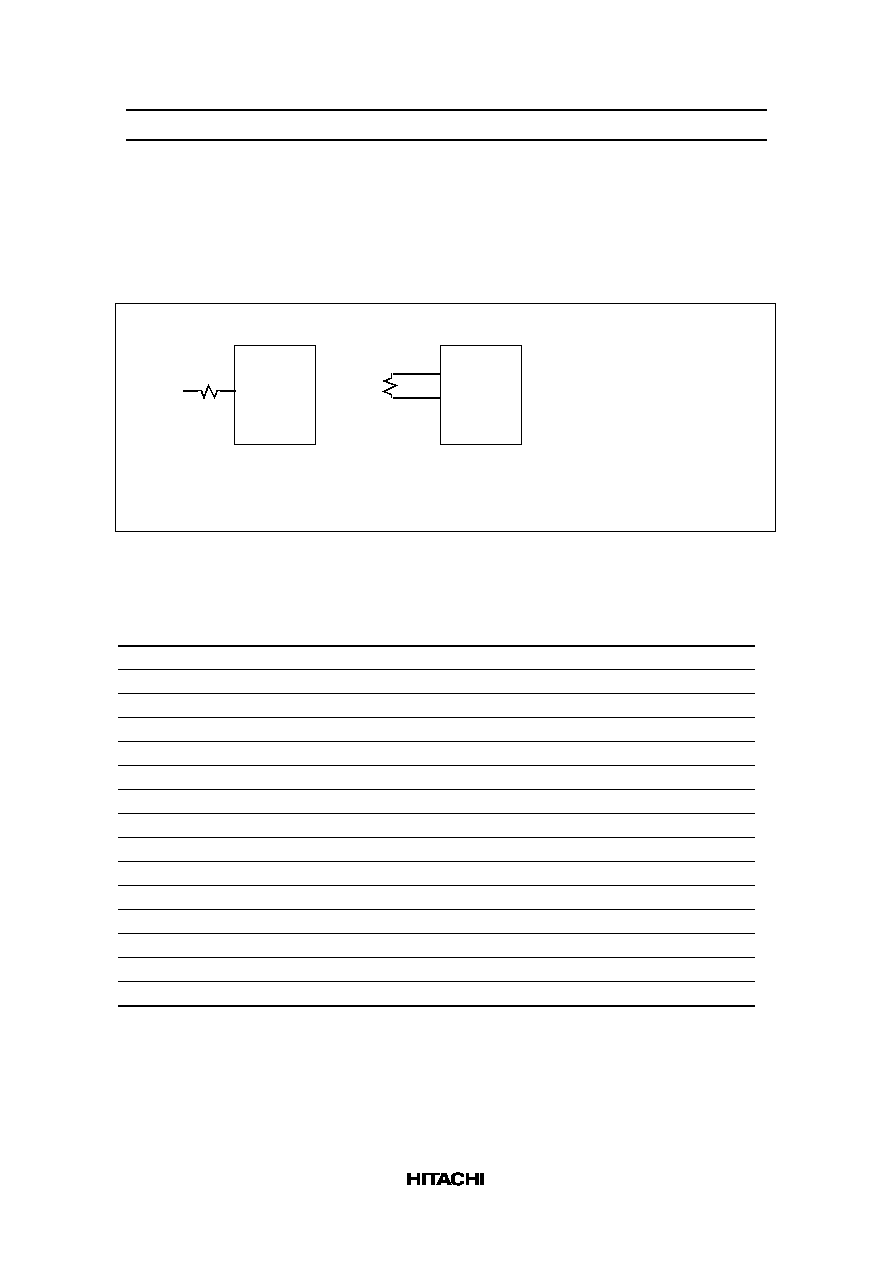

OSC1,

OSC2

2

I or O

Oscillation-

resistor or clock

For R-C oscillation using an external resistor, connect

an external resistor. For external clock supply, input

clock pulses to OSC1.

Vci

1

I

Power supply

Inputs a reference voltage and supplies power to the

booster; generates the liquid crystal display drive

voltage from the operating voltage. The boosting

output voltage must not be larger than the absolute

maximum ratings.

Must be left disconnected when the booster is not

used.

VLOUT

1

O

V

LCD

pin/booster

capacitance

Potential difference between Vci and GND is two- to

seven-times-boosted and then output. Magnitude of

boost is selected by instruction.

C1+, C1≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C2+, C2≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C3+, C3≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C4+, C4≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C5+, C5≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

C6+, C6≠

2

--

Booster

capacitance

External capacitance should be connected here for

boosting.

RESET*

1

I

MPU or external

R-C circuit

Reset pin. Initializes the LSI when low. Must be reset

after power-on.

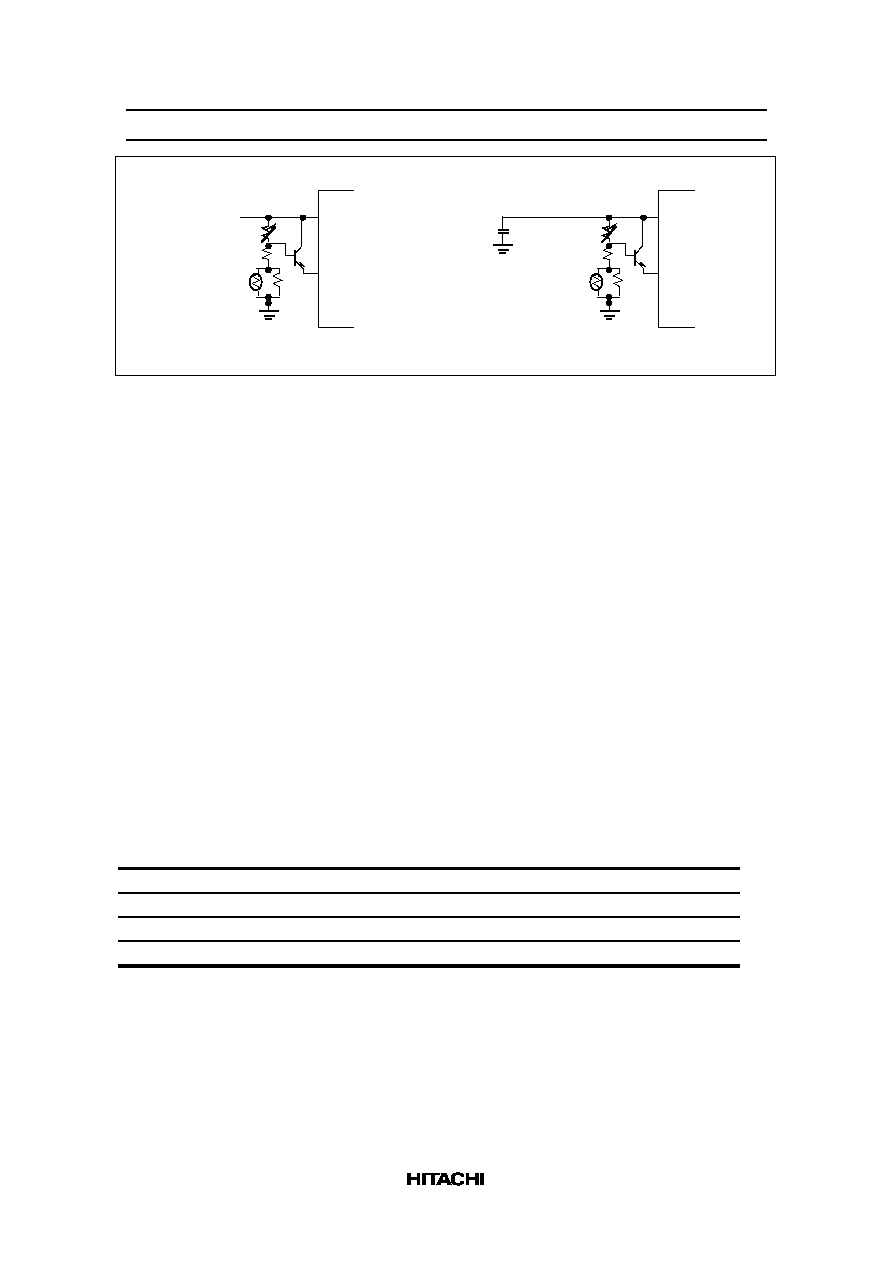

OPOFF

1

I

V

CC

or GND

Turns the internal operational amplifier off when

OPOFF = V

CC

, and turns it on when OPOFF = GND. If

the amplifier is turned off (OPOFF = V

CC

), V1 to V5

must be supplied to the V1OUT to V5OUT pins.

VccDUM

2

O

Input pins

Outputs the internal V

CC

level; shorting this pin sets the

adjacent input pin to the V

CC

level.

GNDDUM

4

O

Input pins

Outputs the internal GND level; shorting this pin sets

the adjacent input pin to the GND level.

Dummy

4

--

--

Dummy pad. Must be left disconnected.

TEST

1

I

GND

Test pin. Must be fixed at GND level.

VTEST

1

--

--

Test pin. Must be left disconnected.

HD66750/1

16

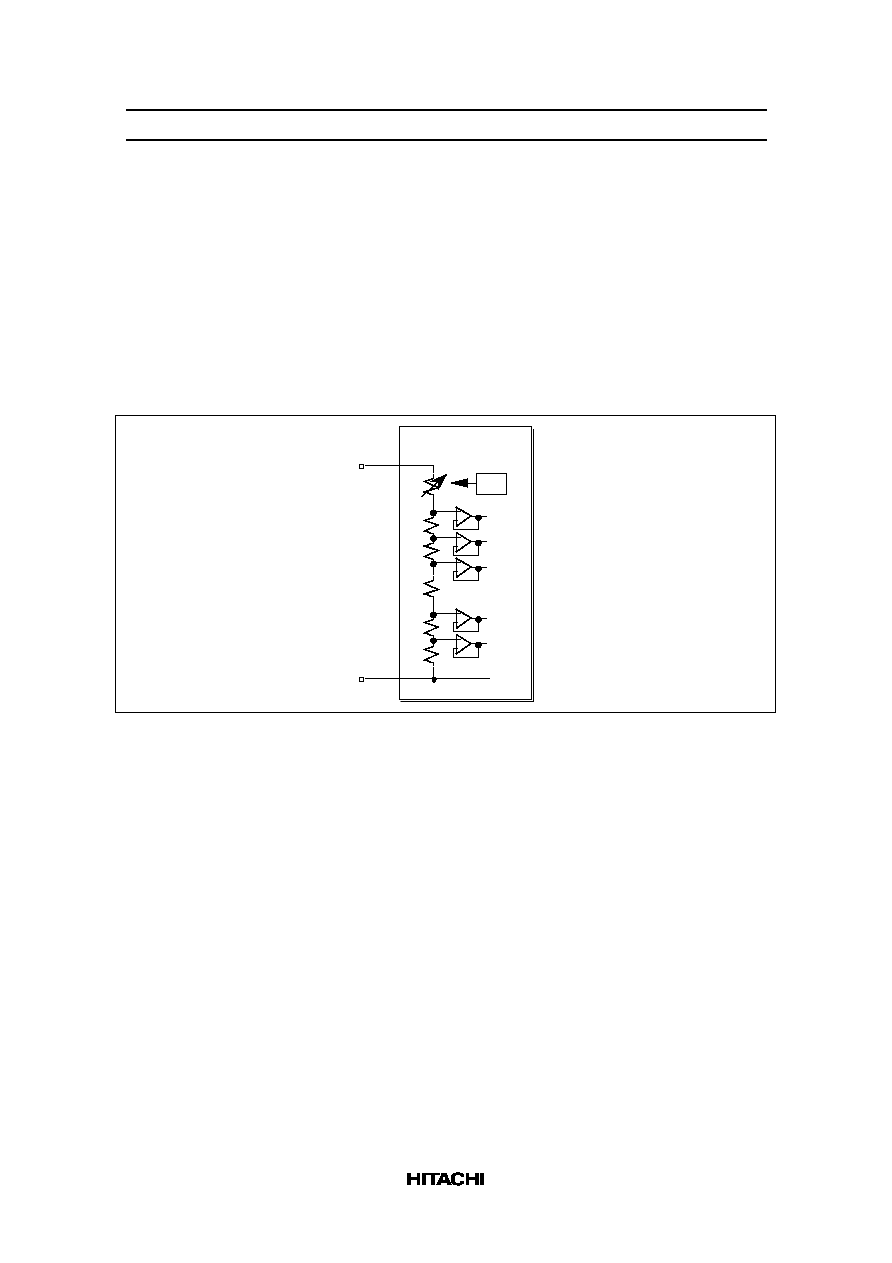

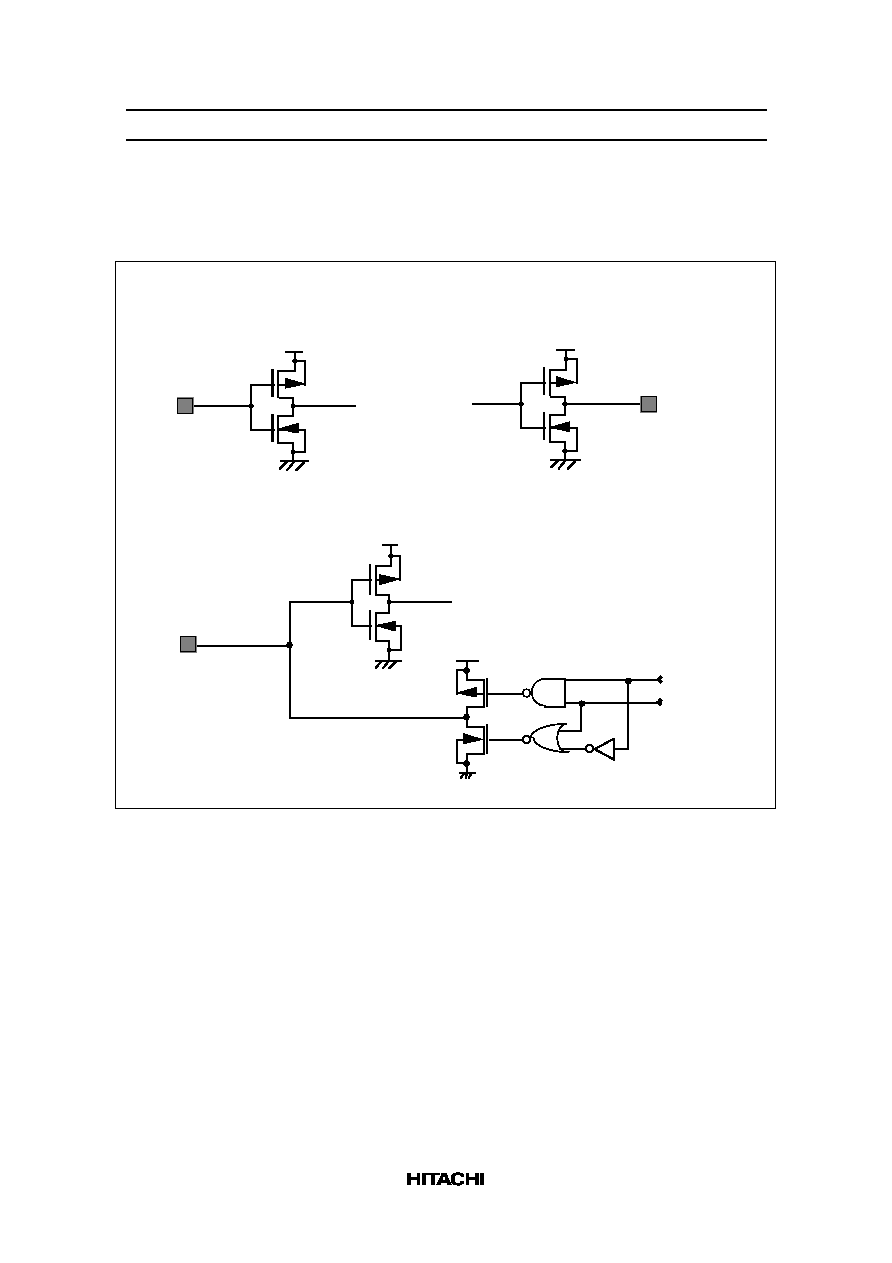

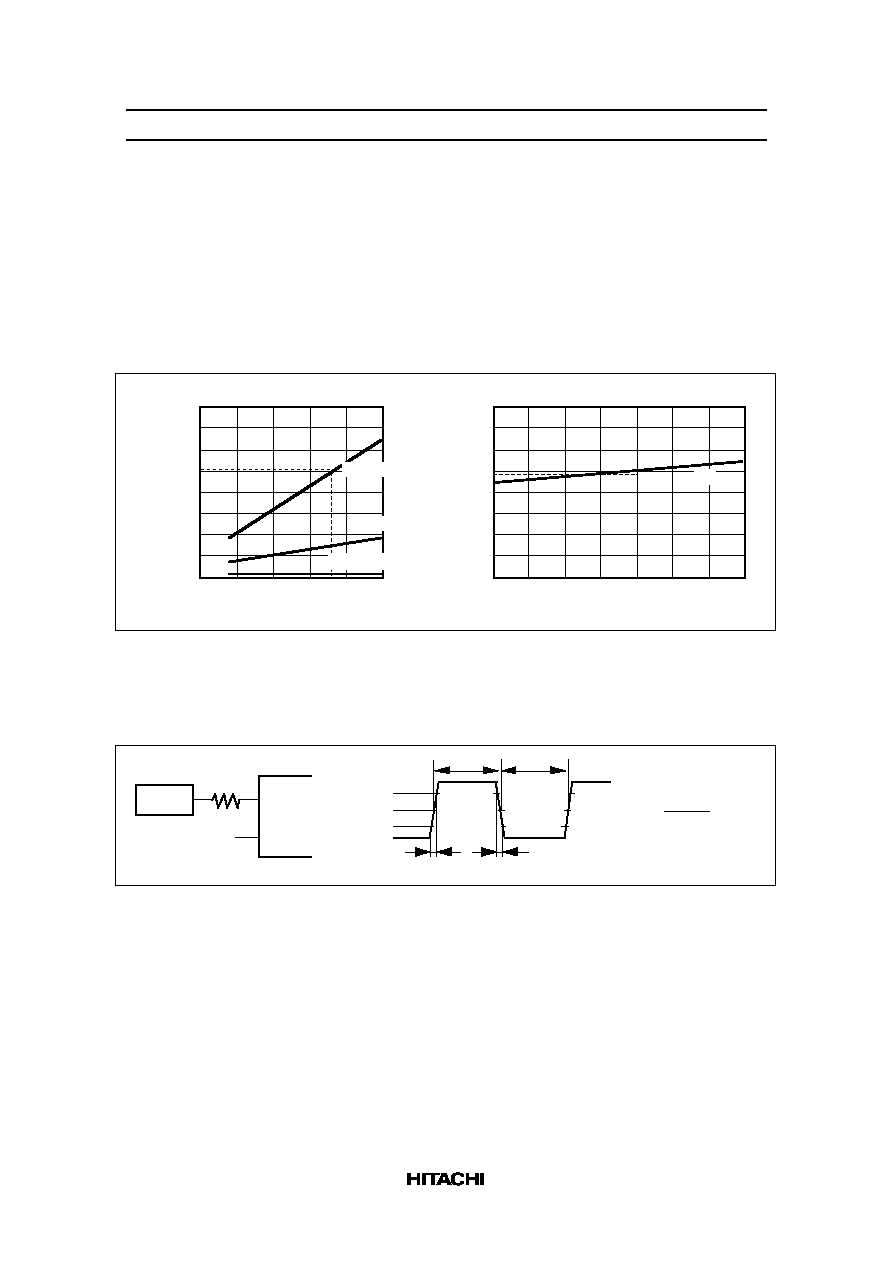

Block Function Description

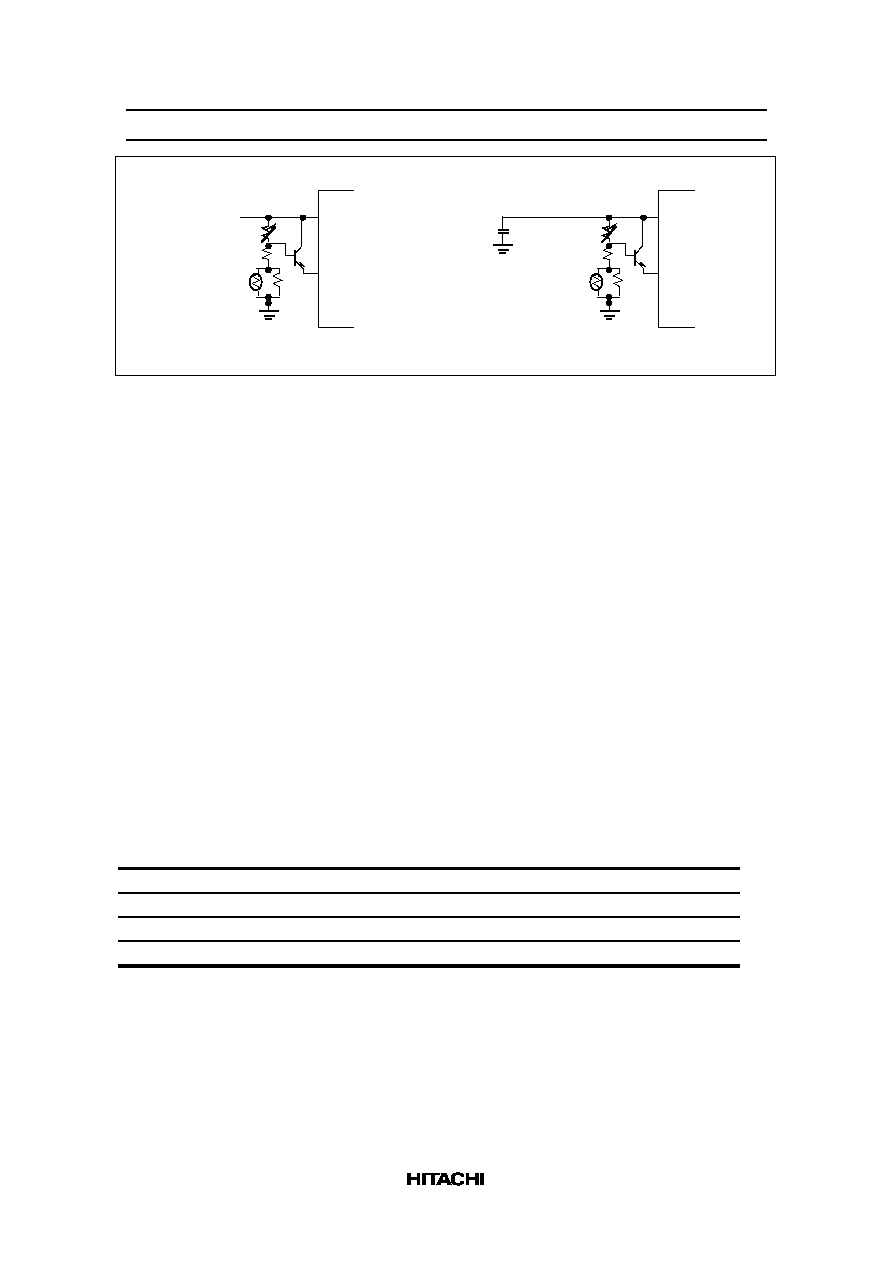

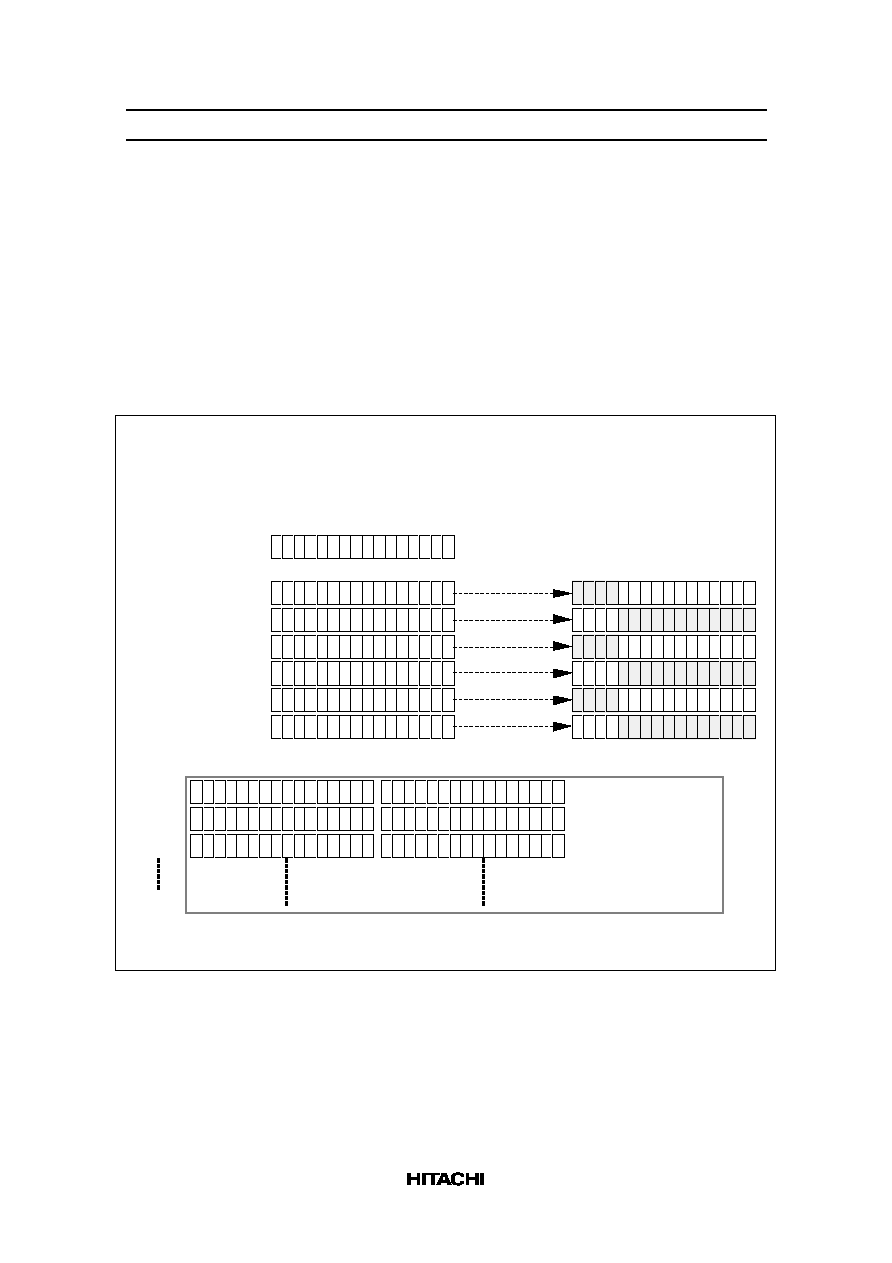

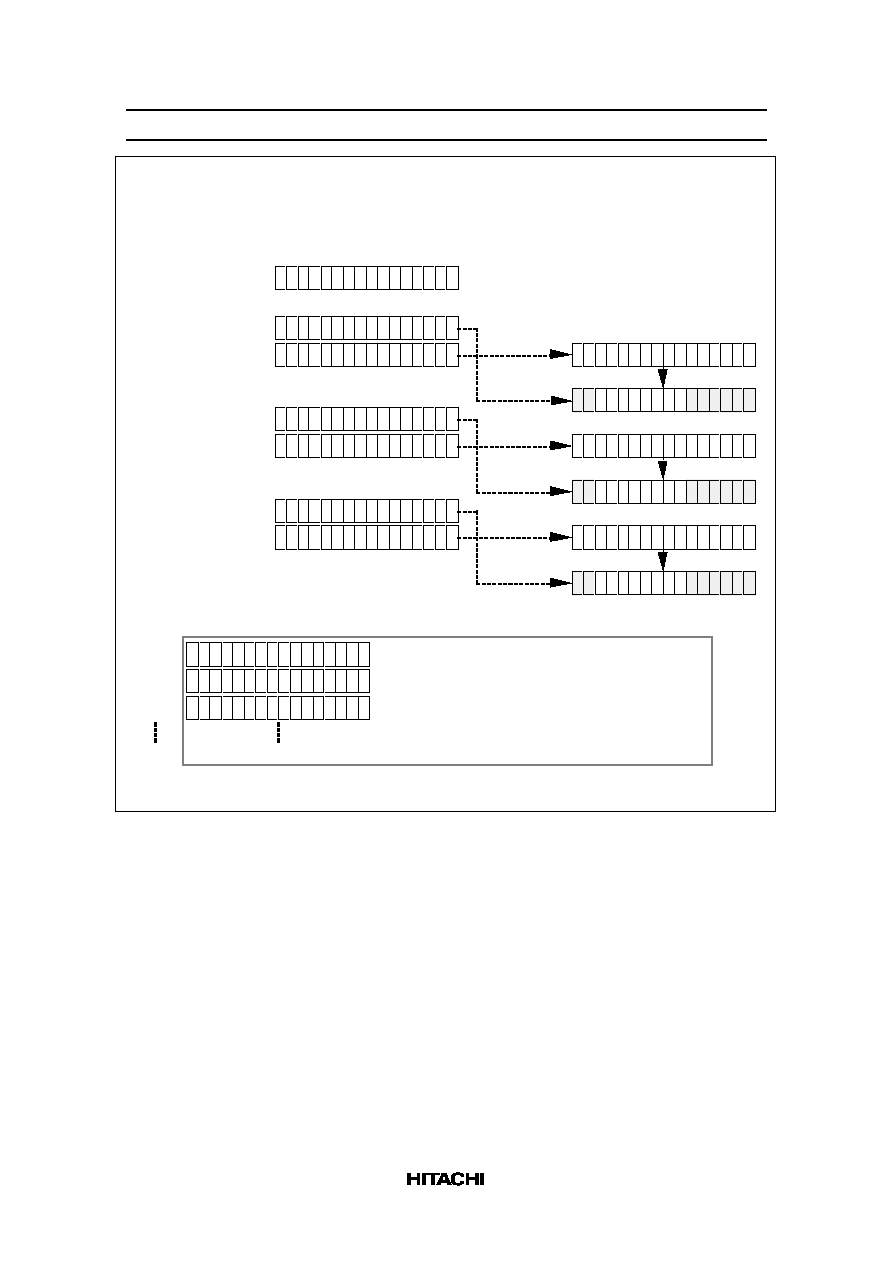

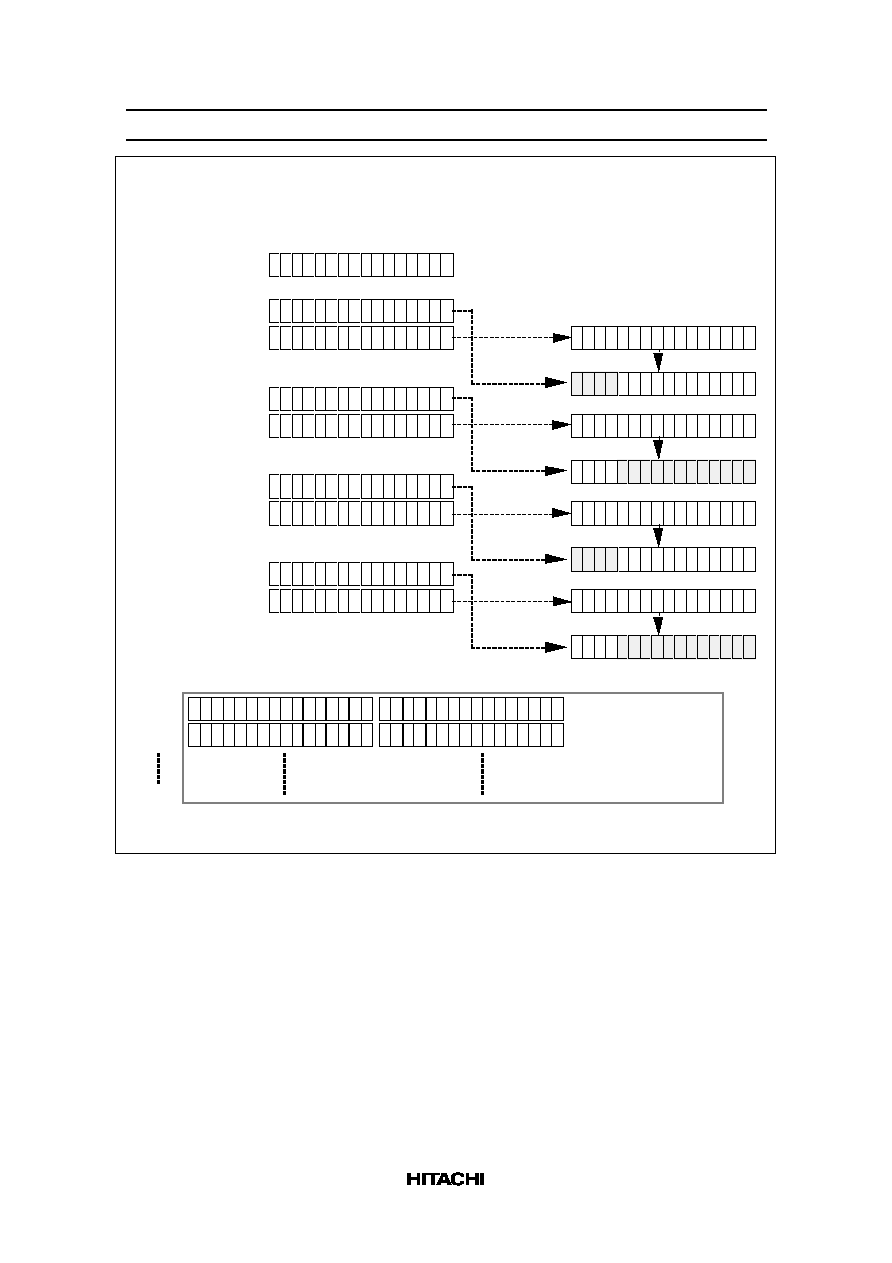

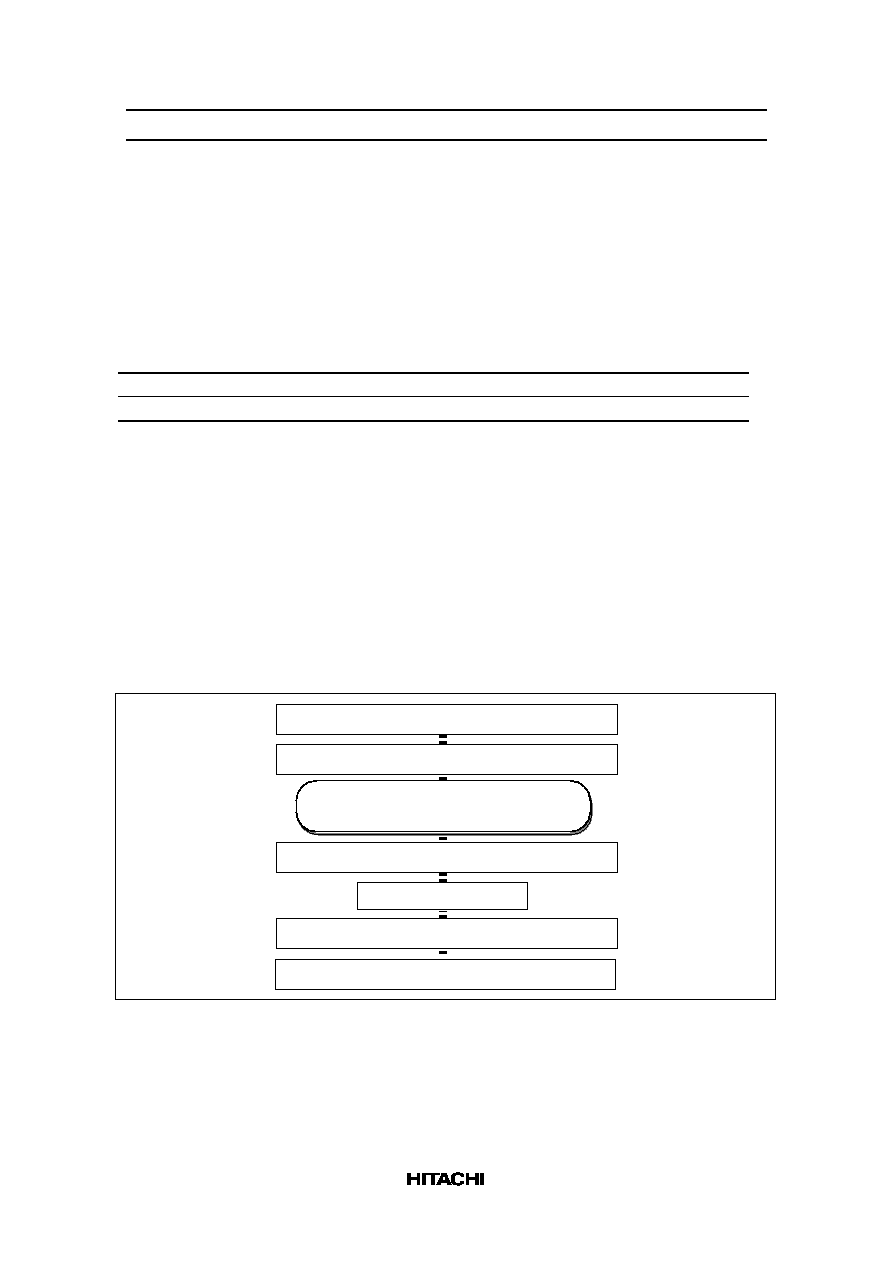

System Interface

The HD66750/1 has four high-speed system interfaces: an 80-system 16-bit/8-bit bus and a 68-system 16-

bit/8-bit bus. The interface mode is selected by the IM1-0 pins.

The HD66750/1 has three 16-bit registers: an index register (IR), a write data register (WDR), and a read

data register (RDR). The IR stores index information from the control registers and the CGRAM. The WDR

temporarily stores data to be written into control registers and the CGRAM, and the RDR temporarily stores

data read from the CGRAM. Data written into the CGRAM from the MPU is first written into the WDR and

then is automatically written into the CGRAM by internal operation. Data is read through the RDR when

reading from the CGRAM, and the first read data is invalid and the second and the following data are