| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HD74AC374 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

HD74AC374/HD74ACT374

Octal D-Type Flip-Flops with 3-State Output

Description

The HD74AC374/HD74ACT374 is a high-speed, low-power octal D-type flip-flop featuring separate D-

type inputs for each flip-flop and 3-state outputs for bus-oriented applications. A buffered Clock (CP) and

Output Enable (

OE) are common to all flip-flops.

Features

∑

Buffered Positive Edge-Triggered Clock

∑

3-State Outputs for Bus-Oriented Applications

∑

Outputs Source/Sink 24 mA

∑

See HD74AC273/HD74ACT273 for Reset Version

∑

See HD74AC373/HD74ACT373 for Transparent Latch Version

∑

See HD74AC574/HD74ACT574 for Broadside Pinout Version

∑

See HD74AC564/HD74ACT564 for Broadside

∑

Pinout Version with Inverted Outputs

∑

HD74ACT374 has TTL-Compatible Inputs

HD74AC374/HD74ACT374

2

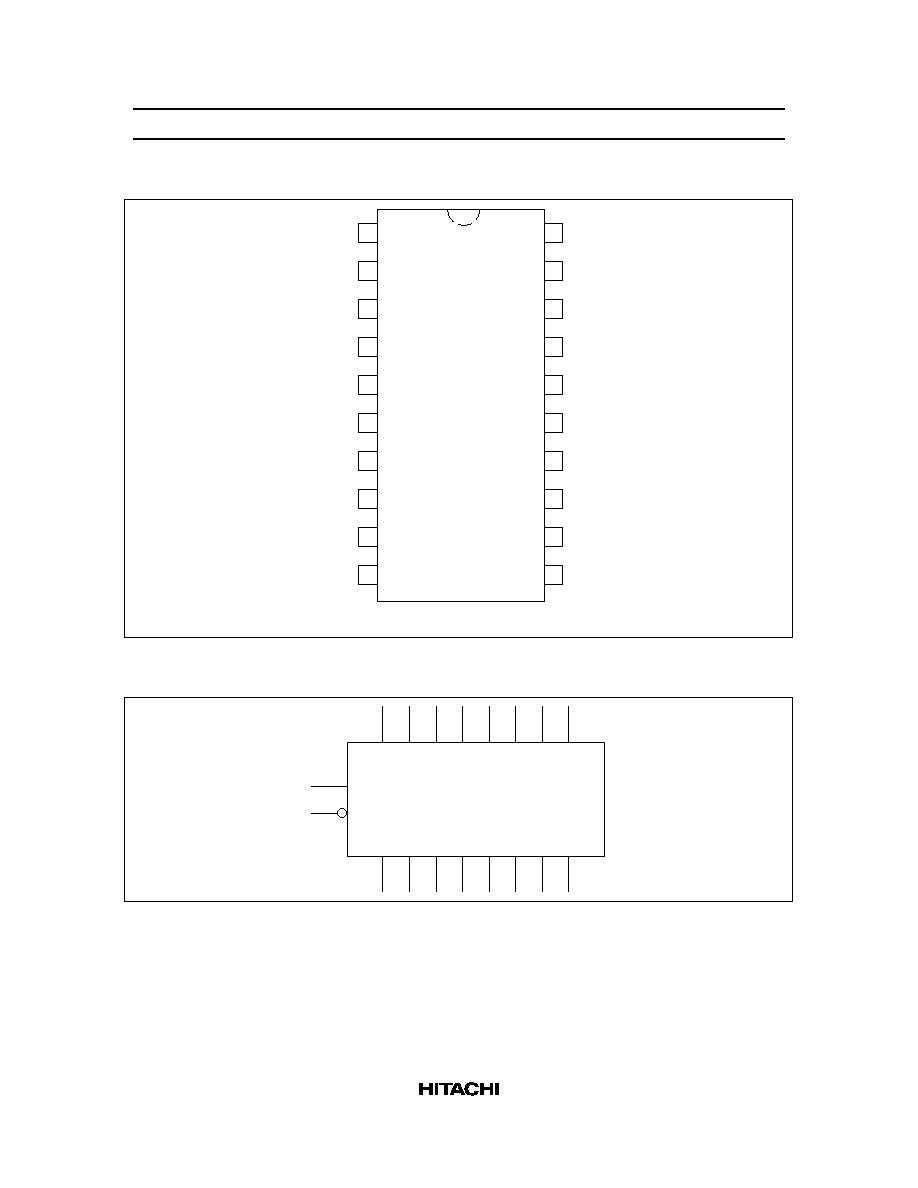

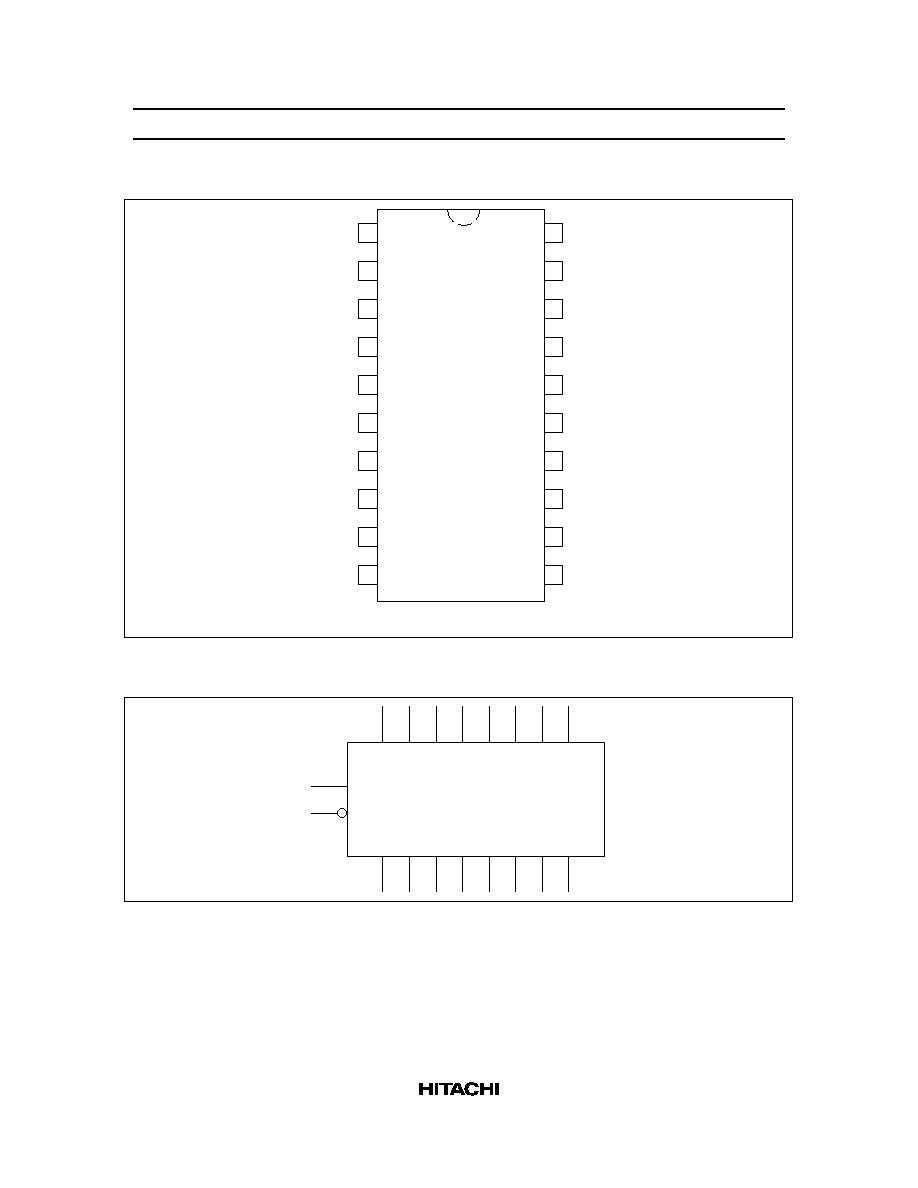

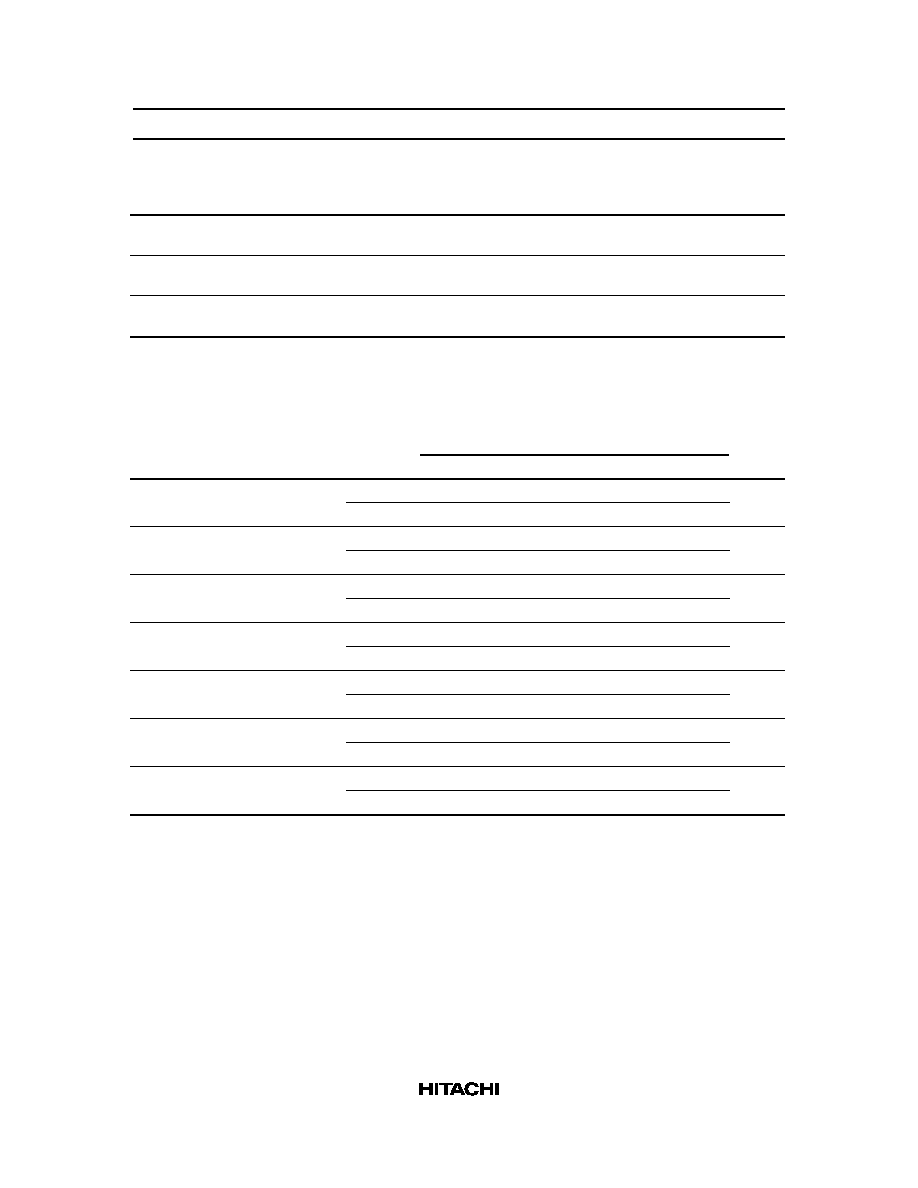

Pin Arrangement

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20 V

CC

O

7

D

7

D

6

O

6

O

5

OE

O

0

D

0

D

1

O

1

O

2

D

2

D

3

O

3

Gnd

D

5

D

4

O

4

CP

(Top view)

Logic Symbol

CP

OE

D

0

D

2

D

4

D

6

D

3

D

5

D

7

D

1

O

0

O

2

O

4

O

6

O

3

O

5

O

7

O

1

Pin Names

D

0

≠ D

7

Data Inputs

CP

Clock Pulse Input

OE

3-State Output Enable Input

O

0

≠ O

7

3-State Outputs

HD74AC374/HD74ACT374

3

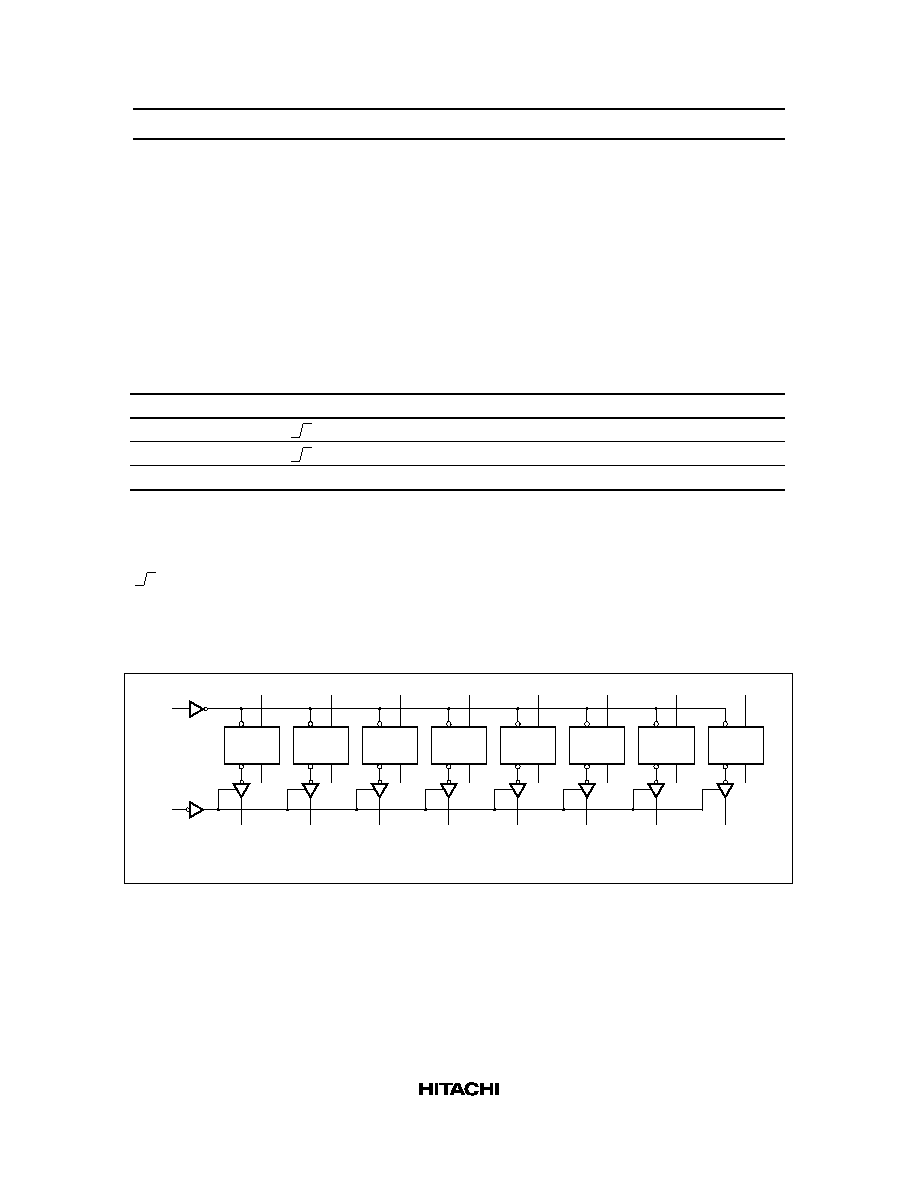

Functional Description

The HD74AC374/HD74ACT374 consists of eight edge-triggered flip-flops with individual D-type inputs

and 3-state true outputs. The buffered clock and buffered Output Enable are common to all flip-flops. The

eight flip-flops will store the state of their individual D inputs that meet the setup and hold time

requirements on the Low-to-High Clock (CP) transition. With the Output Enable (

OE) Low, the contents

of the eight flip-flops are available at the outputs. When the

OE is High, the outputs go to the high

impedance state. Operation of the

OE input does not affect the state of the flip-flops.

Truth Table

Inputs

Outputs

D

n

CP

OE

O

n

H

L

H

L

L

L

X

X

H

Z

H :

High Voltage Level

L

:

Low Voltage Level

X :

Immaterial

Z

:

High Impedance

: Low-to-High Transition

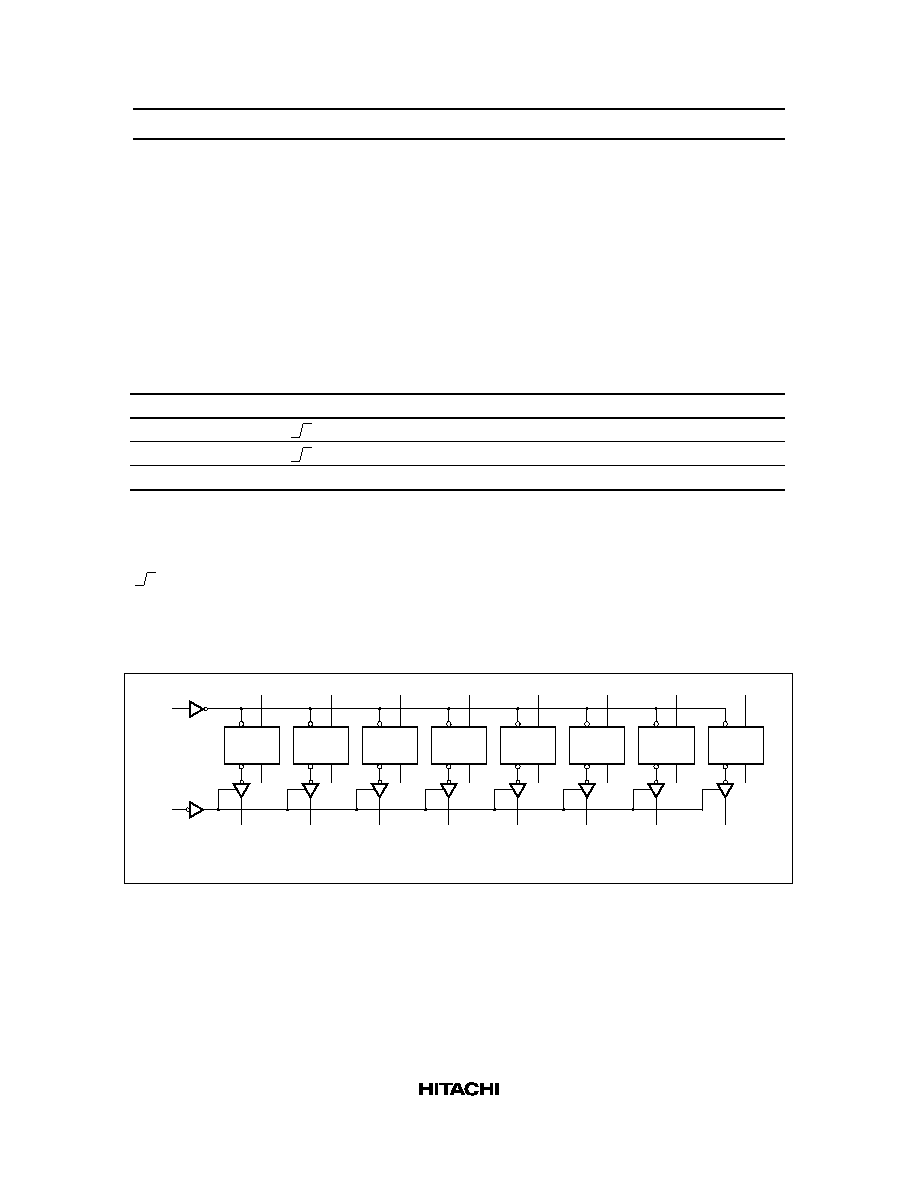

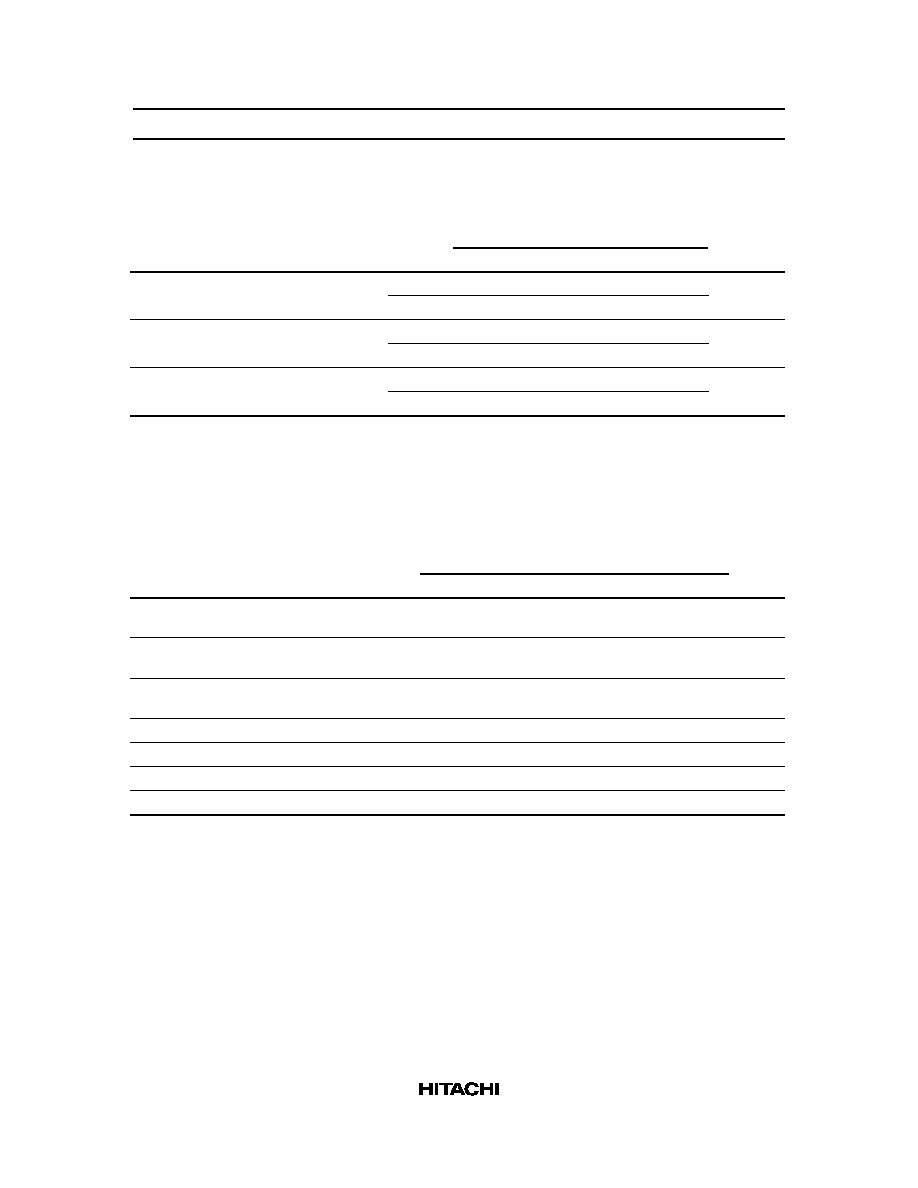

Logic Diagram

O

7

D

7

CP

Q

Q

D

O

6

D

6

CP

Q

Q

D

O

5

D

5

CP

Q

Q

D

O

4

D

4

CP

Q

Q

D

O

3

D

3

CP

Q

Q

D

O

2

D

2

CP

Q

Q

D

O

1

D

1

CP

Q

Q

D

O

0

D

0

CP

OE

CP

Q

Q

D

Please note that this diagram is provided only for the understanding of logic operations and should not be

used to estimate propagation delays.

HD74AC374/HD74ACT374

4

DC Characteristics (unless otherwise specified)

Item

Symbol

Max

Unit

Condition

Maximum quiescent supply current

I

CC

80

µ

A

V

IN

= V

CC

or ground, V

CC

= 5.5 V,

Ta = Worst case

Maximum quiescent supply current

I

CC

8.0

µ

A

V

IN

= V

CC

or ground, V

CC

= 5.5 V,

Ta = 25

∞

C

Maximum I

CC

/input (HD74ACT374)

I

CCT

1.5

mA

V

IN

= V

CC

≠ 2.1 V, V

CC

= 5.5 V,

Ta = Worst case

AC Characteristics: HD74AC374

Ta = +25

∞

C

C

L

= 50 pF

Ta = ≠40

∞

C to +85

∞

C

C

L

= 50 pF

Item

Symbol

V

CC

(V)*

1

Min

Typ

Max

Min

Max

Unit

Maximum clock

f

max

3.3

60

110

--

60

--

MHz

frequency

5.0

100

155

--

100

--

Propagation delay

t

PLH

3.3

1.0

11.0

13.5

1.0

15.5

ns

CP to O

n

5.0

1.0

8.0

9.5

1.0

10.5

Propagation delay

t

PHL

3.3

1.0

10.0

12.5

1.0

14.0

ns

CP to O

n

5.0

1.0

7.0

9.0

1.0

10.0

Output enable time

t

PZH

3.3

1.0

9.5

11.5

1.0

13.0

ns

5.0

1.0

7.0

8.5

1.0

9.5

Output enable time

t

PZL

3.3

1.0

9.0

11.5

1.0

13.0

ns

5.0

1.0

6.5

8.5

1.0

9.5

Output disable time

t

PHZ

3.3

1.0

10.5

12.5

1.0

14.5

ns

5.0

1.0

8.0

11.0

1.0

12.5

Output disable time

t

PLZ

3.3

1.0

8.0

11.5

1.0

12.5

ns

5.0

1.0

6.5

8.5

1.0

10.0

Note:

1. Voltage Range 3.3 is 3.3 V

±

0.3 V

Voltage Range 5.0 is 5.0 V

±

0.5 V

HD74AC374/HD74ACT374

5

AC Operating Requirements: HD74AC374

Ta = +25

∞

C

C

L

= 50 pF

Ta = ≠40

∞

C

to +85

∞

C

C

L

= 50 pF

Item

Symbol

V

CC

(V)*

1

Typ

Guaranteed Minimum

Unit

Setup time, HIGH or LOW

t

su

3.3

2.0

5.5

6.0

ns

D

n

to CP

5.0

1.0

4.0

4.5

Hold time, HIGH or LOW

t

h

3.3

≠1.0

1.0

1.0

ns

D

n

to CP

5.0

≠4.0

1.5

1.5

CP pulse width, HIGH or LOW t

w

3.3

4.0

5.5

6.0

ns

5.0

2.5

4.0

4.5

Note:

1. Voltage Range 3.3 is 3.3 V

±

0.3 V

Voltage Range 5.0 is 5.0 V

±

0.5 V

AC Characteristics: HD74ACT374

Ta = +25

∞

C

C

L

= 50 pF

Ta = ≠40

∞

C to +85

∞

C

C

L

= 50 pF

Item

Symbol

V

CC

(V)*

1

Min

Typ

Max

Min

Max

Unit

Maximum clock

frequency

f

max

5.0

100

160

--

90

--

MHz

Propagation delay

CP to O

n

t

PLH

5.0

1.0

8.5

10.0

1.0

11.5

ns

Propagation delay

CP to O

n

t

PHL

5.0

1.0

8.0

9.5

1.0

11.0

ns

Output enable time

t

PZH

5.0

1.0

8.0

9.5

1.0

10.5

ns

Output enable time

t

PZL

5.0

1.0

8.0

9.0

1.0

10.5

ns

Output disable time

t

PHZ

5.0

1.0

8.5

11.5

1.0

12.5

ns

Output disable time

t

PLZ

5.0

1.0

7.0

8.5

1.0

10.0

ns

Note:

1. Voltage Range 5.0 is 5.0 V

±

0.5 V