HM5164805F Series

HM5165805F Series

64 M EDO DRAM (8-Mword

◊

8-bit)

8 k Refresh/4 k Refresh

ADE-203-1057B (Z)

Rev. 2.0

Nov. 30, 1999

Description

The Hitachi HM5164805F Series, HM5165805F Series are 64M-bit dynamic RAMs organized as

8,388,608-word

◊

8-bit. They have realized high performance and low power by employing CMOS process

technology. HM5164805F Series, HM5165805F Series offer Extended Data Out (EDO) Page Mode as a

high speed access mode. They have the package variation of standard 32-pin plastic SOJ and standard 32-

pin plastic TSOPII.

Features

∑

Single 3.3 V supply: 3.3 V

±

0.3 V

∑

Access time: 50 ns/60 ns (max)

∑

Power dissipation

Active: 414 mW/378 mW (max) (HM5164805F Series)

: 486 mW/414 mW (max) (HM5165805F Series)

Standby : 1.8 mW (max) (CMOS interface)

: 1.1 mW (max) (L-version)

∑

EDO page mode capability

∑

Refresh cycles

RAS-only refresh

8192 cycles /64 ms (HM5164805F, HM5164805FL)

4096 cycles /64 ms (HM5165805F, HM5165805FL)

CBR/Hidden refresh

4096 cycles /64 ms (HM5164805F, HM5164805FL, HM5165805F, HM5165805FL)

HM5164805F Series, HM5165805F Series

2

∑

4 variations of refresh

RAS-only refresh

CAS-before-RAS refresh

Hidden refresh

Self refresh (L-version)

∑

Battery backup operation (L-version)

Ordering Information

Type No.

Access time

Package

HM5164805FJ-5

HM5164805FJ-6

50 ns

60 ns

400-mil 32-pin plastic SOJ

(CP-32DC)

HM5164805FLJ-5

HM5164805FLJ-6

50 ns

60 ns

HM5165805FJ-5

HM5165805FJ-6

50 ns

60 ns

HM5165805FLJ-5

HM5165805FLJ-6

50 ns

60 ns

HM5164805FTT-5

HM5164805FTT-6

50 ns

60 ns

400-mil 32-pin plastic TSOP II

(TTP-32DC)

HM5164805FLTT-5

HM5164805FLTT-6

50 ns

60 ns

HM5165805FTT-5

HM5165805FTT-6

50 ns

60 ns

HM5165805FLTT-5

HM5165805FLTT-6

50 ns

60 ns

HM5164805F Series, HM5165805F Series

3

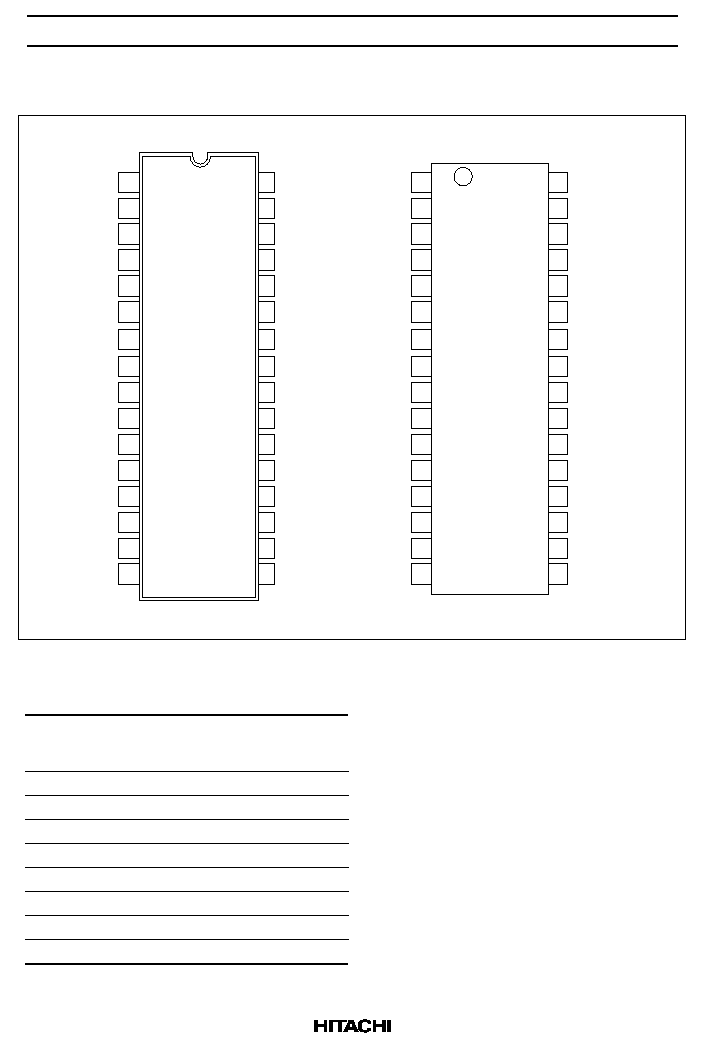

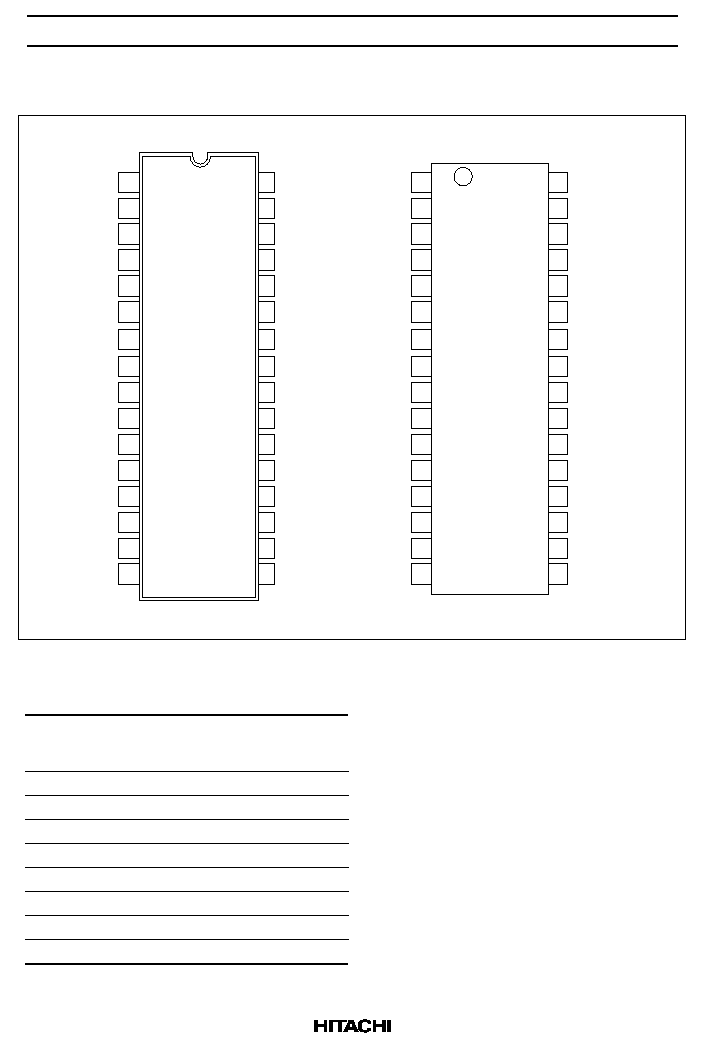

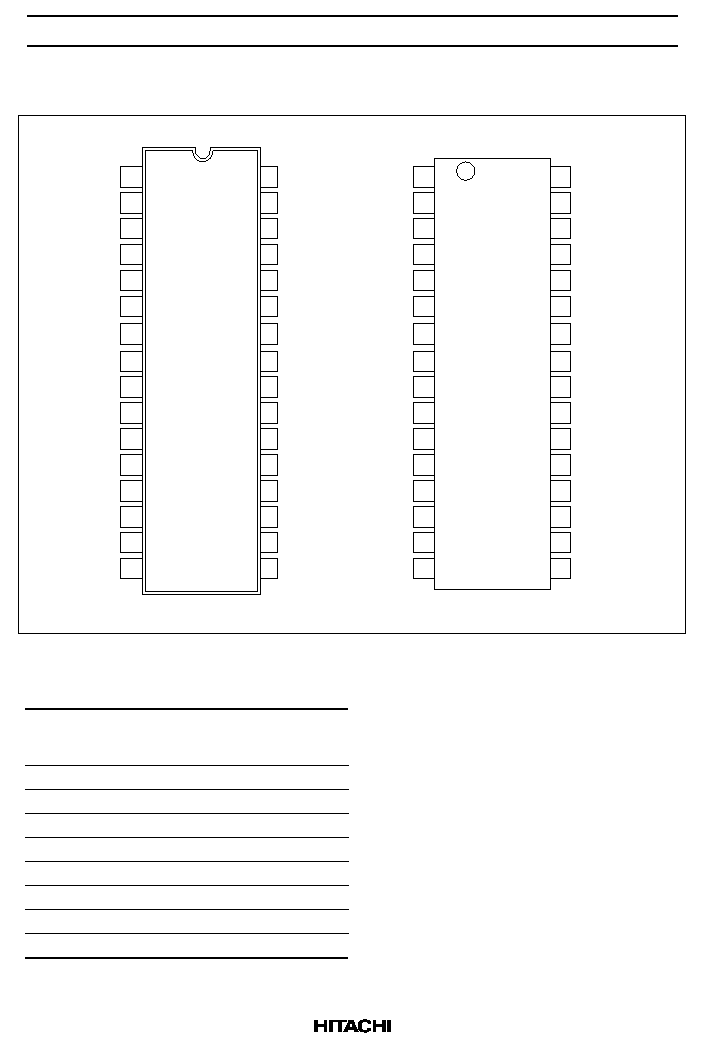

Pin Arrangement (HM5164805F Series)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

(Top view)

(Top view)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

CC

I/O0

I/O1

I/O2

I/O3

NC

V

CC

WE

RAS

A0

A1

A2

A3

A4

A5

V

CC

V

CC

I/O0

I/O1

I/O2

I/O3

NC

V

CC

WE

RAS

A0

A1

A2

A3

A4

A5

V

CC

V

I/O7

I/O6

I/O5

I/O4

V

CAS

OE

A12

A11

A10

A9

A8

A7

A6

V

SS

SS

SS

V

I/O7

I/O6

I/O5

I/O4

V

CAS

OE

A12

A11

A10

A9

A8

A7

A6

V

SS

SS

SS

32-pin TSOP

32-pin SOJ

Pin Description

Pin name

Function

A0 to A12

Address input

-- Row/Refresh address A0 to A12

-- Column address

A0 to A9

I/O0 to I/O7

Data input/output

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

OE

Output enable

V

CC

Power supply

V

SS

Ground

NC

No connection

HM5164805F Series, HM5165805F Series

4

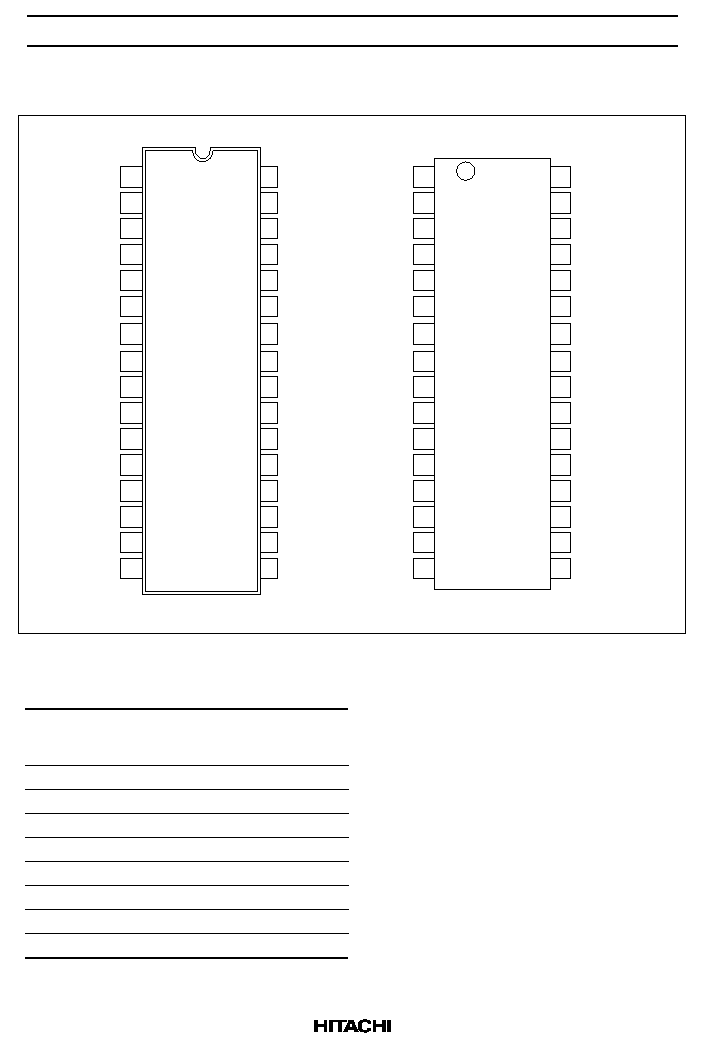

Pin Arrangement (HM5165805F Series)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

32-pin TSOP

32-pin SOJ

(Top view)

(Top view)

V

I/O7

I/O6

I/O5

I/O4

V

CAS

OE

NC

A11

A10

A9

A8

A7

A6

V

SS

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

CC

I/O0

I/O1

I/O2

I/O3

NC

V

CC

WE

RAS

A0

A1

A2

A3

A4

A5

V

CC

V

CC

I/O0

I/O1

I/O2

I/O3

NC

V

CC

WE

RAS

A0

A1

A2

A3

A4

A5

V

CC

SS

V

I/O7

I/O6

I/O5

I/O4

V

CAS

OE

NC

A11

A10

A9

A8

A7

A6

V

SS

SS

SS

Pin Description

Pin name

Function

A0 to A11

Address input

-- Row/Refresh address A0 to A11

-- Column address

A0 to A10

I/O0 to I/O7

Data input/output

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

OE

Output enable

V

CC

Power supply

V

SS

Ground

NC

No connection

HM5164805F Series, HM5165805F Series

5

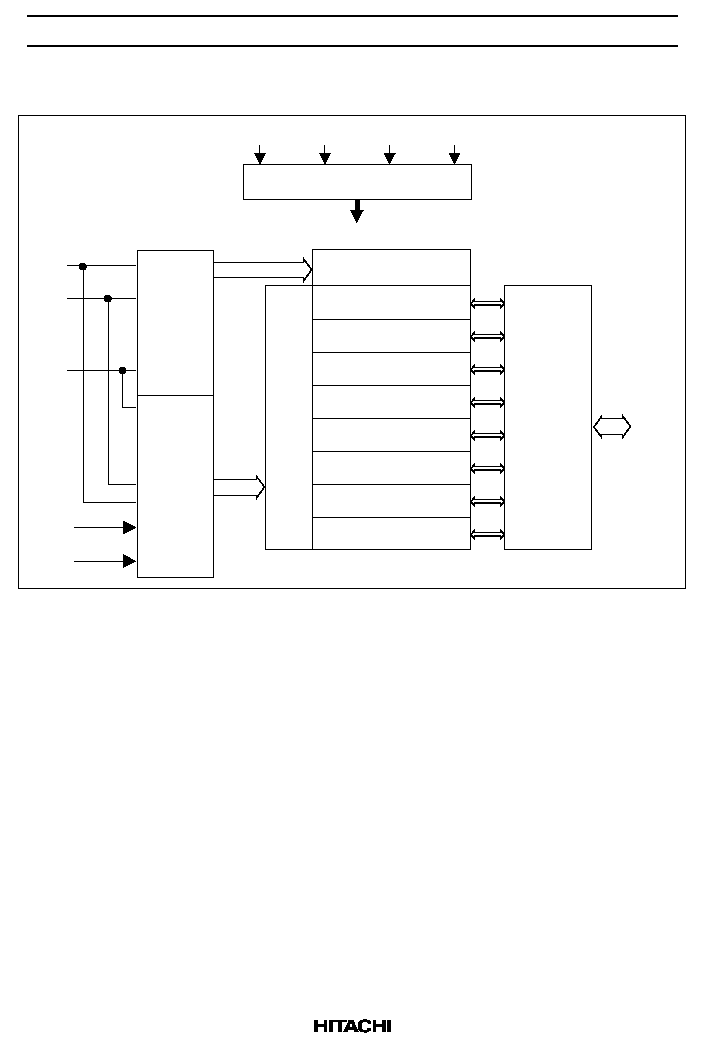

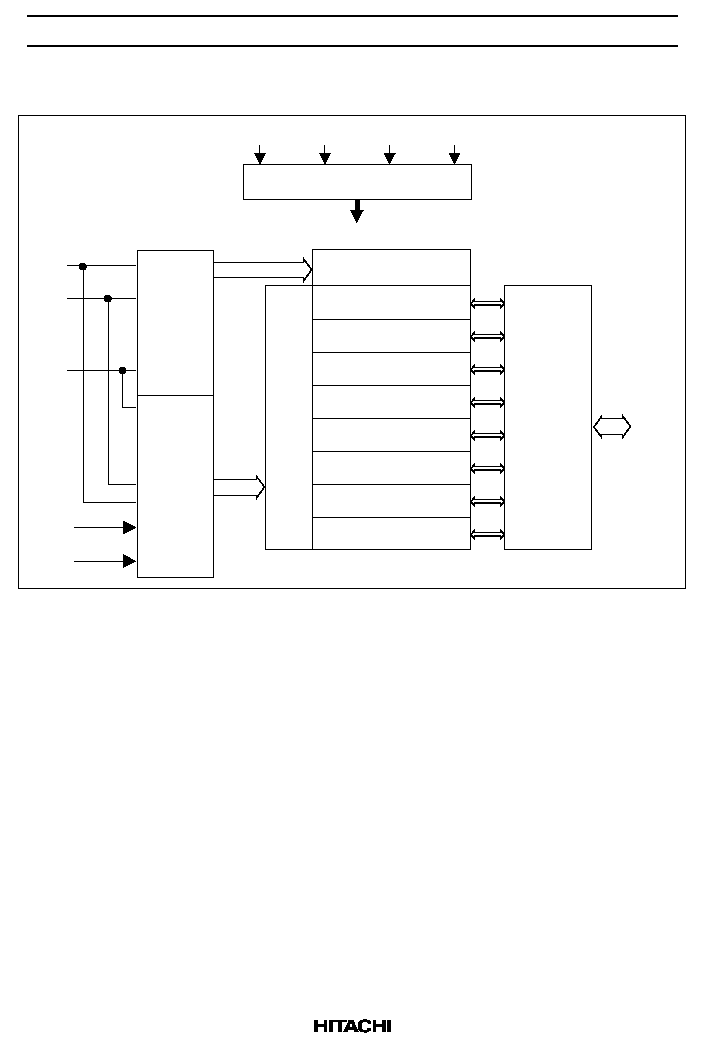

Block Diagram (HM5164805F Series)

∑

∑

∑

∑

∑

∑

A0

A1

to

A9

Timing and control

Column

address

buffers

Row

address

buffers

I/O buffers

I/O0

to

I/O7

RAS

CAS

WE

OE

Column decoder

Row decoder

8M array

8M array

8M array

8M array

8M array

8M array

8M array

8M array

A10

to

A12